# Fabrication of Extremely Smooth Nanostructures Using Anisotropic Etching

by

Andrea Elke Franke

Submitted to the

Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements

for the degree of

Master of Science

at the

Massachusetts Institute of Technology

May, 1997

(c) 1997 Massachusetts Institute of Technology all rights reserved.

| Signature of Author |                                                           |

|---------------------|-----------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science |

|                     | May, 1997                                                 |

| Certified by        | <del></del>                                               |

|                     | Professor Henry I. Smith                                  |

|                     | Keithly Professor of Electrical Engineering, MIT          |

|                     | Thesis Supervisor                                         |

| Accepted by         |                                                           |

|                     | Arthur C. Smith                                           |

Chair, Department Committee on Graduate Students

JUL 2 4 1997 F ARCHIVES

MADSACHUSETTS INSTITUTE OF TECHNOLOGY

LIBRARIES

# Fabrication of Extremely Smooth Nanostructures Using Anisotropic Etching

by

#### Andrea Elke Franke

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Master of Science

#### Abstract

Anisotropic etching has the potential to produce structures in silicon with extremely smooth surfaces, possibly even atomically smooth. Anisotropic etchants etch in <111> directions orders of magnitude more slowly than in other directions. Hence, etching virtually ceases when the etch front encounters a {111} plane. Any surface protrusion that exposes a plane other than a {111} is quickly etched. Structures defined by extremely smooth {111} planes result. An application of this etching technique is the fabrication of 200 nm period arrays of inverted pyramids in (100) silicon substrates. These substrates promise to reduce defect density in lattice mismatched epilayers. Also, anisotropic etching can be used to improve efficiency of grazing incidence, blazed, X-ray diffraction gratings.

Thesis Supervisor: Henry I. Smith

Title: Keithley Professor of Electrical Engineering, MIT

# Table of Contents

| 1. Anisotropic Etching                                         | 5            |

|----------------------------------------------------------------|--------------|

| 2. Epitaxy of Lattice Mismatched Semiconductors                |              |

| on Silicon                                                     | 11           |

| 2.0 Introduction                                               | <b>. 1</b> 1 |

| 2.1 Epitaxy on (100) Silicon: Dislocations and Antiphase Domai | ns 1J        |

| 2.2 Epitaxy on (111) Silicon: Stacking Faults and Twin Boundar | ries 18      |

| 2.3 Epitaxy on Sawtooth Patterned Silicon                      |              |

| 2.4 Epitaxy on Inverted Pyramid Patterned Silicon              |              |

| 3. Design of Inverted Pyramid Process                          | 21           |

| 3.0 Introduction                                               |              |

| 3.1Interferometric Lithography                                 |              |

| 3.2 Titanium Evaporation                                       |              |

| 3.3 RIE of ARC                                                 | 26           |

| 3.4 Cr Evaporation                                             |              |

| 3.5 RCA Clean                                                  | 30           |

| 3.6 RIE of SiN                                                 | 31           |

| 3.7 Cr Etch, KOH Etch of Si, HF Etch of SiN                    |              |

| 4. Grazing Incidence, Blazed, X-ray Diffraction                |              |

| Gratings                                                       |              |

| 4.0 Introduction                                               |              |

| 4.1 Diffraction Gratings                                       | 37           |

| 4.2 Ruled Gratings                                             | <b>. 3</b> 8 |

| 4.3 Interferometric Lithography and Ion Etching                | 39           |

| 4.4 Interferometric Lithography and Anisotropic Etching        | 40           |

| 5. Design of Anisotropically Etched Grating   |

|-----------------------------------------------|

| Process                                       |

| 5.0 Introduction                              |

| 5.1 Interferometric Lithography               |

| 5.2, 5.3 RIE of SiO2, ARC, and SiN, RCA Clean |

| 5.4 KOH Etch Silicon                          |

| 5.5 Cr Evaporation and HF Etch of SiN         |

| 5.6 AFM Analysis of Gratings                  |

| 6. Future Work, Other Applications            |

| Appendix A. Recipe for Inverted Pyramid       |

| Process                                       |

| Appendix B. Recipe for X-ray Diffraction      |

| Gratings                                      |

| Appendix C. Measurement of Anisotropically    |

| Etched Grating Efficiency                     |

| Toured Grading Limitory                       |

## Chapter 1

## **Anisotropic Etching**

Anisotropic etching has the potential to produce structures in silicon with extremely smooth surfaces, possibly even atomically smooth.

Applications of anisotropically etched structures exist in crystal growth, optics, biology, micromachined sensors, and possibly other fields. In this chapter the behavior of anisotropic etching, basic crystallography, and alignment issues will be discussed.

High quality silicon crystal is easily available due to its importance in integrated circuits. Anisotropic etching takes advantage of this high quality crystallinity by etching in <111> crystal directions orders of magnitude more slowly than others. This means that any step or protrusion above a {111} crystal plane will quickly be etched, leaving behind a smooth surface bounded by a {111} plane.

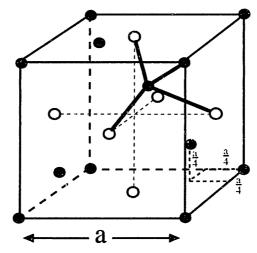

This difference in etch rates can be explained in part by studying the silicon crystal structure. Silicon is of the diamond cubic crystal structure (Figure 1.1). Silicon atoms are at each corner of the cube (black), at the center of each cube face (white), and four silicon atoms (gray) are 1/4 of a lattice constant, 'a', in each direction from a corner atom. Each silicon atom has four nearest neighbors to which it is most strongly bonded. In the front upper right-hand corner of Figure 1.1, the four bonds are indicated with thick black lines. The diamond cubic structure can be thought of as two interpenetrating face centered cubic (fcc) sublattices. The first sublattice is the black and white atoms and the second is the gray atoms in Figure 1.1.

Figure 1.1 The diamond cubic unit cell with lattice constant, 'a'.

As with all crystals, silicon consists of the unit cell repeated through three dimensional space. This results in considerable symmetry. For example, consider rotating the silicon unit cell, or a crystal containing many unit cells, 180° about a unit cell edge. There will be no noticeable difference. Hence, the origin can be the corner of any unit cell, and axes can be chosen along any three edges of a unit cell which intersect the origin.

Crystal planes are defined with three coordinates, called Miller indices. Planes are described by first locating the intercepts of the plane along the x, y, and z axes in a unit cell. The Miller indices are obtained by taking the reciprocals of the intercepts, and if necessary multiplying each by the same integer to give integer indices (Figure 1.2). Using this method, planes which do not have an intercept with an axis will have a zero for the Miller index corresponding to that axis. Consider the (1 0 2) plane. It intercepts the x, y, and z axes at 1, infinity, and 1/2, respectively. Taking the reciprocals gives (1 0 2).

Figure 1.2 Examples of crystal planes and directions.

Similarly, to determine the indices for a direction, projections of the direction in a unit cell on the axes are located, and if necessary are multiplied by an integer to give integer indices. The projections of the [1 0 2] direction in

the unit cell on the x, y, and z axes are 1/2, 0, and 1, respectively. Multiplying by two gives [1 0 2].

Specific planes are labeled (h k l), and families of planes are  $\{h \ k \ l\}$ . Specific directions are labeled  $[h \ k \ l]$ , and families of directions are  $\{h \ k \ l\}$ . For example, the planes (1 0 0) and (0 0  $\overline{1}$ ) are in the  $\{1 \ 0 \ 0\}$  family which means that they are equivalent planes whose labelling depends only on the choice of origin and axes. A bar over an index indicates a plane which intercepts a negative portion of an axis, or a direction whose projection is on a negative portion of an axis. In cubic crystals such as silicon the direction  $[a \ b \ c]$  is always perpendicular to the plane with the same indices,  $(a \ b \ c)$ .

The {111} planes in silicon have the highest atomic lattice packing density, or number of atoms per area. The spacing between adjacent, parallel {111} planes is the greatest, and there is the least number of bonds between adjacent, parallel {111} planes. The bond densities are 1:0.71:0.58 between adjacent, parallel planes for the {100}:{110}:{111}. The lower the density of bonds between adjacent, parallel planes, the more bonds there are between atoms in the plane, and so the more difficult to remove atoms. However, etch rates as selective as 300:600:1 for the <100>:<110>:<111> directions have been found<sup>4</sup>. The differences in etch rates can not be explained solely by the differences in bond densities. It has been proposed that the high selectivity is a result of selective passivation of the {111} planes. The {111} planes of silicon are known to oxidize more quickly than other planes. This oxide could be protecting the {111} planes during etching. The fact that the etch rates of {111} silicon planes and silicon dioxide have been found to be nearly equal supports this theory.

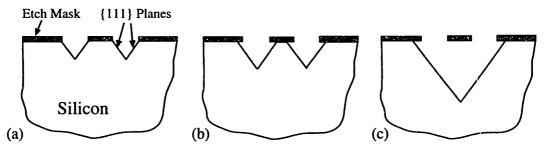

Anisotropic etching proceeds as depicted in Figure 1.3. In this example a (100) wafer is used. Etching proceeds quickly until the {111} planes are encountered (Figure 1.3a). The etch rate in the <111> directions is small yet does allow for undercutting of the mask (Figure 1.3b). If the etching is allowed to proceed for a long enough period of time, parts of the mask can be completely undercut (Figure 1.3c).

Figure 1.3 As anisotropic etching proceeds, the etch mask is slowing undercut. This figure was adapted from a figure by Peterson<sup>5</sup>.

For most anisotropic etching applications careful alignment of the etch mask to the crystallographic planes is required. As discussed by Kendall<sup>4</sup>, misalignment results in altered etch rates, and surface steps on etch facets (Figure 1.4). As the misalignment angle,  $\Theta$ , increases, the density of surface steps on the etched facets increases. Edge roughness of the etch mask produces similar surface steps on etch facets and is discussed further in Chapter 5.

Figure 1.4 Misalignment of the etch mask results in surface steps on the etched facets. This figure is from Kendall<sup>4</sup>.

There are several solutions which can be used as anisotropic etchants<sup>6-10</sup>. Potassium hydroxide, KOH, was chosen for the following work because the etch rate selectivity is the highest. This results in extremely smooth facets. Two applications of anisotropic etching were investigated: arrays of inverted pyramids and grazing incidence, blazed, X-ray diffraction gratings. The arrays of inverted pyramids promise to improve the crystal quality of epitaxial layers of other semiconductors. The X-ray diffraction gratings are shown to provide enhanced efficiency by a factor of two in comparison to currently available gratings, and are more reliably fabricated.

- G. Kaminsky. Micromachining of silicon mechanical structures. J. Vac. Sci. Technol. B., vol. 3, no. 4, pp. 1015-1024, 1985.

- 2 Kenneth E. Bean. Anisotropic etching of silicon. *IEEE Transactions on Electron Devices*, vol. ED-25, no. 10, pp. 1185-1192, 1978.

- 3 Ernest Bassous. Fabrication of novel three-dimensional microstructures by the anisotropic etching of (100) and (110) silicon. *IEEE Transactions on Electron Devices*, vol. ED-25, no. 10, pp. 1178-1185, 1978.

- Don L. Kendall. Vertical etching of silicon at very high aspect ratios. *Ann. Rev. Mater. Sci.*, vol. 9, pp. 373-403, 1979.

- Kurt E. Petersen. Silicon as a mechanical material. *Proceedings of the IEEE*, vol. 70, no. 5, 1982.

- 6 H. Seidel, L. Csepregi, A. Heuberger, and H. Baumgartel. Anisotropic etching of crystalline silicon in alkaline solutions, I. Orientation Dependence and Behavior of Passivation Layers. *J. Electrochem. Soc.*, vol. 137, no. 11, pp. 3626-3632, 1990.

- 7 H. Seidel, L. Csepregi, A. Heuberger, and H. Baumgartel. Anisotropic etching of crystalline silicon in alkaline solutions, II. Influence of Dopants. J. Electrochem. Soc., vol. 137, no. 11, pp. 3612-3626

- 8 H. Linde and L. Austin. Wet silicon etching with aqueous amine gallates. J. Electrochem. Soc., vol. 139, no. 4, pp. 1170-1174, 1992.

- 9 Osamu Tabata, Ryouji Asahi, Hirofumi Funabashi. Anisotropic etching of silicon in (CH<sub>3</sub>)<sub>4</sub>NOH solutions. 1991 International Conference on Solid State Sensors and Actuators, pp. 811-814, 1991.

- 10 U. Schnakenberg, W. Benecke, P. Lange. TMAHW etchants for silicon micromachining. 1991 International Conference on Solid State Sensors and Actuators, pp. 815-818, 1991.

## Chapter 2

Epitaxy of Lattice Mismatched Semiconductors on Silicon

#### 2.0 Introduction

There is great interest in SiGe alloys<sup>1-5</sup>, GaAs<sup>6-9</sup>, and InP<sup>10-12</sup> because of their higher mobilities and/or higher bandgaps compared to silicon. These properties indicate the possibility of higher speed electronic devices and smaller wavelength optical devices. Epitaxially growing these materials on silicon would provide larger wafer areas and would be less expensive than using bulk grown wafers. High density silicon circuitry could be combined with high speed and optical devices on the same substrate, thereby eliminating interchip capacitances and increasing speed.

However, the lattice mismatch of  $\mathrm{Si}_{1\text{-x}}\mathrm{Ge}_x$  on silicon varies from 0 to 4.2% as x varies from 0 to 1. GaAs and InP on silicon have lattice mismatches of 4.1% and 8.1% respectively. This leads to dislocations, stacking faults, twin boundaries, and surface roughness in the epitaxial films. Thermal expansion coefficients for Si, Ge, GaAs, and InP are  $2.6\times10^{-6}$  K<sup>-1</sup>,  $5.8\times10^{-6}$  K<sup>-1</sup>,  $6.86\times10^{-6}$  K<sup>-1</sup>, and  $4.75\times10^{-6}$  K<sup>-1</sup> respectively<sup>13</sup>. Thermal cycling introduces defects since the thermal expansion coefficients of the epitaxial films are different than that of silicon. Finally, epitaxy of polar semiconductors, GaAs and InP, on Si, a nonpolar semiconductor, leads to anti-phase domains.

## 2.1 Epitaxy on (100) Silicon: Dislocations and Antiphase Domains

In order to combine high speed electronic devices or optical devices with conventional silicon circuitry on the same substrate, (100) silicon wafers must be used for epitaxy. Epilayers on (100) silicon tend to have high dislocation densities which negatively affect the epitaxial film quality in three ways. First, they form nonradiative recombination centers. Second, impurities diffuse more easily along dislocations than in perfect crystal, and this can allow silicon to diffuse into the epilayer and cause unintentional doping<sup>8</sup>. Third, the dislocations greatly decrease carrier mobility<sup>3</sup>. The dislocations are due to lattice mismatch, and the strain that the mismatch causes in the epilayer. Strain is accommodated by elastic deformation, if the epilayer is

below a critical thickness or if the growth area is small enough. Requiring that the film is thinner than the critical thickness or that the growth areas are small is too limiting for most applications. However, dislocations that do not thread to the surface of the epilayer do not have deleterious effects.

There are two different kinds of dislocations. Type I dislocations have a Burgers vector of 1/2<011>, in the (100) plane, and a dislocation line in the (100) plane. Type II dislocations have a Burgers vector of 1/2<110>, 45° to the (100) plane, and a dislocation line 60° to the (100) plane. Dislocations tend to slip along planes that contain both their Burgers vector and their dislocation line, so only type II dislocations thread to the epilayer surface. Type I dislocations tend to be generated at atomic scale steps on the silicon surface. Misorienting the crystallographic planes by a few degrees, so that the wafer surface is not exactly the (100) plane, results in more steps. This leads to more type I dislocations, and dislocation densities at the epitaxial surface that are 2-3 orders of magnitude less than epilayers grown on exactly oriented (100) wafers<sup>8</sup>. However, misorienting the silicon wafer degrades devices.

Another approach to reduce defect density is to anneal the epilayer at high temperature for a long period of time or to use rapid thermal annealing (RTA). Type I dislocations are energetically favorable to type II, and so annealing leads to the reduction of type II dislocations. Long anneal times tend to increase interdiffusion and unintentional doping. RTA does not have noticeable diffusion problems<sup>8</sup>, but annealing at high temperatures is damaging to silicon devices that may have previously been fabricated on other parts of the wafer. Annealing relaxes strain which can not be tolerated when attempting to grow strained layers for mobility enhancement and bandgap engineering. Also, large temperature gradients can introduce more defects due to thermal expansion mismatches<sup>14</sup>.

Another problem with epitaxy on (100) silicon is antiphase boundaries (APB) which reduce mobility<sup>6</sup>. APBs are charged structural defects made of cation-cation and anion-anion bonds which act as acceptors and donors. There tends to be an equal number of these bonds, and so the epilayer acts like a highly compensated semiconductor. Silicon is a nonpolar semiconductor because both fcc sub-lattices of the diamond structure are occupied by silicon atoms. GaAs and InP are polar because each fcc sublattice is exclusively occupied by one kind of atom. Antiphase boundaries occur between domains where atoms switch sublattices. Growth of polar semiconductors on (100)

silicon substrates consists of alternating monolayers of cation and anion atoms. Nonuniform surface coverage of the first epitaxial monolayer and monoatomic steps on the silicon surface lead to antiphase domains in the polar epilayer. Beginning growth by exposing the substrate to only one species can provide uniform surface coverage of the first monolayer. Misorienting the silicon substrate and high temperature annealing tend to increase the formation of double atomic steps on the silicon surface because these are energetically favorable to single atomic steps. Double atomic steps do not lead to APBs, but neither substrate misorientation nor high temperature annealing are desirable for integrated circuit fabrication.

### 2.2 Epitaxy on (111) Silicon: Stacking Faults and Twin Boundaries

Although epitaxy on (111) silicon is not compatible with VLSI technology, it provides some interesting insights. The easy slip and twinning planes are {111} planes, because the spacing between adjacent, parallel {111} planes is greatest and the Peierls barrier to dislocation motion is the lowest. With (100) wafers there are no {111} planes parallel to the epilayer interface, and there are four {111} planes that intersect the epilayer surface at 54.7°. (111) wafers have one {111} plane parallel to the epilayer interface, and three planes that intersect the epilayer surface at 70.5°.

The dislocation density in InP epilayers on (100) silicon is about  $10^8 \, \mathrm{cm}^{-2}$ , and is an order of magnitude less when grown on (111) silicon  $^{12}$ . High resolution TEM of InP epilayers on (111) silicon performed by Krost et al.  $^{12}$  shows that the lattice mismatch is accommodated by twinning and dislocations near the interface. Twins appear to nucleate close to steps on the (111) silicon surface. At the steps, growth of a twinned or perfect (111) monolayer is equally likely. Above the twinned region the defect density is reduced, and the (111) planes inclined to the surface have the same orientation as in the silicon. Twins and stacking faults were still observed due to the three other {111} planes. However, the density was smaller than that in InP grown on (100) silicon. Stacking faults at the interface accommodated for the lattice mismatch of GaAs grown on (111) silicon  $^{14}$ . Another advantage of epitaxy on (111) silicon is that APBs do not form as long as nucleation is uniform and islands of growth do not form, because the growth surface has both cations and anions exposed.

#### 2.3 Epitaxy on Sawtooth Patterned Silicon

Several groups have tried to improve the crystal quality of epilayers by growing on sawtooth patterned silicon <sup>16-25</sup>. Unfortunately, there is a lot of variation between studies in wafer cleaning methods, growth parameters, patterning of the sawtooth structure, and techniques used to analyze the resulting epilayers (Table 2.1). This makes it difficult to compare nucleation, growth, and defect generation mechanisms and to conclude which is a repeatable process with optimal crystallinity. However, very promising improvements in epilayer defect density have been made in epilayers grown on sawtooth patterned silicon.

|                                        | Hashimoto et al.,<br>Refs. 16-18 | Sprung et al.,<br>Ref. 19 | Karam et al.,<br>Refs. 20-22                                                                                       | Krost et al.,<br>Refs. 14, 23-25                                                                        |

|----------------------------------------|----------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Off cut from (100)                     | 3° towards <011>                 | exactly (100)             | 2° towards [110]                                                                                                   | exactly (100)                                                                                           |

| Wafer Clean                            | HF solution, 1 min.              | none<br>mentioned         | trichoroethane,<br>acetone, methanol,<br>NH <sub>4</sub> OH:H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O,<br>HF | propanol, DI, H <sub>2</sub> SO <sub>4</sub> :<br>H <sub>2</sub> O:H <sub>2</sub> O <sub>2,</sub><br>HF |

| Wafer Anneal                           | 930°C, 5 min.                    | 850°C, 5 min              | 900°C, 5 min,<br>(MBE); 1000° C,<br>(MOCVD)                                                                        | none                                                                                                    |

| Buffer Growth<br>Temp, Thickness       | 450°C, 20 nm                     | 380°C, 50 nm              | 350°C, 40 nm,<br>(MBE); 400°C,<br>5-20 nm, (MOCVD)                                                                 | 425°C (GaAs); 400°C<br>(InP), 50nm                                                                      |

| Layer Growth                           | 750°C, MOCVD,<br>100 Torr        | 580°C, MBE                | 640°C, MBE;<br>600-700° C,<br>MOCVD                                                                                | 700°C, 500 mbar<br>(GaAs); 640°C, 20<br>mbar (InP), MOCVD                                               |

| Groove Width,<br>Width btw.<br>Grooves | 2 μm, 3 μm and<br>larger         | ~350 nm, ~50<br>nm        | ~170 nm, 30 nm                                                                                                     | 320 nm, 80 nm (GaAs);<br>200 nm, 200 nm (InP)                                                           |

Table 2.1 Comparison of epitaxy parameters on sawtooth patterned silicon

Hashimoto et. al.  $^{16-18}$  studied the epitaxy of  $Al_xGa_{1-x}As$  by MOCVD on silicon patterned with V grooves 2  $\mu m$  wide etched at 3, 5, 8, and 350  $\mu m$  intervals. SEM and scanning Auger electron spectroscopic (AES) measurements revealed that no epitaxy occurred on the {111} facets. It was proposed that the migration velocities of Ga and/or Al species were too high for nucleation to occur on {111} planes. Microscopic photoluminescence and Raman scattering measurements indicated that silicon originating from the

{111} facets contaminated the epilayers and that the epilayers were more stressed near the edge between the (100) and {111} planes, which implied a reduction of dislocation density near the edge. No more direct measurements of dislocation or other defect densities were made. The other research groups did not replicate this selective growth phenomenon 18-25, possibly because the growth temperatures in the other studies were lower which decreased the surface mobilities of the reactants.

Sprung et al. 19 grew GaAs by MBE on exactly oriented (100) silicon patterned with sawtooth grooves of 400 nm period. Unlike the Chong and Fonstad<sup>9</sup> study, reflected high-energy electron diffraction (RHEED) did not exhibit (2X2) reconstruction which indicates that surface oxide was desorbed after the sample was cleaned with a high temperature anneal. Yet both studies found (2X2) reconstruction after exposure to As. During the GaAs buffer growth the RHEED pattern was spotty, indicating that threedimensional GaAs islands were being grown. The epilayer grown on the buffer exhibited streaky RHEED patterns indicating (2X4) surface reconstruction which is characteristic of single domain GaAs. However, epilayers of GaAs grown on unpatterned (100) silicon had blurred RHEED patterns thought to be due to APBs and large defect densities. Nomarski phase contrast micrographs confirmed the absence of APBs in the epilayers grown on the patterned silicon and the presence of APBs in epilayers grown on the unpatterned silicon. The crystal structure was further examined by x-ray diffraction. The full width at half maximum (FWHM) of the rocking curve was 220" for the epilayer grown on patterned silicon, and 390" for the epilayer on the exactly oriented, unpatterned silicon. The 220" measurement is higher than measurements of epilayers homoepitaxially grown, yet is comparable to measurements of epilayers grown on off-cut (100) silicon substrates. An estimate of dislocation density can be made using the FWHM measurement  $^{26}$ :  $D \approx \beta^2/9b^2$ , where D is the dislocation density,  $\beta$  is the FWHM, and b is the Burgers vector of the dislocations. Using this estimate,  $D = 1 \times 10^7 \text{ cm}^{-2}$  for the epilayer grown on the sawtooth patterned silicon, and  $D \approx 6 \times 10^7$  cm<sup>-2</sup> for the epilayer grown on unpatterned silicon. These are promising results for integrating high speed electrical or optical GaAs devices with conventional silicon VLSI on the same substrate. However, little can be concluded about the nucleation and defect generation mechanisms from this study.

Karam et al.<sup>20-22</sup> grew GaAs by MBE and MOCVD on (100) silicon tilted 2° toward [110] and with 200 nm period sawtooth patterning. In earlier studies<sup>20-21</sup>, RHEED patterns during MBE growth indicated that the buffer layer was amorphous, and that heating to 600°C or above caused (2X4) surface reconstruction, which indicated crystallization of the buffer layer. For MOCVD growth, RTA or thermal cycle growth was used to eliminate the high density of twins and stacking faults that were observed in initial epilayers. Shallow (~0.8 µm above the GaAs/Si interface) and deep (~0.1 µm above the GaAs/Si interface) KOH etches of the MOCVD epilayers resulted in 10<sup>4</sup> cm<sup>-2</sup> and 10<sup>5</sup> cm<sup>-2</sup> etch pit densities respectively. These etch pit densities give a lower bound on the dislocation density. Plan view TEM produced an upper bound on the dislocation density of 10<sup>5</sup> cm<sup>-2</sup>. A thin interfacial amorphous SiO<sub>x</sub> layer between the silicon and the epilayer was believed to be the cause of the low dislocation densities. It was proposed that the initial GaAs growth senses the symmetry but not the precise positions of the silicon beneath the SiO<sub>x</sub>, and so the epilayer crystallizes without the mismatch induced defects. Another possibility mentioned was that growth was seeded through pinholes in the SiO<sub>x</sub>. More detailed TEM work was performed in Ref. 22, and no SiO<sub>x</sub> layer was seen in the micrographs. Most dislocations were confined to the first micron of epilayer and were observed to loop back to the GaAs/Si interface or to terminate without threading out of the V-grooves. No APBs were observed. Twinning was believed to be more prevalent when initial growth was on {111}. The extremely low dislocation densities measured in the earlier studies make this procedure for substrate preparation and epilayer growth very promising. However, high resolution TEM might be useful to more fully understand the  $SiO_x$  film and how it affects epitaxy.

The earlier studies of Krost et al.  $^{23, 24}$  investigated MOCVD epitaxy of InP on exactly oriented (100) silicon patterned with grooves 6  $\mu$ m and 4.5  $\mu$ m wide separated by (100) facets 3.5  $\mu$ m and 0.6  $\mu$ m wide, respectively. The width of the grooves and the spacing between grooves were too large for planarization of the epilayer. However, some interesting insights were obtained. Nucleation took place on both (100) and {111} facets. Growth on the structures with smaller (100) facets between the grooves resulted in no APB formation. APBs are caused by monoatomic steps on the (100). Reducing the width of the (100) facets reduced the probability of monoatomic steps and APBs. In a later study  $^{14}$ , epilayers of GaAs and InP were grown on substrates

with 320 nm and 200 nm grooves, and 80 nm and 200 nm wide (100) facets, respectively. Planarization did occur, and no APBs were formed. TEM images revealed that there were voids above the (100) facets, and it was concluded that growth initiated on the {111} facets of the grooves. Recent research<sup>25</sup> investigated in more detail the growth process of InP on sawtooth patterned (100) silicon. SEM micrographs were taken during each stage of growth. The nucleation layer homogeneously covered both the {111} and the (100) facets. After heating up the same sample to 640° C, InP migrated along the surface from the (100) facets to the {111} facets. By examining the planar area next to the grooves, it could be seen that InP up to 0.5 µm from the grooves had migrated into the grooves. This indicates that the epilayers in previous studies<sup>23, 24</sup> did not planarize in part because the distance between the grooves was too large for the nucleated material to migrate to the grooves. Growth in the grooves continued at 640° C and coalesced above the (100) facets leaving voids. The FWHM of double crystal x-ray diffraction rocking curves indicated that the defect density was almost as low as that of epilayers grown on off-cut (111) silicon. An etch pit density of  $7x10^4$  cm<sup>-2</sup> was found for the epilayer on the patterned (100) silicon. However unlike growth on (111) silicon, a large number of twins and stacking faults aligned to the {111} groove facets did propagate to the epilayer.

## 2.4 Epitaxy on Inverted Pyramid Patterned Silicon

Twins and stacking faults were observed in GaAs<sup>22</sup> and InP<sup>25</sup> epilayers grown on sawtooth patterned (100) silicon. Growth was found to initiate on the {111} facets, and twins have been found to nucleate on surface steps of {111}. In papers that have shown SEMs of the sawtooth structure before growth<sup>19, 21</sup> the {111} have large surface steps. This is to be expected because it is not possible to align masks perfectly with the silicon crystal planes for the anisotropic etch of the sawtooth structure. Any misalignment will result in surface steps (Chapter 1). Also, the edges of the etch mask are quite rough, and this transfers into steps on the etched {111} groove facets (Chapter 5).

Anisotropic etching of inverted pyramids on (100) silicon is not sensitive to mask alignment. Regardless of where a circular hole in the mask is placed, a square inverted pyramid defined by {111} will be etched. Roughness of the edges of the mask is also not critical. As long as the hole in

the mask is symmetric, a square indentation will form. Epitaxy on arrays of inverted pyramids could take advantage of the growth mechanisms on sawtooth patterned silicon which result in low dislocation densities and no APBs, while reducing twins and stacking faults by eliminating surface steps on the inverted pyramid {111} facets. High temperature anneals would not be necessary to reduce the density of the twins and stacking faults, and epitaxy would be more compatible with standard silicon circuitry.

- Martin O. Tanner, Michael A. Chu, Kang L. Wang, Marjohn Meshkinpour, and Mark S. Goorsky. Relaxed Si<sub>1-x</sub>Ge<sub>x</sub> films with reduced dislocation densities grown by molecular beam epitaxy. *Journal of Crystal Growth*, vol. 157, pp. 121-125, 1995.

- K. Werner, A. Storm, S. Burzke, J. W. Maes, M. van Rooy, P. Alkemade, E. Algra, M. Somers, B. de Lange, E. van der Drift, T. Zijlstra, S. Radelaar. Gas source MBE growth of Si/SiGe device materials. *Journal of Crystal Growth*, vol. 164, pp. 223-234, 1996.

- 3 K. Ismail. Correlation between dislocations and electron transport properties in Si/SiGe. *Solid State Phenomena*, vols. 47-48, pp. 409-418, 1996.

- 4 K. Ismail, J. O. Chu, and B. S. Meyerson. High hole mobility in SiGe alloys for device applications. *Appl. Phys. Lett.*, vol. 64, no. 23, pp. 3123-3126, 1994.

- A. Sadek and K. Ismail. Si/SiGe CMOS Possibilities. Solid-State Electronics, vol. 38, no. 9, pp. 1731-1734, 1995.

- 6 Masahiro Akiyama, Yoshihiro Kawarada, and Katsuzo Kaminishi.

Growth of single domain GaAs layer on (100)-oriented Si substrate by

MOCVD. Japanese Journal of Applied Physics, vol. 23, no. 11, pp. L843-L845, 1984.

- 7 N. H. Karam, V. E. Haven, S. M. Vernon, J. C. Tran, and N. A. El-Masry. Atomic layer epitaxy of GaAs on Si by MOCVD. *Mat. Res. Soc. Symp. Proc.*, vol 145, pp. 331-336, 1989.

- 8 S. F. Fang, K. Adomi, S. Iyer, H. Morkoc, H. Zabel, C. Choi, and N. Otsuka. Gallium arsenide and other compound semiconductors on silicon. *J. Appl. Phys.*, vol. 68, no. 7, pp. R31-R58, 1990.

- Tow C. Chong and Clifton G. Fonstad. Growth of high quality GaAs layers directly on Si substrate by molecular-beam epitaxy. J. Vac. Sci. Technol. B, vol. 5, no. 3, pp. 815-818, 1987.

- M. Grundmann, A. Krost, and D. Bimberg. Observation of the first-order phase transition from single to double stepped Si(001) in metalorganic chemical vapor deposition of InP on Si. J. Vac. Sci. Technol. B, vol. 9, no. 4, pp. 2158-2166, 1991.

- A. Krost, F. Heinrichsdorff, F. Schnabel, K. Schatke, D. Bimberg, and H. Cerva. Optical and Cyrstallographic Properties of High Perfection InP Grown on Si (111). *Journal of Electronic Materials*, vol. 23, no. 2, pp. 135-139, 1994.

- A. Krost, F. Heinrichsdorff, D. Bimberg, and H. Cerva. InP on Si(111): Accommodation of lattice mismatch and structural properties. *Appl. Phys. Lett.*, vol. 64, no. 6, pp. 769-771, 1994.

- J. Singh, *Physics of Semiconductors and Their Heterostructures*, McGraw-Hill, Inc., New York, p. 825, 1993.

- A. Krost, R. F. Schnabel, F. Heinrichsdorff, U. Rossow, D. Bimberg, and H. Cerva. Defect reduction in GaAs and InP grown on planar Si(111) and on patterned Si(001) substrates. *Journal of Crystal Growth*, vol. 145, pp. 314-320, 1994.

- H. Cerva, A. Krost, R. F. Schnabel, D. Bimberg. Interface defect structure of metal-organic chemically vapour-deposited InP and GaAs on Si(111). *Philosophical Magazine A*, vol. 71, no. 5, pp. 1145-1159, 1995.

- A. Hashimoto, T. Fukunaga, and N. Watanabe. GaAs growth properties on V-grooved Si substrates. *Appl. Phys. Lett.*, vol. 54, no. 11, pp. 998-1000, 1989.

- A. Hashimoto, T. Fukunaga, and N. Watanabe. Selective growth and optical properties of an AlGaAs layer on V-grooved Si substrates. J. Appl. Phys., vol. 66, no. 11, pp. 5536-5541, 1989.

- M. Grundmann, J. Christen, D. Bimberg, A. Hashimoto, T. Fukunaga, and N. Watanabe. Direct imaging of Si incorporation in GaAs masklessly grown on patterned Si substrates. *Appl. Phys. Lett.*, vol. 58, no. 19, pp. 2090-2092, 1991.

- 19 K.-R. Sprung, K. Wilke, G. Heymann, J. Varrio, and M. Pessa. GaAs single-domain growth on exact (100) Si substrate. *Appl. Phys. Lett.*, vol. 62, no. 21, pp. 2711-2712, 1993.

- Jane G. Zhu, M. M. Al-Jassim, N. H. Karam, and K. M. Jones. Defect reduction in GaAs grown on Si by using saw-tooth-patterned substrates. *Mat. Res. Soc. Symp. Proc.*, vol. 281, pp. 327-332, 1993.

- N. H. Karam, V. Haven, K. Ismail, F. Legoues, J. Carter, and Henry I. Smith. A new approach for low defect density GaAs on patterned Si substrates by MOCVD. *Mat. Res. Soc. Symp. Proc.*, vol. 221, pp. 399-404, 1991.

- K. Ismail, F. Legoues, N. H. Karam, J. Carter, and Henry I. Smith. High-quality GaAs on sawtooth-patterned Si substrates. *Appl. Phys. Lett.*, vol. 59, no. 19, pp. 2418-2420, 1991.

- A. Krost, M. Grundmann, D. Bimberg, and H. Cerva. InP on patterned Si(001): defect reduction by application of the necking mechanism. Journal of Crystal Growth, vol. 124, pp. 207-212, 1992.

- M. Grundmann, A. Krost, D. Bimberg, O. Ehrmann, and H. Cerva. Maskless growth of InP stripes on patterned Si (001): Defect reduction and improvement of optical properties. *Appl. Phys. Lett.*, vol. 60, no. 26, pp. 3292-3294, 1992.

- R. F. Schnabel, A. Krost, M. Grundmann, D. Bimberg, and H. Cerva. Maskless selective area growth of InP on sub-μm V-groove patterned Si(001). *Journal of Electronic Materials*, vol. 24, no. 11, pp. 1625-1629, 1995.

- N. Chand, J. Allam, J. M. Gibson, F. Capasso, F. Beltram, A. T. Macrander, A. L. Hutchinson, L. C. Hopkins, C. G. Bethea, B. F. Levine, and Y. Cho. GaAs avalanche photodiodes and the effect of rapid thermal annealing on crystalline quality of GaAs grown on Si by molecular-beam epitaxy. J. Vac. Sci. Technol. B, vol. 5, no. 3, pp. 822-826, 1987.

## Chapter 3

## Design of Inverted Pyramid Process

#### 3.0 Introduction

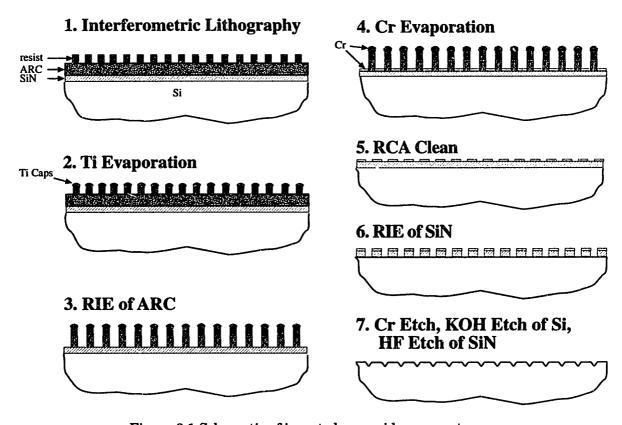

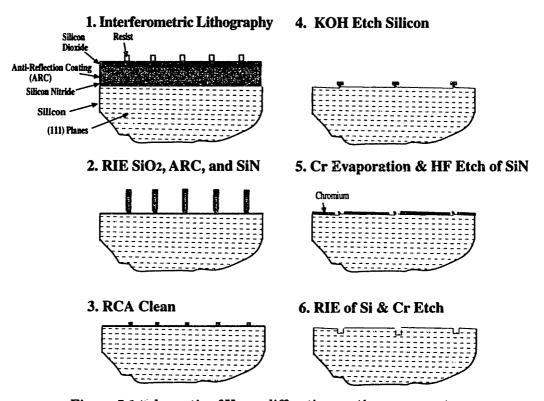

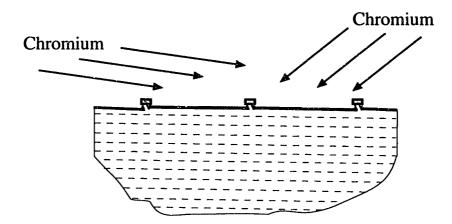

The inverted pyramid process steps are shown in Figure 3.1, and the process conditions for each step are described in detail in Appendix A. The process began with a (100) silicon wafer coated with silicon nitride, anti-reflection coating (ARC), and Shipley 1813 resist. The resist was patterned using interferometric lithography. Titanium was shadow evaporated on the resist posts to act as a hard mask for the reactive ion etch (RIE) of the ARC. Chromium lift-off reversed the tone of the pattern, and the holes were transferred into the silicon nitride layer using RIE. The patterned nitride layer was then an etch mask for the anisotropic etch of the silicon that produced inverted pyramids.

Figure 3.1 Schematic of inverted pyramid process steps.

#### 3.1 Interferometric Lithography

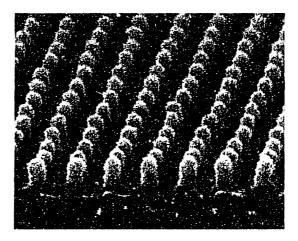

Positive resist was exposed using interferometric lithography at 351.1 nm wavelength and for a 200 nm period pattern<sup>1</sup>. The wafer was exposed twice, with the wafer rotated 90° for the second exposure. After development, the posts of resist remained where the light destructively interfered in both exposures. The exposure dose was chosen to be high enough that shoulders between the posts were small compared to the posts and low enough that the posts were not thinner at the base than at the top (Figure 3.2). The dose was chosen for each exposure session by examining developed resist profiles from wafers exposed with several doses.

Figure 3.2 SEM micrograph of resist posts with appropriate interferometric dose.

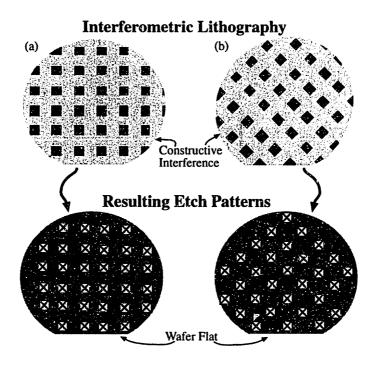

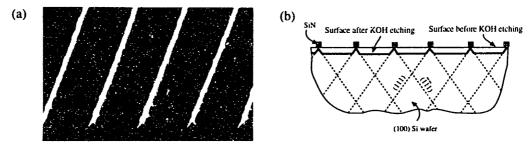

The wafer must be aligned such that the lines of constructive interference run perpendicular and parallel to the wafer flat which is a {110} plane (Figure 3.3). The larger the misalignment angle with the crystallographic planes, the larger the spacing between inverted pyramids. As discussed in Chapter 2, the spacing between the V grooves in sawtooth structures must be small in order to reduce defects and have the epilayer planarize. Similarly, the spacing between inverted pyramids should be minimized.

Figure 3.3 The correct interferometric lithography pattern is depicted in (a). Not aligning the lines of constructive interference parallel and perpendicular to the wafer flat results in larger spacing between inverted pyramids after KOH etching which is not desirable (b).

#### 3.2 Titanium Evaporation

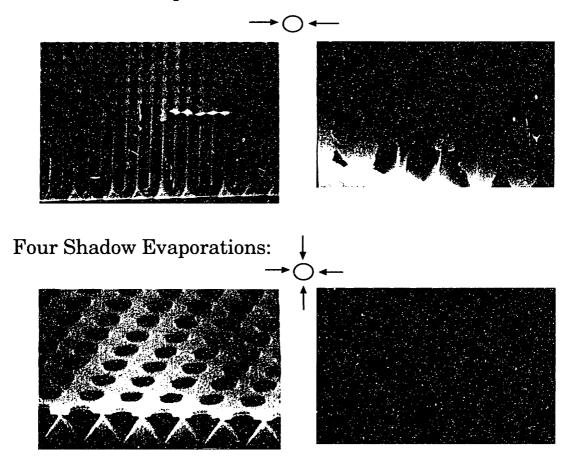

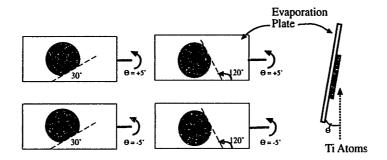

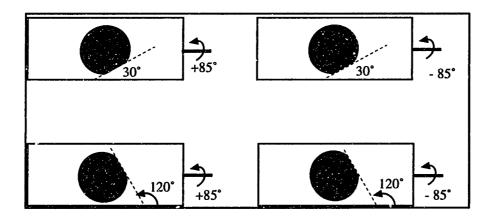

One of the main goals of the remaining steps was to produce small, round holes in the silicon nitride layer. If the holes in the silicon nitride were oval, more silicon area was exposed to the KOH along the larger axis of the oval, and rectangular trough-like indentations were etched (Figure 3.4). Hence, the titanium caps evaporated on the resist posts had to be as circular as possible. Originally, the caps were shadow evaporated from two directions, and this produced oval patterns. Four shadow evaporations each 90° apart resulted in circular patterns (Figure 3.5). A program written by another student<sup>2</sup> calculated that aligning the wafer flat at 30° and 120° with the evaporation plate edge allowed adequate shadowing, so titanium was not evaporated between the posts or on the bases of the posts (Figure 3.6).

Figure 3.4 Top view of anisotropically etched indentations seen beneath the etch mask. An irregular oval hole in the silicon nitride etch mask resulted in a rectangular trough-like indentation. Irregular, yet not oval, and perfectly circular holes in the silicon nitride etch mask both resulted in inverted pyramids.

# Two Shadow Evaporations:

Figure 3.5 Four shadow evaporations resulted in more circular titanium caps, and hence more circular holes in the silicon nitride. In the above case, the nitride holes were so oval that during KOH etching the pyramids coalesced along the larger axis of the oval nitride holes.

Figure 3.6 Configurations for shadow evaporations.  $\Theta$  is the angle the plane of the wafer made with the titanium flux.

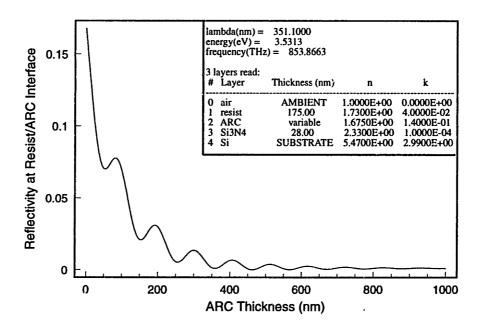

The evaporation plate tilt angle,  $\Theta$ , was calculated by first realizing that in aligning the wafer to the evaporation plate above, the resist post A casts a shadow towards post B in Figure 3.7. The period of the interferometric lithography was 200 nm, so d  $\cong$  450 nm. The width of the holes in the silicon nitride were approximately the same as the width of the titanium caps. The smaller the holes in the silicon nitride were, the easier it was to control the anisotropic etching. However, the titanium caps had to be wide enough that the ARC posts did not fall together during RIE. The width of a titanium cap, w, was chosen to be  $\cong$  80 nm. The height, x, of the desired titanium cap was then approximated with an SEM micrograph of the resist profile after titanium evaporation and was on the order of 60 nm. This resulted in  $\Theta$  = 7.6° or less. An angle of 5° was used.

Figure 3.7 Determination of evaporation plate angle,  $\Theta$ .

#### 3.3 RIE of ARC

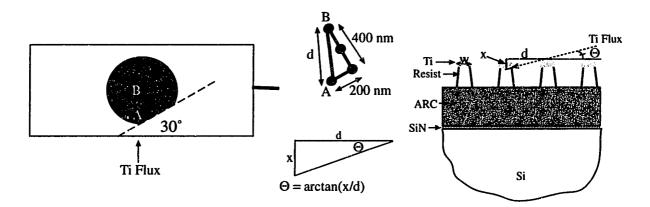

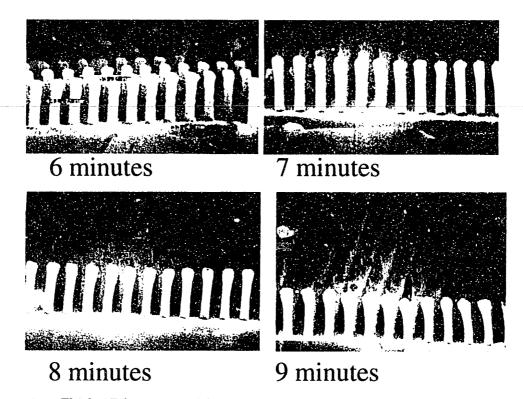

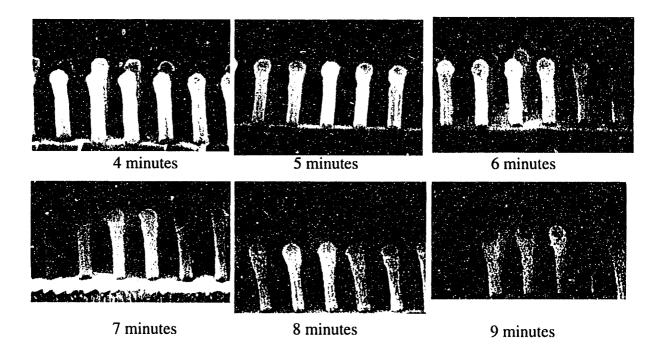

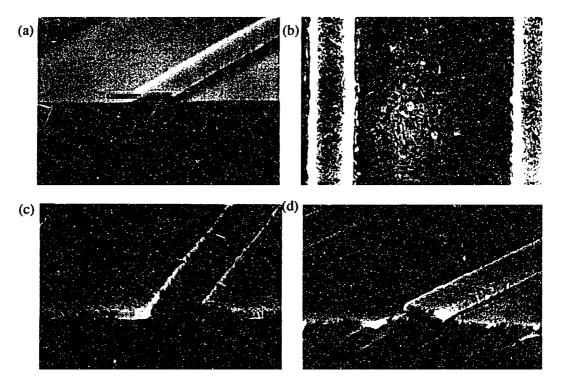

Oxygen RIE was used to transfer the pattern of the array of titanium circles into the ARC layer. The purpose of the ARC was to suppress standing waves in the resist due to reflection from the underlying silicon nitride and silicon layers in the interferometric lithography step. Without the ARC the standing wave would have created a vertical rippling in the resist profile or even prevented complete resist development. Initially, the ARC was spun to be 350 nm thick. This thickness gave a reflectivity of less than 1% at the resist/ARC interface (Figure 3.8). However, the process latitude of the RIE step was quite small with this thickness of ARC. If the ARC was not etched long enough, the chromium used for liftoff was evaporated onto ARC which dissolved away in the RCA step, and no pattern remained (Figure 3.9). If the ARC was over-etched the posts began to fall over because the RIE laterally etched the posts to the point where they could no longer support the titanium caps. As can be seen in Figure 3.10, after 6 minutes of RIE 33.4 nm of ARC remained. After 7 minutes of RIE the ARC cleared, yet an additional minute of RIE caused the posts to fall over. Because there is some variation in etch rate due to deposition of etched materials on the RIE chamber and other factors<sup>3</sup>, the process latitude with 350 nm of ARC was too small. Decreasing the ARC thickness to 220 nm gave adequate standing wave suppression while greatly increasing the RIE process latitude (Figure 3.11). Using 220 nm of ARC the RIE etching was complete within 5 minutes. Although the posts became thinner with additional etching, they did not fall over, even after 9 minutes of etching. With this increased process latitude it was possible to over etch to ensure that the ARC had been etched through without the posts falling over.

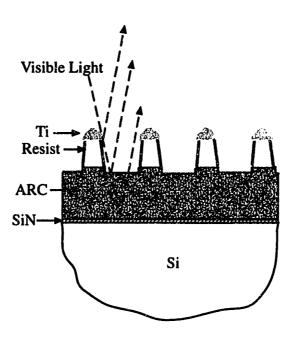

Another way to check that the ARC had been etched through was to visually note the color of the wafer when the etch was thought to be complete based on the results of previous runs, and etch the wafer for an additional period, say 30 seconds. If the color did not change, the etch was complete. This method relies on interference from the ARC film being etched (Figure 3.12). As the thickness of the ARC changes, different wavelengths of light reflecting from the air/ARC and ARC/silicon nitride interfaces constructively interfere. Diffraction of light by the posts does not occur except possibly at grazing

angles because the period of the posts, 200 nm, is smaller than half the wavelength of visible light.

Figure 3.8 Calculated reflectivity at resist/ARC interface vs. ARC thickness.

Figure 3.9 Insufficient RIE of the ARC. The ARC will dissolve in the RCA cleaning step, preventing chromium from adhering to the substrate around the bases of the posts.

Figure 3.10 Thick ARC, 350 nm. After 7 minutes of etching all of the ARC had been etched through. However, with only one more minute of etching the posts began to fall together. The posts fell together more noticably after 9 minutes of etching.

Figure 3.11 Thin ARC, 220 nm. The ARC has been completely etched through in 5 minutes. With further etching the posts became thinner but did not fall together.

Figure 3.12 As the thickness of the ARC changes, different wavelengths of light reflecting from the air/ARC and ARC/silicon nitride interfaces constructively interfere. Diffraction of light by the posts does not affect the observed color because the period of the posts is smaller than the wavelength of visible light.

## 3.4 Cr Evaporation

The crucial consideration for the chromium evaporation step was to make sure the sample was centered on the evaporation plate and that the evaporation plate was exactly normal to the incident chromium atom flux. Any deviation from this configuration resulted in chromium deposition on the sides of the posts and shadowing. (Figure 3.13) The end result was oval holes in the silicon nitride. Also, it was important to use the second shutter in the evaporation chamber to block 'spitting' of the chromium at the beginning of the evaporation. Spitting refers to the ejection of chromium chunks from the evaporation target which can knock over posts on the sample.

Figure 3.13 SEM micrographs of the centers of two wafers. The wafer shown in (a) was not placed in the center of the evaporation plate, and the holes in the silicon nitride are oval. The wafer shown in (b) was placed in the center of the evaporation plate, and the holes are smaller and more round.

#### 3.5 RCA Clean

Considerable chromium redeposition occurred during the RCA clean used to remove the posts (i. e. the lift-off step). Chromium does not dissolve in RCA. If the chromium caps which were deposited on the tops of the posts came in contact with the chromium that was deposited around the posts, the caps stuck. (Figure 3.14) If these chromium caps obscured holes which were to be transferred into the silicon nitride layer via RIE, the holes were not transferred. Several approaches were tried to alleviate this problem. The solution was to use two baths of RCA. In the first solution the posts dissolved. The wafer was then rinsed, removing some caps. The wafer was not allowed to dry because drying caused any caps which had redeposited to permanently adhere to the wafer. The second RCA bath was put in an ultrasound vessel. The ultrasound vibration shook free caps which had redeposited, and since the concentration of caps in the new clean bath was low, the chance or redeposition again was low.

Figure 3.14 After RCA cleaning (a), chromium caps redeposited and obscured holes in the chromium mask. The obscured holes were not transferred into the silicon nitride layer (b), and inverted pyramids were not KOH etched where a chromium cap obscured a hole.

#### 3.6 RIE of SiN

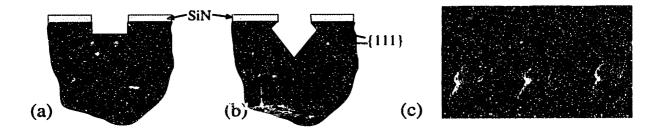

To transfer the pattern from the chromium into the silicon nitride CF<sub>4</sub> or CHF<sub>3</sub> RIE was used. Originally, CF<sub>4</sub> was used. However, CF<sub>4</sub> plasma etches silicon faster than silicon nitride. Hence, it was difficult not to etch the silicon under the silicon nitride. If the underlying silicon was etched, another set of {111} planes defined the etched structure (Figure 3.15). CHF<sub>3</sub> prevents etching of silicon because a teflon-like polymer is deposited on silicon surfaces<sup>4,5</sup>(Figure 3.16). This polymer must be removed to allow potassium hydroxide (KOH) anisotropic etching. The polymer can be removed either by piranha cleaning or oxygen RIE. (Piranha is a 3 parts sulfuric acid:1 part hydrogen peroxide mixture which dissolves organic compounds.)

Figure 3.15 The schematic labeled (a) depicts a CF<sub>4</sub> RIE etch that did not stop at the silicon nitride/silicon interface. After KOH etching, {111} planes facing downward resulted (b). The SEM micrograph (c) is a sample after KOH etching, and after the silicon nitride had been removed.

Figure 3.16 A teflon-like polymer film prevented uniform KOH etching. Etching occurred at the edges of the holes in the silicon nitride where the polymer film was thinner. As the silicon was etched out from beneath the polymer, some of the polymer film flaked off.

## 3.7 Cr Etch, KOH Etch of Si, HF Etch of SiN

KOH etching is slowed by silicon dioxide. To remove native silicon dioxide or silicon dioxide that resulted from oxygen RIE, a buffered HF or concentrated HF dip was used. It was found that concentrated HF and buffered oxide etch (BOE) fairly quickly dissolved the silicon nitride, and only buffered HF removed the oxide without damaging the nitride (Figure 3.17). If the silicon nitride was left in BOE or concentrated HF for too long, the nitride completely dissolved away, and there was no mask for the KOH etch.

Figure 3.17 A dip in buffered oxide etch (BOE) partially dissolved the silicon nitride.

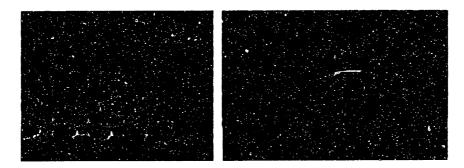

KOH etching of silicon produces gaseous products<sup>6</sup>. Bubbles form on the silicon surface which prevent the KOH from reaching the silicon, and etching is inhibited (Figure 3.18). Gently agitating the wafer with tweezers dislodges the bubbles.

Figure 3.18 Unwanted Si in the bottom of the pyramids resulted from inadequate agitation during the KOH etching. The diagram shows a bubble protecting the silicon from the etchant.

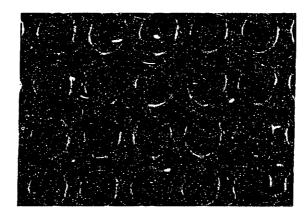

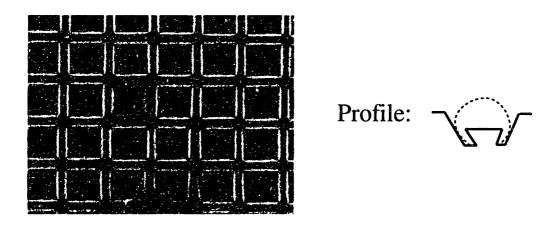

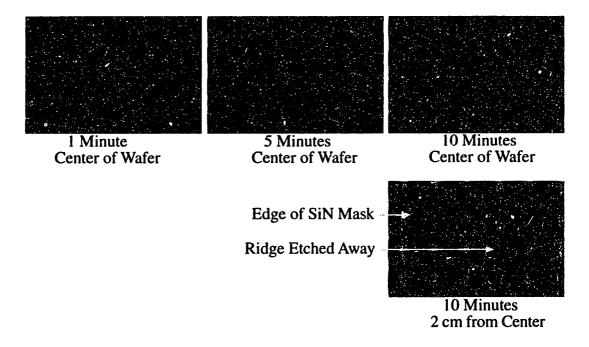

With small, round holes in the silicon nitride, it was easy to control the width of the ridges separating the pyramids. As described in Chapter 2, this is an important factor in epitaxial growth on these substrates. An SEM can image both the edges of the silicon nitride holes and the edges of the pyramids (Figure 3.19). So, the width of the ridges can be monitored during the KOH

etch process, and etching can proceed until the desired ridge width is achieved. Although the etch rate in the <111> directions is small, it does allow for increased pyramid size with further etching. Also, there is some variation in the size of the holes in the silicon nitride across the wafer. This originates from the interferometric lithography step. The intensity of the radiation is greatest in the center of the wafer. This causes the resist posts to be thinner in the center of the wafer, and the silicon nitride holes to be smaller. So, the width of the ridges between the pyramids will decrease towards the edge of the wafer. As can be seen in Figure 3.19, 2 cm from the center of the wafer the ridges between the pyramids became so thin that in some places they were completely etched away, and in these places rectangular troughs formed.

Figure 3.19 SEM micrographs at 19kV, illustrating that as KOH etching proceeds the size of the pyramids increases, and the ridges between the pyramids become smaller.

The holes in the silicon nitride are larger away from the center of the wafer. This can cause the ridges to be etched away and pyramids to coalesce after long KOH etches.

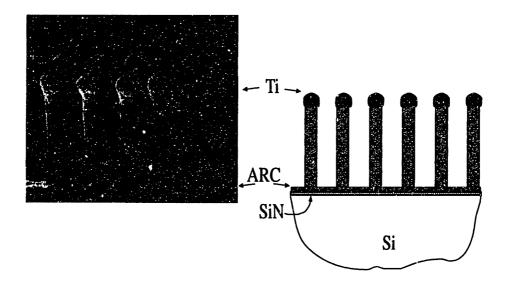

In conclusion, large areas can be reliably patterned with arrays of 200 nm period inverted pyramid arrays (Figure 3.20). This is a promising structure for improving crystal quality in lattice mismatched epilayers grown on (100) silicon.

Figure 3.20 Inverted pyramid array. In SEM micrograph (b) the accelerating voltage is 19kV which is high enough to make the walls between inverted pyramids transparent.

- M. L. Schattenburg, E.H. Anderson, and H. I. Smith. X-ray/VUV transmission gratings for astrophysical and laboratory applications", *Physica Scripta*, vol. 41, pp. 13-20 (1990).

- 2 NSL/ Procedures/Holography/Gridshadow, by Ken Yee.

- 3 S. Wolf and R. N. Tauber, Silicon Processing for the VLSI Era Volume 1 Process Technology, Lattice Press, 1986, p. 556.

- P. J. Astell-Burt, J. A. Cairns, A. K. Cheetham, and R. M. Haze. A study of the deposition of polymeric material onto surfaces from fluorocarbon RF plasmas. *Plasma Chemistry and Plasma Processing*, vol. 6, no. 4, pp. 417-427, 1986.

- 5 Yue Kuo. Reactive ion etching of PECVD amorphous silicon and silicon nitride thin films with fluorocarbon gases. *J. Electrochem. Soc.*, vol. 137, no. 4, 1990.

- S. A. Campbell, K. Cooper, L. Dixon, R. Earwaker, S. N. Port, and D. J. Schiffrin. Inhibition of pyramid formation in the etching of Si p<100> in aqueous potassium hydroxide-isopropanol. J. Micromech. Microeng, vol. 5, pp. 209-218, 1995.

# Chapter 4

Grazing Incidence, Blazed, X-ray Diffraction Gratings

#### 4.0 Introduction

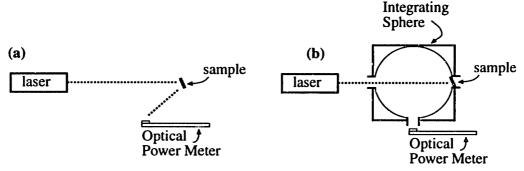

There are a great number of astrophysical sources which emit in the 5 Å to 300 Å band. K-shell transitions of C, N, and O, and the L-shell transition of Fe are in the 6 Å to 60 Å range<sup>1</sup>. High spectral resolving power is required to identify these lines, which can be provided by grazing incidence, blazed, diffraction gratings. Similarly these gratings are used in spectrometers to image radiation from hot coronas of stars and to detect Doppler shifts and spectral features of intervening material<sup>2</sup>. In this chapter the basic operation of these diffraction gratings, traditional fabrication processes, and a new, more reliable process with higher diffraction efficiency will be discussed.

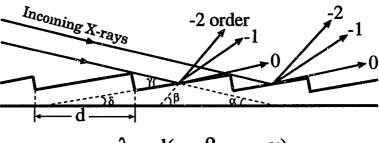

## 4.1 Diffraction Gratings

A groove profile with incident and diffracted rays, and the grating equation are depicted in Figure 4.1. The grating consists of triangular grooves of period, d. X-rays of wavelength,  $\lambda$ , at an incident angle,  $\alpha$ , are diffracted. The mth order diffracts at an angle of  $\beta_m$ . The maximum diffraction efficiency occurs when the incident and exit angles on the facets are equal, or  $\gamma = \alpha + \delta = \beta_m - \delta.$  Determining grating parameters is a trade-off between short wavelength cut-off, diffraction efficiency, and spectral resolution<sup>3</sup>. It is desirable to be able to alter grating parameters easily in the design of spectrometers.

$m\lambda = d(\cos\beta_m - \cos\alpha)$

Figure 4.1 Diffraction of X-rays on a blazed, grazing incidence grating, and the grating equation.

### 4.2 Ruled Gratings

There are three methods to fabricate diffraction gratings: 1) ruling, 2) interferometric lithography with ion etching, and 3) interferometric lithography with anisotropic etching. The ruled gratings have traditionally had the highest efficiencies and are the most widely used. They are made by scribing grooves with a diamond tip<sup>4</sup>. The position of the diamond tip with respect to the beginning of the ruling is measured interferometrically by having a mirror attached to the diamond carriage and a mirror and beam splitter at the beginning of the ruling. The carriage progresses at a rate defined by the turning of a ruling screw and an electromechanical gear system. Errors in this system can be detected with the interferometric fringe signal and can be corrected.

Yet, there are errors in the ruling engine system which can not be totally corrected. Temperature, pressure, and humidity changes degrade the accuracy of the interferometric system. Wear on the diamond in the course of the ruling leads to changes in the groove profile<sup>5</sup>. Periodic errors in the ruling screw cause periodic errors in groove placement which give rise to ghosts, images of the parent line at a different angle and with less intensity. Another serious ruling error is nonparallelism of the grooves which degrades resolution. Ruling is typically done in aluminum or gold which has been evaporated on a glass substrate. The properties of evaporated metals which effect the ruling process are not well understood. Hence, two coatings of the same metal with the same evaporation parameters may not rule in the same manner. Optimal optical properties of the metals and success in ruling depend on the evaporation, and do not necessarily both result from the same evaporation parameters. Evaporations with high deposition rates have better optical properties, but are also known to have voids and small metal globules in the films. Finally, the metal thickness must be one half to several microns depending on the groove density, and this results in fairly rough surfaces, which are only partially smoothed by the ruling process.

Ruling gratings is a time intensive process. A grating 148.8 cm<sup>2</sup> in area with a groove density of 3600 grooves per mm required four weeks of ruling<sup>5</sup>. Hence, it is quite costly to produce a high quality ruled grating over a large area, and replicas of the master gratings are made. Replicas are made of these master gratings by coating the master with a parting agent followed by the

metal which is to be the replica's surface. Epoxy is poured onto the coated master, and the glass replica substrate is placed on top of the epoxy. Pressure is applied to the replica substrate so that the epoxy is as uniform and thin as possible. This is done to reduce distortion due to shrinkage as the epoxy cures. Once the epoxy has hardened, the replica and master are separated.

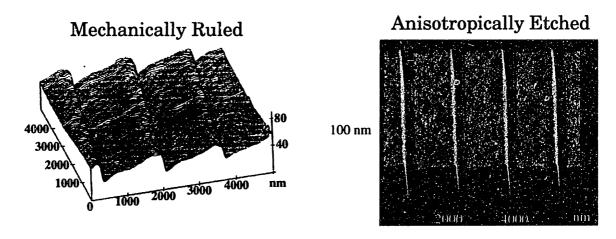

As can be seen in Figure 4.2, a master grating from Bixler et al.<sup>6</sup>, the blaze facets are quite rough and have considerable curvature. The fraction of scattered X-rays depends on the square of surface roughness:

$$S = (2\pi\sigma[\sin(\alpha) + \sin(\beta)]/\lambda)^2$$

where  $\sigma$  is the rms surface roughness, and S is the fraction of scattered radiation<sup>6</sup>. The curvature of the facets also decreases diffraction efficiency. Replicas have even less smooth and less flat profiles, and they are made with materials which degrade with heat cycling and use.

Figure 4.2 A scanning tunneling micrograph of a master ruled grating from Bixler et al.<sup>6</sup>

# 4.3 Interferometric Lithography and Ion Etching

Defining the grating with interferometric lithography greatly reduces errors in the grating pattern<sup>7</sup>, and patterning can be completed within minutes. However, a pattern in photoresist in not very durable, and it is difficult to make a particular groove pattern in the resist, such as a blazed groove. To

make the blazed groove, ion etching is used with the resist as the mask and with the ions impinging on the substrate at the blaze angle<sup>5, 8, 9</sup>. Again, the resist is not very durable and etches faster than the substrate, so that only shallow etch grooves are attainable<sup>5</sup>. Reactive ion etching the resist pattern into a hard mask and then ion etching to make the grooves may alleviate this problem, but has not been attempted. A problem with this process that is more difficult to solve is that any edge roughness of the resist profile will be transferred into the facets, reducing flatness and resulting in the apex of a groove not being a straight line.

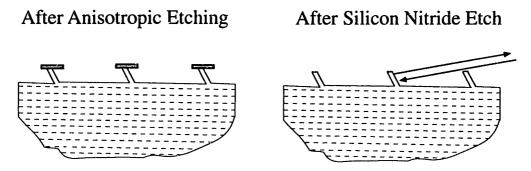

### 4.4 Interferometric Lithography and Anisotropic Etching

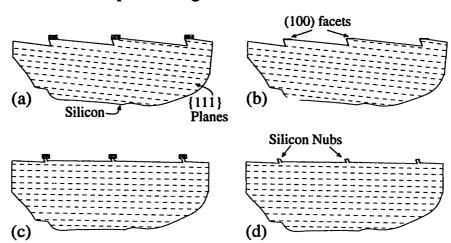

Another approach is to define the grating with interferometric lithography, or another lithographic technique, and to anisotropically etch the blaze facets<sup>5, 10, 11, 12</sup>. This has the potential of producing atomically smooth blaze facets. A silicon wafer is used as the substrate which has been cut and polished so that the (111) crystal planes intersect the surface of the wafer at the desired blaze angle. The process consists of patterning the grating in resist, transferring the pattern into silicon dioxide or silicon nitride, anisotropically etching, and then removing the silicon dioxide or nitride. The silicon dioxide or silicon nitride acts as the anisotropic etch mask. The etch rate in <111> directions is quite small compared to other directions and so the anisotropic etching defines facets that are bounded by the {111} planes. However, in previous work a good solution was not found to the problem of removing the silicon from beneath the etch mask (Figure 4.3). These silicon 'nubs' or (100) facets that are parallel to the initial wafer surface will decrease diffraction into the -1 order and will increase scatter. Roszhart<sup>5</sup> used thin lines for the etch mask to reduce the width of the nubs. Fujii et al. 10 did not address this issue. Philippe et al. 11 used an isotropic etch after removing the anisotropic etch mask. However, this rounds the apex of the groove, and introduces roughness on the blaze facets. Ciarlo and Miller<sup>12</sup> suggest continuing with an anisotropic etch after removal of the mask, which would quickly round the apex, and would be very difficult to control.

## After Anisotropic Etching

## After Removal of Etch Mask

Figure 4.3 If anisotropic etching is stopped when {111} planes are reached (a), (100) facets result which reduce diffraction into the -1 order and increase scatter (b). If anisotropic etching continues (c), nubs are formed underneath the etch mask. These nubs can completely block grazing incident radiation.

In the following chapter a process is described which eliminates the nubs with a lift-off technique. Atomic force microscopy was performed to determine the smoothness of the facets, and rms roughness of less than 4 Å was achieved. Even more importantly, the gratings made with this process had peak X-ray diffraction efficiencies up 100% more than ruled gratings.

- Steven M. Kahn. High Throughput Soft X-ray Spectroscopy with Reflection Gratings. High Resolution X-ray Spectroscopy of Cosmic Plasmas, ed. P. Gorenstein and M. Zombeck, pp. 365-375, 1990.

- John F. Meekins, Michael P. Kowalski, and Raymond G. Cruddace. Efficiency measurements of reflection gratings in the 100-300-Å band. Applied Optics, vol. 28, no. 7, pp. 1369-1377, 1989.

- A. J. F. den Boggende, P. A. J. de Korte, P. H. Videler, A. C. Brinkman, S. M. Kahn, W. W. Craig, C. J Hailey, and M. Neviere. Efficiency of x-ray reflection gratings. SPIE X-ray Instrumentation in Astronomy II, vol. 982, pp. 283-298, 1988.

- E. Wolf, ed. *Progress in Optics, Volume II*, North-Holland Publishing Company, pp. 45-47, 1963.

- W. R. Hunter. Spectrometric Techniques, Volume IV, Academic Press, New York, pp. 63-182, 1985.

- J. V. Bixler, C. J. Hailey, C. W. Mauche, P. F. Teague, R. S. Thoe, S. M. Kahn, and F. B. S. Paerels. Performance of a Variable Line Spaced Master Reflection Grating for Use in the Reflection Grating Spectrometer on the X-ray Multimirror Mission. SPIE EUV, X-ray, and Gamma-ray Instrumentation for Astronomy II, vol. 1549, pp. 420-428, 1991.

- Juan Ferrera, M. L. Schattenburg, and Henry I. Smith. Analysis of distortion in interferometric lithography. J. Vac. Sci. Technol. B, vol. 14, no. 6, pp. 4009-4013, 1996.

- 8 M. Stedman, D. W. Butler, T. H. English, A. Franks, B. Gale, M. C. Hutley, and P. R. Stuart. Recent developments in X-ray diffraction gratings at NPL. Space Science Instrumentation 2, pp. 355-362, 1976.

- Jack C. Rife, William R. Hunter, Troy W. Barbee, Jr., and R. G. Cruddace. Multilayer-coated blazed grating performance in the soft X-ray region. *Applied Optics*, vol. 28, no. 15, pp. 2984-2986, 1989.

- Yohji Fujii, Koh-Ichi Aoyama, and Jun-Ichiro Minowa. Optical demultiplexer using a silicon echelette grating. *IEEE Journal of Quantum Electronics*, vol. QE-16, no. 2, pp. 165-169., 1980.

- P. Philippe, S. Valette, O. Mata Mendex, and D. Maystre. Wavelength demultiplexer: using echelette gratings on silicon substrate. *Applied Optics*, vol. 24, no. 7, pp. 1006-1011, 1985.

- D. R. Ciarlo and D. E. Miller. Silicon diffraction gratings for multilayer structures. SPIE, Multilayer Structures and Laboratory X-ray Laser Research, vol. 688, pp. 163-170, 163.

# Chapter 5

# **Design of Anisotropically Etched Grating Process**

#### 5.1 Introduction

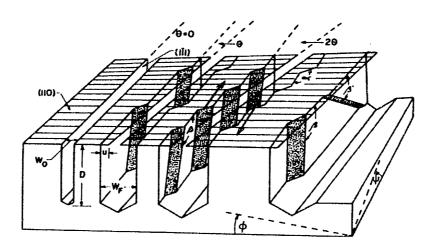

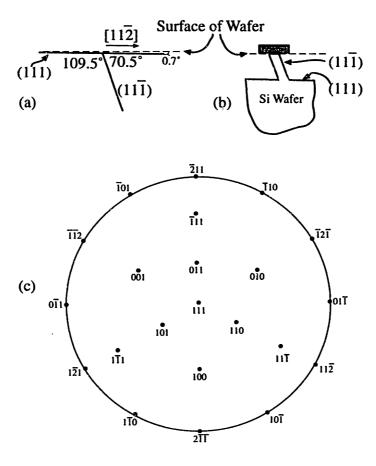

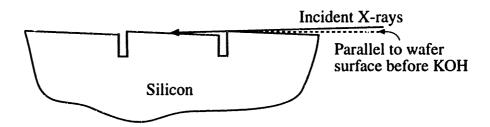

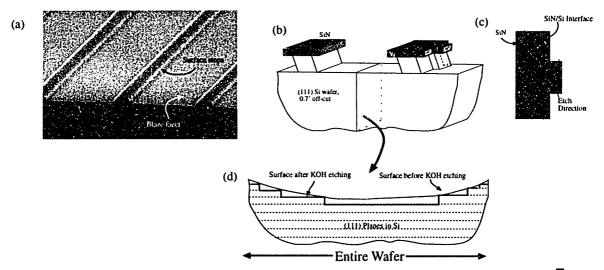

The anisotropically etched X-ray diffraction grating process steps are shown in Figure 5.1, and a detailed description of the steps can be found in Appendix B. The process began with a (111) silicon wafer off-cut so that the (111) planes were at a blaze angle to the surface of the wafer of 0.7 degrees (Figure 5.2). The wafer was coated with silicon nitride, anti-reflection coating (ARC), silicon dioxide, and Sumitomo PFI-34 resist. The resist was patterned using interferometric lithography. The pattern was transferred into underlying layers by reactive ion etching (RIE). RCA removed all but the silicon nitride on the silicon. Anisotropic etching with KOH terminated on the {111} planes. Chromium evaporation and an HF etch removed the silicon nitride and protected the (111) facets desired for the blaze facets. RIE removed the silicon nubs and resulted in trenches. The incident X-rays do not 'see' these trenches, because the incident angle is so small that the trenches are shadowed (Figure 5.3).

Figure 5.1 Schematic of X-ray diffraction grating process steps.

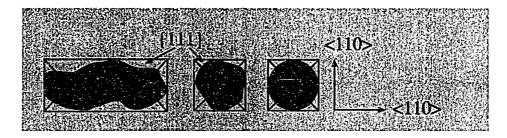

Figure 5.2 Important crystal planes and directions (a) are shown in a cross-section parallel to the  $(\overline{1}10)$  plane. The (111) plane can be seen to be at the blaze angle,  $0.7^{\circ}$ , to the surface of the wafer. After KOH etching (b) the (111) and  $(11\overline{1})$  planes are exposed. The stereographic projection (c) indicates where the normal to plane (h l k) intersects a semisphere above a (111) wafer.

Figure 5.3 X-rays are incident on the grating at such a small grazing angle that the troughs between facets are completely shadowed.

The silicon wafers are cut from a boule which can be aligned to the desired angle to within 0.2 degrees. However, chemical mechanical polishing (CMP) may add some error to the angle the crystallographic planes make with the surface of the wafer. This may be a critical concern if large quantities of the diffraction gratings with a more precise and accurate blaze angle are desired. To ensure the correct crystallographic orientation, X-ray diffraction can be performed on each wafer after CMP to determine the crystallographic orientation to within 0.01 degrees.

The wafers must have no boron dopants. Boron greatly reduces etch rates in KOH solutions. It is also desirable to have minimal phosphorous, antimony, or contaminants as these alter the silicon lattice near the dopant atom, and may introduce roughness on etched facets.

### 5.1 Interferometric Lithography

Positive resist was exposed using interferometric lithography with 351.1 nm wavelength and 1.0  $\mu$ m or 1.7  $\mu$ m period<sup>2</sup>. Unlike in the pyramid process, the wafer was exposed only once so as to make a grating, instead of a grid. The dose used was 250 mJ, which is unusually high. A line to space ratio of approximately 1:10 resulted. This was desired in order to have only a small distance between blaze facets.

Correct alignment to the wafer flat was important. The lines of constructive interference had to be perpendicular to the flat, the  $(1\overline{1}0)$  plane. This was because the wafers had been cut from the boule with the (111) plane tilted  $0.7^{\circ}$  towards the  $[11\overline{2}]$  direction (Figure 5.2).

## 5.2, 5.3 RIE of SiO<sub>2</sub>, ARC, and SiN, RCA Clean

The RIE step to etch through the silicon dioxide, ARC, and silicon nitride layers was much less critical than the RIE steps in the pyramid process. This was because the feature sizes were considerably larger and because stopping the etch at the silicon nitride/silicon interface was not necessary. However, etching of the silicon dioxide for too long resulted in unacceptably rough edges of the lines (Figure 5.4).

Figure 5.4 The silicon dioxide was over-etched. The edge roughness of the silicon dioxide lines transferred to the ARC and silicon nitride. In Figure 5.4(a) the rough-edged silicon nitride and the silicon ridge supporting the nitride can be seen after KOH etching. After chromium evaporation and lift-off, the edge roughness can be seen to have transferred to the chromium edge. This will also transfer into the edge of the blaze facets, causing scatter.

A polymer deposited during the CF<sub>4</sub> RIE of the silicon nitride was found to interfere with the KOH etch process (Figure 5.5). This was similar to the polymer that was encountered in the pyramid process, and it was also easily removed with oxygen RIE and/or piranha. The ARC present during the RIE of the silicon nitride was a probable source of hydrogen which produced similar results as RIE etching the silicon nitride with CHF<sub>3</sub>. It was difficult to understand, however, why in some cases polymer was found on top of the silicon nitride lines. Possibly, the polymer can migrate along the surface or redeposit during the RCA clean.

Figure 5.5 A polymer was found to impede KOH etching, and in some cases it covered the silicon nitride.

#### 5.4 KOH Etch Silicon

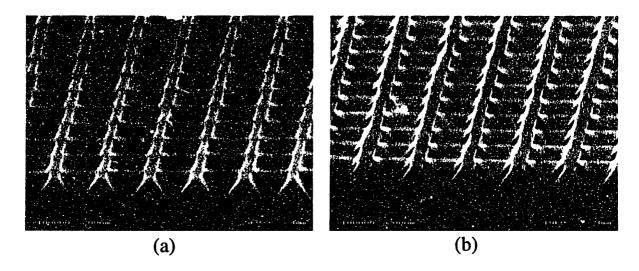

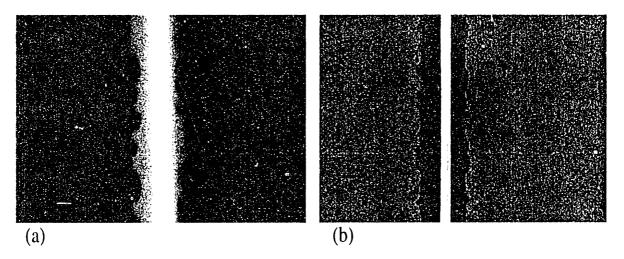

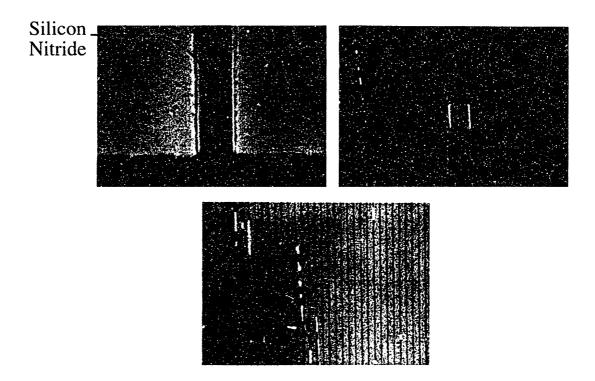

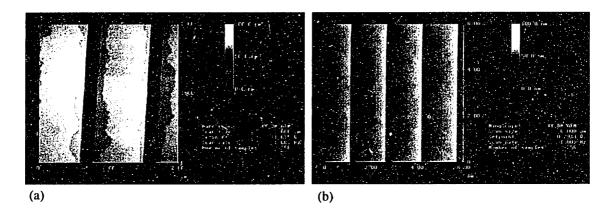

The purpose of the grating process is to produce extremely smooth blaze facets. As can be seen in the SEM of Figure 5.6 (a), the (111) planes have numerous surface steps, while the blaze facets, the (111) planes, have no surface steps that are noticeable in the SEM. Surface steps can also be seen in the SEM of the (100) wafer of Figure 5.7 (a) which are similar to steps in the sawtooth structure discussed in Chapter 2.

The surface steps on the (111) planes in Figure 5.6 (a) can be explained by studying the schematics in Figures 5.6 (b) and (c). Etching in <111> directions occurs, since this etch rate is small yet not negligible. The surface steps are due to misalignment of the silicon nitride strips to the crystallographic planes (Chapter 1), and the edges of the silicon nitride strips not being perfectly straight. In Figure 5.6 (b), roughness of the silicon nitride edge is depicted. The (111) planes are pinned by the silicon nitride, and so there are surface steps in the (111) planes. The surface steps expose non-{111} planes at the convex corners, and so are etched quickly. The steps must be etched to the edge of the wafer unless there is a step being etched in the opposite direction (Figure 5.6 (c)). In this case, once the two convex corners come together, the step can be etched away. A detailed study is needed to understand more fully how these steps are etched, and whether they are nearly eliminated given enough etching.

In contrast, there is no etch mask to pin the etch front in the downward direction and no surface steps are noticable on the (111) planes (Figure 5.6(a)). However, the (111) blaze facets are most likely not atomically smooth. Surface curvature of standard wafers is less than 40  $\mu m$  from peak to valley for a standard 4" wafer³. As depicted in Figure 5.6 (d), if the crystallographic planes do not conform with the curvature of the wafer, etching will leave surface steps. The atomic spacing of (111) planes is 1.81 Å. So in this worst case, there would be atomic steps approximately every 0.25  $\mu m$ , assuming also that none of these steps are etched away. Surface steps also nucleate at crystalline defects. Given enough time, an equilibrium density of surface steps is reached on the (111) blaze facets. However, these steps are of such small height and/or density that they were not detected with a AFM and may not be a significant factor in reducing X-ray diffraction efficiency.

Figure 5.6 (a) is an SEM micrograph after KOH etching. Note the roughness of the (111) planes which intersect the silicon nitride. The blaze facets, though, do not have any noticeable steps. Roughness of the silicon nitride is depicted (b). A top view of the silicon nitride and the silicon nitride/silicon interface is depicted (c). Once etching proceeds to the point where the two convex corners come together, the step can be etched away. The entire wafer is depicted (d) with an exagerated surface bowing. (d) is the cross-section of (b) indicated. Surface steps on the blaze surface may result from the wafer bowing or not being polished parallel to the (111) plane.

Figure 5.7 KOH etching of a (100) wafer can also lead to surface steps on the planes that intersect the mask. (a) is the SEM after partial etching of a sawtooth pattern. (b) depicts the positions of the {111} and how etching will proceed.

## 5.5 Cr Evaporation and HF Etch of SiN

For sucessful lift-off a material must protect the silicon blaze facets from the HF, and allow the silicon nitride to dissolve so the underlying silicon is exposed. In Figure 5.8(b), a top view after chromium evaporation and HF,

etching has occurred at the chromium grain boundaries, yet has not completely etched through the layer. However, the chromium on top of the silicon nitride has not been removed. In Figures 5.8(c) and (d), SEMs taken near a cleaved edge, this can be explained by noticing that there is not a large height difference from the regions with silicon nitride and the blaze facets. Hence, the chromium film was continuous.

Figure 5.8 (a) is a sample after KOH etching. (b) shows the etching of the chromium grain boundaries after chromium evaporation and HF. (c) and (d) are along a cleave, where some of the chromium peeled off.

In Figure 5.9, another sample is shown where lift-off was not successful. High pressure  $CO_2$  was used to remove some of the chromium, exposing silicon nitride which had not been etched with HF long enough to completely dissolve. The longer the sample is exposed to the concentrated HF, the longer the chromium protecting the blaze facets is etched. Depositing a thicker chromium film, would allow longer HF etch times. However, if the film is continuous, the silicon nitride will not be exposed to the HF. Clearly, another approach is necessary.

Figure 5.9 Another sample with unsuccessful lift-off. High pressure  ${\rm CO_2}$  was used to blow off the chromium strips revealing that the silicon nitride was not completely removed.

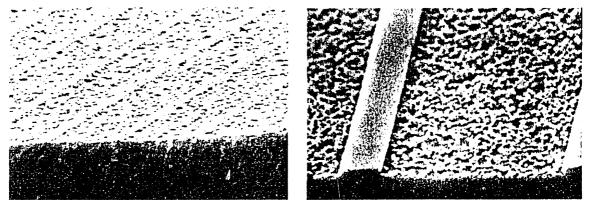

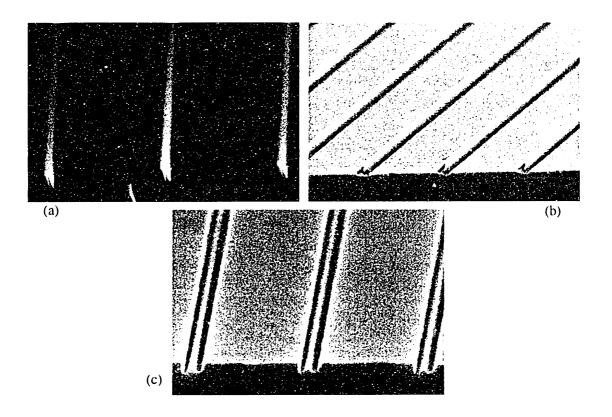

KOH etching until the silicon nitride was greatly undercut was found to give more successful lift-off (Figure 5.10). Etching in the <111> directions, the slowest etching directions was necessary. To increase the etch rate, the KOH concentration was increased to 20% KOH by weight. Etch times were on the order of 15 minutes at room temperature. Adding KOH to water is exothermic. The solution was allowed to cool to room temperature in order to have consistent etch rates.

Figure 5.10 SEMs showing a sample after a long etch in 20% KOH by weight (a), after chromium evaporation and HF etch (b), and after the silicon nubs have been RIE etched down into troughs (c).

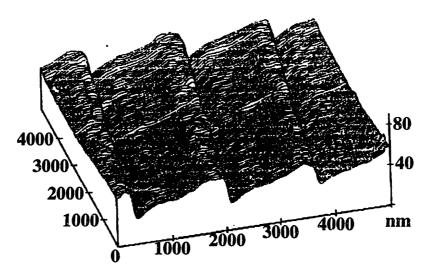

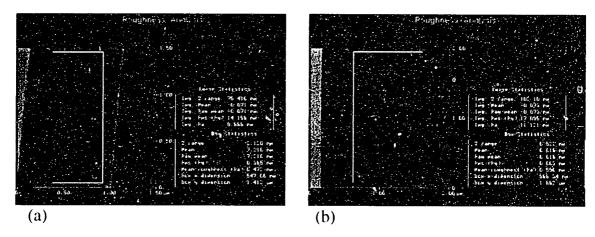

## 5.6 AFM Analysis of Gratings

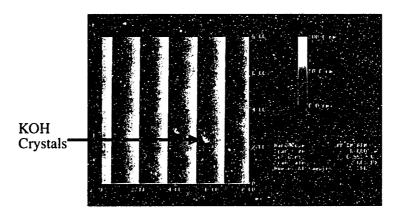

If the KOH solution is not allowed to cool to room temperature, KOH can crystallize out of solution and deposit on the sample in rinsing (Figure 5.11). The crystals are not easily removed in piranha, RCA, or solvents. A similar result has been found to occur when etching silicon to expose silicon nitride membranes for X-ray lithography masks. Rinsing in water heated to the KOH solution temperature or higher, or allowing the KOH solution to cool to room temperature before etching are solutions to this problem.

Figure 5.11 AFM micrograph showing KOH crystals remaining from rinsing the sample in water cooler than the KOH solution. The crystals are not removed with piranha, RCA, or solvents.

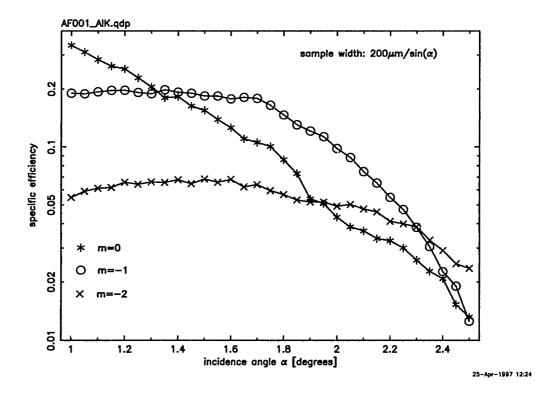

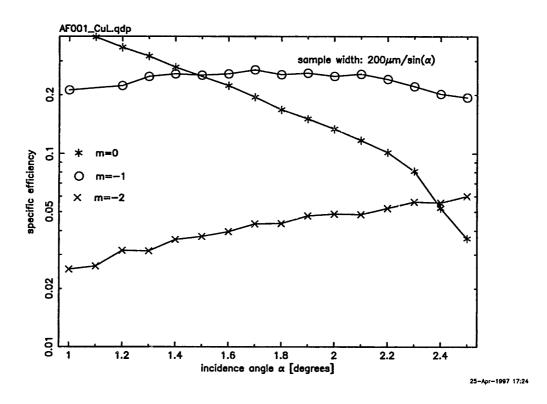

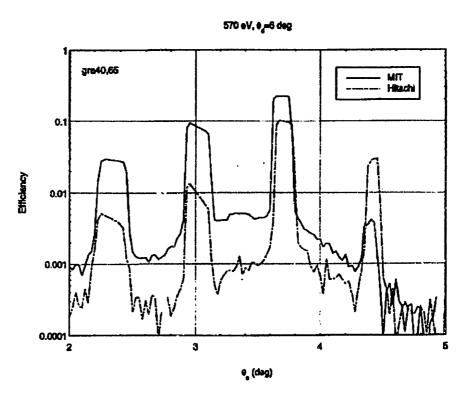

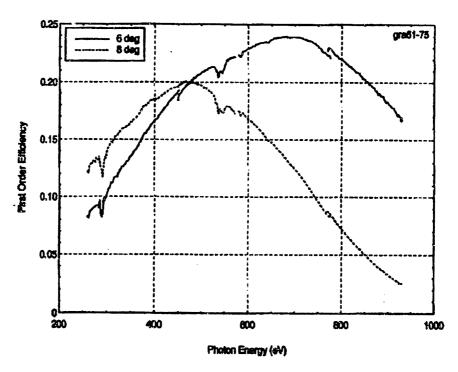

Figure 5.12 AFM micrographs showing how the silicon ledge is reduced (b) by careful RIE of the silicon nubs.