# Enabling HF Power Conversion: Magnetic Components and a Wide Voltage Range Converter

by

Alex J. Hanson

B.E., Electrical Engineering

Thayer School of Engineering at Dartmouth (2014)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2016

© Massachusetts Institute of Technology 2016. All rights reserved.

| Author       | Signature re          | edact | ed                                             |

|--------------|-----------------------|-------|------------------------------------------------|

| Depa         | Signature             |       | May 20, 2016                                   |

| Certified by |                       |       | David J. Perreault Professor Thesis Supervisor |

| A 4 - 1 1    | Signature             | reda  | -                                              |

| Accepted by  | Chair. Department Con | •     | eslie A. Kolodziejski<br>Graduate Students     |

# Enabling HF Power Conversion: Magnetic Components and a Wide Voltage Range Converter

by

#### Alex J. Hanson

Submitted to the Department of Electrical Engineering and Computer Science on May 20, 2016, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

High frequency switching in power converters offers the benefits of high power density and faster transient response; however, high frequency losses have limited efforts to increase frequency into the HF (3–30 MHz) regime. This thesis addresses two of the dominant frequency-dependent loss mechanisms: magnetic material core loss and switching loss. Appropriate metrics are derived to evaluate magnetic materials in core loss limited components. A survey of material core loss shows the potential for significant performance improvement in the HF regime using materials previously overlooked in the power electronics community. One such material is then used in a high frequency converter which achieves zero-voltage switching over a wide range of voltages and powers (e.g. for grid-connected applications). Using appropriate magnetic materials and converter techniques like those presented here, power densities in certain applications can be improved by an order of magnitude by operating at HF.

Thesis Supervisor: David J. Perreault

Title: Professor

# Acknowledgments

This work was supported by funds from Lockheed Martin and Fairchild Semiconductor. Much of the magnetic material data collection and inductor size demonstration was carried out with Julia Belk. Data collection for the wide-range resonant-transition converter was largely carried out by Rachel Yang. The converter was originally conceived by Seungbum Lim and Dave Perreault. Naturally, much of the research direction, planning, and organization was provided by Dave Perreault.

For all of this support, I am grateful.

.

6

# Contents

| 1 | Int | roduction                                                   | 13 |

|---|-----|-------------------------------------------------------------|----|

|   | 1.1 | Background                                                  | 13 |

|   | 1.2 | High Frequency Magnetic Materials and Components            | 15 |

|   | 1.3 | A High Frequency Wide Input Voltage Converter               | 17 |

|   | 1.4 | Impact                                                      | 18 |

| 2 | HF  | Magnetic Materials and Components                           | 19 |

|   | 2.1 | Background                                                  | 19 |

|   | 2.2 | Performance Factors and Modeling                            | 25 |

|   | 2.3 | Core Loss Data Gathering                                    | 30 |

|   | 2.4 | Performance Factor Analysis and Comparison                  | 31 |

|   | 2.5 | Low Permeability Materials are Still Useful                 | 35 |

|   | 2.6 | Conclusion                                                  | 45 |

| 3 | A V | Vide-Operating-Range Converter for High Frequency Operation | 47 |

|   | 3.1 | Background                                                  | 47 |

|   | 3.2 | Converter Operation                                         | 53 |

|   | 3.3 | Advantages and Opportunities                                | 58 |

|   | 3.4 | Design and Optimization                                     | 59 |

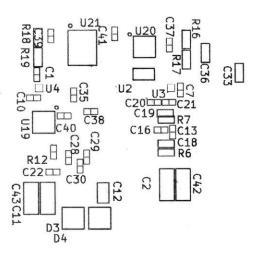

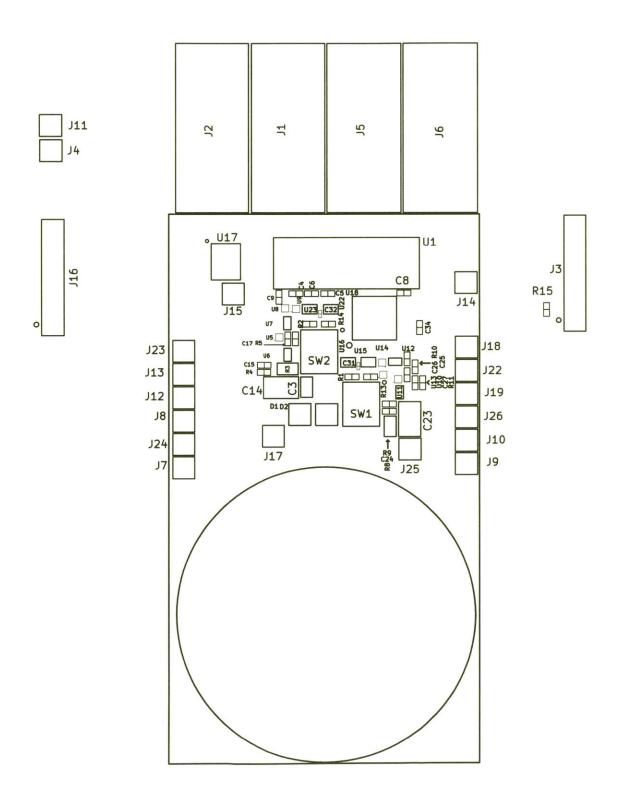

|   | 3.5 | Prototype Implementation                                    | 60 |

|   | 3.6 | Experimental Performance                                    | 64 |

| 4 | Cor | nclusion                                                    | 69 |

| Appendix A | Modified Performance Factor Background and Variations | 71           |

|------------|-------------------------------------------------------|--------------|

| Appendix B | Core Loss Measurement Methods                         | 77           |

| Appendix C | DC Bias and Other Effects                             | 81           |

| Appendix D | ZVS Buck Modes In The Wide-Range Resonant-Transition  | 1            |

| Converter  |                                                       | 85           |

| Appendix E | Wide-Range Resonant-Transition Circuit Analysis       | 91           |

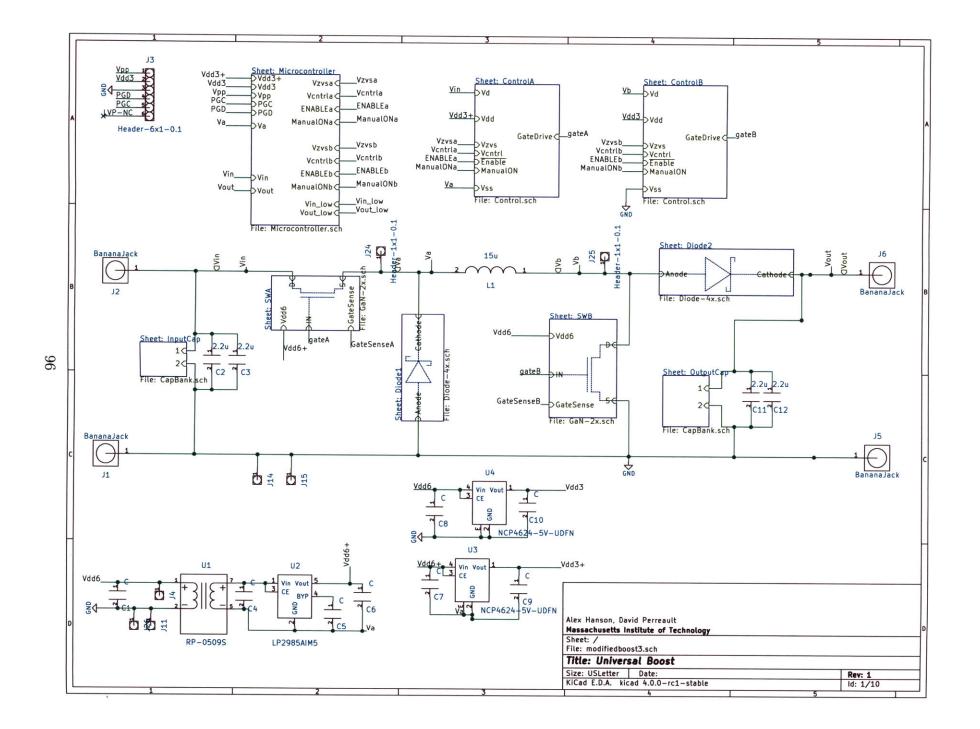

| Appendix F | Converter PCB Schematics                              | 95           |

| Appendix G | Microcontroller Code                                  | 107          |

| Appendix H | PCB Layout Reference                                  | 135          |

| Appendix I | LTSpice Simulation Files                              | l <b>4</b> 5 |

# List of Figures

| 2-1  | Performance factor survey prior to this work                  | 25 |

|------|---------------------------------------------------------------|----|

| 2-2  | Transformer models for examinining performance factor         | 28 |

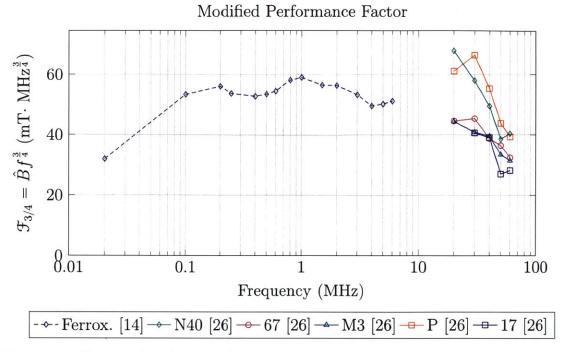

| 2-3  | Modified performance factor survey prior to this work         | 30 |

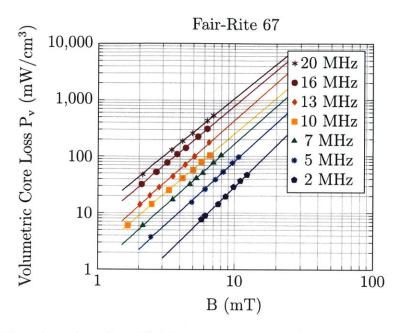

| 2-4  | Fair-Rite 67 Core Loss                                        | 32 |

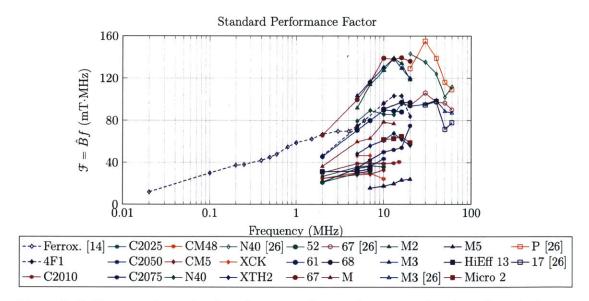

| 2-5  | Performance Factor Survey                                     | 33 |

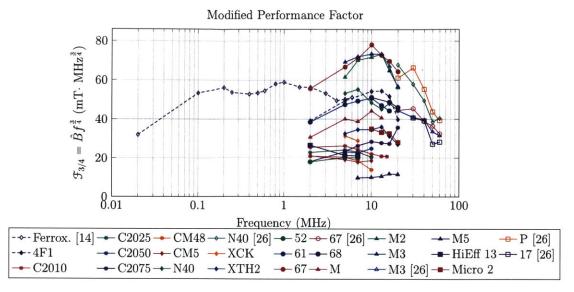

| 2-6  | Modified Performance Factor Survey                            | 34 |

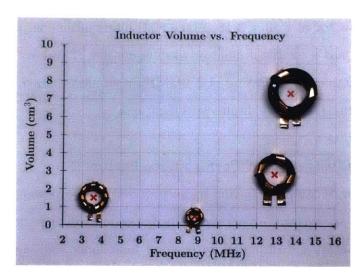

| 2-7  | Inductor sizes vs frequency                                   | 36 |

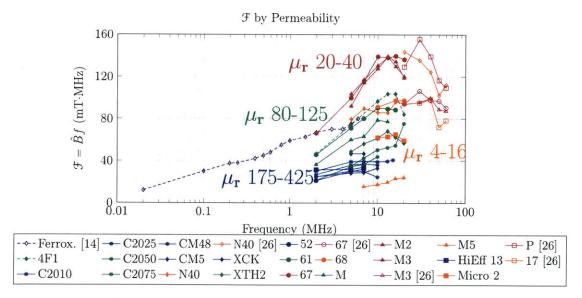

| 2-8  | Performance factor sorted by permeability                     | 36 |

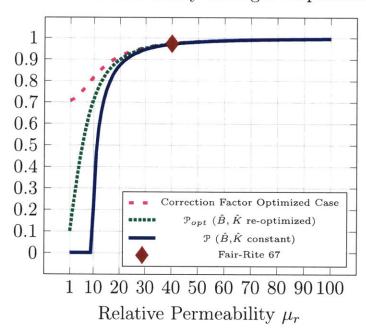

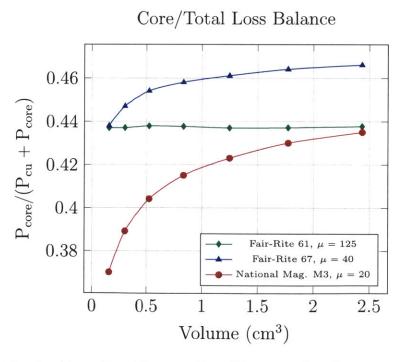

| 2-9  | Power ratio thought experiment                                | 42 |

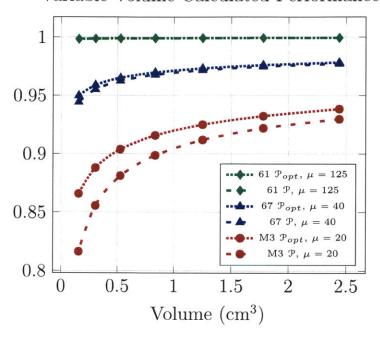

| 2-10 | Power ratio for real materials                                | 44 |

| 2-11 | Loss breakdown for power ratio calculations                   | 44 |

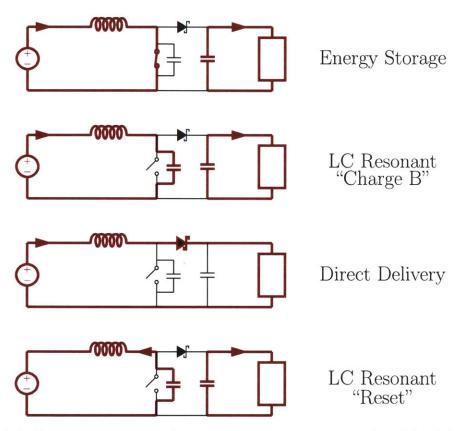

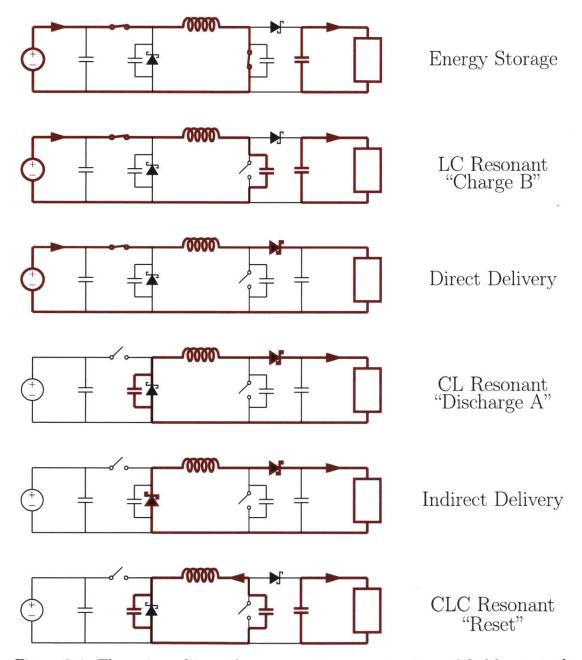

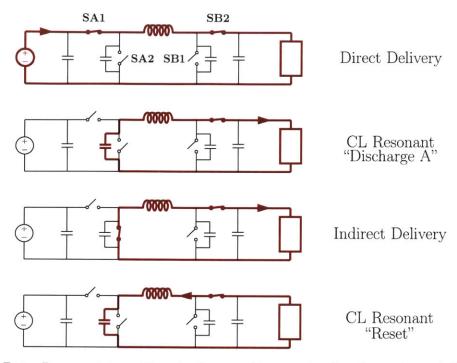

| 3-1  | Resonant-transition boost converter operation                 | 51 |

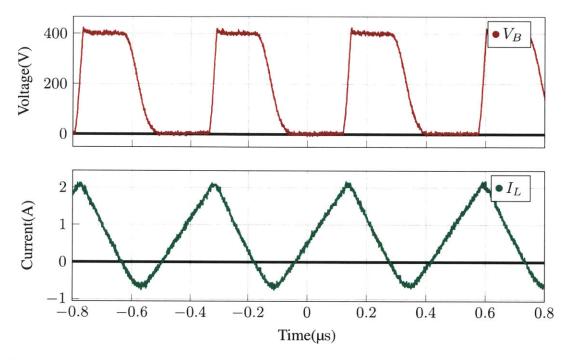

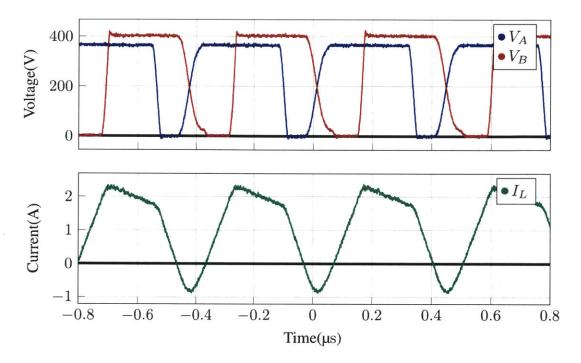

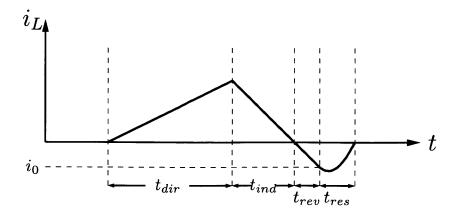

| 3-2  | Resonant-transition boost operating waveforms                 | 52 |

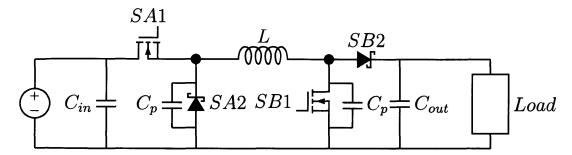

| 3-3  | Wide-range resonant-transition converter                      | 54 |

| 3-4  | Wide-range resonant-transition converter – modified operation | 55 |

| 3-5  | Modified boost mode operating waveforms                       | 56 |

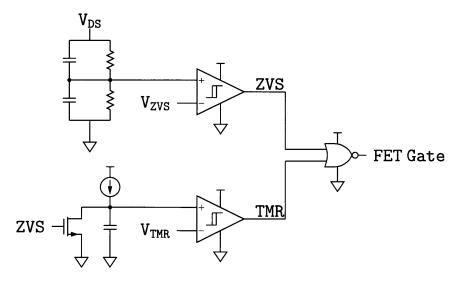

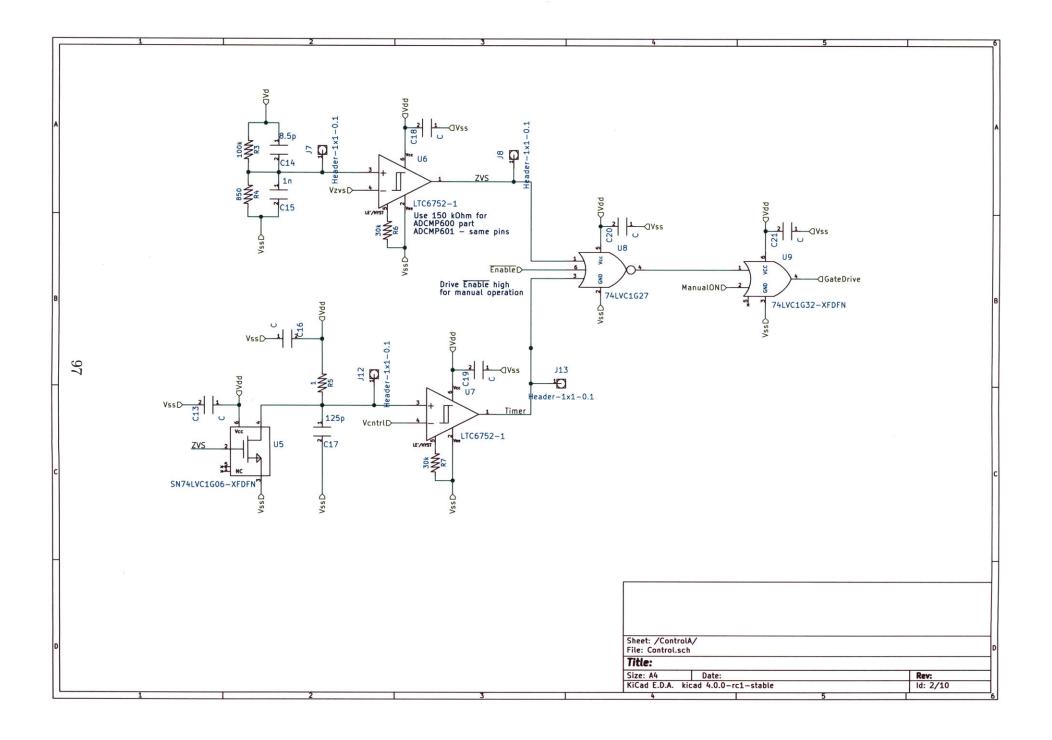

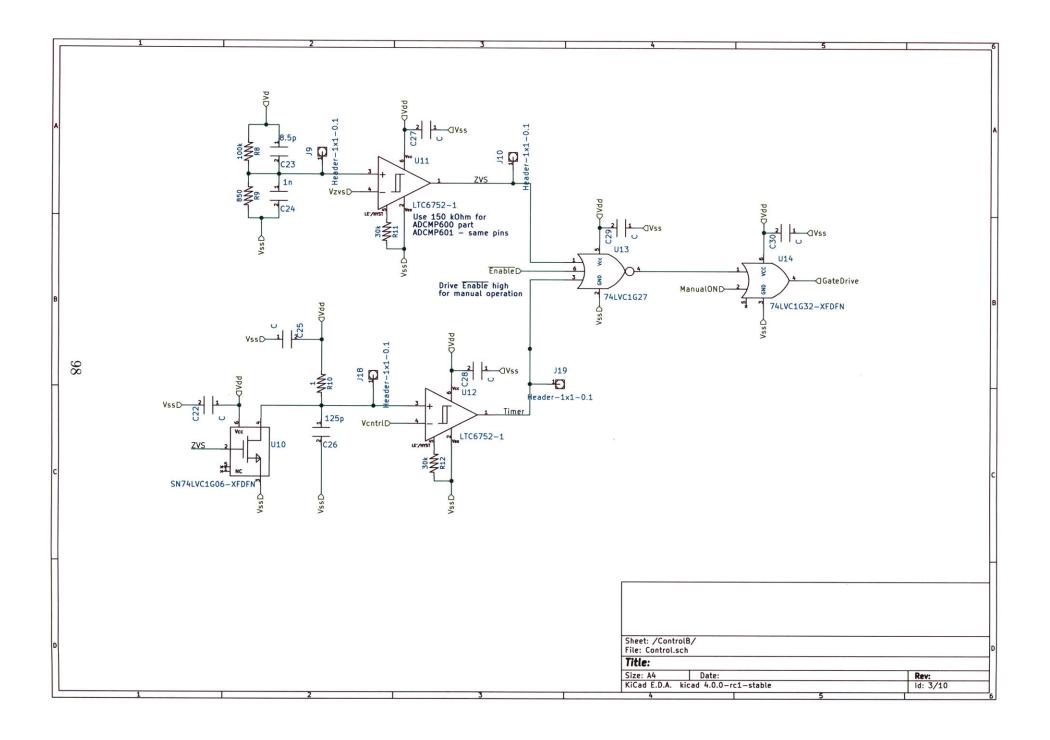

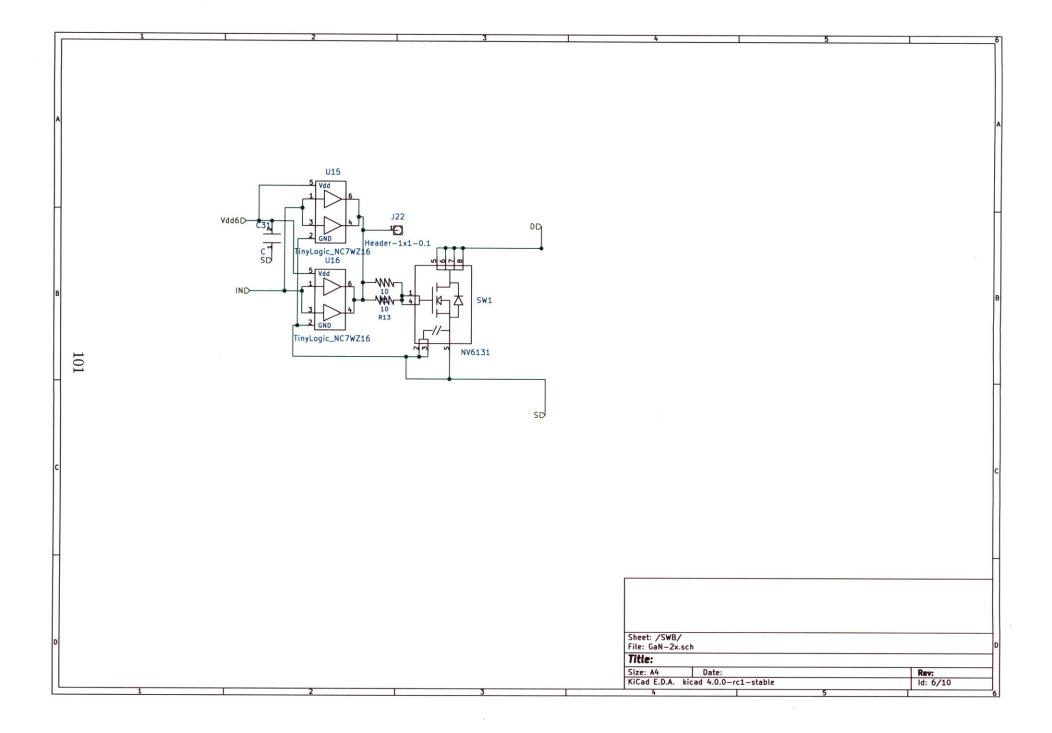

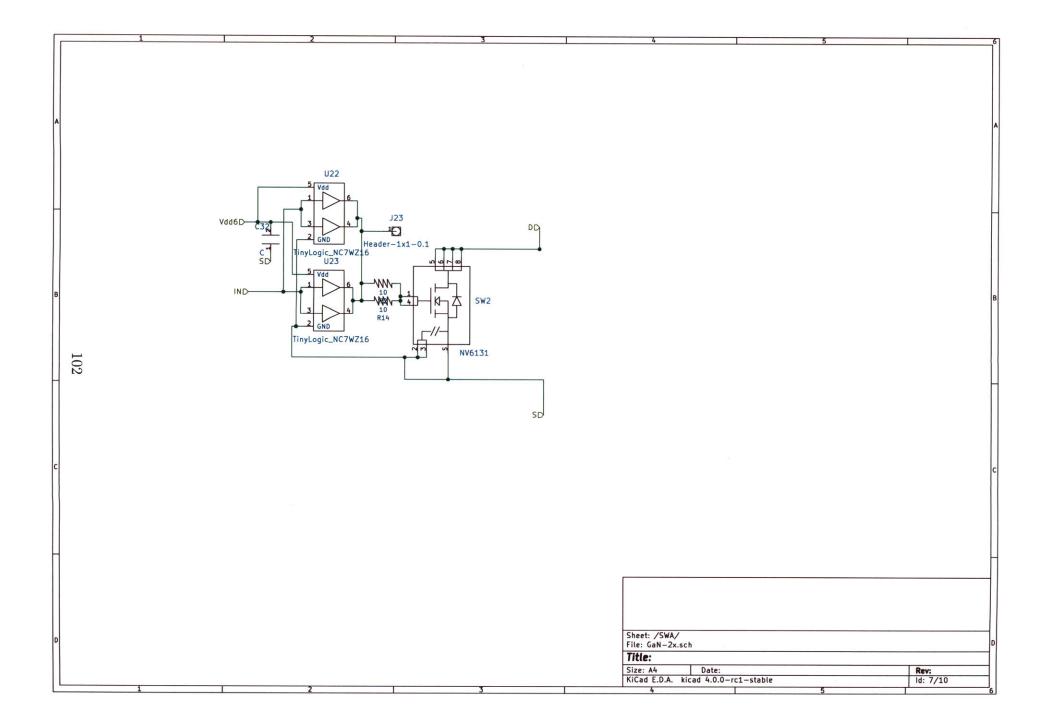

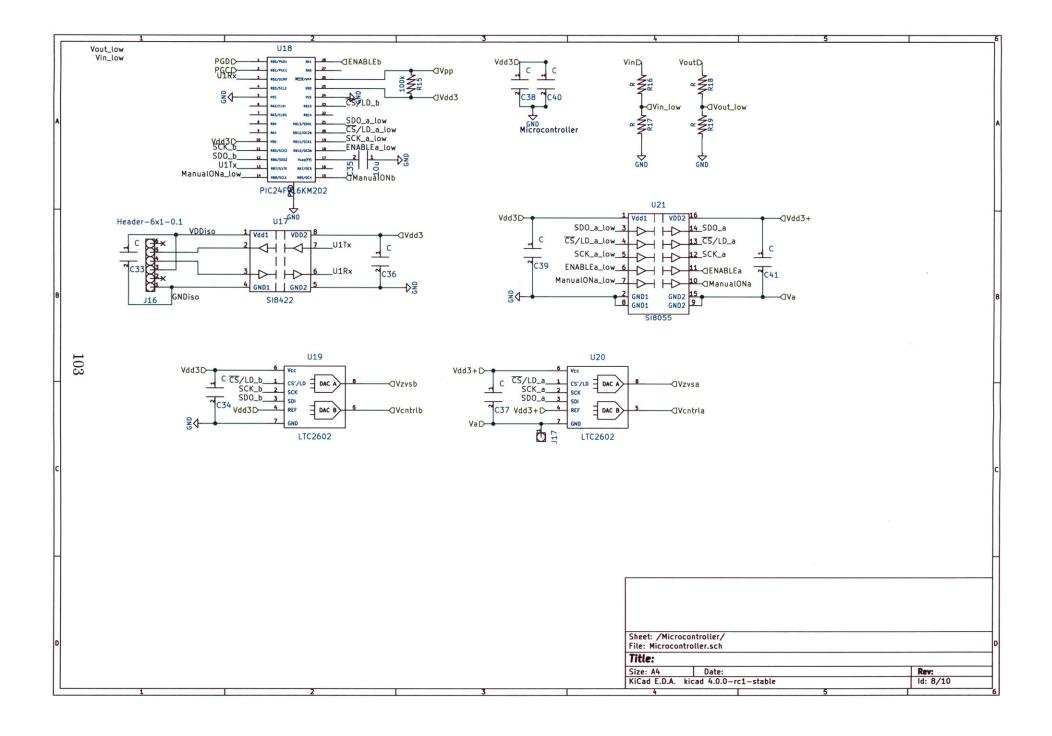

| 3-6  | Actuation control circuit for active FETs                     | 57 |

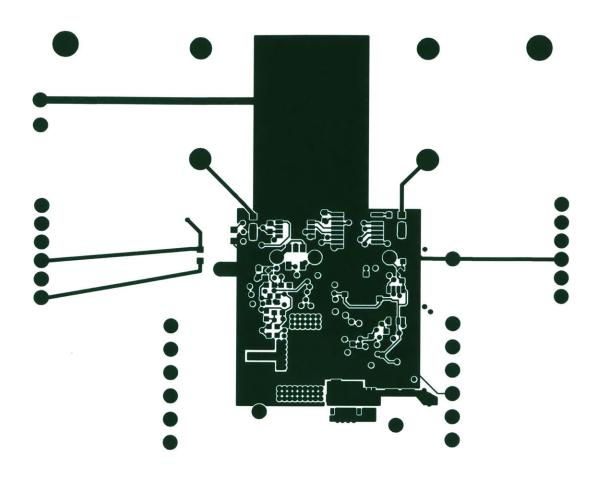

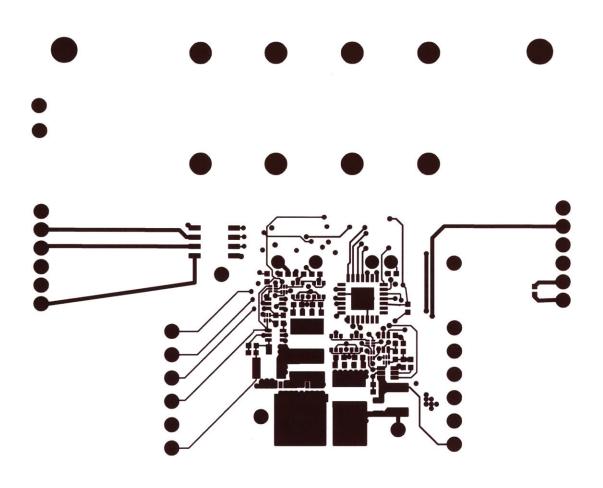

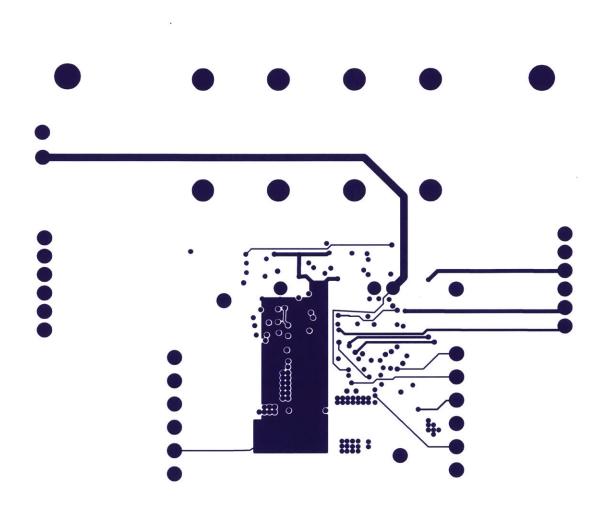

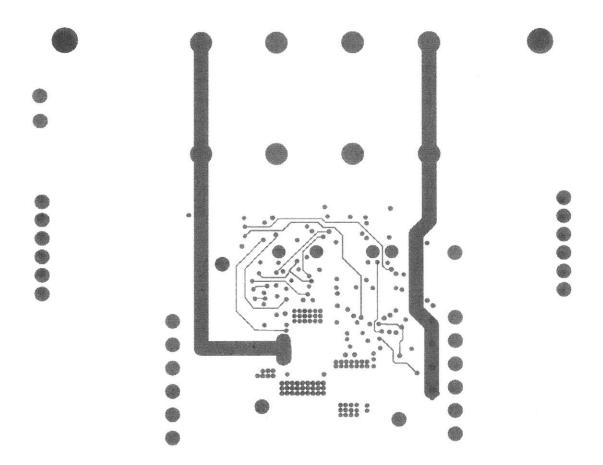

| 3-7  | First prototype board                                         | 64 |

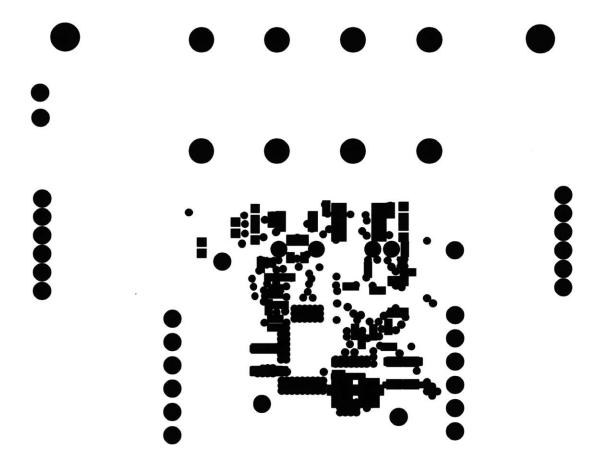

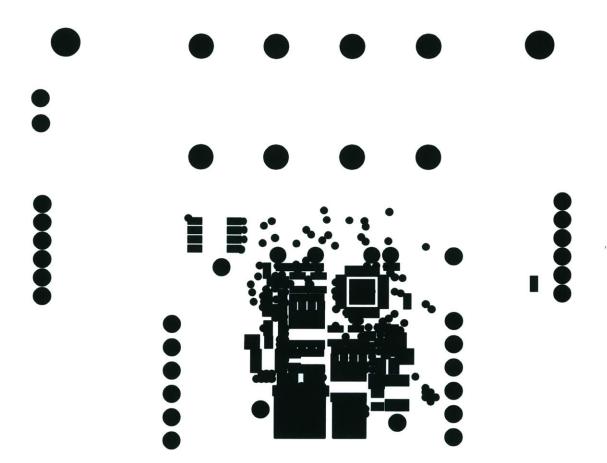

| 3-8  | Second prototype board                                        | 65 |

| 3-9  | Experimental setup                                            | 66 |

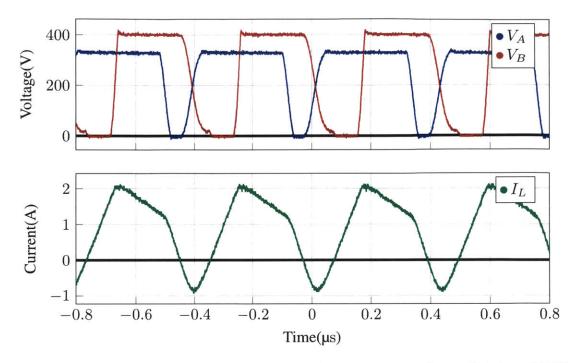

| 3-10 | Modified boost waveforms; second operating point              | 67 |

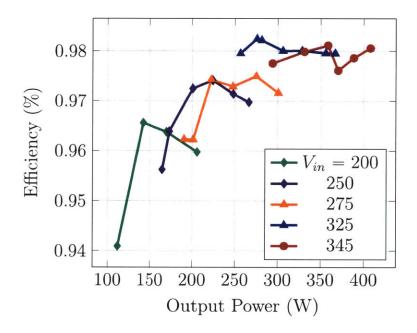

| 3-11 | Experimental efficiency                                       | 68 |

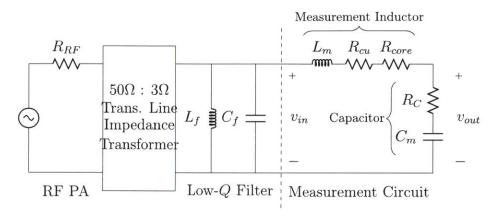

| B-1 | Circuit schematic used for core loss measurement. |     |    |   | • |   |  |   |   | 78 |

|-----|---------------------------------------------------|-----|----|---|---|---|--|---|---|----|

| B-2 | Image of test circuit in operation                |     | •  |   | • |   |  |   |   | 78 |

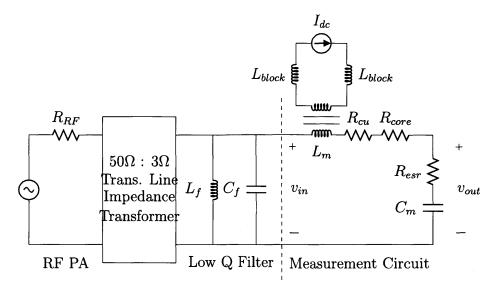

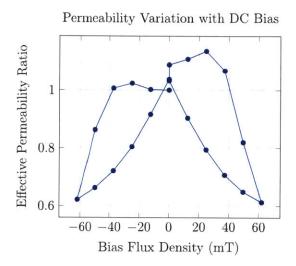

| C-1 | Measurement circuit with dc bias                  |     |    |   |   |   |  |   | • | 82 |

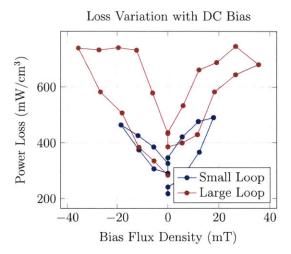

| C-2 | Core loss change with dc bias                     |     |    |   |   |   |  |   |   | 83 |

| C-3 | Permeability change with dc bias                  |     |    |   |   | • |  | • | ٠ | 84 |

| D-1 | Resonant-transition buck converter operation      |     |    |   |   |   |  |   |   | 86 |

| D-2 | Buck mode inductor current for ZVS timing calcula | at: | io | n |   |   |  |   |   | 87 |

# List of Tables

| 2.1 | Measured Steinmetz parameters                                                                      | 32 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 2.2 | VHF Steinmetz parameters reported in the literature                                                | 33 |

| 2.3 | Inductor size/frequency demonstration parameters                                                   | 35 |

| 2.4 | Parameters for power ratio calculations                                                            | 40 |

| 3.1 | Device implementation in two prototype iterations of the wide-range resonant-transition converter. | 63 |

| A.1 | Performance factor variations                                                                      | 75 |

# Chapter 1

# Introduction

# 1.1 Background

# Power Electronics are a Bottleneck for Miniaturized Systems

Energy delivery is a principal challenge of the modern world. Renewable energy sources require ever more sophisticated power electronic interfaces to handle their inherently variable, unreliable, and unpredictable nature. To better utilize the energy that is produced, electrical loads are becoming more demanding in terms of power factor, efficiency, and effective and fast sleep/wake modes. These loads are also increasingly mobile, both as transportable devices and as the transportation itself, making generated energy even more locally precious. As the capability of information electronics has exponentially expanded through Moore's law to consume less power, provide smarter functionality, and fit in the palms of our hands, their power electronic interfaces have become a primary bottleneck to further advancement.

This is not an accident. While a computer's 1s and 0s are essentially the same whether held on a cm-scale vacuum tube or on the gate of a nm-scale transistor, the energy temporarily stored in a power converter's inductors and capacitors is not. When packed into ever smaller volumes, energy-storing fields can cause losses, overheating, material breakdown, material saturation, nonlinearity, and other negative effects. Power electronic components resist concentrated energies.

Power electronics also tend to resist the high speeds demanded by modern loads.

Dynamic switch on-resistances, magnetic core losses, and even conductive wire resistances all increase (sometimes rapidly) with operating frequency. Parasitic reactances also become more prominent at higher frequencies which put limits on speed and complicate simulation, design, and control.

#### High Frequency Offers Performance if Challenges are Overcome

Nevertheless, high operating frequency can be very useful. First, it allows power converters to react rapidly to changing source availability or load demand (e.g. a dormant processor core suddenly demanding full power) [1]. Second, high operating frequency fundamentally allows the use of smaller passive components which typically dominate converter volume and weight. At a basic level, this may be seen in the passive impedances:  $Z_L = L\omega$ ,  $Z_C = 1/C\omega$ : Increased frequency allows the use of smaller L and C values and, in turn, physically smaller components.

State-of-the-art switching frequencies for low-medium power, low-medium voltage converters extend to about 1 MHz. Some work has used frequencies over 30 MHz for very low voltage integrated applications and some higher power applications, but logic speeds limit available control techniques at this frequency and very high magnetic losses and parasitics make these kinds of converters difficult to implement. In between, there is a gap in the high frequency (HF, 3–30 MHz) range which potentially offers great opportunities for high density power conversion.

The challenge, then, is clear: how can the advantages of high frequency power conversion and small size be obtained while avoiding their negative repercussions? In this thesis, two approaches are taken to the solve this challenge. The first aims to improve power converter components, specifically magnetic components, through a materials and design investigation. The second aims to provide, at the converter level, a topology and design framework suitable for high frequency operation. It should be noted that these are two contributions to a larger community effort which includes improvements to other components, topologies for different applications, and system-level holistic design – these efforts are very valuable, but outside the scope of this work.

# 1.2 High Frequency Magnetic Materials and Components

# Power Magnetics Loss Inhibits Size and Frequency Scaling

Magnetic components for power electronics typically consist of one more more windings around a ferromagnetic core. By Ampère's law, current through the windings generates a magnetic flux in the core. Through the magnetic flux and Faraday's law, energy may be transferred to a second winding or stored temporarily and extracted via the same winding. The isolation, voltage/current transformation, and energy storage functions of magnetic components are critical to most power converters; nevertheless these useful components can be problematic, for two reasons. First, they often dominate the size and weight of power converters (usually setting the converter height and occupying ~30-50% of converter PCB area). Second, magnetic component losses are often high and increase rapidly with frequency, resisting that route to miniaturization.

The reason for both of these difficulties may be seen in the Steinmetz equation (1.1), a simplified but useful empirical expression for the core loss in a magnetic component. The power loss per unit volume  $P_V$  is expressed as a function of frequency f and peak magnetic flux density  $B_{pk}$

$$P_V = k f^{\alpha} B_{pk}^{\beta} \tag{1.1}$$

where k,  $\alpha$ , and  $\beta$  are the Steinmetz parameters, material constants with appropriate units. Both  $\alpha$  and  $\beta$  are close to 2 (over a finite range), with  $\alpha$  usually somewhat smaller and  $\beta$  usually somewhat larger. As magnetic flux is packed into a smaller volume  $(B_{pk} \uparrow)$  and as frequency increases  $(f \uparrow)$  power losses quickly result in either unacceptable efficiencies or temperatures.

## Low Permeability Materials Offer High HF Performance

For power magnetic materials at up to a few megahertz, Steinmetz parameters

are published on the material datasheets. However, these data have not been available for higher frequency materials due to both technical and economic factors (see Section 2.1). This has rendered optimized design of cored power magnetic components (i.e. with proper performance tradeoffs) impossible in the HF regime. To open up this design space, we measure and report Steinmetz parameters for a collection of materials suitable for HF operation but previously lacking loss data. To make this possible we use a resonant measurement technique, very different from traditional methods, which provides suitable accuracy at HF (see Appendix B). The data gathered is useful both for design with particular materials and for surveying the materials landscape. This survey reveals the potential for  $\sim 45\%$  improvement in magnetic component power density by increasing frequency from a typical  $\sim 500\,\mathrm{kHz}$  design to about  $10\,\mathrm{MHz}$  by using commercially available materials that have not been widely used for power conversion applications.

Additionally, we find that materials suited to HF operation have lower permeability ( $\mu_r \approx 20-200$ ) than materials typically used for power inductors and transformers at more conventional frequencies ( $\mu_r \approx 800-2000$ ). These materials will require new design paradigms to accommodate or even take advantage of their non-negligible core reluctances and incomplete flux guidance. In this thesis, we begin this work by demonstrating theoretically and experimentally that low permeability does not present a fundamental obstacle to high performance.

Therefore, we will show that

- 1. there are commercially available magnetic materials with useful material properties for power magnetics in the HF regime,

- 2. the advantages of HF operation outweigh the costs in terms of magnetic component performance, and that

- 3. low permeabilities common to HF magnetic materials need not fundamentally limit component performance.

See [2,3] for peer-reviewed publication arising from this work on magnetic materials and components.

# 1.3 A High Frequency Wide Input Voltage Converter

#### New Components Extend HF Converter Application

Many converter components are becoming more suitable for high frequency operation. Through this work, the opportunities for HF magnetic components have been expanded. Modern ceramic capacitors with low loss are available to hundreds of MHz and beyond, and with continued evolution fo semiconductor processes and design, control circuitry continues to operate at higher speeds with more functionality for less power. Wide band gap semiconductor switches based on gallium nitride (GaN) and silicon carbide (SiC) can switch faster than silicon devices at a given voltage/power due to lower capacitance, higher electron mobility, and majority-carrier physics. In order to take full advantage of high performance components, new topologies and approaches to HF design are necessary at the circuit level to realize highly dense and efficient systems.

In particular, the development of 650 V GaN FETs raises the possibility of implementing universal input (120–265 VAC) grid-connected converters in the HF range. Previous converters have required slow high voltage Si switches or complex stacked topologies to reduce voltage stress on GaN switches.

## HF Converters Offer High Performance at Higher Voltage/Power

High frequency operation has challenges that must be met at the circuit level in addition to the component level. For example, switching losses increase rapidly with both voltage and frequency. All real circuit nodes have parasitic capacitance. When a switch turns on with some voltage across its parasitic capacitor, the capacitor is discharged, and the energy is lost. Although the energy is dissipated in a resistive transient V-I overlap, the total energy lost is not a function of the switch resistance value or the switching time. A similar effect is seen in short-circuit charging, which yields a total  $f \cdot CV^2$  power loss. This effect can be avoided through circuit techniques that allow switches to turn on with zero potential across them (zero-voltage-switching

or ZVS). Achieving ZVS at high frequency and high voltage is essential to maintaining thermal and efficiency limits.

As a vehicle for exploring efficient HF converters, we present the design and performance results for a wide-range resonant-transition converter suitable for application in (for example) universal input power factor correction (PFC) stages. Such PFC stages are placed after a grid-connected diode bridge and are designed to draw input current proportional to input voltage, thereby most effectively utilizing the ac grid without corrupting it. Such a PFC converter acts as a rectifier (ac-dc converter), but since the input varies slowly relative to the switching frequency (by roughly five orders of magnitude), it may be considered a dc-dc converter with wide input voltage range. All experimental results will be reported at dc with the understanding that, in full operation, a feedback loop would shape the input current waveform along a line cycle.

# 1.4 Impact

We expect the results of this thesis to be broadly applicable outside of the academic sphere. As the power electronics community moves to implement higher switching frequencies, design of both components and converters will rely on results like these to inform future work and products in industry. Magnetic material data gathered here will be necessary to implement optimized HF inductors and transformers. Additionally, circuit topologies and techniques like those presented here will be critical to achieving HF (and therefore miniaturized) converters that do not succumb to HF loss mechanisms.

Superior power converters will enable greater penetration of renewable energy through flexibility and efficiency improvements, longer battery lives for portable devices, and more intelligent distribution of energy. Relieving this bottleneck will be important in both the near and over the long term.

# Chapter 2

# HF Magnetic Materials and Components

# 2.1 Background

# Unified Circuit and Component Design Minimizes Magnetics Size

Magnetic components are typically the largest and most lossy components in power converters [4]. Their size is not primarily limited by manufacturing capability or modeling barriers (as has been the case for information processing devices), but rather by fundamental physics. A small magnetic component has less area over which to divide core flux  $(B\uparrow)$  and less area over which to divide winding current  $(J\uparrow)$  while still providing the same inductance and processing the same current/power. Therefore, both core and winding loss increase as a component shrinks. Efficiency and thermal constraints prevent designers from continuing this process indefinitely, and magnetic components for power applications are constrained to a minimum size which typically is much larger than most other components (switches, control circuitry, capacitors with similar energy storage) [1]. Scaling of magnetic components is inherently challenging [5].

Three principal strategies have been adopted to decrease the size of magnetic components.

- 1. Reduce the required inductance value through circuit design

- 2. Reduce the required power/current processing through circuit design

- 3. More fully utilize the available volume through advanced geometries and material selection

The required inductance value may be decreased by first examining the inductor circuit constitutive relation,  $v_L = L \frac{di_L}{dt}$ . The required inductance value can principally be reduced by allowing the inductor current to have large swing  $(di_L \uparrow)$  as in resonant or DCM converters, or by increasing the frequency of operation  $(dt \downarrow)$ .

The required power/current processing can be managed through topological choices that reduce required energy storage and/or divert more of the energy storage requirements to other components (typically capacitors). The extreme end of this process is the switched capacitor (SC) power converter, which uses no magnetic components at all. In a way, such circuits fail to take advantage of the dual nature (voltage and current) of electrical energy and have some severe shortcomings. Modern resonant switched capacitor circuits attempt to correct for these disadvantages by reintroducing small magnetic components into the circuit while achieving the majority of the energy storage in capacitors.

Finally, component design has advanced to more fully take advantage of available component volume. Such efforts include thinner insulation on wires, litz wire that more fully utilizes the copper area even at high frequency, 3D printing to optimally cover the whole core surface [6], and the use of printed circuit board (PCB) traces as the component windings for volume sharing and better thermal dissipation. This category also includes materials research into reducing losses, from laminating iron cores to the use of high resistivity ceramic ferrites and powdered-iron cores.

For a given power handling, a magnetic component for high density applications will often have large current swings  $(i_{L,ac} \gtrsim I_{L,dc})$ , operate at high frequency, and will rely on advanced design approaches.

#### Frequency Scaling is Limited by Magnetics Loss

There are limits to the techniques mentioned above. The current swing cannot be greater than that of an ac inductor which carries no dc current. From a component design perspective, some component design techniques either offer only marginal benefit (e.g. 3D printed windings) or are fixed (e.g. material availability). This leaves little room for improvement.

The remaining approach, frequency scaling, rapidly increases several sources of magnetics loss (and converter loss, see Chapter 3). Limitations on frequency not only limit the density of power stage components, but severely limit the density of elements like EMI filters which are not themselves limited by loss but could be made smaller with higher corner frequency requirements. It is possible to mitigate HF losses and access the benefits of high frequency operation by understanding the sources of HF loss.

Skin Effect: A current carrying wire generates a magnetic field, even inside the wire itself. If the current is changing, the changing magnetic field will induce an EMF and hence eddy currents within the wire so as to oppose the change in flux. These currents tend to reinforce the current carried near the edge ("skin") of the wire and cancel the current carried in the center. Current, as a function of depth, is an exponentially decaying function with a characteristic length  $\delta = \sqrt{\frac{\rho}{\pi \mu f}}$ , known as the skin depth. The net effect is that, for wires significantly larger than a skin depth, current is only carried near the surface ("only within a skin depth"), greatly increasing the effective resistance of the wire.

This effect can be mitigated through the use of flat conductors with high surface area to volume ratios or many small strands of individually insulated wire. The latter, when woven/structured to provide good current sharing among the strands, is known as litz wire (from the German *litzendraht*, woven or braided wire) [7,8].

Proximity Effect: Eddy currents may also be induced in a wire due to other sources of magnetic field, typically other nearby wires. In particular, in a multilayer winding structure, the leakage field that must exist between each layer to satisfy Ampere's law increases with the number of layers, and the ratio of high frequency loss to do loss increases as roughly the square of the number of layers [9–11]. This effect limits

the applicability of using many (thin) parallel conductors, which effectively build up to a many layer structure. The specific weaving pattern of litz strands effectively mitigates this problem, though multiple layers of litz wire still incurs a proximity effect penalty.

The analysis of proximity effect can quickly become very complicated and the reader is referred to standard texts for reference [7,9,11]. It suffices to say that the proximity effect increases with frequency and strongly limits the number of layers of conductor that can be used.

Like the skin effect, the proximity effect can be reduced if the conductors are thin compared to a skin depth. In multi-winding components, primary and secondary windings may also be interleaved such that their opposing currents reduce the net fields  $H \propto \sum i$  seen by other conductors.

It should be noted that the mitigation techniques listed above are limited. The skin depth in copper at 10 MHz is 20.6 µm, which is 34 % thinner than 48 AWG wire (roughly the economical limit of individual litz strands), whereas the inverse relationship would be closer to ideal. Even if it were available, such litz wire consumes space in insulation, limiting the window area available for copper. Interleaving transformer primary and secondary turns has a similar effect, but is challenging as every insulating layer (rather than just one) must be rated to for the full isolation voltage rather than the inter-turn voltage.

Core Loss: The magnetic core which is used to guide flux and increase inductance (or magnetizing inductance in the case of a transformer) also has losses associated with alternating magnetic fields. Some of these losses are due to hysteresis in the core B-H loop (note that  $[B \cdot H] = \text{energy}$ , such that the area of the B-H loop is the energy lost per cycle). This hysteresis derives from fundamentally quantum mechanical phenomena which are beyond the scope of this thesis. Nevertheless, the core concept is that microscopic dipoles flip their orientation irreversibly, creating local eddy currents which induce loss. Another component of the loss derives from the macroscopic eddy currents induced in a conducting magnetic core. For this reason, highly conductive iron cores are laminated into magnetically permeable but electri-

cally insulated sheets; high resistivity ferrites suffer less from this effect, but are not immune. Finally, core loss has a component which has frequently been called the "anomalous loss," though there is very little anomalous about it – it is simply a frequency-dependent modification to the so-called "static" hysteresis loss (indeed, the B-H loop expands as frequency increases). As such, it has also been called the "excess eddy current loss" [12]. It should be noted that the fundamental loss mechanisms are, physically, all eddy current losses. The only distinction is the source and scale of interest.

The net effect is a loss which is very difficult to predict from first principles. Even the frequency dependence is uncertain: on a per-cycle basis, the "static" hysteresis loss is independent of frequency, the classical eddy current loss is proportional to frequency, and the "anomalous" loss is frequently unknown.

#### Loss Data is Not Available at HF

A more useful approach to core loss is empirical, with the model from Section 1.2 re-written in (2.1) in the form originally conceived by Steinmetz in 1892 [13]:

$$P_V = k_f B_{pk}^{\beta_f} (2.1)$$

Here there is no explicit frequency dependence; rather, there are different  $k_f$  and  $\beta_f$  values for each measured frequency. Listing Steinmetz parameters as different values at distinct frequencies  $(k_f,\beta_f)$ , rather than as functions of frequency  $(k(f),\beta(f))$  is the convention most commonly followed in industry and the literature. This formulation recognizes that loss is *not* proportional to  $f^{\alpha}$  across a broad range of (especially high) frequencies.

This approach, while tractable, requires empirical core loss data across the range of frequencies of interest. Measurement of core loss can be tedious and error-prone, leading most designers to rely on data provided by the material manufacturer. Unfortunately, core loss data is only available below ~1 MHz [14], for a few reasons. The first is that core loss is difficult to measure at HF. The (very expensive) equipment

that manufacturers use to automate this process uses a technique that is only accurate at lower frequencies [15]. Measuring core loss at HF would require both an investment in expertise about advanced measurement techniques and an investment of time in the tedious measurement process for which no automated equipment currently exists. There is also little incentive to make such an investment; most power electronics markets have designs below ~1 MHz, and most materials that might be appealing for HF power conversion are typically marketed for signal conditioning applications where large-signal core loss is not considered an important parameter.

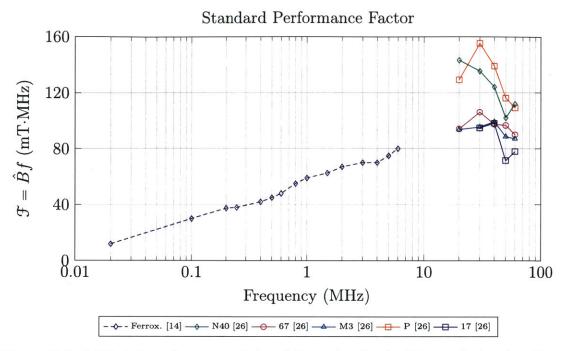

Nevertheless, the data that is currently available indicates some promise in the HF regime. Figure 2-1 shows the state of the art prior to the research presented here. The data is presented in terms of performance factor [16–25] (explained in detail in Section 2.2) which is a figure of merit expressing the power handling capability per unit volume and is effectively a material property. The data from Ferroxcube (a leading manufacturer) is taken as representative of typical power magnetic materials. Each point in this curve represents the highest performing material at that frequency. Also listed is data from several VHF materials from the academic literature.

It can be seen that, generally, increasing frequency increases the available power handling density of a component (assuming appropriate material selection), consistent with the logic presented earlier. However, at VHF, available data points to a negative trend with respect to frequency as core losses overtake the advantages of smaller required inductance values. Two motivating conclusions can be drawn from Figure 2-1. First, there is a lack of data in the HF range, making it difficult to design optimized power magnetic components in that range. Second, it may be hypothesized from the trends in Figure 2-1 that HF magnetic materials would outperform their lower- or higher-frequency counterparts. Data gathered in this thesis will show that this is indeed the case.

#### Material Figure of Merit Ignores HF Winding Losses

The performance factor rests on several assumptions about magnetic component design. Among these is the assumption that winding loss is not a function of fre-

Figure 2-1: Material performance state of the art prior to this work (explanation, etc.)

quency. At HF (indeed, even at MF), this is nearly never the case due to the proximity and skin effects. As such, we first investigate modifications to the concept of performance factor in Section 2.2. Based on more realistic assumptions about HF component design, we arrive at a modified performance factor which takes into account HF winding losses. This modified performance factor is then used to survey magnetic loss data to determine an appropriate operating regime for high density magnetic components. We find that HF operation, with appropriate materials, offers a significant performance increase over lower frequencies (even with the more realistic modified performance factor).

# 2.2 Performance Factors and Modeling

Magnetic component design involves many controllable parameters and hence complex tradeoffs that make optimization difficult. Figures of merit are devised to simplify the design process, allowing for rapid convergence on approximately optimal designs.

One such figure of merit is the performance factor  $\mathcal{F}$  which is meant to reflect the power handling per unit volume of a given material [16–25]. As such, it is related to the achievable power density of a component, and hence of a converter. The larger the performance factor  $\mathcal{F}$ , the more dense a component can be for a given function and loss. With the performance factor, a designer can compare materials against each other across frequency [14].

The performance factor is derived by considering the voltage across and the current through a magnetic component. The voltage across the component is given by  $V = \left|\frac{d\phi}{dt}\right|$ . For a sinusoidal drive, this is  $V = NA_C \hat{B}\omega \sin(\omega t) \propto A_C \hat{B}f$ . It can immediately be seen that the voltage relates directly to the frequency and flux density in the component, both of which contribute to core loss. Thus at increased frequency the allowable flux density peak must be lower (or vice-versa). A low loss component will allow larger flux densities for a given frequency or higher frequencies for a given flux density, and hence will have a higher voltage handling.

The current handling for a component may likewise be related to the current density handling of the windings. While not a reflection of the core material itself, winding losses may discount the attractiveness of high frequency operation for a component. Nevertheless, the traditional performance factor  $\mathcal{F}$  assumes that the current handling of the windings, the maximum ampere-turns or NI, is independent of frequency (i.e. negligible or mitigated skin and proximity effect). Likewise, it is assumed to be independent of the flux density in the core. Thus the relevant current handling proportionality is  $I \propto l_c f^0$ , where a longer core length allows for proportionally wider windings and hence more current. The frequency component is explicitly included for later modification.

A power (or "VA") handling may be defined as the product of the voltage and current handling for the component. Thus  $VA = V_{pk}I_{pk} \propto (A_C\hat{B}f) \cdot (l_cf^0)$ , where the proportionality is meant to isolate fundamental aspects of the core and frequency of operation. The performance factor is the power density achievable by the core  $(\mathcal{F} \propto \frac{VA}{A_Cl_c})$ , and so

$$\mathcal{F}_1 = \hat{B}f^1 \tag{2.2}$$

where the explicit 1 in both the subscript of  $\mathcal{F}$  and the exponent of f will distinguish the standard performance factor  $\mathcal{F}_1$  from its modified counterpart.

It should first be noted that the value of the performance factor depends on the allowable loss level chosen: the core flux  $\hat{B}$  is chosen to be that which provides the specified core loss density at the frequency of interest. Typical core loss values are  $200 \,\mathrm{mW \, cm^{-3}}$  (conservative),  $300 \,\mathrm{mW \, cm^{-3}}$  (typical), or  $500 \,\mathrm{mW \, cm^{-3}}$  (with aggressive cooling or high surface area). For notational simplicity, this parameter is usually stated or assumed in context and is omitted from the performance factor expression  $\mathcal{F}_1$ .

In order to calculate the performance factor, a loss level is first chosen. Then, for any frequency, the maximum sinusoidal flux density amplitude that results in the chosen loss level is found from empirical data or Steinmetz parameters. This flux density is the quantity  $\hat{B}$ . The product  $\hat{B}f^1$  for a given material, plotted against frequency, is a curve which typically rises (as high frequency allows smaller components), peaks, and then falls (as core loss overtakes any high frequency advantage). A material maximizes its power handling density at a particular frequency; thus it is sensible to speak of "low frequency materials" or "high frequency materials" as those which are best utilized and hence "belong" in those regimes.

#### **Transformer Derivation**

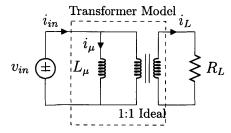

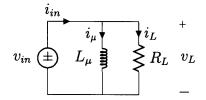

The relationship between the performance factor and the power handling of a component may be illustrated in the simple case of a 1:1 transformer driving a resistive load (Fig. 2-2). Let the peak magnetic flux density be limited to  $\hat{B}$  in accordance with some loss limit. This will relate to the voltage handling of the transformer. Further, let the surface current density in the windings be limited to  $\hat{K} = NI_{in}/l_c$ . This will relate to the current handling of the component. The average power delivered to the

(a) Transformer circuit with transformer model.

#### (b) Simplified Transformer Circuit

Figure 2-2: Transformer circuits used to examine achievable power density and its relationship to performance factor and permeability.

load is given by

$$P_{del} = \frac{1}{2} V_{out} I_{out} \tag{2.3}$$

where capital symbols such as  $V_{out}$  and  $I_{out}$  represent the peak of the load voltage and current waveforms. The peak load voltage is limited by the allowed magnetic flux density induced in the magnetizing inductance. The relationship is given by Faraday's law:

$$V_{out} = V_{in} = \omega N A_c \hat{B} \tag{2.4}$$

The load current is related to the total current by

$$I_{out} = \sqrt{I_{in}^2 - I_{\mu}^2} \tag{2.5}$$

where  $I_{\mu} = V_{in}/(\omega \mu L_{\mu})$  is the peak current through the equivalent magnetizing inductance.

Thus the power deliverable to the load with constraints on magnetic flux density

and surface current density is given by

$$P_{del} = \frac{1}{2} V_{out} I_L = \frac{1}{2} \omega N A_c \hat{B} \sqrt{\left(\frac{\hat{K}l_c}{N}\right)^2 - \left(\frac{l_c \hat{B}}{N\mu}\right)^2}$$

(2.6)

This can be rearranged and expressed in power per unit core volume as:

$$\frac{P_{del}}{A_c l_c} = (\pi \hat{K})(\hat{B}f) \sqrt{1 - \left(\frac{\hat{B}}{\hat{K}\mu}\right)^2}$$

(2.7)

where the volumetric power handling is shown proportional to the performance factor  $\mathcal{F}_1 = \hat{B}f^1$ . The effect of frequency dependent current handling  $\hat{K}(f)$  will be discussed in the next section. Core permeability (usually assumed to be large) also plays a role in (2.7). Its impact for low-permeability materials is considered in Section 2.5.

#### **Modified Performance Factor**

The transformer example suggests that the performance factor can be modified to include high frequency winding effects by changing the expression for  $\hat{K}$ . The most common scenario would be to include only skin effect at HF, as single-layer windings are used to avoid proximity effect losses and litz wire is unlikely to compensate for small skin depths. To maintain fidelity to the winding same loss  $I_{rms}^2 R_{eff}$ , as the effective resistance increases with frequency  $(R_{eff} \uparrow)$ , the current handling must decrease  $(I_{rms} \downarrow)$  to maintain constant loss. Since skin-effect resistance increases with  $\sqrt{f}$ , current handling must decrease as  $f^{-\frac{1}{4}}$ . The current density limit  $\hat{K}$  can then be expressed as  $\hat{K} = K_0 f^{-\frac{1}{4}}$ . The derivation of the performance factor follows as before, resulting in the modified performance factor:

$$\mathcal{F}_{3/4} = \hat{B}f^{\frac{3}{4}} \qquad . \tag{2.8}$$

The original performance factor could be modified to account for different assumptions than for a single layer winding. However, these other modified forms are less likely in practice at HF, and are therefore considered in Appendix A. For the remainder of

Figure 2-3: Survey of modified performance factor, incorporating data from industry, the literature, and this work.

this thesis, the term "modified performance factor" will refer to  $\mathcal{F}_{3/4}$ .

From (2.8), it is clear that the modified performance factor discounts the benefit of high frequencies. Whether this makes HF attractive or not, as with the standard performance factor, depends on empirical data of available materials. To illustrate this, compare the standard performance factor calculated from existing data (Fig. 2-1) with the modified performance factor calculated from the same data (Fig. 2-3). The effect of the  $f^{-1/4}$  factor is clearly evident, showing that the modified performance factor remains roughly constant throughout the MF regime. However, extrapolating backwards from the VHF data clearly suggests that HF materials have the potential for very high performance.

# 2.3 Core Loss Data Gathering

As discussed in the background, core loss data is lacking for HF materials. Some VHF data exist from academic sources only [26] and, by those frequencies, shows a rapid decline in performance. Available data in Figures 2-1 and 2-3, however, suggests that HF materials may achieve higher power density than both their MF and VHF counterparts.

Using the method described in Appendix B and [26], we measured core loss characteristics for 20 materials from a variety of manufacturers. Materials were chosen based on complex permeability – stable real parts and low imaginary parts into the HF regime were considered candidates for experiment<sup>1</sup>. Core loss measurements were made under free convection for a set of discrete frequencies and at sufficiently many values of  $B_{pk}$  to fit a curve based on the Steinmetz equation (2.1) (empirical data conforms strongly to this model, so only a handful of data points are necessary to curve fit at a given frequency). While core loss data is frequently reported graphically in manufacturer datasheets (as in Figure 2-4), it may be represented more compactly by Steinmetz parameters alone. We report our experimental data in this format in Table 2.1. We also reproduce, for completeness, data from [26] in Table 2.2 in the same manner.

## Applicability of Data

Several factors influence the applicability of the data in Table 2.1. These are considered in Appendix C.

# 2.4 Performance Factor Analysis and Comparison

The core loss data in Table 2.1 is used to calculate both the standard performance factor  $\mathcal{F}_1$  and the modified performance factor  $\mathcal{F}_{3/4}$ , using a loss density of  $P_v = 500 \,\mathrm{mW \, cm^{-3}}$ . The data is presented in Figures 2-5, 2-6 along with previously available data.

Generally, it can be seen that the maximum performance factor of available materials increases roughly as  $\sqrt{f}$  between 20 kHz and 100 kHz, indicating that increased

<sup>&</sup>lt;sup>1</sup>This selection method is only a heuristic, as small-signal measurements like complex permeability do not accurately account for large-signal behavior. Nevertheless, this method helps narrow a very wide field to promising candidate materials.

Figure 2-4: Core loss data from Fair-Rite 67 as a sample material suitable for HF operation. Fair-Rite 67 has a nominal relative permeability  $\mu_r = 40$ .

Table 2.1: Steinmetz parameters measured in this work for commercially available materials at HF,  $P_v = k \times B^{\beta}$ , where  $P_v$  is in  $mW/cm^3$  and B is in mT; valid for  $P_V < 1000\,mW/cm^3$ .

| Frequ                       | ency→   | 2 N  | 1Hz  | 5 N   | 1Hz  | 7 N   | 1Hz  | 10 N  | $_{ m MHz}$ | 13 N  | MHz  | 16 N  | MHz  | 20 N  | ИHz  |

|-----------------------------|---------|------|------|-------|------|-------|------|-------|-------------|-------|------|-------|------|-------|------|

| Material                    | $\mu_r$ | k    | β    | k     | β    | k     | β    | k     | β           | k     | β    | k     | β    | k     | β    |

| Ceramic Magn. C2010 [27]    | 340     | 0.20 | 2.89 | 2.61  | 2.56 | 10.61 | 2.23 | 22.23 | 2.29        | 51.55 | 2.04 | -     |      | -     | -    |

| Ceramic Magn. C2025 [27]    | 175     | 0.49 | 2.67 | 3.14  | 2.58 | 11.33 | 2.27 | 30.15 | 2.20        | 1-    | 72   |       | 12   | -     | -    |

| Ceramic Magn. C2050 [27]    | 100     | 0.52 | 2.9  | 2.47  | 2.75 | 5.25  | 2.76 | 12.44 | 2.50        | -     | -    | 1-1   | -    | -     | -    |

| Ceramic Magn. C2075 [27]    | 50      | -    | - /- | 2.31  | 2.77 | 3.42  | 2.77 | 5.81  | 2.76        | 11.88 | 2.69 | 20.67 | 2.61 | 19.57 | 2.45 |

| Ceramic Magn. CM48 [27]     | 190     | 0.59 | 2.68 | 7.49  | 2.33 | 21.5  | 2.17 | 80.01 | 2.05        | -     | -    | -     | -    | -     | -    |

| Ceramic Magn. CM5 [27]      | 290     | 0.61 | 2.66 | 9.42  | 2.29 | 22.55 | 2.19 | 42.04 | 2.08        | -     | -    |       | -    | -     | _    |

| Ceramic Magn. N40 [27]      | 15      | -    |      | 1.52  | 2.09 | 3.04  | 2.00 | 6.61  | 2.01        | 11.09 | 2.02 | 12.47 | 2.06 | 21.20 | 2.04 |

| Ceramic Magn. XCK [27]      | 210     | 150  | -    | 1.07  | 2.75 | 4.86  | 2.44 | -     | -           | -     | 7-1  | -     | -    | -     | -    |

| Ceramic Magn. XTH2 [27]     | 80      | - 1  | -    | 0.83  | 2.82 | 1.72  | 2.72 | 3.86  | 2.68        | 7.07  | 2.57 | 15.20 | 2.57 | 42.00 | 2.38 |

| Fair-Rite 52 [28]           | 250     | 0.46 | 2.97 | 5.44  | 2.53 | 14.44 | 2.32 | -     | -           | -     | -    | -     | -    | -     | -    |

| Fair-Rite 61 [28]           | 125     | 0.08 | 2.79 | 0.42  | 2.67 | 0.83  | 2.62 | 1.80  | 2.56        | 4.31  | 2.47 | 6.66  | 2.53 |       |      |

| Fair-Rite 67 [28]           | 40      | 0.10 | 2.44 | 0.69  | 2.20 | 1.11  | 2.18 | 2.09  | 2.08        | 2.91  | 2.18 | 6.06  | 2.04 | 10.95 | 1.99 |

| Fair-Rite 68 [28]           | 16      | -    | -    | -     | 1-   | (4)   | -    | 3.92  | 2.2         | -     | -    | 11.71 | 2.08 | 22.67 | 1.96 |

| Ferroxcube 4F1 [14]         | 80      | 0.15 | 2.57 | 1.11  | 2.27 |       | -    | 2.86  | 2.28        | 6.53  | 2.09 | 10.89 | 2.05 | 23.20 | 2.14 |

| Metamagnetics HiEff 13 [29] | 425     | 0.11 | 3.06 | 10.44 | 2.10 | 12.69 | 2.32 | -     | _           | -     | _    | 121   | -    | -     |      |

| Micrometals 2 [30]          | 10      | -    | -    |       | -    |       | -    | 10.97 | 2.09        | 19.32 | 2.07 | 28.79 | 2.04 | 57.09 | 2.00 |

| National Magn. M [31]       | 125     | 0.03 | 3.36 | 0.45  | 2.83 | 1.35  | 2.69 | 2.52  | 2.57        | 5.23  | 2.56 | _     |      | -     | 2.00 |

| National Magn. M2 [31]      | 40      | -    | -    | 0.41  | 2.44 | 0.69  | 2.36 | 1.45  | 2.3         | 2.85  | 2.18 | 5.39  | 2.13 | 12.58 | 2.07 |

| National Magn. M3 [31]      | 20      | - 4  | 2    | 0.85  | 2.10 | 1.66  | 2.03 | 2.55  | 2.05        | 4.87  | 1.95 | 7.54  | 2.01 | 14.44 | 1.98 |

| National Magn. M5 [31]      | 7.5     | -    | -    | -     | 1-1  | 90.34 | 2.14 | 147.6 | 2.17        | 198.3 | 2.21 | 225.1 | 2.12 | 335.1 | 2.15 |

Table 2.2: Steinmetz parameters measured in [26] (reproduced here for completeness) for commercially produced materials at VHF,  $P_v=k\times B^\beta,$  where  $P_v$  is in  $mW/cm^3$  and B is in mT; valid for  $P_V<1000\,mW/cm^3.$

| Freq              | uency→  | 20 MHz |      | 30 MHz |      | 40 MHz |      | 50 MHz |      | 60 MHz |      | 70 N | ИHz |

|-------------------|---------|--------|------|--------|------|--------|------|--------|------|--------|------|------|-----|

| Material          | $\mu_r$ | k      | β    | k      | β    | k      | β    | k      | β    | k      | β    | k    | β   |

| National Magn. M3 | 20      | 0.0008 | 3.46 | 0.0068 | 3.24 | 0.191  | 2.45 | 1.03   | 2.15 | 1.76   | 2.11 | - 2  |     |

| Ferronics P       | 40      | 0.036  | 2.29 | 0.051  | 2.33 | 0.218  | 2.18 | 0.696  | 2.09 | 1.34   | 2.04 | 1-1  | -   |

| Fair-Rite 67      | 40      | 0.142  | 2.12 | 0.210  | 2.18 | 0.740  | 2.04 | 1.150  | 2.05 | 2.40   | 1.97 | -    | _   |

| Ceramic Magn. N40 | 15      | 0.0364 | 2.23 | 0.227  | 2.02 | 0.518  | 2.00 | 0.208  | 2.58 | 0.690  | 2.25 | -    | -   |

| Micrometals 17    | 4       | - 1    | -    | 0.0361 | 2.76 | 0.0825 | 2.72 | 1.860  | 2.10 | 1.95   | 2.16 | 2.35 | 2.2 |

Figure 2-5: Survey of standard performance factor, incorporating data from industry, the literature, and this work.

Figure 2-6: Survey of modified performance factor, incorporating data from industry, the literature, and this work.

frequency can improve power density in that regime. From  $100 \,\mathrm{kHz}$  to the edge of the HF regime, the improvement is slower (approximately  $\propto f^{1/4}$ ). Indeed, high frequency winding effects become important in this regime – taking them into account with the modified performance factor shows little improvement up to about  $2 \,\mathrm{MHz}$ .

However, both the standard and modified performance factors indicate that some materials have superior performance in the HF range. The performance increase from 2 to 10 MHz is about 100 % in the standard performance factor (which would apply if, theoretically, frequency-dependent increases in winding losses could be made negligible at HF). The more realistic case of a single layer winding with skin effect is demonstrated by the modified performance factor, which shows approximately 45 % improvement between 1 and 10 MHz.

This improvement is substantial for loss-limited power stage components. Additionally, the size of auxiliary components (e.g. EMI filters) which are not bounded by core loss can be shrunk much more. If the use of HF materials allows the power stage to operate at higher frequency (e.g. 10x) without significant sacrifice (or even some gain), then filter corner frequencies are increased by the same factor (10x). If filter quality factors are held constant, both the capacitive and inductive elements would

be reduced by a factor of  $\sqrt{10} \approx 3.16$ . Since EMI filters often compose > 20 % of system volume, this has a sizable impact on system density. This effect is demonstrated in [32], where a converter operating at 5–10 MHz is smaller than the EMI filter alone of a 100 kHz counterpart with similar specifications.

#### **Experimental Illustration of Performance Factor**

The performance factor is meant to be proportional to power handling density. This feature is demonstrated experimentally for the modified performance factor in Figure 2-7. Inductors are designed with equal impedance and equal quality factor (for a given sinusoidal current) across frequency. Lower frequency requires a larger inductance L, increasing the size. Higher frequency designs suffer from increased losses, requiring more core area to achieve the same Q. There is an optimal frequency in between. By comparing with Figure 2-6, it can be seen that the inductor with the highest power density is designed at the frequency where  $\mathcal{F}_{3/4}$  peaks (around 9 MHz for Fair-Rite 67). This both shows the validity of the modified performance factor metric and provides a striking visual example of the relationship between frequency, material selection, and final component volume. Similar relationships for lower-frequency materials can be seen in [1,5,11].

# 2.5 Low Permeability Materials are Still Useful

Table 2.3: Power inductors designed for identical impedance and large-signal quality factor at an ac current of 1.6 A, corresponding to those in Fig. 2-7.

| Frequency<br>MHz | $\begin{array}{c} \textbf{Impedance} \\ 1\Omega \end{array}$ | Large-Signal Q | $\begin{array}{c} \textbf{Volume} \\ \text{cm}^3 \end{array}$ | P/N        |

|------------------|--------------------------------------------------------------|----------------|---------------------------------------------------------------|------------|

| 3.58             | 36.5                                                         | 212            | 1.50                                                          | 5967001801 |

| 8.83             | 33.7                                                         | 193            | 0.49                                                          | 5967001101 |

| 12.90            | 33.4                                                         | 220            | 2.83                                                          | 5967001001 |

| 13.70            | 39.9                                                         | 202            | 7.33                                                          | 5967002701 |

Many of the materials with high performance factor in Figure 2-6 have relatively low permeability ( $\mu_r < 250$ ) for power applications, with some of the highest per-

Figure 2-7: Inductors using ungapped toroidal cores of Fair-Rite 67 material ( $\mu_r = 40$ ) designed for sinusoidal current at an impedance level of approximately 35  $\Omega$  and a quality factor of approximately 200 (see Table 2.3). The figure illustrates the inductor volume vs frequency at a given quality factor. Minimum inductor volume (highest power density) is achieved in the frequency range where material performance factor peaks.

Figure 2-8: Performance factor sorted by permeability. Curves shown in orange are for relative permeabilities of 4–16, those in red are for relative permeabilities of 20–40, in green for relative permeabilities of 80–125 and in blue for relative permeabilities of 175–425. It can be seen that materials having permeabilities of 20–40 often have the highest performance factor in the HF range.

forming materials having  $\mu_r \approx 40$  (see Fig. 2-8). High permeability is sometimes thought to be important for the design of magnetic components. However, we will show that only very modest permeabilities are needed for effective HF power magnetics design – a requirement which is easily satisfied by the majority of materials that have experimentally shown high performance at HF. Thus, though neither the standard performance factor  $\mathcal{F}$  nor the modified performance factor  $\mathcal{F}_{3/4}$  directly depend on permeability, they can still be used to identify high performance materials for HF magnetics design.

#### In Inductors

The impact of permeability may most simply be shown for the case of an inductor. In power applications, a gapped inductor is almost always used to reduce core loss [33]. For this case, the inductance value is given by

$$L_{gapped} = \frac{N^2}{\mathcal{R}_{tot}} = \frac{\mu_0 N^2 A_g}{l_g + \frac{l_c}{\mu_r}}$$

(2.9)

where  $A_g$  and  $l_g$  are the gap area and length,  $l_c$  is the length of the core, N is the number of winding turns, and  $\mu_r$  is the relative permeability of the core. It can immediately be seen that high permeability has a diminishing impact on inductance once  $\frac{l_c}{\mu_r} \ll l_g$ .

If the core permeability were decreased (imagining this to be possible independent of other material parameters), the length of the gap  $l_g$  would have to be decreased to compensate and maintain the same inductance. Since the total core reluctance  $\mathcal{R}_{tot}$  and the number of turns N are held constant, both the flux density swing (and hence core loss) and the winding loss are the same. Therefore, the power handling is independent of permeability until the core reluctance is so large that the gap is no longer necessary ( $l_g \to 0$ ). Past this point, the only way to maintain inductance while continuing to decrease permeability is to increase the number of turns, compromising winding loss and hence power handling.

Thus there is a permeability threshold above which the material performance is

independent of the actual permeability value for purposes of gapped inductor design. For a given scenario if the permeability threshold were, say,  $\mu_r = 10$ , then performance would be no different between materials with  $\mu_r = 10$  or  $\mu_r = 1000$  (other factors held constant). The permeability threshold occurs at the value which produces the desired inductance for the desired core size and number of turns with no gap.

$$\mu_{r,threshold} = \frac{Ll_c}{\mu_0 N^2 A_c} \tag{2.10}$$

Thus, we see diminishing returns on increasing permeability. In the case of inductors, the advantage of permeability decays to zero at the threshold.

#### In Transformers

The principle of diminishing returns on permeability for transformers will be shown to also hold for cases where the loss associated with magnetizing the core is considered to be a principal consideration in permeability requirements<sup>2</sup>. In this case, the advantage will merely approach zero as permeability increases.

The transformer calculation was already done in Section 2.2. The resulting power density from (2.7) is repeated here for convenience:

$$\frac{P_{del}}{A_c l_c} = (\pi \hat{K})(\hat{B}f) \sqrt{1 - \left(\frac{\hat{B}}{\hat{K}\mu}\right)^2}$$

(2.7 Revisited)

$$=$$

(Constant)( $\mathcal{F}$ )(Correction Factor)

The use of the standard performance factor or the modified performance factor only affects  $\hat{K}$  and will be ignored in discussing permeability.

For a transformer, the magnetic material permeability both guides flux and increases the magnetizing impedance. However, in considering additional conduction

<sup>&</sup>lt;sup>2</sup>Low permeability cores will also have a greater degree of leakage. This challenge can be addressed at the component level through innovative magnetic structures and winding patterns and also at the circuit level by incorporating leakage inductance into circuit operation (e.g. in an LLC converter).

losses required for magnetization of the core, increasing the shunt impedance of the magnetizing inductance is only important when  $|Z_{\mu}| \sim R_L$ . Once  $|Z_{\mu}| \gg R_L$ , the benefit saturates and additional permeability cannot significantly reduce conduction loss associated with magnetization and thereby improve component performance. The correction factor  $\sqrt{1-(\frac{\hat{B}}{\hat{K}\mu})^2}$  approximates to 1 and drops out of consideration. Whether this actually occurs for a case of interest depends on the values of  $\hat{B}$  and  $\hat{K}$ . To show that this is plausible, typical numbers for a medium frequency design are used  $(\hat{B}=100\,\mathrm{mT},\,\hat{K}=2\,\mathrm{A}\,\mathrm{mm}^{-1}$  for a 1 mm thick layer of litz wire, and  $\mu_r=500$ ) and the correction factor comes to 0.997, a negligible quantity.

In order to show that permeability does not significantly affect performance in the case of (relatively) low permeability HF materials, it is necessary to set values for  $\hat{B}$  and  $\hat{K}$ . For an efficiency or temperature-rise limited component, a total loss budget  $P_{loss}$  is fixed and the allowed magnetic flux density and current density are related generally by

$$P_{loss} = P_{core}(\hat{B}) + P_{cu}(\hat{K}) \qquad (2.11)$$

The copper loss,

$$P_{cu} = \frac{1}{2} I_{in}^2 R_{cu} (2.12)$$

is specified by the total winding resistance in terms of the turn length  $l_w$  and the width of one (e.g. foil) turn w,

$$R_{cu} = \rho \frac{Nl_w}{w\delta} = \rho \frac{N^2 l_w}{l_c \delta} \tag{2.13}$$

assuming a single-layer winding distributed around the full perimeter of the core,  $l_c$ , in the skin-depth limit. This yields:

$$P_{cu} = \frac{1}{2} I_{tot}^2 \rho \frac{N^2 l_w}{l_c \delta} = \frac{1}{2} \hat{K}^2 \rho \frac{l_c l_w}{\delta}$$

(2.14)

The core loss is given by measured Steinmetz parameters (e.g. those in Section 2.3):

$$P_{core} = A_c l_c k_f \hat{B}^{\beta} \tag{2.15}$$

Table 2.4: Parameters for Power Ratio Calculations

| Outer Diameter  | $scale \times 22.1  mm$                           |

|-----------------|---------------------------------------------------|

| Inner Diameter  | $scale \times 13.7  mm$                           |

| Thickness       | scale $\times$ 6.35 mm                            |

| Temperature     | 50 °C                                             |

| Rise            |                                                   |

| Thermal Law [1] | $P_{loss} = 0.0475 \times$                        |

|                 | Surface Area (cm <sup>2</sup> ) × $\Delta T$ (°C) |

| Frequency       | 10 MHz                                            |

A relationship between  $\hat{B}$  and  $\hat{K}$  that approximately delivers maximum power can be found by setting core loss and copper loss equal to each other. While this does not guarantee maximum delivered power for a given loss budget (or maximum efficiency for given power handling), it usually provides a good first-order approximation [33]. The resulting relationship is:

$$\frac{\hat{B}^{\beta/2}}{\hat{K}} = \sqrt{\frac{\rho l_w}{2A_c k_f \delta}} \qquad (2.16)$$

The exact expression can also be used,

$$\hat{K} = \sqrt{(P_{loss} - A_c l_c k_f \hat{B}^{\beta}) \frac{2\delta}{\rho l_c l_w}} \qquad (2.17)$$

Given the constraint relating  $\hat{B}$  to  $\hat{K}$ , the best choice of  $\hat{B}$  and  $\hat{K}$  is the combination of values which maximizes delivered power. To select  $\hat{B}$  and  $\hat{K}$ , therefore, it is necessary to plug either (2.16) or (2.17) into (2.7) and find the maximum of  $P_{del}$  numerically.

To illustrate the realistic effect of permeability on high performance HF cores, we take one material (Fair-Rite 67) as an example and carry out a thought experiment in which we can vary the material permeability alone, leaving its loss characteristics unchanged. We consider a thermally limited design on a toroid of volume  $1 \, \mathrm{cm}^3$  (parameters in Table 2.4). We will find that the real permeability of Fair-Rite 67 ( $\mu_r = 40$ ) is sufficient to fully take advantage of the magnetic core.

We begin with a reference design in which the hypothetical permeability is very

high, and therefore the magnetizing inductance  $L_{\mu}$  is very large and the magnetizing current  $I_{\mu}$  is negligible. We maximize deliverable power using (2.7) for the parameters in Table 2.4. The resulting delivered power is the highest achievable for the given parameters, and deliverable powers at finite permeabilities will be normalized to this maximum reference. The values of  $\hat{B}$  and  $\hat{K}$  for this design are also kept as references.

We next substitute cores of identical parameters but decreasing permeability. For a first thought experiment, we do not re-optimize for each permeability but continue to use the same values of  $\hat{B}$  and  $\hat{K}$  as the reference design. As the permeability is decreased, the component achieves less and less deliverable power for the available temperature rise, owing to the increase in magnetizing current. Normalizing the achievable power density at finite permeability to the maximum achievable power density (i.e. for the reference design with infinite permeability) gives a ratio which is denoted the *unoptimized power ratio*  $\mathcal{P}$ , and the result is plotted in Fig. 2-9.

It can immediately be seen that the benefit of added permeability saturates above a certain point, as expected. Indeed, above  $\mu_r = 100$ , the difference between the finite-permeability design and the reference (infinite permeability) is almost indiscernible. For permeabilities as low as  $\mu_r \approx 22$  (lower than the real permeability of Fair-Rite 67), the component incurs less than 10% performance loss compared to the reference. Below  $\mu_r \approx 22$ , performance collapses until the temperature budget is used up by the loss due to the magnetizing current alone and no power can be delivered to the load. It can be seen that the real permeability of Fair-Rite 67 ( $\mu_r = 40$ ) allows it to achieve very nearly the same performance as if it had infinite permeability, i.e. to nearly fully provide the available benefit of a magnetic core.

These conclusions are actually overly pessimistic because we did not reoptimize the design at each finite permeability. If we do reoptimize, the results improve substantially. This experiment follows as before, but the power delivered in (2.7) is maximized for each permeability by changing the operating points  $\hat{B}$  and  $\hat{K}$ . The achievable power for this experiment is also normalized to the reference (high permeability) design and the ratio is denoted the *optimized power ratio*  $\mathcal{P}_{opt}$ . The results are also plotted in Fig. 2-9.

#### Variable Permeability Thought Experiment

Figure 2-9: A theoretical ensemble of materials with the same material loss parameters but different permeabilities. Each point represents an optimization with (2.7) maximized using the parameters in Table 2.4 with a volume of  $1\,\mathrm{cm}^3$ . The deliverable power, normalized to a high-permeability design, is plotted where  $\hat{B}$  and  $\hat{K}$  are held constant ( $\mathcal{P}$ ). The same ratio is also plotted with re-optimized designs ( $\mathcal{P}_{opt}$ ), along with the correction factor for this case. The loss parameters used match those of Fair-Rite 67 at 10 MHz; its permeability ( $\mu_r = 40$ ) is noted on the graph.

It can be seen that  $\mathcal{P}_{opt}$  falls off less sharply as permeability is decreased than the unoptimized case  $\mathcal{P}$ . For example, an optimal component at  $\mu_r = 10$  would still provide substantial power delivery while an unoptimized design would have lost all utility at that permeability.

The reason for this improvement lies in the interaction between the  $\hat{B} \cdot \hat{K}$  product and the correction factor in (2.7). In Fig. 2-9, the plot for the un-optimized case is its own correction factor, as neither  $\hat{B}$  nor  $\hat{K}$  are allowed to vary. This is no longer true for the optimized case, so the correction factor is plotted separately. It can be seen that, at low permeability, the deliverable power collapses in the unoptimized case due to the correction factor, whereas the optimized case trades lower  $\hat{B}$  for higher  $\hat{K}$  to keep the correction factor high. In that case the deliverable power still drops because both the  $\hat{B} \cdot \hat{K}$  product and the correction factor are slowly reduced, but the collapse is not as severe.

Based on these thought experiments, it may be concluded that practical designs can achieve high power density with relatively modest permeabilities. The principle of diminishing returns on permeability is demonstrated for some real materials by calculating  $\mathcal{P}$  and  $\mathcal{P}_{opt}$  using the parameters in Table 2.4 and allowing volume to vary while maintaining the geometric ratios. The results are plotted in Fig. 2-10, from which several conclusions may be drawn. First, the power ratios of the lower permeability materials fall farther below 1 as expected from the previous thought experiments. Second, the lower permeability materials see a greater variation between  $\mathcal{P}$  and  $\mathcal{P}_{opt}$  in the same way that their values diverge at low permeability in Fig. 2-9. Third, as volume is decreased there is both a decline in achievable performance and a greater deviation between the power ratios. Finally, despite all these effects, in most cases the power ratios for low permeabilities are above 0.9, indicating that permeability has only a small practical influence on performance. Additionally, the balance of core loss and total loss for the optimized case is plotted in Fig. 2-11, and is consistent with the general rule that minimizing total loss usually requires core loss to be equal to or slightly less than copper loss [34].

#### Variable Volume Calculated Performance

Figure 2-10: Un-optimized and optimized power ratios  $(\mathcal{P},\mathcal{P}_{opt})$  for example materials and volumes. Parameters in Table 2.4.

Figure 2-11: The fraction of total loss attributable to core loss for example materials and volumes for the optimized case as in Fig. 2-9. Parameters in Table 2.4.

#### 2.6 Conclusion

The drive to increase frequency in power conversion circuits, enabled by advanced circuit designs and wide-band-gap semiconductors, is primarily predicated on the idea that passive components can be made smaller and cheaper, and that systems can achieve higher performance. The extent to which power magnetic components can be improved at higher frequencies hinges on their loss behavior at those frequencies. We have undertaken measurements to produce this necessary data in the HF range, where material data was previously lacking. The results suggest that significant improvements in performance are possible through HF operation using commercially available materials.

Additionally, the extension of the performance factor  $\mathcal{F}$  to the high frequency modified performance factor  $\mathcal{F}_{3/4}$  allows for a more sober and realistic assessment of the benefits of high frequency operation. Using this metric and the newly gathered data, we foresee a roughly 45% improvement in loss-limited magnetic component density (with even greater gains in other magnetic components) through designs operating deep in the HF regime using currently-available materials.

Finally, we observe that the materials which offer such promising results have relatively low permeabilities. We conclude that an upper bound exists on the amount of relative permeability necessary to develop optimized components, and that for most designs the actual permeabilities available in high performance HF materials are sufficient to avoid any disadvantage.

# Chapter 3

# A Wide-Operating-Range Converter for High Frequency Operation

# 3.1 Background

#### Conventional Converters Are Ill-Suited for Wide-Range HF Operation

It was shown in Chapter 2 that operating frequencies can extend up to at least 10 MHz while still improving the size of magnetic components having loss constraints. Frequencies could further be increased to about 30 MHz while achieving similar power stage density to conventional designs. In making this change, the other advantages of HF operation continue to apply (smaller EMI filters, faster transient responses, etc.).

Nevertheless, even with high performance magnetic materials and wide-band-gap switching devices, many conventional power converter topologies and control techniques are ill-suited to the HF regime at hundreds of volts and watts. Switching losses in particular limit the application of hard-switched topologies in this space. For example, in a boost converter with  $V_{out} = 400 \,\mathrm{V}$  and  $P_{out} \sim 300 \,\mathrm{W}$ , appropriate state-of-the-art GaN FETs would have an energy stored in their output capacitances (at turn-on) of about  $E_{oss} = 3 \,\mathrm{\mu J}$ . If the converter is hard-switched (as is convention-

ally done, even in DCM), the switch will dissipate this energy every cycle, resulting in a switching loss of 3 W/MHz. At conventional frequencies, this loss ( $\sim 0.3 \text{ W}$ ) may be acceptable; in the MHz regime the loss ( $\sim 3 \text{ W}$ ) may be merely tolerable (with good heat sinks); deep in the HF range, the loss ( $\sim 30 \text{ W}$ ) would be prohibitive both from thermal and efficiency perspectives. Therefore, circuit-level design must achieve some degree of soft-switching to operate at HF in many applications.

#### Soft-Switching Converters Typically Have Narrow Operating Range

Soft switching techniques (e.g. zero voltage turn-on or zero current turn-off) are commonly employed to avoid switching losses and enable high efficiency and/or high power density [35–37]. However, such converters typically lose their soft-switching characteristics (or suffer other disadvantages) outside a particular operating range. For example:

Resonant converters (e.g. series, parallel, LLC, etc.) are usually operated under frequency control above the relevant resonant frequency to have inductive loading and achieve ZVS. The operating frequency increases to limit output power; higher frequencies result in low light-load efficiency [38, 39]. Additionally, series-resonant peak voltages and parallel-resonant circulating currents can be much higher than the input/output voltages/currents under some operating conditions, placing extra strain on converter components. This is especially true of quasi-resonant converters and single-switch inverters which must use switches rated for significantly higher voltages than the input/output voltages. Wide frequency variations required by low-Q resonances can also make EMI filter design difficult.

Phase-shift control can also be used (typically with full-bridge resonant converters). While this technique can be employed at a single frequency, there are difficulties in achieving soft switching for all of the devices as well as achieving current sharing in the inverter legs, especially as power is varied [40,41]. Other techniques also lose ZVS as output power is varied, including asymmetrical clamped mode control and asymmetrical pulse width control [42,43].

Resonant-transition pulse-width-modulated converters operate similarly to bound-

ary conduction PWM converters. During resonant phases, the primary inductor is allowed to resonate with the parasitic switch capacitances to discharge them before the switches are turned on [44]. For example, a buck converter may have some dead time after the high-side switch is turned off, allowing the inductor to discharge the device capacitances before the low-side switch is turned on. Additionally, after the inductor current reaches zero and the low-side switch (or diode) is off, the inductor will again resonate with the device capacitances to bring the switching node voltage up and allow the high-side switch to turn on with reduced voltage. While these converters can operate over a wide power range and maintain ZVS, they have significant limitations. Since such converters must allow the inductor current to reach zero (as in boundary conduction mode) and must allow a fixed resonant transition period, they therefore must operate with variable frequency to vary output power. Additionally, these converters can only achieve ZVS for a narrow range of voltages. For example, the resonant-transition buck converter only achieves ZVS for the high-side switch when  $V_{in} < 2V_{out}$ .

This chapter will present a converter topology and control scheme suitable for HF operation at hundreds of volts and watts. The converter is particularly well-suited to applications which require operation over a wide range of voltages and/or powers, thereby overcoming many of the disadvantages of existing soft-switching topologies. To introduce this converter, it will be compared to the resonant-transition boost converter, which is sometimes used in grid-connected applications.

#### The Resonant-Transition Boost Converter Has Limited Voltage Range

One application of wide-operating range converters is in power factor correction (PFC). Such PFC converters are typically connected to a rectified ac source (such as a single-phase ac power grid) and are operated to draw current proportional to their input voltage. This makes the converter look like a resistive load to the grid, drawing real power and minimizing wasteful reactive power. Since such converters must draw current over the a wide portion of the line cycle (ideally the whole line cycle), they inherently must operate with wide input voltage range and wide power range.