## Synchronization in Timestamp-Based Cache Coherence Protocols

by

Quan Minh Nguyen

B.S., University of California, Berkeley (2014)

Submitted to the Department of

Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2016

© Massachusetts Institute of Technology 2016. All rights reserved.

| •             |                                                                                             |

|---------------|---------------------------------------------------------------------------------------------|

| Author        | Signature redacted                                                                          |

| Ι             | Department of Electrical Engineering and Computer Science May 20, 2016                      |

| Certified by. | Signature redacted                                                                          |

|               | Srinivas Devadas Professor of Electrical Engineering and Computer Science Thesis Supervisor |

|               |                                                                                             |

Signature redacted

#### Synchronization in

### Timestamp-Based Cache Coherence Protocols

by

Quan Minh Nguyen

Submitted to the Department of Electrical Engineering and Computer Science on May 20, 2016, in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

#### Abstract

Supporting computationally demanding workloads into the future requires that multiprocessor systems support hundreds or thousands of cores. A cache coherence protocol manages the memory cached by these many cores, but the storage overhead required by existing directory-based protocols to track coherence state scales poorly as the number of cores increases. The Tardis cache coherence protocol uses timestamps to avoid these scalability problems. We build a cycle-level multicore simulator that implements a version of the Tardis protocol that uses release consistency. Changing the coherence protocol, which affects what memory values a processor can observe, changes inter-processor communication and synchronization, two processes crucial to the operation of a multicore system. We construct Tardis versions of synchronization primitives and the atomic instructions they use, and compare them to their analogous implementations on a directory-based cache coherent multicore system. Simulations on several benchmarks suggest that the Tardis system performs just as well as the baseline system while preserving the ability to scale systems to hundreds or thousands of cores.

Thesis Supervisor: Srinivas Devadas

Title: Professor of Electrical Engineering and Computer Science

## Acknowledgments

Before I begin, I'd like to take this opportunity to thank the people who have made this journey even remotely tractable. First, I would especially like to thank my adviser, Srini, for providing key insights and guidance in this project and so warmly welcoming me into the group two years ago. I am very grateful to Xiangyao, who has never wavered from answering my unrelenting stream of questions about Tardis. I aspire to emulate their contagious enthusiasm and wide-spanning knowledge. In addition to my lab mates, my friends here have made my stay at the Institute at least as much play as it is work; a heartfelt thank-you to Aaron, Fady, Lisa, Liz, Mehrdad, Michael, and Wendy, who have been by my side the entire time. I am tremendously grateful to Albert, Andrew, Krste, Stephen, and Yunsup of the ParLab and ASPIRE Lab at Berkeley for intellectually launching me into the place where I am today. And, finally, I want to thank my family: my mother, father, and sister (better known to me as  $M\hat{a}$ , Ba, and  $Uy\hat{e}n$ ), for making it all possible. Just thinking of you and the love you have shown me is always a source of inspiration and hope.

## Contents

| 1 Introduction |     |         |                                          | 13 |

|----------------|-----|---------|------------------------------------------|----|

| 2              | Tin | estam   | p-Based Cache Coherence Protocols        | 17 |

|                | 2.1 | The T   | Cardis Cache Coherence Protocol          | 17 |

|                |     | 2.1.1   | Timestamps                               | 19 |

|                |     | 2.1.2   | Reading Cache Blocks with Leases         | 22 |

|                |     | 2.1.3   | Writing Cache Blocks through Time Travel | 23 |

|                |     | 2.1.4   | Renewals                                 | 24 |

|                |     | 2.1.5   | Per-Program Timestamps                   | 25 |

|                |     | 2.1.6   | Main Memory, Incoherent Memory, and I/O  | 27 |

|                | 2.2 | Releas  | se Consistency and RISC-V                | 28 |

|                |     | 2.2.1   | Fences                                   | 29 |

|                |     | 2.2.2   | Release and Acquire Instructions         | 31 |

|                | 2.3 | Releas  | se Consistency Support for Tardis        | 31 |

|                |     | 2.3.1   | Compact Timestamp Configurations         | 32 |

|                |     | 2.3.2   | Cache Transactions                       | 34 |

|                |     | 2.3.3   | Leases and Renewals in Tardis-RC         | 37 |

|                | 2.4 | Stale 2 | Reads                                    | 37 |

|                | 2.5 | Techn   | iques for Writing Tardis Programs        | 40 |

|                | 2.6 |         | ous Use of Timestamps for Coherence      | 41 |

| 3              | Ato | mic In  | astructions                              | 43 |

|                | 3.1 | Comp    | are-and-Swap                             | 43 |

|   | 3.2 | Load-Reserved and Store-Conditional       | 45 |

|---|-----|-------------------------------------------|----|

|   | 3.3 | Atomic Memory Operations                  | 48 |

| 4 | Syn | chronization                              | 51 |

|   | 4.1 | Locks                                     | 51 |

|   |     | 4.1.1 The Mellor-Crummey-Scott Queue Lock | 53 |

|   | 4.2 | Barriers                                  | 54 |

| 5 | Imp | plementation                              | 61 |

|   | 5.1 | Guiding Principles                        | 61 |

|   | 5.2 | The RISC-V Rocket Microarchitecture       | 62 |

|   |     | 5.2.1 Pipelining Timestamps               | 62 |

|   |     | 5.2.2 Extending the Memory Hierarchy      | 63 |

|   | 5.3 | Network-on-Chip                           | 64 |

|   |     | 5.3.1 Manager/Client Abstraction          | 64 |

|   |     | 5.3.2 Network Topology                    | 65 |

| 6 | Eva | luation                                   | 67 |

|   | 6.1 | Atomic Instructions                       | 67 |

|   | 6.2 | Synchronization Primitives                | 70 |

|   | 6.3 | Application Performance                   | 72 |

| 7 | Cor | nclusion                                  | 81 |

|   | 7.1 | Future Work                               | 81 |

|   | 7.2 | Concluding Remarks                        | 83 |

# List of Figures

| 2-1  | Simplified system diagram                                             | 18 |

|------|-----------------------------------------------------------------------|----|

| 2-2  | Last-level cache metadata layout                                      | 18 |

| 2-3  | Timeline diagram representing the validity of cache blocks within the |    |

|      | Tardis protocol                                                       | 21 |

| 2-4  | Timeline diagram demonstrating a cache block read                     | 23 |

| 2-5  | Timeline diagram demonstrating a cache block write                    | 24 |

| 2-6  | Timeline diagram demonstrating a cache block renewal                  | 25 |

| 2-7  | Timeline diagram demonstrating interaction with main memory           | 27 |

| 2-8  | Assembly code demonstrating a potential hit-under-miss situation a    |    |

|      | cache                                                                 | 28 |

| 2-9  | Timeline diagram demonstrating one of the limitations of Tardis with  |    |

|      | sequential consistency.                                               | 29 |

| 2-10 | Timeline diagram demonstrating a write-read fence in Tardis           | 30 |

| 2-11 | Timeline diagram demonstrating timestamps used in Tardis-RC           | 33 |

| 2-12 | Example producer-consumer code                                        | 38 |

| 2-13 | Using synchronization to communicate updated data through an ex-      |    |

|      | ternal cache block                                                    | 40 |

| 3-1  | Hypothetical source code for a compare-and-swap instruction           | 44 |

| 3-2  | Timeline diagram demonstrating avoidance of the ABA problem           | 45 |

| 3-3  | Load-reserved/store-conditional instruction sequence                  | 45 |

| 3-4  | Timeline diagram demonstrating livelock freedom on the LR/SC in-      |    |

|      | struction pair                                                        | 47 |

| 4-1 | Source code for spin lock that uses compare-and-swap                     | 52 |

|-----|--------------------------------------------------------------------------|----|

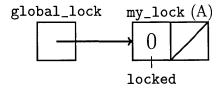

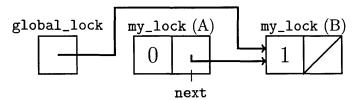

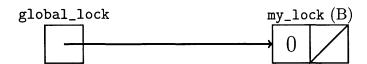

| 4-2 | Diagram depicting linked-list nature of the MCS queue lock               | 54 |

| 4-3 | Source code for an implementation of the Mellor-Crummey-Scott queue      |    |

|     | lock                                                                     | 55 |

| 4-4 | Timeline diagram illustrating the effects of a barrier in physiological  |    |

|     | time                                                                     | 56 |

| 4-5 | Source code for a sense-reversing barrier                                | 57 |

| 4-6 | Barrier exploiting the exclusive ownership state to notify other cores.  | 58 |

| 6-1 | Microbenchmark source code.                                              | 68 |

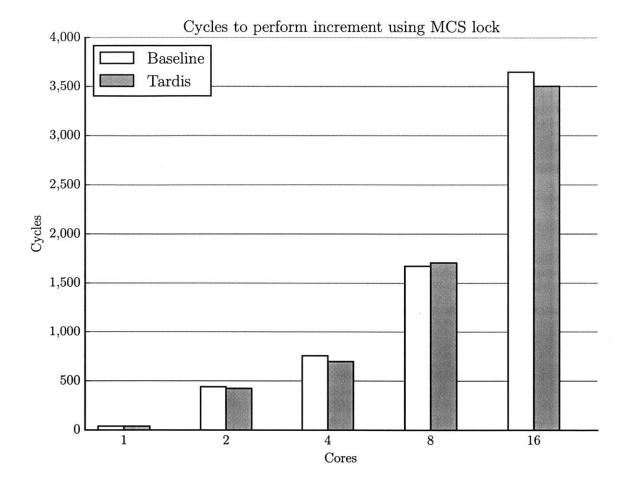

| 6-2 | Performance of the MCS queue lock microbenchmark                         | 71 |

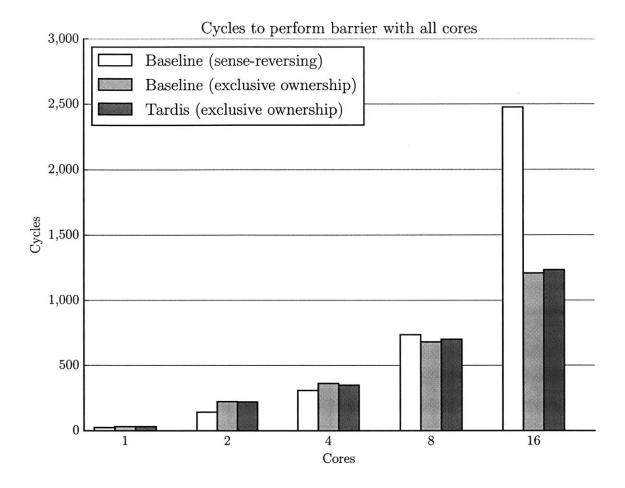

| 6-3 | Performance of a barrier microbenchmark                                  | 72 |

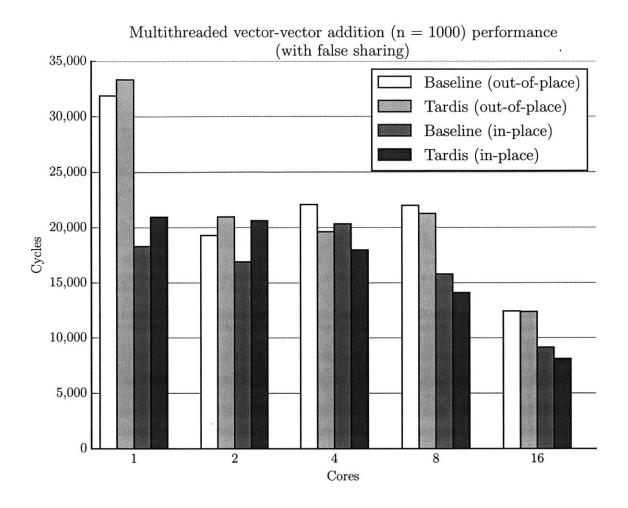

| 6-4 | Performance of a vector-vector add benchmark exhibiting false sharing.   | 74 |

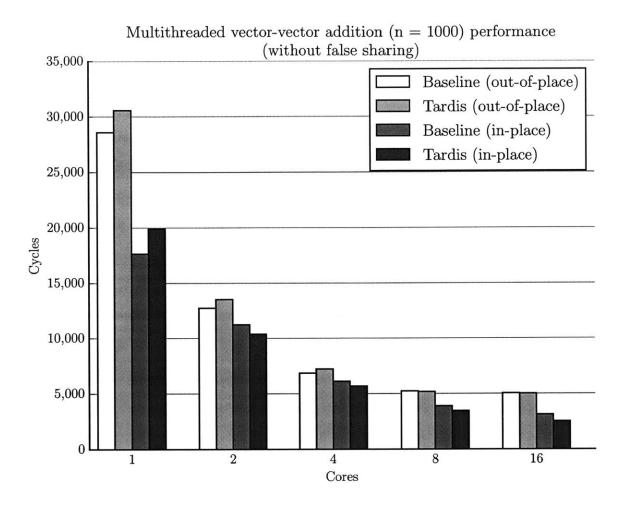

| 6-5 | Performance of a vector-vector addition benchmark without false sharing. | 75 |

| 6-6 | Number of acquire messages sent on the TileLink networks                 | 76 |

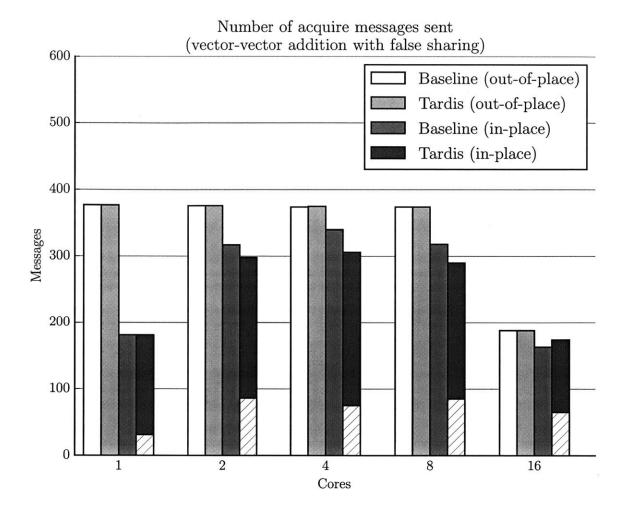

| 6-7 | Number of acquire messages sent on the TileLink networks                 | 77 |

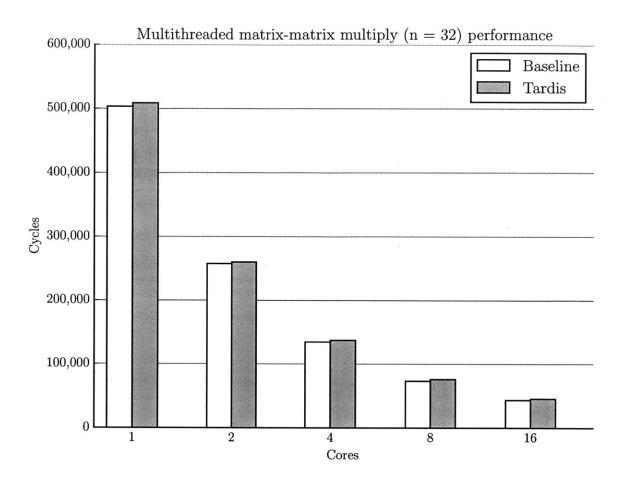

| 6-8 | Performance of a matrix-matrix multiplication                            | 78 |

# List of Tables

| 1-1 | Size and latencies of a computer's memory hierarchy                      | 14 |

|-----|--------------------------------------------------------------------------|----|

| 2-1 | Timestamps for Tardis-SC, a sequentially consistent version of Tardis.   | 21 |

| 2-2 | Timestamp update rules for the manager in the sequentially consistent    |    |

|     | version of the Tardis cache coherence protocol                           | 26 |

| 2-3 | Timestamp update rules for the manager in the sequentially consistent    |    |

|     | version of the Tardis cache coherence protocol                           | 26 |

| 2-4 | Message types used in Tardis                                             | 26 |

| 2-5 | Timestamp update rules needed to support relaxed consistency mem-        |    |

|     | ory models.                                                              | 32 |

| 2-6 | Timestamps for Tardis-RC, a release-consistent version of Tardis, as     |    |

|     | implemented in this thesis                                               | 33 |

| 2-7 | Actions performed by the client in the Tardis cache coherence protocol.  | 35 |

| 2-8 | Actions performed by the manager in the Tardis cache coherence protocol. | 36 |

| 2-9 | Guidelines for timestamps to be sent along with messages to the last-    |    |

|     | level cache during cache misses                                          | 37 |

| 5-1 | Logical networks in the TileLink coherence protocol abstraction          | 64 |

| 5-2 | Timestamps required in network messages for coherence in the Tardis      |    |

|     | protocol                                                                 | 65 |

| 5-3 | Evaluation system configuration                                          | 66 |

| 6-1 | Performance of the load-reserved/store-conditional microbenchmark.       | 68 |

| 6-2 | Performance of the atomic memory operation microbenchmark                | 69 |

## Chapter 1

## Introduction

We must build multicore systems that scale well to hundreds or thousands of cores to run applications increasingly necessary for progress and discovery in modern society. These systems have become ubiquitous in everyday life, from mobile platforms to datacenter computers. Even systems with one microprocessor may have multiple cores running independently and in parallel. Computer architects have taken advantage of the falling cost of transistors and evolving circuit fabrication techniques to increase both the number of cores and the amount of memory or a single system.

Low-latency, high-throughput memory ensures that these applications run quickly. On a shared-memory machine, all cores access the same main memory. However, these cores rarely make changes directly to main memory – instead, they change the data stored in a cache. A cache contains small sections of frequently used memory to exploit spatial and temporal locality, and are essential in the design of high-performance computers. Nowadays, the computer's memory hierarchy separates a processor's registers from main memory with multiple levels of progressively larger caches. A processor's registers, at the top of the hierarchy, are fast, but small; main memory, at the bottom of the hierarchy, is relatively slow, but large. By balancing the speed and size trade-offs, the memory hierarchy grants the illusion of a vast, fast memory [1]. Yet, programmers assume that any core may immediately observe the changes to memory made by another core. The cache coherence system, which implements a specific cache coherence protocol, communicates with the cores to keep cached data in a state

| Type                | Size              | Latency                |

|---------------------|-------------------|------------------------|

| Processor registers | 1000 B            | 300 ps                 |

| L1 caches           | $64~\mathrm{KB}$  | $1 \mathrm{\ ns}$      |

| L2 caches           | $256~\mathrm{KB}$ | 3 - 10  ns             |

| Main memory         | 4 – 16 GB         | $50-100 \mathrm{\ ns}$ |

Table 1-1: Size and latencies of a computer's memory hierarchy, from [1].

that a programmer can reason about.

Caches typically maintain data in equally-sized parcels known as *cache blocks*. Throughout the execution of a program, cache blocks move between levels of the memory hierarchy – from the expansive but slow main memory to the cache nearest the processor, the first-level (or "L1") cache. The cache coherence protocol must ensure maximum memory throughput, so it must permit multiple cores to *share* the same area of memory. However, the protocol must also propagate any changes to memory to these caches so that the system stays coherent.

The prevailing method to ensure cache coherence today is the directory protocol. The directory manager, which resides at the outer levels of the cache hierarchy, maintains a list of all cores currently caching a cache block as a part of its metadata. At its simplest, the directory manager uses a bit vector with n bits, one for each core, to track who currently accesses a cache block, and a manager keeps a bit vector for each cache block. Before a core may write to a cache block, it must obtain exclusive ownership so that no other core may read stale data. To obtain exclusive ownership, the directory manager invalidates all copies of the cache block at all other cores. The manager scans this "full-map" bit vector and sends each core a message instructing it to no longer cache that area of memory. This scheme works well due to its simplicity and because the number of cores sharing a particular cache block, up until recently, has remained small.

However, the number of cores on a single die continues to rise, as does the number of processors in a shared-memory system. For instance, Intel's second-generation Xeon Phi processors, code-named "Knights Landing", boasts 72 cores with access to up to 384 GB of main memory [2]. A typical "full-map" directory, if implemented on this

system, would require 72 bits per cache block to represent all possible combinations of sharers. This amount of storage would represent more than 10% metadata overhead for a 64-byte cache block, and will only grow as the number of cores increases. Several techniques [3, 4, 5] reduce the cost of scaling the directory, but no technique suitably solves the problem of effectively broadcasting invalidation messages to all sharers.

Tardis, a timestamp-based cache coherence protocol, reduces the per-cache block metadata overhead from O(n) to  $O(\log n)$  in the number of sharers [6]. Instead of tracking all sharers of a cache block, the Tardis protocol only tracks its exclusive owner. To maintain coherence, the Tardis protocol also assigns each cache block a set of timestamps. Each core, which gains a timestamp counter in this protocol, may only read a cache block if it satisfies conditions on its counter and the cache block's timestamps. The Tardis protocol, which provably preserves sequential consistency [7], opens the door to dramatically scaling the number of cores in a system by dispensing with excess metadata.

We wish to understand the effects of a system running Tardis to establish a case for future implementation in real-world systems. The first efforts at modeling the performance of the Tardis protocol were completed in Graphite, a functional simulator that only performs *lax synchronization*. In this model, cores are only synchronized when they interact on "true synchronization" events [8], making it possible for simulated events to occur out-of-order from when they would occur on a real system. However, synchronization is a necessary component of a parallel program running on a multicore machine. Furthermore, Graphite cannot faithfully model effects that arise from inter-processor communication, such as message latency and network contention, even while modeling the memory ("full" mode). These shortcomings prevent us from fully measuring and understanding Tardis, so we opt to model it with cycle-level simulation.

## Organization and Contributions of this Thesis

In this thesis, we study synchronization on a machine implementing the Tardis protocol on a cycle-level simulator in the interest of building it on a real platform, whether synthesized for a field-programmable gate array (FPGA) or for fabrication. We modify a version of Tardis that supports sequential consistency ("Tardis-SC") to produce "Tardis-RC", a version of Tardis that supports the release consistency memory model in Chapter 2. Using Tardis-RC, we define new semantics for atomic instructions and observe their impacts on synchronization primitives in Chapters 3 and 4. We implement a prototype cycle-level simulator in Chapter 5, the first known implementation of Tardis-RC with cycle-level detail. In Chapter 6, we demonstrate the performance of Tardis implementations of atomic instructions and synchronization primitives and their baseline counterparts on several benchmarks. We summarize our findings and discuss possibilities for future work in Chapter 7.

## Chapter 2

# Timestamp-Based Cache Coherence Protocols

In this chapter, we provide an overview of the Tardis cache coherence protocol. First, we introduce the sequentially consistent version of Tardis, Tardis-SC, as described in [6]. We specify Tardis-RC, a version of Tardis that supports release consistency, to match the architecture used in our cycle-level simulator. We also extend Tardis to memory-mapped devices and input/output (I/O).

## 2.1 The Tardis Cache Coherence Protocol

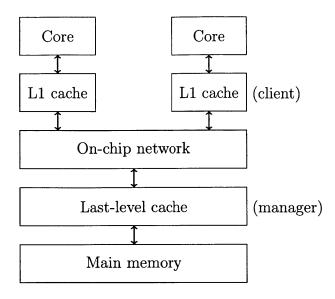

A system that implements the Tardis protocol has a number of cores and their caches connected by an on-chip network that is eventually serviced by a shared last-level cache, as typified in Figure 2-1. We refer to the system that maintains metadata at the last-level cache as the manager. Clients, such as a core's private data and instruction caches, communicate with the manager to receive cache blocks. Clients that may store modified blocks in a private cache are cached clients. Cached clients require invalidations, while uncached clients (for instance, memory-mapped I/O) do not. Tardis distinguishes itself from other cache coherence protocols because the manager stores only the identity of the exclusive owner of the cache block, if it exists, resulting in  $O(\log n)$  metadata storage per cache block. Consequently, the

Figure 2-1: Simplified system diagram.

manager has no knowledge of the state of read-only cache blocks in the system. For these blocks, timestamps inform clients as to whether reading the block preserves the memory consistency guarantees of the system. The next several sections discuss the rules regarding these timestamps. Figure 2-2 depicts a possible layout of a cache block's metadata at the manager. The size of the timestamps does not grow with the number of sharers, preserving scalability in systems with potentially hundreds or thousands of cores.

| Client  | State | Tag   | w   | ts | r   | ts |            |

|---------|-------|-------|-----|----|-----|----|------------|

| Manager | State | Owner | Tag | u  | rts | rt | $\ddot{s}$ |

Figure 2-2: The potential layout of cache block metadata at the client (for example, an L1 data cache) and the manager (for example, a last-level cache).

As in an ordinary directory-based protocol, any cache block may be read by any client. The permissible operations on a cache block at the client are tracked with states identical to a typical directory protocol, such as MESI [9]. We use these protocol states for the rest of the thesis.

#### Time

The definition of "time" plays an important role in the Tardis protocol, so we take care to define it here<sup>1</sup>. Physical time is the time observed in accordance with natural phenomena; that is, wall-clock time. Logical time, perhaps most well-established as Lamport clocks, numbers events based on a monotonically increasing counter without regard to the passage of physical time [11]. Tardis combines both notions of time to form physical-logical time, shortened to physiological time<sup>2</sup>, to establish a global memory ordering between memory operations on cache blocks within a multiprocessor system. Thus, something said to occur at the same physiological time may have actually happened at two different physical times.

Memory models describe how the memory operations in a program (which defines the program order) may be interleaved to form a global memory order. The sequential consistency model stipulates that "the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program" [12]. The physiological time rule of Tardis-SC [6] establishes a global memory order with timestamps assigned to memory operations:

**Definition 1** (Physiological time rule). For an operation X to occur before Y in the global memory order, X's timestamp must be ordered before Y's timestamp, or if they have the same timestamp, that X must be ordered before Y in the program.

### 2.1.1 Timestamps

The Tardis protocol assigns a write timestamp and a read timestamp to each cache block, which we denote as wts and rts respectively. These timestamps do not correspond to any actual operation, but instead specify which physiological times a memory operation may occur. In Tardis-SC, the sequentially consistent version of the Tardis protocol, each client keeps a timestamp counter to track its own sense of

<sup>&</sup>lt;sup>1</sup>More precisely than "a big ball of wibbly wobbly timey wimey stuff." [10]

<sup>&</sup>lt;sup>2</sup>Physiological time has no relation to the biological notion of physiology.

physiological time, which we denote as pts.<sup>3</sup> To satisfy the protocol's requirement for totally ordered timestamps, we represent physiological timestamps with integers. In practice, 64-bit unsigned integers suffice and will never roll over in human-fathomable timescales. A client can store pts in a register, while caches at the client and manager can store wts and rts in a cache metadata array.

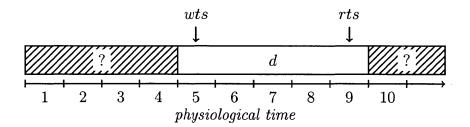

The write timestamp wts and the read timestamp rts denote the minimum and maximum physiological times at which the cache block data assigned those timestamps are considered valid. To have valid cache block data, the read timestamp must be no less than the write timestamp; that is,  $wts \leq rts$ . In Section 2.1.2, we will restrict reads to the cache block to clients that have a pts that fall within this range. The validity of a cache block can then be expressed as an integer interval, which we denote in this thesis as [wts, rts], emulating the notation for real-valued intervals that contain both the start and end values. The Tardis protocol stipulates a crucial invariant for these timestamps which we term the  $Tardis\ invariant$ :

**Definition 2** (Tardis invariant). For a specific cache block, only one version of its data may exist in a given timestamp interval [wts, rts].

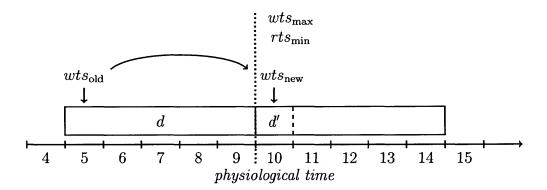

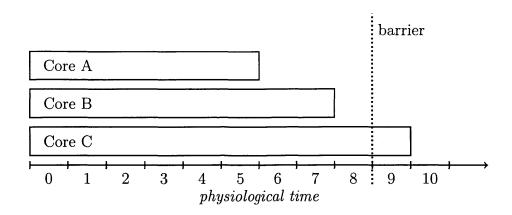

Figure 2-3 depicts the validity of a cache block on a timeline. In this figure, physiological time increases to the right. The cache block's data, d, are valid in the interval [5,9]. Reads to the cache block occurring at timestamps before 5 or after 9 may yield different data different from d.

An immediate consequence of this invariant is that changes to the data always generate a new pair of timestamps with an interval disjoint from that of the old data. A more subtle implication is that the value of rts may be increased as long as the data in the cache block do not change. Increasing the rts of a cache block amounts to "renewing" a cache block. Renewals, covered in Section 2.1.4, allow clients to extend the range of physiological times they may read the data. The Tardis invariant helps programmers and computer architects reason about the function of the protocol. For

$<sup>^3</sup>$ The term  $processor\ timestamp$  gives rise to the abbreviation pts, but such a timestamp applies to any caching client.

Figure 2-3: Timeline diagram representing the validity of a cache block. Physiological time increases to the right, and all timestamps are integers. Rectangles on the same row refer to the same cache block, and the text enclosed refers to the data. The smallest integer a rectangle overlaps represents that cache block's wts; the largest integer represents that cache block's rts. We use a hatched pattern to emphasize that the data outside wts and rts may not be known to the client.

instance, in Chapter 3 we demonstrate that the Tardis invariant can mitigate the ABA problem for the compare-and-swap atomic instruction.

A client's pts may only increase; however, pts only changes when the client interacts with memory – pts does not increase with wall-clock time or the cycle count. Reading memory may not alter a client's pts at all. With a single timestamp, a caching client can maintain sequential consistency; the next several sections review Tardis-SC as specified in [6]. Physiological timestamps exist for uncached regions of memory as well; they are discussed in Section 2.1.6. We summarize the timestamps discussed so far, and their function, in Table 2-1.

| Name             | Purpose                                                                                                                              |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| $\overline{pts}$ | Tracks a client's position in physiological time.                                                                                    |  |  |  |

| wts              | The physiological time for which the data assigned to this timestamp are valid.                                                      |  |  |  |

| rts              | At a client, the last physiological time for which the data assigned are valid. At the manager, the last time for <i>any</i> client. |  |  |  |

Table 2-1: Timestamps for Tardis-SC, a sequentially consistent version of Tardis.

#### 2.1.2 Reading Cache Blocks with Leases

In the Tardis protocol, the manager leases cache blocks to clients by sending data and the timestamps indicating when the data are valid. The difference between wts and rts is the "length" of the lease, and it roughly corresponds to the number of intervening memory operations before the cache block must be renewed, discussed in Section 2.1.4. At the last-level cache, the wts of a cache block represents the timestamp of the most recent store. The rts of a cache block represents the last physiological time for which the data currently stored in the cache block are valid. To request a read-only copy of the cache block, a client sends its pts to the manager. The manager advances the rts its cache block as prescribed in Equation (2-1).

$$rts \leftarrow \max \begin{cases} wts + \text{lease} \\ rts \\ pts + \text{lease} \end{cases}$$

(2-1)

At minimum, we add the lease value to the block's current wts (line 1). If the cache block has been leased to another core, the manager will have already updated rts; we ensure that rts never decreases (line 2). Finally, in cases where pts far exceeds the other two values, we ensure that the lease will be valid for the core by including pts in the lease computation (line 3). The write timestamp (wts) does not change in computing the lease. Along with the cache block data, the last-level cache sends the wts and updated rts to the sharer.

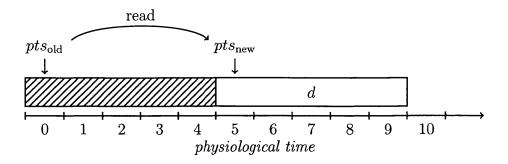

If the cache block's wts exceeds pts, the client advances its pts to at least wts to satisfy the Tardis invariant. Advancing pts causes the core to "travel through time," possibly changing the data it may read from other cache blocks. Figure 2-4 demonstrates a read performed by the client.

Suppose that a cache block is valid from timestamps [5, 9]. If a client's pts is 0, and it reads the cache block, it advances its pts to at least wts – in this case, 5 – to observe data d. We exploit Tardis's ability to "jump" forward in time to also write cache blocks.

Figure 2-4: Reading from a cache block. Because pts < wts, we advance pts to at least wts to read the cache block's data.

#### 2.1.3 Writing Cache Blocks through Time Travel

Clients must request exclusive ownership of a cache block to modify its data. If another client exclusively owns that cache block, the manager issues a writeback request to that client before granting the original requester the exclusively-owned cache block. In the directory protocol, the manager must also invalidate all read-only copies of the cache block. In Tardis, invalidations of read-only copies of the cache block are not necessary. To grant exclusive ownership of a cache block, the manager sends its values of wts and rts for that cache block to the requester. Because rts represents the last physiological time at which a client may read the current version of that cache block, the earliest timestamp at which the data may change is rts + 1. The client "jumps" to this physiological time to modify the data, thus lending the protocol its name. Figure 2-5 demonstrates a write operation.

Equation 2-2 describes the update process for wts when a client writes to a cache block:

$$wts \leftarrow \max \begin{cases} rts + 1 \\ pts \end{cases} \tag{2-2}$$

When a client writes to its exclusively-owned copy of a cache block, it modifies the timestamps of its local copy with no need to notify the timestamp manager. When writing to a cache block, the client must advance wts to at least rts + 1 (line 1). However, wts must also be at least the value of pts (line 2). To preserve the Tardis

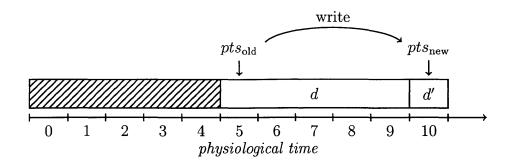

Figure 2-5: Writing a cache block. We advance pts past the rts of the cache block containing d to write d'.

invariant, we also advance pts and rts to the updated wts.

Suppose a client has permissions to write to a cache block that is currently valid from timestamps [5, 9], and its pts is 5. When it performs a write, the client advances the timestamps of its local copy of the cache block to at least rts + 1, which is 10, and also advances its pts to that point as well. At timestamp 10, it writes new data to the cache block, d', overwriting the cache block originally storing d.

This makes it possible for two cores to cache the same region of memory but have different data in the cache blocks. However, these cache blocks will have disjoint timestamp intervals. To make space for another cache block, clients may have to *evict* cache blocks. For read-only blocks, clients in the Tardis protocol may simply clear them to evict them. In a conventional directory-based protocol, the client would have to notify the manager of the cache eviction for bookkeeping. If they evict exclusively-owned cache blocks, clients must return the (possibly) modified data to the last-level cache.

#### 2.1.4 Renewals

Clients advance their timestamp counters whenever they modify cache blocks. A cache block expires at a client when the client's pts exceeds the rts of that cache block. The cache block's data may have changed beginning at timestamp rts + 1, so the client must learn whether the cache block has changed by sending a renewal request to the manager. The manager compares the wts of the request to the wts

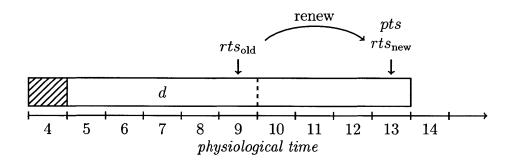

of the cache block stored at the manager to discern whether the cache block has changed. If they do not differ, the renewal succeeds, and the manager advances the rts of the cache block at the manager to contain at least the client's pts, also sent with the renewal message. The manager completes the renewal process by informing the client of the cache block's rts, and no cache block data transfer is needed. If the data have changed at the manager, the manager sends the client the modified data alongside the updated timestamps as if it were an ordinary cache block read request. Figure 2-6 demonstrates the renewal process.

Figure 2-6: Renewing a cache block. Because  $pts > rts_{\text{old}}$ , we must renew the cache block to make sure it has not changed by the time we read it at timestamp pts.

In this case, the cache block is valid from timestamps 5 to 9, but pts is 13. The client sends a renewal request to the manager with the cache block's wts and the client's pts. If wts = 5 at the manager, the data has not changed; the manager extends rts to at least pts, and sends the new rts – in this case, 13 – to the client. If the data have changed, it sends the data and a new set of timestamps. Tables 2-2 and 2-3 summarize the key timestamp update rules for Tardis-SC. Table 2-4 details the messages used in the Tardis protocol.

### 2.1.5 Per-Program Timestamps

Programs that do not interact through shared memory should maintain disparate sets of timestamps to prevent memory operations in one program from prematurely expiring cache blocks in other programs. However, this tasks the operating system with saving and restoring timestamp state during a context switch. However, simpler

| Core event      | Cache Block State      | Result     | Actions                                                                 |

|-----------------|------------------------|------------|-------------------------------------------------------------------------|

| L1 load Invalid |                        | Load miss  | Send Share request to L2                                                |

|                 | Shared; $pts > rts$    | Load miss  | Send RENEW request to L2                                                |

|                 | Shared; $pts \leq rts$ | Load hit   | $pts \leftarrow \max\left(pts, wts\right)$                              |

|                 | Exclusive              | Load hit   | $pts \leftarrow \max(pts, wts)$<br>$rts \leftarrow \max(pts, wts, rts)$ |

| L1 store        | Shared                 | Store miss | Send UPGRADE request to L2                                              |

|                 | Exclusive              | Store hit  | $wts, rts, pts \leftarrow \max(rts + 1, pts)$                           |

| Eviction        | Shared                 |            | Silently drop cache block State $\leftarrow$ Invalid                    |

Table 2-2: Timestamp update rules for the client in the sequentially consistent version of the Tardis cache coherence protocol. Only the key rules are listed; the reader is referred to [6] for the full table.

| Network event  | State     | Actions                                                                                                                                                        |

|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Any request    | Exclusive | Send owner WRITEBACK request                                                                                                                                   |

| SHARE request  | Shared    | $rts \leftarrow \max(wts + \text{lease}, pts + \text{lease}, rts)$<br>Send client SHARE response                                                               |

| RENEW request  | Shared    | $rts \leftarrow \max(wts + \text{lease}, pts + \text{lease}, rts)$<br>If $wts_{\text{request}} = wts$ , send client RENEW response else send SHARE response    |

| MODIFY request | Shared    | $ \begin{array}{l} \text{Owner} \leftarrow \text{requestor} \\ \text{State} \leftarrow \text{Exclusive} \\ \text{Send requestor MODIFY response} \end{array} $ |

Table 2-3: Timestamp update rules for the manager in the sequentially consistent version of the Tardis cache coherence protocol. Only the key rules are listed; the reader is referred to [6] for the full table.

| Message          | Purpose                                                                                       | Timestamps      |

|------------------|-----------------------------------------------------------------------------------------------|-----------------|

| SHARE<br>MODIFY  | Read a cache block Read or write a cache block                                                | pts             |

| RENEW<br>UPGRADE | Extend a lease of a currently shared cache block<br>Request permission to write a cache block | $pts,wts \ wts$ |

| WRITEBACK        | Cede write permission; maybe write back data                                                  | wts,rts         |

Table 2-4: Descriptions of basic messages in the Tardis cache coherence protocol. Clients send Share, modify, renew, and upgrade requests, while they send writeback responses.

systems running only a single program will not incur performance penalties, as there is no context switching.

#### 2.1.6 Main Memory, Incoherent Memory, and I/O

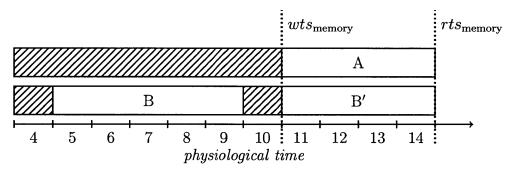

At system reset, no cache blocks are valid. Accesses to main memory bring cache blocks to the last-level cache, but Tardis does not propagate timestamps to main memory. In [6], the timestamp mts tracks accesses to main memory. For congruence with our existing timestamps, we split mts into  $wts_{\rm memory}$  and  $rts_{\rm memory}$ , which respectively represent the highest wts and rts of any cache block written back to main memory. When a cache block is loaded from main memory, it assumes the timestamps  $wts_{\rm memory}$  and  $rts_{\rm memory}$ . Although it applies to all cache blocks brought in from main memory, this conservative measure preserves coherence with a minimum of additional hardware. Figure 2-7 demonstrates the effects of reading and writing from main memory.

Figure 2-7: Interacting with main memory. When cache block A is written to main memory, it moves  $wts_{\text{memory}}$  and  $rts_{\text{memory}}$ . Any blocks read from main memory take timestamps  $wts_{\text{memory}}$  and  $rts_{\text{memory}}$ , even if their original wts and rts are smaller.

If the manager evicts cache block A to main memory, it adjusts  $wts_{memory}$  and  $rts_{memory}$ . If the manager then evicts cache block B to main memory, it does not adjust  $wts_{memory}$  or  $rts_{memory}$  because B's timestamps are smaller. However, if cache block B is brought back into the cache, denoted in the figure as B', it takes on timestamps  $[wts_{memory}, rts_{memory}]$ .

Timestamps that enforce a lower-bound on cache blocks' timestamps may be analogously applied to system input/output (I/O) operations, which, from the perspective

of the last-level cache, behave like accesses to main memory. Timestamps may be more generally applied to govern the interactions with data that comes from off-chip ("incoherent" memory).

## 2.2 Release Consistency and RISC-V

Sequentially consistent systems impose major limitations on program optimizations that reorder memory operations [13]. In fact, modern instruction set architectures do not implement full sequential consistency [14]. However, Tardis-SC inherits the limitations of sequentially-consistent computing. To demonstrate such a limitation, consider a processor connected to a decoupled non-blocking L1 data cache executing the instructions in Figure 2-8.

```

1 | ld x1, 0x0(x2); cache miss

2 | ld x3, 0x0(x4); cache hit

```

Figure 2-8: RISC-V assembly demonstrating a possible hit-under-miss situation, with registers x2 and x4 addressing separate cache blocks.

In Figure 2-8, the processor loads to x1 from the address specified by x2 and then to x3 from the address specified by x4. Suppose that the first instruction triggers a cache miss while x3 is a cache hit. Sequential consistency requires operations to complete in program order [12]. However, if the two memory locations are not causally associated, we unnecessarily wait for x1. An ordinary non-blocking data cache would be able to supply the value of x3 to the processor for further computation.

In the Tardis protocol, if the block containing the data for x3 contains timestamps  $wts_2$  and  $rts_2$  that happen to be greater than pts, the processor timestamp must be advanced to a value within the range  $[wts_2, rts_2]$ . Even worse, reading x1 may cause the premature expiration of the cache block containing the data to be stored in x3, as shown in Figure 2-9.

If the cache block addressed by x2 returns with a timestamp range  $[wts_1, rts_1]$  less than the now-updated pts, then the block must be renewed. In a relaxed consistency model, without an explicit fence instruction, renewals are not necessary – the

Figure 2-9: Timeline diagram demonstrating the limitations of Tardis with sequential consistency. By reading x1, the client expires the cache block storing x3.

processor can read the value x3 without waiting for x1. These optimizations make a strong case for modifying Tardis to support release consistency.

In this thesis, we implement the Tardis cache coherence protocol on the Berkeley Rocket Chip [15] design, which implements RISC-V, a free, open-source ISA from the University of California, Berkeley [16]. Although no particular design choice compels the use of the RISC-V ISA or the release consistency memory model, the existing cycle-level simulator infrastructure for RISC-V is especially attractive for an elegant implementation of Tardis. Although our discussion focuses on release consistency as implemented in RISC-V, these techniques may of course be extended to other architectures.

A relaxed consistency memory model such as release consistency gives architectures the ability to aggressively reorder operations and trusts the programmers to insert fences as needed to preserve all true memory dependencies. In the following sections, we build Tardis-RC, a version of Tardis that implements the release consistency memory model.

#### 2.2.1 Fences

A memory fence instruction preserves the ordering of memory operations as they appear in the program and how they actually apply to memory. Fences force all memory operations leading up to the fence (in the program) to be observable in

memory before proceeding to any memory operation in the program after the fence.

The RISC-V ISA provides a fine-grained fence instruction that specifies which types of memory operations the fence affects. Any memory operation in the *successor* set (in the program) may not be observed until all memory operations in the *predecessor* set (in the program) have been observed. Bits in the instruction encoding specify the members of the predecessor and successor sets, allowing arbitrary combinations of memory fences between reads, writes, inputs, and outputs. For instance, the fence instruction fence w,r prevents any read operation (r) from occurring until all writes (w) before the fence have been observed.

Memory fences in Tardis also have an additional stipulation: that memory operations occurring at physiological timestamps after the fence must occur after the most recent (in physiological time) memory operation. We can derive the physiological time requirements for the fence w,r instruction by examining the predecessor and successor sets: if we must prevent reads from happening before writes, we must require that read operations' timestamps be lower-bounded by any previous write operations' timestamps.

Figure 2-10: Using a write-read fence to prevent reads from happening before writes.

Figure 2-10 demonstrates the effects of a write-read fence. Suppose a client performs a write-read fence after overwriting d with d'. This fence means that any read operation occurring after the fence must occur after any write operation before the fence. Because the most recent write occurred at  $wts_{\text{new}}$ , at timestamp 10, no read operation (that is, no rts) should fall below that timestamp. Therefore, we establish

a minimum read timestamp  $rts_{\min}$  that sets the lowest bound for a read at this client. After performing the fence, a client may read d', but only at timestamps greater than 10. In this thesis, we only consider read/write fences, although we can extend our results to incorporate input/output memory fences.

#### 2.2.2 Release and Acquire Instructions

Atomic instructions, described in greater detail in Chapter 3, modify memory with the guarantee that no other core interposes on theses accesses – "indivisible" instructions. To support release consistency, the RISC-V ISA allows atomic instructions to encode that it represents an acquire or a release access. No memory operation after an acquire operation (in program order) can occur before the acquire operation (in memory order). Similarly, no memory operation before a release operation (in program order) can occur after the release operation (in memory order).

## 2.3 Release Consistency Support for Tardis

To fully relax memory operation ordering while supporting memory fences, we introduce additional timestamps. For arbitrary combinations of read/write memory fences, we need four new timestamps, which express minimum and maximum values for rts and wts, which we will term  $wts_{\min}$ ,  $rts_{\min}$ ,  $wts_{\max}$ , and  $rts_{\max}$ . The timestamps  $wts_{\min}$  and  $rts_{\min}$  express the earliest possible time at which memory operations can occur with respect to previous fences or acquire/release operations. The timestamps  $wts_{\max}$  and  $rts_{\max}$  express the earliest possible time at which the client may complete all of its memory operations. Unlike the minimum timestamps, the maximum timestamps do not enforce bounds; they merely track what values the  $wts_{\min}$  and  $rts_{\min}$  should be set to upon the next fence instruction. It is important to remark that the maximum timestamps required to observe all writes and reads are not necessarily set by the wts and rts of a particular cache block. If the operation may be observed at a timestamp less than  $wts_{\max}$  or  $rts_{\max}$ , then these timestamps do not change.

To support acquire and release atomic operations, we introduce a fifth timestamp,  $ts_{\rm rel}$ , which tracks the timestamp at which a release operation occurred. The processor must guarantee that a release operation occurs after all preceding memory operations by ensuring store buffers have drained and all loads have been serviced. We also define an acquire timestamp,  $ts_{\rm acq}$ , which expresses the time of the acquire operation following the most recent release operation. However, the acquire timestamp merely takes on the value of  $ts_{\rm rel}$ . Thus, we can eliminate  $ts_{\rm acq}$  by requiring that we check  $ts_{\rm rel}$  whenever we must check  $wts_{\rm min}$  or  $rts_{\rm min}$ . We summarize the new rules for updating timestamps in Table 2-5.

| Operation                                                           | Example Instruction                     | Timestamp Update Rule                                                                                                                       |

|---------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Read-read fence Write-write fence Write-read fence Read-write fence | fence r,r fence w,w fence w,r fence r,w | $rts_{\min} \leftarrow rts_{\max}$ $wts_{\min} \leftarrow wts_{\max}$ $rts_{\min} \leftarrow wts_{\max}$ $wts_{\min} \leftarrow rts_{\max}$ |

| Acquire<br>Release                                                  | lr.d.aq<br>sc.d.rl                      | Do nothing $ts_{\text{rel}} \leftarrow \max(wts_{\text{max}}, rts_{\text{max}})$                                                            |

| Load<br>Store                                                       | ld<br>sd                                | $rts_{\max} \leftarrow \max(rts_{\max}, ts_{\text{load}})$ $wts_{\max} \leftarrow \max(wts_{\max}, ts_{\text{store}})$                      |

Table 2-5: Rules for updating the timestamps needed to support relaxed consistency on RISC-V. Timestamps  $ts_{\text{load}}$  and  $ts_{\text{store}}$  represent the earliest physiological times at which a load or store may occur.

We no longer explicitly track the client's place in physiological time with pts. Instead, we use a range of timestamps that bounds when memory operations may occur. Similarly, a load may happen as long as some part of the cache block's timestamp interval extends past  $ts_{min}$ .

### 2.3.1 Compact Timestamp Configurations

Design constraints may limit timestamp storage, or the scheme we describe may be too fine-grained for the architecture and thus underutilized. To reduce the number of timestamps on the system, while preserving correctness, we must tighten constraints on when memory operations can occur. However, reducing the number of timestamps may not impact performance if the architecture implementation, such as Rocket's, does not support the full breadth of memory operation orderings. We can merge  $wts_{\min}$  and  $rts_{\min}$  to create a timestamp  $ts_{\min}$  that contains the lowest possible timestamp at which any memory operation can occur. We can analogously create  $ts_{\max}$  by merging  $wts_{\max}$  and  $rts_{\max}$ .

| Name          | Purpose                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------|

| $ts_{ m min}$ | The earliest physiological time a client may read a cache block.                                                  |

| $ts_{ m max}$ | The earliest physiological time that allows a client<br>to perform all memory operations thus far per-<br>formed. |

| $ts_{ m rel}$ | The value of $ts_{\text{max}}$ at the most recent release operation.                                              |

Table 2-6: Timestamps for Tardis-RC, a release-consistent version of Tardis, as implemented in this thesis.

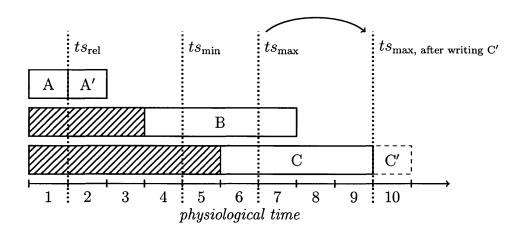

Figure 2-11: Timeline diagram representing timestamps used in Tardis-RC. A release operation sets  $ts_{\rm rel}$ , and reads and writes may change  $ts_{\rm max}$ . Reads are valid only after  $ts_{\rm min}$ .

Figure 2-11 demonstrates the timestamps used in Tardis-RC. The timestamp  $ts_{\rm rel}$  would be set to 2 if a release operation writes A'. No cache blocks need renewals as long as their validity exists at some point after  $ts_{\rm min}$ . Cache block B may be read at timestamps 5 through 7, but not at 4; cache block A must be renewed if the core

loses exclusive ownership after writing A'. The timestamp  $ts_{\min}$  may only be moved by a fence instruction – in the absence of fence instructions, clients may read cache blocks B and C in any order. If a client writes to cache block C, it would be written at timestamp 10;  $ts_{\max}$  would be set to 10 to express the highest timestamp of any operation performed by the client.

To conserve even more space, we can combine  $ts_{\min}$  and  $ts_{\text{rel}}$  into just one time-stamp,  $ts_{\min/\text{rel}}$ . Such a timestamp would be adjusted on every release operation and fence.

#### 2.3.2 Cache Transactions

Tables 2-7 and 2-8 specify the timestamp update rules for the relaxed consistency version of Tardis for the client and manager, respectively.

| Core event         | Cache Block State               | Result     | Actions                                                                                                                         |

|--------------------|---------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| L1 load            | Invalid                         | Load miss  | Send Share request to L2                                                                                                        |

|                    | Shared and $ts_{\min} > rts$    | Load miss  | Send RENEW request to L2                                                                                                        |

|                    | Shared and $ts_{\min} \leq rts$ | Load hit   | $ts_{\max} \leftarrow \max\left(ts_{\min}, rts\right)$                                                                          |

|                    | Exclusive (clean or dirty)      | Load hit   | $ts_{\max} \leftarrow \max\left(ts_{\min}, rts\right)$                                                                          |

| L1 store           | Invalid                         | Store miss | Send MODIFY request to L2                                                                                                       |

|                    | Shared                          | Store miss | Send UPGRADE request to L2                                                                                                      |

|                    | Exclusive (clean or dirty)      | Store hit  | State $\leftarrow$ Exclusive (dirty)<br>$wts \leftarrow rts + 1$<br>$ts_{\text{max}} \leftarrow \max(ts_{\text{min}}, rts + 1)$ |

| Memory fence       |                                 |            | $ts_{\min} \leftarrow ts_{\max}$                                                                                                |

| Eviction           | Shared                          |            | Silently drop cache block State ← Invalid                                                                                       |

|                    | Exclusive (clean or dirty)      |            | Send WRITEBACK response to L2 State $\leftarrow$ Invalid                                                                        |

| WRITEBACK request  | Invalid or Shared               |            | Ignore                                                                                                                          |

| WRITEBACK request  | Exclusive                       |            | $rts \leftarrow wts + \text{lease}$<br>Send WRITEBACK response to L2<br>State $\leftarrow$ Shared                               |

| Other L2 responses |                                 |            | Set cache block data and state $[wts, rts]_{\text{data}} \leftarrow [wts, rts]_{\text{response}}$                               |

Table 2-7: Actions performed by the client (the core and L1 cache). The possible protocol states mirror those in the standard MESI directory-based protocol, and the core maintains three timestamps:  $ts_{\min}$ ,  $ts_{\max}$ , and  $ts_{\text{rel}}$ . Without subscripts, wts and rts refer to the cache block stored at the client.

| Network event      | Cache Block State | Actions                                                                                                                                                                      |  |

|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Any request        | Invalid           | Load from main memory $wts \leftarrow wts_{\text{mem}}$ $rts \leftarrow \max (wts + \text{lease}, ts_{\text{request}} + \text{lease}, rts_{\text{mem}})$                     |  |

|                    | Exclusive         | Send owner WRITEBACK request                                                                                                                                                 |  |

| SHARE request      | Shared            | State $\leftarrow$ Shared $rts \leftarrow \max(wts + \text{lease}, ts_{\text{request}} + \text{lease}, rts)$ Send client SHARE response                                      |  |

| RENEW request      | Shared            | $rts \leftarrow \max(wts + \text{lease}, ts_{\text{request}} + \text{lease}, rts)$<br>If $wts_{\text{request}} = wts$ , send core RENEW response<br>else send SHARE response |  |

| MODIFY request     | Shared            | $Owner \leftarrow requestor$ $State \leftarrow Exclusive$ $Send requestor MODIFY response$                                                                                   |  |

| WRITEBACK response |                   | Write back data $[wts, rts]_{\text{data}} \leftarrow [wts, rts]_{\text{response}}$                                                                                           |  |

| Eviction           | Shared            | $wts_{\text{mem}} \leftarrow \max(wts_{\text{mem}}, wts)$<br>$rts_{\text{mem}} \leftarrow \max(rts_{\text{mem}}, rts)$<br>Store to main memory                               |  |

Table 2-8: Actions performed by the manager (the last-level cache) in the Tardis cache coherence protocol, in response to actions performed by the core in Table 2-7. The last-level cache manages timestamps  $wts_{mem}$  and  $rts_{mem}$ , which are external to any cache block. Without subscripts, wts and rts refer to the cache block stored at the manager. Unlike the client, the manager has three cache block states: Invalid, Shared, and Exclusive.

In the event of a miss in the L1 data cache, the processor will need to request the missing cache block (if invalid) or renew it (if shared with an expired lease). No memory load can be observed at a time earlier than  $ts_{\rm rel}$  or  $rts_{\rm min}$ , so the timestamp sent to the timestamp manager should be  $\max(ts_{\rm rel}, rts_{\rm min})$  to ensure that the block can be read once it has been granted to the processor. Although a store may possibly return a new set of timestamps, the client may attempt an upgrade request to reduce network traffic, in which case it should send wts. Table 2-9 summarizes the timestamps sent with cache misses.

| Operation | Action                                                                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|

|           | $rts_{\text{message}} \leftarrow \max(ts_{\text{rel}}, rts_{\text{min}})$ $wts_{\text{message}} \leftarrow wts_{\text{data}}$ |

Table 2-9: Guidelines for timestamps sent along with messages to the timestamp manager in the event of a cache miss.

#### 2.3.3 Leases and Renewals in Tardis-RC

In Tardis-SC, the duration of the lease must balance the freshness of data and the number of renewals. Relaxed memory semantics explicitly permit cores to read stale values of the data, so it is not necessary to send a renewal request until absolutely necessitated by the rules in Table 2-7. Tardis-RC reduces the importance of fine-tuning the length of the lease, because renewals are only necessary when the core performs a release operation or memory fence.

### 2.4 Stale Reads

Tardis's timestamps allow cores to remain consistent even if they cache stale data, but programmers occasionally require that a core eventually reads the *latest* value of a cache block. "Spinning" on a variable in memory, by repeatedly reading the same address in memory until its value changes, requires that the latest value eventually reaches the core. Conventional directory-based cache coherence protocols only permit

```

1

static int x;

2

3

void produce(int y)

4

5

x = y;

6

7

8

int consume()

9

10

return x;

}

11

```

Figure 2-12: Example producer-consumer implementation in C.

readers of a cache block to observe the latest value. Before any core can update this value, the coherence manager invalidates all read-only copies of the cache block to avoid reading stale data. Unfortunately, a naïve implementation of Tardis may never return the latest value if nothing forces a client to contact the manager for the updated value. In this section, we explore stale reads and how to mitigate its problems.

Consider the producer-consumer example in Figure 2-12, and suppose that the producer code and consumer code run on separate cores. One core running the producer code writes integer y into a global variable x, and a separate core reads x using the consumer code. Programmers expect that all writes occurring to x will be visible to the consumer. In the directory protocol, this is enforced by cache invalidation; each time the producer writes to x, the coherence manager invalidates cores caching x before allowing modifications to the cache block.

In a naïve implementation of the Tardis protocol, no such invalidations enforce coherence for loading stale values. Thus, a consumer core already caching a read-only copy of x may never observe that the producer has written it, even if the producer has written back the data to the main memory.<sup>4</sup> If the consumer code spins on reading x without ever renewing the cache block, the consumer will never complete. To force cores in the Tardis protocol to read the latest value, computer architects must implement at least one of the following techniques below:

Auto-incrementing timestamps Cores periodically increment the minimum time-

$<sup>^4</sup>$ Issuing load requests against an invalid cache block will trigger a writeback to obtain a modified value.

stamp at which a core may observe data,  $ts_{\min}$ . Eventually,  $ts_{\min}$  exceeds the rts of the block and forces a renewal which produces the latest value. This is the method presented in [6].

**New instructions** A new instruction to force the processor to load the latest value, issuing a writeback to a core exclusively caching the cache block if necessary.

Take exclusive ownership A core obtaining the cache block in the exclusive state will always read the latest data.

**Synchronization** Using the above methods, a core can signal through a separate cache block that that the data has changed. Using a memory fence, the core can observe the updated data.

Of the aforementioned techniques, automatically incrementing timestamps is one of the simplest backwards-compatible solutions. This technique does not require adding instructions to the ISA or program binary modifications, and will be essential for legacy code. The time between increments of  $ts_{\min}$  requires careful tuning. Too frequent increments will prematurely expire cache blocks, but too infrequent increments will cause long delays for programs that spin. As a result, this technique is particularly poorly suited for spin locks, which are normally regarded as the simplest solution for extremely short locking periods. Aggressively optimized architectures implementing Tardis may increment  $ts_{\min}$  when spinning on memory is detected.

It may be attractive to implement a new instruction that forces the processor to observe the latest value of the cache block. Such an instruction, however, would require the core to send a message to the last-level cache. Worse yet, a core spinning on a cache block, waiting for another core to update it, could flood the on-chip network. Furthermore, this requires modifications to the instruction set and the creation of a new network message, adding complexity to the hardware-software interface. We conclude that this is not an effective way to obtain the latest data in a cache block.

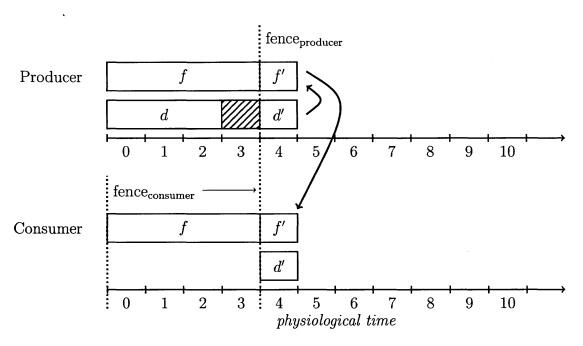

Finally, cores can obtain a fresh copy of the cache block by letting another core signal to it that the cache block has changed; that is, through synchronization. The two cores maintain separate cache blocks. The "producer" uses one of the previously mentioned techniques (auto-incrementing timestamps, executing new instructions, or seizing exclusive ownership) to signal that data in the other cache block have changed. The "consumer" core performs a fence to observe the latest value. (The producer also performs a fence to ensure the data write completes before signalling the consumer.)

Figure 2-13: Timeline diagram demonstrating the use of synchronization to communicate updated data through an external cache block. The consumer uses load-latest instructions to maintain exclusive ownership of f, the flag. Once the producer writes f', the consumer performs a fence to make sure that the read of d', the new data, occurs after the read of f.

### 2.5 Techniques for Writing Tardis Programs

Programs written for systems that implement Tardis differ from conventional programs. Because Tardis may return the stale value of a cache block, programmers wishing to read the *latest* value must obtain the cache block in the exclusive state. On Rocket, the load-reserved instruction happens to load the cache block in the exclusive state, allowing us a way to read the latest data. We discuss the load-reserved instruction in greater depth in Chapter 3. Programs must avoid spinning, as they

may never make forward progress in the absence of auto-incrementing timestamps. Leveraging the exclusive state to implement synchronization sidesteps the problem of stale reads, as we will demonstrate in Chapter 4.

## 2.6 Previous Use of Timestamps for Coherence

Timestamps, including logical timestamps, are not new to coherent distributed shared systems. Lamport discussed logical time in what are now called Lamport clocks [11]. Vector clocks track shared data by assigning timestamps to each processor. The Ficus [17] and Bayou [18] systems tracked file version history with vector clocks and permitted disconnected operation. Treadmarks [19] also uses vector timestamps to manage distributed shared memory at the page level with a relaxed consistency model. However, each vector timestamp contains as many timestamps as there are processors in the system, so these schemes scale poorly to hundreds or thousands of cores.

Google's Spanner system [20] distributes data across its datacenters using globally synchronized timestamps. Tardis does not require globally synchronized timestamps, and Spanner's methods for ensuring consistency, including the use of atomic clocks, are excessive for the scale at which Tardis operates.

## Summary

In this chapter, we introduced the notion of physiological time and a sequentially consistent version of Tardis. With additional timestamps, we augmented Tardis to support a release consistency memory model as used in RISC-V, the ISA used by our simulator infrastructure. We discussed techniques to obtain the latest data in a cache block and how to write effective programs for Tardis. In the next chapter, we extend physiological time to atomic instructions.

# Chapter 3

# Atomic Instructions

Atomic instructions allow processor to modify memory without any other processor modifying the same part of memory. The name for these instructions arises from the notion that no other operation may "divide" these instructions. They are necessary in multiprocessor systems because ordinary loads and stores are not sufficient to perform synchronization [21].

Many types of atomic instructions exist, but some of the most well-known today include compare-and-swap (CAS), atomic memory operations (AMOs), and the load-reserved/store-conditional (LR/SC) pair. These instructions have usability trade-offs that make them suitable for some situations but not others. In this chapter, we take advantage of the Tardis invariant to implement new forms of commonly-used atomic instructions that eliminate some of the drawbacks affecting these instructions.

## 3.1 Compare-and-Swap

The compare-and-swap instruction has existed in the IBM System/370 [22] and in the x86 architecture since the Intel 486 [23]. The compare-and-swap (CAS) instruction compares a value in memory to one of the instruction's operands; if so, the core switches the value in memory with another operand [22]. It returns the old value to the core. Invocations of compare-and-swap that fail the comparison do not affect memory.

Figure 3-1: Hypothetical source code for a compare-and-swap instruction that swaps val with the memory addressed by m if the old value matches old. The whole subroutine completes atomically.

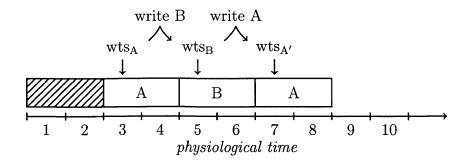

The compare-and-swap instruction suffers from the ABA problem, in which clients are unable to detect changes to a memory location, even if the value has changed in the interim, because it has changed back to its original value [21]. A solution like double-word compare-and-swap increments a counter when it changes the data so that a second client reading from the memory will at least detect the change in the counter. Because Tardis associates data validity with the write timestamp, we can emulate the behavior of double-word compare-and-swap by reading the wts of the cache block to assure that the data has not changed. In fact, it is sufficient to only check wts! If any intervening writes have occurred, wts will change, due to the Tardis invariant. Figure 3-2 illustrates the utility of the Tardis invariant. Suppose a cache block initially starts with data A valid beginning  $wts_A$ . If B replaces A in a cache block, the write timestamp changes to  $wts_B$ . If A later replaces B, it also changes write timestamp, but to a value distinct from the first value of A,  $wts_{A'}$ .

Using Tardis's timestamps allows us to differentiate cache block data and ameliorate the ABA problem affecting the compare-and-swap instruction. We employ the same technique to solve the livelock problem in the load-reserved/store-conditional instruction pair.

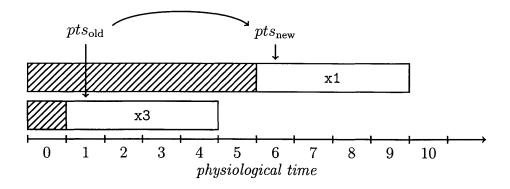

Figure 3-2: Timeline diagram demonstrating avoidance of the ABA problem on Tardis. Even though the data in intervals [3,4] and [7,8] are the same, a client can tell the cache block has changed because  $wts_A$  has changed to  $wts_{A'}$ .

### 3.2 Load-Reserved and Store-Conditional

The S-1 AAP multiprocessor introduced the load-reserved/store-conditional instruction pair [24]. The load-reserved/store-conditional (LR/SC) instruction pair allows critical, short computations to be made atomic by ensuring that no other processor changes the cache block between the load-reserved and store-conditional operations. If the reserved cache block is invalidated or otherwise modified, the store-conditional fails and indicates to the processor that it has failed, thus allowing the processor to try again. Figure 3-3 depicts a RISC-V assembly-language example of an instruction sequence using the LR/SC instruction pair.

Figure 3-3: RISC-V assembly demonstrating a typical load-reserved/store-conditional sequence that implements fetch-and-add.

Two cores executing the same LR/SC instruction sequence can create livelock by executing the load-reserved instruction at nearly the same (physical) time. Because this instruction strongly predicts a store-conditional instruction will follow, the manager grants the first core exclusive ownership. However, the second request forces the first core to write back its exclusively owned cache block in order to grant the second core exclusive ownership. The first core detects the cache block has changed,

and its store-conditional instruction fails. Livelock results from exclusive ownership ping-ponging between the two processors, never allowing one processor to successfully perform a store-conditional.

One solution to livelock requires delaying exclusive ownership requests [25]. The RISC-V ISA, for instance, requires that implementations guarantee the success of LR/SC sequences no longer than 16 instructions [16]. The L1 data cache on Rocket enforces this stipulation by preventing invalidations from reaching the data cache, even if they do not target the block addressed by the LR/SC pair. A store-conditional following a load-reserved in the Rocket core only fails if:

- the processor takes an interrupt or handles an exception,

- the address of the store-conditional does not match the address from the previous load-reserved, or

- more than 32 cycles have elapsed since the data cache processed the loadreserved instruction.

We observe that the last requirement is especially restrictive, because it prevents programmers from making modifications to data requiring more than 32 cycles to complete. As some instructions may stall, 32 cycles may not suffice to meet the ISA-mandated sixteen-instruction guarantee. This could result in programmers resorting to mutual exclusion locks to guard otherwise atomically modifiable memory, causing an increase in complexity and a reduction in performance.

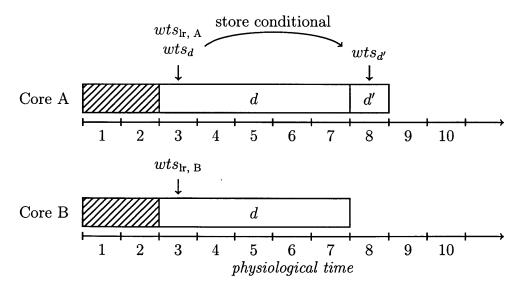

Tardis can implement LR/SC functionality in a livelock-free manner by permitting cache blocks to exist in the shared state despite the presence of an exclusive owner. Typical implementations of the LR/SC pair use a "link register" that stores the address targeted by the load-reserved instruction to ensure that the store-conditional instruction targets the same address. In Figure 3-3, such a register would store the value of x2. In addition to the link register, Tardis maintains a register which we call  $wts_{lr}$  to store  $wts_{data}$ , the wts of the addressed cache block. When the cache performs the store-conditional operation, the L1 data cache gains exclusive ownership of the

block if it does not already have it. The data cache then checks  $wts_{lr}$  against the cache block's current  $wts_{data}$ . If  $wts_{lr} \neq wts_{data}$ , the store-conditional fails because the block has been written since it was load-reserved at this core. Otherwise, the timestamps match and the store-conditional succeeds, as no other core has written the block.

If an exclusive request to the manager causes this core to lose exclusive ownership of the cache block, the core retains  $wts_{\rm lr}$  and the link register of the reservation. As long as  $wts_{\rm data}$  does not change when we regain exclusive ownership of the original cache block, the store-conditional instruction can succeed. Note that the store-conditional instruction will still fail if the processor receives an interrupt or takes an exception. It will also fail if the store-conditional targets a different address from the one targeted by the load-reserved instruction. Most importantly, we no longer need the 32-cycle counter or a sixteen-instruction guarantee provided by the ISA. Now able to use nearly as many cycles as we need, we can design LR/SC sequences that modify the data in considerably more meaningful ways. Of course, keeping instruction sequences short will reduce the number of overlapping LR/SC sequences and keep the store-conditional failure rate low.

Figure 3-4: Timeline diagram demonstrating livelock freedom on the LR/SC instruction pair. Even if Core A loses exclusive ownership of d, it retains  $wts_{lr, A}$ . Upon regaining exclusive ownership, it can complete the store-conditional by verifying that it matches  $wts_{d}$ .