# Investigation and Application of High-Efficiency Large-Step-Down Power Conversion Architectures

by

Samantha Joellyn Gunter

B.S., University of Illinois at Urbana-Champaign (2009)

S.M., Massachusetts Institute of Technology (2011)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2016

$\hbox{@ 2016}$  Massachusetts Institute of Technology. All rights reserved.

| Signature of Author |                                                                    |

|---------------------|--------------------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science          |

|                     | August 31, 2016                                                    |

| Certified by        |                                                                    |

|                     | David J. Perreault                                                 |

|                     | Professor of Electrical Engineering and Computer Science           |

|                     | Thesis Supervisor                                                  |

| Certified by        |                                                                    |

|                     | Khurram K. Afridi                                                  |

|                     | Assistant Professor of Electrical, Computer and Energy Engineering |

|                     | University of Colorado Boulder                                     |

|                     | Thesis Supervisor                                                  |

| Accepted by         |                                                                    |

|                     | Leslie A. Kolodziejski                                             |

|                     | Professor of Electrical Engineering and Computer Science           |

Chair, Department Committee on Graduate Students

## Investigation and Application of High-Efficiency Large-Step-Down Power Conversion Architectures

by

Samantha Joellyn Gunter

Submitted to the Department of Electrical Engineering and Computer Science on August 31, 2016, in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

#### **Abstract**

In this thesis, we introduce two large-step-down dc-dc converter architectures that are designed to provide zero-voltage switching of the power devices. While the techniques used in these converters can be used in a wide range of applications, the operating voltage and power levels used in this thesis are for data centers, where dc distribution power delivery is expected to see its first deployment. The nominal 380 V bus voltage will need to be converted to 12 V using a high-efficiency dc-dc converter that can deliver several hundred watts of power to each rack to power the servers. The converters are expected to operate efficiently across a wide input voltage range of 260 V to 410 V and down to powers in the tens of watts range.

The first converter architecture is based on the concept of an Impedance Control Network (ICN) resonant converter. Using phase-shift control along with a specifically designed impedance network, this converter can maintain resistive loading of the inverters as the input voltage varies. To back down in power, the converter can be efficiently operated using burst (on/off) mode control. To deliver lower power, we introduce an additional control technique using Variable Frequency Multiplier (VFX) inverters and/or rectifiers.

The second converter architecture combines the properties of an active bridge converter with multiple stacked inverters, a multi-winding single core transformer, and a reconfigurable rectifier. The stacked inverter topology improves the range of powers over which zero-voltage switching can be achieved. The multi-winding transformer and reconfigurable rectifier further extend the efficient operating range to very low powers by reducing core loss and increasing zero-voltage switching capability.

Both proposed architectures are suitable for large-step-down, wide-input voltage, wide-output power applications such as dc-dc converters for dc distribution.

Thesis Supervisor: David J. Perreault

Title: Professor of Electrical Engineering and Computer Science

Thesis Supervisor: Khurram K. Afridi

Title: Assistant Professor of Electrical, Computer and Energy Engineering

University of Colorado Boulder

Thesis Reader: Jeffrey H. Lang

Title: Professor of Electrical Engineering and Computer Science

#### Acknowledgments

This thesis presents an accumulation of work, but it is by the grace of God and through the support of many that I have been able to come this far. I have been truly blessed to be able to work with such a gracious committee. My advisors, David Perreault and Khurram Afridi, have been so generous with their time and knowledge. I am grateful for their mentorship, helping me to nurture and refine many professional skills. And as a testimony to their thoughtfulness, they have opened up their homes to me and others, multiple times. I am also grateful for the patience, support, and encouragement of my other committee member, Jeffrey Lang. His kindness has made me feel at ease through this process and his enthusiasm for the work is always refreshing.

I would also like to acknowledge the financial support of the MIT Energy Initiative, the National Science Foundation, the Skolkovo Institute of Science and Technology, and Texas Instruments. It is from their support that I was able to spend the time to theorize, design, build, and test multiple converters.

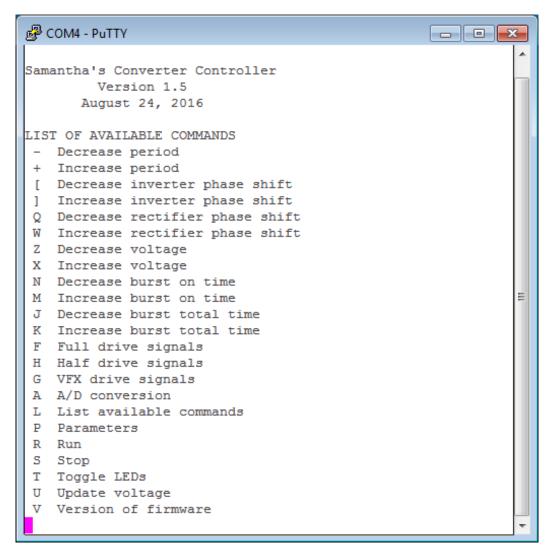

There are many others who I am indebted to. It was a real pleasure to get to know David Otten, who developed the control board for the converters. He is such an invaluable resource to LEES! Not surprisingly, his controller design is amazing – it can pretty much do whatever I ask of it and more. Rose Abramson has also been a tremendous help and source of support. First as a UROP and then as an MEng, she has been there with me as we would spend hours soldering or running the converter. She gathered many of the final efficiency curves to make this work so exciting. There are many others who have helped me along the way, answering a plethora of questions. Thank you, Minjie, Juan, Seungbum, Wardah, Yiou, Matt, and Alex.

When I applied to graduate schools, I applied for Master's only because I figured only a couple more years of school would be enough. Little did I know that I would be spending many more years at MIT than I had originally anticipated. In just a few short weeks, it became abundantly clear to me that MIT was an amazing place full of an incredible diversity of people. I am just so happy to have been a part of this community. Thank you to all my friends who have made me believe I have truly found paradise – Stephen, Michael, Phil, Nick, Dave, Ian, Grant, Seoyoung, Morgan, Richard, Aaron, Kevin, Chi, Kendall, Marianna, Janet, Francine and so many more.

I also found an incredibly amazing person at MIT. Thank you, Justin, for being there, always. I have enjoyed exploring the world with you as well as just sitting on the couch and watching TV. I am grateful for all the support you have given me and I am comforted to know I can depend on you. You have been a great gift to me.

I would also like to thank my family. Mom and Dad, you have taught me well and I know I would not be here today without your love and support. I know I can always depend on you, and no

matter how much I learn, you will still have things to teach me. Thank you, for all you have done my entire life.

### Contents

| Chapter 1 | Intr  | oduction                                                 | 39 |

|-----------|-------|----------------------------------------------------------|----|

| 1.1       | Mot   | ivation                                                  | 39 |

| 1.2       | State | e of the Art                                             | 41 |

|           | 1.2.1 | Resonant Converters                                      | 44 |

|           | 1.2.2 | Dual Active Bridge Converters                            | 47 |

| 1.3       | Thes  | sis Scope and Objectives                                 | 49 |

| 1.4       | Thes  | sis Organization                                         | 51 |

| Chapter 2 | 2 Imp | edance Control Network Resonant Converter                | 53 |

| 2.1       | The   | ory of the Proposed Architecture                         | 54 |

|           | 2.1.1 | Double Stacked-Bridge Inverter                           | 54 |

|           | 2.1.2 | Transformation Stage: Lossless Impedance Control Network | 55 |

|           | 2.1.3 | Rectification Stage                                      | 62 |

|           | 2.1.4 | Simulation of the Proposed Architecture                  | 63 |

| 2.2       | Exp   | erimental Implementation                                 | 65 |

|           | 2.2.1 | Switching Devices                                        | 65 |

|           | 2.2.2 | Transformer Design                                       | 68 |

|           | 2.2.3 | Coupled Inductor Design                                  | 73 |

|           | 2.2.4 | Resonant Inductor Design                                 | 76 |

| 2.3       | ICN   | Converter Performance                                    | 77 |

|           | 2.3.1 | Converter Waveforms across Input Voltage                 | 80 |

|           | 2.3.2 | Converter Loss Analysis                                  | 85 |

|           | 2.3.3 | Converter Performance across Output Power                | 88 |

| 2.4       | Sum   | mary of the ICN Resonant Converter                       | 93 |

| Chapter 3 | 8 Var | iable Frequency Multiplier                               | 95 |

| 3.1       | The   | ory of the Proposed Method                               | 95 |

| 3.2       | App   | lication of the Frequency Multiplier Technique           | 99 |

|           | 3.2.1 | Simulation of the Proposed Frequency Multiplier Method               |

|-----------|-------|----------------------------------------------------------------------|

|           | 3.2.2 | Experimental Application 108                                         |

| 3.3       | Sum   | mary of the VFX Technique                                            |

| Chapter 4 | 4 Rec | onfigurable Double Stacked Active Bridge Converter Theory113         |

| 4.1       | The   | ory of the Proposed Architecture                                     |

|           | 4.1.1 | Double Stacked-Bridge Inverter 11:                                   |

|           | 4.1.2 | Single Magnetic Component                                            |

|           | 4.1.3 | Reconfigurable Rectifier                                             |

| 4.2       | Ope   | rating Modes                                                         |

| 4.3       | Sim   | ulation                                                              |

| 4.4       | Sum   | mary of the Proposed Reconfigurable Double Stacked Topology136       |

| Chapter 5 | 5 Rec | onfigurable Double Stacked Active Bridge Converter Implementation    |

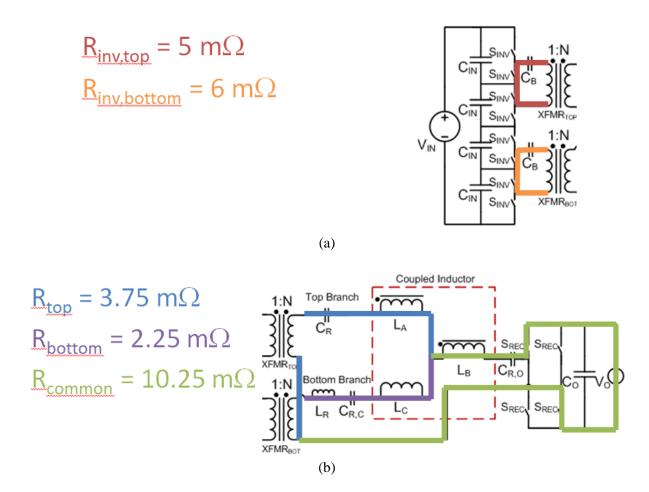

| 5.1       | Con   | aponent Selection and Design                                         |

|           | 5.1.1 | Switching Devices                                                    |

|           | 5.1.2 | Transformer Implementation                                           |

|           | 5.1.3 | Benchmark Prototypes                                                 |

| 5.2       | Con   | verter Performance                                                   |

|           | 5.2.1 | Converter Waveforms Across Input Voltage                             |

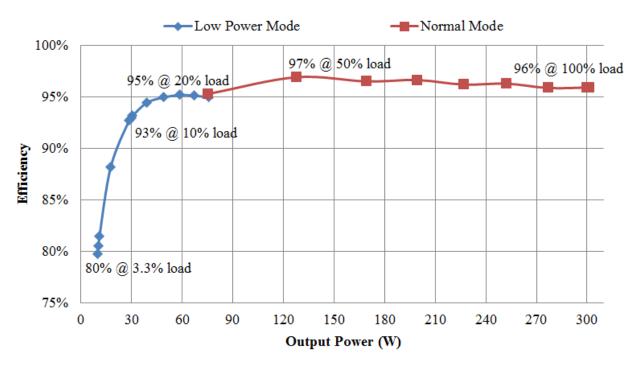

|           | 5.2.2 | Converter Performance Across Output Power under Normal Operation 164 |

|           | 5.2.3 | Converter Performance Across Output Power in Low-Power Mode          |

| 5.3       | Sum   | mary of the Reconfigurable Double Stacked Active Bridge Converter172 |

| Chapter 6 | 5 Sun | nmary and Future Work                                                |

| 6.1       | Sum   | mary                                                                 |

| 6.2       | Con   | clusions                                                             |

| 6.3       | Dire  | ctions for Future Work                                               |

| Appendix  | A M   | MATLAB Code                                                          |

| Appendix  | к В М | 12Spice Geometry Files                                               |

| B.1 Transformer                                                                     | 215 |

|-------------------------------------------------------------------------------------|-----|

| B.2 Coupled Inductor                                                                | 223 |

| B.3 Resonant Inductor                                                               | 229 |

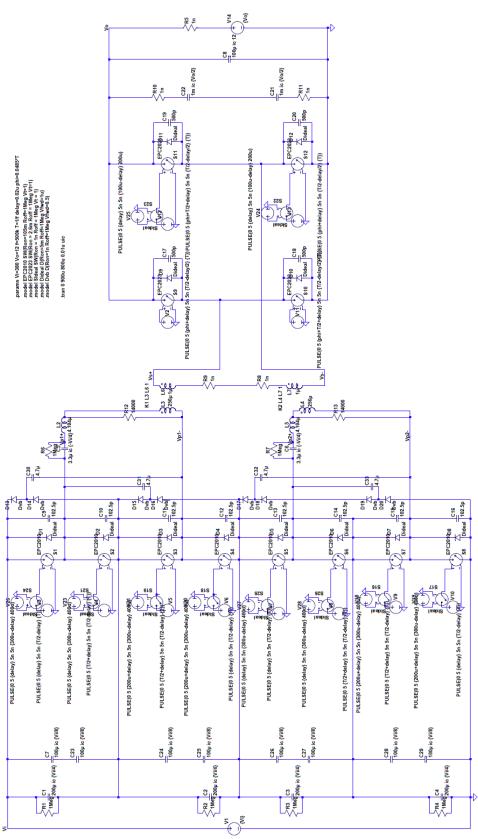

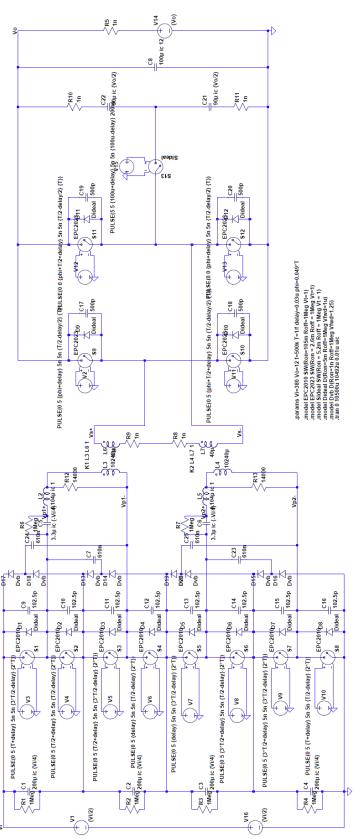

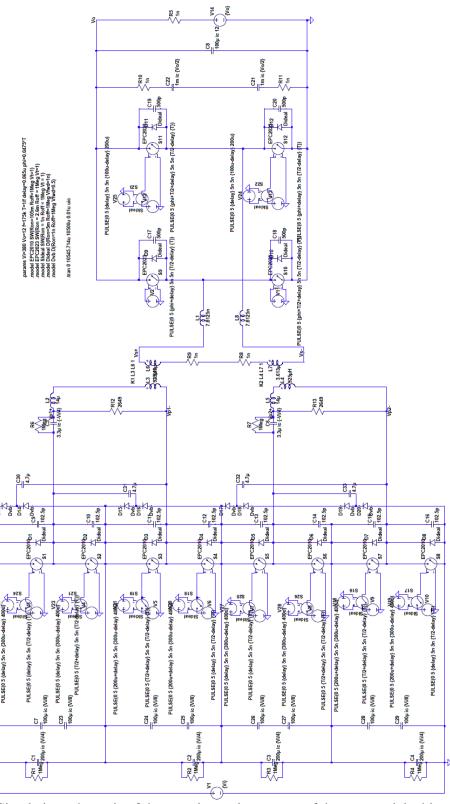

| Appendix C LTSpice Simulation Files                                                 | 231 |

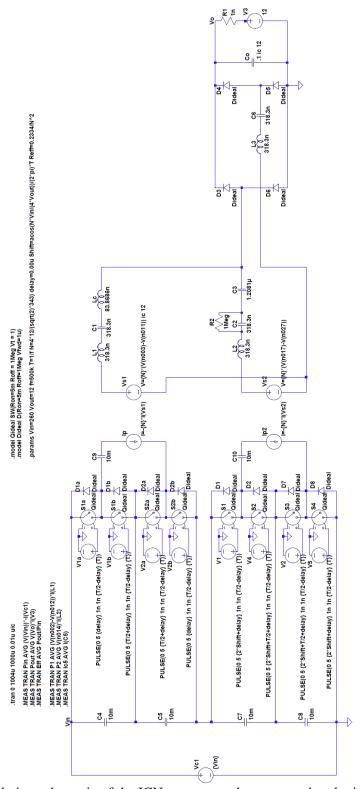

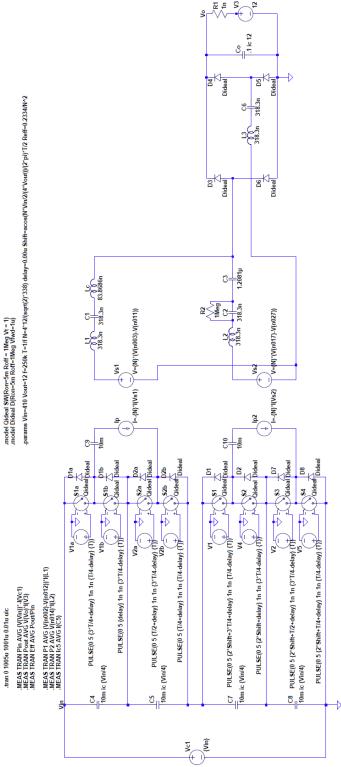

| C.1 ICN Converter Simulations in Fundamental Mode                                   | 232 |

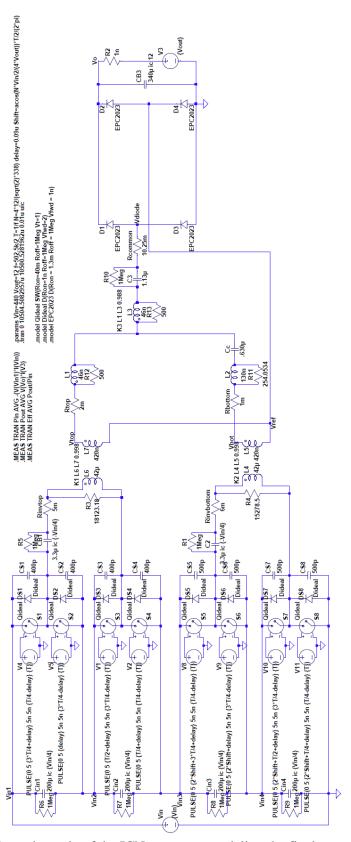

| C.2 ICN Converter Simulations in VFX Mode                                           | 240 |

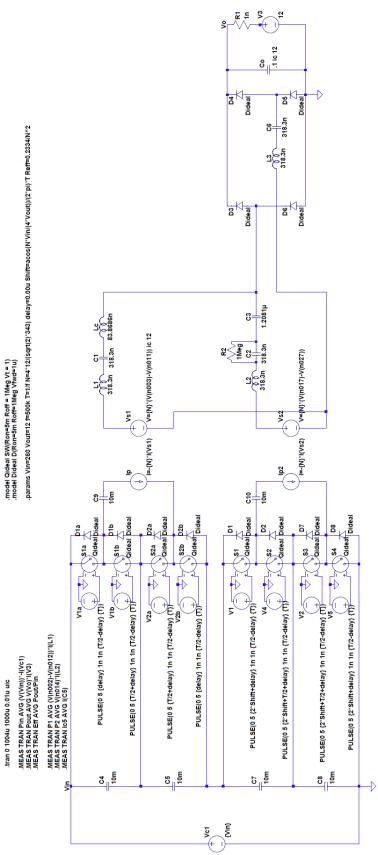

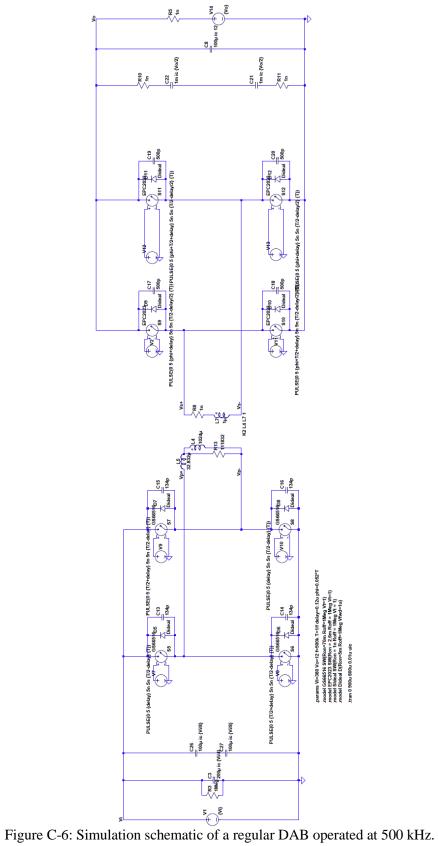

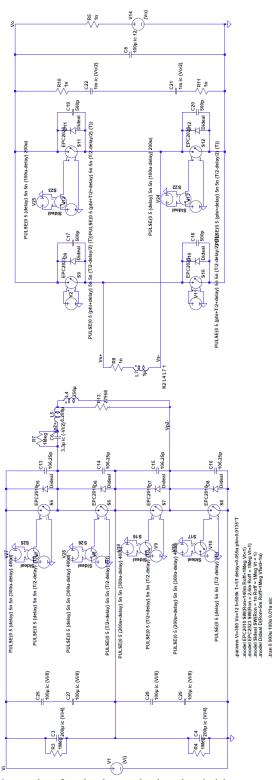

| C.3 Active Bridge Converter Simulations                                             | 246 |

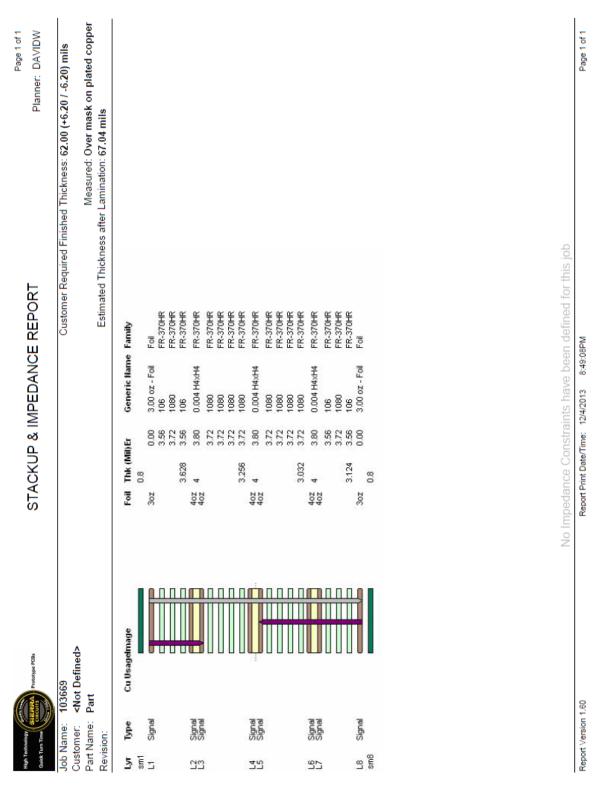

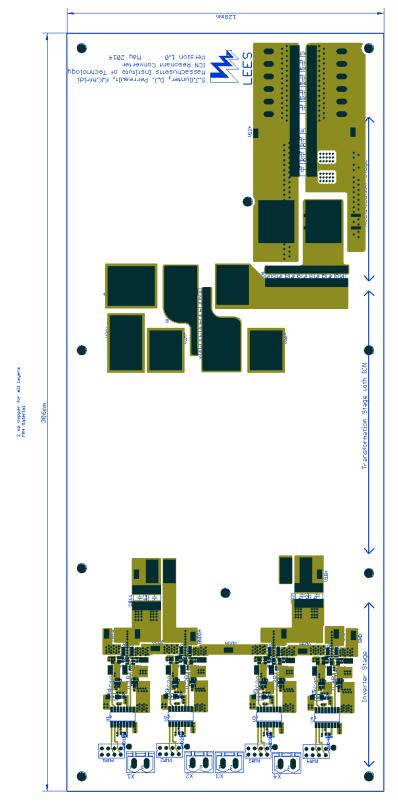

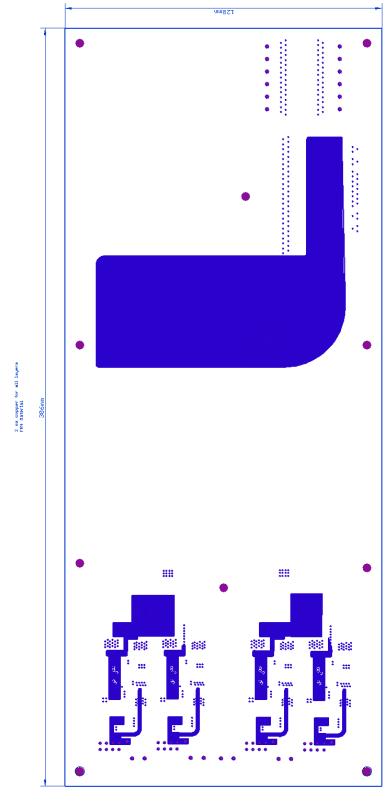

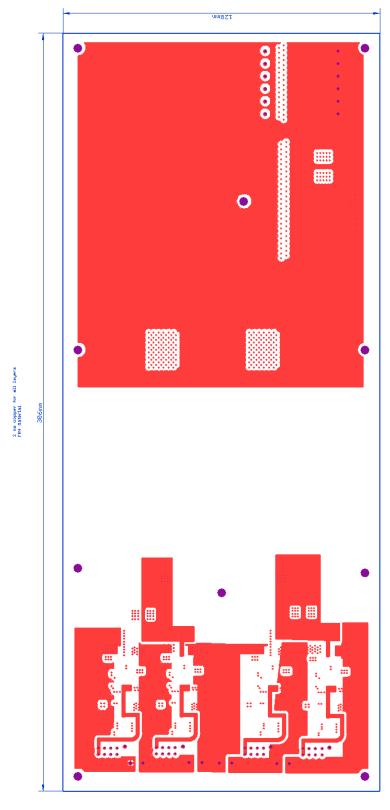

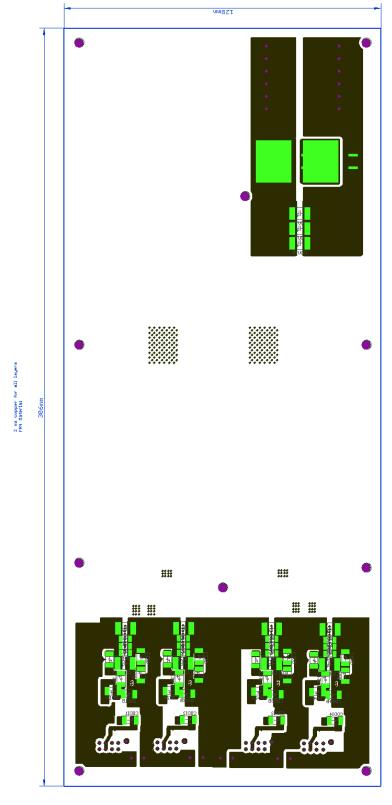

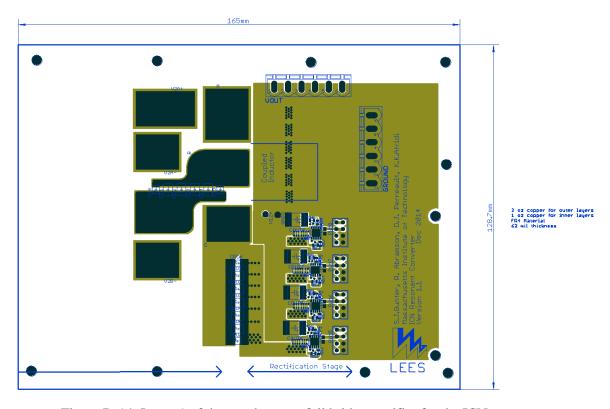

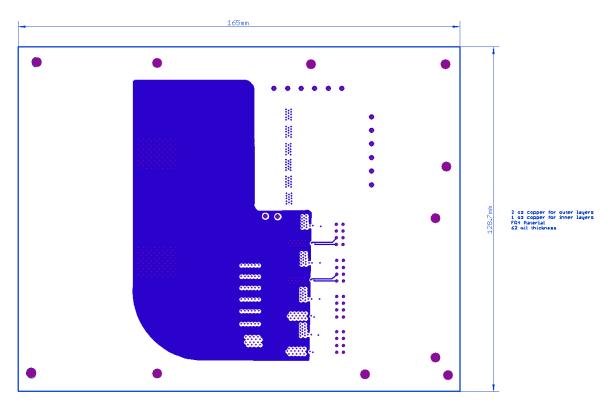

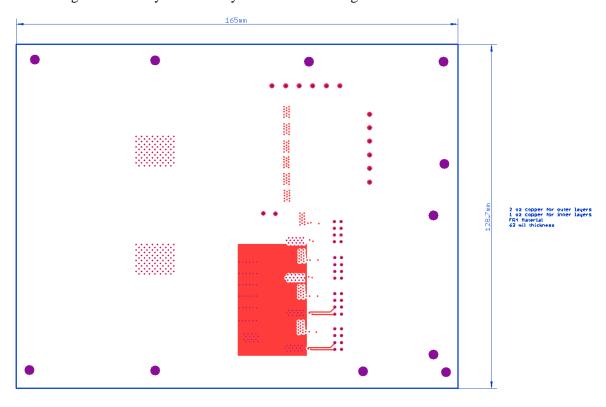

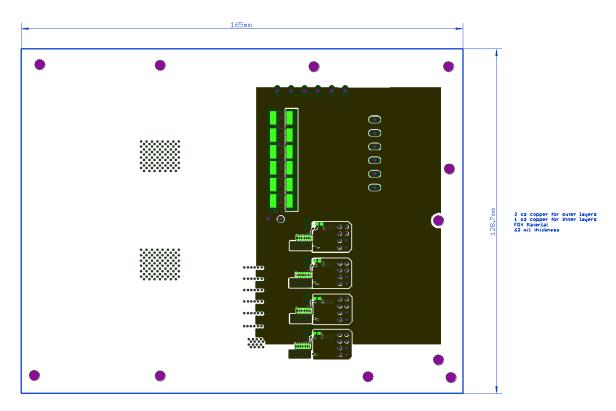

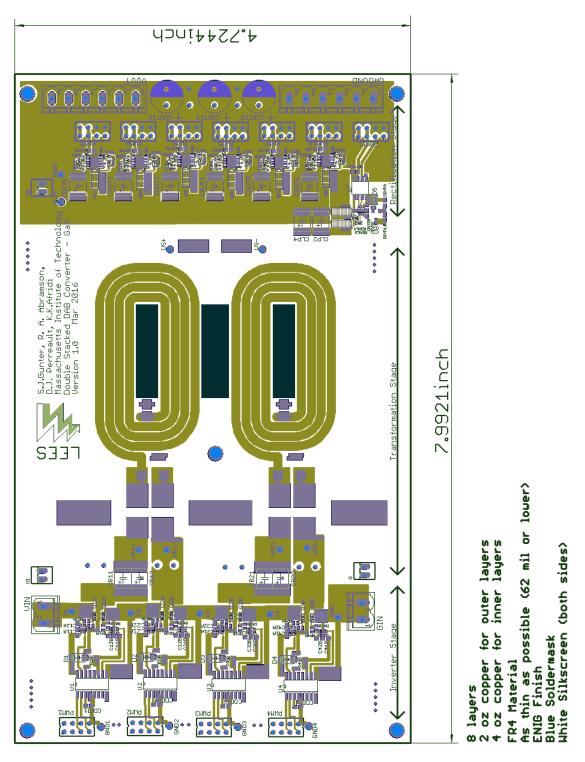

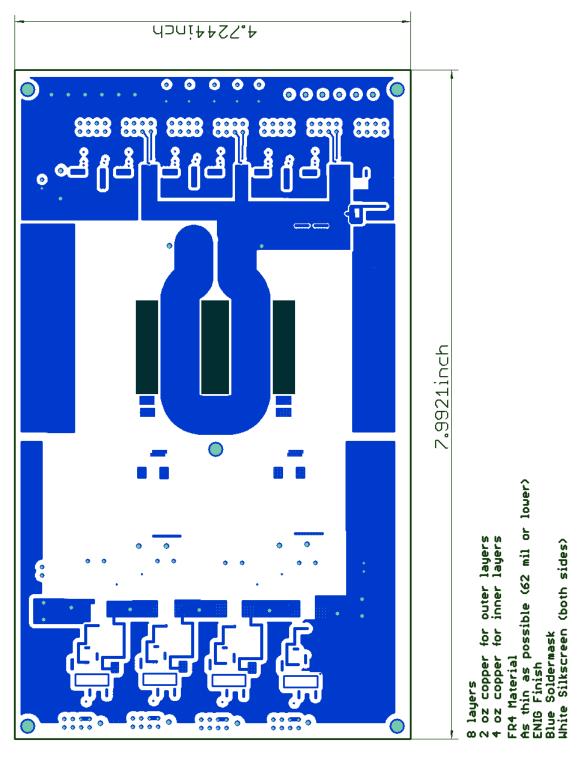

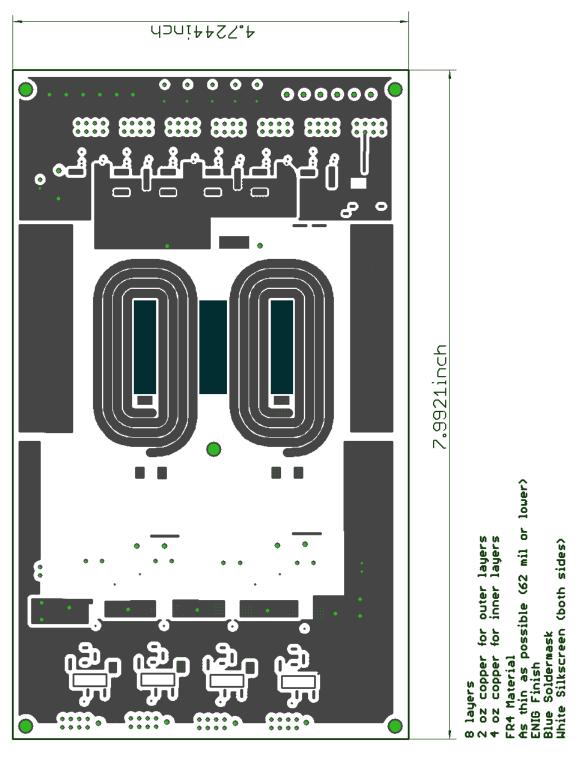

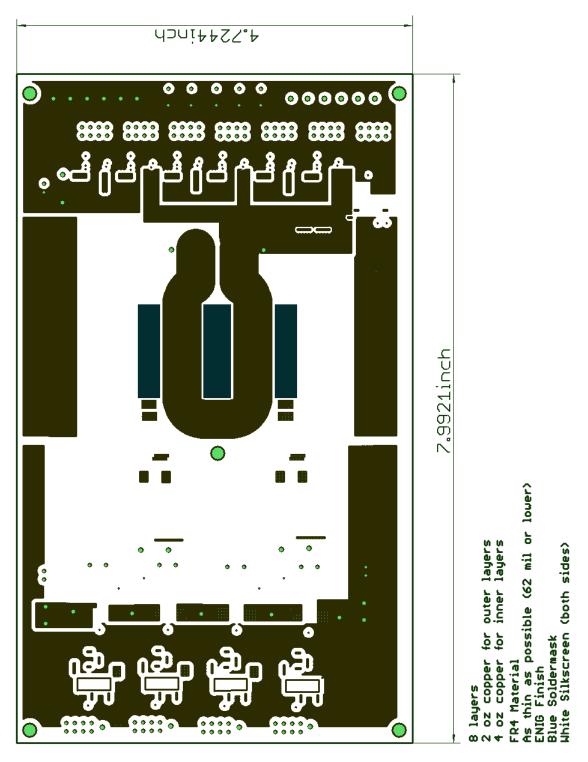

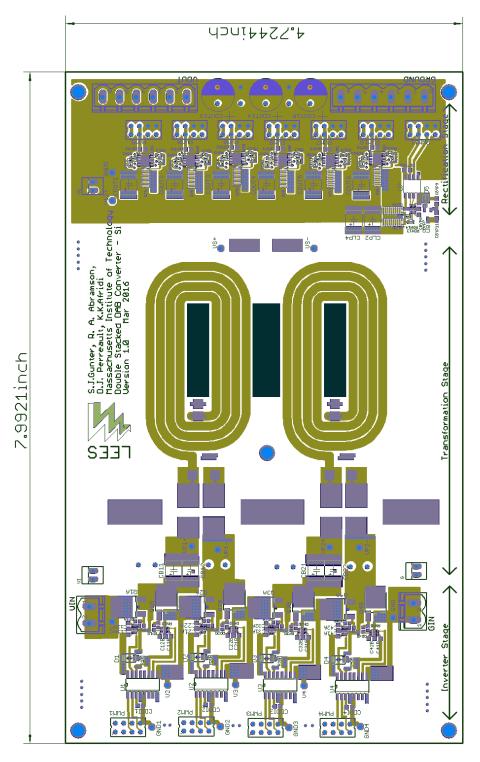

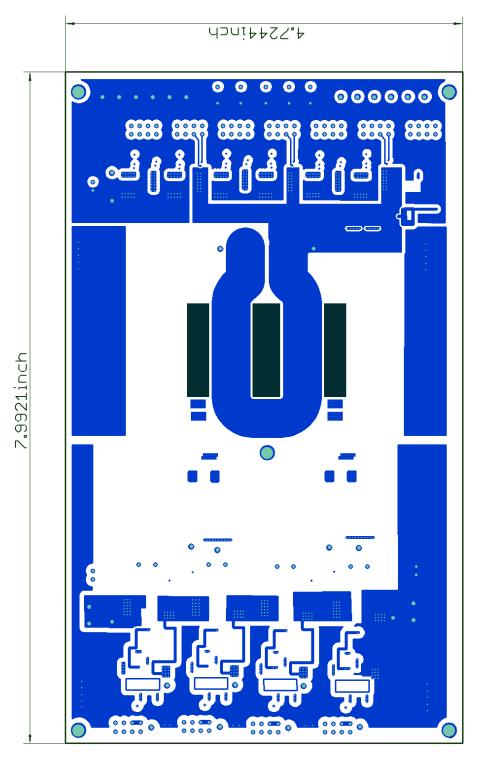

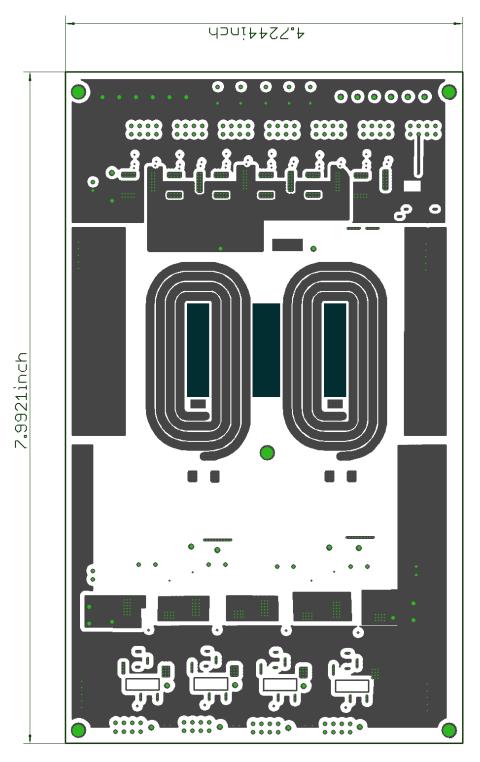

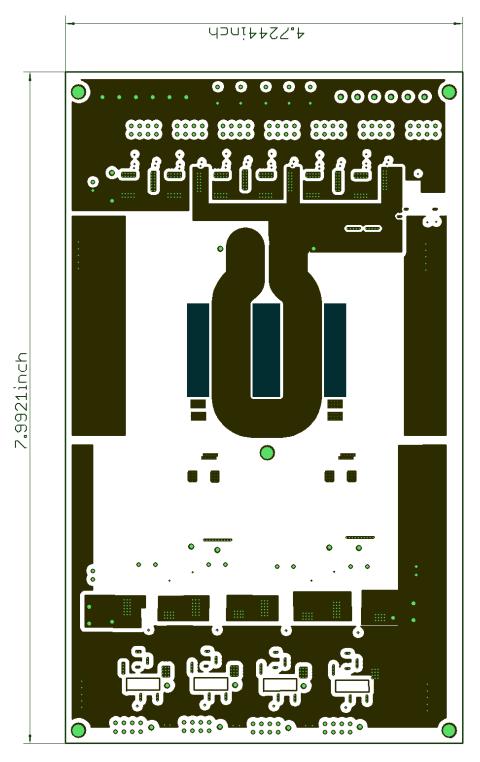

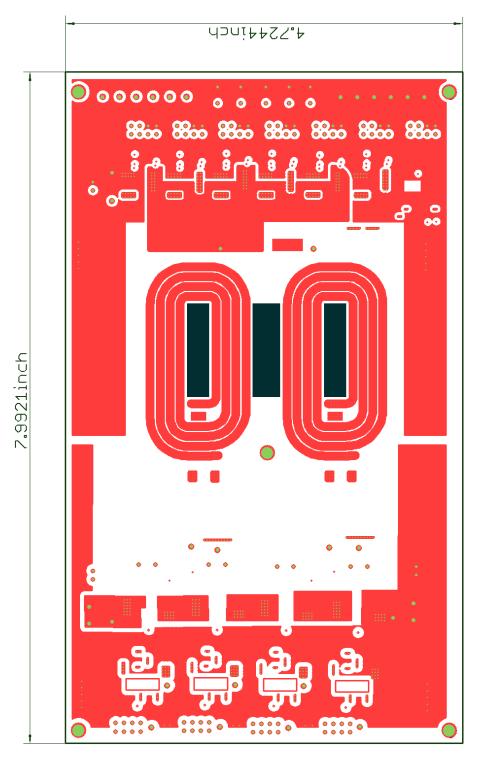

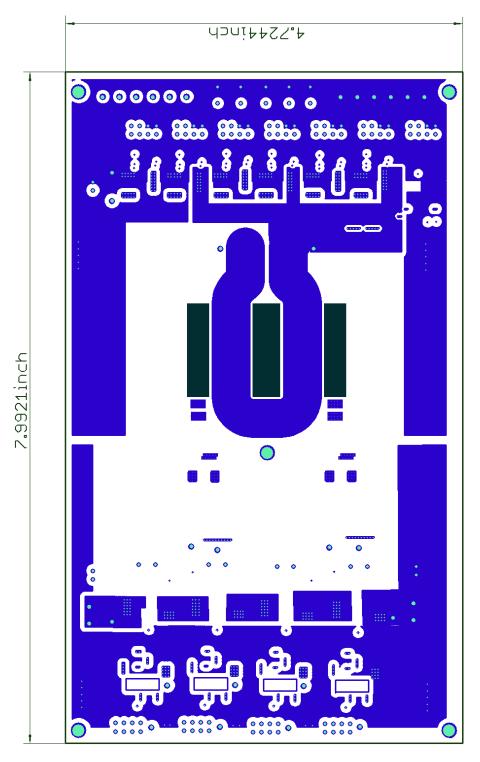

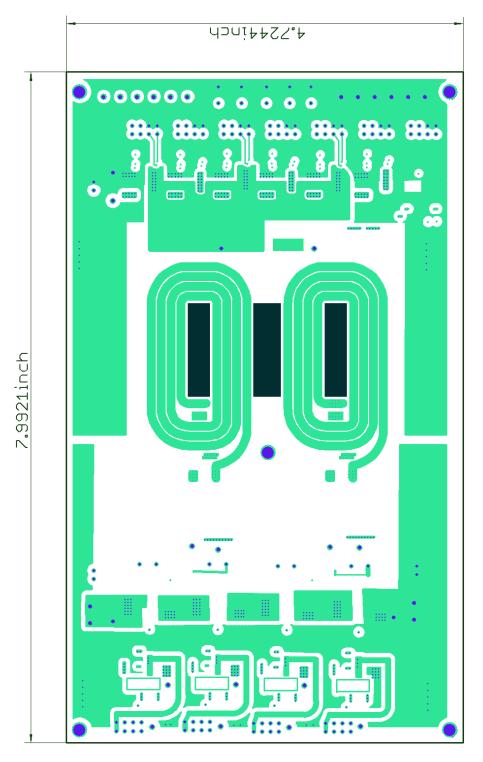

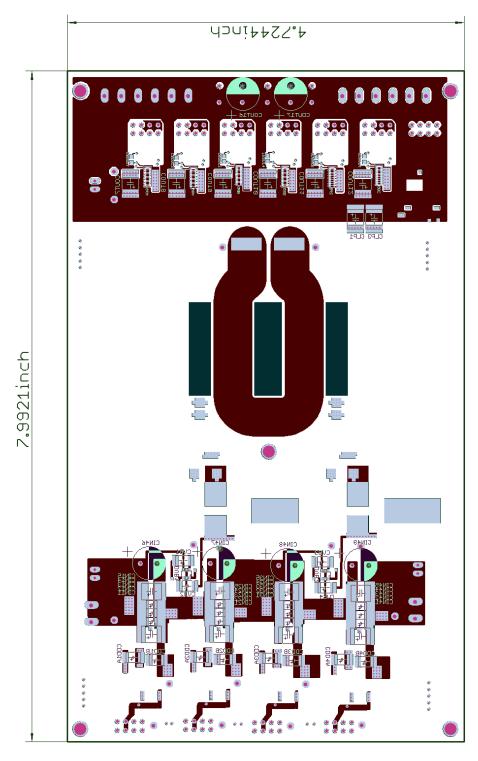

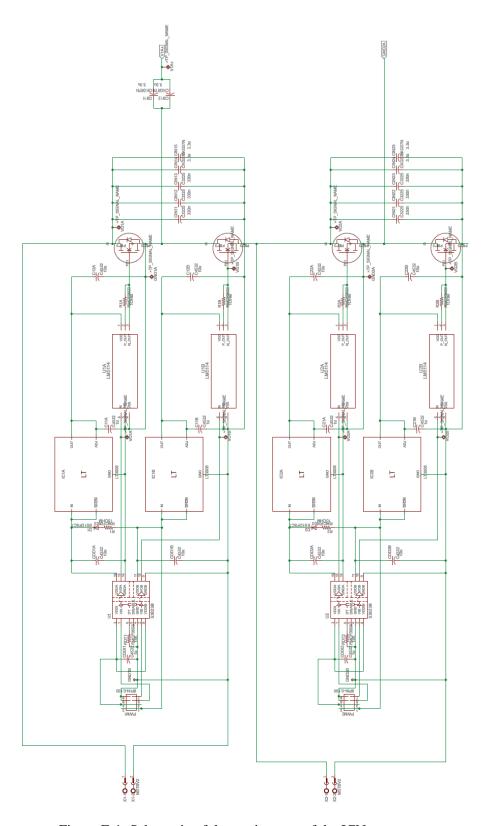

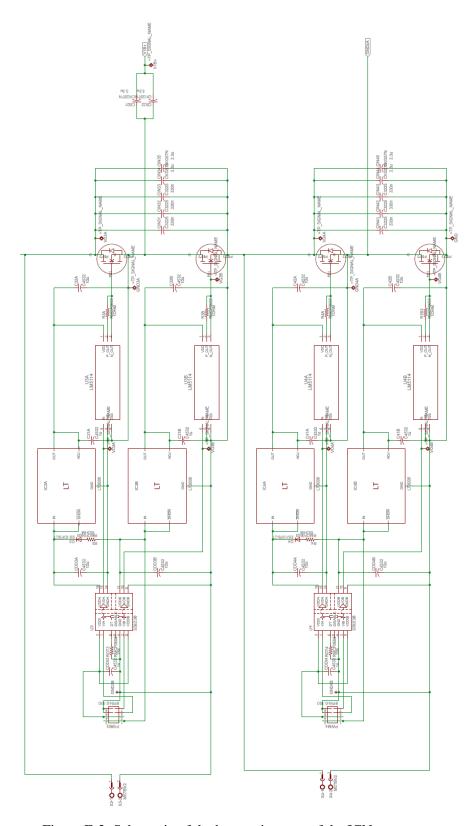

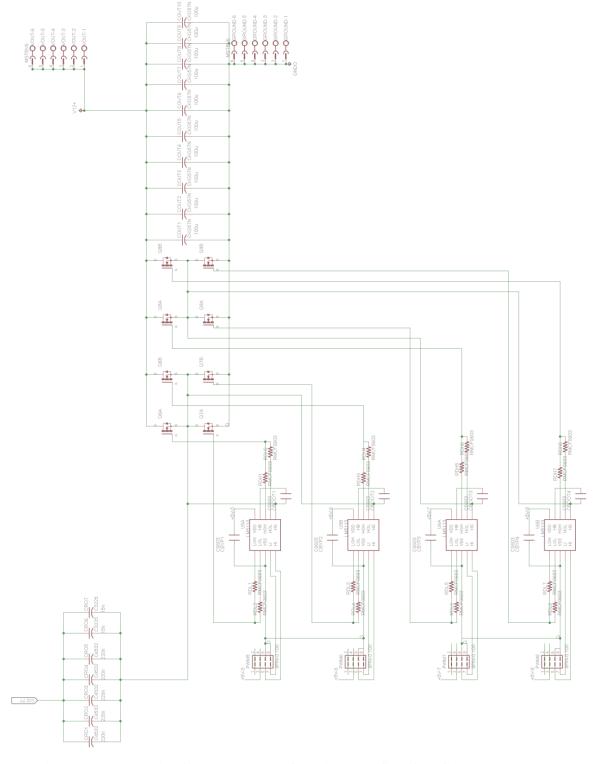

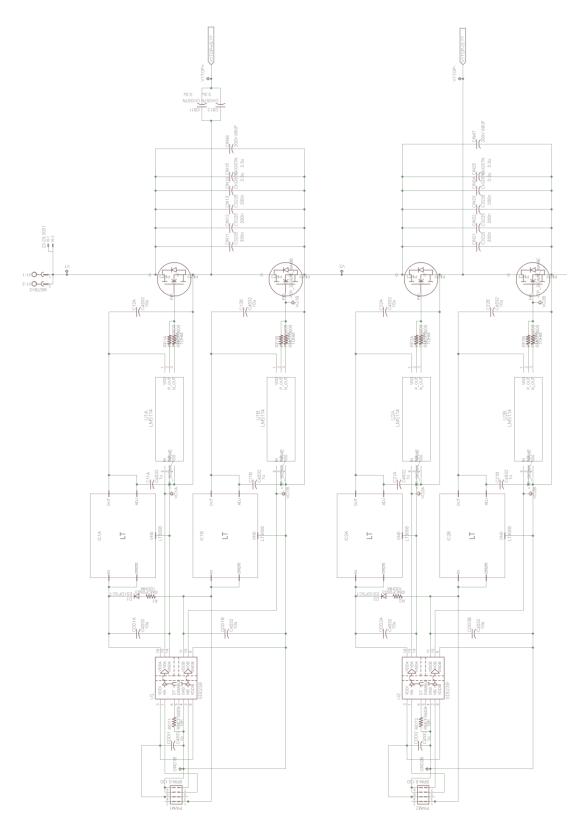

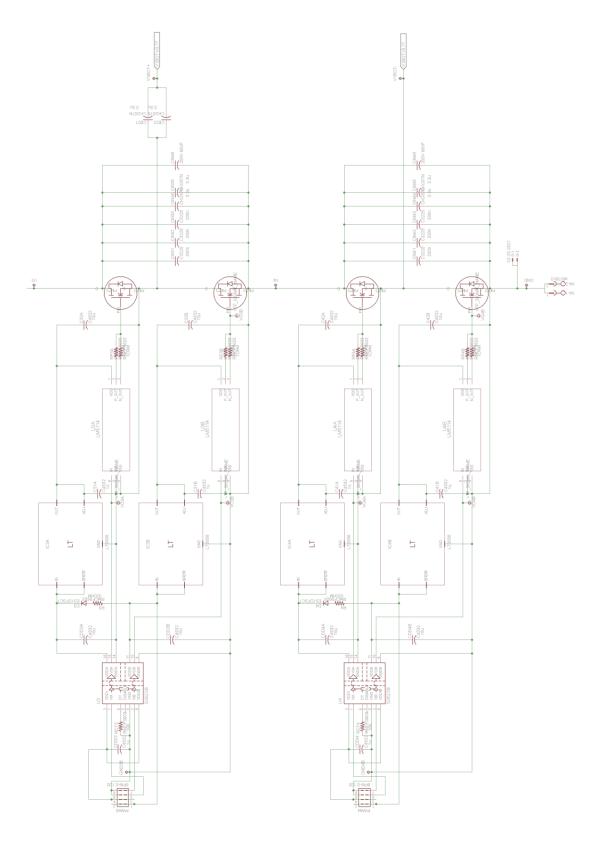

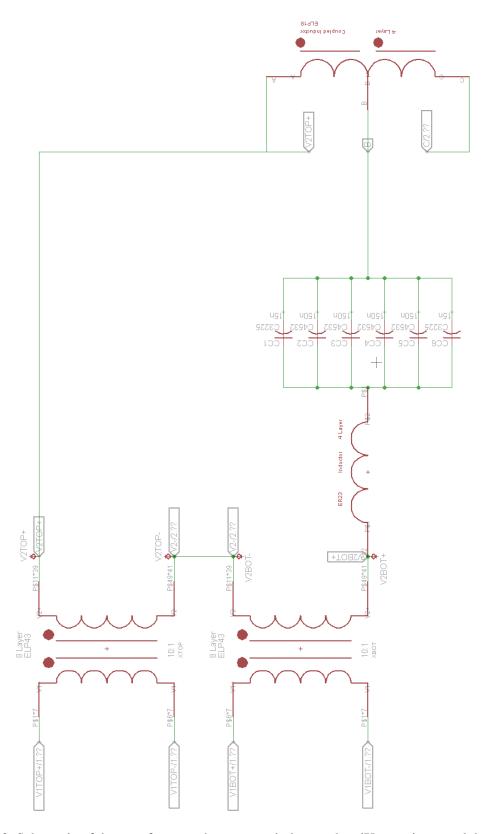

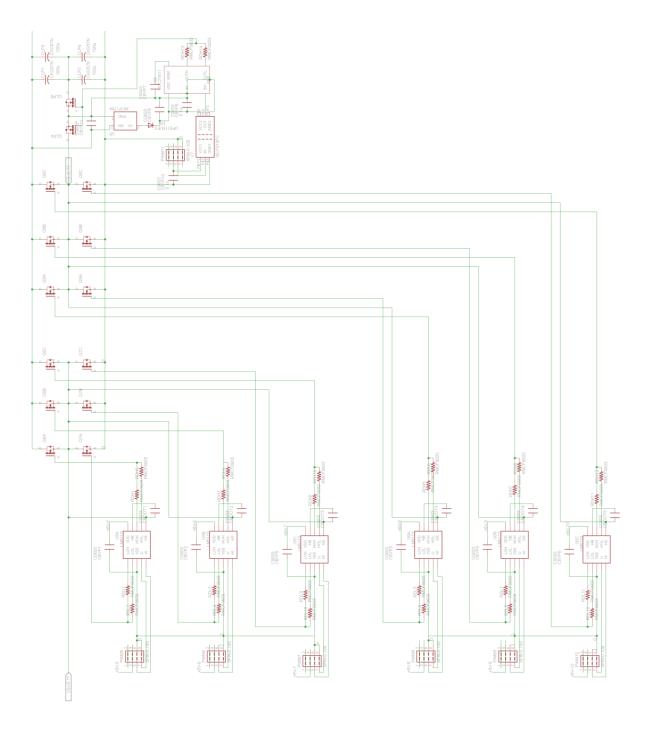

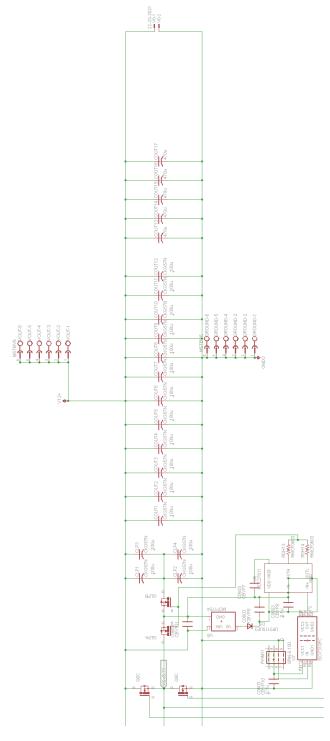

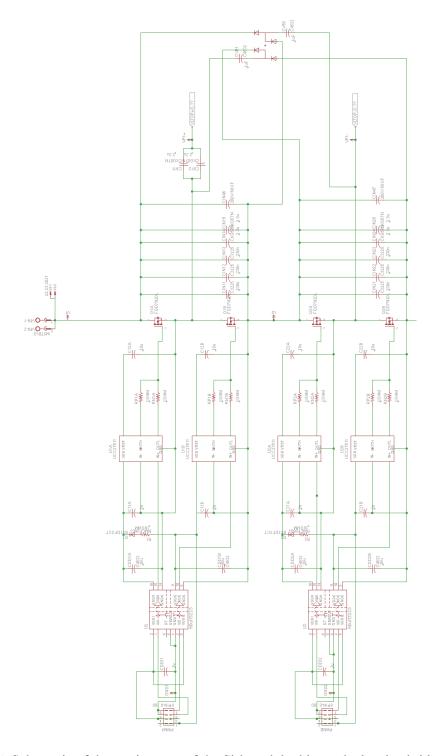

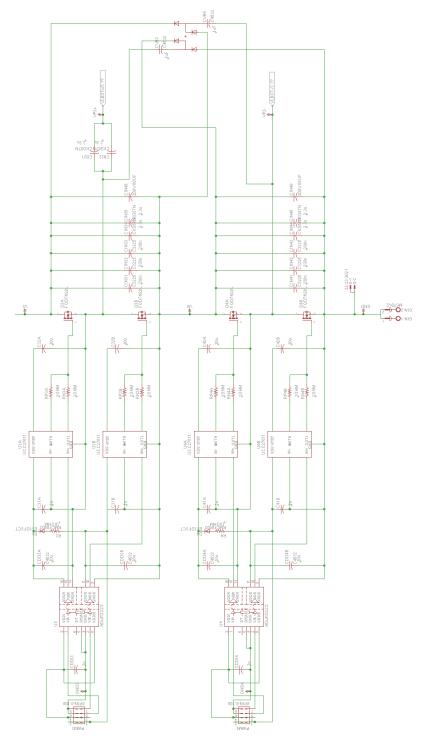

| Appendix D EAGLE Layout Files                                                       | 267 |

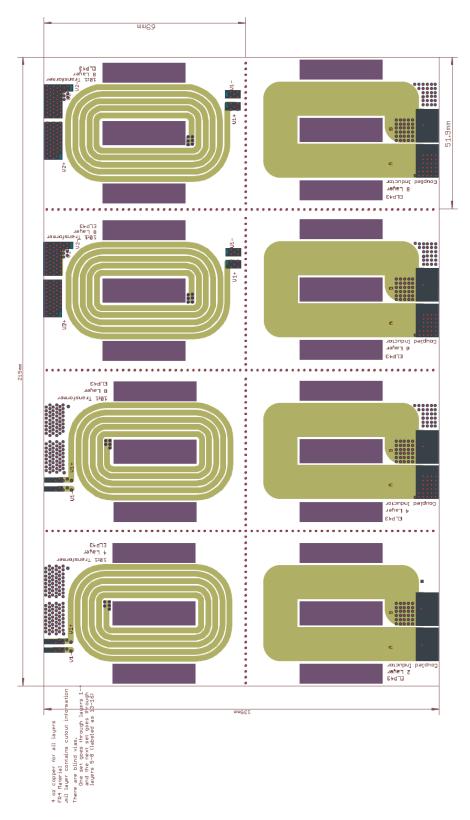

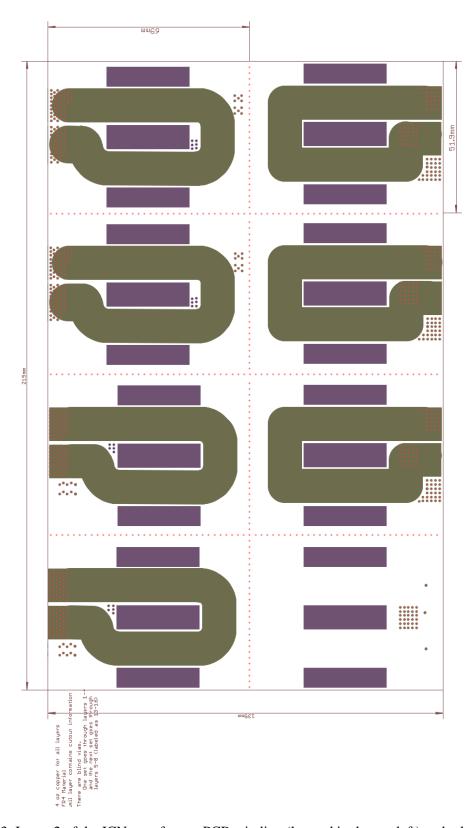

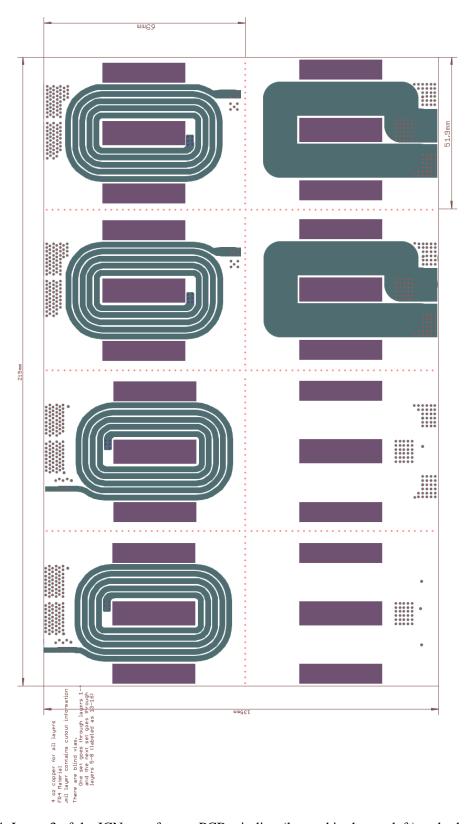

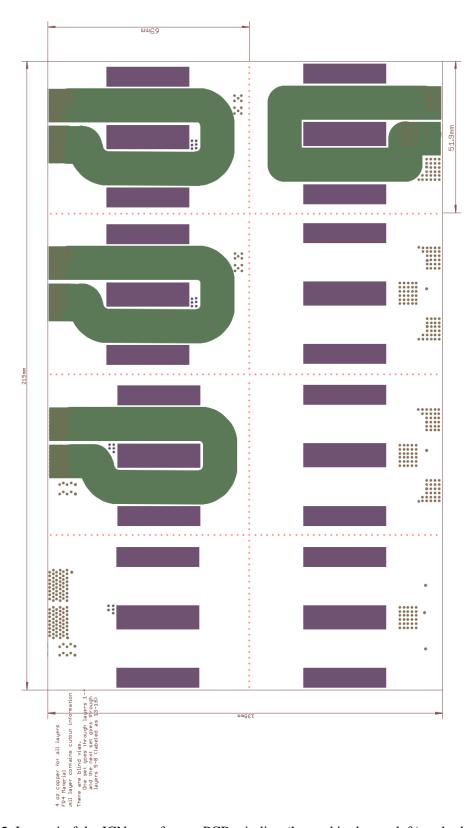

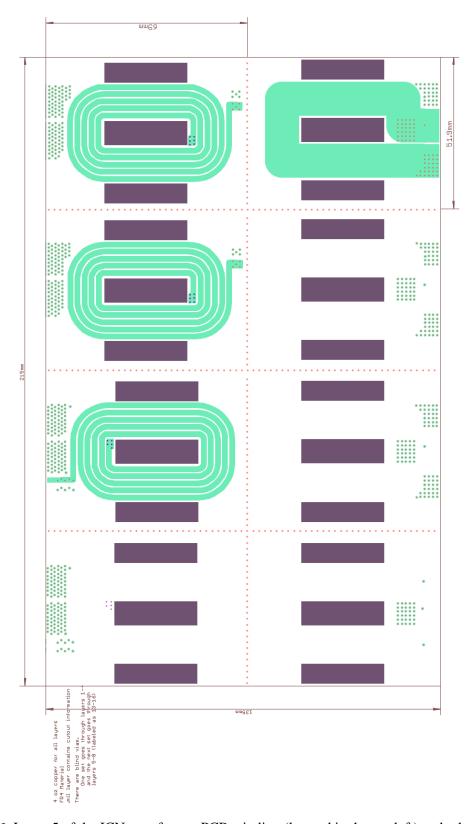

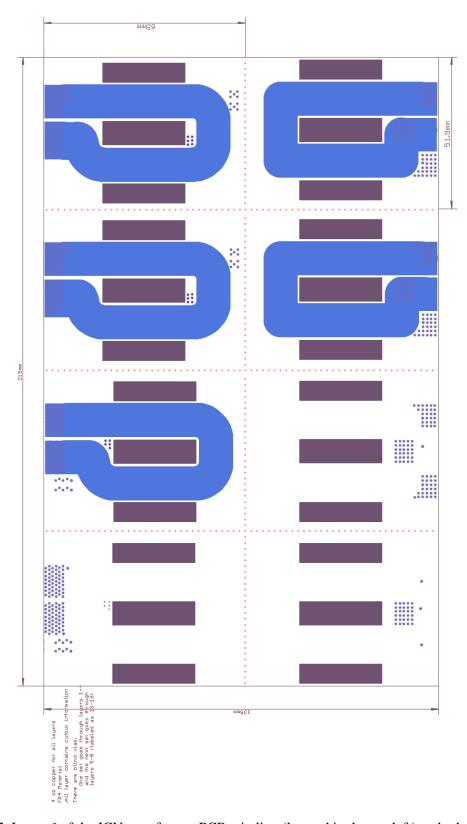

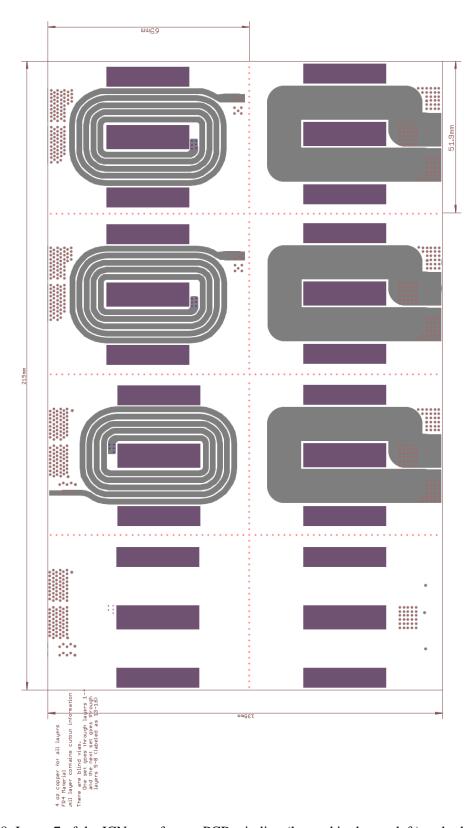

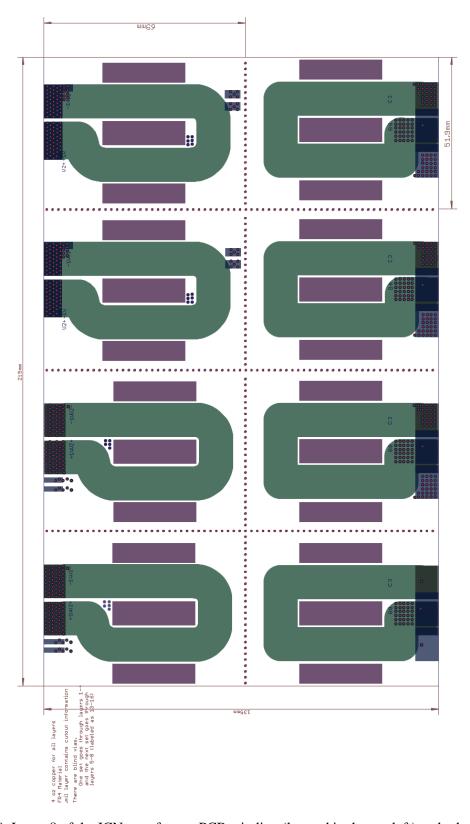

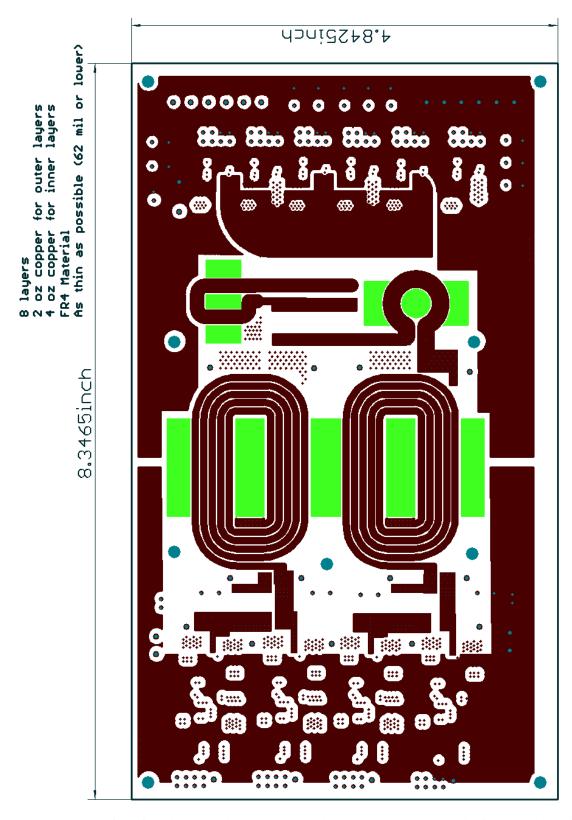

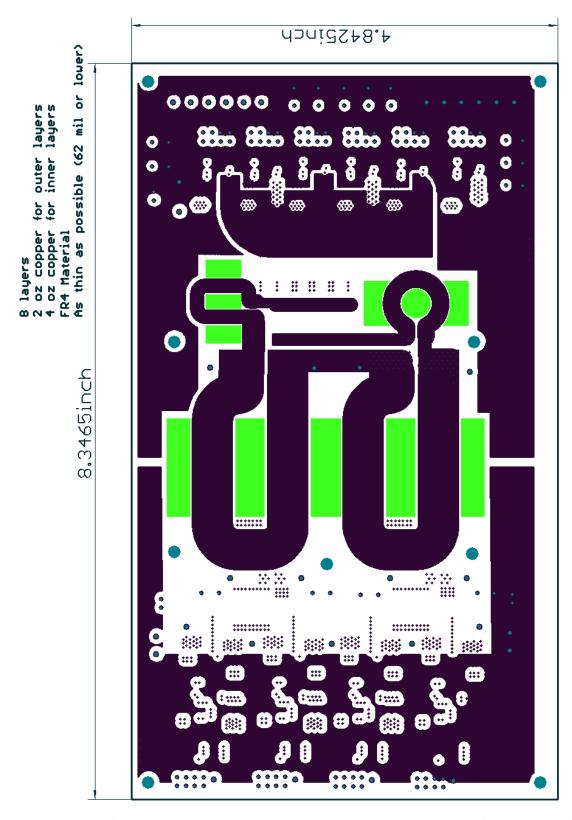

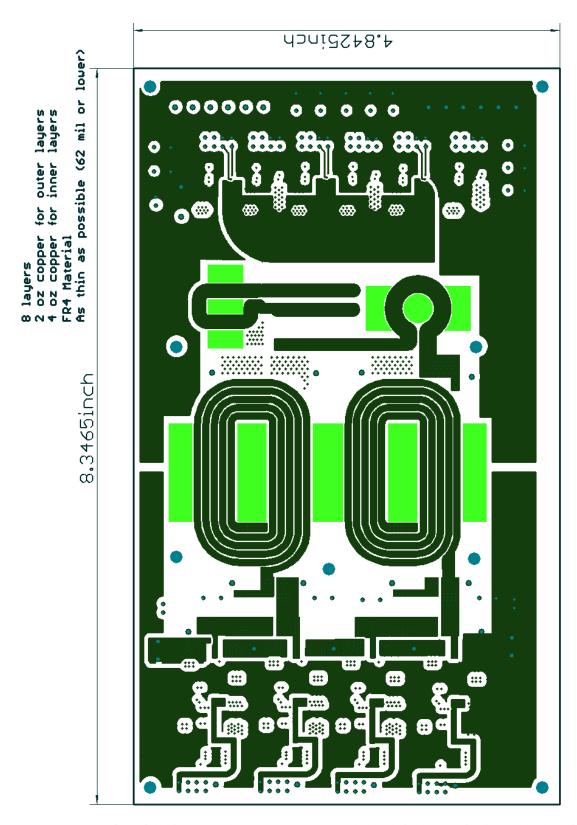

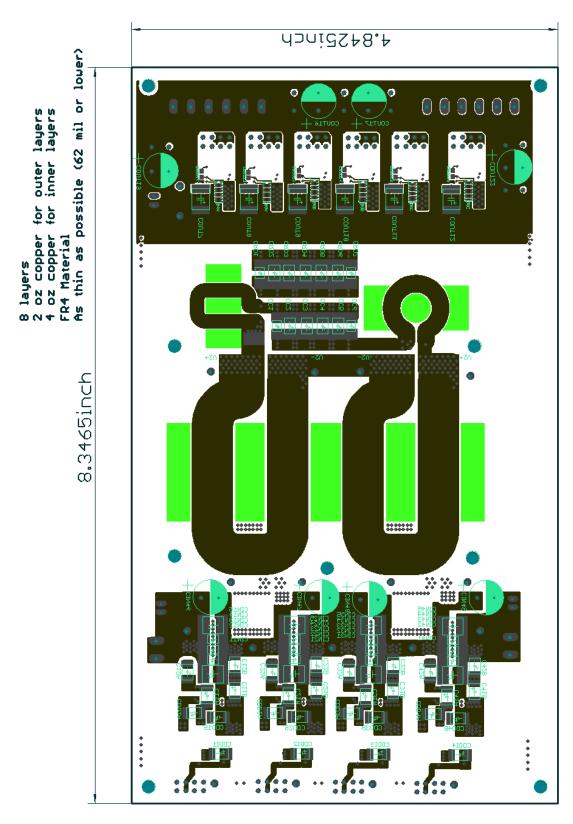

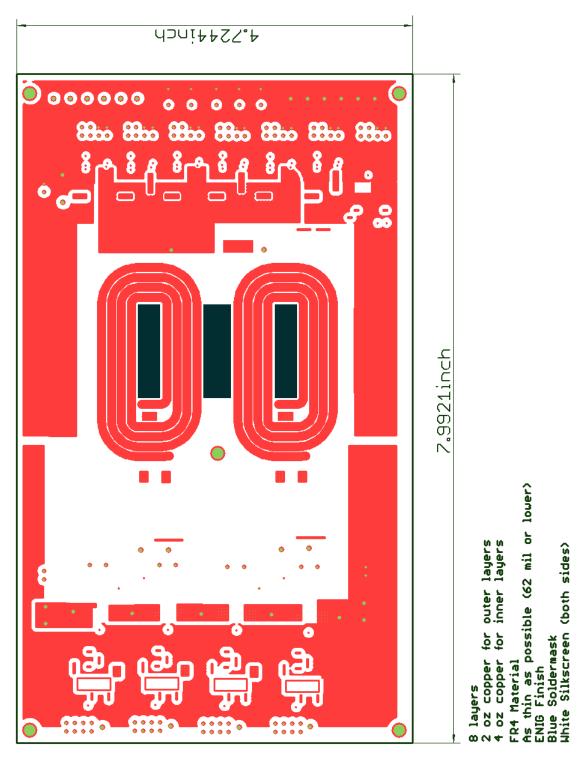

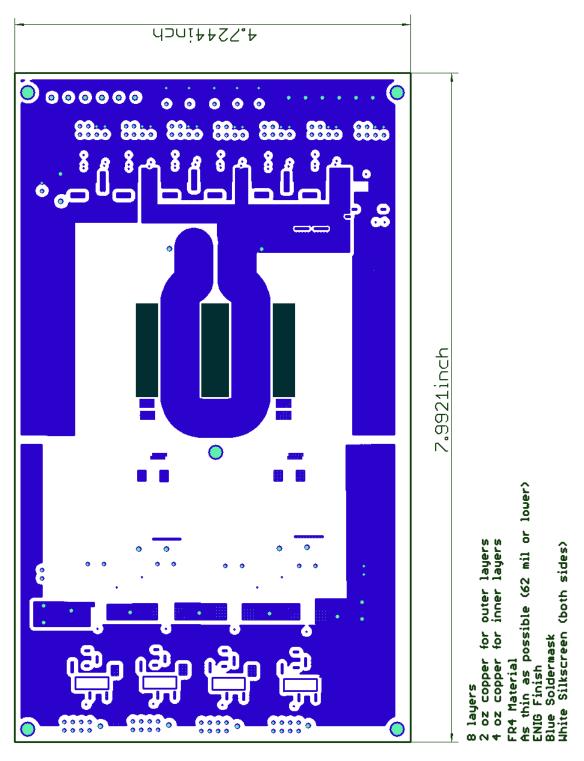

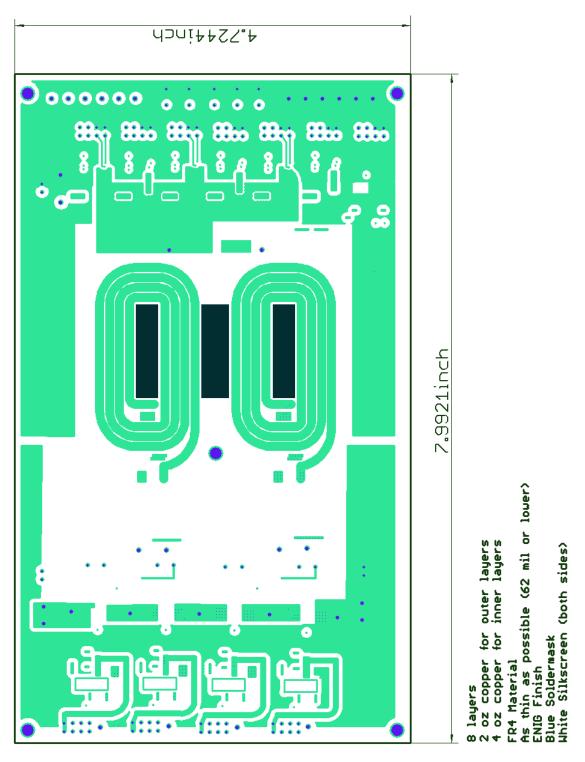

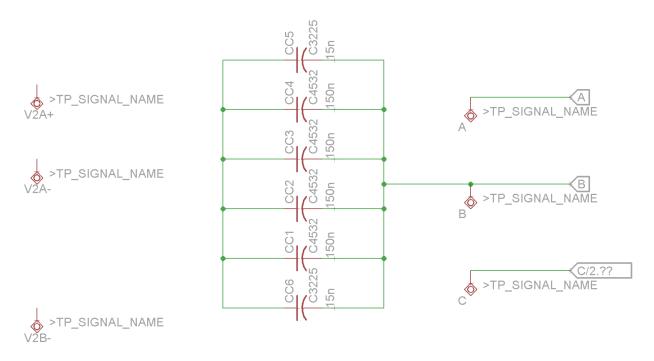

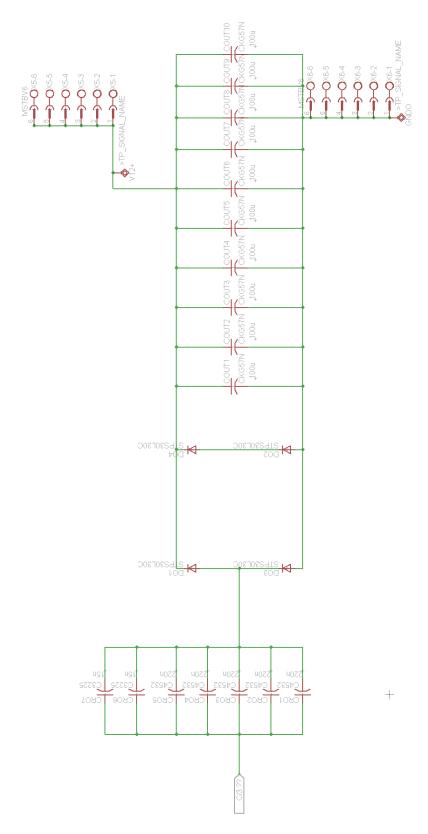

| D.1 Planar Magnetic PCB Windings                                                    | 267 |

| D.2 First Generation ICN Converter                                                  | 277 |

| D.3 Synchronous Full Bridge Rectifier for the ICN Converter                         | 282 |

| D.4 Fully Integrated ICN Converter Prototype                                        | 284 |

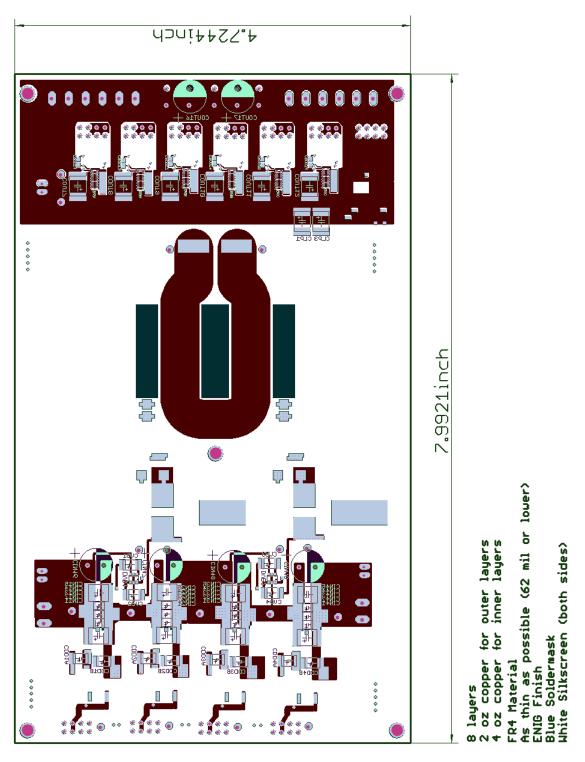

| D.5 GaN-based and Si-based Reconfigurable Double Stacked Active Bridge Prototypes . | 293 |

| Appendix E EAGLE Schematic and Bill of Materials (BOM)                              | 311 |

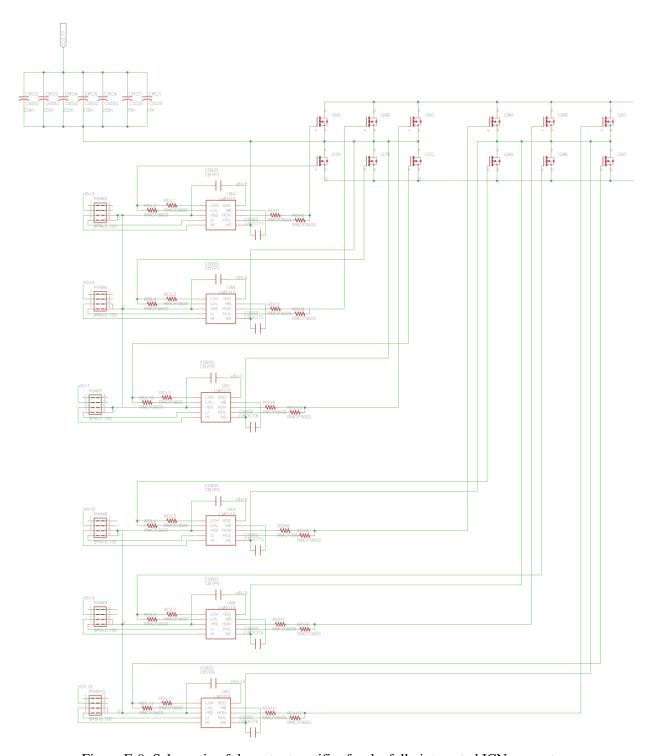

| E.1 First Generation ICN Converter                                                  | 311 |

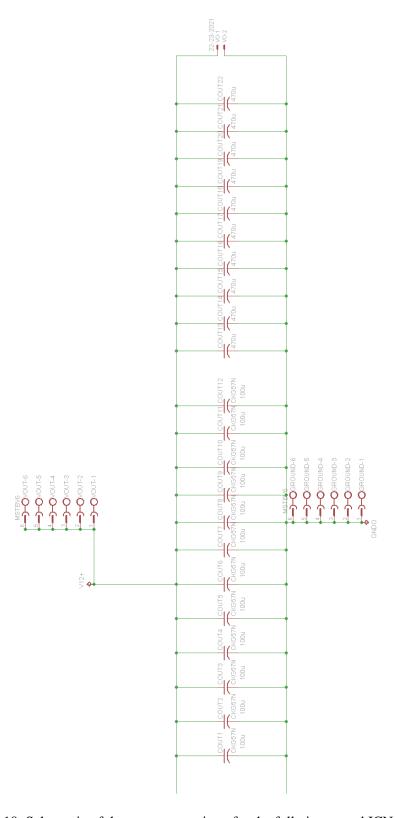

| E.2 Synchronous Rectifier for the ICN Converter                                     | 316 |

| E.3 Fully integrated ICN Converter                                                  | 317 |

| E.4 ICN Converter Bill of Materials                                                 | 323 |

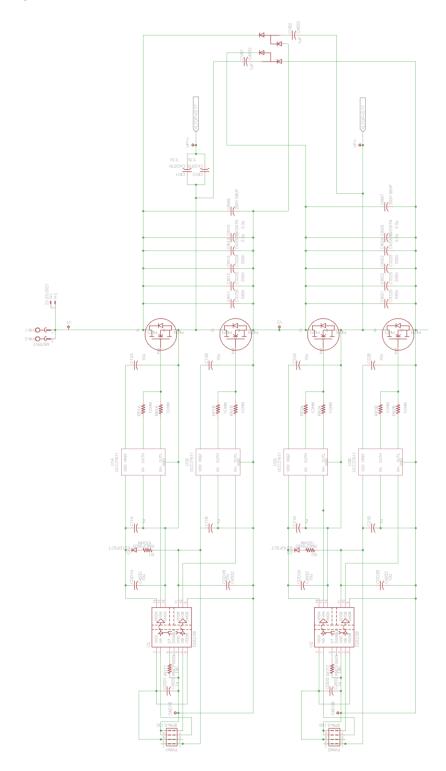

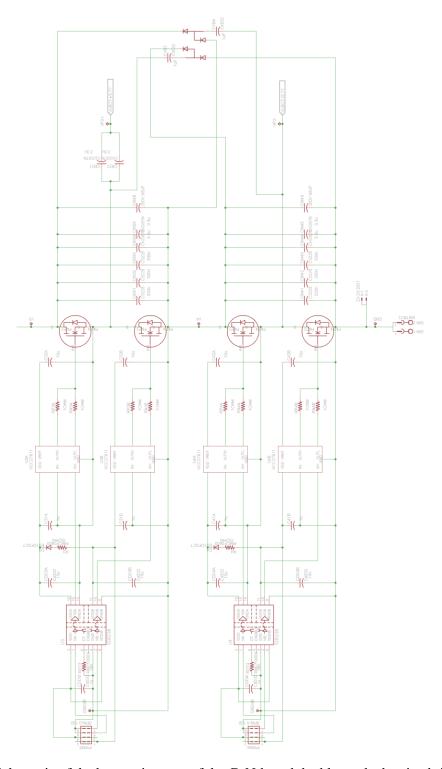

| E.5 Reconfigurable Double Stacked Active Bridge Converter                           | 324 |

| E.6 Active Bridge Converter Bill of Materials                                       | 331 |

| Appendix F Converter Operating Parameters and Data                                  | 333 |

| F.1 ICN Converter Operated in Normal Mode                                           | 334 |

| F.2 ICN Converter Operated in Burst Mode                                            | 338 |

| F.3 ICN Converter Operated in VFX Mode                                              | 342 |

| F.4 Reconfigurable Double Stacked Active Bridge Converter Operation                 | 346 |

| References                                                                          | 355 |

## **List of Figures**

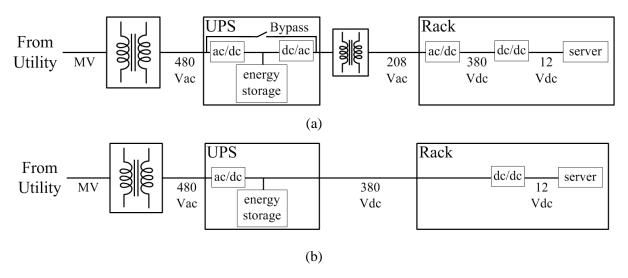

| Figure 1-1: Data center power delivery structure for (a) 208 V ac distribution and (b) 380 V dc       |    |

|-------------------------------------------------------------------------------------------------------|----|

| distribution [8,9].                                                                                   | 40 |

| Figure 1-2: (a) An ideal half-bridge supplying a constant load current and its corresponding (b)      |    |

| idealized switch voltage and current waveforms. (c) A half-bridge switch structure                    |    |

| with discrete parallel diode and capacitance representing the intrinsic body diode                    |    |

| and capacitance of a transistor supplying the same constant load current. (d) The                     |    |

| turn on and turn off switch transitions for a non-ideal half-bridge structure with                    |    |

| constant current load. Both switches can turn off with low voltage but only the                       |    |

| bottom switch can turn on at low voltage. The top switch has overlap loss as it                       |    |

| begins conducting while still sustaining the full input voltage, $V_{\text{in}}$ , plus the bottom    |    |

| diode's forward voltage drop, V <sub>D</sub> . It must also dissipate the energy stored in the        |    |

| parallel capacitance as indicated by the large spike in current.                                      | 43 |

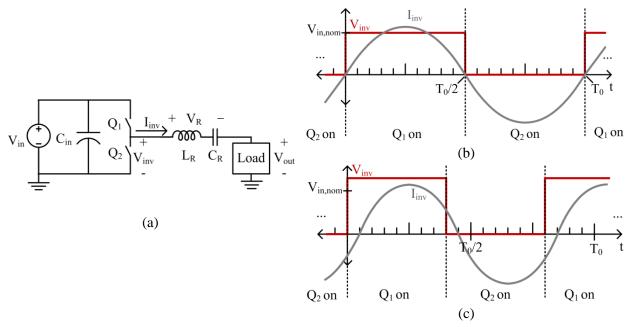

| Figure 1-3: (a) An ideal half-bridge supplying a load through a series resonant tank comprising       |    |

| inductor L <sub>R</sub> and capacitor C <sub>R</sub> . (b) Idealized inverter square wave voltage and |    |

| sinusoidal current waveforms when the input voltage, $V_{\text{in}}$ , is equal to the nominal        |    |

| input voltage. (c) Idealized inverter square wave voltage and sinusoidal current                      |    |

| waveforms when the input voltage, $V_{\text{in}}$ , is more than the nominal input voltage and        |    |

| the frequency has been increased so that the voltage across the resonant tank, V <sub>R</sub> ,       |    |

| increases to prevent the load voltage from increasing. It can be seen that the inverter               |    |

| current becomes inductive and lags the voltage.                                                       | 45 |

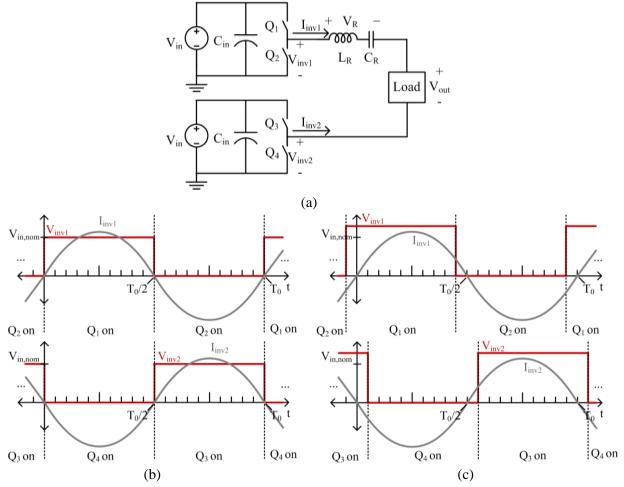

| Figure 1-4: (a) Two ideal half-bridges supplying a load through a series resonant tank comprising     |    |

| inductor L <sub>R</sub> and capacitor C <sub>R</sub> . (b) Idealized inverter square wave voltage and |    |

| sinusoidal current waveforms when the input voltage, $V_{\text{in}}$ , is equal to the nominal        |    |

| input voltage. The bottom inverter's waveforms are one half cycle delayed from the                    |    |

| top inverter's waveforms. (c) Idealized inverter square wave voltage and sinusoidal                   |    |

| current waveforms when the input voltage, $V_{\text{in}}$ , is more than the nominal input            |    |

| voltage. The bottom inverter is delayed, or phase-shifted, further from the top                       |    |

| inverter so that the average voltage across the load does not increase. Under this                    |    |

| scenario, the top inverter current lags the top inverter voltage and the bottom                       |    |

| inverter current leads the bottom inverter voltage.                                                   | 46 |

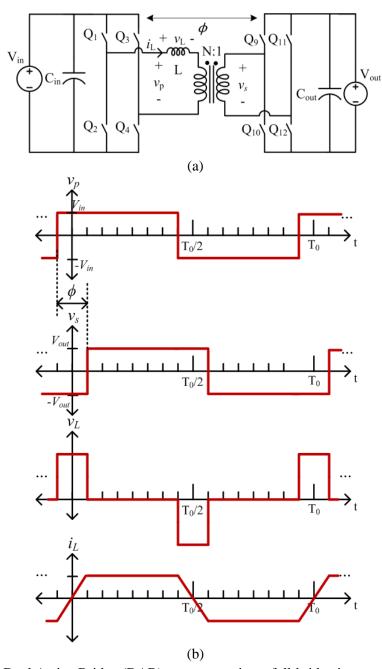

| Figure 1-5: (a) A Dual Active Bridge (DAB) converter using a full-bridge inverter and rectifier.      |    |

| Two bridges are phase-shifted from each other across a transformer with turns ratio,                  |    |

| N, and               | d an inductance, L. (b) Example operating waveforms of the DAB where the                             |    |

|----------------------|------------------------------------------------------------------------------------------------------|----|

| rectific             | er square wave voltage is phase-shifted by angle, $\phi$ , after the inverter square                 |    |

| wave.                | In this illustration, the dc input voltage to dc output voltage ratio is equal to                    |    |

| the tra              | insformer turns ratio, resulting in a flattop trapezoidal current.                                   | 48 |

| Figure 1-6: (a) Exa  | ample operating waveforms of the DAB with an input voltage that is higher                            |    |

| than th              | he nominal input voltage (the voltage at which the input voltage divided by the                      |    |

| output               | t voltage is equal to the transformer turns ratio). Because the input-to-output                      |    |

| voltag               | e ratio is greater than the transformer turns ratio, the current no longer has a                     |    |

| flat to              | p. The grey dashed lines in the current plot represent the amount of current                         |    |

| necess               | sary to ensure ZVS on both the rectifier and inverter. In this example, the                          |    |

| rectific             | er loses ZVS. (b) Example operating waveforms of the DAB with an input                               |    |

| voltag               | e that is lower than the nominal input voltage so that the input-to-output                           |    |

| voltag               | e ratio is lower than the transformer turns ratio. In this example, the inverter                     |    |

| loses 2              | ZVS. (c) Example operating waveforms of the DAB operated with a low phase                            |    |

| shift fo             | or low power. In this example, both the inverter and the rectifier lose ZVS                          | 50 |

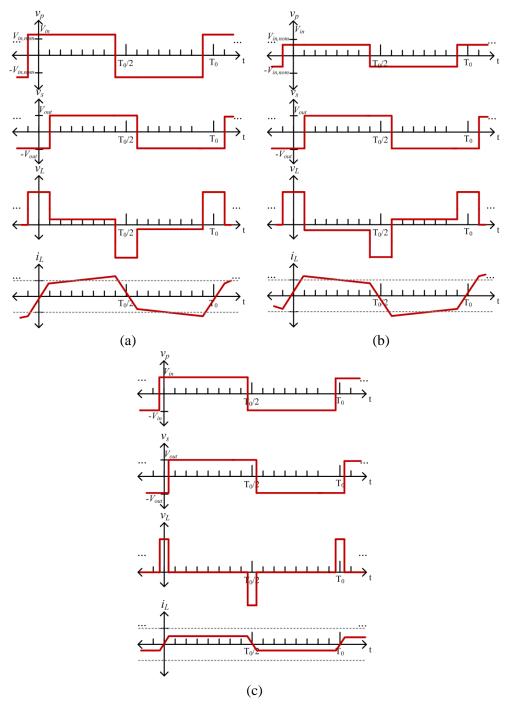

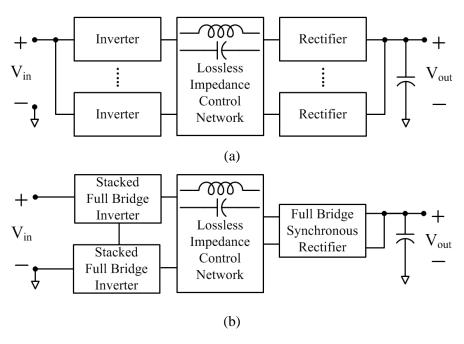

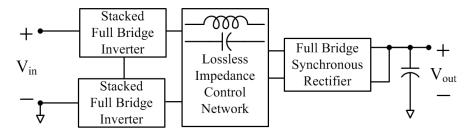

| Figure 2-1: Architec | cture of the proposed Impedance Control Network (ICN) resonant converter in                          |    |

| its (a)              | most general form, and (b) as pursued here. A plurality of phase-shifted                             |    |

| inverte              | ers and one or more rectifiers interact through a lossless impedance control                         |    |

| netwo                | rk that ensures desirable operating points for the inverter and rectifier blocks                     | 53 |

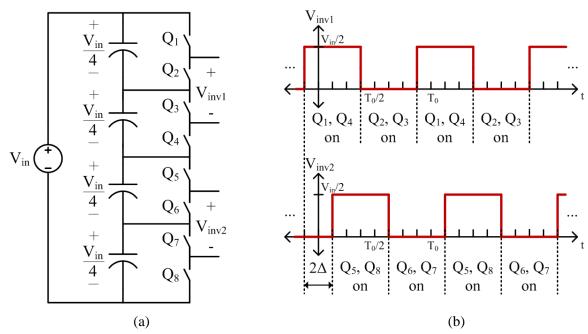

| Figure 2-2: (a) A    | double stacked-bridge inverter. The input voltage $V_{\text{in}}$ is split into four                 |    |

| (nomin               | nally equal) values with voltage balance maintained passively or through                             |    |

| active               | control. The two stacked full bridge inverters deliver output voltages                               |    |

| design               | nated as $V_{inv1}$ and $V_{inv2}$ for the top and bottom inverter, respectively. (b)                |    |

| Opera                | ting switch waveforms to generate symmetric square waves for $V_{\text{inv}1}$ and $V_{\text{inv}2}$ |    |

| with p               | period $T_0$ and an example phase shift of $2\Delta$ between inverters. The switch                   |    |

| dead-t               | imes provided to enable ZVS and avoid shoot-through are not illustrated for                          |    |

| simpli               | city.                                                                                                | 54 |

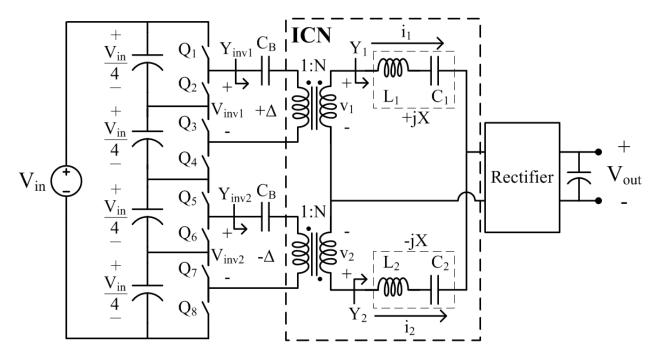

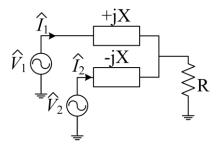

| Figure 2-3: An ICN   | resonant converter comprising a pair of stacked bridges that are also stacked.                       |    |

| The to               | op inverter is phase-shifted by $2\Delta$ ahead of the bottom inverter. The two series               |    |

| LC bra               | anches, $L_1C_1$ and $L_2C_2$ , are selected to have equal and opposite reactances (i.e.,            |    |

| +jX ar               | nd -jX) at the switching frequency.                                                                  | 56 |

| Figure 2-4: Simplif  | fied representation of the lossless ICN structure coupled with an equivalent                         |    |

| resisti              | ve load                                                                                              | 57 |

| Figure 2-5: S | Superposition analysis of the ICN structure of Figure 2-4. By suppressing (a) $V_2$ and                         |      |

|---------------|-----------------------------------------------------------------------------------------------------------------|------|

|               | (b) V <sub>1</sub> independently, we can easily analyze the current flowing through each                        |      |

|               | reactive component from (c) $V_1$ and (d) $V_2$ for a given set of reactance, $X$ , and                         |      |

|               | resistance, R.                                                                                                  | . 57 |

| Figure 2-6:   | Superposition of currents and voltages in the ICN. With a specific phase shift                                  |      |

|               | between source voltages, the source currents can be in phase with the voltages,                                 |      |

|               | thereby providing resistive loading and improved efficiency.                                                    | . 58 |

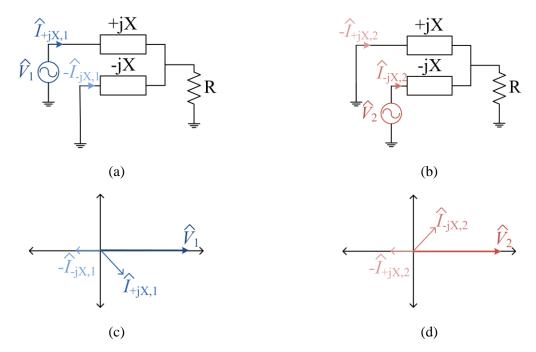

| Figure 2-7:   | Effective conductance and susceptance from (2.19) seen by the two inverters in                                  |      |

|               | Figure 2-3 (at ports defined by $V_{\text{inv1}}$ and $V_{\text{inv2}}$ ) as a function of their relative phase |      |

|               | shift for example low, medium, and high dc input voltage values: 260V, 335V and                                 |      |

|               | 410V. For these plots, $V_{\text{out}}$ is 12V, $N$ is 0.1, and X is 0.2639 $\Omega$ . Both inverters see       |      |

|               | the same conductance, but one sees the negative of the susceptance shown above                                  | . 60 |

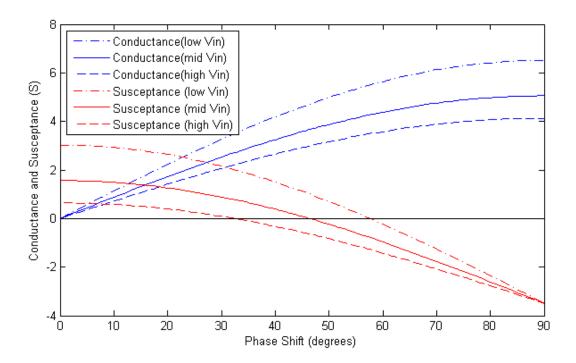

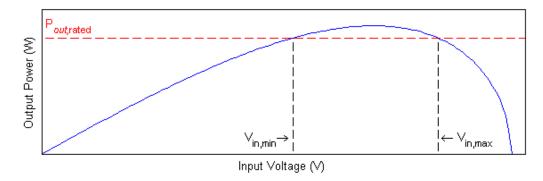

| Figure 2-8:   | The output power of (2.21) as a function of input voltage for the topology                                      |      |

|               | implementation of Figure 2-3. For these plots, $V_{\rm in}$ ranges from 0 V to 500 V, $V_{\rm out}$ is          |      |

|               | 12V, N is 0.1, and X is $0.2639\Omega$ . In order to minimize variance in output power                          |      |

|               | across the input voltage range while guaranteeing a specified power capability, the                             |      |

|               | rated output power should be achieved at the minimum and maximum input voltages                                 |      |

|               | as illustrated by the dashed lines                                                                              | 61   |

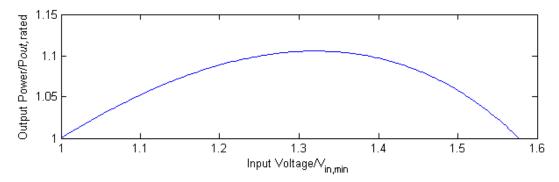

| Figure 2-9:   | Variation in output power as a function of input voltage for the ICN converter                                  |      |

|               | operated with the phase-shift between two inverters controlled to provide zero                                  |      |

|               | effective susceptance of the inverters. With the design parameters of (2.23) and                                |      |

|               | (2.24), converter power varies only minimally (~10%) over the designed output                                   |      |

|               | power, Pout, rated, of 400 W even though the input voltage increases almost 60%                                 |      |

|               | from its minimum value (i.e., $V_{in} = 260 \text{ V} - 410 \text{ V}$ at $V_{out} = 12 \text{V}$ ).            | 61   |

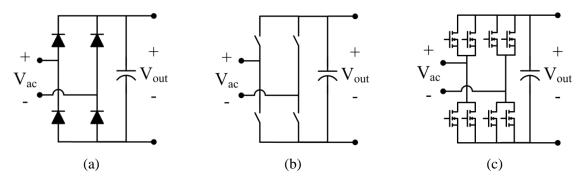

| Figure 2-10:  | Three variants of a full bridge rectifier using (a) diodes, (b) active devices, and (c)                         |      |

|               | paralleled FETs used to implement the switches.                                                                 | . 62 |

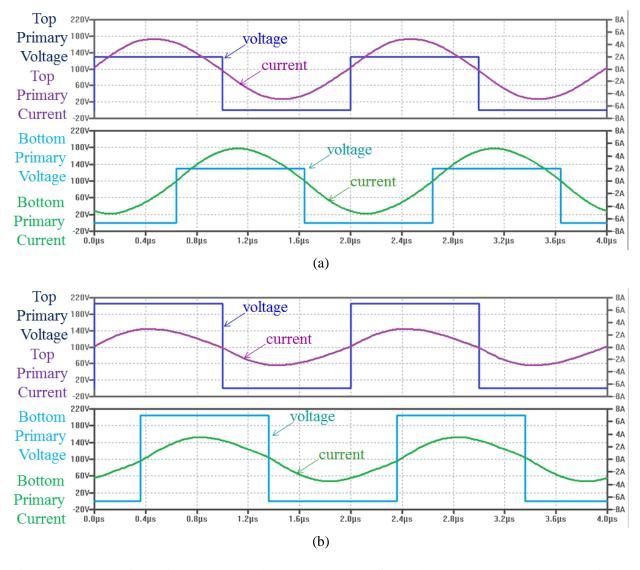

| Figure 2-11:  | Early simulation results showing ZVS and ZCS of a lossless ICN resonant converter                               |      |

|               | with an input voltage of (a) 260 V and (b) 410 V. The output voltage was 12 V, and                              |      |

|               | the output power was 400 W. For all plots, the top pane shows the primary voltage                               |      |

|               | and current for the top transformer and the bottom pane shows the primary voltage                               |      |

|               | and current for the bottom transformer. For all plots, the current is sinusoidal and                            |      |

|               | crosses zero almost simultaneously with the square wave voltage transitions.                                    | . 63 |

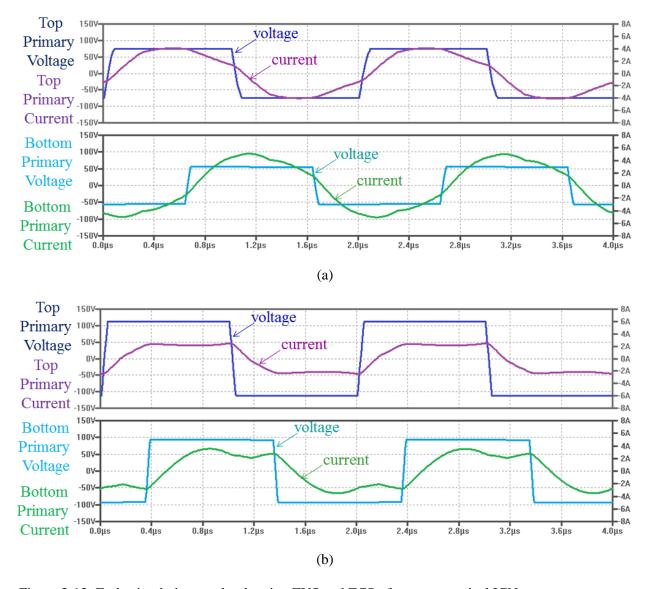

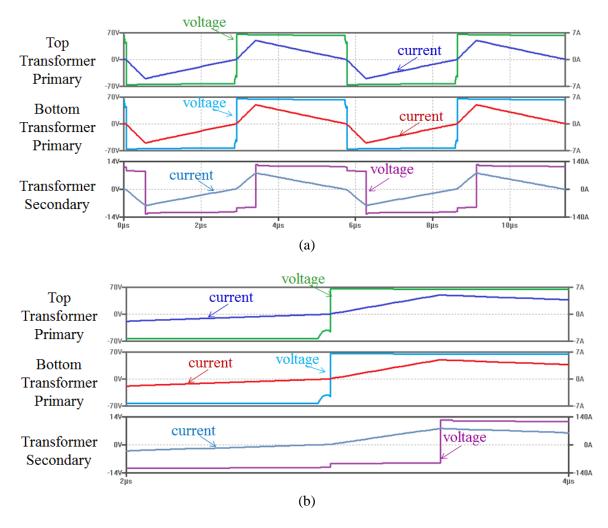

| Figure 2-12:  | Early simulation results showing ZVS and ZCS of a more practical ICN resonant                                   |      |

|               | converter with an input voltage of (a) 260 V and (b) 410 V. The output voltage was                              |      |

|              | 12 V, and the output power was 400 W. For all plots, the top pane shows the                                                  |    |

|--------------|------------------------------------------------------------------------------------------------------------------------------|----|

|              | primary voltage and current for the top transformer and the bottom pane shows the                                            |    |

|              | primary voltage and current for the bottom transformer.                                                                      | 64 |

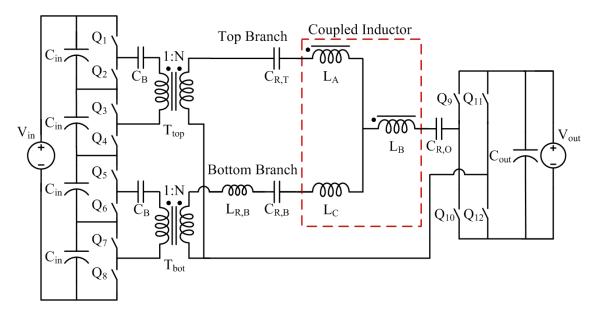

| Figure 2-13  | : Proposed implementation of the ICN converter. The ICN incorporates harmonic                                                |    |

|              | filtering through the use of resonant tanks as well as two equal but opposite                                                |    |

|              | impedances. This structure contains four magnetic structures - two transformers, a                                           |    |

|              | coupled inductor (indicated by the red-dashed box), and a resonant inductor                                                  | 65 |

| Figure 2-14: | Front View of the ICN Controller.                                                                                            | 67 |

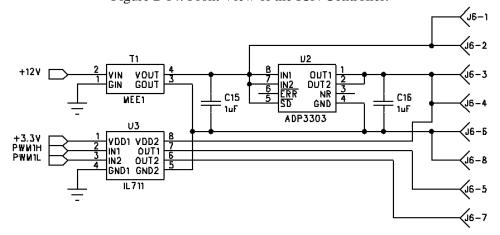

| Figure 2-15: | : Schematic showing the isolation and power circuitry for one half-bridge channel                                            |    |

|              | [51]. In this particular schematic, isolated gate drive power is supplied by a muRata                                        |    |

|              | MEE1 Series 1W isolated DC/DC converter that delivers an unregulated 9 V to the                                              |    |

|              | main converter board. That 9 V is also regulated to 5 V using an Analog Devices                                              |    |

|              | ADP3303 low dropout linear regulator, which is delivered to the main board. To                                               |    |

|              | provide isolation, the gate drive signals are routed through a NVE Corporations                                              |    |

|              | IL711 two-channel digital isolator before going to the main converter board.                                                 | 67 |

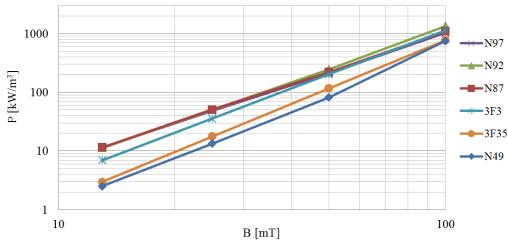

| Figure 2-16: | : Magnetic core loss per volume as a function of magnetic flux density for several                                           |    |

|              | materials operated at 500 kHz and assuming a temperature of 100 °C [57,58,59]                                                | 69 |

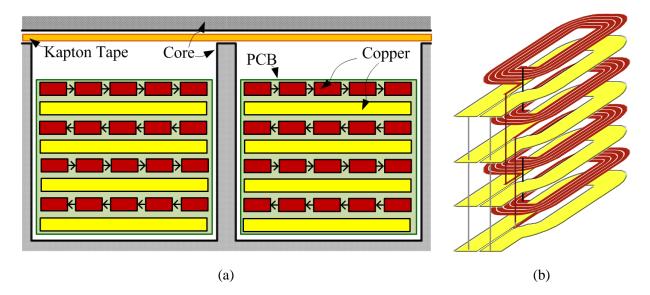

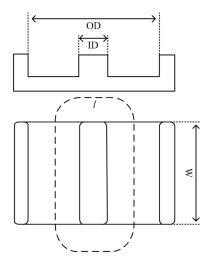

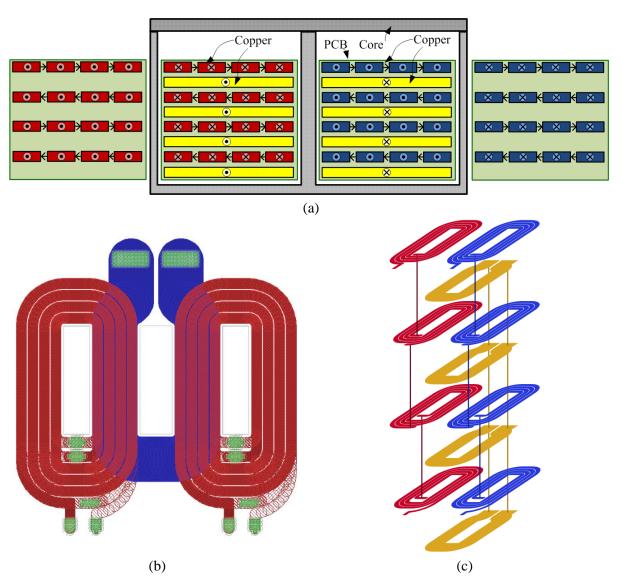

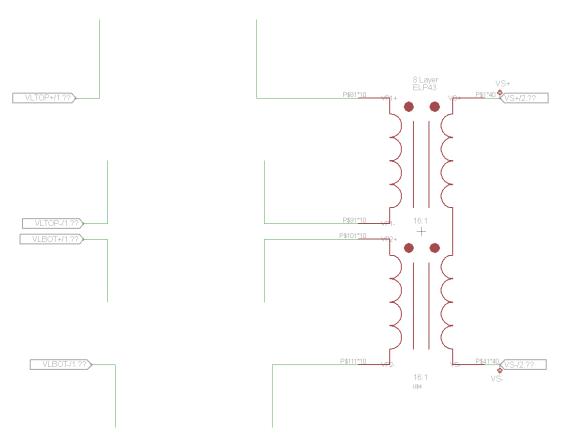

| Figure 2-17: | PCB winding structure for the transformer showing both (a) a cross sectional view                                            |    |

|              | and (b) a 3D view. The 3D view shows the interconnection between the layers. The                                             |    |

|              | 1st and 3rd layer form one series connected primary winding and the 5th and 7th layer                                        |    |

|              | form a second series connected winding. Both primary windings are then connected                                             |    |

|              | in parallel. All even layers comprise the secondary winding and are connected in                                             |    |

|              | parallel. (The foil secondary winding is not shown.) The core used is an EPCOS                                               |    |

|              | EILP43 using N49 material and a gap of ~0.75 mm is created using kapton tape                                                 | 71 |

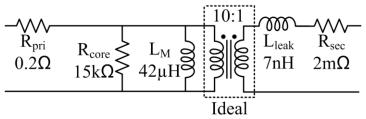

| Figure 2-18: | Transformer circuit model used in simulation. In this model, $R_{\text{pri}}$ , $R_{\text{sec}}$ , and $L_{\text{leak}}$ are |    |

|              | parasitic elements. $L_{\text{M}}$ is the magnetizing inductance that was specifically chosen                                |    |

|              | and $R_{\text{core}}$ is a means of incorporating the core loss. It should be noted that these are                           |    |

|              | approximate values and may vary for the actual experimental setup.                                                           | 72 |

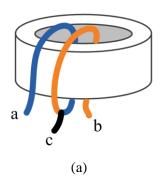

| Figure 2-19: | Coupled inductor (a) example implementation and (b) equivalent circuit model. This                                           |    |

|              | implementation uses a toroidal magnetic core and each inductor is composed of only                                           |    |

|              | one turn. This model is referred to as the "T" model [64,65]. Inductors $L_A$ , $L_B$ and $L_C$                              |    |

|              | are the apparent inductors of the T model of the coupled magnetic winding                                                    | 73 |

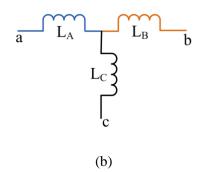

| Figure 2-20: | Coupled inductor loss as the layer stack varies for an input voltage of (a) 260 V and                                        |    |

|              | (b) 410 V. The primary winding carries the current that goes through the top branch                                          |    |

|              | of Figure 2-13 and the secondary winding carries the current that goes to the output          |      |

|--------------|-----------------------------------------------------------------------------------------------|------|

|              | rectifier. The top layer is closest to the gap.                                               | .75  |

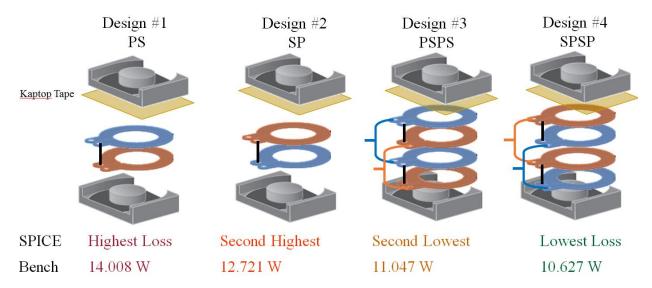

| Figure 2-21  | : Coupled inductor design variants that were experimentally tested in the ICN                 |      |

|              | converter to determine the optimal design. This was used to compare against the               |      |

|              | results that were gathered from using M2Spice generated netlists in simulation.               |      |

|              | Shown under each design is the comparative loss that SPICE predicted and the                  |      |

|              | actual loss of the circuit when running the converter with an input voltage of 100 V,         |      |

|              | output voltage of 5 V, and output current of 10 A                                             | .76  |

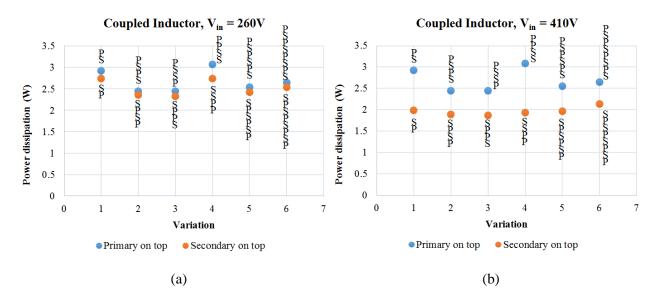

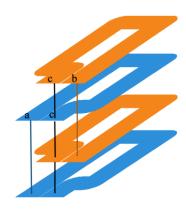

| Figure 2-22: | : Winding structure for the coupled inductor. Ports a, b, and c correspond to those           |      |

|              | shown in Figure 2-19. A detailed PCB layout is shown in Appendix D.                           | .76  |

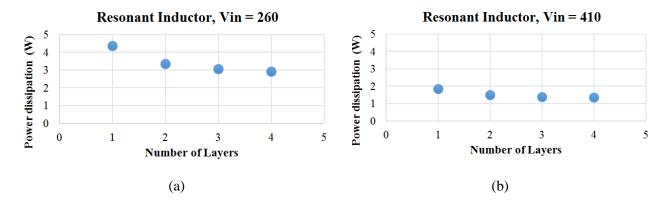

| Figure 2-23: | Resonant inductor loss as the number of layers increases for (a) 260 $V_{\rm in}$ and (b) 410 |      |

|              | V <sub>in</sub>                                                                               | .77  |

| Figure 2-24: | Winding structure for the resonant inductor. A detailed PCB layout and circuit board          |      |

|              | stackup for the windings is shown in Appendix D.                                              | .77  |

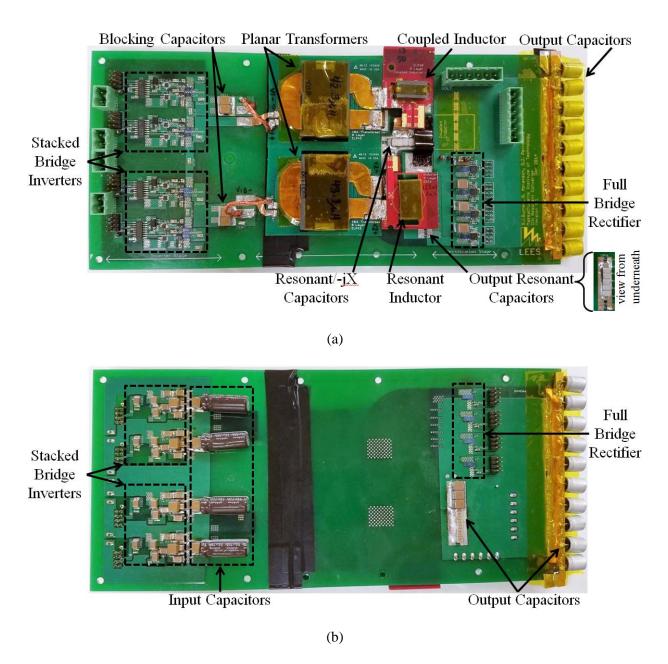

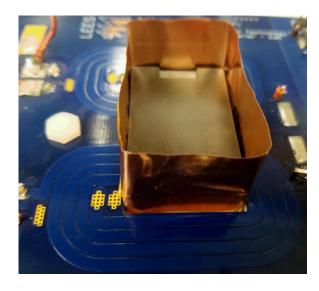

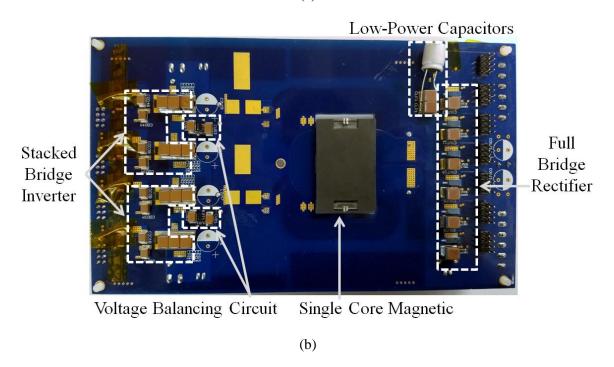

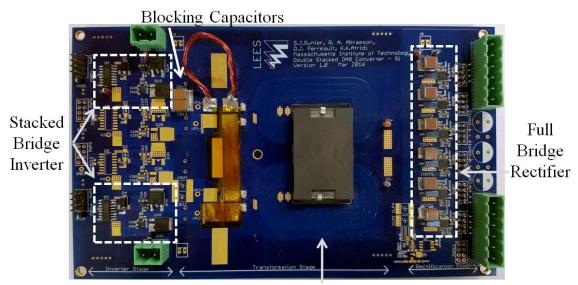

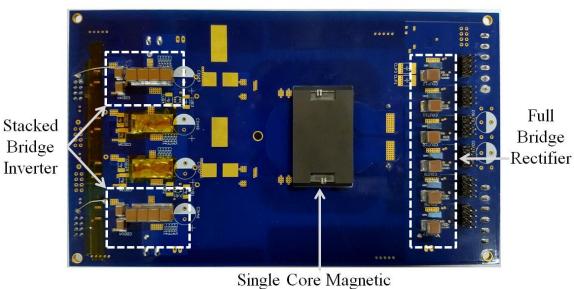

| Figure 2-25: | Populated ICN resonant converter showing both (a) top and (b) bottom views                    | .78  |

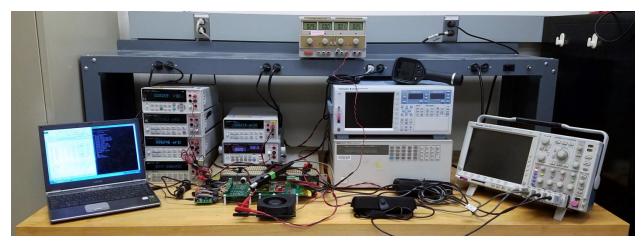

| Figure 2-26: | Experimental test setup for running the proposed ICN resonant converter. Several              |      |

|              | meters are used to measure various parameters such as dc input voltage, dc input              |      |

|              | current, dc output voltage, dc output current, gate drive voltage, gate drive current,        |      |

|              | and transformer voltage and current waveforms. A comprehensive list of equipment              |      |

|              | used is found in Table 2-5.                                                                   | . 79 |

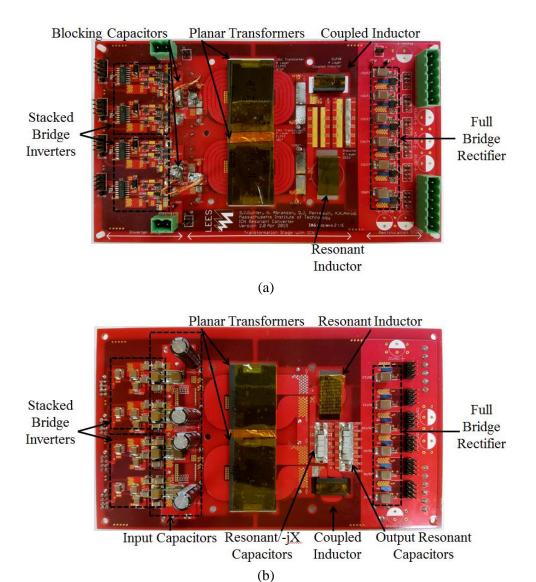

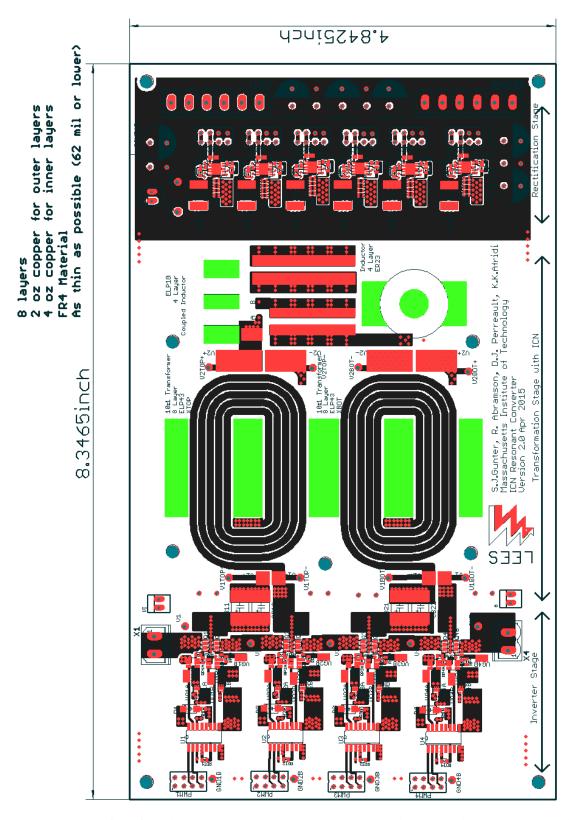

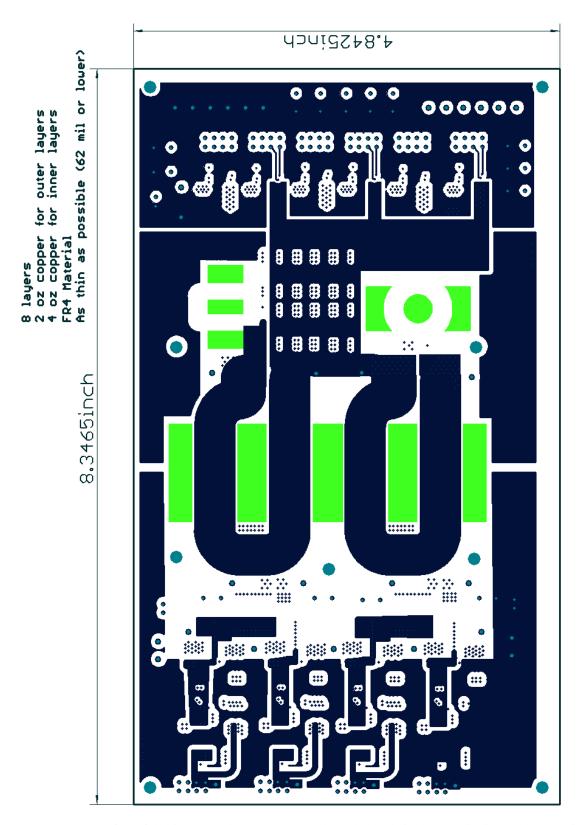

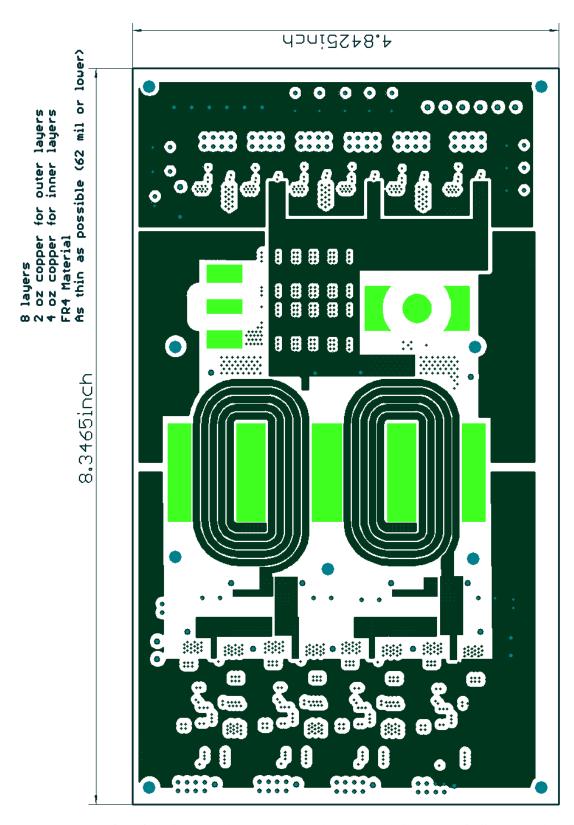

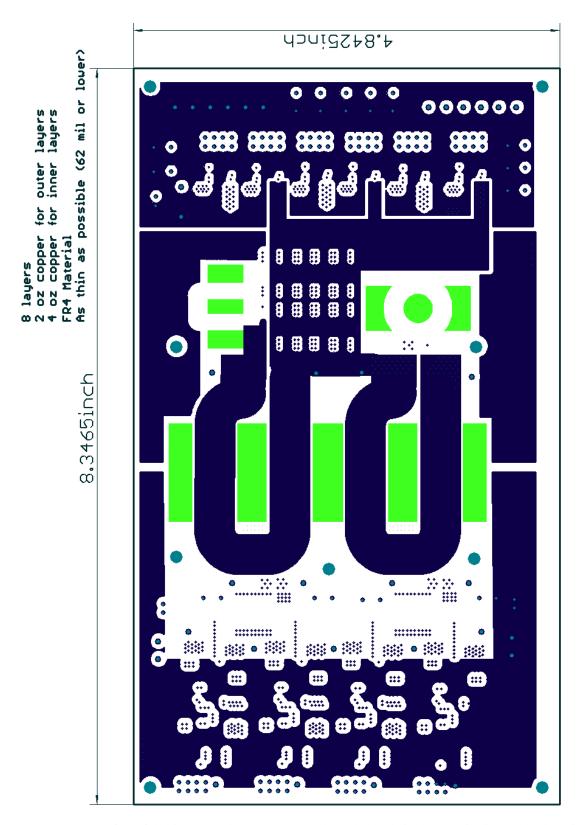

| Figure 2-27: | Populated fully integrated converter showing both (a) top and (b) bottom views                | . 81 |

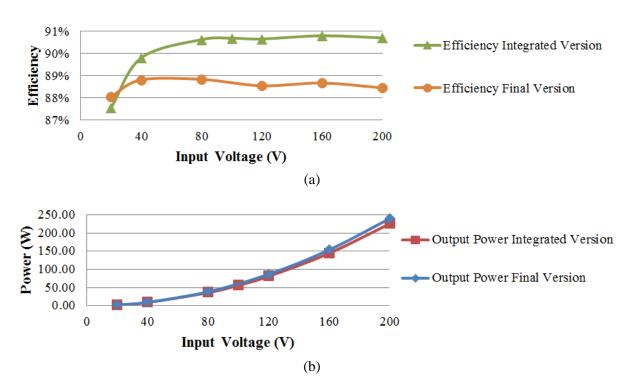

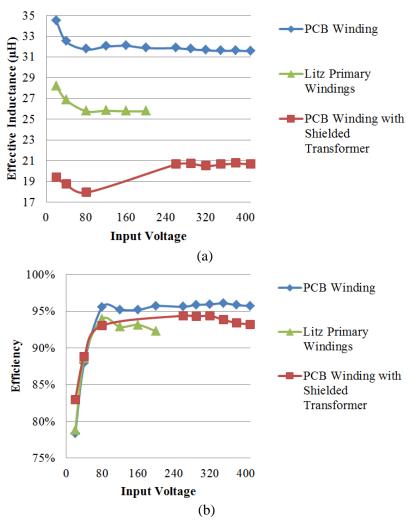

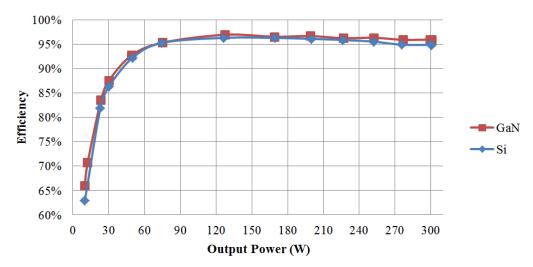

| Figure 2-28: | : Efficiency comparison between the fully integrated board of Figure 2-27 and the             |      |

|              | final version of the prototype that is not fully integrated. Across the same input            |      |

|              | voltage range, the power delivered by both converters was comparable but the                  |      |

|              | efficiency was higher for the fully integrated version showing promise in developing          |      |

|              | a more refined ICN resonant converter prototype.                                              | . 82 |

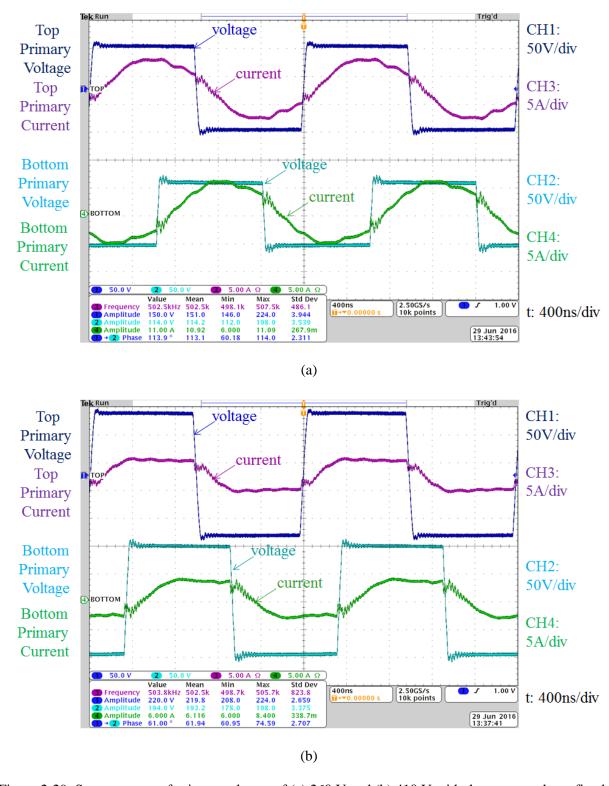

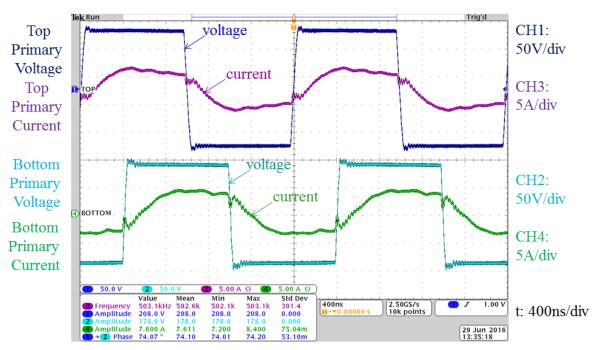

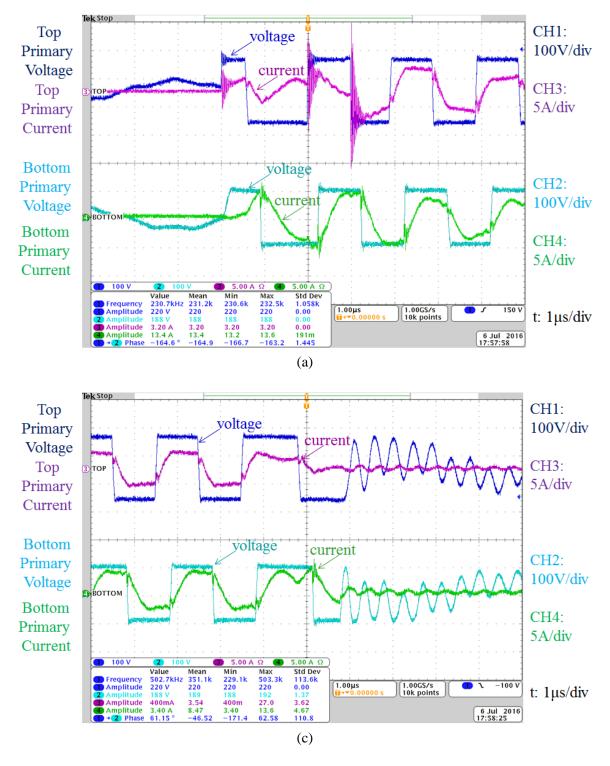

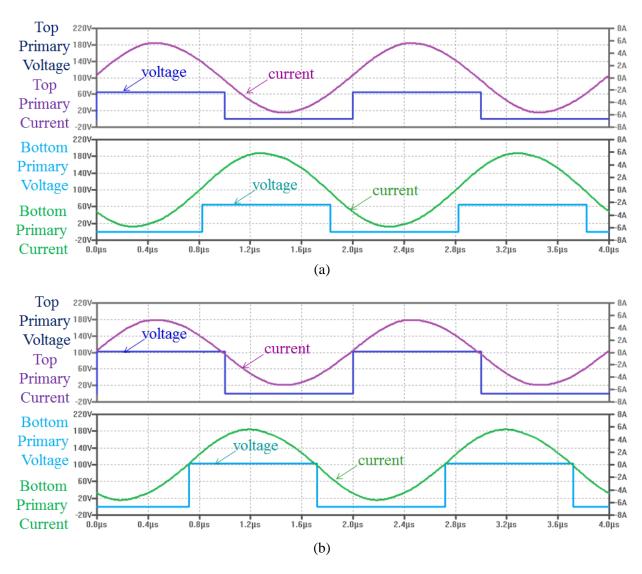

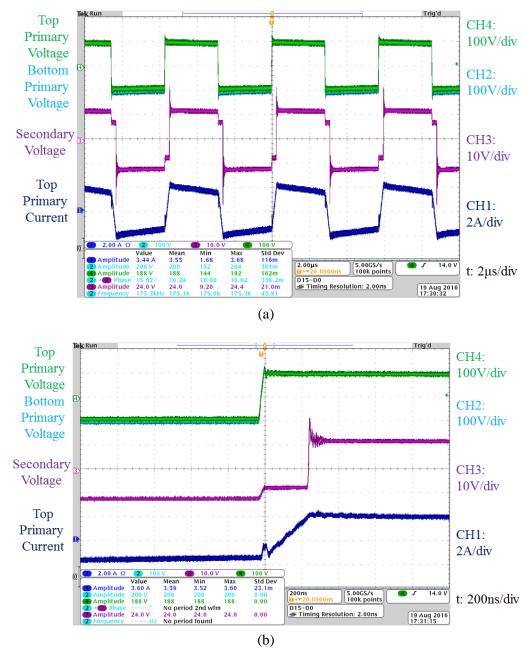

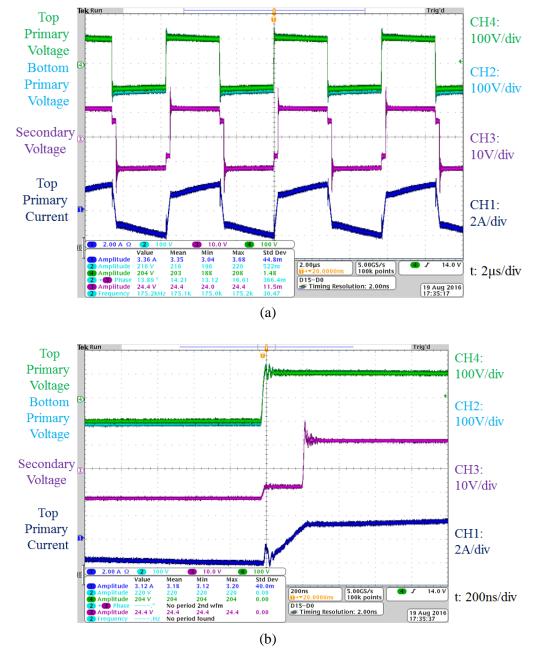

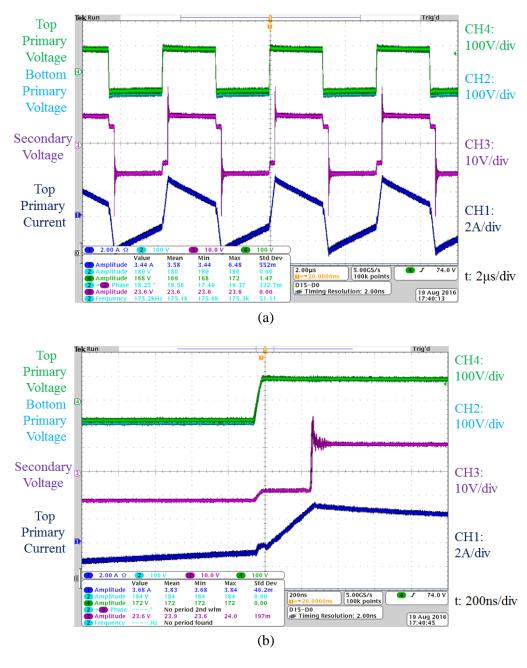

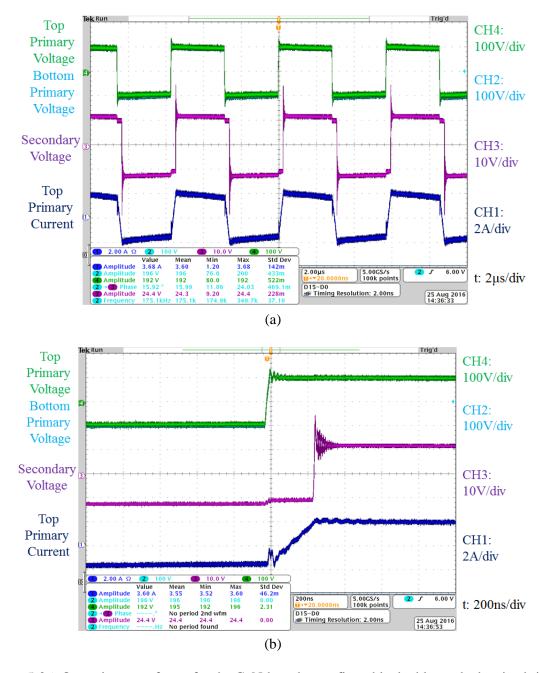

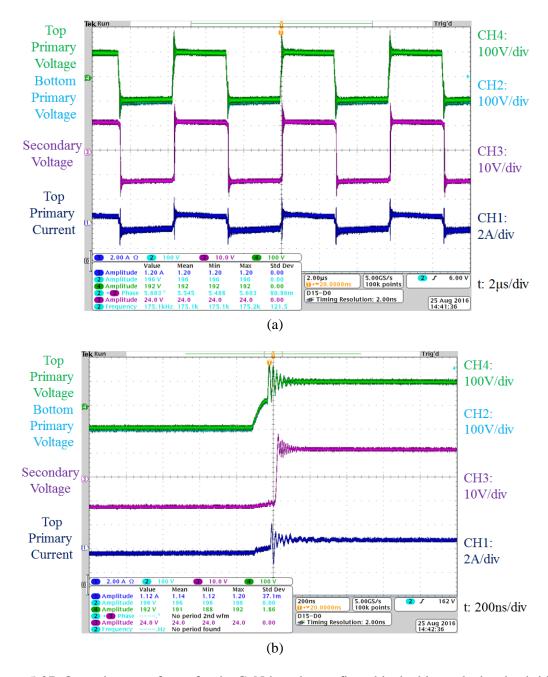

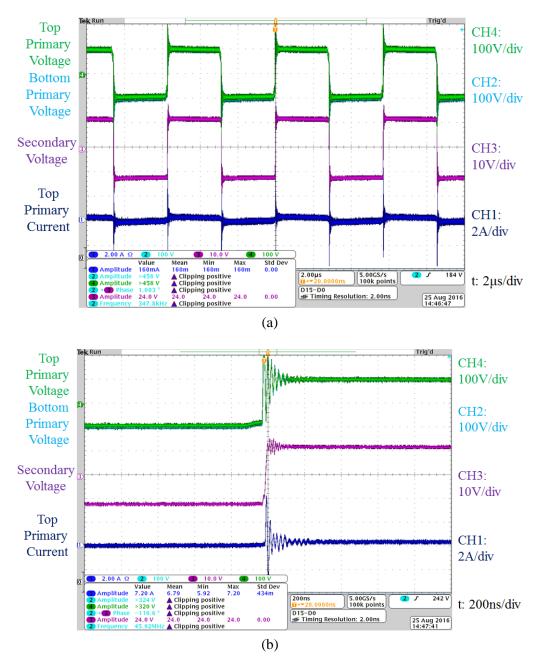

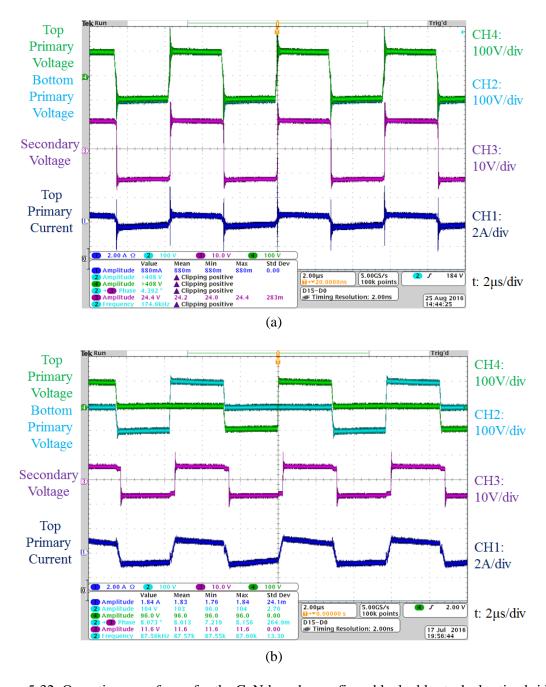

| Figure 2-29: | Scope captures for input voltages of (a) 260 V and (b) 410 V with the output voltage          |      |

|              | fixed at 12 V by an electronic load. The top set of waveforms shows the voltage               |      |

|              | across the primary of the top transformer and the current into the primary. The               |      |

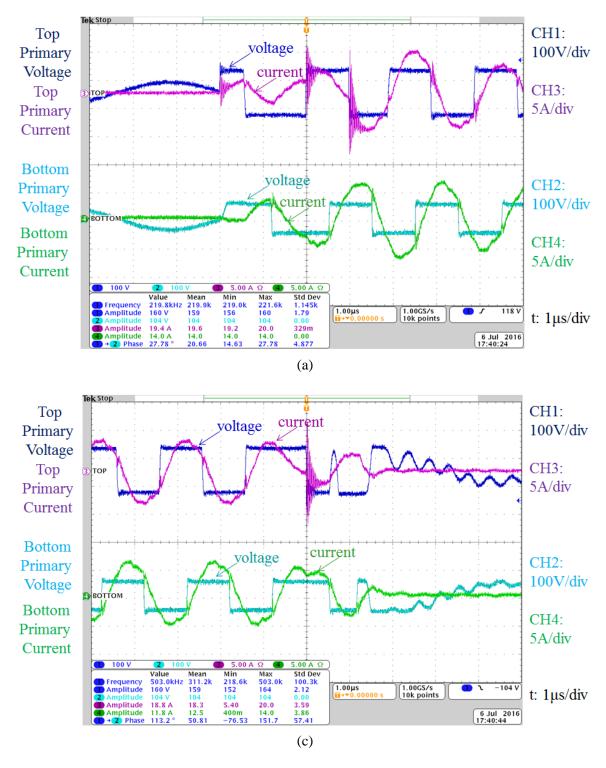

|              | second set shows the voltage across the primary of the bottom transformer and the             |      |

|              | current into the primary.                                                                     | . 83 |

| Figure 2-30: | Scope captures for the nominal input voltage of 380 V with the output voltage fixed           |      |

|              | at 12 V by an electronic load. The top set of waveforms shows the voltage across              |      |

|              | the primary of the top transformer and the current into the primary. The second set           |      |

|              | shows the voltage across the primary of the bottom transformer and the current into the primary | 84  |

|--------------|-------------------------------------------------------------------------------------------------|-----|

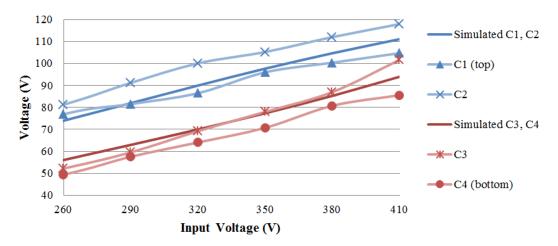

| Figure 2-31. | Voltage across the input capacitors based on simulation and experimental data. The              | 0 1 |

| rigure 2-31. | four input capacitors are stacked across the input voltage with C1 on top above C2              |     |

|              |                                                                                                 |     |

|              | which is above C3 which is above C4. In simulation, C1 and C2 have the same                     |     |

|              | voltage across them and C3 and C4 have the same voltage. In practice, there is                  | 0.5 |

| E: 2.22      | some variance between the voltages.                                                             | 85  |

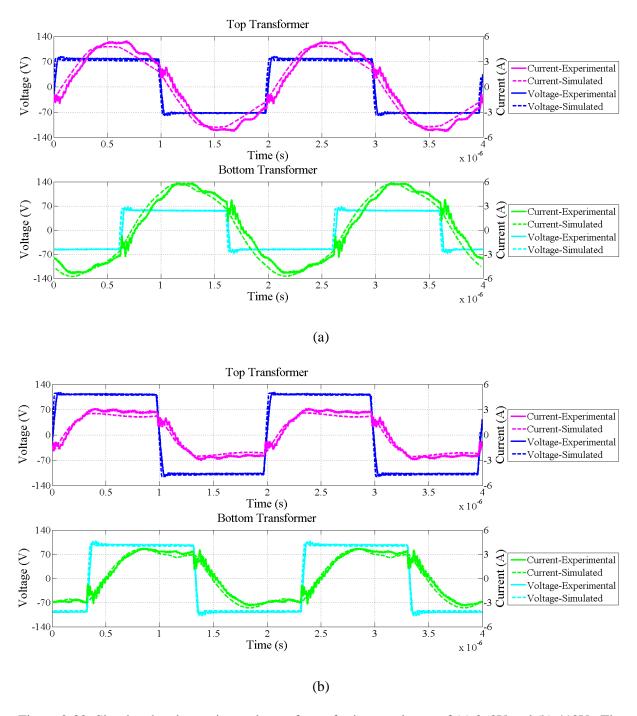

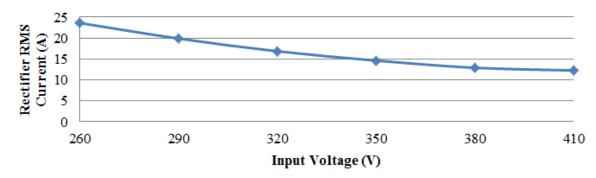

| Figure 2-32: | Simulated and experimental waveforms for input voltages of (a) 260V and (b) 410V.               |     |

|              | The top pane of each set of waveforms shows the voltage across the primary of the               |     |

|              | top transformer and the current into the primary. The second pane shows the                     |     |

|              | voltage across the primary of the bottom transformer and the current into the                   |     |

|              | primary. For all plots, the solid line is the experimental data of Figure 2-29 and the          |     |

|              | dashed line is the simulated data                                                               | 86  |

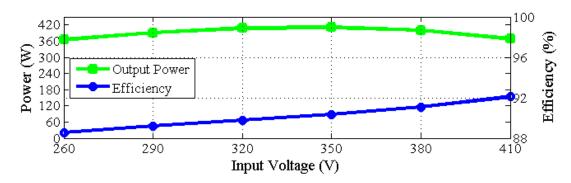

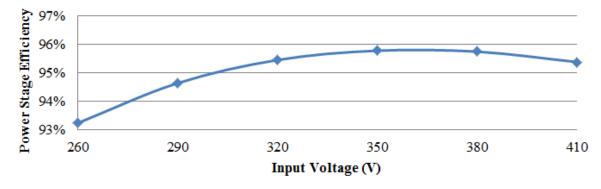

| Figure 2-33: | Experimental results for power stage output power and efficiency.                               | 87  |

| Figure 2-34: | Thermal images of the board operating at an input voltage of (a) 260 V and (b) 410              |     |

|              | V. A fan can be seen at the bottom and is intended to keep the output stage                     |     |

|              | (particularly the switching devices) from overheating.                                          | 87  |

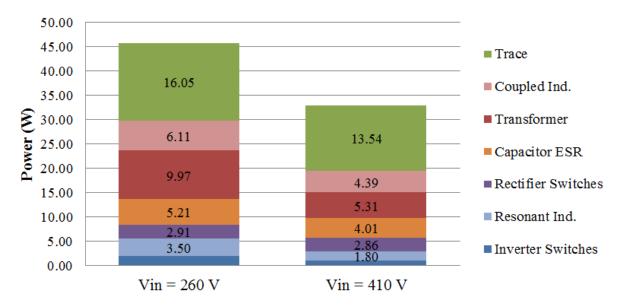

| Figure 2-35: | Simulated breakdown and comparison of loss for input voltages of 260V and 410V.                 |     |

|              | At both of these operating points, the power delivered to the output is approximately           |     |

|              | equal at around 365W.                                                                           | 88  |

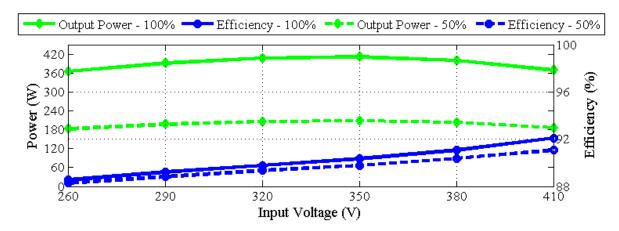

| Figure 2-36: | Experimental results for power stage output power and efficiency when operated at a             |     |

|              | 100% power and with a 50% burst duty ratio to deliver 50% power                                 | 89  |

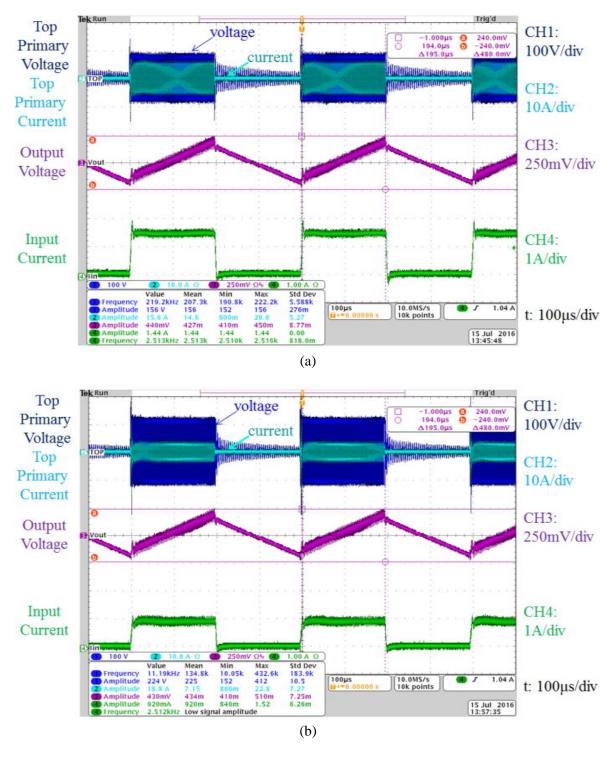

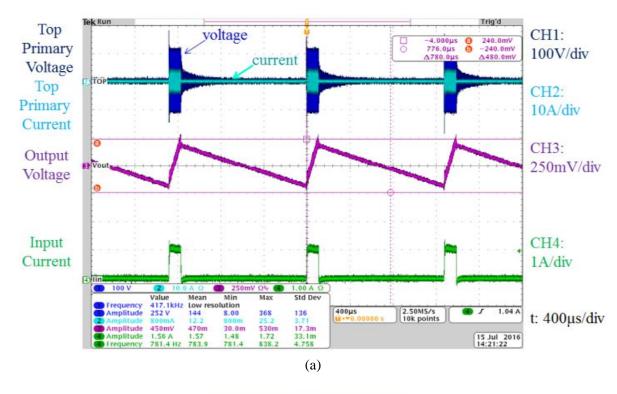

| Figure 2-37: | Converter voltages and currents when operating with a 50% burst duty cycle at a                 |     |

|              | frequency of 2.5 kHz and an input voltage of (a) 260 V and (b) 410 V. For each                  |     |

|              | screenshot, the top two waveforms are the primary voltage and current for the top               |     |

|              | transformer, the middle waveform is the ac component of the output voltage and the              |     |

|              | bottom waveform is the input current from the power supply. The horizontal cursor               |     |

|              | bars are set at +240 mV and -240 mV, which define the voltage ripple bands to stay              |     |

|              | within ±2%                                                                                      | 90  |

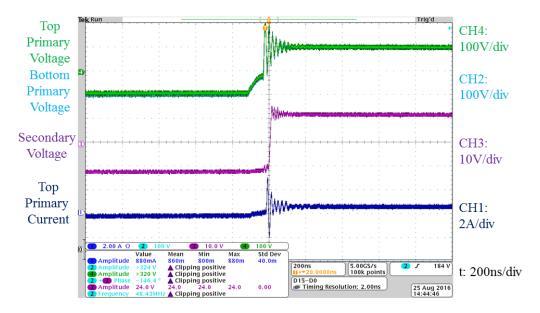

| Figure 2-38: | Transformer primary voltages and currents during (a) startup and (b) shutdown when              |     |

| C            | operating under burst mode with an input voltage of 260 V. For each screenshot, the             |     |

|              | top two waveforms are the primary voltage and current for the top transformer and               |     |

|              | the bottom two waveforms are the primary voltage and current for the bottom                     |     |

|              | transformer. It can be seen that steady state currents and soft switching are reached           |     |

|              | ransformer. It can be seen that steady state entremts and soft switching are reached            |     |

| within a couple of switching cycles and when the converter is turned off, the                                  |    |

|----------------------------------------------------------------------------------------------------------------|----|

| transformer current quickly goes to zero.                                                                      | 91 |

| Figure 2-39: Transformer primary voltages and currents during (a) startup and (b) shutdown when                |    |

| operating under burst mode with an input voltage of 410 V. For each screenshot, the                            |    |

| top two waveforms are the primary voltage and current for the top transformer and                              |    |

| the bottom two waveforms are the primary voltage and current for the bottom                                    |    |

| transformer. It can be seen that steady state currents and soft switching are reached                          |    |

| within a couple of switching cycles and when the converter is turned off, the                                  |    |

| transformer current quickly goes to zero.                                                                      | 92 |

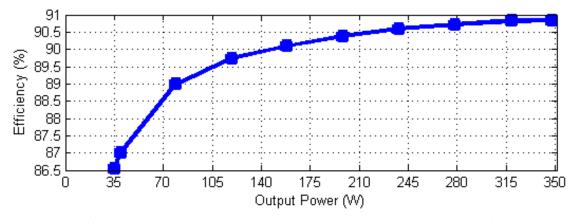

| Figure 2-40: Efficiency across output power when operated with an input voltage of 380 V and                   |    |

| using burst mode to control the power and keep the output voltage at 12 V                                      | 93 |

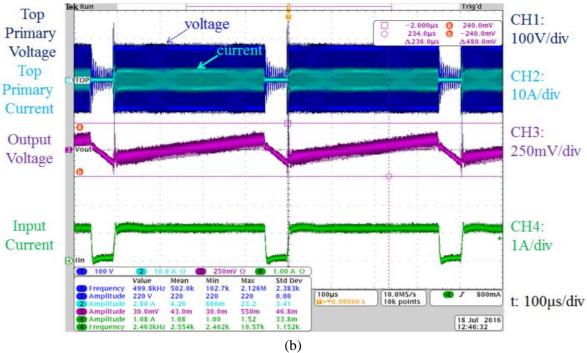

| Figure 2-41: Converter voltages and currents when operating under burst mode to deliver (a) 35                 |    |

| W and (b) 350 W at 380 $V_{\rm in}$ . For each screenshot, the top two waveforms are the                       |    |

| primary voltage and current for the top transformer, the middle waveform is the ac                             |    |

| component of the output voltage and the bottom waveform is the input current from                              |    |

| the power supply. The horizontal cursor bars are set at +240 mV and -240 mV,                                   |    |

| which define the voltage ripple bands to stay within ±2%.                                                      | 94 |

| Figure 3-1: Architecture of the proposed Impedance Control Network (ICN) resonant converter as                 |    |

| pursued here. A plurality of phase-shifted inverters and one or more rectifiers                                |    |

| interact through a lossless impedance control network that ensures desirable                                   |    |

| operating points for the inverter and rectifier blocks.                                                        | 95 |

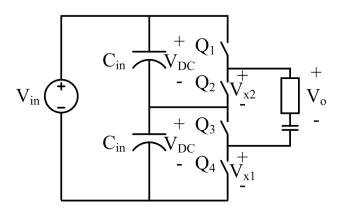

| Figure 3-2: A stacked-bridge inverter. The total bus voltage $V_{\text{in}}$ is split in two (nominally) equal |    |

| values of $V_{\text{DC}} = 0.5 \ V_{\text{in}}$ , with voltage balance maintained passively or through active  |    |

| control. The inverter output voltage is $V_{\text{out}}$ , shown across an element representing                |    |

| the input to the load network.                                                                                 | 96 |

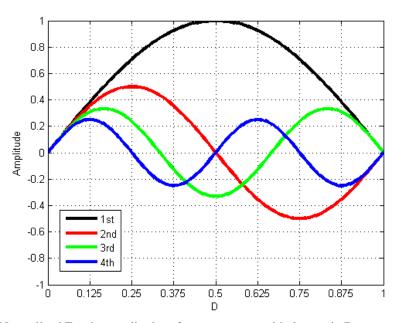

| Figure 3-3: Normalized Fourier amplitudes of a square wave with duty ratio D.                                  | 97 |

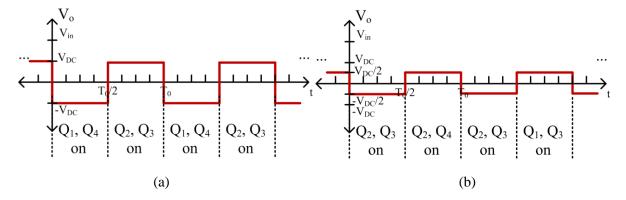

| Figure 3-4: Output voltage waveforms of the stacked-bridge inverter of Figure 3-2. (a) Operation               |    |

| in fundamental mode, where each half-bridge inverter switches $f_0 = 1/T_0$ and at a                           |    |

| 50% duty ratio. (b) Operation in VFX mode. In this case the half-bridge inverters                              |    |

| each operate at half that of the desired output frequency with one half bridge having                          |    |

| duty ratio of 25% and the second half bridge having duty ratio of 75%. The net                                 |    |

| output voltage is at the same frequency as the fundamental mode, but provides half                             |    |

| the output voltage, while the individual transistors switch at half the rate as in                             |    |

| fundamental mode                                                                                               | 97 |

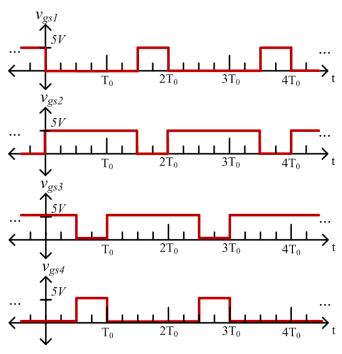

| Figure 3-5: One example implementation of the gate drive signals for the stacked inverter when                |

|---------------------------------------------------------------------------------------------------------------|

| operated in "frequency doubler" mode or "VFX" mode. In this mode, the duty cycle                              |

| of the devices is either 25% or 75% and switching period is $2T_0$                                            |

| Figure 3-6: (a) A full bridge rectifier. The voltage at the input to the rectifier, $V_{rect}$ , is shaped by |

| the active devices and depends on operating mode. (b) Operation in fundamental                                |

| mode, where each half-bridge switches at $f_0 = 1/T_0$ and at a 50% duty ratio. (c)                           |

| Operation in VFX mode. In this case the half-bridges each operate at half that of the                         |

| desired output frequency with one half-bridge having duty ratio of 25% and the                                |

| second half-bridge having duty ratio of 75%. The net rectifier voltage is at the same                         |

| frequency as the fundamental mode, but provides half the voltage amplitude, while                             |

| the individual transistors switch at half the rate as in fundamental mode99                                   |

| Figure 3-7: Proposed implementation of the ICN converter. The ICN incorporates harmonic                       |

| filtering through the use of resonant tanks as well as two equal but opposite                                 |

| impedances. This structure contains four magnetic structures - two transformers, a                            |

| coupled inductor (indicated by the red-dashed box), and a resonant inductor 100                               |

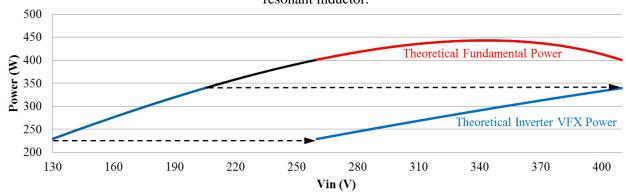

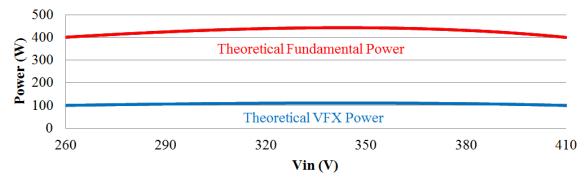

| Figure 3-8: Variation in output power as a function of input voltage for the ICN converter                    |

| operated with the phase-shift between the two inverters controlled to provide zero                            |

| effective susceptance of the inverters. Converter power varies only minimally over                            |

| the voltage range of fundamental operation (i.e., $260\ V-410\ V$ ). During VFX                               |

| mode on the inverter, the transformation stage sees half the input voltage and                                |

| therefore the additional power capabilities are also highlighted                                              |

| Figure 3-9: Variation in output power as a function of input voltage for the ICN converter                    |

| operated with the phase-shift between the two inverters controlled to provide zero                            |

| effective susceptance of the inverters. Converter power varies only minimally over                            |

| the voltage range of fundamental operation (i.e., $260\ V-410\ V$ ). During VFX                               |

| mode on both the inverter and the rectifier, the output power profile is lowered. The                         |

| additional power capability, approximately a quarter of the original, is highlighted 101                      |

| Figure 3-10: Variation in output power as a function of input voltage for the ICN converter                   |

| operated under four different modes: fundamental mode (blue curve), VFX mode                                  |

| applied to the inverters (red curve), VFX mode applied to the rectifier (purple                               |

| curve), and VFX applied to both inverters and rectifier (green curve)                                         |

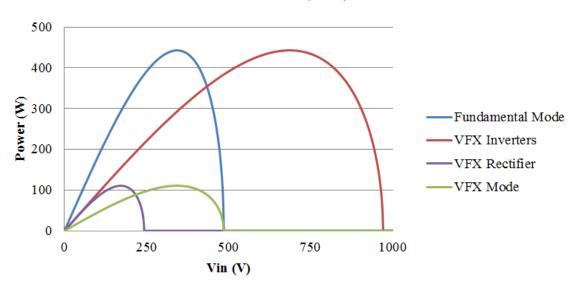

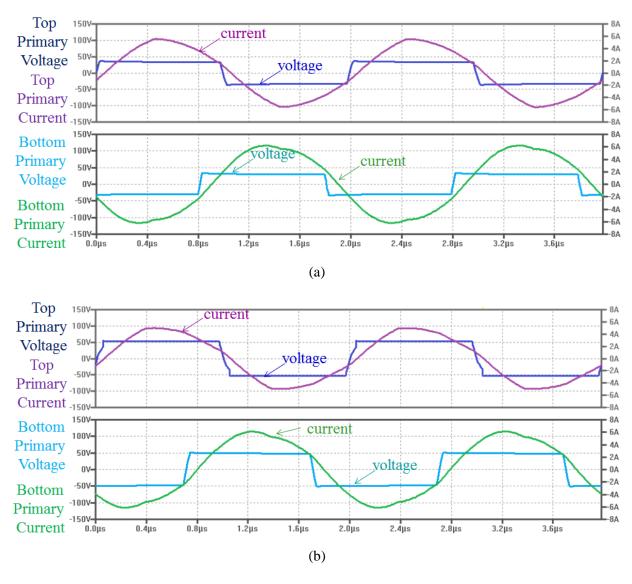

| Figure 3-11: Simulation results showing ZVS and ZCS of a lossless ICN resonant converter when                 |

| the inverters are operated in VFX mode with an input voltage of (a) 260 V and (b)                             |

| 410 V. The output voltage was 12 V, and the output power was 400 W. For all                                   |

|              | plots, the top pane shows the primary voltage and current for the top transformer             |

|--------------|-----------------------------------------------------------------------------------------------|

|              | and the bottom pane shows the primary voltage and current for the bottom                      |

|              | transformer. For all plots, the current is sinusoidal and crosses zero almost                 |

|              | simultaneously with the square wave voltage transitions                                       |

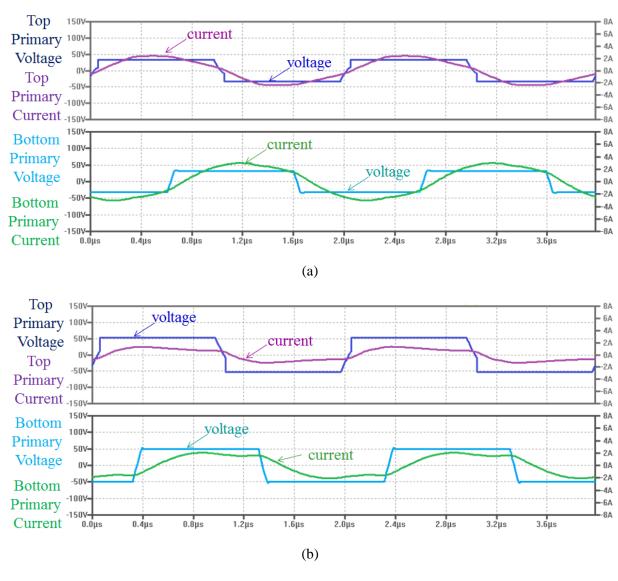

| Figure 3-12: | Simulation results comparing the operation of a lossless ICN resonant converter in            |

|              | fundamental and inverter VFX modes with an input voltage of (a) 260 V and (b) 410             |

|              | V. The output voltage was 12 V, and the output power was 400 W. For all plots, the            |

|              | top pane shows the primary voltage and current for the top transformer and the                |

|              | bottom pane shows the primary voltage and current for the bottom transformer. The             |

|              | brighter waveforms are from VFX operation while the darker waveforms are for                  |

|              | fundamental operation. 105                                                                    |

| Figure 3-13: | Simulation results of a more practical ICN resonant converter when the inverters are          |

|              | operated in VFX mode with an input voltage of (a) 260 V and (b) 410 V. The                    |

|              | output voltage was 12 V. For all plots, the top pane shows the primary voltage and            |

|              | current for the top transformer and the bottom pane shows the primary voltage and             |

|              | current for the bottom transformer                                                            |

| Figure 3-14: | : Simulation results of a more practical ICN resonant converter when both the                 |

|              | inverters and the rectifier are operated in VFX mode with an input voltage of (a) 260         |

|              | V and (b) 410 V. The output voltage was 12 V, and the output power was                        |

|              | approximately 90 W. For all plots, the top pane shows the primary voltage and                 |

|              | current for the top transformer and the bottom pane shows the primary voltage and             |

|              | current for the bottom transformer                                                            |

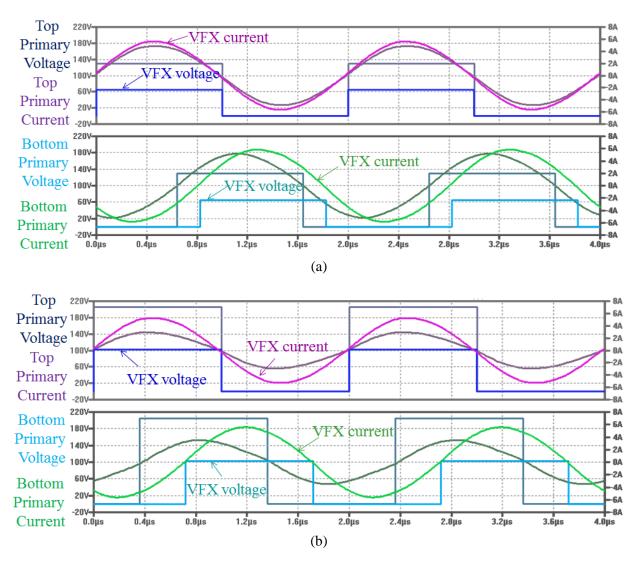

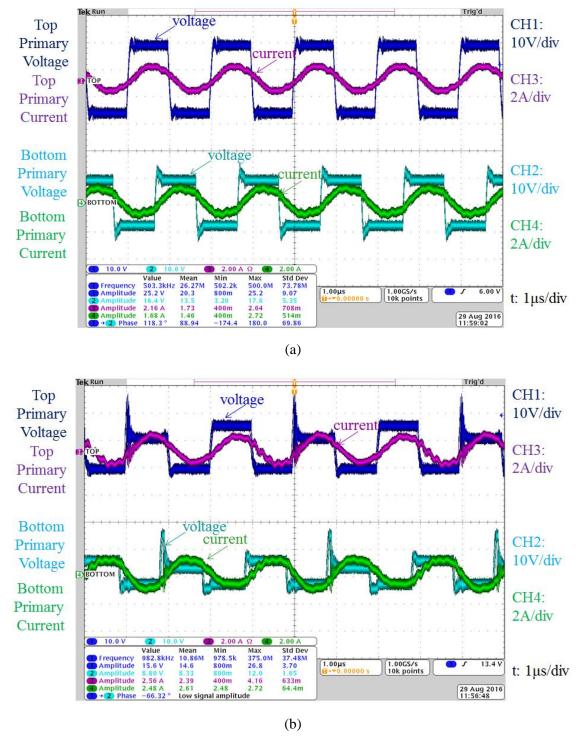

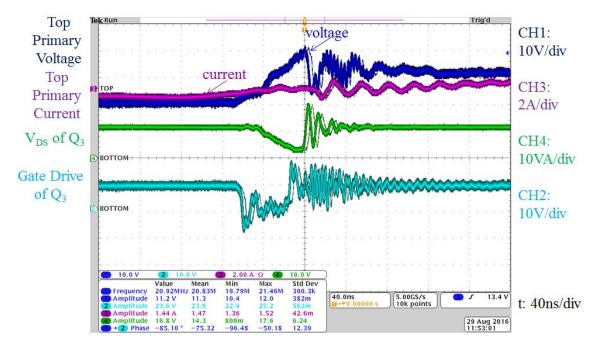

| Figure 3-15: | Experimental waveforms of the ICN resonant converter prototype with an input                  |

|              | voltage of 40 V and an output voltage of 2 V when operated in (a) fundamental                 |

|              | mode and (b) VFX mode for the inverters. For all plots, the top set of waveforms              |

|              | shows the voltage across the primary of the top transformer and the current into the          |

|              | primary. The second set shows the voltage across the primary of the bottom                    |

|              | transformer and the current into the primary                                                  |

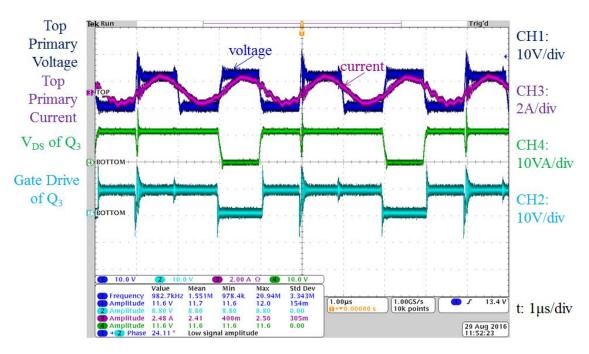

| Figure 3-16: | Experimental waveforms of the ICN resonant converter prototype with an input                  |

|              | voltage of 40 V and an output voltage of 2 V when operated in VFX mode. The top               |

|              | set of waveforms shows the voltage across the primary of the top transformer and              |

|              | the current into the primary. The middle (green) waveform shows the voltage across            |

|              | $Q_3$ of Figure 3-7. The last (cyan) waveform shows the voltage into the driver for $Q_3$ 111 |

| Figure 3-17:  | Experimental waveforms of the ICN resonant converter prototype with an input                                           |     |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|

|               | voltage of 40 V and an output voltage of 2 V when operated in VFX mode. The top                                        |     |

|               | set of waveforms shows the voltage across the primary of the top transformer and                                       |     |

|               | the current into the primary. The middle (green) waveform shows the voltage across                                     |     |

|               | $Q_3$ of Figure 3-7. The last (cyan) waveform shows the voltage into the driver for $Q_3$                              | 111 |

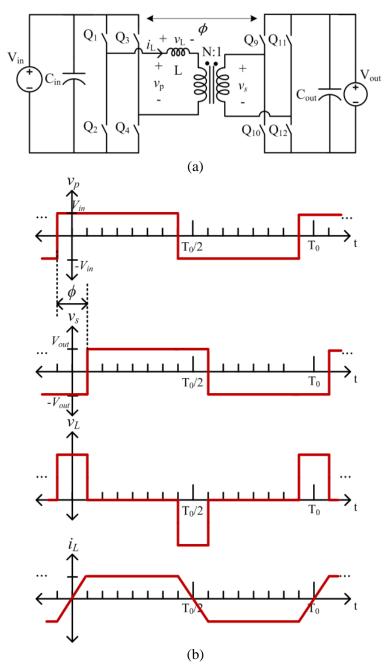

| Figure 4-1: ( | (a) A Dual Active Bridge (DAB) converter using a full-bridge inverter and rectifier.                                   |     |

|               | Two bridges are phase-shifted from each other across a transformer with turns ratio,                                   |     |

|               | N, and an inductance, L. (b) Example operating waveforms of the DAB where the                                          |     |

|               | rectifier square wave voltage is phase-shifted, $\phi$ , after the inverter square wave. In                            |     |

|               | this figure, the input voltage to output voltage ratio is equal to the transformer turns                               |     |

|               | ratio, resulting in a flattop trapezoidal current                                                                      | 114 |

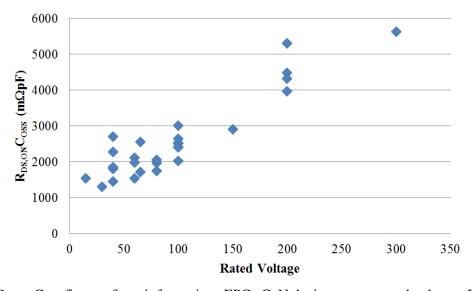

| Figure 4-2: I | R <sub>DS,ON</sub> C <sub>OSS</sub> figure-of-merit for various EPC eGaN devices across rated voltage. For             |     |

|               | each data point, the $R_{DS,ON}$ is the typical on-resistance in $m\Omega$ when the gate-to-                           |     |

|               | source voltage is 5V. The C <sub>OSS</sub> value indicated is the switch output capacitance in                         |     |

|               | pF at half the rated switch voltage. Devices evaluated from manufacturer datasheets                                    |     |

|               | online [77] as of Aug., 2016.                                                                                          | 116 |

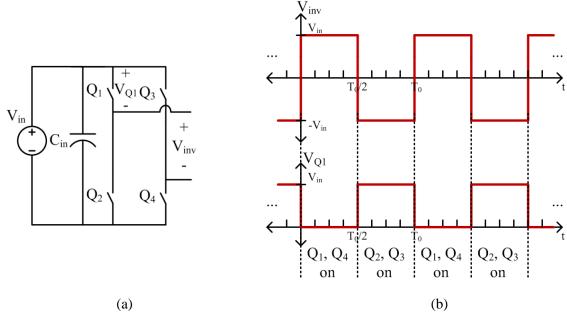

| Figure 4-3:   | (a) A full bridge inverter that delivers an output voltage designated as $V_{inv}$ . The                               |     |

|               | voltage across switch Q1 is explicitly labeled. (b) Operating switch waveforms to                                      |     |

|               | generate a square wave for $V_{inv}$ with period $T_0$ and the corresponding voltage across                            |     |

|               | $Q_1$ . While only the voltage across $Q_1$ is shown, all switches see a voltage profile                               |     |

|               | with the same amplitude.                                                                                               | 117 |

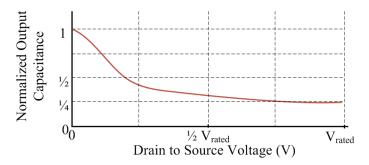

| Figure 4-4: I | Example device capacitance across drain-to-source voltage. The output capacitance                                      |     |

|               | at low voltages is much higher than the output capacitance at higher drain-to-source                                   |     |

|               | voltages.                                                                                                              | 117 |

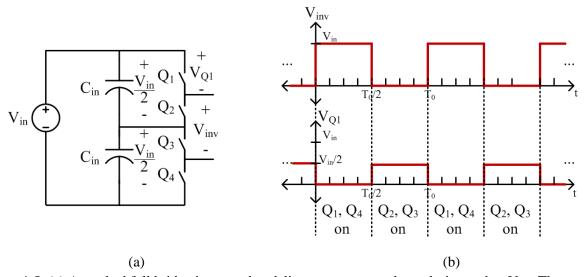

| Figure 4-5: ( | (a) A stacked full bridge inverter that delivers an output voltage designated as $V_{\rm inv}$ .                       |     |

|               | The voltage across switch $Q_1$ is explicitly labeled. (b) Operating switch waveforms                                  |     |

|               | to generate a square wave for $V_{inv}$ with period $T_0$ and the corresponding voltage                                |     |

|               | across $Q_1$ . While only the voltage across $Q_1$ is shown, all switches see a voltage                                |     |

|               | profile with the same amplitude                                                                                        | 118 |

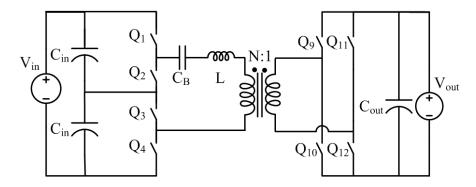

| Figure 4-6: C | Circuit diagram for an active bridge converter using a stacked full-bridge on the input                                |     |

|               | and a full bridge on the output. A blocking capacitor, C <sub>B</sub> , is used to remove the dc                       |     |

|               | component in the inverter output voltage                                                                               | 119 |

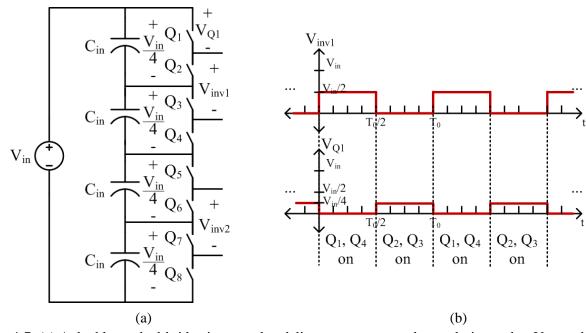

| Figure 4-7: ( | (a) A double stacked-bridge inverter that delivers two output voltages designated as                                   |     |

|               | V <sub>init</sub> and V <sub>init</sub> . The voltage across switch O <sub>1</sub> is explicitly labeled (b) Operating |     |

|              | switch waveforms to generate a square wave for $V_{invl}$ with period $T_0$ and the                                  |       |

|--------------|----------------------------------------------------------------------------------------------------------------------|-------|

|              | corresponding voltage across Q1. While only one inverter voltage is shown, the                                       |       |

|              | other inverter voltage can have the same profile. Similarly, while only the voltage                                  |       |

|              | across Q <sub>1</sub> is shown, all switches see a voltage profile with the same amplitude                           | . 119 |

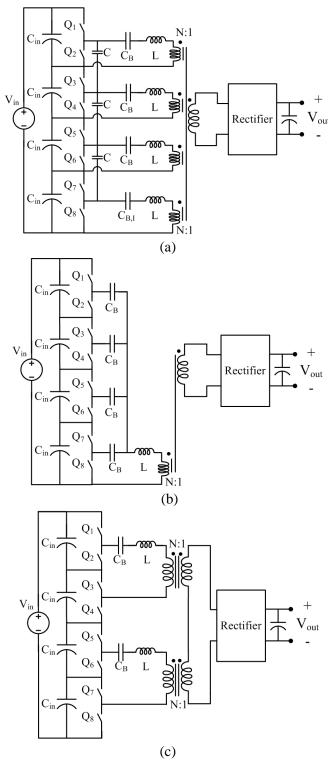

| Figure 4-8:  | Three possible variants of an active bridge converter with a double stacked-bridge                                   |       |

|              | inverter. (a) The outputs of four half-bridges are combined through a four primary,                                  |       |

|              | one secondary transformer structure. Voltage difference is compensated through the                                   |       |

|              | use of multiple interconnected capacitors. (b) The outputs of four half-bridges are                                  |       |

|              | connected in parallel before a single primary, single secondary transformer. (c) The                                 |       |

|              | outputs of two stacked full bridges are fed through two (single primary, single                                      |       |

|              | secondary) transformers whose secondaries are connected in series                                                    | . 122 |

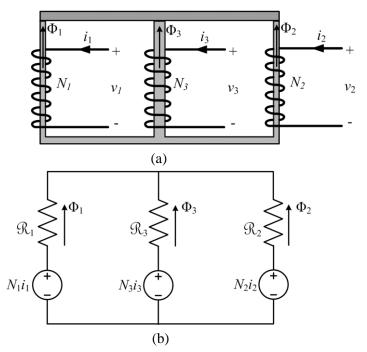

| Figure 4-9:  | (a) An example physical implementation of a three-winding magnetic component for                                     |       |

|              | use in the topology of Figure 4-8(c). This implementation has three windings on                                      |       |

|              | three separate legs. The $N_1$ , $N_2$ , and $N_3$ turns generate a flux of $\Phi_1$ , $\Phi_2$ , and $\Phi_3$ ,     |       |

|              | respectively. (b) A magnetic reluctance circuit model of the three-winding magnetic                                  |       |

|              | structure. The magnetic flux generated from the windings will travel through the                                     |       |

|              | reluctance, $\Re_1$ , $\Re_2$ , and $\Re_3$ of each core leg. In this simplified model we neglect                    |       |

|              | other flux paths (e.g., flux return paths outside the core) which are important for                                  |       |

|              | realizing the transformer leakage inductance.                                                                        | . 123 |

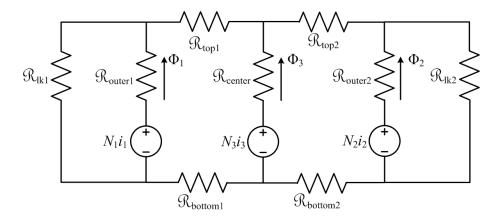

| Figure 4-10  | 2: A magnetic reluctance circuit model of the three-winding magnetic structure                                       |       |

|              | incorporating core and leakage reluctance. The magnetic flux generated from the                                      |       |

|              | outer windings will travel through the reluctance, $\Re_{\text{outer}1}$ and $\Re_{\text{outer}2}$ of each core leg. |       |

|              | The flux is then split between the reluctance in the top of the core, $\Re_{top1}$ and $\Re_{top2}$ ,                |       |

|              | and the reluctance outside the core, $\Re_{lk1}$ and $\Re_{lk2}$ .                                                   | . 125 |

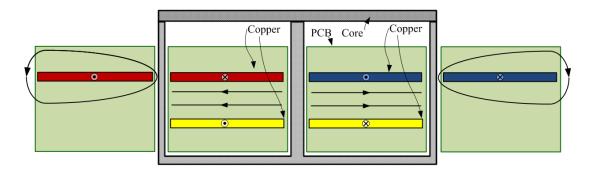

| Figure 4-11  | : A cross sectional view of a simplified winding structure of the three-winding                                      |       |

|              | magnetic component. For illustration, some magnetic field lines are drawn simply to                                  |       |

|              | represent their presence but they are not intended accurately represent the shape or                                 |       |

|              | magnitude.                                                                                                           | . 125 |

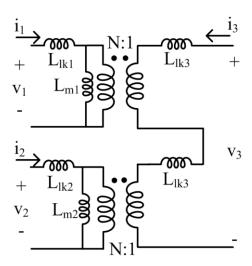

| Figure 4-12: | : A three-port model of the proposed three-winding magnetic structure                                                | . 126 |

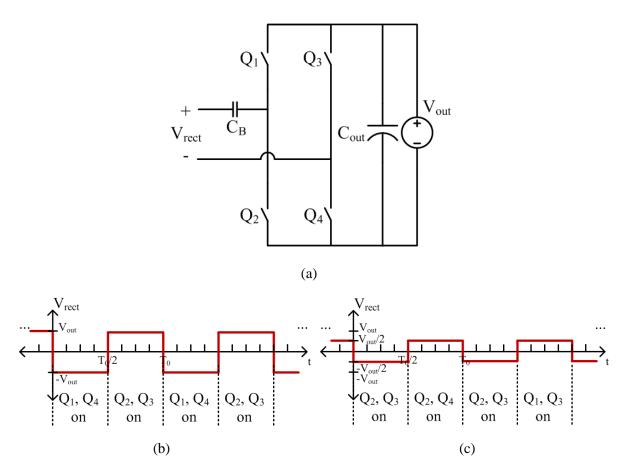

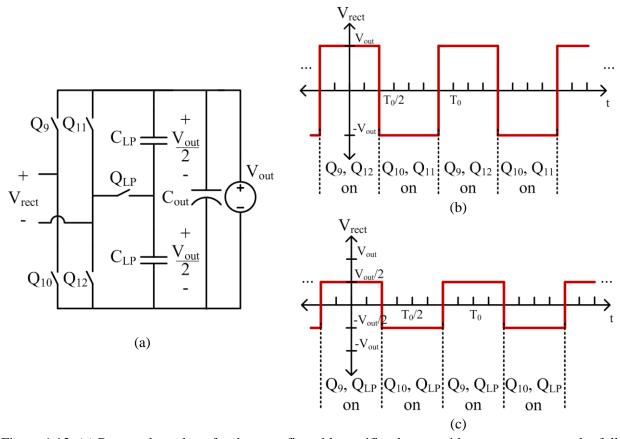

| Figure 4-13  | : (a) Proposed topology for the reconfigurable rectifier that can either operate as a                                |       |

|              | regular full bridge rectifier or as a half-bridge rectifier. (b) Operating voltage                                   |       |

|              | waveform at the rectifier input when operated as a full bridge rectifier. During this                                |       |

|              | mode, $Q_{LP}$ remains off. (c) Operating voltage waveform at the rectifier input when                               |       |

|              | operated as a half-bridge rectifier. During this mode, O <sub>11</sub> and O <sub>12</sub> remain off and            |       |

| $Q_{LP}$ remains on. The voltage at the rectifier input is supplied by one of the $C_{LP}$                   |     |

|--------------------------------------------------------------------------------------------------------------|-----|

| capacitors, which is nominally at half of the output voltage.                                                | 127 |

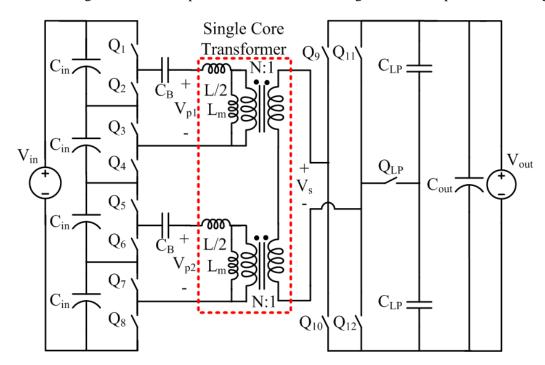

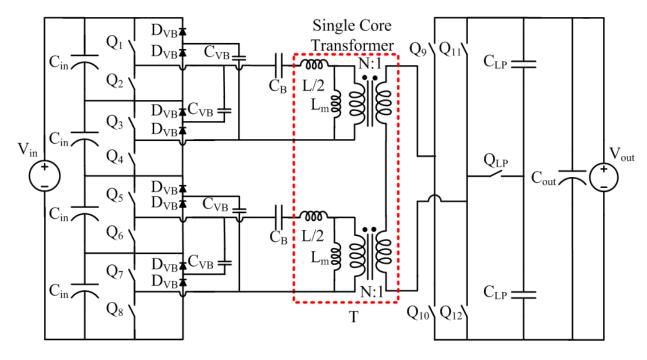

| Figure 4-14: Circuit diagram for the proposed system. The dashed red box contains an equivalent              |     |

| circuit model for the single magnetic component. Each of the stacked full bridges                            |     |

| feeds the primary winding of a single-core, three-winding transformer. An auxiliary                          |     |

| switch, Q <sub>LP</sub> , and capacitors C <sub>LP</sub> in the rectifier allow for a mode switch into a low |     |

| power mode. A blocking cap, CB, is used to remove the DC component in the                                    |     |

| square-wave output of each stacked-bridge. The total primary-referred leakage                                |     |

| inductance, L, is split between the two primaries.                                                           | 128 |

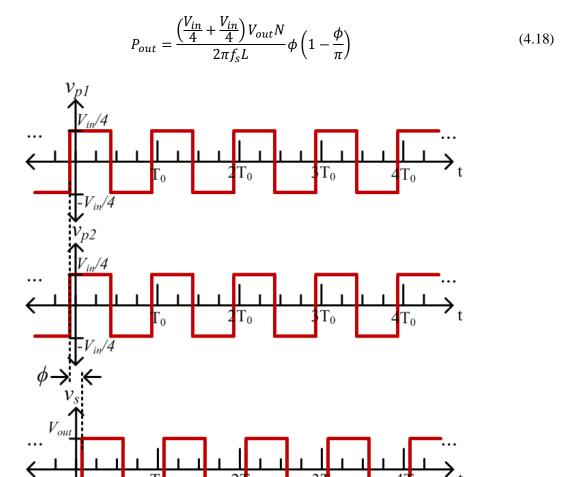

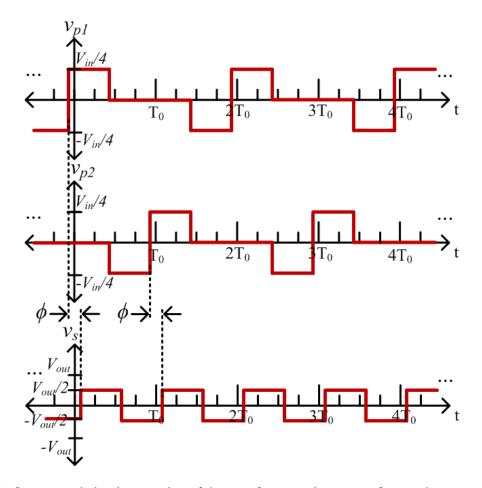

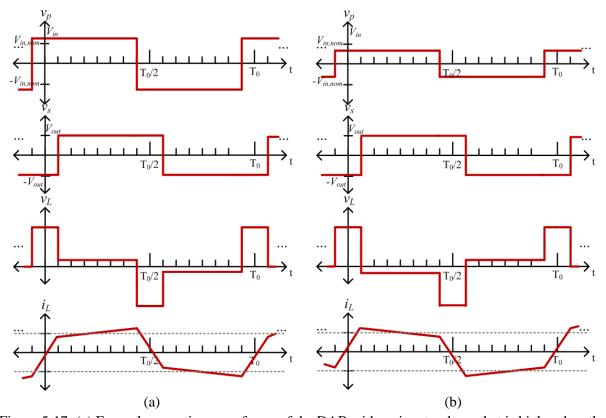

| Figure 4-15: Transformer voltage waveforms when operated in normal mode. Both transformer                    |     |

| primary windings see an identical square-wave voltage. The secondary voltage is                              |     |

| also a square-wave and is phase-shifted behind the primary voltages by $\phi$ (in                            |     |

| radians). In this mode, the switching period of the primary and secondary voltages is                        |     |

| $\mathrm{T}_0$                                                                                               | 129 |

| Figure 4-16: One example implementation of the transformer voltage waveforms when operated                   |     |

| in low-power mode. One transformer primary winding is energized while the other                              |     |

| is shorted. This particular scheme alternates which primary is energized every cycle.                        |     |

| The secondary voltage is still a square-wave but now with half the amplitude as                              |     |

| compared to the normal mode operation. It is still phase-shifted behind the primary                          |     |

| voltages by $\phi$ (in radians). In this mode, the switching period of the primary voltage                   |     |

| (and inverter) is now $2T_0$ and the secondary voltage (and rectifier) is still $T_0$                        | 131 |

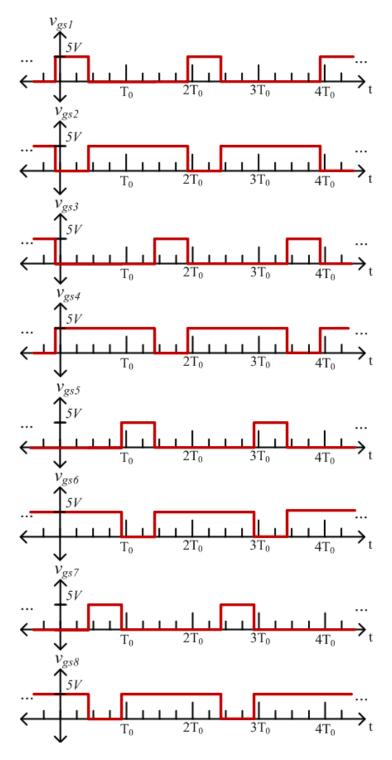

| Figure 4-17: One example implementation of the gate drive signals for the double stacked                     |     |

| inverter when operated in low-power mode. Through these signals one transformer                              |     |

| primary winding is energized while the other is shorted. This particular scheme                              |     |

| alternates which primary is energized every cycle. In this mode, the duty cycle of                           |     |

| the devices is either 25% or 75% and switching period is 2T <sub>0</sub> . Each half-bridge                  |     |

| signal is simply phase-shifted from the following half-bridge signal (i.e., the half-                        |     |

| bridge that is stacked underneath) by ½T <sub>0</sub>                                                        | 132 |

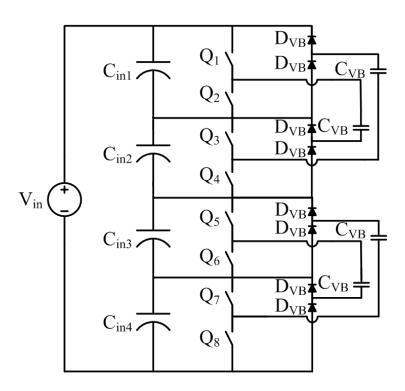

| Figure 4-18: A double stacked-bridge inverter with passive voltage balancing circuits on each                |     |

| stacked full-bridge inverter. This switched capacitor networked comprised of                                 |     |

| multiple diodes and capacitors will balance the voltage between capacitors $C_{\text{in}1}$ and              |     |

| $C_{in2}$ and the voltage between capacitors $C_{in3}$ and $C_{in4}$ .                                       | 133 |

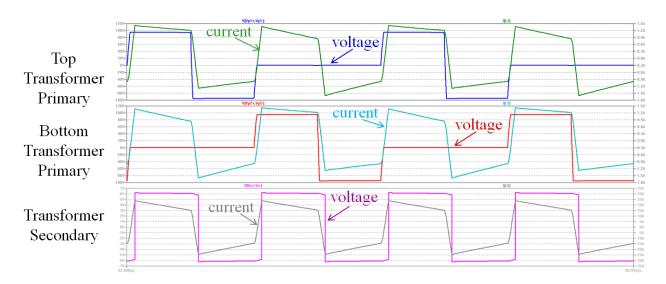

| Figure 4-19: Simulation results of the proposed reconfigurable double stacked active bridge                  |     |

| converter when operated in low-power mode with an input voltage of 380 V, an                                 |     |

|               | output voltage of 12 V, and a phase shift of 0.308 radians (approximately 5% of the                                             |       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|-------|

|               | total period). It can be seen that every cycle, one transformer winding is shorted                                              |       |

|               | while the other is energized. Current continues to flow through all windings. The                                               |       |

|               | slope of the transformer primary current varies depending on if the winding is                                                  |       |

|               | energized or shorted due to the magnetizing inductance, which is 256 $\mu H$ in this                                            |       |

|               | simulation.                                                                                                                     | . 134 |

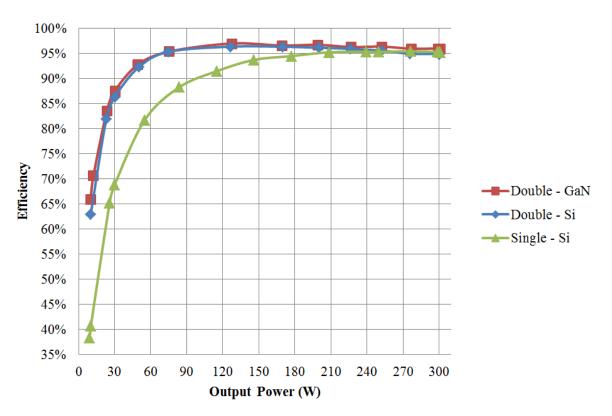

| Figure 4-20:  | Simulated power stage efficiencies of the traditional full bridge DAB converter, the                                            |       |

|               | single stacked active bridge converter, and the proposed double stacked active                                                  |       |

|               | bridge converter (operated in normal and low-power mode) using commercially                                                     |       |

|               | available GaN-based switching devices. Simulation conditions were: $V_{in} = 380 \text{ V}$ ,                                   |       |

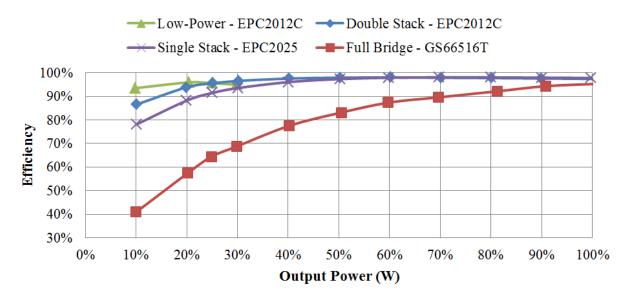

|               | $V_{out} = 12 \text{ V}, f_s = 500 \text{ kHz}, L = 8.204  \mu\text{H}, \text{ and } P_{out,rated} = 400 \text{ W}.$            | . 136 |

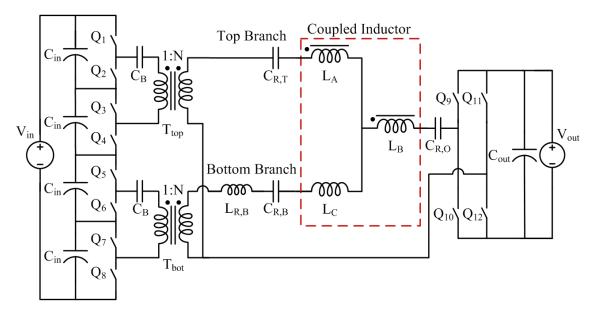

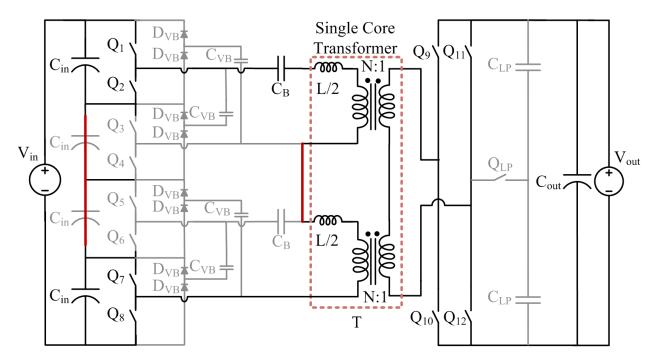

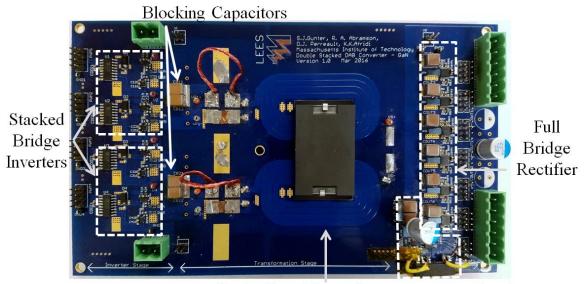

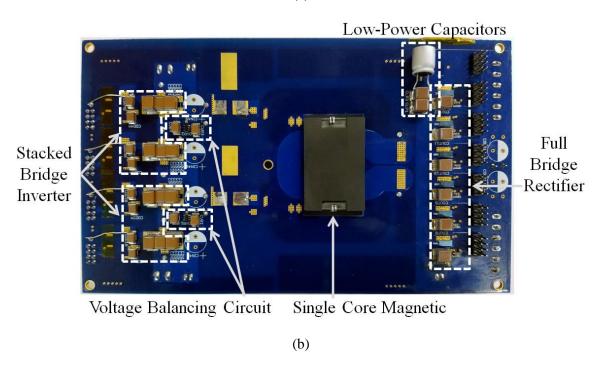

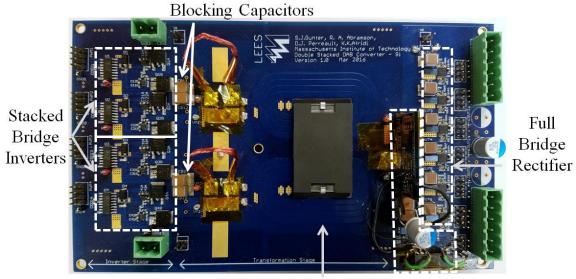

| Figure 5-1:   | Proposed implementation of the reconfigurable double stacked active bridge                                                      |       |

|               | converter. The dashed red box contains an equivalent circuit model for the single                                               |       |

|               | magnetic component. Each of the stacked full bridges feeds the primary winding of                                               |       |

|               | a single-core, three-winding transformer. Passive switched capacitor balancing                                                  |       |

|               | circuits are included. An auxiliary switch, $Q_{LP}$ , and capacitors $C_{LP}$ in the rectifier                                 |       |

|               | allow for a mode switch into a low power mode. A blocking cap, C <sub>B</sub> , is used to                                      |       |

|               | remove the DC component in the square-wave output of each stacked-bridge. The                                                   |       |

|               | total primary-referred leakage inductance, L, is split between the two primaries.                                               |       |

|               | Each primary has a magnetizing inductance, $L_{\rm m}$ .                                                                        | . 137 |

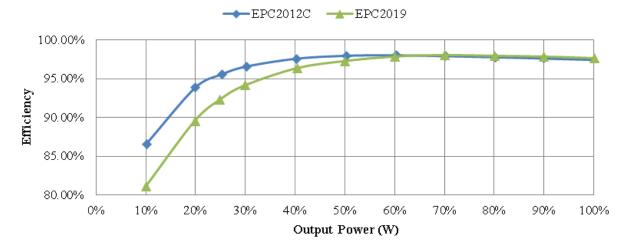

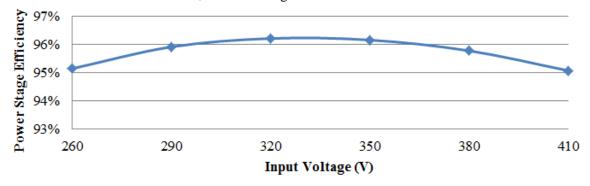

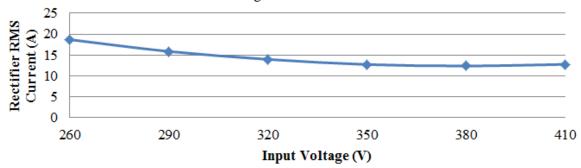

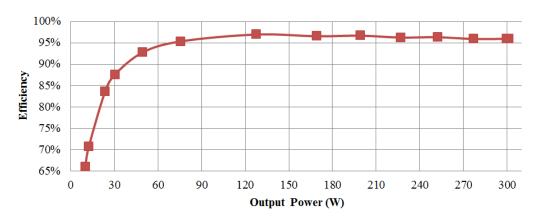

| Figure 5-2: S | Simulated power stage efficiencies of the reconfigurable double stacked active bridge                                           |       |

|               | converter using EPC2012C ( $R_{DS,ON} = 105 \text{ m}\Omega$ , $C_{OSS,eff} = 102.5 \text{ pF}$ ) and EPC2019                   |       |

|               | $(R_{DS,ON} = 55 \text{ m}\Omega, C_{OSS,eff} = 185 \text{ pF})$ for the inverter switches. For these simulations,              |       |

|               | $V_{in} = 380 \text{ V}$ , $V_{out} = 12 \text{V}$ , $f_s = 500 \text{ kHz}$ , and $P_{out,rated}$ is 400W. Each transformer of |       |

|               | Figure 5-1 has a turns ratio of 16 to 1 and an energy transfer inductance of $4.104~\mu H$                                      |       |

|               | (so that $L = 8.208 \mu H$ ). At full power, the simulated efficiency using the EPC2012C                                        |       |

|               | devices is 0.25% lower than the efficiency using the EPC2019 devices. At 10%                                                    |       |

|               | load, in the presence of hard switching, the efficiency using the EPC2012C devices                                              |       |

|               | is 5.5% higher than the efficiency using the EPC 2019 devices                                                                   | . 140 |

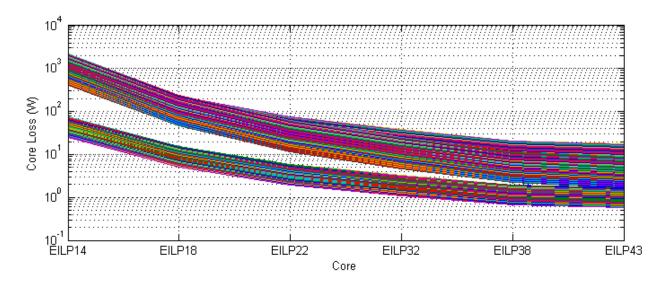

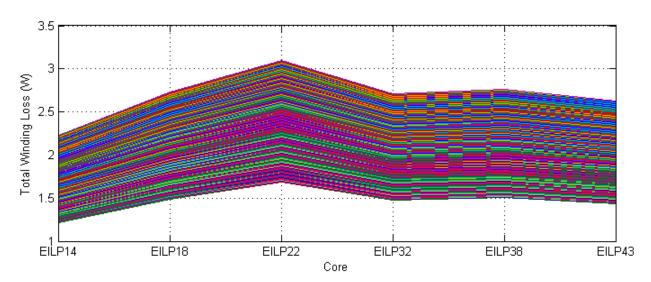

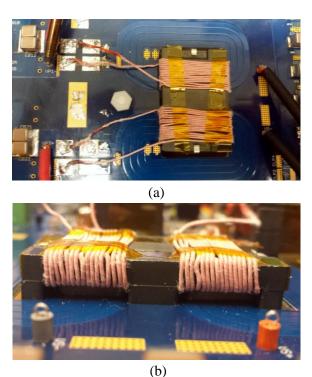

| Figure 5-3:   | Core loss across core geometry. Each line represents a frequency from 100 kHz to 1                                              |       |

|               | MHz. Calculations are based on a transformer primary voltage of ±95Vfor half a                                                  |       |

|               | cycle. Core loss is calculated based on (5.3) with the parameters taken from the                                                |       |

|               | EPCOS MDT [57] depending on first the frequency and then the magnetic flux                                                      |       |

|               | density. (The gap in the plot is due to inconsistencies between the core loss equation                                          |       |

|               |                                                                                                                                 |       |

| and the magnetic flux density over which it is valid. Because the loss is so high, this          |     |

|--------------------------------------------------------------------------------------------------|-----|

| core would not be chosen.) The MATLAB code to generate this plot is provided in                  |     |

| Appendix A                                                                                       | 142 |

| Figure 5-4: Example of how parameters to calculate resistance are listed on a datasheet          | 143 |

| Figure 5-5: Winding loss across core geometry. Each line represents a frequency from 100 kHz     |     |

| to 1 MHz. Calculations are based on a transformer secondary RMS current of                       |     |

| 37.169 A – determined from a simulation with $V_{in} = 380$ V, $V_{out} = 12$ V, $f_s = 500$     |     |

| kHz, $L = 8.204 \mu H$ , and $P_{out} = 400W$ . Winding loss for the secondary is calculated     |     |

| based on the mean length of a single turn, assuming one skin-depth of conduction                 |     |

| (up to 140 μH) spread out across 4 PCB layers. It is assumed that each winding has               |     |

| the same winding loss, so the total winding loss is three times the loss of the                  |     |

| secondary winding. The MATLAB code to generate this plot is provided in                          |     |

| Appendix A                                                                                       | 143 |

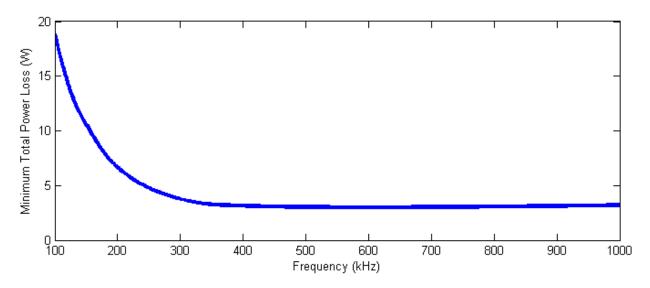

| Figure 5-6: Total power loss for the lowest lost design across frequency. The total loss is      |     |

| calculated as the summation of the core loss and the winding loss (which were                    |     |

| shown in Figure 5-3 and Figure 5-5, respectively). The line represents the lowest                |     |

| loss across six different core sets. The MATLAB code to generate this plot is                    |     |

| provided in Appendix A.                                                                          | 144 |

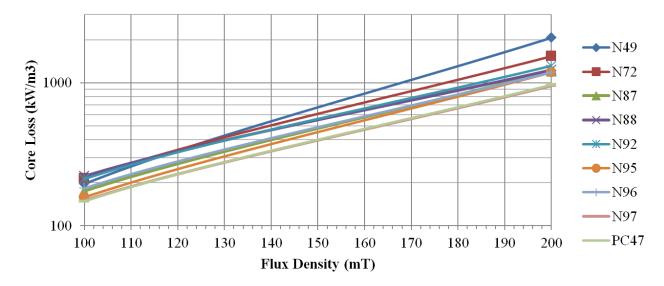

| Figure 5-7: Core loss per unit volume across flux density for several EPCOS materials at 200 kHz |     |

| and 100 °C [57]. The range of flux densities shown is relevant for an input voltage              |     |

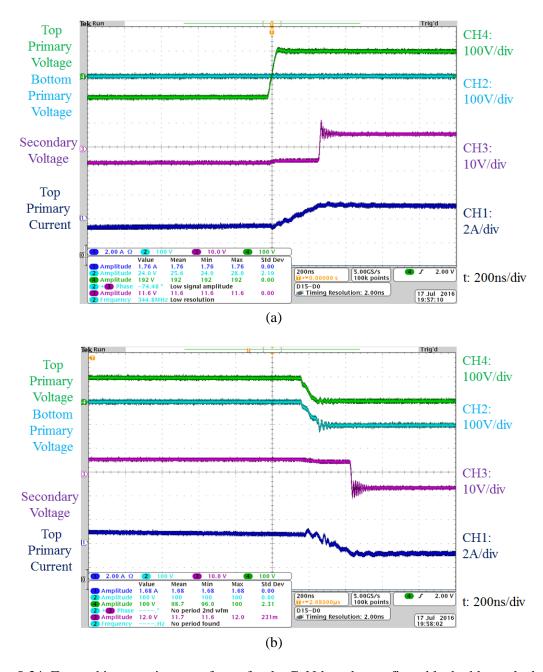

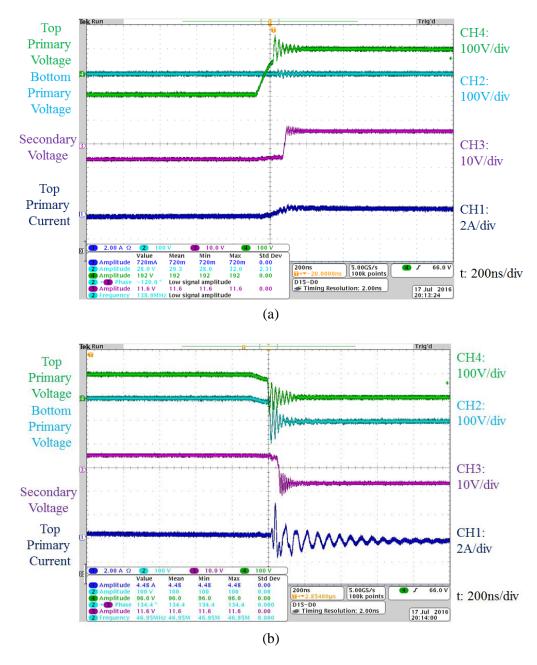

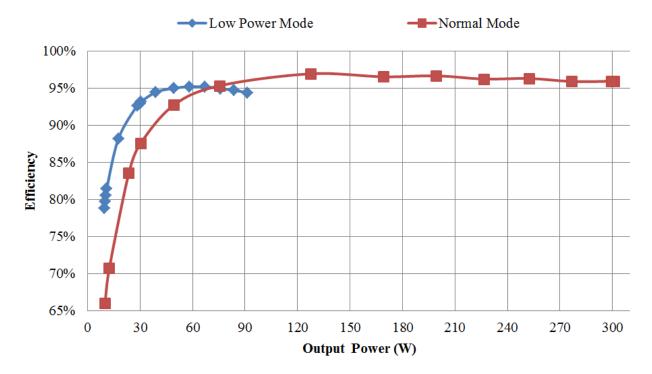

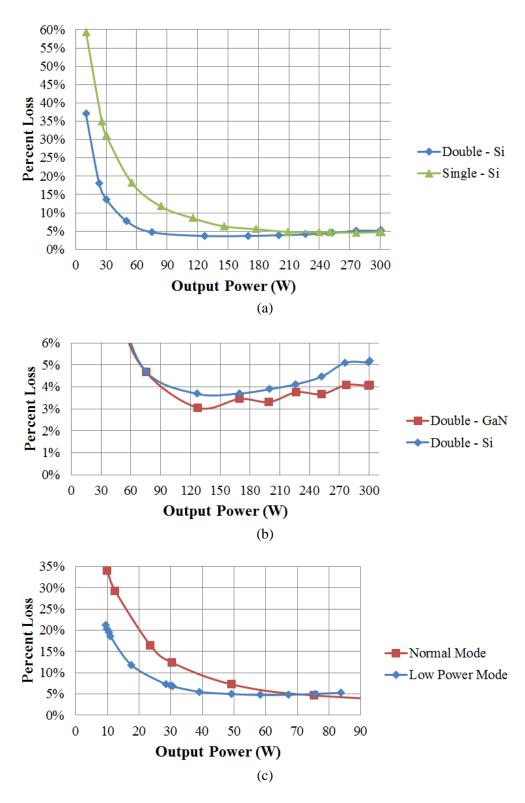

| of 380 V and ELP43 core area.                                                                    | 145 |