# Techno-economical Evaluation of Intra-datacenter Optical Transceiver Designs

by

Wei Yu

B.S., Materials Physics University of Science and Technology of China, 2011

### SUBMITTED TO THE DEPARTMENT OF MATERIALS SCIENCE AND ENGINEERING IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

### AT THE

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

JUNE 2018

© 2018 Massachusetts Institute of Technology. All Rights Reserved.

| Signature of Author:Signat | Department of Materials Science and Engineering<br>June 8 <sup>th</sup> , 2018                                        |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Contribut hur              | ignature redacted                                                                                                     |

|                            | Lionel C. Kimerling<br>Lord Professor of Materials Science and Engineering<br>Thesis Supervisor<br>Signature redacted |

| Accepted by:               | John F. Elliott Professor of Materials Chemistry<br>Chair, Departmental Committee on Graduate Student                 |

## Techno-economical Evaluation of Intra-datacenter Optical Transceiver Designs

by

#### Wei Yu

Submitted to The Department of Materials Science and Engineering on May 17<sup>th</sup>, 2018 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Materials Engineering

### Abstract

The evolution of data center network interconnects is based: at the component level, on cost, power, and bandwidth density; and at the system level, on cost, unit count, footprint, and implementation time. The decision for iterative vs. transformational design depends critically on the product horizon view that amortizes R&D, manufacture tooling and infrastructure preparation. An iterative platform can be implemented earlier, but it may present limited performance scalability. A transformational design can have large creation and implementation costs that are amortized over a longer time window. A framework for quantitatively capturing these variables using a new technology inventory model is developed. Scenarios for deployment of six different transceiver package platforms to meet the projected data center capacity scaling ramp are constructed. The iterative designs provide better return on investment for a 3-year time window, while the transformational designs are optimized for a 20-year window.

Thesis Supervisors:

Lionel C. Kimerling Title: Thomas Lord Professor of Materials Science and Engineering

### Acknowledgements

I want to thank my advisor Professor Lionel Kimerling, who has been unreservedly encouraging me, supporting me and believing me. I want to thank Dr. Randolph Kirchain and Professor Elsa Olivetti for guiding me and sitting in my thesis committee. I want to thank Dr. Jurgen Michel and Dr. Yan Cai from EMAT for teaching the design and processing of Germanium lasers.

I want to thank Dr. Peter O'Brien, Dr. Lee Carroll from Tyndall National Institute, Mr. Ashish Kelbar, Dr. Katharine Schmidtke, Dr. Naadar Hasani, Dr. Zhiping Yao from Facebook, Mr. Dick Otte, Dr. Madelaine Glick (now in Columbia), Dr. Terry Smith, Mr. Tom Marrapode from PSMC Roadmap TWG, Dr. Peter De Dobbelaere from Luxtera, Dr. Wei-ping Huang, Dr. Yu Zhu from Hisense, Dr. Qianggao Hu from Accelink for generously sharing their valuable knowledge and visions with me.

Lastly but not the least, I want to thank my family and friends. I feel very lucky that I can have the chance to enjoy wonderful moments with you.

# **Table of Contents**

| Abstract                                        |

|-------------------------------------------------|

| Acknowledgements4                               |

| Table of Contents                               |

| Chapter 1 Introduction6                         |

| Chapter 2 Intra-datacenter Transceiver Designs  |

| Chapter 3 Cost and Time for Product Development |

| Chapter 4 Cost and Time for Mass Production69   |

| Chapter 5 Cost and Time for System Integration  |

| Chapter 6 Conclusion and Future Work 119        |

## Chapter 1 Introduction

### **Optical Transceivers**

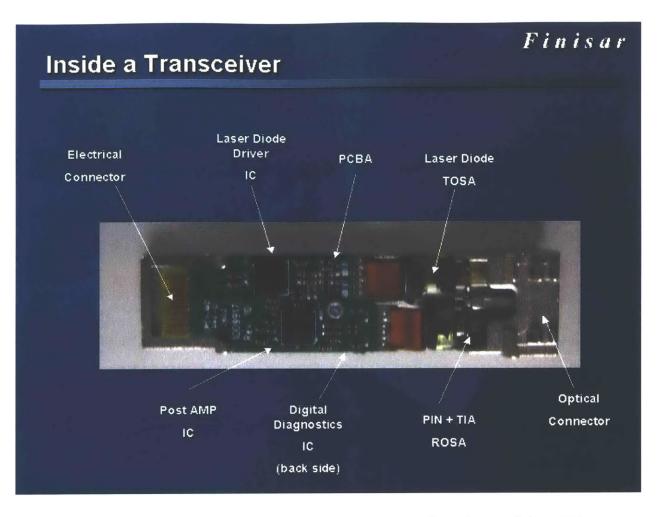

An optical transceiver is a device that sends and receives data using optical fiber rather electrical wire. The device is usually composed of two parts: a transmitter that converts electrical signals into optical signals before transmitting data and a receiver that converts optical signals back to electrical signals after receiving data. The transmitter requires a modulated light source, an electrical IC block that drives the light source or the modulator. The receiver requires a photodetector, an electrical IC block that turns current signals to voltage signals (e.g. transimpedance amplifiers) and an electrical IC block that converts analog signals into digital signals (post amplifiers). Besides, for high speed signals (e.g. 25G per channel), there are also information clock data recovery blocks timing and and to extract serializer/deserializer blocks to compensate for limited input/output. For even higher speeds (e.g. 100G per channel), digital signal processing blocks for signal modulation (e.g. PAM4) are needed. Those are the main functional blocks. To make them work together as a device, there are additional electrical interconnect components (e.g. printed circuit board and bonding wires) and optical alignment components (micro-lens, optical benches, and mechanical housings).

Optical transceivers are signal converters between electrical and optical signals. Together with optical transmission media such as optical fibers and waveguides et al, they form optical interconnects between electrical circuits-based servers and network switches. By far the information computation and storage are still dominated by electrical circuits. Naturally the information transmission should be also done by electrical interconnects such as on-chip metal lines, backplane PCB, copper cables et al. However, those electrical interconnects are subject to basic physical limits such as RC delay at high bandwidth.[1] During the exponential bandwidth scaling, electrical interconnects are losing their fields to optical interconnects. [2]

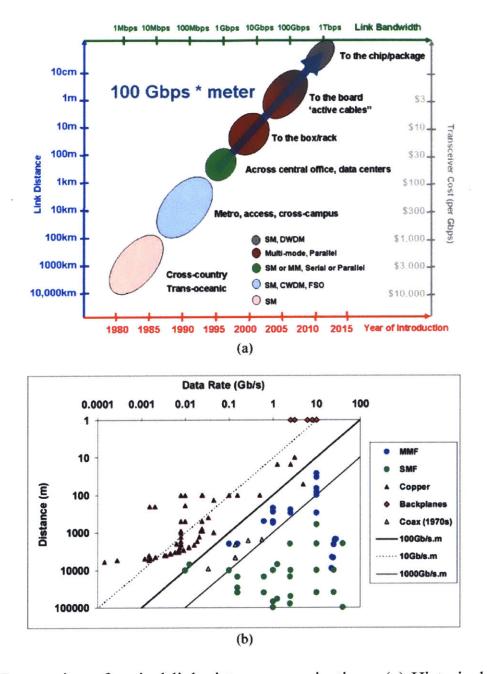

Figure 1 Penetration of optical links into communications. (a) Historical roadmap for introduction of optical interconnections into digital systems. (b) Data rate versus distance of commercial electrical versus optical links. [3]

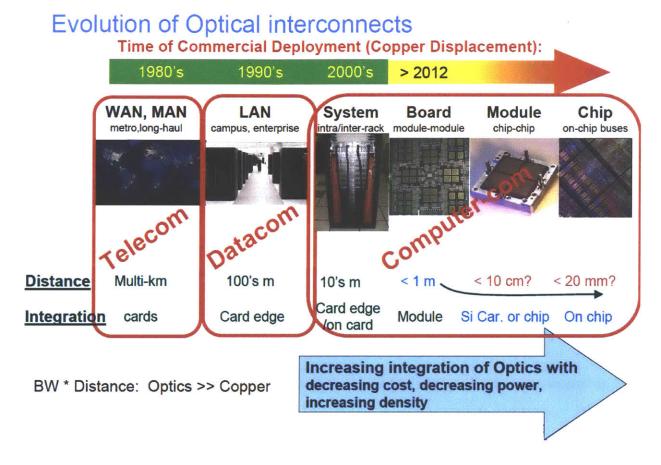

Figure 2 Copper interconnects are being displaced by optical interconnects [4]

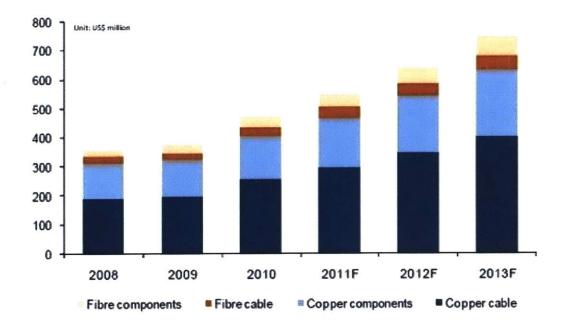

### Barriers for entry

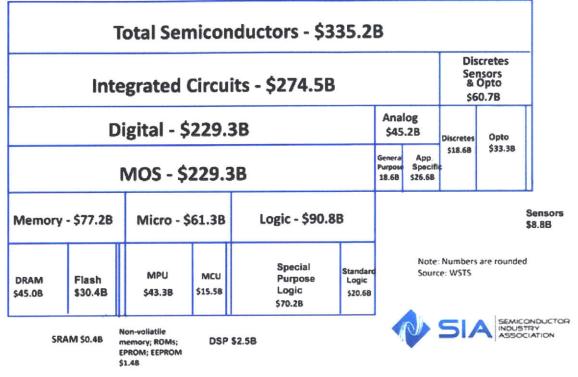

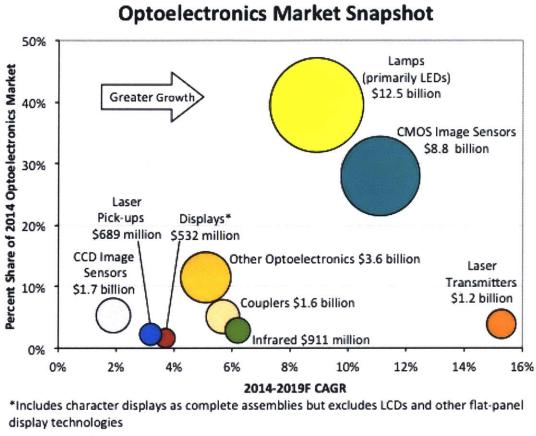

The forecasted growth rate for fiber-optic laser transmitters is highest among all kinds of optoelectronic product categories but the total market is still small. A market size of \$1.2 billion, is far below the total semiconductor market of \$335 billion [5] and the network equipment and software market of \$200 billion [6]. The data communication market, the current battleground between optical and copper interconnects, is still dominated by copper [7].

## Worldwide Semiconductor Market Product Breakdown (2015)

Figure 3 The market share of optoelectronics is only 10% of the total

semiconductors market [5]

Source: IC Insights

Figure 4 The growth rate for fiber-optic laser transmitters is forecasted to be as

high as 15% [8]

Figure 5 Copper interconnect still dominates the data communication market [7]

In 1997, Fine and Kimerling pointed out that there were three barriers for optical communication products and optoelectronic industry in general: supply chain disaggregation, insufficient government support and lack of a killer application. [9] In addition, general studies about market entry barriers can also be applied to optical interconnect products. Cost advantages of incumbents are often identified as the most crucial gating factor [10]. The communication interconnect community agrees with that point and often lists cost as the first and the important metrics for evaluation when comparing different technologies. [11] Besides, Porter's theory suggests that early market entrants have advantages in customer switching cost [12]. For example, network switch ASICs are still setting the loss margin based on copper cables.

flexibility that copper cables are pluggable and flexible and complain that optical fibers are fragile and sensitive to dust.

| Barriers                              | Implications                                                                                                                                                                   | For optical interconnects                                                                       |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Cost advantage of incumbents          | One of the most important<br>entry barriers, and usually<br>results from economies of<br>scale and learning curve<br>effect.                                                   | Cost is the most important metrics.                                                             |

| Product differentiation of incumbents | Established firms have<br>brand<br>identification and<br>customer loyalties due to<br>advertising, being first in<br>a market, customer<br>service, or product<br>differences. |                                                                                                 |

| Capital requirements                  |                                                                                                                                                                                | Both government and<br>industry are making<br>heavy investments, e.g.<br>AIM Photonics in U.S., |

|                         | barrier to entry, and is                                                                                                              | Photonics21 in E.U.,         |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                         | higher in capital-intensive                                                                                                           | PETRA in Japan,              |

|                         | industries.                                                                                                                           | A*STAR IME in                |

|                         |                                                                                                                                       | Singapore, MOST plan         |

|                         |                                                                                                                                       | on "Photonics and            |

|                         |                                                                                                                                       | microelectronics device      |

|                         |                                                                                                                                       | and integration" in China    |

|                         |                                                                                                                                       | et al.                       |

|                         |                                                                                                                                       | •                            |

|                         |                                                                                                                                       | Network switch ASICs         |

|                         |                                                                                                                                       | are still setting the loss   |

|                         | Switching costs prevent<br>the buyer from changing<br>suppliers, and<br>technological changes<br>often raise or lower these<br>costs. | margin based on copper       |

|                         |                                                                                                                                       | cables. Installation and     |

|                         |                                                                                                                                       | maintenance staff are still  |

| Customer switching cost |                                                                                                                                       | used to the flexibility that |

|                         |                                                                                                                                       | copper cables are            |

|                         |                                                                                                                                       | pluggable and flexible       |

|                         |                                                                                                                                       | and complain that optical    |

|                         |                                                                                                                                       | fibers are fragile and       |

|                         |                                                                                                                                       | sensitive to dust.           |

| Access to distribution channels | First or early market<br>entrants use intensive<br>distribution strategies to<br>limit the access to<br>distributors for the<br>potential market entrants. | There is not much<br>discussion yet.                                                                  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                 |                                                                                                                                                            |                                                                                                       |

| Government policy               | Government limits the<br>number of firms in a<br>market by requiring<br>licenses, permits, etc.                                                            |                                                                                                       |

| Advertising                     |                                                                                                                                                            | discussion yet. Besides,<br>copper cables firms are<br>also investing on optical<br>interconnects for |

|                       | dollar revenues to         |                                 |

|-----------------------|----------------------------|---------------------------------|

|                       | decline.                   |                                 |

|                       | Market entry is expected   |                                 |

|                       | to be more likely during   |                                 |

|                       | periods of increasing      |                                 |

| Number of competitors | incorporations and less    | There is not much               |

|                       | likely after a lag, during | discussion yet.                 |

|                       | periods when high          |                                 |

|                       | numbers of business        |                                 |

|                       | failures occur.            |                                 |

|                       | The barrier is usually     |                                 |

|                       | short-lived. Incumbent     | It is true that there are still |

|                       | firms may prevent the      | investments on R&D of           |

|                       | entry of new firms by      | copper cables but the           |

| Research and          | investing effectively in   | market of copper cables is      |

| development           | R&D, which increases       | keeping shrinking. (The         |

|                       | technological scale        | reach of copper cables          |

|                       | economies and forces the   | shrinks by 40% every            |

|                       | ongoing industry context   | generation.)                    |

|                       | to evolve in a way that    |                                 |

|                      | would make subsequent        |                           |

|----------------------|------------------------------|---------------------------|

|                      | attempts to enter even       |                           |

|                      | more ineffectual.            |                           |

|                      | Price warfare can be a       |                           |

|                      | significant deterrent to     |                           |

|                      | entry, particularly in       | There is not much         |

| Price                | industries where firms are   |                           |

|                      | more likely to lower their   | discussion yet.           |

|                      | prices to fill underutilized |                           |

|                      | plants.                      |                           |

|                      | Usually present in high      |                           |

|                      | tech industries and can      |                           |

| Technology and       | actually raise or lower      | The point is incorporated |

|                      | economies of scale,          | in the "consumer          |

| technology change    | which is one of the major    | switching cost" barrier   |

|                      | sources of cost              |                           |

|                      | advantages.                  |                           |

| Market concentration | The influence and impact     | There is not much         |

|                      | of concentration on entry    | discussion yet.           |

|                      | appear to be minimal.        |                           |

|                         | Entry is unlikely to be as             |                   |  |  |  |  |

|-------------------------|----------------------------------------|-------------------|--|--|--|--|

|                         | easy in highly                         | There is not much |  |  |  |  |

| Seller concentration    | concentrated as in less                | discussion yet.   |  |  |  |  |

|                         | concentrated markets.                  |                   |  |  |  |  |

|                         | Only expected in                       |                   |  |  |  |  |

|                         | exceptionally profitable               |                   |  |  |  |  |

|                         | oligopolistic industries,              |                   |  |  |  |  |

|                         | Incumbent firms create                 |                   |  |  |  |  |

| Divisionalization       | new independent                        | There is not much |  |  |  |  |

|                         | divisions more cheaply discussion yet. |                   |  |  |  |  |

|                         | than potential entrants                |                   |  |  |  |  |

|                         | who must incur additional              |                   |  |  |  |  |

|                         | overhead costs for entry.              |                   |  |  |  |  |

|                         | New entrants to an                     |                   |  |  |  |  |

| Brand name or trademark | industry are denied the                |                   |  |  |  |  |

|                         | benefits of brand name                 | There is not much |  |  |  |  |

|                         | created by others as a                 | discussion yet.   |  |  |  |  |

|                         | result of the exclusive                |                   |  |  |  |  |

|                         | rights to use given with a             |                   |  |  |  |  |

|                                               | trademark. Usually a                                                                                                                                                        |                                      |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                                               | weak barrier.                                                                                                                                                               |                                      |

| Sunk costs                                    | Contribute to entry<br>barriers that can also give<br>rise to monopoly profit,<br>resource misallocation,<br>and inefficiencies.                                            | There is not much discussion yet.    |

| Selling expenses                              | Shiftsindemandfunctionscanresultfromsellingeffortsmakingmarketentryendogenous.                                                                                              |                                      |

| Incumbent's expected reaction to market entry | May deter market entry<br>only if the incumbent<br>firms are able to influence<br>potential entrants'<br>expectation about the<br>post-entry reaction of the<br>incumbents. | There is not much<br>discussion yet. |

| Possession of strategic                       | Access to strategic raw                                                                                                                                                     |                                      |

| raw materials                                 | materials contributes to                                                                                                                                                    | discussion yet. Besides              |

| firms'  | absolute | cost | the key raw materials for |

|---------|----------|------|---------------------------|

| advanta | ges      |      | copper interconnects and  |

|         |          |      | optical interconnects are |

|         |          |      | different.                |

Table 1 List of market entry barriers from literature [10]

There have been quite a few solutions suggested to accelerate the technology diffusion and help optical interconnect products overcome those commercialization barriers. One is vertical integration of the supply chain through ownership or knowledge sharing [9], [13], [14]. However, after the dotcom bubble, the ownership approach sounds like a minefield for many U.S. companies, although Asian companies, such as Samsung, are still taking the ownership approach. As for knowledge sharing, companies are worried about intellectual properties. For example, Samsung, as a supplier of Apple's iPod and iPhone products since 2005, gained critical knowledge of technologies and market, launched its own smart phone in 2010 and has since become Apple's largest competitor. [14]

Another proposed solution is standardization [15]. However, starting from the strategic planning phase, different interest groups are arguing for different standards. The market is highly fragmented. For example, for post-100G intra-datacenter

optical transceiver products, there are two speeds (200G & 400G), three form factors (QSFP-DD, OSFP and COBO) and three combinations of channels (2, 4 and 8 channels) being discussed. When there are so many standards coexisting, the benefit of standards become nominal.

### New environment, new way of thinking

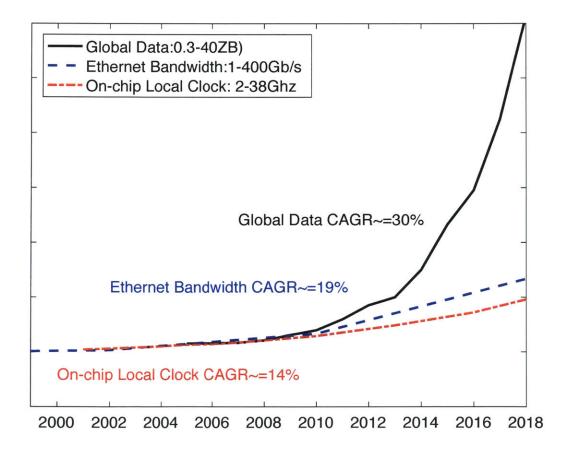

Figure 6 The increasing gap between component performances and the data

volume [16]–[18]

The data communication market is new for optical transceiver vendors. The optical interconnect technology is also new for data center customers. What's more, the world of information technology is experiencing the ending of Moore's law on the side of technology supply and the booming of big data on the side of market demands. Moore's law has been giving the industry the confidence to believe that people can improve cost and power efficiency of logic and memory devices through shrinking the size of transistor. Now the technology node has been down to sub-10 nm and both the quantum effect and the fabrication challenge start to put the brake on the scaling law. [19]-[21] On the other hand, the amount of big data tasks and the size of a single task are keeping increasing [22], [23]. It requires more and more powerful logic and memory units. When the logic and memory units are failing the demanded performance scalability individually, system-level redesigns, such as GPU computing [24], [25] and distributed storage [26], [27], become necessary to realize efficient parallelism. On the algorithm level, a big task is decomposed into small sub-tasks. On the hardware level, logic, memory and storage units are rearranged to facilitate the communication within each sub-task and between different sub-tasks.

When the environment changes, straight extrapolations of past successes may cause misunderstandings that impede future successes. Through my field studies and interviews with different stakeholders, I have discovered a few points to notice.

| Location                            | Relevant design scope                                                            |

|-------------------------------------|----------------------------------------------------------------------------------|

| Edge of network                     | Distance, bandwidth, (latency), cost, power, size, of                            |

| (Internet network)                  | the link (fiber + 2 transceivers)                                                |

| Edge of system<br>(Intra-datacenter | Distance, bandwidth, (latency), cost, power, size of the network (link + switch) |

| network)                            |                                                                                  |

| Edge of                             | (Latency), cost, power, size of the system (network                              |

| device/chip                         | + CPU/GPU + memory + hard disk)                                                  |

1. The evaluation of optical transceiver should be done at a system level.

Table 2 The system scope is expanding

In a telecommunication network, the physical network topology is almost fixed and the performance and cost of optical transceivers is discussed within the scope of an interconnect link. In an intra-datacenter network, the physical network topology becomes a decision variable which is coupled with the choice of optical transceivers. The performances and costs of different optical transceivers are being examined at the network scale. For the discussion of resource-centric disaggregated datacenters, the performances and costs of network, CPU/GPU, memory and hard disks are evaluated together as a system [28], [29]. Nowadays, instead of competing with other optical transceivers only, optical transceivers are even facing the challenge of GPUs for cost-effectiveness. [30] An updated techno-economical evaluation of optical transceiver designs should take system integration into account rather than look at optical transceiver devices only.

2. The long procurement lead time of optical transceivers affects customers' adoption.

For data centers, the choice of optical transceivers, the fiber set-up and the network switches are coupled. In 2016-2017, when data centers started to install 100G optical transceivers inside a data center, the delivery of orders were delayed for six months to a year. That unexpected long procurement lead time of optical transceivers not only postponed the network production start but also put their inventories of other network components at risk. When data centers make decisions for next purchases, the length of procurement lead time is influencing their choice. For example, for next-generation network, a network customer may

choose the old generation optical transceivers of 100G bandwidth over the new generation optical transceivers of 400G bandwidth to avoid supply risks.

3. The product development cost is non-trivial for intra-datacenter optical transceiver products

Due to the need of dynamically re-assignment of resources such as virtual machines and storage volumes regardless of physical distances, data centers prefer homogeneous network interconnect fabrics [31]. One hyperscale data center may install 100s of thousands of optical transceiver devices of the same design. Some people think the upfront investment on product development become trivial at such a high volume and focus on minimizing manufacturing cost only. However, the product development cost is actually non-trivial. "It takes more than a thousand wafers to qualify the process flow of silicon photonic chips in the foundry", introduced an engineering lead of a silicon photonics company which chose a two-chip design over a single-chip design to save product development cost.

#### An evaluation framework for integrating stakeholders

There have been several metrics proposed to compare different optical transceiver designs to provide guidance on optical transceiver research and product planning. In optical communication systems, a widely adopted metric is the bandwidth-distance product. [32]In 2005, D. Neilson et al. from Bell Labs presented a chart of data rate and data transmission distance to compare different interconnect technologies at European Conference on Optical Communication.[3] In 2011, E. Fuchs et al. from MIT estimated the manufacturing cost of different 100G optical transceiver designs.[33] In In 2011, Dr. A. Vahdat et al. from Google put forward a few requirements for data center interconnects: lower cost, larger scale, faster switching time and lower insertion loss.[34] That set of metrics introduced cost into the evaluation. In 2012, Dr. M. Taubenblatt from IBM proposed a spider plot composed of six factors to compare optical interconnects for high performance computers: density, 1/power, reliability, 1/BER, latency. [33] In 2013, the 1/cost. communications technology roadmap working group led by Professor L. Kimerling at MIT Microphotonics Center came up with three key metrics: cost, energy, bandwidth density and scalability. In 2015, D. Mahgerefteh et al. from Finisar stated that single-channel solutions would be more cost-effective than multi-channel solutions and among single-channel solutions a VCSEL-based solution would be the most cost-effective one due to its simple structure and large alignment tolerance of

multi-mode light coupling.[35] In 2016, Dr. A. Chakravarty et al. mentioned that Facebook had shrunk the required temperature range and shortened the communication distance to enable lower cost points.[36] In 2017, Mr. D. Zhuo et al. from Microsoft, Columbia University and University of Washington argued that the BER of 10<sup>-6</sup> was a legacy from telecom and more than needed in the data center applications. They pointed out optical links were major cost drivers of data center network and designed a system of redundant arrays of inexpensive links to stretched transceivers' reach and reduced the cost by 44%.[37] In 2017, Dr. R. Urata et al. introduced the evolution of Google datacenter network bi-section bandwidth from 1Tbps to 1000Tbps within 8 years and advocated the reduction of power and cost of optical transceivers through further integration within the device. Still, in the same year, X. Zhou et al. from Google gave out a ranked set of criterions: 1. bandwidth cost, 2. power consumption, 3. serviceability, 4. latency. [48]

With the existing literature, there are still a few questions remaining to be answered.

Most of the literatures agree that cost would be the most important metrics but which exact cost is the cost that matters? Is the selling price of the device? What factors other than the manufacturing cost may affect the selling price? When the adoption of different transceiver devices means setting up network topologies differently, should the system setup cost be included? To help different stakeholders communicate efficiently and reach an agreement, a clear definition of cost is necessary.

- 2) How should the trade-offs among different kinds of metrics be evaluated and balanced? By far, there are many metrics that have been put forward, such as various bandwidth cost, power, size, distance, number of wavelengths, number of fibers, reliability, serviceability, scalability and latency. None of the existing solutions dominates in every aspect. To rank different solutions, people need to know an effective way to make trade-offs among different aspects.

- 3) Time should also be an indispensable dimension in the evaluation. In general, time-to-market is a crucial metrics for comparing different goods and studies have been done to balance the trade-off between time-to-market and product performance [38], [39]. In the optical transceiver case, time is as crucial as in general, if not more. Google's data center network bandwidth expands 1000 times within 8 An OFC (the Optical Networking years. and Communication Conference & Exhibition) report also writes that large scale Could Data Center need to upgrade networking hardware every two years [46]. To ensure a smooth large-scale network upgrade, it is critical for data centers to have the optical transceivers ready with the promised cost, performance and quantity on time.

28

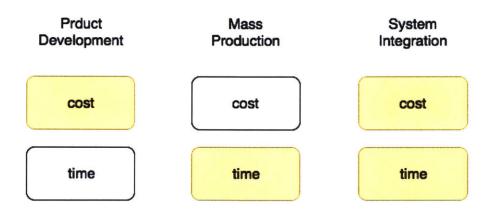

Here I design a systematic techno-economic evaluation framework, in which there are six factors identified as the critical path elements for decision process. Those factors form a two-by-three matrix. The "two" are the two dimensions: cost and time. The "three" are the three phases: product development, mass production and system integration. Taking into account of multiple criteria in decision making, the framework integrates interests of different stakeholders. I hope such a framework can help facilitate communication among different groups and accelerate the resolution of conflicts and disagreements during strategic product planning. In the following chapters, I examine those factors and the interactions among them in detail.

Figure 7 A six-component techno-economic evaluation framework integrating different stakeholders. The white blocks in the figure are factors that have been explored before and are the focus of previous techno-economical evaluations. The yellow blocks in the figure are factors that are often overlooked. [1] D. A. B. Miller, "Device Requirements for Optical Interconnects to Silicon Chips," *Proc. IEEE*, vol. 97, no. 7, pp. 1166–1185, Jul. 2009.

[2] D. T. Neilson, D. Stiliadis, and P. Bernasconi, "Ultra-high capacity optical IP routers for the networks of tomorrow: IRIS Project," in *2005 31st European Conference on Optical Communication, ECOC 2005*, 2005, vol. 5, pp. 45–48 vol.5.

[3] A. V. Krishnamoorthy *et al.*, "Progress in Low-Power Switched Optical Interconnects," *IEEE J. Sel. Top. Quantum Electron.*, vol. 17, no. 2, pp. 357–376, Mar. 2011.

[4] MIT Microphotonics Center, "On-Board Optical Interconnection." Apr-2013.

[5] "The Semiconductor Market: 2015 Performance, 2016 Forecast, and theData to Make Sense of It | SEMI.ORG." [Online]. Available:

http://www.semi.org/en/semiconductor-market-2015-performance-2016-forecastand-data-make-sense-it. [Accessed: 14-May-2018].

[6] "Infonetics: US\$1 Trillion to Be Spent on Telecom and Datacom Equipment and Software Over Next 5 Years." [Online]. Available:

https://finance.yahoo.com/news/infonetics-us-1-trillion-spent-211622815.html.

[Accessed: 14-May-2018].

[7] Amelia.Liu, "How Far Will Copper Network Go," *Fiber Optic Cabling Solutions*, 11-Jun-2013.

[8] "Three trends driving optoelectronics market growth through 2019 | Solid

State Technology." [Online]. Available: http://electroiq.com/blog/2015/06/three trends-driving-optoelectronics-market-growth-through-2019/. [Accessed: 14-May-2018].

[9] C. H. Fine and L. C. Kimerling, "Biography of a Killer Technology," Spec.*Rep. Optoelectron. Ind. Dev. Assoc.*, p. 23, Jun. 1997.

[10] F. Karakaya and M. J. Stahl, "Barriers to Entry and Market Entry Decisions in Consumer and Industrial Goods Markets," *J. Mark.*, vol. 53, no. 2, pp. 80–91, 1989.

[11] X. Zhou, H. Liu, and R. Urata, "Datacenter optics: requirements, technologies, and trends (Invited Paper)," *Chin. Opt. Lett.*, vol. 15, no. 5, p. 120008, May 2017.

[12] M. E. Porter, "Technology and competitive advantage," *J. Bus. Strategy*, vol. 5, no. 3, pp. 60–78, 1985.

[13] C. H. Fine, *Clockspeed: Winning Industry Control in the Age of Temporary Advantage*. ReadHowYouWant.com, 2010.

[14] R. W. Seifert and O. H. Isaksson–October, "The Perks and Pitfalls of Knowledge Diffusion in the Supply Chain," 2013.

[15] G. Tassey, "Standardization in technology-based markets," *Res. Policy*, vol.

29, no. 4–5, pp. 587–602, Apr. 2000.

[16] "Cisco Visual Networking Index: Global Mobile Data Traffic Forecast

Update, 2016–2021 White Paper - Cisco." [Online]. Available:

https://www.cisco.com/c/en/us/solutions/collateral/service-provider/visualnetworking-index-vni/mobile-white-paper-c11-520862.html. [Accessed: 24-May-2018].

[17] "Singularity is Near -SIN Graph - Micro Processor Clock Speed." [Online].

Available: http://www.singularity.com/charts/page61.html. [Accessed: 24-May-2018].

[18] "The Ethernet community is working to introduce six new rates in the next 3 years | Network World." [Online]. Available:

https://www.networkworld.com/article/3060250/lan-wan/the-ethernet-communityis-working-to-introduce-six-new-rates-in-the-next-3-years.html. [Accessed: 24-May-2018].

[19] "Moore's law," Wikipedia. 10-Sep-2017.

[20] T. Simonite, "Intel is putting the brakes on Moore's Law," *MIT Technology Review*. [Online]. Available: https://www.technologyreview.com/s/601102/intel-puts-the-brakes-on-moores-law/. [Accessed: 24-May-2018].

[21] J. Burt, "Memory And Logic In A Post Moore's Law World," 22-Mar-2017.

[Online]. Available: https://www.nextplatform.com/2017/03/22/memory-logic-post-moores-law-world/. [Accessed: 24-May-2018].

[22] A. Canziani, A. Paszke, and E. Culurciello, "An Analysis of Deep Neural Network Models for Practical Applications," *ArXiv160507678 Cs*, May 2016.

[23] S. Miao, K. Hendrickson, and Y. Liu, "Computation of three-dimensional multiphase flow dynamics by Fully-Coupled Immersed Flow (FCIF) solver," *J. Comput. Phys.*, vol. 350, pp. 97–116, Dec. 2017.

[24] J. Nickolls and W. J. Dally, "The GPU Computing Era," *IEEE Micro*, vol.30, no. 2, pp. 56–69, Mar. 2010.

[25] F. Liu, N. Luehr, H. J. Kulik, and T. J. Martínez, "Quantum Chemistry for Solvated Molecules on Graphical Processing Units Using Polarizable Continuum Models," *J. Chem. Theory Comput.*, vol. 11, no. 7, pp. 3131–3144, Jul. 2015.

[26] S. Ghemawat, H. Gobioff, and S.-T. Leung, "The Google File System," in *Proceedings of the Nineteenth ACM Symposium on Operating Systems Principles*, New York, NY, USA, 2003, pp. 29–43.

[27] F. Chang *et al.*, "Bigtable: A Distributed Storage System for Structured Data," *ACM Trans Comput Syst*, vol. 26, no. 2, pp. 4:1–4:26, Jun. 2008.

[28] S. Han, N. Egi, A. Panda, S. Ratnasamy, G. Shi, and S. Shenker, "Network support for resource disaggregation in next-generation datacenters," 2013, pp. 1–7.

[29] B. Abali, R. J. Eickemeyer, H. Franke, C.-S. Li, and M. A. Taubenblatt, "Disaggregated and optically interconnected memory: when will it be cost effective?," *ArXiv150301416 Cs*, Mar. 2015.

[30] Y. Lin, S. Han, H. Mao, Y. Wang, and W. J. Dally, "Deep Gradient

Compression: Reducing the Communication Bandwidth for Distributed Training,"

ArXiv171201887 Cs Stat, Dec. 2017.

[31] "Designing the Flat Data Center Network," *Electronic Component News*, 01-Mar-2011. [Online]. Available:

https://www.ecnmag.com/article/2011/03/designing-flat-data-center-network.

[Accessed: 24-May-2018].

[32] T. Li, "Optical Fiber Communication-The State of the Art," *IEEE Trans.Commun.*, vol. 26, no. 7, pp. 946–955, Jul. 1978.

[33] E. R. H. Fuchs, R. E. Kirchain, and S. Liu, "The Future of Silicon Photonics: Not So Fast? Insights From 100G Ethernet LAN Transceivers," *J. Light. Technol.*, vol. 29, no. 15, pp. 2319–2326, Aug. 2011.

[34] A. Vahdat, H. Liu, X. Zhao, and C. Johnson, "The Emerging Optical Data Center," presented at the Optical Fiber Communication Conference, 2011, p. OTuH2.

[35] D. Mahgerefteh and C. Thompson, "Techno-economic Comparison of Silicon Photonics and Multimode VCSELs," in *Optical Fiber Communication Conference (2015), paper M3B.2*, 2015, p. M3B.2.

[36] A. Chakravarty, K. Schmidtke, S. Giridharan, J. Huang, and V. Zeng, "100G

CWDM4 SMF optical interconnects for facebook data centers," in 2016 *Conference on Lasers and Electro-Optics (CLEO)*, 2016, pp. 1–2.

[37] D. Zhuo *et al.*, "{RAIL}: A Case for Redundant Arrays of Inexpensive Links in Data Center Networks," 2017. .

[38] R. E. Burkart, "Reducing R&D cycle time," *Res. Technol. Manag.*, vol. 37, no. 3, p. 27, Jun. 1994.

[39] M. A. Cohen, J. Eliashberg, and T.-H. Ho, "New Product Development: The Performance and Time-to-Market Tradeoff," *Manag. Sci.*, vol. 42, no. 2, pp. 173–186, 1996.

[40] "Cloud Data Center Evolution - From 0 to 400G | OFC." [Online].

Available: https://www.ofcconference.org/en-us/home/about/ofc-

blog/2017/november/cloud-data-center-evolution-from-0-to-400g/. [Accessed: 08-May-2018].

## Chapter 2 Intra-datacenter Transceiver Designs Optical Transceivers

An optical transceiver is a device that sends and receives data using optical fiber rather electrical wire. The device is usually composed of two parts: a transmitter that converts electrical signals into optical signals before transmitting data and a receiver that converts optical signals back to electrical signals after receiving data. The transmitter requires a modulated light source, an electrical IC block that drives the light source or the modulator. The receiver requires a photodetector, an electrical IC block that turns current signals to voltage signals (e.g. transimpedance amplifiers) and an electrical IC block that converts analog signals into digital signals (post amplifiers). Besides, for high speed signals (e.g. 25G per channel), there are also extract timing information clock and data recovery blocks to and serializer/deserializer blocks to compensate for limited input/output. For even higher speeds (e.g. 100G per channel), digital signal processing blocks for signal modulation (e.g. PAM4) are needed. Those are the main functional blocks. To make them work together as a device, there are additional electrical interconnect components (e.g. printed circuit board and bonding wires) and optical alignment components (micro-lens, optical benches, and mechanical housings).

Extrinsically, there are multiple ways to categorize optical transceivers, such as applications, protocols, number of fibers, data rate, distance, size etc. Intrinsically, optical transceivers come with different kinds of designs. I pick out six representative designs of intra-data center optical transceivers and describe them in the following sections.

# Transceiver design 1: optical sub-assembly optical transceivers

The optical sub-assembly optical transceivers are the most traditional designs of optical transceivers. The optical and mechanical components are mainly separate parts. Those nonintegrated parts are relatively large in size but have good and reliable technical performance.

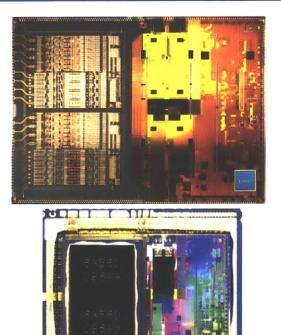

Figure 8 A optical sub-assembly optical transceiver from Finisar [2]

#### Transceiver design 2: hybrid silicon photonics transceivers

Silicon photonics is a newly emerged disruptive technology in the field of optical transceivers. There are one or several electronic dies, a photonic die and a micro-optics bench in a hybrid silicon photonics transceiver. Functionally, the electronic dies here are similar to the electronic dies in the transceiver design one. The photonic die includes modulators, photodetectors and waveguides except the optical light source. The micro-optics bench sub-assembly contains the light source, a laser chip.

A hybrid silicon photonics transceiver replaces part of the discrete optical components in optical sub-assembly optical transceivers with a silicon photonic die.

There are both upsides and downsides from that integration. The upsides include reducing the number of discrete components, shrinking the size, and shortening the interconnection distance. In the meantime, the partial on-chip integration brings difficulty for optical alignment between the chip and non-integrated optical parts because 1) the mismatch between the scale of a chip waveguide (~1 micron) and the scale of discrete parts such as micro-optics bench and optical fibers (~100 microns); 2) the planar integration on a chip breaks the axial symmetry and thus requires controlling six degrees of freedoms in the alignment. The alignment is so challenging that there is an additional ~6dB optical loss when light is coupled in and out of the photonic chip.

In addition, the integration is a partial integration because the light source is still off the chip and depends on micro-optics assembly. The size of the light source remains relatively large and thus currently only one light source can be hosted on top of the photonic chip. That gives difficultly to realize the traditional wavelength multiplexing on such a platform and thus the spatial multiplexing MSA (Multi-Source Agreement) PSM4 (Parallel Single Mode fiber 4-lane) is developed, in which there are four fiber lanes, one for each channel and all carrying the same wavelength signal. Besides, the laser output power needs to four times that the required input power for each lane. The integration upside wins over those downsides for coherent optical transceivers which involves complex optical designs but may not compensate the downsides for noncoherent single-channel optical transceivers whose optical designs are simple. [3]

# Transceiver IC Example 2: Hybrid Si P @200 Gbps

#### Electronic die (not shown)

- TSMC N28HPM technology

- E-interface with programmable signal conditioning and by-passable CDR

- BIST capabilities

- 2 wire communication

- Laser driver

- MZI drivers & TIAs

- Digital core for control and communications

#### Photonic die (500 photonic devices)

- MZI modulators

- · Ge high-speed photo-detectors

- Ge monitor photo-detectors for control and monitoring

- BIST capability

- Photonics assembly & sort features

LUXTERA

Figure 9 A hybrid silicon photonics transceiver from Luxtera

Transceiver design 3: hybrid silicon photonics transceivers with chip-bonded lasers The design also applies a silicon photonic chip to replace part of the discrete optical parts. The difference is that the light source is a laser chip bonded on the silicon photonic chip instead of a micro-optics bench packaged laser chip. It further removes the need of optical lens and mechanical cages for aligning the laser to the silicon photonic chip and thus shrinks the size of the light source. Different from the design 2, in which only one light source can be hosted on the silicon photonic chip, design 3 is able to host multiple light sources on one silicon photonic chip. A design 3 100G transceiver can be either wavelength multiplexing or spatial multiplexing.

Transceiver design 4: single-chip silicon photonics transceivers with off-chip lasers

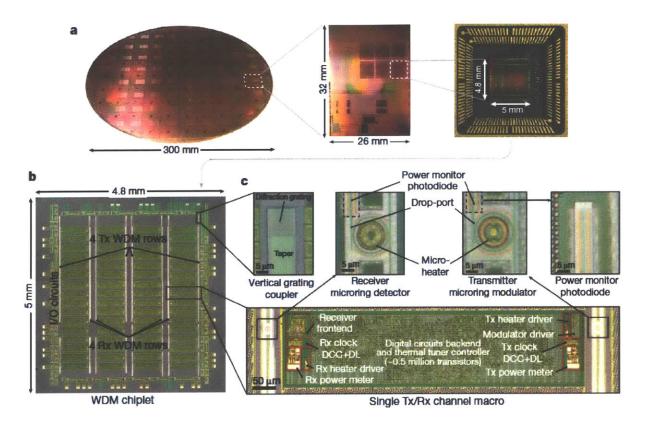

Figure 10 A single-chip silicon photonics transceiver [4], [5]

The design integrates both the photonic part and the electronic part onto the same chip except that it leaves the laser light source off the chip. On the chip, the light is traveling in the waveguides. Off the chip, the light is traveling in single-mode fibers. The light is coupled into and out of the chip through vertical grating couplers. The electronic part here includes not only the functional electronic blocks that processes the electro-optical and optical-electrical conversion but also the logical computing units. The design moves the photonic components close to the logic units and offers one tenth of the latency of those hybrid designs. The same structure has been demonstrated to realize chip-to-chip optical communications. However, currently the short latency feature is not yet highly valued by intra-data center network interconnects.

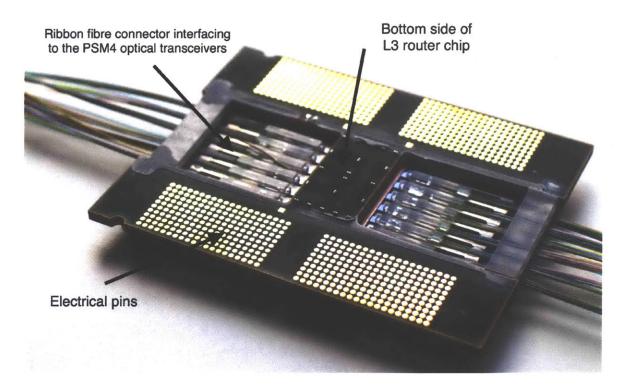

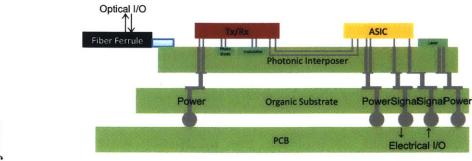

# Transceiver design 5: on-board optics

Figure 11 An in-packaged optics design from Rockley Photonics [6]

The on-board optics design targets to resolve the bandwidth density bottleneck on the network switch faceplate. Instead of innovating individual optical transceivers, the design mainly focuses on the system design that it moves optical transceivers onto the same board with the network switching chip.

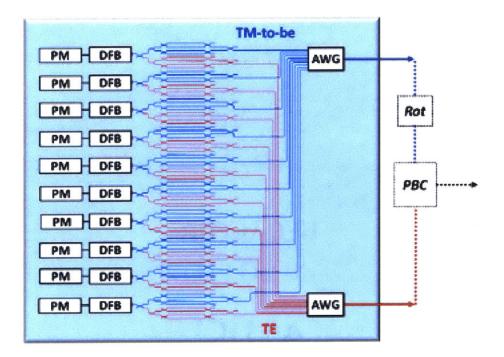

### Transceiver design 6: Indium-phosphide integrated optical transceivers

The design utilizes the indium-phosphide substrate instead of silicon for integrating both the light source and the other photonic functions onto the same chip. The electronic blocks are separate silicon chips. The main challenge is that the manufacturing yield on the Indium-phosphide platform is low, which limits the level of integration on a single Indium-phosphide chip.

Figure 12 A 500G PIC (photonics integrated circuit chip) from Infinera [7]

L. A. Barroso, J. Clidaras, and U. Hoelzle, *The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines*. Morgan & Claypool, 2013.

[2] "defa14a." [Online]. Available:

https://www.sec.gov/Archives/edgar/data/1094739/000095013404013944/f01954a ldefa14a.htm. [Accessed: 08-May-2018].

[3] C. Doerr *et al.*, "Single-chip silicon photonics 100-Gb/s coherent transceiver," in *OFC 2014*, 2014, pp. 1–3.

[4] C. Sun *et al.*, "Single-chip microprocessor that communicates directly using light," *Nature*, vol. 528, no. 7583, pp. 534–538, Dec. 2015.

[5] A. H. Atabaki *et al.*, "Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip," *Nature*, vol. 556, no. 7701, pp. 349–354, Apr. 2018.

[6] "Gazettabyte - Home - Rockley Photonics showcases its in-packaged design at OFC." [Online]. Available:

http://www.gazettabyte.com/home/2018/3/15/rockley-photonics-showcases-its-inpackaged-design-at-ofc.html. [Accessed: 08-May-2018].

[7] F. Kish, "500Gb/s and Beyond PIC-Module Transmitters and Receivers," in *Optical Fiber Communication Conference (2014), paper W3I.1*, 2014, p. W3I.1.

[8] T. Li, "Optical Fiber Communication-The State of the Art," *IEEE Trans.Commun.*, vol. 26, no. 7, pp. 946–955, Jul. 1978.

[9] D. T. Neilson, D. Stiliadis, and P. Bernasconi, "Ultra-high capacity optical IP routers for the networks of tomorrow: IRIS Project," in *2005 31st European*

*Conference on Optical Communication, ECOC 2005*, 2005, vol. 5, pp. 45–48 vol.5.

[10] E. R. H. Fuchs, R. E. Kirchain, and S. Liu, "The Future of Silicon Photonics: Not So Fast? Insights From 100G Ethernet LAN Transceivers," *J. Light. Technol.*, vol. 29, no. 15, pp. 2319–2326, Aug. 2011.

[11] A. Vahdat, H. Liu, X. Zhao, and C. Johnson, "The Emerging Optical Data Center," in *Optical Fiber Communication Conference/National Fiber Optic Engineers Conference 2011 (2011), paper OTuH2*, 2011, p. OTuH2.

[12] MIT Microphotonics Center, "On-Board Optical Interconnection." Apr-2013.

[13] D. Mahgerefteh and C. Thompson, "Techno-economic Comparison of Silicon Photonics and Multimode VCSELs," in *Optical Fiber Communication Conference (2015), paper M3B.2*, 2015, p. M3B.2.

[14] A. Chakravarty, K. Schmidtke, S. Giridharan, J. Huang, and V. Zeng, "100G

CWDM4 SMF optical interconnects for facebook data centers," in 2016 *Conference on Lasers and Electro-Optics (CLEO)*, 2016, pp. 1–2.

[15] D. Zhuo *et al.*, "{RAIL}: A Case for Redundant Arrays of InexpensiveLinks in Data Center Networks," 2017. .

[16] X. Zhou, H. Liu, and R. Urata, "Datacenter optics: requirements, technologies, and trends (Invited Paper)," *Chin. Opt. Lett.*, vol. 15, no. 5, p. 120008, May 2017.

[17] "Cloud Data Center Evolution - From 0 to 400G | OFC." [Online].

Available: https://www.ofcconference.org/en-us/home/about/ofcblog/2017/november/cloud-data-center-evolution-from-0-to-400g/. [Accessed: 08-May-2018].

# Chapter 3 Cost and Time for Product Development

# Product development

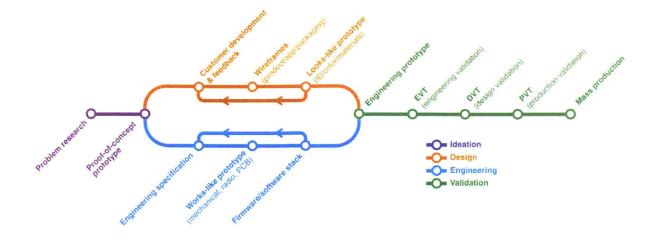

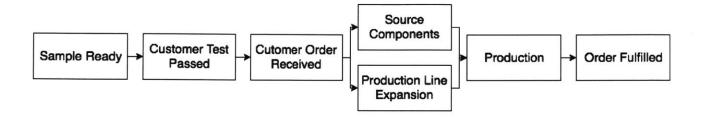

Product development is the set of activities beginning with the perception of a market opportunity and ending in the production, sale, and delivery of a product. The general product development process is usually composed of six phases: planning, concept development, system-level design, detail design, testing and refinement and production ramp-up. [1] For a hardware product, although the exact process may vary from company to company and from product to product, the following stream of activities is usually shared:

- 1) brainstorm & proof-of-concept prototype,

- 2) engineering validation test (EVT),

- 3) design validation test (DVT),

- 4) production validation test (PVT),

- 5) mass production (MP).

Figure 13 Hardware product development process [2]

During the brainstorm and proof-of-concept prototype phase, ideas are generated and the promising ones are selected for further engineering and design. During EVT, 20~50 units with the major targeting functions, production intent materials and manufacturing processes are built and tested. The product development team can show those EVT builds to potential users and learn new requirements and feedbacks from users. For example, the transceiver samples and demos shown at OFC conference are sometimes such EVT builds. During DVT, a production environment should be in place and build 50~200 units for battery stress and regulatory testing. During PVT, 500 to thousands of units that can be sold to customers are built to finalize the tools and manufacturing processes. Right after PVT, the first full production run can be carried out to meet the minimum order quantity of most customers. During mass production, continuous efforts are made on improving the yield, qualifying new vendors and optimizing the supply chain. [3][4]

#### Duration and cost of product development

The duration of product development ranges from 1 year to 10 years. In terms of the production itself, the product development time depends on the product complexity, the sales lifetime and the product update cycle. In addition, it depends on the development team size and the development investment.

The cost of product development is often called as non-recurring engineering (NRE) cost. There are mainly two parts of spending. The first part is the spending on the engineering efforts, which are roughly proportional to the number of people on the project team and to the duration of the project. The second part is the investment in the tooling and equipment required for production, which is commonly taken as a fixed cost item in the production cost for in-house manufacturing. Usually, the development cost and the production investment are roughly the same.

|            | Ice Cream  | Avalanche  | HP         | Tesla      | Boeing 787 |

|------------|------------|------------|------------|------------|------------|

|            | Scoop      | Probe      | Laserjet   | Model S    |            |

|            |            |            | Printer    |            |            |

| Annual     | 10,000     | 1000       | 4 million  | 50,000     | 120        |

| production | units/year | units/year | units/year | units/year | units/year |

| volume     |            |            |            |            |            |

| Sales       | 10 years  | 3 years     | 2 years      | 5 years   | 40 years     |

|-------------|-----------|-------------|--------------|-----------|--------------|

| lifetime    |           |             |              |           |              |

| Sales price | \$40      | \$2,250     | \$130        | \$80,000  | \$250        |

|             |           |             |              |           | million      |

| Development | 1 year    | 2 years     | 1.5 years    | 3.5 years | 7 years      |

| time        |           |             |              |           |              |

| Peak team   | 6 people  | 18 people   | 175 people   | 2000      | 17,000       |

| size        |           |             |              | people    | people       |

| Development | \$100,000 | \$1 million | \$50 million | \$500     | \$15 billion |

| cost        |           |             |              | million   |              |

| Production  | \$20,000  | \$250,000   | \$25 million | \$500     | \$15 billion |

| investment  |           |             |              | million   |              |

Table 3 Attributes of five products and their associated development efforts. [1],

# [5]

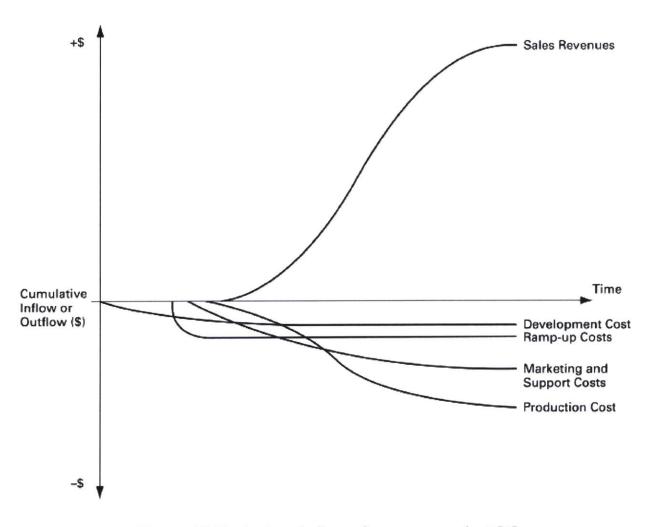

If we decompose the duration and cost of product development into different stages. The figure below presents the cumulative cash inflow and outflow over the life cycle of a typical successful product.

Figure 14 Typical cash flows for a new product [1]

# Bottlenecks of optical transceiver product development

At the downstream of optical transceiver products, due to network system design uncertainties, it is very challenging for optical transceiver manufacturers to focus on one design in the early stage of product development. Optical transceivers are components of intra-datacenter networks. Its specification depends on the intra-

datacenter network system specifications. Optical transceiver manufacturers need to wait for IEEE 802.3 standards to know the desired technical requirements for the optical transceiver from the network system perspective. However, the standardmaking process involves a lot of negotiation from different parties and takes long. For example, the IEEE P802.3ba task force for 40G and 100G ethernet started in December 2007 and completed in June 2010. In addition, many important aspects including form factors are left unspecified. Several multi-source agreements (MSA), e.g. CFP, PSM4, CWDM, QSFP-DD et al., are needed to shorten the waiting of IEEE standards and fill in the gaps of technical specifications. That brings a new problem: there are many variations of standards for one application. Last but not the least, customers may alter the requirements for their own economic benefits. For example, for 100G intra-datacenter optical transceivers, Facebook has relaxed several specifications including reducing the operating case temperature to 15-55°C, reducing the distance requirements from 2km to 500m, and eased specifications on product lifetime. [6] Due to network system design uncertainties, it is very challenging for optical transceiver manufacturers to focus on one configuration in the early stage of optical transceiver product development. A common practice is that optical transceivers deliver EVT samples to customers to avoid spending on PVT and ramp-up for unsuccessful products. However, that practice makes customers to wait for PVT and production ramp-up in addition to normal order lead time.

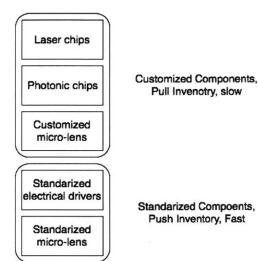

At the upstream of optical transceiver products, many optical transceiver components are made-to-order goods that cannot be purchased off-the-shelf. Those components need to be sourced from vendors or ordered from contract manufacturers. Sometimes they even require significant amount of engineering and design efforts from upstream vendors. For example, many optical transceiver companies rely on other companies' supply of lasers and those lasers are made-to-order products. That creates three challenges in the product development of optical transceivers: 1. the optical transceiver design is constrained by the availability of desired components; 2. both the product development and the mass production is commonly delayed by the supply of components.

| Component               | Order lead time    |  |  |

|-------------------------|--------------------|--|--|

| lasers                  | $6 \sim 12$ months |  |  |

| (made-to-order)         |                    |  |  |

| silicon optical benches | $\sim$ 3 months    |  |  |

| (made-to-order)         |                    |  |  |

| photonic chips          | $6 \sim 18$ months |  |  |

| (made-to-order)       |                  |

|-----------------------|------------------|

| electrical chips      | $2 \sim 3$ weeks |

| (off-the-shelf)       |                  |

| electrical chips      | 6 months         |

| (made-to-order)       |                  |

| optical lenses        | ~ 1 month        |

| (made-to-order)       |                  |

| lensed fibers         | ~ 1 month        |

| (made-to-order)       |                  |

| printed circuit board | ~1 month         |

|                       |                  |

Table 4 Estimated order lead time for optical transceiver components

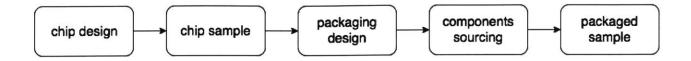

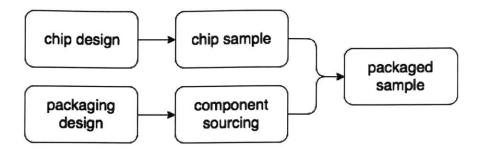

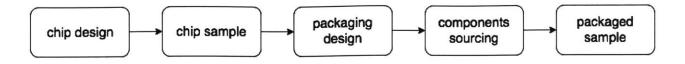

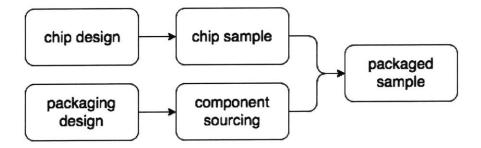

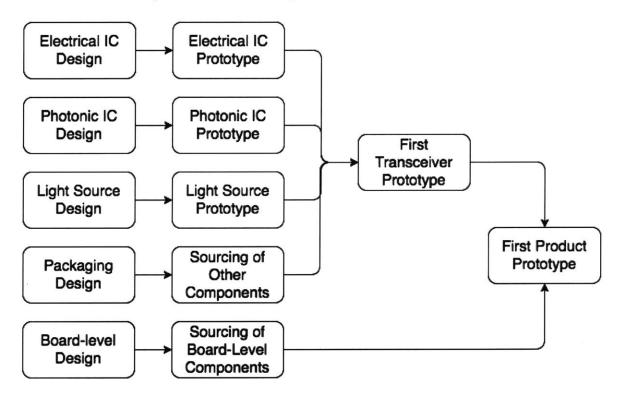

There are also bottlenecks in the ordering of the process flow. Optical transceivers are usually composed of several functional blocks and several components, which require electrical, optical and mechanical engineering and designs. For optical subassembly transceiver products, the product development is decomposed into parallel stages of work on different subsystems and component. For integrated design products, because the integrated chip design is so novel that the full product development won't start until the success of the chip, the product development is a sequential engineering process, which starts with chip design and test, followed by packaging design.

Because of the lack of consideration of component integration in the early stage, the sequential engineering method caused a few problems in the following packaging steps which could have been avoided with little cost in the chip design. For example,

- there was not enough space reserved on chip for optical alignment fixture;

- the optical input and output directions didn't match;

- the spacing between optical channels were too dense.

Now the situation has improved a lot. Packaging research groups are becoming involved in the chip design stage. Also, chip foundries and packaging service providers are designing packaging standards and advocating the adoption of such standards. The concurrent engineering of chip and packaging becomes more and more common.

#### R&D time estimation methodologies

In fast cycle industries, in which product life cycles are often three years or less, rapid product development is widely viewed as a key source of competitive edge. Datar et al. concluded that lead-time advantage affects market share positively. [1] Cohen et al. studied the trade-off between the performance and time-to-market in new product development. [2] Research efforts have also been made on developing models to estimate the product development time. Bashir et al. developed a parametric model to estimate the design hours (E) based on product complexity (PC) and severity of requirements (SR), in which

$$E = aPC^{b}SR^{c}.$$

The a, b and c are company-specific coefficients. Johnson et al. divided the product development into four stages: detailed design, formability engineering, fabrication engineering and assembly engineering. [3] For each stage, the development lead time (ST) is estimated by required design efforts in man-hours for component for a given component x (TDH<sub>x</sub>), the total number of engineers available (TEA), the

maximum development effort required for one component (MEPC) and work hours per week.

$$ST in weeks = \frac{\max\left(\frac{\sum_{x} TDH_{x}}{TEA}, \max(TDH_{x}) / MEPC\right)}{work hours per week}$$

### R&D cost estimation methodologies

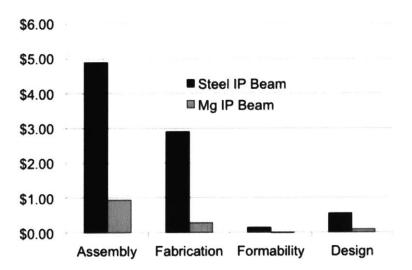

Johnson et al. compared the development cost of two car component designs, a tube-based steel design and a die-cast magnesium design, by calculating the labor and IT cost of design efforts in man hours and the manufacturing cost of prototypes[4] in different stages of product development.

Fig. 6. Unit development costs for alternative IP beam designs at 75,000 units per year.

$$C_{R\&D} = (W_{engineer} + P_{software} + P_{computer}) * T_{Design} + C_{prototype}$$

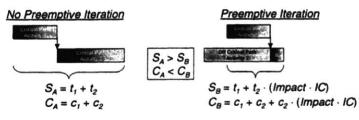

Browning et al. estimated the new product development cost of five different product designs of uninhabited aerial vehicle through design structure matrix[5]. The study assumes different sequences of product development activities for different product architectures. The design structure matrix is used to map the correlation between different activities and estimate the probability and intensity of rework a previous step.

Figure 11: Effect of Preemptive Iteration on Cost and Schedule

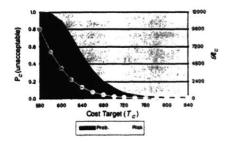

Figure 12: Pc(unacceptable) and Rc for Various Cost Targets (Tc)

#### Status of Optical Transceiver R&D

For optical transceivers, the product development process varies. In a few cases that Tyndall National Institute was facing, the process started with chip design, followed by packaging design.

Due to the lack of consideration of integration in the early stage, the sequential engineering method caused a few problems in the following packaging steps which could have been avoided with little cost in the chip design. For example, there was not enough space reserved on chip for optical alignment fixture; the optical input and output directions didn't match; the spacing between optical channels were too dense.

Now the situation has improved a lot. Packaging research groups are becoming involved in the chip design stage. Also, chip foundries and packaging service providers are designing packaging standards and advocating the adoption of such standards. The concurrent engineering of chip and packaging becomes more and more common.

Still, even in the concurrent engineering scenario, there are two known time bottlenecks:

waiting for MPW run,

waiting for customized components for packaging.

$$T_{R\&D} = \max(T_{chipdesign} + T_{chipmake}, T_{packagingdesign} + T_{componentsourcing})$$

$$+ T_{packagingmake}$$

$$T_{chipmake} = T_{waitforMPWrunstart} + T_{MPWrun}$$

(Time from design to prototype product when there is no re-engineering.)

Standardization is not only an enabler of concurrent engineering of chip design and packaging design but also reduces the need of customized components and thus shorten the waiting time.

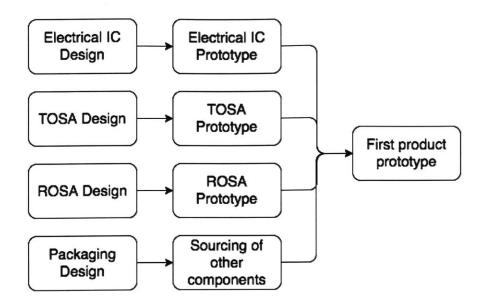

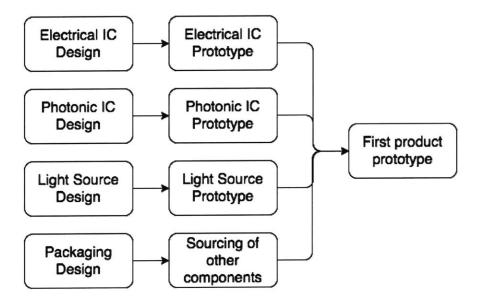

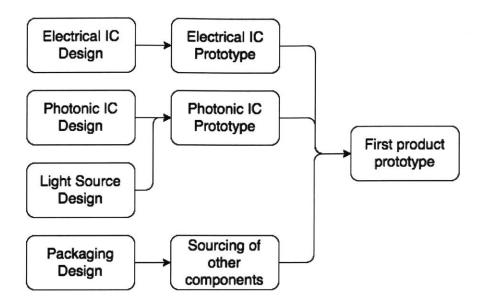

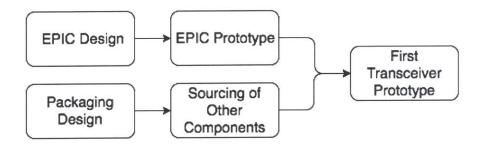

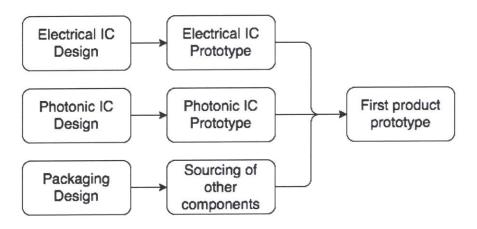

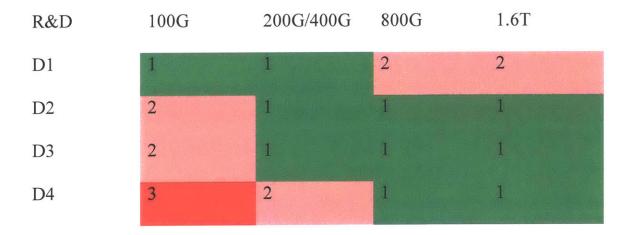

Comparison among different transceiver designs

Transceiver Design 1 - Optical sub-assembly optical transceivers

Rate limiting factor: TOSA design or Packaging design

Transceiver Design 2 - Silicon photonics transceivers with a micro-optics bench

Rate limiting factor: photonic IC prototype or sourcing of other components Transceiver Design 3 - Silicon photonics transceivers with hybrid silicon lasers

Rate limiting factor: photonic IC prototype/sourcing of other components

Transceiver Design 4 - On-board Optics

Transceiver Design 5 - Silicon photonics transceivers with off-chip lasers

Rate limiting factor: EPIC design

Transceiver Design 6 - Indium-phosphide integrated optical transceivers

Rate limiting factor: photonic IC prototype

Ranking of prototype announcement speed (100G, 200G/400G, news stats. 800G, 1.6T assumption)

[1] K. T. Ulrich and S. D. Eppinger, *Product design and development*. New York, NY : McGraw-Hill Education, [2016], 2016.

[2] B. Einstein, "The Illustrated Guide to Product Development (Part 1: Ideation)," *Bolt Blog*, 20-Oct-2015. [Online]. Available: https://blog.bolt.io/theillustrated-guide-to-product-development-part-1-ideation-ab797df1dac7.

[Accessed: 09-May-2018].

[3] I. Instrumental, "Hardware engineers speak in code: EVT, DVT, PVT decoded," *Instrumental*, 09-May-2018. [Online]. Available:

https://www.instrumental.com/blog/2016/11/14/hardware-engineers-speak-in-code-evt-dvt-pvt-decoded. [Accessed: 10-May-2018].

[4] B. Einstein, "The Illustrated Guide to Product Development (Part 4: Validation)," *Bolt Blog*, 20-Oct-2015. [Online]. Available: https://blog.bolt.io/theillustrated-guide-to-product-development-part-4-validation-1b5ab3aeaf35.

[Accessed: 10-May-2018]. [5] K. T. Ulrich and S. D. Eppinger, *Product Design and Development, 5th Edition*, 5 edition. New York: McGraw-Hill Education, 2011.

[6] A. Chakravarty, K. Schmidtke, S. Giridharan, J. Huang, and V. Zeng, "100GCWDM4 SMF optical interconnects for facebook data centers," in 2016

Conference on Lasers and Electro-Optics (CLEO), 2016, pp. 1–2.

[7] L. A. Barroso, J. Clidaras, and U. Hoelzle, *The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines*. Morgan &

Claypool, 2013.

[8] "defa14a." [Online]. Available:

https://www.sec.gov/Archives/edgar/data/1094739/000095013404013944/f01954a 1defa14a.htm. [Accessed: 08-May-2018].

[9] C. Doerr *et al.*, "Single-chip silicon photonics 100-Gb/s coherent transceiver," in *OFC 2014*, 2014, pp. 1–3.

[10] C. Sun *et al.*, "Single-chip microprocessor that communicates directly using light," *Nature*, vol. 528, no. 7583, pp. 534–538, Dec. 2015.

[11] A. H. Atabaki *et al.*, "Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip," *Nature*, vol. 556, no. 7701, pp. 349–354, Apr. 2018.

[12] "Gazettabyte - Home - Rockley Photonics showcases its in-packaged design at OFC." [Online]. Available:

http://www.gazettabyte.com/home/2018/3/15/rockley-photonics-showcases-its-in-packaged-design-at-ofc.html. [Accessed: 08-May-2018].

[13] F. Kish, "500Gb/s and Beyond PIC-Module Transmitters and Receivers," in *Optical Fiber Communication Conference (2014), paper W3I.1*, 2014, p. W3I.1.

[14] T. Li, "Optical Fiber Communication-The State of the Art," *IEEE Trans.Commun.*, vol. 26, no. 7, pp. 946–955, Jul. 1978.

[15] D. T. Neilson, D. Stiliadis, and P. Bernasconi, "Ultra-high capacity optical IP routers for the networks of tomorrow: IRIS Project," in 2005 31st European Conference on Optical Communication, ECOC 2005, 2005, vol. 5, pp. 45–48 vol.5.

[16] E. R. H. Fuchs, R. E. Kirchain, and S. Liu, "The Future of Silicon Photonics: Not So Fast? Insights From 100G Ethernet LAN Transceivers," *J. Light. Technol.*, vol. 29, no. 15, pp. 2319–2326, Aug. 2011.

[17] A. Vahdat, H. Liu, X. Zhao, and C. Johnson, "The Emerging Optical Data Center," in *Optical Fiber Communication Conference/National Fiber Optic Engineers Conference 2011 (2011), paper OTuH2*, 2011, p. OTuH2.

[18] MIT Microphotonics Center, "On-Board Optical Interconnection." Apr-2013. [19] D. Mahgerefteh and C. Thompson, "Techno-economic Comparison of Silicon Photonics and Multimode VCSELs," in *Optical Fiber Communication Conference (2015), paper M3B.2*, 2015, p. M3B.2.

[20] D. Zhuo *et al.*, "{RAIL}: A Case for Redundant Arrays of InexpensiveLinks in Data Center Networks," 2017. .

[21] X. Zhou, H. Liu, and R. Urata, "Datacenter optics: requirements, technologies, and trends (Invited Paper)," *Chin. Opt. Lett.*, vol. 15, no. 5, p. 120008, May 2017.

[22] "Cloud Data Center Evolution - From 0 to 400G | OFC." [Online].

Available: https://www.ofcconference.org/en-us/home/about/ofc-

blog/2017/november/cloud-data-center-evolution-from-0-to-400g/. [Accessed: 08-May-2018].

# **Chapter 4 Cost and Time for Mass Production**

Prior to the current PSMC effort, there have been relatively few published (i.e. publicly available) cost analysis studies that focused on the manufacturing of integrated photonics.

In the earliest such study, Schuelke and Pande analyzed the manufacturing cost of an optoelectronic integrated circuit chips based on a cost model developed for millimeter and microwave integrated circuits.[6] Specifically, they examined the economics of integrated four core functions (detection, preamplification, amplification & filtering, and decision making) into a single GaAs chip. Their conclusion was that integrating only two of the four functions was economically preferred because of decreases in net yield as the circuit grows in size and complexity. Marz et al. established an analytical model to estimate the relative yields and the relative costs over time of integrated optical chips to a reference chip.[7] Their detailed model would allow decision makers to estimate how costs might be expected to change with integration and therefore optimize current levels of integration. As presented this model depends on the costs of an existing reference chip. As mentioned by the authors, to be complete, the scope of the model would need to be expanded to consider packaging and assembly of the complete module. An acitivity-based cost model is applied by Stirk et al. to calculate the cost of a 2-D

VCSEL array communication module.[8] Although few details of the model are provided, this analysis makes clear that assembly yield is a critical aspect of ultimate module cost.

More recently, the research team at MIT built upon these various earlier studies. Specifically, Kirchain, Fuchs et al. from MIT Materials System Laboratory developed a process-based cost model (PBCM) with data collected from numerous firms across the optoelectronics supply chain covering front end, back end and packaging. This model allows for the user to specify the process flow, individual processing conditions, operational characteristics, and level of automation at each step.

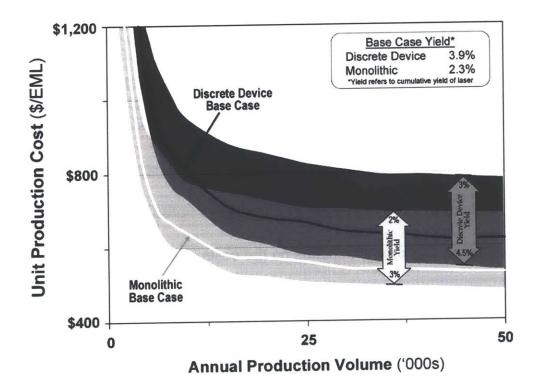

Figure 15. Cost sensitivity of production volume analysis of monolithic and discrete integration of InP-based DFB laser and EA modulator.

With the PBCM tool, the cost of integration of a 1550-nm DFB laser with an electroabsorptive (EA) modulator on an InP platform was analyzed.[9] The results suggest that a monolithically integrated design should be more cost competitive over a discrete component options regardless of production scale (see Figure 15) unless the integrated yield is particularly poor. The research also identified the dominant cost drivers as packaging, testing, and assembly - the focus of current PSMC cost modeling activities. Besides, component alignment, bonding, and metal-organic chemical vapor deposition (MOCVD) are identified as processes where technical improvements were most critical to lowering costs. It is estimated that economies of scale for manufacturing the components occurred between 30,000 and 200,000 units/year, depending on the type and complexity of the device being evaluated, which encourages photonic industry to consolidate its manufacturing sites in order to achieve economies of scale.

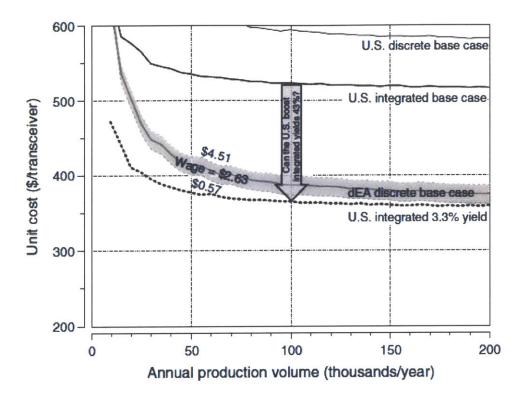

In a subsequent study[10], the optoelectronics PBCM model was applied to model transmitter designs with a Discrete Laser and Modulator (Prevailing Design) and an Integrated Laser and Modulator (Emerging Design) and study the impact of off-

shore manufacturing on optoelectronics. It was found that the economics of offshore production increases the cost advantage of the prevailing technology and therefore reduces incentives for innovation (see Figure 16).

Figure 16. Cost competitiveness of U.S.-produced integrated laser modulator vs. developing east asia (dEA)-produced discrete laser and modulator design.

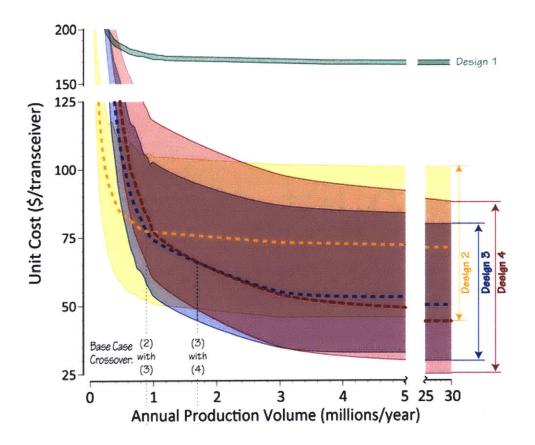

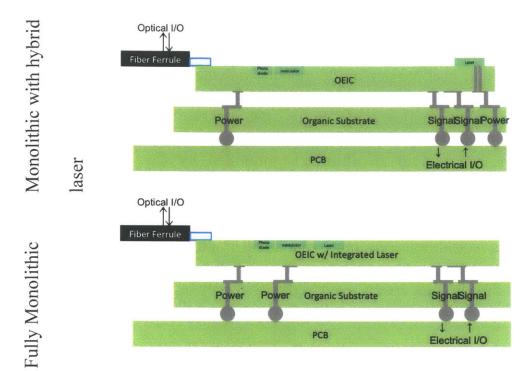

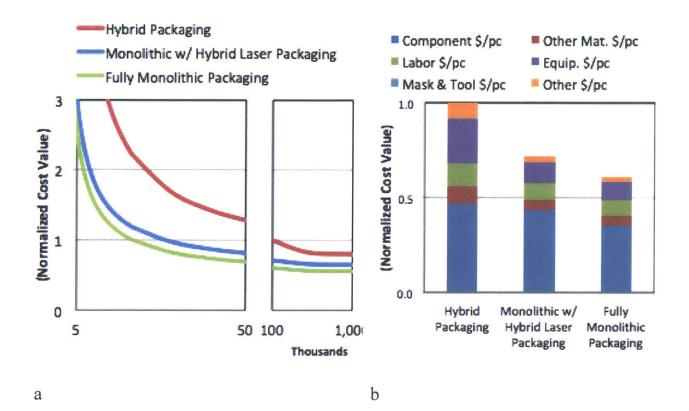

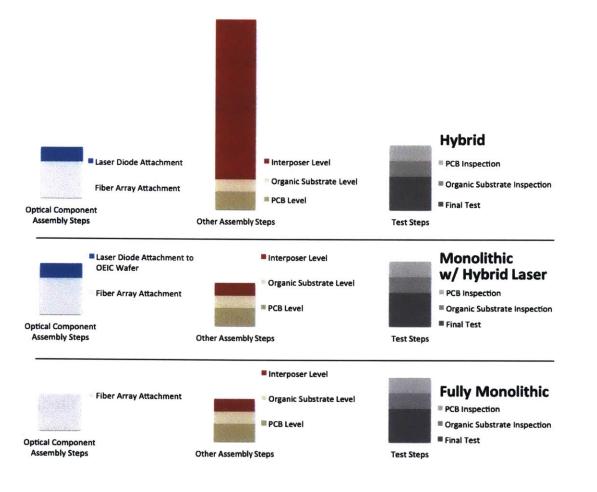

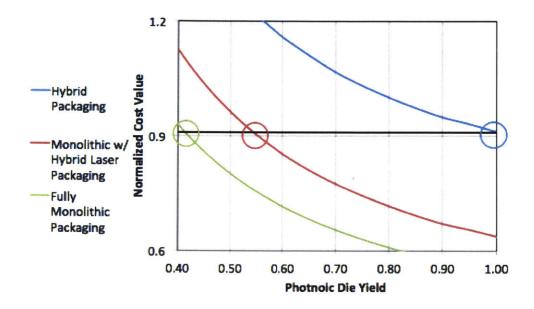

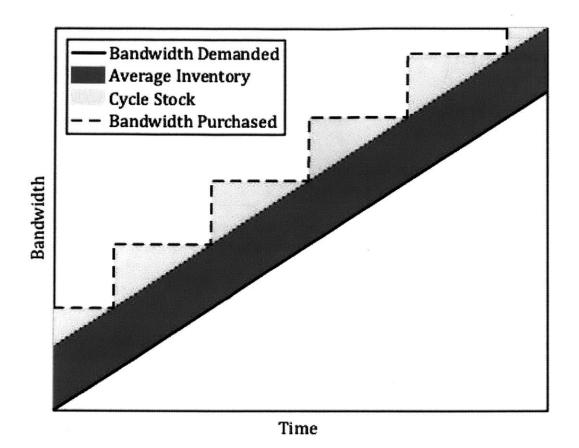

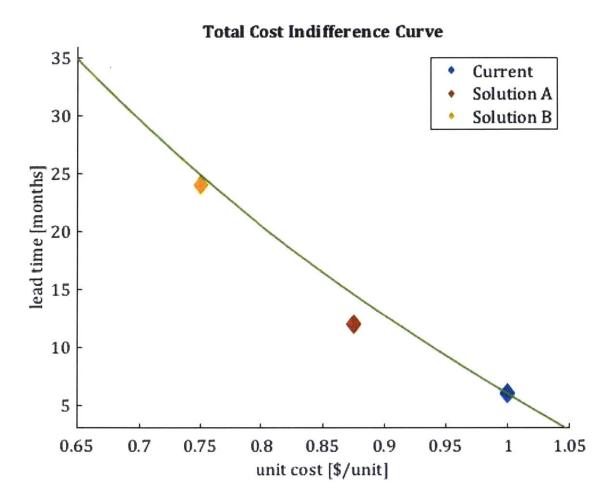

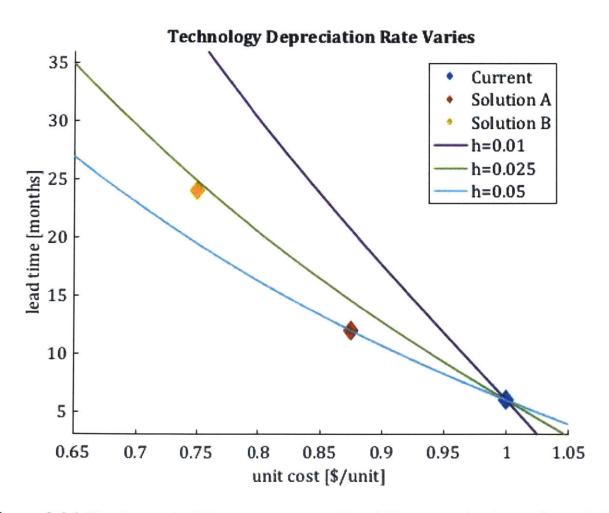

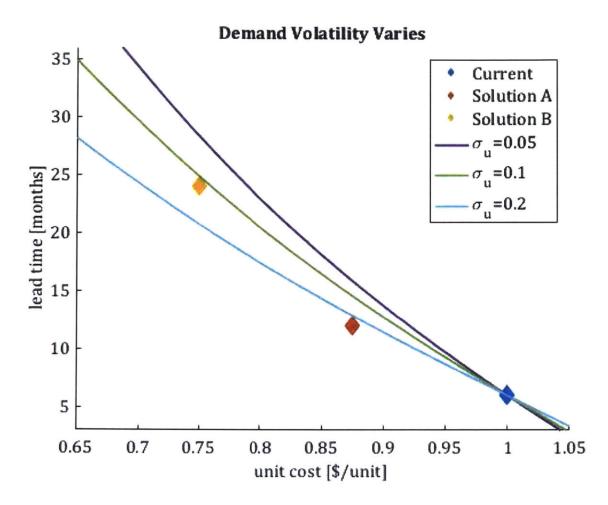

Finally, in a third study[11], the MIT research team explored the competitiveness of two Si photonic designs against InP-based alternatives for a 1310 nm, 100 gigabit ethernet LAN transceiver. The research suggested great promise for silicon photonics to meet cost targets in midterm server and storage area network applications and to provide even lower cost devices for future, high-volume consumer and mobile computing applications. Specifically, it was found that silicon photonics holds great potential to be cost competitive in markets with annual sales volumes above 900 000, including servers, computing, and mobile devices (see Figure 17). These results should motivate academic research into integration on the Si substrate from the perspective of cost.