# LABORATORY FOR COMPUTER SCIENCE (formerly Project MAC)

// MIT/LCS/TR-189

24

FORMAL SPECIFICATIONS FOR PACKET COMMUNICATION SYSTEMS

18 David J. Ellis

#### MIT/LCS/TR-189

Bally for the second own of the Paris for

#### FORMAL SPECIFICATIONS FOR PACKET COMMUNICATION SYSTEMS

by

DAVID J ELLIS

November, 1977

lang kan salah kelalan di kelalan bermalah menjadi belah di kelalah di kelalah di kelalah di kelalah di kelala Permajan bermanan di kelalah di k

医囊皮囊 化多极管 医自己性 海 经净额 医电影医路影

The state of the s

This research was supported by the National Science Foundation under grant DCR75-04060 and by the Advanced Research Projects Agency of the Department of Defense, monitored by the Office of Maxel, Research under constact no. N00014-75-C-0661.

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

LABORATORY FOR COMPUTER SCIENCE (formerly Exoject MAC)

CAMBRIDGE

**MASSACHUSETTS**

#### FORMAL SPECIFICATIONS FOR PACKET COMMUNICATION SYSTEMS

рЛ

#### DAVID J ELLIS

Submitted to the Department of Electrical Engineering and Computer Science on October 25, 1277 in partial Engineering and Computer Science of October 25 the Degree of Dector of Philosophy.

#### Abstract

One of the most difficult tasks facing computer scientists is that of designing systems and making sure that they perform their intended functions correctly. As computer systems have grown in size and complexity, the problems of system design and varification have become increasingly acute. Formal specifications, which are precise descriptions of a system's function, provide a basis for understanding system operation as well as for proving correctness.

Although there has been much work in formal specification and verification of computer programs, relatively little research has been done on system specification. A particular claim of algorithments systems, known as packet communication systems, has been though at the subject of this study. Packet communication systems are composed of independently operating units that interact only by transmitting packets of information. These systems possess a number of desirable structuring properties that make them suitable for formal analysis.

We have developed a model for formally describing the behavior of packet systems and for proving correctness. The model is based on the fact that packet systems may be viewed both externally, in terms of their interaction with the outside world, and internally, in terms of their structural composition from smaller units. A nacket system is shown to be correct by proving that its formal characterizations corresponding to these two views are equivalent.

Our model is used to prove the correctness of three sample packet systems, and a general characterization of anythic systems is stated and proved.

Thesis Supervisor: Jack B. Dennis

Title: Professor of Computer Science and Engineering

The American

·不敢性致力。

#### Acknowledgments

The hardest part of this research was the interminably long time spent grappling with vague, abstruse notions, trying to find appropriate underlying concepts. During this period, I needed -- and received, -- assistance from many people around me.

Professor Jack Dennis, my research supervisor, showed a remarkable technical insight in working with me on developing new approaches for new areas. I am grateful that he matched my stubbornness by insisting I investigate certain ideas that seemed barren at first but later bore fruit.

Professors Liba Svobodova and Vaughan Pratt, my readers, have both been tremendously helpful in evaluating my ideas and approaches. They shared generous amounts of time with me and made sure I kept my ideas in the proper perspective.

All three of my committee members made substantial contributions to the form and content of this document, pointing out obscurities, errors and misconceptions to be corrected.

I wish to thank my fellow graduate students for listening patiently to many versions of my presentations of my ideas, pregressing from the unclear to the coherent. Thanks to Bill Ackerman, Waldis Berzins, Andy Boughton, Dean Brock, Clement Leung, Glan Miranker, Craig Schaffert, Ken Weng and a number of other students for helping me clerify my ideas and come up with the right definitions and proofs.

The MIT Laboratory for Computer Science has been a stimulating environment to work in. Thanks are due for their generous financial support throughout the research as well as for the use of stell computer facilities in preparing this document.

My parents gave me constant advice, support and encouragement, standing by me when I needed it and stimulating my confidence in myself through their confidence in me.

Finally, I wish to express my appreciation and gratitude to Toby, my fiancee and wife to be, for patiently bearing with me for two and a half long and difficult years, giving me emotional support and companionship, and believing in me.

# Table of Contents

| Abstrac     | ot                                                                            | . 2 |

|-------------|-------------------------------------------------------------------------------|-----|

| Acknow      | wiedgments                                                                    | . 3 |

| Conten      |                                                                               | . 4 |

| Chapte      | r 1: Introduction                                                             | . 5 |

| 1.1.        | System design and specification                                               |     |

| 1.2.        | Packet communication architecture and its buckground                          | . 9 |

| 1.3.        | Formal spacifications                                                         | 17  |

| 1.4.        |                                                                               |     |

| Chapte      | The approach to be presented  1 2: Packet Systems and their Systems  Overview | 26  |

| 2.1.        | Overview                                                                      | 26  |

| <b>Z.Z.</b> | A closer look at packet systems                                               | 29  |

| 2.3.        | Correctness                                                                   | 34  |

| 2.4.        | Structumi descriptions                                                        | 38  |

| Chapte      | r 3: Specifications for Packet District                                       | 41  |

| 3.1.        | The slice relation approach                                                   | 41  |

| 3.2.        | Streams and their operations                                                  | 44  |

| 3.3.        | Examples                                                                      | 48  |

| 3.4.        | Evaluation                                                                    | 54  |

| Chapte      | r 4: Specifications for Pariest Systems                                       | 56  |

| 4.1.        | Internal specifications                                                       | 56  |

| 4.2.        | Execution sequences (introductory)                                            | 60  |

| 4.3.        | Proportios of execution sugmentes                                             | 68  |

| 4.4.        | Execution arguments (formally)                                                | 78  |

| 4.5.        | Characterization of internal specifications                                   | 84  |

| Chapte      | r 5: Proving Packet Systems Correct                                           | 86  |

| 5.1.        | Setting my a convectment proof                                                | 86  |

| 5.2.        | Proof for the system ID                                                       | 89  |

| 5.3.        | Correctness of a cyclic system                                                |     |

| 5.4.        |                                                                               | 100 |

| <b>5.5.</b> | Proving correction of more complete pecket hystenes                           | 109 |

| Chapte      | r 6. Constitute                                                               | 120 |

| 6.1.        |                                                                               | 20  |

| 6.2.        |                                                                               | 24  |

| 6.3.        |                                                                               | 29  |

| Bibliog     |                                                                               | 31  |

| Glossar     | y                                                                             | 136 |

|             |                                                                               | 38  |

# CHAPTER 1. INTRODUCTION

### 1.1. System design and specification

The fields of computer hardware and software both deal with the same fundamental goal: building systems to perform designated functions. A hardware system is constructed from physical components, while a software system is realized by writing programs in a language implemented on some computer. As both hardware and software systems have grown in size and capability over the years, their structure and operation have grown tremendously in complexity. This has made the task of designing systems increasingly difficult, especially so for large, high-performance systems. It is important that both system designers and users have confidence that their systems perform their functions as intended. System testing, debugging and modification constitute a significant fraction of the time and expense involved in designing systems. The issues of making certain that a system being designed will operate correctly are thus of particular importance to both hardware and software system designers.

Verifying the logical correctness of system designs has been accomplished in practice mostly by "seat of the pants" techniques. The drawbacks of such an informal approach are clear: one can be intuitively certain that a system design is correct, but this is far from a guarantee of correctness. There are numerous "horror stories" about systems that had to be redesigned or scrapped because their designs had serious conceptual errors that went undetected in the verification process. Such errors indicate a lack of

understanding on the part of the designers as to exactly what functions the systems are supposed to serfering la erder to have a sound understanding of the way a system operates, and in order to be sure that it behaves correctly, it is necessary to make use of precise hearingthous of the system's legical It is for just this reason that the discipline of formal Literatura de La Companio de C specifications has arisen. Specifications are descriptions of the behavior or remarked breakfull floor in monthly of desired of a system, and a system is shown to be correct by verifying that it 一名 100 高好性的 经常3000 本门 1000000 电 11000000 satisfies its specifications, i.e. operates as it is intended to behave. There are emailigang program on the first of the contwo significant benefits that may be realized by using formal specifications. ice form of several and a First, it becomes possible to develop formal verification methodologies, which makes it feasible to prove that systems are correctly designed to perform their CAT LEANGING G intended tasks. Second, formal descriptions provide a model through which complex systems can be better understood. Thus, the task of system design the mere deal rest to see the may be facilitated through the study of formal system specification and THE POLICE OF THE PARTY STORES FOR THE PROPERTY OF THE PARTY OF THE PA verification techniques.

Formal specification techniques cannot be used blindly without considering the nature of the systems being described. For large, complex systems, the specifications may become so complicated as to make correctness proofs intractably difficult. However, this problem can be alleviated by treating only those systems that satisfy "nice" properties. By insisting on appropriate system constraints that must be satisfied, one can identify classes of systems that have more orderly and structured design with no real sacrifice in functional capability. Through judicious use of this concept of structured system design, the system designer can be assured of working with systems that can be more easily understood, described and verified.

A. 20、8点の1時間は100円。 ままずだ 八字に

Formal specifications have been the center of much research activity within the software field [Rustin, 1972; Liskov and Berzins, 1976]. addition, an entire discipline known as structured programming has arisen to study ideas of structured system design and their ramifications on the programming process [Dijkstra, 1972; Wortman, 1977]. However, there has been relatively little research in corresponding areas of the hardware field. One might explain this difference by saying that there is a much greater concentration of theoreticians specializing in software than hardware, but there is a more crucial underlying reason. Design costs for hardware systems have long been overshadowed by the costs of materials, fabrication and assembly. Once a machine is into production, the design process is ended; all further costs lie in replication and maintenance. For these economic reasons, the physical construction of systems has been the dominant factor in hardware development. With suftware, on the other hand, design costs have always predominated; since everything is realized on paper. Moreover, software systems are designed for specific applications, if the problems to be handled are changed, then the programs must coften be rewritten or redesigned. Hardware systems are general-purpose in that for a change in application it is the program and not the machine that is modified. Software is thus far more transient than hardware, which makes design costs even more important for software. It is therefore no wonder that the initiatives for studying design and specification methodologies have been strongest in the software field.

The rapid developments in semiconductor technology over the past few years are beginning to alter the economic balance in hardware development. Integrated circuit chips can be mass-produced at extremely low

cost. Construction costs for hardware systems are dropping dramatically as new fabrication techniques are coming into precise. Since design costs are remaining essentially the same, they are becoming more and more significant in relation to system development. This means that system design techniques and approaches will soon be on the cutting edge of hardware technology. For large and complex systems, whose logical functions are especially difficult to comprehend and work with, the approaches to system design are even more crucial. It is therefore important to open up a thorough investigation of formal specification and structured system design methodologies for hardware systems. And since much of the initiative in this area has come from software research, it is natural to look for ways to apply new technologies used in software design to the hardware field.

A perticular class of systems called packet communication systems, which are described in the next section, has been chosen as the domain for the research presented here. Packet communication systems are based on a set of structural preparties which provide for the heritary of large, high-performance systems and which also support the development of a theoretical framework for formal specification and verification. In this thesis, we shall develop techniques for formal specification of the behavior of packet communication systems. We shall also take a look at how the formal specifications may be applied towards verifying the legisle correctness of these systems. Because there has been so little formal study into methodologies for hardware system design, specification and verification, the research here may be considered as the first step in a new direction.

and the first of the first of the state of the first of the first of the state of

- 「痛疾、鬼がしょうしょうし、お露る、霜を食む、ましゃ

# 1.2. Packet communication architecture and its background

Packet communication architecture is a set of principles according to which systems may be designed and structured. The systems satisfying these principles are collectively known as pecket communication systems; for brevity, they shall also be called pecket systems. As introduced by Dennis in [Dennis, 1975b], packet systems are essentially interconnections of independently functioning units that interact only by sending each other packets of information. The information contained in a packet may have arbitrarily complex structure.

In this research, we have taken a particular point of view, regarding packet systems as being physically composed from hardware units. Some of the important concepts underlying packet communication architecture are particularly advantageous when applied to the design and implementation of hardware systems. It is equally valid, though, to implement packet systems in software. There are no existing techniques for formally specifying or verifying packet systems viewed from the software standpoint, so our work here may also be seen as an advance in the study of software specification as well.

There are two particular notions from the study of structured programming that are directly supported by the principles of packet communication architecture: modularity and hierarchy. These notions play a large role in the suitability of applying formal specification techniques to packet systems.

Modularity is an approach for structuring programs or systems by composing them from smaller units called modules. The basic idea is that the use of a module is separated from the internal details of its implementation. In this way, a module sees be developed and changed without affecting other modules. The concepts of modularity are discussed in more detail in [Myers, 1975, Feuresen, 1976; Bennia, 1972b]. An example of a mechanism for supporting medularity in software systems is the notion of data abstraction [Liskov and Effice, 1974]. A desirable design goal for modular systems is that individual modules be as felf-contained and independent as possible. This goal can be realized by making interaction among different modules as simply structured as possible, through a clean, well-defined interfaces. Although the advantages of modularly structured systems are obser, the issues of deciding where to draw smalled houndaries present an open problem. We shall not investigate this problem here.

The netion of hierarchy relates to how systems may be viewed and described. A hierarchically structured system is one that may be stratified into different levels of conceptual detail. Each level makes use of mechanisms whose internal details are hittlen away in lower levels. Each mechanism within the system is used at higher, more abstract levels than where it is defined. In this way, low-level detail is isolated so that it will not interfere with higher-level conceptual views of the system. The basic principles and concepts of hierarchy in systems have been presented by Pernas [Parnas, 1974; Parnas, 1975].

The properties of modularity and hierarchy make systems in general easier to understand and work with. Each module in a hierarchical and modular system has a set of "neighbor" modules with which it communicates. The behavior of a given module depends on the conventions by which it interacts with its neighbors, but it is completely independent of the internal characteristics of the other modules in the system. Consequently, the designer of a module need not worry about what goes inside any other modules; the only relevant concerns are the internal construction and the interface conventions for the particular module being designed. In this way, design information is partitioned along the boundaries of the modules, insulating the system designer from irrelevant detail. This insulation is further enhanced in hierarchical system structures. Each level of abstraction in the hierarchy is isolated from the other levels. The designer of a module has to know the external behavioral characteristics of the submodules from which the module. is composed, but the internal structures of the submodules should be totally irrelevant to the design of the given module. Thus, systems that are both modular and hierarchical have two dimensions along which design details are partitioned. When the structure of a system prevents certain design information from affecting areas it does not concern, the system design is simpler to understand. Conceptual simplicity is an important design goal whenever system recification and verification are to be daken into account.

Although the concepts of modularity and hierarchy have been given far less theoretical attention in relation to hardware than software, they are almost universally regarded as fundamental to good hardware design practice. Hardware systems have for a long time been built up from modules such as

adders, clocks and shift registers, and now there is an even greater variety of off-the-shelf compenent chips to use as modules. At a higher level of abstraction, a typical microcomputer is composed of a microprocessor, some RAM storage, I/O drivers and interface elements. Each of these components. can be treated as a module, and these modules can themselves be decomposed. For example, the processor has as submodules an adder, various registers, gating logic, an instruction decoder and other compenents; these submodules can in turn be further decomposed. This example shows how digital system design exhibits hierarchical and modular properties. In general, these properties are realized by intelligent system design, but they are difficult to achieve when designing large computing systems. Feetures such as virtual memory, multi-user environments, parallel programming and the sharing of data among different processes are difficult to realize, they are usually implemented in practice either by simulating them in software or by adding new components as afterthoughts to a basic Von Neumann machine. The interactions among these added components are anything but modular in nature, which is one of the reasons why large computing systems are so difficult to build. Packet communication architecture, as we shall see, provides direct support for hierarchy and modularity.

Packet systems are both madular and hierarchical in structure. The modules in a packet systems can easily be structured so that their modules correspond to the conceptual units in the designer's view of the system. Further, the principles of packet communication architecture allow the modules that form a packet system to be viewed individually as systems that

may themselves be decomposed into interconnected component modules. This hierarchical property of packet systems provides some of the major conceptual foundations of the approach to specification and verification that will be developed. By making hierarchy and modularity explicit, packet communication architecture not only facilitates formal specification and verification, but in addition serves to encourage good system design practice.

045:14:17 EU-UALEU

One of the most important design goals for packet systems is that the modules within a system operate as independently as possible. In support TATION OF THE STATE OF of this goal, it is required that modules communicate with each other by IN Add the IS an passing packets asynchronously. This principle eliminates the need for a centralized control facility to coordinate the action of all the modules, which itzir susiny# 3: greatly simplifies system structure. Moreover, it provides for concurrent operation of the modules, leading to enhanced system performance. A module, while awaiting response from other modules in order to perform certain tasks, and being bei it is 9, can busy itself with other tasks for which the required responses have ring that they're at his print. already arrived. An operation may proceed as soon as the information it needs the access of the second at all second is received, as opposed to what happens with conventional architectures, in Remails of the s which operations cannot be performed until they are explicitly initiated by the sequential control. It is this distinction that provides for concurrency and Charage and Live An thus allows packet systems to make more effective use of the available resources than do conventional large systems.

The microcomputer example given above exhibits a number of hierarchical levels of abstraction. It may be noted that the interfaces between modules at different levels of the hierarchy have completely different

characteristics. At the top level, one deals with transmission of applications data; within the microprocessor, microinstructions are passed; and at a still lower level, it is basic logical signals that are passed and gated. In digital systems as they are currently designed, interface protocols depend on the speed at which the various modules process control and data signals. This dependence limits the degree of modularity that can be achieved in existing systems, since a module's interface with its outside world is not free of internal speed and timing considerations.

Packet systems are not subject to such limitations; one of their important properties is that the timing characteristics of an individual module in a packet system do not affect the operation of any other module. A module in a packet system can be replaced with another unit that performs the same task orders of magnitude faster or slower than the original module, and this change will not alter the logical functioning of the system. Packet systems are thus speed independent, which removes from the designer the burden of having to take into account the speed and timing properties of system components in order to assure logical correctness. Speed independence enhances the degree of modularity in a system and thus provides an additional element of structuring in systems, which further assists system design and verification. It should be noted that a system must operate asynchronously in order to achieve the goal of speed independence. Packet systems, since they TOURS OF BUTT EXPERS OF are speed independent, can accommodate a uniform protocol for communication of packets among their component modules. This uniformity of interface provides the basis for the method of system specification that will be described here.

The idea of building systems by connecting independent modules under an asynchronous and speed-independent discipline is not new. An early exposition was given by Muller [Muller, 1963]. There was a major research effort several years later directed towards realizing systems that were to be hardware units physically constructed from called macromodules [Ornstein, 1967]. Patil has investigated logical designs for modules with which asynchronous systems may be built [Dennis and Patil, 1971], and more recently he has been working with applying programmable logic arrays to this task [Patil, 1975]. All of these designs differ from packet communication architecture in that control signals and data values are passed through the systems separately, traveling on two distinct sets of communication pathways. In packet systems, the notions of control and data are unified, eliminating the need for separate pathways. This is yet another respect in which the principles of packet communication architecture serve to simplify system structure, and the large many and the many and the state of the state

Since packet systems operate concurrently, a significant area of application for packet communication architecture lies in realizing computer systems that provide direct support for parallel programming. If different parts of a program can be executed in parallel, then it is advantageous to run the program on a machine for which the hardware can overlap their execution. In this way, one can optimize running speed and utilization of resources such as memory, processing elements and peripheral devices. The study of data flow computation has precisely this goal in mind. Data flow is the representation of programs in such a way as to make the data dependencies and inherent parallelism explicit. Given any two operations O<sub>1</sub>

and O2 in a data flow program, it should be immediately apparent from the program structure whether O1 should be performed before O2, whether O1 needs results of O2 in order to be performed, or whether O1 and O2 are independent (can be done in parallel). Data flow programming has been treated extensively in the literature; for both exposition and references, see Substantial effort has gone into studying [Dennis, 1975a; Weng, 1975]. designs for machines that can directly and efficiently execute data flow [Rumbaugh, 1975; Dennis, 1974; Dennis, 1977; Arvind, 1975; programs Plas, 1976]. On such a machine, there is no sequencing of instructions, an instruction may be executed any time after its operands become available. This is essentially the same principle as the one underlying the operation of modules within a packet system; in fact, the concepts of packet systems have been directly influenced by the research in developing architectures to implement data flow.

The conceptual compatibility between the ideas of data flow and packet communication architecture yields a natural connection between them. In a packet system, the activity that takes place within a module is initiated by the arrival of the appropriate data packets. There is no explicit sequencing of operations in data flow programs, and it should be practical to implement them on systems that do not require ordered sequences of instructions as their programs. This is one of the motivating factors behind the conception of packet communication architecture. Most of its concepts are far from new or original, but it is the combination that makes it suitable for realizing data flow computation in hardware. Conversely, data flow is a natural way to represent programs that will run on processors designed according to the

principles of packet communication architecture. Thus, there is a commonality between data flow and packet systems that arises because they share similar goals and principles.

There is one more property of packet systems that should be noted here. The behavior of a packet system (or of any of its modules) is observable in terms of the packets it sends out in response to the packets it receives. In general, packet systems are nondeterminate, which means that given the packets received by a module, there may be several distinct but equally valid responses to the input. Nondeterminacy is one of the factors that make the behavior of packet systems difficult to understand and formalize. This will have a definite bearing on the approach taken here towards specification and verification.

This concludes the overview of the basic ideas of packet communication architecture. The principal reason why packet systems were chosen for this research is that their design is structured in a way that supports system specification and verification. The next section presents an overview of some of the major concepts and techniques that have been developed for formal specification of computer programs and systems.

en den desidet bei

## 1.3. Formal specifications

Much of the research concerned with formally describing the activity within computer systems has dealt with programming language specifications. There are essentially three basic approaches to describing the behavior specified by a piece of program text: axiomatic, denotational and

operational. Each approach may be applied to verifying the correctness of program text as well as serving as a pure descriptive vehicle.

Axiomatic specifications capture the effect of executing a program by comparing properties of the system state before and after execution. The paradigm "if assertion A is true before program text P is executed, then assertion B is true after P is executed" describes the meaning of program text P. Special rules of inference are set up to describe the meanings of various combinations of program texts in terms of their components' meanings; these rules incorporate the basic semantic properties of constructs such as iteration and conditionals. This approach became known through the work of Floyd [Floyd, 1967] and Hoare [Hoare, 1969] in which it was used to prove correctness of simple flowchart-like programs that manipulated integers. The assertions they used related values of program variables. There has been a substantial amount of more recent research in axiomatic specifications. Dijkstra [Dijkstra, 1976] has built up an entire methodology of programming around the ideas of axiomatic specification. Owicki and Gries [Owicki, 1976] extended Hoare's techniques to parallel programs; their assertions made use of auxiliary state variables to keep track of interprocess coordination. [Greif, 1975] took a different approach to parallel programs, using a partial time-ordering on events to express coordination properties

Denotational specifications capture the effect of a program by viewing the objects they model as abstract mathematical entities. This approach provides a formal mathematical description of the computational notions being treated. An early denotational approach to specifications for

programming languages was the application of a mathematical formalism known as lambda calculus towards describing the semantics of Algol 60 programs [Landin, 1965]. The best known work in denotational specifications has followed from the research of Scott and Strachey [Scott and Strachey, 1971]. Mathematical results from lattice theory are used in the construction of complex domains over which programs are represented as functions. Programs are proved equivalent by showing that their functions coincide. A tutorial presentation of the Scott-Strachey approach is given in [Tennent, 1976].

Operational specifications deal with the changing states within computer systems as computations are performed. This is done by means of a state-transition model in which a state represents information present in the system at a given moment in time. The action of a program is captured by the sequence of transitions of the model. The sequence of states the model passes through as a program is executed defines the action of an interpreter for the program. The idea of using such an interpreter to define the meaning of programs in some language originated with McCarthy [McCarthy, 1962]. A well-known approach to operational specifications is the Vienna Definition Language (VDL) described in [Wegner, 1972b], which uses an interpreter that manipulates tree-structured system states. Dennis' Common Base Language [Dennis, 1971] is similar, dealing with more general directed graphs in place of trees. Another approach to operational specifications is due to Parnas [Parnes, 1972]. This approach distinguishes two kinds of operations: that yield state information, and those that alter the state of the system. Parnas applied his approach to operations on abstract data in programming

languages; this was extended to the domain of systems in [Robinson, 1975]. Verification is achieved within an operational framework by proving that the behavior of the interpreter in question is equivalent to the behavior of one that is known to perform the desired function. The ideas underlying verification by interpreter equivalence were developed by Milner [Milner, 1971] and are also presented in [Wegner, 1973a].

Although hardware specification has not reserved as much attention as software specification, there has been a substantial amount of study of computer hardware description languages (CHDL's). The approaches taken towards hardware specification have been almost entirely operational. language APL, before it was ever implemented as a programming language, was used as a hardware description language to specify the operation of IBM/360 computers [Falkoff, 1964]. Another CHDL, called ISP, was developed by Bell and Newell [Bell and Newell, 1971] to describe the operation of a large number of different computers. Both of these CHDL's describe their target systems at the instruction set level, treating machine words as a basic data type with operations for byte extraction and bitwise arithmetic and logical functions. On the other hand, the language PMS, which was also developed by Bell and Newell [Bell and Newell, 1971], describes the structure of computer systems in terms of their component processors, memories, controllers and I/O devices. This is an example of a CHOL describing systems from a higher-level conceptual point of view. DDL [Dietmeyer, 1974] is an example of a lower-level CHDL that defines the behavior of elements such as multipliers by specifying them as interconnections of basic logic sates.

Most of the CHDL's have been developed with two particular goals in mind: automated system design, and system testing by means of simulation. However, the microprogram certification project at IBM has developed an approach to hardware system specification that is directed towards formal verification of system design [Birman, 1974]. For both the instruction execution level and the microprogram level, a VDL-style interpreter is used to supply formal specifications. These two interpreters are then proved equivalent in exactly the same way that correctness is proved in operational specifications for programming languages as described above. The proof techniques for this approach are additionally described in [Leeman, 1975; Leeman, 1977]. Rumbaugh takes a similar approach to the IBM group in proving the correctness of a data flow processor [Rumbaugh, 1975]. He shows that an interpreter for his machine is equivalent to one that models the operations in a data flow language.

#### 1.4. The approach to be presented

The research in specifications that has been reviewed here cannot be directly applied to the task of formally describing and verifying packet systems. The principal reason for this is that conventional techniques are not equipped to handle the asynchronous operation of packet systems. The concurrency in packet systems makes it difficult to verify their correctness: in order to establish some property of a packet system, it must be shown true for all possible sequencings of packet transmissions and receptions within the system. Most existing techniques for formal specifications do not lend themselves to this kind of task. Moreover, the notion of sequencing of

actions, which is fundamental to nearly all the approaches that have been taken towards formal specifications, is not present in the context of packet systems.

There is a descriptive formalism, Petri nets, that has been developed specifically for specifying exynchronous behavior mithin systems. Petri nets [Peterson, 1977] are directed graphs in which markers called tokens pass along the arcs and through the vertices to model the accompance of various events. Although they have received much attention in this regard [Patil, 1970; Hack, 1976], they cannot be directly applied to verifying packet systems. Petri nets convey only control information for use in coordinating concurrent activities the nature of these activities is left-uninterpreted. In particular, they do not treat data values that are passed within packet systems. Also, although many mathematical apparation have been established for Petri nets, no methodology has been developed for applying them to system verification. Most of their practical applications have been in connection with simulating asynchronous behavior rather than proving properties of systems. For these reasons of packet systems.

Within a packet system, the modules receive and process fright packets, generate new packets for output and send them out, all asynchronously and in parallel. The hind of approach that seems most suited to specifying this kind of behavior is basically operational in nature. The state of a packet system describes which packets have been passed between which modules (and map also convey any energination information relevant to

o por superior service and the contract of the

the correct operation of the system). However, unlike conventional operational models, the transitions between states need to be governed not by an externally supplied sequence of instructions to be processed by the system, but rather by the presence or absence of packets as needed for processing. This means that an operational model for a packet system must take into account the many possible sequences of execution that could arise from the flow of packets.

Describing the internal operation of packet systems is not sufficient by itself for verification purposes. There must also be a method for specifying the logical function a system is expected to perform. This function concerns the system's input/output behavior as seen by the outside world in terms of packets received and sent out. Of the three kinds of approaches to specifications as discussed in the previous section, a denotational approach seems best suited for our needs because it can be easily tailored to describe sequences of packets that have been passed between various modules. Because of this flexibility, a denotational approach will also interface nicely with the hierarchical structuring of packet systems. Thus, we shall be working with two kinds of specifications for packet systems: operational specifications to describe the internal operation, and denotational specifications to describe their behavior in relation to the outside world. Verifications of correctness for a packet system will be demonstrated by proving that these two sets of specifications for the system agree with each other.

A recent research effort is specifically directed towards formally describing the structure and behavior of packet communication systems. The

descriptions are expressed in a formalism called ADL (Architecture Description Language), which is introduced in flowing 1977; There are two ways in which a system may be described in ADL structurally and behaviorally. A structural description characterises how the system is formed as an interconnection of modules. A behavioral description is an operational characterization of the system's interactive with the outside world, describing reception, processing and transmission of individual packets. The notation used here is similar to the programming lenguage Pascal [Wirth, 1971], and the underlying sementics are also based on the principles of date flow. As a first approach to plecing pecket systems on a formal foundation, ADL is both helpful and illuminating. However, the concept of specifying the internal operation of a packet system has not been developed within the ADL framework. This idea, which has not been studied previously, is crucial for verifying the correctness of systems in a hierarchical and modular fashion. The development of this concept is the most significant contribution of our The denotational approach to be used in our treatment for specifying the function of systems turns out to be more convenient to use than the operational approach found in ADL.

The body of this thesis consists of four chapters. Chapter 2 describes the basic properties of packet systems in more detail. The notion of correctness is defined, and a formalism for describing the structural composition of packet systems is also presented. Chapter 3 presents the denotational part of the packet system specifications. The behavior of a packet system or module is formally defined as a relation between the packets it receives as input and the corresponding packets sent out in response.

Chapter 4 motivates and defines the central concepts of the research, giving an operational characterization of the actions that take place within a packet system. Chapter 5 shows how the specification model developed in the two preceding chapters may be applied to the task of verifying correctness of packet systems. Three sample systems are proven correct, and a theorem is presented to show how the model may be simplified in certain cases.

### CHAPTER 2: PACKET SYSTEMS AND THEIR STRUCTURE

and a first the second of the first the second of the second second of the second of t

# 2.1. Overstaws: bus the highlight of the said of the parade proba-

In this chapter the concepts of packet communication architecture will be elucidated in detail. We shall clarify the action of a packet system and develop a means for formally describing the structural composition of such a system. We will also informally introduce the concept of correctness for packet systems. The machinery needed to formally define and prove correctness will be developed in Chapters 3 and 4.

Pecket communication architecture is a discipline dealing with a special class of systems known as packet systems. Packet systems are composed of independently functioning units, known as modules, which interact only by passing information to each other. The information is passed in the form of units called packets. There is no centralized facility for coordinating the action of the modules. Data processing and communication within packet systems are asynchronous, and the various modules operate concurrently.

In a packet system, the various modules are interconnected through one-way data paths known as channels. A channel connects two modules in a specified direction and is used to pass data from the first module to the second. Channels leading into a module are called input channels for the module, and channels leading out are called output channels. A packet system has its own set of input and output channels connecting it to the outside

world. The other ends of these channels are never explicitly designated.

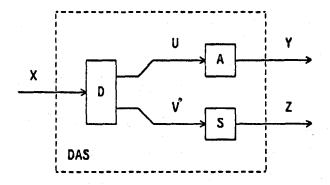

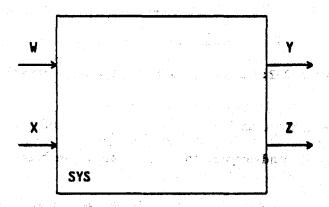

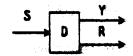

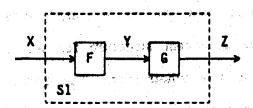

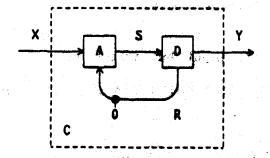

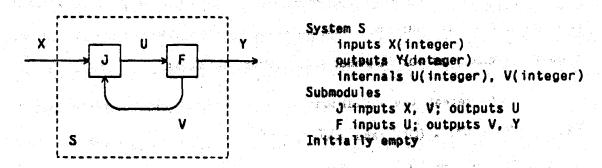

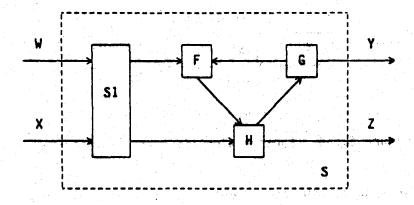

The structure of a packet system is determined by the way it is composed from modules and channels, and always remains fixed for a particular system. Modules and channels within a system are uniquely named. Figure 2.1-1 depicts a packet system DAS composed from three modules D, A and S. There is one system input channel X and two system output channels Y and Z. The internal channel U connects module D to module A, and channel V connects module D to module S.

Figure 2.1-1: A sample packet system DAS.

All data treated by a packet system appear in the form of packets, which are passed along the various channels of the system. Each packet carries a value of some type. The modules in a packet system all have the same basic principle of operation: a module receives packets on its input channels, processes them internally and generates packets to be sent out on its output channels. This principle applies to entire packet systems just as it does to their individual component modules. Packet systems are data-driven in the sense that the progress of a computation in a packet system is

determined by the passage of packets through the system.

There are two ingredients which together determine the behavior of a packet system: its structure and the behavior of its modules. Thus, for instance, in order to describe how the system DAS acts, one must first decide what the modules D, A and S do. We now describe the behavior of these three modules.

All three modules receive and pass integer-united packets. Module A, upon receiving a packet from its imput channel U, white one to the value and sends out the incremented value as a packet on its output channel Y. Module S behaves identically except for subtracting one instead of adding. Module D duplicates the packets it receives on X, sending out identical copies on U and V.

DAS acts. Any packet input from X is copied onto internal channels U and V. The packet passed on U will be incremented and sent out on Y; the packet passed on V will be decremented and sent out on Z. Thus each packet received by DAS causes two packets to be generated: a packet with value one greater on Y and a packet with value one less on Z.

It may occur to some readers here that these characterizations are incomplete. There is embiguity in describing what happens when several packets are to be processed in sequence: in what order are resulting packets generated and passed? In our example we can receive such questions by stipulating that the selative order of packets on a channel is always preserved. Precise methods for dealing with questions of this nature will be described in

the next chapter.

#### 2.2. A closer look at packet systems

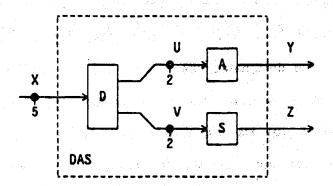

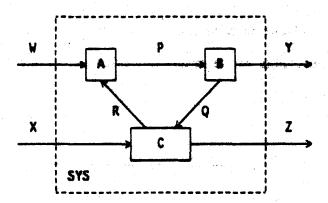

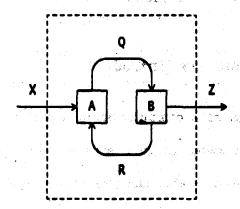

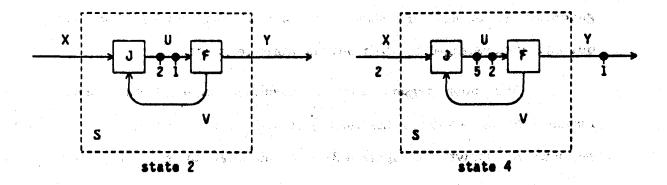

In this section the workings of packet systems will be examined in greater detail. The first thing we discuss is one of the fundamental properties they satisfy: the internal resources of a packet module or packet system may be allocated and utilized in any arbitrary manner as long as the specified operations will be performed correctly. Consider, for example, the system DAS from the previous section when it is in a state depicted in figure 2.2-1. An input packet with value 2 has been received on the X channel and processed by the D module, leaving copies of the packet on channels U and V. Another packet with value 5 is still waiting on channel X to be processed by the system.

Figure 2.2-1: A sample state of system DAS.

There are three actions that should now be performed within the system:

(1) module A absorbing and processing the packet on channel U; (2) module S processing the packet on V; and (3) system DAS accepting the packet from

channel X and initiating its processing in module D. The crucial property of packet systems exhibited here is that these three actions may be performed in any order, serially or concurrently, and the cassest execution of system DAS will be completely independent of whatever particular order is chosen. It is this property that makes the behavior of packet systems genuinely asynchronous.

We can gain a better understanding of the action of packet systems by taking a more detailed view of the operation of their component modules. When a module receives a packet from one of its input channels, it begins to process the packet internally. Sometimes the only effect of the packet's absorption is that the module's internal state may change. In general, though, the module's semantics may require that it generate one or more packets to be sent out on its output channels in reply to the packet received. The sequences of packets generated by a module in reply to a packet received are said to be the module's response to that packet. It is important to note that a module's response to a particular packet may depend on previous packets input as well as the designated one. There may be an arbitrary finite delay between the time a module receives a packet and the time the module generates and sends out its response to that packet. The fact that packet modules and systems must be able to tolerate such delays is an essential consequence of their asynchronous operation.

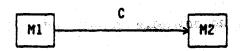

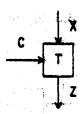

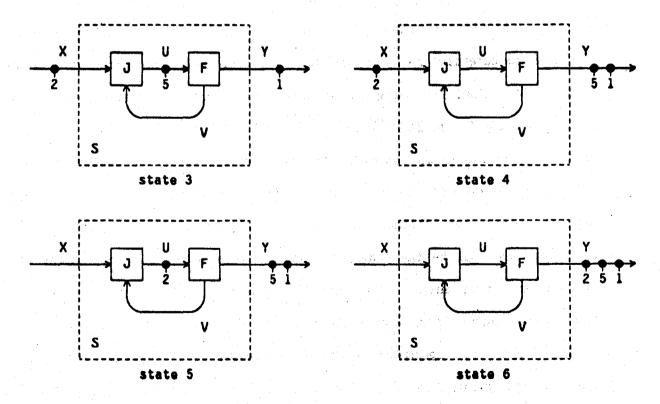

There is a special protocol that must be fulfilled in packet systems for the transmission and receipt of packets through the various modules and channels. Suppose a channel C connects module M1 to module M2, as

illustrated here:

Figure 2.2-2: A channel in a packet system.

It is desirable for medule M1 to have some way of knowing when it has successfully sent a packet out on channel C. The convention that has been adopted is that when a packet sent on C from M1 is received by module M2, M2 will send a signal to M1 on channel C in the reverse direction to indicate that it now has the packet safely in hand. Such a signal is known as an acknowledge signal. It is not until M1 receives an acknowledge signal for a particular packet that it knows it is done with the process of generating and sending that packet. Thus, from the point of view of module M1, there are three discrete steps in the transmission of a packet generation, sending and receipt of acknowledgment. It should be noted that module M2 cannot generate output to packets it receives from channel C until it has sent back on C an acknowledge signal for those packets. There is a caveat with regard to acknowledge signals: although they are sent in response to every packet transmission in a packet system, we regard them as part of the hardware and not available to be manipulated by system designers.

The channels in a packet system are assumed to have certain special characteristics as transmission media. The first, and simplest, is that any time a packet is sent out on a channel, it will eventually be received at the other end. A packet generated to be sent out from some module in a packet system

can never be called back. This means that whenever a module generates a packet to be sent out, it will receive an acknowledge signal for the packet within some finite span of time. It is assumed that the channels never "break" and that acknowledge signals will always be received by the appropriate modules. Failure of mechanism, for the purposes of verification, invalidates the entire system function. The issues of fault tolerance in systems are beyond the scope of this research. Thus, packet summunication architecture requires that every packet semental by some candidate must actually be sent out and soknowledged within some finite time interval. It should be noted that this requirement is a consideration of some times nather than performance, because packet systems are specification of some times packet.

A second important property of channels is that if a module receives a packet from one of the impart channels, then that peolest mind have been sent out on that channel at some precious time. Thus, for attainple, medule M2 may not receive a gardest from channel C unites module MI had already sent that packet out on C. Another way of stating this property is that no channel may generate sputient packets of its own.

A third characteristic of channels is that they act as FIFO queues, which means that if the module M1 above sends a packet x out on channel C and then sends another packet y out on C at a later time, then M2 must receive and acknowledge x before y. We make the further assumption that the channels have influented buffering tapacity, which means that there is no limit to the senses of packets that can be on the channel C at any given moment of time and be eveniting receipt by the "target" medule M2.

in a large that a man the second of the second and a second second second second second and the second of the

Physically speaking, this assumption is not realizable in general, because no real device can have infinite capacity, let alone a high-speed transmission medium. However, if we assume the unbounded buffering, then we rule out the possibility of system deadlock caused by packets piling up in certain channels and inhibiting further packet output into those channels. Unbounded buffering is therefore a convenient assumption to make.

Finally, we shall assume that for each channel in a packet system there is a designated set (type) of packets that may be passed on the channel. For example, one channel may carry only integer packets, while another channel may accept only packets that consist of an employee name together with a corresponding identification number.

There is an extremely important property of packet systems which we will be treating, namely nondeterminacy. A module or system is said to be nondeterminate if its semantics allow two or more distinct possible responses to a given packet input. A simple example of a nondeterminate module is one that models the toss of a coin. It has one input channel and one output channel, and its response to any packet received will be a single packet with either the value "heads" or the value "tails." The choice is arbitrary and independent of the input packet. Nondeterminate modules and systems are very difficult to work with because the multiplicity of possible results is cumbersome to model mathematically. We will explicitly allow for nondeterminate modules and systems in our treatment.

A certain class of nondeterminate system behavior will be of particular interest because it arises frequently in the design of packet systems.

This kind of behavior concerns the relative order of packets sent out on a channel. Consider a system in which the task of generating and sending out packets in response to inputs taken from a specific channel is relatively complicated or time-consuming. One would naturally wish to allow the processing of distinct inputs to proceed concurrently if possible. But then it may turn out that responses to a recent input will be ready to be sent out before responses to inputs received earlier. Moreover, it cannot be determined in advance whether or not such "cutting ahead" behavior will actually occur. It is possible to impose a synchronization discipline that will force the outputs into a desired order, but in doing so all the advantages of asynchronous processing of different inputs are lost. Thus, if the system application and design can tolerate "cutting ahead," it is wise to allow it. In general, then, providing for nondeterminate behavior that involves different alternative orderings of generated output packets should often in practice become an attractive design goal for packet communication exchitecture.

#### 2.3. Correctness

The notion of correctness for packet systems bears a close relationship to the ways the issues of system structuring and composition are treated within the framework of packet communication architecture. At a very intuitive level, a system is correct if it satisfies certain conditions laid out for it in edvance. For packet systems, these conditions take the form of behavioral specifications. As we mentioned in the preceding chapter, a packet system's behavior is observable by the way it responds to its inputs. More precisely, the behavior is a relationship between inputs received and outputs

generated in response to those inputs. A packet system, therefore, is correct if this relation satisfies a given set of specifications. The nature of such specifications will be discussed in detail in subsequent sections.

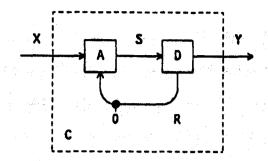

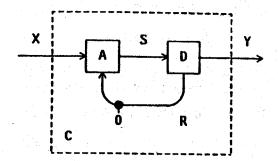

It is important to note that one cannot prove correctness of a system without some knowledge of its internal workings. If a system is viewed as a "black box" (figure 2.3-1).

Figure 2.3-1: "Black box" view of a packet system.

then the only things that can be seen are packets entering and leaving. There is simply not enough information available to determine whether or not a system is behaving correctly. Since modules operate asynchronously and with arbitrary finite delays, one cannot tell if additional output packets are forthcoming. For example, suppose a system has already sent out all the packets it should transmit in response to some particular input. The module only appears to be behaving correctly, since there is no guarantee that an invalid packet will be unexpectedly sent out later. Even if this were determinable, observation alone could never suffice to decide whether the system would respond correctly in all situations. The only way to tie down

the notion of correctness for a particular packet system, therefore, is to open the system up and look inside:

Figure 2.3-2: Internal view of the same packet system.

If we view the system as being realized in terms of its component modules, then the following fundamental correctness principle becomes evident:

A packet system is correct if its given structural decomposition satisfies the behavioral specifications for the system whenever the component modules satisfy their own respective behavioral specifications.

The notion of a system's decomposition satisfying a set of specifications is not yet formally defined; it will be treated in detail in Chapter 4. The notion of a module satisfying specifications is simply that of a physical device acting as intended. The above correctness principle defines only a relative nature of system correctness. An obvious question that arises is how to establish the correctness of the modules in order to show the system correct. We already have the answer to this question: just as with the system itself, correctness of the component modules can be established only in terms of their own

respective internal structures.

A significant ramification of this approach is that packet systems and modules are really two different views of the same thing: a module is revealed to be a system when one examined its internal structure, and ignoring the composition of a packet system is that the same as regarding it as a module. There is an underlying source for this obaceptual unity, which is that packet communication architecture supports the hierarchical structuring and composition of systems. Packet systems can (and should) be designed so that there are distinct and well-structured levels of discounts sition, each level consisting of systems built up from simpler modules. In this sense, our fundamental correctness principle for packet systems supports a top-down verification methodology in which correctness proofs are broken down level by level into their natural logical and conceptual constituents. Logically distinct lines of argument are isolated so that they cannot interfere with one another. Thus the notion of modular and hierarchical system structure is carried through in the approaches we take to correctness and verification.

It may seem for a moment that there is a potential infinite regress in working with smaller and smaller modules within modules, but this can never arise. There is always a well-defined bottom level to the hierarchy in which the modules are regarded as implementing primitive operations such as adding and gating. At this point, correctness has been reduced to the way the primitive functions are defined.

Our approach to correctness and verification of packet systems allows a system to be viewed in two different ways: Internally, in terms of

its structural composition from modules, and externally, by concealing the internal workings. The idea of distinguishing between internal and external views of systems is closely related to the notion of data abstractions in programming languages [Liskov and Zitles, 1974]. As we shall see in Chapter 3, it is fairly straightforward to construct behavioral specifications for a packet system viewed externally. However, in order to establish correctness of a system, we need to show that the external characterization agrees with the system's structure. It is a difficult task to formally describe the behavior of a system in terms of its internal composition. We shall address this task in Chapter 4.

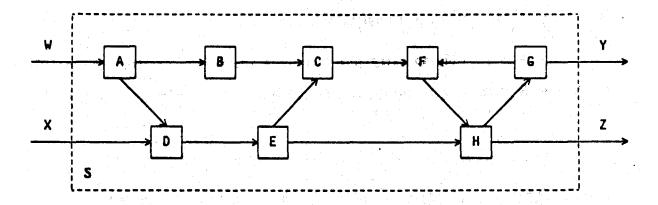

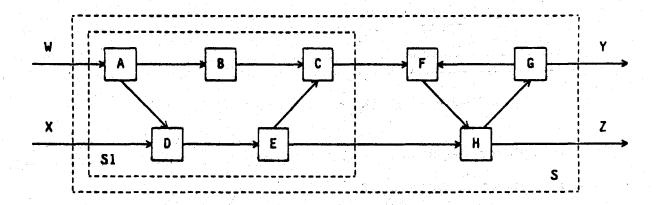

# 2.4. Structural descriptions

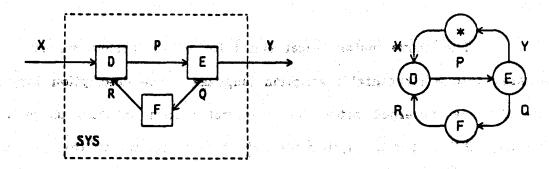

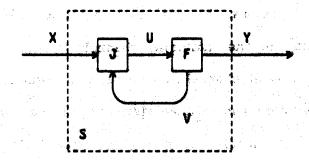

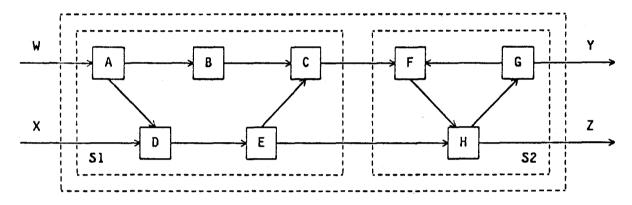

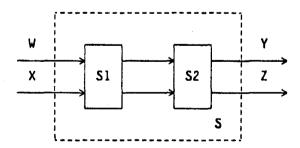

The only means we have used so far to describe the structure of packet systems is through informal block diagrams. If any general assertions are to be made involving system composition, we will need a more precise vehicle for structural description. Such a technique is introduced in this section.

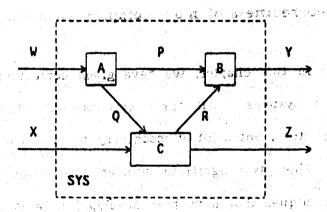

The structure of a packet system may be modeled in very straightforward fashion by a directed graph in which nodes representing modules are connected by directed arcs representing channels. Figure 2.4-1 shows a sample packet system segether with the directed graph that models it. Note that the directed graph has an extra node labeled "\*." This gives explicit representation to the system's "outside world," which serves as both the source of system input channel X and the target of system output channel Y. The graph may look like just another stylized drawing of the system, but

Figure 2.4-1: A packet system and its directed graph.

it is a mathematical object of specific characteristics. Formally speaking, a directed graph is an ordered pair of the form (N, A) in which N is the set of its nodes and A is the set of its arcs. Each arc in A is an ordered triple containing a source node, an arc name and a target node. An arc asA has the form (a.source, a.name, a.target). For example, the graph in figure 2.4-1 is the ordered pair

$(\{*,D,E,F\}, \{(*,X,D), (D,P,E), (E,Q,F), (F,R,D), (E,Y,*)\}).$

It is easy to see that for each node n in the directed graph we can define the sets of arcs leading into and out of n. These sets are given by

inputs(n) =  $\{a \in A: a.target = n\}$  and outputs(n) =  $\{a \in A: a.source = n\}$ .

The directed graph characterization thus mathematically specifies how the modules in a system are interconnected.

There are two additional properties of packet systems that can be incorporated into our formal structural descriptions. First, we can model the packet type restrictions for the channels by associating a type description with each channel. Second, we can specify packets initially present on the channels with an initial packet sequence for each channel. Both properties are handled easily in the directed graph model by adding extra fields to the

arcs.

The above mathematical model for packet system structure may be sugared into a structural description language. The description language we use here is patterned after the structural portion of ADL as presented in [Leung, 1977]. For the system we have been discussing in this section, if we assume that all channels carry only integer valued packets and that there is one packet with value zero initially present on channel R, then the formal description of its structure may be represented as follows:

System SYS

inputs X(integer)

outputs Y(integer)

internals P(integer), Q(integer), R(integer)

Submodules

D inputs X, R; outputs P

E inputs P; outputs Q, Y

F inputs Q; outputs R

Initially R(0)

While descriptions of this form do not explicitly name the source and target modules for each channel, these are very easily determined since each internal channel in the system must appear exactly once in a submodule input list and exactly once in a submodule output list.

This section has presented structural specifications for packet systems. The next two chapters present a model for behavioral specifications.

#### CHAPTER 3: SPECIFICATIONS FOR PACKET MODULES

# 3.1. The slice relation approach

Because of the way a packet system is built up from component modules, the behavior of a system will be a function of its structure and the behavior of the modules in it. In this chapter we shall develop a method for formally specifying the behavior of packet modules. Specifications defined by this method will be called external specifications because they describe the behavior of packet modules without considering their internal structural composition.

A packet module has a fixed number of input channels on which it receives packets to be processed, and there are a fixed number of output channels on which it sends out packets in response to the inputs it has received. A formal behavioral specification for a module must be able to rigorously determine for each input exactly what is a valid output response. Because packet systems are in general nondeterminate, the potential multiplicity of valid entput responses rules out a direct functional mapping. Instead, we shall supply external specifications for a module M in the form of a relation EXT<sub>M</sub> that formally relates inputs to the semantically valid corresponding outputs. Such a relation will be called an external characteristic relation for the module M.

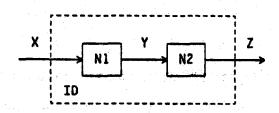

The most obvious approach is to use a relation from input packets to output packets, but this does not suffice in even the simplest case: consider a

module ID that "does nothing," that is, sends out its input packets untouched.

$$\xrightarrow{\mathsf{X}} \boxed{\mathsf{ID}} \xrightarrow{\mathsf{Y}}$$

Figure 3.1-1: The identity module 10.

The identity relation EXT<sub>ID</sub> on packets defined by the equation

(p,q) ∈ EXTn if and only if p = q

does not completely describe the behavior of the module ID. If ID receives as input a packet with value 1 followed by a packet with value 2, there are two different possible responses: ID can send out the 1 followed by the 2, or it can send out the 2 first and the 1 later. Thus a specification for the module must describe the sequencing of packets in order to completely capture its behavior. For example, if we intend for the module ID to preserve the relative order of the packets it receives, then its behavior would be correctly specified by the identity relation EXT<sub>D</sub> taken over the domain of sequences of packets rather than individual packets. Such sequences are required in general to describe the behavior of a module when it depends on a memory of previous packets received in order to decide how to respond to a given packet. We therefore need to develop some mathematical machinery for manipulating sequences of packets. We will use the term stream to denote a sequence of packets. The mathematics of streams will be discussed in the next section.

In general, the behavior of a module is specified by a binary relation that relates presented inputs to valid output responses. For the module ID, we see that presented input may be correctly modeled by a stream

number of input channels, in order to model presented input we need a separate packet stream for each input channel. We therefore define an *input slice* for a module M to be a collection of streams, one for each input channel of M. Similarly, an *output slice* has as its components one stream for each output channel. Thus the formal specifications for a module M will consist of a binary relation between input slices and output slices. This relation is called the *characteristic relation* for M. We reserve the notation EXT<sub>M</sub> from now on to denote the characteristic relation for a module M. The slice relation approach to module specifications is not original, and a corresponding definition may be found in [Dennis, 1972a],

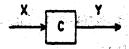

As an example, an input slice for the module J shown below is a pair (u,v) in which u and v are packet streams for channels U and V, respectively; an output slice for J has the form (z), where z is a packet stream over Z.

$$\begin{array}{c|c} U & Z \\ \hline V & J \end{array}$$

Thus the characteristic relation EXT, for J will have elements of the form ((u,v), (z)).

Slices distinguish the time ordering between packets passed on each individual channel but not between packets on different channels. It may seem that crucial behavioral information is lost by not imposing a total ordering on all packet transmissions into and out of a module, but this turns

out not to be the case. If a packet pl is sent out on a channel Cl in some packet system before packet p2 is sent out on channel C2, there is no guarantee that pl will arrive ahead of p2 in their race to their respective destinations. This is because asynchronous packet systems impose no constraints on transmission times along channels, allowing for different channels with different characteristics suited to their needs. Thus, the extra information obtained from interstream packet ordering is rendezed useless by the properties of channels in a packet communication system. The use of slices in our model, then, provides exactly the information needed for proper behavioral specifications.

### 3.2. Streams and their operations

In this section the basic definitions, operations and mathematical properties of streams are laid out in detail. Because of the technical nature of the material, an index to the notations and technical terms is provided in an Appendix.

For any arbitrary packet module, we take as given for each of its input and output channels a well-defined space (set) of packet values that may be passed along that channel. The space, which we call a channel space for the channel, is identified with the channel and shares the same name. Similarly, elements of a channel space are identified with packets passed on the channel.

We will define a stream to be a sequence of packets passed on a particular channel. Individual packets in a stream 2 will be referred to by

expressions of the form Z[i]. A stream z will be denoted by an expression of the form (Z[1], Z[2],...). Streams may be finite or (countably) infinite. The size of a stream z, written #z, is the number of packets in it. Two streams are equal if they have the same size and corresponding packets in them are equal. This means that a stream is uniquely determined by its size and by its elements and their ordering. The space of streams for a channel Z is denoted by Z\*. Formally, we have:

<u>Definition</u>: A set S of natural numbers is said to be an *initial segment* of the natural numbers iff for any  $i \in S$ ,  $j \le i$  implies  $j \in S$ .

<u>Definition</u>: A stream over a space Z is a function mapping some initial segment of the natural numbers into Z. The space of all streams over Z is denoted by Z\*.

<u>Definition</u>: The empty stream over a space Z, denoted by  $\in$  or by  $\langle \rangle$ , is the unique stream over Z having empty domain and no elements.

<u>Definition</u>: If i is in the domain of a stream z, we define the i-th element of z, denoted z[i], to be the image of i under z.

Observe that Z[i] is undefined if i is not in the domain of Z, and that if Z[i] is defined then Z[j] is defined for all  $j \le i$ .

a To Sauchton I

<u>Definition</u>: For any stream Z, the size of Z, denoted #Z, is the number of elements in the domain of Z. If the domain of Z is infinite, then we say  $\#Z = \infty$ .

Note that Z[i] is defined if and only if  $1 \le i \le \#Z$ . In particular, Z[i] is defined for all natural numbers if and only if  $\#Z = \infty$ .

<u>Definition</u>: Two streams Z and Z' are said to be equal, written Z = Z', iff #Z = #Z' and Z[i] = Z'[i] for all  $i \le \#Z$ .

In our treatment, we shall regard the token " $\Rightarrow$ " as a distinguished natural number whose arithmetic properties are defined in an obvious manner, such as  $i \le \infty$  and  $\Rightarrow + i = \infty$  for all natural numbers i. The value  $\Rightarrow$  may or may not be counted in the range of natural number quantifiers; this depends on context. Hecause all streams are countable, an expression such as  $Z[\infty]$  has no meaning, even when Z is an infinite stream.

An important relation over streams is the gradix relation. Stream Z is a prefix of stream Z' whenever Z "occurs" at the beginning of Z', as shown below:

ျ<del>န်းရွာမှန်းရွား</del> ကြေးသည်များကို သည်မှန်သည်။ သည်များကို သည်မြောင်းသည်

r slog kas in jord grade products for a constant of the second of the constant of the constant

occurring after the prefix z.

For any stream 2, we use the special notation  $\mathbb{Z}[k:m]$  to denote the segment of Z consisting of the k-th through m-th elements of Z in order.  $\mathbb{Z}[k:m]$  is a stream of size m-k+I, and we allow the special case of an infinite stream when  $m = \infty$ . If k > m, then  $\mathbb{Z}[k:m]$  is the empty stream. As a special case, whenever  $k \le \mathbb{Z}$ ,  $\mathbb{Z}[1:k]$  is the unique prefix of Z of length k. This means that  $\mathbb{Z}[1:k][i] = \mathbb{Z}[i]$  for each  $i \le k$ .

Given streams  $Z_1$  and  $Z_2$  we can form their concatenation  $Z_1 \in Z_2$ , which is a stream consisting of the packets in  $Z_1$  followed by the packets in  $Z_2$ . The formal definitions now follow:

<u>Definition</u>: Given two streams z, z' over the space Z, we say z is a prefix of z', denoted z PREFIX z', if and only if

$$#z \le #z' \text{ and}$$

(2)

$$1 \le \#Z \Rightarrow Z'[i] = Z[i].$$

<u>Definition</u>: For any stream z, if  $k \le m \le \#z$ , then z[k:m] is the unique stream of size m-k+1 such that z[k:m][i] = z[k+i-1] for each i in its domain.

<u>Definition</u>: Given streams z and z' for which z PREFIX z', we define the difference z' - z by z' - z = z'[1+#z:#z'].

<u>Definition</u>: For any two streams  $Z_1$  and  $Z_2$  over the same space  $Z_1$ , their concatenation  $Z_1 \in Z_2$  is the unique stream  $Z_1 \in Z_1 + Z_2$  satisfying  $Z_1 = \{if \mid 1 \le Z_1 \mid i \in Z_1 \mid i \in Z_2 \mid i = Z_1 \}$ .

There are two stream operations we will use which count and find particular packets in a stream: count(p,z) is the number of packets in z equal to packet p, and index(p,z,j) is the position in z of the j-th occurrence of packet p. They are defined by:

<u>Definition</u>: count(p,z) = card{i  $\leq \#z$ : z[i] = p}.

<u>Definition</u>:  $index(p,Z,j) = (if \exists i \leq \#Z: Z[i] = p \& count(p[1:i-1],Z) = j-1$ then i else undefined).

This is well-defined since if such i exists, then it is uniquely determined.

Two more important relations over streams are the subsequence and merge relations. A stream  $z_1$  is a subsequence of stream  $z_2$  if the elements of  $z_1$  occur in the same relative order within  $z_2$ . They do not have to occur contiguously. A stream z is a merge of streams  $z_1$  and  $z_2$  if and only if  $z_1$  and  $z_2$  occur in z as disjoint subsequences and together exhaust z. All merges of  $z_1$  and  $z_2$  are of length  $\#z_1 + \#z_2$ . The formal definitions are:

<u>Definition</u>: Given two streams  $z_1$  and  $z_2$  over the space Z, we say  $z_1$  is a subsequence of  $z_2$ , denoted  $z_1$  SUBSEQ  $z_2$ , if and only if there exists a function f that maps the domain of  $z_1$  into the domain of  $z_2$  such that

(1)

$$k_1 < k_2 \Rightarrow f(k_1) < f(k_2)$$

and

(2) for each

$$k \le \# z_1, z_1[k] = z_2[f(k)].$$

A function f setisfying properties (1) and (2) will be called an insertion. Any subset S of the domain of a stream Z defines a unique subsequence of Z which is formed simply by arranging the elements of Z indexed by S. in increasing order.

<u>Definition</u>: Given three streams  $z_1, z_2$  over a common space Z, we say z is a merge of  $z_1$  and  $z_2$  if and only if the demain of z can be partitioned into two disjoint subsets, one defining  $z_1$  as a subsequence of z and the other defining  $z_2$  as a subsequence of z.

This concludes the presentation of the fundamentals of streams.

# 3.3. Examples

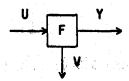

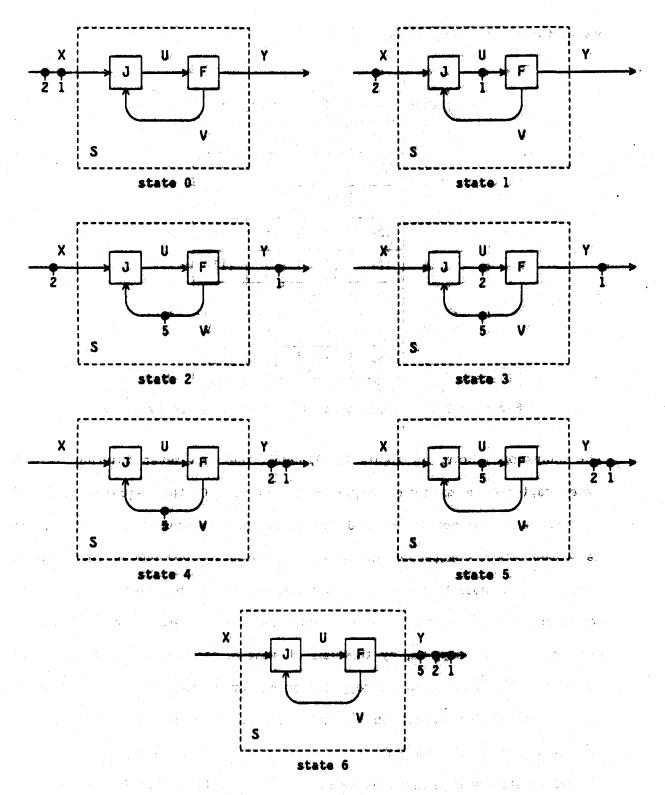

In this section we exhibit some elementary packet modules with their specifications. The first module we describe is the distribute module D (figure 3.3-1).

Figure 3.3-1: The distribute module D.