# **AEGIS: A Single-Chip Secure Processor**

by

Gookwon Edward Suh

Bachelor of Science in Electrical Engineering Seoul National University, 1999

Master of Science in Electrical Engineering and Computer Science Massachusetts Institute of Technology, 2001

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2005

© Massachusetts Institute of Technology 2005. All rights reserved.

Author ...... Department of Electrical Engineering and Computer Science September 6, 2005

Certified by..... Srinivas Devadas Professor of Electrical Engineering and Computer Science

> ۰. ۲۰۰۰ ۱۹۹۳ - ۲۰۰۲ ۱۹۹۳ - ۲۰۰۲

Thesis Supervisor

Accepted by

Arthur C. Smith Chairman, Department Committee on Graduate Students

BARKER

#### **AEGIS: A Single-Chip Secure Processor**

by

Gookwon Edward Suh

Submitted to the Department of Electrical Engineering and Computer Science on September 6, 2005, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

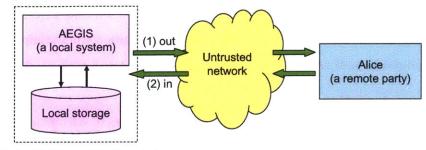

Trust in remote interaction is a fundamental challenge in distributed computing environments. To obtain a remote party's trust, computing systems must be able to guarantee the privacy of intellectual property and the integrity of program execution. Unfortunately, traditional platforms cannot provide such guarantees under physical threats that exist in distributed environments.

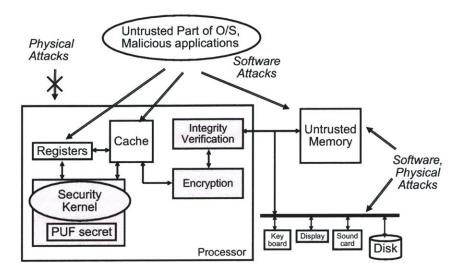

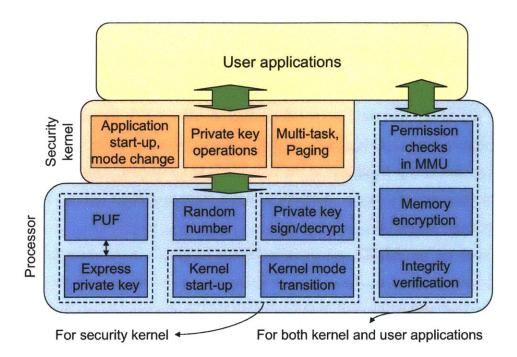

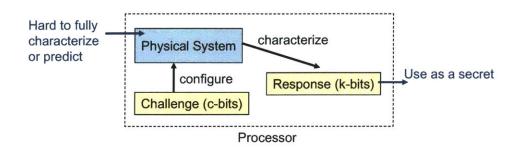

The AEGIS secure processor enables a physically secure computing platform to be built with a main processor as the only trusted hardware component. AEGIS empowers a remote party to authenticate the platform and guarantees secure execution even under physical threats. To realize the security features of AEGIS with only a single chip, this thesis presents a secure processor architecture along with its enabling security mechanisms. The architecture suggests a technique called suspended secure processing to allow a secure part of an application to be protected separately from the rest. Physical random functions provide a cheap and secure way of generating a unique secret key on each processor, which enables a remote party to authenticate the processor chip. Memory encryption and integrity verification mechanisms guarantee the privacy and the integrity of off-chip memory content, respectively.

A fully-functional RTL implementation and simulation studies demonstrate that the overheads associated with this single-chip approach is reasonable. The security components in AEGIS consumes about 230K logic gates. AEGIS, with its off-chip protection mechanisms, is slower than traditional processors by 26% on average for large applications and by a few percent for embedded applications. This thesis also shows that using AEGIS requires only minor modifications to traditional operating systems and compilers.

Thesis Supervisor: Srinivas Devadas Title: Professor of Electrical Engineering and Computer Science

### Acknowledgments

It has been my pleasure to work with my advisor, Professor Srinivas Devadas. Srini provided me with an exceptional environment for research, and guided my work. His door was always open and he was never too busy to give advice on my research as well as my personal life. I thank Srini for being not only a good research advisor, but an excellent mentor.

I would like to thank my committee members, Professor Frans Kaashoek, Ronald Rivest, and Krste Asanovic, for their invaluable time and helpful feedback. Meetings with Frans made me think beyond a processor architecture and work on high-level issues such as programming models and detailed application scenarios. Ron provided me with valuable comments on cryptographic primitives used in AEGIS. Krste allowed me to use his computing resources as well as benchmarks in evaluating the AEGIS prototype. I thank Professor Mihir Bellare for discussion on hardware implementations of MAC and hashes. I also thank Professor Arvind and Larry Rudolph for helpful advice throughout my graduate life.

The work described in this thesis would not have been possible without the help of other members involved in the AEGIS project. I heavily collaborated with Dwaine Clarke, Blaise Gassend, and Marten van Dijk on the processor architecture and memory protection algorithms. Jae Wook Lee and Daihyun Lim implemented the PUF circuit in ASIC. Charles O'Donnell was in charge of software aspects of the AEGIS prototype. Ishan Sachdev helped me work out the details of the programming model by implementing the ideas in practice. As a UROP, Kevin Chen helped me implement PUF error correction. I thank my colleagues for their help in research as well as friendship.

I would love to thank my special friend Judy, Jongdeuk, or Joonhee Park for her encouragement and support through tough times. She made my life fun and enjoyable. I was fortunate to have more friends around me. Dan and Dave kept me healthy by playing many squash games together. Nirav, Mike P, Mike Z, Alfred, Albert, and Seongmoo all made CSAIL a great place to work. I also thank Sungwon, Yongguen, and Jongchul as well as all other friends for their support and many fun times we have had together.

My family always supported me during these years. Their prayer, encouragement and love for me is undoubtedly the greatest source of my inspiration and motivation. They have given me far more than words can express.

Most of all, I would like to thank God for His guidance and grace throughout my life.

# Contents

| 1 | $\mathbf{Intr}$ | oducti        | on                                | <b>21</b> |

|---|-----------------|---------------|-----------------------------------|-----------|

|   | 1.1             | Securi        | ty Challenges                     | 22        |

|   |                 | <b>1.1</b> .1 | Trusted Remote Interaction        | 22        |

|   |                 | 1.1.2         | Other Security Issues             | 24        |

|   | 1.2             | Applic        | ations                            | 25        |

|   |                 | 1.2.1         | Digital Rights Management         | 26        |

|   |                 | 1.2.2         | Distributed Computation           | 26        |

|   |                 | 1.2.3         | Trusted Third Party Computing     | 27        |

|   |                 | 1.2.4         | Mobile Agents                     | 27        |

|   |                 | 1.2.5         | Embedded and Mobile Devices       | 28        |

|   | 1.3             | Appro         | aches for Trusted Platforms       | 28        |

|   |                 | 1.3.1         | Tamper-Proof Packages             | 29        |

|   |                 | 1.3.2         | Smartcards                        | 29        |

|   |                 | 1.3.3         | Auxiliary Security Chips          | 30        |

|   |                 | 1.3.4         | AEGIS: Secure Main Processor      | 30        |

|   | 1.4             | Contri        | butions                           | 30        |

|   |                 | 1.4.1         | Security Mechanisms               | 31        |

|   |                 | 1.4.2         | Summary of Contributions          | 33        |

|   | 1.5             | Organ         | ization                           | 35        |

| 2 | Sec             | ure Co        | omputing Overview                 | 37        |

|   | 2.1             |               | ty Features                       | 37        |

|   |                 | 2.1.1         | Secure Execution Environments     | 39        |

|   |                 | 2.1.2         | Suspended Secure Processing (SSP) | 41        |

|   |                 |               |                                   |           |

|   |     | 2.1.3    | Other Security Features                                 | 2 |

|---|-----|----------|---------------------------------------------------------|---|

|   | 2.2 | AEGI     | S Secure Computing Model                                | 2 |

|   | 2.3 | Protec   | tion Mechanisms                                         | 4 |

|   |     | 2.3.1    | Secret Key                                              | 4 |

|   |     | 2.3.2    | Secure Execution                                        | 5 |

|   |     | 2.3.3    | Secure Communication                                    | 5 |

|   |     | 2.3.4    | Hardware Software Partition                             | 5 |

|   | 2.4 | Limita   | 4                                                       | 7 |

| 3 | Phy | vsical H | Random Functions 49                                     | • |

|   | 3.1 | Goals    |                                                         | 9 |

|   | 3.2 | Non-V    | Olatile Memory         50                               | 0 |

|   |     | 3.2.1    | ROM                                                     | ) |

|   |     | 3.2.2    | Fuses                                                   | ) |

|   |     | 3.2.3    | EEPROM                                                  | l |

|   |     | 3.2.4    | Common Security Issues                                  | 1 |

|   | 3.3 | Physic   | al Random Functions                                     | 1 |

|   |     | 3.3.1    | Concept                                                 | 2 |

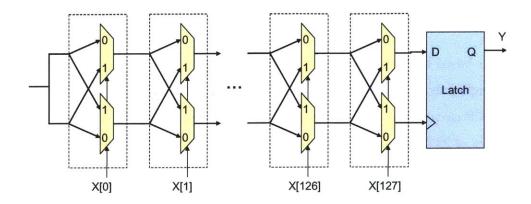

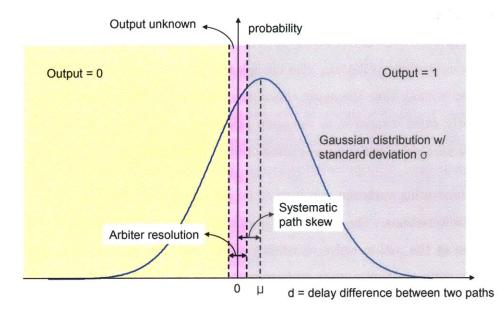

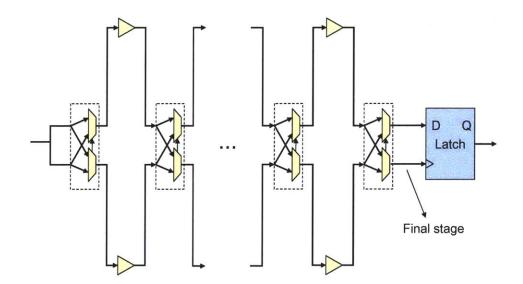

|   |     | 3.3.2    | Arbiter-Based PUF                                       | 2 |

|   |     | 3.3.3    | Experimental Results                                    | 1 |

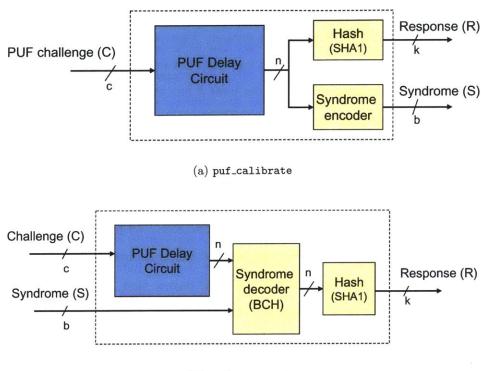

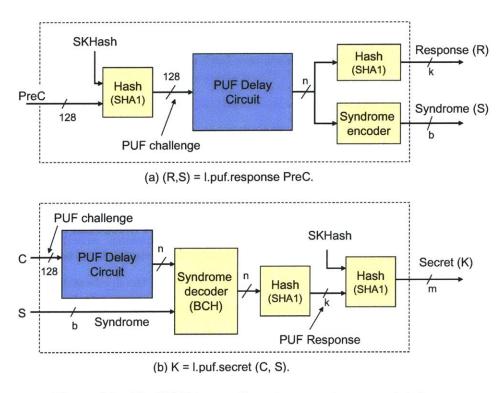

|   | 3.4 | Reliab   | le Secret Generation                                    | 1 |

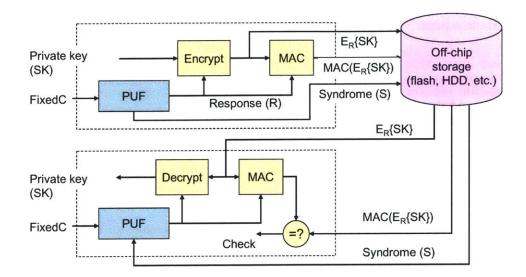

|   | 3.5 | Expre    | ssing a Private Key with PUFs                           | 3 |

|   |     | 3.5.1    | Key Generation                                          | 7 |

|   |     | 3.5.2    | Reloading                                               | 3 |

|   | 3.6 | Evalua   | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $58$ | 3 |

|   |     | 3.6.1    | Functionality                                           | 3 |

|   |     | 3.6.2    | Cost                                                    | 3 |

|   |     | 3.6.3    | Security                                                | • |

|   | 3.7 | Desigr   | a Considerations                                        | ) |

|   |     | 3.7.1    | Manufacturing Variations                                | ) |

|   |     | 3.7.2    | Analytical PUF Model                                    | L |

|   |     | 3.7.3    | Circuit Design                                          | 3 |

|   |      | 3.7.4 Error Correction Parameters               | 55 |

|---|------|-------------------------------------------------|----|

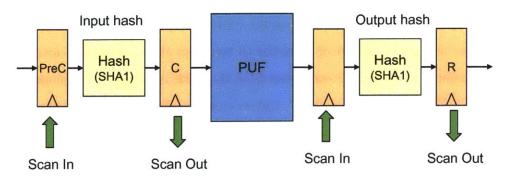

|   | 3.8  | Manufacturing Tests                             | 6  |

| 4 | Off- | Chip Memory Protection 6                        | 9  |

|   | 4.1  | Overview                                        | ;9 |

|   | 4.2  | Memory Encryption                               | '1 |

|   |      | 4.2.1 Security Goal                             | '1 |

|   |      | 4.2.2 Block Cipher                              | '1 |

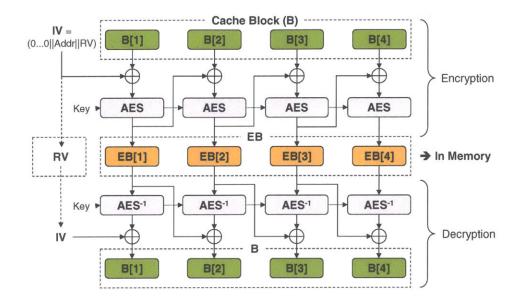

|   |      | 4.2.3 CBC Encryption                            | 2  |

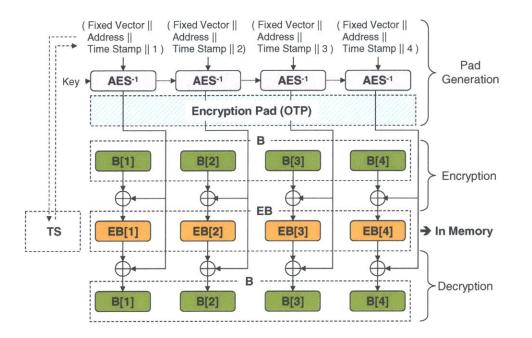

|   |      | 4.2.4 Counter-Mode Encryption                   | '3 |

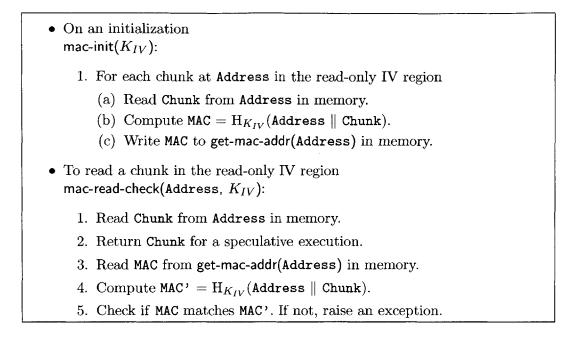

|   |      | 4.2.5 Decryption of the Read-Only ME Regions    | '5 |

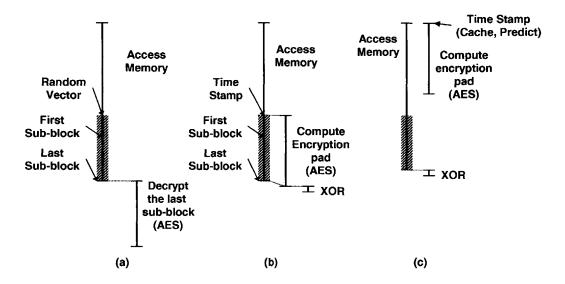

|   |      | 4.2.6 Impacts on Memory Latency                 | 6  |

|   |      | 4.2.7 Security Discussion                       | 7  |

|   | 4.3  | Integrity Verification                          | 7  |

|   |      | 4.3.1 Security Goal                             | 8  |

|   |      | 4.3.2 Message Authentication Code (MAC)         | 78 |

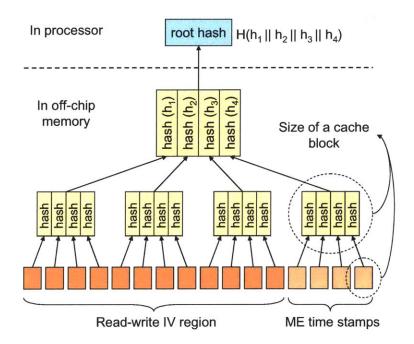

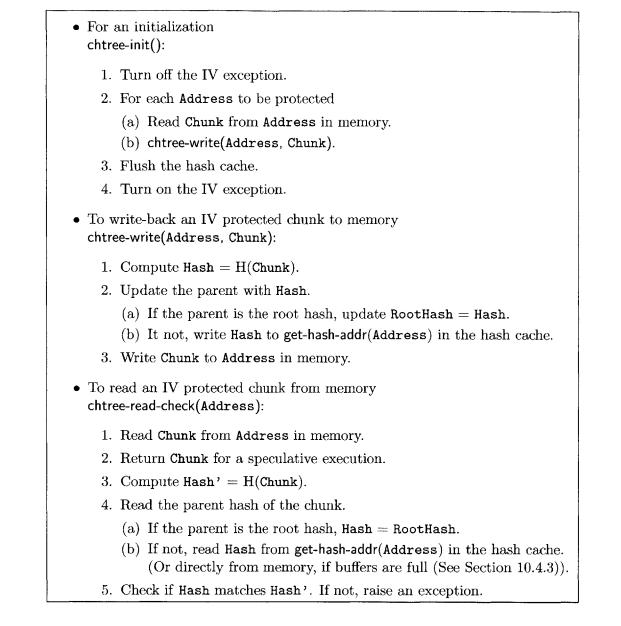

|   |      | 4.3.3 Hash Trees                                | '9 |

|   |      | 4.3.4 Cached Hash Trees: Making Hash Trees Fast | 80 |

|   |      | 4.3.5 Security Discussion                       | 33 |

|   | 4.4  | Real World Issues                               | 33 |

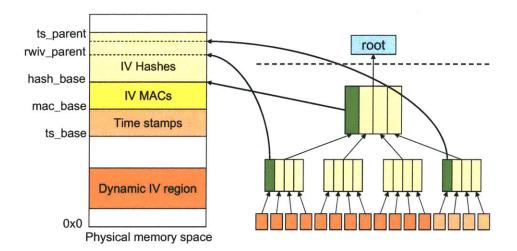

|   |      | 4.4.1 Memory Layout                             | 33 |

|   |      | 4.4.2 Re-Sizing Protected Regions               | 36 |

|   |      | 4.4.3 Direct Memory Access                      | 37 |

| 5 | Pro  | ecessor Architecture 8                          | 9  |

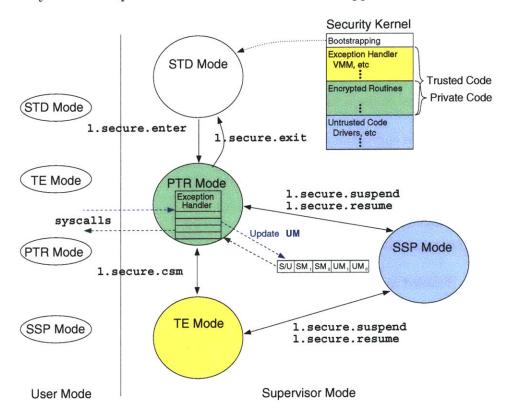

|   | 5.1  | Secure Execution Modes                          | 39 |

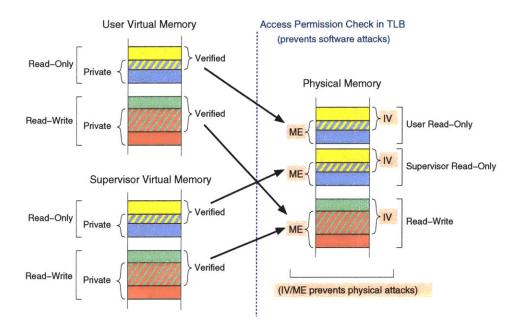

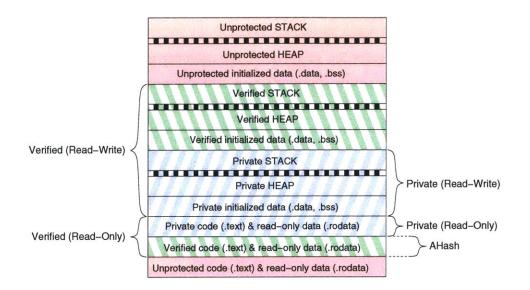

|   | 5.2  | Memory Protection                               | )1 |

|   |      | 5.2.1 Overview                                  | 91 |

|   |      | 5.2.2 Protection Against Physical Attacks       | )1 |

|   |      | 5.2.3 Protection Against Software Attacks       | )3 |

|   |      | 5.2.4 Speculative Execution                     | 94 |

|   | 5.3  | Execution Mode Transition                       | 94 |

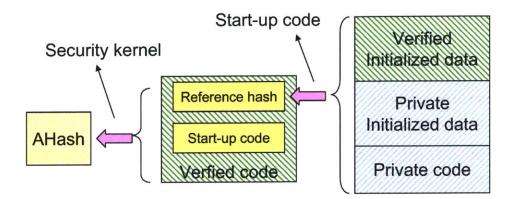

|   |      | 5.3.1 Start-Up                                  | 95 |

|   |                                                                             | 5.3.2                                                                                                               | Changes between TE and PTR                                                                                                                                                                                                                                           | 96                                                                                                                                                        |

|---|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                             | 5.3.3                                                                                                               | Suspend and Resume                                                                                                                                                                                                                                                   | 97                                                                                                                                                        |

|   |                                                                             | 5.3.4                                                                                                               | Exit                                                                                                                                                                                                                                                                 | 97                                                                                                                                                        |

|   |                                                                             | 5.3.5                                                                                                               | Exceptions                                                                                                                                                                                                                                                           | 97                                                                                                                                                        |

|   | 5.4                                                                         | Privat                                                                                                              | e Key Instructions                                                                                                                                                                                                                                                   | 98                                                                                                                                                        |

|   |                                                                             | 5.4.1                                                                                                               | Signing                                                                                                                                                                                                                                                              | 98                                                                                                                                                        |

|   |                                                                             | 5.4.2                                                                                                               | Decryption                                                                                                                                                                                                                                                           | 99                                                                                                                                                        |

|   | 5.5                                                                         | Miscel                                                                                                              | llaneous Instructions                                                                                                                                                                                                                                                | 99                                                                                                                                                        |

|   |                                                                             | 5.5.1                                                                                                               | Random Number Generation                                                                                                                                                                                                                                             | 99                                                                                                                                                        |

|   |                                                                             | 5.5.2                                                                                                               | Special Register Accesses                                                                                                                                                                                                                                            | 100                                                                                                                                                       |

|   | 5.6                                                                         | Debug                                                                                                               | gging Support                                                                                                                                                                                                                                                        | 101                                                                                                                                                       |

|   | 5.7                                                                         | Securi                                                                                                              | ity Instruction Summary                                                                                                                                                                                                                                              | 101                                                                                                                                                       |

|   | 5.8                                                                         | Securi                                                                                                              | ity Discussion                                                                                                                                                                                                                                                       | 102                                                                                                                                                       |

|   |                                                                             | 5.8.1                                                                                                               | Program Integrity                                                                                                                                                                                                                                                    | 102                                                                                                                                                       |

|   |                                                                             | 5.8.2                                                                                                               | Program Privacy                                                                                                                                                                                                                                                      | 105                                                                                                                                                       |

|   |                                                                             | 5.8.3                                                                                                               | Protection Summary                                                                                                                                                                                                                                                   | 105                                                                                                                                                       |

|   |                                                                             |                                                                                                                     |                                                                                                                                                                                                                                                                      |                                                                                                                                                           |

| 6 | Sec                                                                         | urity I                                                                                                             | Kernel                                                                                                                                                                                                                                                               | 107                                                                                                                                                       |

| 6 |                                                                             | •                                                                                                                   |                                                                                                                                                                                                                                                                      | <b>107</b><br>107                                                                                                                                         |

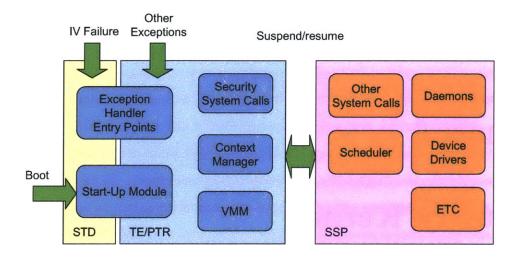

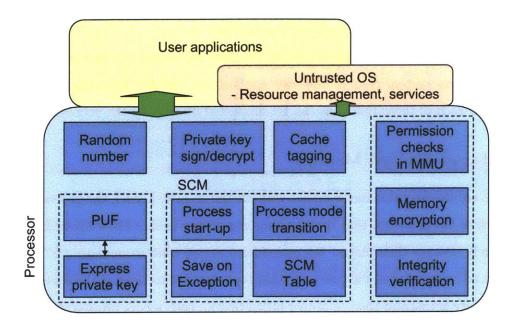

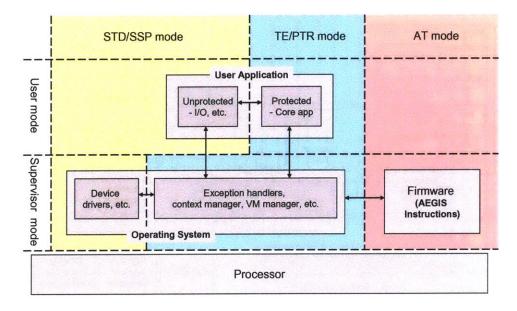

| 6 | 6.1                                                                         | Opera                                                                                                               | ating System Partition                                                                                                                                                                                                                                               | 107                                                                                                                                                       |

| 6 | $6.1 \\ 6.2$                                                                | Opera<br>Kerne                                                                                                      | ating System Partition                                                                                                                                                                                                                                               | 107<br>109                                                                                                                                                |

| 6 | 6.1                                                                         | Opera<br>Kerne<br>Protec                                                                                            | ating System Partition                                                                                                                                                                                                                                               | 107<br>109<br>110                                                                                                                                         |

| 6 | $6.1 \\ 6.2$                                                                | Opera<br>Kerne<br>Protec<br>6.3.1                                                                                   | ating System Partition                                                                                                                                                                                                                                               | 107<br>109<br>110<br>110                                                                                                                                  |

| 6 | $6.1 \\ 6.2$                                                                | Opera<br>Kerne<br>Protec<br>6.3.1                                                                                   | ating System Partition                                                                                                                                                                                                                                               | 107<br>109<br>110                                                                                                                                         |

| 6 | $6.1 \\ 6.2$                                                                | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3                                                                 | ating System Partition   el Start-Up   ction Management   Virtual Memory Manager   Context Manager   Exception Handlers                                                                                                                                              | 107<br>109<br>110<br>110<br>111<br>111                                                                                                                    |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3                                                                 | ating System Partition                                                                                                                                                                                                                                               | 107<br>109<br>110<br>110<br>111                                                                                                                           |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3<br>Securi                                                       | ating System Partition                                                                                                                                                                                                                                               | 107<br>109<br>110<br>110<br>111<br>111<br>112                                                                                                             |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3<br>Securi<br>6.4.1                                              | ating System Partition                                                                                                                                                                                                                                               | 107<br>109<br>110<br>110<br>111<br>111<br>112<br>113                                                                                                      |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3<br>Securi<br>6.4.1<br>6.4.2<br>6.4.3                            | ating System Partition   el Start-Up   ction Management   Virtual Memory Manager   Context Manager   Exception Handlers   ity System Calls   Execution Mode Transition   Private Key Operations   Read-Only ME Key Management                                        | <ol> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> <li>112</li> <li>113</li> <li>114</li> </ol>                                        |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3<br>Securi<br>6.4.1<br>6.4.2<br>6.4.3                            | ating System Partition   Al Start-Up   ction Management   Virtual Memory Manager   Context Manager   Context Manager   Exception Handlers   Exception Handlers   ity System Calls   Execution Mode Transition   Private Key Operations   Read-Only ME Key Management | <ol> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> <li>112</li> <li>113</li> <li>114</li> <li>115</li> <li>117</li> </ol>              |

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                   | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3<br>Securi<br>6.4.1<br>6.4.2<br>6.4.3<br><b>ogramm</b><br>Progra | ating System Partition                                                                                                                                                                                                                                               | <ol> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> <li>112</li> <li>113</li> <li>114</li> <li>115</li> <li>117</li> <li>117</li> </ol> |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>Pro</li> </ul> | Opera<br>Kerne<br>Protec<br>6.3.1<br>6.3.2<br>6.3.3<br>Securi<br>6.4.1<br>6.4.2<br>6.4.3                            | ating System Partition                                                                                                                                                                                                                                               | <ol> <li>107</li> <li>109</li> <li>110</li> <li>111</li> <li>111</li> <li>112</li> <li>113</li> <li>114</li> <li>115</li> <li>117</li> </ol>              |

|   |                | 7.1.3    | Declassification               | 122 |

|---|----------------|----------|--------------------------------|-----|

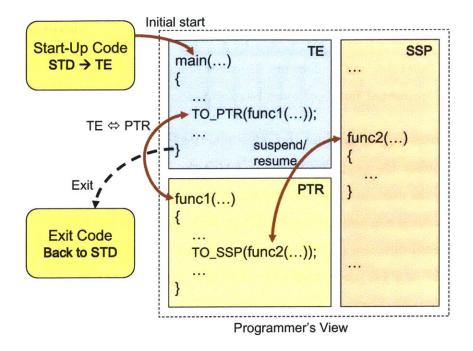

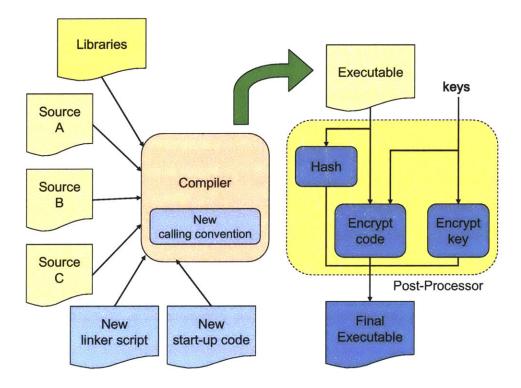

|   | 7.2            | Impler   | nentation                      | 123 |

|   |                | 7.2.1    | Compilation Flow               | 123 |

|   |                | 7.2.2    | Memory Layout                  | 125 |

|   |                | 7.2.3    | Start-Up Code                  | 126 |

|   |                | 7.2.4    | Mode Transition                | 128 |

|   |                | 7.2.5    | Multiple Decryption Keys       | 132 |

| 8 | $\mathbf{Ext}$ | ension   | s and Variants                 | 133 |

|   | 8.1            | Secure   | Booting                        | 133 |

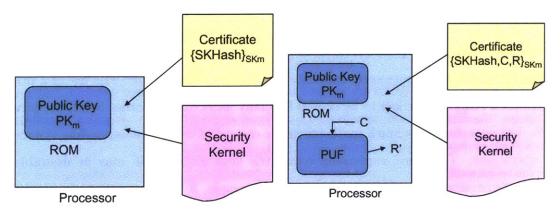

|   |                | 8.1.1    | Simple Public-Key Approach     | 134 |

|   |                | 8.1.2    | Per-Device Authorization       | 135 |

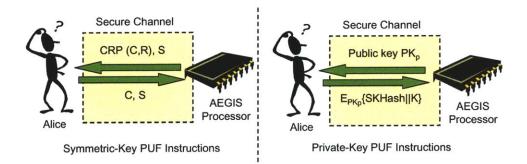

|   | 8.2            | PUF I    | nstructions for Symmetric Keys | 136 |

|   |                | 8.2.1    | Security Kernel                | 136 |

|   |                | 8.2.2    | User Applications              | 138 |

|   |                | 8.2.3    | Bootstrapping                  | 138 |

|   |                | 8.2.4    | Example                        | 139 |

|   |                | 8.2.5    | Additional Attacks on the PUF  | 139 |

|   | 8.3            | Remov    | ving the Security Kernel       | 141 |

|   |                | 8.3.1    | Secure Context Manager         | 142 |

|   |                | 8.3.2    | Virtual Memory Protection      | 143 |

|   |                | 8.3.3    | Security Instructions          | 146 |

|   |                | 8.3.4    | Security Discussion            | 147 |

|   | 8.4            | L-Hasl   | h Integrity Verification       | 150 |

| 9 | Арг            | olicatio | on Scenarios                   | 155 |

|   | 9.1            |          | lanagement                     | 155 |

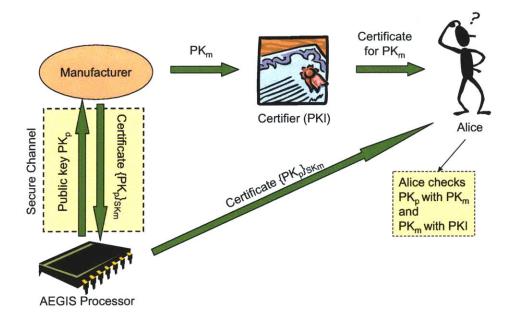

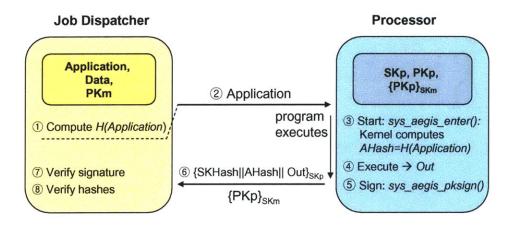

|   |                | 9.1.1    | Remote Introduction            | 156 |

|   |                | 9.1.2    | Direct Bootstrapping           | 157 |

|   | 9.2            |          | ed Execution                   | 158 |

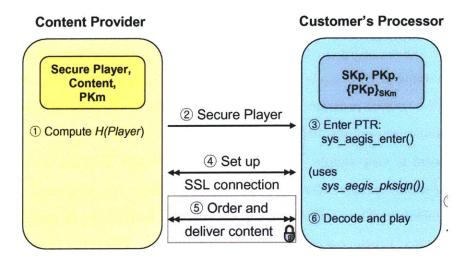

|   | 9.3            | Digita   | l Rights Management            | 159 |

|   | 9.4            | Ũ        | e Sensor Networks              | 160 |

| 10 Imp | lementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 163          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

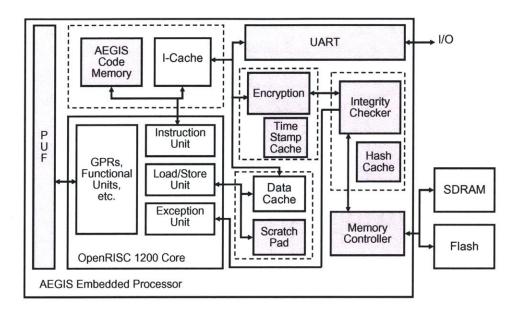

| 10.1   | Implementation Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 163          |

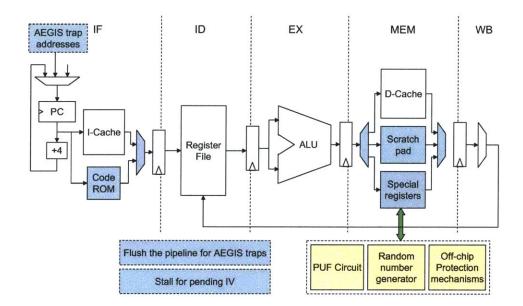

| 10.2   | Processor Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 165          |

|        | 10.2.1 AEGIS Trap Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 165          |

|        | 10.2.2 AEGIS Trap Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 166          |

|        | 10.2.3 Pipeline Stalls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 168          |

|        | 10.2.4 Instructions Manipulating Off-Chip Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 168          |

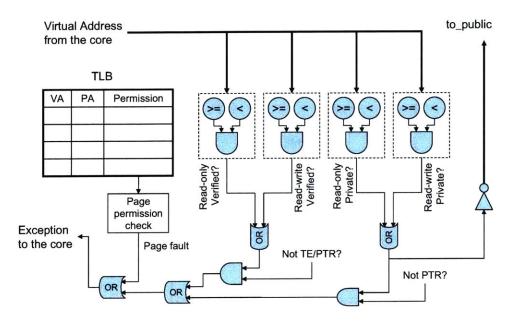

| 10.3   | Memory Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 169          |

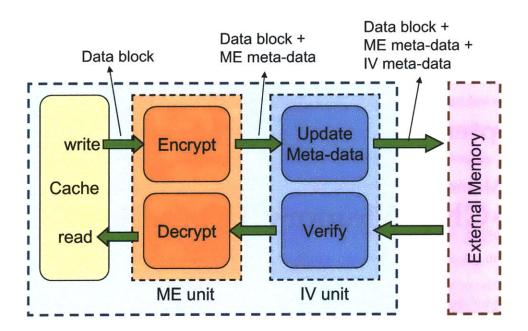

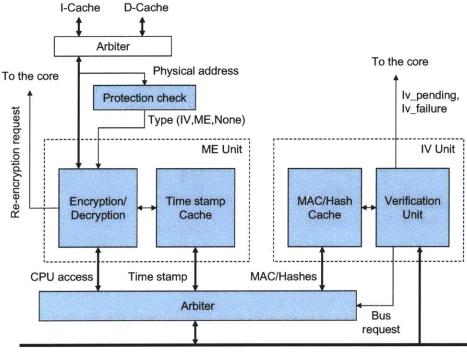

| 10.4   | Off-chip Protection Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 <b>7</b> 0 |

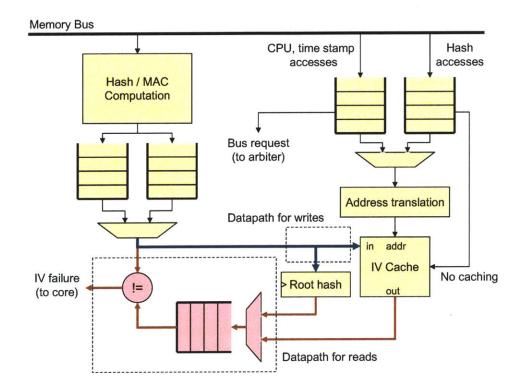

|        | 10.4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 170          |

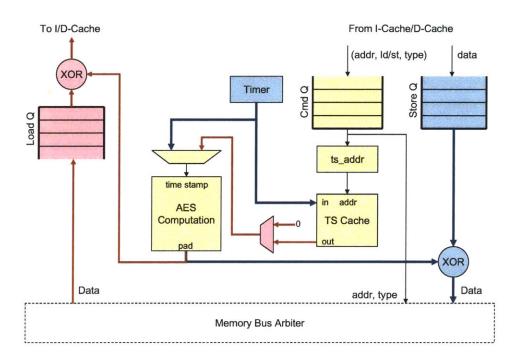

|        | 10.4.2 Encryption Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 172          |

|        | 10.4.3 Integrity Verification Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 174          |

| 11 Eva | luation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 177          |

|        | Memory Space Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 177          |

| 11.1   | 11.1.1 Encryption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 178          |

|        | 11.1.1 Energyption         11.1.2 Integrity Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 178          |

|        | 11.1.2         Integrity         Vermetation         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ·····         ······         ·····         ····· <td>179</td> | 179          |

| 11.9   | Hardware Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 179          |

| 11.2   | 11.2.1 Processor Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 180          |

|        | 11.2.1       Freeessor Farameters         11.2.2       Security Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 181          |

|        | 11.2.2       Security instructions         11.2.3       Silicon Area Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 182          |

|        | 11.2.3       Discussion on High Performance Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 182          |

| 11 3   | Performance I: Embedded Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 185          |

| 11.0   | 11.3.1       Security Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 186          |

|        | 11.3.1       Security instructions         11.3.2       Off-Chip Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 187          |

|        | 11.3.3       Suspended Secure Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 189          |

| 11 /   | Performance II: High-End Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105          |

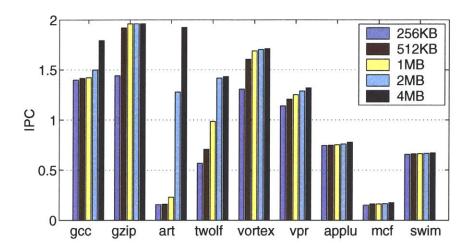

| 11.4   | 11.4.1       Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 190          |

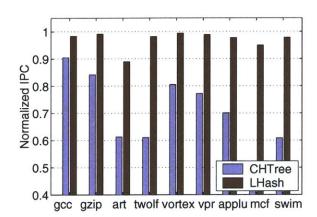

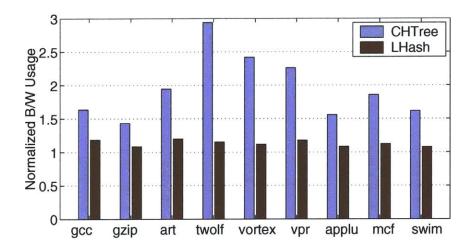

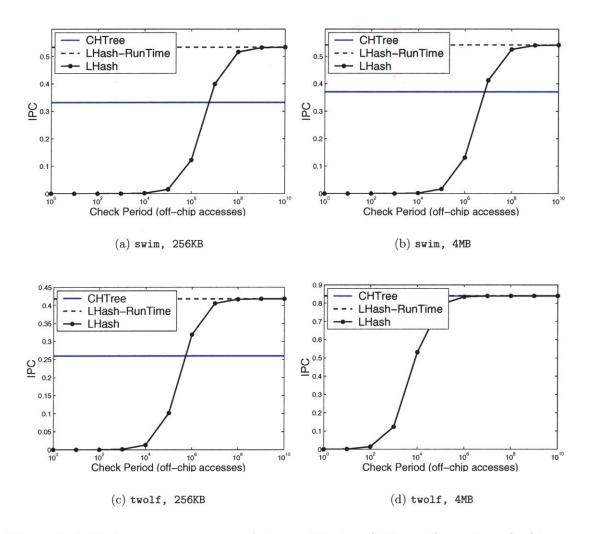

|        | 11.4.1       Simulation Framework         11.4.2       Integrity Verification: TE Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 190          |

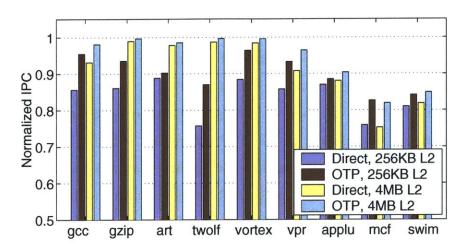

|        | 11.4.3 Memory Encryption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 191          |

|        | v v.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

|        | 11.4.4 Re-Encryption Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 198          |

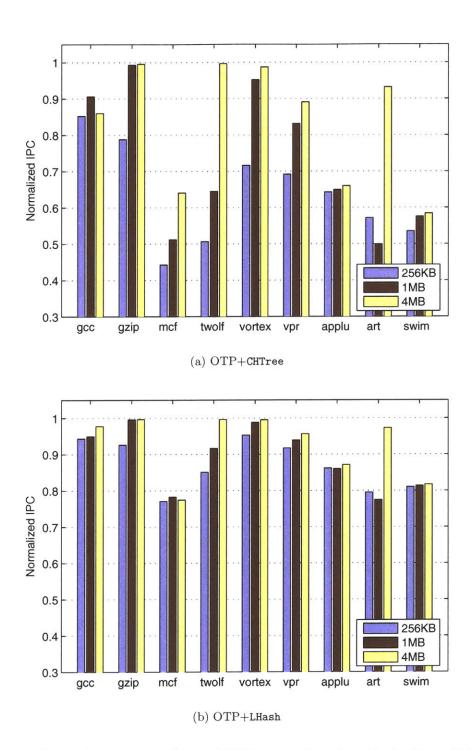

|         | 11.4.5 PTR Processing                             | 198        |

|---------|---------------------------------------------------|------------|

| 12 Rela | ated Work                                         | 201        |

| 12.1    | Physical Random Functions                         | 201        |

| 12.2    | Off-Chip Memory Protection                        | 202        |

|         | 12.2.1 Integrity Verification                     | 202        |

|         | 12.2.2 Encryption                                 | 203        |

|         | 12.2.3 Symmetric Multi-Processors (SMPs)          | 205        |

| 12.3    | Trusted Computing Platforms                       | 207        |

|         | 12.3.1 Secure Co-Processors                       | 207        |

|         | 12.3.2 Emerging Industry Platforms                | 207        |

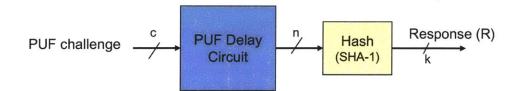

|         | 12.3.3 Execution Only Memory (XOM)                | 209        |

|         | 12.3.4 SP Architecture                            | 210        |