# Program Management Systems for the Semiconductor Processing Capital Equipment Supply Chain

by

## **Thomas B. Chandler**

B.S., Electrical Engineering, California State University Fresno, 1992 M.S., Electrical Engineering, University of Southern California, 1996

Submitted to the Sloan School of Management and the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degrees of

Master of Business Administration and Master of Science in Electrical Engineering and Computer Science

In Conjunction with the Leaders for Manufacturing Program at the Massachusetts Institute of Technology September 2004

©2004 Massachusetts Institute of Technology. All rights reserved.

| Sloan School of Management                                                            |

|---------------------------------------------------------------------------------------|

| Department of Electrical Engineering and Computer Science                             |

| June 25, 2004                                                                         |

| • , , , , , , , , , , , , , , , , ,                                                   |

|                                                                                       |

| Duane Boning, Nesis Supervisor                                                        |

| Professor of Electrical Engineering and Computer Science                              |

|                                                                                       |

| Care Dealuman Thesis Sumanisan                                                        |

| Sara Beckman, Thesis Supervisor                                                       |

| Irer, Haas School of Business, University of California at Berkeley                   |

|                                                                                       |

| 1,                                                                                    |

| Donald B. Rosenfield, Thesis Reader                                                   |

| Senior Lecturer of Management                                                         |

| -                                                                                     |

|                                                                                       |

| Margaret Andrews Executive Director of Masters Program                                |

| Margaret Andrews, Executive Director of Masters Program<br>Sloan School of Management |

| / Stoart School of Management                                                         |

|                                                                                       |

| Arthur C. Smith, Chairman, Committee on Graduate Students                             |

| Department of Electrical Engineering and Computer Science                             |

|                                                                                       |

MASSACHUSETTS INSTITUTE OF TECHNOLOGY JUL 0 1 2004 LIBRARIES

BARKER

ð

## Program Management Systems for the Semiconductor Processing Capital Equipment Supply Chain

by

## Thomas B. Chandler

Submitted to the Sloan School of Management and the Department of Electrical Engineering and Computer Science on June 25, 2004 in Partial Fulfillment of the Requirements for the Degrees of

> Master of Business Administration and Master of Science in Electrical Engineering and Computer Science

#### Abstract

The Capital Equipment Procurement group of Intel Corporation is responsible for developing and procuring the semiconductor processing capital equipment that is used throughout all of the company's development and manufacturing facilities. The semiconductor industry is faced with rapid technology change, increase in the complexity of the manufacturing process, and high cost of capital. In this challenging environment, the group is concerned with the following two issues required to maintain their leadership position in the industry.

First is the need to evaluate risk earlier in the capital equipment specification and development cycle to ensure that the semiconductor processing capital equipment is developed on schedule (on-line, on-time) at an affordable cost. A previous model developed and used in the manufacturing readiness phase of process development serves as the basis for a new risk assessment approach. Modifications, including new risk categories, criteria, and processes enable the new model to be applied earlier, in the technology development phase.

Second is the need for a more accurate cost model to capture the costs of new processes that employ equipment from existing processes at Intel. As Intel faces increasing cost pressure on some of the new commodity products it is developing, it must increase equipment reuse in its new process designs. A target costing model is developed that first sets target and baseline costs, and then tracks progress from the baseline cost until the target cost is achieved. This model is used to closely manage various cost reduction programs or projects being undertaken in its process development organization.

The overall theme of this thesis is to demonstrate how these two program management systems can be used to manage the development of new manufacturing equipment such as needed in the semiconductor and other capital intensive industries.

#### Thesis Advisors:

Sara L. Beckman, Senior Lecturer, Haas School of Business, University of California at Berkeley

Duane Boning, Professor of Electrical Engineering and Computer Science

Thesis Reader:

Donald B. Rosenfield, Senior Lecturer, Sloan School of Management

This page is intentionally left blank.

## Acknowledgements

First, I wish to gratefully acknowledge the Leaders for Manufacturing Program for its support of this work at the Massachusetts Institute of Technology.

Special thanks go to my thesis advisors, Sara Beckman and Duane Boning, for their guidance and insights during the internship and thesis writing process.

Additionally, I would like to extend my appreciation to Intel for sponsoring the internship and Mark Sandoval, my supervisor at Intel, for his guidance throughout the internship.

Most importantly, I would like to thank my wife, Anne Di Pasquale, for everything.

This page is intentionally left blank.

.

| Abstract       |                                                                     | 3    |

|----------------|---------------------------------------------------------------------|------|

| Acknowledge    | ements                                                              | 5    |

| Table of Con   | tents                                                               | 7    |

| List of Figure | es                                                                  | . 10 |

| List of Table  | S                                                                   | .11  |

| Chapter 1: O   | verview of Thesis                                                   | . 13 |

| Chapter 2: Tl  | ne Intel Corporation and the Capital Equipment Procurement group    | . 15 |

| 2.2 Inte       | el Corporation                                                      | .15  |

| 2.3 Sei        | niconductor supply chain                                            | . 17 |

| 2.4 Ca         | pital Equipment Procurement group                                   | . 18 |

| 2.5 Ma         | inufacturing environment at Intel in 2003                           | . 19 |

| 2.6 Pro        | oduct and process development timeline                              | .20  |

| 2.7 Pro        | ocess and product terminology                                       | .21  |

| 2.8 Th         | e importance of program management within the CEP                   | .22  |

| 2.9 Op         | portunities to improve the existing program management tools        | .23  |

| Chapter 3: Li  | terature review in project risk management                          | .25  |

| 3.1 Int        | roduction to project risk management                                | .25  |

| 3.1.1          | Example to introduce the concept of risk management                 | .26  |

| 3.1.2          | Risk: inevitable but manageable                                     | .27  |

| 3.1.3          | Purpose of project risk management                                  | .28  |

| 3.2 Ov         | erview of six-phase approach of risk management                     | . 28 |

| 3.2.1          | Risk management planning                                            |      |

| 3.2.2          | Risk identification                                                 | . 30 |

| 3.2.3          | Qualitative Risk Analysis                                           | . 31 |

| 3.2.4          | Quantitative Risk Analysis                                          | . 32 |

| 3.2.5          | Risk Response Planning                                              | . 33 |

| 3.2.6          | Risk Monitoring and Control                                         | . 33 |

| 3.3 Pro        | oject risk management at a semiconductor company                    | . 34 |

| 3.3.1          | Risk identification                                                 |      |

| 3.3.2          | Risk quantification                                                 |      |

| 3.3.3          | Risk response development                                           |      |

| 3.3.4          | Risk control                                                        |      |

| 3.4 Ch         | apter summary                                                       | 38   |

| Chapter 4: E   | xisting and new risk assessment systems                             | 39   |

|                | pject risk management at Intel                                      |      |

| 4.2 Ex         | isting manufacturing readiness risk assessment                      | 41   |

| 4.2.1          | Risk management planning background                                 |      |

| 4.2.2          | Risk criteria                                                       |      |

| 4.2.3          | Risk matrix                                                         |      |

| 4.2.4          | Risk monitoring and control                                         | 46   |

| 4.3 Th         | e need for a new technology development risk assessment methodology | 47   |

| 4.4 Ne         | w technology development readiness risk assessment                  | 48   |

| 4.4.1          | Risk management planning background                                 | 48   |

| 4.4.2          | Developing and identifying the new risk criteria                    | 49   |

# **Table of Contents**

| 4.4.3 Risk criteria analysis                                                      | 51                |

|-----------------------------------------------------------------------------------|-------------------|

| 4.4.4 Quantitative risk analysis                                                  |                   |

| 4.4.5 Risk response planning, monitoring, and control                             |                   |

| 4.5 Risk assessment example                                                       |                   |

| 4.5 Chapter summary                                                               | Critical analysis |

| of project risk management                                                        | •                 |

| 5.1 Risk identification                                                           |                   |

| 5.2 Rank both risk probability and impact                                         |                   |

| 5.3 Institute risk assessment as early as cost-effective in the development cycle | 64                |

| 5.4 Implementation with existing IT systems                                       |                   |

| 5.5 Chapter summary                                                               | review of cost    |

| management systems                                                                |                   |

| 6.1 History and primary functions of cost management systems                      | 69                |

| 6.2 The four phases of cost management systems                                    |                   |

|                                                                                   |                   |

| 6.3 Activity based costing                                                        |                   |

| 6.4 Target costing for product development                                        |                   |

| 6.5 Total cost of ownership                                                       | 76                |

| 6.6 Chapter summary                                                               |                   |

| Chapter 7: Target Cost-Based Modeling at Intel                                    |                   |

| 7.1 Expected wafer cost models at Intel                                           |                   |

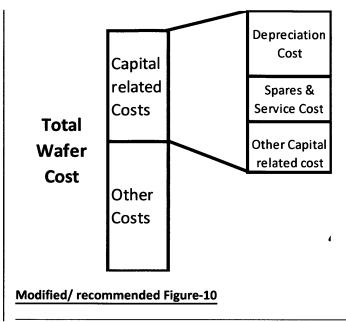

| 7.1.1 Cost models for the finance group responsible for total wafer cost          |                   |

| 7.1.2 Cost models for the Capital Equipment Procurement group                     |                   |

| 7.2 Different cost model requirements for the existing and new models             |                   |

| 7.2.1 Allocation of personnel across process technologies                         | 81                |

| 7.2.2 Type of semiconductor process equipment                                     |                   |

| 7.2.3 Characterization of manufacturing process                                   |                   |

| 7.2.4 Timeline requirements to set the baseline semiconductor manufactu           |                   |

| 7.2.5 Tool quantities for the expected production volume                          |                   |

| 7.2.6 Feedback from users of the existing GEN-T model                             |                   |

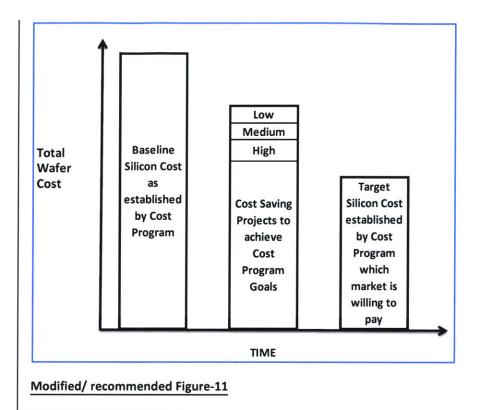

| 7.3 Target costing approach                                                       |                   |

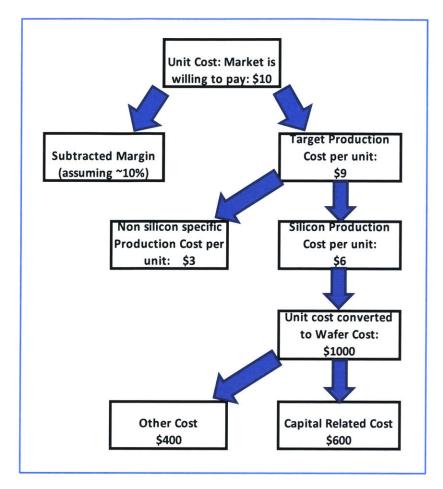

| 7.4 Wafer target cost                                                             |                   |

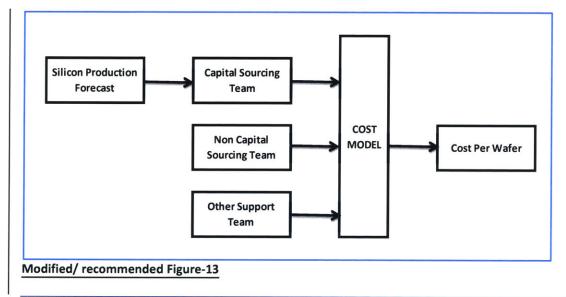

| 7.5 Cost model to set baseline cost                                               |                   |

| 7.5.1 Areas included in cost model                                                | 00                |

| 7.5.2 Areas excluded from cost model                                              |                   |

| 7.5.3 New capital                                                                 | 90                |

| 7.5.4 Conversions kits                                                            | 02                |

| 7.5.5 Reuse                                                                       | 92                |

| 7.5.6 Spares                                                                      | 02                |

| 7.5.7 Service                                                                     |                   |

| 7.5.8 End of Life (EOL) costs                                                     | 0.4               |

| 7.6 Project cost tracker                                                          |                   |

| 7.6.1 Project cost tracker description                                            |                   |

| 7.6.2 Project cost tracker usage process                                          |                   |

| 7.6.3 Cost accuracy dependence upon users                                         |                   |

| 7.7 Example of cost model usage                                                   |                   |

| 7.8      | Chapter summary                                                      | 103       |

|----------|----------------------------------------------------------------------|-----------|

| Chapter  | 8: Critical analysis of cost systems                                 |           |

| 8.1      | Target costing best practices currently followed at Intel            | 105       |

| 8.2      | Recommendation: Increase focus on target costing                     | 107       |

| 8.3      | Recommendation: Improve the target cost setting process              | 108       |

| 8.4      | Recommendation: Incorporate expected cost ranges into cost systems   |           |

| 8.5      | Recommendation: Follow the cardinal target costing rule              | 110       |

| Chapter  | 9: Final thoughts                                                    |           |

| 9.1      | Program management systems evolve over time to maximum effectiv      | eness.113 |

| 9.2      | Risk assessments allow employees to flag issues to senior management |           |

| 9.3      | Target cost models should be transparent and easy to use             | 114       |

| 9.4      | Identify and manage key stakeholders                                 | 115       |

| 9.5      | Conclusion                                                           | 116       |

| Bibliogr | aphy                                                                 | 117       |

|          | ix A: List of risk sources                                           |           |

|          |                                                                      |           |

# **List of Figures**

-

| Figure 2: How Capital Equipment Procurement fits into the organization19Figure 3: Product and Process Development Timeline21Figure 4: The timing and impact of management attention27Figure 5: Risk probability and impact matrix32Figure 6: Risk assessment timeline40Figure 7: Manufacturing readiness risk system42Figure 8: Manufacturing readiness risk matrix46Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87 | Figure 1: Semiconductor Supply Chain                  | . 17 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|

| Figure 3: Product and Process Development Timeline21Figure 4: The timing and impact of management attention27Figure 5: Risk probability and impact matrix32Figure 6: Risk assessment timeline40Figure 7: Manufacturing readiness risk system42Figure 8: Manufacturing readiness risk matrix46Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                         |                                                       |      |

| Figure 4: The timing and impact of management attention27Figure 5: Risk probability and impact matrix32Figure 6: Risk assessment timeline40Figure 7: Manufacturing readiness risk system42Figure 8: Manufacturing readiness risk matrix46Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                                                                             |                                                       |      |

| Figure 5: Risk probability and impact matrix32Figure 6: Risk assessment timeline40Figure 7: Manufacturing readiness risk system42Figure 8: Manufacturing readiness risk matrix46Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                                                                                                                                      |                                                       |      |

| Figure 6: Risk assessment timeline40Figure 7: Manufacturing readiness risk system42Figure 8: Manufacturing readiness risk matrix46Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                                                                                                                                                                                    |                                                       |      |

| Figure 7: Manufacturing readiness risk system.42Figure 8: Manufacturing readiness risk matrix46Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                                                                                                                                                                                                                       |                                                       |      |

| Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                                                                                                                                                                                                                                                                                                                      |                                                       |      |

| Figure 9: Partial risk ranking questionnaire56Figure 10: CEP influenced wafer costs79Figure 11: Target cost model approach85Figure 12: Wafer target cost87                                                                                                                                                                                                                                                                                                                                                                      | Figure 8: Manufacturing readiness risk matrix         | .46  |

| Figure 11: Target cost model approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |      |

| Figure 11: Target cost model approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |      |

| Figure 12: Wafer target cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |      |

| Figure 13: Baseline cost set model functional diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |      |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 13: Baseline cost set model functional diagram |      |

# List of Tables

| Table 1: Process and product terminology                              | 22  |

|-----------------------------------------------------------------------|-----|

| Table 2: Example results from using risk analysis tool                |     |

| Table 3: Qualitative analysis tool after risk identification          |     |

| Table 4: Results from the quantitative analysis tool                  |     |

| Table 5: Risk prioritizes from analysis tool                          |     |

| Table 6: Risk response development                                    |     |

| Table 7: Outcome table for program                                    |     |

| Table 8: Manufacturing readiness risk criteria                        |     |

| Table 9: Technology development risk criteria                         |     |

| Table 10: Expected semiconductor wafer costs                          |     |

| Table 11: Different requirements for the existing and new cost models |     |

| Table 12: Project cost tracker                                        |     |

| Table 13: Tool baseline cost and equipment target cost                | 98  |

| Table 14: Tool level target costs                                     | 99  |

| Table 15: Productivity improvement and price reductions               | 100 |

| Table 16: Tool allocation shift and negotiated cost reduction         | 101 |

| Table 17: Conversion kit with higher total cost of ownership          |     |

| Table 18: Achievement of total equipment cost reductions              |     |

| Table 19: Possible risk sources                                       |     |

This page is intentionally left blank.

#### **Chapter 1: Overview of Thesis**

The Capital Equipment Group (CEP) at Intel Corporation is responsible for developing and procuring the semiconductor processing capital equipment used in wafer processing fabs throughout the world. In that effort, it worries about a number of issues that affect Intel's ability to maintain a one-generation lead over the competition. Of those, two were of particular concern to this thesis: First, CEP wanted to evaluate risk earlier in the capital equipment specification and development cycle than they had been to date to ensure that the semiconductor processing capital equipment is developed on schedule (on-line, on-time) at an affordable cost. This thesis takes a model Intel had developed and implemented in the manufacturing readiness phase of process development, and modifies it to be applied earlier in the technology development phase. Second, CEP wanted to develop a more accurate cost model to capture the costs of new processes when those processes employ equipment from existing processes at Intel. As Intel faces increasing cost pressure on some of the new products it is developing, it wishes to increase equipment reuse in its new process designs. Further, it wishes to closely manage various cost reduction programs or projects being undertaken in its process development organization.

The discussion of these two issues is the core topic of this thesis. However, since these issues are separate analyses, involving two separate products and requiring interaction with distinct functional groups within Intel, the thesis will be divided in two separate sections: one, addressing project risk management, and the second, addressing cost modeling for new product development. The overall theme is based upon the project cost and risk management associated with the development of a new product produced with a new manufacturing process technology. A secondary theme through these sections is to demonstrate how these program management systems can be valuable for other industries, especially those with highly complex capital intensive manufacturing processes.

Chapter 2 introduces the Intel Corporation and shows how the Capital Equipment Procurement group fits into the company in the current manufacturing environment. We also discuss Intel's product lines, process and product terminology, and the

13

semiconductor supply chain. Finally, we review program management and how Intel uses it as a tool for competitive success.

Chapter 3 reviews the current project risk management literature and develops a general framework that is used for project risk management. This project risk management framework is then applied in Chapter 4 to the extension of an existing manufacturing risk assessment methodology earlier into the process and product development cycle. After working through the thought process of this new model, in Chapter 5 we critically analyze the project risk management system at Intel and provide potential opportunities for improvement considering the current state of the industry.

In the next part of the thesis, we transition to discussion of cost modeling as a second equipment development management tool. Chapter 6 reviews the current cost modeling literature and shows the evolution of cost models over time before focusing in on target costing. Chapter 7 discusses the product target cost methodology used at Intel and then describes the cost model that was developed during the internship for the semiconductor processing equipment that will be used to produce a new product. In Chapter 8, the cost model developed at Intel is critically analyzed and compared to current industry best practices from the literature. Several opportunities for improvements considering current industry trends are described.

Chapter 9 is the overall conclusion to the thesis as a whole, stating the key ideas and results that can be applied to other similar capital intensive manufacturing industries.

#### **Chapter 2: The Intel Corporation and the Capital Equipment Procurement group**

This chapter introduces Intel Corporation and the Capital Equipment Procurement group (CEP), which will be at the center of this thesis. To understand what CEP does, we review Intel's business, the semiconductor supply chain, the Capital Equipment Procurement group's function within Intel, the manufacturing environment at Intel in 2003, the product and process development timeline, and terminology used throughout the thesis. Finally, we review program management for semiconductor products within CEP; the importance of program management (as a way that Intel maintains its lead in the industry) and opportunities to improve the existing program management tools.

## 2.2 Intel Corporation

Intel was founded in 1968. After introducing the first microprocessor in 1971, it rapidly grew to its current status as a leader in the semiconductor industry. Most every computer user has heard the slogan "Intel Inside" or can recognize the Intel signature sound following television commercials from various computer manufacturers.<sup>1</sup> Although Intel is a Dow Jones company with 31 billion dollars in revenue in 2003,<sup>2</sup> it is in a rapidly changing industry with semiconductor process technologies and products becoming outdated in only two years. Intel is able to stay in its leadership position by leveraging its ability to flawlessly execute the simultaneous introduction of an initial lead product with a new generation of process technology.<sup>3</sup> Efficiently and effectively introducing affordable products is achieved with solid program management.

Intel Corporation designs, develops, manufactures and markets computing and communications products at various levels of integration.<sup>4</sup> It has three product line operating segments: the Intel Architecture business, which is composed of the Desktop Platforms Group, the Mobile Platforms Group and the Enterprise Platforms Group; the Intel Communications Group (ICG), and the Wireless Communications and Computing Group (WCCG). The Intel Architecture operating segment's products include microprocessors and related chipsets and motherboards. It is the microprocessors group

<sup>&</sup>lt;sup>1</sup> Jackson, pp. 313-316.

<sup>&</sup>lt;sup>2</sup> 2003 Intel Corporation Annual Report

$<sup>^{3}</sup>$  Hayes, p. 3.

<sup>&</sup>lt;sup>4</sup> 2003 Intel Corporation Annual Report

that people think of when they think of Intel. We discuss this group in the context of the risk assessment part of this paper.

ICG's products include wired Ethernet and wireless connectivity products, network processing components and embedded computing products. WCCG's products include flash memory, application processors and cellular baseband chipsets for cellular handsets and hand-held devices. We discuss this group in part two of this thesis, when we discuss cost models for High-Mix Low-Volume products (HMLV) such as flash memory. The company's products are sold directly to Original Equipment Manufacturers (OEMs), and through retail and industrial distributors, as well as reseller channels throughout the world.<sup>5</sup>

Within Intel, the Capital Equipment Procurement group (CEP) is responsible for developing and procuring the semiconductor processing capital equipment used in wafer processing fabs for all three product line operating segments and for all the fabs worldwide (Israel, Ireland, California, Oregon, Arizona, New Mexico, Colorado, and Massachusetts). This means that CEP works with semiconductor equipment manufacturing companies to develop new machines that have the new capabilities required to produce the next generation chips. Low-Mix High-Volume (LMHV) microprocessor products require new machines every generation since the newest rapidly changing technology is required to produce industry leading products.

The development and purchase of this equipment requires CEP to control billions of dollars. In fact, this highly specialized equipment is a major cost driver in chip prices.<sup>6</sup> The concurrent drop in average semiconductor selling prices and increase in product diversity is causing Intel to augment its focus on cost and risk issues in the capital equipment development and procurement process. Specifically, Intel is interested in moving its examination of cost and risk upstream in the process development process to identify issues and opportunities earlier and further ensure successful manufacturing ramps and product launches.

<sup>&</sup>lt;sup>5</sup> Ibid.

<sup>&</sup>lt;sup>6</sup> Tortoriello

## 2.3 Semiconductor supply chain

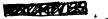

As shown in Figure 1 below, the semiconductor supply chain begins with raw silicon ingots. After these ingots are sliced into thin wafers, they are bought by Intel and are brought to a Fab (or plant) where they are processed with chemicals on the highly specialized machines that CEP has developed and procured to make many individual devices on a single wafer. The processed silicon wafers are then transported to a chip assembly and test factory where they are tested, diced into individual chips, and assembled into packages that can be attached to circuit boards.<sup>7</sup>

Figure 1: Semiconductor Supply Chain

Development and procurement of the machines that make the chips (the "tools") in the wafer factory or fab occurs several years before the supply chain is in operation. Equipment cost is a major portion of the total cost to produce a semiconductor. Standard & Poor's *Semiconductors* reports the following on the huge capital investments:

Each year, semiconductor manufacturers invest significant sums of money in new plants and equipment. Currently, a state-of-the-art fabrication facility, or fab – the plant where chips are made – costs nearly \$3 billion to build. In 1984, the figure was just \$10 million. According to Sematech, an industry trade group, this cost could balloon to \$10 billion by 2015, making a semiconductor manufacturing plant the most expensive facility in the world – more costly than a nuclear power plant.<sup>8</sup>

Including cost restraints, time is also a limited resource that the Intel supply chain has to manage. Semiconductor processing is a highly complex process requiring several hundred processing steps performed on around one hundred unique semiconductor processing tools.<sup>9</sup> The continuation of Moore's Law, which states that the number of transistors that can be placed on a given silicon chip will double every eighteen months, causes modern fabs to be outdated in only two years.<sup>10</sup> Further complicating this process are the globally dispersed fabs and equipment suppliers.<sup>11</sup>

# 2.4 Capital Equipment Procurement group

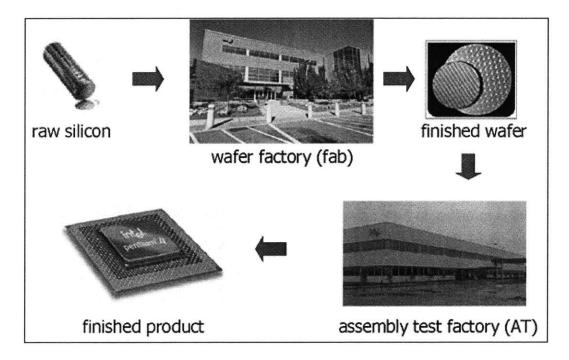

As shown in Figure 2, the Capital Equipment Procurement group plays an integral role within the Intel manufacturing organization. The group's engineers and commodity managers direct information flow between suppliers, development factories, manufacturing factories and other internal departments. They are also responsible for overseeing the current supply line and creating long-term supplier strategies. Supervising variable information requires the creation of business processes that must be flexible enough to withstand changing business conditions. Despite information volatility, managing the total cost of ownership for semiconductor processes is an important function that the group must perform.

<sup>&</sup>lt;sup>7</sup> Tortoriello, pp. 14-16.

<sup>&</sup>lt;sup>8</sup> Smith, p. 18.

<sup>&</sup>lt;sup>9</sup> Tortoriello, pp. 14-16.

<sup>&</sup>lt;sup>10</sup> *Ibid.* p.14.

<sup>&</sup>lt;sup>11</sup> *Ibid.* p. 9.

Figure 2: How Capital Equipment Procurement fits into the organization

## 2.5 Manufacturing environment at Intel in 2003

The semiconductor industry has historically been characterized by having high capital costs, rapidly changing manufacturing technology, highly cyclical markets and strong competition.<sup>12</sup> The manufacturing environment at Intel today consists of more fabs, faster product ramp times, greater cost pressure, more products and aggressive equipment suppliers than in the past.<sup>13</sup>

Intel developed a large network of semiconductor manufacturing fabs during a period of rapid growth in the 1990s. Today Intel owns and operates eight fabrication facilities throughout the world. This makes coordination among the development organization, all of the fabs and the capital equipment suppliers difficult.

<sup>&</sup>lt;sup>12</sup> Smith, pp. 1-6.

<sup>&</sup>lt;sup>13</sup> Ibid., pp. 16-24.

The average selling prices for the core microprocessor business are dropping as the prices for computers fall. This creates increased pressure to maintain low costs to sustain market leadership.<sup>14</sup>

Faster and steeper manufacturing ramps of new process technologies require flawless execution to obtain returns on large capital expenditures. It is imperative that all parts of the manufacturing process and the associated tools are ready to go for the ramp of a new process technology. The failure of one small part in the manufacturing process will create huge losses as expensive equipment lays idle and the competition gains ground.<sup>15</sup>

As Intel diversifies away from the core microprocessor business, it offers an increasingly larger number of semiconductor products. In addition to multiple different microprocessors for different market segments, Intel produces chips for wired Ethernet, wireless connectivity, flash memory, application processors, and cellular baseband chips, just to name a few.<sup>16</sup> This requires major changes as the company determines how to effectively produce a high mix of products produced in low volumes.

Suppliers that are under pressure to reduce new semiconductor processing equipment costs are aggressively protecting their revenue streams by increasing costs for spare parts and service for maintenance and repairs.<sup>17</sup> Intel must be careful to understand the entire cost of ownership when purchasing new semiconductor processing tools.

## 2.6 Product and process development timeline

Intel develops a new generation of process technology simultaneously with a new product. This process and product development cycle for new semiconductor products at Intel, shown in Figure 3, is broken up into sections of time.

• **Strategic enabling**: Basic research conducted with universities and suppliers to develop knowledge and technologies for future semiconductor processes.

<sup>&</sup>lt;sup>14</sup> Smith., pp. 16-24.

<sup>&</sup>lt;sup>15</sup> Weber, pp. 420-426.

<sup>&</sup>lt;sup>16</sup> Intel Corporation Annual Report

<sup>17</sup> Tortoriello

- **Pathfinding**: A proof-of-concept of the entire process and all of the semiconductor processing tools is developed.

- **Technology development**: The designs of the process, product and associated semiconductor processing tools are all finalized.

- **Manufacturing ramp**: The process and product knowledge is transferred from the development fab to the volume fab as the volume fab begins to a produce a product on the new semiconductor process technology.

- Volume production: Products are fully transitioned from the development factories to the production factories where they are produced in volume.

|                       | Cost                                                         | Model                                            |                       |                      |

|-----------------------|--------------------------------------------------------------|--------------------------------------------------|-----------------------|----------------------|

|                       | Technology<br>Development<br>Readiness<br>Risk<br>Assessment | Manufacturing<br>Readiness<br>Risk<br>Assessment | н<br>Н                |                      |

| Strategic<br>Enabling | Pathfinding                                                  | Technology<br>Development                        | Manufacturing<br>Ramp | Volume<br>Production |

| years                 | one year                                                     | one year                                         | months                | years                |

#### **Figure 3: Product and Process Development Timeline**

The majority of the resources from the Capital Equipment Procurement group are involved in the technology development stage of the product development cycle. Smaller percentages of people are assigned to the pathfinding, ramp, and production stages of development.

### 2.7 Process and product terminology

As a general introduction to the products and processes that are discussed in upcoming chapters, we identify in Table 1 the different products examined in this thesis, the processes used to produce them, and characterizations of the manufacturing process. Note that some of the products are High-Mix Low-Volume, while others are Low-Mix High-Volume, and that the products are in different phases of development (pathfinding

21

or technology development). These differences will become important in later chapters of this thesis.

|                                           | Process technology |                |               |

|-------------------------------------------|--------------------|----------------|---------------|

|                                           | GEN-T              | GEN-W          | GEN-Q         |

|                                           | Technology         | pathfinding Y  | pathfinding Y |

| Current phase of the development cycle    | development        | nm             | nm            |

| minimum feature size                      | X nm               | Y nm           | Y nm          |

| lead product                              | microprocessor     | microprocessor | flash HMLV    |

| Characterization of manufacturing process | LMHV               | LMHV           | flash HMLV    |

|                                           |                    | Chapter 4 and  |               |

| discussion                                | Chapter 4 and 7    | 7              | Chapter 7     |

**Table 1: Process and product terminology**

## 2.8 The importance of program management within the CEP

Program management is the application of knowledge, skills, tools, and techniques to project activities to meet project requirements. Program management is accomplished through the use of many different processes such as: initiating, planning, executing and controlling<sup>18</sup>. Within the Capital Equipment Procurement group, program management requires that all of the semiconductor processing tools be procured on time, meet process requirements, and meet program affordability objectives. Two important systems that are used to manage programs are the risk assessment methodology and the total cost of ownership affordability model.

A manufacturing readiness risk assessment methodology is currently used to ensure that all of the semiconductor processing tools will be available to successfully ramp a new process technology. This system is used during technology development to ensure that all of the tools will be procured in time to meet the ramp and that they will meet the performance requirements for the new process. The goal of this risk assessment methodology is to save valuable money and time and ensure that the project is on line, on time.

A cost of ownership affordability model is used to ensure that the costs of the machinery (over its depreciation life) 1) allow Intel to meet its target competitive microprocessor prices and 2) do not grow such that Intel's margins on chips are eroded. Producing products that are affordable is increasingly important within the current

<sup>&</sup>lt;sup>18</sup> PMBOK® Guide.

manufacturing business environment, especially with the advent of globalization and the decreasing cost of microprocessors.<sup>9</sup>

## 2.9 Opportunities to improve the existing program management tools

The existing processes within the Capital Equipment Procurement group are highly effective. However, the constantly changing dynamics of the semiconductor processing capital equipment industry require that most processes stay in an iterative state of constant improvement to maintain industry leadership. Intel identified two opportunities for process improvement that became the basis of the internship that led to this thesis:

- 1. Intel desires to control whether products built on new semiconductor process technologies will be manufactured according to schedule: "on time, on line." Intel requires a manufacturing readiness risk assessment model that will be extended earlier in the development cycle to assess the risk of successful completion of the technology development phase. Therefore, we developed a risk assessment methodology for the pathfinding stage discussed above (and detailed further in the Chapter 4 on risk).

- 2. Intel desires to better manage the price of semiconductor processing capital equipment used to create multiple different types of chips (such as flash) such that the cost of the expensive machinery will enable the production of affordable products. Therefore, a new cost model is developed to ensure cost control on equipment for the GEN-Q process used for its high-mix low-volume flash business.

'9 Smith.

This page is intentionally left blank.

#### **Chapter 3: Literature review in project risk management**

What is the risk that we will not be on line, on time with production? How do we assess this risk early in a product development cycle? These are some of the issues that concern a program manager during the development of a new product. Assessing and responding to these issues is crucial to a new product's successful introduction into the market.<sup>20</sup> This is especially important in semiconductor manufacturing at a modern fab where the loss rates can exceed \$10,000 per minute when production is delayed.<sup>21</sup>

This chapter provides a review of the literature on project risk management, and an example of risk management at a semiconductor company.

## 3.1 Introduction to project risk management

Project risk management is the art and science of identifying, assessing and responding to project risk throughout the life of a project and in the best interests of the project's objectives.<sup>22</sup> A project risk management framework will serve to structure the discussion of risk in this thesis; this framework consists of six phases: risk management planning, risk identification, qualitative risk analysis, quantitative risk analysis, risk response planning, and risk monitoring and control.<sup>23</sup> These will be described in more detail later in the chapter.

A company's future is determined in part by a series of judgments and decisions made within the company. Ideally, business decisions would be made in an environment of total certainty where all the necessary information is available and the future outcome of decisions can be predicted with confidence. In reality, most decisions are made without complete information resulting in uncertainty in the outcome. In the extreme case, nothing is known about the outcome and total uncertainty prevails.<sup>24</sup>

To introduce the concept of risk assessment, the following is a simple example.

<sup>23</sup> A Guide to the Project Management Body of Knowledge (hereinafter referred to as "PMBOK® Guide"), pp. 127-146.

<sup>&</sup>lt;sup>20</sup> Pritchard, pp. 1-48.

<sup>&</sup>lt;sup>21</sup> Weber, p. 420.

<sup>&</sup>lt;sup>22</sup> Wideman, p. II-3.

<sup>&</sup>lt;sup>24</sup> Wideman, 11-17.

## 3.1.1 Example to introduce the concept of risk management

Max Wideman gives this example in his book, *Project & Program Risk* Management:

[O]ne way of avoiding a possible traffic jam while driving on the highway to a particular destination is to consider alternative forms of transportation. Granted that each may have its own particular set of risks, but careful comparison should identify the best set of alternatives with the lowest overall degree of uncertainty or risk of arriving late. However, the impact of each on the time and cost of the journey must also be taken into account if the best overall arrangement for a successful arrival is to be achieved. The selection may well depend on the relative priorities given to the cost, schedule, and quality of the journey. If the real objective of the exercise is to hold a meeting, then perhaps the opportunity could be taken to hold the meeting at a more favorable intermediate location.<sup>25</sup>

This example shows that there are subjective factors to risk assessment (overall quality of the journey) and there are objective factors (cost and schedule). There are also many variable factors that make predicting an outcome uncertain. For example, after quantifying the risk of avoiding a possible traffic jam, an accident on the road may occur spontaneously throwing off the risk assessment made earlier. This highlights the iterative nature of risk assessment; risk must be reevaluated at various periods on the time continuum. Further, one can make better assessments of risk if one surveys knowledgeable people. For example, in Wideman's hypothetical example, one can survey those who drive that route and avoid traffic jams, ask them what went right and what went wrong, and then change a risk assessment model based on those inputs. Finally, this example shows that information early in the process (such as checking weather forecasts before going) can help risk assessment.

Austin (2004) identifies many sources of risk that a manager has to deal with every day: financial resource risk (foreseeing cash flow shortages), human resource risk (foreseeing key employees and knowledge holders leaving a project or company), supply risk (foreseeing adequate supply and managing buffer stock) and quality risk (foreseeing compliance with standards).<sup>26,27</sup>

<sup>&</sup>lt;sup>25</sup> Ibid, p. I-2.

<sup>&</sup>lt;sup>26</sup> Austin, pp. 101-110.

## 3.1.2 Risk: inevitable but manageable

Survival in today's highly competitive business environment is achieved by pursuing risky development projects with uncertain outcomes. The goals of risk management are to identify project risks and develop strategies to significantly reduce them or avoid them altogether if possible.<sup>28</sup>

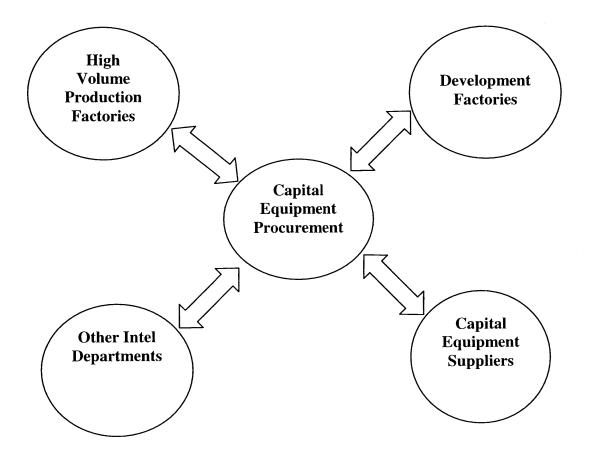

Projects and the associated project risk factors are characterized by change throughout the project life cycle. In general, the ability to influence a project's outcome and the associated project risk is higher during the earlier stages of the product development cycle and then becomes lower during the later stages as shown in Figure 4. The amount at stake (e.g., money or resources) and the corresponding management activity (i.e., management attention to the project) typically increase later in the project development cycle. One of the objectives of risk management is to move management attention earlier in the process cycle when the greatest opportunity exists to influence the outcome at the lowest possible cost.

Figure 4: The timing and impact of management attention<sup>29</sup>

<sup>&</sup>lt;sup>27</sup> Casciano, pp. 13-15.

<sup>&</sup>lt;sup>28</sup> Wideman, pp. II1-7.

<sup>&</sup>lt;sup>29</sup> Henderson, p. 11.

#### 3.1.3 **Purpose of project risk management**

The purpose of project risk management is to identify factors that are likely to impact the project objectives (such as time, cost, safety and quality), quantify the likely impact of each factor, and then mitigate impacts by exercising influence over items that are controllable.<sup>30</sup>

Project risk management should be seen as advanced preparation for possible adverse future events, rather than responding as they happen. With this advanced planning it is possible to minimize the potential problems and maximize the chance that the project objectives are achieved successfully.

#### 3.2 Overview of six-phase approach of risk management

The Project Management Institute, the world's leading not-for-profit professional association in the area of project management, identifies a six-phase approach to project risk management:<sup>31</sup>

- **Risk Management Planning:** deciding how to approach and plan the risk management activities for a project.

- Risk Identification: determining which risks might affect the project and • documenting their characteristics.

- Qualitative Risk Analysis: performing a qualitative analysis of risks and conditions to prioritize their effects on project objectives.

- Quantitative Risk Analysis: measuring the probability and consequences of risks and estimating their implications for project objectives.

- **Risk Response Planning:** developing procedures and techniques to enhance • opportunities and reduce threats to the project's objectives.

- **Risk Monitoring and Control:** monitoring residual risks, identifying new risks, • executing risk reduction plans, and evaluating their effectiveness throughout the project life cycle.

<sup>&</sup>lt;sup>30</sup> Pritchard, pp. 3-23.

<sup>31</sup> PMBOK® Guide, pp. 127-146.

Every project risk management plan is unique for each company and for each project, so a manager must evaluate the general criteria set forth by the Project Management Institute and determine what is necessary for his or her project. We now will discuss each of the six project risk phases in more detail below.

## 3.2.1 Risk management planning

Risk management planning is the process of deciding how to approach and plan the risk management activities for a project. There are many types of risk management techniques that are suited for diverse types of projects. Correctly matching the type of risk management to an individual project will minimize the probability of known risks adversely affecting the project's outcome while simultaneously minimizing the costs associated with the risk management process.<sup>32</sup> For example, managing quality risk (whether a product will be developed to specification) requires a different risk management plan than managing human resource risk (whether key employees will leave).

A risk management plan is developed by a team that includes the project manager, project team leaders, key stakeholders, and others as appropriate. This group of people develops and writes the plan by taking into account the organization's risk management policies and then tailoring these policies to the unique project needs. Often organizations have existing risk management plans and templates that are customized for new projects.33

The risk management plan is a written plan that describes the steps for risk identification, qualitative analysis, quantitative analysis, response planning, monitoring, and control throughout the project life cycle. There are eight different areas that may be included in the plan:

- Methodology: the tools, approach, and data sources that are used to perform risk • management on a project.

- **Roles and responsibilities**: for all of the risk management team members.

<sup>&</sup>lt;sup>32</sup> Pritchard, pp. 25-31. <sup>33</sup> Ibid, pp. 25-31

- Budgeting: set so that the cost of risk management will be lower than the benefits derived from it.

- Timing: where in the project life cycle the risk management process will be used to positively affect the project outcome.

- Scoring and interpretation: must be determined at the beginning of the project life cycle to ensure that qualitative and quantitative risk analysis is performed consistently.

- Thresholds: the risk levels that will trigger a response along with how much of a response is required.

- Reporting formats: how the results from the risk management process will be ٠ documented, analyzed, and communicated.

- Tracking: how the risk activities will be documented for the current project along • with lessons learned for future projects.<sup>34</sup>

These eight factors should be carefully considered and tailored by a manager and his or her team to customize the risk management plan to the project.

#### 3.2.2 **Risk identification**

The second phase, risk identification, results in a list of risks that will potentially affect a project. This process is typically conducted by experienced personnel and requires an understanding of the project's mission, scope, and objectives. Identifying risks is an iterative process that includes input from as many different people as possible in an attempt to achieve an unbiased of an analysis as possible.<sup>35</sup>

## Types of risk to identify

Risks that may affect the project outcome are grouped into categories: Technical, quality, or performance risk includes items such as unproven or complex technology. Project management risk includes items such as poor allocation of time and resources. Organizational risk includes items such as lack of prioritization of projects, inadequacy or

<sup>&</sup>lt;sup>34</sup> *PMBOK*® *Guide*, pp. 127-130. <sup>35</sup> Pritchard, pp. 31-34.

interruption of funding, and resource conflicts with other projects. External risks include items such as a changing regulatory environment, currency exchange rates, and country risks. The risk categories mentioned above are some of the more common risk categories, but there are many additional categories that must be considered as described below. Historical information including results from previous projects and the lessons learned should be incorporated in the development of new risk areas.<sup>36</sup>

# Tools and techniques for identifying risk<sup>37</sup>

- **Brainstorming:** is performed by the project team to obtain a comprehensive list of potential risk areas. A team comes together and identifies risk areas.<sup>38</sup>

- The Delphi technique: is a way to reach a consensus of experts on a subject such as project risk.<sup>39</sup>

- Interviewing: is a technique that consists of identifying appropriate experts and then questioning them about risk in their areas of expertise as related to the project.<sup>40</sup>

- **SWOT:** is an acronym for "strengths, weaknesses, opportunities and threats" to a project. It looks at strengths of a projects, it weaknesses, opportunities for success and threats to its success. This is a directed risk analysis designed to identify risks and opportunities within the greater organizational context.<sup>41</sup>

## 3.2.3 Qualitative Risk Analysis

Qualitative risk analysis, the third phase of the six-phase approach, is the process of assessing the impact and likelihood of identified risks. This allows for the qualitative evaluation and comparison of the individual risks that have previously been identified.<sup>42</sup>

A template for a risk impact and probability rating matrix is shown in Figure 5. The impact scale shows the magnitude of the effect on the project's objective, while the

<sup>&</sup>lt;sup>36</sup> Ibid, pp. 31-34.

<sup>&</sup>lt;sup>37</sup> *PMBOK*® *Guide*, pp. 131-133.

<sup>&</sup>lt;sup>38</sup> Pritchard, pp. 115-120.

<sup>&</sup>lt;sup>39</sup> Ibid, pp. 109-114.

<sup>&</sup>lt;sup>40</sup> Ibid, pp. 57-64.

<sup>&</sup>lt;sup>41</sup> Ibid, pp. 129-136.

<sup>&</sup>lt;sup>42</sup> *PMBOK*® *Guide*, pp. 133-137.

probability scale shows the probability that an individual risk will occur. The scales can be broken into additional sections and do not have to be linear, but they are typically kept simple so that they show clear risk rankings.<sup>43</sup>

|          | probability                        |                                      |                                     |  |

|----------|------------------------------------|--------------------------------------|-------------------------------------|--|

| Impact   | low                                | moderate                             | high                                |  |

| low      | low probability<br>low impact      | moderate probability<br>low impact   | high probability<br>low impact      |  |

| moderate | low probability<br>moderate impact | moderate probability moderate impact | high probability<br>moderate impact |  |

| high     | low probability<br>high impact     | moderate probability<br>high impact  | high probability<br>high impact     |  |

## Figure 5: Risk probability and impact matrix

Risk ranking is a subjective process, so it is important that the risk rating scheme is built against an agreed upon set of criteria to help minimize discrepancies.<sup>44</sup> For some projects a qualitative risk analysis is sufficient to guide the risk response (e.g., if hard quantitative data is expensive to obtain and not expected to add value), but for some other projects (e.g., when quantitative data exists is readily available and expected to add value) a manager may, in his or her opinion, want to perform an additional quantitative risk analysis.

## 3.2.4 Quantitative Risk Analysis

The quantitative risk analysis process, the fourth phase, numerically identifies the probability of each risk, the consequence of each risk (on each project's objectives), and the risk of the project as a whole. This analysis determines which risks are most important and pose the greatest threats to the project.<sup>45</sup>

Some of the common tools used to quantify risks include: The *expert interview technique* consists of first identifying appropriate experts and then methodically questioning them about risks in their area of expertise. *Sensitivity analysis* is used to

<sup>&</sup>lt;sup>43</sup> Pritchard, pp. 34-38.

<sup>&</sup>lt;sup>44</sup> Ibid, pp. 34-38.

<sup>&</sup>lt;sup>45</sup> *PMBOK*® *Guide*, pp. 137-140.

determine which risks have potentially the greatest project impact. *Decision tree analysis* shows the potential impact of project outcomes by incorporating a combination of project options, the probability of the options, and the expected value of the options. *Simulations* such as Monte Carlo analysis are used to show ranges and probabilities of possible project outcomes.<sup>46</sup>

The output from the combination of the qualitative and quantitative risk analysis is a prioritized list of risks that pose the greatest threats to the project's outcome.

## 3.2.5 Risk Response Planning

Risk response planning, the fifth phase of the six-phase approach, is the process of developing procedures and techniques to enhance opportunities and reduce threats to the project's objectives. It determines what actions will be taken to address risk issues evaluated in the identification, qualification, and quantification stages.

Risk response planning strategies fall into the following categories: Risk *avoidance* alters the project plan to eliminate the condition or protect the project from its impact. Risk *transference* transfers the risk to a third party. Risk *mitigation* reduces either the probability or impact of a risk by taking a specific course of action. Risk *acceptance* is the decision to acknowledge and endure the consequences if a risk event occurs. It is the project manager's responsibility to identify the proper strategy for each individual risk.

The output from risk response planning includes a list of all of the risks, the actions required to mitigate them and assignment of ownership responsibility. It is important that all of the tasks are clearly documented along with the expected timeframe in which a response is required.<sup>47</sup>

#### 3.2.6 Risk Monitoring and Control

Risk monitoring and control is the last phase of the six-phase approach, and involves monitoring residual risks, identifying new risks, executing risk reduction plans, and evaluating their effectiveness throughout the project life cycle. After the risk

<sup>&</sup>lt;sup>46</sup> Pritchard, pp. 215-223.

<sup>&</sup>lt;sup>47</sup> Pritchard, pp. 41-44.

management plan is put into action it must be continually reevaluated to ensure that it is still valid for the project and thoroughly documented.<sup>48</sup>

There are many different methods used for risk monitoring and control. Project risk response audits are performed during the project life cycle to examine the project team's progress on identifying, assessing, and developing appropriate risk strategies. Project risk reviews are scheduled on a regular basis to determine if the risk ratings and prioritization require changes. Technical performance measurement is performed to ensure that the technical performance is advancing per the project's technical achievement plan. Additional risk response planning is required when a previously unidentified risk emerges as one that will potentially affect the project and requires a response.<sup>49</sup>

Effective risk monitoring and control processes significantly reduce the probability of a risk occurring by making decisions that alter the outcome before the risk occurs. These decisions can include developing alternative strategies and plans. It is important to document the events and changes that occur throughout the cycle to ensure that the organization has the opportunity to apply lessons learned during the next project.<sup>50</sup>

Up to this point, this chapter has outlined the importance and purpose of project risk management and summarized the six-phase approach promoted by the leading authorities on project risk management. We will now show how this phased approach has been applied at a semiconductor manufacturing company.

## **3.3** Project risk management at a semiconductor company

In this section, we show how the project risk management framework can be applied within a semiconductor manufacturing company. Thompson (2000) shows how risk management is combined with project management in the new product introduction process for Motorola's Semiconductor Products Sector.<sup>51</sup> The four phase approach taken

<sup>&</sup>lt;sup>48</sup> Wideman, pp. IV1-4.

<sup>&</sup>lt;sup>49</sup> *PMBOK*® *Guide*, pp. 144-146.

<sup>&</sup>lt;sup>50</sup> Pritchard, pp. 44-47.

<sup>&</sup>lt;sup>51</sup> Thompson, pp. 49-54.

includes risk identification, risk quantification, risk response development, and risk control.

# 3.3.1 Risk identification

Motorola's risk identification process is most commonly accomplished with a brainstorming technique by the New Product Introduction (NPI) team, through which all of the team members identify potential risk sources without judgement or analysis. A partial simplified list of the identified risks from one of these sessions is shown in Table 2. The list was simplified in the paper to show the process, but not to show a complete list of all potential risks.

| No. | Risk                                         |

|-----|----------------------------------------------|

| 1   | New silicon will not function after tape out |

| 2   | Process in fab results in poor yield         |

| 3   | Test program not established                 |

| 4   | Schedule slip due to lack of resources       |

| 5   | Package problem meeting thermal perf.        |

| 6   | Solder joint requirement not met             |

| 7   | Burn-in Req'd for Infant Mortality           |

Table 2: Example results from using risk analysis tool

# 3.3.2 Risk quantification

Risk quantification is either qualitative or quantitative. An example of a qualitative risk ranking is shown in Table 3 where the probability and impact are both ranked on a high, medium, or low scale. The advantage of this qualitative technique is that it is simple and easy to implement. The disadvantage is that it is difficult to monitor across organizations and that it is difficult to create definitions that clearly differentiate between the various rankings.<sup>52</sup>

<sup>&</sup>lt;sup>52</sup> Ibid., p. 51.

| No. | Risk                                         | Probability | Impact |

|-----|----------------------------------------------|-------------|--------|

|     | New silicon will not function after tape out | high        | high   |

| 2   | Process in fab results in poor yield         | low         | high   |

| 3   | Test program not established                 | medium      | low    |

| 4   | Schedule slip due to lack of resources       | low         | medium |

| 5   | Package problem meeting thermal perf.        | medium      | low    |

|     | Solder joint requirement not met             | low         | low    |

| 7   | Burn-in Req'd for Infant Mortality           | high        | high   |

Table 3: Qualitative analysis tool after risk identification

An example of a quantitative risk ranking including numeric probability and impact values is shown in Table 4. The probability that a risk will occur is determined with statistical data, subjective judgment, simulations, or historical data. Impact analysis can be accomplished with historical data, estimates, subjective judgement, or simulations of both cost and schedule. The advantage of a quantitative analysis is that it provides a feeling of security or knowledge. The disadvantage is that it takes additional time and the numbers can be misleading since they are all estimates, but represented as "real" numbers.

| No. | Risk                                         | Probability | Impact (\$ M) |

|-----|----------------------------------------------|-------------|---------------|

| 1   | New silicon will not function after tape out | 60%         | 2             |

| 2   | Process in fab results in poor yield         | 20%         | 3             |

| 3   | Test program not established                 | 50%         | 0.5           |

| 4   | Schedule slip due to lack of resources       | 10%         | 1.5           |

| 5   | Package problem meeting thermal perf.        | 30%         | 0.1           |

|     | Solder joint requirement not met             | 10%         | 0.1           |

| 7   | Burn-in Req'd for Infant Mortality           | 70%         | 2.5           |

#### Table 4: Results from the quantitative analysis tool

After the qualitative or quantitative analysis is complete, the risks are ranked to prioritize which are most important and in what order to address them. This ranking is simple if the risks have been quantitatively analyzed by probability and impact, requiring the simple multiplication between the two columns in the table. In this example, risk number 7 has a 70% probability multiplied by a \$2.5 million dollar impact results in a value of \$1.75 million dollar impact which is larger than all of the other impacts so it is ranked as the number one priority risk to address. The rankings for this example are shown in Table 5. A similar ranking is not shown, but can be accomplished with the

qualitative data by making all risks with high probabilities and high impacts the first risks to be addressed.

| No.                                      | Risk                                         | Probability | Impact (\$ M) | Priority |

|------------------------------------------|----------------------------------------------|-------------|---------------|----------|

| 1                                        | New silicon will not function after tape out | 60%         | 2             | 2        |

| 2                                        | Process in fab results in poor yield         | 20%         | 3             | 3        |

| 3 Test program not established           |                                              | 50%         | 0.5           | 4        |

| 4 Schedule slip due to lack of resources |                                              | 10%         | 1.5           | 5        |

| 5                                        | Package problem meeting thermal perf.        | 30%         | 0.1           | 6        |

|                                          | Solder joint requirement not met             | 10%         | 0.1           | 7        |

| 7                                        | Burn-in Req'd for Infant Mortality           | 70%         | 2.5           | 1        |

Table 5: Risk prioritizes from analysis tool

## 3.3.3 Risk response development

Now that the risks have been identified, quantified, and ranked, responses are developed for each of the risks in order of importance. Cost, complexity, time, resources, ease of implementation and which stage of the project that the risk occurs are all taken into account during risk response planning which is summarized for this example in Table 6. Three options for addressing risks are acceptance, mitigation, and avoidance. A risk is accepted and documented if it is determined that the company is willing to accept it. For mitigation and avoidance the company takes actions to reduce the probability or impact of the risks if they do occur.<sup>53</sup>

| No. | Risk                                         | Risk Response                                   | Owner       |

|-----|----------------------------------------------|-------------------------------------------------|-------------|

| 1   | New silicon will not function after tape out | Design review and verification before tape out  | D. Kerr     |

| 2   | Process in fab results in poor yield         | Start back-up lots after 1st Si w/ alt. Process | M. Lowe     |

|     | Test program not established                 | Test engineer report status daily to PM         | C. Burnes   |

| 4   | Schedule slip due to lack of resources       | Assure test manager assigns engineer            | K. Sullivan |

| 5   | Package problem meeting thermal perf.        | Perform simulations using Theta                 | J. Miller   |

| 6   | Solder joint requirement not met             | Perform analysis on daisy chains in lab         | A. Mawer    |

| 7   | Burn-in Req'd for Infant Mortality           | Purchase baords so they are available           | J. Berr     |

| Table 6: | Risk | response | development |

|----------|------|----------|-------------|

|----------|------|----------|-------------|

## 3.3.4 Risk control

An example of the final phase, risk control, is shown in Table 7. The outcome from the risk response plan is shown in the table. This status is continuously updated

<sup>&</sup>lt;sup>53</sup> Ibid., p. 53.