## Low Energy Digital Circuit Design Using Sub-threshold Operation

by

#### Benton H. Calhoun

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

December 2005

| © Massachusetts Institute of Technology 2005. All rights reserved. |

|--------------------------------------------------------------------|

| Author                                                             |

| Certified by                                                       |

| Accepted by                                                        |

# Low Energy Digital Circuit Design Using Sub-threshold Operation

by

#### Benton H. Calhoun

Submitted to the Department of Electrical Engineering and Computer Science on December 8, 2005, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

#### Abstract

Scaling of process technologies to deep sub-micron dimensions has made power management a significant concern for circuit designers. For emerging low power applications such as distributed micro-sensor networks or medical applications, low energy operation is the primary concern instead of speed, with the eventual goal of harvesting energy from the environment. Sub-threshold operation offers a promising solution for ultra-low-energy applications because it often achieves the minimum energy per operation. While initial explorations into sub-threshold circuits demonstrate its promise, sub-threshold circuit design remains in its infancy.

This thesis makes several contributions that make sub-threshold design more accessible to circuit designers. First, a model for energy consumption in sub-threshold provides an analytical solution for the optimum  $V_{DD}$  to minimize energy. Fitting this model to a generic circuit allows easy estimation of the impact of processing and environmental parameters on the minimum energy point. Second, analysis of device sizing for sub-threshold circuits shows the trade-offs between sizing for minimum energy and for minimum voltage operation. A programmable FIR filter test chip fabricated in  $0.18\mu m$  bulk CMOS provides measurements to confirm the model and the sizing analysis. Third, a low-overhead method for integrating sub-threshold operation with high performance applications extends dynamic voltage scaling across orders of magnitude of frequency and provides energy scalability down to the minimum energy point. A 90nm bulk CMOS test chip confirms the range of operation for ultra-dynamic voltage scaling. Finally, sub-threshold operation is extended to memories. Analysis of traditional SRAM bitcells and architectures leads to development of a new bitcell for robust sub-threshold SRAM operation. The sub-threshold SRAM is analyzed experimentally in a 65nm bulk CMOS test chip.

Thesis Supervisor: Anantha P. Chandrakasan

Title: Professor, Department of Electrical and Computer Engineering

#### Acknowledgments

From my first weeks at MIT, a significant part of the advice offered to incoming graduate students focused on finding the right advisor. I was blessed to end up with the best. I am so grateful to Professor Anantha Chandrakasan for his continuous support and help over the last five years. My initial plan for graduate studies totally excluded circuit design until Anantha's 6.374 class captivated my interest. From those early days, Anantha has taught me a tremendous amount about circuits and other technical topics, but the other lessons I have learned from him are even more valuable. Anantha has shown me how to pursue research with zeal while maintaining the highest ethical standards and while remaining sensitive to the needs of the people involved. Anantha unswervingly pursues the best interests of his students, as I have experienced repeatedly. I have learned a lot from watching the way that he manages a large research group while constantly supporting and promoting the students who comprise it. Thank you, Anantha, for your amazing support and advice over the years. Your leadership has enriched my experience at MIT tremendously.

I also am grateful to the other members of my thesis committee, Professor Charlie Sodini and Professor Duane Boning. From my first meeting with them for my Research Qualifying Exam and throughout the process of developing my dissertation, they have challenged me with insightful questions, provided excellent suggestions, and helped me to improve my work. Thank you for your advice and support.

My friends and colleagues in Ananthagroup have made graduate school a true joy for me. I must first thank Margaret Flaherty, who helps to keep all of us in line and sane. Margaret has bailed me out of numerous crises (many of my own making). It seems that last minute emergencies frequently land on her desk, but she is always helpful and often heroic in her response. I cannot overstate how valuable it has been to be to have the friendship and fellowship of Alice Wang and Fred Lee. Our times talking and praying together always helped me to refocus my priorities and to remember what is truly important. I have certainly felt uplifted by your support and prayers, and I know that our friendships will be lifelong. Thank you!

In my earliest days in Ananthagroup, I benefitted from the tutelage of Manish Bhardwaj and Eugene Shih. Those guys helped me to relax a little bit and showed me the ropes of how to survive MIT. How interesting that Manish is now a brand new PhD student in the group (although I still turn to him for advice!). I am extremely grateful also to Travis Simpkins, who has been a great friend since even before I joined Ananthagroup. I am so thankful that Travis was always willing to escape with me for some "R and R" to the disc golf course, the basketball court, or the mountains. I am also grateful to Dave Wentzloff for good times on the basketball court, for answering my endless questions, and for being a good friend. I really appreciate all of the other folks who make our group such a great place to work (and relax). Thanks to Frank Honoré, Theodoros Konstantakopoulos, Raul Blazquez-Fernandez, Nathan Ickes, Alex Kern, and Yogesh Ramadass. Thanks to the Canadians: Naveen Verma, Denis Daly, Daniel Finchelstein, Payam Lajevardi, Vivienne Sze, Joyce Kwong, ... and Brian Ginsburg. Thanks to Nisha Checka, Shamik Das, Rex Min, CheeWe Ng, SeongHwan Cho, Julia Cline, Johnna Powell, Puneet Newaskar, Nigel Drego, and Piyada Phanaphat. Thanks to the newbies: Tao Pan, Taeg Sang Cho, Vikram Chandrasekhar, and Fred Chen. I have thoroughly enjoyed the technical discussions, jokes, riddles, lunch-time debates, invention marketing meetings, political discussions, and good times. I also want to thank the many other MIT students whom I have known in the context of classes, technical discussions, sports, and fun.

This thesis cites several publications for which I am indebted to my co-authors: Denis Daly, Naveen Verma, Daniel Finchelstein, Dave Wentzloff, SeongHwan Cho, and especially Alice Wang and Anantha Chandrakasan. Alice was so helpful ramping me up on her work when I decided to investigate sub-threshold circuits, and Anantha always knew the right way to present our results and where to submit. I am also grateful to Siva Narendra, Paul Peter Sotiriadis, Frank Honoré, James Kao, and Curt Schurgers (and his dog) for their collaboration on other works. I appreciate the help of Naveen, Joyce, and especially Payam for reading parts of this thesis.

I want to thank the sponsors who have supported my research during my time at MIT: the Defense Advanced Research Projects Agency (DARPA) and Texas Instruments. I am very grateful to the employees of Texas instruments who have repeatedly shared their time and knowledge with me. I have thoroughly enjoyed our collaboration, and I am very impressed with this company and its wonderful employees. I want specifically to thank Alice Wang (again!), David Scott, Andrew Marshall, Terence Breedijk, Richard White, and Dennis Buss.

Although most of the work in this dissertation got done at the lab, most of my support came from home. I cannot express enough appreciation and thanks to my wife, Mary Kathryn. She has been my strength throughout our time in Cambridge, providing me with the love and caring that I needed to sustain me. She has made our home a place of refuge for me where I can find rest. Our marriage has been amazing, and I find myself falling more in love with her each day. I am so blessed to be loved by a woman who is the excellent wife from the Proverb:

An excellent wife who can find?

She is far more precious than jewels.

The heart of her husband trusts in her, and he will have no lack of gain.

Proverbs 31:10-11 (ESV)

I cannot imagine facing life without my best friend and most cherished companion. One of the many ways that my wife amazes me is with her parenting. I learn how to be a better father by watching the patience and wisdom that she uses with our children. The Lord has blessed us with two great daughters, Anna Grace and Ruby Kate, and with a son on the way! My girls are amazing. It is such a pleasure to get home from work and to soak up their love and enthusiasm! The joys of sharing life with these girls made any frustrations from work seem insignificant in comparison. Plus, they always made sure I was up early in the morning in case I was tempted to sleep late!

Our family has had the privilege of making many wonderful friends during our time in Cambridge. I especially want to thank our friends at Christ the King Presbyterian Church. We have thoroughly enjoyed sharing in your lives for the last several years as we served one another and served the Lord together. Thanks to the Kyes, the Barnes, the Ashes, the Vickers, the Hixons, the Sondereggers, the Dykxhoorns, the

Killeens, the Russells, the Woolberts, and the Litmans. We have learned a lot from you and appreciate all of the good times. I am also grateful for the community in the Westgate apartments. We love playing with all of the kids on the playground and hanging out with so many great families.

I am very thankful for my parents, Sam and Jackie Calhoun. They have provided for me generously in every way in every step of my life. I am grateful always to have them to turn to for encouragement and advice. I am especially aware of all of their prayers on our behalf. I am also thankful to my brothers, Brian and Stephen Calhoun, for lots of conversations over the last few years. I am looking forward to spending more time together in the years to come. I also want to thank my grandfather, James L. Highsmith, Sr. (Gungy to us), who gave me my first exposure to computers. As an electrical engineer himself, he was eager to introduce me to an IBM machine like the ones that he built and sold. I still clearly remember writing my first BASIC program with Gungy giving instructions over my shoulder.

I included the following verses in the acknowledgements for my Master's thesis at MIT a few years ago:

<sup>28</sup>Do you not know? Have you not heard? The LORD is the everlasting God, the Creator of the ends of the earth. He will not grow tired or weary, and his understanding no one can fathom. <sup>29</sup>He gives strength to the weary and increases the power of the weak.  $^{30}\mathrm{Even}$  youths grow tired and weary, and young men stumble and fall; <sup>31</sup>but those who hope in the LORD will renew their strength. They will soar on wings like eagles; they will run and not grow weary, they will walk and not be faint. Isaiah 40:28-31 (NIV)

These words remain a description of God's faithfulness to me up until now. Although problem sets, tape-outs, and paper deadlines certainly made me weary at times, God renewed my strength when I set my hope on him. He has made me increasingly aware

during my time at MIT of his grace, which he gives freely to those who seek it. I am grateful for the way that Pastor Rick Downs at CTK Presbyterian Church emphasizes God's grace in his sermons. He is quick to point out the amazing attribute of God from this verse:

15 For thus says the One who is high and lifted up, who inhabits eternity, whose name is Holy:

"I dwell in the high and holy place, and also with him who is of a contrite and lowly spirit, to revive the spirit of the lowly, and to revive the heart of the contrite."

Isaiah 57:15 (ESV)

On those rare occasions when my heart is contrite, the truth of this verse becomes very apparent. By now, I should not be surprised at God's grace because he has lavished it on me so frequently. His propensity to dwell with the contrite of heart is also perfectly consistent with the gospel message on which I depend, expressed in John 3:16 and summarized as:

- <sup>3</sup> ... that Christ died for our sins in accordance with the Scriptures,

- $^4$  that he was buried, that he was raised on the third day in accordance with the Scriptures,

- $^{5}$  and that he appeared to Cephas, then to the twelve.

1 Corinthians 15:3-5 (ESV)

As I complete my time at MIT and move on to a new phase of life, I am eager to continue to seek to magnify God's glory and to know him more fully. His faithfulness to me and to my family even when we are not faithful is certain to continue in accordance with his promises.

Romans 11:33-36 (ESV)

<sup>33</sup> Oh, the depth of the riches and wisdom and knowledge of God!

How unsearchable are his judgments and how inscrutable his ways!

<sup>34 &</sup>quot;For who has known the mind of the Lord, or who has been his counselor?"

$<sup>^{35}</sup>$  "Or who has given a gift to him that he might be repaid?"

$<sup>^{36}</sup>$  For from him and through him and to him are all things. To him be glory forever. Amen.

## Contents

| 1 | Intr | oducti                                             | ion                                                                                                                                                                 | 27                               |

|---|------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   | 1.1  | Proble                                             | em Statement                                                                                                                                                        | 27                               |

|   | 1.2  | Micro                                              | -sensor Networks and Nodes                                                                                                                                          | 29                               |

|   |      | 1.2.1                                              | Micro-sensor Applications                                                                                                                                           | 30                               |

|   |      | 1.2.2                                              | Micro-sensor Nodes                                                                                                                                                  | 34                               |

|   | 1.3  | Energ                                              | y Harvesting                                                                                                                                                        | 35                               |

|   | 1.4  | Sub-tl                                             | areshold Operation                                                                                                                                                  | 37                               |

|   |      | 1.4.1                                              | Motivation - Energy and Power Savings                                                                                                                               | 37                               |

|   |      | 1.4.2                                              | Previous Work: History of Sub-threshold                                                                                                                             | 39                               |

|   |      | 1.4.3                                              | Inverter Operation in Sub-threshold                                                                                                                                 | 41                               |

|   | 1.5  | Thesis                                             | Contribution and Organization                                                                                                                                       | 45                               |

| 2 | Mod  | deling                                             | Minimum Energy Consumption                                                                                                                                          | 49                               |

|   |      |                                                    |                                                                                                                                                                     |                                  |

|   | 2.1  | Sub-th                                             | nreshold Current                                                                                                                                                    | 50                               |

|   | 2.1  | Sub-th<br>2.1.1                                    | Sub-threshold Current Models                                                                                                                                        | 50<br>50                         |

|   | 2.1  |                                                    |                                                                                                                                                                     |                                  |

|   | 2.1  | 2.1.1<br>2.1.2                                     | Sub-threshold Current Models                                                                                                                                        | 50                               |

|   |      | 2.1.1<br>2.1.2                                     | Sub-threshold Current Models                                                                                                                                        | 50<br>51                         |

|   |      | 2.1.1<br>2.1.2<br>Model                            | Sub-threshold Current Models                                                                                                                                        | 50<br>51<br>53                   |

|   |      | 2.1.1<br>2.1.2<br>Model<br>2.2.1<br>2.2.2          | Sub-threshold Current Models                                                                                                                                        | 50<br>51<br>53<br>53             |

|   | 2.2  | 2.1.1<br>2.1.2<br>Model<br>2.2.1<br>2.2.2          | Sub-threshold Current Models                                                                                                                                        | 50<br>51<br>53<br>53<br>60       |

|   | 2.2  | 2.1.1<br>2.1.2<br>Model<br>2.2.1<br>2.2.2<br>Minim | Sub-threshold Current Models  Other Components of Current  ing the Minimum Energy Point  Developing the Model  Calibrating the Model  cum Energy Point Dependencies | 50<br>51<br>53<br>53<br>60<br>61 |

|   | 2.4  | Summ            | nary and Conclusions                             | 68  |

|---|------|-----------------|--------------------------------------------------|-----|

| 3 | Sizi | ng for          | Minimum Energy                                   | 69  |

|   | 3.1  | Theor           | etical Sizing                                    | 69  |

|   |      | 3.1.1           | Sizing for Minimum Energy at a Specific $V_{DD}$ | 70  |

|   |      | 3.1.2           | Sizing for Minimum Operating Voltage             | 70  |

|   |      | 3.1.3           | Ratioed Circuits                                 | 73  |

|   | 3.2  | Stand           | ard Cells                                        | 75  |

|   | 3.3  | Measu           | ared Results from Test Chip                      | 77  |

|   | 3.4  | Sumn            | nary and Conclusions                             | 81  |

| 4 | Ult  | ra <b>-</b> Dyr | namic Voltage Scaling                            | 83  |

|   | 4.1  | DVS a           | and Local Voltage Dithering                      | 84  |

|   |      | 4.1.1           | Voltage Dithering                                | 86  |

|   |      | 4.1.2           | Local Voltage Dithering                          | 87  |

|   | 4.2  | Ultra-          | Dynamic Voltage Scaling (UDVS) Test Chip         | 88  |

|   |      | 4.2.1           | UDVS Test Chip Architecture                      | 90  |

|   |      | 4.2.2           | Measurements                                     | 92  |

|   | 4.3  | UDVS            | System Considerations                            | 97  |

|   | 4.4  | Sumn            | nary and Conclusions                             | 102 |

| 5 | Sub  | -thres          | hold SRAM                                        | 103 |

|   | 5.1  | Low F           | Power SRAM Design                                | 106 |

|   |      | 5.1.1           | SRAM Overview                                    | 106 |

|   |      | 5.1.2           | Voltage Scaling                                  | 111 |

|   |      | 5.1.3           | Write Access                                     | 115 |

|   |      | 5.1.4           | Data Sensing for SRAM Read                       | 116 |

|   |      | 5.1.5           | Address Decoding                                 | 119 |

|   |      | 5.1.6           | Alternative Bitcells                             | 120 |

|   |      | 5.1.7           | Embedded SRAM versus Embedded DRAM               | 123 |

|   | 5.2  | 6-Trai          | nsistor SRAM Bitcell in Sub-threshold            | 125 |

| В            | Lam  | bert <b>V</b>   | W Function                                 | 187 |

|--------------|------|-----------------|--------------------------------------------|-----|

| $\mathbf{A}$ | Acre | onyms           |                                            | 183 |

|              | 6.2  | Concli          | isions and Open Problems                   | 177 |

|              | 6.1  | Summ            | ary of Contributions                       | 175 |

| 6            | Con  | clusio          | ns                                         | 175 |

|              | 5.6  | Summ            | ary and Conclusions                        | 173 |

|              |      | 5.5.3           | Proposed Improvements                      | 172 |

|              |      | 5.5.2           | Measurements                               | 164 |

|              |      | 5.5.1           | Test Chip Architecture                     | 161 |

|              | 5.5  | $65\mathrm{nm}$ | Sub-threshold SRAM Test Chip               | 161 |

|              |      | 5.4.2           | Enabling Sub-threshold Write               | 156 |

|              |      | 5.4.1           | Enabling Sub-threshold Read                | 150 |

|              | 5.4  | A Sub           | -threshold Bit-cell Design                 | 148 |

|              |      | 5.3.4           | Implications for Sub-threshold SRAM        | 146 |

|              |      | 5.3.3           | Dependence on Random Doping Variation      | 139 |

|              |      | 5.3.2           | Sub-threshold SNM Dependencies             | 136 |

|              |      | 5.3.1           | Modeling Sub-threshold Static Noise Margin | 133 |

|              | 5.3  | Static          | Noise Margin                               | 133 |

|              |      | 5.2.2           | Read Operation                             | 131 |

|              |      | 5.2.1           | Write Operation                            | 126 |

## List of Figures

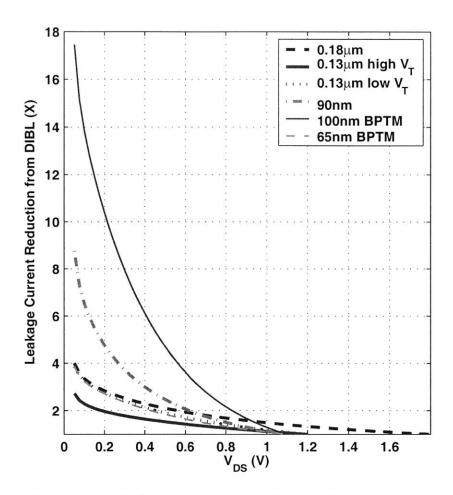

| 1-1 | Reduction in leakage current from Drain-Induced Barrier Lowering                                                                                                                      |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | (DIBL) for different technologies. The Berkeley Predictive Technol-                                                                                                                   |    |

|     | ogy Models (BPTMs) are from $[1][2]$                                                                                                                                                  | 38 |

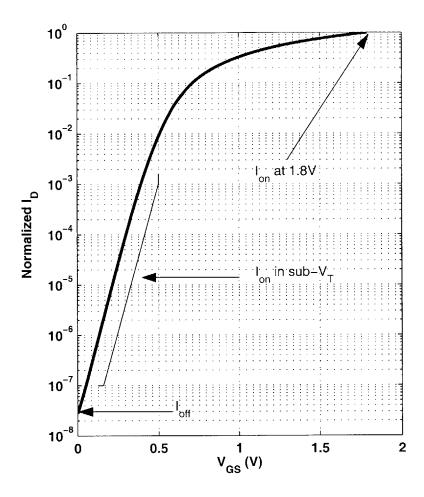

| 1-2 | MOSFET drain current, $I_D$ , versus gate to source voltage, $V_{GS}$ in                                                                                                              |    |

|     | $0.18 \mu \mathrm{m}$ with $V_{DD}=1.8 \mathrm{V}$ . In sub-threshold, $I_D$ varies exponentially                                                                                     |    |

|     | with $V_{GS}$ . In fact, we define $V_T$ by looking at where the $I_D$ curve                                                                                                          |    |

|     | deviates from its original exponential trajectory. In the sub-threshold                                                                                                               |    |

|     | region, the $I_{on}/I_{off}$ ratio reduces relative to strong inversion                                                                                                               | 42 |

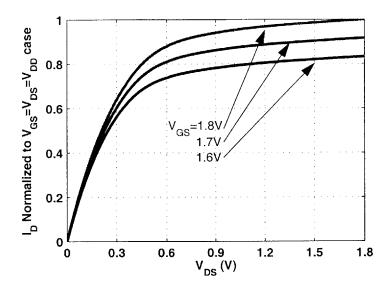

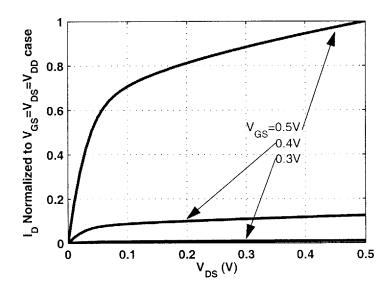

| 1-3 | $I_D$ versus $V_{DS}$ curves for three values of $V_{GS}$ in a $0.18 \mu\mathrm{m}$ process with                                                                                      |    |

|     | $V_{DD}=1.8\mathrm{V}.$ This above-threshold inverter shows velocity saturation,                                                                                                      |    |

|     | since $I_D$ increases linearly with $V_{GS}$                                                                                                                                          | 44 |

| 1-4 | $I_D$ versus $V_{DS}$ curves for three values of $V_{GS}$ in a $0.18 \mu \mathrm{m}$ process,                                                                                         |    |

|     | but $V_{DD}=500 \mathrm{mV},$ so the inverter is in the sub-threshold region. $I_D$                                                                                                   |    |

|     | increases exponentially with $V_{GS}$                                                                                                                                                 | 44 |

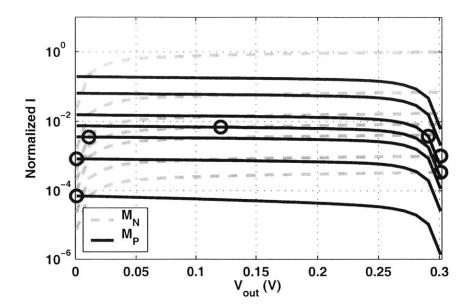

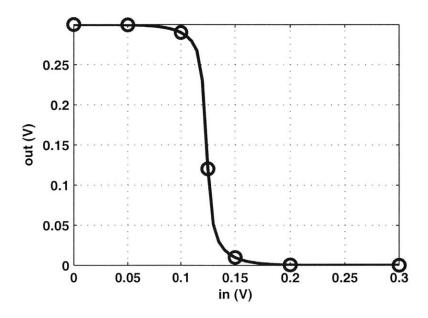

| 1-5 | Load line analysis at the output of a sub-threshold inverter with $V_{in}=% \left\{ $ |    |

|     | [0.01, 0.05, 0.1, 0.125, 0.15, 0.2, 0.3]V                                                                                                                                             | 46 |

| 1-6 | Voltage Transfer Characteristic (VTC) for the inverter with the load                                                                                                                  |    |

|     | lines in Figure 1-5. $V_{DD}=300 \mathrm{mV}.$                                                                                                                                        | 46 |

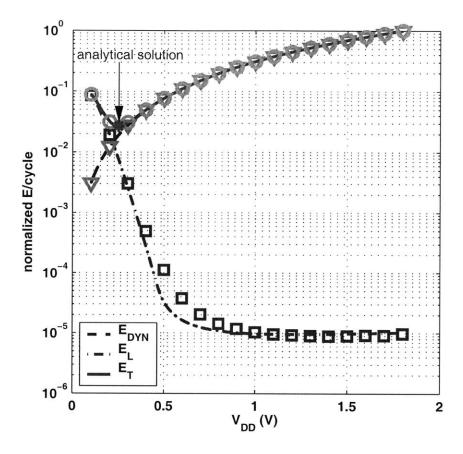

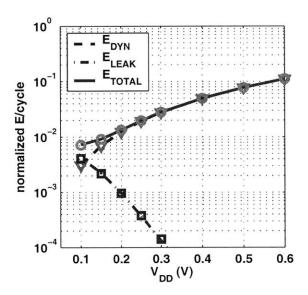

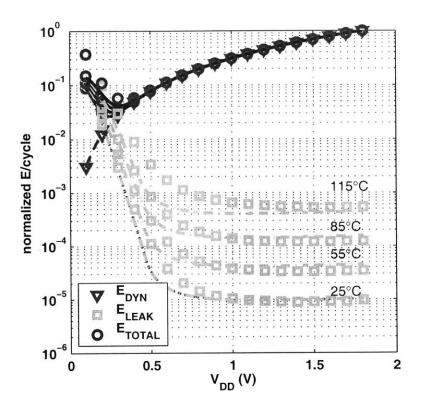

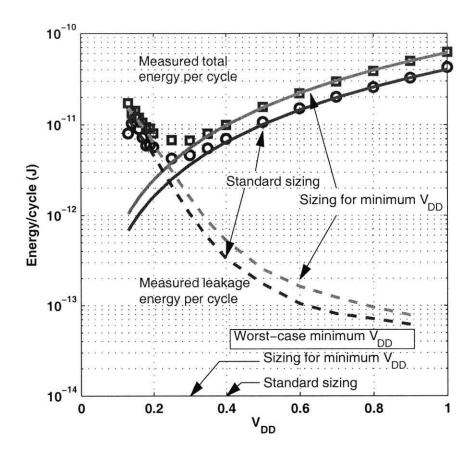

| 2-1 | Model versus simulation of FIR filter showing minimum energy point                                                                                                                    |    |

|     | and contribution of active and leakage energy. Markers are simulation                                                                                                                 |    |

|     | values, lines are model [3]. Analytical solution from eqs. (2.10) and                                                                                                                 |    |

|     | (2.7) is shown                                                                                                                                                                        | 57 |

|      | 16                                                                                                                                                               |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | minimizes operational $V_{DD}$ but increases energy consumption                                                                                                  | 72 |

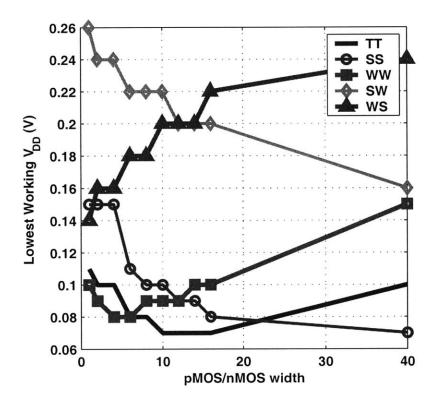

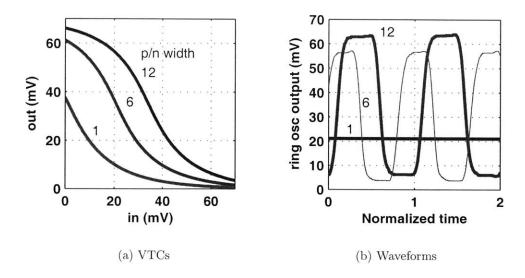

| 3-2  | VTCs (a) and 9-stage ring oscillator output (b) at the minimum $V_{DD}$ for the typical corner (simulation). pMOS/nMOS width ratio of 12                         |    |

|      | ring oscillator across process corners (simulation)                                                                                                              | 71 |

| 3-1  | Minimum achievable voltage retaining 10%-90% output swing for $0.18 \mu \mathrm{m}$                                                                              |    |

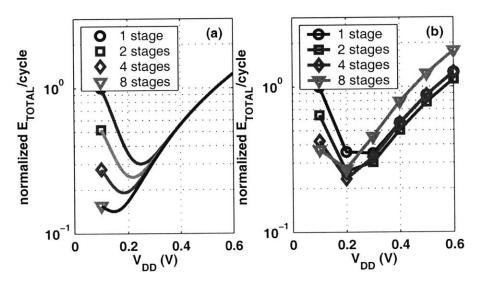

| 2-11 | Effect of pipelining on minimum energy and optimum $V_{DD}$ for the FIR filter. Ideal pipelines (a) and simulated (b).                                           | 67 |

|      | ulation (markers) and by the numerical model (lines). Temperature varies from 25°C to 115°C                                                                      | 66 |

| 2-10 | Dependence of minimum energy point on temperature shown in sim-                                                                                                  |    |

|      | d. Simulation $V_{DD}$ quantized to 100mV                                                                                                                        | 64 |

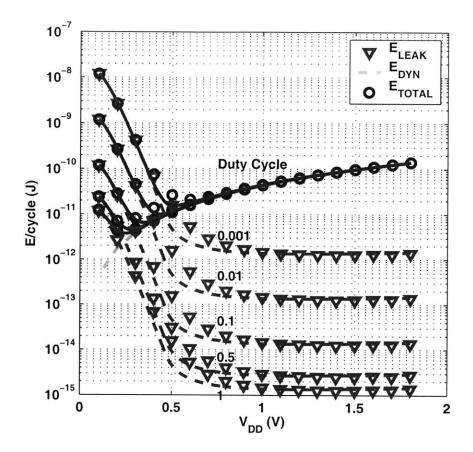

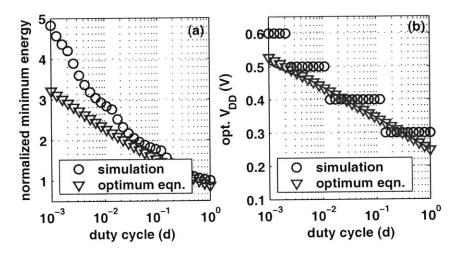

| 2-9  | Normalized energy (a) and optimum $V_{DD}$ (b) for FIR versus duty cycle,                                                                                        |    |

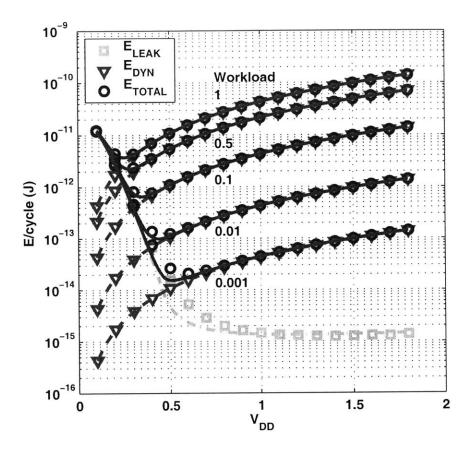

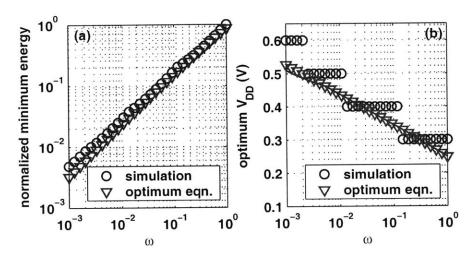

| 2-8  | Normalized energy (a) and optimum $V_{DD}$ (b) for FIR versus workload, $\omega$ . Simulation $V_{DD}$ quantized to 100mV.                                       | 64 |

| 2-7  | Energy versus $V_{DD}$ for changing duty cycle                                                                                                                   | 63 |

| 2-6  | Energy versus $V_{DD}$ for changing workload                                                                                                                     | 62 |

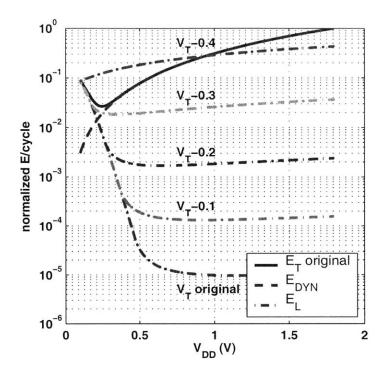

|      | ergy point                                                                                                                                                       | 60 |

|      | threshold region, but it will increase performance at the minimum en-                                                                                            |    |

| 2-5  | Lowering $V_T$ does not improve the energy per operation in the sub-                                                                                             |    |

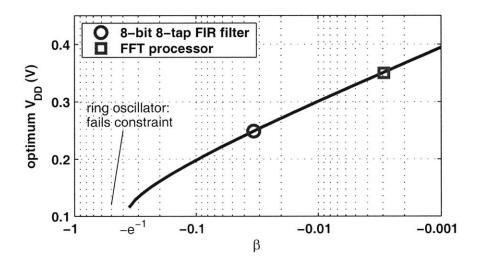

| 2-4  | Energy per operation versus $V_{DD}$ for a 21-stage ring oscillator has no minimum point. Markers show simulation data and lines show equations.                 | 59 |

|      | FFT processor [4] also shown.                                                                                                                                    | 58 |

| 2-3  | $V_{DD}$ optimum calculated with equation (2.10). $\beta$ for ring oscillator ( $L_{DP}=21$ ) fails constraint. $\beta$ for 8x8 parallel FIR filter and scalable |    |

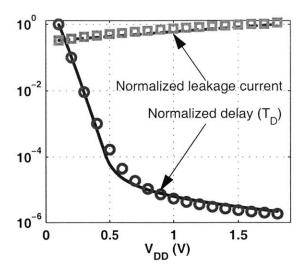

|      | increase in sub-threshold                                                                                                                                        | 58 |

|      | ulation and lines are model [3]. Although DIBL caused $I_{LEAK}$ to decrease, the exponential increase in $T_D$ causes leakage energy $(E_L)$ to                 |    |

|      | Normalized leakage current $(I_{LEAK})$ and delay $(I_D)$ . Markers are sim-                                                                                     |    |

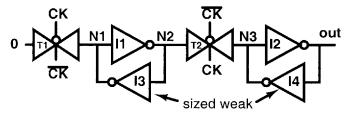

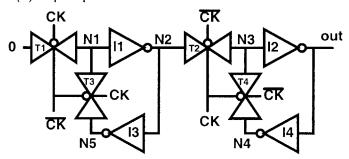

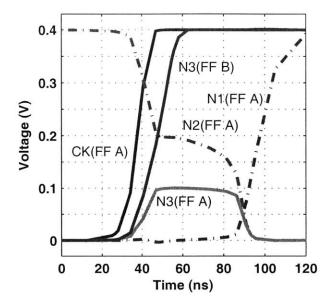

| J-J         | Two hip-hops for evaluation for sub-threshold operation. Flip-flop A            |     |

|-------------|---------------------------------------------------------------------------------|-----|

|             | has ratioed feedback, and Flip-flop B does not. Ratioed circuits cannot         |     |

|             | function across process corners in sub-threshold at the minimum energy          |     |

|             | voltage because the exponential dependence of current on $V_T$ becomes          |     |

|             | more important than sizing. Cutting the feedback loop for writing a             |     |

|             | latch is robust across all corners for operation at the minimum energy          |     |

|             | voltage                                                                         | 73  |

| 3-4         | Plot showing the failure of ratioed Flip-flop A at the strong nMOS,             |     |

|             | weak pMOS corner at 400mV. The master stage fails to write the slave            |     |

|             | stage and is itself overwritten                                                 | 74  |

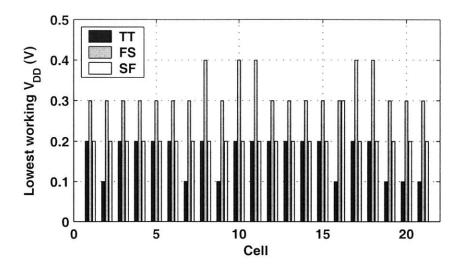

| 3-5         | Standard cell functionality in synthesized FIR filter using normal cell         |     |

|             | selection over process corners (simulation)                                     | 76  |

| 3-6         | Standard cell flip-flop at worst-case failure point where $CK = 0$ at FS        |     |

|             | corner (fast nMOS, slow pMOS)                                                   | 76  |

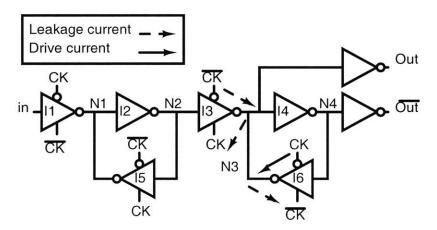

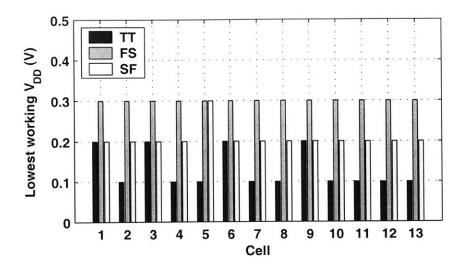

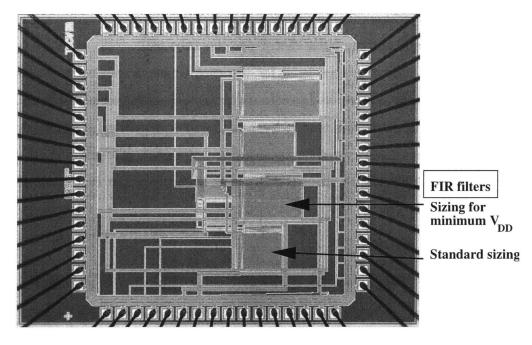

| 3-7         |                                                                                 | • • |

| 3- <i>1</i> | Standard cell functionality in synthesized FIR filter using cells sized to      |     |

|             | minimize $V_{DD}$ over process corners (simulation)                             | 77  |

| 3-8         | Measured performance of programmable FIR filters on the test chip.              |     |

|             | Standard FIR is 10% faster than the minimum-voltage FIR                         | 78  |

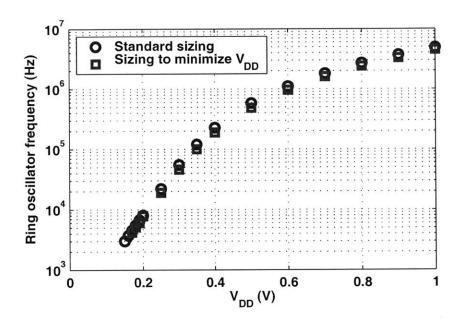

| 3-9         | Oscilloscope plot from the test chip showing $V_{DD}=150 \mathrm{mV}$ filtering |     |

|             | operation with ring oscillator clock at 3.2kHz                                  | 79  |

| 3-10        | Measured energy per operation of the FIR filters on the test chip               | 80  |

|             | Annotated die photo of $0.18\mu\mathrm{m}$ sub-threshold FIR test chip          |     |

| , 11        | Timestated the photo of 0.10µm sub-timeshold Fift test cmp.                     | 81  |

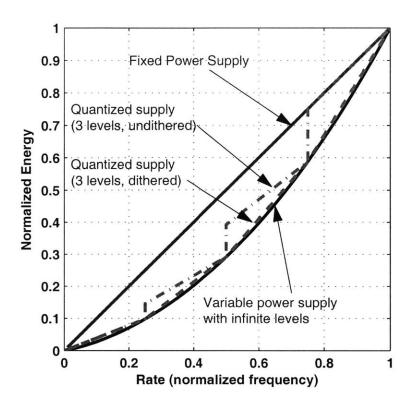

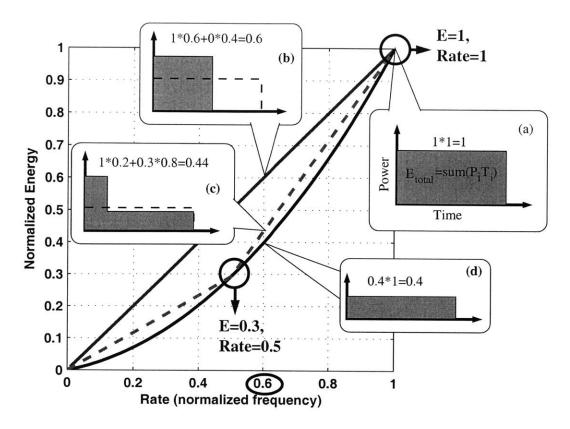

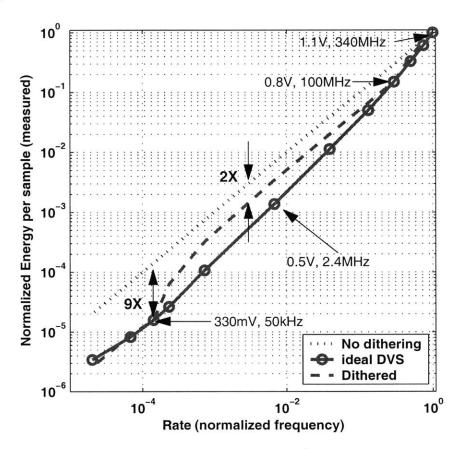

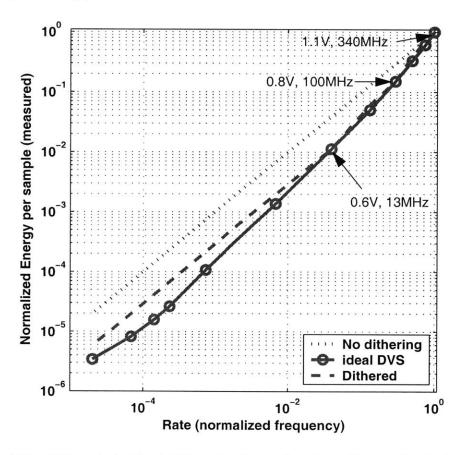

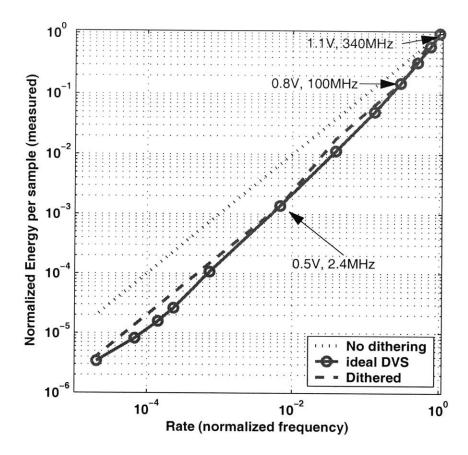

| <b>1-</b> 1 | Theoretical energy consumption versus rate for different power supply           |     |

|             | strategies [5]                                                                  | 85  |

| 1-2         | Voltage dithering example for 0.6 rate normalized to full rate (a). Ex-         |     |

|             | ample shows fixed supply (b), voltage dithering (c), and ideal variable         |     |

|             | supply (d)                                                                      | 87  |

|             |                                                                                 | - ' |

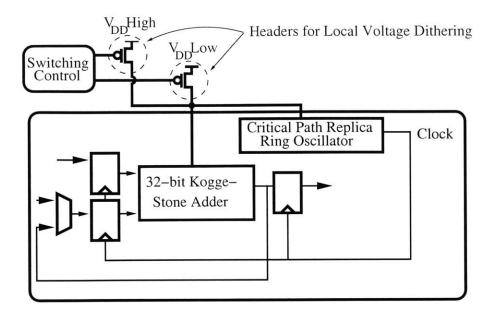

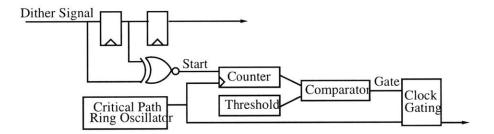

| 4-3  | Block diagram of voltage dithered adder and critical path replica using                  |    |

|------|------------------------------------------------------------------------------------------|----|

|      | two local header switches for local voltage dithering (Local Voltage                     |    |

|      | Dithering (LVD))                                                                         | 89 |

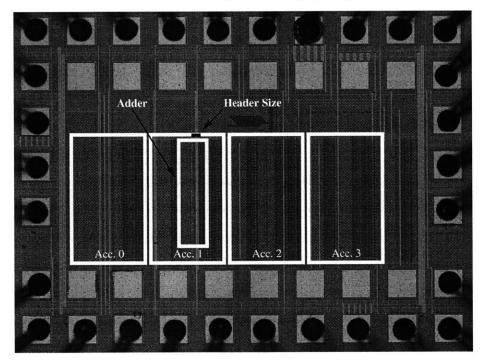

| 4-4  | Annotated die photograph showing accumulators with $0,\ 1,\ 2$ and $3$                   |    |

|      | headers. The size of one header is highlighted for reference                             | 89 |

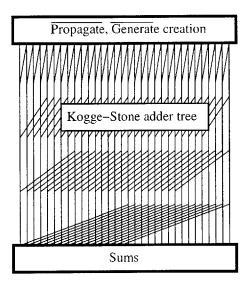

| 4-5  | Schematic of adder circuits. Kogge-Stone-based tree with inverting                       |    |

|      | stages of dot operators (at each reconvergence of the tree)                              | 90 |

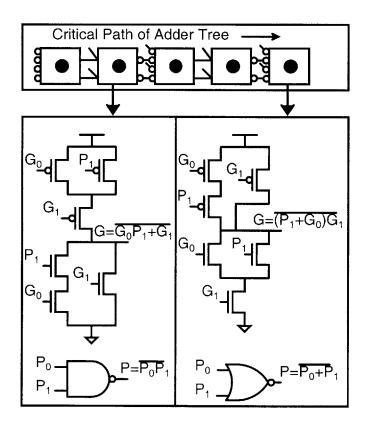

| 4-6  | Circuits for Kogge-Stone adder. Inverting stages of dot operators are                    |    |

|      | in series along the critical path. Circuits do not require large stacks of               |    |

|      | transistors, which degrade sub-threshold operation.                                      | 91 |

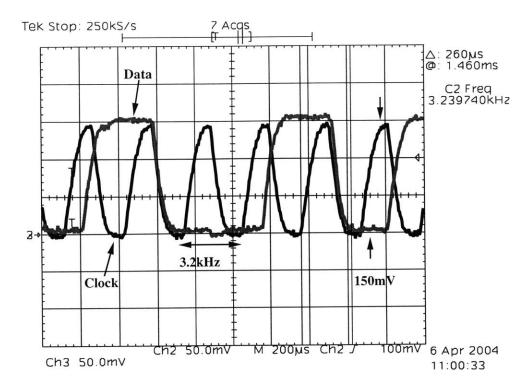

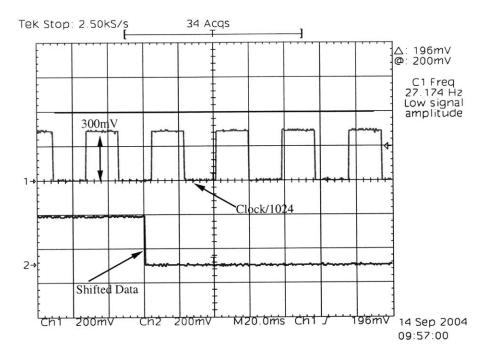

| 4-7  | Oscilloscope plot showing the clock and data from the 90nm test chip                     |    |

|      | operating at $300 \text{mV}$ , just below the minimum energy point. The adders           |    |

|      | functioned to $200 \text{mV}$                                                            | 92 |

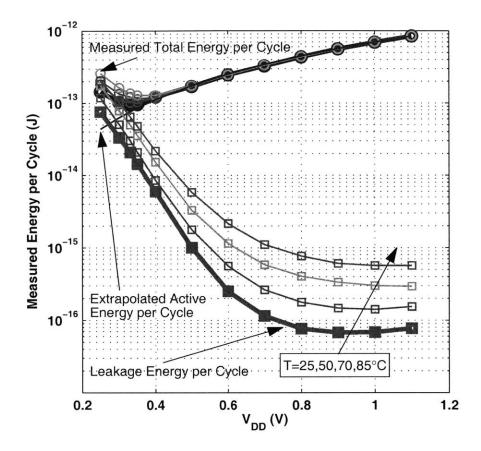

| 4-8  | Measured energy per cycle in the sub-threshold region for input activity                 |    |

|      | of one. Minimum energy point occurs at $330\mathrm{mV}$ (50kHz) and $0.1\mathrm{pJ}$ per |    |

|      | operation at $25^{\circ}$ C. The optimum supply voltage is relatively insensitive        |    |

|      | to temperature variation                                                                 | 93 |

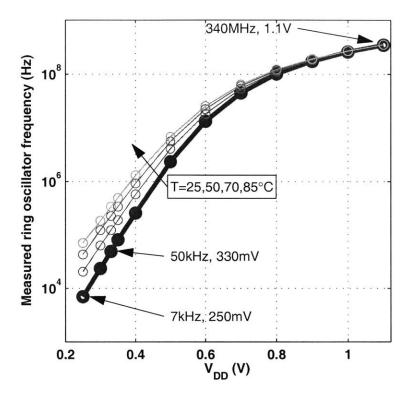

| 4-9  | Measured ring oscillator frequency versus $V_{DD}$ and temperature                       | 94 |

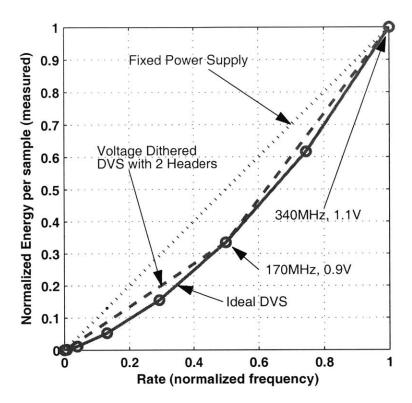

| 4-10 | Characterized local voltage dithering using measured results for 32-bit                  |    |

|      | Kogge-Stone adder                                                                        | 95 |

| 4-11 | Circuit for measuring timing overhead of LVD that gates the clock at                     |    |

|      | a $V_{DD}$ transition for a given number of cycles. The duration of this                 |    |

|      | clock gating is decreased until the circuit fails                                        | 95 |

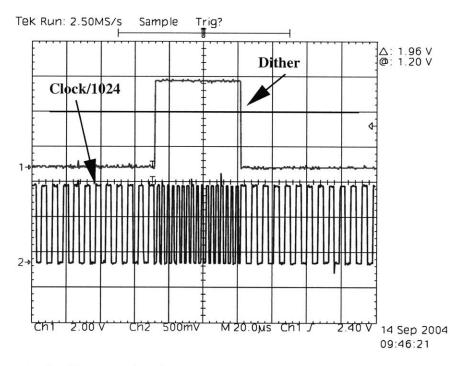

| 4-12 | Oscilloscope plot showing the system clock while dithering between                       |    |

|      | rate 0.5 (170MHz) and rate 1 (340MHz). Measurements show correct                         |    |

|      | accumulation at both transitions even no clock gating (see Figure 4-11).                 | 96 |

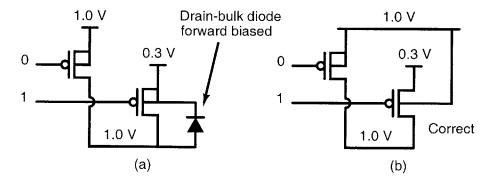

| 4-13 | For UDVS, the bulk connections of the pMOS header switches have to                       |    |

|      | connect to the highest supply voltage                                                    | 97 |

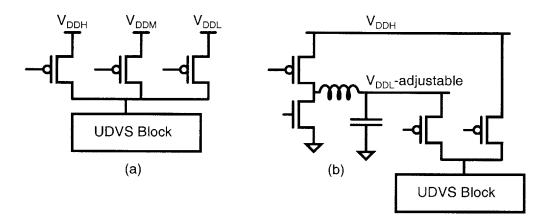

| 4-14 | Ultra-Dynamic Voltage Scaling (UDVS) using two headers with one                          |    |

|      | variable dc-dc converter or using three headers (c.f. Figure 4-17)                       | 98 |

| 4-10 | of $V_{DD}$                                                                  | 99   |

|------|------------------------------------------------------------------------------|------|

| 4-16 | Different choice of dithered voltages for closer fit over the entire range   |      |

|      | of $V_{DD}$                                                                  | 100  |

| 4-17 | Options for UDVS headers at the system level                                 | 101  |

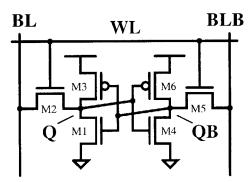

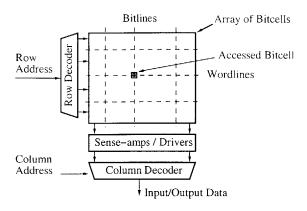

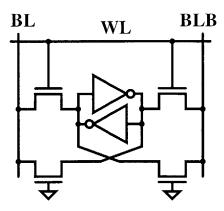

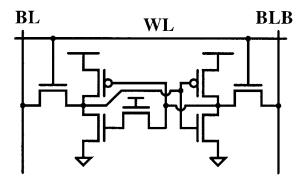

| 5-1  | Schematic for a standard 6T bitcell                                          | 106  |

| 5-2  | Standard architecture for an SRAM using the 6T bitcell                       | 107  |

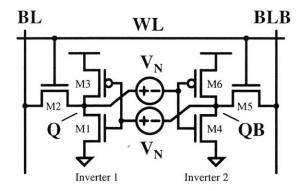

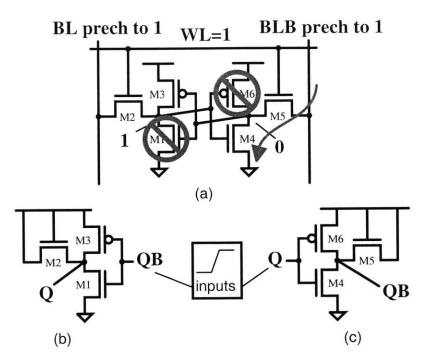

| 5-3  | Schematic for 6T bitcell showing voltage noise sources for finding SNM [6    | .108 |

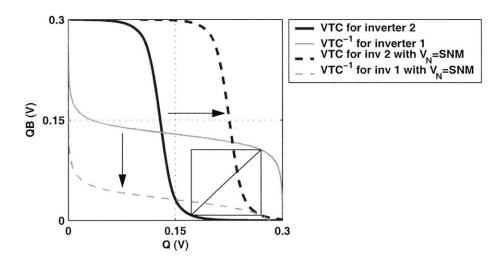

| 5-4  | The length of the side of the largest embedded square in the butterfly       |      |

|      | curve is the SNM. When both curves move by more than this amount             |      |

|      | (e.g. $V_N = \text{SNM}$ ), then the bitcell is mono-stable, losing its data | 108  |

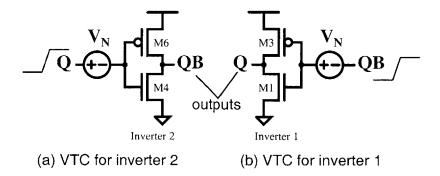

| 5-5  | Equivalent circuits for 6T bitcell for finding VTCs in the butterfly         |      |

|      | curve. (a) shows the equivalent circuit for the VTC of inverter 2,           |      |

|      | where Q is swept and the output is at QB. (b) shows the equivalent           |      |

|      | circuit for the VTC of inverter 1, where QB is swept and the output is       |      |

|      | at Q (the butterfly curve shows the inverse of this because Q is on the      |      |

|      | x-axis)                                                                      | 109  |

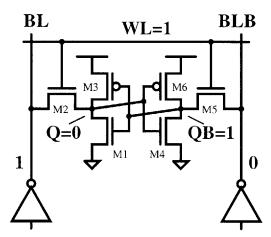

| 5-6  | Schematic of the 6T bitcell at the onset of a read access (a). WL has        |      |

|      | just gone high, and both BLs are precharged to $V_{DD}$ . The voltage        |      |

|      | dividing effect across $M_4$ and $M_5$ pulls up node $Q_B$ , which should be |      |

|      | 0V, and degrades the SNM. (b) shows the equivalent circuit of the            |      |

|      | bitcell for plotting the VTC of inverter 1 in the butterfly curve (QB        |      |

|      | input, Q output). (c) shows the equivalent circuit of the bitcell for        |      |

|      | plotting the VTC of inverter 2 in the butterfly curve (Q input, QB           |      |

|      | output)                                                                      | 110  |

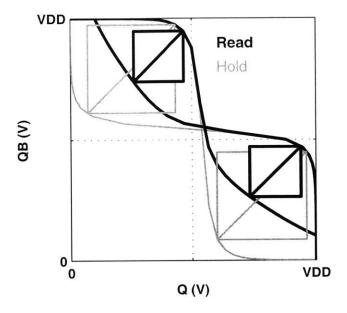

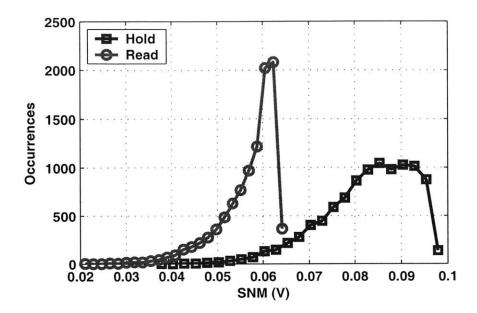

| 5-7  | Example butterfly curve plots for SNM during hold and read                   | 111  |

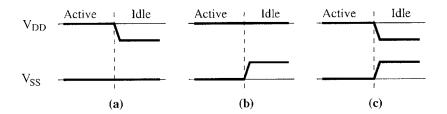

| 5-8  | General approaches using voltage scaling to lower idle power in SRAM.        |      |

|      | Lowering $V_{DD}$ (a), raising $V_{SS}$ (b), or both (c)                     | 112  |

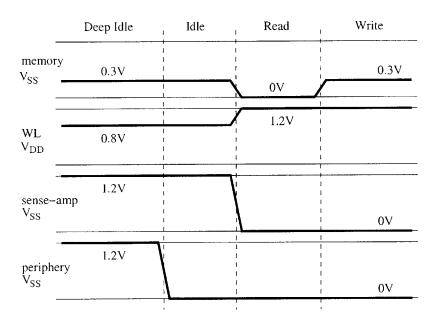

| 5-9  | Voltage scaling strategies for different operating modes in [7]              | 114  |

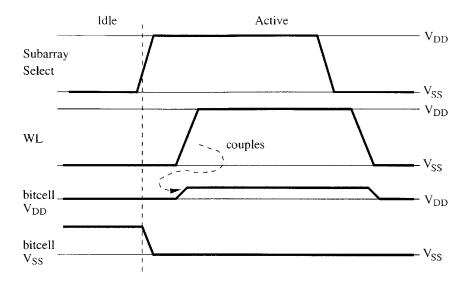

| 5-10 | Voltage is boosted to accessed cells using capacitive coupling from the                           | 115 |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | wordline in [8]                                                                                   | 115 |

| 5-11 | An 8T bitcell in [8] equalizes leakage to the bitlines by forcing the                             |     |

|      | worst-case leakage current to both                                                                | 119 |

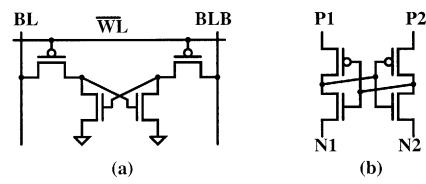

| 5-12 | Four transistor bitcells. Leakage through low $V_T$ pMOS access tran-                             |     |

|      | sistors provide the load for the cell in (a) [9], and manipulating the                            |     |

|      | sources of the transistors in (b) provides access to the bitcell [10]                             | 120 |

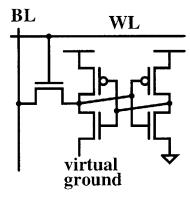

| 5-13 | Single ended read and write access allow the omission of one access                               |     |

|      | transistor in this 5T bitcell. Single-ended write is enabled by allowing                          |     |

|      | the labelled virtual ground node to float during write access [11]                                | 121 |

| 5-14 | A 7T bitcell that takes advantage of the predominance of zeros at the                             |     |

|      | bit level to decrease gate leakage [12]                                                           | 122 |

| 5-15 | Schematic showing conceptual write of '1' into node 'Q' in the 6T                                 |     |

|      | bitcell. Data shown for Q and QB must be overwritten                                              | 126 |

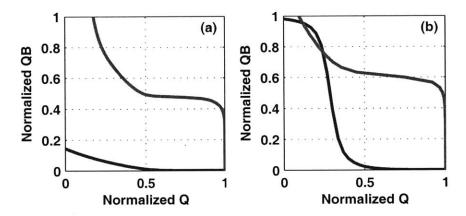

| 5-16 | Example VTCs for write access showing write 'SNM'. A negative write                               |     |

|      | SNM indicates a successful write to the mono-stable point (a). If the                             |     |

|      | write SNM remains positive, then the write fails because the state of                             |     |

|      | the bitcell is not changed - example shown in (b)                                                 | 127 |

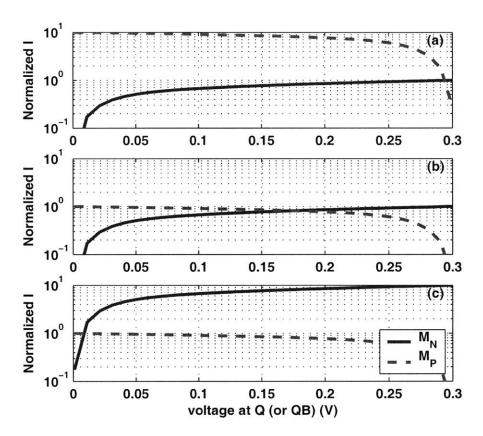

| 5-17 | Plot showing the impact of relative pMOS and nMOS on-current on                                   |     |

|      | voltage at internal bit<br>cell node. $I_P > I_N$ (a), $I_P \approx I_N$ (b),<br>$I_P < I_N$ (c). | 128 |

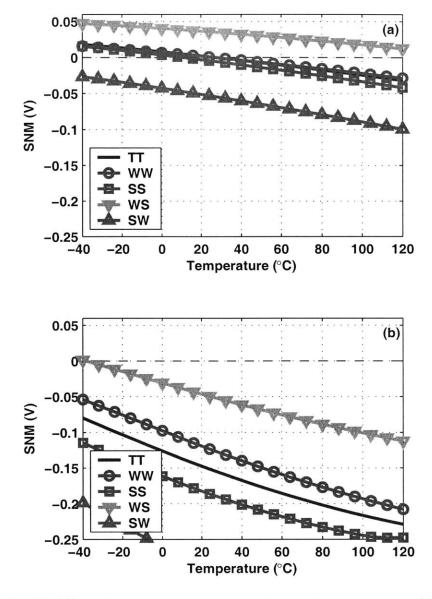

| 5-18 | SNM for write access versus temperature and process corner ( Typical                              |     |

|      | nMOS, Typical pMOS (TT), Weak nMOS, Weak pMOS (WW), Strong                                        |     |

|      | nMOS, Strong pMOS (SS), Weak nMOS, Strong pMOS (WS), and                                          |     |

|      | Strong nMOS, Weak pMOS (SW)) at $V_{DD}=0.3\mathrm{V}$ (a) and $V_{DD}=0.6\mathrm{V}$             |     |

|      | (b). Negative SNM indicates successful write                                                      | 130 |

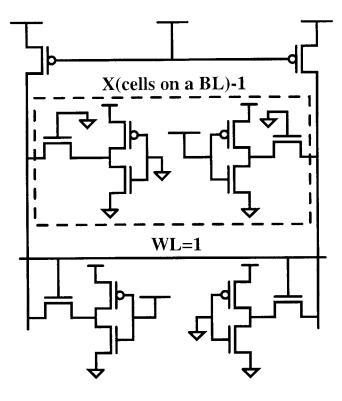

| 5-19 | Schematic showing the simulation set-up for finding steady-state be-                              |     |

|      | havior for the worst-case scenario for bit<br>line leakage. For $\boldsymbol{X}$ cells on a       |     |

|      | bitline, $X-1$ cells hold the complement of the value in the accessed                             |     |

|      | cell, maximizing leakage in opposition of the desired read                                        | 131 |

| 5-20 | Simulation of scenario in Figure 5-19 showing steady-state bitline volt-    |      |

|------|-----------------------------------------------------------------------------|------|

|      | ages. Bitline leakage severely limits the number of cells that can share    |      |

|      | a bitline                                                                   | 132  |

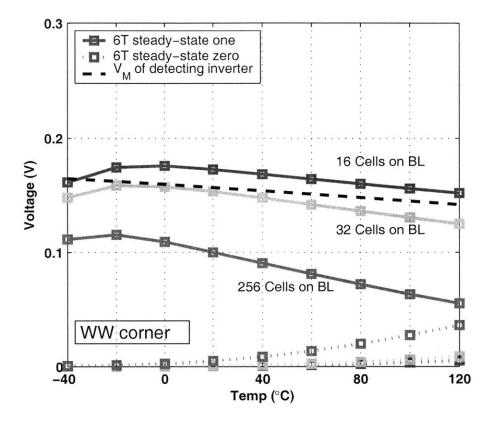

| 5-21 | First-order VTC equations versus simulation for hold (a) and for read       |      |

|      | (b). Line A is (5.2), line B is (5.3), line C is a piecewise combination    |      |

|      | of (5.5) and (5.2), and line D is a piecewise combination of (5.3) and      |      |

|      | the graphical inverse of $(5.5)$                                            | 135  |

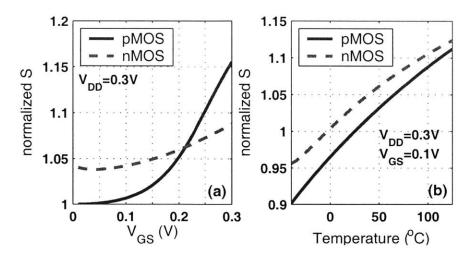

| 5-22 | Changes in sub-threshold slope (S) versus $V_{CS}$ (a) and temperature (b). | .136 |

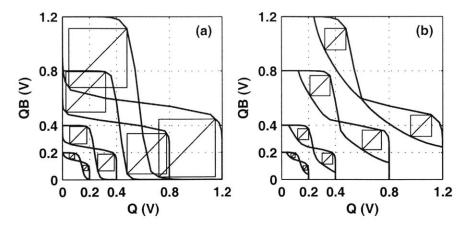

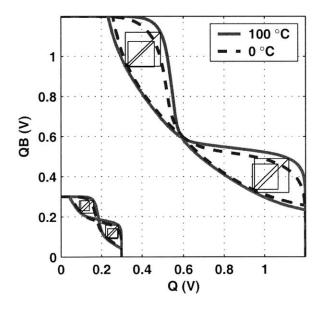

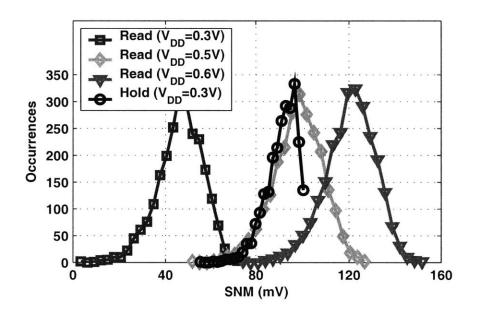

| 5-23 | VTCs for Hold (a) and Read (b) with varying $V_{DD}$                        | 137  |

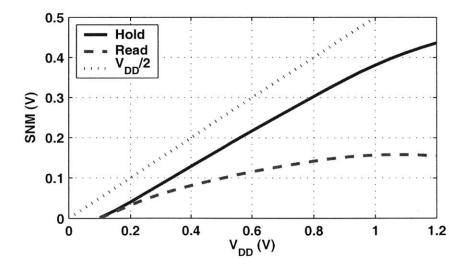

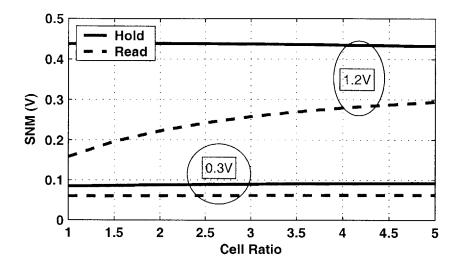

| 5-24 | SNM versus $V_{DD}$                                                         | 137  |

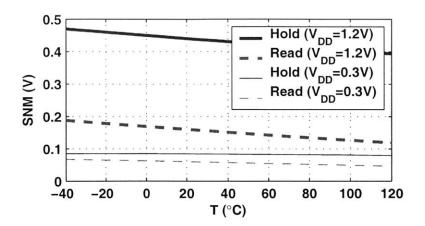

| 5-25 | SNM versus temperature                                                      | 138  |

| 5-26 | VTCs during a read access across temperature                                | 138  |

| 5-27 | Cell ratio affects SNM less in sub-threshold                                | 139  |

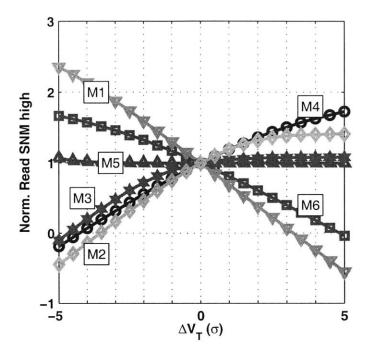

| 5-28 | Dependence of SNM high on single FETs is nearly linear                      | 140  |

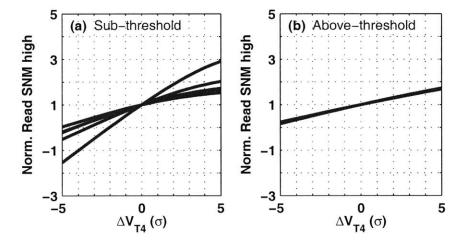

| 5-29 | Dependence of SNM high on a single FET depends on other $V_T{ m s}$ in      |      |

|      | sub-threshold (a), unlike for above-threshold (b)                           | 140  |

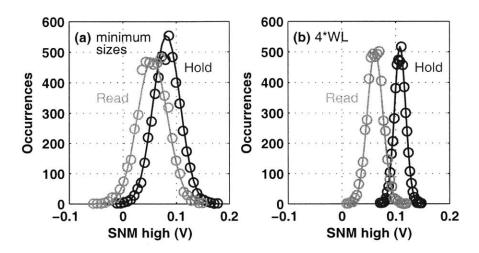

| 5-30 | SNM high and low (not shown) for a minimum sized cell (a) and for           |      |

|      | $4*W*L$ (b) is normally distributed with random $V_T$ mismatch in all       |      |

|      | transistors                                                                 | 141  |

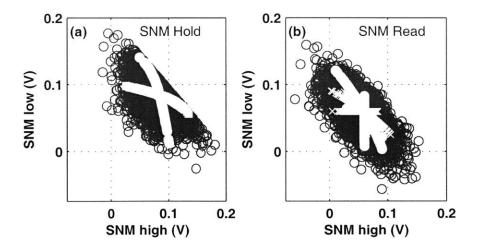

| 5-31 | Scatter plots for SNM high vs. SNM low with single FET dependencies         |      |

|      | overlaid in white                                                           | 142  |

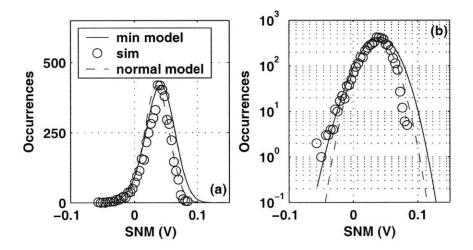

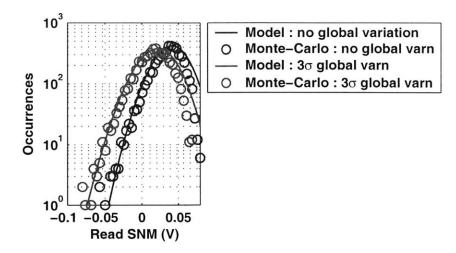

| 5-32 | Histogram of Read SNM Monte-Carlo simulation (circles) with normal          |      |

|      | PDF (dash) and PDF based on (5.7) (solid) over-laid. The semilog            |      |

|      | plot (b) shows that the PDF based on (5.7) matches the worst-case           |      |

|      | tail quite well                                                             | 142  |

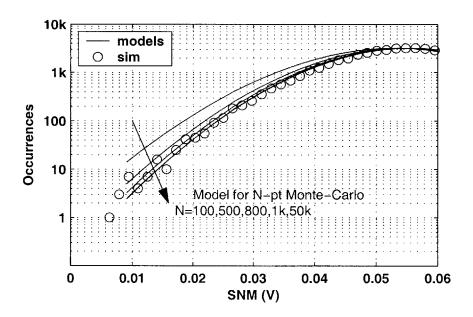

| 5-33 | 50k-point Monte-Carlo simulation for SNM with $4*WL$ sized transis-         |      |

|      | tors. Model based on 1k-point Monte-Carlo data matches the 50k-point        |      |

|      | model with $< 3\%$ error                                                    | 143  |

| 5-34 | Monte-Carlo simulation showing global variation impact on SNM for           |      |

|      | a minimum sized bitcell                                                     | 145  |

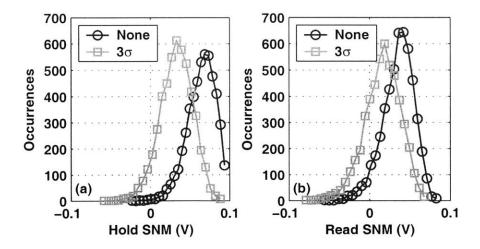

| 5-35 | SNM Monte-Carlo simulations for local mismatch on top of global vari-                          |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | ation                                                                                          | 146 |

| 5-36 | SNM Monte-Carlo simulations for local mismatch on top of global vari-                          |     |

|      | ation (none or $3\sigma$ ) compared to the model for Hold (a) and Read (b).                    | 147 |

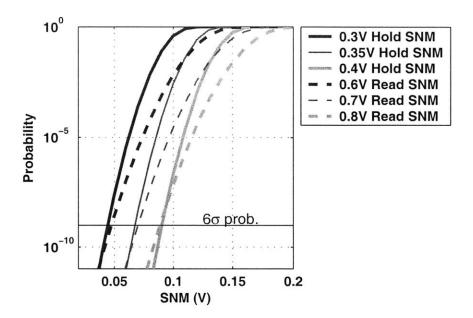

| 5-37 | Distribution of Hold SNM at 300mV compared with Read SNM dis-                                  |     |

|      | tributions at different voltages. Read SNM at $500 \mathrm{mV}$ has the same                   |     |

|      | mean, but it has a larger standard deviation                                                   | 147 |

| 5-38 | Cumulative Distribution Functions (CDFs) of SNM distributions show-                            |     |

|      | ing that avoiding the Read SNM allows a reduction in $V_{DD}$ by $\sim 0.5$                    |     |

|      | for the same $6\sigma$ stability                                                               | 148 |

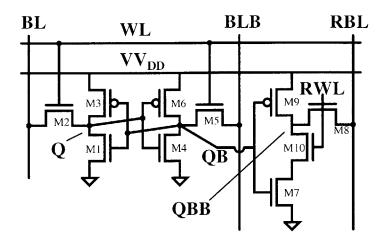

| 5-39 | Schematic of the 10T sub-threshold bitcell                                                     | 150 |

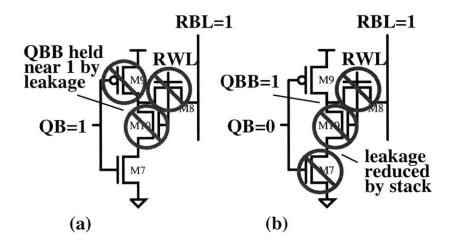

| 5-40 | Schematic of read buffer from 10T bitcell for both data values. In both                        |     |

|      | cases, leakage is reduced to the bitline and through the inverter relative                     |     |

|      | to the case where $M_{10}$ is excluded                                                         | 151 |

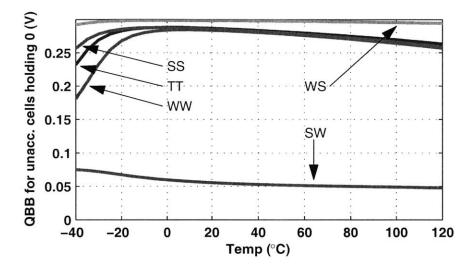

| 5-41 | Simulation of voltage at node QBB in unaccessed 10T bitcells versus                            |     |

|      | temperature and process corner. Strong pMOS leakage holds QBB                                  |     |

|      | near $V_{DD}$ except at the SW corner. Even at SW, QBB is higher than                          |     |

|      | it is for the 6T cell, lowering bitline leakage                                                | 152 |

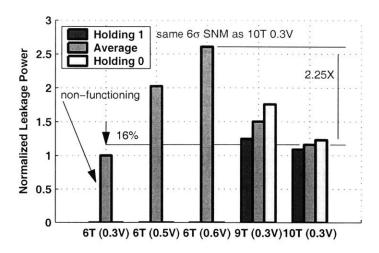

| 5-42 | Relative leakage of bitcells. The 10T bitcell imposes $16\%$ overhead                          |     |

|      | leakage at 300mV, but the 6T bitcell cannot function at that voltage                           |     |

|      | (it can only hold data). The $10\mathrm{T}$ cell saves $2.25\mathrm{X}$ leakage power relative |     |

|      | to the 6T at 0.6V                                                                              | 153 |

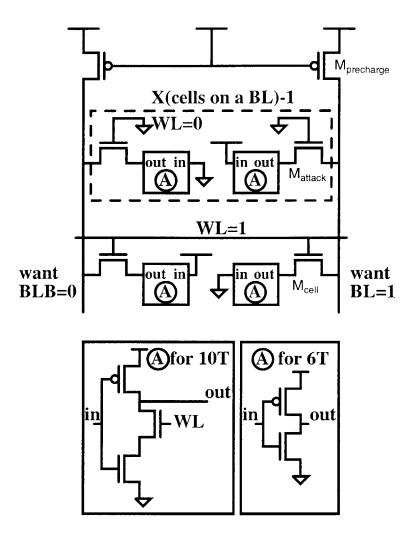

| 5-43 | Schematic showing the simulation set-up for estimating the worst-case                          |     |

|      | steady-state bitline voltages when expecting a '0' or '1'. The same                            |     |

|      | setup works for both 10T and 6T depending on which cell (A) is used                            |     |

|      | for the simulation.                                                                            | 154 |

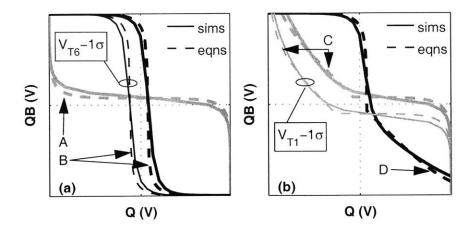

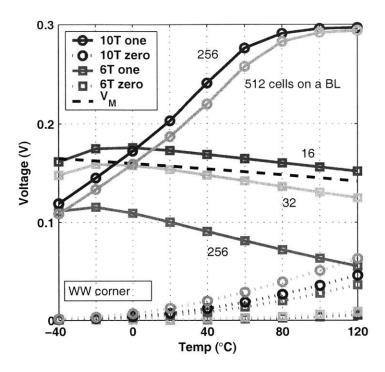

| 5-44 | Simulation of scenario in Figure 5-43 showing steady-state bitline volt-                       |     |

|      | ages. The 10T bitcell exhibits much better steady-state bitline sepa-                          |     |

|      | ration than the 6T cell. The WW corner is shown at 300mV                                       | 155 |

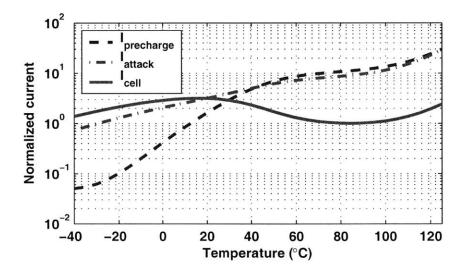

| 5-45 | Plot showing relative currents at steady-state in the worst-case for                  |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | bitline leakage for the $10\mathrm{T}$ cell (transistors in Figure 5-43) at the WW    |     |

|      | corner                                                                                | 155 |

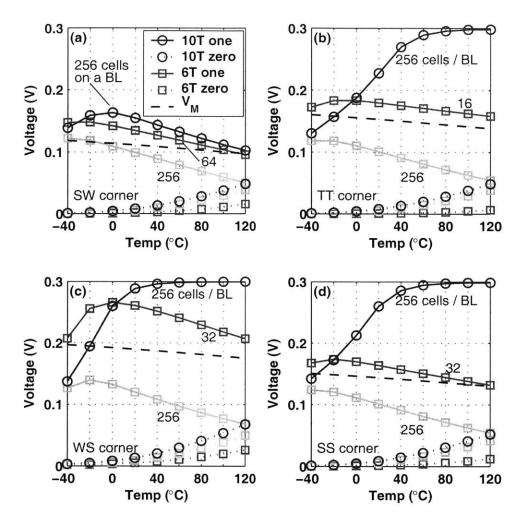

| 5-46 | Simulation of scenario in Figure 5-43 showing steady-state bitline volt-              |     |

|      | ages for the SW corner (a), the TT corner (b), the WS corner, (c), and                |     |

|      | the SS corner (d)                                                                     | 157 |

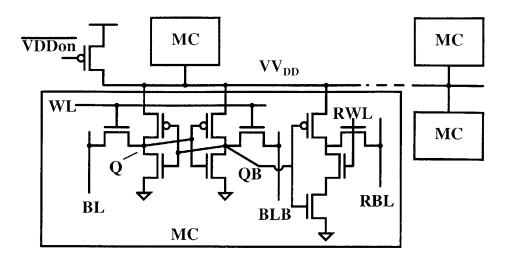

| 5-47 | Schematic of write architecture for a single row using a floating power               |     |

|      | supply $(VV_{DD})$ . The row is 'folded' in layout so that its cells share            |     |

|      | n-wells, and the entire row is written at once.                                       | 158 |

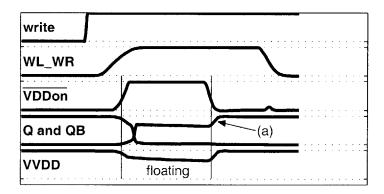

| 5-48 | Timing diagram for write operation. When $\overline{V_{DDon}}$ goes low while         |     |

|      | $WL_{WR}$ remains asserted, the cell's feedback restores full voltage levels          |     |

|      | for the new values of Q and QB (point (a))                                            | 158 |

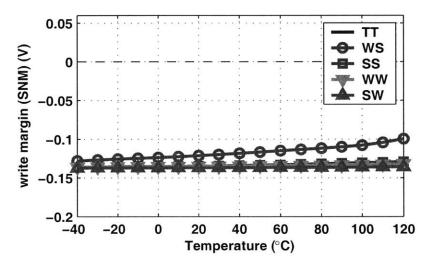

| 5-49 | Write margin (write SNM) versus temperature at 0.3V for 10T bitcell                   |     |

|      | with floating $VV_{DD}$ supply. Negative margin for all corners, signifying           |     |

|      | successful write operation                                                            | 159 |

| 5-50 | VTCs showing write SNM with and without using a virtual power rail                    |     |

|      | $(VV_{DD})$ at $V_{DD}=300 \mathrm{mV}$ . Normal write fails even under normal condi- |     |

|      | tions of process corner and temperature, but the virtual rail approach                |     |

|      | works even in the worst-case as shown by significant negative noise                   |     |

|      | margin                                                                                | 160 |

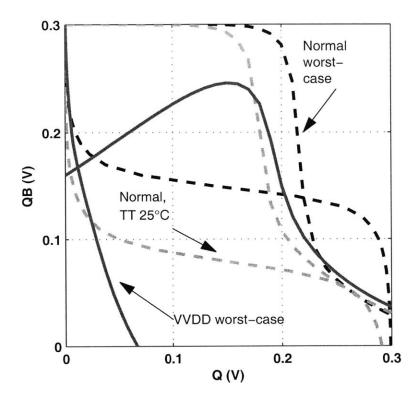

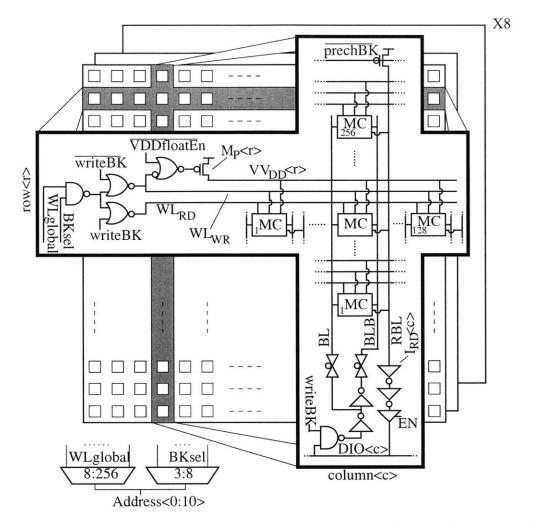

| 5-51 | Architecture diagram of the 256kb memory on the test chip using $10\mathrm{T}$        |     |

|      | sub-threshold bitcells                                                                | 162 |

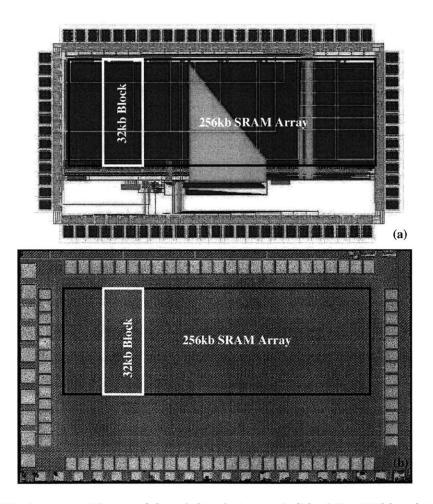

| 5-52 | Annotated layout (a) and die photograph (b) of the 256kb sub-threshold                |     |

|      | SRAM in 65nm. Die size is 1.89mm by 1.12mm                                            | 165 |

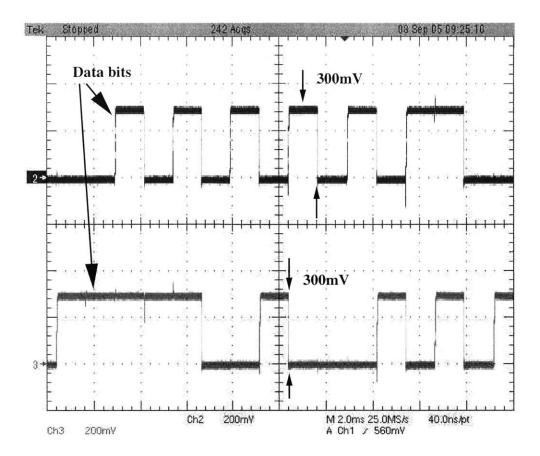

| 5-53 | Oscilloscope waveform showing correct functionality at $V_{DD}=300 \mathrm{mV}.$      |     |

|      | At this low voltage, a small fraction of bits have errors                             | 166 |

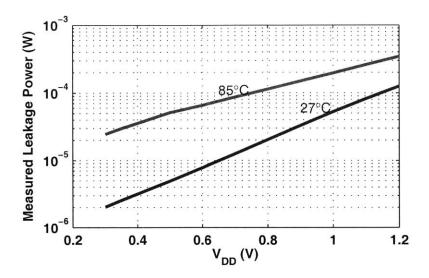

| 5-54 | Measured leakage power from the memory test chip                                      | 167 |

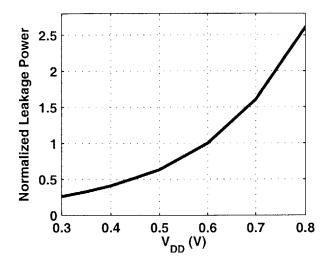

| 5-55 | Relative leakage power savings at 27°C achieved by $V_{DD}$ scaling                   | 168 |

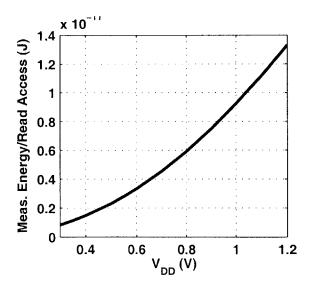

| 5-56 | Measured active energy per read access.                                               | 168 |

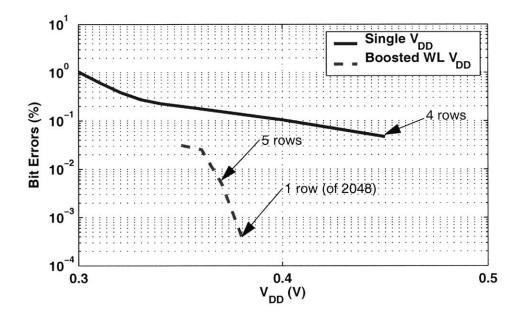

| 5-57 | Measured percentage of bit errors for read versus $V_{DD}$ . Boosting the   | of bit errors for read versus $V_{DD}$ . Boosting the |  |

|------|-----------------------------------------------------------------------------|-------------------------------------------------------|--|

|      | WL voltage dramatically reduces these errors                                | 169                                                   |  |

| 5-58 | Measured percentage of bit errors for write versus $V_{DD}$ . Again, boost- |                                                       |  |

|      | ing the WL voltage dramatically reduces these errors                        | 171                                                   |  |

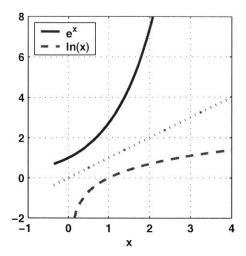

| B-1  | The natural log function, $W = \ln x$ , provides the inverse of $e^W = x$   |                                                       |  |

|      | and is analogous to the Lambert W Function                                  | 188                                                   |  |

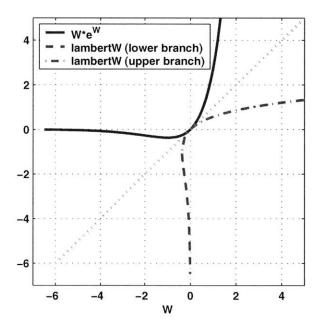

| B-2  | The Lambert W Function, $W = lambertW(x)$ , gives the solution to           |                                                       |  |

|      | $We^{W}=x$ . This plot shows the inverse relationship between these two     |                                                       |  |

|      | equations, and it shows the upper and lower branch solutions for the        |                                                       |  |

|      | Lambert W Function                                                          | 188                                                   |  |

## List of Tables

| 1.1 | Examples of power densities for potential energy harvesting mechanisms | 35  |

|-----|------------------------------------------------------------------------|-----|

| 1.2 | Power savings from voltage reduction alone (constant current)          | 37  |

| 1.3 | Active energy savings from voltage reduction                           | 39  |

| 5.1 | System-level modes of operation for SRAM                               | 104 |

| 5.2 | Voltage scaling approaches used for SRAM                               | 112 |

| 5.3 | 6T and 10T architecture comparison                                     | 163 |

## Chapter 1

### Introduction

#### 1.1 Problem Statement

The Integrated Circuits (ICs) world is accustomed at this point to following Moore's Law. Gordon Moore first posed his famous relation in 1965 when he observed an annual doubling of the number of transistors on a die [13]. Since that time, the IC industry has maintained the astounding exponential trends that Moore first observed by continuing to scale process technologies. As Moore joked in his 2003 keynote address to the IEEE International Solid-State Circuits Conference, "Moore's Law" now commonly refers to any set of data that, when plotted on a semilog plot, yields a straight line. His talk showed the benefits of scaling according to Moore's Law. Semiconductor revenue and transistors shipped per year have increased exponentially as the average price per transistor has dropped off exponentially with the minimum feature size. An additional benefit of this scaling is the increased performance of circuits, as Moore demonstrated by plotting MIPS versus years; sure enough, they increase exponentially. As Moore points out, however, no exponential can continue forever. In fact, process scaling has produced a number of problems that threaten to stop these exponential trends. Perhaps most notably, both the active and leakage power of processors are increasing exponentially as scaling continues [14].

As each new technology rolls out of the fab, it offers smaller transistors. The traditional goal is to reduce the minimum feature size by 30% with each new technology.

nology. This scaling theoretically will allow gate delays to decrease by 30% and area to lower by 50%. Likewise, active power should decrease for a given circuit by 30% to 65% due to smaller transistors and lower supply voltage [15]. These gains sound straight-forward, but in reality, technology scaling has become an extremely complicated process. For example, shorter transistors with thinner gate oxide require a lower supply voltage to avoid wear-out. Lowering  $V_{DD}$  too much prevents the desired decrease in delay, so the device threshold voltage,  $V_T$ , must also decrease. Lowering  $V_T$  leads to the exponential increase in sub-threshold leakage current, which increases leakage power and affects circuits like dynamic gates and memories [15]. These types of trade-offs ultimately mean that the problems facing process and circuit engineers become more complicated with each generation. Additionally, rather than simply porting old designs, chip designers take advantage of smaller devices to throw more transistors at their designs so that, for example, overall microprocessor energy increases with time and now measures over 100W [14]. Furthermore, leakage power contributes a sizeable percentage of total power [16].

High-performance applications such as microprocessors face a crop of issues related to increased power consumption. These include temperature management, heat removal, power supply networks, power density, reliability, etc. Furthermore, although it previously provided the dominant metric for almost all designs, speed is not the ultimate metric for all modern applications. Instead, a broad class of applications are emerging for which power and more specifically energy is a fundamental problem. These low power applications do not require the blazing performance of high end processors. Low power applications include portable devices such as cell phones, Personal Digital Assistant (PDA)s, and cameras. For this class of applications, lower performance requirements coupled with the need for portability demand the introduction of more stringent power constraints. Other emerging applications such as distributed sensor networks or medical applications have low energy operation as the primary concern instead of performance. These applications must maintain long system lifetimes with severely constrained energy resources. Thus, the most critical metric for a successful system is energy per operation.

All of this attention on power consumption in circuit design has motivated a significant investigation of the optimum design for minimizing energy or power. Although most of this work assumes a performance constraint, examination of voltage scaling has shown that true minimum energy operation usually occurs in the sub-threshold region  $(V_{DD} < V_T)$  [17][18]. While initial explorations into sub-threshold circuits demonstrate its promise, sub-threshold circuit design is not a well-developed field. A more complete understanding of how the minimum energy solution changes in different scenarios will make sub-threshold design more attractive for generic systems. Also, since many systems cannot operate exclusively in sub-threshold, it is important to explore ways to couple sub-threshold operation with higher performance modes. Finally, previous work with sub-threshold circuits has focused on combinational logic. Full sub-threshold systems are not possible without memories that function in the sub-threshold region.

This thesis focuses on extending the state-of-the-art for sub-threshold design of digital circuits by addressing these issues. The remainder of this chapter introduces micro-sensor networks as an example application class that fits well with sub-threshold circuits, points out previous work on digital sub-threshold circuits, describes the basics of digital operation in sub-threshold, and lists the contributions of this thesis.

#### 1.2 Micro-sensor Networks and Nodes

Since the optimum supply voltage for minimizing total digital energy often occurs in sub-threshold, severely energy-constrained applications can benefit from this circuit design approach. Micro-sensor networks and the micro-sensor nodes that comprise them are one energy-constrained class of systems that provide a compelling driver for sub-threshold circuit operation primarily because the most critical limitation for micro-sensor node cost and volume is energy [19]. A micro-sensor node refers to physical hardware that provides sensing, computation, and communication functionality. A wireless micro-sensor network consists of tens to thousands of distributed nodes that sense and process data and relay it to the end-user. In the context of sen-

sor networks, the sensor node usually is further defined to have a small form factor and an energy-constraint that is often the node's primary limitation. Typically, this constraint is imposed by the capacity of the node's battery. For this reason, most micro-sensor nodes duty cycle, or shutdown unused components whenever possible. Although duty cycling helps to extend sensor network lifetimes, it does not remove the energy constraint placed by the battery.

This section describes the basic concepts related to micro-sensor nodes, focusing on the applications for which they are designed and the subsequent requirements for energy consumption. The breadth of applications and the energy-constrained nature of micro-sensor networks points to the need for circuits that consume minimal energy and, in some cases, that can scale in performance from ultra-low levels to top-speed operation.

The fervor of research related to micro-sensor networks in recent years attests to the variety of interesting problems faced in actually implementing and using the networks. In addition to the academic value of micro-sensor networks, there are numerous real and proposed applications for putting them to use. The following section gives a look at some of the many potential applications for micro-sensor nodes.

#### 1.2.1 Micro-sensor Applications

Proposed applications for micro-sensor networks often seem to be as numerous as the nodes in a network. This section describes some promising areas of application for micro-sensor networks to show that their requirements fit well with the strengths of sub-threshold circuits. The applications we mention are by no mean comprehensive.

#### Habitat Monitoring

Habitat monitoring involves long-term data collection from a natural environment, primarily for scientific study [20]. A key constraint for this application is that the solution be unobtrusive. If the process of data collection regularly disrupts the environment under observation, then it inherently changes the validity of the data itself.

Additionally, direct human disturbance can disrupt fragile animals or habitats and, even if unintentionally, can be destructive. Micro-sensor networks offer a compelling solution to this problem. If micro-sensors have a small enough form factor, they can exist in a natural environment without causing as much disruption as direct human observation (think guy in a tree with binoculars). Also, the potential for a high node density covering a large area translates to large scale data collection with high resolution. Clearly, to satisfy the requirement for unobtrusiveness, the nodes must have long lifetimes to avoid the need for re-insertion of the network. This translates directly to the need for minimizing energy per operation.

Micro-sensor networks have been employed successfully for habitat monitoring already. For example, a micro-sensor network on Great Duck Island in Maine monitors the nesting behavior of seabirds (the Leach's Storm Petrel) [21]. Specifically, the nodes collect data on the nesting environment, such as temperature, humidity, etc. Also, temperature data from inside the nests accounts for the comings and goings of the birds themselves, since the bird's body heat registers with the sensor node. The network must last for the duration of the nesting season (months) so that researchers never have to physically visit the island during that time. Thus, the energy constraint is the most important concern for this network. Furthermore, [21] proposes that compressing data on the nodes prior to communicating data can save energy overall. This points to the need more specifically for low energy digital computation.

The PODS project at the University of Hawaii gives another example of microsensor network for habitat monitoring. This network monitors the habitats of endangered species of plants [22]. In addition to measuring environmental parameters, the micro-sensor nodes collect, process, and send high-resolution image data. Since these plants are very fragile, the micro-sensors allow scientists to collect data without regularly visiting the site.

#### Environment Observation and Forecasting System (EOFS)

Environment Observation and Forecasting Systems (EOFSs) are similar to habitat monitoring, but they cover a much larger geographic area. These proposed systems collect data that can be post-processed to produce models and ultimately to forecast certain phenomena such as weather, flooding, or pollution along beaches.

One early implementation of an EOFS systems called CORIE monitors data from the lower Columbia River in Oregon [23]. Based on information gathered at different stations, the project predicts complicated circulation and mixing processes at the river's mouth. These results have implications for the habitats of local wildlife as well as for hydropower management. The initial implementation uses a relatively small number of fixed sensoring points. This type of research provides an ideal scenario for micro-sensor networks, which could extend the resolution and quality of acquired data. Also, the broad geographic distribution of the sensors makes energy efficiency important to avoid the cost of replacing all of the nodes.

The Automated Local Evaluation in Real-Time (ALERT) is a second example of an EOFS [24]. The National Weather Service implemented this system in the 1970's to monitor for potential flooding [24]. The current implementation uses a variety of different hardware. Again, this type of system would be streamlined by the use of a micro-sensor network.

#### Health

There are many opportunities in the category of health to use micro-sensor networks. Since many of these applications involve direct contact of the micro-sensor nodes with human patients, either implanted or external, the micro-sensor nodes must be very safe and reliable. For certain implantable nodes, additional constraints may apply, such as a limit on the amount of heat that can be dissipated due to power consumption (e.g. in the eye). Also, the energy constraint becomes very important especially for implantable nodes, because replacing a node or its battery requires surgery.

One example of an implantable micro-sensor network is an array of micro-sensors used as an artificial retina [25]. The package containing this array rests on the retina of the patient and stimulates the retina using electrical signals that physically contact the retina through micro bumps. As this type of technology progresses, it could conceivably help blind people to sense light with enough resolution to 'see'.

Another potential application is for glucose monitoring [25]. Implantable sensors could detect the glucose levels in the blood of a diabetic patient. This allows the patient to forgo daily finger pricks and provides earlier notification when insulin is needed. Other example applications for medical sensors include monitoring organs that are awaiting transplant, early detection of cancer cells via implantable sensors, and general health monitors (heart rate, blood pressure, temperature, etc.) [25].

There certainly are other opportunities to extend the lifetime of implantable medical devices (e.g. pacemakers, cochlear implants) using sub-threshold operation, but these devices are not micro-sensors.

#### Structural Monitoring

Structural Health Monitoring (SHM) has the goal of identifying damage in large structures [26]. A great variety of techniques fall into this category, and sensor arrays play a big part. For example, an array of sensors crafted into an optic fiber is used to monitor bridges in [27]. Likewise, sensor arrays (although not necessarily wireless arrays) are under investigation for deployment in vehicles such as aircraft [28] for monitoring structural integrity. Most SHM analysis is based on detecting the response of the structure to either ambient or applied vibrations. Wireless micro-sensors are well-suited to SHM, because they add flexibility to sensor placement and avoid the cost of running wires to numerous sensors [26]. Micro-sensor networks in this scenario also add fault tolerance and increase the rate of detection relative to other systems [29].

#### Other Applications

The examples of micro-sensor applications in the preceding sections only give a glimpse of the many possibilities. Other examples include sensors in tires to monitor tire pressure and networks distributed through automotive exhaust system for emission measurement [25]. The military is interested in wireless micro-sensors for target tracking on the battlefield and for early biological and chemical weapons detection. Micro-sensor networks in cities can monitor traffic density, and networks in

buildings can oversee climate control. Even Hollywood is getting excited; embedding micro-sensors in a scene during filming allows easy post-processing for synchronizing special effects and computer generated characters with the video [30]. Numerous other applications are also under investigation or being imagined [31][32].

Conservation and efficient use of energy is a key requirement for micro-sensor nodes in all of the applications that we have described. This problem must be addressed in all modes of operation. Since sub-threshold circuits can minimize energy per operation, they are an ideal choice for implementing micro-sensor nodes.

#### 1.2.2 Micro-sensor Nodes

Over the last decade, several academic and industrial research groups have been actively designing wireless micro-sensor nodes. Most of these nodes contain sensing capability, processing or computational capability, and structures for wireless communication. Micro-sensor nodes (for low end applications) use special architectures (e.g. [33][34]). Many algorithms are developed specifically for micro-sensor nodes (e.g. distributed local algorithms [32]).

Examples of micro-sensor nodes include the Wireless Integrated Network Sensors (WINS) at UCLA [19], Crossbow Technology's Mica2 sensor node [35], the Telos mote [36], UC Berkeley's Smartdust [37], and the Massachusetts Institute of Technology's  $\mu$ AMPS node [38].

The earlier implementations of many of these nodes used commercial, off-the-shelf (COTS) components. Now many of the nodes use custom ICs that are tailored to the micro-sensor application space. As the nodes become more specialized, sub-threshold circuit design can make a significant impact on reducing overall power consumption in the nodes, where processor [35] power can be 50% of total power on average [33].

#### 1.3 Energy Harvesting

For some micro-sensor applications, a limited lifetime is sufficient, and a non-rechargeable battery power is the logical choice. A 1cm<sup>3</sup> Lithium battery can continuously supply  $10\mu W$  of power for five years [39]. However, some applications demand higher peak power or a longer lifetime in an environment where changing batteries is impractical or impossible. These types of applications require a renewable energy source. The concept of energy harvesting or energy scavenging involves converting ambient energy from the environment into electrical energy to power circuits or to recharge a battery.

Research into energy scavenging suggests that micro-sensors can utilize energy harvested from the environment. The most familiar sources of ambient energy include solar power, thermal gradients, radio-frequency (RF), and mechanical vibration. Ta-

Table 1.1: Examples of power densities for potential energy harvesting mechanisms

| Technology                           | Power Density $(\mu W/cm^2)$ |

|--------------------------------------|------------------------------|

| Vibration - electromagnetic [40]     | 4.0                          |

| Vibration - piezoelectric [39]       | 500                          |

| Vibration - electrostatic [41]       | 3.8                          |

| Thermoelectric (5°C difference) [42] | 60                           |

| Solar - direct sunlight [43]         | 3700                         |

| Solar - indoor [43]                  | 3.2                          |

ble 1.1 [44] gives a comparison of some energy harvesting technologies. Power per area is reported because the thickness of these devices is typically dominated by the other two dimensions. The power available from these sources is highly dependent on the nodes environment at any given time. However, these examples show that it is reasonable to expect 10's of microwatts of power to be harvested from ambient energy. Thus, researchers agree that micro-sensor nodes must keep average power consumption in the  $10\text{-}100\mu\text{W}$  range to enable energy scavenging [37][33]. Coupling energy harvesting hardware with the micro-sensor node can lead to self-powered micro-sensor networks (e.g. [45]). Barring significant advances in energy scavenging technology, the high instantaneous power consumption of an active wireless transceiver (mil-

liwatts for Mbps) requires micro-sensors to retain local energy storage. Coupling energy-harvesting techniques with some form of energy storage can theoretically extend micro-sensor node lifetimes indefinitely. Clearly, this type of system will greatly benefit from the significant power and energy savings made possible by sub-threshold operation.

# 1.4 Sub-threshold Operation