### Automating the Construction of Compiler Heuristics Using Machine Learning

by

Mark W. Stephenson

Bachelor of Science, Computer Engineering University of Utah, 1998

Master of Science, Electrical Engineering and Computer Science Massachusetts Institute of Technology, 2000

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy of Science in Computer Science and Engineering

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2006

© Massachusetts Institute of Technology 2006. All rights reserved.

Author ...... Department of Electrical Engineering and Computer Science May 23, 2006

Certified by.....

Safnan Amarasınghe Associate Professor

Accepted by .....

C. Smith Chairman, Department Committee on Graduate Students

BARKER

#### Automating the Construction of Compiler Heuristics Using Machine Learning

by

Mark W. Stephenson

Submitted to the Department of Electrical Engineering and Computer Science on May 23, 2006, in partial fulfillment of the requirements for the degree of Doctor of Philosophy of Science in Computer Science and Engineering

#### Abstract

Compiler writers are expected to create effective and inexpensive solutions to NP-hard problems such as instruction scheduling and register allocation. To make matters worse, separate optimization phases have strong interactions and competing resource constraints. Compiler writers deal with system complexity by dividing the problem into multiple phases and devising approximate heuristics for each phase. However, to achieve satisfactory performance, developers are forced to manually tweak their heuristics with trial-and-error experimentation.

In this dissertation I present meta optimization, a methodology for automatically constructing high quality compiler heuristics using machine learning techniques. This thesis describes machine-learned heuristics for three important compiler optimizations: hyperblock formation, register allocation, and loop unrolling. The machine-learned heuristics outperform (by as much as 3x in some cases) their state-of-the-art hand-crafted counterparts. By automatically collecting data and systematically analyzing them, my techniques discover subtle interactions that even experienced engineers would likely overlook. In addition to improving performance, my techniques can significantly reduce the human effort involved in compiler design. Machine learning algorithms can design critical portions of compiler heuristics, thereby freeing the human designer to focus on compiler correctness.

The progression of experiments I conduct in this thesis leads to *collaborative compilation*, an approach which enables ordinary users to transparently train compiler heuristics by running their applications as they normally would. The collaborative system automatically adapts itself to the applications in which a community of users is interested.

Thesis Supervisor: Saman Amarasinghe Title: Associate Professor

#### Acknowledgments

I want to begin by thanking the people who directly contributed to this thesis. First on the list is my advisor, Saman Amarasinghe. I can't thank him enough for his time, ideas, sound advice, friendship, and yes, financial support during the seven years he advised me. It's pretty scary how quickly Saman can digest, distill, and evaluate ideas; his ability to quickly discard my harebrained ideas came in pretty handy. I also thank Saman for giving me the flexibility to work on the projects that interested me the most. I feel genuinely lucky to have had him as an advisor. Thanks to Una-May O'Reilly, Martin Martin, Ben Wagner, and Diego Puppin for contributing so much to the ideas presented in this dissertation. Thanks also to my thesis committee — Leslie Kaelbling, Una-May O'Reilly, and Martin Rinard — for giving me great feedback on this dissertation. It was a pleasure and a privilege to work with you all. Thanks to all my sources of funding: NSF Graduate Fellowship, NSF grants EIA9810173, EIA-0071841, and CCR- 0073510, and DARPA grants DBT63-96-C-0036, F29601-01-2-0166, PCA-F29601-03-2-0065, F3060200-2-0562, and HPCA/PERCS-W0133890.

Next on the list, I give a collective shout-out to the "Institute"; I really can't think of a better (academic) place to spend eight years. I thank the student body and faculty at MIT for being so damn brilliant and open to anything.

I have had a lot of mentors during my academic career. I want to thank Erik Brunvand, Al Davis, and Mike Parker at the University of Utah; it was truly an honor to work under them. Thanks to Matt Frank, Michael Taylor, Walter Lee, Ben Greenwald, David Wentzlaff, and the rest of the RAW group for showing me the ropes. Jon Babb, MIT just hasn't been the same since you graduated: thanks for your guidance during my first couple of years and for showering me with all of your "Babb" ideas. Thanks to the many fine members of the Assam group, especially Heidi Pan, Mark Hampton, and Jessica Tseng. Anant Agarwal and Krste Asanović deserve special recognition for being such approachable and wise sounding boards. Anant has an amazing blend of intellect, charisma, and suaveness that makes people clamor to be around him. Krste is incredible because, among other things, he's the smartest person in the world. Seriously.

There are two people who I want to thank for caring so much about the welfare of students: Mary McDavitt and Srini Devadas. To properly thank Mary McDavitt would take too long. Mary goes *way* above the call of duty and I hope she knows how much the students love her for that (she baked me a Guinness cake for my defense for heaven's sake). Similarly, Srini takes it upon himself to know the students around him. I love running into him at the water cooler because he always has some bit of advice or funny observation to share.

I am fortunate to have belonged to the commit group, and I thank all of its past and current members for making the lab a pleasant place to be. The group has seen its share of amazing people. Bill Thies, you are a brilliant man, and I thank you for all your insights and help over the years; you will most likely win a Nobel Prize someday. The whole commit group was also lucky to have recruited Rodric Rabbah. Rodric is the first (and usually the last) person I go to whenever I have a question. He is the man. Ben Wagner is a star, and it has been fantastic working alongside him.

I've made the best friends I could *ever* have during my time at MIT. Michael Zhang, you made 80 Allston Street what it was. Michael "Gordo" Gordon, pub crawling wouldn't have been the same without you. Ronny "Ralph's<sup>®</sup> Rewards Card" Krashinsky, I truly think you're the man (you have to share this title with Rodric). Steve Gerding, buddy, you are quite possibly the most entertaining person I have ever met. And Sam "[expletive]" Larsen! Thanks for not only being such a great colleague, but for being such a damn fantastic friend over the years. I'm going to miss you guys.

I'd like to thank the people who have *always* been there for me: my family. Even though my parents have *no idea* what I've been working on for the last eight years, they couldn't be prouder, and I'm grateful for that. I'm proud of you too mom and dad. My sister Donna and my brothers Joe and Bob (and their families) are the best, and it saddens me that I don't get to see them more often. And Dominic Primé isn't technically a brother of mine, but it sure seems like he is. I don't know where I'd be without you all.

Finally, über thanks to my fiancée, Kristen Grauman. She's without a doubt the best thing that's ever happened to me.

## Contents

| 1 | Intr  | roduction                                           | 17 |

|---|-------|-----------------------------------------------------|----|

|   | 1.1   | Challenges Facing Compiler Writers                  | 19 |

|   | 1.2   | Overview of Meta Optimization                       | 23 |

|   | 1.3   | Contributions                                       | 25 |

|   | 1.4   | Roadmap                                             | 26 |

| 2 | Cor   | npiler Construction                                 | 27 |

|   | 2.1   | Compiler Flow                                       | 27 |

|   | 2.2   | Important NP-Hard Compiler Problems                 | 33 |

|   |       | 2.2.1 Case Study: Instruction Scheduling            | 33 |

|   |       | 2.2.2 Heuristic Solution for Instruction Scheduling | 37 |

| 3 | Ма    | ta Optimization                                     | 41 |

| 3 | Ivrei |                                                     | 41 |

|   | 3.1   | Insight: Correctness v. Policy                      | 41 |

|   | 3.2   | Meta Optimization : Learning Effective              |    |

|   |       | Compiler Heuristics                                 | 43 |

|   |       | 3.2.1 Objective Search                              | 44 |

|   |      | 3.2.2   | Meta Optimization                     | 44 |

|---|------|---------|---------------------------------------|----|

|   | 3.3  | Using   | Empirical Observations                | 45 |

|   | 3.4  | Traini  | ing Compiler Policies                 | 46 |

| 4 | Sea  | rching  | and Pattern Recognition               | 49 |

|   | 4.1  | Search  | $\operatorname{ning}$                 | 49 |

|   |      | 4.1.1   | Exhaustive Search                     | 50 |

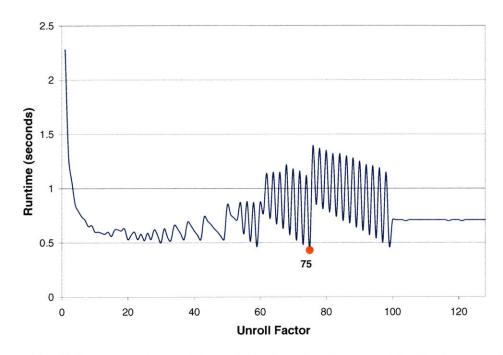

|   |      | 4.1.2   | Genetic Algorithms                    | 51 |

|   |      | 4.1.3   | Hill Climbing and Simulated Annealing | 53 |

|   | 4.2  | Super   | vised Learning                        | 55 |

|   |      | 4.2.1   | Regression                            | 55 |

|   |      | 4.2.2   | Classification                        | 59 |

|   |      | 4.2.3   | Validation for Supervised Learning    | 61 |

|   | 4.3  | Reinfo  | preement Learning                     | 62 |

| 5 | Poli | icy Sea | arch for Meta Optimization            | 65 |

|   | 5.1  | Priorit | ty Functions                          | 65 |

|   | 5.2  | Policy  | Search with Genetic Programming       | 67 |

|   | 5.3  | Metho   | odology                               | 71 |

|   | 5.4  | Case S  | Study I: Hyperblock Formation         | 75 |

|   |      | 5.4.1   | Branching v. Predication              | 75 |

|   |      | 5.4.2   | Feature Extraction                    | 78 |

|   |     | 5.4.3  | Trimaran's Heuristic                   | 80  |

|---|-----|--------|----------------------------------------|-----|

|   |     | 5.4.4  | Experimental Setup                     | 82  |

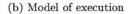

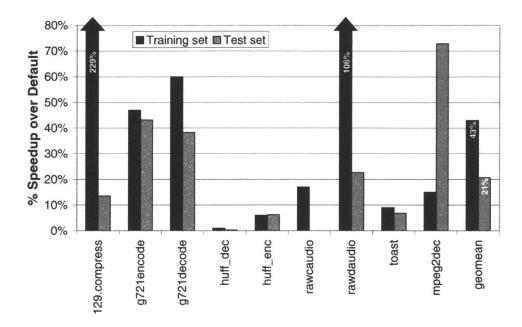

|   |     | 5.4.5  | Experimental Results                   | 83  |

|   | 5.5 | Case S | Study II: Register Allocation          | 90  |

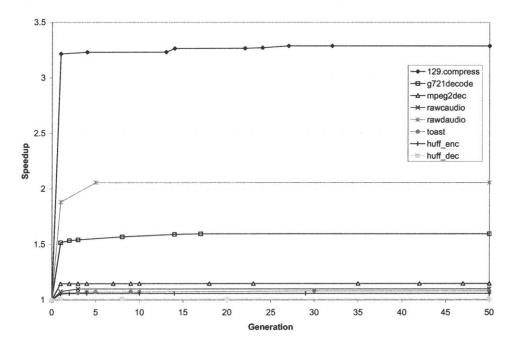

|   |     | 5.5.1  | Experimental Results                   | 91  |

|   | 5.6 | Effort | and Training Time Involved             | 97  |

|   | 5.7 | Conclu | usion                                  | 98  |

| 6 | Sup | ervise | d Learning for Meta Optimization       | 101 |

|   | 6.1 | Loop   | Unrolling                              | 102 |

|   | 6.2 | Metho  | odology and Infrastructure             | 104 |

|   |     | 6.2.1  | Supervised Learning                    | 105 |

|   |     | 6.2.2  | Compiler and Platform                  | 106 |

|   |     | 6.2.3  | Loop Instrumentation                   | 106 |

|   |     | 6.2.4  | Effort Involved                        | 108 |

|   |     | 6.2.5  | Benchmarks Used                        | 108 |

|   | 6.3 | Multi- | Class Classification                   | 109 |

|   |     | 6.3.1  | Near Neighbor Classification           | 109 |

|   |     | 6.3.2  | Support Vector Machines                | 111 |

|   | 6.4 | Exper  | iments with Multi-Class Classification | 114 |

|   |     | 6.4.1  | Realizing Speedups                     | 115 |

|   | 6.5 | Featur | re Selection                           | 117 |

|   |     | 6.5.1 Mutual Information Score                 | 117 |

|---|-----|------------------------------------------------|-----|

|   |     | 6.5.2 Greedy Feature Selection                 | 119 |

|   | 6.6 | Conclusion                                     | 120 |

| 7 | Col | laborative Data Collection                     | 123 |

|   | 7.1 | Collaborative Compilation                      | 123 |

|   | 7.2 | Collaborative Instrumentation                  | 127 |

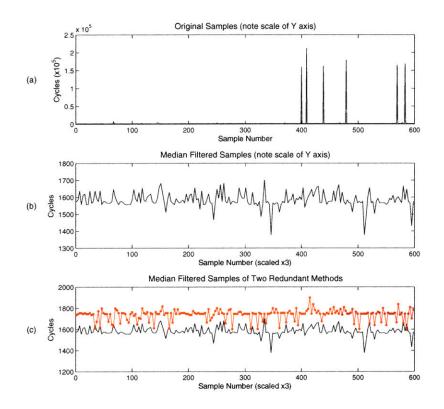

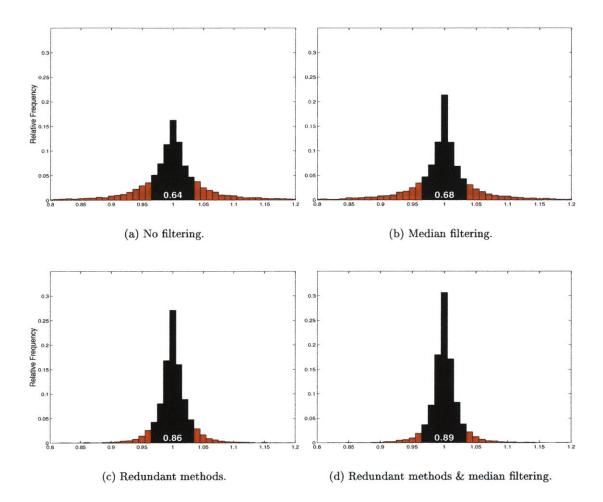

|   |     | 7.2.1 Coping with Noise                        | 129 |

|   |     | 7.2.2 Implementation Details                   | 135 |

|   |     | 7.2.3 Runtime Overhead                         | 135 |

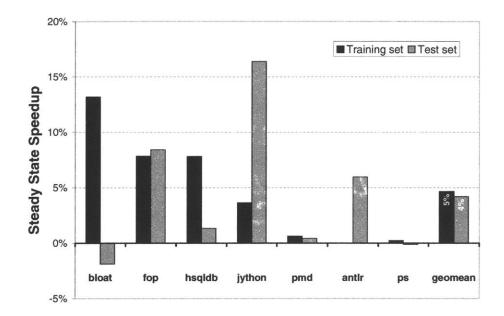

|   | 7.3 | Case Study: Improving Steady-State Performance | 136 |

|   | 7.4 | Reducing Privacy Concerns                      | 139 |

|   | 7.5 | Conclusion                                     | 139 |

| 8 | Rel | ated Work                                      | 141 |

|   | 8.1 | Program Specialization                         | 141 |

|   | 8.2 | Meta Optimization Related Work                 | 144 |

|   | 8.3 | Collaborative Compilation Related Work         | 146 |

| 9 | Con | nclusion                                       | 149 |

# List of Figures

| 1-1 | Layers of abstraction in a typical system                                    | 18 |

|-----|------------------------------------------------------------------------------|----|

| 1-2 | Anatomy of an optimizing compiler                                            | 20 |

| 2-1 | Anatomy of an optimizing compiler (repeat)                                   | 28 |

| 2-2 | An example control flow graph                                                | 29 |

| 2-3 | Optimization examples.                                                       | 31 |

| 2-4 | Instruction scheduling example                                               | 34 |

| 2-5 | The effectiveness of two different instruction schedules                     | 36 |

| 3-1 | Abstract depiction of a heuristic's task                                     | 42 |

| 3-2 | Various ways in which to train a compiler policy                             | 47 |

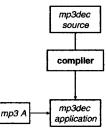

| 4-1 | Performance of a small matrix multiply kernel using various unroll factors . | 50 |

| 4-2 | Genetic algorithm flow and representation                                    | 52 |

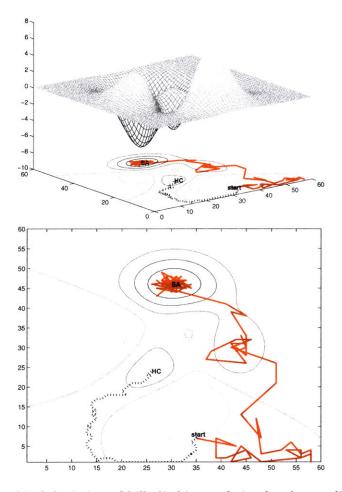

| 4-3 | Graphical depiction of hill climbing and simulated annealing                 | 54 |

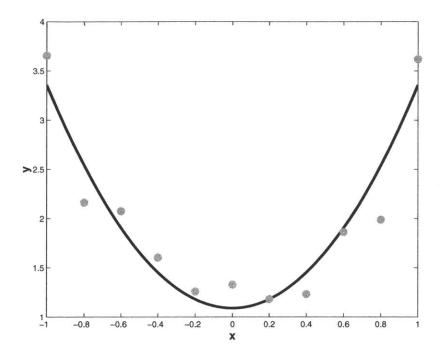

| 4-4 | Regression example                                                           | 57 |

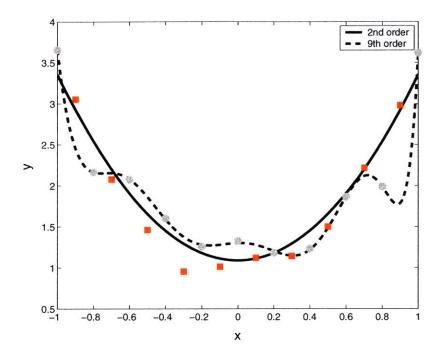

| 4-5 | Model complexity and overfitting                                             | 59 |

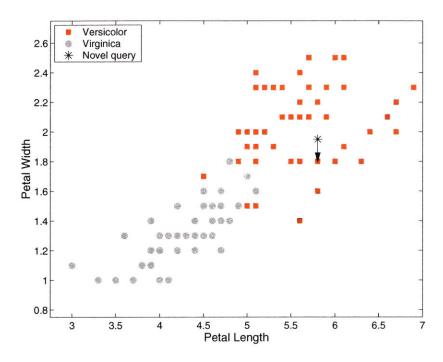

| 4-6  | Binary classification with nearest neighbor                    | 60  |

|------|----------------------------------------------------------------|-----|

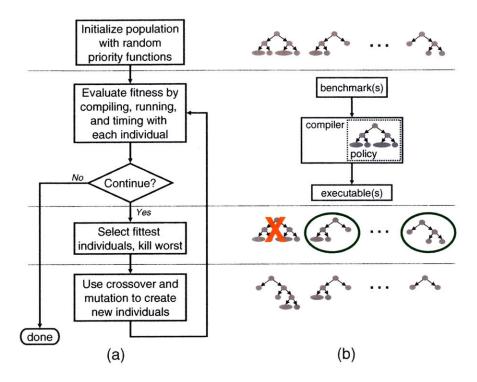

| 5-1  | Genetic programming flow                                       | 69  |

| 5-2  | GP individuals                                                 | 70  |

| 5-3  | Influence of control flow on processing                        | 76  |

| 5-4  | Hyperblocks and predicated execution                           | 78  |

| 5-5  | Hyperblock specialization using SASI                           | 85  |

| 5-6  | Hyperblock formation evolution                                 | 85  |

| 5-7  | Training on multiple benchmarks with MASI                      | 87  |

| 5-8  | Validation of the general-purpose priority function            | 88  |

| 5-9  | A GP-generated priority function for hyperblock scheduling     | 89  |

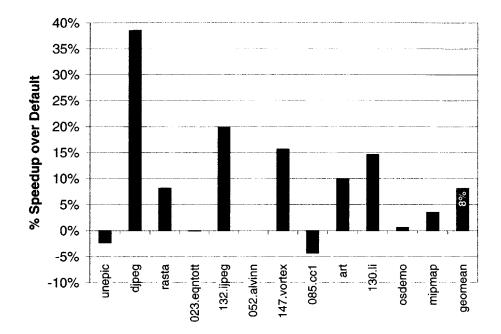

| 5-10 | Register allocation specialization with SASI                   | 93  |

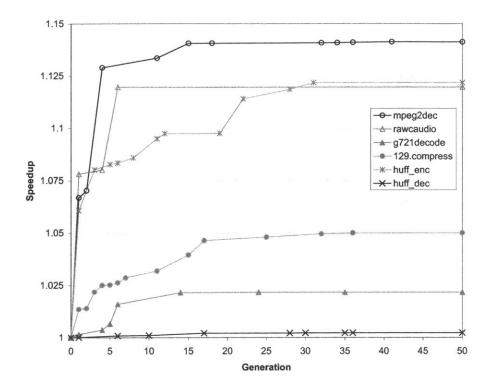

| 5-11 | Register allocation evolution                                  | 94  |

| 5-12 | Finding a general-purpose register allocation policy           | 95  |

| 5-13 | Validation of the register allocation policy                   | 96  |

| 5-14 | Speedups over a simple register allocation policy              | 96  |

| 5-15 | The best general-purpose register allocation priority function | 97  |

| 6-1  | Loop unrolling example                                         | 102 |

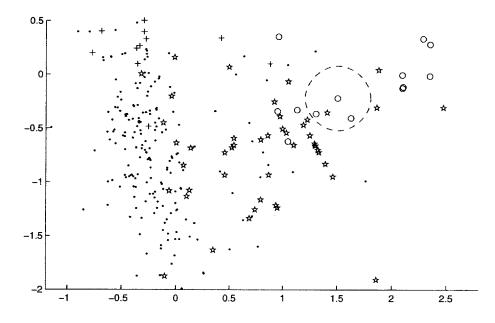

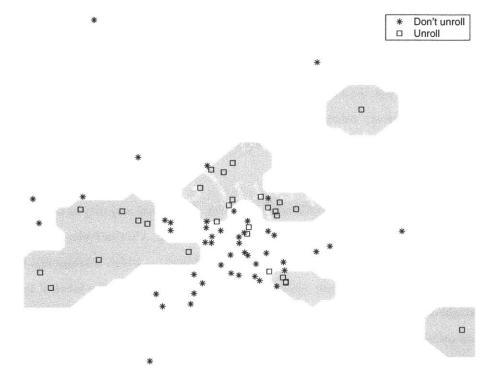

| 6-2  | Near neighbor classification                                   | 110 |

| 6-3  | Support vector machine classification                          | 112 |

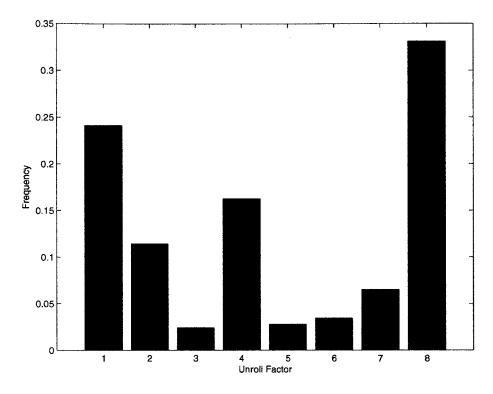

| 6-4  | Histogram of optimal unroll factors                            | 115 |

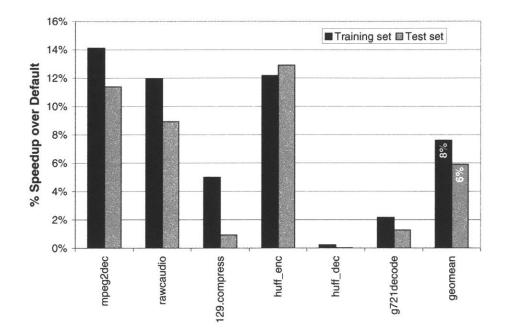

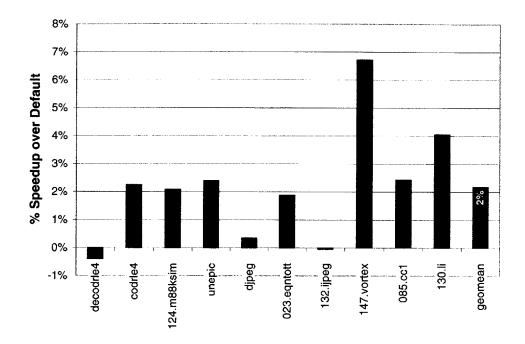

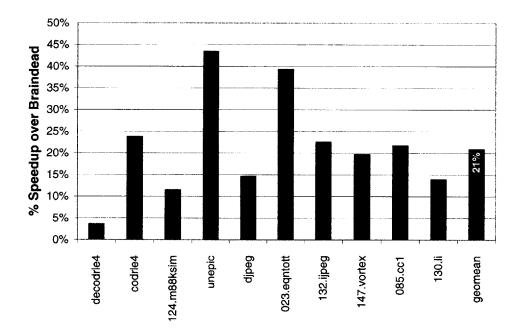

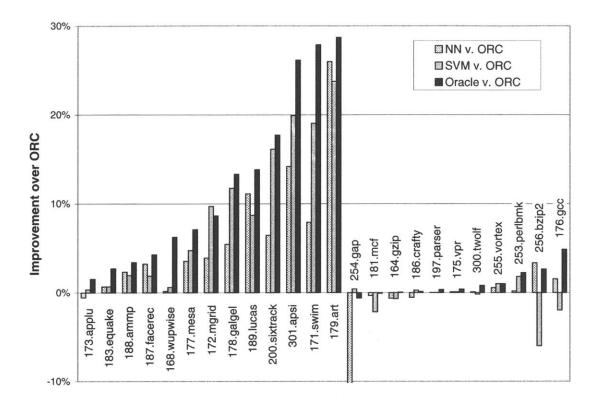

| 6-5 | Realized performance on the SPEC 2000 benchmarks             | 116 |

|-----|--------------------------------------------------------------|-----|

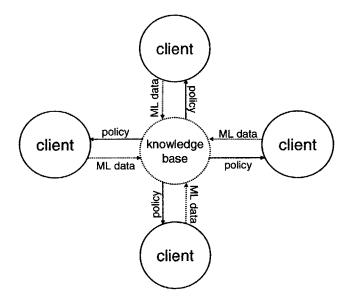

| 7-1 | Collaborative compilation                                    | 125 |

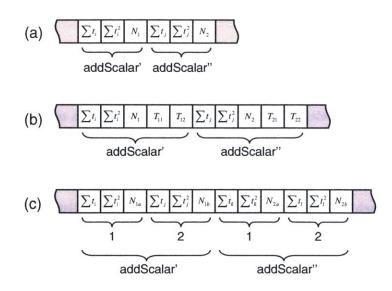

| 7-2 | (Naive) Instrumentation by a collaborative compiler          | 128 |

| 7-3 | Various accumulator arrays                                   | 130 |

| 7-4 | A typical series of method samples                           | 131 |

| 7-5 | Checking the accuracy of collaborative training labels       | 133 |

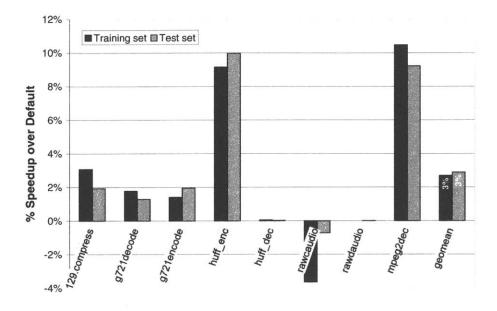

| 7-6 | Steady-state performance of a collaboratively tuned compiler | 138 |

# List of Tables

| 1.1 | Compiler infrastructures considered in this thesis | 21  |

|-----|----------------------------------------------------|-----|

| 1.2 | Hardware complexity                                | 22  |

| 2.1 | NP-hard compiler optimizations                     | 33  |

| 2.2 | Distribution of valid schedules                    | 37  |

| 3.1 | Approaches to training compiler policies           | 48  |

| 4.1 | Choosing an appropriate model                      | 58  |

| 5.1 | GP primitives                                      | 73  |

| 5.2 | GP parameters                                      | 74  |

| 5.3 | Architectural characteristics                      | 81  |

| 5.4 | Hyperblock selection features                      | 82  |

| 5.5 | Benchmarks used to train and test                  | 84  |

| 5.6 | Memory hierarchy access times                      | 90  |

| 5.7 | Register allocation features                       | 92  |

| 6.1 | A subset of features for loop classification       | 104 |

| 6.2 | Predictive accuracy for NN and SVM                            | 113 |

|-----|---------------------------------------------------------------|-----|

| 6.3 | Best unrolling characteristics according to feature selection | 118 |

| 6.4 | Greedy feature selection for nearest neighbor                 | 118 |

| 6.5 | Greedy feature selection for SVM                              | 118 |

| 7.1 | Runtime overhead of collaborative compilation                 | 135 |

### Chapter 1

## Introduction

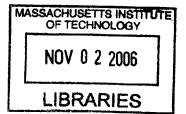

The level of complexity in today's systems is unprecedented. Figure 1-1 shows that playing a simple Java game on a typical user's computer spans several abstraction layers. The game runs within a virtual machine, which is likely embedded within a Web browser; the Java virtual machine runs on top of the Windows (a) operating system which executes on a Pentium 4 (b). Even the instruction set architecture of the Pentium 4 is an abstraction: the processor first converts x86 instructions into substantially simpler "micro-operations" on which the rest of the processor operates [45].

The numerous layers of abstraction in the computing hierarchy facilitate the design of sophisticated systems. However, as systems become increasingly layered and modularized, the designers' scope becomes increasingly myopic. Stitching together hundreds of locally designed pieces into a single system creates several formidable challenges, one of which is finding a synergy between all of the individual components.

The compiler is a critical link in the chain of complexity. The efficiency of the code that the compiler generates has an enormous effect on a compiled application's system-level performance. Optimizing compilers are themselves the product of hundreds of thousands of lines of code, and a typical compiler applies over a dozen optimizations to an input program. Furthermore, many important compiler optimization problems are NP-complete, and therefore they necessitate suboptimal heuristics to reasonably constrain compilation time. Because compilers are so complex, most of the optimizations that a compiler performs are

Figure 1-1: Layers of abstraction in a typical system.

not well-coordinated with "downstream" optimizations, let alone the target architectures, which today are comprised of over 100 *million* transistors and feature such innovations as deep pipelines, speculation, hyperthreading, and trace caching.

It is difficult for human engineers to design effective compiler optimizations because of the myriad of complexities in the compiler and target system. Despite these difficulties, optimizing compilers can extract high levels of performance from programs written in high level languages. One study empirically shows that modern compiler technology accounts for large speedups (2.5x to 17.3x) on a common set of benchmarks [86]. It is because of this potential boost in performance that compiler writers are willing to cope with the complexities wrought by compiler optimizations; in fact, they often spend a large portion of their time tweaking heuristics in order to achieve suitable performance improvements. For instance, the Open Research Compiler [77], on which I validate some of my techniques, features a loop unrolling heuristic that researchers manually updated between every major release (significantly in some cases).

I will show how to *automatically* construct effective compiler heuristics that are specialized for a given computing platform. Specifically, in this dissertation I describe *meta optimization*, an approach that can automatically induce compiler heuristics using well-known machine learning techniques. In most cases, the machine-learned heuristics perform substantially better than their state-of-the-art hand-crafted counterparts. Furthermore, meta optimization reduces the human effort involved with designing an optimizing compiler: machine learning techniques can automatically design significant portions of a compiler heuristic, thereby freeing the human designer to focus on compiler correctness.

The rest of this chapter discusses the challenges facing compiler writers, examines the inherent complexity of compilers, describes the increasing complexity of architectures, gives an overview of meta optimization, and highlights the contributions of this research.

#### 1.1 Challenges Facing Compiler Writers

This section discusses the many reasons why it is difficult to design optimizing compilers. A compiler, for the most part, creates the applications that run on top of all subsequent layers of abstraction, and therefore, the effectiveness of the compiler is critical to achieving top-notch application performance.

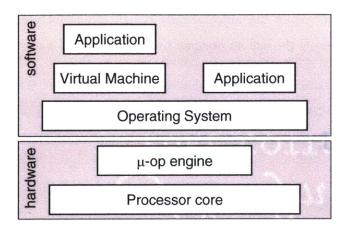

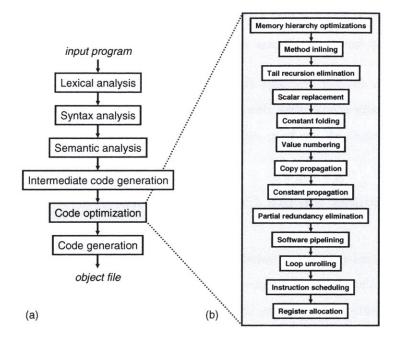

An optimizing compiler is a development tool that has the nontrivial task of converting a high-level description of a program into instructions that can natively execute on a machine. During the conversion, the semantics of the input program are maintained,<sup>1</sup> but the program itself often undergoes dramatic transformations. Figure 1-2(a) shows the flow of a typical optimizing compiler, while part (b) focuses on the *code generation* component, which is responsible for producing quality code from input programs. The blocks in part (b) of the figure are referred to as *passes* (or equivalently *phases*).

Each of the passes in the code generator performs an *optimization*, or in some cases a set of optimizations. An optimization restructures the code, while preserving the code's semantics, in order to attain a higher performance on the target architecture. Optimizing a program for a given computer architecture is inherently a high-dimensional problem. In other words, there are many facets of performance that the compiler must try to balance; there are optimizations to improve register, processor, memory, and communication resource utilization.

Each optimization, which the compiler sequentially applies, focuses on a subset of these dimensions, and it is not uncommon to optimize along a single dimension of performance. For

<sup>&</sup>lt;sup>1</sup>Sometimes the user of the program can instruct a compiler to sacrifice numerical precision for increased performance, but the vast majority of transformations preserve the semantics of the original program.

Figure 1-2: The anatomy of an optimizing compiler. Part (a) shows a coarse view of the compilation process, from a high-level program description to an object file. Part (b) zooms in on the flow of the compiler's code optimizer; a typical optimizer applies a dozen optimizations or more to an input program. Many of these optimizations are not well-coordinated with the other optimizations that are performed.

simplicity's sake, compiler writers often assume that compiler optimizations are orthogonal and independent, but this is definitely not the case. For example, in multiprocessor environments, maximizing processor utilization (across all N processors in the multiprocessor) may be completely at odds with minimizing traffic to the architecture's communication system. Likewise, optimizations aimed at reducing inter-processor communication are likely to affect processor utilizations. Another more subtle example is the interaction between the register allocator and the instruction scheduler. Instruction schedulers often tend to increase the lifetime of program variables, which can tax the register allocation optimization; on the other hand, the register allocation optimization constrains the instruction scheduler.

As shown in Figure 1-2, a compiler typically performs a whole host of high-level optimizations first (*e.g.*, method inlining, constant folding, constant propagation) [75]. Many of these optimizations try to simplify the input program. The compiler performs loop optimizations next: optimizations such as loop unrolling and software pipelining aim to expose massive amounts of instruction parallelism. Afterwards the compiler schedules the order

| Infrastructure | Source Language | Input Language | Lines of Code |

|----------------|-----------------|----------------|---------------|

| JikesRVM [6]   | Java            | Java Bytecodes | 300,000       |

| ORC [77]       | C++             | C              | 1,200,000     |

| Trimaran [94]  | C/C++           | С              | 750,000       |

Table 1.1: Compiler infrastructures considered in this thesis. The source language column describes the language in which the compiler is written. The language that the compiler translates is shown in the third column. The last column lists the number of lines of source code that comprises the compiler infrastructure.

in which instructions should execute. A register allocation phase, which assigns program variables to fast hardware registers, is often one of the last optimizations performed before the object file is generated. A seemingly worthwhile optimization performed early on in the compilation process may hamper the effectiveness of the subsequent passes. Chapter 2 discusses such situations.

The compiler flow shown in Figure 1-2 mirrors the compiler infrastructures that this thesis considers, all of which are listed in Table 1.1. While there are many differences between these three infrastructures, they all have one vital characteristic in common: they are all big systems. The last column in the table lists the number of lines of source code that comprise each infrastructure. The size of the source base is not the best indication of complexity, but these figures do begin to convey the significant amount of work a compiler performs.

Perhaps a more convincing argument about compiler complexity is that several key optimizations are NP-complete. In fact, even the simplest form of instruction scheduling is NP-complete for realistic architecture models [13]. Likewise, optimal register allocation is NP-complete [35] since the problem can be reduced to a graph coloring problem. For such optimizations, it is simply not practical to find the optimal solution. Given enough time, optimal solutions to NP-hard problems can be found, but compile time must be reasonably bounded. Fortunately there are many *heuristics* that approximately solve NP-hard problems.<sup>2</sup>

Because the set of all programs is diverse (and infinite), compiler writers are currently responsible for crafting, and then fine-tuning heuristics that work well across a wide range of input programs; this is a formidable task. A heuristic that is tuned to perform well on one class of applications may not perform well on other types of applications. For instance,

<sup>&</sup>lt;sup>2</sup>In general this thesis refers to any potentially suboptimal compiler algorithm as a heuristic.

| Processor   | Year | Transistors | Frequency | New Features                                                                                            |

|-------------|------|-------------|-----------|---------------------------------------------------------------------------------------------------------|

| Pentium     | 1993 | 3,100,000   | 233 MHz   | 2-way superscalar, 5-stage pipeline, in-<br>teger SIMD instruction set (MMX).                           |

| Pentium II  | 1997 | 7,500,000   | 450 MHz   | 3-way superscalar, 12-stage pipeline,<br>out-of-order execution, larger L1<br>cache.                    |

| Pentium III | 1999 | 9,500,000   | 1 GHz     | Floating-point SIMD instructions (SSE), new registers.                                                  |

| Pentium 4   | 2000 | 169,000,000 | 3.73 GHz  | Hyper-threading, trace cache, double<br>clocked ALU, 20-deep pipeline, im-<br>proved branch prediction. |

Table 1.2: Hardware complexity. This data shows the chronological progression of Intel's Pentium line of microprocessors [44]. Massive increases in the number of transistors from generation to generation have allowed Intel's computer architects to increase the sophistication and complexity of their processors.

scientific applications are more amenable to loop optimizations than control-intensive "integer" programs; aggressive loop optimizations may help scientific applications, but harm the performance of branchy codes.

Increasingly complex computer architectures, the target of optimizing compilers, also make a compiler's task more difficult. In order to generate high quality code, the compiler must have an accurate model of the target architecture. Whereas processors were once easy to model, abstract models can no longer adequately describe today's sophisticated processor designs. Exponentially improving process technology continues to give computer architects additional resources with which to incorporate sophisticated processing mechanisms.

Table 1.2 contains data on Intel's Pentium line of microprocessors [44]. The last column of the table shows some of the key features added to each successive generation of Intel's microprocessors. This indicates that architects have not squandered the sizable silicon real estate increases. For example, in a relatively short amount of time, Intel has added a significant number of architectural features to its Pentium processors. The original Pentium processor, introduced in 1993, was a simple, in-order superscalar processor that was designed on a budget of three million transistors. The most recent Pentium 4 processor at the time of this writing consists of 169 million transistors. The designers used this extra silicon real estate to add several performance-enhancing features (e.g., larger caches, speculative execution, branch prediction, multi-media units, and improved floating point computation units). An aggressive architecture like Intel's Pentium 4 actually performs many (compiler) optimizations at *runtime* (e.g., register renaming and trace construction). The Pentium 4 processor is capable of simultaneously executing up to 126 instructions. Because such processors are not easily modeled, it is difficult to predict what impact a given compiler optimization will have on a processor like the Pentium 4.

Not only is the coupling of compiler technology and the target architectures difficult to model, their relationship changes over time. Consider the re-tuning effort that a compiler writer must undertake for new releases of a processor. At the time of this writing there are no fewer than 16 revisions of the Pentium 4, some of which provide substantially different features than their predecessors [44]. How can compiler writers manually specialize heuristics for the array of architectures even within a single processor family? Because the effort involved in is too drastic, developers typically do not re-tune the compiler for every release.

Nevertheless, it is well known that achieving the best performance requires that the compiler match the target processor. I argue in this thesis that there is a considerable amount of slack in a typical compiler heuristic. In other words, a well-tuned heuristic can produce far more efficient code than an un-tuned heuristic. Chapters 5, 6, and 7 experimentally support my claim.

#### **1.2** Overview of Meta Optimization

This chapter has discussed the complexity inherent to compilers and modern-day architectures. A major implication of systems complexity is that manually tuning a compiler heuristic to work well within a modern day system is not an easy task: for a given system, a designer has to ensure that the heuristic works well across a wide range of programs.

I propose to address this by using machine learning techniques to create heuristics that are catered to the target system. Machine learning techniques, which have the ability to "make sense" of complex, high-dimensional spaces, have the potential to change the way compiler writers develop heuristics. By offloading much of the tedium of heuristic tuning to an automated process, my techniques stand to both improve performance as well as reduce the human effort involved in compiler construction.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>I make no claims about reducing compiler complexity. My focus is on *dealing* with compiler complexity.

I call my approach meta optimization because it essentially optimizes compiler optimizations. Meta optimization takes advantage of the fact that many compiler optimizations are naturally separated into two distinct phases: *correctness checking*, and *policy*. The correctness checking phase finds a bounded (but large) set of *legal* optimization possibilities. For many optimizations, finding the set of legal options is straightforward and precise; the more difficult task is the policy phase, which chooses the best option from this set. While the correctness checking component of an optimization ensures that the compiler will produce code that is correct, the policy completely dictates what the attainable performance of the optimization will be.

Meta optimization makes it possible to *automatically* search for effective policies. Consider the global ramifications of a compiler optimization such as loop unrolling, which replicates the body of a loop some number of times to increase parallelism. Loop unrolling interacts with all other compiler passes; in some cases it can enable a host of downstream optimizations, but it can also adversely affect instruction cache performance and the effectiveness of the register allocator. Constructing a heuristic to predict when loop unrolling is appropriate is nontrivial; yet if the heuristic is not well-designed, the performance of the whole system may suffer. Currently human engineers use intuition and manual trial-and-error experimentation to painstakingly construct loop unrolling heuristics.

One instantiation of meta optimization, which I describe in Chapter 6, uses empirical measurements and supervised learning to automatically create effective policies. For the loop unrolling problem, the approach first automatically gathers a database of empirical observations by inspecting over 2,500 loops drawn from multiple benchmarks: for each loop, the meta optimizer extracts a vector of characteristics  $\vec{x}$  that abstractly describes the loop's structure; it also empirically, and exhaustively finds the best unroll factor y for each loop. With this database in place we can use well-known supervised learning techniques to automatically construct a function  $y \leftarrow f(\vec{x})$  that can accurately predict the unroll factor y for a loop described by the vector  $\vec{x}$ . In this way, the supervised learning algorithm learns to predict the loops for which a given unroll factor best applies.

Meta optimization frees compiler writers of the burden of trial-and-error tuning associated with human-constructed heuristics: once the database of loop examples is in place, it only takes a few seconds to generate an effective compiler heuristic. Furthermore, the meta optimized heuristics generate faster compiled code than their human-designed counterparts. For loop unrolling, meta optimization achieves speedups (over a widely used human-designed heuristic) of up to 26%, and attains an average speedup of 9% on a common set of scientific applications.

On today's complex systems, the only way to know how well a compiler heuristic works is to test it empirically; as such, all of the experiments that I present in this thesis use empirical performance observations to drive the machine learning process.

#### **1.3** Contributions

This thesis investigates the hypothesis that machine learning algorithms can automatically create effective compiler heuristics. I present several novel ideas and findings throughout this document. This following list summarizes the contributions that this thesis makes:

- I have developed a generalized methodology for automatically creating compiler heuristics. The technique is aided by the fact that many compiler heuristics are naturally separated into two components. The first component is immutable and ensures the correctness of the heuristic. The second component however, which I call the policy, is flexible and it dictates the effectiveness of the heuristic. By "learning" the policy and leaving the correctness component intact — my technique drastically reduces the search space size, making machine learning a feasible, and indeed a palatable approach to heuristic design. In addition, any policy derived by a machine learning technique will generate *correct* code. Chapter 3 discusses this approach.

- I introduce a technique that focuses on small, but high-impact functions called priority functions [91]. By iteratively searching for quality priority functions via policy search, a compiler's effectiveness can, in many cases, be improved by large margins. Chapter 5 discusses this work.

- I show that it is possible to effectively learn compiler policies that make *multi-class* decisions [90]. Recently, other researchers have applied supervised machine learn-

ing to compilation problems where possible actions are binary. However, there are many compiler optimizations for which the set of possible actions is larger; these optimizations require a multi-class approach. Furthermore, I evaluate the multi-class experimentation in a real computing environment using real applications, proving the scalability of the technique. Chapter 6 describes this work in detail.

- I show that *feature selection* can automatically identify the most salient features for creating effective compiler policies [90].

- I introduce *collaborative compilation*, a paradigm that enables ordinary users of alreadydeployed systems to transparently contribute to and benefit from the machine learning data collection process. Collaborative users share their automatically extracted empirical runtime data with other members of a user community. In exchange for sharing, collaborative users are granted access to the community knowledge base, which houses the most current and effective machine-learned heuristics. These users are essentially training the compiler to perform well on the applications and systems in which the community as a whole is interested.

#### 1.4 Roadmap

The next chapter describes the anatomy of an optimizing compiler. I outline my general approach to tuning compiler heuristics with machine learning in Chapter 3. Chapter 4 discusses the machine learning concepts that are necessary for an adequate understanding of the experiments performed in the remainder of the thesis. Chapter 5 shows how policy search can effectively fine-tune small, but high-impact portions of a compiler heuristic. Chapter 6 describes an experiment with multi-class supervised learning. I discuss collaborative compilation in Chapter 7. Finally, I present related work in Chapter 8, and I conclude in Chapter 9.

### Chapter 2

## **Compiler Construction**

This chapter presents an overview of modern-day compiler construction. I focus on the details that directly pertain to this thesis, and I purposely omit many aspects of compiler construction that are not particularly relevant to my work. I relegate some important, but not necessarily essentially details to footnotes. Readers who are familiar with compiler construction can safely skip to the next chapter where I outline my approach.

#### 2.1 Compiler Flow

The last chapter diagrammed the high-level flow of an optimizing compiler. This section fills in many of the details that the last chapter omitted. Figure 2-1(a) graphically depicts the operation of a modern compiler. A compiler begins with a high-level description of a program. The compiler first ensures that the input program is well-formed by applying *lexical, syntactic, and semantic analyses* [75, 4].

From this point, the compiler generates an intermediate representation (IR) on which the remainder of the compiler will operate. The IR merely provides a semantic-preserving representation of the input program that facilitates optimization and analysis. There are typically a couple of different types of IR: high-level IR, which retains many of the high-level constructs associated with a modern day programming language, and low-level IR, which resembles assembly language for an abstract machine. A compiler typically uses high-level

Figure 2-1: Anatomy of an optimizing compiler (repeated from Chapter 1).

IR early in the compilation of a program [75]. For instance, optimizations that aim to improve the performance of the memory hierarchy (*i.e.*, the performance of caches and main memory) benefit from high-level knowledge of memory access patterns, which may not be available in the low-level IR. However, all of the optimizations that I study in this thesis operate on low-level IR.

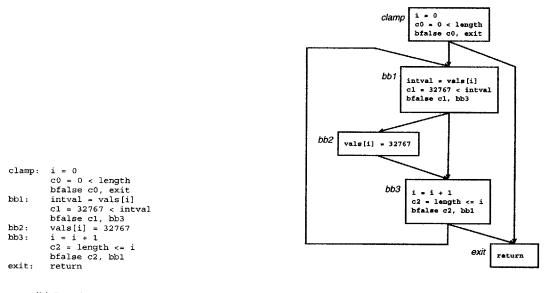

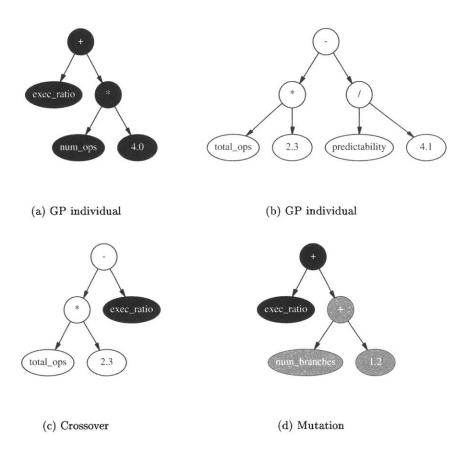

Figure 2-2(a) shows a simple method written in C. A modern-day processor cannot directly execute the high-level statements in this example because they are too expressive; it is the job of a compiler to disassemble the statements into simple instructions that a processor can execute, and conversion to low-level IR is a big step toward that end. Figure 2-2(b) shows the method's corresponding low IR representation.<sup>1</sup> Notice in particular how the compiler has transformed the high-level control flow (*i.e.*, the for loop, and the if-statement) to low-level *branches*, *labels*, and *conditional tests*. If we were to omit control flow, the low-level IR instructions would execute sequentially, and while that would certainly simplify compiler analyses and code generation, it would severely limit the types of programs that we could write. Labels designate the locations of code. In Figure 2-2(b) for example, the label

<sup>&</sup>lt;sup>1</sup>Intermediate representations differ from compiler to compiler, and thus I just mean for this example to give the reader a feel for what an IR looks like.

```

1: void clamp (int vals[], int length)

2: {

3: int i;

4: for (i = 0; i < length; i++)

5: {

6: int intval = vals[i];

7: if ( intval > 32767 )

8: vals[i] = 32767;

9: }

10: }

```

(a) Original program.

(b) Low-level IR.

(c) Control flow graph.

Figure 2-2: An example control flow graph.

**bb3** identifies the location of the instruction that increments the variable i. The IR also includes instructions to set a variable's value based on the outcome of a conditional test. For instance, the instruction

$$c0 = 0 < length$$

assigns c0 a value of true if length is greater than zero. The branch instructions in the figure (*i.e.*, the bfalse instructions) transfer execution to the specified label if the conditional test is false. If, on the other hand, the conditional test is true, execution simply *falls through* to the next instruction in the sequence.

Branches and jumps introduce ambiguity about which portions of code will execute. For instance, in Figure 2-2(a), the if-statement on line (7) controls whether the statement on line (8) is executed. This uncertainty complicates program analysis, but does not prohibit it. One commonly used structure that facilitates many compiler analyses in the presence of branches is a *Control Flow Graph* (CFG). Figure 2-2(c) shows the CFG for the example in part (a).

The nodes of a CFG are referred to as *basic blocks*, each of which is an ordered sequence of instructions. A basic block can have at most one branch or jump instruction, which if present must occur at the end of the block. All jumps or branches must transfer execution to the beginning of a basic block. As a ramification of these traits, if one instruction in a basic block executes they will all execute. The edges of the CFG denote control dependencies between two basic blocks. For instance, in the entry block labeled "clamp" in Figure 2-2(c) execution can either fall through to "bb1", or it can branch to the "exit" block.

With an IR and a CFG in place, the compiler is armed to apply many classical compiler optimizations. This thesis focuses on the next step of compilation: optimizing the IR to produce a high-quality program. Figure 2-1(b) shows the phases, or equivalently, the *passes* of a typical code optimizer [75]. Code optimizers are essentially a pipeline of optimization passes, and remember, there is little or no coordination between these passes.

Sometimes one pass will facilitate a downstream optimization pass, and other times it

```

double fhelper (double x,

double omega,

int select)

ł

double f()

switch(select)

double t0 = 1.0;

case 0: return(pow(x+1.0,x));

case 1: return(pow(x+1.0,x) * cos(omega*x));

double t1 = 3.14;

int t2 = 0;

case 2: return(pow(x+1.0,x) * sin(omega*x));

switch(t2)

return 0.0;

case 0: return(pow(t0+1.0,t0));

case 1: return(pow(t0+1.0,t0) * cos(t1*t0));

case 2: return(pow(t0+1.0,t0) * sin(t1*t0));

}

double f()

return fhelper(1.0, 3.14, 0);

return 0.0;

}

(a) Original program.

(b) After inlining.

double f()

double f()

switch(0)

switch(0)

case 0: return(pow(2.0,1.0));

case 1: return(pow(2.0,1.0) * cos(3.14));

case 2: return(pow(2.0,1.0) * sin(3.14));

case 0:

return(pow(1.0+1.0,1.0));

case 1: return(pow(1.0+1.0,1.0) * cos(3.14*1.0));

case 2: return(pow(1.0+1.0,1.0) * sin(3.14*1.0));

return 0.0;

return 0.0;

}

(c) After constant propagation.

(d) After constant folding.

double f()

return(pow(2.0,1.0));

```

(e) After dead code elimination.

Figure 2-3: Optimization examples.

may inhibit the ability of a downstream pass to perform effectively. The method inlining optimization nicely illustrates this concept. Method inlining, also referred to as procedure integration, is an optimization that replaces method calls (*i.e.*, calls to other methods) with the actual body of the method [75]. Figure 2-3(a) shows the C description of a method that calls another method. The method f calls fhelper, and the switch statement in fhelper steers the computation based on the value of the variable select. Figure 2-3(b) shows the result of inlining the fhelper method directly into  $f.^{2,3}$

<sup>&</sup>lt;sup>2</sup>Note that for clarity I omit the fhelper method in Figure 2-3(b) even though a C compiler would have generated code for it (since an external method may call it).

<sup>&</sup>lt;sup>3</sup>The compiler cannot inline the calls to  $\cos$ , pov, and  $\sin$  because they are defined in an external library and the source code may not be available.

In this example, inlining fhelper opens several optimization opportunities to the downstream compiler passes. For instance, the constant propagation pass identifies program variables that represent constants, and replaces each of them with the actual constant they represent. In Figure 2-3(b), the constant propagation pass would replace all occurrences of t0 with the value 1.0 since this is the only value to which t0 ever refers. Note that constant propagation cannot optimize the code in part (a); only through method inlining does constant propagation become effective for this example. Constant propagation of the code in Figure 2-3(b) results in the code of part (c). Figure 2-3(d) reveals how constant propagation can facilitate the *constant folding* optimization. When all of an arithmetic operation's operands are constants, constant folding can replace the operation with the value that would have been computed at runtime. For instance, the argument to cos in Figure 2-3(c) is known at compile time to be 3.14\*1.0, or just 3.14.

For this example, method inlining combined with constant propagation also enables the *dead* code elimination optimization. Dead code elimination removes code that program execution cannot possibly reach. For instance, it is only possible for execution to ever reach case 0 in Figure 2-3(d), and thus the compiler can eliminate the switch statement. Figure 2-3(e) shows the streamlined version that results after the compiler applies dead code elimination.

It is important to note that compiler optimizations are not universally applicable [4, 75, 18]. For instance, method inlining is not *always* a beneficial optimization to perform. Furthermore, predicting the circumstances under which inlining is beneficial is difficult. Method inlining expands the memory footprint of an application — since the optimization essentially creates redundant versions of a method — which may lead to deleterious memory system behavior. For example, the register allocation phase attempts to map program variables to a limited number of fast hardware registers. In the event that the register allocator cannot assign a hardware register to all variables in a method, the allocator has to *spill* a subset of the variables to memory, which is much slower to access. Inlining can burden the register allocator by increasing the density of variables in a method. Chapter 7 studies a method inlining heuristic; in some cases, aggressive inlining leads to enormous slowdowns.

| Probl   | em                                           |

|---------|----------------------------------------------|

| Boolea  | an simplification [5]                        |

| Cluste  | r assignment [29]                            |

| Cyclic  | instruction scheduling [29]                  |

| Instru  | ction scheduling with limited resources [35] |

| Loop f  | fusion with loop interchange [5]             |

| Loop s  | selection [5]                                |

| Minim   | izing waits in presence of control flow [5]  |

| Multi-  | dimensional scheduling [29]                  |

| Profita | ability determination [5]                    |

| Regist  | er allocation [75]                           |

Table 2.1: Compiler optimizations that have been proven to be NP-hard.

#### 2.2 Important NP-Hard Compiler Problems

Many of the most performance-critical compiler problems are NP-hard [75, 29]. Table 2.1 lists some example compiler problems that have been proven to be NP-hard. Even the most basic scheduling problem is NP-complete when targeting a machine with limited resources. Recent research has shown that integer linear programming (ILP) can effectively solve *some* instances of important NP-hard compiler problems *somewhat* quickly [57]. However, ILP techniques still take orders of magnitude longer to compute than the heuristic techniques compiler writers have crafted to cope with NP-hard problems.

Heuristic techniques strike a balance between compile time and code generation quality that suits most compiler users. The remainder of this section takes an in-depth look at instruction scheduling, a critical NP-complete compiler problem; I also describe a popular heuristic solution that (sub-optimally) solves it. The next chapter will use this problem to illustrate meta optimization.

#### 2.2.1 Case Study: Instruction Scheduling

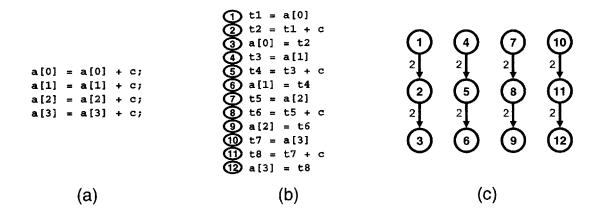

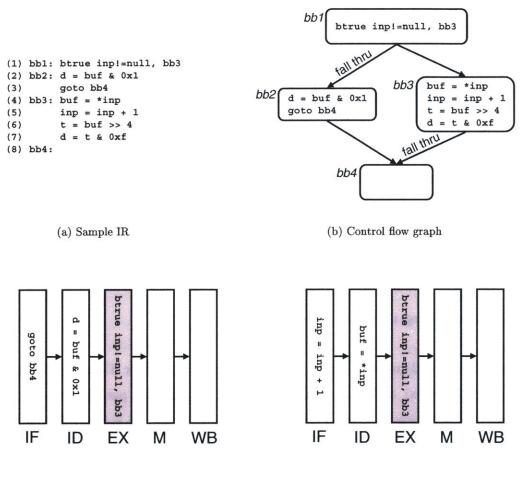

The instruction scheduling pass is responsible for arranging the order in which instructions execute on a processor, and scheduling order can have a large impact on performance [75, 4, 29]. A simple example illustrates the instruction scheduling problem. Figure 2-4(a) shows four C statements that add a scalar value to a four-element vector. The compiler lowers the high-level description in (a) to low-level IR, which I show in part (b).

Figure 2-4: Instruction scheduling example. The low-level instructions in (b) show how a typical compiler would convert the high-level instructions in (a). Only a small fraction of the 12! possible orderings of the instructions in (b) are legal. The dependence graph in (c) shows the partial ordering for this example that the compiler must satisfy to generate correct code. The labels on the edges in the dependence graph correspond to instruction latencies.

For each high-level statement, the compiler creates three low-level IR instructions. Take the first statement for instance:

a[0] = a[0] + c;

The compiler first generates an instruction (1) to load the current value of a[0] from memory into the temporary variable t1. The next compiler-generated instruction (2) adds the variable c to t1 and stores this result in the temporary variable t2. To complete the high-level statement, the compiler generates an instruction (3) that stores t2 to the memory location a[0]. The low IR description in part (b) contains a list of twelve instructions. There are 12! = 479,001,600 ways to schedule the instructions in (b), but only a small fraction of those schedules are actually legal.

It is important for the instruction scheduler to adhere to *dependencies* in a program, otherwise the compiler will likely generate incorrect code. *Data dependencies* impose a partial order on instruction schedules which insures that data correctly flows between instructions in a program. For instance, the read of t1 in instruction (2) requires that t1's value first be set in instruction (1). Figure 2-4(c) depicts a *dependence graph* — which is straightforward to generate given a list of instructions [75] — that places a partial order on the instructions in part (b). The nodes of the dependence graph correspond to the instructions in part (b), and an edge between two nodes implies a constrained order between two instructions. For instance, the example dependence graph says that instruction (3) is dependent on (2) and (1); in other words, (3) cannot be scheduled before (1) or (2). The constraints that the dependence graph specifies are intuitive: in the running example, adding c to t1 before t1 contains the value of a[0] will almost certainly produce an incorrect result.

We can see from the dependence graph that there are four independent "computations" in the example (e.g., [(1),(2),(3)] is a single computation), and the relative ordering of the instructions within a computation is completely constrained. We can think of this problem in the following way: we have twelve slots, each of which will hold a single instruction from the list in part (b). We can first choose any three of these locations to place one of the completely constrained computations. There will then be nine remaining slots in which to schedule an additional computation. Finally, after scheduling the next computation, there will be six remaining slots in which to schedule an additional computation. Therefore, there are  $\binom{12}{3}\binom{9}{3}\binom{6}{3}\binom{3}{3} = 369,600$  legal schedules, which is still a rather large number considering the size of this small example.

While finding the set of legal schedules is straightforward, finding the best-performing subset of schedules can be difficult. For a given target processor (*i.e.*, the processor for which the compiler generates code), some of the legal schedules are much better than others. The numbers next to each edge in the dependence graph in part (c) correspond to the *latency* of the associated dependence. The latency is the amount of time, measured in the number of processor clock cycles, until an instruction's result is ready to pass along to dependent instructions.

For simplicity I have assigned a two cycle latency to all the instructions in the graph. Modern processors are *pipelined*, which, as the name implies, means they can execute multiple instructions simultaneously. A pipelined processor is split up into a number of disparate stages, each of which performs a small part of the overall computation of an instruction [81]. A hypothetical target processor with five stages, for example, can execute up to five instructions simultaneously. However, each of the concurrently executing instructions will be in

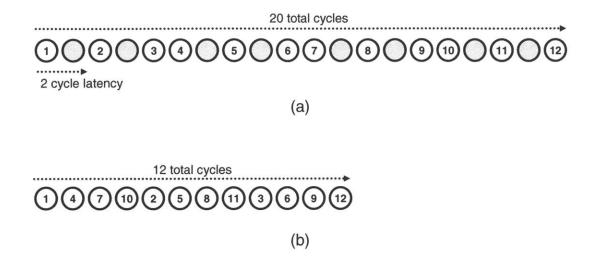

Figure 2-5: The effectiveness of two different instruction schedules.

different phases of the execution. An excellent real-world analogy is a manufacturing assembly line.

Figure 2-5 shows the effectiveness of two different instruction schedules for the code in Figure 2-4(b). The figure assumes execution occurs on an abstract, pipelined processor.<sup>4</sup> The processor will execute the instructions in the order in which they are scheduled,<sup>5</sup> and it will *stall* an instruction's execution until its operands are ready. A stall in this context represents an idle processor cycle.

The instruction schedule shown in Figure 2-5(a) often stalls the processor (stalls are represented as gray circles). For example, instruction (1) takes two cycles to execute, and therefore instruction (2), which is dependent on instruction (1), cannot begin executing until the third clock cycle. The schedule in part (a) takes 20 total cycles to compute the short vector addition. In contrast, the schedule, shown in part (b) only takes twelve total cycles, and it completely eliminates processor stalls. Table 2.2 shows the distribution of the effectiveness of all the valid schedules for the example dependence graph. Even for this simple example, over 80% of the possible, legal schedules are suboptimal.

<sup>&</sup>lt;sup>4</sup>The figure also assumes that the processor does not include bypassing support.

<sup>&</sup>lt;sup>5</sup>This assumption is not entirely correct for modern-day architectures which can execute several instructions in parallel and possibly out of order. Nevertheless, instruction scheduling can still drastically affect the performance of such machines.

| Cycles | Number of solutions |  |  |

|--------|---------------------|--|--|

| 12     | 75,488              |  |  |

| 13     | 125,096             |  |  |

| 14     | 100,504             |  |  |

| 15     | 48,608              |  |  |

| 16     | 16,360              |  |  |

| 17     | 2,720               |  |  |

| 18     | 800                 |  |  |

| 19     | 0                   |  |  |

| 20     | 24                  |  |  |

| total  | 379,600             |  |  |

Table 2.2: Distribution of valid schedules for the example dependence graph. Each row shows the number of valid schedules that lead to the associated schedule length. Even for this simple

Garey and Johnson proved that instruction scheduling is NP-complete for resource-constrained processors (which describes any implementable processor) [35]. While NP-completeness makes it infeasible for the compiler to optimally arrange instructions, the next section shows how heuristic solutions can create *good* schedules; this is the task of an instruction scheduler.

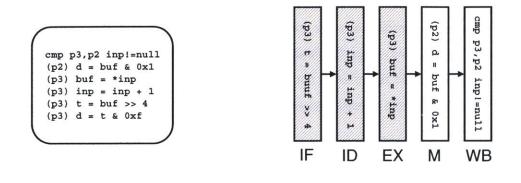

#### 2.2.2 Heuristic Solution for Instruction Scheduling

Given enough time, compilers can find optimal solutions to many difficult compilation problems. While some users might be willing to exchange long compilation times for higherquality code generation, most users prefer a balance between the effectiveness and the efficiency of their compiler. This tradeoff is especially important in just-in-time (JIT) compilation where compilation occurs every time a user runs an application (Chapter 7 describes JIT compilation). Heuristic techniques can often quickly find good approximate solutions to NP-hard problems. This section describes *list scheduling*, which is a heuristic solution for scheduling a list of instructions [4, 75]. List scheduling is a greedy, priority-based algorithm that schedules a sequential list of instructions (*e.g.*, the instructions within a basic block). List scheduling iterates N times, where N is the number of instructions to be scheduled. On each iteration the algorithm schedules one instruction from the set of instructions that can be *legally* scheduled, also called the *ready worklist*. For the example in Figure 2-4, on the first iteration, the ready worklist consists of  $\{(1),(4),(7),(10)\}$  (because these instructions are not dependent on any instructions that have not already been scheduled). Instructions are removed from the worklist when they are scheduled, and new instructions are added to the worklist when all of their dependencies have been satisfied.

Even randomly choosing instructions from the ready worklist will generate a legal schedule. However, generating correct code is only a part of the scheduling problem: a scheduler should also generate efficient instruction schedules. For list scheduling, the manner in which instructions are scheduled from the ready worklist is crucial. On each iteration the algorithm assigns a weight, or *priority* to each instruction in the ready worklist. Once the relative priority of each ready instruction has been computed, the algorithm chooses the instruction with the highest priority and schedules it next. For list scheduling, the function that computes instruction priorities is extremely important for performance, but again note that the priority function cannot affect the correctness of the generated code.

A popular heuristic assigns priorities using latency-weighted depths [37]:

$$P(i) = \begin{cases} latency(i) : & \text{if } i \text{ is independent.} \\ \max_{j \text{ depends on } i} latency(i) + P(j) : & \text{otherwise.} \end{cases}$$

The priority of instruction *i* therefore depends on its depth in the dependence graph, taking into account the latency of instructions on all paths to the leaf nodes. For the simple, in-order, pipelined machine described above, the best schedule for the example code in Figure 2-4 is obtained by scheduling instructions with the greatest latency-weighted depths first. This heuristic schedules (1),(4),(7), and (10) first because they all have a dependence of height of 4. After (1),(4),(7), and (10) have been scheduled, (2),(5),(8), and (11) are the instructions with the highest priority values, and therefore, the heuristic schedules these instructions next. Continuing in this fashion, the heuristic creates the (non-uniquely) optimal schedule shown in Figure 2-5(b).

It is important to note however, that the critical path heuristic does not always generate optimal schedules. A scheduling heuristic for modern processors must consider many factors. Production compilers use sophisticated priority functions that account for many competing factors such as instruction occupancy in the pipeline, and how a given schedule may affect downstream compiler passes. As we will see in later chapters, machine learning techniques can effectively juggle many factors that may be important for a given optimization.

We can use machine learning to automatically create priority functions of the sort described here. Priority functions can more generally be described as policies. The next chapter describes, at a high level, how we can apply meta optimization techniques to learn compiler policies.

# Chapter 3

# Meta Optimization

Abstractly, I automatically create powerful compiler heuristics using machine learning techniques. The purpose of this chapter is to briefly describe the approach that is common to all the experiments performed in this thesis. The reader could benefit greatly by keeping this chapter's content in mind when reading the next chapter, which describes the machine learning techniques that this thesis considers.

There are four main points that I convey in this chapter. First, I focus my efforts on the portions of compiler algorithms that are most amenable to machine learning. Second, my goal is to automatically "learn" critical pieces of the compiler's code generator, which indirectly will improve the code that the compiler generates. Third, I describe how empirical observations drive the machine learning process, and finally, I mention how compiler writers can use my approach to create specialized and general-purpose compiler heuristics alike.

## 3.1 Insight: Correctness v. Policy

A key insight that enables the research that I present in this thesis is that compiler writers tend to separate heuristics into two disparate phases: one that ensures correctness, and one that focuses on performance. I call the phase of a compiler heuristic that concerns itself with performance, the *policy* of the heuristic. The work I present in this thesis focuses on learning effective policies.

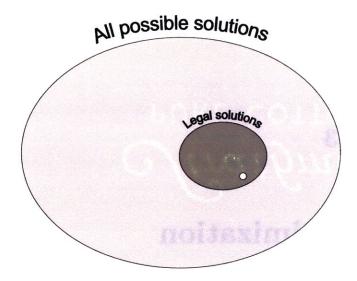

Figure 3-1: An abstract depiction of a heuristic's task. The large, light gray circle represents the space of all possible solutions to a compiler problem. The heuristic first finds a subset of solutions, represented by the dark gray circle, that will generate *legal* code. The heuristic's policy then chooses a single solution, denoted by the small white circle, from this subset.

Figure 3-1 abstractly shows the operation of a compiler heuristic. The light gray circle in the figure represents the space of *all* possible solutions for a compiler problem; this space is potentially *extremely* large. The correctness phase identifies a subset of the solutions — represented by the dark gray circle — that will generate legal code. For most compiler problems, it is relatively easy to identify legal solutions. The goal of the policy is more difficult: choose the *best* (or close to the best) solution from the legal subset of solutions, which I denote by the small white circle in the figure.

As a concrete example, consider the priority-based list scheduling heuristic we discussed at the end of the last chapter. The heuristic first identifies, using a dependence graph, the set of instructions that can legally be scheduled in the next slot. The policy for the heuristic is a priority function which has the task of choosing *a single* instruction from the set to schedule next. The policy for list scheduling completely dictates the effectiveness of the optimization; and as we saw, some policies are much better than others.

The correctness phase is an absolutely critical component of the heuristic, but in most cases it is relatively easy for humans to reason about and design. The constraints that enforce the legality of a transformation are clearly known in most cases, and when they are not, the compiler writer can always make conservative assumptions. The policy, on the other hand, is difficult to design because the factors that may affect performance are not well known, and can be too complex for humans to fully grasp.

Policies have two main qualities that make them ideal targets for machine learning techniques: first, policies have a large affect on attainable performance, and second, *any* policy that a machine learning algorithm constructs will generate *correct* code. The latter quality is extremely important from the user's perspective: users trust, above all else, that the compiler will generate code that correctly represents their input programs.

Users and compiler writers alike benefit from my approach. Using my techniques, compiler writers need only design the correctness enforcing component of a compiler algorithm. Although the policy component is a small portion of a compiler heuristic, from a performance perspective, it is extremely important that the policy is well-tuned. For instance, Chapter 5 describes an experiment where I use machine learning to modify a single priority function in a compiler that is composed of 750,000 lines of C code. On a suite of multimedia and integer applications, the machine-learned priority function attains large speedups (~ 1.2x) over its human-crafted counterpart.

# 3.2 Meta Optimization : Learning Effective Compiler Heuristics

Broadly speaking, there are two main approaches for applying searching and machine learning techniques to compilation: *objective search* and *meta optimization*. I refer to any approach that embeds a searching algorithm *in* compilation policies as objective search (e.g., [70], [12]). This approach is used to specialize an application by searching for good solutions at *compile time*. In contrast my approach, meta optimization, improves the compiler policies themselves, which will indirectly improve the performance of applications that they optimize. The next two subsections clarify the difference between the two approaches.

#### 3.2.1 Objective Search

Every time a user invokes the compiler, objective search looks for good solutions that are specific to the code that is being compiled. A human-crafted objective function steers the search process. For the list scheduling problem that the last chapter introduced, one could imagine using an objective function to estimate the cost of a given instruction schedule.<sup>1</sup> A search algorithm that is embedded in the list scheduler could iteratively adjust the priorities of the instructions, looking for schedules with a lower cost than the best-so-far schedule. Chapter 8, which covers related work, discusses an approach to list scheduling that does exactly this. Field programmable gate array (FPGA) compilers also use objective search to find good placements of hardware components. These compilers estimate the cost of a given placement of hardware components, and use search techniques to find progressively better layouts.

Note that objective search does not alter compiler heuristics in any way; the heuristics, including the objective functions, are fixed. Instead, objective search iteratively perturbs and tests the code that the compiler generates. While objective search can be quite effective, its success hinges on the quality of the objective function. Remember that today's complex systems are difficult to model. Thus, it is unlikely that a human-constructed objective function can accurately describe the costs and benefits of a given solution.

#### 3.2.2 Meta Optimization

This thesis presents an orthogonal approach, called meta optimization, that searches for effective compiler policies offline. For instance, we can use meta optimization to find effective priority functions. One could even use meta optimization to improve the quality of the objective function used in objective search.

The machine-learned policy, which for now can be thought of as a black box, has the same input and output as a human-generated policy. For instance, consider learning a policy for assigning the priorities of instructions for list scheduling. The policy in this case is a function

<sup>&</sup>lt;sup>1</sup>One could even create an objective function that simulates the execution of a given instruction schedule and returns the number of cycles needed to run to completion.

that takes as input a vector of characteristics that abstractly describes an instruction, and returns a real number that represents the instruction's priority:

$$p_i \leftarrow f(\vec{x_i})$$

Here  $\vec{x_i}$  is a vector of characteristics that describes instruction *i*. Ideally, these characteristics should be useful for determining relative instruction priorities. For example, the dependence height of instruction *i* and the number of instructions that depend on it are two potentially discriminating characteristics. The value  $p_i$  in this case, is the priority value that the list scheduling algorithm would use to schedule instructions. The goal of meta optimization then reduces to finding a function, *f*, that generates effective code sequences.

One important difference between objective search and meta optimization pertains to *when* the searching is performed. Objective search is performed every time a user invokes the compiler, and thus it can incur significant compile-time overheads. Meta optimization on the other hand, incurs little or no compile-time overhead. Meta optimization subjects a compiler to a training phase, during which time the meta optimizer finds an effective policy. After the training phase is completed however, the compiler heuristic directly uses that policy to make its compilation decisions. Thus, the compiler policy could be trained "at the factory", and the learned heuristic could be shipped with the compiler.

## 3.3 Using Empirical Observations

The approach I take to meta optimization is evidence-based. I use actual observed metrics to drive the machine learning process. What then are the metrics by which we can judge the quality of a compiler policy? Because my goal is to create compiler policies that maximize end-to-end performance, the only metric I consider in this thesis is the actual runtime of the code a policy generates.

Alternatively, we could search for policies that generate the shortest, most succinct code sequences. Such an approach might be beneficial for compiling to embedded devices which are memory-limited. However, consider an optimization such as loop unrolling that increases the footprint of the generated code, yet also can yield large performance improvements. We could also consider minimizing cache misses, or the number of loads from memory. Such metrics would perform poorly for the many methods that infrequently touch memory.

Because compilers and architectures are multi-faceted systems, we should not base optimization decisions on *indirect* performance criteria. The only way to know the *full* impact of a policy is to time its end-to-end performance. Other metrics may correlate with runtime performance, but they are generally inadequate predictors of performance. Of course, meta optimization is a general approach, and depending on the goals of the compiler, one may wish to use other metrics to guide the learning process. The next section abstractly discusses four different methodologies for training compiler policies.

## **3.4 Training Compiler Policies**

Many people view a compiler as a tool that can effectively compile a diverse set of input programs. The compiler will ideally generate high-quality code for applications ranging from multimedia applications and integer codes to computationally intensive scientific applications. In addition, users expect the compiler-generated executables to perform well on a wide range of program inputs (*e.g.*, users expect their mp3 players to work well for a diverse collection of music).

We can use meta optimization techniques to train a compiler policy to perform well on a broad spectrum of applications. Later chapters will expound upon the notion of a *training* set of data, but for now it will suffice to mention that the machine learning algorithms create heuristics that are catered to this data. In other words, we can include in the training set, data from applications on which we want a learned compiler policy to excel. If the training set includes abundant data from a diverse set of applications, the learned policy will be general-purpose.

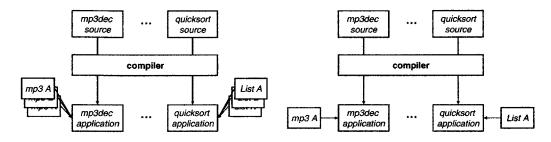

Later chapters use an approach that I call *Multiple Applications Single Input* (MASI) to train general-purpose compiler policies. The MASI approach, as shown in Figure 3-2(b) trains a policy using data drawn from multiple applications, each of which runs a single input. This thesis does not consider the *Multiple Applications Multiple Inputs* (MAMI)

(a) Multiple Applications Multiple Inputs (MAMI).

(b) Multiple Applications Single Input (MASI).

(c) Single Application Multiple Inputs (SAMI).

(d) Single Application Single Input (SASI).

Figure 3-2: The various ways in which to train a compiler policy. The MAMI and MASI approaches shown in (a) and (b) train a general-purpose policy that will perform well across a suite of applications. The SAMI and SASI approaches specialize compiler policies for a single application.

approach shown in part (a), which uses data drawn from multiple applications, each of which runs multiple inputs, to induce policies. The MAMI approach would increase training time, but would likely lead to more robust solutions.

Of course, we can also use meta optimization to specialize the compiler for a single application. In this case, the training data set is comprised of data that comes from a single application. This thesis experiments with a Single Application Single Input (SASI) training model, which caters the compiler to a particular application that runs a fixed input (e.g., an mp3 player that plays a single mp3). This mode of operation, which is shown in Figure 3-2(d) is beneficial for embedded systems developers who target platforms with tight resource constraints. Though the compiler policy is trained using a single input, I empirically show that the learned policy performs well when other inputs are applied. A Single Application Multiple Inputs (SAMI) approach as part (c) shows would likely improve the