### An Analysis of Current Guidance in the Certification of Airborne Software

by

#### Ryan Erwin Berk

B.S., Mathematics | Massachusetts Institute of Technology, 2002 B.S., Management Science | Massachusetts Institute of Technology, 2002

Submitted to the System Design and Management Program In Partial Fulfillment of the Requirements for the Degree of

#### Master of Science in Engineering and Management

at the

**ARCHIVES**

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2009

SEP 2 3 2009

LIBRARIES

© 2009 Ryan Erwin Berk All Rights Reserved

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now known or hereafter created.

| Signature of Author |   |           |                                           |

|---------------------|---|-----------|-------------------------------------------|

| -                   |   | •         | Ryan Erwin Berk                           |

|                     |   |           | System Design & Management Program        |

|                     |   |           | May 8, 2009                               |

| Certified by        |   |           |                                           |

| Certified by        | / |           | Nancy Leveson                             |

|                     |   |           | Thesis Supervisor                         |

|                     | ^ | _         | Professor of Aeronautics and Astronautics |

|                     |   | A ~ ! O A | Professor of Engineering Systems          |

| Accepted by         |   |           |                                           |

|                     |   | 1.        | Patrick Hale                              |

|                     |   |           | Director                                  |

|                     |   |           | System Design and Management Program      |

This page is intentionally left blank.

#### An Analysis of Current Guidance in the Certification of Airborne Software

by

#### Ryan Erwin Berk

Submitted to the System Design and Management Program on May 8, 2009 in Partial Fulfillment of the Requirements for the Degree of Master of Science in Engineering and Management

#### **ABSTRACT**

The use of software in commercial aviation has expanded over the last two decades, moving from commercial passenger transport down into single-engine piston aircraft. The most comprehensive and recent official guidance on software certification guidelines was approved in 1992 as DO-178B, before the widespread use of object-oriented design and complex aircraft systems integration in general aviation (GA). The new technologies present problems not foreseen by the original guidance material and may complicate demonstration of compliance with such guidance material.

The Federal Aviation Administration has deferred to industry experts in the form of the Radio Technical Commission for Aeronautics (RTCA) and the Society of Automotive Engineers (SAE) to create software and system approval guidance. The FAA's Advisory Circular (AC) 23.1309-1C created a four-tier approval system to reduce software and system approval burden on smaller aircraft, creating a lower standard for small aircraft in the hopes that safety gains from technology would outweigh the potential cost of defects from less stringent requirements. Further guidance regarding the role of software in the overall system is spread across other documents including Aerospace Recommended Practice (ARP) 4754, ARP 4761, and applicable SAE Aerospace Standards (AS).

The guidance material, spread across several documents, lacks sufficient specificity to be of use to an everyday practitioner. In addition the guidelines are not necessarily rigorously enforced when the same artifacts are required at different levels of design assurance as stated within DO-178B itself.

After a literature review and regulatory analysis, this thesis investigates some example defects that escaped detection during application of the guidance in a real-world product, making specific recommendations to improve the guidance in a usable way.

Thesis Supervisor: Nancy Leveson

Title: Professor of Aeronautics and Astronautics, Professor of Engineering Systems

This page is intentionally left blank.

#### **Acknowledgments**

First and foremost I must thank my wife, Leigh-Ann, for encouraging me to return to school. Without your support, none of the last two and a half years would have been possible. The late nights, weekends, and vacations I spent reading, writing, and performing simulations are finally over!

To my mother and father, thank you for your never-ending support of my educational aspirations. It began when I was just a boy and continues now as I approach 30 years old. You convinced me to come to Boston and attend MIT as an undergraduate, and I have not regretted it. An MIT connection brought me my first real job, and that job has returned me to MIT. It was your encouragement to travel far from our home in Wisconsin to the East Coast that has led me down the path I now find myself. Thank you for letting go enough to allow me to find my own way.

To my sponsor company, thank you for your support and commitment to me. To my first boss, Steve "Jake" Jacobson, thank you for taking a chance on me. I know I didn't fit the mold of a typical employee, but then again, you never did hire me. Thank you for not throwing me off the premises when you returned from vacation and found me sitting at a computer. Thank you for your support over the last seven years, and thank you for your help in acquiring sponsorship. I doubt I would be where I am today without your patronage. To my current boss, Steve Rosker, thank you for your flexibility and understanding as I complete this journey. Without your support I might have dragged this thesis out for a few years. To Yossi Weihs, thank you for introducing me to the Engineering Systems Division at MIT and encouraging me to return to school. I would not be where I am today without your guidance and support of my career growth.

To my advisor, Nancy Leveson, thank you for opening my eyes to the different facets of my profession. Thank you for the guidance in selecting a topic, the reviews, and the late-night email responses to my questions. The more I talk to people, the more I realize what a valuable resource I found in you. I will never look at another safety document quite the same way since meeting you.

To Pat Hale, Bill Foley and Chris Bates, thank you for running a great program and continuing to evolve the program as the needs of the students change. And to the rest of my SDM cohort, thank you for all the effort on our group projects and assignments as we worked our way through the program. I appreciate all that my teammates have done for me and all that we have accomplished together.

It's been an enlightening six and a half years at MIT.

This page is intentionally left blank.

### **Table of Contents**

| ABSTRACT                                                | 3  |

|---------------------------------------------------------|----|

| Acknowledgments                                         | 5  |

| Table of Contents                                       | 7  |

| List of Figures                                         |    |

| List of Tables                                          |    |

| Chapter 1 Introduction                                  | 11 |

| The Growth of Software                                  |    |

| Motivation                                              |    |

| Chapter 2 Literature Review                             | 15 |

| Comparisons                                             |    |

| Value                                                   |    |

| General Concerns                                        | 17 |

| Chapter 3 Software Approval Process                     | 19 |

| Part 23 vs. 25                                          |    |

| AC23.1309-1C, 1999                                      | 21 |

| System Safety Process                                   |    |

| Human Factors                                           |    |

| Structural Coverage                                     |    |

| Reuse                                                   |    |

| Development Verification                                |    |

|                                                         |    |

| Chapter 4 Case Studies                                  |    |

| Methodology Product Information                         |    |

| General Technical Details                               |    |

| Case 1: Green Screen                                    |    |

| Case 2: Persisted Settings Fail to Persist              |    |

| Case 3: Data Recorder Gaps                              |    |

| Case 4: GPS Approach                                    |    |

| Case 5: ARINC Transmission Rates                        | 73 |

| Chapter 5 Conclusions                                   | 79 |

| Recommendations Summary                                 |    |

| Limitations and Future Research                         | 81 |

| Appendix A – Acronyms and Initialisms                   | 85 |

| Appendix B - Description of Rate-Monotonic Architecture | 87 |

| Poforonces                                              | 80 |

This page is intentionally left blank.

### List of Figures

| Figure 1 Overview of the Development Process                                     | 19           |

|----------------------------------------------------------------------------------|--------------|

| Figure 2 Relationships Among Airplane Classes, Probabilities, Severity of Failur | e Conditions |

| and Software and Complex Hardware DALs, from AC23.1309-1D                        | 22           |

| Figure 3 Standard View of the Primary Flight Display                             |              |

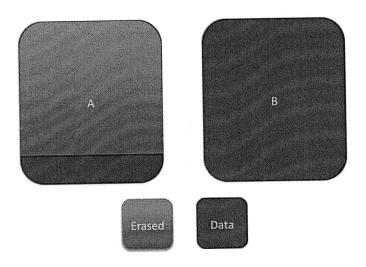

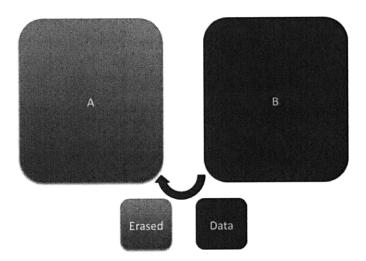

| Figure 4 Ping-pong Buffers with Block A Full and Block B Empty                   |              |

| Figure 5 Ping-pong Buffers with Block A Full and Block B Partially Full          | 49           |

| Figure 6 Ping-pong Buffer with Block A Partially Full and Block B Full           | 50           |

| Figure 7 Ping-pong Buffer with Block A Empty and Block B Full                    |              |

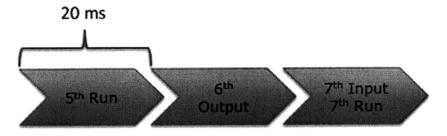

| Figure 8 Data Recorder Timing                                                    |              |

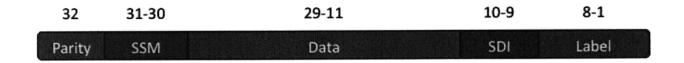

| Figure 9 Breakdown of an ARINC 429 Word                                          |              |

| Figure 10 HDI and VDI Displayed with WAAS Data                                   | 66           |

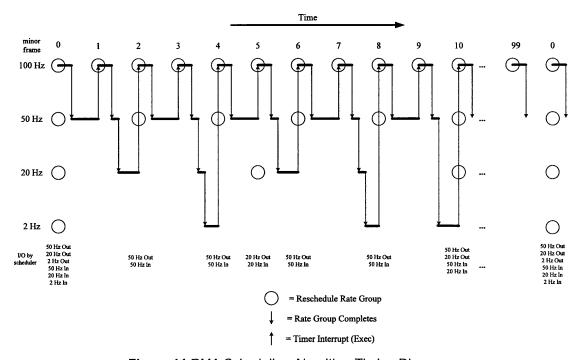

| Figure 11 RMA Scheduling Algorithm Timing Diagram                                | 87           |

|                                                                                  |              |

| List of Tables                                                                   |              |

| Table 1 PFD Flash Memory Layout                                                  | 38           |

| Table 2 Partial PFD Physical Memory Map                                          | 42           |

| Table 3 Data Logger Rates                                                        | 58           |

This page is intentionally left blank.

## Chapter 1 Introduction

#### The Growth of Software

Aircraft have flown with mechanical instruments since long before the first electromechanical instruments were conceived. Eventually the mechanical instruments have given way to more sophisticated electromechanical instruments and electronic displays, exchanging those old steam gauges with high-tech replacements.

Technological advances in the 1970s and 1980s allowed hardware to shrink in size, and newer technologies such as liquid-crystal displays have further reduced the space required to create electronic instrument displays. These advances have allowed for a rapid increase in the functionality allocated to software instead of hardware. Software controls a vast number of decisions and connections in modern aircraft: from fuel pumps, to autopilots, to radios, to primary instruments. As an example, the nation is covered with radio towers that broadcast on specific VHF frequencies to allow determination of position. The first radios were completely analog, but over time the analog tuners were replaced with digital tuners that use software to configure the receiver. Now all-digital radios are being produced that use software to tune the frequencies and process the signals received from the VHF stations.

To address the growing use of software in aviation, the Radio Technical Commission for Aeronautics, known as the RTCA, released a document of guidelines for software development in 1982. The document was the result of consensus opinion from a wide range of domain experts periodically meeting as part of a working group tasked with the creation of guidelines. This document was titled DO-178, Software Considerations in Airborne Systems and Equipment Certification. Its purpose was to provide industry-accepted best practices to meet regulatory requirements for airworthiness such as Part 23 and Part 25 of the Federal Aviation Regulations (FARs). The document was revised in 1985 (DO-178A) and again in 1992 (DO-178B) to reflect the experience gained and criticisms of previous revisions. The current revision (in 2009) is DO-178B, and there are many references to DO-178B throughout this document.

It should be noted that DO-178 is not the only means of compliance with airworthiness regulations and that no portion of DO-178 is official government policy. RTCA is an association of government and private organizations that working together to develop recommended practices, but applicants for software approval are free to demonstrate compliance to the certification authority using any other acceptable means. Despite the possibility of developing software using alternative means of compliance, DO-178B is the de facto standard (Jackson, et al. 2007) by which all software submissions for approval are judged at the local Aircraft Certification Offices (ACOs).

#### **Motivation**

I became interested in improving the certification process for software from my first month after college graduation. I started my first "real" job, and the first document handed to me after the employee handbook was DO-178B. I read the standard twice, and I still did not comprehend what I would be doing with the document. Even now, after seven years, I can re-read the standard and discover subtleties I have missed in previous readings. As I gained experience I

could relate what I have learned to seemingly innocuous statements and gain critical insight into the "why" of some aspects of the standard.

One of my concerns with the standard is the lack of specificity in the guidance. Two different designated engineering representatives (DERs) may come to different conclusions regarding the acceptability of a particular document or artifact based on their particular experiences and preferences because the guidelines are quite vague. One of the issues with consensus-based documents may the lack of specificity to ensure that each of the members can continue their current practices while abiding by the guidelines because the guidelines are quite broad.

Reading the standard, I realize now that the guidance document tries to balance the need for tangible content against the heterogeneity of airborne software and company processes. While the standard provides information, it does not provide specific, useful information that can be immediately applied.

One of my first tasks as a new-hire was to develop low-level requirements for a product that was fairly well along the prototype path. I went to DO-178B to figure out how to write a low-level requirement, and the standard was almost silent on the topic. The only definition I could find in DO-178B was, "Low-level requirements are software requirements from which Source Code can be directly implemented without further information." I asked other engineers, but no one had significant experience with low-level requirements or DO-178B software developed to a design assurance of Level C, the lowest design assurance level that requires low-level requirements be written, traced, and verified.

From then on I have been involved in refining our corporate processes and standards in addition to auditing for compliance and "goodness" of process outputs from other development teams.

Through this document I intend to provide practical recommendations for improvements to the

software certification process under DO-178B in addition to providing meaningful root cause analysis and process improvements to my sponsor company.

# Chapter 2 Literature Review

Research and study has been devoted to software standards and certification for as long as certification guidelines have existed. Examining the revisions of the certification guidelines demonstrates a fact that guidelines are constantly being reviewed, revised, and replaced. DO-178, the first release of Software Considerations in Airborne Systems and Certification was a goal oriented process document written at the conceptual level released in 1982 (Johnson, 1998). Companies developed to the standard by meeting the "intent" of the document. DO-178A was the first major revision of the standard, released in 1986, followed by DO-178B, another major revision, in 1992. The guidelines changed dramatically between DO-178A and DO-178B as practitioners gained experience with DO-178A and recommended changes as part of an industry working group.

#### **Comparisons**

Civilian aviation software was not the only area developing software standards. The United States Military provided its own software standards such as MIL-STD-1679, MIL-STD-2167, and MIL-STD-498. The European Space Agency has also released PSS-05-0, titled ESA Software Engineering Standards, in response to the growth of software and complex systems safety concerns. With these standards brings the comparisons of DO-178B with MIL-STD-498 and

ESA PSS-05-0. The ESA standard is more direct and specific than DO-178B, providing templates and examples of methods of compliance while DO-178B is more abstract and process oriented (Tuohey, 2002).

Software approval and certification standards are not unique to aerospace. Software security professionals along with the National Security Agency (NSA) and the National Institute of Standards and Technology (NIST) have established the Common Criteria for Information Security Evaluation to provide guidelines for developing secure software for information technology. Further comparisons map Common Criteria assurance classes on to DO-178B processes. Such mapping demonstrates gaps in the DO-178B processes such as assurance of Delivery and Operation (Taylor et al., 2002).

#### **Value**

Others have questioned whether certification makes a difference in the quality of the final product or whether other factors are at work (Jackson, et al., 2007). Many of the DO-178B mandated procedures are difficult to trace to direct effects on the quality of the software output. Some have hypothesized that the development of software within a "safety culture" may be the key to developing software with fewer defects. While software engineers are notoriously protective of their source code, operating in an environment with human lives at stake may encourage them to value the opinions of colleagues, act cautiously, and pay meticulous attention to detail (Jackson et al., 2007).

While Jackson laments the strictures put in place by DO-178B, others appreciate the flexibility provided by the standard. Though DO-178B was released in 1992, it does not preclude the use of agile methods that gained popularity in the 1990s. Agile methods rose in response to the traditional waterfall methods used in "big-aerospace" for twenty-five years. DO-178B Section 4

emphasizes transition criteria in an apparent endorsement of a waterfall development process, but the individual development process sections allow for feedback and iteration at any stage. Some agile methods may be used to satisfy DO-178B objectives. At higher certification levels, (Levels A and B), satisfaction of the development objectives requires demonstration of independence in the development of requirements, code, and test. The goal of the independence objectives may be to minimize potential interpretation problems arising from a single person reading and implementing a requirement. The agile method of pair programming can be used to meet the independence objectives (Wils, 2006).

#### **General Concerns**

The generality of the DO-178B standard likely derives from the way in which the standard was developed and ratified, specifically by consensus. It would be very difficult to achieve consensus on specific templates or document formats as in ESA PSS-05-0 in an environment of competing aviation professionals. (Hesselink, 1995) argues that DO-178B is not intended to be a software development process, but a point of common understanding between the applicant and the certification authority in his comparison of DO-178B with MIL-STD-2167A and ESA PSS-05-0. Others support that thought by describing DO-178B as an assurance standard, not a development standard (Sakugawa et al, 2005). None of those standards are self-contained, but by maintaining a process-oriented standard, DO-178B makes it the most flexible of the three standards.

The broadest identification of concerns in the certification of airborne software comes from Sakugawa, Cury, and Yano. They provide a list of relevant technical issues and brief discussion ranging from high-level concerns, such as the purpose of DO-178B, to detailed issues, such as configuration control of software compatibility spread across systems. Much of the discussion identifies concerns that should be addressed in future revisions to the guidance material but

fails to provide any evidence or suggestions as to improvements. By contrast, this document includes specific recommendations to improve the certification guidance material supported by examples from industry.

# Chapter 3 Software Approval Process

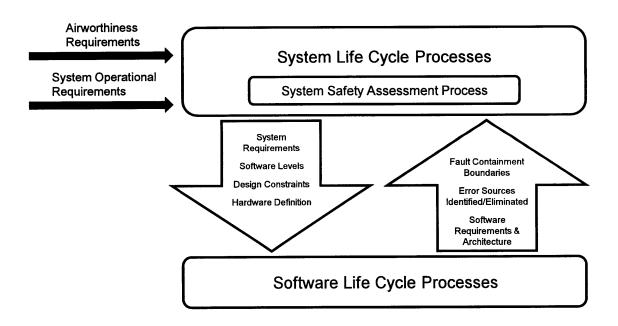

The software approval process is just one part of an overall aircraft certification. The FARs govern the airworthiness of an aircraft, and the software covers just a portion of all that is required by the airworthiness regulations. As outlined by section 2.1 of DO-178B and shown in **Figure 1** below, the system life cycle processes including a system safety assessment (SSA) process evaluate the product development at the aircraft installation level.

Figure 1 Overview of the Development Process

A major part of the development of a system for airborne installation is the analysis of the airworthiness and system operational requirements. The system requirements must be defined and determined to meet the airworthiness requirements set by the certification authority. Only after the airworthiness analysis has been performed should the system requirements be allocated between software and hardware. Guidelines for performing a system safety assessment are outlined in documents released by the Society of Automotive Engineers (SAE) as Aerospace Recommended Practice (ARP) documents. The specific documents that are called out by the FAA Advisory Circular (AC) 23.1309-1D are ARP 4754, Certification Considerations for Highly-Integrated or Complex Aircraft Systems, and ARP 4761, Guidelines and Methods for Conducting the Safety Assessment Process on Civil Airborne Systems and Equipment. A detailed discussion of the safety assessment process and compliance with airworthiness requirements is beyond the scope of this document.

As software design becomes more complex, features once allocated to hardware such as circuit breakers are more frequently allocated to software because the software can be changed with little marginal cost after the aircraft has been certified. A software development is a costly proposition, and more costly at higher design assurance levels, but changing a piece of dedicated hardware may be more expensive than designing in the flexibility in software from an early stage.

Once system requirements have been allocated to software and the software design has implemented the requirements or sufficiently determined the design regarding those requirements, feedback—in the form of derived requirements—must be provided back to the safety assessment process or team to ensure the architectural implementation meets the design assurance levels specified by the safety assessment and that no assumptions of the safety assessment have been violated by the software architecture. The constant feedback between

the SSA process and the software development process is designed to ensure that the final product meets the design assurance levels required by the SSA as well as the airworthiness requirements to receive approval for installation in certified aircraft.

#### Part 23 vs. 25

The FARs are technically a portion of Title 14 of the Code of Federal Regulations (CFR). This thesis examines DO-178B only as it pertains to Part 23 of 14 CFR in an effort to restrict the scope to a manageable level. The main difference between Part 23 and Part 25 aircraft is the size and weight of the aircraft. Part 23 aircraft are restricted to have gross takeoff weights of 12,500 pounds or less, while aircraft certified under Part 25 have no such restrictions. In more concrete terms, Part 23 covers small aircraft up through Commuter category aircraft, while Part 25 governs larger business jets up through air transport and commercial airliners. Certain ACs are specific to Part 23 or Part 25 of the FARs and this document will only discuss the Part 23 ACs. DO-178B was originally intended for aircraft certified under Part 25 of the FARs. It was not until the release of AC 23.1309-1C in 1999 that DO-178B could be applied to small aircraft in a cost-effective manner.

#### AC23.1309-1C, 1999

Published in 1999, AC23.1309-1C was a watershed document for light general aviation. This AC lowered the minimum required design assurance levels for Part 23 aircraft from the DO-178B mandated levels intended for Part 25 aircraft. The reduction in minimum DALs opened the door to lower-cost avionics development projects by reducing the certification burden and overhead required to receive approval from the certification authority. A critical product of the SSA as outlined in ARP 4761 is the required minimum software design assurance levels for different aircraft functions. There are five levels of design assurance as outlined in DO-178B

(expanded from three levels in DO-178A), and the five levels mirror the five levels of failure conditions.

| Classification of                                                              | No Safety Effect                                                                               | <>                                                                     | <major></major>                                                                | <hazardous></hazardous>                                                              | < Catastrophic>                         |  |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| Failure<br>Conditions                                                          |                                                                                                |                                                                        |                                                                                |                                                                                      |                                         |  |  |

| Allowable Qualitative Probability                                              | No Probability<br>Requirement                                                                  | Probable                                                               | Remote                                                                         | Extremely<br>Remote                                                                  | Extremely<br>Improbable                 |  |  |

| Effect on Airplane                                                             | No effect on<br>operational<br>capabilities or<br>safety                                       | Slight reduction in<br>functional<br>capabilities or<br>safety margins | Significant<br>reduction in<br>functional<br>capabilities or<br>safety margins | Large reduction in<br>functional<br>capabilities or<br>safety margins                | Normally with hull loss                 |  |  |

| Effect on<br>Occupants                                                         | Inconvenience for passengers                                                                   | Physical<br>discomfort for<br>passengers                               | Physical distress<br>to passengers,<br>possibly including<br>injuries          | Serious or fatal<br>injury to an<br>occupant                                         | Multiple<br>fatalities                  |  |  |

| Effect on Flight<br>Crew                                                       | No effect on flight<br>crew                                                                    | Slight increase in<br>workload or use of<br>emergency<br>procedures    | Physical<br>discomfort or a<br>significant<br>increase in<br>workload          | Physical distress<br>or excessive<br>workload impairs<br>ability to perform<br>tasks | Fatal Injury or incapacitation          |  |  |

| Classes of<br>Airplanes:                                                       | Allowable Quantitative Probabilities and Software (SW) and Complex Hardware (HW) DALs (Note 2) |                                                                        |                                                                                |                                                                                      |                                         |  |  |

| Class I<br>(Typically SRE<br>under 6,000 lbs.)                                 | No Probability or<br>SW & HW DALs<br>Requirement                                               | <10 <sup>-3</sup><br>Note 1 & 4<br>P=D, S=D                            | <10 <sup>-4</sup><br>Notes 1 & 4<br>P=C, S=D<br>P=D, S=D(Note 5)               | <10 <sup>-5</sup><br>Notes 4<br>P=C, S=D<br>P=D, S=D(Note 5)                         | <10 <sup>-6</sup><br>Note 3<br>P=C, S=C |  |  |

| Class II<br>(Typically MRE,<br>STE, or MTE<br>under 6000 lbs.)                 | No Probability or<br>SW & HW DALs<br>Requirement                                               | <10 <sup>-3</sup><br>Note 1 & 4<br>P=D, S=D                            | <10 <sup>-5</sup><br>Notes 1 & 4<br>P=C, S=D<br>P=D, S=D(Note 5)               | <10 <sup>-6</sup><br>Notes 4<br>P=C, S=C<br>P=D, S=D(Note 5)                         | <10 <sup>-7</sup><br>Note 3<br>P=C, S=C |  |  |

| Class III<br>(Typically SRE,<br>STE, MRE, &<br>MTE equal or<br>over 6000 lbs.) | No Probability or<br>SW & HW DALs<br>Requirement                                               | <10 <sup>-3</sup><br>Note 1 & 4<br>P=D, S=D                            | <10 <sup>-5</sup><br>Notes 1 & 4<br>P=C, S=D                                   | <10 <sup>-7</sup><br>Notes 4<br>P=C, S=C                                             | <10 <sup>-8</sup><br>Note 3<br>P=B, S=C |  |  |

| Class IV<br>(Typically<br>Commuter<br>Category)                                | No Probability or<br>SW & HW DALs<br>Requirement                                               | <10 <sup>-3</sup><br>Note 1 & 4<br>P=D, S=D                            | <10 <sup>-5</sup><br>Notes 1 & 4<br>P=C, S=D                                   | <10 <sup>-7</sup><br>Notes 4<br>P=B, S=C                                             | <10 <sup>-9</sup><br>Note 3<br>P=A, S=B |  |  |

Note 1: Numerical values indicate an order of probability range and are provided here as a reference. The applicant is usually not required to perform a quantitative analysis for minor and major failure conditions. See figure 3.

Figure 2 Relationships Among Airplane Classes, Probabilities, Severity of Failure Conditions, and Software and Complex Hardware DALs, from AC23.1309-1D

Note 2: The alphabets denote the typical SW and HW DALs for most primary system (P) and secondary system (S). For example, HW or SW DALs Level A on primary system is noted by P=A. See paragraphs 13 & 21 for more guidance.

Note 3: At airplane function level, no single failure will result in a catastrophic failure condition.

Note 4. Secondary system (S) may not be required to meet probability goals. If installed, S should meet stated criteria. Note 5. A reduction of DALs applies only for navigation, communication, and surveillance systems if an altitude encoding altimeter transponder is installed and it provides the appropriate mitigations. See paragraphs 13 & 21 for more information.

The as-written regulations prior to AC 23.1309-1C required that primary instruments and other systems critical to the continued safe operation of an aircraft must be certified to Level A. The figure above shows the updated guidance information from 23.1309-1C. Examining Class I and Class II aircraft, the most critical failure category, Catastrophic, requires a minimum DAL of just Level C, two levels lower than the DO-178B guidance requires.

According to the FAA, accidents in Part 23 certificated aircraft are primarily attributed to pilot error and a loss of situational awareness (AC 23.1309-1C). The resulting behavior of a disoriented pilot is typically known as controlled flight into terrain or CFIT. The FAA believes that equipping these small aircraft with additional technologies that provide more easily understandable information regarding aircraft position and attitude will reduce the severity and frequency of such errors, improving overall aviation safety.

Certifying software to Level A is a very expensive proposition for development companies, and prior to 1999 there was limited adoption of complex avionics in Part 23 aircraft because of the relatively high prices required by avionics manufacturers to recoup the costs associated with a Level A certification. By reducing the minimum required DALs for small aircraft, the FAA encourages new avionics development at lower price points due to lower costs associated with the certification activities. The FAA believes that increasing the equipage rates of small aircraft will provide a safety benefit that outweighs the risks associated with reduced design assurance levels in Class I-Class IV aircraft.

One of the criticisms of the entire DO-178B/ARP4754/ARP4761 process is the lack of cohesiveness between the regulatory guidance provided and a concrete implementation of the process in certifying an aircraft. All of the aforementioned documents were developed for Part 25 aircraft. While DO-178 and DO-178A outlined the role of software and its relation to overall system safety, the current revision of the standard has removed the references to Type

Certification (TC), Supplemental Type Certification, Technical Standards Order Authorization and equivalent FARs (Johnson, 1998). AC23.1309-1C lowered the minimum bar for small aircraft but fails to address some of the changes required amongst all the documents to adequately handle Part 23-specific changes such as conducting a system safety assessment for Part 23 aircraft. The AC specifically cites ARP 4754 and ARP 4761 as only partially applicable for Part 23 certification, but fails to identify what portions of those documents should be satisfied and what portions can be disregarded. This oversight implies the certification system as a whole was not prepared or intended to handle such modernization in 1999 when the last well-prepared modifications to the software certification guidelines were released in 1992.

Another common criticism of the structure of the FAA can be seen in AC 23.1309-1C. The FAA's mission demonstrates a bit of a conflict of interest. The mission statements on the FAA website (FAA Website, 2009) indicate that the FAA's major roles include:

- 1. Regulating civil aviation to promote safety

- 2. Encouraging and developing civil aeronautics, including new aviation technology

The FAA is responsible for promoting safety, yet it also promotes new technologies. AC23.1309-1C promotes new technology by reducing required DALs for software in small aircraft, allowing installation of safety-enhancing equipment into aircraft where previous avionics were not cost-effective. It seems that the FAA is walking a fine line by reducing safety requirements to increase safety by increasing the installed base of advanced avionics. While I agree with the assertion that increasing the availability of advanced avionics in Part 23 aircraft will have a positive impact on safety for the Part 23 aircraft, the overall impact on the National Aerospace System (NAS) with increased air traffic in instrument meteorological conditions (IMC) may have a negative effect on air safety for the Part 25 aircraft relied upon by the majority of the traveling public.

**Recommendation:** Separate the aviation promotion and safety aspects of the FAA to preclude any conflicts of interest regarding reduced safety in the name of advancing technology and popularizing general aviation.

Within the past few months AC 23.1309-1C has been superseded by AC23.1309-1D, replacing a previous hardware design assurance standard with the new DO-254, Design Assurance Guidance for Airborne Electronic Hardware, released in April of 2000. AC23.1309-1D followed almost nine years after the release of DO-254. That delay is indicative of the speed at which some aerospace regulations can be expected to be updated; change happens slowly.

#### **System Safety Process**

DO-178B calls out SAE ARP 4754 and SAE ARP 4761 as recommended guidance in developing complex airborne systems and performing system safety assessments. Examining DO-178B Section 5.1.2, the document requires derived requirements to be provided to the system safety assessment process for evaluation against assumptions and calculations made while administering the process outlined in ARP 4761. A system safety assessment team would typically consist of different aircraft-level experts allocating functionality and defining high-level functional failure modes. Such personnel may be insufficient in assuring system safety. One of the recommendations from the literature is to ensure that software engineers and code developers understand the software-related system safety requirements and constraints (Leveson, 1995). By highlighting the requirements and features that are safety-related and needed to support the preliminary SSA, software engineers will have the insight into the intent and purpose of the requirement in addition to the text of the requirement.

Can the system safety assessment team adequately comprehend the implications of a single low-level design choice such as the use of a ping-pong buffer scheme as it relates to the aircraft level functionality? The aircraft level would typically exist at least two levels of abstraction

higher than the level at which the software requirement is describing some internal design detail of the software. As shown in **Figure 1**, the software requirements must trace up to system requirements, and the system requirements derive from a combination of airworthiness requirements and system operational requirements. It would seem that the composition of aircraft-level safety analysts might not be the appropriate personnel to critically evaluate detailed design and architecture decisions as increases in software complexity have outpaced our ability to master new technologies such as object-oriented design.

**Recommendation:** The system safety assessment team must include software safety expertise to evaluate software design decisions and the implications of those decisions in the context of overall system and aircraft safety margins.

#### **Human Factors**

With the increasing complexity in avionics and airborne software comes an increasing level of information conveyed to the pilot via displays, buttons, and knobs. Safety standards and TSOs govern basic aircraft functionality and required depictions and abbreviations, but there has been very little guidance regarding human factors and the human-machine interface. Safety assessments have focused on failure rates of hardware and design assurance levels of software but fail to explicitly consider the exact manner in which the data is presented to the pilot. As an example, a digital readout of manifold pressure is less visually compelling than a digital readout below a tape or dial presentation of the same information. The impact of user interface design is difficult to quantify, as the evaluation is subjective. That subjectivity makes it very difficult to provide consistent safety analysis guidelines for user interfaces. The National Transportation Safety Board (NTSB) realizes that the only evaluations of software user interface occur late in the certification process (NTSB, 2006) as part of the FAA's Multi-Pilot System Usability Evaluation (MPSUE). A MPSUE consists of a group of FAA expert pilots that evaluate the proposed system for compliance with FARs and other industry guidance such as readability.

color choices, and pilot workload. The evaluations are subjective by their very nature and only peripherally address aircraft safety issues as impacted by user interface.

#### **Structural Coverage**

As software complexity increased in the 1970s and 1980s it became obvious that exhaustive path testing of a software program would be cost-prohibitive. Imagine a program consisting of 60 different conditional checks. To exhaustively test each possible path in such a program, it would require 2^60 (1.15e18) tests. By comparison, the universe is only 4e17 seconds old, so developing and running such a test suite for even a simple program as described is not feasible (Myers, 1976). To that end, structural coverage has been accepted as a proxy for path coverage.

DO-178B defines three different levels of structural coverage for demonstration at three different design assurance levels. The lowest DAL that requires structural coverage is Level C. Structural coverage of code developed per a Level C process requires statement coverage, or coverage of every executable statement or block of source code. Level B structural coverage adds the requirement of branch coverage in addition to statement coverage. Branch coverage requires execution of every decision or local path at least once. In source code written in C/C++, this requirement implies that implicit "else" cases and switch/case defaults are explicitly tested and covered. Level A structural coverage requires demonstration of modified condition/decision coverage (MCDC). MCDC adds the requirement that each part of a conditional check can affect the outcome of the decision.

Each of the structural coverage requirements presented by the ascending DALs requires more effort than the preceding level. Total productivity can slow to 100 lines of source code per manmonth at the highest level of design assurance (Binder, 2004). Some evidence has recently

been presented indicating that the additional certification requirements for Level A including MCDC do not show any increase in safety or reliability of the software (Jackson et al, 2007). Other research recommends additional coverage metrics such as mandatory loop coverage for safety-critical software development (NASA 2004). Loop coverage ensures that software control loops are verified to perform the intended function when each loop body is executed zero times, exactly once, and more than once (consecutively). Such loop testing provides additional confidence that the loops under test do not exhibit adverse behavior that may be missed when performing MCDC or branch coverage.

#### Reuse

One of the more recent criticisms of DO-178B in the wake of AC 23.1309-1C has been the difficulty of reusing software in avionics. Prior to the relaxed standards introduced in 1999, Commercial Off The Shelf (COTS) software was not widely implemented because of the certification costs for software. COTS software is more general than a custom piece of software designed for a specific goal because COTS parts are developed to be sold for use in more than one environment. That flexibility requires source code beyond the minimum required set for any given use, and that extra code requires certification under DO-178B as prescribed under Section 2.4 (f). Certifying COTS under DO-178B requires a significant amount of effort (Maxey, 2003) and the use of COTS has not been demonstrated to make avionics products safer.

The FAA has heard the complaints of authors such as Maxey and attempted to address the changing landscape of embedded software systems by releasing AC 20-148 in December 2004. That document establishes a certification mechanism for creating a Reusable Software Component (RSC) that can be used for software features such as algorithm libraries and operating systems. An RSC can be used to satisfy some of the certification objectives of DO-178B by providing an integration package of life-cycle data to attach to the applicant submission

for approval. RSCs require verification of the code in the target environment as well as satisfaction of design constraints within which the original software approval was granted. The virtues of RSCs are just now becoming apparent, but some believe the use of RSCs will usher in a new era of productivity as development firms can focus on product specifics instead of core services (Matharu, 2006).

#### **Development**

Another criticism of DO-178B has been the rigor with which the development standard was followed for a piece of software. It is possible to develop a piece of software using any process and subsequently back-fill the requirements, design information, and reviews (Kim et al, 2005). Creating the life-cycle data *a posteriori* defeats the purpose of developing to a standard (Brosgol, 2008), yet systems often must be adapted to meet certification guidelines after development. DO-178 has evolved over three revisions and DO-178B Section 12.1.4 discusses the upgrading of a development baseline to bring software into compliance with the current guidance. Section 12.1.4 sub-paragraph d specifically calls out the use of reverse engineering to augment inadequate life-cycle data to meet the objectives specified throughout the standard. Such reverse engineering has been encouraged and purported to provide value to legacy systems (Hicks, 2006), though others have claimed that it is not possible to adequately reverse engineer a product towards a standard (Hesselink, 1995).

The first drafts of DO-178B appeared in 1989 and the final version of DO-178B was released in 1992, before the widespread use of object-oriented (OO) design in airborne systems. While DO-178B does not preclude the use of OO, it seems clear that parts of OO design complicate the satisfaction of objectives in DO-178B. The guidance documents require traceability between requirements and source code. Such traceability is relatively easy to demonstrate when programming procedurally as a method or group of methods contained within a module

perform a task that traces directly to requirements. OO design creates mental abstractions that may spread directly related functions across modules and complicate traceability.

Another DO-178B objective complicated by OO is the handling of dead and deactivated code.

DO-178B provides the following definitions of dead and deactivated code:

Dead code - Executable object code (or data) which, as a result of a design error cannot be executed (code) or used (Data) in an operational configuration of the target computer environment and is not traceable to a system or software requirement. An exception is embedded identifiers.

Deactivated code - Executable object code (or data) which by design is either (a) not intended to be executed (code) or used (data), for example, a part of a previously developed software component, or (b) is only executed (code) or used (data) in certain configurations of the target computer environment, for example, code that is enabled by a hardware pin selection or software programmed options.

OO design provides the ability to override a method provided by a base class in a child class. The overriding may create dead or deactivated code in a module that has not been modified in the software release under development, yet such effects may be difficult to detect outside of a human review. In response to the shortcomings of DO-178B with regards to OO technology, certification authorities from around the world have highlighted unique problems presented by OO in the Certification Authorities Software Team (CAST) Position Paper CAST-4. CAST-4 does not provide any additional regulation or guidance over DO-178B, but instead highlights the relevant concerns regarding the use of OO by an applicant. The issues raised by the position paper should receive consideration in DO-178B documents such as the Plan for Software Aspects of Certification (PSAC) and the Software Accomplishment Summary (SAS). Industry experts have also generated the Object-Oriented Technology in Aviation (OOTiA) Handbook in an effort to identify other concerns in the use of OO in airborne systems. The OOTiA Handbook was released in 2004 (12 years after DO-178B) and provides discussion of the issues and

examples of how to use a subset of OO techniques that permit the demonstration of compliance with DO-178B objectives.

#### Verification

Others have criticized the regulatory guidance for its lack of testing discussion. Section 2.7 of DO-178B is titled "Software Considerations in System Verification". The very first sentence of the section reads, "Guidance for system verification is beyond the scope of this document." With the advent of low-cost MEMS sensors for attitude, air data, and navigation systems, one software "product" can effectively satisfy an aircraft level feature such as VHF navigation, for example. The scope of the software has increased since 1992, and system verification may need to be addressed because the software and hardware within a single product is the entire system. Whether I put an integrated attitude display system in a car, a boat, or a plane, the entire set of functionality (aside from power) is under the control of a single software product and software testing becomes synonymous with system testing. Furthermore the software requirements flow down from system requirements, yet there is no explicit mention of system requirements testing as DO-178B only provides guidance on software considerations. DO-178B was written under the assumption that the aircraft certification applicant is the same entity as the software developer (Sakugawa et al., 2005), but the avionics industry has expanded to include development firms that sell complex avionics to original equipment manufacturers (OEMs). How can a development firm create system requirements and allocate/expand those system requirements into software requirements but never verify the system requirements are satisfied at a system level?

**Recommendation:** Regulatory guidance should outline testing processes such as an Integrated System Test Plan (ISTP) to verify that System Requirements are met as the system is integrated into a target aircraft.

Others have suggested that DO-178B Section 6, Software Verification Process, will need revision soon. Software complexity is increasing rapidly and current testing methods will not scale to meet orders of magnitude more complex software (Allerton, 2006). DO-178B recognizes that verification is not just testing, but a combination of reviews, analyses, and tests. The difference between analysis and review is reviews are more qualitative while analysis is repeatable and often quantitative. "Analyses provide repeatable evidence of correctness and reviews provide a qualitative assessment of correctness." For example, a verification engineer could verify the system timing to ensure that attitude display meets published minimum operating performance standards (MOPS) for application of a Technical Standards Order (TSO). One technique might be to review the source code and associated timing tables to ensure that the system/software requirements are met in addition to the MOPS. The review relies on a human's reading of the applicable requirements and review of source materials that directly determine the software behavior and characteristics. An equivalent analysis might include development of minimally intrusive software or hardware instrumentation that measures or signals the timing characteristics of the software. Such an analysis is repeatable as required by the definition from the document. In addition the analysis could provide an objective answer as to confidence that the software behaves as expected. The repeatability of an analysis makes it preferable to a qualitative or subjective review as a means of verification.

Other verification tasks do not lend themselves to analytic techniques as above. DO-178B requires demonstration of traceability from source code and tests all the way up to system requirements (unless intermediate requirements are derived). While analysis may be used to verify that all requirements are traced, only review can determine the correctness of the trace between requirements because human interpretation is required to understand the implications of any given requirement. The implications must be considered not only for the directly traced

requirements but also for the untraced but applicable requirements. Human review techniques are better suited to such qualitative judgments than are analyses.

Section 6.4 of DO-178B discusses the Software Testing Process as it pertains to overall software verification and calls out two objectives from testing. The first objective is to show that the requirements are fully satisfied, known as requirements coverage. The second goal of testing is to demonstrate "with a high degree of confidence that errors which could lead to unacceptable failure conditions, as determined by the system safety assessment process, have been removed". The second objective is noble, but rather abstract. To what level of confidence should software be tested? Earlier in the guidance document the writers acknowledge software does not exhibit hardware-like failure rates because software is deterministic. Full path testing is not possible for complex software as demonstrated above in the example from (Myers, 1976). The guidance document is silent as to how to achieve that level of confidence through testing; leaving the development firm to make an engineering judgment as to how much testing is enough.

There are many gaps in DO-178B, AC 23.1309-1C/-1D and the associated ARPs for software approval. Through review, refinement, and iteration the guidance writers should be able to release a new draft of the DO-178 that addresses the concerns raised over the last seventeen years, incorporating experience and suggestions from published research such as this document.

This page is intentionally left blank.

# Chapter 4 Case Studies

#### Methodology

Each of the following cases represents a real-world example of defects in software design according to DO-178B compliant processes. Some of the examples demonstrate gaps in DO-178B coverage or treatment of specific artifacts required for a successful product development. Other examples demonstrate software developed following the guidance but still include defects that the process does not protect against.

The five examples that follow each introduce the problem briefly, identifying the high level feature and the defect that was observed. Each example then covers the technical details necessary to understand the complexity of the defect. In addition the exact source code that caused the behavior is identified. A discussion of the DO-178B process artifacts follows in the certification discussion section for each example, identifying the associated requirements, tests, and development processes associated with the defect. Those artifacts demonstrate defects in the process from which the source code is developed. By identifying the process defects, I will identify recommendations for improvements to the DO-178B guidance material to assist others in preventing the same types of defects that are under investigation. While every software

project is unique, the suggested DO-178B process improvements should provide concrete improvements in certified software development processes.

### **Product Information**

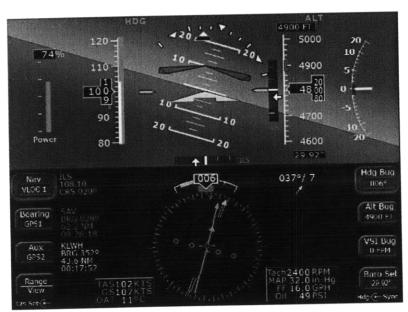

All of the examples presented below are extracted from the defect tracking system for a piece of avionics known as a Primary Flight Display, or PFD. The PFD incorporates eleven different compiled applications spread across nine processors, but all the defects under review here are from the highest-level processor that controls the display and user interface functionality. The PFD's main purpose is to provide critical aircraft flight parameters, integrated in a single piece of avionics. Aircraft air data and attitude information, such as altitude, airspeed, pitch, roll, and heading, are provided via an integrated sensor solution. Other flight parameters such as the active flight plan, traffic information, and radio navigation aids are provided over standardized digital databus interfaces.

Figure 3 Standard View of the Primary Flight Display

In addition to the obvious graphical features of the PFD, other features are embedded below the graphics, such as supplying navigation information to the traffic and autopilot systems.

A data recorder was added to the PFD after the initial release. One of the goals of the recorder was to provide data for internal use to determine life-cycle reliability and error conditions in returned units. According to an industry publication 35%-60% of avionics returns result in "No Fault Found" or "Could Not Duplicate" resolutions (Avionics Magazine, 2005). A data recording mechanism was developed in an effort to provide better information for our service center to decrease the rate of such problems as those problems can end up becoming multiple returns for the same failure. Those multiple returns cost a significant amount of money both to the company and to the aircraft owner due to Aircraft on Ground (AOG) situations.

## **General Technical Details**

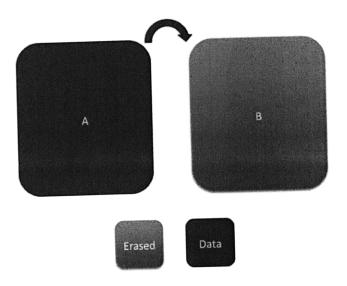

One of the common sources of defects in the PFD has been access and writing to high reliability flash memory. The PFD contains onboard memory storage in the form of embedded flash memory chips. The flash memory chips read/write/access times are significantly slower than system RAM. This slower speed requires special consideration in embedded real-time systems because of the non-negligible impact to thread timing. The PFD's flash memory includes 128 blocks of 256 Kbytes (where 1kByte equals 1024 bytes and 1 byte is 8 binary bits).

When examining a block of erased memory, every bit in the block appears as a '1'. Writing to a block is the equivalent of masking off some of the bits, switching them from '1' to '0'. Once data has been written, the only way to rewrite to the same address is to erase the entire block of 256 Kbytes and then write the new data. The writing of data to an erased address is relatively quick, on the order of 10 microseconds, while a block erase can take up to 1.5 million microseconds. The erasing of a block of flash memory locks up the entire flash memory chip for the duration of the erase, so care must be taken to only perform an erase before the system is held to its runtime schedule, or the erase must be performed by a background process while the foreground processes buffer their data as they wait for flash memory access.

## Case 1: Green Screen

### Introduction

As part of ongoing product improvements and feature additions, a flight data recorder was added to the software inside the primary flight display (PFD) software. During a subsequent release, additional data files were added to the system configuration. The additional files caused a reboot of this flight-critical system whenever the flight data recorder attempted to access the physical end of the file system.

#### **Technical Discussion**

The code for the main processor resides on 32 MB of high reliability flash memory. As previously discussed, the flash memory is addressed by physical blocks, and the chips chosen for this application are broken down into 128 blocks of 256 Kbytes each. Blocks are numbered from 0 to 127, and a block allocation scheme was chosen early on in the design process once the approximate size of difference components was determined. The memory layout is shown in the table below.

| Block Number  | Description                                                 |

|---------------|-------------------------------------------------------------|

| Block 0       | Header Block                                                |

| Block 1       | System Information Block                                    |

| Block 2       | Major fault block                                           |

| Block 3       | Pilot non-volatile data block ID A                          |

| Block 4       | Pilot non-volatile data block ID B                          |

| Blocks 5-19   | Application data blocks                                     |

| Block 20      | Base block for FAT table                                    |

| Blocks 21-127 | Texture (graphics) files, configuration data, and log files |

Table 1 PFD Flash Memory Layout

From **Table 1** above one can see that Block 20 is reserved for creating a rudimentary file system and blocks 21 through 127 are reserved for "files" such as graphical texture sheets,

configuration files, and data logs. The set of texture files that are loaded onto a unit are typically identical from release to release. To simplify the graphics drivers used in the product, all textures are moved from flash memory into video memory and statically stored in video memory so that dynamic loading of data would not be required. The list of textures and the sizes of the textures change only when additional textures are required because of the fixed amount of VRAM dedicated to hold textures. If a new texture is needed, some of the other textures would need their bit depths to be cut, or decals within each texture sheet would be moved to a new texture sheet to optimize the use of the fixed size texture sheets, replacing an empty texture with the new texture file to be fit into VRAM.

To prevent any errant textures from slipping into the product, all textures are check summed, and a master checksum of all texture files is calculated and displayed on a maintenance page to permit auditing of the conformity of all loaded software and data.

The manufacturing process loads all texture files in contiguous blocks starting at Block 21. In addition to the texture files, a configuration file is loaded as part of the manufacturing process that determines whether the system should enable a specific set of features related to autopilot integration. The remaining portion of flash memory is left blank after the manufacturing procedure.

The software inside the PFD records different data to each of three files that reside in the file area of blocks 21 through 127. Because the manufacturing process loads all texture and configuration data before any software is running on the main processor, any files created at run-time by the main processor must be created in the memory remaining after the manufacturing files are loaded. During the first power-up of the full system after manufacturing, the application software attempts to open the three log files used by the data recorder to fulfill

the recording requirements. The first two files are each 512 Kbytes (2 blocks), while the third file was initially sized to 1 megabyte (4 blocks).

Later in the development process a high level requirement indicated that 20 hours was the minimum recording time desired. The third file was resized to meet the new high-level requirement. The new number of blocks (84) allocated to the periodic data consumed all available remaining flash memory as calculated in the flash memory analysis.

The flash memory usage analysis relied on the assumption that the exact same files used in the analysis were present in flash memory prior to log file creation. The list of files from the analysis was compared with the list of files loaded on the PFD, and the lists matched exactly. In addition the checksum of the texture files matched the expected checksum, indicating the exact specified textures were properly loaded.

Tests for Credit (TFCs) were performed with conforming hardware and software as reported on the status page. The hardware was loaded by a copy of load media prepared by engineering to be used during TFC. The formal build procedure was run before testing began and after testing completed to ensure the software was properly archived and could be regenerated (see DO-178B, Section 8.3 – Software Conformity Review). After all testing was completed, the formal, complete build procedure was run again for all parts to be included in the shipping product, and again all software matched expected checksums. A new piece of load media was created to become the manufacturing gold master, and the master was released through the configuration management organization.

During manufacturing acceptance testing, the PFD was seen with random displays of an allgreen display. That green screen indicates a reboot of the main processor that controls the graphics. A system reboot completes in under a second, so visually catching a reboot requires patient attention. The screen is loaded with a green rectangle early in the boot sequence while texture files are moved from flash memory into VRAM for use by the graphics chip. A system reboot is a very serious issue that must be investigated until a cause is found, even if the event is only witnessed in one unit. Other manufacturing units were loaded from the same load media, and eventually all such units began rebooting randomly.

The PFD has a variety of mechanisms by which it could command a reboot of itself via software or via hardware. All software-commanded reboots log data to internal flash memory (Block 2, above) for diagnostic purposes. None of the units from manufacturing showed any data stored in the major fault block. Testing was performed on the offending units to ensure that the major fault logging was working, and the feature was confirmed to be active and functional. Once software-commanded reboots were ruled out, suspicion moved toward hardware-commanded reboots. The PFD's main processor has a companion supervisor processor that will reboot the main processor if active communication is lost between the two processors. When the timer expires the supervisor triggers a hardware reset by toggling the main processor reset line. To prevent such a reset, the main processor must "ping" the supervisor within the time period of the timer by writing a specific data value to a specific shared memory address that can be read by the supervisor. The main processor sends that ping in a periodic manner such that a ping is transmitted every major run cycle that completes in the time allowed. That internal time is measured by a precision timer interrupt running on the main processor.

One of the more useful pieces of information discovered during the subsequent investigation into the anomalous reboots was that the PFDs used by the engineering group during the TFCs were not afflicted by the same symptoms. As the units used during the TFCs were conformed to be identical to the manufacturing units, some suspicion was cast upon the manufacturing process. The key to understanding the root of the issue occurred when a "wall of shame" was

built to run several PFDs side by side on a tabletop to perform extended run-time tests. Two of the PFDs rebooted within seconds of each other, signifying that a timing related issue might be at work. By counting back from the exact time the units were loaded with fresh software and configuration data, it was determined that approximately 19 hours had passed between the initial power-on after first load and the observed reboots on each PFD. Once word reached the developers of a 19-hour period on the reboots, the search for the cause immediately focused on the data recorder. Within a matter of hours the cause had been determined.

The cause of the reboot was an attempt by the main processor to write a data record to an address that was not within the address bounds of the flash memory. **Table 2** below shows the overall PCI memory layout by address of the physical devices.

| Device            | Address    |

|-------------------|------------|

| Flash Memory Base | 0xF8000000 |

| PLX 9030 Base     | 0xFA000000 |

Table 2 Partial PFD Physical Memory Map

Recall that the flash memory was built as 128 blocks of 256 Kbytes. 128 Blocks x 256 Kbytes/Block x 1024 bytes/Kbytes = 0x2000000 bytes. Starting at the FLASH\_BASE address of 0xF8000000, one can see that the PLX9030 PCI bridge memory space was adjacent to the flash memory part at 0xFA000000. Any attempt to write at an address off the far end of the flash memory would result in an attempt to write random data into the PCI bridge device. Writing garbage into the PCI bridge caused the main processor to wait for an appropriate response from the flash memory controller, however the flash memory controller had not received a command and therefore the main processor waited in a loop, failing to ping the supervisor. The supervisor would wait for the timeout period then externally reset the main processor.

The proximal cause can almost always be traced to software because software is the final output of the development process and software is the only part of the development process that actually flies in the airplane. This case is no different.

### **Certification Discussion**

The defect traced to the software was that no software modules performed any checks as to the size of the files created or the addresses of any attempted reads or writes. An engineering analysis provided the maximum size of the data recorder file and the size was implemented as a constant. No low level requirement existed to document the expected behavior in the event of attempted flash reads or writes outside the address space of the part. The original flash driver was developed when only 30-35 flash blocks were in use, and the use of the entire flash device was not foreseen. Because the driver software was certified to DO-178B Level B, structural coverage objectives may have deterred the developer from adding additional branches to the code. Those additional conditions would need to be tested for both true and false cases, requirements would need updating, and tests would need to be written for a case that was not expected during normal or abnormal operation.

The high level requirement (PFD-REQ-14891) states, "The FDR shall be able to store at least 19 hours of flight data". The data logging rates specified in other high level requirements were analyzed to use of 84 blocks of flash memory. The implementation of that 84-block value was hard-coded in a macro, leaving it untraced to any requirement or design information. The logging-related low-level requirements described the timing mechanisms used to ensure periodic logging of data, while the flash driver low-level requirements described the memory layout in blocks with block and offset access. No comment or limitation is documented within the flash driver design or requirements information, and no device bounds checks were included in the source code.

The testing that traces to the high and low level requirements does verify that at least 19 hours of data are recorded, and those steps passed when run during the formal TFC.

As part of the engineering process improvement group, a new procedure was written to formalize the steps previously undertaken to create load media. Prior to this document, a single build master was responsible for creating the formal build of the released load media. A default load media image was stored in our source control system and engineers developed a procedure to be executed alongside the released software build procedures to create the released load media. When TFC completed, the newly drafted load media creation procedure was executed and the output of that procedure was provided to our configuration management organization for archival and distribution. It was this load disc that was provided to manufacturing along with a system traveler containing the checksums of all components to be loaded from that disc. Manufacturing executed the released load procedures on conforming hardware and signed off on the release of the disc as acceptable. Only days later did the problems appear in the manufacturing units.

The subsequent investigation determined the default load media stored in the source control system was never reviewed or compared against previously released load media. The stored media contained the flawed file. The source of the default load media in source control was the released load media from a release that preceded the current by two versions—not the current prototype load media used during engineering test for credit. The current release was not the first to use the entire amount of memory inside the flash part. The logging features were added in the release immediately preceding the current development effort. It was during that immediately preceding development effort that the size of a configuration file was changed from 1 byte to 0 bytes. That change allowed the system to record an additional 14 minutes of flight data by freeing up an additional flash block for use by the recorder. The default version of the

load media was created from two releases prior, (without the configuration file change); therefore the configuration file change was not included in the source control tree.

One of the shortcomings of DO-178B and its cross-references is the lack of any guidance about being able to manufacture a production version of the software and hardware together. The development company is free to determine how to best produce the equipment in mass quantities while maintaining compliance with the conformity documentation provided as part of the original approval process. In this case the approved software parts all identically matched their expected checksums, but still the error reached the manufacturing stage.

The specific process defect that caused the offending behavior was the incorrect creation of load media for manufacturing. DO-178 Section 11.4 and our Software Configuration Management Plan (SCMP) focus heavily on the control of source code and executable object code, but fail to mention associated utilities required to load the approved software onto the hardware.

Section 7.2.8 of DO-178B, Software Load Control, only discusses guidance regarding executable object code. The omission of databases, graphical textures, and configuration data are glaring omissions. It's possible that additional guidance in this section regarding the conformity of the load media used in both verification and manufacturing may have prevented this defect from reaching the post-TFC state. Section 8.3, Software Conformity Review, requires that approved/released software be loaded via released instructions, but again, there is no mention of the configuration data and tools associated with the executable object code. A single file with a single character difference (empty vs. a "1" character) caused a block of memory to be allocated for a file that should have only existed in the file allocation table (FAT). That extra data caused the properly sized data recorder file to run off the end of the flash part. When the software attempted to write to that address every 19+ hours, the supervisor processor would

reboot the main processor, leaving no stack trace or hint as to the source of the problem.

Complex and parameterized systems rely on data to operate properly, and the lack of control on such associated data seems to be an area that current guidance neglects.

**Recommendation:** In addition to executable object code, all utilities and data files used to load and configure the system should be under the strictest control and subject to review processes.

This defect in the load media is not a new problem. A similar mistake was made in the Titan IV B/Centaur TC-14/Milstar-3 Accident. A roll filter constant was mistyped as -0.1992476 instead of -1.992476 when loading the satellite launcher inertial measurement system. The result was a loss of roll control of the satellite launcher and eventual loss of the Milstar satellite (Pavlovich, 1999).