## MASSACHUSETTS INSTITUTE OF TECHNOLOGY ARTIFICIAL INTELLIGENCE LABORATORY

A.I. Technical Report No. 1545

June, 1995

## Thread Scheduling Mechanisms for Multiple-Context Parallel Processors

## James Alexander Stuart Fiske

stuart@ai.mit.edu This publication can be retrieved by anonymous ftp to publications.ai.mit.edu.

Copyright © Massachusetts Institute of Technology, 1995

This report describes research done at the Artificial Intelligence Laboratory of the Massachusetts Institute of Technology. This research was supported by the Advanced Research Projects Agency and monitored by the Air Force Electronic Systems Division under contract number F19628-92-C-0045.

## Thread Scheduling Mechanisms for Multiple-Context Parallel Processors

by

James Alexander Stuart Fiske Submitted to the Department of Electrical Engineering and Computer Science on May 26, 1995, in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

Scheduling tasks to efficiently use the available processor resources is crucial to minimizing the runtime of applications on shared-memory parallel processors. One factor that contributes to poor processor utilization is the idle time caused by long latency operations, such as remote memory references or processor synchronization operations. One way of tolerating this latency is to use a processor with multiple hardware contexts that can rapidly switch to executing another thread of computation whenever a long latency operation occurs, thus increasing processor utilization by overlapping computation with communication. Although multiple contexts are effective for tolerating latency, this effectiveness can be limited by memory and network bandwidth, by cache interference effects among the multiple contexts, and by critical tasks sharing processor resources with less critical tasks. This thesis presents techniques that increase the effectiveness of multiple contexts by intelligently scheduling threads to make more efficient use of processor pipeline, bandwidth, and cache resources.

This thesis proposes *thread prioritization* as a fundamental mechanism for directing the thread schedule on a multiple-context processor. A priority is assigned to each thread either statically or dynamically and is used by the thread scheduler to decide which threads to load in the contexts, and to decide which context to switch to on a context switch. We develop a multiple-context model that integrates both cache and network effects, and shows how thread prioritization can both maintain high processor utilization, and limit increases in critical path runtime caused by multithreading. The model also shows that in order to be effective in bandwidth limited applications, thread prioritization must be extended to prioritize memory requests. We show how simple hardware can prioritize the running of threads in the multiple contexts, and the issuing of requests to both the local memory and the network.

Simulation experiments show how thread prioritization is used in a variety of applications. Thread prioritization can improve the performance of synchronization primitives by minimizing the number of processor cycles wasted in spinning and devoting more cycles to critical threads. Thread prioritization can be used in combination with other techniques to improve cache performance and minimize cache interference between different working sets in the cache. For applications that are critical path limited, thread prioritization can improve performance by allowing processor resources to be devoted preferentially to critical threads. These experimental results show that thread prioritization is a mechanism that can be used to implement a wide range of scheduling policies.

Thesis Supervisor: William J. Dally

Title: Associate Professor of Electrical Engineering and Computer Science

#### Acknowledgments

Now that this thesis is finally coming to an end, there are many people that I would like to thank wholeheartedly for the help and support they provided me with along the way.

First of all, thanks to my research advisor Bill Dally for providing the knowledge, guidance, encouragement, and resources that were necessary to complete this work. Miraculously he succeeded in convincing me come back to MIT after my world travels, although he had the advantage that my memory had faded somewhat after a year and a half away. I would also like to thank my readers Charles Leiserson and Bill Weihl for their insightful and helpful suggestions on the various proposals and thesis drafts I sent their way.

The great people of Tech Square that I have had the privilege to meet and know greatly enriched my ordeal. The members of the CVA group all deserve my undying gratitude, as they patiently listened to my countless group meeting talks on various thread scheduling topics, and only occasionally nodded off. Rich Lethin, my friend and office mate of many years, gave me valuable support and council, read many of my thesis chapter drafts, set me up with all sorts of great job contacts, and lent me his car whenever some major system on it was about to collapse. Steve Keckler always had a good bad joke ready and waiting for me, and taught me the true meaning of the word dedication as he worked on his various sailboat projects. Kathy Knobe gave me good advice and encouragement, and always offered insightful comments about the various random scribbles I asked her to read. Peter and Julia Nuth were good friends, and provided amusing stories from the West Coast. John Keen gave many interesting talks on ephemeral logging and related topics, and was just generally a very good-hearted guy. Eric MacDonald gave me the chance to share an office with the star of the MIT cable network Star Trek phone in show. Duke Xanthopolous was always around late at night and was always willing to take a break and exchange some good natured verbal abuse. Larry Dennison provided a great example of how hard I should be working. Marco Fillo showed me how not to agonize over job offers. Michael Noakes gave me many lifts to hockey practice, and was full of insightful skepticism. Andrew Chang always kept things up and running, and was always interested in how things were going. Lisa Kozsdiy always found a way to fit me into Bill's Tuesday calendar. Debby Wallach deserves my thanks for always knowing how to do esoteric things on the computer system, and for clearing up lots of disk space when she finished her Master's thesis so I had space to do my work. Fred Chong, Ken MacKenzie, and Kirk Johnson regularly exchanged good hard hockey checks with me over the years. I shared regular talks and good laughs at Dilbert cartoons with John Kubiatowicz and Don Yeung at the coffee machine. Jim O'Toole played tennis with me regularly before we both got too busy finishing our theses. Ellen Spertus foisted off her wooden cow on me, one with a big painted smile, allowing me to drive my roommates crazy by keeping it in our living room. Thanks to the many other past and present inhabitants of Tech Square that have made this a truly colorful and fun place to be including Whay Lee. Waldemar Horwat, Nick Carter, Gino Maa, Silvina Hanono, Russ Tessier, Anne McCarthy, David Kranz, Tom Simon, and John Nguyen just to name a few.

Amazingly enough I did have some friends OUTSIDE of the Tech Square environment. Mark Wilkinson and Shawn Daly were always willing to go for a beer and tear up the town. My roommates Marilyn Feldmeier and Taylor Galyean were great company, and great cooks. My roommate Mike Drumheller allowed me to put aside any notion that I might be going deaf by treating me to his impressive operatic voice periodically. Kati Flagg deserves my thanks for her faithful phone calls and inquiries about when I was going to graduate. I hope that she does not require treatment for shock when she hears I actually have. Brian Totty provided regular amusing E-mail, and I am hoping we will get together for a beer someday if he ever gets out of central Anatolia where I last left him. Carlos Noack, my long departed Colombian yogurthead friend from the early MIT days, continued to provide encouragement by regular correspondence.

A very big thank you goes to my special friend Adrienne, who has so patiently put up with me through the worst of the thesis and job search stress. She has provided a great incentive for me to lead some semblance of a normal life, and for me to do all sorts of fun things: biking 100 miles in one day down to Cape Cod, spending 8 hours in a car on trip to Washington D.C. with her mom, her mom's cat, and her Hungarian cousin, charging down black diamond mogul ski runs after not skiing for two years, and hiking up Mount Monadnock in gale force winds. Life just would not be much fun without her.

Finally, a special thanks to my entire family, especially my parents. Without their encouragement, support, and emphasis on education, I would probably never have come to MIT at all, let alone got through. I am thankful also that Dad will have to find a new way to greet me since "Are you almost done?" will no longer be appropriate. "Have you found a job?" has a nice ring to it I think — at least for a little while.

## Contents

| 1 | Intr | oductio | on                                              | <b>2</b> 1 |

|---|------|---------|-------------------------------------------------|------------|

|   | 1.1  | The Pr  | oblem                                           | 21         |

|   |      | 1.1.1   | The Latency Tolerance Problem                   | 21         |

|   |      | 1.1.2   | Using Multiple Contexts to Tolerate Latency     | 22         |

|   |      | 1.1.3   | Problems with Multiple-Context Processors       | 23         |

|   | 1.2  | Thread  | Prioritization                                  | 25         |

|   | 1.3  | Contrib | butions                                         | 26         |

|   | 1.4  | Outline | e and Summary of the Thesis                     | 27         |

| 2 | Bac  | kgroun  | d                                               | 29         |

|   | 2.1  | Thread  | Scheduling                                      | 30         |

|   |      | 2.1.1   | An Application Model                            | 30         |

|   |      | 2.1.2   | The Thread Scheduling Problem                   | 30         |

|   | 2.2  | Thread  | Scheduling Strategies                           | 32         |

|   |      | 2.2.1   | Temporal Scheduling Strategies                  | 33         |

|   |      | 2.2.2   | Thread Placement Strategies                     | 35         |

|   | 2.3  | Thread  | Scheduling Mechanisms                           | 37         |

|   |      | 2.3.1   | Hardware Scheduling Mechanisms                  | 37         |

|   |      | 2.3.2   | Software Scheduling Mechanisms                  | 39         |

|   | 2.4  | Multitł | nreading and other Latency Tolerance Techniques | 40         |

|   |     | 2.4.1  | Multithreading 4                                                            | 0        |

|---|-----|--------|-----------------------------------------------------------------------------|----------|

|   |     | 2.4.2  | Multiple-Context Processors                                                 | 0        |

|   |     | 2.4.3  | Other Latency Tolerance Techniques                                          | 1        |

|   |     | 2.4.4  | Comparison of Techniques                                                    | 3        |

|   | 2.5 | Summ   | ary                                                                         | 3        |

| 3 | Thr | ead P  | rioritization 4                                                             | 5        |

|   | 3.1 | Threa  | d Prioritization                                                            | 6        |

|   |     | 3.1.1  | Software and Hardware Priority Thread Scheduling                            | 6        |

|   |     | 3.1.2  | Assigning Priorities: Deadlock and Fairness                                 | 7        |

|   |     | 3.1.3  | Higher Level Schedulers                                                     | 8        |

|   | 3.2 | Effect | of Multiple Contexts on the Critical Path                                   | 8        |

|   |     | 3.2.1  | Total Work and the Critical Path                                            | 9        |

|   |     | 3.2.2  | Previous Models                                                             | 9        |

|   |     | 3.2.3  | Metrics and Parameters                                                      | 0        |

|   |     | 3.2.4  | Basic Model                                                                 | 1        |

|   |     | 3.2.5  | Spin-waiting Synchronization                                                | <b>2</b> |

|   |     | 3.2.6  | Memory Bandwidth Effects                                                    | 7        |

|   |     | 3.2.7  | Network Bandwidth Effects                                                   | 60       |

|   | 3.3 | Netwo  | ork and Cache Effects                                                       | 51       |

|   |     | 3.3.1  | Network Model                                                               | 51       |

|   |     | 3.3.2  | Cache Model                                                                 | 3        |

|   |     | 3.3.3  | Complete Model                                                              | 64       |

|   |     | 3.3.4  | Discussion                                                                  | 5        |

|   |     | 3.3.5  | Cache and Network Effects with Spin-Waiting and with Limited Band-<br>width | 57       |

|   | 3.4 | Threa  | d Prioritization in the Multithreaded Model                                 | 8        |

|   |     | 3.4.1  | Prioritizing Threads in the Basic Model                                     | 8        |

|                   | 3.4.2                                                                       | Prioritizing Threads for Spin-Waiting Threads                                                                                                   | 69                                                     |

|-------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|                   | 3.4.3                                                                       | Prioritizing Bandwidth Utilization                                                                                                              | 71                                                     |

|                   | 3.4.4                                                                       | Prioritizing Threads in the Complete Model                                                                                                      | 73                                                     |

|                   | 3.4.5                                                                       | Effect of Prioritization on the Critical Thread Runtime                                                                                         | 77                                                     |

| 3.5               | Limits                                                                      | of the Model                                                                                                                                    | 79                                                     |

| 3.6               | Conclu                                                                      | asions                                                                                                                                          | 80                                                     |

| Imp               | lemen                                                                       | tation                                                                                                                                          | 82                                                     |

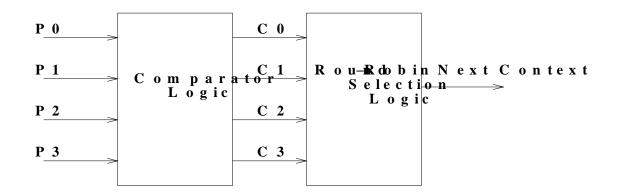

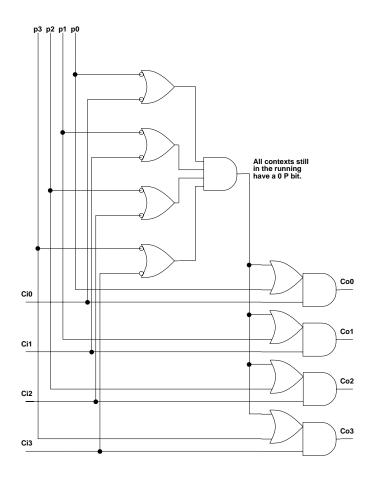

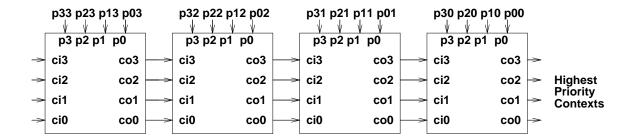

| 4.1               | Conte                                                                       | xt Prioritization                                                                                                                               | 83                                                     |

|                   | 4.1.1                                                                       | Hardware                                                                                                                                        | 83                                                     |

|                   | 4.1.2                                                                       | Software                                                                                                                                        | 86                                                     |

|                   | 4.1.3                                                                       | Hardware/Software                                                                                                                               | 86                                                     |

| 4.2               | Memo                                                                        | ry System Prioritization                                                                                                                        | 88                                                     |

|                   | 4.2.1                                                                       | Transaction Buffer Implementation                                                                                                               | 89                                                     |

|                   | 4.2.2                                                                       | Thread Stalling                                                                                                                                 | 92                                                     |

|                   | 4.2.3                                                                       | Memory Request Prioritization                                                                                                                   | 93                                                     |

|                   | 4.2.4                                                                       | Preemptive Scheduling                                                                                                                           | 94                                                     |

| 4.3               | Unloa                                                                       | ded Thread Prioritization                                                                                                                       | 94                                                     |

| 4.4               | Summ                                                                        | ary                                                                                                                                             | 95                                                     |

|                   |                                                                             |                                                                                                                                                 |                                                        |

| Sim               | ulation                                                                     | n Parameters and Environment                                                                                                                    | 96                                                     |

| <b>Sim</b><br>5.1 |                                                                             | n <b>Parameters and Environment</b><br>n Parameters                                                                                             | <b>96</b><br>97                                        |

|                   |                                                                             |                                                                                                                                                 |                                                        |

|                   | Syster                                                                      | n Parameters                                                                                                                                    | 97                                                     |

|                   | Syster<br>5.1.1                                                             | n Parameters                                                                                                                                    | 97<br>98                                               |

|                   | Syster<br>5.1.1<br>5.1.2<br>5.1.3                                           | n Parameters                                                                                                                                    | 97<br>98<br>99                                         |

| 5.1               | Syster<br>5.1.1<br>5.1.2<br>5.1.3                                           | n Parameters                                                                                                                                    | 97<br>98<br>99<br>101                                  |

|                   | <ul> <li>3.6</li> <li>Imp</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | 3.4.4<br>3.4.5<br>3.5 Limits<br>3.6 Conclu<br>1mplemen<br>4.1 Conter<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2 Memo<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | 3.4.4       Prioritizing Threads in the Complete Model |

| $\mathbf{Syn}$ | chronization Sched                                                                                                                              | duling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1            | Synchronization Sch                                                                                                                             | neduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.1.1 Synchronizat                                                                                                                              | tion Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 6.1.2 Synchronizat                                                                                                                              | tion Scheduling Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.2            | Test-and-Test_and_S                                                                                                                             | Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

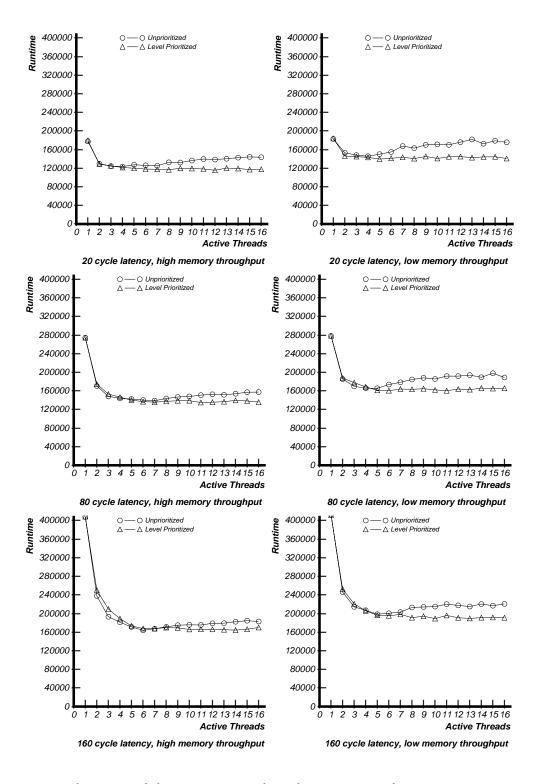

|                | 6.2.1 Results                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.3            | Barrier Synchroniza                                                                                                                             | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

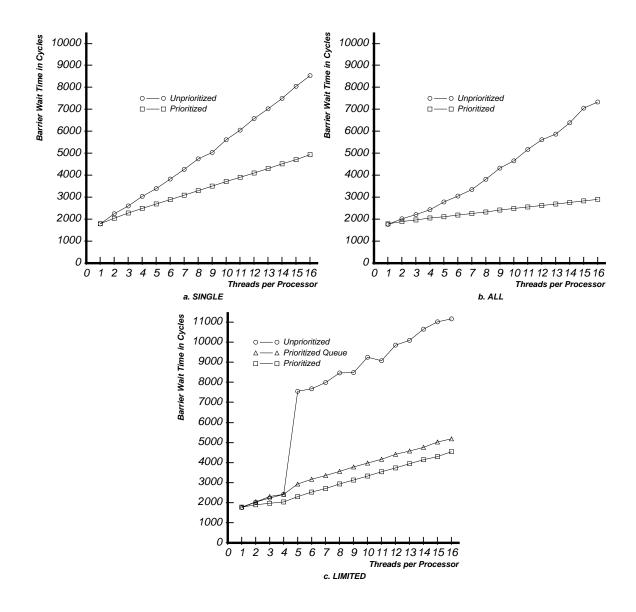

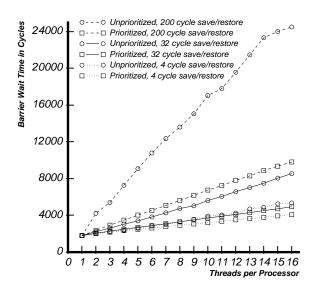

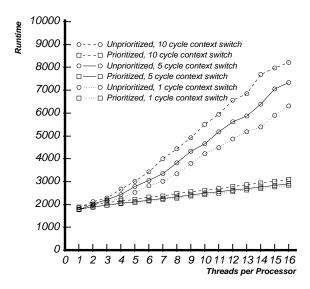

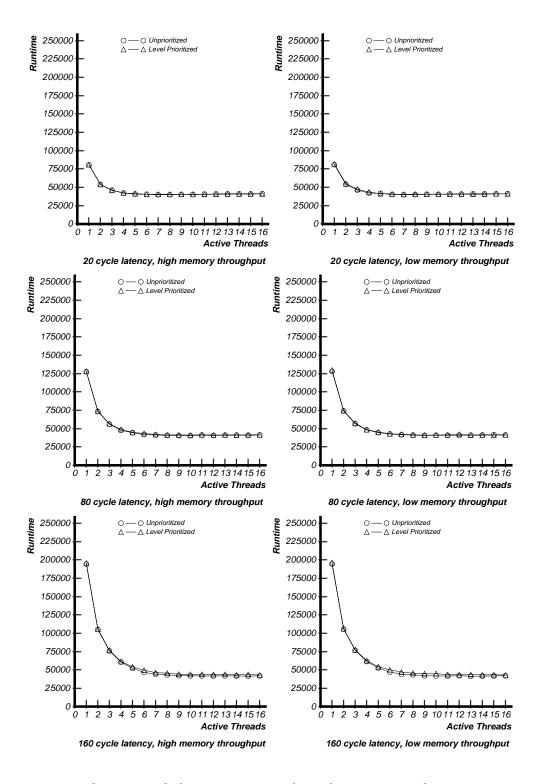

|                | 6.3.1 Results                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.4            | Queue Locks                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

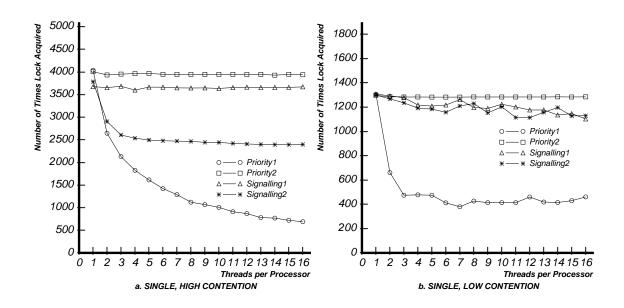

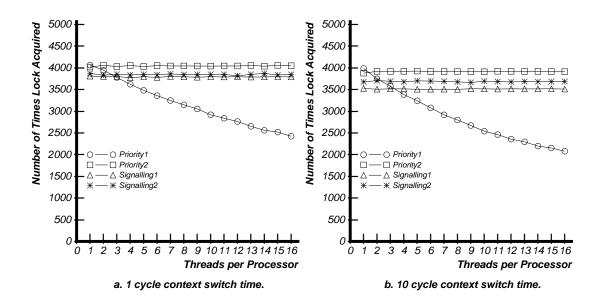

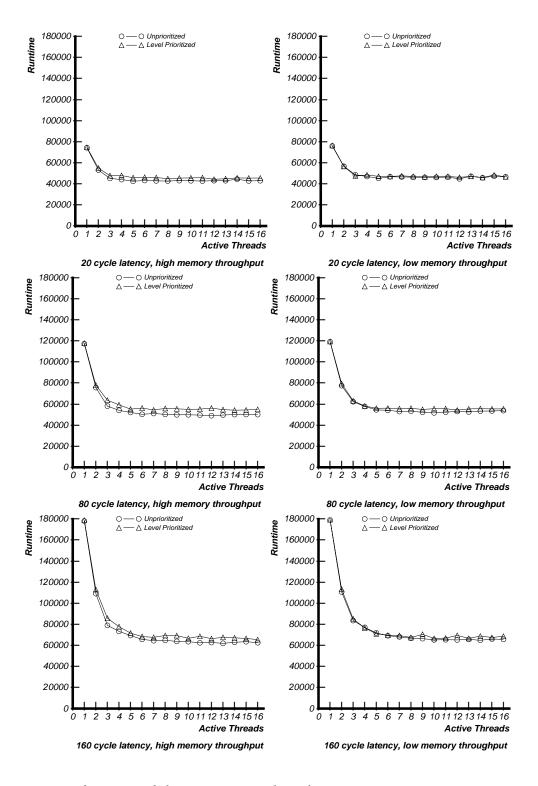

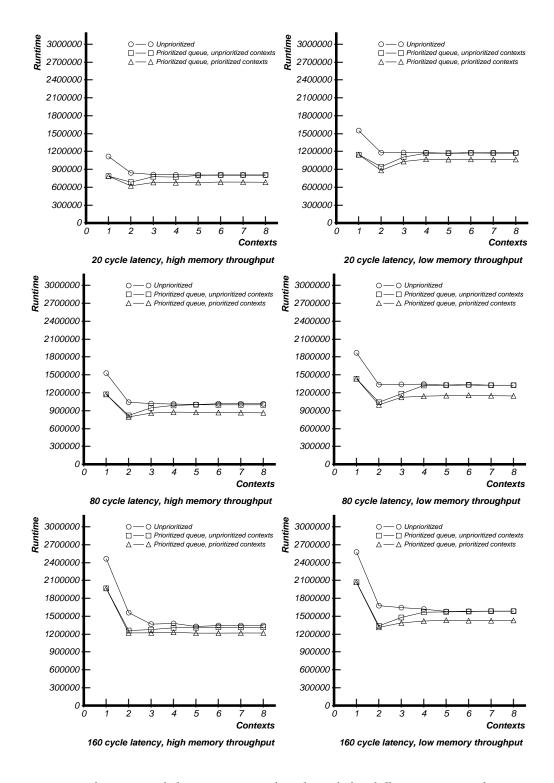

|                | 6.4.1 Results                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.5            | Summary                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Sah            | duling for Cood (                                                                                                                               | Casha Dayfaymanaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 <b>2</b> 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | 0                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.1            | Data Sharing                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 7.1.1 Blocked Algo                                                                                                                              | orithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 7.1.2 Reuse Patter                                                                                                                              | rns in Blocked Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 7.1.3 Loop Distrib                                                                                                                              | oution to Achieve Positive Cache Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 7.1.4 Data Prefetc                                                                                                                              | ching and Data Pipelining Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.2            | Favored Thread Exe                                                                                                                              | ecution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.3            | Experiments                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

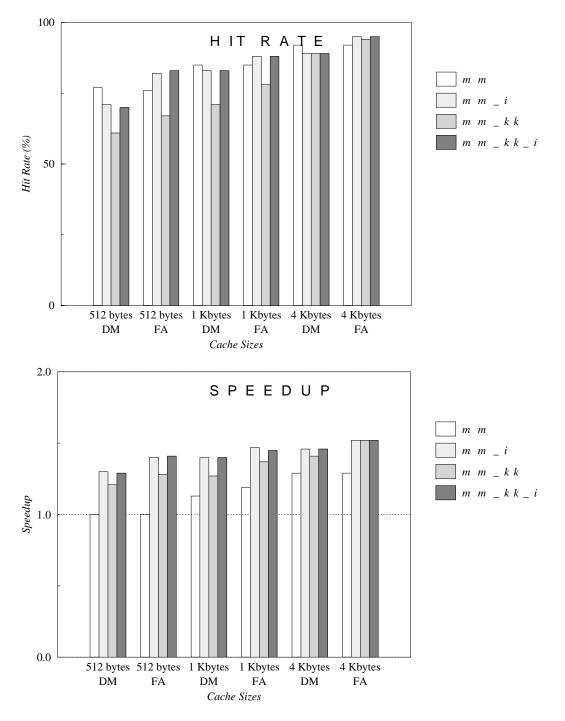

|                | 7.3.1 Matrix Multi                                                                                                                              | iply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

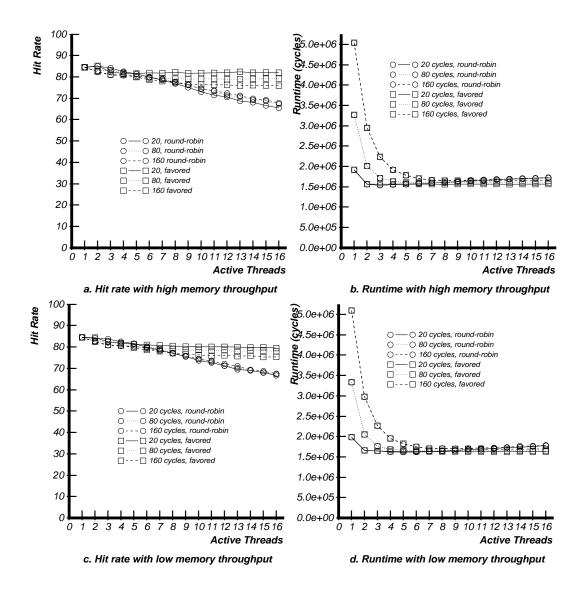

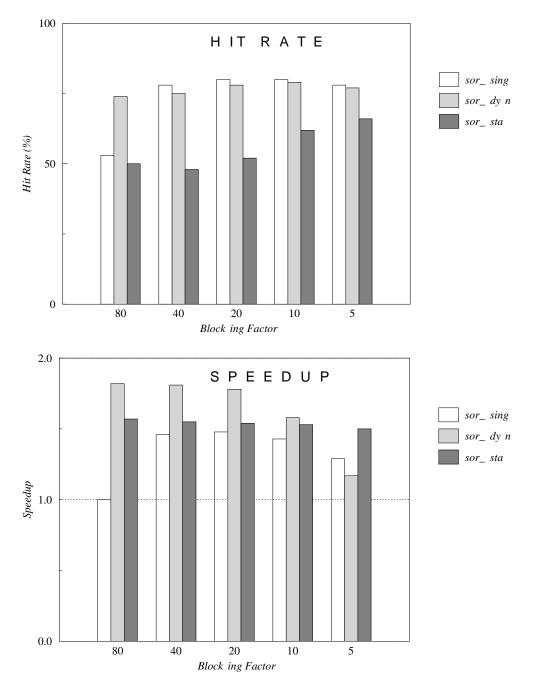

|                | 7.3.2 SOR                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

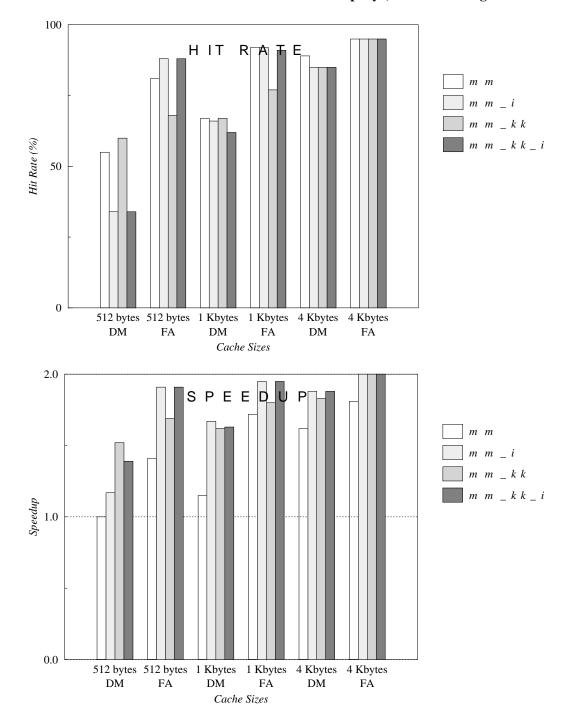

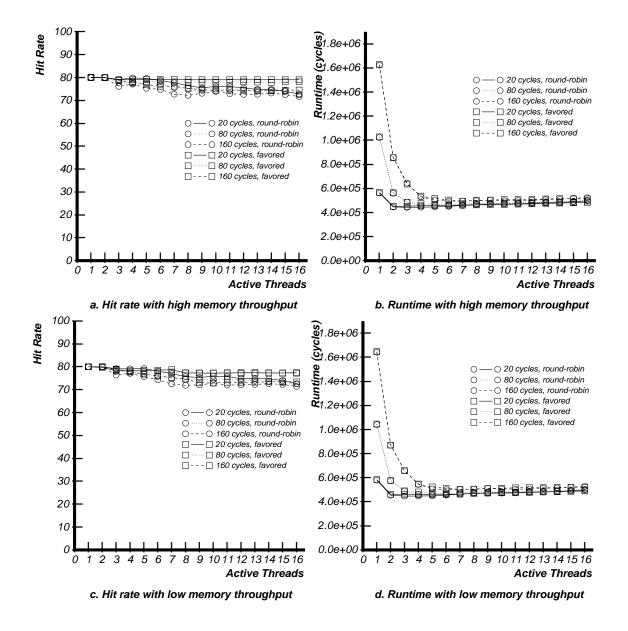

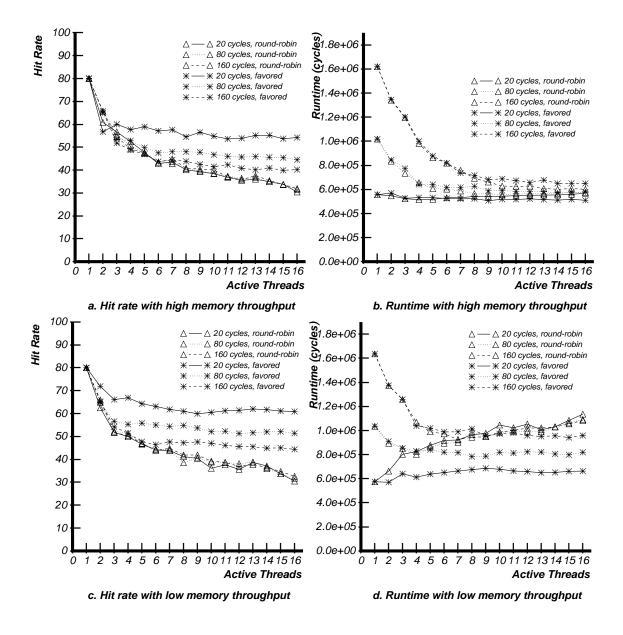

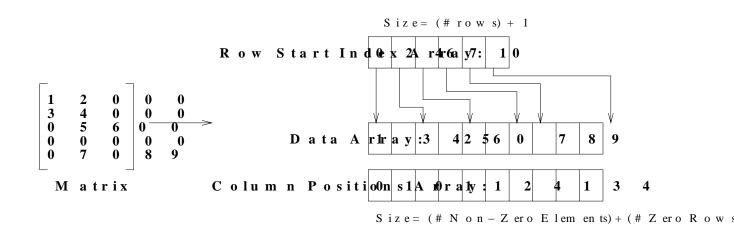

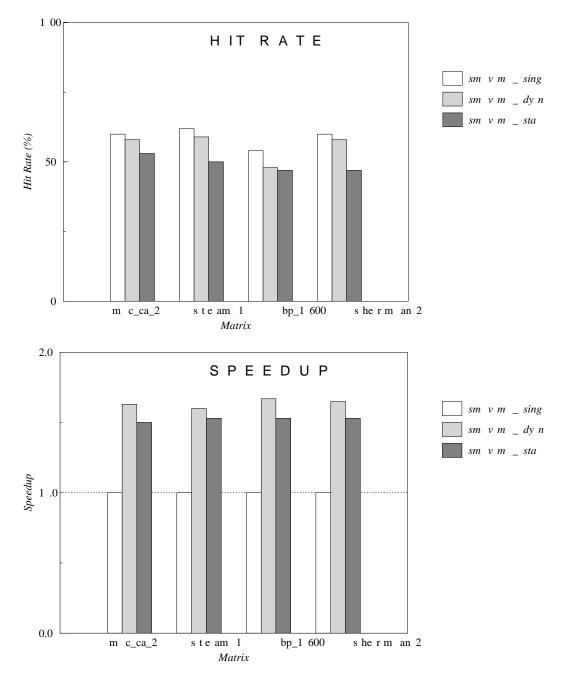

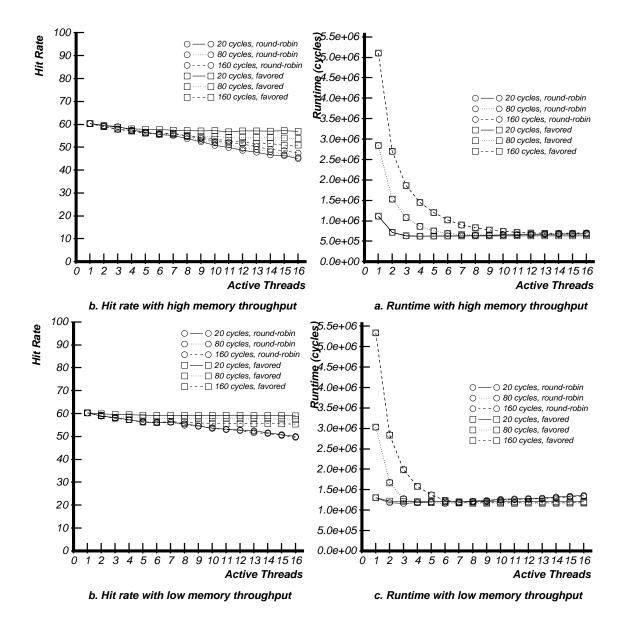

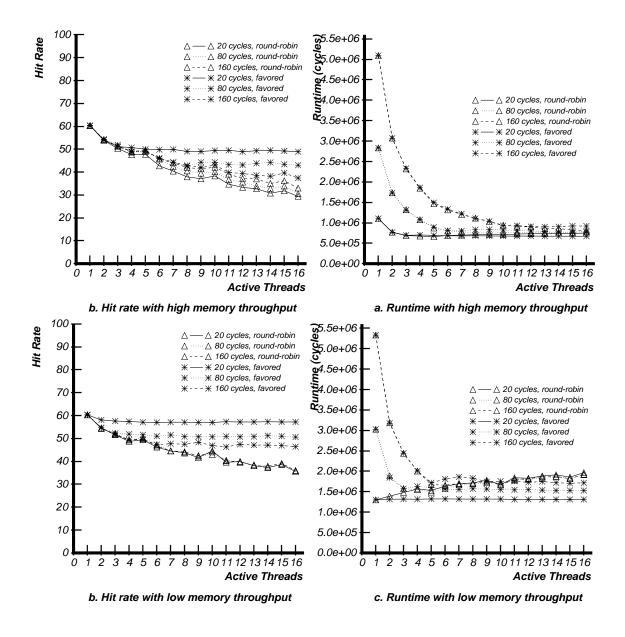

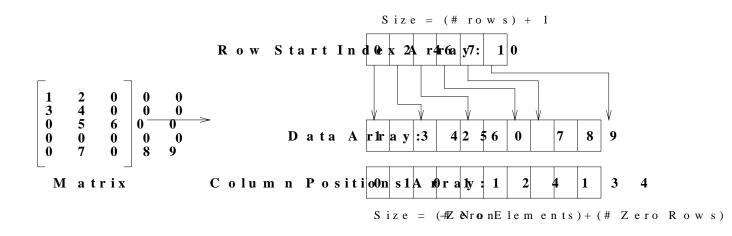

|                | 7.3.3 Sparse-Matri                                                                                                                              | ix Vector Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.4            | Summary                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Crit           | ical Path Scheduli                                                                                                                              | ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Schell</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ul> | <ul> <li>6.1 Synchronization Sch<br/>6.1.1 Synchronizat<br/>6.1.2 Synchronizat<br/>6.2 Test-and-Test_and_S<br/>6.2.1 Results</li> <li>6.3 Barrier Synchroniza<br/>6.3.1 Results</li> <li>6.4 Queue Locks<br/>6.4.1 Results</li> <li>6.5 Summary</li> <li>6.5 Summary</li> <li>7.1 Data Sharing</li> <li>7.1.1 Blocked Algo<br/>7.1.2 Reuse Patter<br/>7.1.3 Loop Distrib<br/>7.1.4 Data Prefeto</li> <li>7.2 Favored Thread Exe<br/>7.3 Experiments<br/>7.3.1 Matrix Mult<br/>7.3.2 SOR<br/>7.3.3 Sparse-Matr</li> <li>7.4 Summary</li> <li>8.1 Benchmarks</li> </ul> | 6.1.1       Synchronization Scenarios         6.1.2       Synchronization Scheduling Strategies         6.2       Test-and_Test_and_Set         6.3       Barrier Synchronization         6.3.1       Results         6.3       Barrier Synchronization         6.3.1       Results         6.4       Queue Locks         6.4.1       Results         6.5       Summary         Scheduling for Good Cache Performance         7.1       Data Sharing         7.1.1       Blocked Algorithms         7.1.2       Reuse Patterns in Blocked Algorithms         7.1.3       Loop Distribution to Achieve Positive Cache Effects         7.1.4       Data Prefetching and Data Pipelining Effects         7.2       Favored Thread Execution         7.3       Experiments         7.3.1       Matrix Multiply         7.3.2       SOR         7.3.3       Sparse-Matrix Vector Multiply         7.4       Summary         Critical Path Scheduling         8.1       Benchmarks |

|    |      | 8.1.2    | Sparse Triangular Solve                | 159 |

|----|------|----------|----------------------------------------|-----|

|    |      | 8.1.3    | Dense LUD                              | 161 |

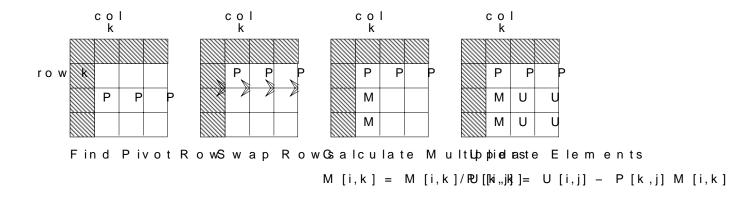

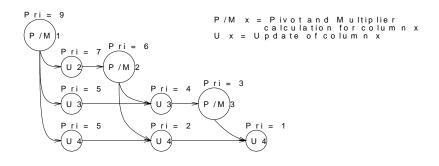

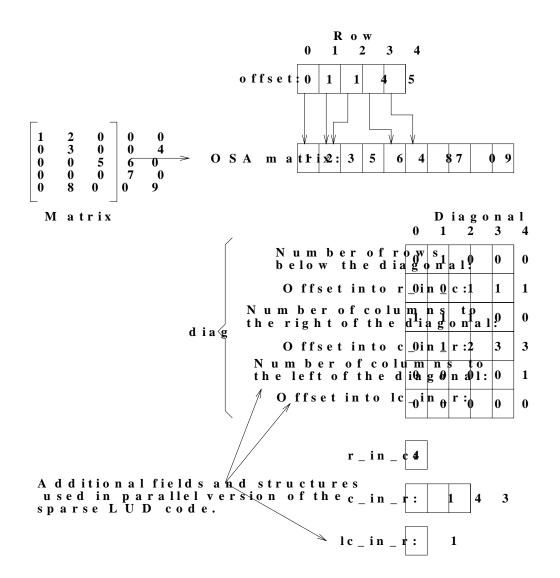

|    |      | 8.1.4    | Sparse LUD                             | 163 |

|    | 8.2  | Results  |                                        | 167 |

|    |      | 8.2.1    | Dense Triangular Solve                 | 167 |

|    |      | 8.2.2    | Sparse Triangular Solve                | 167 |

|    |      | 8.2.3    | Dense LUD                              | 173 |

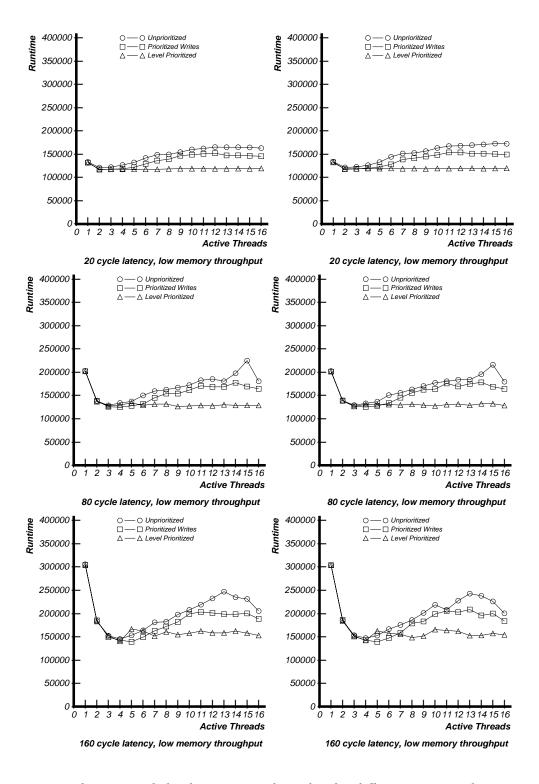

|    |      | 8.2.4    | Sparse LUD                             | 175 |

|    | 8.3  | Summa    | ary                                    | 179 |

| 9  | Red  | ucing \$ | Software Scheduling Overhead           | 181 |

|    | 9.1  | Messag   | ge Handler Scheduling                  | 182 |

|    | 9.2  | Genera   | l Thread Scheduling                    | 183 |

|    | 9.3  | Using 1  | Multiple Contexts                      | 185 |

|    |      | 9.3.1    | Radix Sort Example                     | 186 |

|    |      | 9.3.2    | General Problem Characteristics        | 189 |

|    | 9.4  | Summa    | ary                                    | 189 |

| 10 | Con  | clusion  | L                                      | 191 |

|    | 10.1 | Summa    | ary                                    | 191 |

|    | 10.2 | Future   | Work                                   | 193 |

|    |      | 10.2.1   | Applications                           | 193 |

|    |      | 10.2.2   | Automated Thread Prioritizing          | 193 |

|    |      | 10.2.3   | Other Uses of Thread Prioritization    | 194 |

|    |      | 10.2.4   | Combining Latency Tolerance Strategies | 194 |

|    | 10.3 | Epilogu  | 1e                                     | 195 |

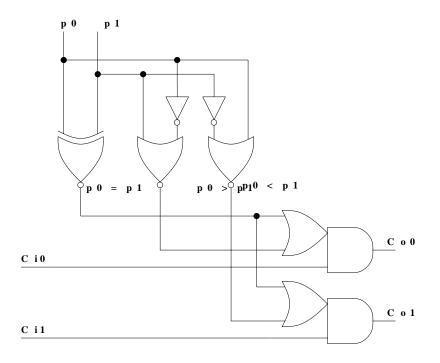

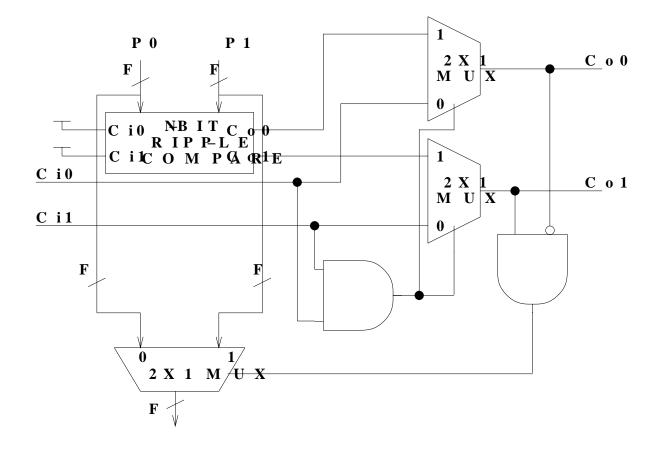

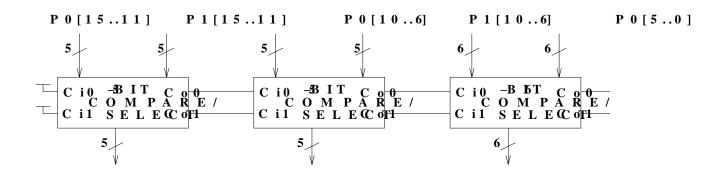

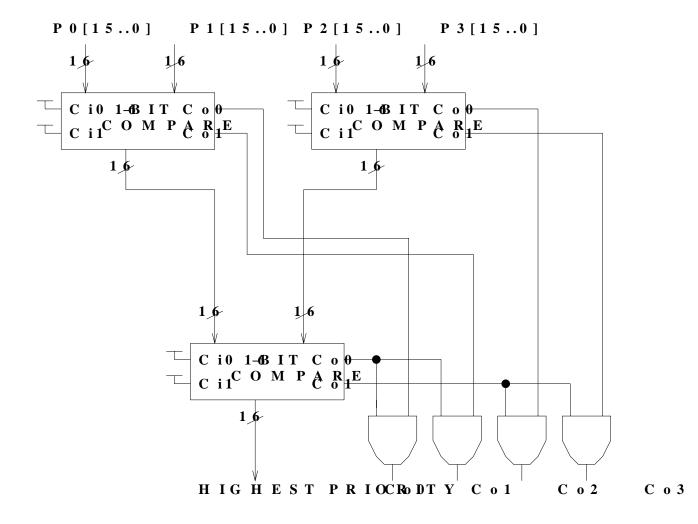

| A  | A F  | ast Mu   | lti-Way Comparator                     | 196 |

CONTENTS

# List of Figures

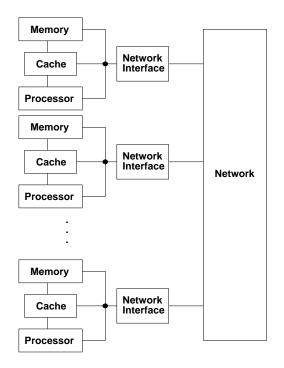

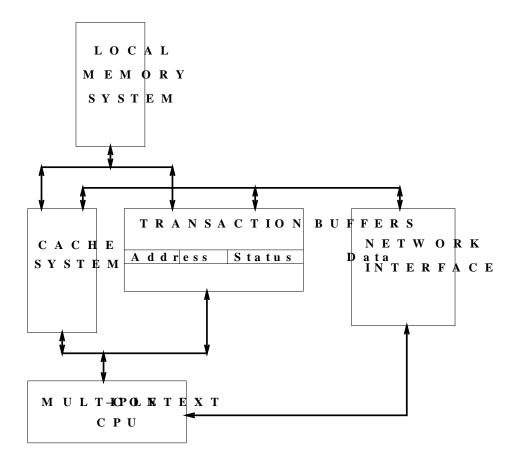

| 1.1 | General multiprocessor system configuration.                                                                                                                                                                                                                                                                                                                                               | 22 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

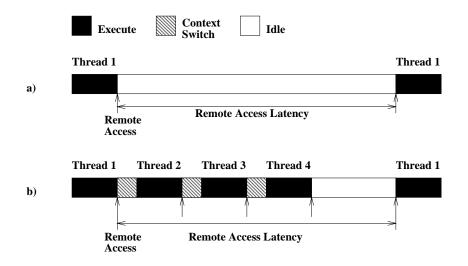

| 1.2 | Effect of long latency operations. a. Without multithreading long idle periods are spent waiting for long latency operations to complete. b. With multithreading the processor can context switch and overlap computation with communication.                                                                                                                                              | 23 |

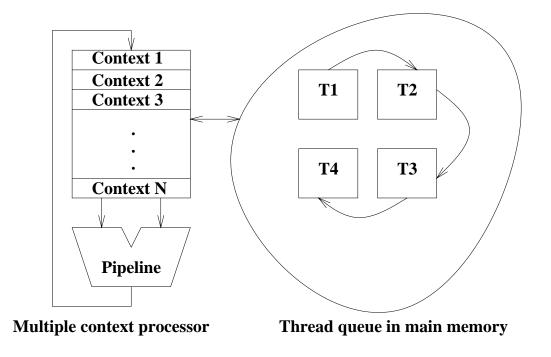

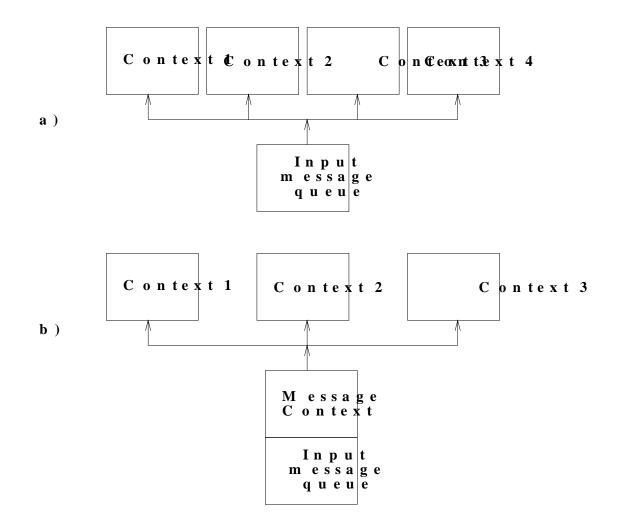

| 1.3 | Multiple-context processor with N contexts. Loaded threads have their state<br>loaded in one of the hardware contexts. Unloaded threads wait to be acti-<br>vated in a thread scheduling queue in memory.                                                                                                                                                                                  | 24 |

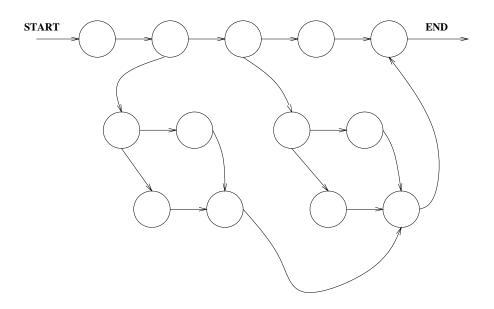

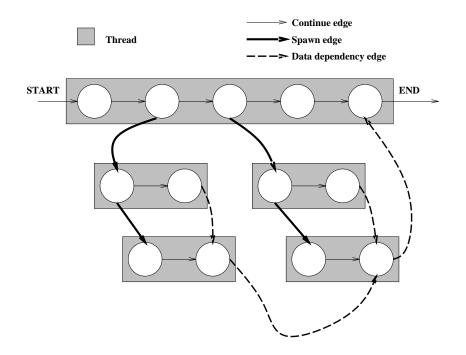

| 2.1 | General DAG                                                                                                                                                                                                                                                                                                                                                                                | 31 |

| 2.2 | General DAG viewed as a set of threads                                                                                                                                                                                                                                                                                                                                                     | 31 |

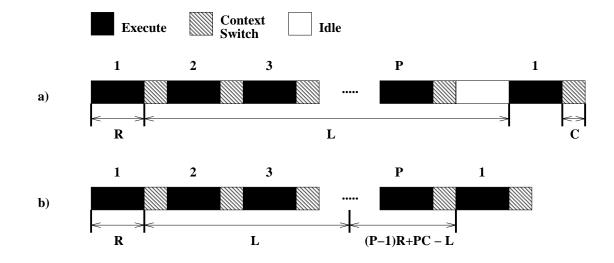

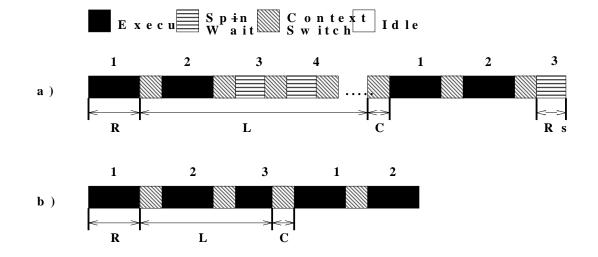

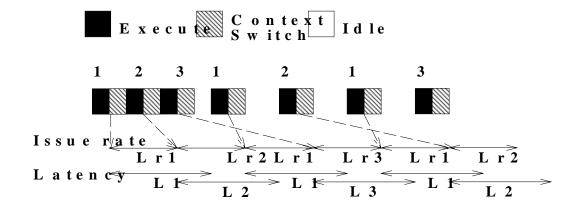

| 3.1 | Multithreading using P contexts. a. Communication bound $((P-1)R+PC < L)$ . b. Computation bound $((P-1)R+PC > L)$ .                                                                                                                                                                                                                                                                       | 53 |

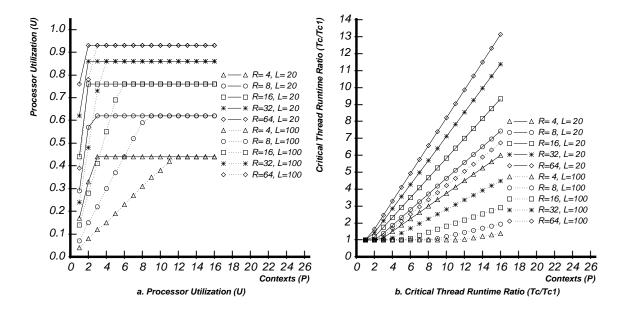

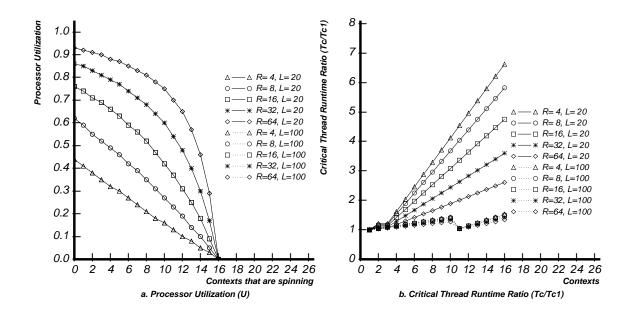

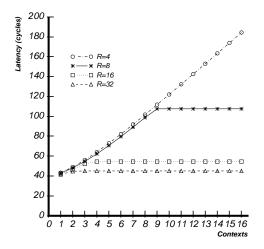

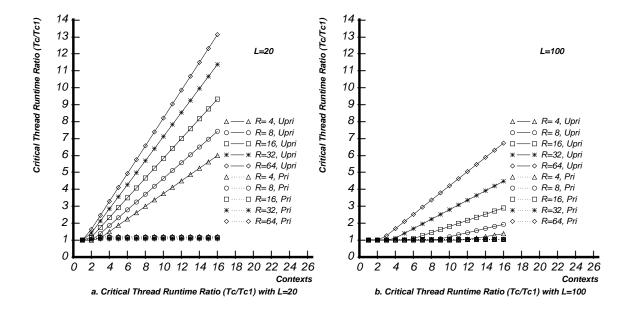

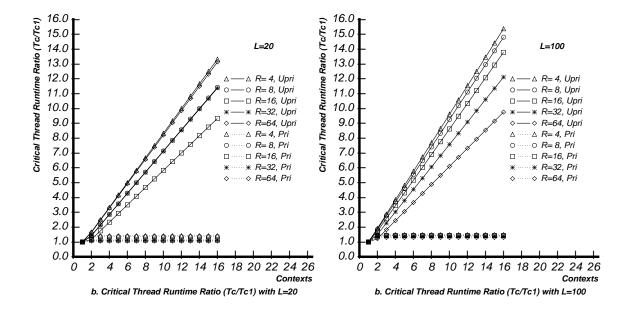

| 3.2 | $U$ and $T_c/T_{c1}$ for different values of R (4, 8, 16, 32) and L (20, 100)                                                                                                                                                                                                                                                                                                              | 53 |

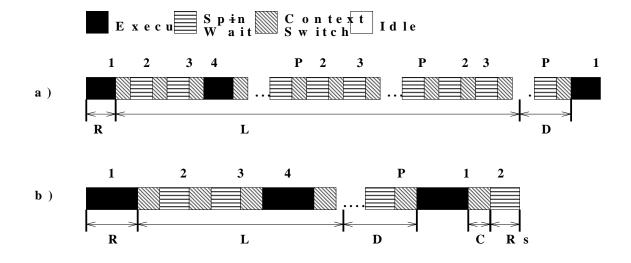

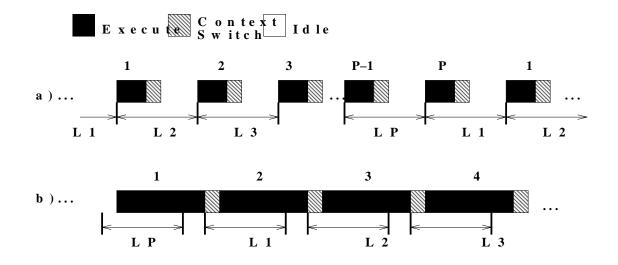

| 3.3 | Multithreading assuming some threads are spin-waiting. D is the extra time added to the execution of a critical thread. a. Communication bound $((P - P_s - 1)R + P_sR_s + PC < L)$ . b. Computation bound $((P - P_s - 1)R + P_sR_s + PC > L)$ .                                                                                                                                          | 54 |

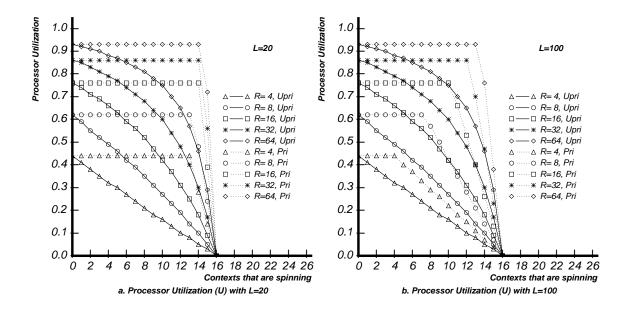

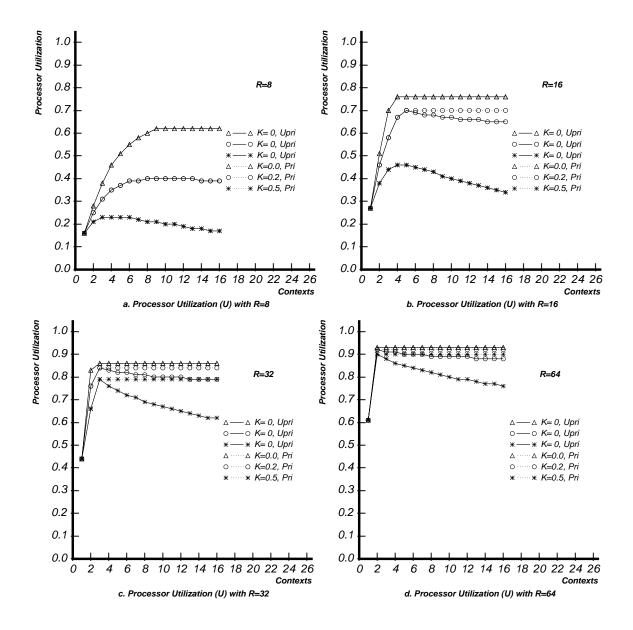

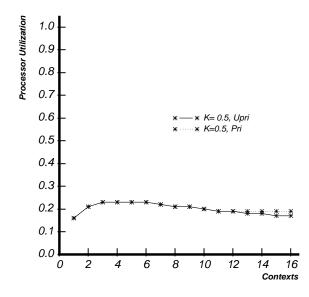

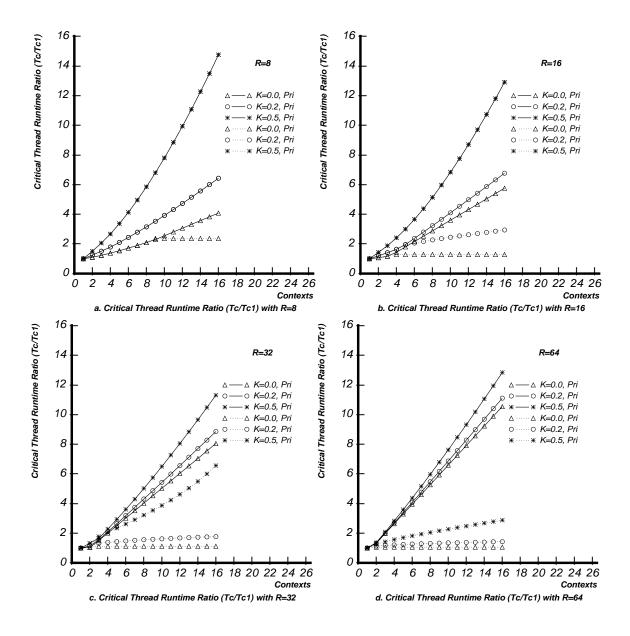

| 3.4 | $U$ and $T_c/T_{c1}$ when threads are spin-waiting for different values of R (4, 8, 16, 32, 64) and L (20, 50). a. Processor utilization $U$ assuming that there are 16 threads running and that an increasing number of these threads are spin-waiting. b. Critical thread runtime ratio $T_c/T_{c1}$ assuming that only one thread is running and all the other threads are spin-waiting | 55 |

| 3.5 | Multithreading in a single processor multiple-context system, assuming mem-<br>ory requests cannot be pipelined. a. Communication bound $(R + C < L)$ . b.<br>Computation bound $(R + C > L)$                                                                                                                                                                                              | 58 |

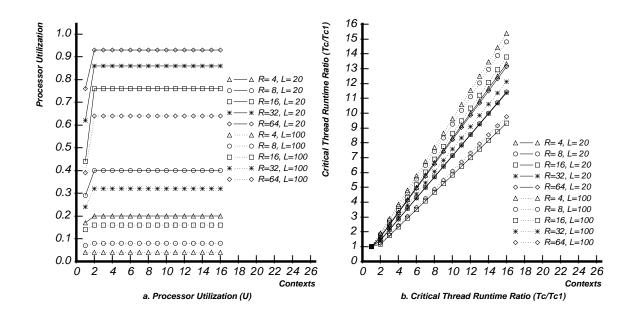

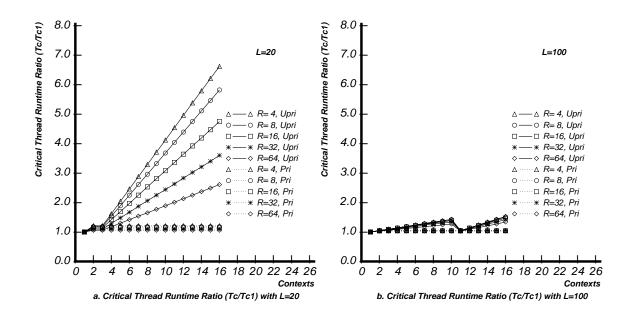

| 3.6  | $U$ and $T_c/T_{c1}$ assuming references cannot be pipelined, for different values of R (4, 8, 16, 32, 64) and L (20, 100)                                                                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

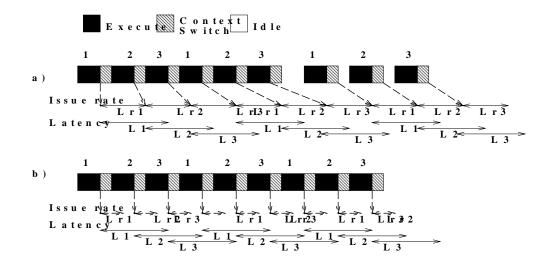

| 3.7  | Multithreading in a single processor multiple-context system, assuming mem-<br>ory requests can be pipelined at a rate of one request every $L_r$ cycles with<br>a latency of L. a. Communication limited $(R + C < L_r)$ . b. Computation<br>limited $(R + C > L_r)$ .                                         |

| 3.8  | Predicted latency for different values of R $(4, 8, 16, 32)$                                                                                                                                                                                                                                                    |

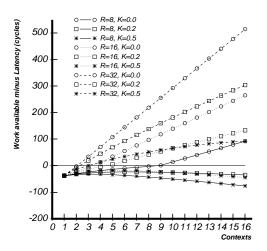

| 3.9  | Region of operation for different values of R (8, 16, 32) and K (0.0, 0.2, 0.5). The curves plot $(P-1)R + PC - L$ which is just the work available to overlap with latency, minus the latency. The processor is computation bound when the curve is above 0 and communication bound when the curve is below 0. |

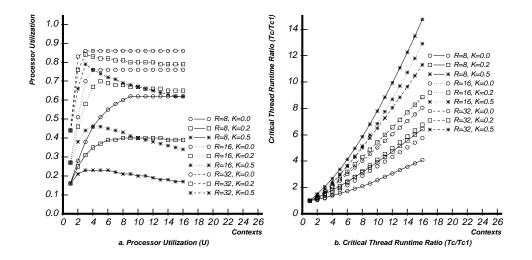

| 3.10 | $U$ and $T_c/T_{c1}$ for different values of R (8, 16, 32) and K (0.0, 0.2, 0.5)                                                                                                                                                                                                                                |

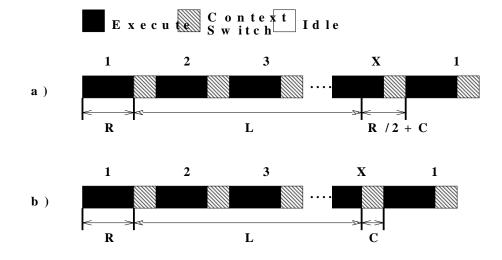

| 3.11 | Multithreading with thread prioritization in the computation bound case.<br>Thread 1 is the critical thread. a. Non-preemptive scheduling. b. Preemptive<br>scheduling.                                                                                                                                         |