# Coaxial Recess Integration of InGaAs Edge Emitting Laser Diodes with Waveguides on Silicon Substrates: A Complete Solution to Laser Integration on ICs

by

## Shaya Famenini

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2012

© Massachusetts Institute of Technology 2012. All rights reserved.

| Author        |                                                                     |

|---------------|---------------------------------------------------------------------|

|               | Department of Electrical Engineering and Computer Science 5/23/2012 |

|               |                                                                     |

|               |                                                                     |

| Certified by  |                                                                     |

|               | Clifton G. Fonstad                                                  |

|               | Professor of Electrical Engineering                                 |

|               | Thesis Supervisor                                                   |

| Accepted by   |                                                                     |

| 11000pt04 0 j | Leslie Kolodziejski                                                 |

|               | Chair of the Committee on Graduate Students                         |

## Coaxial Recess Integration of InGaAs Edge Emitting Laser Diodes with Waveguides on Silicon Substrates: A Complete Solution to Laser Integration on ICs

by

#### Shaya Famenini

Submitted to the Department of Electrical Engineering and Computer Science on 5/23/2012, in partial fulfillment of the requirement for the degree of Doctor of Philosophy

#### **Abstract**

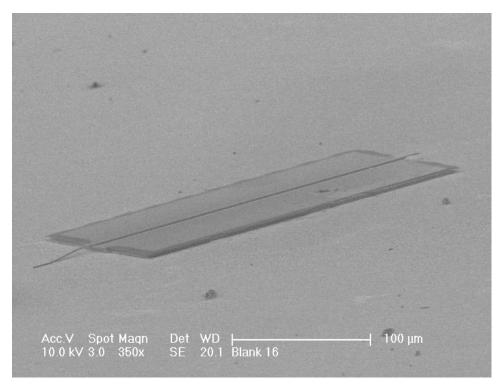

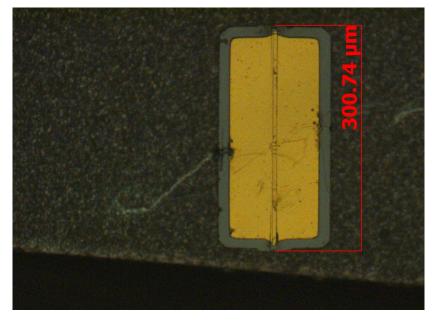

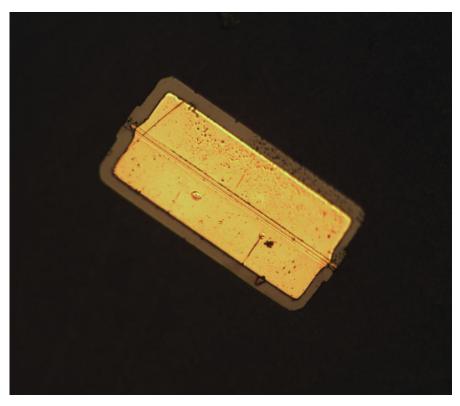

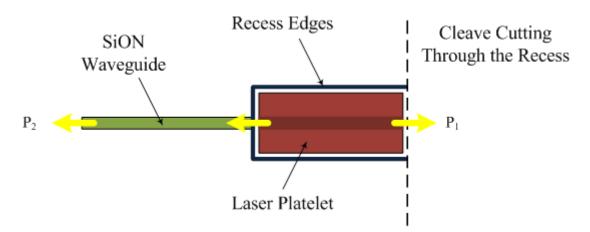

In this thesis, the first demonstration of the full integration of 1.55µm InGaAs/InP edge emitting platelet laser diodes with SiON/SiO<sub>2</sub> dielectric waveguides on a silicon substrate is presented. Small footprint laser platelets (300µm long by 150µm wide and 6.3µm high), are integrated and bonded in recesses etched in SiO<sub>2</sub> deposited on a Si substrate, and are coaxially coupled to the dielectric waveguides fabricated on the same wafer.

Lasers assembled in 6.5µm deep recesses are securely solder-bonded in place with a thin film Al/In bonding layer, which also brings the laser platelet back side n-contact to the wafer front side for measurements. The Al/In bonding layer composition and thickness are carefully optimized to provide highly reproducible vertical alignment to maximize the coupling of the laser output beam to the dielectric waveguide. Lasers are bonded into the recesses with this solder-bonding layer during a pressure assisted temperature cycle at 220°C. The low temperature nature of the bonding phase makes this integration technique CMOS compatible.

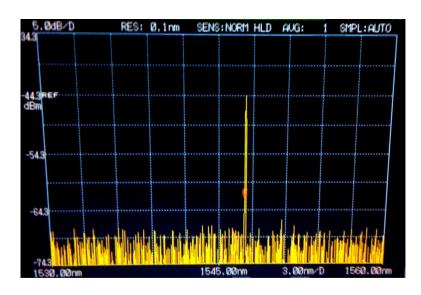

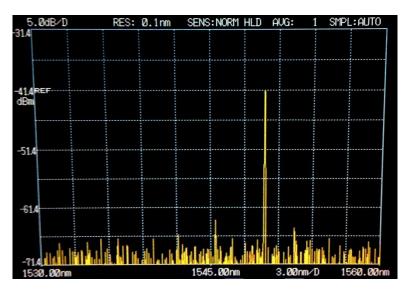

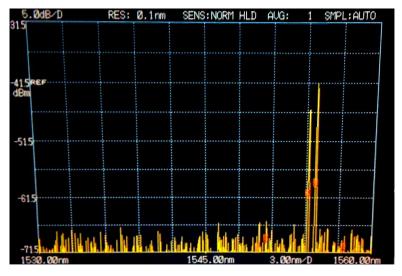

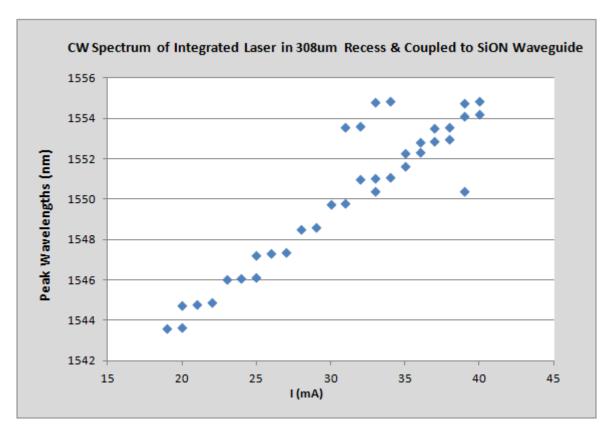

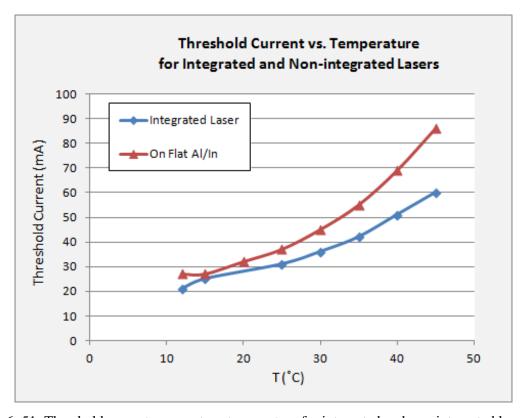

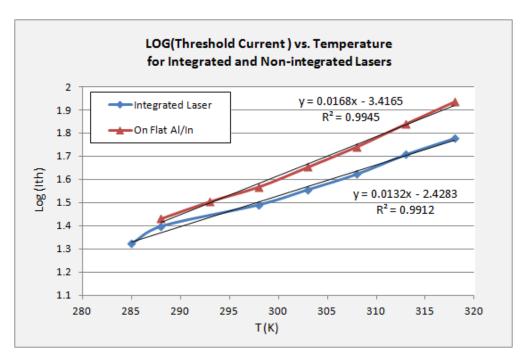

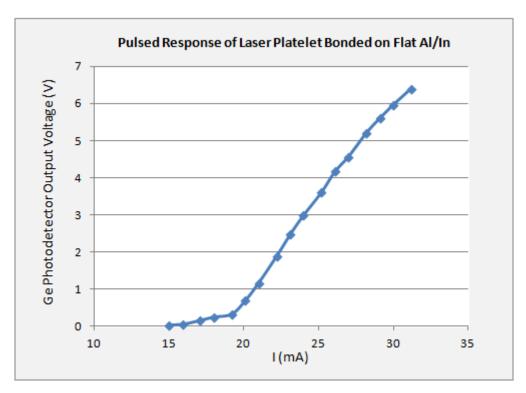

The integrated lasers show lasing operation with threshold currents of  $I_{th}$ =17mA and  $I_{th}$ =19mA for pulsed and continuous wave drives respectively, at T=15°C. The output spectrum shows single mode lasing near 1550nm, and a side mode suppression ratio of 25dB which is significantly higher than typical Fabry Perot cavity laser diodes. Furthermore, the integrated lasers have a characteristic temperature,  $T_0$ , of 76K which is improved from 60K for non-integrated lasers. Also the integrated lasers consistently show lower threshold currents compared to their non-integrated counterparts. The coupling loss between the laser and dielectric waveguide is extracted to be as low as 1dB, a value that can be further reduced by improved horizontal alignment and better matching the widths of laser stripe and dielectric waveguide.

Overall, this recess integration approach is CMOS compatible, is highly modular, compact and flexible, permits testing and selection of devices prior to integration, and allows integration of lasers emitting at different wavelengths on the same chip. It eliminates the need for wafer bonding III/V substrates to the host Si IC along with added complexity and cost it involves, and can be implemented using easily accessible technologies.

Thesis Supervisor: Clifton G. Fonstad Title: Professor of Electrical Engineering

## **Acknowledgements**

First and foremost I would like to thank my adviser Prof. Clifton Fonstad, whose patience was iconic during the peaks and valleys of this project. His non-judgmental, professional and very stable character, in addition to his strongly motivational leadership skills, were quite empowering and enlightening to me and had a major impact in bringing this project to a success. I cannot possibly thank him enough for all I learned from him. Both through our discussions on optoelectronics and their integration, as well as the vast amount of very valuable management and life lessons I learned from him by just observing his balanced reactions to events and extremely healthy character. Such lessons, all learned implicitly, have a life time impact in helping me be a better leader, manager, and hopefully a better person in life. I feel blessed by having had the chance of working with such a great supervisor during these years and to learn so much from him, both academically and personally.

I would also like to thank my thesis committee members, Prof. Leslie Kolodziejski and Prof. Rajeev Ram for their insightful comments and very helpful suggestions. Also I am very grateful to Prof. Kolodziejski for making it possible for me to use the BeamProp software from Rsoft in their group, as well as sharing the lab space where I performed the device measurements that are presented in this thesis. I would also like to thank Prof. Ram for making me familiar with the laser surface temperature measurement technique and also for using Laser Matrix software available in his lab. I would like to thank Prof. Eric Ippen for kindly letting me use the space in his lab for the optoelectronic measurements, and Dr. Connor Rafferty for lending us his Noble Peak Ge imager. Furthermore, my special thanks to Dr. Milos Popovic for developing the FDTD propagation and mode solver software at MIT and generously sharing it with our group, as well as being kindly available to answer questions about using the powerful mode solver software developed by him.

I would like to extend my deep gratitude to Anthony Zorzos and Jorg Scholvin from our group for all their help in phases of this research. I would like to thank Dr. Scholvin especially for taking the time to read this thesis and for all his helpful comments and careful corrections. Many thanks go to Ta-Ming Shih and Sheila Nabanja from Prof. Kolodziejski's group for their kindness and help in sharing the measurement setup with me, and Parthiban Santhanam from Prof. Ram's group in his help with fine thermocouples, as well as Katia Shtyrkova from Prof. Ippen's group for kindly sharing her InGaAs imager and small area

photo detector that were used in my measurements, and her kindness in answering my questions. Also I highly appreciate my friend, Sara Paydavousi, for her kind help and time spent with the depositions carried out in Prof. Valdimir Bulovic's lab.

I would like to extend special thanks to Kurt Broderick for his supervision over the EML facility and being kindly and open heartedly available to answer questions, and provide valuable insights and solutions to the hurdles I faced with fabrication. I would also like to thank Patrick Boisvert for his help in using ESEM in the CMSE facility and making me familiar with Back Scattered SEM, which was very helpful in this project.

I would also like to deeply thank the EECS department at MIT for all the numerous fellowships they provided as financial support, which enabled me to pursue my research and coursework at MIT. Also I would like to thank the Dean of Graduate Education, Prof. Christine Ortiz for providing a fellowship at a very critical semester in finalizing the research results of this project. Also, Prof. Orlando's leadership and insightful remarks during his term as the head of the EECS graduate office were very helpful and influential in helping me moving towards a well-planned and timely graduation.

I would like to thank all the professors and TAs that I had the pleasure of working with during my seven semesters of teaching assistantship at MIT, where I learned a lot both on microelectronics, as well as group dynamics, team work and effective leadership.

Needless to say, my friends both here and abroad have played a major role in making life at MIT more enjoyable. I would like to thank all of them for their kindness, support, and the wonderful community events we have had in the Boston area, which enriched me in both personal and spiritual levels. I would like to specifically thank my Yaraan Jaani friends for all their close and attentive support through the hard and happy times of my PhD and for being as close as siblings to me. Their angelic characters and good heart had been an endless source of support and warmth. I thank them for being so passionate about our friendship that kept our circle alive and active even after each one of us ended up in the opposite corners of the world.

Finally, I like to thank my dear parents for all their love and sacrifice to nourish us and help us reach success and happiness in life. If it had not been for my parents' sole emphasis on education, my path in life might have never crossed MIT nor being this passionate about science and engineering. I would like to whole-heartedly thank my mother, Farzaneh Khorrami, for all the sacrifice she has made raising us. Her level of devotion to our family has always struck me on how self-less and giving a human being can be.

Words come short of thanking my beloved dear late father, Parviz Famenini, for all this support and insightful advice which shaped my character and encouraged me to pursue success and excellence in life. My father's modest life, not giving in to social pressures to conform to what everyone else does, and his constant emphasis encouraging us to have a clear goal in life and to pursue it, have all had a profound impact in making me who I am and forming my ideals. I owe my independent way of thinking, resistance to illogical social pressures, strength of personality, and the constant quest in seeking meaning and goal of life endeavors all to my father and his deep impact on my personality. With that, I would like to dedicate this thesis to the fond memory of him and his pure soul which is deeply missed.

At last to lift the spirit of the reader by a jest, an academic one!, I'd like to conclude with a quote I liked from the book "My life as a Quant", by Emanuel Derman, where he describes his feelings upon graduation from Columbia University with a PhD in particle physics: "A large part of me was exhausted with physics and the seven-year struggle to shine. I consoled myself with a few sentences Einstein wrote in his autobiographical notes, composed at the age of 67, about aftereffects of his final examinations: "This coercion had such a deterring effect [upon me] that, after I had passed the final examination, I found the consideration of any scientific problems distasteful to me for an entire year.""

- My life as a Quant

Shaya Famenini May 2012

## **Table of Contents**

Chanter 1

| Chapter 1                                                        |    |

|------------------------------------------------------------------|----|

| Motivation and Approaches to Optoelectronic Integration          | 15 |

| 1.1. Integrated Circuits                                         | 15 |

| 1.2. Optoelectronic Integration                                  | 17 |

| 1.2.1. Optical versus Electrical Interconnects                   | 18 |

| 1.2.2. Evolution of Application of Optical Interconnects         | 20 |

| 1.3. Approaches to Photonic Integration                          | 23 |

| 1.3.1. Hybrid-Packaging                                          | 24 |

| 1.3.1.1. Flip Chip Bonding                                       | 24 |

| 1.3.1.2. Planar Lightwave Circuits (PLCs)                        | 26 |

| 1.3.2. Si Based Detectors and Lasers                             | 27 |

| 1.3.3. Epitaxial Growth of Compounds on Si Substrate             | 28 |

| 1.3.4. Bonding III/V wafer to Si host IC                         | 31 |

| 1.3.5. III/V Substrate Removal                                   | 34 |

| 1.4. Our Approach to Photonics Integration on Si                 | 36 |

| 1.5. Thesis Flow                                                 | 37 |

| Chapter 2                                                        |    |

| Assessment of Hybrid Evanescent Approach to III/V-Si Integration | 41 |

| 2.1. A Review of the Hybrid Evanescent Approach                  | 42 |

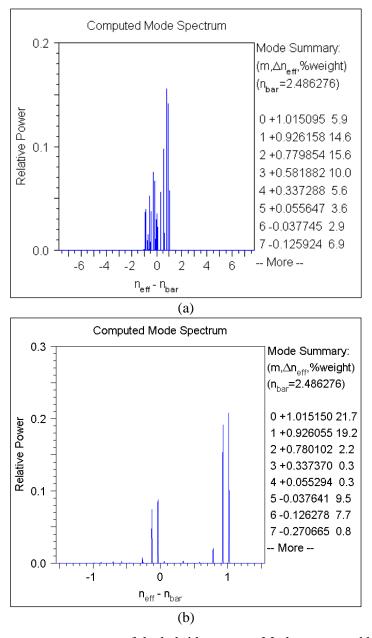

| 2.2.4. Mode Spectrum Response                                                   | 60  |

|---------------------------------------------------------------------------------|-----|

| 2.2.5. Analyzing Simulation Data                                                | 62  |

| 2.2.5.1. Si-guide to Hybrid-guide Transition                                    | 62  |

| 2.2.5.2. Si-guide to Hybrid-guide to Si-guide Transition                        | 66  |

| 2.2.5.3. Hybrid-guide to Si-guide Transition                                    | 69  |

| 2.2.6. Summary                                                                  | 72  |

| 2.3. Conclusion                                                                 | 73  |

| 2.3.1. Coaxial vs. Evanescent Coupling Integration Approaches: Strengths and    |     |

| Limitations                                                                     | 74  |

| Chapter 3                                                                       |     |

| Design and Optimization Simulations                                             | 79  |

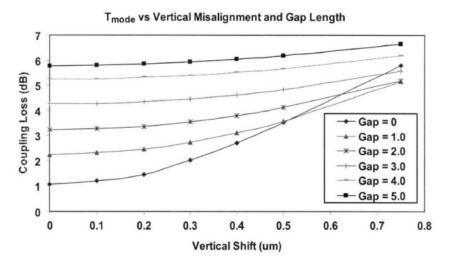

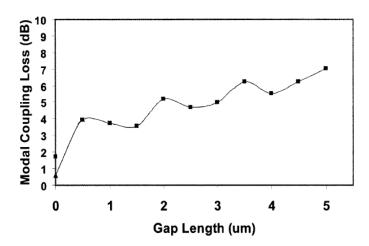

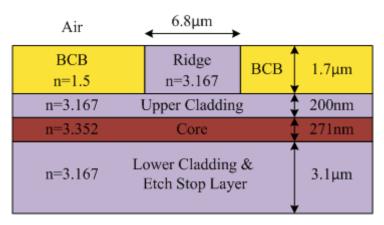

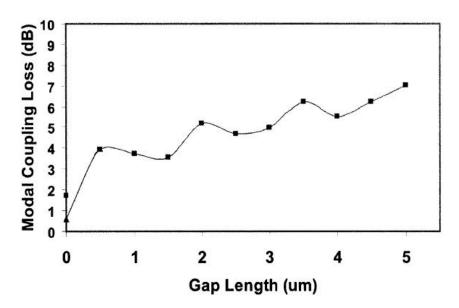

| 3.1. Waveguide and Gap Filling Optimization: Dimensions, and Refractive Indices | 81  |

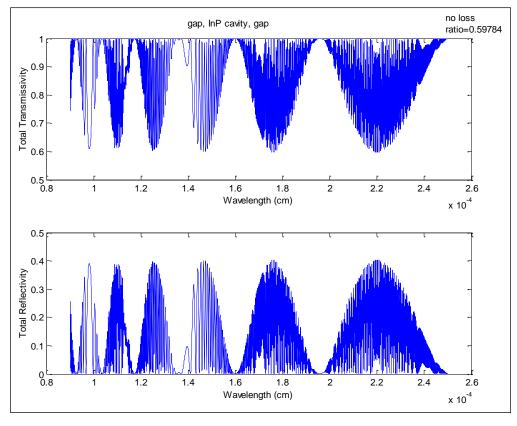

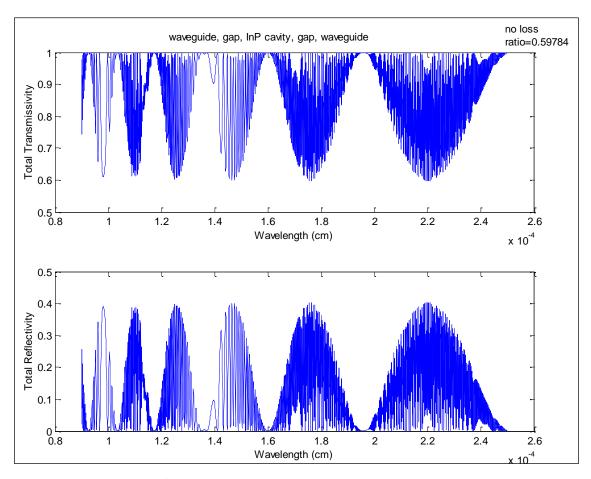

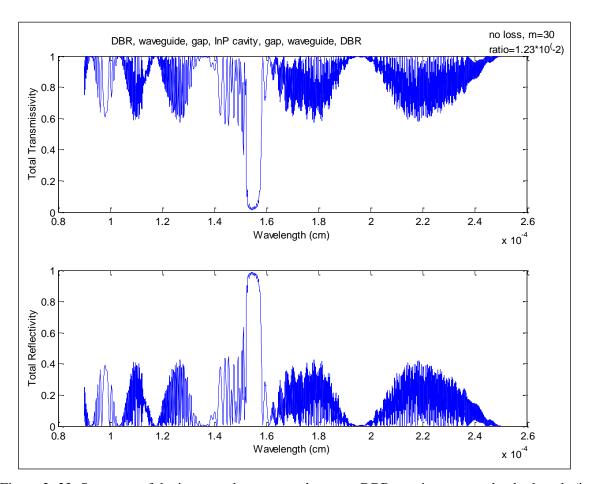

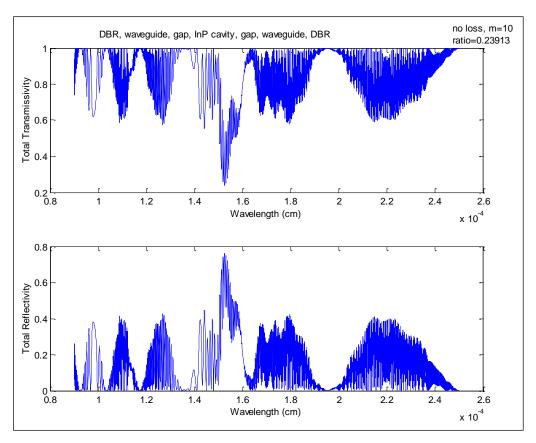

| 3.2. DBR Motivation                                                             | 90  |

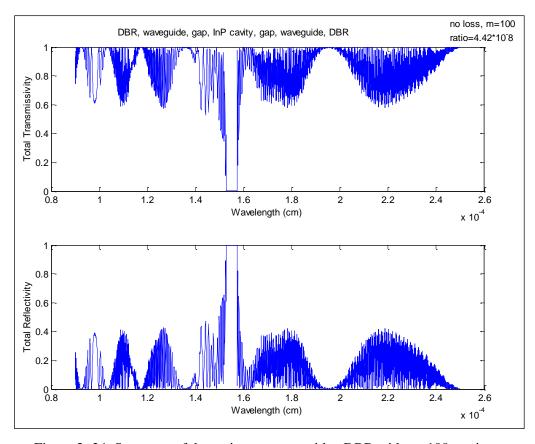

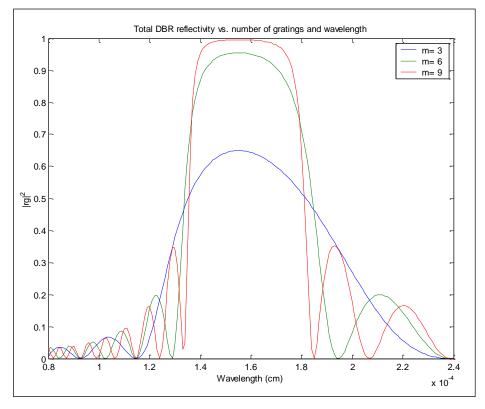

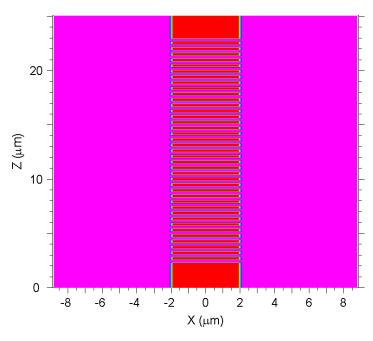

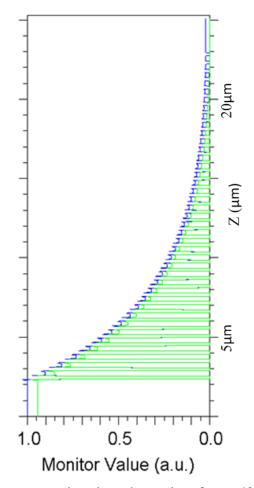

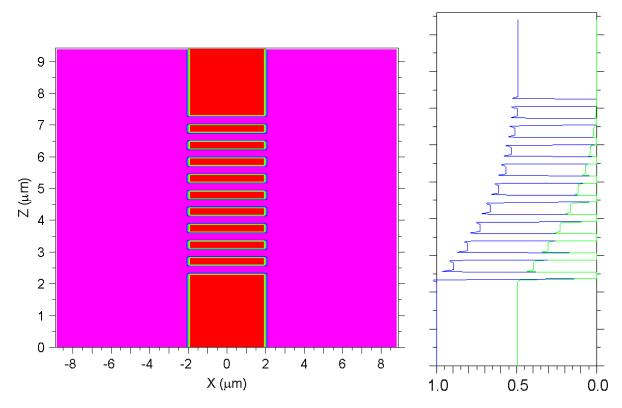

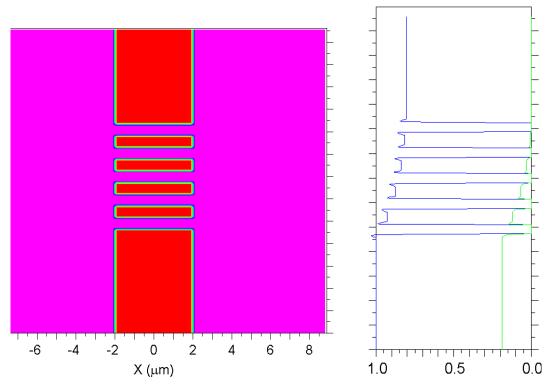

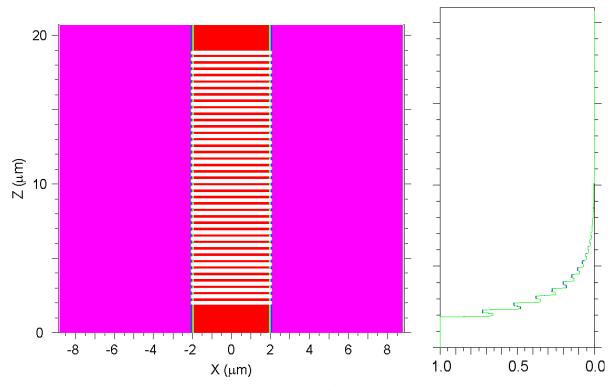

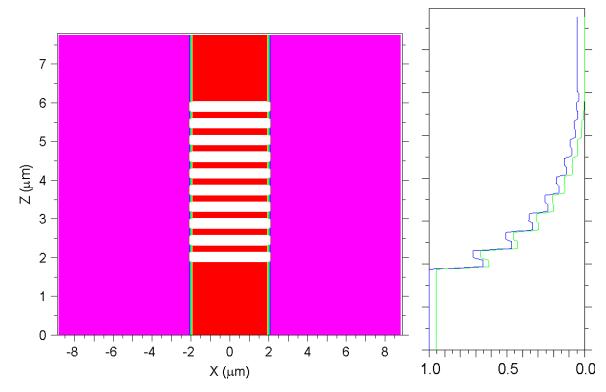

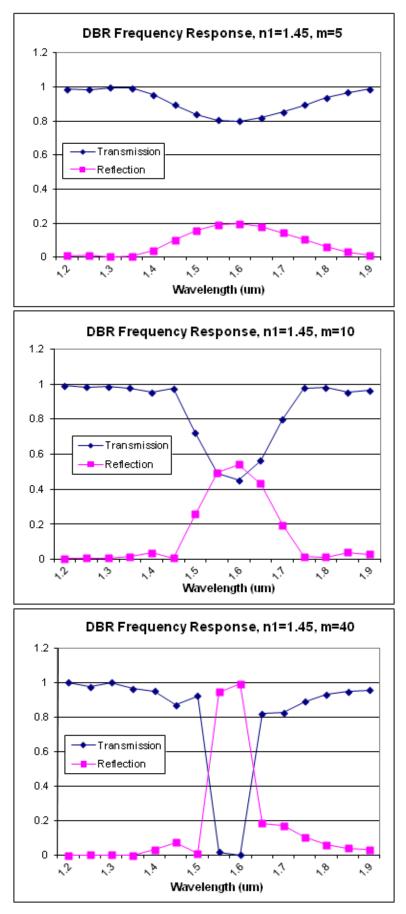

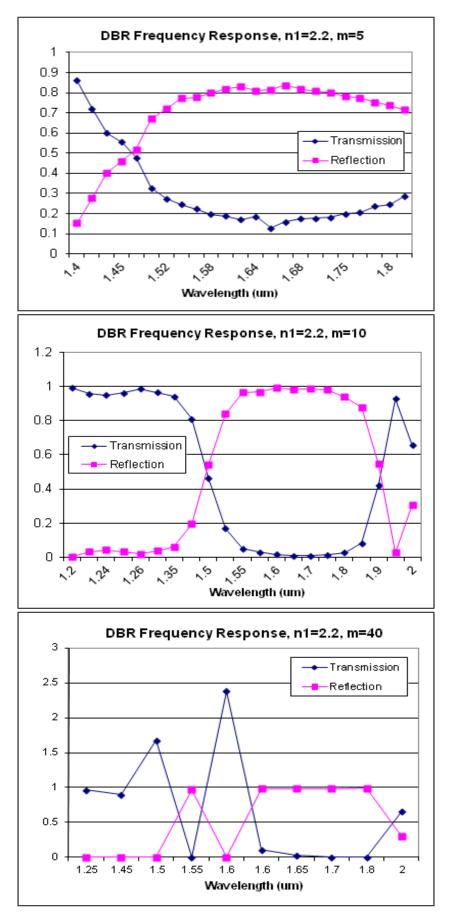

| 3.3. DBR Design via FDTD                                                        | 93  |

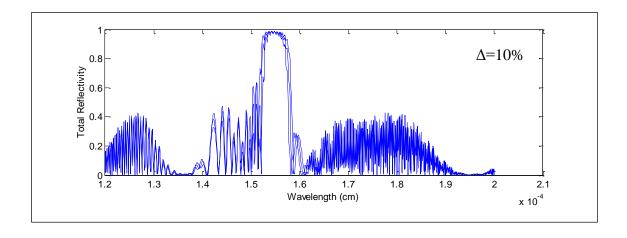

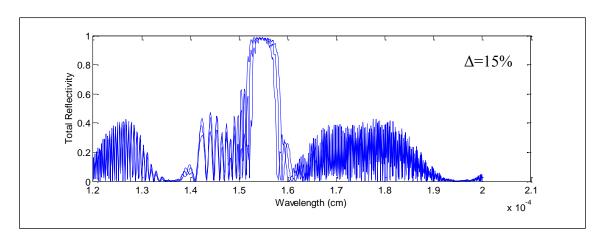

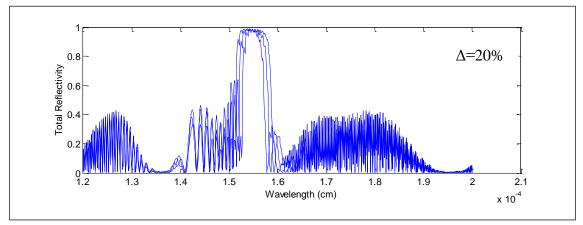

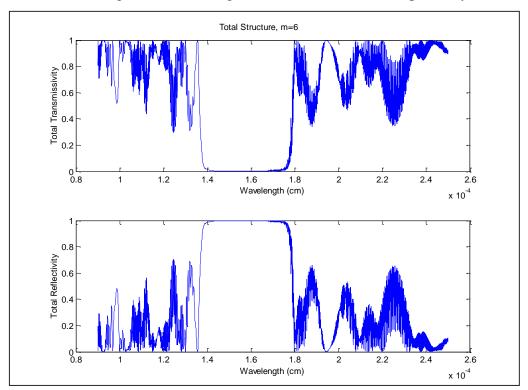

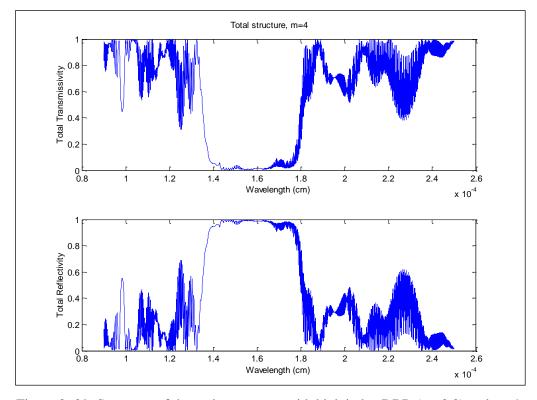

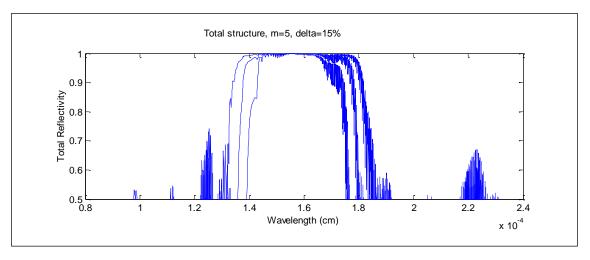

| 3.4. Transmission Matrix Method: Design and Optimization Simulations            | 98  |

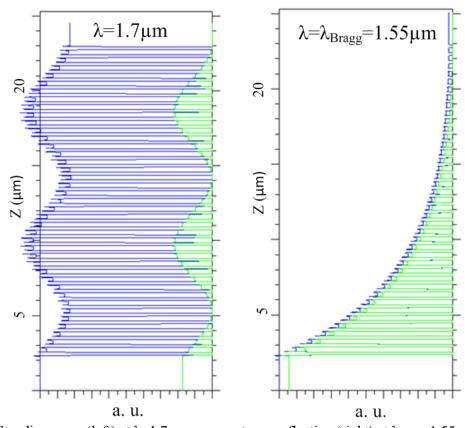

| 3.5. DBR Design via BeamProp: Bidirectional BPM                                 | 112 |

| 3.5.1. Introduction to BPM                                                      | 112 |

| 3.5.2. DBR Design with Bidirectional BPM                                        | 113 |

| 3.6. Summary and Discussion                                                     |     |

| Chapter 4                                                                       |     |

| Integration Components: Lasers, Recesses and Dielectric Waveguides              | 125 |

| 4.1. Passive Components: Dielectric Waveguides and Recesses                     | 125 |

| 4.1.1. Design of Dielectric Waveguides                                          | 126 |

| 4.1.2. Fabrication of Dielectric Waveguides                                     | 128 |

| 4.1.3. Characterization of Dielectric Waveguides                                | 129 |

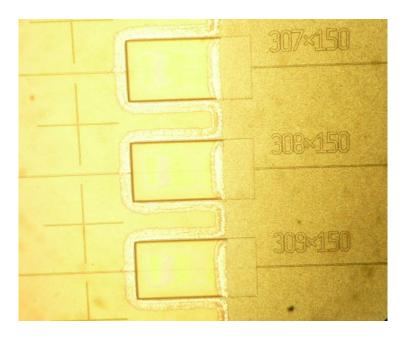

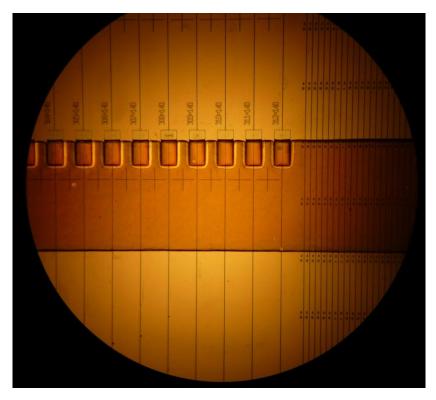

| 4.1.4. Fabrication of Recesses                                                  | 130 |

| 4.1.5. Die-saw Assisted Cleave                                                  | 132 |

| 4.2. Active Component: Edge Emitting InGaAs MQW Platelet Laser Diodes           | 133 |

| 4.2.1. Characterization of Fabricated InGaAs/InP Edge Emitting Laser Diodes     | 133 |

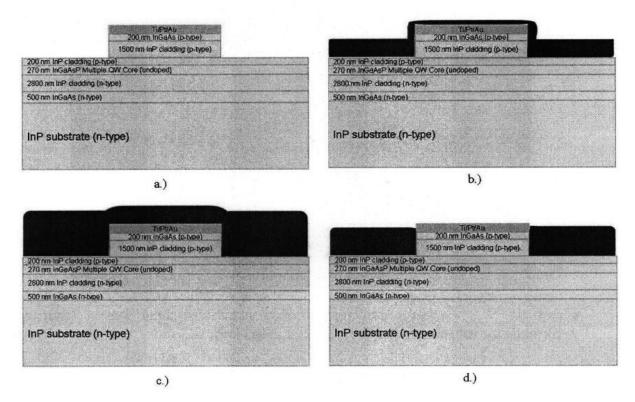

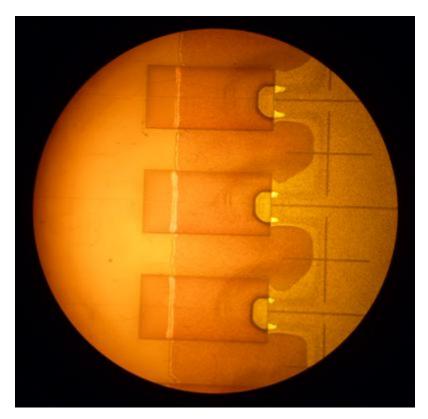

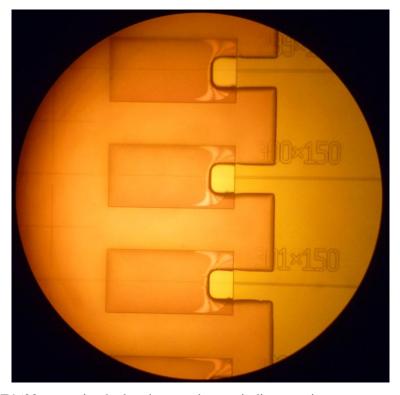

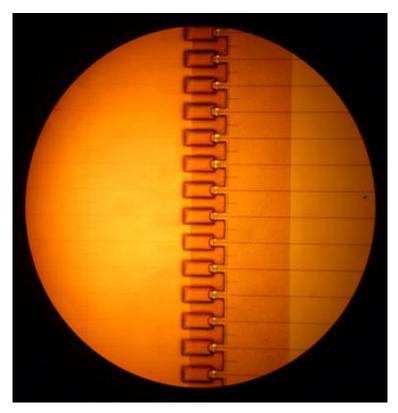

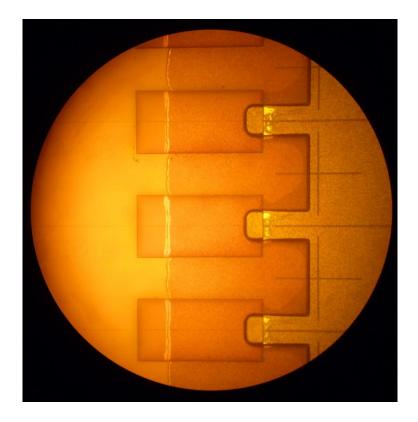

| 4.2.2. Fabrication of Edge Emitting Platelet Laser Diodes                       | 134 |

| Chapter 5                                                                       |     |

| Integration Process                                                             | 149 |

| 5.1. Integration Steps                                                          |     |

| 5.2 Bonding Layer                                                               | 150 |

| 5.2.1. Significance                                               | 150 |

|-------------------------------------------------------------------|-----|

| 5.2.2. Composition                                                | 150 |

| 5.2.3. Intermetallic Compounds Formed in Solder-Bonding Layer     | 152 |

| 5.2.4. Deposition                                                 | 154 |

| 5.2.5. Patterning of the Bonding Layer                            | 155 |

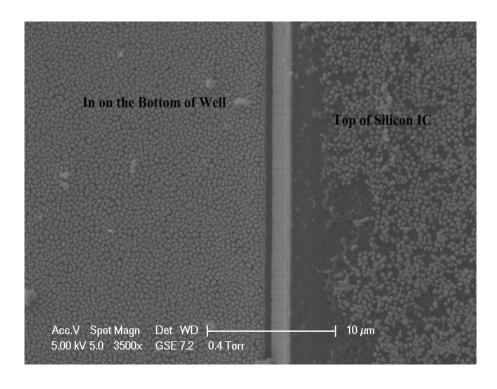

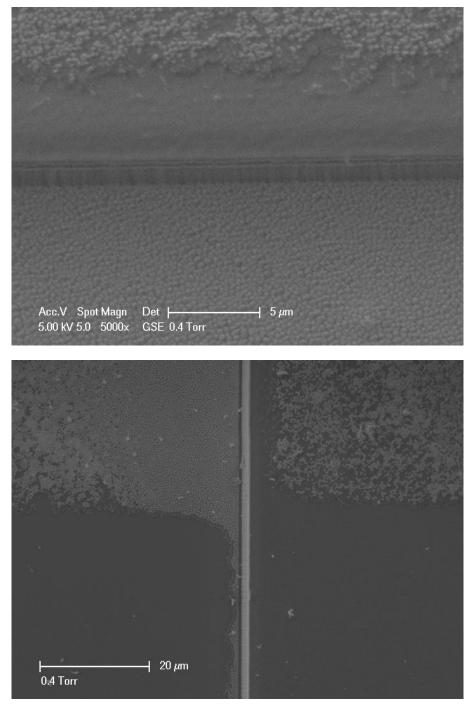

| 5.2.6. Morphology of the Bonding Layer                            | 159 |

| 5.2.7. Other Concerns in Patterning Al/In with AZ4620             | 161 |

| 5.3. Substrate Cleaving and Facet Polishing                       | 165 |

| 5.4. Assembly Process                                             | 165 |

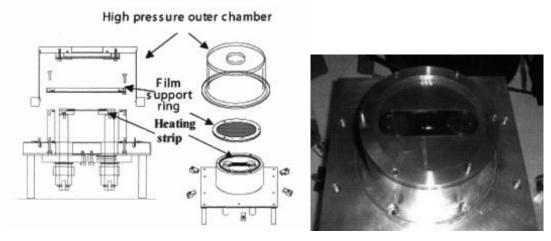

| 5.5. Bonding Step                                                 | 168 |

| 5.6. Optimization of Bonding Layer Thickness                      | 169 |

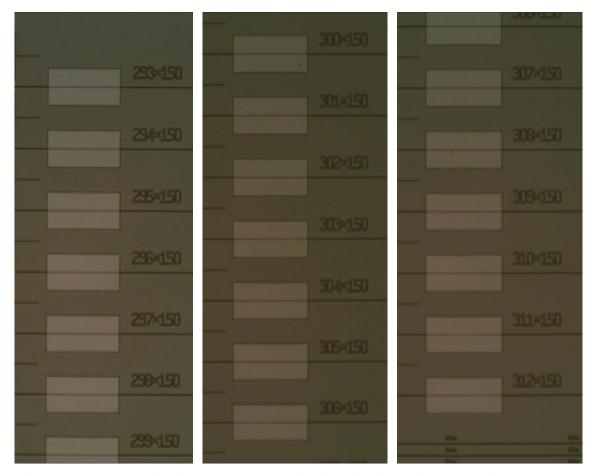

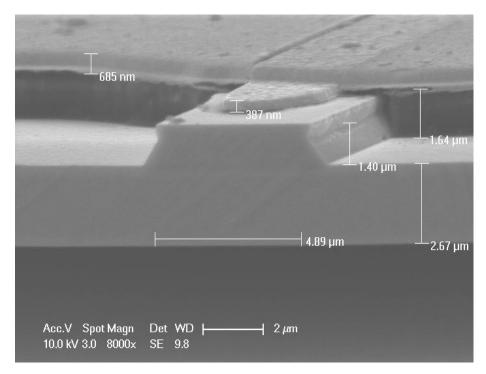

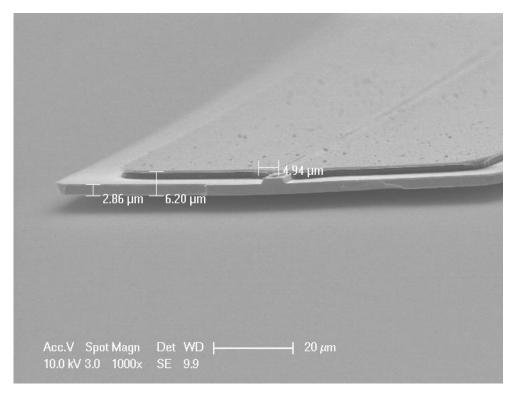

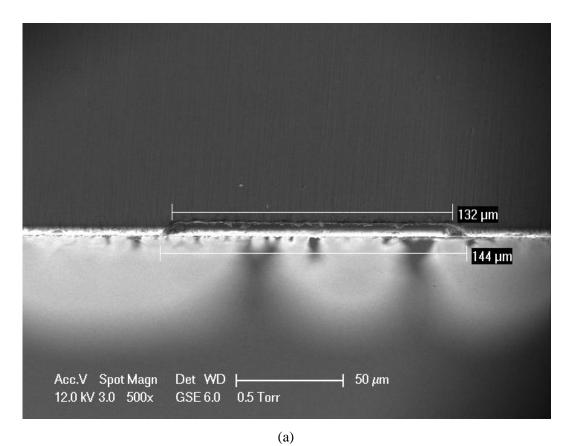

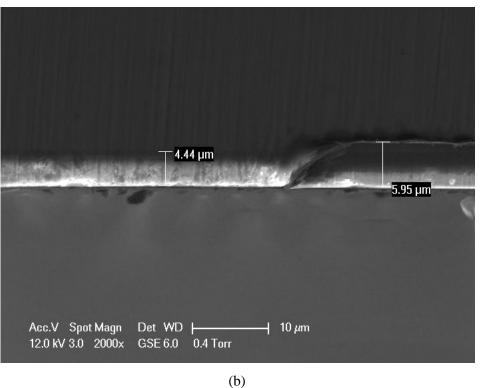

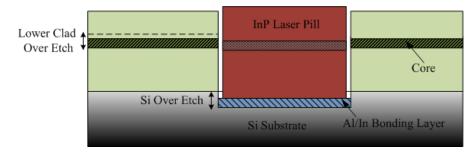

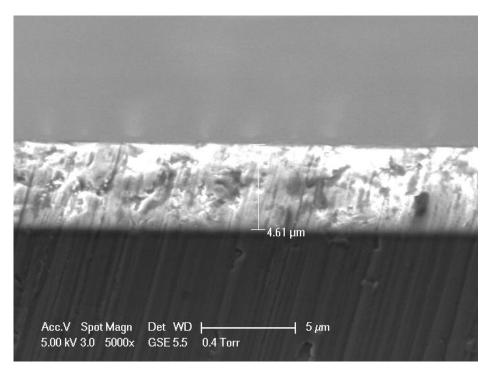

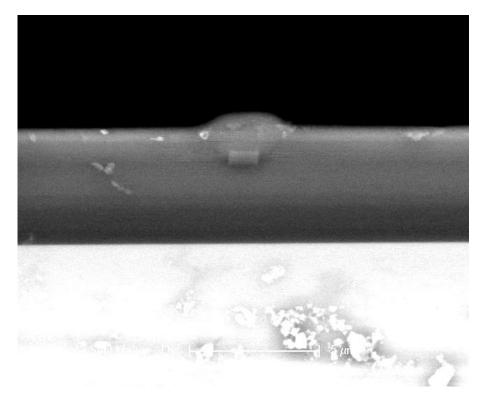

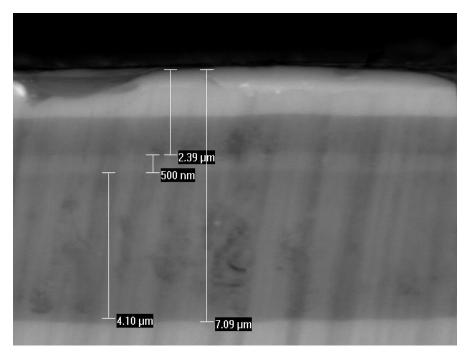

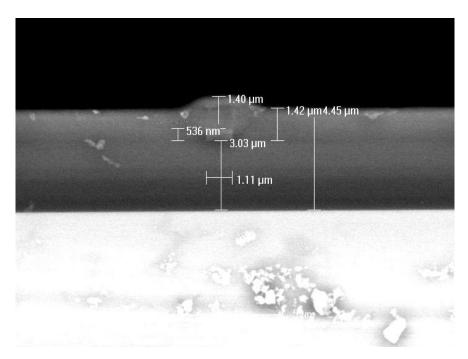

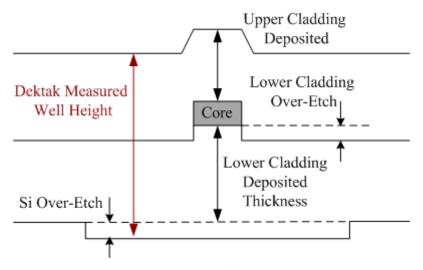

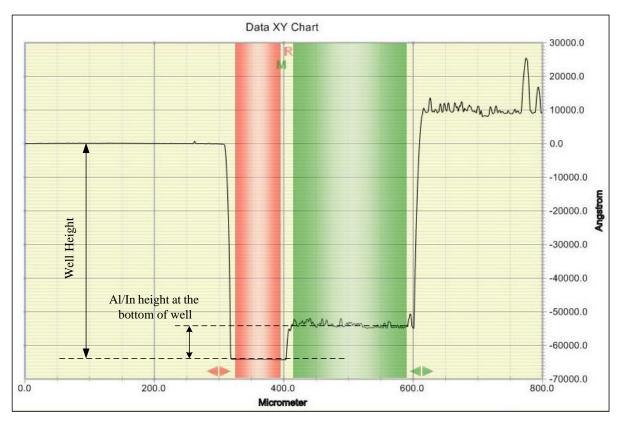

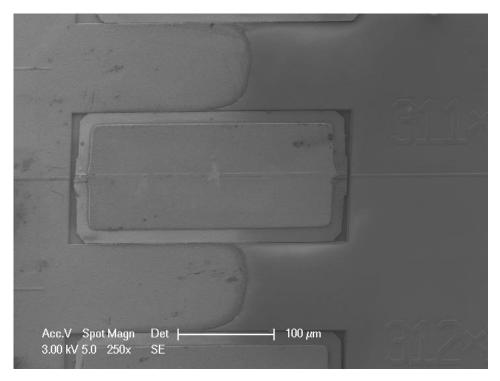

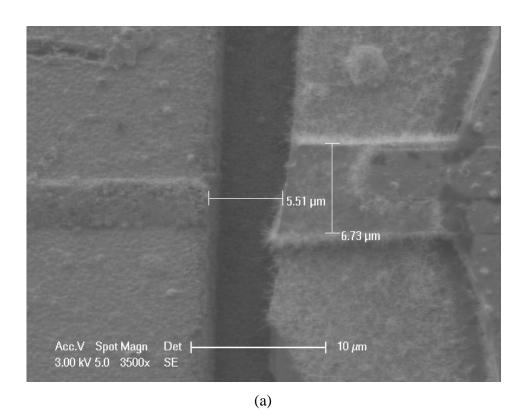

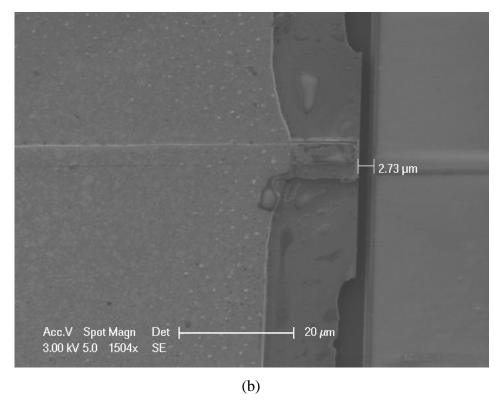

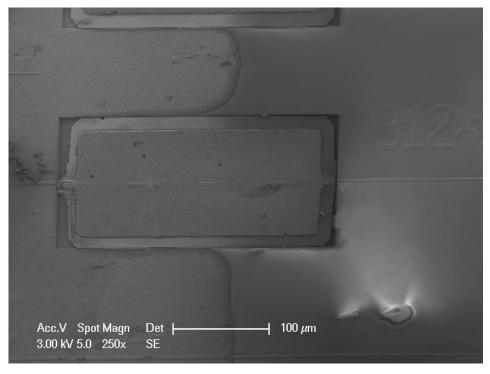

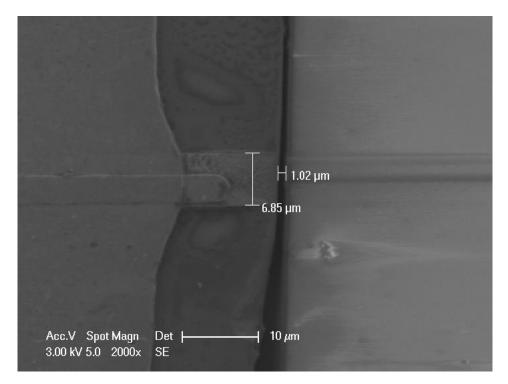

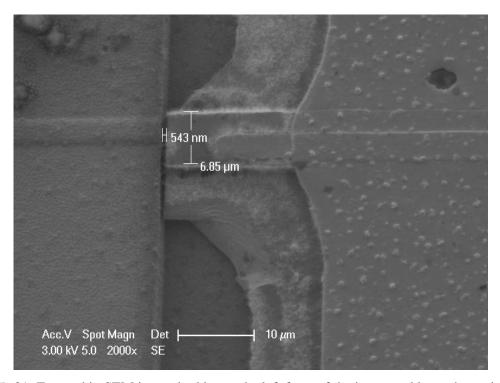

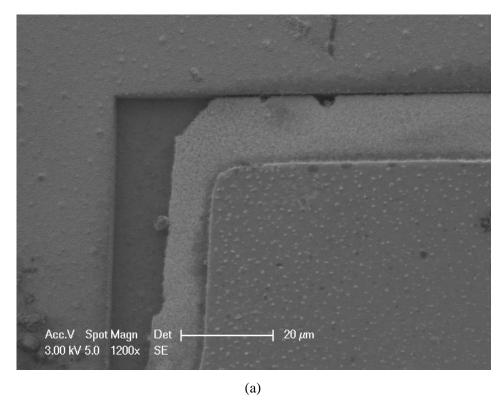

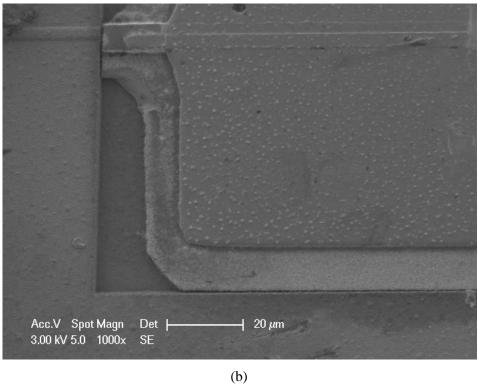

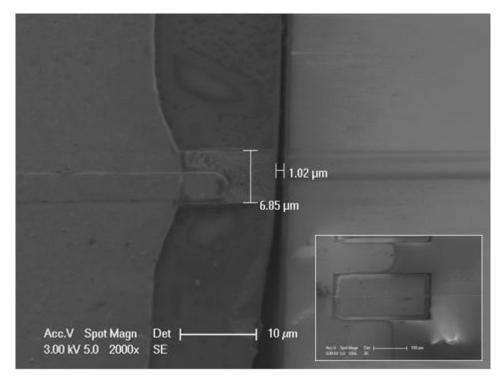

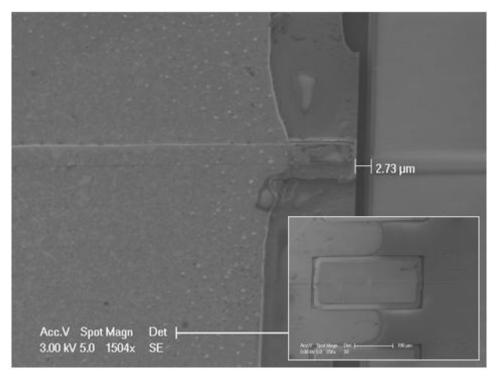

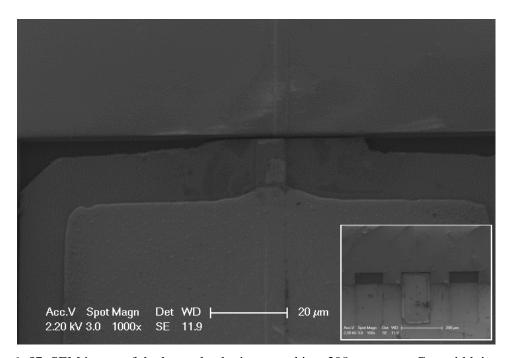

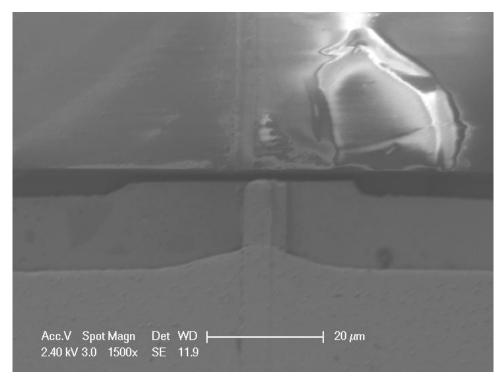

| 5.6.1. Determining Actual Dimensions of Dielectric Stack/Recesses | 171 |

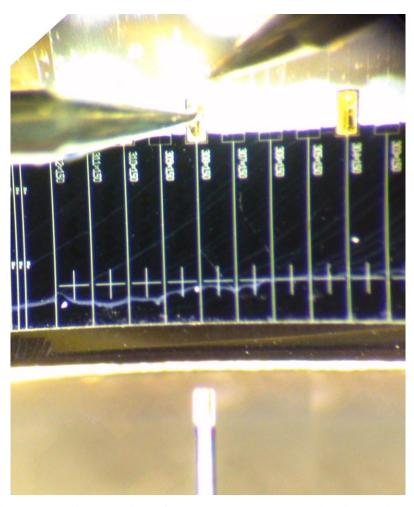

| 5.7. Integrated Structure                                         | 181 |

| Chapter 6                                                         |     |

| Measurements and Results                                          | 187 |

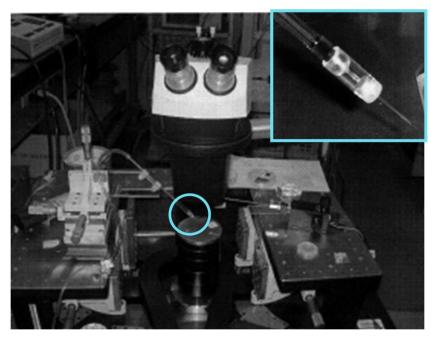

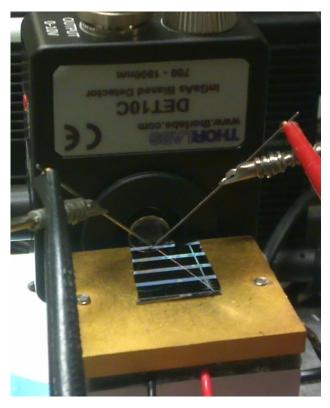

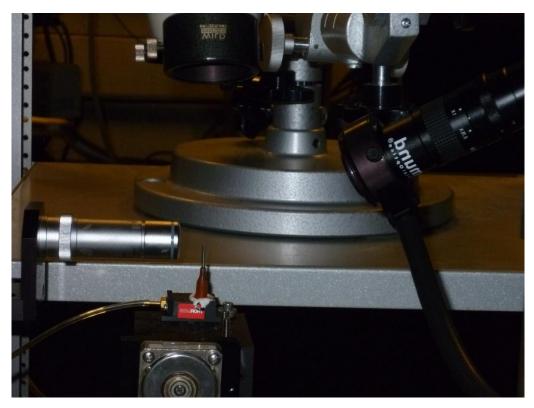

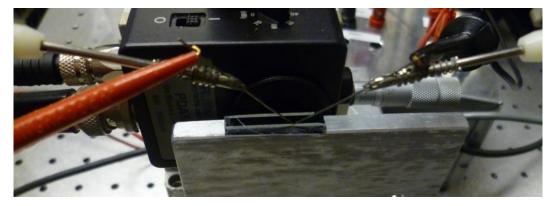

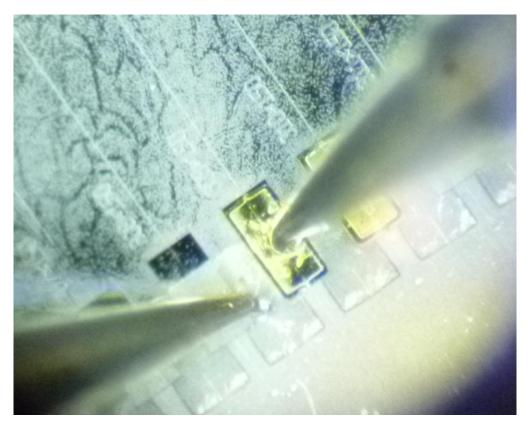

| 6.1. Measurement Setup                                            | 188 |

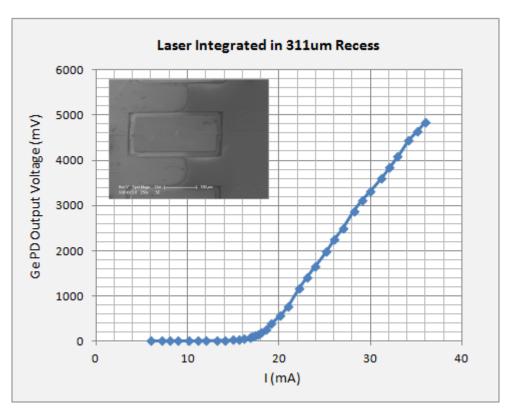

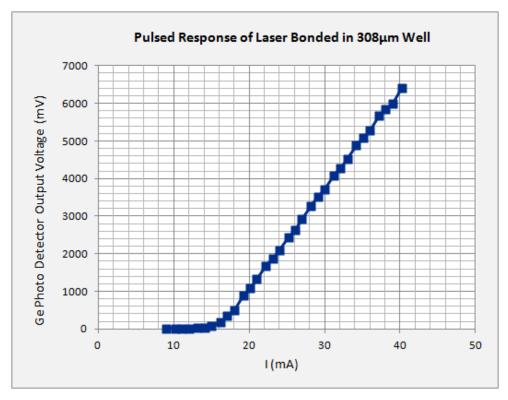

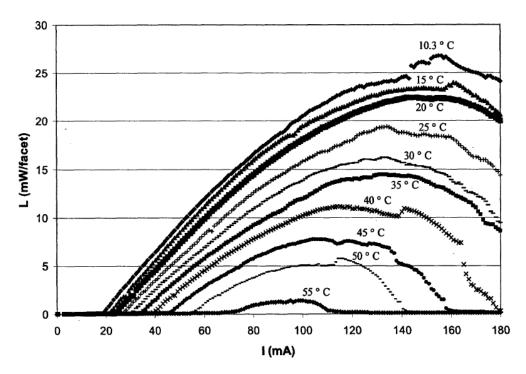

| 6.2. Pulsed LI Measurements                                       | 191 |

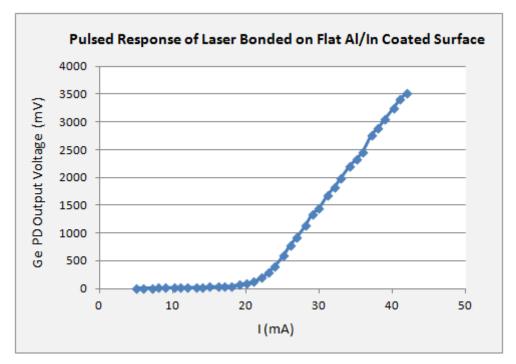

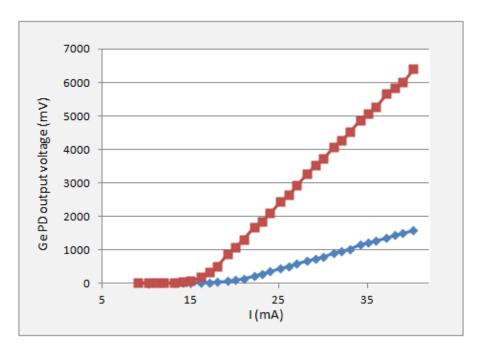

| 6.2.1. Non-integrated lasers                                      | 191 |

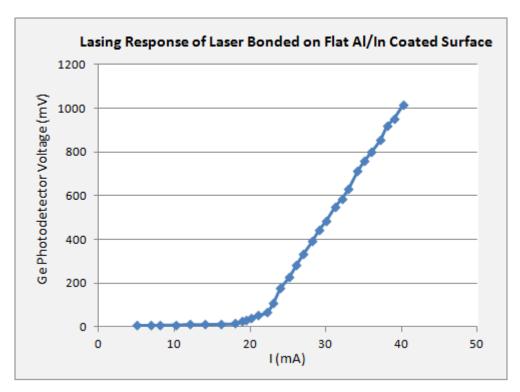

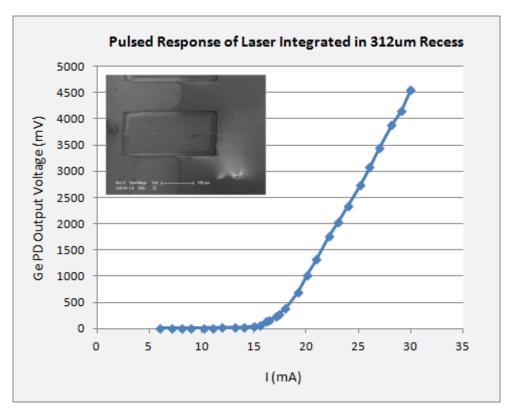

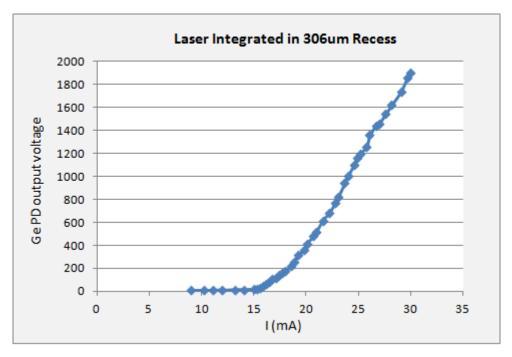

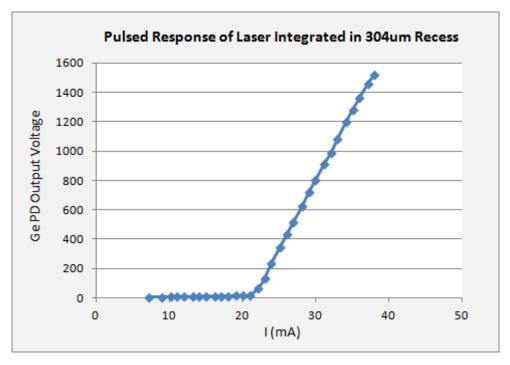

| 6.2.2. Integrated Lasers                                          | 194 |

| 6.2.3. Calculating Optical Power from Detector Output Voltage     | 197 |

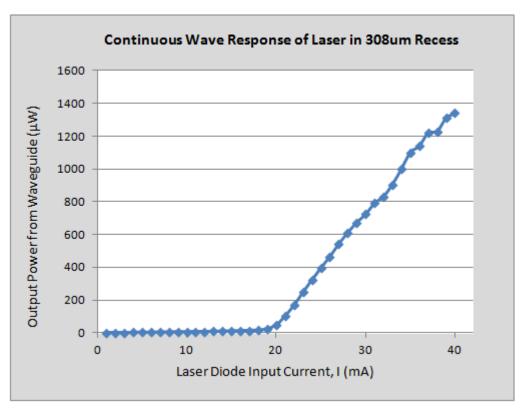

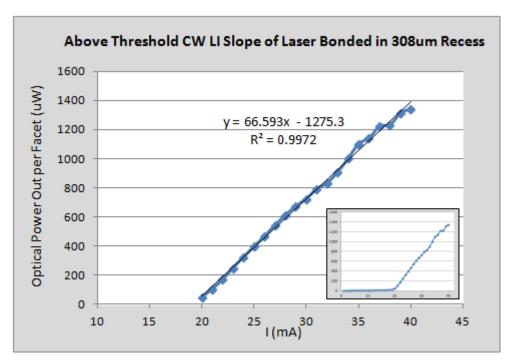

| 6.3. Continuous Wave LI Measurements                              | 198 |

| 6.4. Output Optical Mode Shape                                    | 199 |

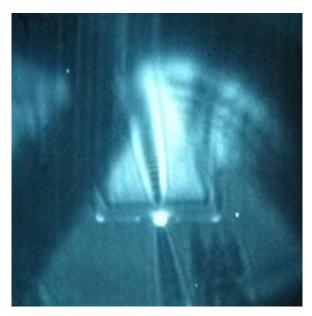

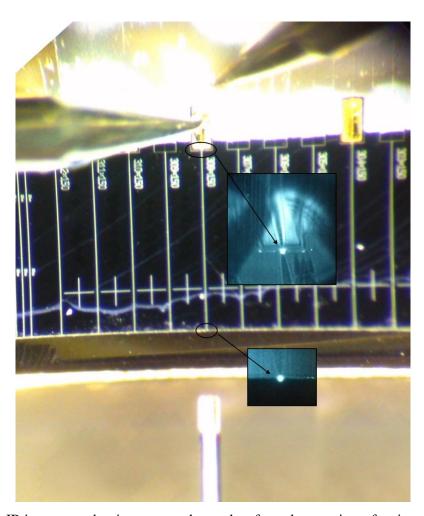

| 6.4.1. IR Images of Output Beam                                   | 201 |

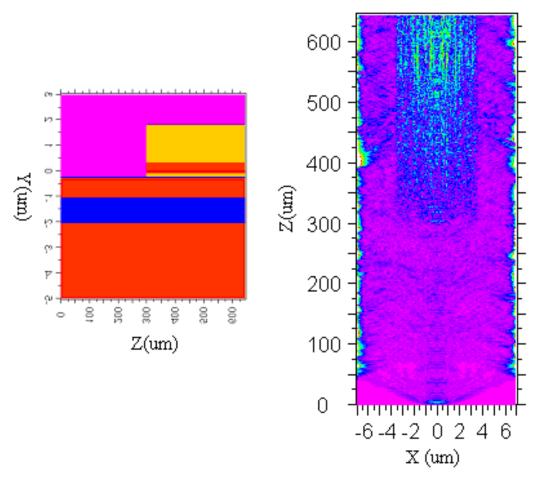

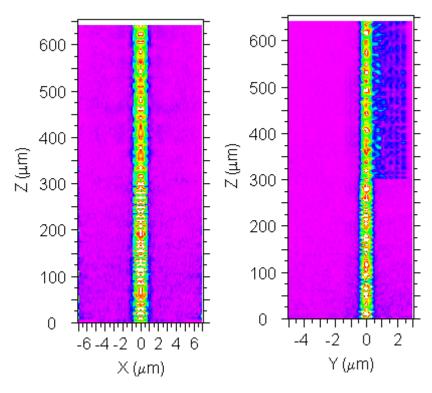

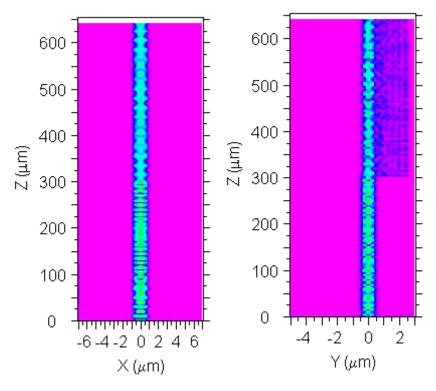

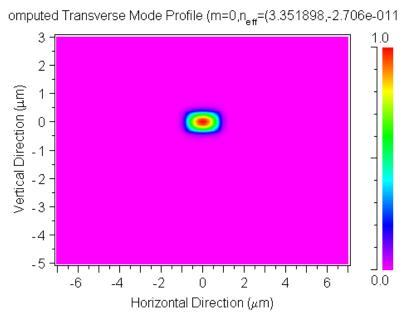

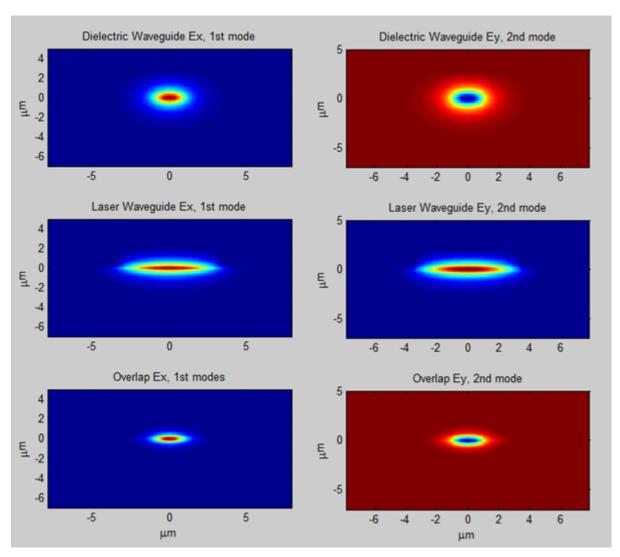

| 6.5. Mode Shape Simulations                                       | 206 |

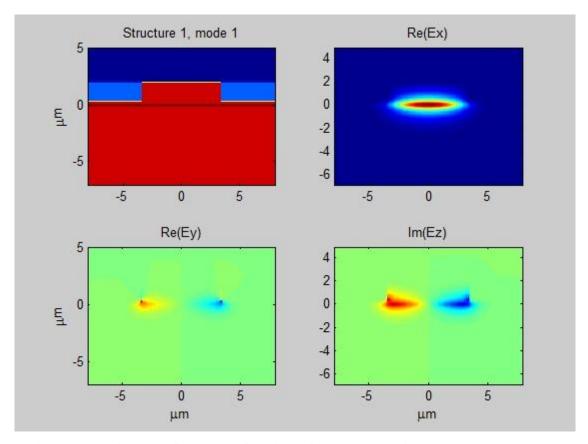

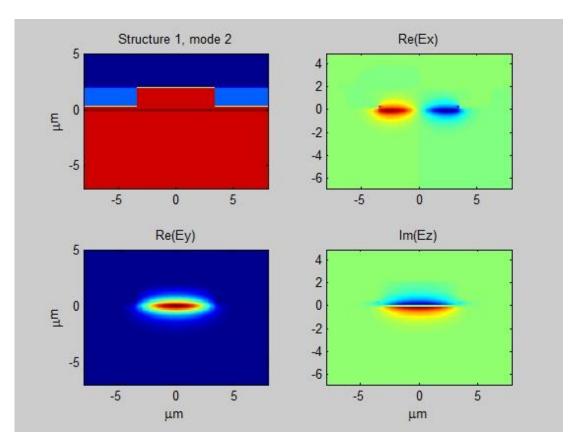

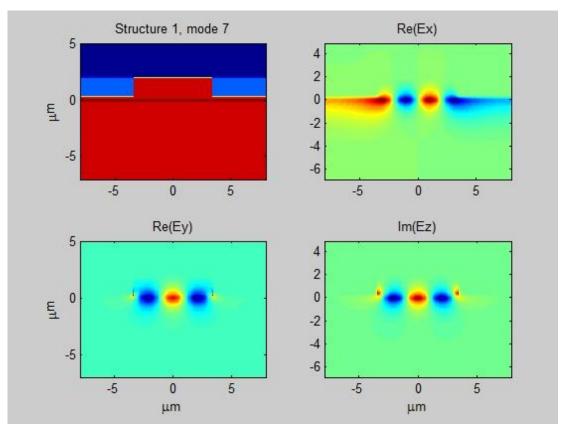

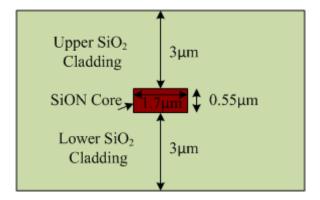

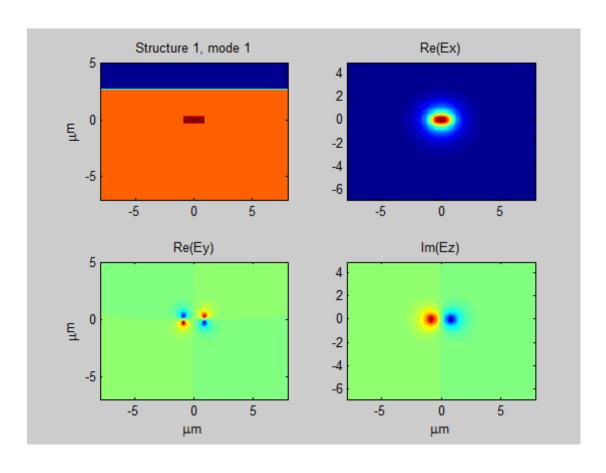

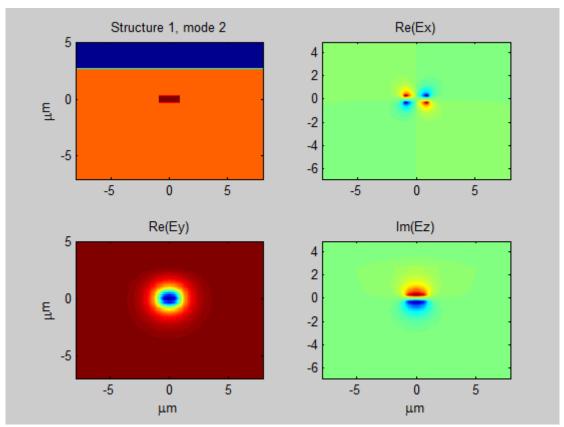

| 6.5.1. Laser Ridge Waveguide Modes                                | 206 |

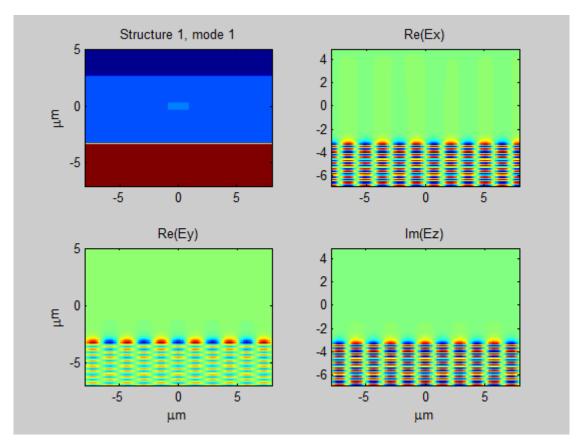

| 6.5.2. Fundamental Modes of Dielectric Waveguide                  | 210 |

| 6.5.3. Fundamental Modes Coupling Integral of Two Waveguides      | 213 |

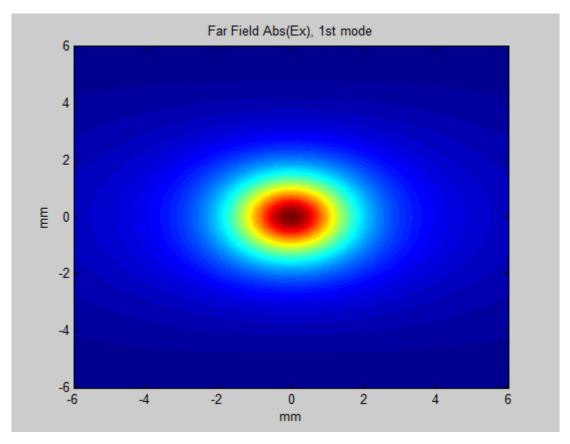

| 6.5.4. Far Field Output Mode Shape                                | 214 |

| 6.6. CW Spectrum of Integrated Lasers                             | 217 |

| 6.6.1. Fabry Perot Cavity Mode Hopping vs. Current                | 220 |

| 6.6.2. Effective Cavity Length                                    | 223 |

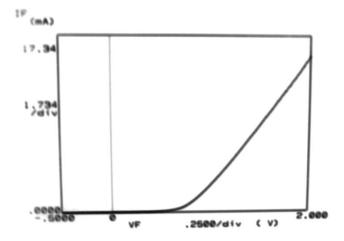

| 6.7. Mode Suppression in Integrated Lasers                        | 224 |

| 6.7.1. Three Mirror External Cavity Model                         | 226 |

| 6.7.2. MSR with Frequency Dependent Mirror Loss                   | 227 |

| 6.7.3. Calculating MSR Numerical Value                                 | 228 |

|------------------------------------------------------------------------|-----|

| 6.8. External Quantum Efficiency                                       | 230 |

| 6.8.1. Aging of Laser Platelets                                        | 232 |

| 6.9. Characteristic Temperature                                        | 233 |

| 6.10. Determining the Coupling Loss                                    | 235 |

| 6.10.1. Open-Ended Recess Method                                       | 236 |

| 6.10.2. Estimating Coupling Loss from Two Different Lasers             | 237 |

| 6.10.2.1. Comparison of Experimental Results with FDTD Simulations     | 242 |

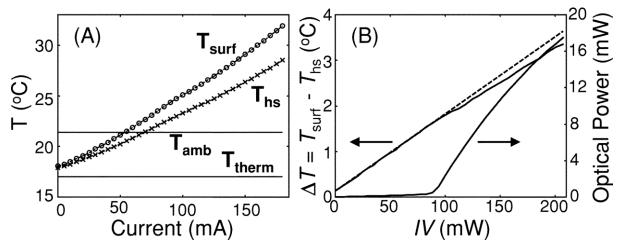

| 6.10.3. Determining Coupling Loss through Surface Temperature Analysis | 244 |

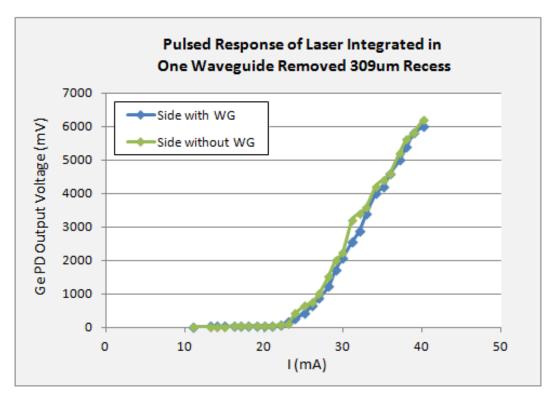

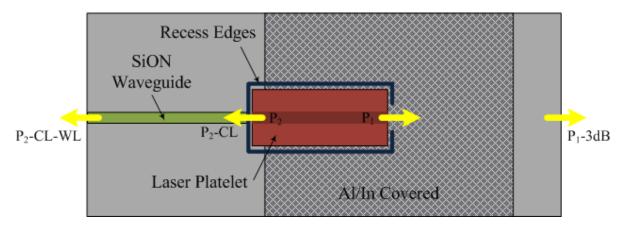

| 6.10.4. One-Waveguide-Removed Approach to Estimate Coupling Loss       | 247 |

| 6.11. Summary                                                          | 255 |

| Chapter 7                                                              |     |

| Conclusion and Suggestions                                             | 257 |

| 7.1. Coaxial Recess Integration Approach                               | 257 |

| 7.2. Achievements of This Research                                     | 260 |

| 7.3. Future Work                                                       | 261 |

| 7.3.1. Effect of External Cavity                                       | 261 |

| 7.3.2. Gap Filling                                                     | 261 |

| 7.3.3. Removing Gap Sensitive Reflection                               | 262 |

| 7.4. Suggested Improvements                                            | 263 |

| 7.4.1. InGaAs/InP Platelet Lasers                                      | 263 |

| 7.4.2. SiON/SiO <sub>2</sub> Waveguides                                | 264 |

| 7.4.3. Recesses                                                        | 266 |

| 7.4.4. Solder-Bonding Layer                                            | 266 |

| 7.4.5. Assembly Setup                                                  | 267 |

| 7.4.6. Bonder Setup                                                    | 267 |

| 7.4.7. Gap Filler Material                                             | 268 |

| 7.4.8. Si Waveguides                                                   | 268 |

| 7.5. Conclusion                                                        | 269 |

| Appendix I                                                             |     |

| Calculation of Hybrid Evanescent Device Specifications                 | 271 |

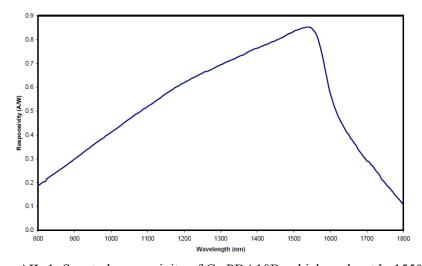

| AI.1. Photodetector Responsivity Derivation                            | 271 |

| AI.2. Edge Emitting Laser Threshold Current Calculation                | 272 |

| AI.3. Race-track Laser Threshold Current Calculation                   | 273 |

| AI.4. Quantum Well Confinement Factor Reality Check | 273 |

|-----------------------------------------------------|-----|

| Appendix II                                         |     |

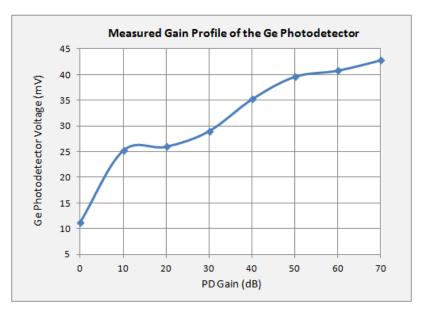

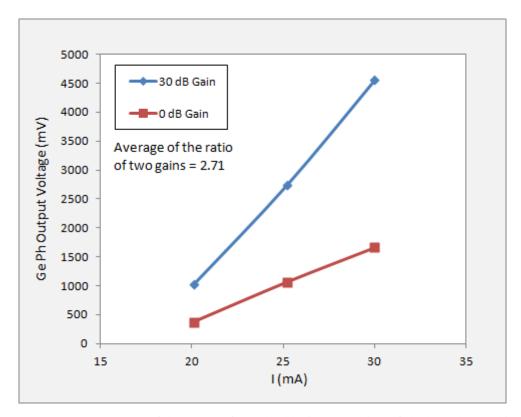

| Calibrating Ge PD Output Voltage                    | 275 |

| References                                          | 279 |

# Chapter 1

# Motivation and Approaches to Optoelectronic Integration

This chapter begins with a very short introduction to integrated circuits in general, followed by a review of the motivation behind photonic integration on silicon substrates. Different techniques that have been developed to achieve this goal will then be covered and the issues with each approach will be discussed. Finally our solution to the integration of III/V photonics on silicon substrates will be introduced, which relies on the coaxial integration of laser platelets with waveguides fabricated on Si substrates.

In the chapters that follow Chapter 1 the process of design, optimization, fabrication and implementation of this integration approach will be detailed, which in turn proves this technique to be a robust, modular, highly flexible solution for photonics integration. From the performance of laser diodes fully integrated with dielectric waveguides on Si substrate, we believe that this approach can provide a very promising solution for the integrated photonics industry and can be readily adopted and commercialized.

# 1.1. Integrated Circuits

The first working transistor was demonstrated in Dec. of 1947 [1], and 11 years later the invention of integrated circuits (ICs) started a new phase in electronics, communications and in an amazingly vast number of diverse other fields. Since integrated circuits provide an

insurmountable cost/performance/reliability advantage over discrete counterparts, industry has been keen to advance the IC technology ever since.

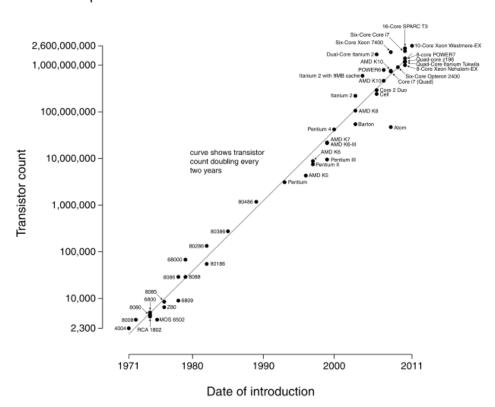

In 1965, Gordon Moore, an Intel co-founder, explained in a paper that in the time span between 1958 and 1965, the number of components per integrated circuit doubled every year and he expected the trend to persist for at least another 10 years. Whether it was his deep insight, luck, or the great inherent potential of the semiconductors microfabrication industry, this prediction turned out to be very true since then. Figure 1- 1 shows how on average the number of transistors on a CPU has doubled every 1.5-2 year since 1971 [2].

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1- 1: CPU transistor count versus dates of introduction of the corresponding microprocessor.

Notice the logarithmic vertical scale. The fitted line corresponds to exponential growth, with transistor count doubling every two years as the modified Moore's Law predicted.

With Moore's Law, the semiconductor industry has been setting up roadmaps for the next generations of microprocessors and memories, and has been pretty successful in meeting these milestones so far. Hence the mass production and large scale integration that such a trend puts forth resulted in stellar cost reduction and performance improvement of these electronic ICs. One might find it hard to believe that the first UNIVAC computer released in

1951 weighed 13 tons and occupied more than 35.5 square meters and had a clock speed of 2.25 MHz [3]. Sixty years later, a personal computer now is a thousand times faster and is light and compact enough that easily fits in a purse and is affordable enough that One Laptop Per Child (OLPC) campaign [4] has over 2.4 million of XO system deployments 1 as of April 2012 [5], [6].

All these make it clear how integration is the leading driver in the advances and wide-spread use of semiconductor components in the 20<sup>th</sup> and 21<sup>st</sup> centuries, which was made feasible by outstanding achievements in the technology and cost reduction simultaneously [7].

# 1.2. Optoelectronic Integration

The integration of optoelectronic devices with electronic circuits and systems has seen growing applications ranging from long haul to micro haul links. In fact this integration has been a concern and area of interest for the last 25 years, however until recently reliable approaches to the compact integration of photonic and electric components on a common substrate had yet to be developed, making optoelectronic integration a continuing challenge for the industry.

Increasingly higher bandwidth requirements for communication systems (from long haul to on-chip) have forced the drive for the integration of optoelectronics to access higher levels of signal processing and faster interconnection, with insight to cost and foot print reduction of the integrated circuits. As discussed earlier, the integration of CMOS electronics has followed the Moore's law trend and the number of transistors per chip has doubled every 1.5 to 2 years. This outstanding progress in the field of integration of transistors and scaling has resulted in having an astonishing number of 2.6 billion transistors integrated on a microprocessor chip commercially available in 2011, the Xeon E7 which is manufactured by Intel and has a clock rate of 1.73-2.67GHz with transistor gate lengths of 32nm and 4-10 cores per die [8]. This clearly shows the maturity of integration in silicon electronics, which is vastly ahead of photonics integration with CMOS. To address this photonics integration bottleneck, in this thesis we will talk about a novel technique to make the integration of active and passive photonics with silicon ICs feasible with a low cost, reliable, and reproducible approach.

\_

<sup>&</sup>lt;sup>1</sup> Specifically Southern American and African countries like Uruguay, Peru and Rwanda data is eye-catching.

First, we will look into why optoelectronic interconnects must (and most probably will) replace electrical interconnects in many applications.

#### 1.2.1. Optical versus Electrical Interconnects

The limitations of electrical interconnects can be summarized as transmission line effects (high rise/fall time and channel attenuation for long channels), non-ideal effects at high frequencies such as the skin effect, frequency dependent dielectric loss, manufacturing variations, geometric issues like discontinuities, echo effect, crosstalk, and self coupling. Quite simply, electromagnetic interference and switching noise combined with higher power consumption pose serious issues with electrical interconnects when going at high bit rates over longer links.

It can be shown that for both RC limited and skin effect limited transmission lines, losses scale with the square of length in electrical interconnects [9]. This will result in frequency dependent distortion and ultimately reduces maximum achievable bit rate with inverse of the square of interconnect length.

Optical interconnects offer lower attenuation and distortion compared to their electrical counterparts, and are immune to crosstalk. As a result, optical links have become the selected choice for long haul communication. It is about a decade that optical WDM links with data rates of 5 Tb/s over 1000 km of single mode fiber without regeneration have been available commercially. In contrast, an electrical link would have a bit rate of only 0.05 b/s over the same distance. This makes it clear why optical communication has had an unbeatable triumph for long haul links. For Ethernet and LANs (local area networks) although the adoption of all optical links was slower historically, the increasingly overwhelming traffic in data centers and the need for higher bit rates has motivated the use of optical links in these applications as well.

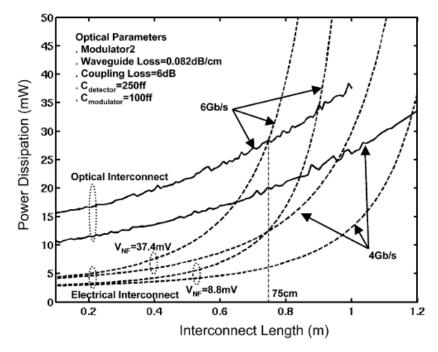

Cho et al, compare the power consumption of optical interconnects to their electrical peers for 10cm to 1m range in [10], and the result is shown in Figure 1- 2. In summary, it is found that beyond a critical length, power optimized optical interconnects dissipate lower power compared to the state of the art high speed electrical signaling scheme. Also it is shown that at higher bit rates and lower BER, the critical length reduces and optics becomes more power favorable, which is intuitive. Consequently it is argued that these trends can be thought of as a tradeoff between optical interconnects downside of power loss in optical-electrical conversion (lower in all-optical systems) and their upside of lower attenuation and

noise (no crosstalk). Since the former is fixed and the later is length and bit-rate dependent, the optical interconnects become superior at longer lengths.

Figure 1- 2: Comparing the power dissipation of optical and electrical interconnects for different interconnect lengths.

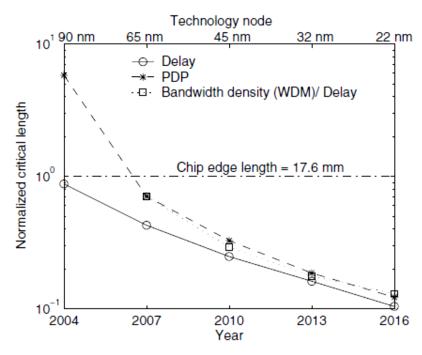

In another effort to compare optical and electrical interconnects, Chen et al have looked into the critical lengths beyond which optical interconnects are advantageous based on delay, PDP and bandwidth density/delay in [11] and [12]. Figure 1- 3 shows the result of this comparison for different technology nodes. Consequently one can see that these critical lengths are well below the chip size with the recent technology scaling.

Therefore, even for on-chip communications, optical interconnects win over their electrical counterparts based on many different criteria.

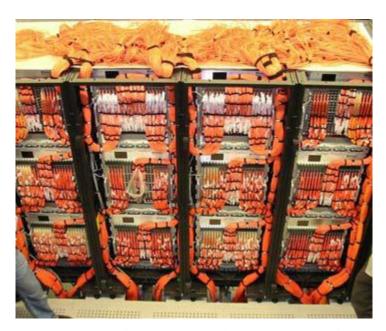

In summary, although material research has provided improvements in electronic interconnects, such as the use of copper instead of aluminum and replacing SiO<sub>2</sub> with other insulators for higher performance interconnects, optical interconnects prevail in providing a high speed, low loss, low latency, massively parallel and cross talk resistant interconnection option [13] from on-chip and chip-to-chip all the way to LAN and long-haul communication applications. In Figure 1- 4 an example of high concentration of rack-to-rack fiber interconnects can be seen in the Barcelona Super Computing Center [14].

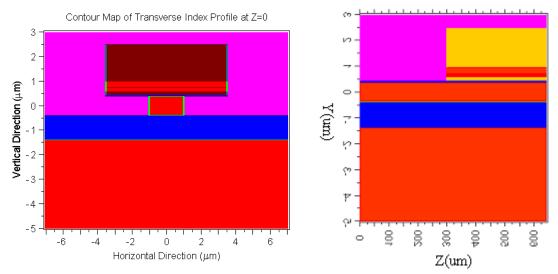

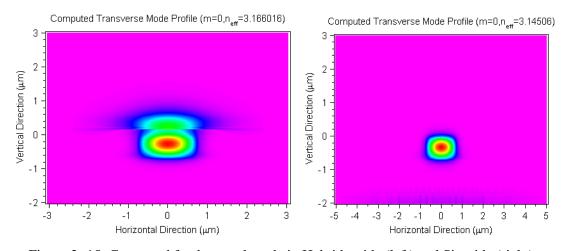

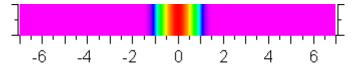

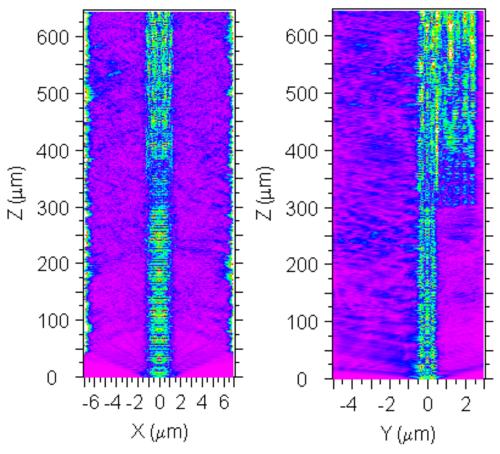

Figure 1-3: Critical length for each recent technology node.

Figure 1-4: Central switch racks, Barcelona Super Computing Center.

## 1.2.2. Evolution of Application of Optical Interconnects

Looking at the timeline of commercial deployment of optical interconnects (and thus copper displacement) [15] gives a good view regarding the history and roadmap of the trend of industry going from electrical to optical data transfer. Table 1- 1 summarizes this trend.

| Year        | 1980's              | 1990's            | 2000's                    |                   | >2012           |                  |

|-------------|---------------------|-------------------|---------------------------|-------------------|-----------------|------------------|

| Range       | Telecom             | Datacom           | Computer-com              |                   |                 |                  |

| System      | WAN, MAN            | LAN               | System                    | Board             | Module          | Chip             |

| Application | Long-haul,<br>metro | Campus, Companies | Inter-rack,<br>intra-rack | Module-<br>module | Chip-chip       | On-chip<br>buses |

| Distance    | Multi-km            | 100's m           | 10's m                    | <1 m              | < 10 cm         | <20 mm           |

| Integration | Cards               | Card edge         | Card edge<br>or on card   | Module            | Chip to<br>Chip | On Chip          |

Table 1- 1: Timeline of the introduction of optical interconnects to different range of systems, from long haul application all the way to on-chip busses [15].

While fibers showed their unbeatable superiority in 1980's in Telecom continental and metropolitan links, and a decade later found their place in LAN networks, it was around 2004-2005 that rack-to-rack fiber interconnects started to be used in super computers. In that time frame, IBM used a combination of copper interconnects for short distances of ≤10m and optical fibers for longer links (20-40m) in the ASCI Purple IBM Federation Switch (LLNL) [15]. The use of rack-to-rack optical links was extended in 2008-9 in IBM Roadrunner, and is a core element in realizing BlueWaters, one of the world's most powerful supercomputers, in a joint effort of IBM and University of Illinois with the goal of being capable of sustained performance of 1 peta flop on a range of real-world science and engineering applications [15], [16]. Figure 1- 5 shows optical fibers running not only rack-to-rack, but also connecting chips in one drawer in an IBM Power7 node network (to be used in BlueWaters system) in which 1.1 Tb/s hub switch and 1 T flop processor are noticeable [17], [18]. Of course there is no doubt that for 200-300 Gb/s speed of data transfer intra and inter drawers in such a system, optical lines are arguably the only solution.

Overall, although there is no doubt that Bandwidth × Distance product is much higher in optical links compared to copper interconnects, bringing in the former to on-chip links in commercial applications had been mainly limited by density and cost factors. However as it is argued in [19], mass production and high volume integration were the driving factors that have allowed today's affordable electronic gadgets to meet consumer budget. Without such a high volume integration, an accurate estimation of cost factor in on-chip optical interconnects is yet to be determined. Therefore, with current research and development cost estimate (i.e.

not having the advantage of high volume integration that VLSI systems have), it will be hard to judge if the cost factor will prevent the introduction of optical interconnects on chip.

Figure 1-5: IMB Power7 IH node hub/switch network.

Needless to say that in order to drive these optical interconnects, having integrated sources is an absolute necessity. However currently most of sources are fabricated off-chip and drive the optical interconnects through suitable special packaging. Figure 1- 6 shows a recent instance of a 24-channel fiber coupled optical transceiver; in which VCSELs and photodetectors are packaged with the chip as well as a fiber array [15], [20].

Figure 1- 6: A recent example of how VCSELs and PDs are currently packaged with fiber arrays on chip for a 300Gb/s transceiver made by researchers at IBM [20].

As the size of electronic devices continues to shrink and the usage of optical communication continues to grow, in addition to higher required data transfer rates and the greater need for higher density and more compact integration of components on chip, "monolithic" integration of electronic circuitry with photonic components (active and passive) has become increasingly desirable and necessary. In the next section, some of the pursued approaches to realize this goal will be presented and discussed with a brief focus on their strengths and weaknesses.

# 1.3. Approaches to Photonic Integration

Due to the importance of having integrated sources, different approaches have been adopted in order to realize lasers on Si ICs. Historically such integration had been primarily of a "hybrid" type, where by using the term "integration", essentially the careful packaging of off-chip fabricated lasers with the IC chip is intended. However this type of integration through packaging does not answer the need for monolithic integration of sources on Si and

thus other approaches have been investigated extensively. Among these attempts, trying to obtain lasing from Si itself, epitaxial growth of III/Vs on Si wafers, bonding III/V and Si wafers together, and in some cases with the removal of the III/V substrate afterwards, can be named. In the following subsections each of these techniques will be briefly reviewed.

Since giving a full breadth of all the attempts to photonic integration is beyond the scope of this introduction, a few examples of each integration approach are covered in each category, and their strengths and weaknesses will be discussed when applicable.

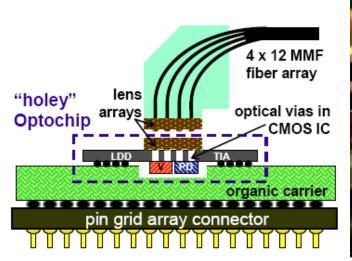

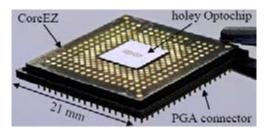

### 1.3.1. Hybrid-Packaging

Traditionally, one approach to integrate photonics with silicon integrated circuits had been "hybrid packaging" [13]. This method entailed manufacturing photonic devices separately and then the photonic chip was bonded to a board with the transceiver electrical circuitry, through wire bonds or bump bonds<sup>2</sup>. This method of integration revealed high parasitics which turned out to be unacceptable for high data rates. A more recent instance of such hybrid assembly and packaging is shown in Figure 1- 6 where VCSELs and PDs are integrated with the CMOS IC via a "holey" optochip [20].

As another instance of such hybrid approach in assembly/integration, researches in the MEMS arena have been interested to look into the integration of photonics on MEMS components, for instance in acoustic and vibration sensing. This can be achieved via interferometric techniques on light emitted from integrated laser components, in which the light path length is changed by an external stimulus like pressure or acceleration. Then this path length change will translate to an amplitude change in a photodetector through diffraction or interference. In [21] an implementation of such a sensor is illustrated using rudimentary assembly techniques. Although the emphasis in this work was not placed on developing a sophisticated small area integration technique, these prototypes put forth the broad area of applications for on-chip photonics when they accompany micro scale MEMS components, although their reliability and endurance should be investigated further.

## 1.3.1.1. Flip Chip Bonding

Flip chip or bump bonding is an approach for hybrid bonding of two material systems. This method (which can be categorized under hybrid packaging as well), has a number of drawbacks. First, it requires all the device electrical contacts to be brought to the front surface

24

<sup>&</sup>lt;sup>2</sup> Since chip-to-chip wire bonds were unreliable, both chips were usually bonded to a board.

which is not usually the case for photonic devices made of III/Vs. This requirement will add to the fabrication steps, increases cost and reduces yield. Furthermore, since the III/V substrate is left on the top of the integrated device and it is absorbing, this poses a limitation when light needs to enter or exit the device vertically. Another significant drawback of this approach is the fact that the final chip will not be flip chip bondable to a system interconnection substrate since the thickness of III/V bonded substrate is much larger than standard bump bonds. One solution to this problem is to deep etch a recess for the III/V substrate on the mother system interconnect substrate, which adds to the complexity of the process and limits the electrical interconnection layout. Also having the III/V substrate prevents 3D stacking of multiple devices.

Removing the III/V growth substrate is advantageous in the sense that for most of active photonic devices, the active layers are in the grown epilayers and the original substrate is not functionally important. Removing the substrate is even beneficial since the back contacts get exposed and in certain applications there will not be a troublesome absorbing substrate present. However, in this approach the substrate removal step is followed by the bonding step (either bump bond or thinner metallization bond), therefore care should be taken not to affect the edges of both substrates; and eventually this approach suffers from some of the drawbacks of the bump bond approach as well.

In an attempt to the integration of optoelectronic components via this method, A. Fritze from Heriot-Watt University describes in his thesis the use of direct laser writing in making waveguides as well as a compatible polymer flip chip bonding [9]. Waveguides are polymerized with HeCd direct laser writing from an in-house-developed PMMA/diacrylate polymer base. With this approach taper writing and 45 degree angle mirrors are fabricated similar to the waveguides which function as interfaces to the external components. For the flip-chip bonding part, the fabrication of bumps and metallization masking is achieved with the same laser writing setup used for waveguides. The goal is to integrate these components with VCSEL lasers to make a fully integrated crosspoint switch. However this work had been the preliminary phases of this project as the testing of an assembled system was yet to be carried out at the time of writing the thesis in [9]. It might worth mentioning that waveguides and flip chip bonds were fabricated on glass substrates at this stage.

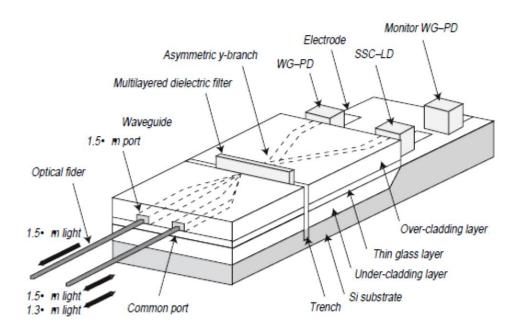

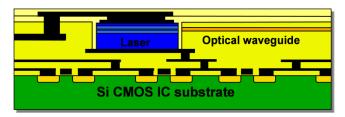

#### 1.3.1.2. Planar Lightwave Circuits (PLCs)

Photonic integrated circuits (PIC) or planar lightwave circuits (PLC) have attracted a good amount of attention in the past decade, and have proven to be very promising in providing a low cost, reliable, and robust integrated photonic solution for industrial applications. PLCs are usually either silica-on-silicon or polymer based. Through this technology a wide range of photonic devices, such as couplers, filters, power splitters, can be integrated on a Si platform [118]. Photo detectors and laser diodes are also integrated on the same platform via flip-chip bonding techniques [119]. In the silica-on-silicon PLCs, the lasers are coupled to SiO<sub>2</sub> based waveguides which in turn couple to comparable dimension fibers that are packaged with the chip. As a result, hybrid integrated WDM transceiver modules have been fabricated for fiber-to-the-home applications based on the PLC silica-on-silicon technology [120]. The schematic in Figure 1- 7 shows this module where photodetectors and lasers, coupled to dialectic waveguides, are flip-chip bonded on the silicon platform. With polymer based PLC also, transceiver modules have been demonstrated [121]. In addition, spot-size converter semiconductor optical amplifiers have been integrated to make a Michelson interferometric wavelength converter on a PLC platform [122].

PLC=platform size : L=14.5mm, W=1.4mm, H=1mm

Figure 1- 7: Schematic of the silica-on-silicon PLC transceiver module, with a flip-chip bonded laser diode and photodetector [120].

Overall, although PLC technology is able to deliver low cost, fiber pig-tailed integrated photonic modules, it is basically a hybrid assembly method, mostly using flip-chip bonding to integrate lasers on a Si platform, and the dimensions and characteristics of it are far from the on-chip compact integration of laser sources on silicon ICs.

#### 1.3.2. Si Based Detectors and Lasers

As an alternative to integration of III/V on Si, extensive efforts had been dedicated to fabricate optical components with Si itself, and thus remove the challenge for integration the first place. The photodetectors that are made on Si (mono material, thus no need for the integration of III/V components) mainly operate at short wavelengths (below 950nm) and suffer from low responsivity, low channel depth and slow speed. Introduction of Ge has brought the wavelength of the SiGe photodetectors to the telecom range and recently in-plane crystalline Ge detectors were developed [23] to increase responsivity and decrease material loss while being integrated on a CMOS chip.

Due to the indirect bandgap of Si (in contrast to the direct bandgap of GaAs and InP), light emission in Si has been a tough challenge. In order to detour this physical hurdle, a set of approaches had been suggested in order to emit light from Si, such as Raman lasers [24] and material engineered light emitting diode structures. In Raman lasers, pure Si crystal and an external laser source are required. In material engineering approaches, porous silicon [25], nano-crystalline silicon [26], SiGe quantum cascade structures [27], dislocation engineered Si [28], Erbium doped SiO<sub>2</sub> [29] and nano-pattering of Si [30] have been exploited for light emission. Most of these approaches need cryogenic temperatures to obtain lasing operation, and they do not fulfill the performance requirements of commercial applications like telecommunications and optical interconnects. Furthermore, lasing in Si, based on stimulated Raman scattering, requires an external optical pump source<sup>3</sup>, which defies the purpose of compact integration of these lasers on IC chips. There has been recent progress in making Si/Ge room temperature lasers [31], but it is still work in progress.

In summary, having lasers made of Si (hence no need for integration), results in suboptimal components with non-optimized performances. In order to be able to separately

27

<sup>&</sup>lt;sup>3</sup> The pump sources usually need to be high power, for instance 1.6W [32]. Such high pump powers not only increases power consumption which is a major concern in ICs, but also induces the nonlinear loss mechanism of two photon absorption (TPA). Introducing delay as well as using a short optical pulse had been helpful in reducing TPA [24].

optimize the performance of optics and electronics on a chip, it is very desirable to be able to optimize the photonic components based on III-V compound semiconductors independently from the Si CMOS VLSI circuitry.

Passive Si-based photonic integrated circuits are not of the main interest of this thesis, thus we only give one example of such integration. At McMaster University, M. Pearson, has shown monolithic integration of WDMs on Si in his PhD [33]. His work consists of design and fabrication of arrayed waveguide grating demutiplexers (AWG) on SOI, and SiGe MSM (metal-semiconductor-metal) photodetectors at 1.55µm, with a major emphasis on "low cost" feature of the developed fabrication technique. Three dimensional growth modes (undulating quantum well layers) where used to enhance the normally very low responsivity of SiGe photodetectors at 1.55µm. Finally the photodetectors are integrated with the waveguides as a demonstration of monolithic integration with any passive optical component. The cost effectiveness of the process primarily relies on the use of local oxidation of silicon (LOCOS) which enables Si microelectronics facilities to fabricate optical components with low change/cost. However optical sources hadn't been discussed in this work and thus this research still emphasizes the need for integration of III/V lasers to make a fully optically integrated circuit.

## 1.3.3. Epitaxial Growth of Compounds on Si Substrate

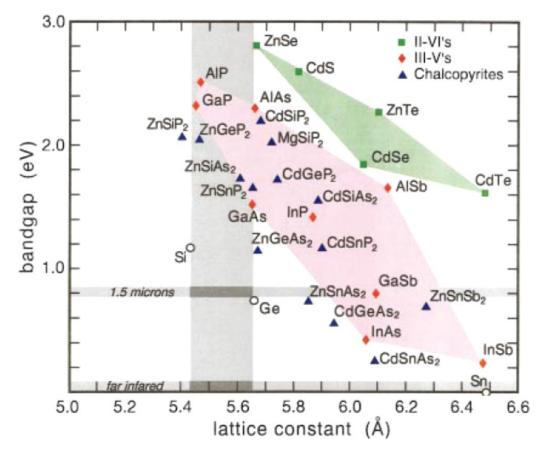

One widely explored approach to integrate optimized III/V optical devices on Si substrates is to heteroepitaxially grow optically active materials (e.g. GaAs), directly on top of Si. However, there are two fundamental issues with epitaxial growth of these optical materials on Si or Ge substrates. Firstly, heteropolar semiconductors, e.g., III-V's and II-VI's, are polar when grown along the (001) direction. This causes a polarity mismatch with the underlying group-IV substrate such as Si. Secondly, most existing optical materials and their alloys do not match the lattice constant of Si or Ge. Figure 1- 8 illustrates the bandgaps and the lattice constants for conventional semiconductor alloys that are used for optically active devices. It can be seen that most of the existing materials have either larger lattice constants or larger band gaps than of interest. They lie in the upper right-hand section of the graph. The desired region for viable compound materials for heteroepitaxial growth, on the other hand, is the intersection of the gray regions, to be lattice matched to Si (or SiGe) and to also provide operation at the wavelength of 1.5µm.

Figure 1- 8: Bandgaps and lattice constants for various traditional semiconductor materials. III/Vs are shown in red diamonds and II-VIs in green squares. The color shaded areas show possible alloyed materials and the gray regions correspond to lattice constants between Si and Ge, and bandgaps corresponding to wavelengths of 1.5 µm and far infrared.

It can be observed from Figure 1- 8 that the III-V alloys that match the telecom operating wavelength ( $\approx 1.5 \mu m$ ) have lattice constants about 8% larger than that of Si<sup>4</sup>, which makes it hard to grow these alloys defect free on Si substrates. This results in threading of misfit dislocation density of  $10^8$ - $10^{10}$  cm<sup>-2</sup> when either of GaAs or InP are grown on Si [34]. Remedies like special surface treatment [35], low temperature buffers [36], growth on patterned substrates [37] and strained superlattices [38], [39] have been looked into to reduce dislocation density to about  $10^5$ - $10^6$  cm<sup>-2</sup>, which is still about two orders of magnitude higher than the case of epitaxial layers grown on native InP or GaAs substrates suitable for CW room temperature operation of III/V laser diodes.

More recently, SiGe [40] and GaSb [41] buffer layers have been employed to realize room temperature GaAs based CW laser diodes on Si, although their reliability remains to be

<sup>&</sup>lt;sup>4</sup> More specifically compared to Si, GaAs and InP have 4.1% and 8.1% lattice mismatches respectively. Furthermore, the thermal expansion coefficient mismatch is 120.4% and 76.9% for these two materials versus Si.

a concern for practical applications [34]. Another promising approach is to exploit a strained Ge-on-Si layer, in which thermal tensile strain of Ge grown on Si makes the Ge bandgap closer to be direct and thus able to emit light through radiative recombination. Photodetectors [42], [43], [44], modulators [45], [46] and CW room temperature optically pumped Ge-on-Si lasers [31] were demonstrated using this technique. Further research is under way to fabricate an electrically pumped laser with the strained Ge on Si idea.

Although exciting research to realize optical gain on Si based substrates is underway, the problems of polarity and lattice mismatch make it very difficult to create optoelectronic integrated devices using heteroepitaxy.

Equally important as the problem of lattice mismatch of III/Vs and Si, is the different thermal expansion coefficient of these materials, which will persist even if layers with matching lattice constant are deposited on the Si substrate.

Therefore, in general the devices made with epitaxial growth of III/Vs on Si, suffer from short lifetimes and low efficiencies due to the problems mentioned above. In addition, the Si CMOS can get damaged by the relatively high temperature growth process [13].

Along the line of attempts to heteroepitaxially grow III/V materials on silicon substrates (the drawbacks of which were discussed earlier), Prof. Joannopoulos group at MIT has been looking into devising new material systems that address lattice mismatch and polarity issues of growing conventional III/Vs (GaAs, InP, etc.) on Si. In [47] they have shown that (ZnSi)<sub>1/2</sub>P<sub>1/4</sub>As<sub>3/4</sub> is a suitable compound that is lattice matched to Si and has a direct bandgap of 0.8eV, which corresponds to the canonical wavelength of 1.5μm, the desired wavelength in optoelectronic applications. They have shown the computational design of the material system and investigated its physical properties using both ab initio total energy and quasiparticle GW calculations.

Furthermore, O. Kwon had looked into the monolithic integration of III-V optoelectronics on Si in his PhD thesis [48] at Ohio State University. In his work he tried to overcome the obstacles of heteroepitaxial growth of III/Vs on Si substrate with the use of graded SiGe relaxed buffers. These buffers result in a low threading dislocation density for the relaxed Ge over large area Si substrate, which makes device quality GaAs components feasible on Si. Kwon first shows the implementation of a visible light QW LED made in GaAs on a Ge substrate. Also, quaternary alloy MBE deposition of the AlGaInP compound for wavelength of 600nm was studied, making fabrication of their second generation surface

emitting AnGaInP resonant cavity LEDs possible on a relaxed SiGe/Si substrate. And finally, stimulated emission was achieved in room temperature strained AlGaInP visible laser diodes on a relaxed SiGe/Si substrate, the third generation of devices in his work. Therefore, if hurdles of growing extremely high quality heteroepitaxial III/V layers and SiGe buffers can be overcome, Kwon's work has shown a potential for optoelectronics integration with this approach. One caveat here is the fact that such approach takes advantage of very close lattice constants of GaAs and Ge, however InP based compounds are not that easy to be integrated on Si with this method of epitaxial growth, as the lattice constant of InP is 3.9% different from GaAs and Ge<sup>5</sup>.

## 1.3.4. Bonding III/V wafer to Si host IC

Another approach to photonic integration had been to bond a photonic III/V device wafer on a Si CMOS wafer in a post-fabrication integration step<sup>6</sup>. Wafer bonding is an option which uses high pressure and temperatures to bond the compound semiconductor wafer to the host Si substrate. One drawback of this technique is the mismatch of Si and III/V wafer sizes. A second issue arises since the required density of photonic elements is generally not the same as the one for Si integrated circuits. Therefore, only a very small fraction of the bonded III-V wafer is being used for making photonic devices, which translates to loosing the majority of the relatively expensive compound semiconductor wafer. These types of losses and costs are not tolerable for commercial low cost components and hence the industry would avoid such techniques to be put into production<sup>7</sup>.

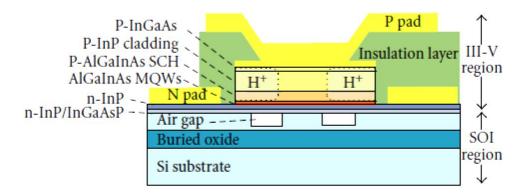

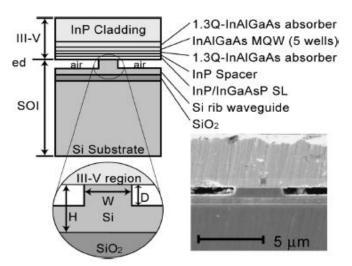

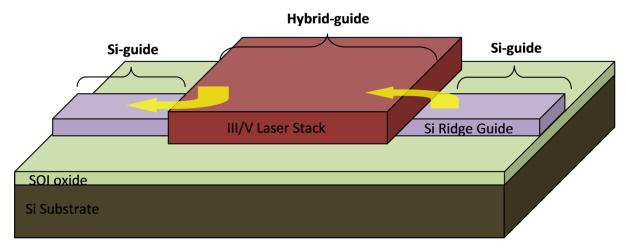

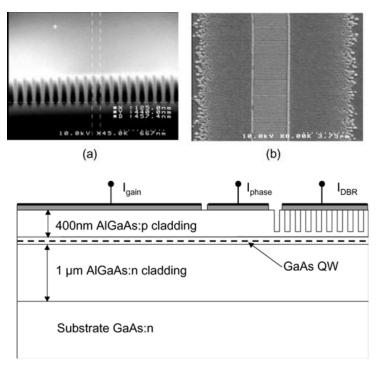

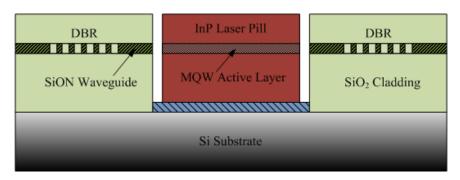

Based on this technique, a promising approach which is recently pursued with a great deal of enthusiasm, revolves around the bonding of an active region III/V wafer on top of a Si ridge waveguide fabricated on an SOI host wafer. Based on this Si-Hybrid idea, researchers at University of California Santa Barbara joint with Intel have developed a library of photonic active components from detectors to modulators and lasers [49]. Since this approach will be discussed in detail and its pros and cons will be looked into in Chapter 2, further details will not be repeated here and the reader is encouraged to follow the discussion regarding this approach to integration in the next chapter.

<sup>5</sup> Lattice constants of Ge, GaAs and InP are:  $a_{Ge} = 5.6461$  Å,  $a_{GaAs} = 5.6533$  Å, and  $a_{InP} = 5.8686$  Å [50]. <sup>6</sup> This approach is also the essence of recently proposed Si-Hybrid integration technique developed by Intel/

UCSB for photonics integration.

<sup>&</sup>lt;sup>7</sup> In Chapter 2, a full investigation of Si-Hybrid approach by UCSB/Intel will be detailed and the strengths and weaknesses of this integration technique will be discussed in depth.

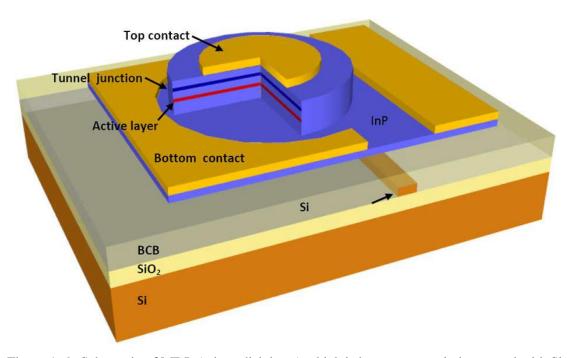

Along the same lines of integration via III/V wafer bonding to a Si host wafer pursued by UCSB and Intel [49], researchers at Ghent University in Belgium have demonstrated a micro-disk laser integrated on Si with an adhesive bonding process using BCB (benzocycobutene) [51]. The schematic of the micro disk laser and the adjacent Si waveguide which carries out the evanescently coupled laser light is shown in Figure 1- 9. The Si waveguide is 500nm wide and has a thickness of 220nm. The laser disk is 580nm thick and 7.5μm or 10μm in diameter. Room temperature CW lasing operation with threshold current of 350μA is observed at 1554nm, and maximum coupled power to the outgoing fiber is measured to be 38μW with 4mA of drive current. Considering the efficiency of grating couplers placed on both sides of the Si waveguide, the maximum power coupled to the waveguide is estimated to be 120μW. Due to low thermal connectivity of the laser, excessive heating had been noticed in earlier generations of these micro-disk lasers and thus a thick (compared to the thickness of micro-disk itself) layer of gold (600nm) is deposited on the top contact of the micro-disk to function as a heatsink.

Figure 1- 9: Schematic of MDL (micro-disk laser) which is heterogeneously integrated with Si waveguide on an SOI substrate [51].

Also, in order to avoid InGaAs p-contact absorption losses and still achieve a good ptype contact in its absence, a tunnel junction is used instead. Quantum wells are made of InAsP and the epitaxial layer sequence is deposited on an InP substrate which is removed subsequently. In another generation of these MDLs, for wavelength tuning purposes, a heater ring is fabricated around the laser disk with tuning rate of 0.31nm/mW.

Overall the output power of such micro-disk structures is quite low, and although the threshold currents are small, the power consumption per bit is about 400fJ/b [51] which needs to be further improved to reach the 100fJ/b target.

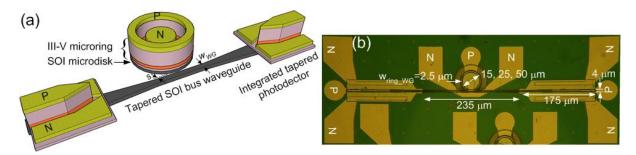

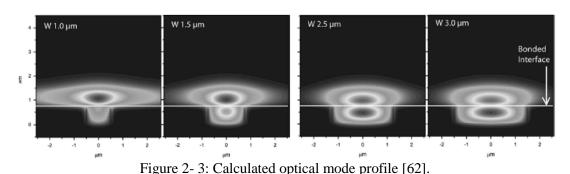

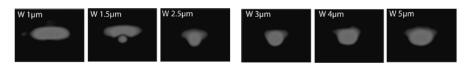

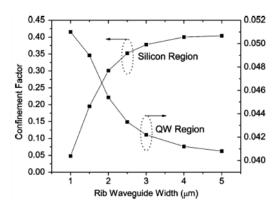

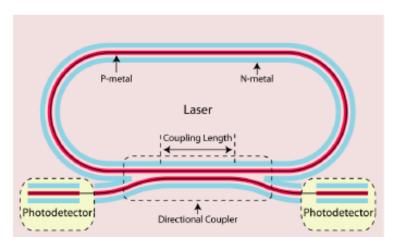

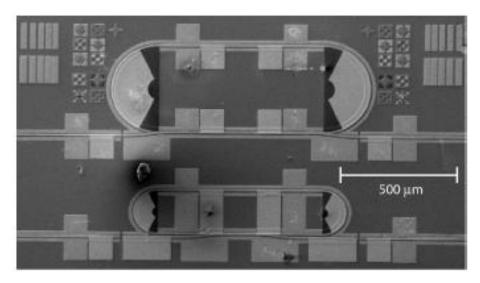

Similar to the micro-disk lasers discussed above, the research group at UCSB/Intel has also made micro-ring lasers [52], [53] with the same integration concept of bonding III/V to Si wafers. Figure 1- 10 show this micro-ring laser bonded on an SOI wafer and coupled to a Si waveguide which terminates with two integrated tapered photodetectors made with the same Si-Hybrid technology. These micro-ring lasers have InAlGaAs-based active region, InP claddings and have diameters ranging from 15µm to 50µm which allow compact integration of a large number of these lasers on chip [34]. In Figure 1- 11 the simulated mode distribution of same micro ring structure along with the adjacent Si waveguide shows that the mode is shifted to the outer area of the micro ring due to the presence of Si waveguide [34].

Figure 1- 10: (a) Schematic and (b) top-view microscopic image of hybrid silicon micro-ring laser with two integrated photodetectors [53].

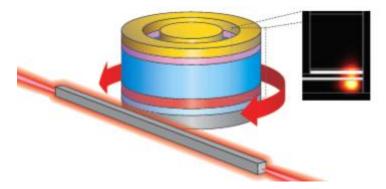

Figure 1-11: Schematic of a Hybrid micro-ring laser with the adjacent Si bus waveguide [34].

A 50µm diameter micro-ring laser fabricated in this approach, and with a waveguide spacing of 250nm, shows CW lasing operation with minimum threshold of 5.15mA at 10°C and with maximum operating temperature of 65°C [53]. The Si-Hybrid approach will be further discussed in Chapter 2.

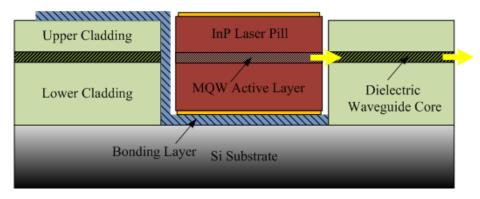

#### 1.3.5. III/V Substrate Removal

Another possible approach is to remove the III/V substrate prior to bonding of the devices to the VLSI substrate (similar to the approach demonstrated in this thesis). The photonic devices are then aligned and bonded to the host substrate with various techniques such as transparent transfer diagram [54] or the pick and place assembly technique used in this thesis. Among the advantages of this approach are achieving a virtually "planar" hybrid integrated optoelectronic circuit as well as access to front and back device contacts, vertical scalability of stacked thin film devices, and the ability of mixing and matching the individually optimized multiple optoelectronic devices integrated with microelectronic circuits using the mainstream microfabrication processing techniques. The only drawback of this integration approach is that the cost is transferred to the assembly phase, which is more or less addressed by the semiconductor industry [13].

The following few examples are among other attempts to photonic integration, which did not perfectly belong to the subsections above. Therefore they are presented here separately.

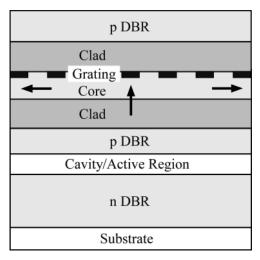

Louderback et al have presented a monolithic VCSEL-based photonic integration on GaAs in [22]. Essentially, with the use of diffraction gratings, the suggested device structure enables the optical output of the VCSELs to be coupled to an internal horizontal waveguide, and the optical signal in the waveguide is tapered off to resonant cavity detectors. More specifically, as shown in Figure 1- 12, a waveguide is placed within the top DBR of the VCSEL structure and the thicknesses are chosen such that the waveguide layers are in phase with the vertical cavity. Then a diffraction grating is etched into the GaAs waveguide core to couple vertically oriented light bidirectionally into the horizontal waveguide. Therefore in Louderback et al work, by integration, mainly the conversion of VCSEL vertical light to horizontal optical waveguides is meant, and the substrate is GaAs, not a Si IC.

Figure 1- 12: Schematic of the structure of the waveguide-coupled VCSELs demonstrated in [22].

In an attempt to integrated photonic components on MEMs devices, a thin film double heterostructure AlGaAs/GaAs p-i-n diode is integrated on a polyimide micromachined platform on silicon by Wilkinson et al in [55]. The objective is that, having optoelectronic devices integrated on movable MEMS actuators can provide micro scale on chip active alignment when high precision alignment of optical emitters/detectors with the rest of the components is required.

In another set of efforts in this field, M. Adams at CalTech has devoted his PhD thesis [56] to use optoelectronics integration for biological and chemical sensing applications. In his work, the goal of achieving a lab-on-chip system, that replaces the cumbersome external interrogation microscope setup, is looked into. The system with the use of integrated lasers and detectors is capable of performing optical analysis both outside of the flow cell a well as directly inside the flow channel. In order to make the integration feasible, modeling, fabrication and the performance of different approaches like the use of CMOS imagers and spectroscopy, the effect of vertical cavity enhancement and photonic crystal lasers (also illustrated in depth in [57] from the same group) have been investigated. As other integrated microfluidic components, soft lithography which uses a silicone based elastomer had been used in fabricating the prototypes. As one may expect, the presence of an integrated light source is a key in making this lab-on-chip idea a reality. With that, the integrated CMOS circuitry not only can detect change of index of refraction of a flow, but also perform analysis on molecular level, as well as study other phenomena like multiphoton generation, optical trapping and Raman processes. Although the vertical cavity approach did not perform as

expected, the attempt shows a large range of applications of integrated optoelectronics in biofluidics as well.

Overall, as reviewed briefly here, the breadth and amount of effort that is devoted to photonic integration on Si demonstrates the importance and vitality of the availability of a reliable, low cost, and monolithic technology for integration of lasers on Si ICs. However, a robust and modular technique that fully answers the requirements of industry for commercial applications is yet to be developed. We believe that the coaxial recess integration approach that we're demonstrating in this thesis is a very promising solution to photonic integration on Si and while not suffering from the issues of other approaches, it is also modular, low cost, CMOS-compatible and has a small footprint on chip. In the following section the basics of this approach will be introduced.

# 1.4. Our Approach to Photonic Integration on Si

Considering the limitations of aforementioned approaches to photonic integration, we propose the coaxial integration technique which proves to be highly modular, flexible, and robust providing very compact, monolithic and planar integration of photonics on silicon ICs<sup>8</sup>.

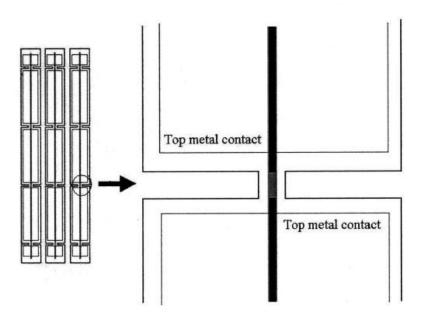

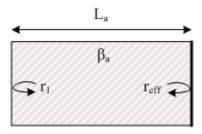

The schematic in Figure 1- 13 shows the general concept of this approach, in which emitted light from an edge-emitting laser diode is coaxially coupled to a dielectric waveguide fabricated on an integrated circuit chip.

Figure 1- 13: Schematic of the coaxially coupled integration approach in which light emitted from a III/V laser bonded in a recess on chip is coaxially coupled to an outgoing waveguide.

8

<sup>&</sup>lt;sup>8</sup> J. Perkins has demonstrated recess integration of VCSEL laser diodes on silicon Integrated Circuits [58] earlier in our research group. In the current thesis such recess integration technique is used for integrating in-plane laser diodes that are coaxially coupled to waveguides fabricated on Si chips.

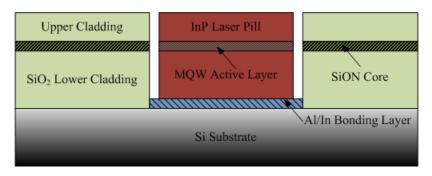

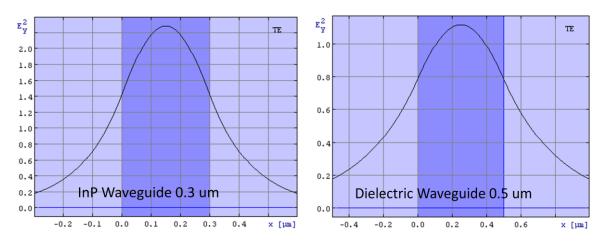

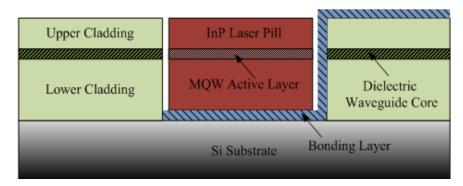

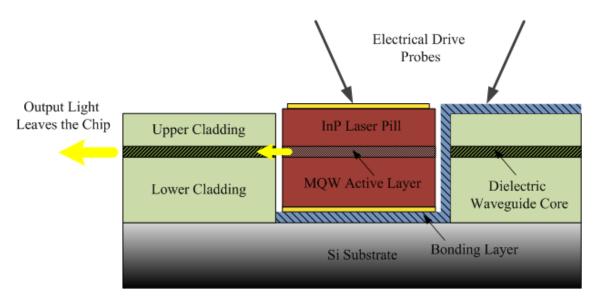

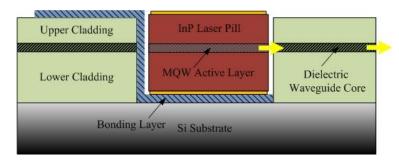

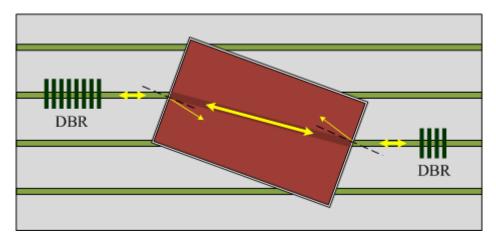

More specifically, in this project the integration of 1.55µm InGaAs/InP in-plane edge-emitting laser diodes in recesses etched into the SiON/SiO<sub>2</sub> dielectric waveguides fabricated on silicon is demonstrated. The active region of the laser diode platelet is coaxially aligned with the silicon oxynitride waveguide core, to ensure the highest coupling between the two. The schematic in Figure 1- 14 depicts the idea of this integration approach, where light from III/V laser diode is coaxially coupled to on-chip optical waveguide on silicon. The laser backside n-contact is brought to the wafer front side through a bonding layer that also ensures a strong mechanical bond of the laser platelet in its recess.

Figure 1- 14: Schematic showing the coaxial integration of edge emitting laser platelets in SiO<sub>2</sub> recesses on Si substrate.

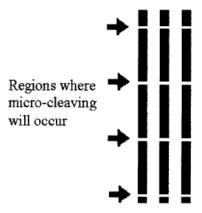

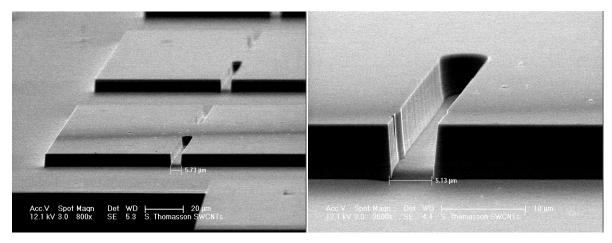

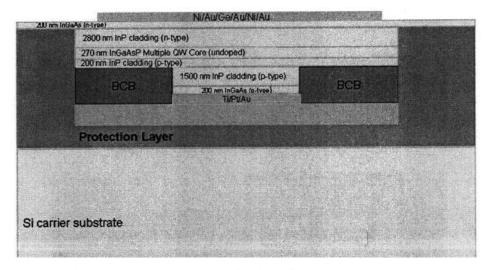

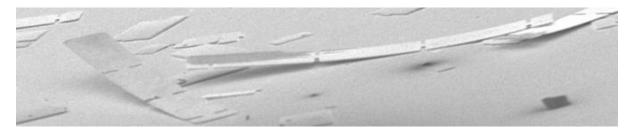

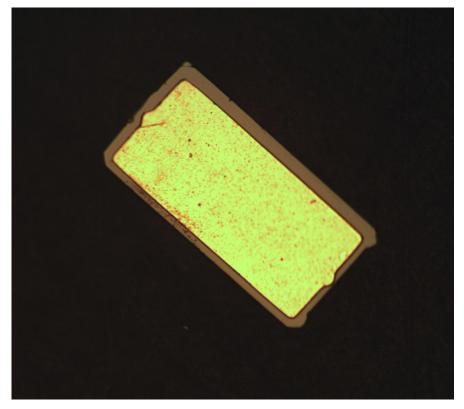

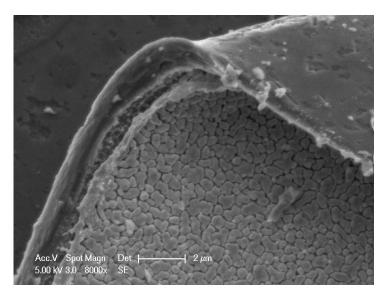

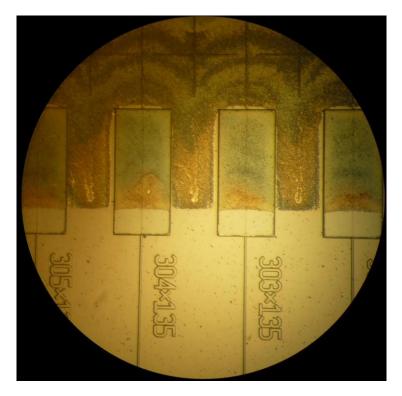

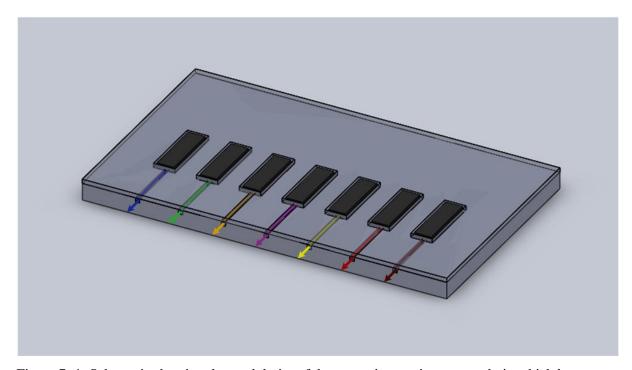

In order to make the coaxially coupled integration approach feasible, previous PhD theses have solved different aspects of this integration. More specifically, E. Barkley has focused his PhD thesis [59] on the fabrication of SiON waveguides and etching the 6 to 7 $\mu$ m deep recesses in their path, and J. Rumpler made an impressive contribution by fabricating micro-cleaved edge emitting laser platelets with dimensions of  $300\mu$ m×150 $\mu$ m×6.3 $\mu$ m, in his PhD thesis [60].

Having these two components on hand, in this thesis, the integration process is demonstrated and optimized.

## 1.5. Thesis Flow

In Chapter 1, the importance of optical interconnects and their gradual industrial adoption from long-haul all the way to rack-to-rack interconnects over that past few decades has been reviewed. With that view in mind, the importance of having on-chip monolithically

integrated sources to bring such application more into computer.com arena, is clear. Therefore, different approaches to realize integrated lasers on Si, ranging from Raman lasers to heteroepitaxial growth of III/V material on Si, and Evanescent-Si-Hybrid approach were presented and discussed. Finally, our proposed integration approach which we believe solves the issues with aforementioned methods was briefly described.

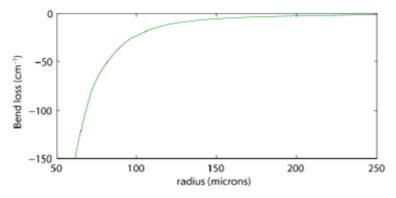

In Chapter 2, the promising integration approach of Evanescent-Hybrid-Si is discussed in further detail and a suggestion to reduce bend diameters in the large footprint race-track structure is made and its effect is simulated using the BeamPROP software. Then the Hybrid-Si and Coaxial integration approaches are compared and pros and cons of each approach are listed so that based on each application, the most suitable approach can be adopted.

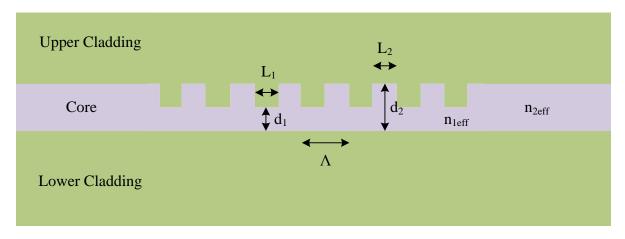

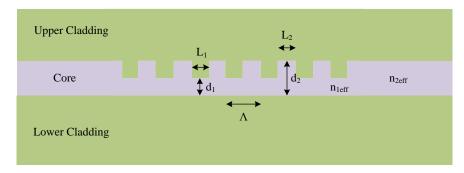

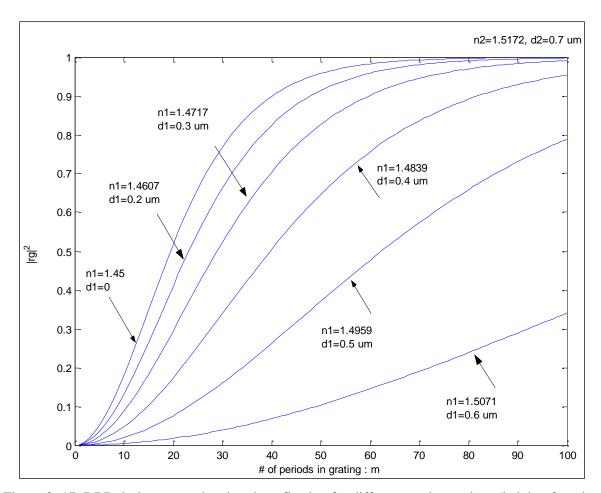

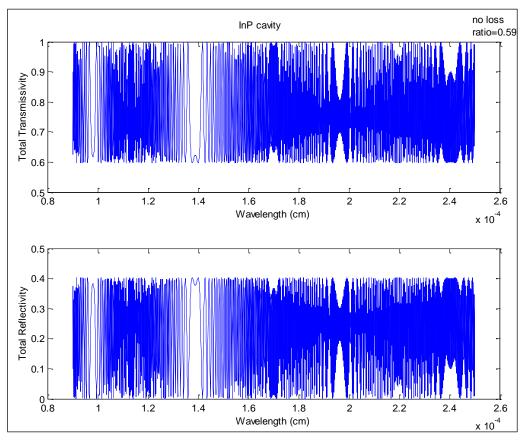

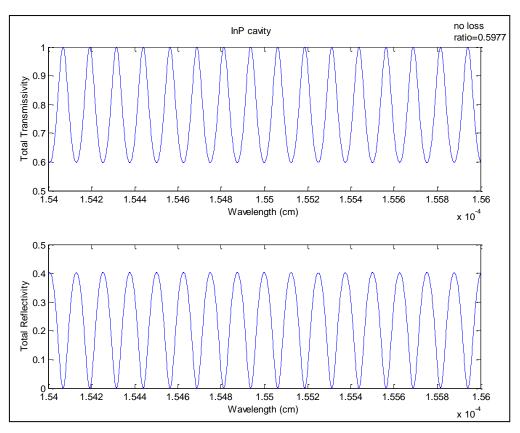

In Chapter 3, design and optimization efforts to find the best dimensions and refractive index for dielectric waveguides used in our coaxially integration approach, as well as the optimized gap filling index is presented. Also, Distributed Bragg Reflectors (DBRs) were designed through three different methods of Finite Difference Time Domain (FDTD), Transmission Matrix Method and Bi-directional Beam Propagation Method (BPM) to provide higher reflectivity external mirrors for the laser cavity.

Since the integration method demonstrated in this thesis highly relies on the two key components of InGaAs laser platelets and dielectric waveguides fabricated on Si substrate, the fabrication of these two components which had been done by two former PhD candidates in our research group (E. Barkley [59] and J. Rumpler [60]), is discussed in Chapter 4 for ease of referencing on how these components were made.

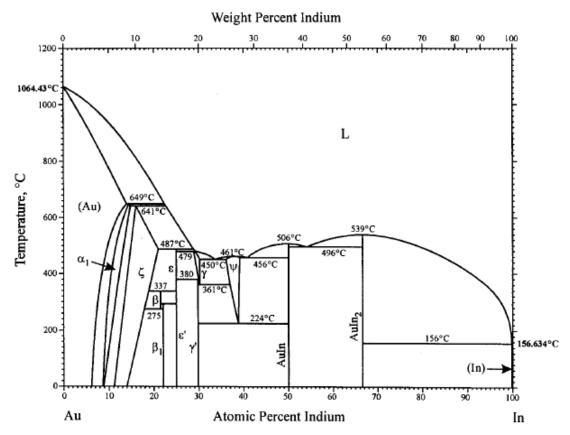

In Chapter 5, the details of the integration process demonstrated in this thesis are explained. Also the process to accurately characterize the dimensions of the formerly fabricated dielectric waveguides is described, which is of paramount importance in ensuring best vertical alignment between laser active region and dielectric waveguide core. Furthermore, the bonding layer composition optimization, deposition and pattering is discussed. The discussion is followed by explaining the procedure for the assembly of laser platelets in recesses, as well as the pressure bonding mechanism. By the conclusion of Chapter 5, laser platelets are successfully integrated in recesses on a Si substrate, well aligned to dielectric waveguides, and are ready for measurement and characterization of the full integrated structure.

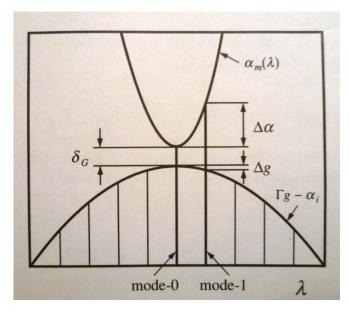

In Chapter 6, the detailed measurements of these integrated lasers for pulsed and continuous wave electrical drive is presented as well as IR images of the beam shape leaving

the chip. The spectrum of CW lasing of the integrated lasers is studied and a significant enhancement to mode suppression ratio is observed. A three-mirror cavity model is presented and good agreement between calculated MSR and the measurement results is achieved. Furthermore, external quantum efficiency and characteristic temperature for the integrated lasers are extracted from the measurement results. Finally, a number of explored approaches with the goal of quantifying the coupling losses in laser-waveguide facet are presented and the results are discussed.

Lastly, in Chapter 7, the discussion on the strengths and limitations of the coaxial integration approach is presented and suggestion are made on how to improve the current generation of the components, considering the desired features of single-mode operation, full CMOS compatibility, low cost, and being fab-less, which help in commercializing an approach by the industry.

# Chapter 2

# **Assessment of Hybrid Evanescent Approach to III/V-Si Integration**

As mentioned in the first chapter, one approach to photonics integration is to fabricate light emitting components in III/V or II/VI compound material systems and then integrate those active components on a Si substrate.

To achieve this integration step, there are a couple of approaches such as flip-chip bonding, coaxial coupling and vertical coupling of membrane devices<sup>1</sup>. Being concerned with the need for sub-micron alignment to ensure efficient coupling, and time and cost intensive nature of it, scientists at UCSB and Intel have proposed Hybrid Evanescent technology to address the requirement of sub-micron alignment of other integration approaches<sup>2</sup>.

We were interested in understanding the Intel/UCSB approach and its strengths and weaknesses, particularly in comparison with the coaxial coupling approach being pursued in

<sup>&</sup>lt;sup>1</sup> Hattori et al. have fabricated membrane disc lasers vertically coupled to a passive Si waveguide [123]. In this approach, alignment reduces to two dimensions, but still an important issue.

In fact our proposed coaxial approach does not impose the need for costly active/passive submicron alignment. Since both laser pills and wells are  $150\mu m$  in width, horizontal alignment is usually very well obtained. By the same token, there is no room for the lasers to have rotational misalignment either. As it will be discussed in Chapter 5, the bonding layer thickness is carefully optimized to ensure the best vertical alignment. The only remaining factor left for the human/automated assembler to care about is the gap length. Since the laser have a  $\pm 1.2$  variation in length depending on where lasers cleave in the notch area using micro-cleaving approach, therefore in the experimental phase of this research a series of wells with various lengths were fabricated on chip, thus the user had flexibility to choose which well will fit the picked up laser the best. This can be efficiently done by either a human user or an automated process. Once the laser is assembled in the well, before breaking the vacuum, the micropipette (used for pick & placing the laser pills) can be used to slide the lasers to one facet of the recess for the highest coupling to that waveguide. Therefore the alignment issue is not a big hurdle by the nature of our approach.

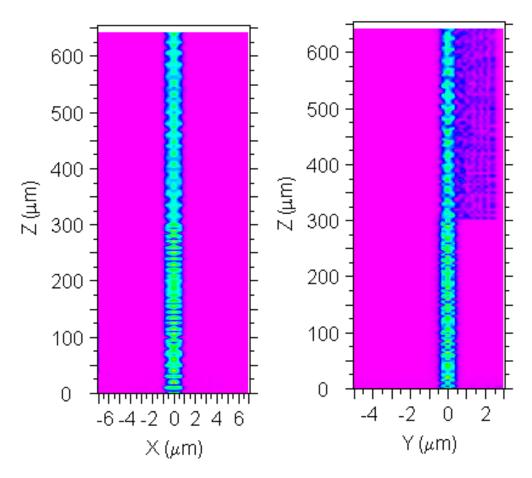

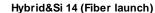

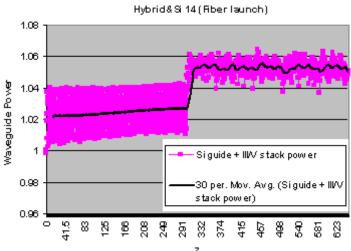

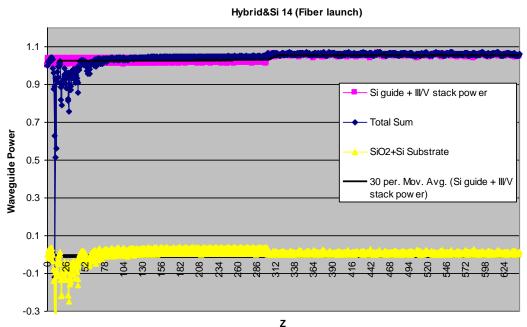

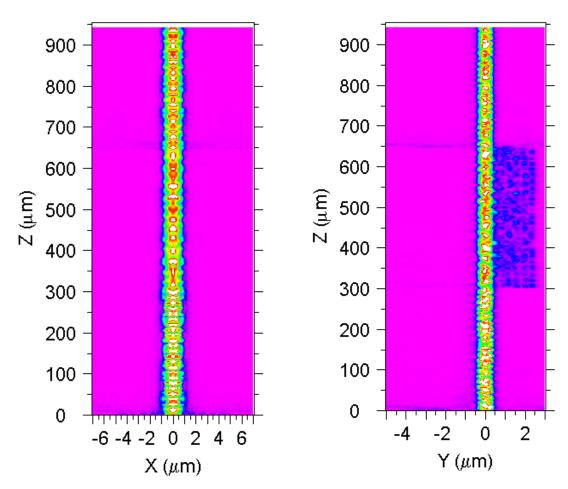

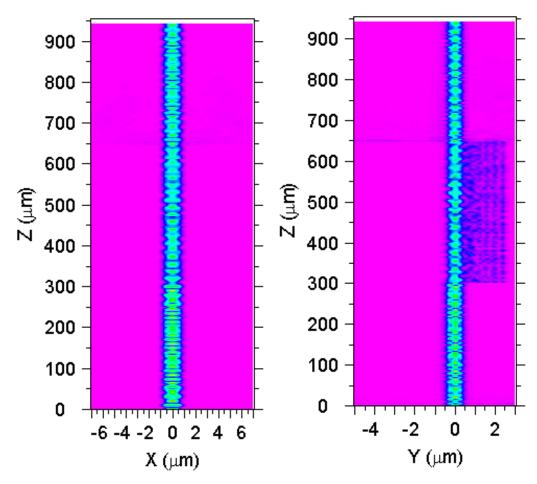

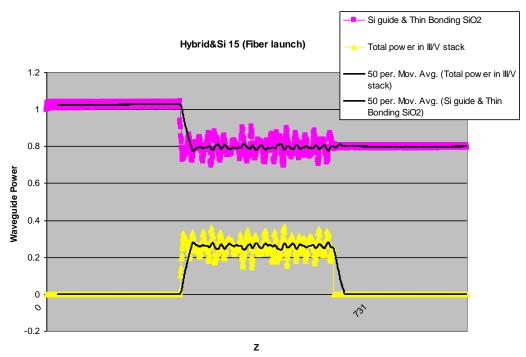

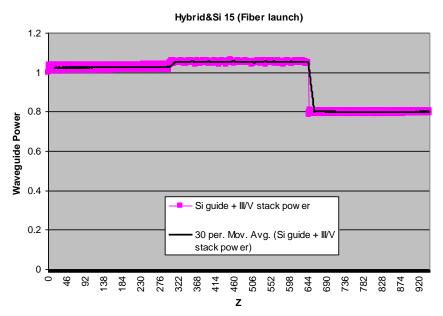

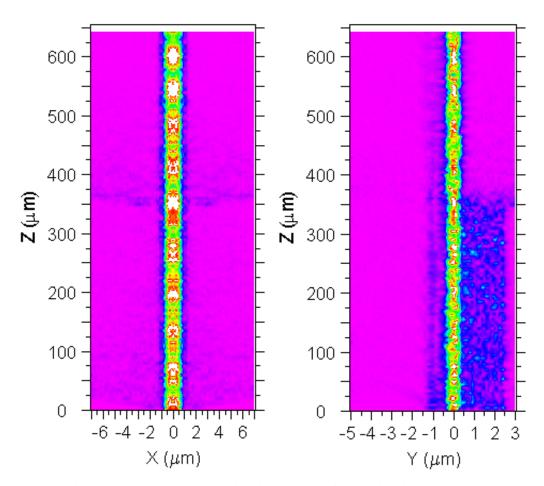

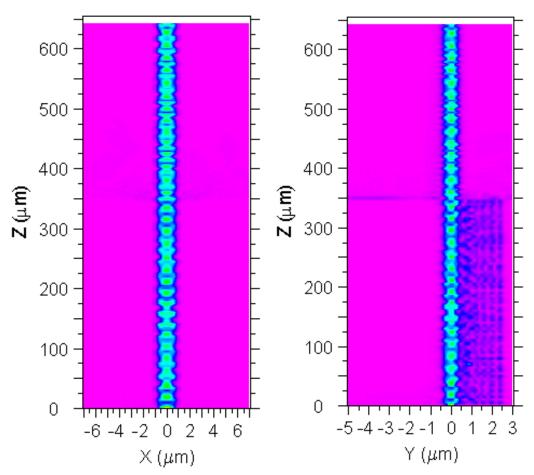

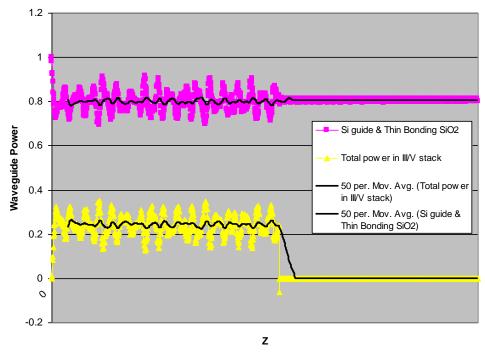

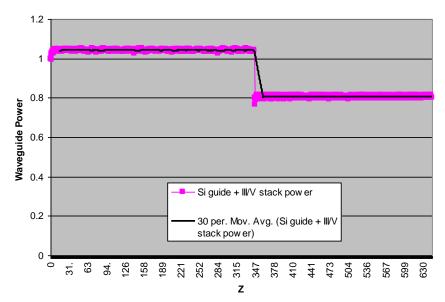

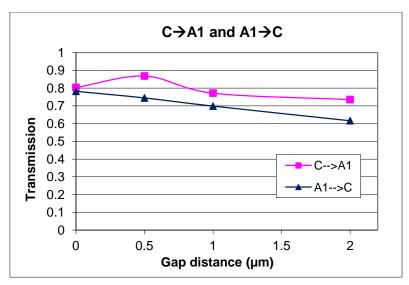

our group at MIT. Therefore, through optical simulations with the BeamProp software, power losses due to evanescent coupling transitions were investigated. Our goal was to see how much scattering and reflection is caused when the optical mode inside a silicon waveguide is coupled vertically to a III/V gain stack, and when it couples vertically back to the silicon ridge waveguide. Our simulation results have shown that unless a well designed taper is used<sup>3</sup>, an insertion loss of almost 20% in power is seen in the transition between Si/Hybrid/Si waveguides.

In addition to discussing the simulated results obtained using the beam propagation method to model insertion loss and scattering at Hybrid/Si interfaces, this chapter will also look into other pros and cons of Hybrid Evanescent Vertical Coupling approach. Finally, the two integration methods, i.e. the coaxial recess integration and Si-Hybrid approaches, will be briefly compared with respect to heat transfer, coupling loss, spatial footprint in chip, reliable manufacturability and mechanical endurance, aligning, monolithic integrability with other components on chip, and industry requirements on device characteristics like threshold current limit.

# 2.1. A Review of the Hybrid Evanescent Approach

Since the simulations presented later in this chapter are focused on characterizing the transitions in Hybrid Evanescent integration, it is essential to first give an introduction to the basics of this approach and the structure of the devices made using this technique. Therefore in the following, a review is given while trying to keep the content concise.

The idea behind the Hybrid Evanescent approach is that the optical mode inside a silicon ridge guide is evanescently coupled<sup>4</sup> to a III/V stack bonded on top of it and thus sees

2

$<sup>^3</sup>$  In further developments of the Hybrid Evanescent Coupling technique, an amplifier with integrated photodetectors was fabricated using this approach [70], in which tapers had been used to couple light from III/V active region to the passive Si-ridge area preceding the photodetector. In that case the taper loss is estimated to be in the range of 0.6-1.2dB, which is comparable to the  $20\%\approx1\,\mathrm{dB}$  loss that our simulations have shown for the reflection/scattering loss should an abrupt transition had been used. Thus the taper does not entirely address the problem of the mode's hardship in coupling back from high index III/V stack to lower index Si-ridge guide.

While in initial publications on this technique, the term "evanescent" had been emphasized, it was dropped for later developments on the project. The latter seems to suit the reality of the structure more, as the mode shape is shared between the Si-ridge and III/V stack, with more concentration of the guided mode on either of these two

gain [61]. This technique has been used to fabricate the following range of devices [49] showing the flexibility of this approach in realizing a series of active photonic components.

- Optically pumped AlGaInAs-Si Fabry Perot laser [62]

- Electrically pumped AlGaInAs-Si Fabry Perot laser for  $\lambda$ =1550nm [63]

- Electrically pumped AlGaInAs-Si Fabry Perot laser for  $\lambda$ =1310nm [64]

- Hybrid Evanescent Photodetectors [65]

- Race-track laser for  $\lambda=1550$ nm integrated with two monitoring photodetectors [66]

- Fabry Perot mode locked laser (with saturable absorber region) for  $\lambda=1550$ nm [67]

- Race-track mode locked laser [68]

- Optical amplifier integrated with photodetectors [69], [70]

- Electroabsorption modulator [49]

- Microring laser [52], [53]

- AWG based multiwavelength laser [113]

- DFB laser array using quantum well intermixing [114]

Beside the initial introduction to the fabrication steps of this approach (which is mostly common among the devices above), when it comes to reviewing specific fabricated devices, the focus will be primarily on the lasers i.e. Fabry Perot cavity and race-track lasers since our major interest is in integrated laser diodes. The details about the rest of the devices listed above can be found in the corresponding references.

## 2.1.1. Fabrication Process in Hybrid Evanescent Approach<sup>5</sup>

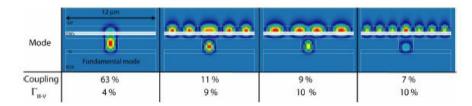

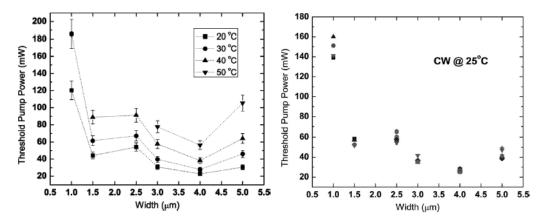

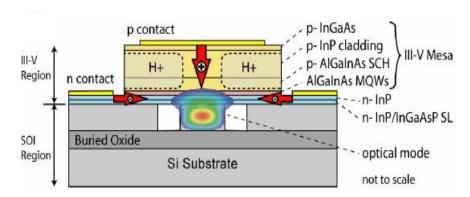

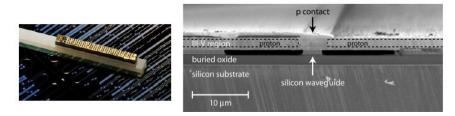

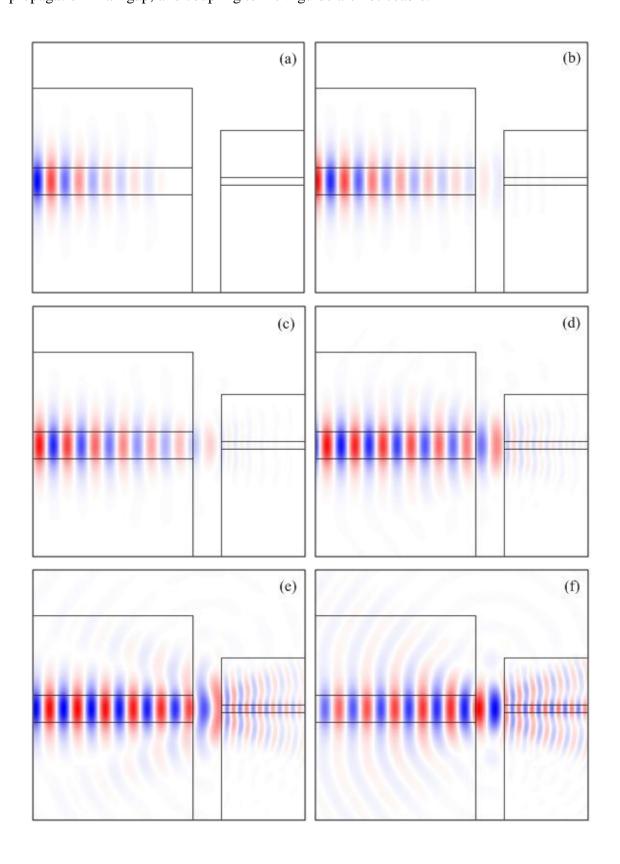

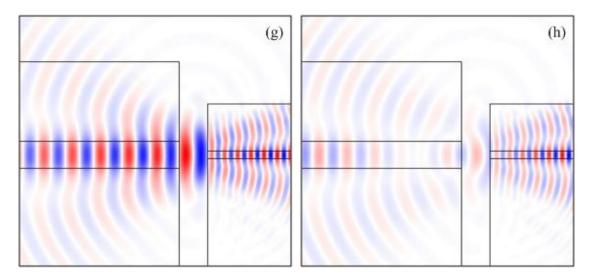

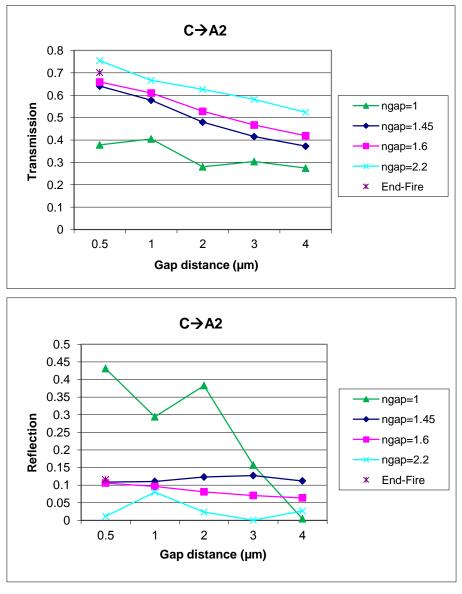

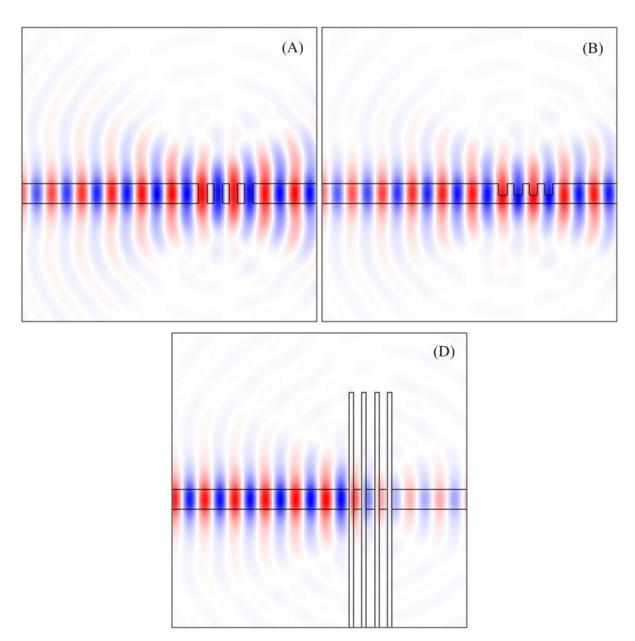

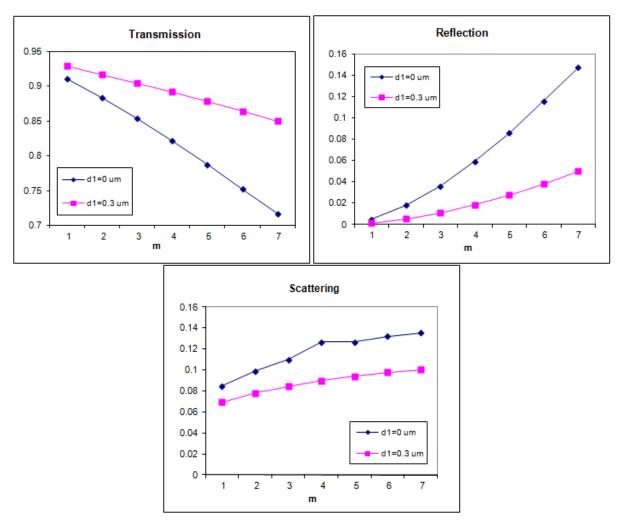

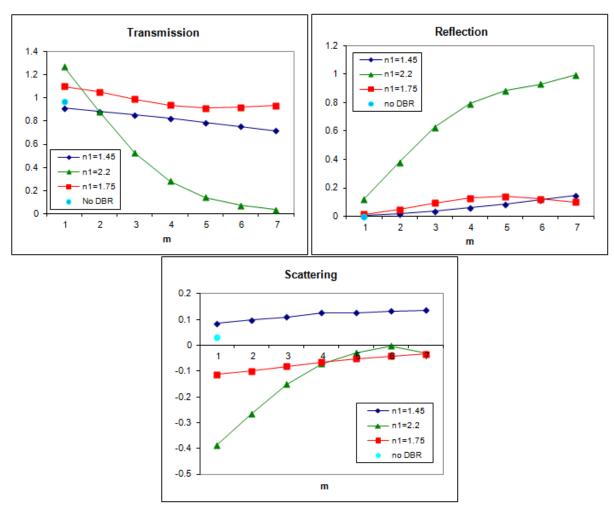

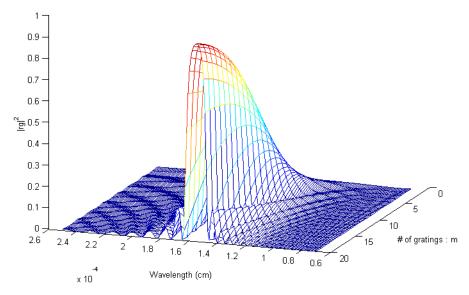

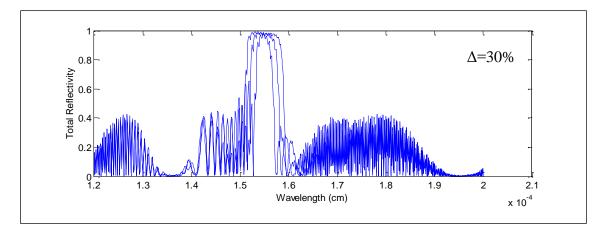

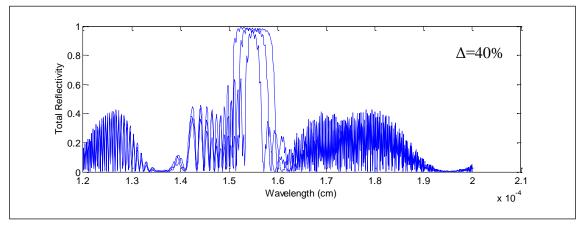

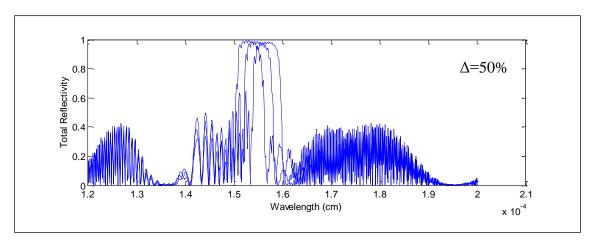

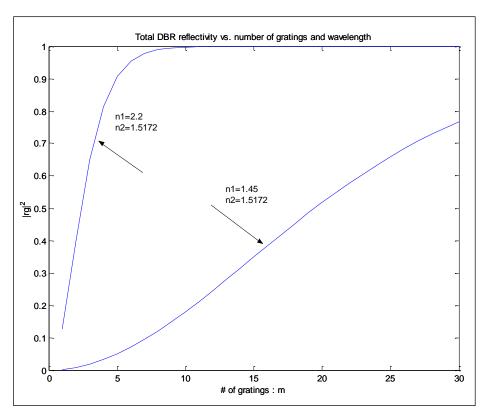

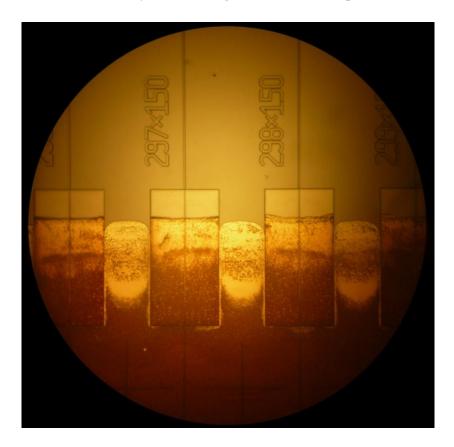

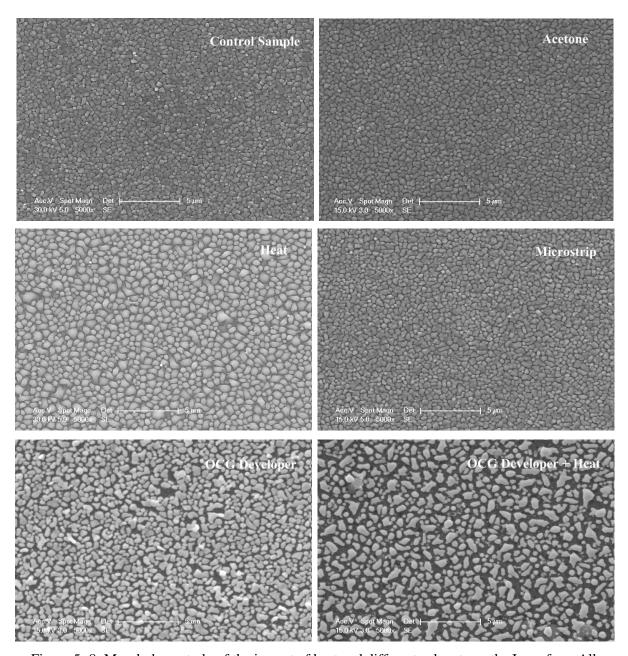

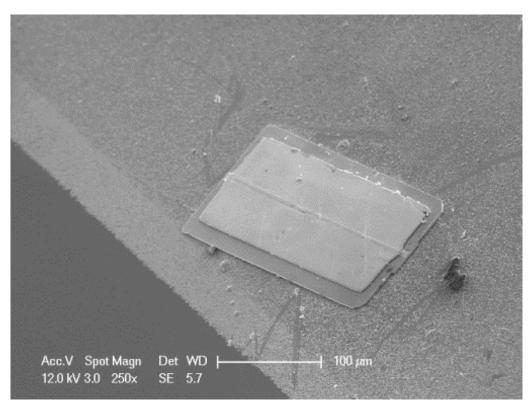

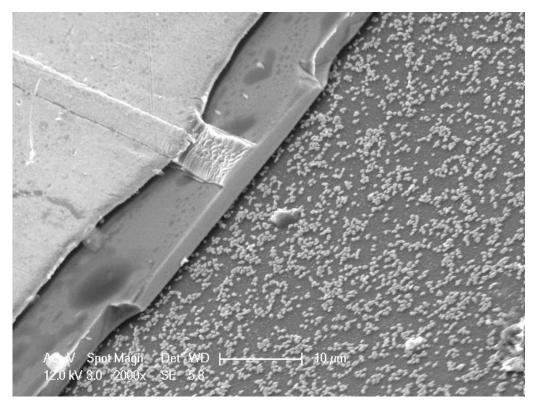

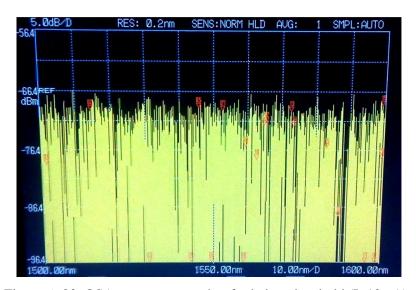

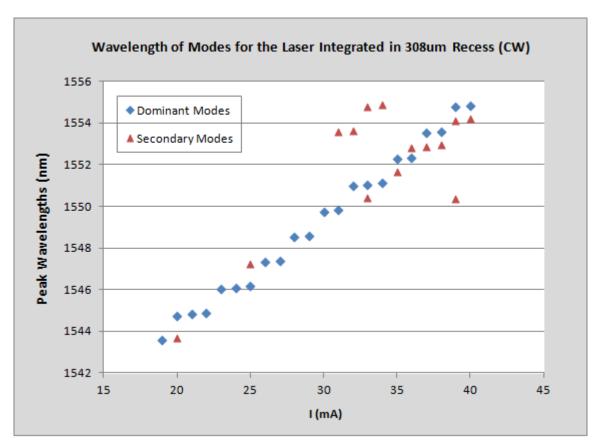

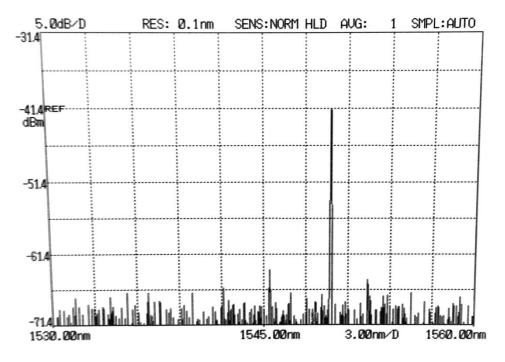

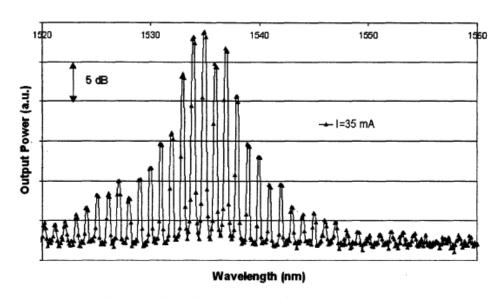

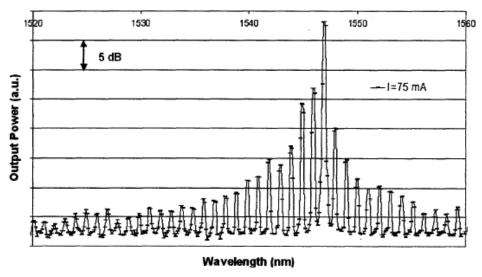

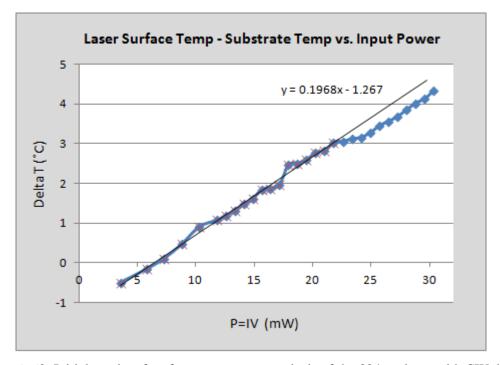

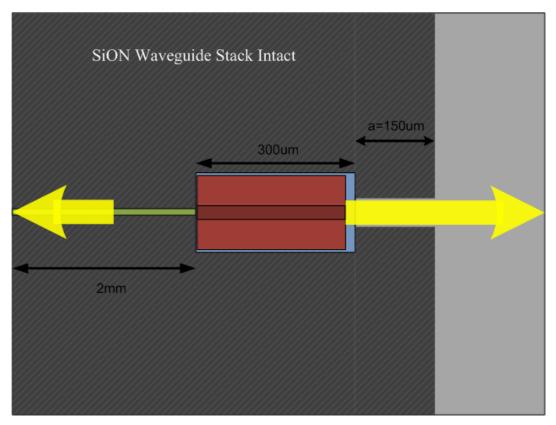

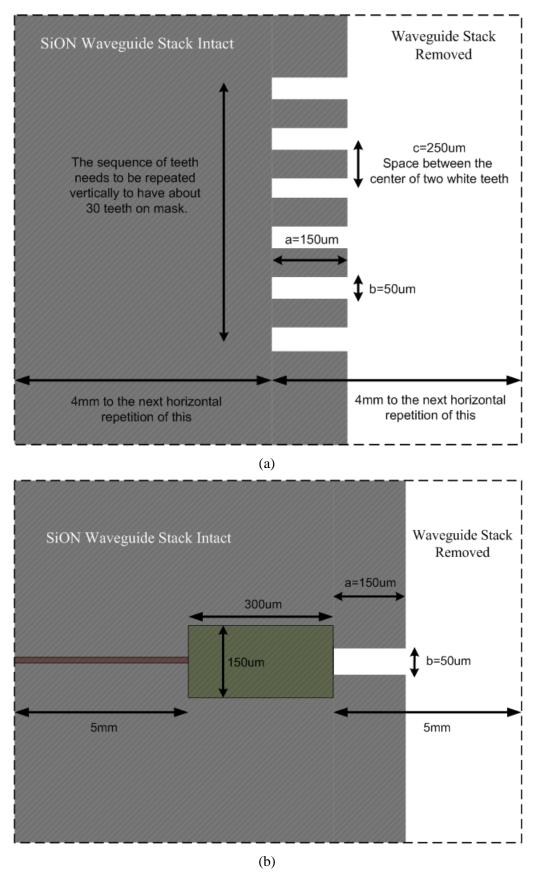

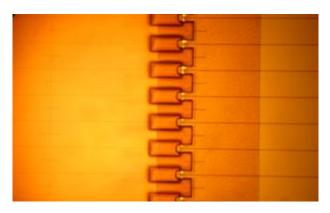

In this technique an InP wafer<sup>6</sup> (containing AlGaInAs QWs) is bonded to an SOI wafer which includes Si ridge passive waveguides. Bonding is done via low temperature O<sub>2</sub> plasma assisted wafer bonding. The low temperature prevents two wafers from cracking due to the mismatch between the thermal expansion coefficients of Si and InP (i.e. direct wafer bonding at 600°C cannot be used).