#### **Body Powered Thermoelectric Systems**

by

Krishna Tej Settaluri

B.Sc., Massachusetts Institute of Technology (2011)

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Master of Engineering in Electrical Engineering and Computer Science

at the Massachusetts Institute of Technology

May 2012

Copyright 2012 Krishna Tej Settaluri. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part and in any medium now known or hereafter created.

| Certified by |                                                                                   |

|--------------|-----------------------------------------------------------------------------------|

| 5            | Dr. Anantha P. Chandrakasan                                                       |

|              | Department Head, Electrical Engineering and Computer Science<br>Thesis Supervisor |

| Certified by |                                                                                   |

| U            | Dr. Timothy Hancock                                                               |

|              | Assistant Group Leader, MIT Lincoln Laboratory                                    |

|              | Thesis Supervisor                                                                 |

| Accepted by  |                                                                                   |

| 1 5          | Professor Dennis M. Freeman                                                       |

|              | Chairman, Masters of Engineering Thesis Committee                                 |

#### Body Powered Thermoelectric Systems

by

Krishna Tej Settaluri

Submitted to the Department of Electrical Engineering and Computer Science

May 21, 2012

In partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science

#### Abstract

Great interest exists for and progress has be made in the effective utilization of the human body as a possible power supply in hopes of powering such applications as sensors and continuously monitoring medical devices [1]. This report furthers into the area of thermal energy harvesting, which focuses on using the temperature differential generated between the human body and the ambient environment to generate power. More specifically, a body-powered, thermoelectric-based power supply and system will be introduced and examined, with hopes that this technology will be utilized alongside low-power, medical monitoring applications in order to achieve self-sufficiency. This report also analyzes the performance of existing thermoelectric-based body-powered energy harvesting applications and compares that with the new design introduced in this work. The new designs were able to output upwards of  $25\mu W/cm^2$  or, equivalently,  $280\mu W$  for the entire heat sink system. Additionally, this report details the physics associated with thermoelectric modules, addresses the issues with modern thermoelectric heat-sinks, introduces two new types of wearable, conformal heat sinks, quantifies the performance of the body-powered thermoelectric supply, tests a flexible EKG processing board, and analyzes future paths for this project.

Thesis Supervisor: Dr. Anantha P. Chandrakasan Title: Department Head, Electrical Engineering and Computer Science

Thesis Supervisor: Dr. Timothy Hancock Title: Assistant Group Leader, MIT Lincoln Laboratory

#### Acknowledgements

It is an understatement to say that the following individuals merely assisted in the development of this thesis. Rather, they shaped my abilities to research, think, and appreciate the world.

To begin, my supervisors, Professor Anantha Chandrakasan and Dr. Timothy Hancock, helped tremendously in creating possible research paths and providing resources to run my experiments. I also thank Professor Rajeev Ram for creating a foundation for my future research path and Dr. Jeremy Muldavin and Chang-Lee Chen at the MIT Lincoln Laboratory for their support. I acknowledge the VI-A Program and the UROP program for their generosity. I also thank Kathy Sullivan, Gary Hackett, Gabrielle Brewington, and Margaret Flaherty for their help.

During my time with this work, I confided in many individuals for their help and opinions. Professor Vladimir Stojanovic, Professor Rahul Sarpeshkar, Professor Steven Leeb, Duke Xanthoupoulos, and, of course, Gim Hom have been a wonderful source of ideas and inspiration. This thesis would not be complete without help from Professor Mary Boyce of the Mechanical Engineering Department, Chris Boyce, and Duncan Boyce for their help with the flex trace technology. All of my friends in both ananthagroup and POE have provided assistance and sanity during the best and worst of times. To begin, Marcus Yip and Dr. Katey Lo have been extremely patient and helpful in assisting me and getting things working. Specifically, I thank Marcus Yip for his assistance with the EKG board design and Dr. Katey Lo for assisting in running simulations for the heat sink designs. Arun Paidimarri, Nachiket Desai, Michael Price, and others in ananthagroup have been a great source of support and sanity during long nights in lab. Jason Orcutt, Parthi Santhanam, and others in POE have also been amazing. I sincerely thank them all for sharing their brilliance :-)

Next, my friends and peers have been extremely patient, gracious, and caring. I frequently looked to them for support, ideas, and, at times, mimicking punching bags. I thank Kevin Zheng and Kat Kononov for their support and assistance in the development of the SAR ADC. I thank the ultra-low power quad core team composed of Allen Yin, Nathaniel Salazar, Joseph Lane, and Danny Bankman for their help in the development of the front end amplifier (and a lot more). To them, specifically, I say thanks and "rooby roo??". Don't worry, they'll understand. I also thank Artur Dmowski for billiard tips, Shahriar Khushrushahi, Al-Thaddeus Avestruz, and Kevin Fischer for life tips, Oz Wassie for being awesome, Vinay Ramasesh and James Noraky for putting up with my incessant altitude humor, and, of course, Ishaan Chugh for supplying tea, irrational comedy, and pre-historic soundtracks.

Lastly, I cannot begin to comprehend the impact my family has had in the development of this thesis as well as in the development of my character. Yet, I will attempt to document it here nonetheless. My father, Raghu, my mother, Sandhya, and my sister, Keertana, have been there for me day in and day out. They are the smartest and most loving people I know.

Thanks.

-Krishna May 15th, 2012

# Contents

| 1        | Intr | roduction                                                                                                   | 12        |

|----------|------|-------------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1  | Overview                                                                                                    | 12        |

|          | 1.2  | Thermoelectric Generators                                                                                   | 13        |

|          |      | 1.2.1 Seebeck Effect                                                                                        | 13        |

|          |      |                                                                                                             | 14        |

|          | 1.3  | •                                                                                                           | 15        |

|          | -    |                                                                                                             | 15        |

|          |      |                                                                                                             | 16        |

|          |      |                                                                                                             | 17        |

|          | 1.4  |                                                                                                             | 19        |

|          |      |                                                                                                             | 19        |

|          |      | 1.4.2 EKG System                                                                                            | 20        |

|          |      | Overview                                                                                                    | 20        |

|          |      | Introduction to EKG                                                                                         | 20        |

|          |      |                                                                                                             | 21        |

|          |      |                                                                                                             | 23        |

|          |      | Analog-to-Digital Converter (ADC)                                                                           | 24        |

|          |      |                                                                                                             | 25        |

|          | 1.5  |                                                                                                             | 25        |

|          | 1.6  |                                                                                                             | 26        |

|          |      |                                                                                                             |           |

| <b>2</b> |      |                                                                                                             | <b>29</b> |

|          | 2.1  |                                                                                                             | 29        |

|          | 2.2  |                                                                                                             | 30        |

|          | 2.3  |                                                                                                             | 31        |

|          |      |                                                                                                             | 31        |

|          |      | 1 0                                                                                                         | 34        |

|          |      |                                                                                                             | 37        |

|          | 2.4  | Experimental Procedure and Analysis                                                                         | 39        |

|          |      | 2.4.1 Fabrication $\ldots$ | 39        |

|          |      | 2.4.2 Tests and Results                                                                                     | 43        |

|          |      | Open-Circuit Voltage and Optimum Power Characterization                                                     | 43        |

|          |      | Field Test                                                                                                  | 44        |

|          |      | Output Loads and Applications                                                                               | 45        |

|          |      | LED Load                                                                                                    | 46        |

|          |      | Wireless Transmitter Load                                                                                   | 47        |

|          | 2.5  | Conclusion                                                                                                  | 49        |

| •        | ы    |                                                                                                             |           |

| 3        |      |                                                                                                             | 51        |

|          | 3.1  |                                                                                                             | 51        |

|          | 3.2  |                                                                                                             | 51        |

|          |      | - · · · · · · · · · · · · · · · · · · ·                                                                     | 51        |

|          |      | 3.2.2 Thermal Impedance Optimization                                                                        | 54        |

|              |              | 3.2.3  | Simulation Results                                                      |

|--------------|--------------|--------|-------------------------------------------------------------------------|

|              | 3.3          | Fabric | ation and Experimental Results                                          |

|              |              | 3.3.1  | Design Procedure and Supplies                                           |

|              |              |        | Flex PCB Design                                                         |

|              |              |        | Hot Side Copper Strip Population                                        |

|              |              |        | TEG Array Placement and Bonding                                         |

|              |              | 3.3.2  | Results                                                                 |

|              |              | 3.3.3  | Design Limitations and Improvement                                      |

|              |              | 0.0.0  | Cold-Side Copper Dimensions   61                                        |

|              |              |        | Trace Width and Electrical Parasitics   61                              |

|              | 3.4          | Conch  |                                                                         |

|              | 0.4          | Conch  |                                                                         |

| 4            | Flex         | c EKG  | System 64                                                               |

|              | 4.1          |        | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $64$        |

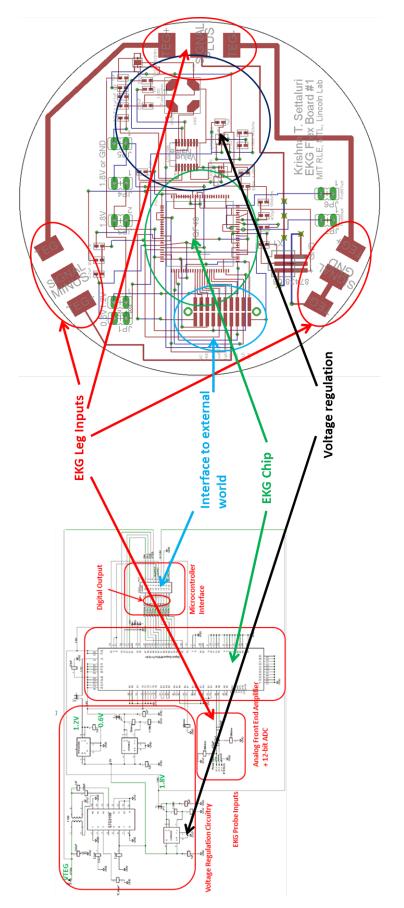

|              | 4.2          |        | System Introduction and Analysis                                        |

|              |              | 4.2.1  | Overview                                                                |

|              |              | 4.2.2  | EKG Board Design and Sub-Systems                                        |

|              |              | 1.2.2  | Introduction                                                            |

|              |              |        | EKG Legs                                                                |

|              |              |        | Centralized Processing Circuitry Area (CPCA)                            |

|              |              |        |                                                                         |

|              |              |        | 0 1                                                                     |

|              |              |        | Voltage Regulation Circuitry       71         FKC Dash - Least       71 |

|              |              |        | EKG Probe Inputs                                                        |

|              |              |        | Microcontroller Interface                                               |

|              |              |        | Printed Circuit Board Layout and Design                                 |

|              |              |        | Interface Between EKG Legs and CPCA                                     |

|              | 4.3          |        | ation and Testing of the Flex EKG board                                 |

|              |              | 4.3.1  | Fabrication    76                                                       |

|              |              | 4.3.2  | Testing and Results                                                     |

|              |              |        | Voltage Regulation Stage                                                |

|              |              |        | Front End Amplifier and ADC Chip                                        |

|              |              |        | Issues and Next Steps                                                   |

|              |              |        | Flex Substrate and Solder Connections                                   |

|              |              |        | ESD Protection On Chip 80                                               |

|              |              |        | Initial Microcontroller Port Noise                                      |

|              |              |        | Next Steps                                                              |

|              | 4.4          | Conclu | •                                                                       |

|              |              |        |                                                                         |

| <b>5</b>     | Con          | clusio | n 83                                                                    |

|              | 5.1          |        | e Research Path                                                         |

|              |              |        |                                                                         |

| $\mathbf{A}$ | 805          | 1 Sam  | ple Code for Chip Programmability 86                                    |

| Б            | <b>D</b> 124 |        |                                                                         |

| в            |              | -      | p Sub-Systems Analysis 96                                               |

|              | B.1          |        | Chip Sub-Systems                                                        |

|              |              | B.1.1  | Front End EKG Amplifier                                                 |

|              |              |        | Schematic Design                                                        |

|              |              |        | Layout                                                                  |

|              |              |        | Results                                                                 |

|              |              | B.1.2  | DC/DC Converter                                                         |

|              |              |        | Schematic and Design                                                    |

|              |              |        | Results                                                                 |

|              |              | B.1.3  | 8-bit SAR ADC                                                           |

|              |              |        | Design                                                                  |

|              |              |        | Block Diagram                                                           |

|              |              |        |                                                                         |

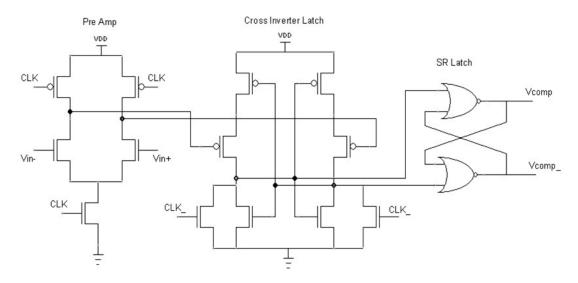

|       | Comparator Architecture                  | 103 |

|-------|------------------------------------------|-----|

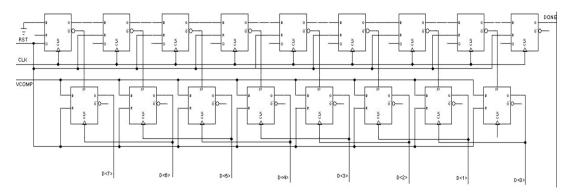

|       | SAR Logic                                | 104 |

|       | Results                                  | 104 |

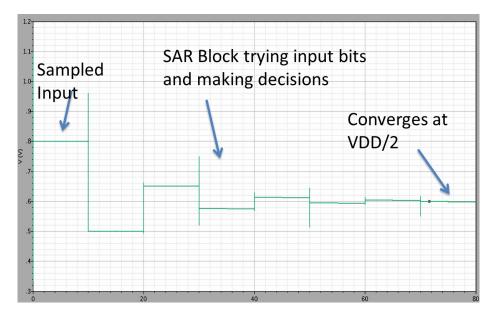

|       | Capacitor Array Voltage into Comparator  | 104 |

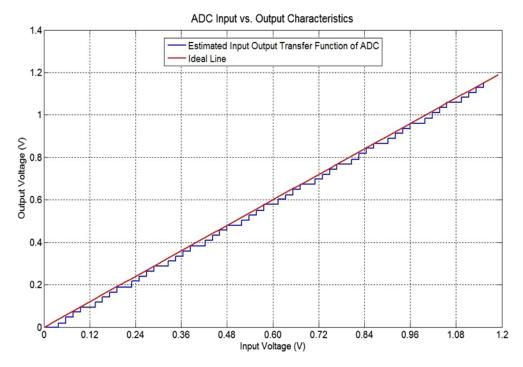

|       | ADC Input-Output Characteristics         | 105 |

| B.1.4 | DC/DC Converter + 8-bit ADC Test Results | 105 |

# List of Figures

| 1.1   | The Seebeck Effect, when viewing a single thermocouple [7]                              | 13              |

|-------|-----------------------------------------------------------------------------------------|-----------------|

| 1.2   | The internals of a TEG, focusing on a single thermocouple upon applying a temper-       |                 |

|       | ature gradient [5].                                                                     | 14              |

| 1.3   | Current TEG-based wearable applications                                                 | 16              |

| 1.4   | The wearable, wristband heat sink ensures that the system remain comfortable and        |                 |

|       | effective. A model and image are shown [41].                                            | 16              |

| 1.5   | The flat(left), length-grooved(middle), and checker-board(right) heat sinks are illus-  |                 |

| 1.0   | trated                                                                                  | 17              |

| 1.6   | A model of the flex TEG is shown.                                                       | 19              |

| 1.7   | A model of the body-powered EKG acquisition system containing the various layers        | 10              |

| 1.0   | is shown.                                                                               | 19              |

| 1.8   | A high-level block diagram representation of the EKG acquisition system is shown.       | 20              |

| 1.9   | A sample EKG waveform with the two phases is highlighted.                               | 21              |

| 1.10  |                                                                                         | 00              |

| 1 1 1 | capacitor.                                                                              | 22              |

| 1.11  | A 35mV input boost converter [32] is shown. Further discussion will continue in         | 94              |

| 1 10  | Chapter 4                                                                               | 24              |

|       | A sample EKG front-end topology is shown [19]                                           | $\frac{26}{27}$ |

|       | A detailed schematic of the three-probe EKG front-end circuit [19]                      | 21              |

| 1.14  | logic block, track/hold circuitry, and a DAC array.                                     | 28              |

| 1 15  | The CC1111 features and contents.                                                       | 28<br>28        |

| 1.15  |                                                                                         | 20              |

| 2.1   | A composite slab containing materials of differing thermal conductivities               | 30              |

| 2.2   | Thermal model of the TEG and wristband heat-sink system.                                | 31              |

| 2.3   | The heat-sink thermal resistance is composed of the plate and the boundary resistance.  | 32              |

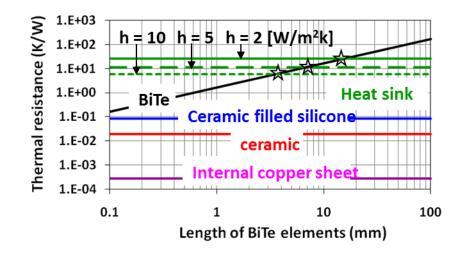

| 2.4   | Simulation of thermal resistances of the various components of the heat-sink system     |                 |

|       | as a function of BiTe element length.                                                   | 33              |

| 2.5   | The simplified thermal model of the heat-sink system, for power optimization            | 34              |

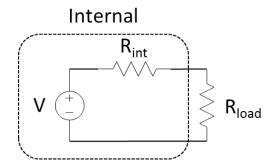

| 2.6   | A voltage source with an internal impedance and load to show power optimization         | 34              |

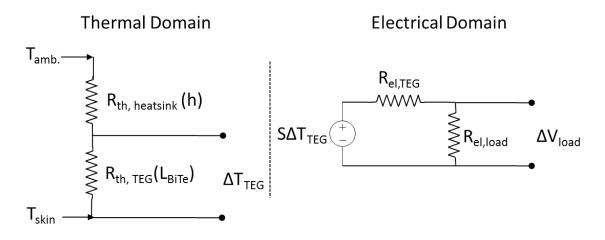

| 2.7   | Thermal and electrical domains of the TEG and heat-sink system.                         | 35              |

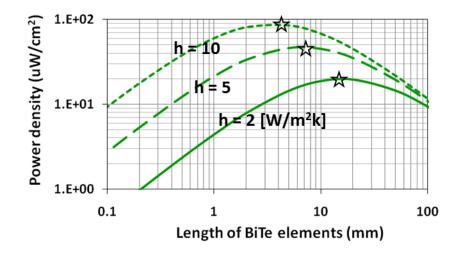

| 2.8   | Output power density of the TEG given particular lengths of the BiTe elements [41].     | 36              |

| 2.9   | Patterned designs for maximizing the convection coefficient.                            | 37              |

|       | Finite-elements results for the differing surface areas                                 | 38              |

|       | The temperature distribution of the plain heat-sink design                              | 38              |

|       | The pitch of the length-grooved heat-sink                                               | 39              |

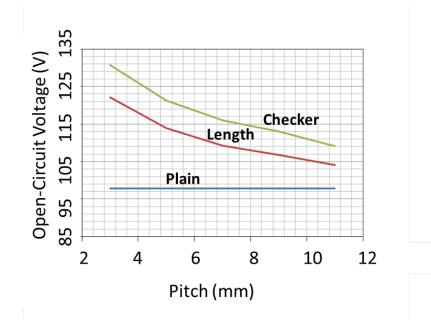

|       | The output voltage was reduced by increasing pitch due to a decrease in surface area.   | 39              |

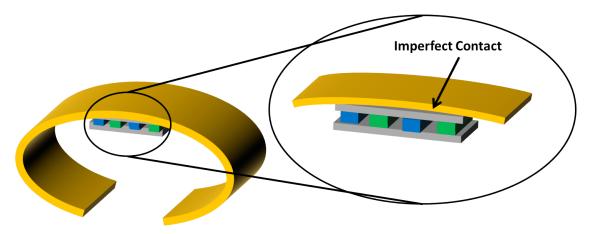

| 2.14  | The completing of the rolling process yields circularly shaped wristband, with imper-   |                 |

|       | fect contact between the TEG and cold-side plate.                                       | 40              |

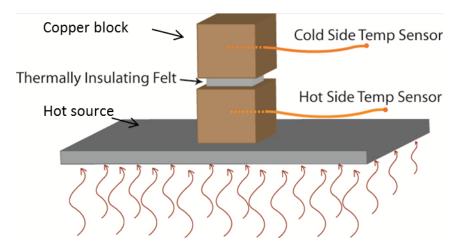

|       | The press flattened the contact area surrounding the cold-side of the TEG               | 40              |

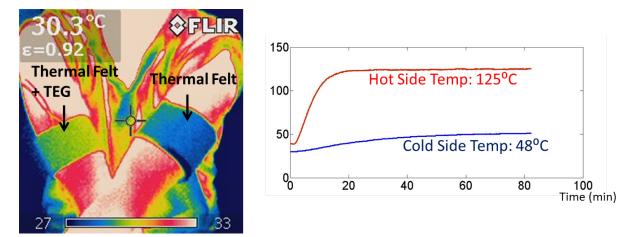

|       | Test set up to characterize the thermally insulating felt                               | 41              |

| 2.17  | Characteristics of the thermal felt when placed on the arm, left, and on the hot plate, |                 |

|       | right                                                                                   | 41              |

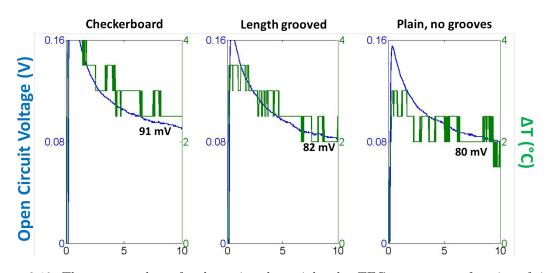

| 2.18  | The completed checkerboard heat sink is shown.                                          | 42              |

|         | The output voltage for the various heat sinks plus TEG systems as a function of time.                 | 43       |

|---------|-------------------------------------------------------------------------------------------------------|----------|

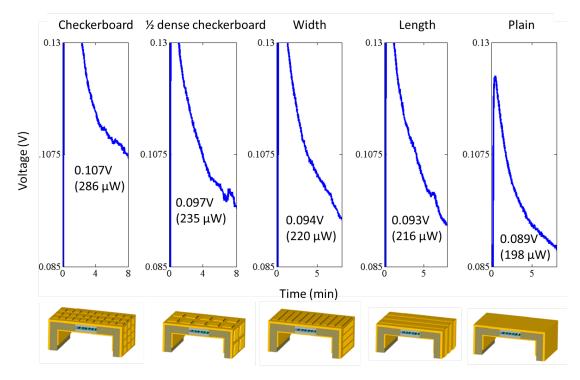

| 2.20    | The optimum power output was measured by connecting a $10\Omega$ resistor as the output               | 4.4      |

| 0.01    | electrical load.                                                                                      | 44       |

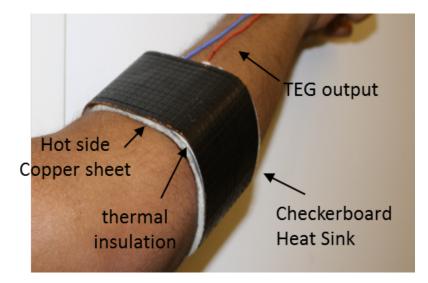

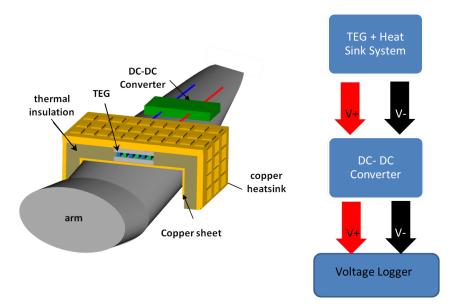

| 2.21    | The setup for the field test used a commercial DC/DC Converter as well as a voltage logger.           | 45       |

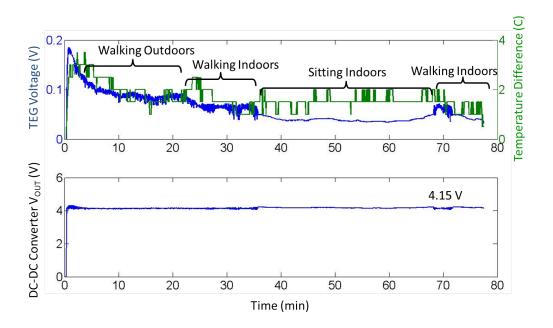

| <u></u> | The data collected from the 80-minute field test shows not only the TEG output (also                  | 40       |

| 2.22    | the DC/DC Converter input), but also the $\Delta T$ of the TEG and the output (also                   |          |

|         | $DC/DC$ Converter input), but also the $\Delta 1$ of the TEG and the output of the $DC/DC$ Converter. | 46       |

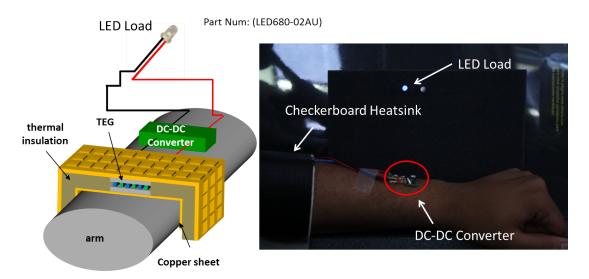

| 2 23    | A model and image of a body-powered LED system are shown.                                             | 40<br>46 |

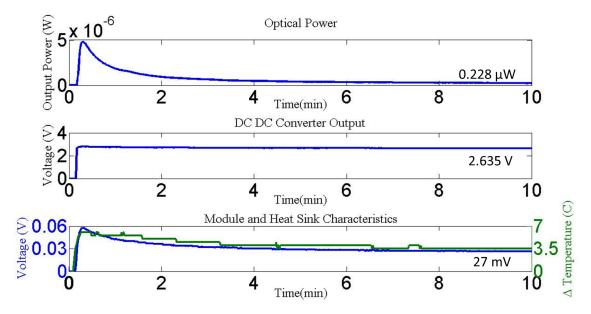

|         | The quantitative characteristics of the LED-loaded DC/DC Converter output are                         | 40       |

| 2.24    | shown, along with the DC/DC Converter output as well as the TEG voltage output                        |          |

|         | and temperature differential.                                                                         | 47       |

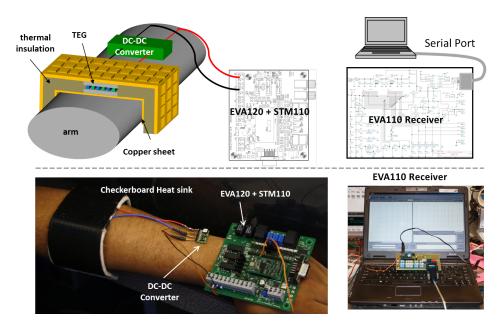

| 2.25    | A model and image of the test setup used to characterize the wireless transmission                    | ті       |

| 2.20    | abilities of the TEG and checkerboard heat sink source                                                | 48       |

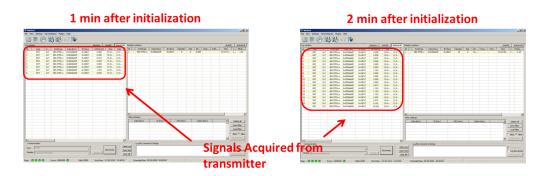

| 2.26    | The user-interface provided with the EnOcean kit records any incoming transmissions                   | 10       |

| 2.20    | from the EVA120+STM110 transmitter board. Screenshots of two different times                          |          |

|         | after beginning communication with the board are shown                                                | 48       |

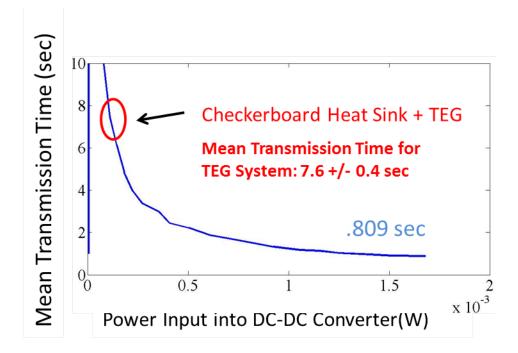

| 2.27    | A power sweep was conducted with the appropriate mean wireless transmission time                      | 10       |

| 2.2.    | plotted for each input power level.                                                                   | 49       |

|         |                                                                                                       | 10       |

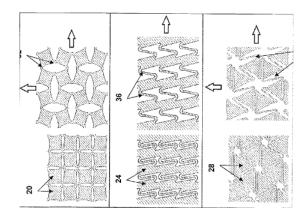

| 3.1     | Unidirectional and bi-directional flex patters [46]                                                   | 52       |

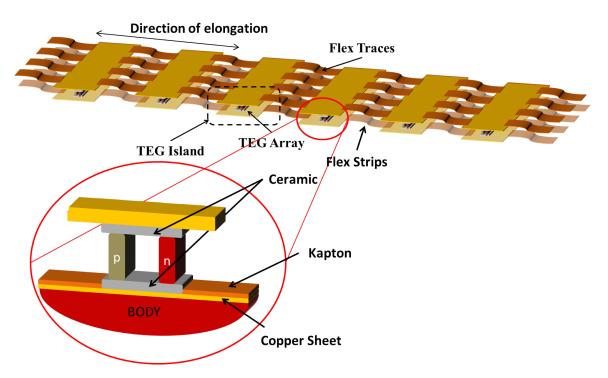

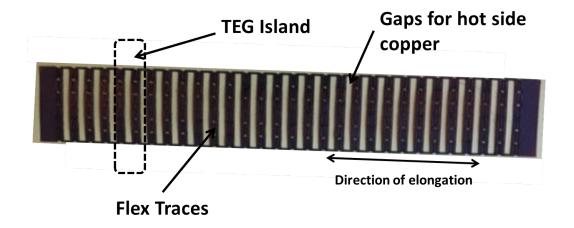

| 3.2     | Flex TEG design.                                                                                      | 52       |

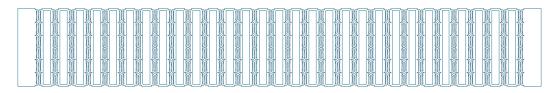

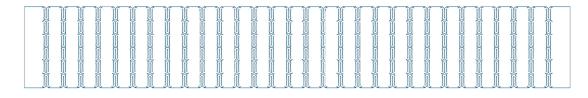

| 3.3     | Top view of the flex kapton layer. Each island is interconnected with the flex patterns.              | 53       |

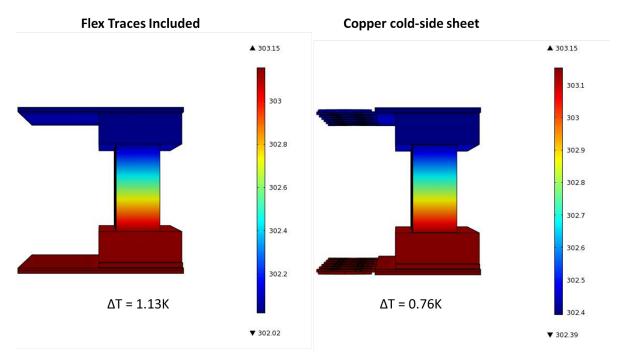

| 3.4     | The inclusion of the flex strips yielded a lower temperature differential when compared               |          |

|         | with just replacing the strips with more copper                                                       | 54       |

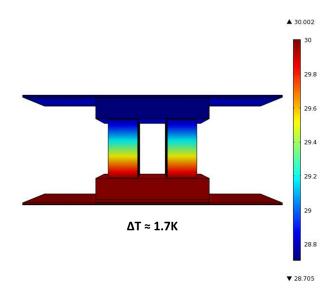

| 3.5     | Single flex TEG island finite-analysis results.                                                       | 55       |

| 3.6     | The uncut TEG required laser cutting of the slits within each TEG island as well as                   |          |

|         | cuts around the electrical traces.                                                                    | 56       |

| 3.7     | The product of the laser cut yields kapton slits on each island for the placement of                  |          |

|         | the TEG arrays.                                                                                       | 56       |

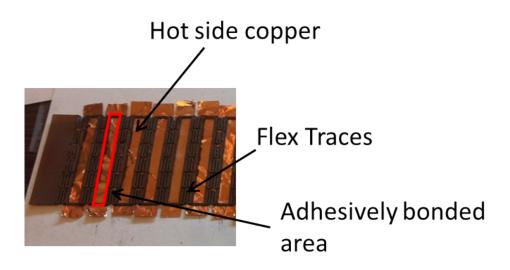

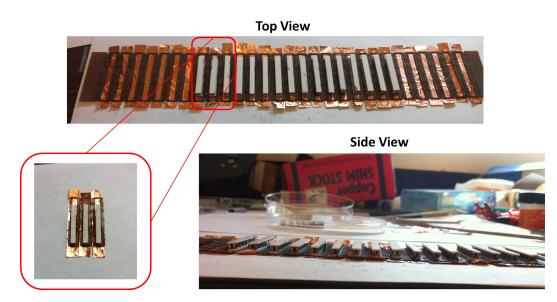

| 3.8     | A thin copper sheet was cut into area equal to that of each individual TEG island.                    |          |

|         | Adhesive was used to append the copper and the cut kapton                                             | 57       |

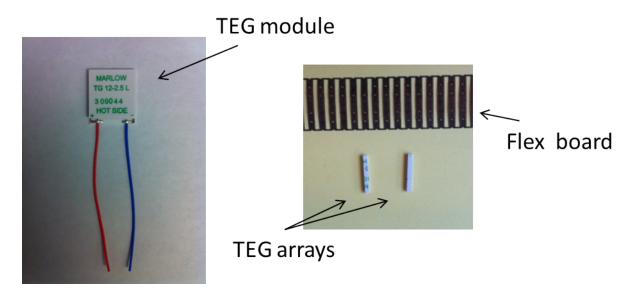

| 3.9     | Two TEG arrays are shown after being cut with a $20\mu$ m dicing saw                                  | 58       |

|         | A side view and top view of the populated flex TEG is shown.                                          | 58       |

| 3.11    | Upon thermally connecting the cold side copper strips with the ceramic, the flex TEG                  |          |

|         | is ready for curing of the TIM (the white sticker was used to hold a thermocouple for                 | 50       |

| 0.10    | thermal measurements)                                                                                 | 59       |

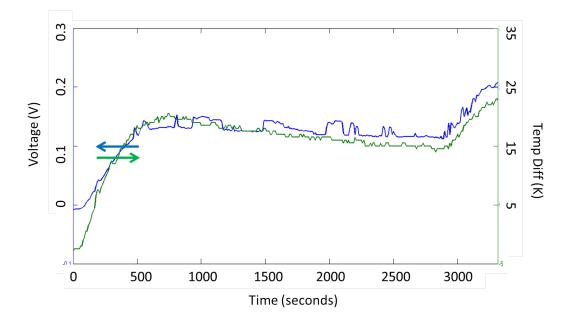

| 3.12    | The flex TEG's open-circuit voltage and temperature difference were measured as a                     | co       |

| 9 1 9   | function of time.                                                                                     | 60<br>60 |

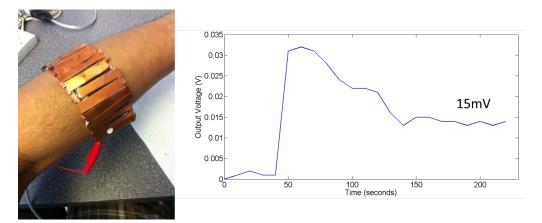

| 3.13    | The performance of the flex TEG was recorded when worn around the upper forearm.                      | 60       |

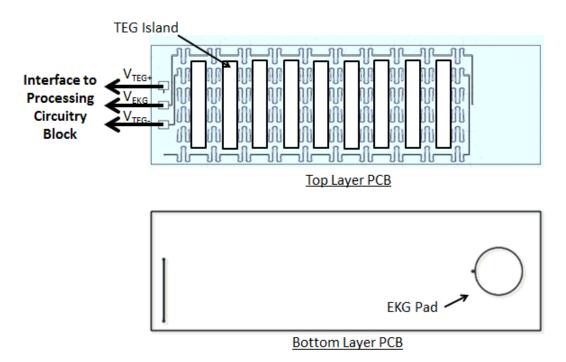

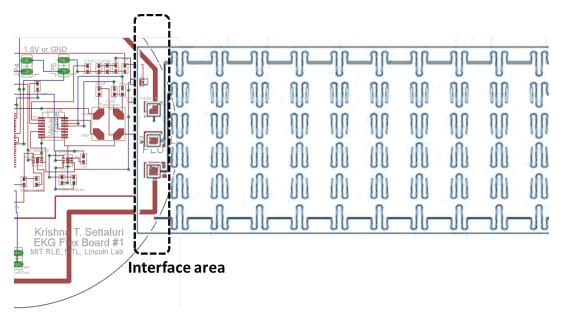

| 4.1     | A block diagram highlighting the various sub-blocks of the EKG system is shown.                       | 65       |

| 4.2     | The proposed EKG system contains not only the centralized processing circuitry but                    | 00       |

|         | also the EKG legs, which serve to acquire the EKG signal as well as generate the                      |          |

|         | necessary energy from the body.                                                                       | 66       |

| 4.3     | The top and bottom layers of the EKG legs are shown. The top layer consists of                        |          |

| -       | the TEG voltage traces ( $V_{TEG+}$ and $V_{TEG-}$ ), whereas the bottom consists of the              |          |

|         | appropriate EKG probe pad input $(V_{EKG})$                                                           | 67       |

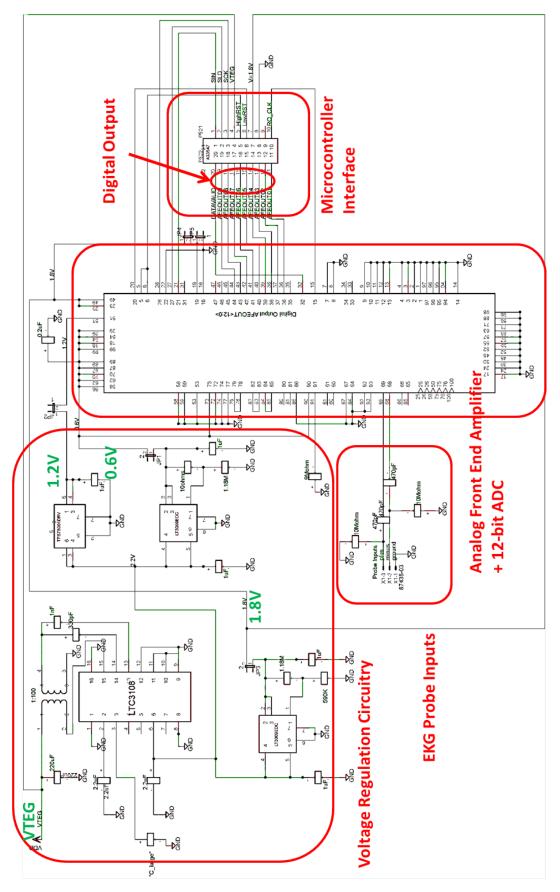

| 4.4     | The circuit diagram for the EKG processing and voltage regulation is shown                            | 68       |

| 4.5     | The chip requires the EKG probes, supplies, and program lines as inputs. Apart from                   |          |

| -       | the N-bit ADC output, the ROCLK is used to test if the chip was programmed properly.                  | 70       |

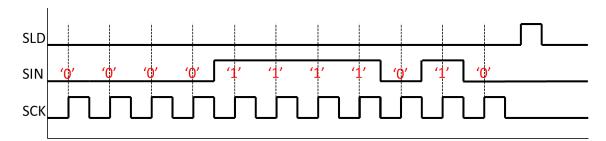

| 4.6     | The positive edge-triggered chip reads the SIN on the appropriate edge of SCK. SLD                    |          |

|         | indicates when the data is ready to be grabbed by the chip                                            | 70       |

| 4.7     | The Chipcon CC1111 board and debugger were used to program the front-end and                          |          |

|         | ADC chip [49]                                                                                         | 72       |

|         |                                                                                                       |          |

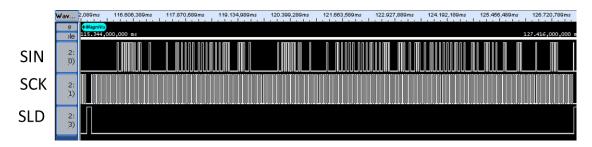

| 4.8 $$ The SLD, SIN, and SCK signals generated from the microcontroller are               |              |     |

|-------------------------------------------------------------------------------------------|--------------|-----|

| sequence was repeated to ease capturing the waveforms on a network analy                  |              |     |

| containing an initial SLD pulse                                                           |              | 73  |

| 4.9 $$ The schematic and corresponding PC Board design for the flex EKG'                  |              |     |

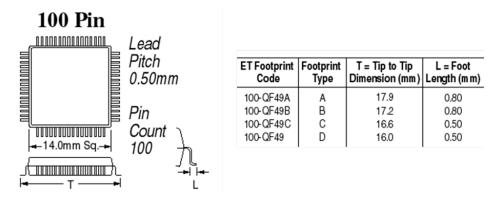

| circuitry is shown.                                                                       |              | 74  |

| 4.10 The footprint for the front end amplifier and ADC chip package is shown              |              |     |

| width and length were also specified                                                      |              | 75  |

| 4.11 The electrical connection between the EKG legs and the CPCA is made                  |              |     |

| paste as well as material epoxy                                                           |              | 75  |

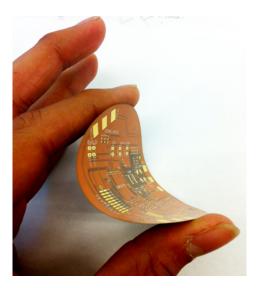

| 4.12 The printed CPCA, shown, has a diameter of 6.4cm                                     |              | 76  |

| 4.13 Due to the minimal thickness of the board, it may be bent and folded as              |              | 77  |

| 4.14 The populated CPCA (minus the jumpers) is shown. The two large con                   |              |     |

| $220\mu F$ capacitors for the input of the voltage regulation stage                       |              | 78  |

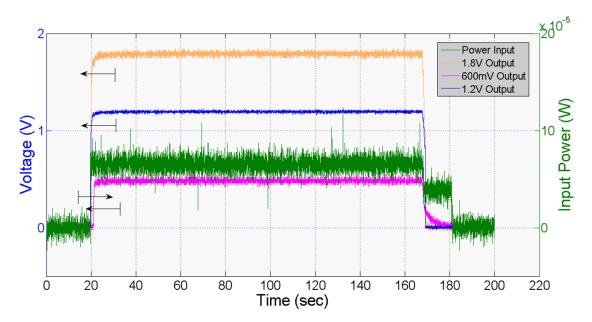

| $4.15$ The input power and output voltage waveforms are shown for the $600\mathrm{m}^{1}$ | V, 1.2V, and |     |

| 1.8V sources                                                                              |              | 79  |

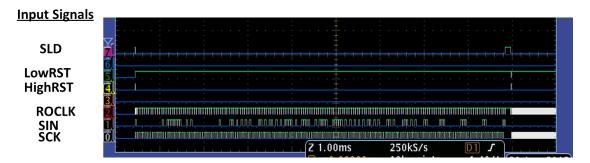

| 4.16 The input sequences to the various pins of the chip are shown. This mod              |              |     |

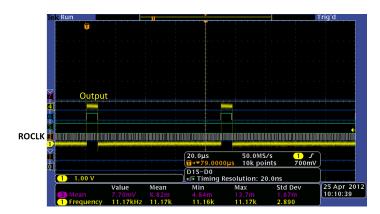

| test the chip's external oscillator functionality. $\ldots \ldots \ldots \ldots \ldots$   |              | 79  |

| 4.17~ The output DATAVALID is approximately a $20%$ duty-cycled waveform. $'$             |              |     |

| signal is also shown.                                                                     |              | 80  |

| 4.18 A test of the internal oscillator reveals the expected $20\%$ duty-cycled I          |              |     |

| signal.                                                                                   |              | 80  |

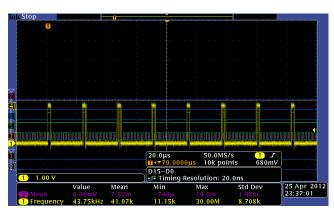

| B.1 The two stage topology was used in designing the EKG amplifier                        |              | 97  |

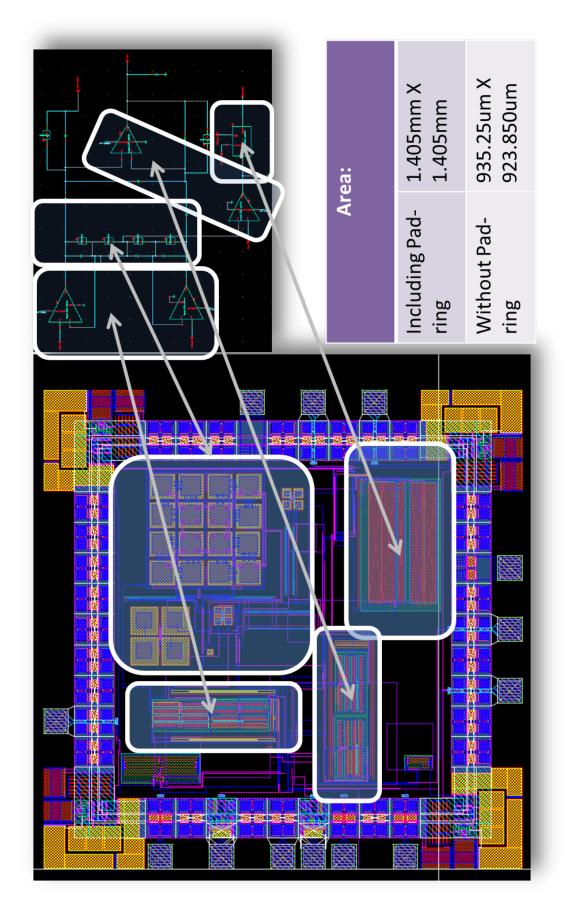

| B.2 The layout for the amplifier as well as the corresponding schematic and               |              | 0.  |

| are shown.                                                                                |              | 98  |

| B.3 The specs for three different cases are shown.                                        |              | 99  |

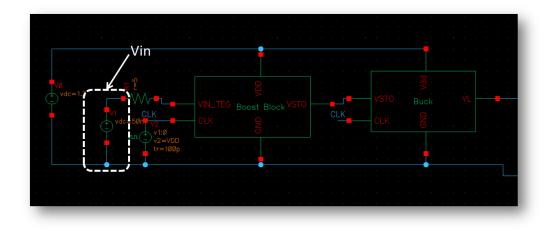

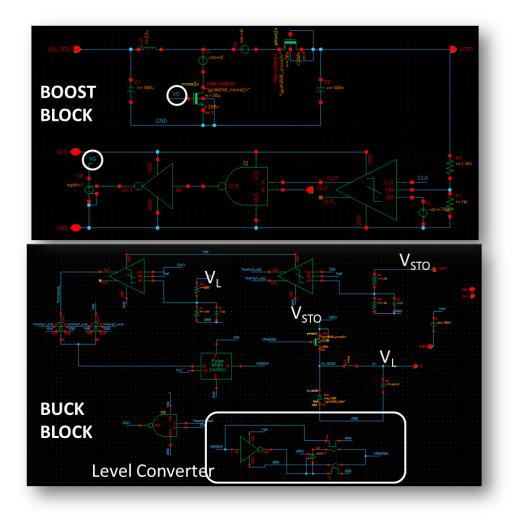

| B.4 The block diagram-level design of the DC/DC Converter is shown                        |              | 100 |

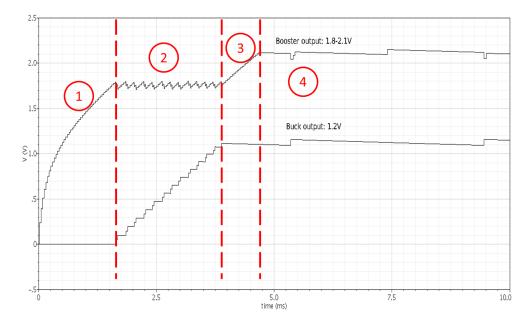

| B.5 The internals of the Boost and Buck Blocks are shown                                  |              | 101 |

| B.6 The output waveforms, divided into four phases, of the Boost Block as                 |              |     |

| Block after a 50mV input was applied.                                                     |              | 102 |

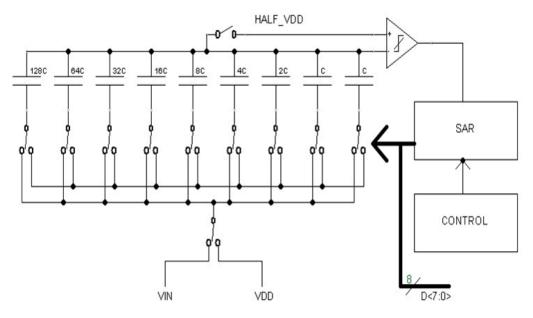

| B.7 A block diagram-level SAR ADC is shown.                                               |              | 103 |

| B.8 The comparator contains a pre-amplifier stage followed by a cross inverte             |              |     |

| a final SR Latch in order to effectively store its state                                  | ,            | 104 |

| B.9 The logic for the SAR block contains the sequencer and the code register              |              | 104 |

| B.10 The negative input of the capacitor converges correctly to the positive              |              | -   |

| comparator at VDD/2                                                                       |              | 105 |

| B.11 An input ramp, when applied to the ADC, yielded the following output                 |              | 106 |

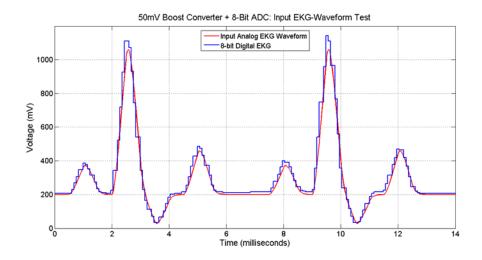

| B.12 The output of the DC/DC Converter plus 8-bit ADC when an input EK                    |              |     |

| is applied is shown.                                                                      |              | 106 |

## List of Tables

| 1.1          | Summary of TEG and heat sink system performance                                        | 18       |

|--------------|----------------------------------------------------------------------------------------|----------|

| 1.2          | Summary of current research in ultra low power boost converters                        | 23       |

| 1.3          | Summary of current research in front-end, analog EKG circuits                          | 25       |

| 1.4          | A list of specifications for the extracted front-end schematic, designed in 600nm pro- |          |

|              | cessing.                                                                               | 25       |

| 1.5          | Summary of current research in front-end, analog EKG circuits                          | 26       |

| $2.1 \\ 2.2$ | Material properties used in calculating thermal resistances                            | 33<br>36 |

| 3.1          | Material properties of 1 mil copper and 1 mil kapton.                                  | 53       |

| 3.2          | Internal Impedance and Power Characterization of the flex TEG                          | 61       |

| 4.1          | Important characteristics of the front-end EKG amplifier and ADC chip are listed.      | 69       |

### Chapter 1

### Introduction

#### 1.1 Overview

The utilization of energy harvesting in running low power, bio-monitoring applications has become more prevalent with the advent of new circuit design techniques and technologies. Thermoelectric generators (TEGs) are of particular interest in body-worn energy harvesting due to their ability to generate power from a temperature gradient between the ambient and the skin [2]. Apart from the ability to harvest energy from arbitrarily small temperature differences, the absence of moving parts is another appealing factor in utilizing such a device for energy harvesting. As with all heat engines a temperature differential is required to generate power, in this case an effective heat-sink is required to maintain a temperature differential across the module. This thesis not only addresses main issues with existing types of heat-sinks in wearable applications, but also introduces a new type of thin, wearable, conformal, and comfortable heat-sink which aims to solve the issues of maintaining a temperature differential across the body. Additionally, this 2-D heat-spreading technique is applied in not only the design of a flexible TEG, but also in an ultra-low power Electrocardiograph (EKG) acquisition and processing unit which, due to its power-hungry nature, provides a foundation for selfsufficiency. Ultimately, such a stand-alone, body-powered, EKG system may be used to continuously monitor patients within a care center or be deployed around the world and aid in monitoring the vitals of soldiers, all while avoiding the need for battery replacement.

#### **1.2** Thermoelectric Generators

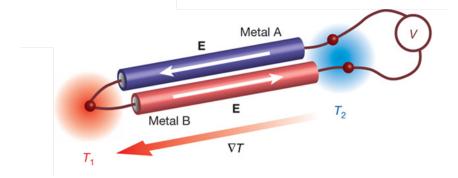

#### 1.2.1 Seebeck Effect

Thermoelectric generator (TEG) behavior is characterized by the Seebeck Effect, which details the conversion of a temperature gradient across a conductor into a voltage [4, 6]. More specifically, when considering a single electrically conducting pipe, say, with a temperature gradient across its length, conduction charge carriers (either holes or electrons) will flow away from the hot side of the pipe towards the cold side. This net flow of charge yields an electric potential build-up called the Seebeck voltage. This voltage,  $\Delta V$ , is defined as follows:

$$\Delta V = -S\Delta T,\tag{1.1}$$

where S is the Seebeck coefficient and  $\Delta T$  is the temperature differential across the conductor.

In order to utilize this Seebeck voltage, one cannot simply connect probes across this conductor and expect a usable voltage. Due to the probe itself developing a Seebeck voltage, an inherent thermocouple is formed between this conducting pipe and the probe. If, however, the probe and the pipe were made of materials with differing Seebeck coefficients, a net voltage may be expected from the system. In general, a thermocouple relies on differing Seebeck coefficients to generate a voltage from a temperature gradient, as illustrated in Figure 1.1.

The Seebeck voltage across a thermocouple containing two differing conductors then becomes

$$V = \int_{T_1}^{T_2} (S_{Metal1}(T) - S_{Metal2}(T)) dT$$

(1.2)

where  $S_{Metal1}(T)$  and  $S_{Metal2}(T)$  are the respective, temperature-dependent Seebeck coefficients of the two metals composing the thermocouple, and  $T_1$  and  $T_2$  are the cold and hot side temperatures.

Figure 1.1: The Seebeck Effect, when viewing a single thermocouple [7].

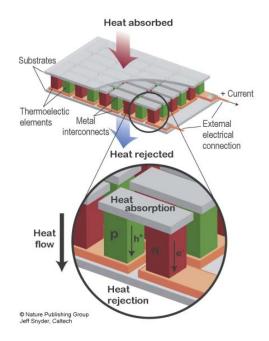

This principle may be applied to the TEG, where the two conductors of the thermocouple are doped n-type and p-type semiconductors. Notice that, now, when a temperature gradient is applied, holes (h+ in Figure 1.2) in the p-type and electrons (e-) in the n-type diffuse away from the hot source. This is apparent when examining the polarity of the Seebeck coefficient for n-type and ptype materials, where p-type have a positive coefficient and n-type a negative coefficient. And, since holes moving in the one directions is equivalent to electrons moving in the other, a closed circuit is formed between the thermocouple and the load. By arranging hundreds of thermocouples in this electrically-series, thermally-parallel pattern, the Seebeck voltage across individual thermocouples is added linearly, as shown in Equation 1.3.

$$V = N\alpha_{couple}\Delta T \tag{1.3}$$

Here, V is the open-circuit voltage across the TEG, N is the number of p-n thermocouples,  $\alpha_{couple}$  is the Seebeck coefficient, and  $\Delta T$  is the temperature differential.

Figure 1.2: The internals of a TEG, focusing on a single thermocouple upon applying a temperature gradient [5].

#### 1.2.2 Thermoelectric Composition and Materials

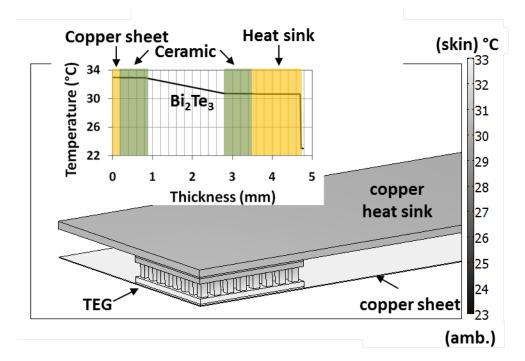

A typical TEG module, shown in Figure 1.2, contains two ceramic layers surrounding a patterned semiconductor layer. The ceramic top and bottom surfaces are required in part for structural stability

as well as for ceramic's inherently low electrical conductivity and high thermal conductivity. These properties are important in not only providing electrical insulation within the semiconductor layer, but also to ensure maximum heat transfer from one side of the ceramic material to the other due to its high thermal conductivity.

Further inspection of the semiconductor layer, see Figure 1.2, reveals doped n-type and p-type semiconductor material. Each module contains numerous thermocouples, which contain a single n-type and p-type semiconductor connected with an electrical junction. The two-terminal thermocouples are arranged in an electrically-series, thermally-parallel pattern, where one thermocouple's n-type block is connected to another's p-type block. More specifically, all p and n blocks see the same hot and cold side temperatures resulting in every thermocouple being in a thermal series configuration. However, the two terminals of the n block connect to differing but adjacent, p blocks.

This pattern is repeated hundreds of times per module, resulting in a few hundred n-type and p-type blocks.

Modern TEGs are typically created using bismuth telluride  $(Bi_2Te_3)$  due to its economic feasibility and relatively high efficiency at low temperatures [8]. High efficiency at low temperature gradients is critical for body-wearable applications, where the gradient is generally on the order of 2-4 degrees Celcius. Lead telluride (PbTe) and Uranium Dioxide  $(UO_2)$  are other researched alternatives [10, 11]. This work primarily utilizes  $Bi_2Te_3$  modules.

#### 1.3 Heat Sink Design

#### 1.3.1 Background and Current, State-Of-the-Art Research

In order to maintain a working potential across a TEG, a heat sink is added to the system to ensure a finite heat flow through the module. Cold-side cooling may be accomplished in many ways. However, convection cooling utilizing the ambient air flow is the most common technique, especially for body-powered applications, where other means of cooling are difficult to incorporate.

Dimensional and material properties of the heat sink should be taken into careful consideration while designing a power-optimized TEG and heat sink system. This concept is further explored in Chapter 2. Current research in body-powered, TEG-based systems target low power applications with the intent of powering watches or other small applications. Figure 1.3 shows some examples of TEG-based wearable applications.

The head band in Figure 1.3 generates 2.5mW of power, translating into a power density of 20  $\mu W/cm^2$ . The watches in the same figure generate 150 to 200  $\mu W$  of power at 0.8 to 1.2V open-

Figure 1.3: Current TEG-based wearable applications

circuit voltage. Such power values may be used in running many micro-power applications including those targeted towards human vital monitoring, such as heartbeat sensors and pulse oximeters [9].

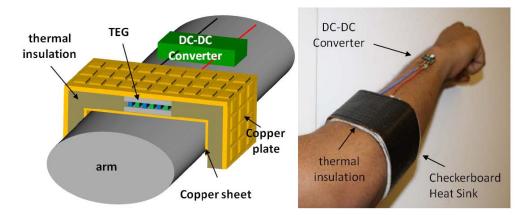

#### 1.3.2 Wearable, Low Profile, 2-D Heat-Spreader

One of the major drawbacks of utilizing the TEG-based applications in Figure 1.3, apart from their minimal power output performance, is the relative thickness of the system as well as the weight of the system. In particular, the thickness of the system is on the order of tens of millimeters, with the headband being about 30mm and weighing about 2 pounds. Such a thickness is essential for this design due to the utilization of the typical, 3-D heat-spreading technique, where cooling is attained through extending as far away from the hot source as reasonably possible, thereby increasing the surface contact area with the ambient coolant. The watches also follow this trend and extend 20mm away from the cold-side. This poses many problems in ensuring comfortableness of the system when worn. Apart from this issue, the relatively small contact surface of the heat sinks and the lack of conformity pose issues in maintaining proper contact between the hot source and the TEG, which in turn results in output power fluctuations.

Figure 1.4: The wearable, wristband heat sink ensures that the system remain comfortable and effective. A model and image are shown [41].

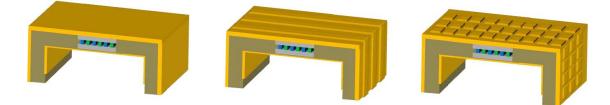

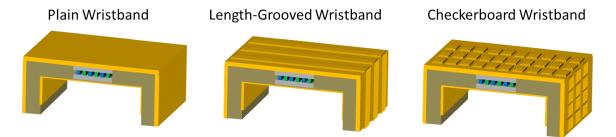

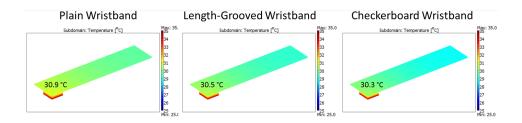

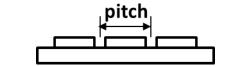

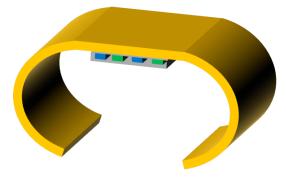

The designed 2-D heat-spreading wristbands, shown in Figure 1.4, take these issues into account. Firstly, by limiting heat flow in only two dimensions (ie only along the contour of one's arm), a low profile is maintained. Additionally, by utilizing the large available surface area of the arm, the heat sink successfully maintains a working temperature differential comparable with that of current research. However, rather than extending more than 20mm away from the hot source, the 2-D wristbands have a thickness of under 5mm, which includes the thickness of the TEG. Additionally, a byproduct of utilizing a large surface area is the increased contact provided between the hot body and the hot-side of the TEG. Tests show that moving or rotating the arm yields minimal contact loss. The design choices and characterization of these heat sinks is further analyzed in Chapter 2. A comparison of the performance, variations, and dimensions of the systems in this work as well as in current research is summarized in Table 1.1. Notice that multiple cold-side groove patterns have been explored and tested. The groove patterns are illustrated in Figure 1.5 and their appropriate performances are listed in Table 1.1.

Figure 1.5: The flat(left), length-grooved(middle), and checker-board(right) heat sinks are illustrated.

#### 1.3.3 Flexible, Stretchable TEG

The concept of 2-D heat-spreading extends beyond the wristband heat sink system introduced in Section 1.3.2. The design of a flexible TEG system, shown in Figure 1.6, allows for further leniency when approaching the concept of a universal energy harvesting system. More specifically, the dimensions of the wristband heat sink limited its use to those with appropriate arm widths. However, by designing a flexible heat sink, a wider range of individuals may comfortably wear the harvester. In addition, by cutting each individual TEG module into arrays with a width of two elements and placing them on interconnected "islands", a more uniform heat distribution across the cold-side heat sink is expected.

The design illustrated in Figure 1.6 parallels that of the wristband heat sink. However, the TEG module in the wristband is cut into arrays. These arrays, in turn, are coupled with a cold-side copper heat sink and a hot-side copper sheet for better contact in order to form islands. The hot-side copper sheet also contains electrical traces to series-connect the arrays. The various components of each

| Name                                                                         | Open<br>Circuit<br>Voltage<br>(mV) | $egin{array}{c} { m Load-} \\ { m matched}, \\ { m optimum} \\ { m power}(\mu { m W}) \end{array}$ | Power<br>Density<br>$(\mu W/cm^2)$ | Heat sink<br>system<br>dimensions<br>(L, W, H)                                                                                         | Reference |

|------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Miniaturized<br>thermoelectric<br>generator for human<br>body applications   | 150                                | 0.0003                                                                                             | ≈0.00173                           | $\approx 4.5 \text{cm x}$<br>4.5 cm x 2 cm                                                                                             | [12]      |

| Flexible<br>Thermoelectric<br>Generator for<br>Wearable Biometric<br>Sensors | 160                                | 0.00418                                                                                            | $\approx 0.00019$                  | $\begin{array}{c} 0.7 \mathrm{cm} \ \mathrm{x} \\ 0.3 \mathrm{cm} \ \mathrm{x} \\ 500 \mathrm{nm} \\ \mathrm{(thin-film)} \end{array}$ | [13]      |

| Wearable Head-Band                                                           | _                                  | 2500                                                                                               | $\approx 17$                       | $\approx 3 \text{cm x} \\ 30 \text{cm x 5 cm} \end{cases}$                                                                             | [14]      |

| Seiko Thermic<br>wristwatch                                                  | 3000                               | 30                                                                                                 | $\approx 26$                       | $\approx 5.5 \text{cm x}$<br>5.5 cm x 2 cm                                                                                             | [15]      |

| Coin-size coiled-up<br>polymer foil<br>thermoelectric power<br>generator     | 750                                | 10                                                                                                 | $\approx 1.1$                      | 1cm x 1cm x<br>1cm                                                                                                                     | [16]      |

| Checkerboard,<br>wearable wristband<br>heat sink                             | 91                                 | 280                                                                                                | 25.0                               | 25.2cm x<br>6.4cm x<br>0.1cm                                                                                                           | This work |

| Length, wearable<br>wristband heat sink                                      | 82                                 | 215                                                                                                | 19.4                               | 25.2cm x<br>6.4cm x<br>0.1cm                                                                                                           | This work |

| Flat, wearble<br>wristband heat sink                                         | 80                                 | 190                                                                                                | 17.6                               | 25.2cm x<br>6.4cm x<br>0.1cm                                                                                                           | This work |

| Flex TEG                                                                     | 20                                 | 11                                                                                                 | 0.13                               | 17cm x 5cm<br>x 0.1cm                                                                                                                  | This work |

Table 1.1: Summary of TEG and heat sink system performance

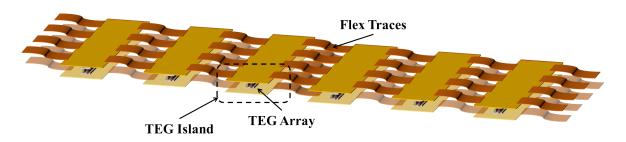

island are thermally bonded using thermal paste. Each island is interconnected to adjacent islands through the utilization of flex traces [46]. These flex traces enable 1-D stretching along the length of the circuit. Notice from Figure 1.6 that the flex traces are bent in such a way as to allow the TEG islands to compress and expand. Initial tests of the designed flex TEG yielded stretching up to 30% of the original length. Each flex TEG contains three individual TEG modules, which were cut into arrays. This yielded matching thermal impedances between the modules and the heat sink. Current design shows a 20mV open-circuit voltage and approximately 40  $\mu$ W of power. The design and performance of the flex TEG are further explored in Chapter 2.

Figure 1.6: A model of the flex TEG is shown.

#### 1.4 Applications

#### 1.4.1 Motivation and Goal

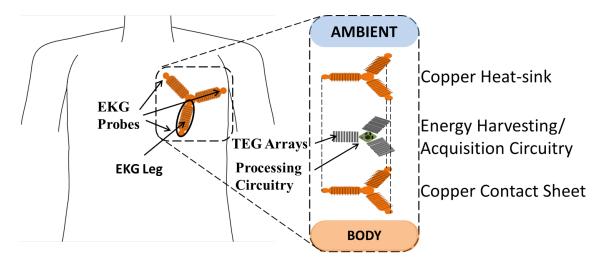

Figure 1.3 showed some example systems utilizing body-powered TEG systems as the main supply. Applications targeted towards medical monitoring are of particular interest due to their power hungry nature and packaging advantages. This work details the creation of a body-powered, EKG acquisition and processing unit. A model of the system is shown in Figure 1.7. The overall system rests on the user's chest and contains not only 2-D heat-spreading TEG arrays for power, but also the EKG probes and processing circuitry.

Figure 1.7: A model of the body-powered EKG acquisition system containing the various layers is shown.

#### 1.4.2 EKG System

#### Overview

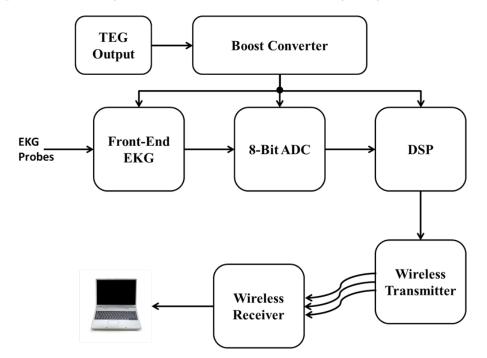

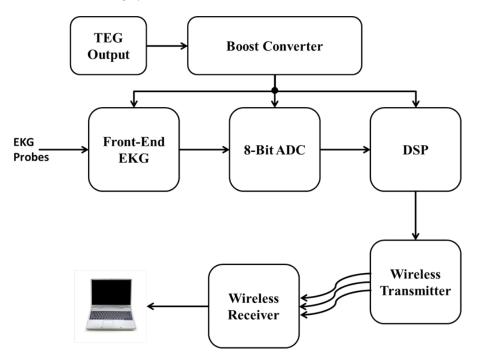

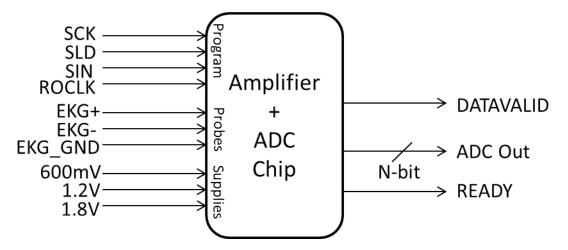

A high-level diagram of the processing circuitry as well as the TEG supply and receiver is shown in Figure 1.8. The processing circuitry contains a boost converter, EKG front-end circuitry, an 8-bit analog-to-digital converter (ADC), an ultra-low power Digital Signal Processor (DSP), and a wireless transmitter. The objective is to acquire one's EKG waveform from the front-end circuitry, digitize the signal using the ADC, perform simple processing in the DSP, and transmit the compressed data to a receiver connected to one's computer. In doing so, power is supplied to these blocks using only the body-powered TEG arrays. These sub-blocks will be individually analyzed in more detail below.

Figure 1.8: A high-level block diagram representation of the EKG acquisition system is shown.

#### Introduction to EKG

An EKG (Electrocardiography) is a tool to measure the health of ones heart. The various states of polarizations of the heart during a cardiac cycle yield measurable electrical signals on one's skin. The interaction between the four chambers of the heart results in a two-phase pumping action, known as diastole and systole. During the diastole phase, blood fills up the heart and during systole, this blood rushes to the bodys organs [9]. Each phase requires a unique set of actions to be performed by the four chambers of the heart. A byproduct of these actions is a noticeable potential difference

between differing parts of the body.

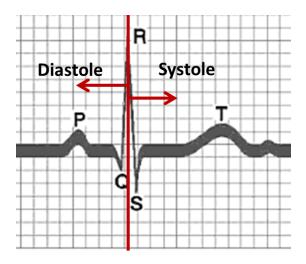

Figure 1.9: A sample EKG waveform with the two phases is highlighted.

A typical EKG waveform, shown in Figure 1.9, amplifies the difference in voltage between electrodes placed on the skin. Conducting gel is used to ensure proper contact and a stronger signal. The electrode locations are based on the dipole-like nature of the heart. Experimentation led to further accuracy in probe placement [18]. By strategically placing these probes and amplifying the resulting electrical difference, various stages of the EKG pulse may be observed. More specifically, every period of a pulse contains noticable P, Q, R, S, and T waves. These waves are generated due to some combination of the aortic and mitral valves opening or closing. By observing the duration and magnitude of these various waves, such medical issues as cardiac murmurs, seizures, arrhythmias, and cardiac dysrhythmias may be detected [24].

#### **DC-DC** Converter

The necessity of a DC-DC Converter becomes evident when handling sub-volt input supplies, which are prevalent in TEG-based applications. DC-DC Converters provide a means of using, say, a 100mV input voltage to drive analog and digital circuits by first boosting this input to an approximately usable 2.0V. By doing so, issues such as subthreshold leakage in digital circuits and inadequate linear range in analog circuits are avoided [31].

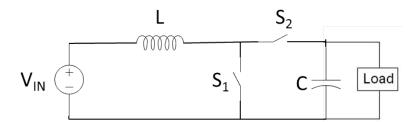

A simple, synchronous boost converter topology is shown in Figure 1.10, with the Supply providing a low input voltage and the Load seeing a higher output voltage. By varying the pulse width of the switch, current storage in the inductor and the following "discharge" into the capacitor produce

Figure 1.10: A basic boost, DC-DC Converter topology contains an inductor, switch, diode, and capacitor.

a dependent output voltage. More specifically, a boost converter's transfer functions is as follows:

$$\frac{V_{out}}{V_{in}} = \frac{1}{1 - D},$$

(1.4)

where  $V_{out}$  and  $V_{in}$  represent the high output voltage and low input voltage, respectively, and D is the duty cycle of the switch. With a duty cycle approaching one (switch is always closed), the inductor current continuously builds up and results in a  $V_{out}$  approaching 0V. As the switch opens, the current in the inductor is dumped onto the capacitor. The presence of the diode ensures that no back-current flows upon charging the capacitor.

Although functional, imperfections in the form of finite resistance in the inductor and capacitor as well as a non-zero voltage drop across the diode result in such a design being infeasible for high efficiency, low power applications. Modifications and additions have been made to this base design in order to ensure proper operation with a higher efficiency. Techniques such as cascading a boost converter followed by a buck converter yield better control over the output [32]. Additionally, incorporating digital control of the switch in both stage yield higher efficiencies and lower leakage. Table 1.2 shows the current state-of-the-art boost converters and their efficiencies.

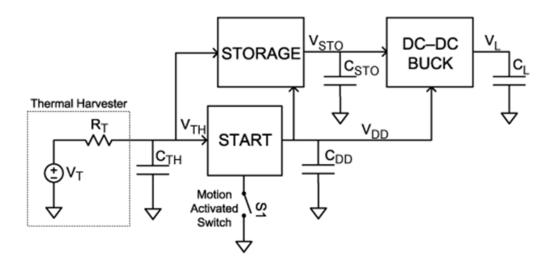

The modified boost converter topology used in this research, which incorporate the modifications detailed above, is shown in Figure 1.11. The circuit contains multiple blocks serving to either control the output, or generate reference and clock signals. In this case, the *START* block utilizes a mechanical actuator (switch S1) and at least a 35mV input voltage,  $V_{TH}$ , in order to begin generating the reference voltages and clock signals. The *STORAGE* block takes the  $V_{TH}$  input and also a supply input,  $V_{DD}$ , in order to boost the output voltage,  $V_{STO}$ , up to a value higher than needed. The DC - DCBUCK lastly bucks this  $V_{STO}$  down to output  $V_L$ . The presence of the buck

| Name                                                                    | Input<br>Voltage<br>(V) | Output<br>Voltage<br>(V) | Peak<br>Efficiency<br>(%) | Reference          |

|-------------------------------------------------------------------------|-------------------------|--------------------------|---------------------------|--------------------|

| Batteryless<br>Thermoelectric<br>Energy-Harvesting<br>Interface Circuit | $35 \mathrm{mV}$        | 1.8V                     | 58%                       | [32]               |

| EnOcean ECT310                                                          | 20mV-<br>250mV          | 4V                       | 30%                       | [33]               |

| 20mV Input Boost<br>Converter                                           | 20mV                    | 1V                       | 50%                       | [34]               |

| LT Ultralow Voltage<br>Step-Up                                          | 20mV - 1V               | 2.2V                     | 60%                       | This work,<br>[35] |

| 50mV Input Low<br>Power Boost<br>Converter                              | $50 \mathrm{mV}$        | 1.8V                     | 60%                       | This work          |

Table 1.2: Summary of current research in ultra low power boost converters

converter ensures more accurate control of the output voltage, since

$$\frac{V_{out}}{V_{in}} = D, \tag{1.5}$$

rather than being inversely proportional to the duty cycle in the case of the boost converter.

#### **EKG Front-End Circuitry**

Current research in acquiring an analog EKG signal is detailed in Table 1.5. A majority of the work, including this work, relies on a two-stage amplifier topology. However, some of the front end amplifier research in Table 1.5 include work done on larger subsystems as well.

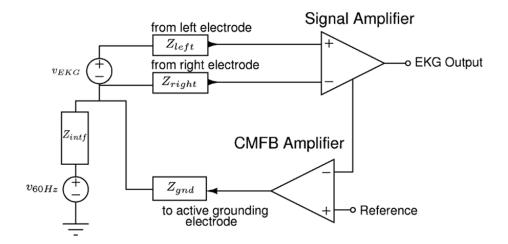

The Ultra Low Power EKG from Table 1.5 for this work utilizes a three probe, EKG front-end topology, shown in Figure 1.12. The probes, labeled  $Z_{left}$ ,  $Z_{right}$ , and  $Z_{gnd}$ , are generally located on the left hand, right hand, and leg, respectively. However, for packaging convenience, the probes may be placed as shown in Figure 1.7. This front-end topology aims to not only amplify the differential voltage generated between the  $Z_{left}$  and  $Z_{right}$  probes, but also uses the  $Z_{gnd}$  probe to feedback and reject 60Hz common mode noise (shown in Figure 1.12 as  $v_{60Hz}$ ). Due to the inherent highimpedance nature of the human body, 60Hz noise is especially prevalent. By using the  $Z_{gnd}$  probe as an active ground which feeds back into the body, a much cleaner differential voltage is observed [25].

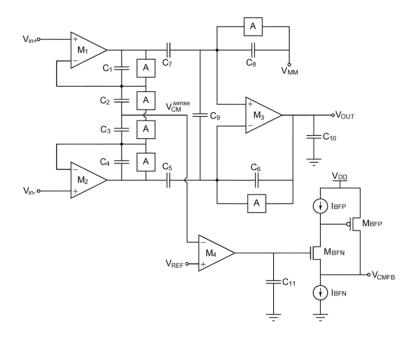

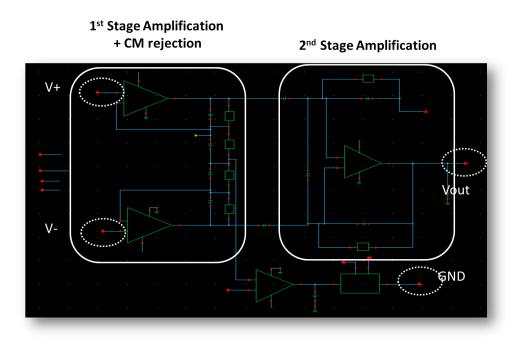

A circuit-level schematic of the topology in Figure 1.12 is shown in Figure 1.13. The Signal Amplifier block contains two gain stages, with the first stage (composed of amplifiers  $M_1$  and  $M_2$

Figure 1.11: A 35mV input boost converter [32] is shown. Further discussion will continue in Chapter 4.

in Figure 1.13) performing differential amplification of the  $V_{in+}$  and  $V_{in-}$  probe inputs. The second gain stage, composed of amplifier  $M_3$ , further gains this differential signal. The output of the first stage passes through amplifier  $M_4$ , capacitor  $C_{11}$ , and a super buffer before being fedback through the body. This feedback path contains an integrator in the form of the  $C_{11}$  capacitor. The various amplifiers are designed as simple transconductance amplifiers with pmos current mirrors and nmos biasing transistors. Specifications for the front-end layout are shown in Table 1.4. The specifications were rendered in Cadence, using 600nm AMI CMOS processing. The layout characteristics are further explored in Chapter 4.

#### Analog-to-Digital Converter (ADC)

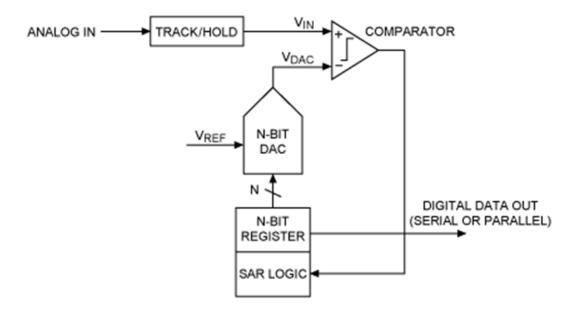

The interface between the DSP and the analog real world occurs through the ADC. By converting an analog waveform such as an EKG output into, say, an 8-bit digital bus, further processing of the data may occur using a microcontroller or Field-Programmable-Gate-Array (FPGA).

The Successive-Approximation-Register (SAR) ADC is generally the ideal choice for low power, high efficiency, and medium to high resolution applications and will be utilized in this work[36]. Table 1.5 shows the performance of current SAR ADC. Appendix B of this work looks further into the design and testing of a SAR ADC in 90nm processing.

| Name                       | Processing<br>Technology | Operating<br>Voltage<br>(V) | $\begin{array}{c} \mathbf{Power} \\ (\mu \mathbf{W}) \end{array}$ | Reference  |

|----------------------------|--------------------------|-----------------------------|-------------------------------------------------------------------|------------|

| Analog CMOS                | 0.05                     | 0.017                       | <b>5</b> 0 0 111                                                  | [24]       |

| Processing Chip for<br>ECG | $0.35\mu$                | 3.3V                        | $72.6\mu W$                                                       | [26]       |

| Sub-threshold              |                          |                             |                                                                   |            |

| Mixed-Signal ECG           | $0.13\mu$                | 0.8V                        | $2.6 \mu W$                                                       | [27]       |

| SoC                        |                          |                             |                                                                   |            |

| Flexible SoC for           |                          |                             |                                                                   |            |

| Biomedical Signal          | $0.35\mu$                | 3.3V                        | $66\mu W$                                                         | [28]       |

| Acquisition                |                          |                             |                                                                   |            |

| Micropower EKG             | $0.5\mu$                 | 1.5V, 3V                    | $2.1 \mu W$                                                       | [29]       |

| Sensor Interface for       |                          | 600mV.                      |                                                                   | This Work, |

| Biomedical                 | $0.18\mu$                | 1.2V, 1.8V                  | $2.5 \ \mu W$                                                     | [30]       |

| Applications               |                          | 1.2 v, 1.0 v                |                                                                   |            |

| Ultra Low Power EKG        | $0.6\mu$                 | 2.1V                        | $10\mu W$                                                         | This Work  |

Table 1.3: Summary of current research in front-end, analog EKG circuits.

Table 1.4: A list of specifications for the extracted front-end schematic, designed in 600nm processing.

| Common mode<br>rejection | -60.89 dB             |

|--------------------------|-----------------------|

| Differential Gain        | 42.96 dB              |

| CMRR                     | 103.825  dB           |

| Noise                    | $6.133 \ \mu V$       |

| Bandwidth                | 2.2 kHz               |

| Power                    | $4.587~\mu\mathrm{W}$ |

#### **DSP** and Transmitter

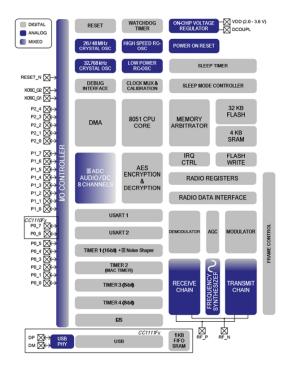

The DSP and Wireless transmitter used in this work are a part of the Chipcon family. The CC1111 is a system-on-chip (SoC) with a built-in microcontroller unit, memory, an RF Transmitter, and a USB controller. The microcontroller contains an 8051 core and various sleep modes. In addition, a supply passes through a voltage regulator before entering the SoC. Complete peripherals of the CC1111 are shown in Figure 1.15.

#### 1.5 Power Management and Efficiency

The measured power budget from the wristband heat sink is approximately 300  $\mu$ W at steady state. A major source of system optimization comes in the form of trade-offs between on chip processing plus compression and packet size transmission. More specifically, the issue of finding a balance between continuous data transmission with minimal on-chip processing and maximum on-chip processing with

Figure 1.12: A sample EKG front-end topology is shown [19].

| Name                                                 | Analog<br>Input<br>Range (V) | Digital<br>Output<br>Resolution | Power<br>Consump-<br>tion                                                      | Reference |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------------------------------------------------------------|-----------|

| SAR ADC for<br>Distributed Sensor<br>Networks        | 0 - 1V                       | 8-bit                           | 31<br>pJ/sample                                                                | [20]      |

| 12-bit Rate-resolution<br>SAR ADC                    | 0 - 1V                       | 12-bit                          | 200nW at<br>500 S/sec                                                          | [21]      |

| Low Power SAR ADC<br>for Bio-medical<br>Applications | 0 - 1V                       | 8-bit                           | 7.75 $\mu$ W at 500 kS/sec                                                     | [22]      |

| 0.5V, 1 $\mu$ W SAR ADC                              | 0 - 1V                       | 8-bit                           | $\begin{array}{c} 0.85 \ \mu W \ \text{at} \\ 4.1 \ \text{kS/sec} \end{array}$ | [23]      |

| 8-bit Ultra-low Power<br>SAR ADC                     | 0 - 1.8V                     | 8-bit                           | 2 pJ/sample<br>at 1.25 MHz                                                     | This work |

Table 1.5: Summary of current research in front-end, analog EKG circuits.

minimal packet size transmission will be further explored in Chapter 4.

#### **1.6** Thesis Organization and Contributions

The need for conformal, low-profile TEG-based heat sink systems is essential for maintaining comfortableness in not only energy harvesting but also in medical monitoring. By applying the concept of 2-D heat-spreading to create flexible TEGs and flexible EKG processing modules, patients and soldiers are better suited to using such self-sustaining applications. This thesis hopes to produce a viable alternative for heat sink design as well as body-powered applications of any sort. Chapter 2 begins by delving into the theory behind heat sink optimization through thermal impedance match-

Figure 1.13: A detailed schematic of the three-probe EKG front-end circuit [19].

ing. This concept will be applied in determining the dimensional and material characteristics of the heat sink for the TEG. Additionally, the same concept will be applied in the design of the flexible TEG. Moving on, Chapter 3 will characterize not only the wristband heat sinks from Figure 1.5, but also the flexible TEGs. Both simulation data as well as experimental results will be shown. Chapter 4 applies the 2-D heat-spreading technique to the design of a flexible EKG patch, placed around the heart. Lastly, Chapter 5 concludes and provides possible future paths for this thesis.

Figure 1.14: A simple Successive-Approximation-Register(SAR) ADC contains a comparator, SAR logic block, track/hold circuitry, and a DAC array.

Figure 1.15: The CC1111 features and contents.

### Chapter 2

# Thermal Impedance Optimization and the Wristband Heat Sink System

#### 2.1 Motivation and Organization

Current wearable, TEG-based systems, due to their minimal contact with the skin and large thickness, maintain a high profile when worn, which translates to a lack of comfortableness. Additionally, the minimal surface contact area poses issues when the body is in motion, yielding differing hot-side contact. This chapter introduces the theoretical models and experimental results obtained for the 2-D wristband heat sink. The chapter begins with an overview to the concept of thermal circuits, which is essential for setting up the theoretical models. Next, in Section 2.3, the thermal model of the 2-D heat sinks are introduced, taking into consideration the various approximations made to simplify the analysis. Additionally, the concept of heat sink optimization shall be applied in order to ensure a maximum power output in a "heat sink-limited regime". In Section 2.4, experimental setups and results for the various heat sinks will be detailed, with design limitations in mind and exploration into powering various load applications. Lastly, Section 2.5 will conclude by providing possible avenues for improvement and set a foundation to Chapter 3.

#### 2.2 Introduction to Thermal Circuits

The integral form of Fourier's Law of thermal conduction yields a relationship between the heat flux through a body and the temperature difference across the body such that

$$\frac{\Delta Q}{\Delta t} = -kA\frac{\Delta T}{\Delta x} \tag{2.1}$$

where  $\frac{\Delta Q}{\Delta t}$  is the heat flux,  $\Delta T$  is the temperature difference, k is the thermal conductivity, A is the cross sectional area, and  $\Delta x$  is the length of the object. Ohm's Law is the electrical analogy to this expression and states that

$$i = \frac{\Delta V}{R} \tag{2.2}$$

where i is charge per time or current, R is the resistance, and  $\Delta V$  is the voltage difference across the element. By studying Equations 2.1 and 2.2, it becomes apparent that the equivalent electrical analogy to thermal heat flux is current and the equivalent analogy to temperature difference is voltage. Notice also that the thermal resistance of a material is defined as

$$R_{thermal} = \frac{\Delta x}{kA}.$$

(2.3)

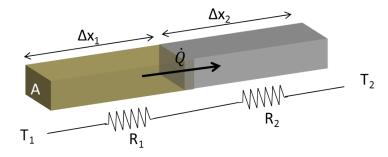

These principles may be applied to characterize thermal environments where multiple materials of differing characteristics are involved. For example, Figure 2.1 shows two separate materials within a composite slab where the heat flux,  $\frac{\Delta Q}{\Delta t}$  or equivalently  $\dot{Q}$ , is conserved but a temperature difference exists between each material[38].

Figure 2.1: A composite slab containing materials of differing thermal conductivites.

The equivalent resistances,  $R_1$  and  $R_2$  are

$$R_1 = \frac{\Delta x_1}{k_1 A} \tag{2.4}$$

$$R_2 = \frac{\Delta x_2}{k_2 A} \tag{2.5}$$

and, with series resistances in mind, the relationship between the heat flux and temperature difference is

$$\dot{Q} = \frac{T_2 - T_1}{R_1 + R_2} \tag{2.6}$$

This example shows that a clear parallel exists between the electrical and thermal domains and the behavior of temperature gradients and heat fluxes is analogous to voltage and current.

#### 2.3 Theoretical Analysis of 2-D Wristband Heat-Sink

#### 2.3.1 Thermal Model

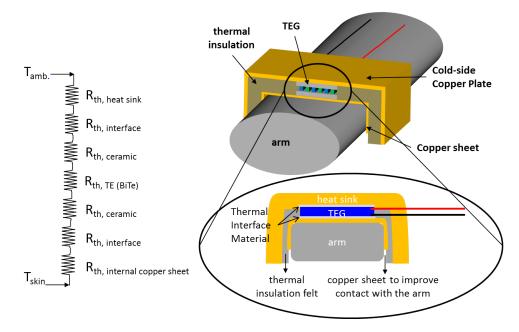

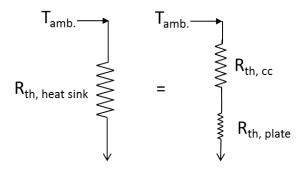

Similar to the composite slab, the TEG and wristband heat-sink system may be modeled as a series of resistances connected between two temperature sources, in this case that of the ambient and the skin. Figure 2.2 shows not only a cross-section of the various materials composing the system, but also the equivalent thermal circuit.

Figure 2.2: Thermal model of the TEG and wristband heat-sink system.

The wristband heat-sink system contains not only the top copper plate utilized for cold-side dissipation but also a thin copper sheet in contact between the hot-side of the TEG and the skin. The purpose of the cold-side copper sheet was experimentally determined to provide a better contact between the rigid TEG module and the skin, and will be explored further in Chapter 3. The system also contains thermal interface material (TIM) in order to thermally adhere the copper with the hot and cold sides of the TEG. Lastly, the TEG itself is comprised of two ceramic plates sandwiching the  $Bi_2Te_3$  elements. Each of these various layers is modeled by individual resistances beginning with  $R_{th,heatsink}$  for the cold-side copper plate, then  $R_{th,interface}$  for the TIM,  $R_{th,ceramic}$  for the hot-side TEG ceramic,  $R_{th,TE(BiTe)}$  for the TEG elements,  $R_{th,ceramic}$  and  $R_{th,interface}$  for the cold-side, and finally  $R_{th,internal copper sheet}$  for the hot-side copper sheet.

Imperfect contact between any material boundary may be modeled with an appropriate interface conductance (or convection coefficient), h [39]. The relationship between the convection coefficient and thermal resistance is

$$R_{th,contact} = \frac{1}{Ah},\tag{2.7}$$