# MIT Open Access Articles

Comparative Studies of the Growth and Characterization of Germanium Epitaxial Film on Silicon (001) with 0° and 6° Offcut

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

**Citation:** Lee, Kwang Hong, Yew Heng Tan, Adam Jandl, Eugene A. Fitzgerald, and Chuan Seng Tan. "Comparative Studies of the Growth and Characterization of Germanium Epitaxial Film on Silicon (001) with 0° and 6° Offcut." Journal of Electronic Materials 42, no. 6 (March 26, 2013): 1133–1139.

**As Published:** http://dx.doi.org/10.1007/s11664-013-2538-7

Publisher: Springer US

Persistent URL: http://hdl.handle.net/1721.1/105856

Version: Author's final manuscript: final author's manuscript post peer review, without

publisher's formatting or copy editing

Terms of use: Creative Commons Attribution-Noncommercial-Share Alike

# Comparative Studies of the Growth and Characterization of Germanium Epitaxial Film on Silicon (001) with 0° and 6° Offcut

KWANG HONG LEE,  $^{1,4}$  YEW HENG TAN,  $^2$  ADAM JANDL,  $^3$  EUGENE A. FITZGERALD,  $^{1,3}$  and CHUAN SENG TAN  $^{1,2,5}$

1.—Singapore–MIT Alliance for Research and Technology (SMART), 1 CREATE Way, #10-01 CREATE Tower, Singapore, Singapore 138602. 2.—School of Electrical and Electronic Engineering, Nanyang Technological University, 50 Nanyang Avenue, Singapore, Singapore 639798. 3.—Department of Materials Science and Engineering, Massachusetts Institute of Technology, Cambridge, MA 02139, USA. 4.—e-mail: kwanghong@smart.mit.edu. 5.—e-mail: tancs@ntu.edu.sg

The quality of germanium (Ge) epitaxial films grown directly on silicon (Si) (001) with  $0^{\circ}$  and  $6^{\circ}$  offcut orientation using a reduced-pressure chemical vapor deposition system is studied and compared. Ge film grown on Si (001) with  $6^{\circ}$  offcut presents  $\sim\!65\%$  higher threading dislocation density and higher root-mean-square (RMS) surface roughness (1.92 nm versus 0.98 nm) than Ge film grown on Si (001) with  $0^{\circ}$  offcut. Plan-view transmission electron microscopy also reveals that threading dislocations are more severe (in terms of contrast and density) for the  $6^{\circ}$  offcut. In addition, both high-resolution x-ray diffraction and Raman spectroscopy analyses show that the Ge epilayer on  $6^{\circ}$  offcut wafer presents higher tensile strain. The poorer quality of the Ge film on Si (001) with  $6^{\circ}$  offcut is a result of an imbalance in Burgers vectors that favors dislocation nucleation over annihilation.

**Key words:** Germanium, offcut, heteroepitaxy, reduced-pressure chemical vapor deposition

### INTRODUCTION

For the past few decades, rigorous scaling methods have been driving silicon (Si) complementary metal–oxide–semiconductor (CMOS) technology to maintain device performance, decrease power consumption, and reduce cost per transistor. <sup>1,2</sup> As the device size approaches the scaling limit, a paradigm shift has occurred in the industry from dimensional scaling alone to materials innovation. One such example is the compound III–V materials, which have unique properties for future high-speed and low-power computation applications. <sup>3–9</sup> Most of the III–V materials show  $20 \times$  to  $70 \times$  higher electron mobility and  $\sim 20 \times$  higher conductivity compared with Si. In addition, the feasibility of bandgap engineering

in III–V materials enables fabrication of devices suitable for communications and optoelectronics applications. However, III–V materials are not able to replace Si completely because the substrates are expensive and smaller in size due to brittleness (wafer diameters are typically less than 200 mm). Therefore, III–V materials have to be integrated onto a Si substrate in order to be compatible with mainstream CMOS manufacturing. To realize III–V materials integration on low-cost, mechanically stronger Si substrates, a number of research groups have investigated III–V growth on Si for optoelectronic and microelectronic applications.

The main challenges of producing high-quality III–V materials on Si are: (i) the large lattice mismatch between the two materials [in the case of gallium arsenide (GaAs), the mismatch is 4.1%], and (ii) the formation of antiphase domains (APDs) due to the polar compound semiconductor growth on

a nonpolar elemental structure. In an attempt to resolve challenge (i), germanium (Ge), which has a lattice constant perfectly matched to GaAs (0.07% at 300 K) and superior electron and hole mobility compared with Si, can be grown on Si to provide a buffer layer for integration and fabrication of GaAsbased devices on a Si substrate. 12-15 Since Ge and GaAs have diamond and zincblende structure, respectively, two possible sublattice allocations are possible for the GaAs layer, although they have exactly the same crystal structure. In one allocation, Ga atoms occupy the face-centered cubic (FCC) sublattice containing the cubic corners, whereas in the other allocation, As atoms occupy this FCC sublattice. Each allocation is rotated by 90° with respect to the other, corresponding to a switching of the cation and anion sublattices. These distinct domains of each sublattice are usually called antiphase domains (APDs). An APD is separated by a plane of incorrect nearest-neighbor bonds (e.g., Ga-Ga or As-As) termed an antiphase boundary (APB), which may propagate into the GaAs epilayer. To resolve this, a high offcut angle (usually 4° to 6°) is used to reduce the step spacing and possibly shrink the sizes of APDs. 16-18

Prior to the growth of III-V on Ge, a Ge layer with high quality needs to be grown on Si. Hartman et al. grew a thick ( $\sim 2.5 \mu m$ ) Ge epilayer on both  $0^{\circ}$  and  $6^{\circ}$ offcut wafers and reported similar Ge qualities [in terms of surface roughness, threading dislocation density (TDD), and strain state]. 19 It is well known that the quality of the Ge film improves with increasing film thickness.<sup>20,21</sup> For a thinner Ge film (e.g.,  $\sim 1 \mu m$ ), one can expect different quality of the Ge epilayer when grown on  $0^{\circ}$  and  $6^{\circ}$  offcut wafers. Recently, an epitaxial Ge film ( $\sim 1~\mu m$ ) grown directly on Si (001) with 0° offcut was reported by Tan et al. 19 using a "three-step growth" approach in a reduced-pressure chemical vapor deposition (RPCVD) system with TDD level of  $\sim\!10^7~\text{cm}^{-2}$  and RMS surface roughness of ~0.9 nm.<sup>22</sup> In this manuscript, the qualities of Ge film (with thickness of 1  $\mu$ m) grown directly on two different Si substrates, namely Si (001) with 0° offcut and Si (001) with 6° offcut toward [110], using the same growth method are studied and compared.

#### EXPERIMENTAL PROCEDURES

In this experiment, silicon (001) wafers (diameter 150 mm, p-type, resistivity 0.018  $\Omega$  cm to 0.025  $\Omega$  cm) with 0° and 6° offcut toward [110] direction were cleaned using RCA solutions followed by drying the wafers using an isopropanol (IPA) dryer. The clean wafers were loaded into the N<sub>2</sub>-purged loadlock of an ASM Epsilon 2000 RPCVD reactor. To initiate growth, each wafer was transferred to the growth chamber and baked in hydrogen (H<sub>2</sub>) at 1000°C for 2 min to desorb the thin surface oxide that is detrimental to the epitaxy process. The precursor for Ge was 10% diluted ger-

mane (GeH<sub>4</sub>) in H<sub>2</sub> balance. A three-step Ge growth was introduced with target thickness of 1  $\mu$ m. <sup>19</sup> The three steps in the growth sequence were: (i) low-temperature growth at 400°C to obtain a relatively smooth and continuous Ge seed layer, (ii) low-to high-temperature ramping from 400°C to 600°C at rate of 6.5°C/min, and (iii) high-temperature growth at 600°C. This approach has been described in detail in a previous publication. <sup>22</sup> Thermal cycling was introduced immediately after step (iii) to enhance the surface mobility of the Ge atoms in order to control the surface roughness and reduce the TDD. Thermal cycling was performed by H<sub>2</sub> annealing between 680°C to 825°C for a repetition of 8× with 10 min annealing at 825°C.

The qualities of the Ge epitaxial film grown on both types of substrate were characterized by various techniques. The Ge surface topography and its thickness were examined by scanning electron microscopy (SEM) using a Zeiss Leo model 1550. The Ge RMS roughness was determined by atomic force microscopy (AFM) using a Veeco/Digital Instrument Dimension 3000 in tapping mode. Transmission electron microscopy (TEM, Philips CM200) with operating voltage of 200 kV was used to study the dislocations along the Ge/Si interface. x-Ray diffraction (XRD, Bruker D8 Discover) analysis was used to determine the crystallinity and strain of the Ge epilayer. The Si (004) reflection was used for the XRD rocking curves. To further confirm the strain and quality of the Ge film, Raman spectra were collected using a WITec alpha 300 confocal Raman microscope. An excitation laser wavelength of 532 nm was used with focal length and objective lens magnification of 80 cm and 100×, respectively. Dynamic secondaryion mass spectroscopy (D-SIMS) profiles were measured using a Cameca IMS 6f. The primary beam and energy used were Cs+ and 10 kV. The beam raster size was 200  $\mu m \times 200~\mu m$ , and the analysis area was 60  $\mu$ m in diameter. The electrical properties of the Ge films were characterized by capacitance-voltage (*C–V*) measurements of metal–oxide–semiconductor (MOS) structure on a Cascade/Suss Microtec PM8PS probe station, using a Keithley 4200-SCS semiconductor characterization system.

#### RESULTS AND DISCUSSION

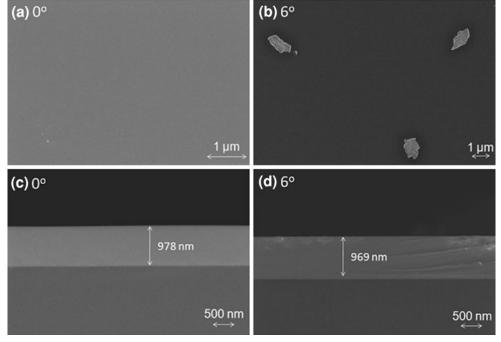

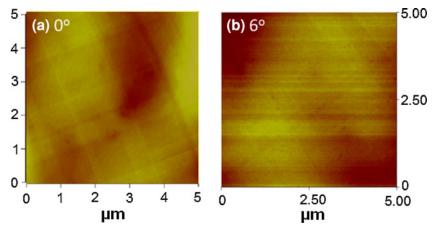

The SEM images in Fig. 1 show plan and cross-sectional views of the  $0^{\circ}$  and  $6^{\circ}$  offcut Ge/Si samples after thermal cycling. From the cross-sectional SEM images, the thickness of the Ge film on  $0^{\circ}$  and  $6^{\circ}$  offcut samples is 978 nm and 969 nm, respectively. These values closely match the target value of 1  $\mu$ m. The RMS surface roughness of the  $0^{\circ}$  and  $6^{\circ}$  offcut samples is 0.98 nm and 1.92 nm, respectively, as estimated from the AFM images shown in Fig. 2. The surface roughness is doubled when the Ge is grown on the  $6^{\circ}$  offcut substrate. In Fig. 2a, a clear cross-hatch pattern is seen on the  $0^{\circ}$  sample. The threading dislocation density (TDD) can be

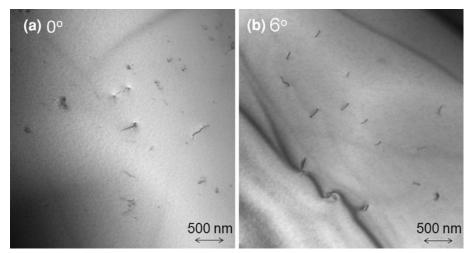

determined from the plan-view TEM image by estimating the dislocations in a given area at a number of locations across the samples, as shown in Fig. 3. The TDD is more prominent in terms of visual contrast and density in the  $6^{\circ}$  offcut sample. The estimated TDD is  $3.95\pm0.663\times10^{7}$  cm $^{-2}$  and  $6.53\pm0.931\times10^{7}$  cm $^{-2}$  for  $0^{\circ}$  and  $6^{\circ}$  offcut samples, respectively. The TDD value was estimated based on an average number of 40 plan-view TEM images for accuracy.

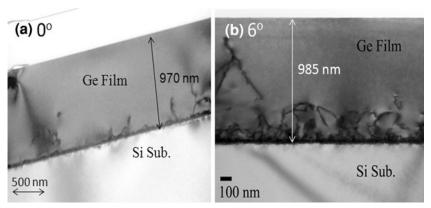

The cross-sectional bright-field TEM images in Fig. 4 show that the thickness of the Ge epitaxial film is  $\sim 970$  nm and  $\sim 985$  nm, respectively, for  $0^{\circ}$ and 6° offcut samples. These values are in good agreement with earlier estimations from the crosssectional SEM images shown in Fig. 1. The crosssectional TEM images also show that, for both cases, the misfit dislocations are mostly confined along the Ge/Si interface. It is evident that a larger number of misfit dislocations are concentrated at the Ge/Si interface of the 6° offcut sample. In addition, within the first ~400 nm (beginning from the Ge/Si interface), a larger number of threading dislocations are propagated into the film in the 6° offcut sample compared with the 0° offcut sample. As a result, the 6° offcut sample presents a higher TDD on the top surface. The apparent discrepancy in the TDD count in both samples can be explained from the point of view of the effect of surface orientation on the dislocation Burgers vectors. On the Si (001) with 0° offcut, an even balance of Burgers vectors are nucleated when misfit dislocations form to relieve the misfit strain. Therefore, the annihilation process has a more balanced probability of locating

the opposite Burgers vectors. When the Si (001) surface is 6° offcut, it is speculated that certain Burgers vectors are preferred at nucleation and this results in an imbalance in the Burgers vectors. <sup>23–25</sup> When the possible annihilation events are completed under the processing conditions used in this experiment, more misfit dislocations remain at the Ge/Si interface for the sample with 6° offcut that eventually thread to the top surface, hence giving rise to a higher net TDD.

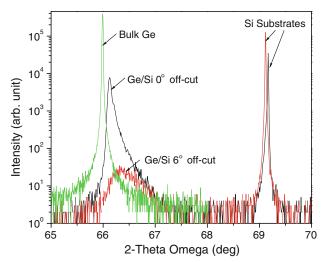

Since the strain state of the final Ge epilayer heavily influences its electrical and optical properties, XRD study was performed to estimate the strain level of the Ge epilayer. The XRD analysis in Fig. 5 shows that the Ge epilayer on the 0° offcut sample has better crystal quality than the 6° offcut sample, as the Ge signal curve is sharper and the peak intensity is much higher. In addition, the difference in intensity of the Ge peak on 0° and 6° offcut samples may be due to the slight misalignment of the 6° offcut sample. The Ge signal from the 6° offcut sample has a broader distribution, possibly due to the presence of Ge clusters with different strain levels. Both of the Ge signal curves are asymmetric and show a clear shoulder at the side towards higher incidence angle. This is due to Ge/Si intermixing at the interface during thermal processing that perturbs the abrupt interface, resulting in an intermediate  $Si_{1-x}Ge_x$  layer. The Ge peaks are shifted to the right with respect to the Ge bulk substrate as a result of tensile strain. The tensile strain is thermally induced in the Ge epilayer during cooling from high-temperature processing steps to room temperature, as Ge (5.8 ppm/°C) and Si

Fig. 1. SEM images of epitaxial Ge on Si substrate with (a, c)  $0^{\circ}$  offcut, (b, d)  $6^{\circ}$  offcut; (a, b) plan view, (c, d) cross-sectional view.

Fig. 2. Two-dimensional (2-D) AFM scans (dimensions 5  $\mu$ m  $\times$  5  $\mu$ m) showing the RMS roughness of the as-grown Ge epilayer on Si substrate with (a) 0° offcut and (b) 6° offcut.

Fig. 3. Plan-view TEM images showing the threading dislocations on the Ge surface for (a) 0° offcut sample and (b) 6° offcut sample.

Fig. 4. Cross-sectional TEM bright-field images showing the Ge epitaxial film for (a) 0° offcut sample and (b) 6° offcut sample. In both cases, the misfit dislocations are confined along the Ge/Si interface and threading dislocations are propagated through the film.

Fig. 5. High-resolution x-ray diffraction (HRXRD) profile illustrating the crystallinity and strain state of the Ge epitaxial films with respect to bulk Ge.

(2.6 ppm/°C) have different linear coefficient of thermal expansion (CTE). <sup>26</sup>

The perpendicular lattice constant  $(a^{\perp})$  of the Ge epilayer in the growth direction can be calculated from the XRD diffraction peak using Bragg's law as follows:

$$a^{\perp} = \frac{2\lambda}{\sin(\frac{\omega_{\text{Ge}}}{2})},\tag{1}$$

where  $\lambda$  is the incident radiation wavelength (Cu  $K_{x1}$  line,  $\lambda=1.5406$  Å) and  $\omega_{Ge}$  is the angular position of the Ge peak from the HRXRD of Si (004). Using Eq. 1, the  $a^{\perp}$  of the Ge on Si 0° and 6° offcut samples can be estimated as 5.6482 Å and 5.6433 Å, respectively. The in-plane lattice constant,  $a^{11}$  of the Ge epilayer can be calculated using Eq. 2 by taking the elastic modulus of Ge, v=0.271, and the unstrained Ge lattice constant,  $a_{Ge}=5.6576$  Å:

$$a^{\parallel} = \left(\frac{1+v}{2v}\right) \left[a_{\text{Ge}} - a^{\perp} \left(\frac{1-v}{1+v}\right)\right].$$

(2)

Therefore, the estimated  $a^{11}$  of Ge on Si 0° and 6° offcut samples is 5.6708 Å and 5.6744 Å, respectively. The residual strain of the Ge epilayer can be calculated by Eq. 3 as

$$\varepsilon = \frac{a_{\text{Ge}}^{\parallel} - a_{\text{Ge}}}{a_{\text{Ge}}}.$$

(3)

Positive and negative values of  $\varepsilon$  for the Ge epilayer indicate either tensile or compressive strain. From the calculation, the Ge epilayers on both Si 0° and 6° offcut substrates exhibit tensile strain. The Ge layer on the 6° offcut substrate has higher average tensile strain of 0.6%, compared with the Ge on the 0° offcut substrate that has 0.2% tensile

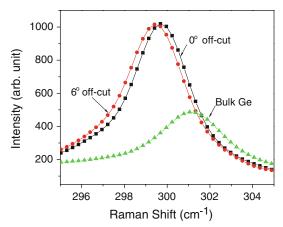

Fig. 6. Raman spectroscopy illustrating the alloy composition and strain of the Ge epilayers with respect to bulk Ge.

strain. This discrepancy is not fully understood and is most likely due to the complex interactions of the larger amount of threading dislocations in the Ge layer on the 6° offcut substrate.

Raman spectroscopy was used to determine the quality and properties of the Ge/Si epitaxial film by measuring the alloy composition and strain. In Fig. 6, a redshift of the Ge-Ge vibration peak position is clearly observed in the Ge/Si samples relative to the bulk Ge reference (peak at 301.3 cm<sup>-1</sup>). The Ge–Ge peak is located at wavenumber of 300.1 cm<sup>-1</sup> and 299.45 cm<sup>-1</sup>, respectively, for the 0° and 6° offcut samples. In both samples, there is only one observable signal peak associated with the Ge-Ge vibration mode, with no other signal originating from Si-Ge or Si-Si vibration modes. This is expected due to the strong absorption property of the Ge layer. The full-width at half-maximum (FWHM) of the Ge-Ge vibration peak for bulk Ge, and the 0° and 6° offcut samples is  $2.50 \text{ cm}^{-1}$ ,  $2.17 \text{ cm}^{-1}$ , and  $2.22 \text{ cm}^{-1}$ , respectively. Hence, the quality of the Ge/Si samples is comparable to that of bulk Ge. Both samples show a Ge-Ge peak that is shifted to lower wavenumber (with respect to the Ge bulk), indicating that they are under tensile strain. This observation agrees with the earlier XRD findings. In addition, the Ge-Ge peak from the 6° offcut sample is shifted to a wavenumber smaller than that of the  $0^{\circ}$  offcut sample, signifying higher tensile strain in the Ge epilayer grown on the 6° offcut sample.

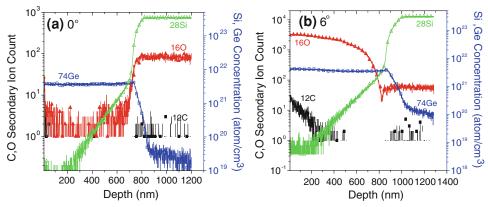

The SIMS depth profiles are summarized in Fig. 7. The 6° offcut sample presents higher carbon (<sup>12</sup>C) and oxygen (<sup>16</sup>O) content in the Ge epilayer, possibly due to poor wafer handling. When the growth sequences are completed, samples are unloaded from the loadlock and exposed to ambient prior to SIMS analysis. There was a longer time lag prior to SIMS analysis for this 6° offcut sample, resulting in more significant surface oxidation and contamination. Based on the SIMS profile, a distinct level of the Ge signal in the epitaxial film that

Fig. 7. SIMS analysis for elements of interest such as carbon (<sup>12</sup>C), oxygen (<sup>16</sup>O), silicon (<sup>28</sup>Si), and germanium (<sup>74</sup>Ge) for Ge epilayers grown directly on Si with (a) 0° and (b) 6° offcut.

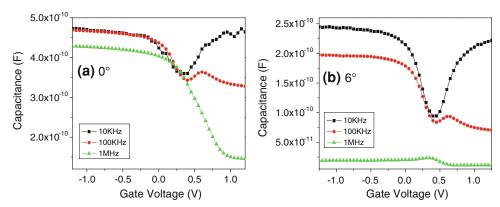

Fig. 8. C-V measurements at different frequencies on MOS structures fabricated on Ge epilayers: (a) 0° offcut sample and (b) 6° offcut sample.

| Characterization Method                        | Ge Epilayer on 0° Offcut Si                                                  | Ge Epilayer on 6° Offcut Si                                                 |

|------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| XRD                                            | 0.2% tensile strain                                                          | 0.6% tensile strain                                                         |

| Raman                                          | Lower tensile strain                                                         | Higher tensile strain                                                       |

| AFM                                            | RMS roughness 0.98 nm                                                        | RMS roughness 1.92 nm                                                       |

| TDD count from plan-view TEM                   | $3.95\pm0.663	imes10^7~{ m cm}^{-2}$                                         | RMS roughness 1.92 nm $6.53\pm0.931	imes10^7~\mathrm{cm}^{-2}$              |

| Cross-sectional TEM                            | Fewer threading dislocations are propagated within the first ~400 nm of film | More threading dislocations are propagated within the first ~400 nm of film |

| $D_{\mathrm{it}}$ from $C	ext{}V$ measurements | $4.7 \times 10^{11} \text{ cm}^{-2}/\text{V}$                                | $1.83 \times 10^{12}  \mathrm{cm}^{-2} / \mathrm{V}$                        |

tapers off rapidly in the Si substrate can be observed. Similarly, the Si signal decays rapidly as it crosses the Ge/Si interface into the Ge film. Therefore, Ge/Si intermixing is well controlled in both samples.

The Ge epitaxial film is undoped during the growth process. However, there is a possibility of background doping due to residual dopants from previous runs. This doping level is low and not reliably quantifiable. The conductivity in the Ge

epilayer, despite its low dopant concentration, is attributed to the large offset between the valence bands of Ge and Si that forms a well that favors hole accumulation. This is confirmed by the C--V measurements on a 200  $\mu\text{m} \times 200~\mu\text{m}$  MOS structure fabricated on both of the undoped Ge layers, presented in Fig. 8. The gate electrode is TiN with thickness of  $\sim\!150$  nm, and the gate dielectric stack consists of  $\text{Al}_2\text{O}_3$  (thickness  $\sim\!10$  nm) and interfacial  $\text{GeO}_x\text{N}_y$  (thickness  $\sim\!2$  nm). The interfacial quality

of both samples was estimated using the conductance method during C–V measurements. The calculated interface state density ( $D_{\rm it}$ ) for the  $0^{\circ}$  and  $6^{\circ}$  offcut samples is  $4.7 \times 10^{11}$  cm<sup>-2</sup>/V and  $1.83 \times 10^{12}$  cm<sup>-2</sup>/V, respectively. This is expected due to the higher TDD in the  $6^{\circ}$  offcut sample.

The properties and qualities of the Ge epitaxial film grown directly on Si (001) with 0° and 6° offcut are summarized in Table I. This study clearly shows that the starting Si substrate with 6° offcut orientation results in a poorer quality Ge layer. This is believed to be due to imbalanced Burgers vector nucleation during dislocation formation, leading to an unfavorable annihilation process. This study points to the need for additional investigation if direct Ge epitaxial growth on Si is to be attempted on substrates with nonzero offcut for III–V-on-Si integration.

#### **CONCLUSIONS**

Ge epitaxial film grown directly on Si substrate with 6° offcut presents higher TDD ( $\sim$ 65% higher) and rougher surface (95% rougher) compared with a substrate with no offcut. The MOS structure fabricated on the 6° offcut sample also shows a higher  $D_{\rm it}$  value (2.89 times higher). The poor quality of the Ge epilayer would be anticipated to degrade any subsequent III–V materials integration, and may also lead to device failure. The poorer quality of the Ge film on Si (001) with 6° offcut is attributed to the imbalance in Burgers vectors that favors dislocation nucleation over annihilation. Hence, additional attention is required if direct Ge ( $\sim$ 1  $\mu$ m) epitaxial growth on Si is to be attempted on substrates with nonzero offcut.

#### **ACKNOWLEDGEMENTS**

This research was supported by the National Research Foundation Singapore through the Singapore MIT Alliance for Research and Technology's "Low energy electronic systems (LEES) IRG" research. This work has also been carried out as part of the Nanyang Assistant Professorship supported by Nanyang Technological University (NTU). Authors are grateful for support provided by the management and technical staff in the Nanyang Nanofabrication Center at NTU.

## REFERENCES

- S. Deleonibus, Eur. Phys. J. Appl. Phys. 36, 197 (2007).

- The International Technology Roadmap for Semiconductor, www.itrs.net.

- M. Passlack, P. Zurcher, K. Rajagopalan, R. Droodpad, J. Abrokwah, M. Tutt, Y.B. Park, E. Johnson, O. Hartin, A. Zlotnicka, P. Fejes, R.J.W. Hill, D.A.J. Moran, X. Li, H. Zhou, D. Macintyre, S. Thoms, A. Asenov, K. Kalna, and I.G. Thayne, 2007 IEEE International Electron Devices Meeting, vol. 1 (2007), p. 621.

- Y. Sun, E.W. Kiewra, J.P. de Sauza, J.J. Bucchignano, and K.E. Fogel, 2008 IEEE International Electron Devices Meeting (2008), p. 367.

- Y. Xuan, T. Shen, M. Xu, Y.Q. Wu, and P.D. Ye, 2008 IEEE International Electron Devices Meeting (2008), p. 371.

- D.H. Kim and J.A. del Alamo, 2006 IEEE International Electron Devices Meeting, vol. 1 (2006), p. 587.

- D.H. Kim and J.A. del Alamo, 2008 IEEE International Electron Devices Meeting (2008), p. 719.

G. Dewey, M.K. Hudait, K. Lee, R. Pillarisetty, W. Rachmady,

- G. Dewey, M.K. Hudait, K. Lee, R. Pillarisetty, W. Rachmady, M. Radosavljevic, T. Rakshit, and R. Chau, *IEEE Electron*. *Device Lett.* 29, 1094 (2008).

- 9. M. Radosavljevic, T. Ashley, A. Andreev, S.D. Coomber, G. Dewey, and M.T. Emeny, 2008 IEEE International Electron Devices Meeting (2008), p. 727.

- R.M. Sieg, S.A. Ringel, S.M. Ting, S.B. Samavedam, M. Currie, T. Langdo, and E.A. Fitzgerald, 16<sup>th</sup> North American Conference on Molecular-Beam Epitaxy, vol. 16 (1998), p. 1471.

- T.K. Yang, M.E. Groenert, G. Tarachi, C.W. Leitz, A.J. Pitera, M.T. Currie, Z. Cheng, and E.A. Fitzgerald, J. Mater. Sci.: Mater. Electron. 13, 377 (2002).

- M.E. Groenert, C.W. Leitz, A.J. Pitera, V. Yang, H. Lee, R.J. Ram, and E.A. Fitzgerald, J. Appl. Phys. 93, 362 (2003).

- J. Oh, S.K. Banerjee, and J.C. Campbell, *IEEE Photonics Technol. Lett.* 16, 581 (2004).

- S. Fama, L. Colace, G. Masini, G. Assanto, and H.C. Luan, *Appl. Phys. Lett.* 81, 586 (2002).

- M. Oye, D. Shahrjerdi, I. Ok, J.B. Hurst, S.D. Lewis, S. Dey, D.Q. Kelly, S. Joshi, X. Yu, M.A. Wistey, J.J.S. Harris, J.A.L. Holmes, J.C. Lee, S.K. Banerjee, and T.J. Mattord, J. Vac. Sci. Technol., B 25, 1098 (2007).

- H. Tanoto, S.F. Yoon, W.L. Loke, E.A. Fitzgerald, C. Dohrman, B. Narayanan, M.T. Doan, and C.H. Tung, J. Vac. Sci. Technol., B 24, 152 (2006).

- S.M. Ting and E.A. Fitzgerald, J. Appl. Phys. 87, 2618 (2000).

- R.M. Sieg, S.A. Ringel, S.M. Ting, E.A. Fitzgerald, and R.N. Sacks, J. Electron. Mater. 27, 900 (1998).

- J.M. Hartmann, A. Abbadie, N. Cherkashin, H. Grampeix, and L. Clavelier, Semicond. Sci. Technol. 24, 055002 (2009).

- Y. Yamamoto, P. Zaumseil, T. Arguirov, M. Kittler, and B. Tillack, Solid-State Electron. 60, 2 (2011).

- J. Hartmann, J.F. Damlencourt, Y. Bogumilowics, P. Holliger, G. Rolland, and T. Billion, J. Cryst. Growth 274, 90 (2005)

- 22. Y.H. Tan and C.S. Tan, Thin Solid Films 520, 2711 (2012).

- R.S. Goldman, K.L. Kavanagh, H.H. Wieder, S.N. Ehrlich, and R.M. Feenstra, J. Appl. Phys. 83, 5137 (1998).

- M.K. Hudait, Y. Lin, and S.A. Ringel, J. Appl. Phys. 105, 061643 (2009).

- M. Gutierrez, D. Gonzales, G. Aragon, M. Hopkinson, and R. Garcia, Mater. Sci. Eng., B 80, 27 (2001).

- D.D. Cannon, J.F. Liu, D.T. Danielson, S. Jongthammanurak, U.U. Enuha, K. Wada, J. Michel, and L.C. Kimerling, Appl. Phys. Lett. 91, 252111 (2007).