## Optimal Digital System Design in Deep Submicron Technology

by

## Seongmoo Heo

Bachelor of Science, Electrical Engineering, Korea Advanced Institute of Science and Technology (1998)

Master of Science, Electrical Engineering and Computer Science, Massachusetts Institute of Technology (2000)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January 2006

[February 2006]

©Massachusetts Institute of Technology 2006. All rights reserved.

| Author       | STILL AND             |

|--------------|-----------------------------------------------------------|

| 1            | Department of Electrical Engineering and Computer Science |

|              | January 13, 2006                                          |

|              |                                                           |

|              | •                                                         |

|              |                                                           |

|              |                                                           |

| Certified by | 18/14/2./                                                 |

| •            | Krste Asanović                                            |

|              | Associate Professor                                       |

|              | Thesis Supervisor                                         |

|              | ·                                                         |

|              |                                                           |

|              |                                                           |

|              |                                                           |

| Accepted by  | Arthur C. Smith                                           |

|              | Arthur C. Smith                                           |

|              | Chairman, Department Committee on Graduate Students       |

JUL 1 2006

LIBRARIES

**ARCHIVES**

#### Optimal Digital System Design in Deep Submicron Technology

by

### Seongmoo Heo

Submitted to the Department of Electrical Engineering and Computer Science on January 13, 2006, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### **Abstract**

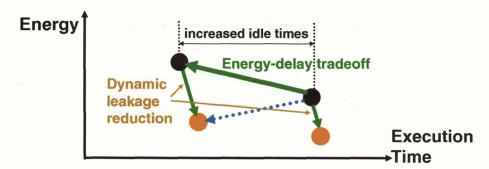

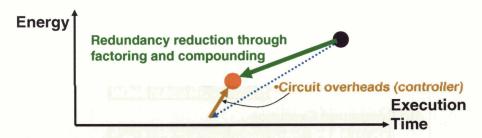

The optimization of a digital system in deep submicron technology should be done with two basic principles: energy waste reduction and energy-delay tradeoff. Increased energy resources obtained through energy waste reduction are utilized through energy-delay tradeoffs.

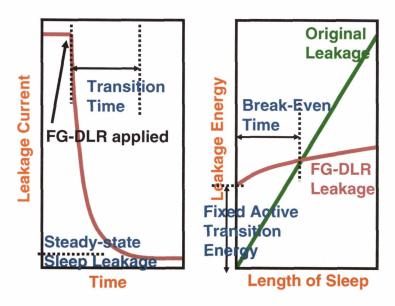

The previous practice of obliviously pursuing performance has led to the rapid increase in energy consumption. While energy waste due to unnecessary switching could be reduced with small increases in logic complexity, leakage energy waste still remains as a major design challenge. We find that fine-grain dynamic leakage reduction (FG-DLR), turning off small subblocks for short idle intervals, is the key for successful leakage energy saving. We introduce an FG-DLR circuit technique, *Leakage Biasing*, which uses leakage currents themselves to bias the circuit into the minimum leakage state, and apply it to primary SRAM arrays for bitline leakage reduction (*Leakage-Biased Bitlines*) and to domino logic (*Leakage-Biased Domino*). We also introduce another FG-DLR circuit technique, *Dynamic Resizing*, which dynamically downsizes transistors on idle paths while maintaining the performance along active critical paths, and apply it to static CMOS circuits.

We show that significant energy reduction can be achieved at the same computation throughput and communication bandwidth by pipelining logic gates and wires. We find that energy saved by pipelining datapaths is eventually limited by latch energy overhead, leading to a power-optimal pipelining. Structuring global wires into on-chip networks provides a better environment for pipelining and leakage energy saving. We show that the energy-efficiency increase through replacement with dynamically packet-routed networks is bounded by router energy overhead.

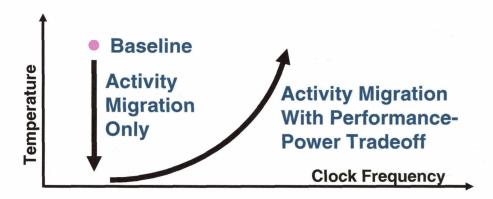

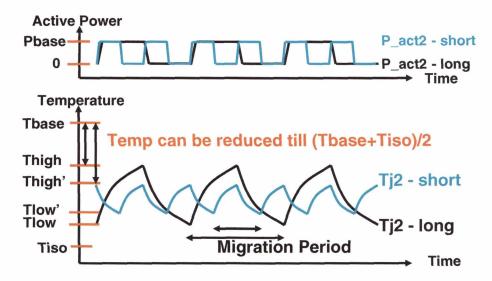

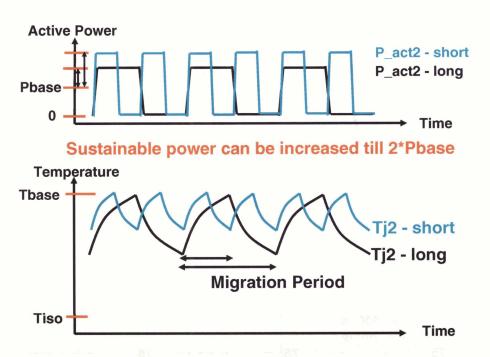

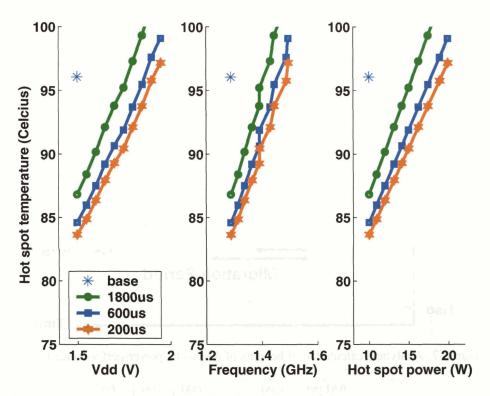

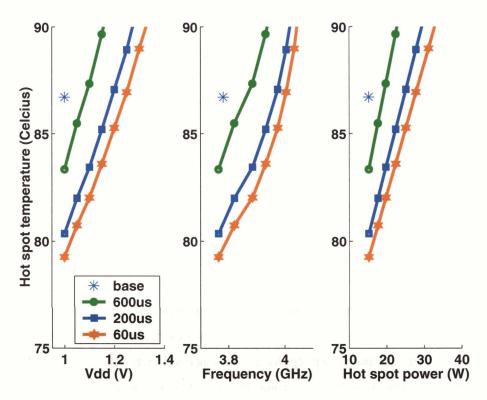

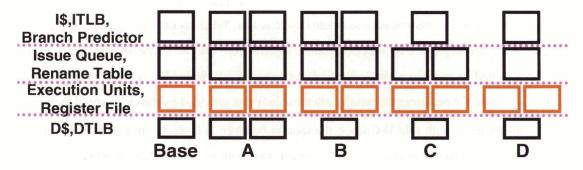

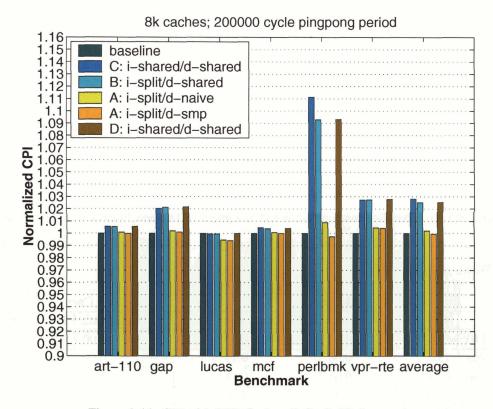

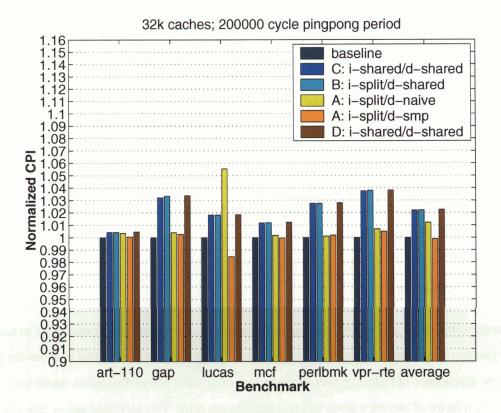

Finally, we provide a way of relaxing the peak power constraint. We evaluate the use of *Activity Migration* (AM) for hot spot removal. AM spreads heat by transporting computation to a different location on the die. We show that AM can be used either to increase the power that can be dissipated by a given package, or to lower the operating temperature and hence the operating energy.

Thesis Supervisor: Krste Asanović

Title: Associate Professor

### Acknowledgments

First of all, I'd like to thank my advisor, Krste Asanović, deeply for his inspiring advice and guidance and also for spending a great deal of time and energy for this thesis. Also I'd like to thank my thesis readers, Prof. Chandrakasan and Prof. Agarwal for the advices.

I thank my group mates, Ken Barr, Elizabeth Basha, Chris Batten, Steve Gerding, Mark Hampton, Ronny Krashinsky, Rose Liu, Albert Ma, Heidi Pan, Jessica Tseng, and Mike Zhang for helpful discussions. Special and extra thanks to my officemates, Mike, Jessica, Ronny and Albert, for sharing all the ups and downs of MIT grad student life together.

I thank Mary McDavitt so much for all the cares and encouragements throughout the last years of my graduate work. I thank Ken and his Sydney Grill bar for great beers and chats. I thank Prof. and Mrs. Lim for the advices on research and life.

Thanks to my MIT Korean friends: Daihyun, Jaewook, Yongwook, Junghoon, Gookwon, Hyunil, Sangwon, Sungho, Joonsung, Minkyu, Jungwon, Sejun, Myungjin, Taeksang, Min, Kyungbum, Jaeyeon, Chungyeon, Jihwan, Junmo, Daekeun, Jungin, Hyeyeon, Taesik, Seonghwan, Yongseok, Hyunjung, Sungtae, Taehong, Sungjun, Soonmin, Taeyi, Jhongwoo, Choonghyun, Hohyun, Hyemin, Jerin, Youjin, Jinyoung, Jooeun, Julie, Jungkeun, Jongchul, Miso, Kwanhong, Meekyoung, Sangil, Seungeun, Tairin, Wonyong, Yoonsung, Yoonsun, and many others.

Thanks to all friends from First Korean Church in Cambridge: Pastor. and Mrs. Kim, Mr. and Mrs. Han, Mr. and Mrs. Sung, David and Kelly, Jin, Jieha, Sunah, Jouwon, Taein, Yejeon, Eunhye, Hyeeun, Hyeju, Inyoung, Jaehoon, Jaewoo, Jihyung, Jinhee, Jiyoung, Junyoung, Kyunghee, Rayoung family, Seungwon, Seoyoung, Jaeseop, Chul, and many others. Very special thanks to Jin, Jieha, Taein, and Yejeon for all the loves and cares.

Funding for my graduate work came from a number of sources including KFAS (Korea Foundation for Advanced Studies), DARPA Grant N66001-99-2-8917, DARPA PAC/C award F30602-00-2-0562, NSF CAREER award CCR-0093354, NSF ITR award CCR-0219545, and donations from Infineon Technologies, Intel Corporation, and MOSIS Educational Program (MEP).

Finally, I want to thank my wonderful parents for supporting me, loving me, and believing in me.

# 어머니 아버지 감사합니다!

## **Chapter 1**

## Introduction

The advent of deep submicron technology is an exciting and challenging time for digital system designers. Emerging applications require huge amounts of computation and memory bandwidth and while deep submicron technology allows us to place billions of transistors on a single chip, thermal and power constraints are ever tightening and thus the efficient use of energy resources is more important than ever. Also, the surge in leakage current has made leakage power an important design challenge for digital system design.

The traditional optimization of a digital system often focused on only a single parameter: either improving performance or saving energy. Initially, performance was the sole goal. Energy consumption was insignificant and most innovations were unaware of energy, resulting in the rapid growth of both useful energy consumption and energy waste in digital systems. Recently, however, with the peak power reaching the thermal limit of transistors and increasing demands for mobility, power (or energy) has become a primary metric for digital system design. Though technology scaling has automatically provided around quadratic reduction of switching power for the same circuit blocks, supply voltage has scaled down sub-linearly. Die size has grown to include many sophisticated architectural innovations and soon will reach a few billion transistors on a single chip. As a result, typical power consumption of many high-performance digital systems has reached many tens of watts, which requires expensive cooling to prevent the threat of thermal emergency.

This power crisis has led to many diverse low-energy techniques. Low-energy techniques first focused on energy waste from spurious switching of parasitic capacitances. Since previous design practices were energy-unaware, even simple techniques could achieve large energy saving by cutting energy waste. However, now that most switching energy waste is well controlled, energy reduction

must be done through energy-delay tradeoffs. The same principle applies to performance improvement. As energy resources are precious, innovations intended for high performance should fully understand the energy-delay curve's behavior. In this deep submicron technology era, obliviously pursuing only high performance or low-energy results in a sub-optimal design.

Though switching energy waste is well managed in modern digital systems, there is still significant leakage energy waste. Though leakage energy waste was trivial in previous technology generations, the continuation of aggressive technology scaling and resulting supply and threshold voltage scaling have led to the exponential increase of leakage current, making leakage waste energy comparable to switching energy. Thus, the development of techniques for leakage energy waste reduction is crucial for optimal digital system design.

With high performance requirements, precious energy resources, significant leakage, and hot die temperatures, optimization of digital systems has become more challenging and critical than ever. We claim that there are two basic principles for digital system optimization in deep submicron technology: energy waste reduction and energy-delay tradeoff. Increased energy resources obtained through energy waste reduction are utilized through energy-delay tradeoff.

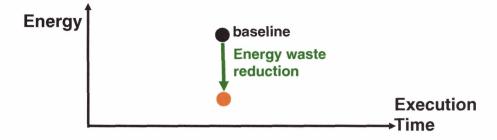

## 1.1 Energy Waste Reduction

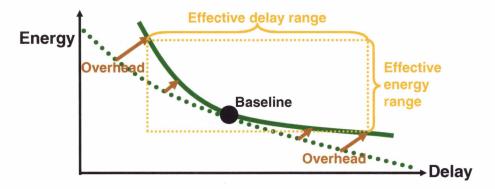

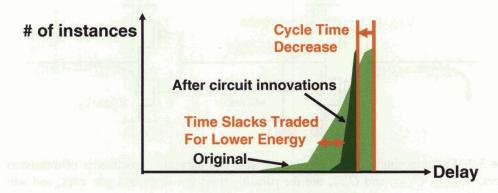

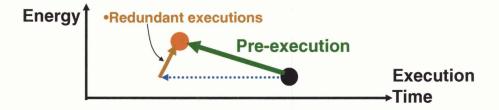

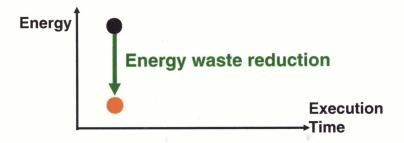

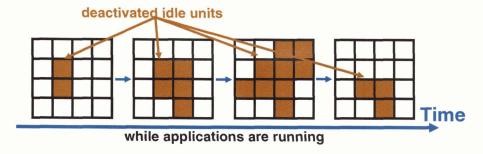

Energy waste in digital systems results from the simplicity of design. Thus, we can reduce energy waste by turning a simple and energy-inefficient design into a complex but energy-efficient design. Figure 1-1 illustrates the impact of an ideal energy waste reduction innovation on energy and execution time.

Figure 1-1: Energy waste reduction.

Energy waste is caused by spurious switching of parasitic capacitances or transistor leakage. The tight control of switching and leakage has been one of the critical themes for recent architectural innovations in digital systems. While modern energy-conscious digital systems have success-

fully minimized switching energy waste with the help of fine-grain clock gating for clock trees and bitline/wordline gating for SRAM arrays, the rapidly-growing leakage energy waste has not been as effectively reduced.

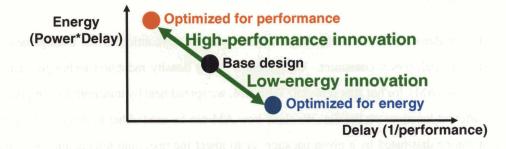

## 1.2 Energy-Delay Tradeoff

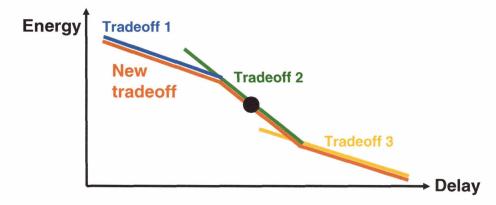

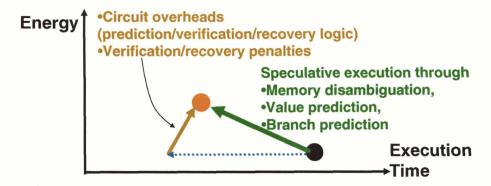

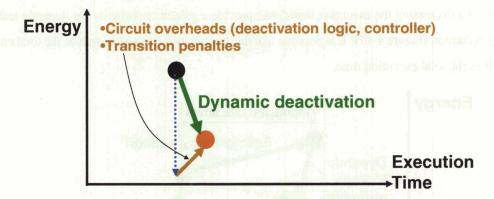

Though ideally we would like to have innovations which decrease both energy and delay at the same time, most high-performance or low-energy innovations are, in essence, energy-delay trade-offs, even though intended for either increasing performance or decreasing energy. The essential difference between high-performance and low-energy innovations is the direction of trade. High-performance innovation increases energy consumption for a performance gain and a low-energy innovation saves energy while sacrificing performance (Figure 1-2). In fact, many innovations can be used in either direction. For example, supply voltage can be up-scaled or down-scaled to find the optimal level where the delay requirement is tightly met and the energy consumption is minimized. Similarly, the issue width of a superscalar processor can be increased for improving performance or decreased for reducing hardware complexity and saving energy.

Figure 1-2: Energy-delay tradeoffs: optimizing for either greater performance or lower energy.

The future digital systems require an urgent change in design philosophy: from purely highperformance or purely low-energy design to an energy-efficient design using energy-delay tradeoffs.

#### 1.3 Contributions of Thesis

The major contributions of this thesis are:

• Fine-Grain Dynamic Leakage Reduction (Chapter 5): We find that leakage energy waste is the most critical target for energy waste reduction and claim that fine-grain dynamic leakage reduction, turning off small pieces for short idle intervals, is the key for continuing leakage reduction. We introduce a FG-DLR technique, *Leakage Biasing* (LB) which uses leakage currents themselves to bias the circuit into the minimum leakage state and hence has low transition overheads. We successfully apply LB to bitline leakage reduction in primary SRAM arrays (*Leakage-Biased Bitlines*) with three microarchitectural deactivation policies and to domino logic, through *Leakage-Biased Domino*. We also introduce *Dynamically Resizable CMOS* (DRCMOS), which dynamically downsizes transistors on idle paths in static CMOS logic.

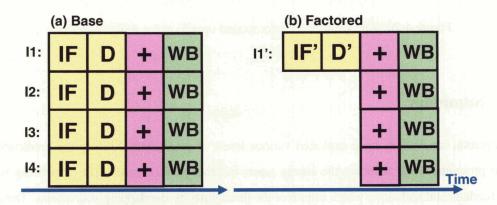

- Pipelining Logic Gates and Wires (Chapter 6 and Chapter 7): We show that energy reduction for high-performance ASIC systems can be achieved with the same computation throughput and communication bandwidth by pipelining logic gates and global wires and then employing other energy-delay tradeoffs. We find that power reduction from pipelining datapaths is eventually limited by the latch energy overhead. We show that structuring global wires into a network provides a better environment for global wire optimization (e.g. pipelining). We find that the energy-efficiency increase through dynamically packet-routed network is bounded by router energy overhead.

- Hot Spot Removal with Activity Migration (Chapter 8): Dynamic thermal management relaxes the peak power constraint. We present a power density reduction technique, activity migration (AM), for hot spot removal. With AM, we spread heat by transporting computation to different locations on the die. We show how AM can be used either to increase the power that can be dissipated by a given package, or to lower the operating temperature and hence the operating energy.

#### 1.4 Thesis Overview

This thesis is an exploration of optimal digital system design in deep submicron CMOS technology focusing on circuit- and architectural-level innovations. While SOI technology for improving CMOS performance has been under research for nearly three decades [CBF00] and is now in production, bulk CMOS technology is by far the most dominant process. We consider only bulk technology throughout the thesis. Among various levels of digital system optimization, we focus on circuit- and architectural-levels. Innovations in technology, system software, and applications are

significant, but are beyond the scope of the thesis. Our main target platforms are high-performance and energy-conscious general-purpose microprocessors, and application-specific integrated chips (ASICs) for digital signal processing (DSP) applications. However, the concepts and techniques of many innovations we describe and develop in this thesis can be easily applied to other digital system platforms.

Chapter 2 provides background for this work. We first describe how to compare and combine energy-delay tradeoffs. Then we move onto power and thermal issues. In spite of continuing technology scaling, power consumption of high-performance digital systems has grown rapidly and now power is a primary metric for any digital system design. We describe two power constraints: peak power and average power. The drastic power increase has led to many low-power techniques. We find that low-power techniques trade increased delay for lower energy, or reduce energy waste, and that switching energy waste has been well managed by clock gating for clock trees and bit-line/wordline gating for SRAM arrays. We present an overview of subthreshold leakage. The rapid and continuing reductions in feature size and threshold voltage have brought exponential increases in leakage. The increase of power densities has brought significant increases in die temperature. We examine the thermal behavior of digital systems and then discuss how we can overcome the thermal limit through dynamic thermal management to effectively increase the available power budget.

Chapter 3 and Chapter 4 categorize circuit- and architectural innovations for digital systems respectively, from the perspective of energy waste reduction and energy-delay tradeoff. We observe that transistors' dimensions and voltages are the two main tuning variables for circuit designs, and categorize circuit techniques according to how they tune the variables while studying the energy-delay tradeoffs with simple test circuits. We find that most architectural innovations are based on three critical techniques: exploiting parallelism, utilizing predictability, and reducing energy waste, and categorize the architectural innovations according to the techniques while analyzing their impacts on energy and delay.

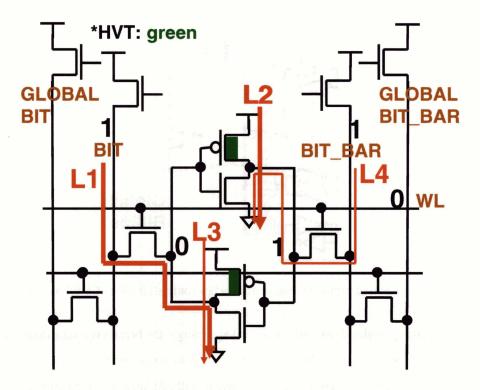

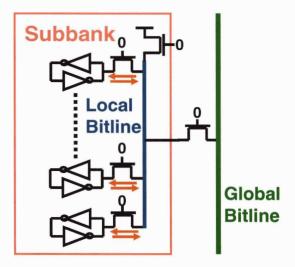

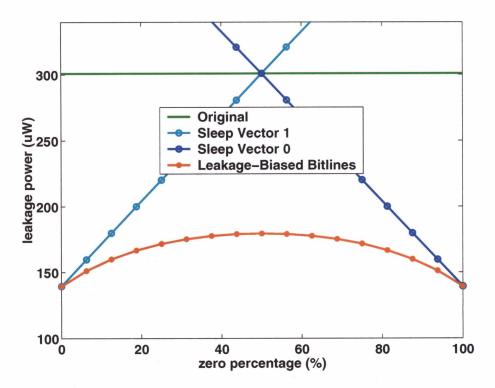

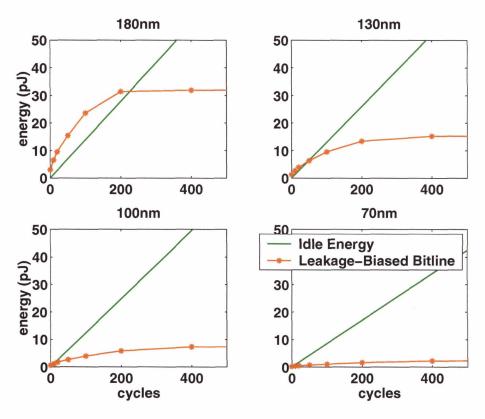

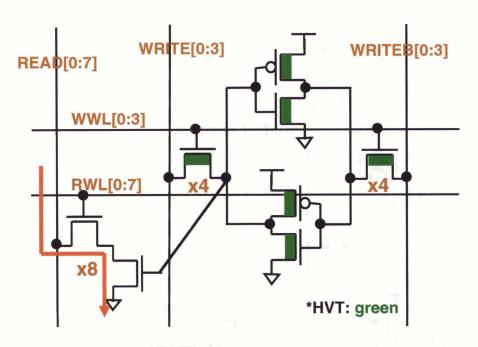

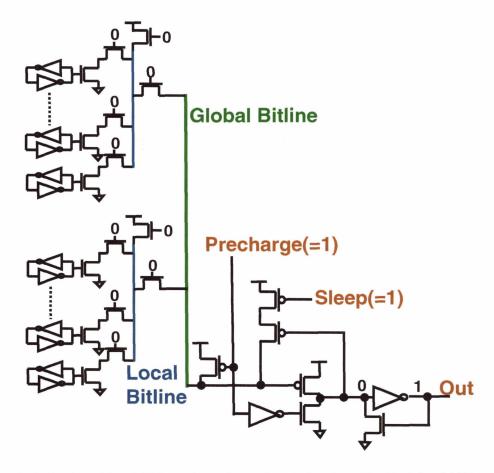

Chapter 5 describes techniques for fine-grain dynamic leakage reduction (FG-DLR). We first categorize existing leakage reduction techniques into static and dynamic approaches and find that leakage on critical paths becomes dominant after static leakage reduction techniques are applied. We discuss candidates for FG-DLR and parameters for comparing different FG-DLR techniques. We introduce a FG-DLR circuit technique, *leakage biasing* (LB). LB uses leakage currents themselves to bias the circuit into the minimal leakage state. We first apply LB to primary SRAM arrays to reduce the bitline leakage, which we call *leakage-biased bitlines* (LBB). LBB dynamically biases

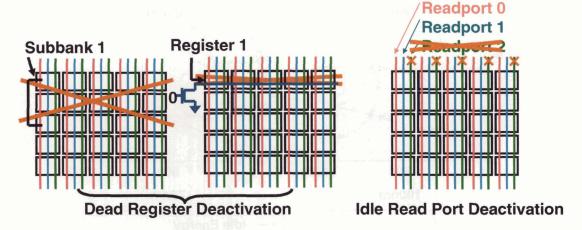

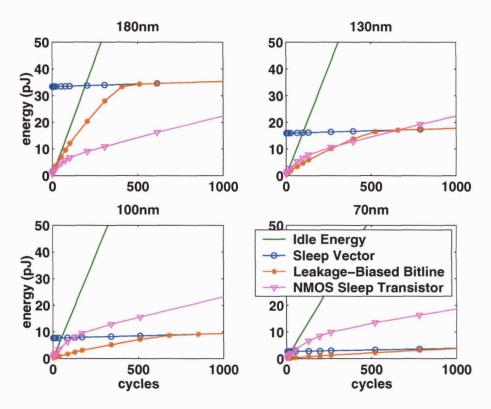

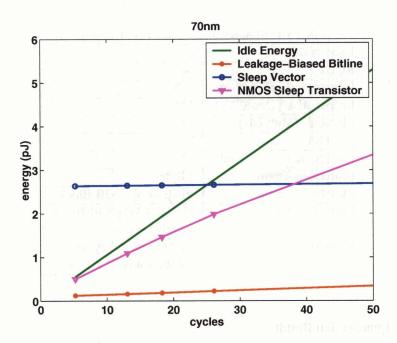

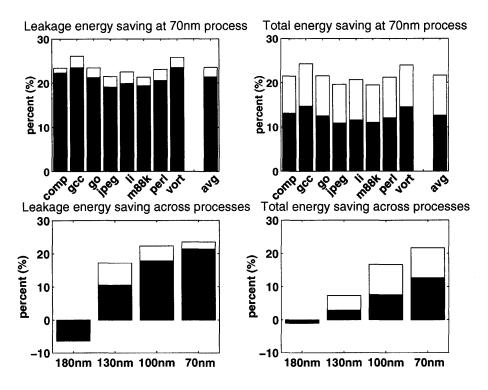

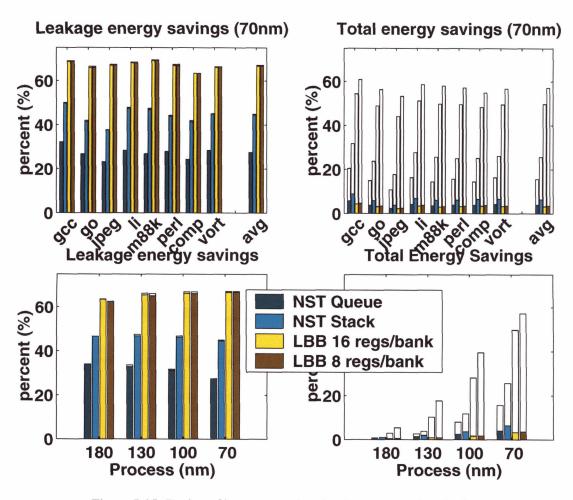

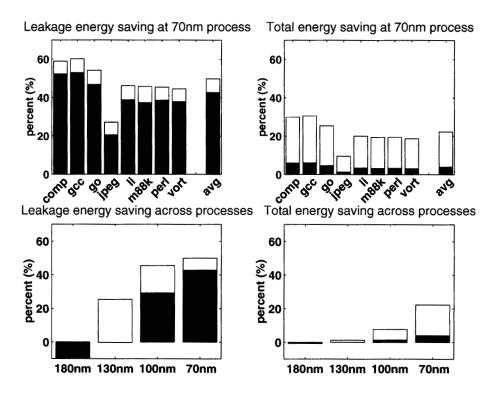

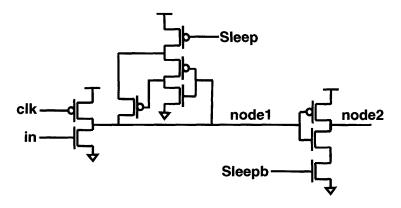

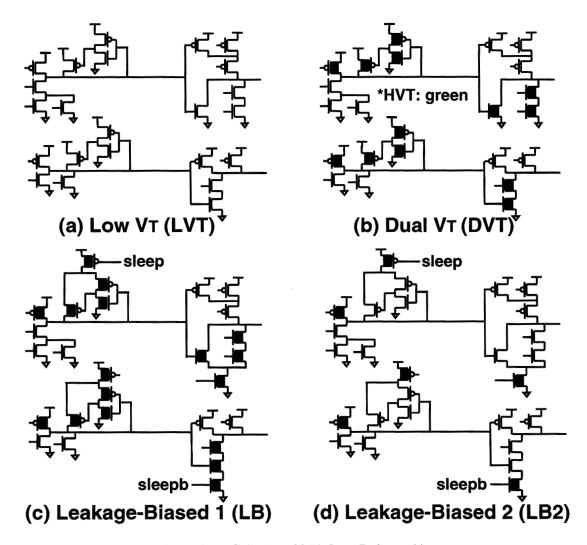

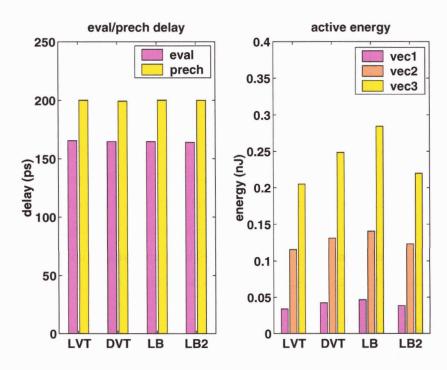

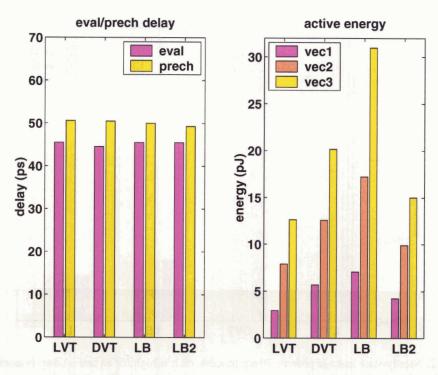

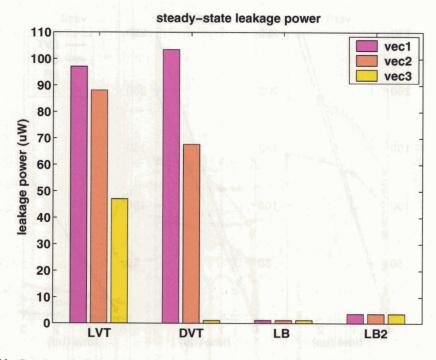

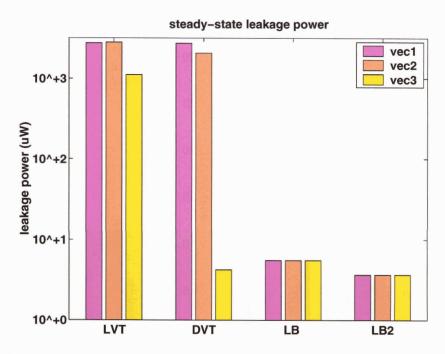

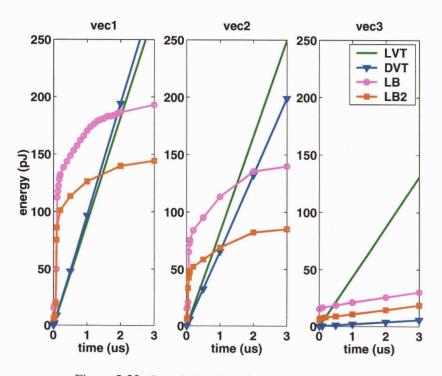

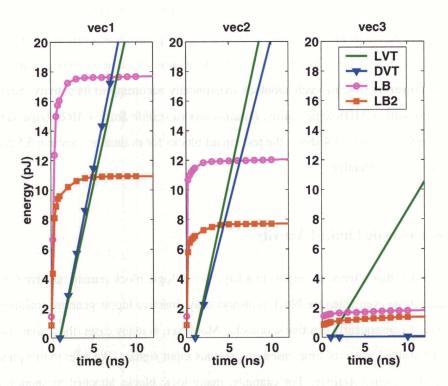

the bitlines of unused memory subbanks into a low-leakage state. LBB has no performance impact and has very low transition energy overheads, and can convert even short idle times into leakage energy savings. We combine LBB with three microarchitectural policies: subbank deactivation for instruction caches, and idle register and read port deactivation for multiported register files. Subbank deactivation saves over 22% of leakage energy and nearly 24% of the total instruction cache energy in a 70 nm technology. Dynamically deactivating idle registers reduces the total register file energy by 57%. Dynamically deactivating read ports saves 4-22% of the total register file energy. Next, we apply LB to domino logic, presenting a new FG-DLR circuit family, Leakage-Biased Domino (LB-Domino) for critical functional units. LB-Domino uses sleep transistors only on non-critical paths and uses the leakage current itself to bias internal critical paths into a minimal leakage state. This technique has little impact on switching energy or delay when applied to conventional domino circuitry. A 32-bit Han-Carlson domino adder circuit is used to compare LB-Domino with conventional and dual  $V_T$  domino circuits. We find that LB-Domino provides two decades reduction in steady-state leakage current compared with low- $V_T$  or dual- $V_T$  domino at equal delay and noise margin, and using LB-Domino to place circuits into a sleep state can yield net energy savings even for sleep times of under 10ns in a 70nm technology.

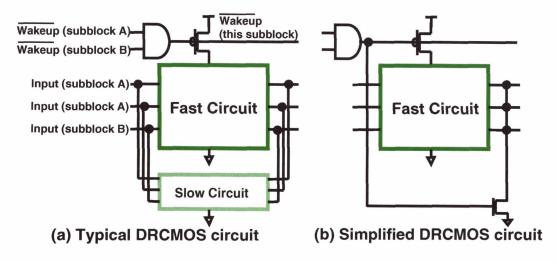

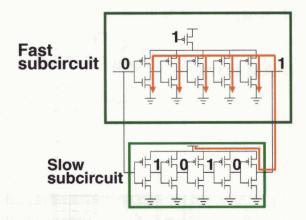

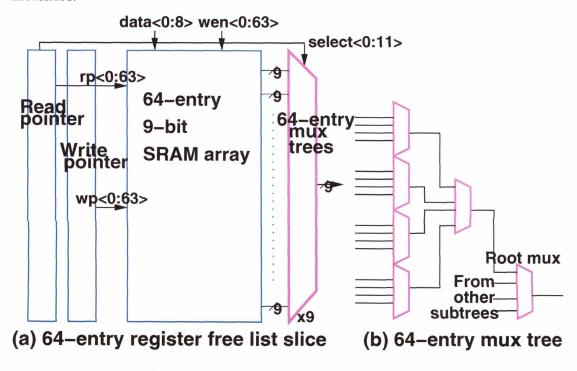

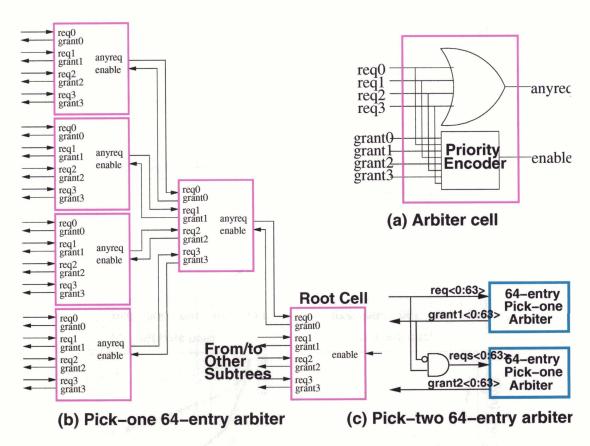

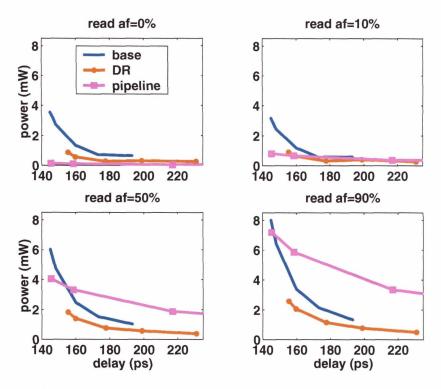

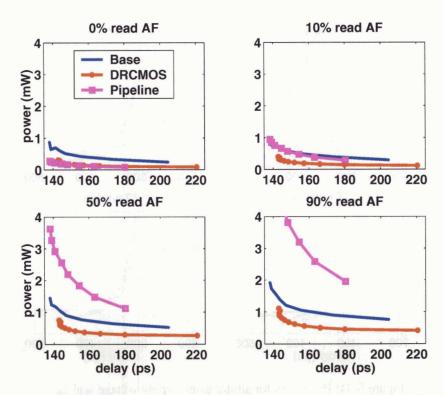

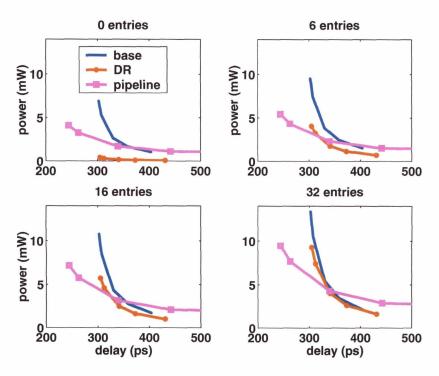

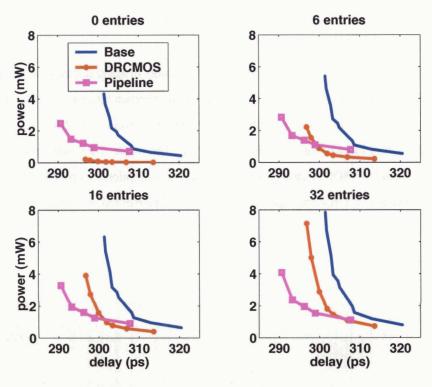

Even within highly active critical blocks, many individual circuit paths are idle on any given cycle, though whether a path is active or inactive changes dynamically during operation. We introduce *Dynamically Resizable CMOS* (DRCMOS) logic that exploits the phenomenon to reduce leakage. DRCMOS dynamically downsizes transistors on idle paths while maintaining speed along active critical paths. DRCMOS logic is successfully applied to two key blocks of a modern superscalar processor: a static 64-entry register free list slice and a static 64-entry pick-two arbiter. We find that DRCMOS can reduce power consumption by up to 50% at equal delay for the critical components of a modern superscalar processor implemented in a 70nm technology.

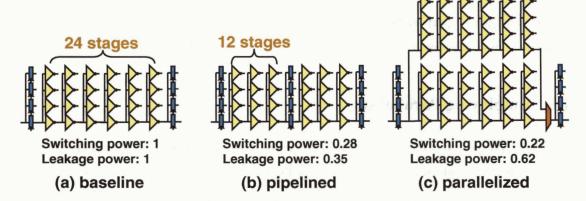

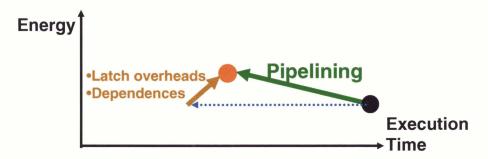

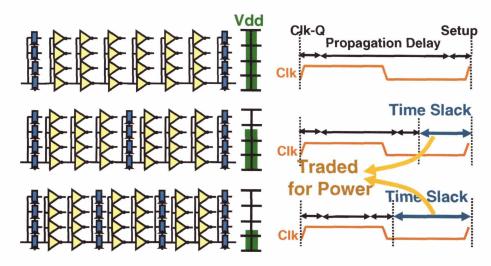

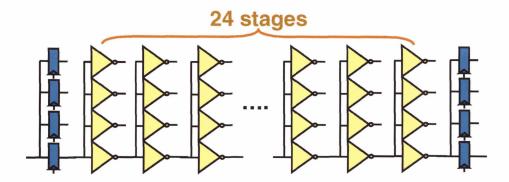

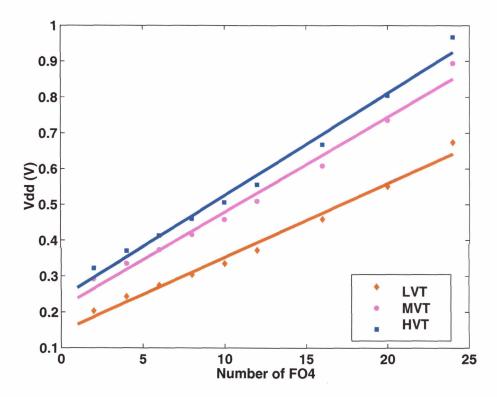

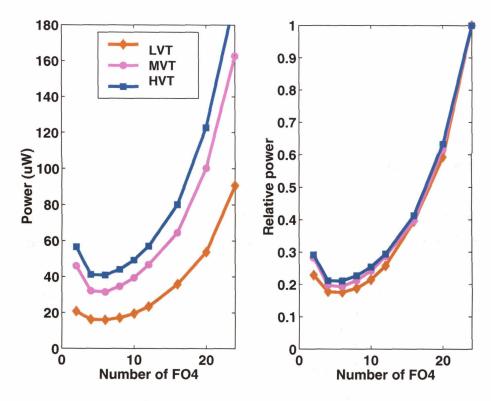

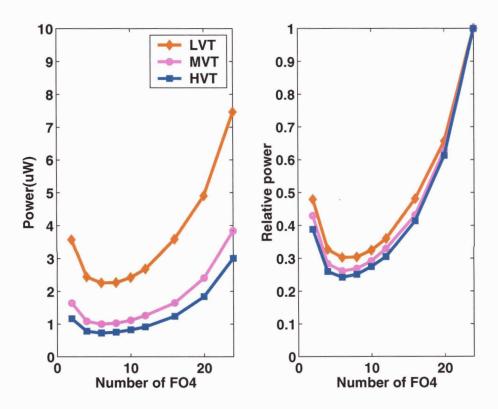

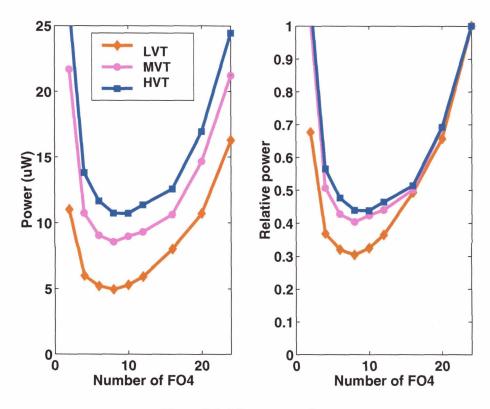

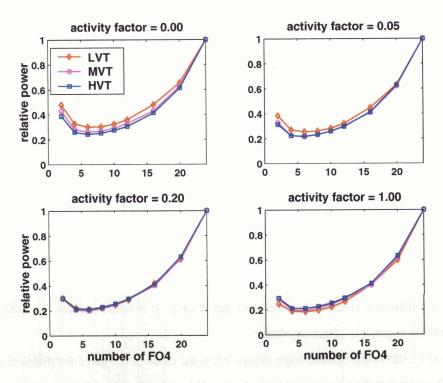

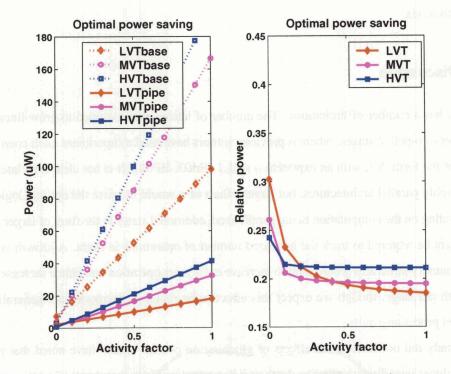

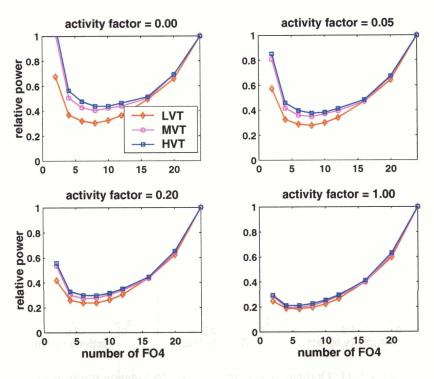

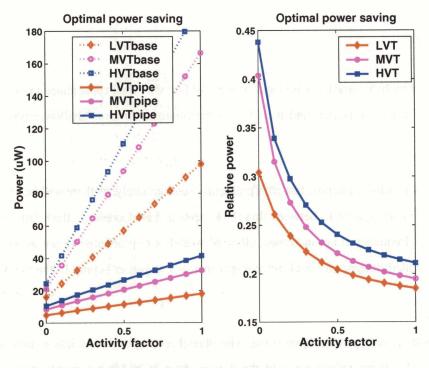

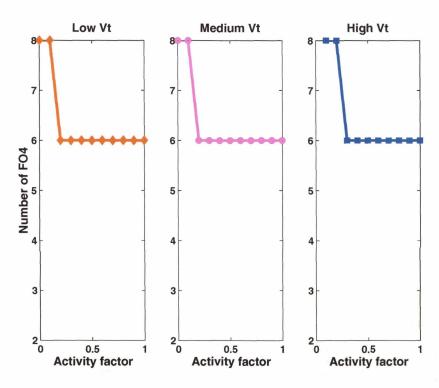

Chapter 6 describes power-optimal pipelining in logic datapaths. Pipelining can be an effective power-reduction tool when used to support voltage scaling in digital systems implementing highly parallel computations. Simulation results show that power-optimal logic depth is 6 to 8 FO4 and optimal power reduction varies from 55 to 80% compared with a 24 FO4 design depending on threshold voltage, activity factor, and the presence of clock-gating in a 70nm technology. We gain some important insights from the simulation results. First, higher activity factors decrease the power-optimal logic depth and increase the optimal power reduction because pipelining is most effective at reducing the additional switching power. Second, pipelining is more effective with lower

threshold voltages, resulting in lower logic depths and lower power, except for low activity factors when leakage power is dominant. Third, clock-gating enables deeper pipelining and more power reduction because it reduces timing element overhead when the activity factor is low.

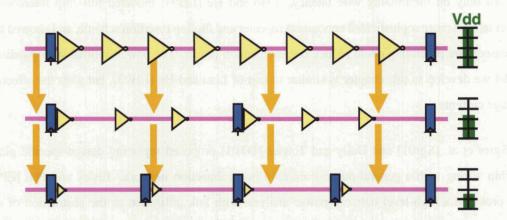

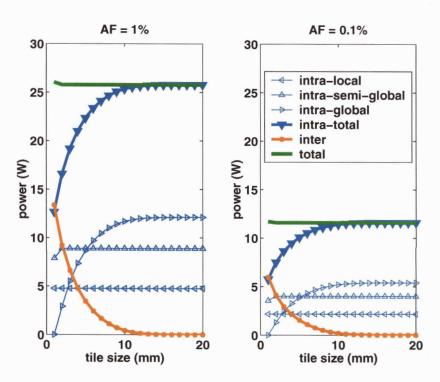

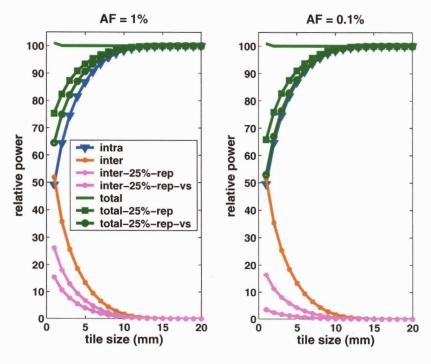

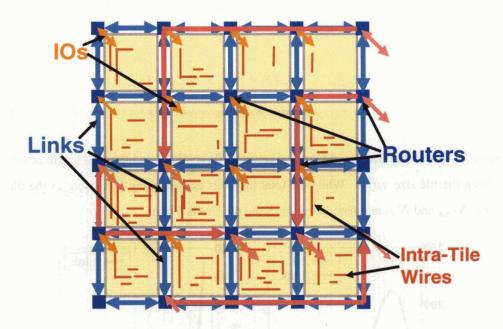

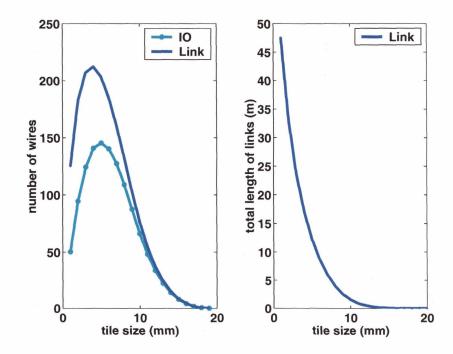

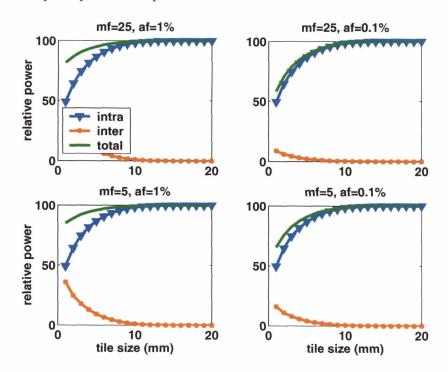

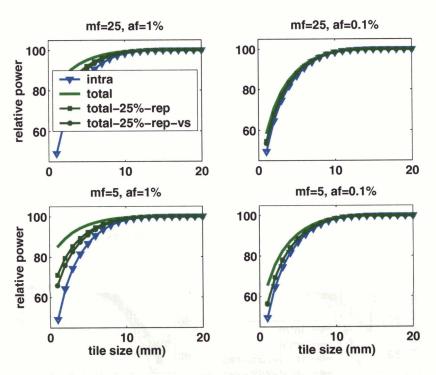

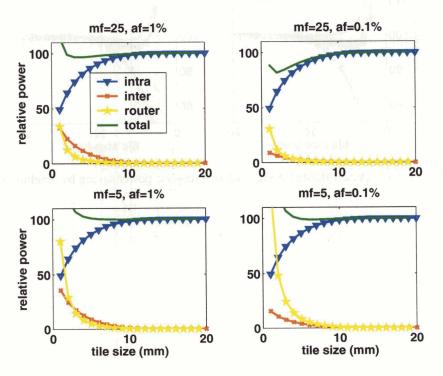

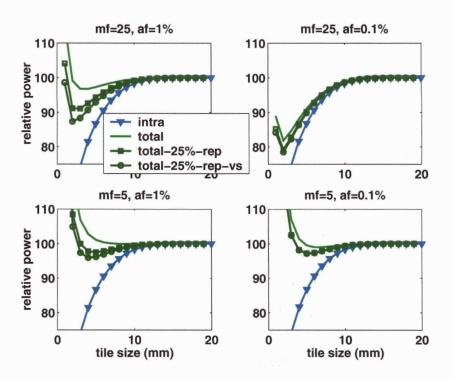

Chapter 7 explores the power implications of replacing global wires with an on-chip network. We optimize network links by combining energy-delay tradeoffs such as pipelining, repeater tuning, and voltage scaling, to significantly reduce the energy to send a bit across a chip. We develop an analytic model of large chip designs with an on-chip two-dimensional mesh network, and estimate the possible power savings for two different design points: a statically wire-routed architecture, and a dynamically packet-routed tiled architecture. For statically wire-routed networks, smaller tiles give more power savings because more inter-tile wires can be power-optimized. Dynamically packet-routed designs have many advantages over wire-routed circuits, such as the reduced number of link wires through multiplexing and signal encoding, but we find that large power reductions are unlikely due to router power overhead. A tile size of around 2mm is optimal in a 70nm technology, balancing the global wire power reduction with the router overhead.

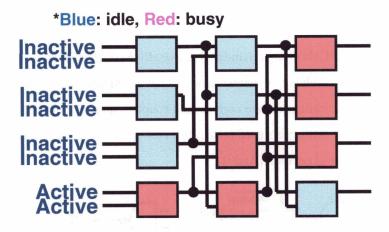

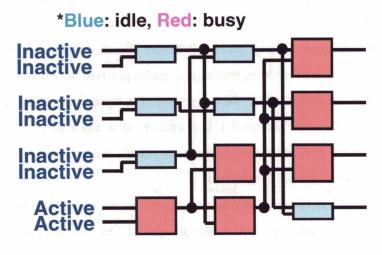

Chapter 8 examines the use of *activity migration* which reduces peak junction temperature by moving computations among multiple replicated units. Using a thermal model that includes the temperature dependence of leakage power, we show that sustainable power dissipation can be increased by nearly a factor of two for a given junction temperature limit. Alternatively, peak die temperature can be reduced at the same clock frequency.

Chapter 9 concludes the thesis, summarizing its contributions and suggesting future work.

## **Chapter 2**

## **Background**

Applications and technology are the major drives in digital system development, but they also have provided ample challenges for circuit designers and architects.

Useful and popular applications, also known as "killer" applications, encourage users to buy systems on which they can run the apps, and encourage system designers to optimize systems so that apps can be run faster with less energy. For personal computing, spreadsheets, word-processing, graphic design tools, and video games were such killer applications. Now, multimedia, streaming, and wireless applications are emerging killer apps throughout all digital platforms, and they are driving circuit and architecture innovations. Multimedia or vector units in high-performance microprocessors are an example of such applications' influence.

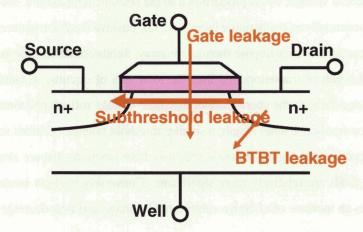

Technology has been the most crucial driving force for the rapid improvement in VLSI digital systems. The success of continuous feature size scaling has brought and will bring greater speed and reliability, lower energy, and smaller size at lower cost. But more importantly, "technology determines the kinds of structures that can be considered and thus comes to shape our view of what a digital system is" [BN71]. Deep submicron technology not only provides great opportunities, but also presents great challenges to circuit designers and architects. A few prominent examples of challenges include ever-increasing leakage from various sources, such as subthreshold, gate, and BTBT leakages, ever-growing susceptibility to process variation, and ever-slowing global interconnects.

This chapter discusses important challenges in optimal VLSI digital system design for deep submicron technology and how circuit- and architectural innovations can be employed to overcome the pending challenges, while next two chapters (Chapter 3 and Chapter 4) describe examples of circuit- and architectural innovations respectively.

Section 2.1 describes how to compare and combine different energy-delay tradeoffs. Section 2.2 describes the ever-tightening peak and average power constraints. Section 2.3 discusses two ways of reducing switching power: trading delay for lower switching power and reducing switching power waste. Section 2.4 gives an overview of subthreshold leakage current. Section 2.5 describes the thermal behaviors of digital systems and then shows how the thermal limit can be overcome and the peak power constraint relaxed using dynamical thermal management.

### 2.1 Energy-Delay Tradeoffs

Optimizing digital systems through energy-delay tradeoffs requires two steps. First, when an innovation is under consideration for a digital system, its energy-efficiency for the target unit and whole system should be analyzed by constructing the energy-delay trading curve. It may be a painstaking task, but the ever-tightening power budget and ever-increasing performance requirement will make this process indispensable. Second, optimal combination among the applicable innovation candidates should be sought.

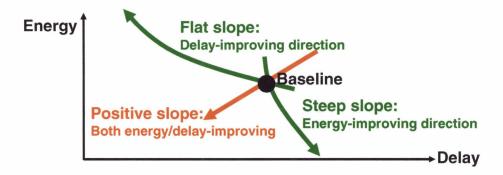

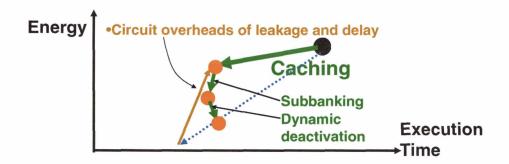

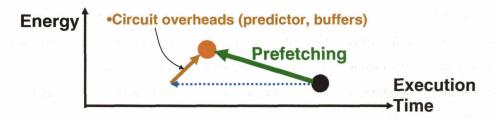

#### 2.1.1 Comparing Energy-Delay Tradeoffs

Slopes, overheads, ranges, and operating regimes are important metrics for comparing energy-delay tradeoffs. Figure 2-1 shows tradeoffs with different slopes. If the slope of a tradeoff is relatively steep (assuming that x axis is delay and y axis is energy), the tradeoff tends to be used for energy reduction. For example, dynamic voltage scaling is usually used to trade time slack for lower energy, not the other way around, because its slope is as steep as quadratic ( $E \propto D^{-2}$ ). Likewise, a tradeoff with a relatively flat slope is often used for improving performance. While most circuit innovations have negative slopes (i.e. delay reduction requires energy increase or energy reduction requires delay increase), some architectural innovations such as caching and subbanking have positive slopes, which mean that the innovations can save energy while improving performance.

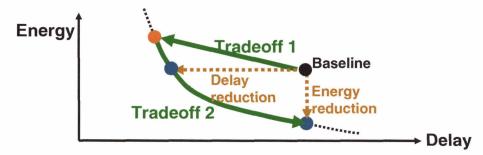

Every tradeoff has a variety of overheads and the overheads make the tradeoff deviate from the ideal slope and give less energy saving or smaller delay reduction than expected from the ideal slope (Figure 2-2). For example, power dissipated by the additional stage latches is the major overhead of pipelining for throughput increase. Each energy-delay tradeoff has its effective energy and delay ranges (Figure 2-2). Utilizing a tradeoff outside the effective ranges is impossible or too costly. For example, supply voltage downscaling is bounded as the circuit becomes too slow due to reduced

Figure 2-1: Energy-delay tradeoffs with different slopes.

gate overdrive  $(V_{dd} - V_T)$  and too vulnerable to noise and process variation. Usually, circuit-level innovations have narrower ranges than architectural ones [Mar04]. Circuit-level techniques that scale voltages, such as supply voltage scaling, often have wider effective ranges compared to those which scale transistor dimension, such as traditional transistor sizing.

Figure 2-2: The overhead and effective ranges of an energy-delay tradeoff.

Tradeoffs have different sensitivities to different operating regimes, which consist of process and environment variables such as oxide thickness and temperature, circuit variables such as circuit styles and supply and threshold voltage levels, and architectural variables such as activity factors and microarchitectures. For example, pipelining combined with supply voltage scaling for energy reduction becomes more effective when the activity factor is high, the threshold voltage is low, and clock gating is present [HA04b].

#### 2.1.2 Combining Multiple Energy-Delay Tradeoffs

A greater level of optimization (smaller energy at the same delay or smaller delay with the same energy) can be achieved by employing multiple energy-delay curves. For example, energy-delay curves with different delay ranges can be combined to make a new energy-delay curve with the extended effective delay range (Figure 2-3).

Figure 2-3: Combining energy-delay tradeoffs for larger effective energy and delay ranges.

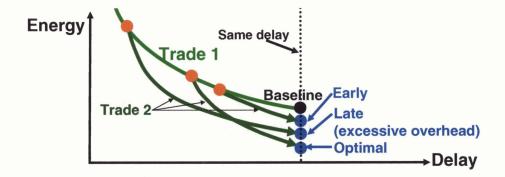

An energy-delay tradeoff with a flatter slope can be combined with an energy-delay tradeoff with a steeper slope, to yield a performance improvement without spending more energy or achieve lower energy at the same performance. Figure 2-4 shows a combination of two tradeoffs with different slopes. From the baseline, performance is increased first with tradeoff1 and then, using tradeoff2, energy can be reduced to the same energy as the baseline with delay reduction or can be further reduced to smaller energy with the same delay as the baseline. Figure 2-5 shows an optimal combination of two energy-delay tradeoffs for maximum energy saving. There exists an optimal combination point because the overhead increases as we decrease the delay or energy through an energy-delay tradeoff.

Figure 2-4: Combining energy-delay tradeoffs for delay reduction at the same energy or energy saving at the same delay.

When optimizing a digital system for minimum energy at the same delay or maximum performance at the same energy, we should carefully compare, select or reject, and combine applicable innovation candidates while observing the energy and delay impacts on the whole system as well

Figure 2-5: Optimal combination of energy-delay tradeoffs for maximum energy saving.

as the target unit. It also should be noted that utilizing multiple energy-delay tradeoffs might increase the design complexity. Also it is possible that some energy-delay tradeoffs are difficult to combine and even when combined, the combination can result in a worse energy-delay tradeoff due to resource conflicts.

### 2.2 Power – Another First-Class Metric

Power was overlooked for years. In the past, power consumption was not significant and a cheap package was enough to cool generated heat, since performance required by applications was relatively low and leakage current was ignorable. Digital system designers were not well aware of power (or energy) inefficiencies and trades between power and performance (or energy and delay). Therefore, innovations were often used for small performance gains while wasting power and other resources such as area and robustness to noise.

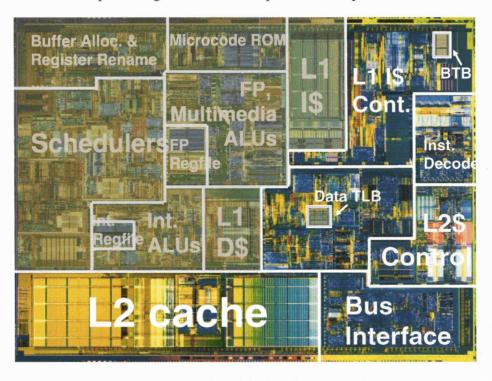

Intel engineers admit that transistor counts and power consumption have been increasing at rates greater than processor performance [Mar01] and over the last ten years. Even when all processors are scaled to the same process technology to isolate the circuit and architecture impacts, relative die size and power has gone up fifteen- and eighteen-fold respectively while relative performance increase is only five- or six-fold. Commonly, for modern high-performance processors, large amounts of area and power are used for work not directly related to computation, such as caching, scheduling, and predicting, to achieve as small as 2X improvement of instruction-per-cycle (IPC). For instance, only a quarter of MIPS R10000 CPU logic is devoted to integer and floating point datapaths, including register files and bypass circuitry [Asa98], and the rest for small performance improvement.

Now power is definitely a first-class metric as well as performance for all digital platforms. The

power metric impacts the optimal digital system design through two constraints.

#### 2.2.1 Power Constraints

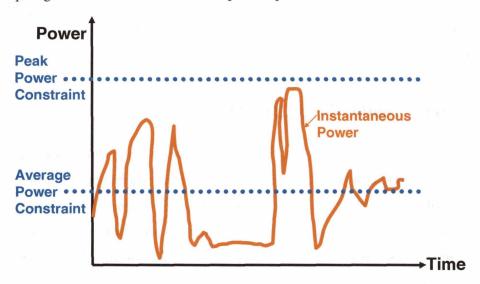

There exist two important power constraints: average power and peak power (Figure 2-6). The first is the average power constraint due to limited battery life or energy cost. To maximize the operating time of a digital system, we have to minimize the energy per task or the average power. We could increase the battery capacity; however, the smaller form-factor and lighter weight requirements of modern mobile digital systems limit the size of battery, and battery technology is only slowly improving. The average power often matters due to the electricity cost (\$/Watt), particularly for large computing resources such as server farms [BDH03].

Figure 2-6: Two power constraints for digital systems.

The second is the peak power constraint due to thermal limits. Transistors dissipate power while charging and discharging parasitic capacitances, and even idle transistors consume significant leakage power. Power is dissipated as heat in digital systems. Because increase in temperature reduces system performance and reliability, heat needs to be removed through packages and fans. It is usual to set a peak power constraint to ensure thermal safety. Therefore, even when a system is plugged into main power, the power which can be traded for performance is still limited by the peak power constraint.

It is important to note that, depending on a system and its applications, there can be more demanding constraints than power. For example, for some systems, area is a critical constraint. There exists a tradeoff between power and area. A larger area budget enables more parallelism to be

exploited for power reduction and allows for a smaller power consumption at a given performance requirement [Mar04]. In addition, since both area and power affect the system cost through the cost of fabrication and the costs of cooling and battery capacity respectively, the optimum is found at the point where the overall cost is minimized. Sensitivity to deterministic and non-deterministic noise and process variation is another important constraint.

## 2.3 Switching Power Reduction

The emergence of the power crisis in digital systems (especially in high-performance processors) has led to the advent of low-power techniques. Low-power techniques have been developed at various levels such as algorithms, architectures, circuits, and devices, and also on various platforms such as general-purpose processors, media processors, DSP ASICs, and FPGAs.

All computations and communications in digital systems are performed via switching and power consumed by switching has dominated total power. The following equation models switching power.

$$P_{switching} = AF \times C_{load} \times V_{dd}^2 \times f_{clock}$$

(2.1)

,where AF is the activity factor,  $C_{load}$  is the parasitic load capacitance,  $V_{dd}$  is the supply voltage, and  $f_{clock}$  is the clock frequency.

Techniques for switching power reduction can be divided into two according to how the power reduction is made. The first group reduces energy waste, energy dissipated by uncontrolled and unnecessary tasks (Section 1.1). Traditionally, energy waste was not significant and often ignored. As a result, the energy-efficiency of such energy-unaware digital systems could be significantly improved by simply finding and minimizing energy waste within the system without a complex re-design. Many architectural innovations reduce energy waste by reducing AF (Eq. 2-1) (Section 4.3). Clock gating is a representative example. Previously, it was common that the whole clock tree in a digital system ticked regardless of whether a circuit block was idle or not. Only after clock power became significantly large did power waste from spurious clock ticking get attention. Clock gating reduces the clock power waste by gating the local branches of the clock tree, if the circuit blocks which local branches feed are not doing any work. The cost for clock gating is an increase in clock control complexity. Likewise, power-aware SRAM arrays gate unnecessary bitline and word-line switching. The cost is again increased control complexity. Now that digital system designers

are well aware of the importance of not wasting precious energy resources, many modern digital systems are well engineered to reduce energy lost to unnecessary capacitance switching.

The second group trades delay for lower energy, that is, through energy-delay tradeoffs (Section 1.2). A variety of circuit-level innovations attempt to tune the transistor dimensions such as the transistor width and length and voltages such as  $V_{dd}$  and threshold voltage  $(V_T)$  to balance energy and delay. The following equation models the transistor delay of a digital circuit.

$$t_{delay} \propto \frac{C_{load} \times V_{dd}}{I_{drain}}$$

(2.2)

$\propto \frac{C_{load}}{k} \times \frac{V_{dd}}{(V_{dd} - V_T)^{\alpha}}$

$$\propto \frac{C_{load}}{k} \times \frac{V_{dd}}{(V_{dd} - V_T)^{\alpha}}$$

(2.3)

,where  $I_{drain}$  is the average on-current,  $\alpha$  is the carrier velocity saturation index (around 1.3 for recent short-channel transistors), and k is the gain factor [Rab96]. As can be seen from the equation, the delay model is closely related to the power model; thus, changing the transistor dimensions or voltage levels provides an intrinsic tradeoff between switching power and delay. For example, scaling down  $V_{dd}$  saves power, but increases the delay. Downsizing transistors reduces  $C_{load}$  and thus switching power, but increases delay because  $C_{load}$  does not scale as fast as k due to the other non-transistor capacitances such as interconnect caps. The design of the StrongArm 110 shows how to lower power, by sacrificing performance through direct energy-delay tradeoffs [Dob96]. The StrongARM's low-power circuit decisions include lowered supply voltage and a design change from latches to flipflops for clock load reduction. Chapter 3 presents more details on how circuit techniques for digital systems tune transistor dimensions and structures, and voltages to trade energy and delay.

#### 2.4 Leakage Current

The recent exponential increase in leakage current results from two main factors: process scaling and die temperature increase. As the feature size shrinks, so do the supply and threshold voltages to keep the electric fields on the channels constant. Linear scale-down of threshold voltage has led to an exponential increase in leakage current. If this trend of constant threshold voltage scaling would continue, leakage current would increase by five times each generation [CBF00, DB99]. Leakage current is also exponentially proportional to die temperature. Continuous increase of total chip power has increased the average die temperature and contributed to leakage increase. Leakage power is now comparable to dynamic switching power in high-performance digital systems.

The trend toward ever more complex processors further exacerbates the situation. Large numbers of transistors are added for relatively small improvements in performance and these additional transistors may dissipate considerable subthreshold leakage power even when not actively switching. Effective leakage reduction techniques will be the key for optimizing digital systems as well as enabling further aggressive technology scaling.

### 2.4.1 Subthreshold Leakage

Leakage current is the drain current when the gate-to-source voltage is zero. Subthreshold leakage current due to weak inversion is now by far the most dominant component of transistor leakage among various transistor leakage components. When gate voltage is below threshold voltage, weak inversion occurs at the channel and causes the carriers to move by diffusion along the surface.

Figure 2-7: Leakage components of deep submicron transistors.

Subthreshold leakage is a complex function of many different variables such as threshold and supply voltages, temperature, and the physical and effective dimensions of channels. The following equation shows the subthreshold leakage model.

$$I_{subthreshold} \propto \frac{W}{t_{OX}L_{eff}}e^{\frac{-V_T - \gamma^{'}V_{sb} + \eta V_{dd}}{nv_T}}$$

(2.4)

$v_T$  is the thermal voltage,  $\gamma'$  is the linearized body effect coefficient,  $\eta$  is the DIBL coefficient, W is the transistor width,  $L_{eff}$  is the effective channel length, and  $t_{OX}$  is the oxide thickness. The subthreshold conduction current is exponentially proportional to threshold voltage (Eq. 2-

4) and threshold voltage is inversely proportional to transistor delay (Eq. 2-3), thus controlling threshold voltage provides a tradeoff between leakage power and delay. Supply voltage affects subthreshold leakage current through the DIBL phenomenon. When the channel length is relatively short compared to drain voltage level, drain voltage can lower the source potential barrier and as a result, effective threshold voltage level. Because of the DIBL effect, supply voltage scaling results in a superlinear reduction of leakage power rather than linear. Body voltage affects the effective threshold voltage through the body effect. Reverse body biasing (biasing the body voltage of NMOS transistors below the source voltage or biasing the body voltage of PMOS transistors above the source voltage) increases the charge stored in the depletion region and the surface potential required for strong inversion, and as a result, it raises the effective threshold voltage and reduces subthreshold leakage.

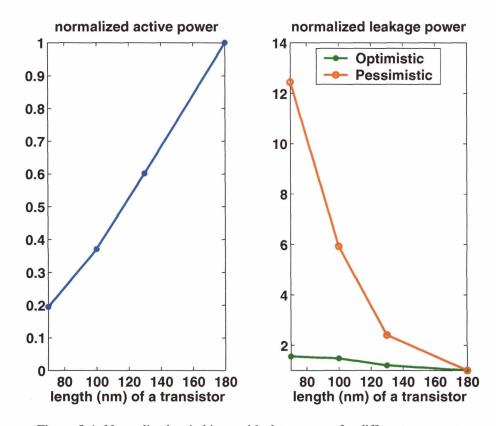

The subthreshold slope ( $nv_T$  in Eq. 2-4) flattens by a factor proportional to the absolute temperature since the thermal voltage,  $v_T$ , is proportional to the absolute temperature. As a result, leakage current grows exponentially as temperature increases. The positive feedback between leakage power and temperature can lead to catastrophic thermal runaway. Subthreshold leakage is linearly proportional to the total width of transistors and thus the total area of circuits. Channel length affects subthreshold leakage through the short-channel threshold voltage roll-off phenomenon (not shown in Eq. 2-4). With a smaller channel length, a smaller threshold voltage becomes sufficient to cause strong inversion because the regions below source and drain junctions that are already depleted by source and drain fields are relatively more significant. Conversely, a slight increase of the channel length leads to an increase of effective subthreshold voltage and thus decrease of subthreshold leakage current.

Process variation, one of the most important source of non-scalability in deep submicron technology, complicates the leakage problem further. The worsened process variation leads to significant delay spread and affects the yield severely, thus favoring faster and leakier designs. The impact on leakage spread is also significant. It has been shown that there can be 20X variation in leakage current in a 150nm technology [Aga05]. Soon, leakage reduction techniques considering the possible yield loss due to the delay and leakage spreads will be crucial.

Aggressive technology scaling has caused various short channel effects (SCE), such as drain-induced barrier lowering (DIBL), threshold voltage roll-off, and reduced on-current to off-current ratio. To mitigate SCEs, oxide thickness scaling and higher and non-uniform doping, such as halo and retrograde well, have been utilized by device engineers. The low oxide thickness gives rise to

high electric field across the oxide  $(E_{ox})$ , resulting in significant gate oxide tunneling current (Figure 2-7). On the other hand, a high doping level leads to high electric field across source and drain junctions, resulting in significant junction band-to-band tunneling (BTBT) current (Figure 2-7). In the near future, gate and junction BTBT leakages are expected to be comparable to subthreshold leakage [Aga05]. Therefore, leakage reduction techniques considering all these components will be indispensable. Though the importance of other leakage components is increasing rapidly, they are beyond the scope of this research and we focus on subthreshold leakage, which requires a more urgent fix. If not specified, leakage implies subthreshold leakage in the remainder of this thesis.

#### 2.5 Thermal Constraint

Ever-increasing power consumption and ever-decreasing form-factor of digital systems have increased heat density and die temperature rapidly. Raised junction temperature causes decreased delay and increased leakage. Increasing temperature raises the thermal agitation of the semiconductor atoms, which in turn increases lattice scattering and causes an approximately quadratic decrease of mobility [Pie96]. The reduced mobility leads to reduced circuit speed and possible timing errors.

The linear increase of temperature makes leakage power increase exponentially (Section 2.4). The leakage power increase might lead to the further temperature increase in return. This positive feedback can cause catastrophic thermal runaway, if there is no dynamic thermal management scheme to sense high temperature and reduce temperature by decreasing power density dynamically. Additionally, soft errors and transistor aging also increase exponentially with temperature.

#### 2.5.1 Thermal Behavior of Digital Systems

Power, P, in electrical systems is mainly converted to heat energy (or heat flow), Q.

$$Q \propto P$$

(2.5)

Heat energy dissipation causes an increase in temperature. The following equation represents the law of heat conduction, where Q is proportional to the gradient of steady-state temperature difference,  $\Delta T$ , and area, A, while inversely proportional to thickness, l.

$$Q \propto \Delta T \frac{A}{l} \tag{2.6}$$

Rearranging the above equations,

$$\Delta T \propto \frac{P}{A}$$

(2.7)

We see that the steady-state temperature difference is proportional to power, P, and inversely proportional to area, that is, power density (power divided by area). As power densities of high-performance digital systems rise above  $100\,\mathrm{W/cm^2}$ , providing adequate heat removal with a low cost package is becoming particularly challenging. Cooling or packaging costs are proportional to net heat density. Heat density or flux is proportional to the amount of heat and inversely proportional to the form factor. Because cost-effective package design is beyond the scope of this thesis, we simply assume that packages with fixed dimensions are given, and heat and heat density are not differentiated in this thesis.

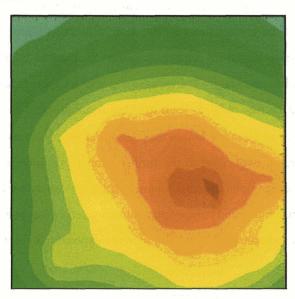

Figure 2-8: A simulated thermal plot of the Pentium 4 processor [Gun01]. Darker color indicates higher temperature.

Three basic observations can be made on the thermal behaviors of digital systems. First, temperatures on dies are far from uniform. The uneven distribution of power dissipation across a die complicates heat removal. The uneven power density leads to hot spots where regions of a die have significantly elevated junction temperatures compared to inactive regions. The reason why hot spots develop is that silicon is a relatively poor heat conductor and cannot efficiently spread heat across a die. Figure 2-8 shows a thermal plot of the Pentium 4 processor [Gun01]. The plot clearly indicates a small region with much higher temperature than the rest. Hot spots provide a serious impedi-

ment to achievable performance since they require that total power dissipation is reduced until all hot spots have junction temperatures below the reliability limit. Hot spots typically occur at the granularity of architecture-level blocks [Ska03].

Second, temperature depends not only on power density, but also on time, due to thermal capacitances. The thermal capacitances of digital systems and surrounding packages are significantly large that all thermal processes such as heating, heat spreading, and cooling take noticeable time. Lastly, there is a significant gap between the typical- and worst-case power since most applications have limited amount of parallelism, due to dependences, compared to the maximum parallelism the digital system can afford, and have low signal transition probabilities compared to the worst-case pattern.

#### 2.5.2 Temperature-Aware Design

Thermal limit has led to strict peak power constraints (Section 2.2.1) and digital system designers optimize systems strictly under the constraints to ensure thermal safety while maintaining reasonably cheap packages. This worst-case design style is safe, but tends to be extremely conservative, resulting in limited performance.

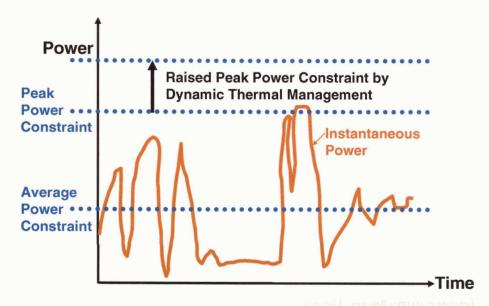

Temperature-aware design has been proposed to attain further optimization. Temperature-aware design deals with thermal issues more directly. Instead of designing for the worst peak power, it designs for the typical high power and the rare thermal emergencies are taken care of dynamically. Through dynamic thermal management, the peak power constraint is effectively relaxed (Figure 2-9).

Temperature-aware design has two requirements: thermal sensors and dynamic thermal management units. Modern high-performance processors include on-die thermal sensors that can detect over-temperature conditions caused by inadequate heat removal. Although originally designed to detect thermal emergencies caused by poorly attached heat sinks, broken fans, or blocked air vents, thermal sensors can also be used in dynamic thermal management schemes that exploit the growing gap between typical- and worst-case power dissipations [San97]. Thermal sensors are usually distributed throughout the whole chip, making sure that the possible hot spot candidate areas are covered. Simulation with benchmark applications would help to find possible locations for thermal sensors. When the thermal sensors detect die temperature increase over a trigger point, they signal the dynamic thermal management unit, and the unit starts to reduce the power density of the problem area. When the temperature falls to a safe range, the unit stops reducing the power density.

Figure 2-9: Relaxing peak power constraint through dynamic thermal management.

The performance penalty during cooling and transition (between the normal state and thermal emergency state) energy and delay costs should be minimized. Cooling only the hot spots usually gives less performance penalty than cooling the whole die, while allowing the same amount of increase in the effective power budget. Dealing with intrinsically-local heating with global cooling is not cost-effective. However, implementing localized cooling might lead to a significant increase in design complexity.

## Chapter 3

## **Categorizing Circuit Innovations**

Numerous circuit- and architectural innovations have led to the rapid improvements of VLSI digital systems. This chapter categorizes circuit innovations from the perspective of energy waste reduction and power-performance tradeoff.

Circuit innovations have two goals (Figure 3-1). First, they can trade time slack on non-critical paths for lower energy. Second, they can reduce the delay of critical paths and decrease the cycle time, and thus total execution time.

Figure 3-1: Goals of circuit innovations.

Circuit innovations often do not stand alone. Commonly, they are combined with architectural innovations. For example, dynamic voltage scaling is a circuit technique which dynamically scales supply voltage and saves energy while meeting the performance requirement. However, an accompanying architectural innovation is necessary for finding time slack. Chapter 4 categorizes the architectural innovations for digital systems.

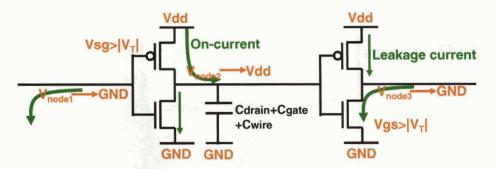

### 3.1 Digital Circuits

We observe that digital circuits are constructed with two major components: first, currents and parasitic capacitances of transistors, and second, voltages (Figure 3-2). A digital system is basically a web of switches, and computes and communicates by switching modes between zero and one. Modern electrical digital systems built in CMOS technologies use transistors as the switches and switching is done through charging and discharging the parasitic capacitances using the on-currents of the transistors. Thus, tuning transistors' dimensions has substantial effect on the energy and delay of the system since it directly impacts both the parasitic caps and on-currents (and also leakage currents). Sizing transistors is the most basic form of circuit-level optimization.

A few discrete voltage levels greatly affect digital circuits. The digital values, zero and one, are established by ground (GND) and supply voltage  $(V_{dd})$  respectively. Transistors are turned on and start to flow on-currents when the gate voltages exceed the threshold voltage  $(V_T)$ . In addition, the body voltage (not shown in Figure 3-2) affects  $V_T$  and thus the on- and off-currents. Thus, it is intuitive that manipulating  $V_{dd}$  and  $V_T$  can provide direct control of the systems' performance and power.

Figure 3-2: Decomposing a digital circuit: currents and parasitic capacitances of transistors and voltages.  $C_{drain}$ ,  $C_{gate}$ , and  $C_{wire}$  are the parasitic transistor drain and gate caps, and wire cap respectively.

We divide circuit innovations into two, according to whether a circuit innovation focuses more on sizing transistors (Section 3.2) or scaling voltages (Section 3.3).

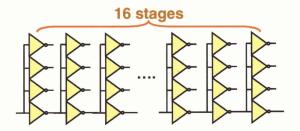

If not specified otherwise, all the energy-delay plots in this chapter were made through Hspice simulation of a 16 FO4 inverter chain (Figure 3-3). BPTM 70nm technology [Dev01] was used and important parameters of the process are summarized in Table 3.1.

Figure 3-3: An FO4 inverter chain.

Table 3.1: Process parameters.

| The state of the s |        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| Nominal supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.0V   |  |  |  |  |

| Nominal NMOS threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.21V  |  |  |  |  |

| Nominal PMOS threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -0.24V |  |  |  |  |

| Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100 °C |  |  |  |  |

## 3.2 Tuning Transistors' Dimensions

Sizing transistors impacts both on-current and leakage currents  $(I_{on}, I_{subthreshold} \propto \frac{W}{L_{eff}})$ , where W and  $L_{eff}$  are the width and effective length of a transistor) and also the parasitic capacitances  $(C_{gate} \propto WL_{eff}, C_{diffusion} \propto W)$ , giving a tradeoff among delay, switching energy, and leakage power. The basic rule of transistor sizing is to upsize transistors on critical paths while downsizing non-critical ones such as feedback transistors in sequential logic or keepers in dynamic circuits. Energy saved by downsizing non-critical transistors and reducing the amounts of parasitic capacitance and leakage current can be exploited by upsizing transistors for delay reduction.

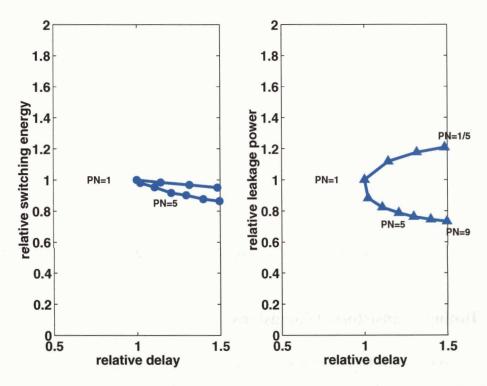

Figure 3-4 shows the effects of varying the PN ratio  $(\frac{W_{PMOS}}{W_{NMOS}})$  when the total sum of PMOS and NMOS widths is fixed. Since the total parasitic capacitance remains constant, the switching energy does not change much. Reducing NMOS transistor width (increasing the PN ratio) decreases leakage power since the leakage current of NMOS transistor is larger than that of PMOS transistor when the sizes are identical.

Most circuit blocks consist of cascaded stages, and load balancing between stages is necessary to achieve the lowest power at a given delay requirement [SSH99]. While the minimum delay design requires the delay of every stage to be the same, the power-optimal sizing downsizes the largest gates toward the output and increases the effective fan-out from the minimum delay point [Sto95] (The fan-out is defined as the amount of logic gates connected to the output of a logic gate).

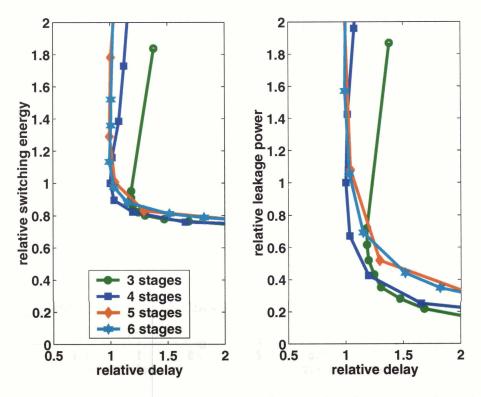

Figure 3-5 shows the effects of varying the fan-outs and number of stages when the load capacitance is fixed. Increasing the fan-out further after the minimum latency point results in the excessive

Figure 3-4: Varying the PN ratio. Switching energy, leakage power, and delay are normalized to the minimum delay point.

energy increase due to overheads such as the increases of parasitic capacitance and leakage current. Around 20% of switching energy and 70% of leakage power can be saved by increasing the delay by 50% from the minimum delay point.

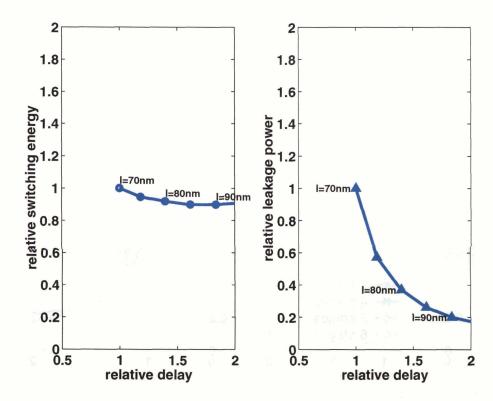

Figure 3-6 shows that lengthening the transistor can be used as an effective leakage reduction tool (Section 5.1.1). A small increase in transistor length away from the minimum gives a significant reduction in leakage current with a small impact on delay, because the effective threshold voltage depends on the length when it is short. The StrongARM processor design reduces leakage current by lengthening devices in cache arrays and pad drivers by 10–30% [Dob96].

## 3.3 Tuning Voltages

This section discusses the effects of varying the supply, threshold, and body voltages on the energy and delay of the digital circuit.

Figure 3-5: Varying the fan-out and hence number of stages when the load capacitance is fixed. Switching energy, leakage power, and delay are normalized to the minimum delay point.

#### 3.3.1 Scaling Supply Voltages

In a deep submicron process, the nominal  $V_{dd}$  is already around the critical voltage [Cha92], and the amount of current is less dependent upon the supply voltage due to the velocity saturation effect. Hence, increasing performance through voltage scaling requires excessively large energy. On the other hand, supply voltage scaling can be used as a highly efficient energy-saving tool. The following equations show that roughly 2% reduction of switching energy can be achieved with only 1% delay increase (assuming  $V_T << V_{dd}$  and the mobility degradation due to the short channel is not significant).

$$E_{switching} = C_{load}V_{dd}^2 (3.1)$$

$$Delay \propto \frac{1}{V_{tt}}$$

(3.2)

$$E_{switching} \propto \frac{1}{Delay^2}$$

(3.3)

$$\Delta E_{switching} = -2\Delta Delay \tag{3.4}$$

Figure 3-6: Lengthening transistors for leakage reduction. Varying the fan-out and number of stages when driving a fixed load. Switching energy, leakage power, and delay are normalized to the minimum length point.

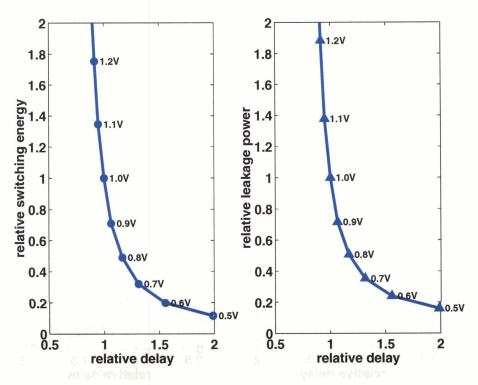

In deep submicron technology, even the leakage current is dependent upon  $V_{dd}$  through the drain-induced-barrier-lowering (DIBL) phenomenon and as a result, the leakage power is super-linearly dependent upon  $V_{dd}$ . Figure 3-7 shows the effects of  $V_{dd}$  scaling. It is clearly seen that the  $V_{dd}$  scaling is effective at both switching energy and leakage power saving.

To keep the gate overdrive,  $V_{dd}-V_T$ , reasonably large and avoid excessive slowdown ( $Delay \propto \frac{V_{dd}}{(V_{dd}-V_T)^{\alpha}}$ , where  $\alpha$  is the mobility degradation factor and around 1.3),  $V_{dd}$  downscaling has been forcing  $V_T$  to scale down too. The  $V_T$  downscaling has led to the rapid increase of leakage power (Section 2.4), which is the major obstacle to  $V_{dd}$  scaling.

Some emerging applications such as medical applications and distributed sensor networks have low energy as the primary concern rather than performance. Subthreshold operation has been used for these ultra low-energy applications because minimum energy operation for low performance situations occurs in the subthreshold region. An ultra-low voltage FFT processor whose  $V_{dd}$  can be lowered to 180mV was implemented in a 180nm process and was measured to be 8x more energy-efficient than the standard superthreshold implementation [Wan02a].

Figure 3-7: Scaling supply voltage. Switching energy, leakage power, and delay are normalized to the nominal voltage, 1V.

#### 3.3.2 Scaling Threshold Voltages

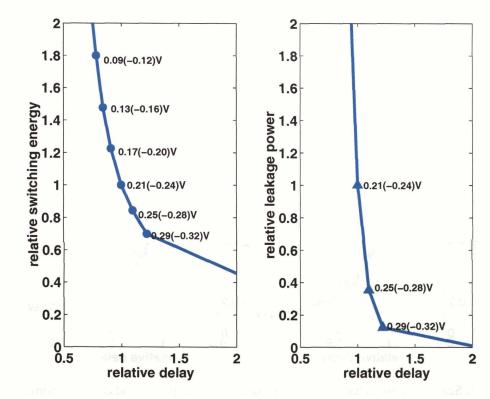

Previously,  $V_T$  was less important than  $V_{dd}$  in terms of both energy and delay. It was too small to affect the gate overdrive,  $V_{dd} - V_T$  and too large to cause a significant subthreshold leakage power consumption. However, continuous supply voltage down-scaling has led threshold voltage to become large enough to impact circuit delay through reduced gate overdrive and small enough to cause leakage power to be comparable to switching power. Figure 3-8 shows the effects of  $V_T$  scaling on delay, switching energy, and leakage power. Switching energy decreases as  $V_T$  increases because the short-circuit current (the current flowing when PMOS and NMOS transistors are simultaneously turned on and the path from  $V_{dd}$  to GND is briefly made) is reduced. It is clearly seen that  $V_T$  scaling provides an effective leakage power reduction tool. At our 70nm process, around 25% delay increase can save 90% of leakage power.

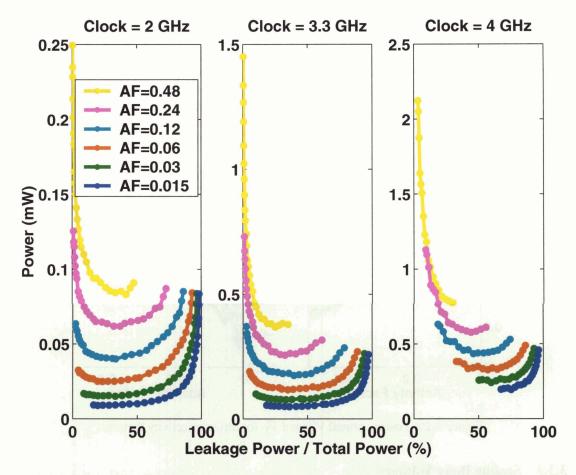

Deep submicron technology often requires the simultaneous scaling of supply and threshold voltages to meet ever-high performance goals while keeping ever-tight power constraints. Figure 3-9 shows the optimal leakage power ratio when both  $V_T$  and  $V_{dd}$  are scaled. We measured the total power and the ratio between leakage and total power while varying  $V_T$  and  $V_{dd}$  for a given delay

Figure 3-8: Scaling threshold voltage scaling. Switching energy, leakage power, and delay are normalized to the nominal threshold voltages, 0.21/-0.24V.

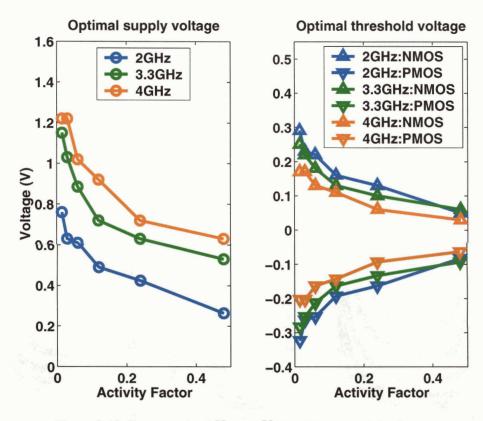

requirement and activity factor (AF). It can be seen that the optimal ratio is rather wide and the total power curves are quite flat around the 50% ratio regardless of the delay requirement. As AF increases, the optimal ratio tends to increase slightly. An analysis by closed-form equations [NS00] and a circuit simulation [Mar04] also show that the total power has a very shallow minimum when represented as a function of leakage and total power ratio, and the optimal ratio is around 30-40%, and that the value of ratio is not changed even over a wide range of design parameters such as activity factor, logic depth, and clock frequency. Figure 3-10 shows the optimal  $V_{dd}$  and  $V_{T}$  that gives the lowest total power. The simulation results show that the optimal threshold voltage is strongly dependent on the activity factor. When AF is low, the optimal  $V_{T}$  become high to reduce leakage power. On the other hand, when AF is high, the optimal  $V_{T}$  becomes low to reduce  $V_{dd}$  and thus switching power. The optimal supply voltage is a function of both the delay requirement and AF.

With additional manufacturing cost, multiple  $V_T$  transistors can be used for a further optimization. One straightforward way of exploiting multiple  $V_T$  transistors when  $V_{dd}$  is fixed is to make non-critical transistors high  $V_T$  for leakage power saving while employing low  $V_T$  transistors on

Figure 3-9: Power-optimal ratio of leakage power and total power for different delay requirements and activity factors.

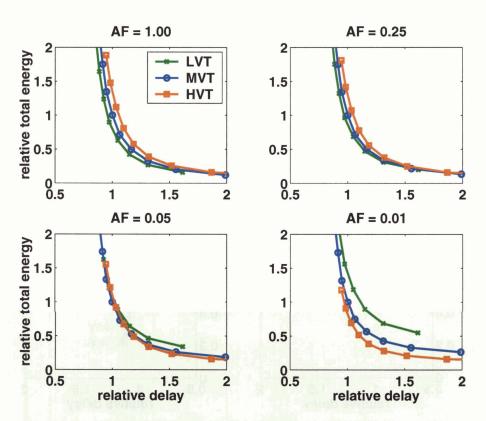

critical paths.  $V_{dd}$  scaling can also be improved by utilizing multiple  $V_T$  transistors. Figure 3-11 shows that the best energy-delay curve differs according to the AF. LVT requires the lowest total energy at the same delay when AF is high, because the  $V_{dd}$  of LVT is the smallest and so is the switching energy. Conversely, HVT is the best when AF is low, since it has the lowest leakage while its  $V_{dd}$  is larger than others.

The optimal voltage levels ( $V_{dd}$  and  $V_T$ ) in individual circuit blocks rarely coincide because of differences in structure when circuit blocks are combined. While allowing multiple  $V_{dd}$  and  $V_T$  leads to a better optimization point, it requires additional manufacturing cost and increases area and design complexity. For example, employing multiple  $V_{dd}$ s, where a low  $V_{dd}$  is used for non-critical paths and a high  $V_{dd}$  on critical paths, requires multiple power planes and level converters between different  $V_{dd}$  regions.

Figure 3-10: Power-optimal  $V_{dd}$  and  $V_T$  for different activity factors.

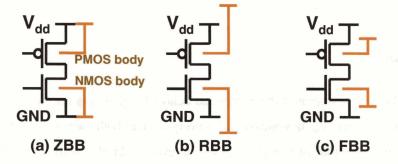

## 3.3.3 Scaling Body Voltages

Traditionally, bodies were tied to supply voltages and grounds in bulk CMOS processes. However, energy-delay tradeoff using body biasing has received attention as leakage power has become significant. Body biasing takes advantage of the body effect to adjust the effective threshold voltage and reduce the leakage power waste. Eq. 3-5 models the body effect. In the equation,  $\Phi_F$  is the Fermi potential,  $\gamma$  is the body effect coefficient,  $V_{T0}$  is the zero bias threshold voltage, and  $V_{sb}$  is the source-body voltage.

$$V_T = V_{T0} + \gamma(\sqrt{|-2\Phi_F + V_{sb}|} - \sqrt{|-2\Phi_F|})$$

(3.5)

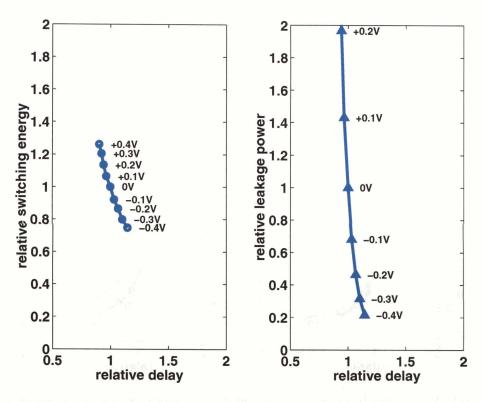

Figure 3-12 shows the impact of body biasing on the delay, switching energy, and leakage power. Reversely body biasing (0 $\sim$ -0.4V) results in reduced switching energy since the short-circuit current decreases when  $V_T$  increases. Around 20% delay increase can bring as much as 80% leakage power saving.

Body biasing can be done in two ways: reverse body biasing (RBB) or forward body bias-

Figure 3-11: Scaling supply voltage for different threshold voltages and activity factors. AF is the activity factor and LVT, MVT, and HVT are low-threshold, medium-threshold, and high-threshold transistors respectively. Switching energy, leakage power, and delay are normalized to the MVT and nominal  $V_{dd}$  point.

ing (FBB) (Figure 3-13). RBB dynamically increases the effective threshold voltage of originally low-threshold transistors when they are idle. On the other hand, FBB dynamically decreases the effective threshold voltage of originally high-threshold transistors when they are in operation. In deep submicron technology, FBB is preferable to RBB because it uses high-threshold transistors, which have less short-channel effect and threshold voltage variation [Nar03].

# 3.4 Summary

Circuit innovations have improved the energy and delay of digital systems through sizing transistors and scaling voltages.  $V_{dd}$  downscaling effectively reduces both switching energy and leakage power. Lengthening the transistor, increasing  $V_T$ , or reversely biasing body voltage provide effective leakage power reduction for delay increase. When both  $V_{dd}$  and  $V_T$  are scaled, the optimal leakage power ratio is around 50% regardless of the activity factor or delay requirement and the

Figure 3-12: Biasing body voltages. Switching energy, leakage power, and delay are normalized to the zero body bias point.

optimal  $V_T$  depends on AF. In a multiple  $V_T$  process, Low- $V_T$  gives the best energy-delay curve for  $V_{dd}$  scaling at high AF while high- $V_T$  gives the best energy-delay curve for  $V_{dd}$  scaling at low AF.

Figure 3-13: Zero body biasing (ZBB), reverse body biasing (RBB), and forward body biasing (FBB) for digital circuits.

# **Chapter 4**

# **Categorizing Architectural Innovations**

The goal of architectural innovations for processors is to provide a structure that can run instruction streams with maximum concurrency, minimum stalls, and minimum waste.

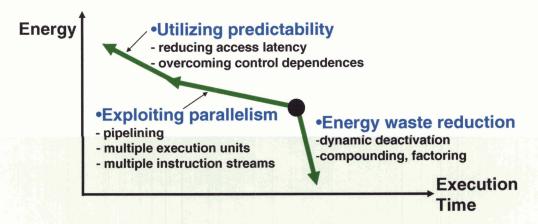

We find that most architectural innovations are based on three critical techniques: employing parallelism, exploiting predictability, and reducing energy waste. Architectural innovations seek and make use of the intrinsic parallelism and predictability in programs and computation models to maximize the utilization of system resources, while minimizing the inefficient use of energy resources. This chapter categorizes architectural innovations for processors from the perspective of energy waste reduction and energy-delay tradeoff principles.

It should be noted that the categorization in this chapter is not exclusive. Many architectural innovations can fall into two or three categories at the same time. We focus on architectural innovations for general-purpose processors since the processors are the most architecturally-complex digital systems which require the most sophisticated architectural innovations.

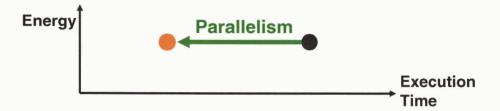

# 4.1 Employing Parallelism

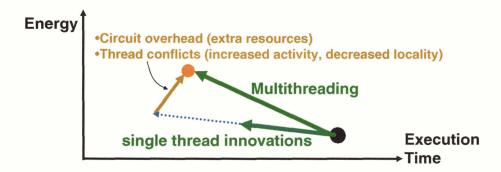

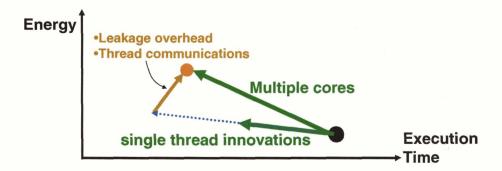

Employing various levels of parallelism has been a key theme in architectural innovation. Parallel execution is a straightforward way of increasing throughput. Especially, in this deep submicron technology era, transistors are numerous and cheap, and providing additional parallel circuitry for parallel execution is one of the best uses of abundant transistors [Cha92]. Figure 4-1 shows the benefit of employing parallelism in terms of energy and execution time. Ideally, employing parallelism shortens execution time while dissipating the same amount of energy for the same task.

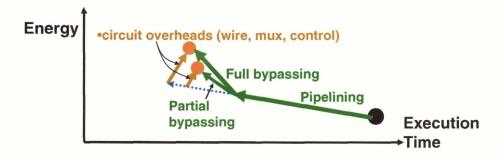

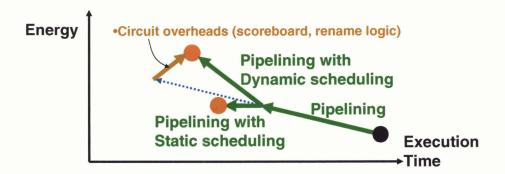

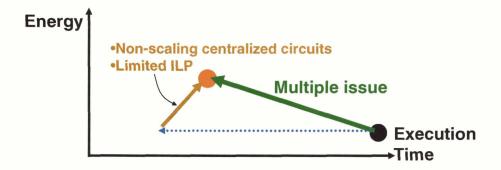

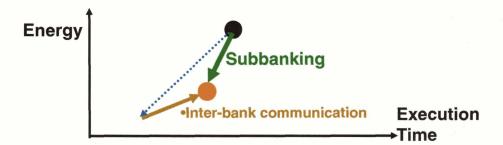

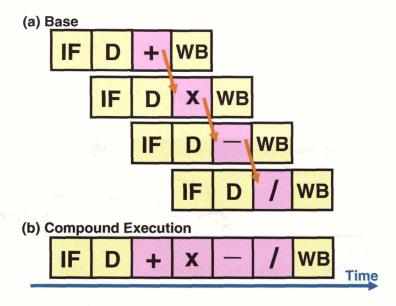

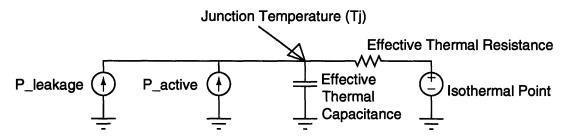

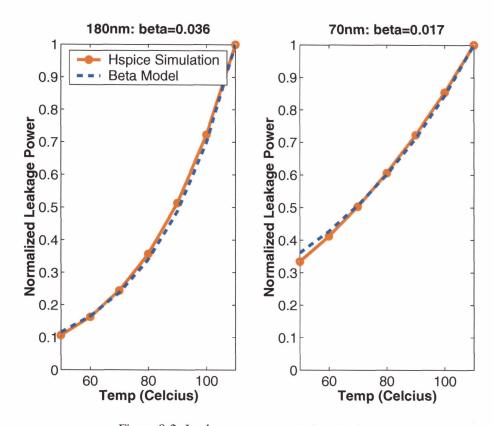

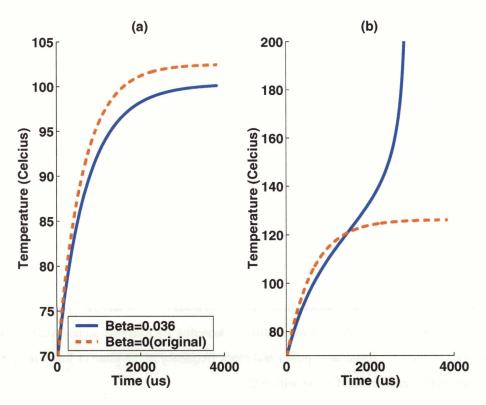

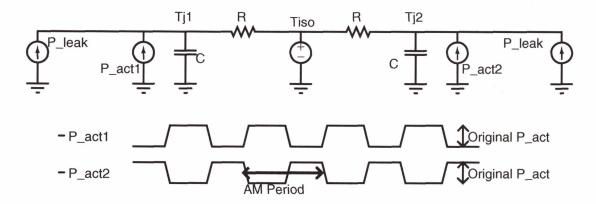

In this category, we include architectural innovations overcoming the factors that limit ex-