### Multigrain Shared Memory

by

### Donald Yeung

B.S., Computer Systems Engineering Stanford University, 1990

S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1993

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 1998

© 1998 Massachusetts Institute of Technology. All rights reserved.

| Signature of Author: _ |                     |                      |                      |

|------------------------|---------------------|----------------------|----------------------|

| <b>~-</b> 0            | Department of Elect | rical Engineering as | nd Computer Science  |

|                        |                     |                      | December 17, 1997    |

|                        |                     |                      |                      |

| Certified by:          |                     |                      |                      |

| Certified by.          |                     |                      | Anant Agarwal        |

|                        | Associate Professo  | or of Computer Scie  | ence and Engineering |

|                        |                     | •                    | Thesis Supervisor    |

|                        |                     |                      |                      |

|                        |                     |                      |                      |

| Accepted by:           |                     | <del></del>          | · • -                |

|                        |                     |                      | Arthur C. Smith      |

|                        | Chairm              | ian, Departmental (  | Graduate Committee   |

MAR 271998

1 MMAPHES

### **Multigrain Shared Memory**

# by Donald Yeung

Submitted to the Department of Electrical Engineering and Computer Science on December 17, 1997 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### ABSTRACT

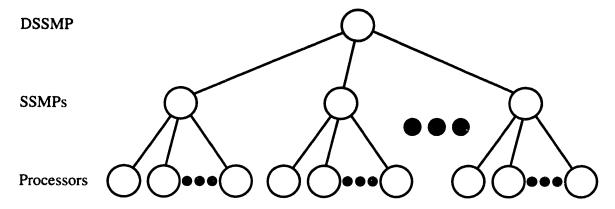

Parallel workstations, each comprising a 10-100 processor shared memory machine, promise cost-effective general-purpose multiprocessing. This thesis explores the coupling of such small- to medium-scale shared memory multiprocessors through software over a local area network to synthesize larger shared memory systems. Multiprocessors built in this fashion are called Distributed Scalable Shared memory Multiprocessors (DSSMPs).

The challenge of building DSSMPs lies in seamlessly extending hardware-supported shared memory of each parallel workstation to span a cluster of parallel workstations using software only. Such a shared memory system is called *Multigrain Shared Memory* because it naturally supports two grains of sharing: fine-grain cache-line sharing within each parallel workstation, and coarse-grain page sharing across parallel workstations. Applications that can leverage the efficient fine-grain support for shared memory provided by each parallel workstation have the potential for high performance.

This thesis makes three contributions in the context of Multigrain Shared Memory. First, it provides the design of a multigrain shared memory system, called MGS, and demonstrates its feasibility and correctness via an implementation on a 32-processor Alewife machine. Second, this thesis undertakes an in-depth application study that quantifies the extent to which shared memory applications can leverage efficient shared memory mechanisms provided by DSSMPs. The thesis begins by looking at the performance of unmodified shared memory programs, and then investigates application transformations that improve performance. Finally, this thesis presents an approach called Synchronization Analysis for analyzing the performance of multigrain shared memory systems. The thesis develops a performance model based on Synchronization Analysis, and uses the model to study DSSMPs with up to 512 processors. The experiments and analysis demonstrate that scalable DSSMPs can be constructed from small-scale workstation nodes to achieve competitive performance with large-scale all-hardware shared memory systems. For instance, the model predicts that a 256-processor DSSMP built from 16-processor parallel workstation nodes achieves equivalent performance to a 128processor all-hardware multiprocessor on a communication-intensive workload.

Thesis Advisor: A. Agarwal

Title: Associate Professor of Computer Science and Engineering

# Acknowledgments

Pursuing my doctorate at MIT has been the most challenging endeavor I have ever undertaken. In retrospect, I definitely appreciate the opportunity I've been given to face such a challenge because of the enrichment I have received both in my professional and personal life in ways I could never have imagined prior to arriving in Cambridge seven and a half years ago. For these life-changing experiences, I owe many thanks to a number of people.

I would like to begin by acknowledging my advisor, Anant, for his invaluable guidance which has kept me going all these years, and for his never-ending moral support, without which I would never have had the confidence to overcome the hurdles of my degree. I will forever be in awe of his ability to think on his feet (a.k.a. "shoot from the hip"), his infinite energy, and his ability to get others excited about almost anything. Most importantly, I will always hold the greatest respect for Anant because of his commitment to promoting his students before himself so that they may succeed.

I would also like to acknowledge the members of the Alewife team, without whom none of my thesis would have been possible. Thanks go to Beng, Dan, David (Chaiken), David (Kranz), and Rajeev, to whom I owe all the simulation, compilation, debugging, and runtime software infrastructure in the Alewife machine. To Kirk, I owe many inspiring technical conversations, particularly early on in my career at MIT. Thanks go to Fred for all his advice on interviews that allowed me to survive my job search. To Anne, I (as well as everyone else in the Alewife group) owe all the support that kept the group from an administrative train wreck. To Ken, perhaps the most compatible office mate I will ever have, I owe many lessons on hardware hacking, as well as many stimulating research discussions, some that lead to important ideas for my thesis. Of course, I will be eternally grateful to Kubi, who managed to be a colleague, mentor, and friend all at the same time, and whose tremendous knowledge and wisdom make him one of the greatest teachers I will ever have. And together, to Kubi and Ken, I owe the endless hours of comradary that have defined the "Alewife experience" for me, and that I will remember for the rest of my life.

Finally, my greatest thanks go to Mom, Dad, Marina, and Melany, whose love and support has allowed me to leave MIT with my sanity intact.

# Contents

| 1 | Int | roduction                                                | 1'         |

|---|-----|----------------------------------------------------------|------------|

|   | 1.1 | Contributions                                            | 19         |

|   | 1.2 | Outline                                                  | 2          |

| 2 | Bac | ckground                                                 | 23         |

|   | 2.1 | Distributed Shared Memory                                | 23         |

|   |     | 2.1.1 Addressing Resource Contention                     | 24         |

|   |     | 2.1.2 Cache Coherence                                    | 25         |

|   | 2.2 | DSM Implementation                                       | 26         |

|   |     | 2.2.1 Hardware Cache Coherence                           | 2          |

|   |     | 2.2.2 Page-Based DSMs                                    | 29         |

| 3 | The | e Multigrain Approach                                    | 33         |

|   | 3.1 | A Definition of Grain                                    | 34         |

|   | 3.2 | Granularity in Conventional Architectures                | 36         |

|   |     | 3.2.1 Supporting Fine-Grain Sharing                      | 36         |

|   |     | 3.2.2 Supporting Coarse-Grain Sharing                    | 38         |

|   | 3.3 | Multigrain Systems                                       | 39         |

|   |     | 3.3.1 A Hybrid Approach for Both Cost and Performance    | 40         |

|   |     | 3.3.2 DSSMPs                                             | 41         |

|   |     | 3.3.3 DSSMP Families                                     | <b>4</b> 4 |

| 4 | MG  | S System Architecture                                    | 47         |

|   | 4.1 | ·                                                        | 47         |

|   |     | 4.1.1 Conventional Shared Memory Mechanisms              | 48         |

|   |     | 4.1.2 Additional Mechanisms for Multigrain Shared Memory | 50         |

|   | 4.2 | Architectural Structure                                  | 57         |

|   |     | 4.2.1 Three-Machine Discipline                           | 57         |

|   |     | 4.2.2 Simultaneous Transactions                          | 64         |

|   |     | 4.2.3 Low-Level Components                               | 67         |

|   | 4.3 | User-Level Multigrain Synchronization                    | 71         |

|   | -   | 4.3.1 Barriers                                           | 72         |

|   |     | 4.3.2 Locks                                              | 73         |

|   |     |                                                          | _          |

| 8 |  | CONTENTS |

|---|--|----------|

|   |  |          |

|   | 4.4  | MGS Library     | Interface       |             |      |      |     | • |   |   | • |   | • | • |   | • | 75  |

|---|------|-----------------|-----------------|-------------|------|------|-----|---|---|---|---|---|---|---|---|---|-----|

| 5 | Imj  | olementation    |                 |             |      |      |     |   |   |   |   |   |   |   |   |   | 77  |

|   | 5.1  | A Platform fo   | or Studying DS  | SSMPs       |      |      |     |   |   |   |   |   |   |   |   |   | 77  |

|   | 5.2  |                 | Multiprocessor  |             |      |      |     |   |   |   |   |   |   |   |   |   | 80  |

|   |      | 5.2.1 Hardw     | vare Cache-Col  | herent Shar | ed M | [em  | ory |   |   |   |   |   |   |   |   |   | 81  |

|   |      | 5.2.2 Fast I    | nter-Processor  | Messages    |      |      |     |   |   |   |   |   |   |   |   |   | 82  |

|   | 5.3  | Implementati    | on Issues on A  | lewife      |      |      |     |   |   |   |   |   |   |   |   |   | 84  |

|   |      | 5.3.1 Softwa    | are Virtual Me  | mory        |      |      |     |   |   |   |   |   |   |   |   |   | 84  |

|   |      | 5.3.2 Simula    | ating Inter-SSN | MP Commu    | nica | tion |     |   |   |   |   |   |   |   |   |   | 92  |

|   |      | 5.3.3 Page (    | Cleaning        |             |      |      |     |   |   |   |   |   |   |   |   |   | 96  |

|   |      | 5.3.4 Mappi     | ing Consistenc  | y           |      |      |     |   |   |   |   |   |   |   |   |   | 99  |

|   |      | 5.3.5 Statist   | tics            |             |      |      |     |   |   |   |   |   |   |   |   |   | 100 |

|   |      | 5.3.6 User-F    | Kernel Decomp   | osition .   |      |      |     |   |   |   |   |   |   |   |   |   | 102 |

| 6 | Ext  | perimental Re   | esults          |             |      |      |     |   |   |   |   |   |   |   |   |   | 105 |

|   | 6.1  |                 | rements         |             |      |      |     |   |   |   |   |   |   |   |   |   | 105 |

|   | 6.2  | Performance 1   | Framework .     | <i></i>     |      |      |     |   |   |   |   |   |   |   |   |   | 109 |

|   | 6.3  |                 |                 |             |      |      |     |   |   |   |   |   |   |   |   |   | 112 |

|   |      |                 | ation Suite .   |             |      |      |     |   |   |   |   |   |   |   |   |   | 113 |

|   |      |                 | ation Results   |             |      |      |     |   |   |   |   |   |   |   |   |   | 117 |

|   | 6.4  |                 | ransformation   |             |      |      |     |   |   |   |   |   |   |   |   |   | 129 |

|   |      |                 | ormation Desc   |             |      |      |     |   |   |   |   |   |   |   |   |   | 130 |

|   |      |                 | ormation Resu   | _           |      |      |     |   |   |   |   |   |   |   |   |   | 132 |

|   |      |                 | sion            |             |      |      |     |   |   |   |   |   |   |   |   |   | 137 |

|   | 6.5  | Sensitivity St  |                 |             |      |      |     |   |   |   |   |   |   |   |   |   | 138 |

|   | 0.0  | _               | SSMP Latency    |             |      |      |     |   |   |   |   |   |   |   |   |   | 139 |

|   |      |                 | Size            |             |      |      |     |   |   |   |   |   |   |   |   |   | 141 |

|   |      |                 |                 |             |      |      |     |   |   |   |   |   |   |   |   | • |     |

| 7 |      | llysis          |                 |             |      |      |     |   |   |   |   |   |   |   |   |   | 145 |

|   | 7.1  | Analytical Fra  |                 |             |      |      |     |   |   |   |   |   |   |   |   |   |     |

|   |      | 7.1.1 Analyz    | zing performan  | ice on DSM  | s.   |      |     |   |   | • | • |   | • | • |   |   | 147 |

|   |      | 7.1.2 Comm      | unication in So | oftware DS  | Ms   |      |     |   |   |   |   |   |   |   |   |   | 148 |

|   |      | 7.1.3 Perform   | mance Model     |             |      |      |     |   |   |   |   |   |   |   |   |   | 154 |

|   | 7.2  | Scalability Stu | ıdy             |             |      |      |     |   |   |   |   |   |   |   |   |   | 163 |

|   |      | 7.2.1 Applic    | ation Descript  | ion for Wat | er . |      |     |   |   |   |   |   |   |   |   |   | 163 |

|   |      | 7.2.2 Model     | Validation      |             |      |      |     |   |   |   |   |   |   |   |   |   | 168 |

|   |      | 7.2.3 Scaling   | g Results       |             |      |      |     |   |   |   |   |   |   |   |   |   | 169 |

| 8 | Rela | ated Work       |                 |             |      |      |     |   |   |   |   |   |   |   |   |   | 181 |

|   | 8.1  | Page-Based Sl   | nared Memory    |             |      |      |     |   |   |   |   |   |   |   |   |   | 181 |

|   | 8.2  | Multigrain Sys  | •               |             |      |      |     |   |   |   |   |   |   |   |   |   | 182 |

|   | 8.3  | Fine-Grained    |                 |             |      |      |     |   |   |   |   |   |   |   |   |   | 186 |

|   |      |                 |                 |             |      | -    | -   |   | - | - |   | - |   |   | - |   |     |

| CC | ONTENTS                    | 9   |

|----|----------------------------|-----|

| 9  | Conclusion                 | 189 |

| A  | MGS Protocol Specification | 205 |

10 CONTENTS

# List of Figures

| 2.1<br>2.2 | Shared memory multiprocessors                                            | $\begin{array}{c} 24 \\ 25 \end{array}$ |

|------------|--------------------------------------------------------------------------|-----------------------------------------|

| 3.1        | ·                                                                        | 35                                      |

| 3.1        | Defining sharing granularity using the <i>grain vector</i>               | აა                                      |

|            | tances.                                                                  | 36                                      |

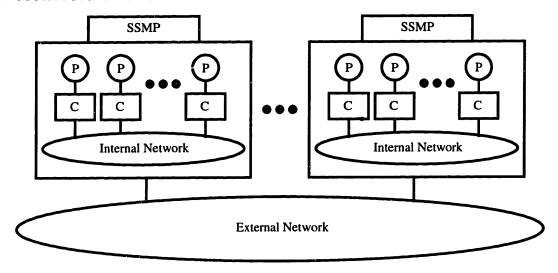

| 3.3        | A Distributed Scalable Shared Memory Multiprocessor                      | 41                                      |

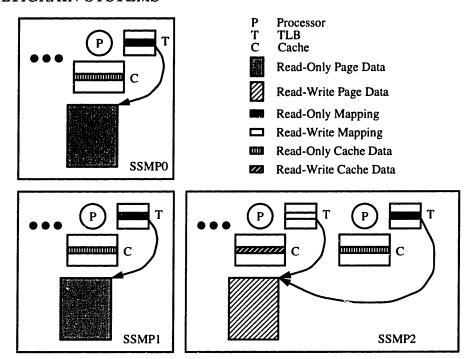

| 3.4        | Distribution of a single page of data across three SSMPs                 | 43                                      |

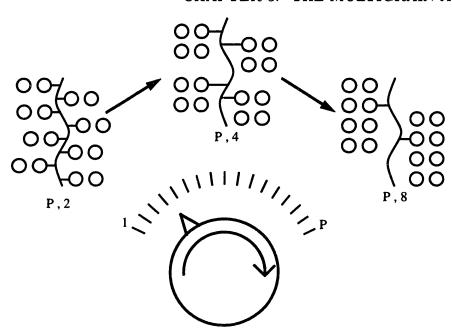

| 3.5        | DSSMP families                                                           | 44                                      |

| 4.1        | Schematic of the MGS system                                              | 48                                      |

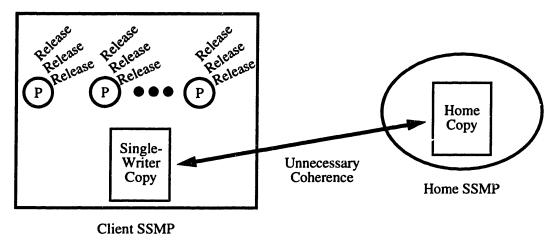

| 4.2        | Unnecessary communication and protocol processing overhead for sharing   |                                         |

|            | under the Single-Writer condition.                                       | 54                                      |

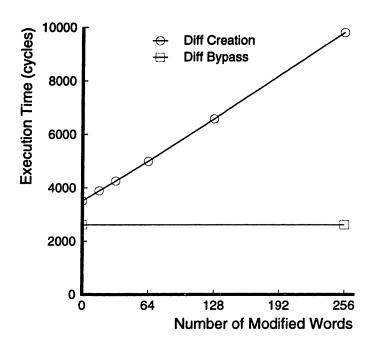

| 4.3        | Overhead of Diff Creation and Diff Bypass as a function of the number of |                                         |

|            | modified words in the page                                               | 56                                      |

| 4.4        | The 2-machine decomposition in conventional software DSM systems         | 58                                      |

| 4.5        | The 3-machine decomposition in multigrain shared memory systems          | 58                                      |

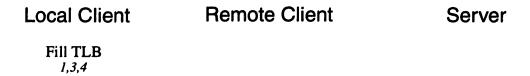

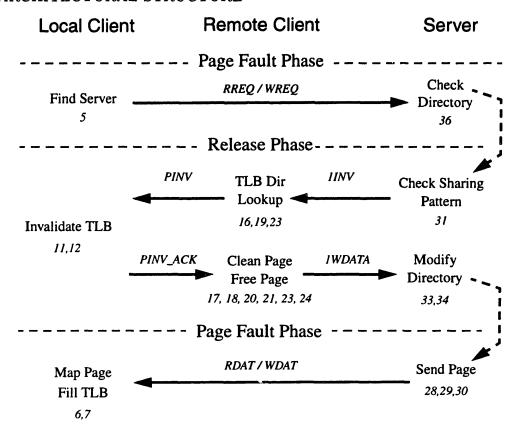

| 4.6        | TLB fault transactions in MGS                                            | 60                                      |

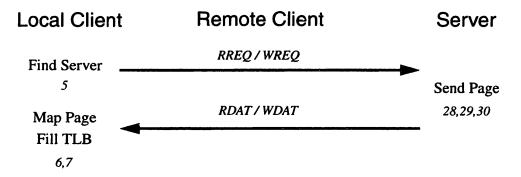

| 4.7        | Page fault transactions in MGS                                           | 60                                      |

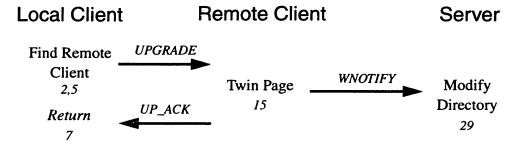

| 4.8        | Page upgrade transactions in MGS                                         | 60                                      |

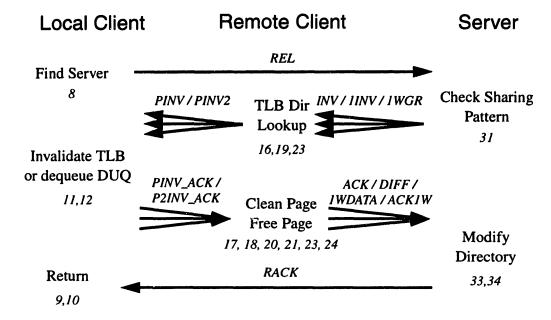

| 4.9        | Release transactions in MGS                                              | 61                                      |

| 4.10       | Single-Writer reversion as the compound of the Page Fault and Release    |                                         |

|            | transactions.                                                            | 63                                      |

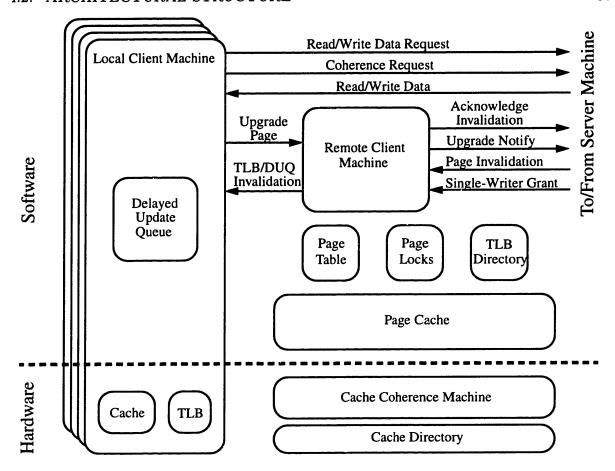

| 4.11       | MGS Client architecture                                                  | 67                                      |

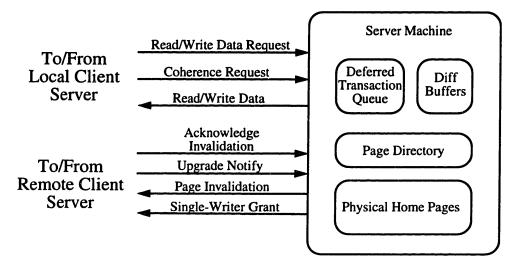

|            | MGS Server architecture                                                  | 68                                      |

|            | MGS Barrier                                                              | 72                                      |

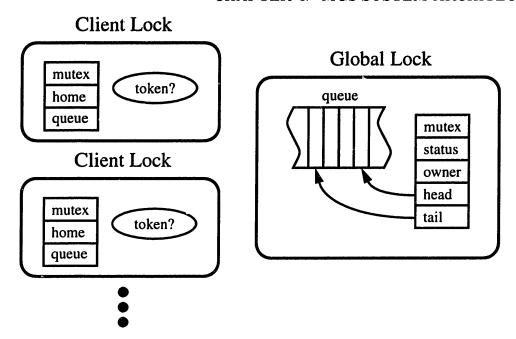

| 4.14       | MGS Lock                                                                 | 74                                      |

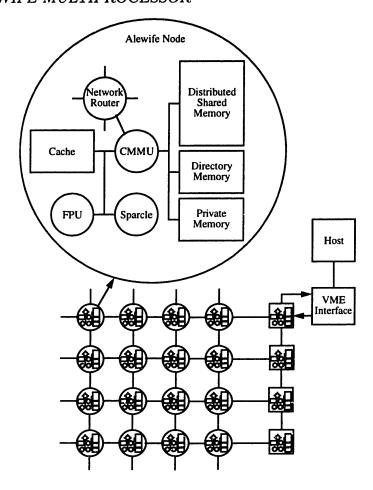

| 5.1        | The Alewife Machine.                                                     | 81                                      |

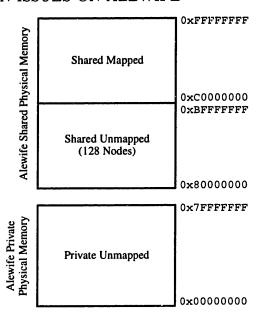

| 5.2        | Memory map for the MGS system                                            | 87                                      |

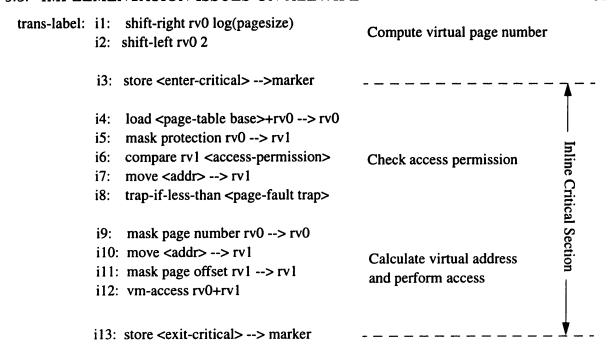

| 5.3        | Pseudo-assembly code for detecting virtual addresses in software virtual |                                         |

|            | memory                                                                   | 88                                      |

| 5 4        | Pseudo-assembly code for performing a mapped access                      | 89                                      |

12 LIST OF FIGURES

| 5.5  | Pseudo-assembly code for performing a mapped access, with code to cor-      | ٠.  |

|------|-----------------------------------------------------------------------------|-----|

|      | rect for the atomicity problem.                                             | 9   |

| 5.6  | Pseudo-C code for performing page cleaning                                  | 96  |

| 5.7  | Pseudo-C code for performing page cleaning with prefetching optimizations.  |     |

| 5.8  | 1                                                                           | 0.  |

| 5.9  | Decomposition of the MGS system into user-space and kernel-space mod-       |     |

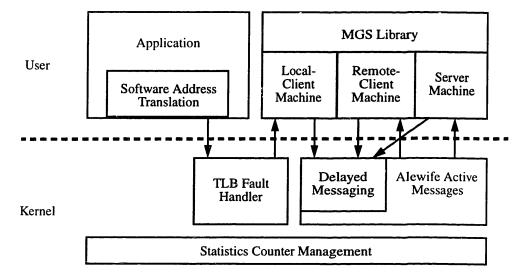

|      | ules                                                                        | 10  |

| 6.1  | A hypothetical application analyzed using the performance framework.        |     |

|      |                                                                             | 1(  |

| 6.2  | A hypothetical application analyzed using the performance framework.        |     |

|      | This application is well-suited for DSSMPs                                  | 1.  |

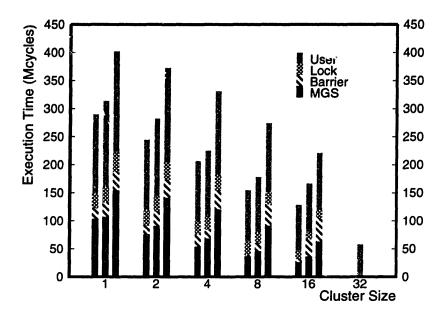

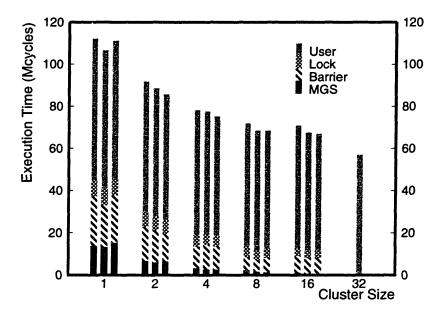

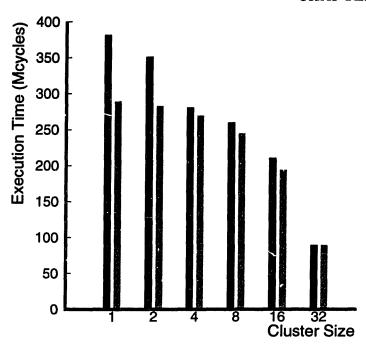

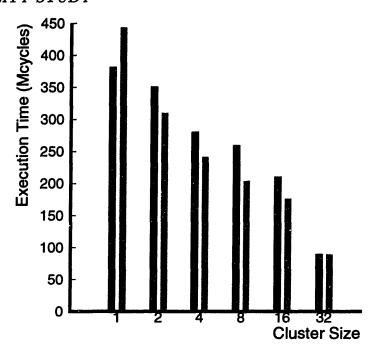

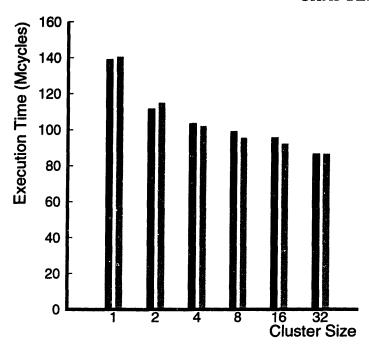

| 6.3  | Results for Jacobi                                                          | 20  |

| 6.4  | Results for Matrix Multiply                                                 | 20  |

| 6.5  | Results for FFT                                                             | 2   |

| 6.6  | Results for Gauss                                                           | 2   |

| 6.7  | Results for Water                                                           | .23 |

| 6.8  | Results for Barnes-Hut                                                      | .23 |

| 6.9  | Pseudo-C code for the force interaction computation in Water                | .24 |

| 6.10 | <b>3</b> 1                                                                  | .25 |

| 6.11 |                                                                             | .27 |

| 6.12 | Results for Unstructured                                                    | .27 |

| 6.13 | 210110202220000200000000000000000000000                                     | .34 |

| 6.14 |                                                                             | 3.  |

| 6.15 |                                                                             | .36 |

|      |                                                                             | 3   |

| 6.17 | 20000109 2010201 209 200 200 200 200 200 200 200 200 200                    | 4(  |

| 6.18 | 2000101 001101 101 101 101 101 101 101 1                                    | .4( |

|      | 20000110, 001101101101101101101101101101101101101                           | 41  |

|      | 2 400 0220 002011107 101 111 1111 11111                                     | 44  |

| 6.21 | Page size sensitivity results for Water-Kernel with tiling                  | .44 |

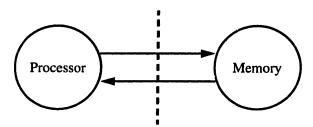

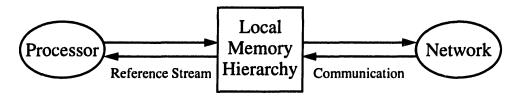

| 7.1  | The local memory hierarchy in a DSM sits between the processor and the      |     |

|      |                                                                             | 47  |

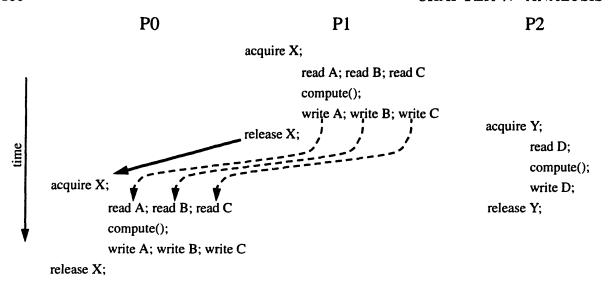

| 7.2  | Data and synchronization dependences in RC programs                         | 5(  |

| 7.3  | Analyzing clustering involves identifying synchronization dependences that  |     |

|      |                                                                             | 53  |

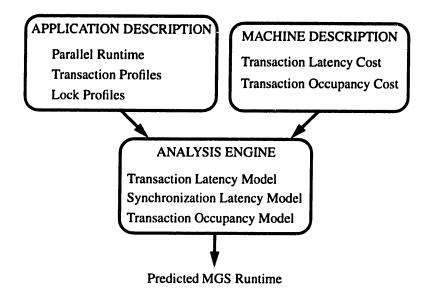

| 7.4  | The performance analysis framework for multigrain systems                   | 55  |

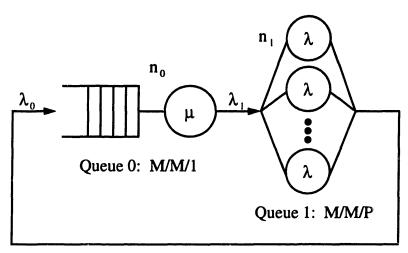

| 7.5  | Closed queuing system used to model lock contention due to critical section |     |

|      |                                                                             | 60  |

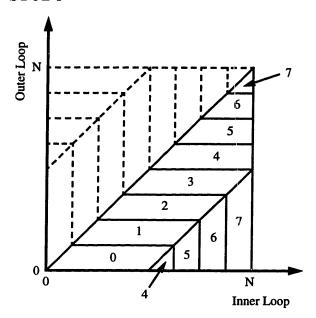

| 7.6  | Partitioning of the iteration space of the force interaction computation in |     |

|      | Water-Kernel-NS                                                             | 65  |

| 7.7  | Validation for Water-Kernel-NS model ignoring interleaving effects 1        | 68  |

| LIST ( | OF FIGURES | 1: |

|--------|------------|----|

| LISI ( | JF FIGURES | 1. |

| 7.8  | Validation for Water-Kernel-NS model accounting for interleaving effects. | 169 |

|------|---------------------------------------------------------------------------|-----|

| 7.9  | Validation for tiled Water-Kernel-NS model                                | 170 |

| 7.10 | Scaling Water-Kernel-NS. 32 Processors                                    | 172 |

| 7.11 | Scaling Water-Kernel-NS. 128 Processors.                                  | 174 |

| 7.12 | Scaling Water-Kernel-NS. 512 Processors                                   | 174 |

| 7.13 | Scaling tiled Water-Kernel-NS. 32 Processors                              | 175 |

| 7.14 | Scaling tiled Water-Kernel-NS. 128 Processors.                            | 176 |

| 7.15 | Scaling tiled Water-Kernel-NS. 512 Processors.                            | 177 |

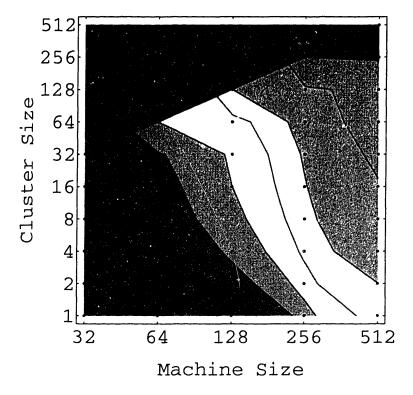

| 7.16 | Performance-equivalent machines for the original version of Water-Kernel- |     |

|      | NS                                                                        | 178 |

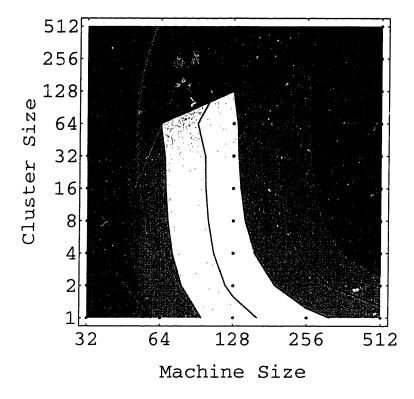

| 7.17 | Performance-equivalent machines for the tiled version of Water-Kernel-NS. | 179 |

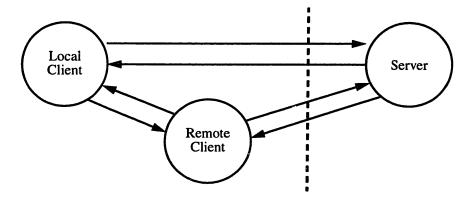

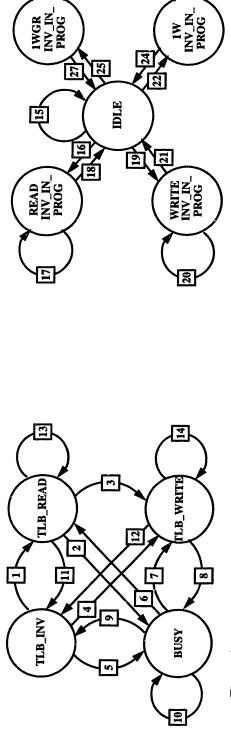

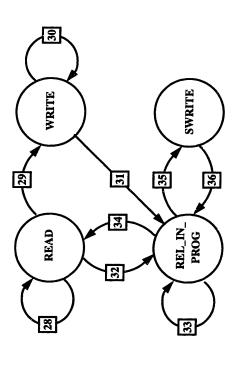

| A.1  | MGS Protocol state transition diagram: Local-Client Machine               | 207 |

| A.2  | MGS Protocol state transition diagram: Remote-Client Machine              | 207 |

| A.3  | MGS Protocol state transition diagram: Server Machine                     | 207 |

|      |                                                                           |     |

14 LIST OF FIGURES

# List of Tables

| 4.1 | A comparison of possible fault events encountered by the software DSM        |     |

|-----|------------------------------------------------------------------------------|-----|

|     | layer in a conventional software DSM system and in the MGS system            | 51  |

| 4.2 | Programmer's interface to the MGS system                                     | 75  |

| 5.1 | Memory objects in MGS                                                        | 86  |

| 5.2 | MGS messages that send data                                                  | 94  |

| 6.1 | Cache-miss penalties on Alewife                                              | 106 |

| 6.2 | Software Virtual Memory costs on MGS                                         | 107 |

| 6.3 | Software shared memory costs on MGS                                          | 107 |

| 6.4 | List of applications, their problem sizes, and their size in number of lines |     |

|     | of C code                                                                    | 113 |

| 6.5 | Baseline application performance                                             | 114 |

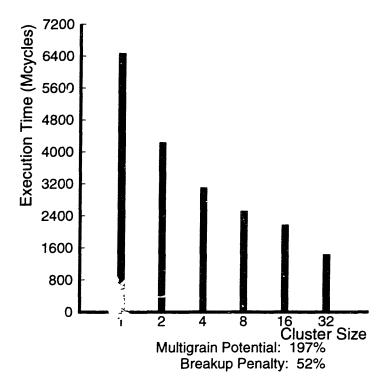

| 6.6 | Summary of application performance on DSSMPs                                 | 118 |

| 6.7 | Summary of performance bottlenecks and transformations                       | 130 |

| 6.8 | Summary of application transformations performance on DSSMPs                 | 133 |

| 6.9 | Relative grain on MGS and other systems                                      | 142 |

| 7.1 | Application transaction profile parameters                                   | 156 |

| 7.2 | Lock profile parameters                                                      | 157 |

| 7.3 | Machine description parameters                                               | 157 |

| 7.4 | Scaling results summary-execution times                                      | 171 |

| 7.5 | Scaling results summary—speedups                                             | 172 |

| A.1 | MGS Protocol state transition table: Local-Client Machine                    | 208 |

| A.2 | MGS Protocol state transition table: Remote-Client Machine                   | 208 |

| A.3 | MGS Protocol state transition table: Server Machine                          | 209 |

| A.4 | Message types used to communicate between the Local-Client, Remote-          |     |

|     | Client, and Server machines in the MGS Protocol                              | 210 |

# Chapter 1

# Introduction

Large-scale shared memory multiprocessors have received significant attention within the computer architecture community over the past decade. The high interest that these architectures have generated is due in large part to their cost-performance characteristics: large-scale shared memory multiprocessors have the potential to deliver supercomputer performance at commodity server costs.

Large-scale shared memory machines offer the promise of remarkable levels of costperformance because they are constructed from computational building blocks, or compute nodes, that require only modest technology. Fueled by the microprocessor, such

compute nodes individually deliver reasonable performance while using commodity computational technology. Supercomputer performance is achieved on these systems by coupling multiple compute nodes together to take advantage of medium- to coarse-grain

parallelism. While the architecture does not assist in the discovery of parallelism, provided enough parallelism can be identified by a compiler or a programmer to keep all

compute nodes busy, high performance can be sustained.

While the promise of remarkable cost-performance has made large-scale shared memory architectures attractive, thus far, this promise has gone unfulfilled. In practice, the potential cost-performance benefits promised by large-scale shared memory architectures are difficult to realize because of the tension between providing efficient communication mechanisms and maintaining cost-efficiency at large scales. Because large-scale shared memory architectures rely on parallelism to achieve performance, they must be equipped to support the communication that arises when the computational load represented by a single application is distributed across multiple computational elements. Therefore, in addition to providing per-node computational throughput, an equally (if not more) important architectural requirement is to provide efficient communication mechanisms. Without efficient communication, parallel applications with demanding communications requirements cannot be supported on these architectures, thus limiting the scope of problems for which these architectures can be effectively applied.

Traditionally, large-scale shared memory multiprocessors provide efficient communication mechanisms through aggressive architectural support. An example is the hardware cache-coherent distributed shared memory (DSM) architecture. Hardware DSMs

are built using custom communication interfaces, high performance VLSI interconnect, and special-purpose hardware support for shared memory. These aggressive architectural features provide extremely efficient communication support between nodes through tightly coupled hardware interfaces. The architectural support for efficient shared memory communication allows hardware DSMs to provide scalable performance even on communication-intensive applications.

While aggressive architectural support leads to high performance, the investment in hardware mechanisms comes at a cost. In particular, tight coupling between nodes is difficult to maintain in a cost-effective manner as the number of nodes becomes large. Fundamental obstacles prevent large tightly-coupled systems from being cost effective. The cost of power distribution, clock distribution, cooling, and special packaging considerations in tightly coupled systems do not scale linearly with size. As system size is scaled, cost grows disproportionately due to the physical limitations imposed by the necessity to maintain tight coupling across all the nodes in the system. Perhaps most important, the large-scale nature of these machines prevents them from capitalizing on the economy of cost that high volume smaller-scale machines enjoy.

In response to the high design cost of large-scale hardware DSMs, many researchers have proposed building large-scale shared memory systems using commodity uniprocessor workstations as the compute node building block. In these lower cost systems, the tightly coupled communications interfaces found in hardware DSMs are replaced by commodity interfaces that do not require any special-purpose hardware. Furthermore, commodity networks such as those found in the local area environment are used to connect the workstation nodes, and the shared memory communication abstraction is supported purely in software. Such software DSM architectures are cost effective because all the components are high volume commodity items and because specialized tightly-coupled packaging is not required.

Unfortunately, software DSMs are unable to provide high performance across a wide range of applications. While communication interfaces for commodity workstations have made impressive improvements, the best reported inter-workstation latency numbers are still an order of magnitude higher than for machines that have tightly-coupled special-purpose interfaces [66]. Furthermore, the best latencies come from special networks that do not have the large volume required for low cost commoditization. The higher cost of communication on commodity systems prevents them from supporting applications with intensive communication requirements.

Existing architectures for large-scale shared memory machines have not satisfactorily addressed the tension between providing efficient communication mechanisms for high performance and designing for cost effectiveness. In this thesis we propose a novel approach to building large-scale shared memory machines that offers higher cost-performance properties than existing architectures. Our approach leverages the scalable shared memory multiprocessor (SSMP) as the building block for larger systems.

SSMP is a general name for any small- (2–16 processors) to medium-scale (17–128 processors) shared memory machine. A familiar example is the bus-based Symmetric Multiprocessor (SMP). Another example is the small- to medium-scale distributed-memory

multiprocessor. The latter architecturally resembles large-scale (greater than 128 processors) tightly-coupled machines, but is targeted for smaller systems. The general nature of the SSMP terminology suggests that both SMPs and distributed-memory architectures are suitable building blocks for larger shared memory systems.

The SSMP is an attractive building block for large-scale multiprocessors for two reasons. First, SSMPs provide efficient hardware support for shared memory. A larger system that can leverage this efficient hardware support has the potential for higher performance than a network of conventional uniprocessor workstations in which shared memory is implemented purely in software. And second, the efficient shared memory mechanisms provided by SSMPs do not incur exorbitant costs because the tight coupling required is only provided across a small number of processors. Unlike large-scale hardware DSMs, small-scale tightly-coupled systems can be cost-effective, as evidenced by the commodity nature of the SMP architecture.

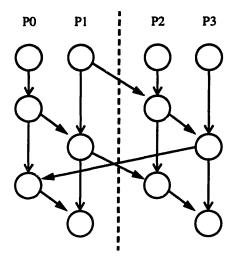

We call a large-scale system built from a collection of SSMPs a Distributed Scalable Shared memory Multiprocessor (DSSMP). DSSMPs are constructed by extending the hardware-supported shared memory in each SSMP using software distributed shared memory (DSM) techniques to form a single shared memory layer across multiple SSMP nodes. Such hybrid hardware-software systems support shared memory using two granularities, hence the name Multigrain Shared Memory. Cache-coherent shared memory hardware provides a small cache-line sharing grain between processors colocated on the same SSMP. Page-based software DSM provides a larger page sharing grain between processors in separate SSMPs.

### 1.1 Contributions

This thesis presents a thorough investigation of multigrain shared memory architectures. The fundamental idea researched by this thesis is the coupling of small- to medium-scale shared memory multiprocessors using software shared memory techniques to build a large-scale system. The challenge lies in synthesizing a single transparent and seamless shared memory layer through the cooperation of both fine-grain hardware cache-coherent and coarse-grain page-based shared memory mechanisms. The thesis reports on an extensive systems building experience that has taken the basic notion of multigrain shared memory and carried it through an exhaustive systems investigation project.

The aggregate contributions from our investigation of multigrain shared memory cover every phase of a complete systems building and evaluation process. Contributions are made in system design, which include a complete set of mechanisms that enable the construction of multigrain shared memory. From the design, our investigation has built a prototype implementation that demonstrates the feasibility and correctness of our design. Using the prototype implementation, we conduct an in-depth evaluation that experimentally characterizes the behavior of the system. Finally, our investigation also includes an analysis phase that tries to provide insight into why the system behaves the way it does.

The specific contributions of this thesis are summarized below, organized into three

categories: design and implementation, evaluation, and analysis.

### Design and Implementation

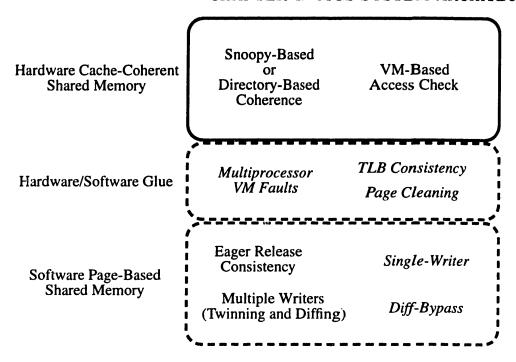

- This thesis investigates the design of multigrain shared memory systems. Fundamental to the design are a set of mechanisms that enable the cooperation of hardware cache-coherent and software page-based shared memory layers. Three key mechanisms are identified that enable such cooperation: multiprocessor VM faults, TLB coherence, and page cleaning.

- In addition to fundamental design issues, this thesis also investigates how to build fast multigrain shared memory systems. For performance, multigrain architectures must export the efficiency of the hardware cache-coherent mechanisms as often as possible. When application sharing patterns permit, the system should remove any intervention from the software layers until software services are absolutely necessary. The thesis proposes the Single-Writer mechanism that achieves this design requirement.

- A complete multigrain shared memory system design is proposed, called MGS. MGS integrates the multigrain-specific mechanisms described above along with conventional software shared memory mechanisms to construct a fully functional multigrain architecture. To our knowledge, MGS is the first system to facilitate a comprehensive study of multigrain shared memory.

- A prototype of the MGS design is implemented on a 32-processor Alewife machine. The prototype demonstrates the correctness of the design, and provides a platform for experimentation. A key feature of the prototype is *virtual clustering*, which allows the clustering configuration of the DSSMP to be changed at runtime. This flexibility enables the evaluation of different DSSMP configurations, a crucial capability leveraged by the experimental methodology of this thesis.

#### **Evaluation**

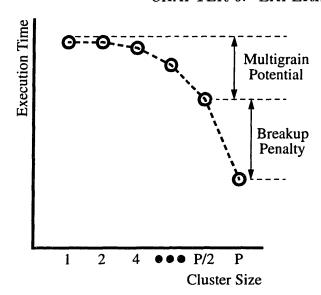

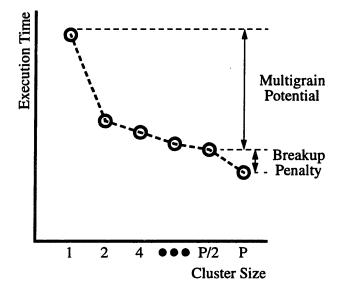

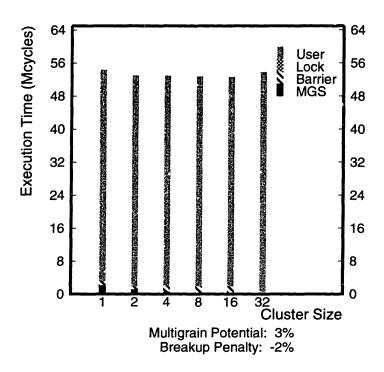

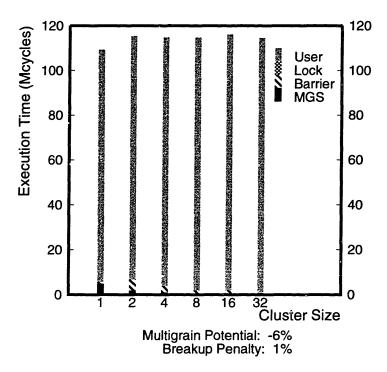

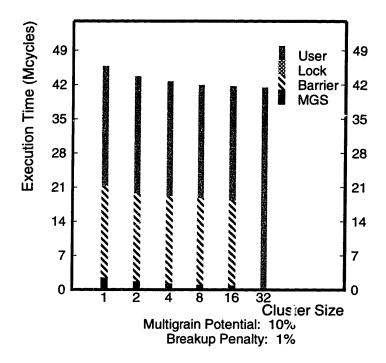

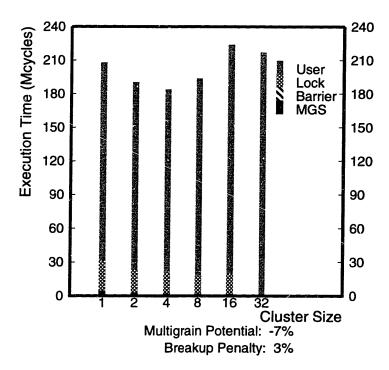

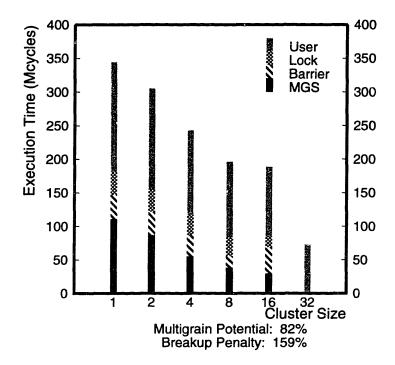

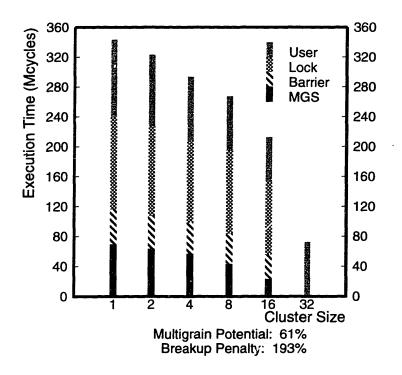

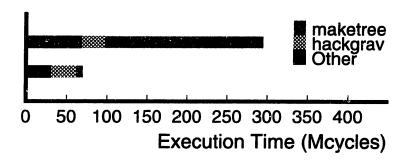

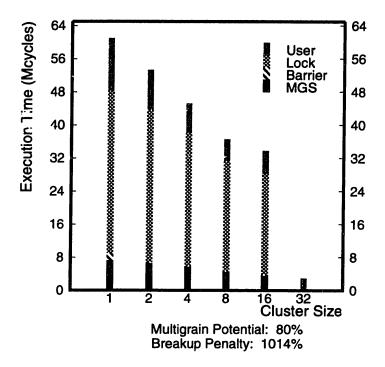

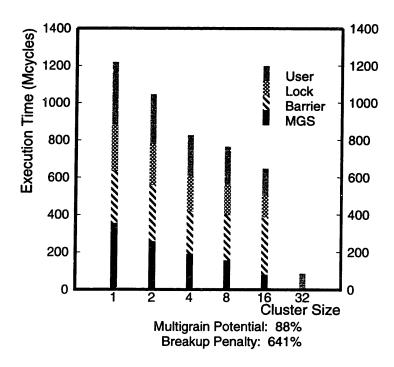

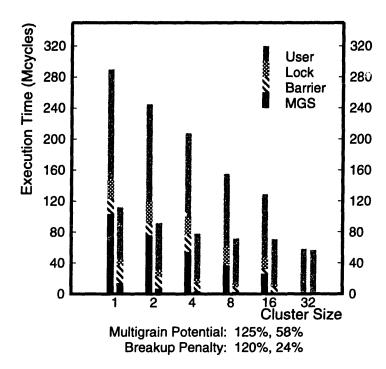

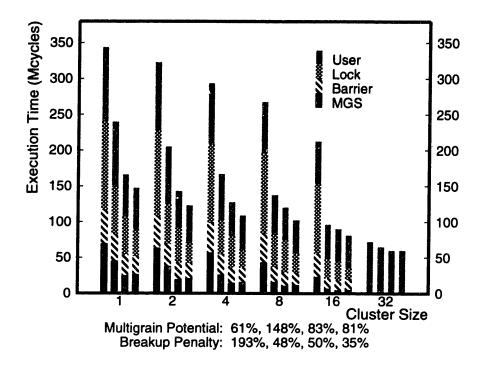

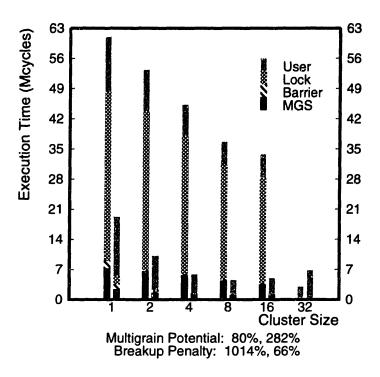

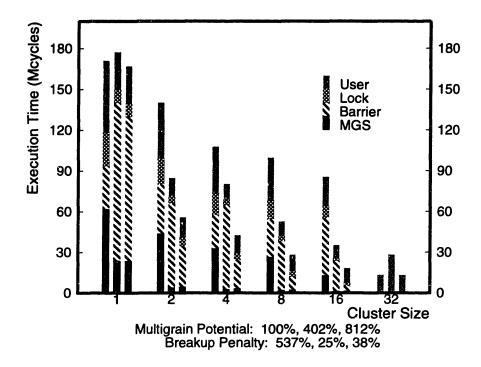

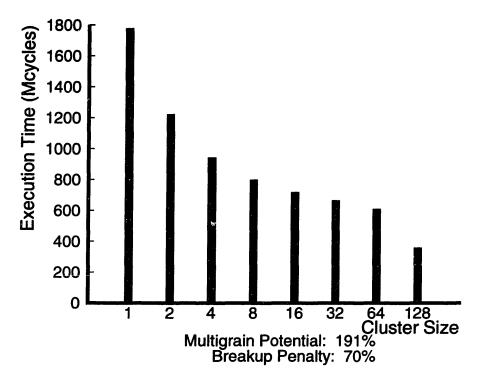

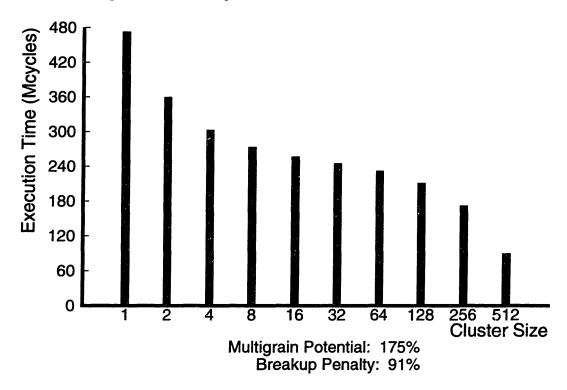

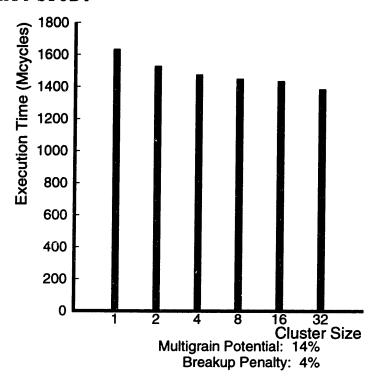

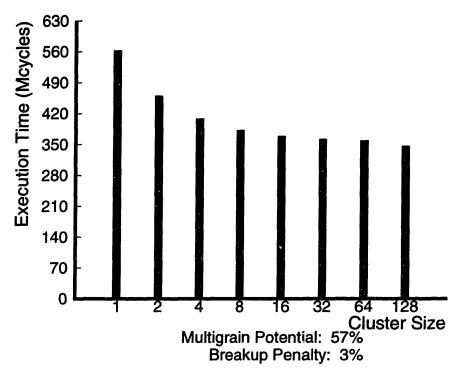

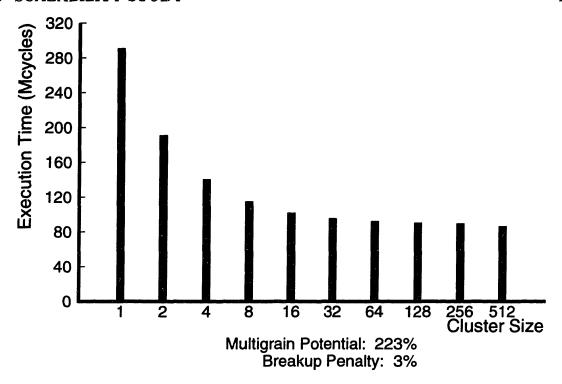

- The thesis presents a performance framework that characterizes application behavior on multigrain systems. The framework measures the sensitivity of application performance to varying cluster configurations using two performance metrics: Multigrain Potential, and Breakup Penalty. Together, these metrics report how an application responds to different mixes of fine-grain and coarse-grain shared memory support, and provides calibration of an application's performance on multigrain systems against its performance on all-software and all-hardware systems.

- An in-depth experimental evaluation is conducted on the MGS prototype. Several micro-benchmarks along with 9 shared memory applications representing a wide range of scientific workloads are studied.

1.2. OUTLINE 21

• An extension to the application study performed above is undertaken to understand the performance bottlenecks encountered by the applications. Transformations to relieve these bottlenecks are applied manually, and the improvements in performance are measured. The extended application study shows the potential performance that multigrain systems can deliver when additional compiler and/or programmer effort is applied to off-the-shelf applications. The study includes a qualitative evaluation of each transformation's sophistication. In the process, those transformations that can be performed automatically by existing compilers are identified.

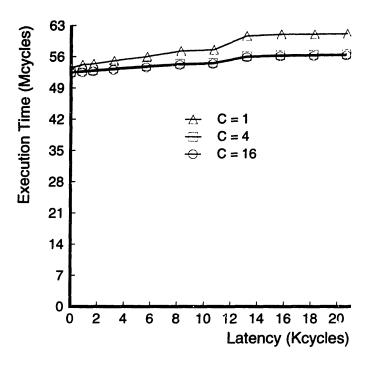

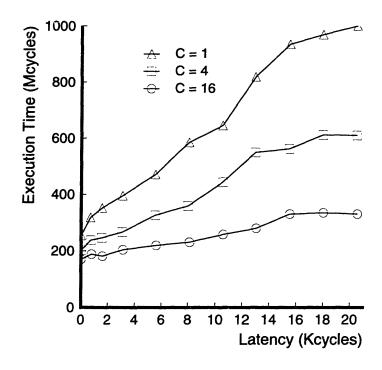

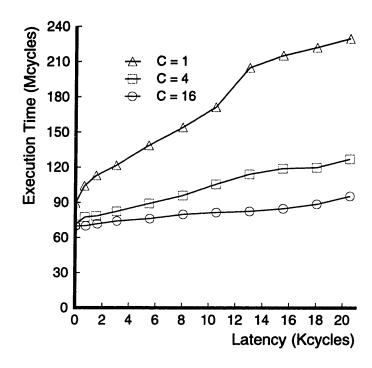

• The sensitivity of application performance on MGS to inter-SSMP communication latency and page size (the granularity of coherence between SSMPs) is studied.

#### **Analysis**

- A novel approach to analyzing performance on software shared memory systems is proposed, called *Synchronization Analysis*. Synchronization analysis enables the prediction of shared memory communication volume through analysis of a program's synchronization dependence graph. This synchronization-centric technique relies on the insight that communication patterns are highly correlated with synchronization patterns in software shared memory systems. Synchronization analysis represents a shift from traditional program analysis techniques used by parallel optimizing compilers that are data-centric in nature.

- The thesis presents a performance model based on synchronization analysis that predicts execution time on multigrain shared memory systems. Model parameters for the MGS prototype are determined to enable prediction of application performance on MGS. The accuracy of the model is validated by comparing model predictions using the MGS model parameters against experimental measurements taken on the MGS prototype.

- Using the performance model developed for MGS, an analytic study is conducted to evaluate the scalability of the MGS system. Both problem size and machine size are scaled beyond what can be studied experimentally. Machines of up to 512 processors are evaluated.

### 1.2 Outline

This section briefly outlines the contents of the thesis. Chapter 2 and 3 provide introductory discussion for the rest of the thesis. Chapter 2 provides background material that forms the foundation for the work reported in this thesis. Concepts from conventional hardware and software distributed shared memory systems are reviewed. Chapter 3 discusses the impact of sharing granularity supported by a shared memory architecture on both application performance and on system cost. The chapter argues that there exists

a tension between supporting fine-grain applications efficiently on large-scale machines, and designing large-scale machines in a cost-effective manner. This tension is the motivation for what we call the *multigrain approach* to designing shared memory systems, which is the foundation for all the ideas presented in this thesis.

Following the introductory chapters, Chapters 4 and 5 present the meat of the system proposed in this thesis, called MGS. Chapter 4 presents the architecture of the MGS system. It first describes the mechanisms necessary to build multigrain shared memory and to make it efficient. The chapter includes fairly detailed discussion on the exact mechanics that support the architecture. While Chapter 4 describes the MGS design, Chapter 5 describes an actual prototype we have built on the Alewife multiprocessor platform. Chapter 5 begins by explaining the *virtual clustering* approach that is central to our implementation (and to the evaluation later on). The chapter covers many implementation issues that arise when implementing MGS on Alewife.

The next two Chapters, 6 and 7, evaluate the performance of the MGS system. Chapter 6 presents the experimental portion of our evaluation that uses both microbenchmarks and a full range of shared memory applications. The behavior of applications is studied both using the original applications in their "off-the-shelf" form, and when transformations are applied to improve their locality properties. Chapter 7 presents the analytic portion of our evaluation. Much of the chapter is devoted to the presentation of a novel approach for performance analysis called *Synchronization Analysis*. Then, a performance model based on synchronization analysis is presented and validated against our MGS prototype. Using the performance model, we study the scalability of the MGS system on one of the applications from the experimental study, scaling machine size up to 512 processors.

Finally, Chapter 8 discusses related work, and Chapter 9 closes the thesis with conclusions.

# Chapter 2

# Background

This chapter describes the concept of distributed shared memory, along with various issues concerning the implementation of distributed shared memory systems. Section 2.1 introduces the notion of distributed shared memory, including a discussion on the cache coherence problem and how it is solved on distributed shared memory machines. And Section 2.2 presents several issues that concern hardware and software implementations of distributed shared memory. The information provided in this chapter forms the basis for the work presented in the rest of this thesis. Those readers familiar with distributed shared memory are encouraged to continue reading in Chapter 3.

## 2.1 Distributed Shared Memory

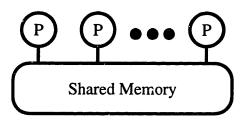

Shared memory is a programming model in which multiple threads of control communicate with one another through a single transparent layer of logically shared memory, as illustrated by Figure 2.1. It has been argued that shared memory is a desirable programming model since communication happens implicitly each time two threads access the same memory location. This is in contrast to a message passing programming model where the responsibility of managing communication is placed explicitly on the programmer [41].

Shared memory multiprocessors implement the shared memory programming model by supporting the shared memory abstraction directly in the system architecture. An example shared memory architecture for which the design faithfully resembles the programming model is the Symmetric Multiprocessor (SMP). SMPs implement the shared memory programming model by connecting multiple processors directly to physical memory through a single memory controller. The connection fabric that allows processors to communicate with the memory controller is a shared bus. Shared memory is supported by the fact that processors share the same image of physical memory.

While the architecture of an SMP directly implements the shared memory programming model, it is not suitable for large-scale shared memory systems because it is not scalable. The bus interconnect and single physical memory image become performance bottlenecks as the number of processors inside the SMP is increased. At some scaling

Figure 2.1: Shared memory multiprocessors provide a single transparent view of memory across all processors.

point, the communication bandwidth between processors and memory saturates resulting in the serialization of concurrently issued shared memory transactions, and performance degradation. To address the resource contention problems that limit scalability in the SMP architecture, it is necessary to replace the serial communication and memory interfaces with parallel interfaces. This is the goal of the distributed shared memory multiprocessor.

### 2.1.1 Addressing Resource Contention

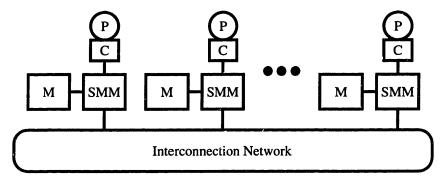

Distributed shared memory (DSM) architectures solve the resource contention problem by distributing physical memory. In a DSM, the single logical shared memory address space is partitioned across multiple physical memory modules, and each memory module is given its own dedicated memory controller that services shared memory requests destined to that module. A shared memory abstraction is synthesized across the physically distributed memories via shared memory modules, one per physical memory and controller, that communicate using point-to-point messages across a switched interconnection network, such as those discussed in [18]. Figure 2.2 illustrates these components that make up the DSM architecture. In the figure, each processor, its local memory, and its local shared memory module together form a DSM node.

Synthesis of a shared memory abstraction in a DSM occurs in the following manner. When a shared memory module receives a shared memory request from a local processor, it determines the physical memory module for which the request is destined using a mapping that reflects the partitioning of logical shared memory across the physical memory modules. If the request maps to the local physical memory module, the request is satisfied immediately through local memory. If the request maps to a remote physical memory module, the shared memory module initiates a remote transaction by sending a message that contains the desired shared memory address across the interconnection network to the appropriate remote shared memory module. The remote shared memory module responds to the transaction by accessing the shared memory location in its local physical memory module, and then sending the data back to the requesting shared memory module in another message. The transaction completes when this data is supplied to the requesting processor.

The distribution of physical memory and memory interfaces in a DSM allow the aggre-

Figure 2.2: DSMs partition the logical shared address space across multiple physical memory modules (M), and synthesize a shared memory abstraction via shared memory modules (SMM) that communicate across an interconnection network. Each shared memory module services memory requests from a processor (P); shown with each processor is a hardware cache (C). Together, a processor (and its hardware cache), its local memory, and its local shared memory module form a DSM node.

gate memory bandwidth to scale along with the number of processing elements. When the size of a DSM is increased, not only are processing elements added, but with the additional processors, physical memory modules and memory controllers are added as well. Furthermore, the amount of communication bandwidth supplied between memory modules can be increased by adding switches to grow the size of the interconnection network. Because of the ability to scale processing, memory, and communication resources together (as opposed to scaling processing resources alone as was the case in the SMP architecture), the DSM provides scalability.

#### 2.1.2 Cache Coherence

Caching replicates data across a memory hierarchy from slower storage into faster storage. The goal is to keep the most frequently accessed data in the highest level of the memory hierarchy (fastest storage) so that it can be accessed efficiently by the processor. For those applications that demonstrate memory access locality, caching can very effectively reduce the overheads associated with memory operations performed by the processor.

The implementation of caching in shared memory multiprocessors leads to the well-known *cache-coherence problem*. In a multiprocessor that permits the caching of shared data, it is possible for the data associated with a single shared memory address to become replicated in multiple processor caches. If a processor tries to write a new value into one cached copy, the other cached copies will become incoherent or stale with respect to the written copy.

The cache coherence problem in shared memory multiprocessors is addressed by maintaining coherence on cached data using a *cache-coherence protocol*. DSMs typically employ cache-coherence protocols that are *directory based* [15, 32, 3, 14, 63]. Directory-based cache-coherence protocols maintain a directory entry for each cache block of data

in shared memory. Each time a request for a cache block is fulfilled by the shared memory module, the ID of the DSM node from which the request originated is recorded in the associated directory entry. Therefore, the directory entry for a cache block records the set of nodes which have a copy of the cache block at any given moment in time.

Coherence can be maintained on a particular cache block by using the directories to perform *invalidation*. The process of invalidation is initiated by the shared memory module where the directory entry resides, typically called the cache block's *home node*. At the home node, the directory entry for the cache block is consulted by the shared memory module, and an invalidation message is sent to every DSM node specified in the directory entry. At each node, the invalidation message causes the copy of the cache block to be purged from the cache. The cache then sends an acknowledgment message back to the home node. If the purged cache block is dirty, the acknowledgment message also includes data that reflects the updates performed on the cache block. At the home, the shared memory module processes the acknowledgments, and any data in acknowledgments with updates are merged into the location in the memory module that provides the backing for the cache block (see Sections 2.2.1 and 2.2.2 for more details on updates and how they are merged). After merging the update(s), the data in the memory module reflects the most recent version of the data as a result of the writes performed on the cache block up to the point when invalidation was initiated.

Invalidation maintains coherence for two reasons. First, it provides a means for updates performed at the caches to propagate back to the home. This allows subsequent requests after an invalidation to receive data that reflects the updates. Second, it is the mechanism by which stale data is reclaimed. Each invalidation removes data that has become stale in a processor's cache. Subsequent accesses performed to an invalidated cache block will therefore not access the stale value, but instead will re-request the cache block from the home and receive an updated value.

### 2.2 DSM Implementation

Section 2.1 above discussed distributed shared memory and caching in DSMs as general concepts. In this section, we take a closer look at two specific DSM implementations, the hardware cache-coherent DSM (examples include [46, 44, 23, 38, 47]), and the software page-based DSM (examples include [48, 6, 13, 36, 37]). We will focus on how the implementation of distributed shared memory and cache coherence differ on these two architectures.

The primary difference between hardware and software DSMs is the level in the memory hierarchy on each DSM node where caching is performed. In the hardware DSM, caching is performed in the hardware processor caches, and in the software DSM, caching is performed in main memory (the "C" and "M" modules, respectively, in Figure 2.2). Where caching occurs determines the *coherence unit*, a block of memory which the DSM treats as an indivisible unit of data during replication and invalidation. Because hardware DSMs perform caching in processor caches, its coherence unit is the processor cache line.

Similarly, because the software DSM performs caching in main memory, its coherence unit is the page. The size or *granularity* of the coherence unit is a crucial system parameter, and is the topic of Sections 3.2 and 3.3 in Chapter 3.

In the next two sections, we discuss the implications for performing caching in either hardware caches or main memory.

#### 2.2.1 Hardware Cache Coherence

Hardware DSMs provide special-purpose hardware support for shared memory (*i.e.* the shared memory modules in Figure 2.2 are implemented in hardware). This shared memory hardware synthesizes a physical shared memory address space, and maintains coherence on the shared data cached in the processor caches, as described in Section 2.1 above.

The shared memory hardware is integrated with the mechanisms that manage the processor caches through cache miss events. When the processor on a DSM node suffers a cache miss, the cache miss is intercepted by the shared memory hardware on the processor's local node. Based on the address of the cache miss, the shared memory hardware either fulfills the cache miss directly from local memory, or from remote memory via communication with a remote shared memory module. In the latter case, the creation and transmission of messages across the interconnection network, as described in Section 2.1.1, is performed purely in hardware.

The shared memory hardware not only supports the shared memory abstraction, but it also supports cache coherence. For simplicity, hardware DSMs typically implement a single-writer protocol using an invalidate-on-write policy (simplicity of the cache-coherence protocol is important due to the complexities of hardware implementation). In a single-writer protocol, multiple outstanding cache copies are allowed so long as accesses to the copies are confined to reads. Once a processor tries to perform a write, the protocol invalidates all outstanding copies. Single-writer protocols are simple because there can be at most one outstanding cache block that is dirty at any given time. Therefore, when a dirty cache block is invalidated, the entire cache block can be written into the memory module at the home node thus propagating any updates performed on the cache block. Supporting multiple writers is more complex because it requires multiple dirty cache blocks to be merged during invalidation. In Section 2.2.2, we discuss the protocol additions necessary to support multiple writers.

While single-writer protocols are simple and therefore desirable from a hardware implementation standpoint, they can introduce performance penalties. In particular, each shared memory write could potentially cause the invalidation of one or more cache copies<sup>1</sup>. If the processor performing such a write is stalled for the duration of the invalidation(s), significant cache miss stall can be introduced, thus degrading performance. Many techniques have been proposed to address such cache miss stall overhead, such as software-controlled prefetching [51], block multithreading [43, 68], and relaxed memory

<sup>&</sup>lt;sup>1</sup>In the worst case, there could be P-1 outstanding copies, where P is the number of DSM nodes.

consistency models [1, 25, 19]. We discuss relaxed memory consistency models below; a discussion and evaluation of all three techniques appears in [27].

#### Relaxed Memory Consistency

The memory consistency model supported by a shared memory multiprocessor determines the ordering in which individual processors view the memory operations performed by other processors in the system. The strongest form of memory consistency is sequential consistency [45]. Sequential consistency states that a total order can be defined across all shared memory operations, and furthermore, all processors see the same total order. Multiprocessors that stall a processor on each shared memory write until all cutstanding cache copies are invalidated support sequential consistency. Stalling writes during invalidation ensures that when a write is performed, no other copies of the cache line exist in the system. Therefore, there is a well-defined moment in time relative to all processors that the write commits, a condition necessary for sequential consistency.

Higher performance can be attained if the system is not required to support such a singular commit point for writes. Memory consistency models that are less strict than sequential consistency in their guarantees on event ordering, known as relaxed memory consistency models, allow systems to overlap the overhead of maintaining consistency on shared data with useful computation. Instead of guaranteeing that the updates performed by a processor are visible to all other processors after every shared memory write (as is provided by sequential consistency), relaxed memory consistency only guarantees that updates are visible at special points in a program. An example of such a relaxed memory model is release consistency (RC) [25]. Programs written assuming an RC memory consistency model must include special annotations, known as releases and acquires, that specify to the memory system when coherence is necessary. The memory system guarantees strict ordering between release and acquire operations (i.e. releases and acquires are sequentially consistent), but individual shared memory operations between releases and acquires can reorder.

Relaxing the order in which individual processors view the updates performed across all processors enables the complete elimination of memory stall due to cache misses on writes. Because a singular commit point is not needed under RC, a processor performing a write can issue the write immediately without being stalled even if the location being written has been cached by other processors. Each write performed by a processor is buffered, usually in a hardware buffer provided by the processor<sup>2</sup>. The shared memory hardware propagates the updates in the write buffer at the pace of the memory system which can be slow if invalidations are required. Meanwhile, the overhead of maintaining coherence on the buffered updates is hidden from the processor because the processor is allowed to continue performing useful computation. Notice this breaks sequential consistency. For example, if two writes are performed simultaneously to the same location in shared memory, each processor will think its write happened first.

<sup>&</sup>lt;sup>2</sup>Most modern processors provide on-chip write buffers.

### 2.2.2 Page-Based DSMs

Software DSMs rely purely on software to support shared memory (i.e. the shared memory modules in Figure 2.2 are implemented in software). Therefore, there is no sharing across physical addresses as there is in hardware DSMs. The memory modules on different DSM nodes have separate physical address spaces. Instead, the shared memory abstraction is constructed by enforcing a single shared virtual address space across DSM nodes.

A shared virtual address space is constructed by leveraging the address translation and protection checking mechanisms as is commonly provided by hardware TLBs (Translation Lookaside Buffers). The address translation mechanism provides the level of indirection needed between shared virtual memory and physical memory so that each DSM node's physical memory can be used as a cache for replicated pages. The protection checking mechanism provides access control on processor accesses so that software shared memory can be invoked for those processor accesses which require distributed shared memory service. The software shared memory module is integrated with the TLB fault handler. TLB faults to pages under software distributed shared memory management are passed to the shared memory module for processing. Therefore, protection checking as provided by TLBs serves the same purpose that cache misses do for hardware DSMs-it is the conduit through which shared memory requests get forwarded from the processor to the shared memory module.

Compared to hardware DSMs, software DSMs are more sensitive to frequent internode communication for two reasons. First, anytime communication occurs, the shared memory module must intervene, and software implementation of the shared memory module is less efficient than hardware implementation. Second, messaging across the inter-node network in Figure 2.2 is expensive for page-based systems because software DSMs usually employ commodity local area networks (LANs) and commodity network interfaces as compared to the VLSI networks and specialized interfaces used in hardware DSMs. Consequently, it is especially important to minimize the amount of inter-node communication for software DSMs. Below, we discuss two techniques that together reduce communication in software DSMs: delayed updates and multiple-writer protocols.

#### **Delayed Updates**

As described in Section 2.2.1 above, the RC memory consistency model allows coherence overhead to be overlapped with useful computation by relaxing the guarantees on event ordering. This permits the updates performed by a processor to be decoupled from the overhead of maintaining coherence on those updates, thereby eliminating stalls due to writes. While this relieves the processor from coherence overheads, it does not relieve the shared memory system and the interconnection network between DSM nodes from such overheads since the coherence of the updates must be enforced eventually.

The relaxation of event ordering guarantees permitted by RC can be further leveraged to reduce the volume of coherence traffic, and thus the coherence load on the shared memory modules and the interconnection network. If coherence on a dirty cache block

is delayed, fewer coherence operations are necessary because multiple updates to the same cache block can be merged and made coherent in one coherence operation. The coherence volume reductions due to delaying coherence can be significant for software DSMs because they employ a large coherence unit, a page. The larger the coherence unit, the greater the likelihood that multiple shared memory writes will fall on the same cache block and thus become merged.

Software DSMs that support an RC memory consistency model can maximize the number of updates that are merged by delaying the coherence on a dirty page for as long as possible—until a release operation is encountered. In such delayed update systems, no coherence operations are invoked on normal shared memory accesses. All updates occur locally and are buffered in the page cache in each node's physical memory. A data structure, known as the *Delayed Update Queue* [13], records all the pages in the page cache that are dirty. At a release operation, the processor performing the release is stalled and coherence is initiated on all the pages listed in the Delayed Update Queue. The stalled processor resumes computation only after its updates have been consolidated.

#### **Multiple-Writer Protocols**

The delayed update technique described above can be effective only if multiple writers are permitted simultaneously on the same page. Otherwise, delayed updates can only be applied to pages with a single writer and zero or more readers. The multiple-writer case is important because of *false sharing*. False sharing occurs when two shared memory accesses with distinct addresses fall on the same cache block [21]. The coherence protocol is fooled into believing that the accesses conflict because it treats each cache block as an indivisible unit of data. Therefore, communication results to maintain coherence even though the coherence is unnecessary. False sharing becomes more severe as the size of the cache block increases. Since the coherence unit in software DSMs is a page, false sharing can be quite severe.

Handling multiple writers requires the ability to merge the updates performed on two or more cache blocks into a single coherent copy of the cache block at the home node. With multiple writers, it is not sufficient to simply store the entire contents of a dirty cache block at the home node as is done in hardware DSMs since all but the last store would overwrite the updates of the other cache blocks. Instead, it is necessary to determine what locations in each cache block have changed and to only update those locations at the home node.

Protocols that support multiple writers perform twinning and diffing to enable the merge of multiple dirty cache blocks [13]. Any processor that wishes to write a page in its page cache must first make a copy of the page, known as a twin. All writes are performed on the original, leaving the twin unmodified. When it becomes necessary to enforce coherence on the page, a comparison is performed between the dirty page and its twin, producing an update list, or diff, that represents all changes made to the page since the creation of the twin. The diff is sent to the home node so that the updates can be merged into the home node's copy of the page. Diffs have the property that multiple

31

diffs can be merged by simply appending them to form a single diff representing all the changes made collectively by the processors that modified the page.

# Chapter 3

# The Multigrain Approach

This chapter presents a novel approach to building large-scale distributed shared memory machines that couples several small- to medium-scale multiprocessors using page-based software DSM techniques. We call this the "multigrain approach" because a single transparent shared memory layer is synthesized through the cooperation of both fine-grain and coarse-grain shared memory mechanisms.

The multigrain approach stems from the tension between supporting efficient shared memory mechanisms for high performance and supporting low-cost design for cost-effectiveness in the construction of large-scale shared memory machines. Fine-grain shared memory mechanisms provide high performance on a broad range of applications. While recent research efforts have enabled such mechanisms to scale in terms of performance, large-scale fine-grain architectures have failed to exhibit cost efficiency because of the engineering challenges presented by maintaining tight coupling across a large number of processors. Conversely, loosely-coupled software DSMs that support coarse-grain shared memory mechanisms are cost-effective because they leverage commodity technology. However, because loose coupling comes at the expense of highly efficient shared memory mechanisms, coarse-grain architectures cannot provide scalable performance, particularly on applications that exhibit fine-grain sharing.

The multigrain approach mediates the tension between performance and cost by building shared memory machines hierarchically and leveraging both fine-grain and coarse-grain shared memory mechanisms at different levels in the hierarchy. Multigrain architectures support fine-grain mechanisms within small- to medium-scale multiprocessor nodes. The size of each node is scaled as much as possible for performance, but only to the extent that the cost incurred by scaling fine-grain mechanisms remains reasonable. As soon as nodes become prohibitive from a cost standpoint, further scaling is facilitated by coupling multiple nodes using coarse-grain mechanisms.

The rest of this chapter motivates and presents the multigrain approach in greater detail, providing the foundation for the work presented in the rest of the thesis. Since granularity plays an important role in determining both performance and cost in shared memory machines, we begin by defining shared memory granularity in Section 3.1. In Section 3.2, we examine how existing conventional shared memory architectures support

granularity, and expose the tension between performance and cost. Finally, in Section 3.3, we introduce the multigrain approach.

### 3.1 A Definition of Grain

Granularity is a familiar term in computer systems research used to describe many different aspects of computation. For instance, granularity of parallelism refers to the size of threads in a parallel computation. Threads that run for only a small number of cycles before exiting are "fine-grained," while threads that run for a large number of cycles are "coarse-grained." Granularity has also been used to describe synchronization. An application can exhibit either fine-grained or coarse-grained synchronization behavior depending on whether processors within the application synchronize frequently or infrequently, respectively.

The sharing patterns exhibited by a shared memory application have been characterized using the notion of granularity as well. Qualitatively, fine-grained sharing implies frequent communication between processors of small units of data, while coarse-grained sharing implies infrequent inter-processor communication of large units of data. However, compared to other uses of granularity, the use of granularity to describe application-level sharing patterns is imprecise because it lacks a quantitative definition. To help illustrate this point, consider our two previous examples, granularity of parallelism and granularity of synchronization. The granularity of parallelism can be quantified in terms of the number of cycles a thread executes before terminating. The granularity of synchronization can be quantified in terms of the frequency with which processors synchronize. Even though sharing granularity is common terminology within the domain of shared memory machines, surprisingly, no precise definition exists. Furthermore, because grain has been used in the context of both space and time, we need a definition that integrates both space and time. In this section, we develop a definition for sharing granularity that has a quantitative foundation to provide precise terminology for the remainder of the thesis.

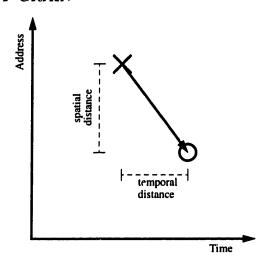

We define the sharing granularity exhibited by two shared memory accesses as fine-grain if they occur close in time and reference memory locations separated by a small distance. Otherwise, the two shared memory accesses are defined to exhibit coarse-grain sharing. To illustrate this definition, let us plot the shared memory accesses made by all processors on a two-dimensional plot with time on one axis and memory address on the other, as shown in Figure 3.1. A grain vector can be defined in this 2-space for any pairing of shared memory accesses performed by different processors whose direction and magnitude are determined by two components, one for space and one for time. Spatial distance is simply the number of distinct memory locations that separate the two shared memory accesses. A smaller spatial distance arises if the two memory accesses are destined to locations that are close together in physical memory. Conversely, a larger spatial distance arises if the two memory accesses are destined to locations that are far apart in memory. Temporal distance can be defined by the number of clock cycles between the issue of the two memory accesses by their respective processors. A small number of

Figure 3.1: Defining sharing granularity using the *grain vector*. Two shared memory accesses, one made by a processor labeled "X" and another made by a different processor labeled "O," are plotted in space and time. Spatial and temporal distance components of the grain vector are labeled.

clock cycles indicates that the memory accesses are performed close in time, while a large number of clock cycles indicates that the memory accesses are performed far apart in time.

The two shared memory accesses in Figure 3.1 constitute sharing between two processors. The granularity of this sharing can be defined by considering both spatial and temporal distance components of the grain vector. Fine-grain sharing occurs when both spatial and temporal distance are small. Coarse-grain sharing occurs when at least one of the two components of distance is large. The requirement that both spatial and temporal distance are small for fine-grain sharing to occur is somewhat non-intuitive. Sharing granularity measures the degree to which shared memory accesses performed by different processors conflict. The definition above states that memory accesses conflict only if they occur close together in space and time. A real-world analogy is two friends who would like to meet face-to-face. For the meeting to occur, they must choose both a time and a place to meet. If either of these criteria are not met, the meeting will not occur.

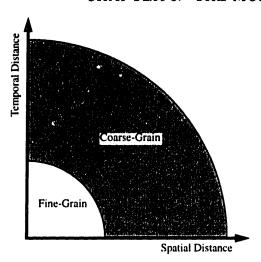

Our definition of sharing granularity is illustrated visually in Figure 3.2. In the figure, spatial and temporal distance are specified along the X- and Y-axes, respectively, defining a plane. Each point inside the plane corresponds to a particular magnitude for a grain vector. The space of grain vector magnitudes is partitioned into those that represent fine-grain sharing, and those that represent coarse-grain sharing.

Figure 3.2 represents a simple definition of sharing granularity which is sufficient for the purposes of this thesis. Several issues must be further addressed in order to provide a more rigorous definition. We will discuss these issues only briefly here. First, we have drawn the partition between fine-grain and coarse-grain regions in Figure 3.2 in a circular fashion for simplicity, implying that sharing granularity is a function of

Figure 3.2: Classification of sharing granularity in terms of spatial and temporal distances. Fine-grain sharing occurs only if both temporal and spatial distance is small. All other sharing is coarse-grained.

only one variable, the grain vector magnitude. It may be desirable to formulate sharing granularity as a function of both spatial and temporal distance independently (leading to a partition boundary that is rectangular), or to adopt more complex formulations that take into account the direction as well as the magnitude of the grain vector. Second, Figure 3.2 shows a discontinuous transition between fine-grain and coarse-grain regions, implying that there is an abrupt delineation. In actuality, the transition should be continuous; therefore, rather than being simply fine-grained or coarse-grained, sharing would be characterized by some continuous quantity, for example, the magnitude of the grain vector. Finally, the development of our definition centers on two shared memory accesses performed by two processors. For the definition to be useful in describing the sharing behavior of an entire application, it is necessary to extend this definition to account for multiple accesses performed by multiple processors.

### 3.2 Granularity in Conventional Architectures

The presence of either fine-grain or coarse-grain sharing, as defined in the previous section, dictates the support needed by an application from a shared memory architecture in order to achieve high performance. In this section, we examine how conventional architectures support the demands of fine-grain and coarse-grain applications, and we discuss the implications of providing such support on system scalability and cost.

### 3.2.1 Supporting Fine-Grain Sharing

Applications that exhibit fine-grain sharing require aggressive architectural support in order to achieve high performance. As indicated by the definition of sharing granularity

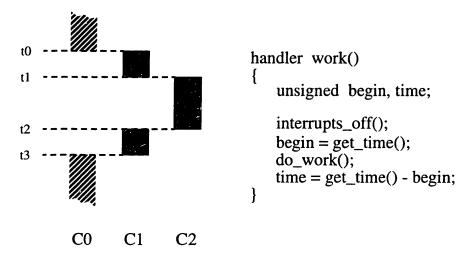

in Section 3.1, fine-grain sharing involves frequent conflicts between the shared memory accesses performed on different processors. Such conflicts invoke service from the shared memory layer in order to provide coherence on the shared data<sup>1</sup>. Because of the high frequency of conflicts (due to the small temporal distances separating conflicting accesses), significant shared memory overhead can be suffered leading to poor application performance unless the underlying architecture provides support for fine-grain sharing.