### **Tiled Microprocessors**

by

Michael Bedford Taylor

A.B., Computer Science Dartmouth College, 1996

S.M., Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1999

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2007

### ARCHIVES

© 2007 Massachusetts Institute of Technology. All rights reserved.

### **Tiled Microprocessors**

by

Michael Bedford Taylor

Submitted to the Department of Electrical Engineering and Computer Science on February 2007 in partial fulfillment of the requirements for the Degree of

Doctor of Philosophy

in Electrical Engineering and Computer Science

#### ABSTRACT

Current-day microprocessors have reached the point of diminishing returns due to inherent scalability limitations. This thesis examines the tiled microprocessor, a class of microprocessor which is physically scalable but inherits many of the desirable properties of conventional microprocessors. Tiled microprocessors are composed of an array of replicated tiles connected by a special class of network, the Scalar Operand Network (SON), which is optimized for low-latency, low-occupancy communication between remote ALUs on different tiles. Tiled microprocessors can be constructed to scale to 100's or 1000's of functional units.

This thesis identifies seven key criteria for achieving physical scalability in tiled microprocessors. It employs an archetypal tiled microprocessor to examine the challenges in achieving these criteria and to explore the properties of Scalar Operand Networks. The thesis develops the field of SONs in three major ways: it introduces the 5-tuple performance metric, it describes a complete, high-frequency <0,0,1,2,0> SON implementation, and it proposes a taxonomy, called AsTrO, for categorizing them.

To develop these ideas, the thesis details the design, implementation and analysis of a tiled microprocessor prototype, the Raw Microprocessor, which was implemented at MIT in 180 nm technology. Overall, compared to Raw, recent commercial processors with half the transistors required 30x as many lines of code, occupied 100x as many designers, contained 50x as many pre-tapeout bugs, and resulted in 33x as many post-tapeout bugs. At the same time, the Raw microprocessor proves to be more versatile in exploiting ILP, stream, and server-farm workloads with modest to large amounts of parallelism.

Thesis Advisor:

Anant Agarwal Professor Electrical Engineering and Computer Science

# Contents

| 1 | Intr       | oduction                                                                             | 13 |

|---|------------|--------------------------------------------------------------------------------------|----|

|   | 1.1        | Emerging Issues in Microprocessor Design                                             | 13 |

|   |            | 1.1.1 VLSI Resources                                                                 | 13 |

|   |            | 1.1.2 Putting VLSI Resources to Use                                                  | 15 |

|   |            | 1.1.3 Problems with Addressing Scalability through Microarchitecture                 | 15 |

|   | 1.2        | Addressing Scalability through Physically Scalable Microprocessor Designs            | 18 |

|   |            | 1.2.1 Seven Criteria for a Physically Scalable Microprocessor Design                 | 18 |

|   | 1.3        | Tiled Microprocessors: A Class of Physically Scalable Microprocessor                 | 22 |

|   |            | 1.3.1 Tiled Microprocessors Meet the Physical Scalability Criteria                   | 23 |

|   |            | 1.3.2 Tiled Microprocessors Overcome Microarchitectural Scalability Limitations .    | 24 |

|   |            | 1.3.3 The Raw Tiled Microprocessor Prototype                                         | 25 |

|   |            | 1.3.4 Contributions                                                                  | 25 |

|   |            | 1.3.5 Thesis Overview                                                                | 26 |

| 2 | The        | e Archetypal Tiled Microprocessor                                                    | 27 |

|   | 2.1        | Basic Elements of a Tiled Microprocessor                                             | 27 |

|   | <b>2.2</b> | Attaining Frequency Scalability (C1)                                                 | 28 |

|   | <b>2.3</b> | Bandwidth Scalability, Locality Exploitation and Proportional Latencies (C2, C3, C4) | 32 |

|   |            | 2.3.1 Bandwidth Scalability by Eliminating Broadcasts                                | 32 |

|   |            | 2.3.2 Providing Usage-Proportional Resource Latencies and Exploitation of Locality   | 33 |

|   | 2.4        | Attaining Efficient Operation-Operand Matching with Scalar Operand Networks (C5)     | 36 |

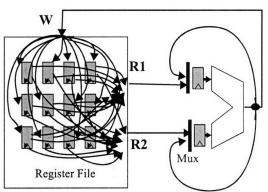

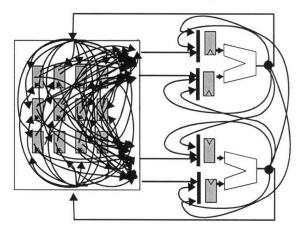

|   |            | 2.4.1 Scalar Operand Networks in Current Day Microprocessors                         | 37 |

|   |            | 2.4.2 Scalar Operand Network Usage in Tiled Microprocessors                          | 39 |

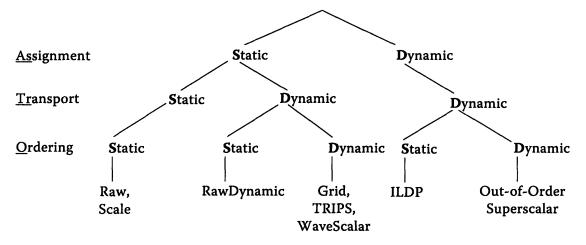

|   |            | 2.4.3 The AsTrO Taxonomy                                                             | 41 |

|   |            | 2.4.4 The 5-tuple Metric for SONs                                                    | 45 |

|   | 2.5        | Parallel Execution on Tiled Microprocessors                                          | 50 |

|   |            | 2.5.1 Multi-Threaded Parallel Execution on Tiled Microprocessors                     | 51 |

|   |            | 2.5.2 Single-Threaded Parallel Execution on Tiled Microprocessors                    | 51 |

|   | 2.6        | The ATM Memory System                                                                | 56 |

|   |            | 2.6.1 Supporting Memory Parallelism                                                  | 59 |

|   |            | 2.6.2 Compiler Enhancement of Memory Parallelism in Single Threaded Programs         | 61 |

|   | 2.7        | I/O Operation                                                                        | 62 |

|   | 2.8        | Deadlock in the ATM I/O and Generalized Transport Network (C6)                       | 62 |

|   |            | 2.8.1 The Trusted Core                                                               | 68 |

|   |            | 2.8.2 The Untrusted Core                                                             | 73 |

|   |            | 2.8.3 Deadlock Summary                                                               | 74 |

|   | 2.9        | Exceptional Events - Especially Interrupts (C7)                                      | 74 |

|   | 2.10       | ATM Summary                                                                          | 77 |

| 3 | Arc  | chitecture of the Raw Tiled Microprocessor 79                        |

|---|------|----------------------------------------------------------------------|

|   | 3.1  | Architectural Overview                                               |

|   | 3.2  | The Raw Tile                                                         |

|   |      | 3.2.1 The Raw Tile's Execution Core                                  |

|   |      | 3.2.2 Raw's Scalar Operand Network                                   |

|   |      | 3.2.3 Raw's Trusted Core                                             |

|   |      | 3.2.4 Raw's Untrusted Core                                           |

|   | 3.3  |                                                                      |

|   | ე.ე  |                                                                      |

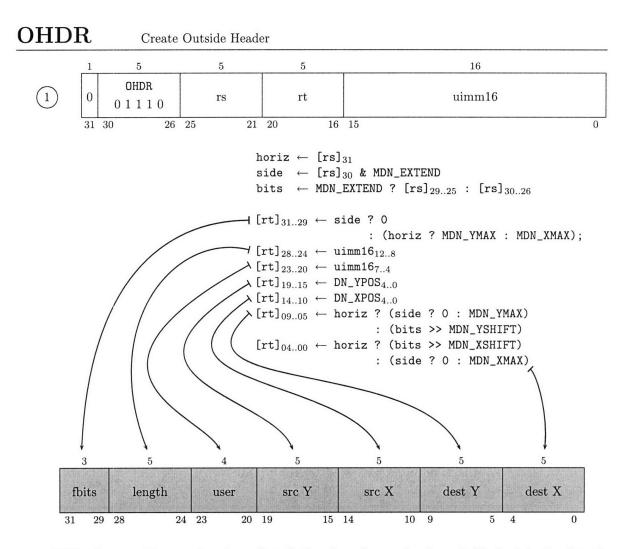

|   | 0.4  | 3.3.1 Raw I/O Programming                                            |

|   | 3.4  | Summary                                                              |

| 4 | The  | e Raw Implementation 99                                              |

| _ | 4.1  | The Building Materials                                               |

|   |      | 4.1.1 The Standard-Cell Abstraction                                  |

|   |      | 4.1.2 Examining the Raw Microprocessor's "Raw" Resources             |

|   | 4.2  | The Raw Chip         102           107                               |

|   |      |                                                                      |

|   | 4.3  | The Raw Systems                                                      |

|   | 4.4  | Conclusions from Building the Raw System 120                         |

| 5 | Per  | formance Evaluation 125                                              |

| - | 5.1  | Evaluation Methodology                                               |

|   | 0.1  | 5.1.1 Challenges in Evaluation Methodology                           |

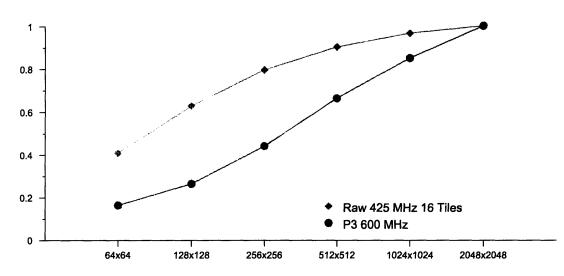

|   |      | 5.1.2 Developing a Comparison with the Pentium III                   |

|   |      |                                                                      |

|   | F 0  |                                                                      |

|   | 5.2  | Evaluation of a Single Tile using SpecInt and SpecFP                 |

|   | 5.3  | Multi-tile Performance as a "Server Farm On A Chip" 134              |

|   | 5.4  | Multi-tile Performance on sequential C and Fortran Applications      |

|   |      | 5.4.1 Memory Parallelism                                             |

|   |      | 5.4.2 Instruction Parallelism                                        |

|   |      | 5.4.3 Results                                                        |

|   |      | 5.4.4 Future Improvements                                            |

|   | 5.5  | Multi-Tile Performance on Streaming Applications with StreamIt       |

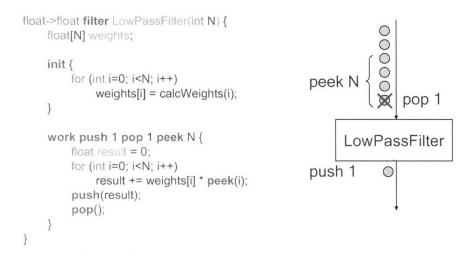

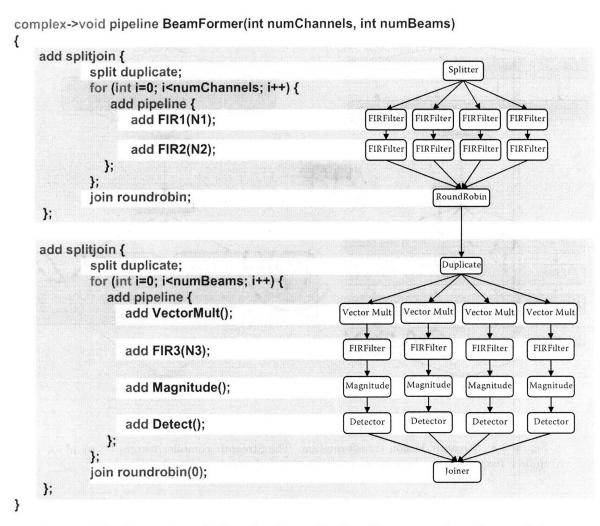

|   |      | 5.5.1 The StreamIt Language                                          |

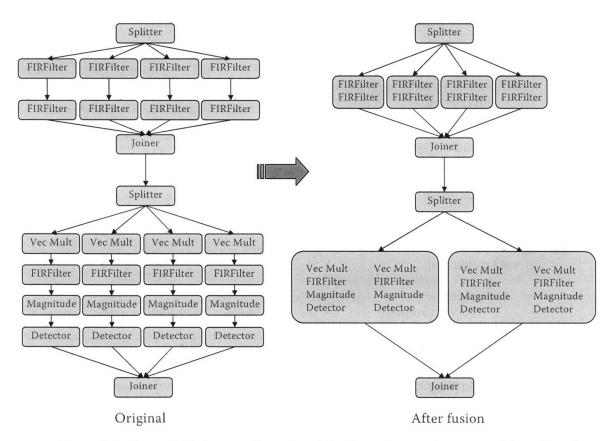

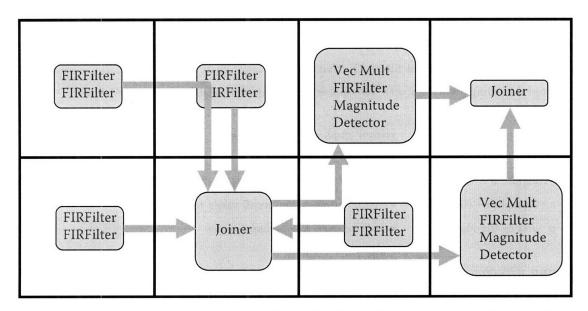

|   |      | 5.5.2 StreamIt-on-Raw Compiler Backend                               |

|   |      | 5.5.3 StreamIt-on-Raw Results                                        |

|   |      | 5.5.4 Future Improvements                                            |

|   | 5.6  | Multi-Tile Performance on Hand-Coded Streaming Applications          |

|   |      | 5.6.1 Linear Algebra Routines                                        |

|   |      | 5.6.2 The STREAM Benchmark 159                                       |

|   |      | 5.6.3 Signal Processing Applications                                 |

|   |      | 5.6.4 Bit-level Communications Applications                          |

|   | 5.7  | The Grain Size Question: Considering a 2-way Issue Compute Processor |

|   | 5.8  | Conclusion                                                           |

|   | 0.0  |                                                                      |

| 6 | Rela | ated Work 171                                                        |

|   | 6.1  | Microprocessor Scalability                                           |

|   |      | 6.1.1 Decentralized Superscalars                                     |

|   |      | 6.1.2 Non-Tiled Parallel Microprocessors                             |

|   |      | 6.1.3 Classical Multiprocessors                                      |

|   |      | 6.1.4         Dataflow Machines         173                          |

|   |      | 6.1.5 Tiled or Partially-Tiled Microprocessors                       |

|   | 6.2  | Scalar Operand Networks                                              |

|   | 6.3  | Conclusion                                                           |

|   | 0.0  |                                                                      |

|   |      |                                                                      |

### 7 Conclusion

| Α |            |                                              | 181 |

|---|------------|----------------------------------------------|-----|

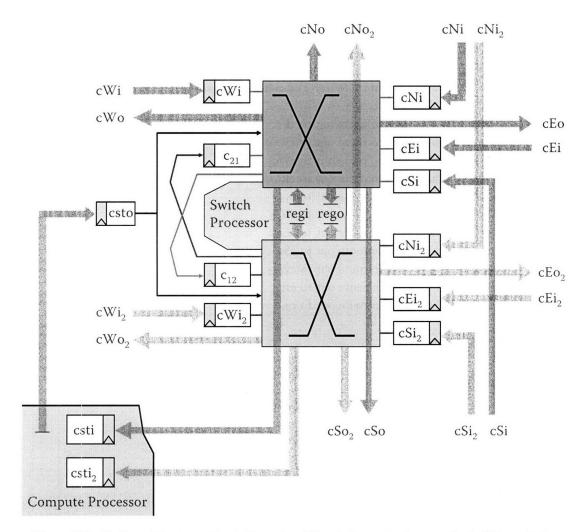

|   | A.1        | Architectural Overview                       | 181 |

|   |            | A.1.1 The Raw Tile                           | 181 |

|   | A.2        | Programming the Networks                     | 185 |

|   |            |                                              | 186 |

|   |            | A.2.2 Switch Processor Programming           | 186 |

|   |            |                                              | 189 |

|   |            | A.2.4 Dynamic Router Programming             | 191 |

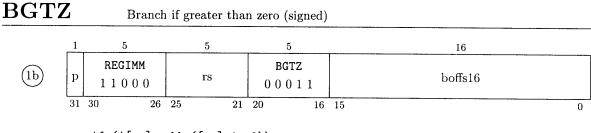

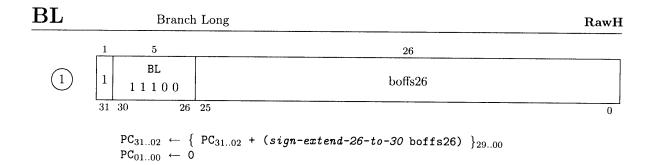

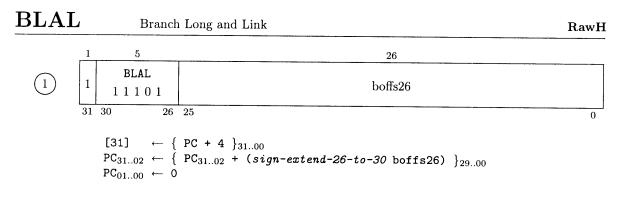

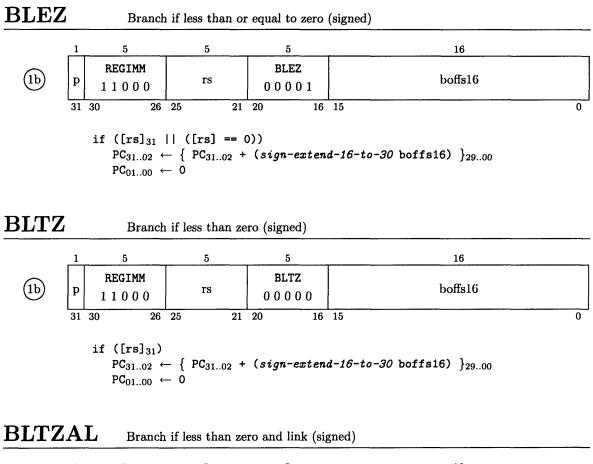

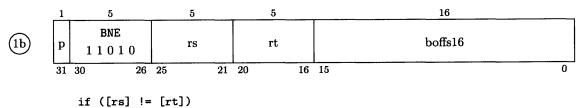

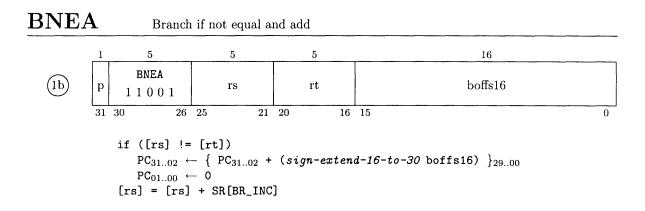

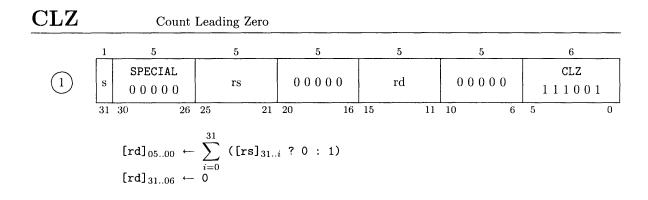

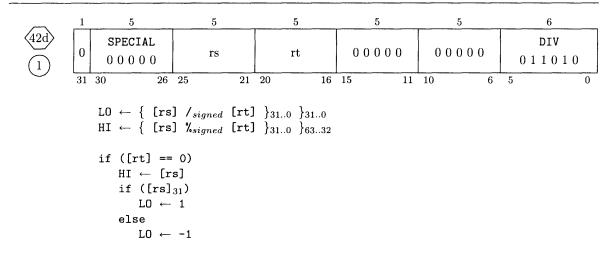

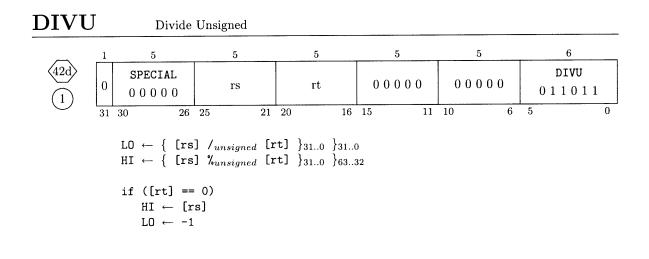

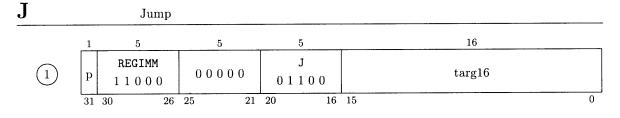

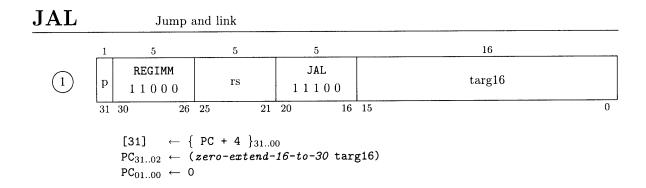

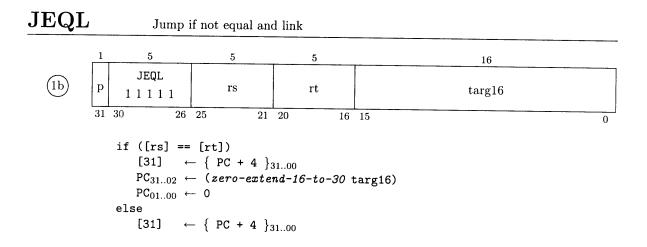

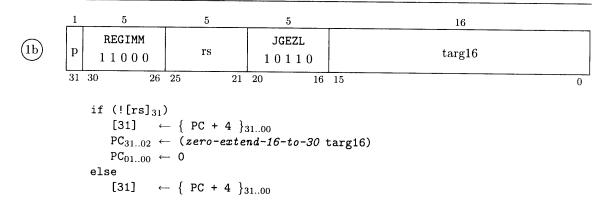

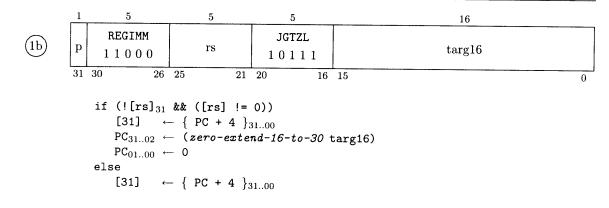

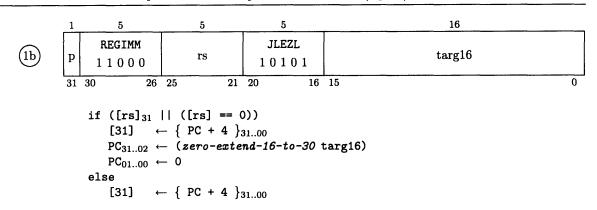

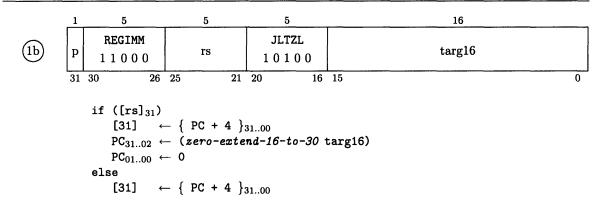

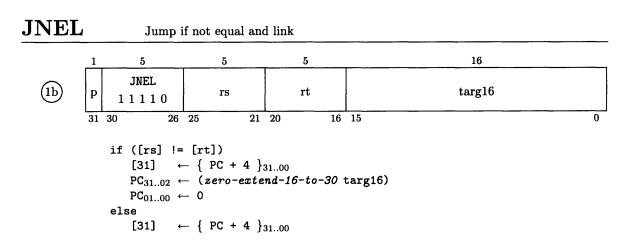

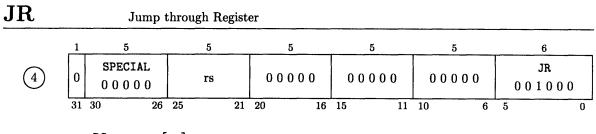

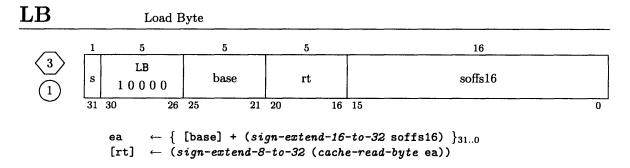

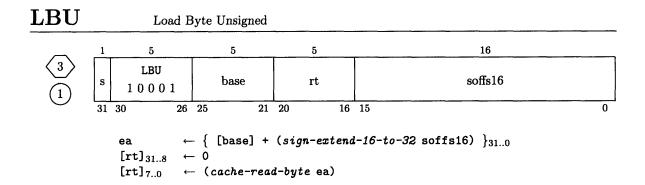

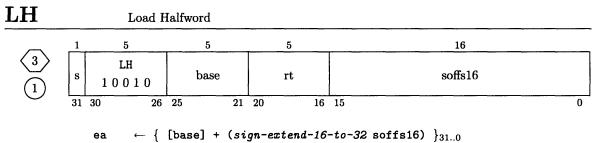

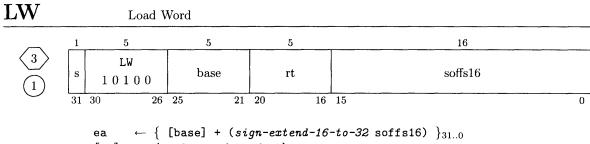

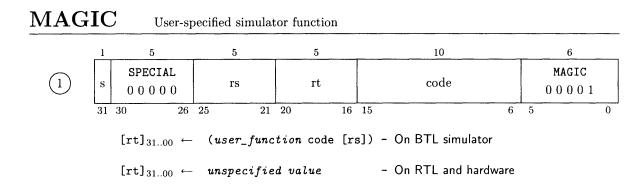

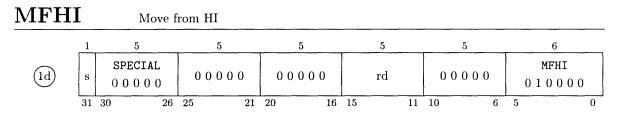

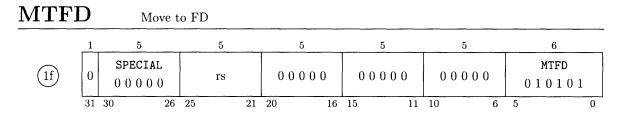

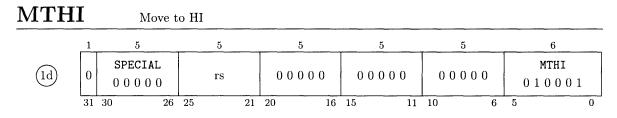

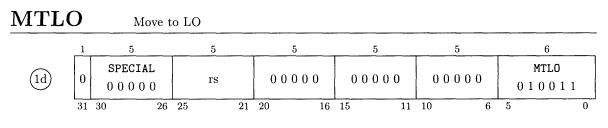

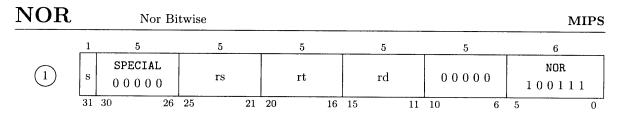

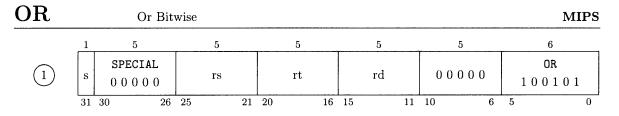

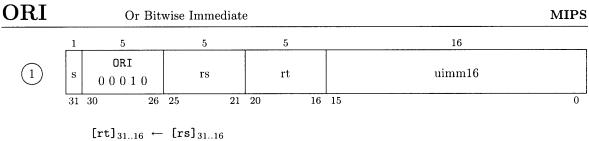

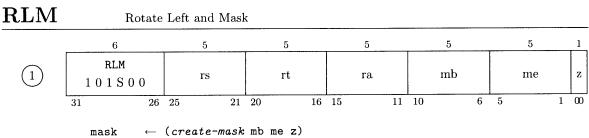

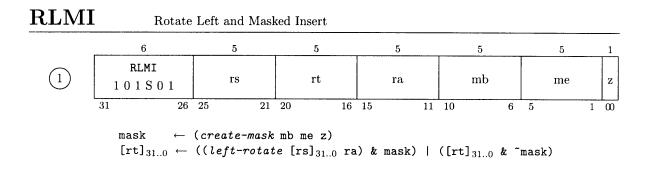

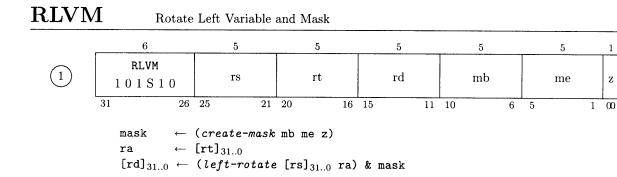

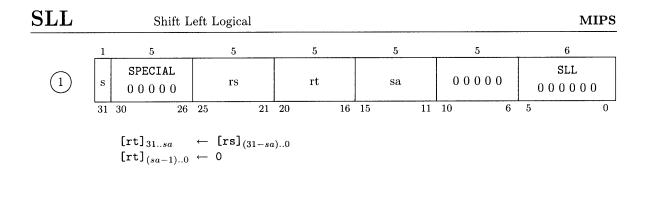

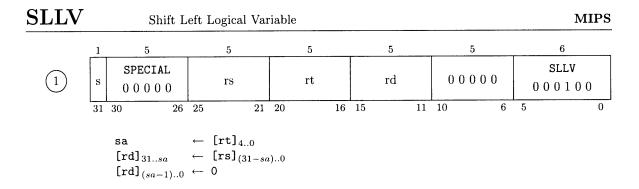

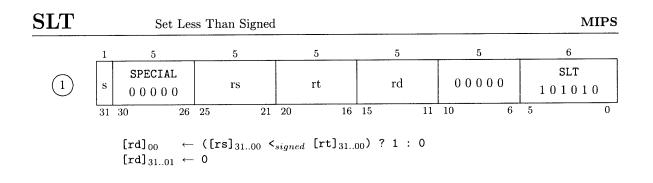

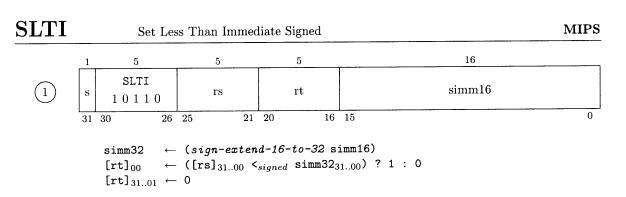

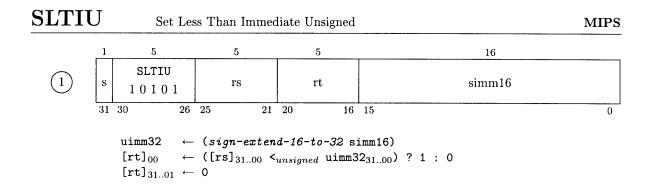

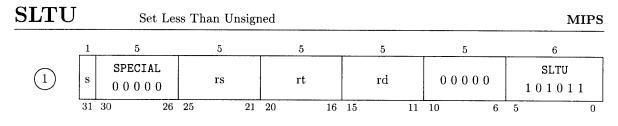

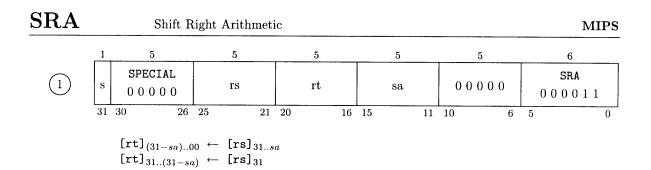

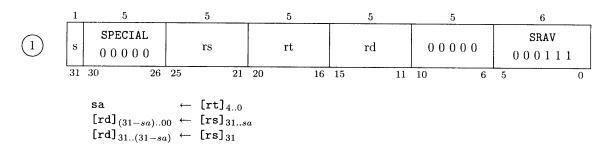

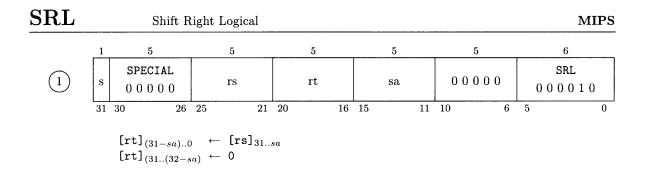

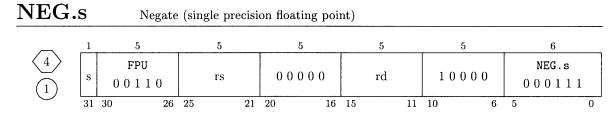

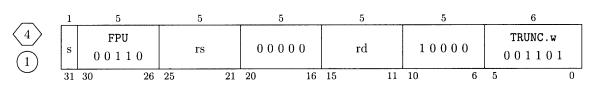

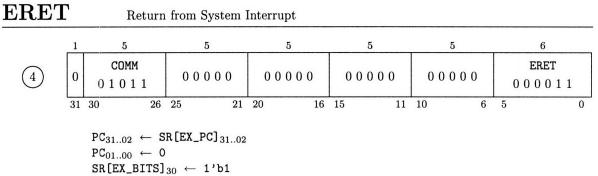

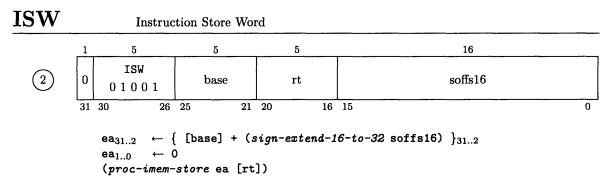

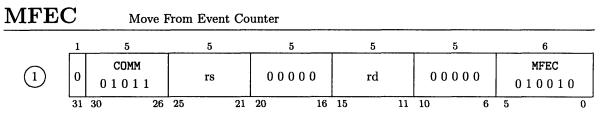

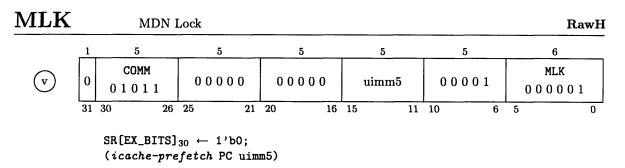

| в | The        | Raw Architecture Instruction Set             | 197 |

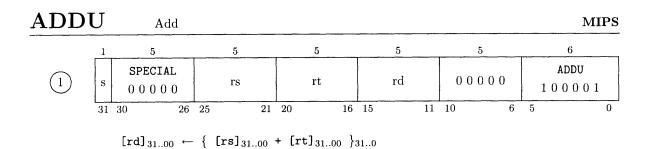

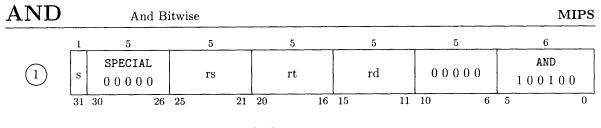

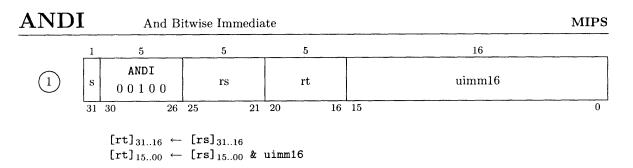

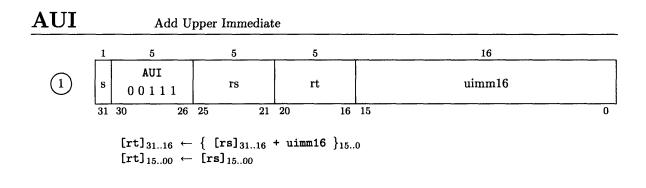

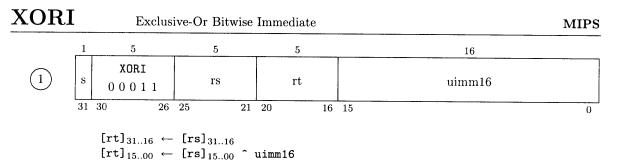

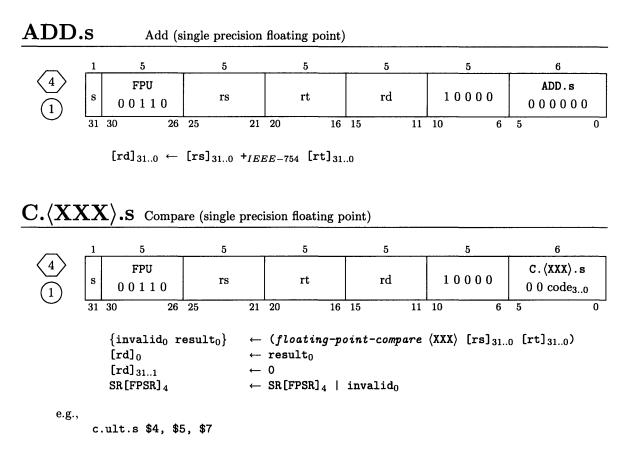

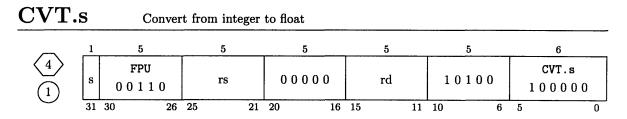

|   | B.1        | Compute Processor Instruction Set            | 197 |

|   |            | B.1.1 Register Conventions                   | 197 |

|   |            | B.1.2 Compute Processor Instruction Template | 198 |

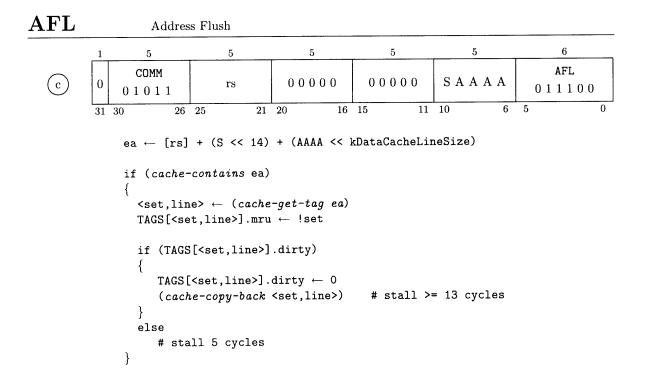

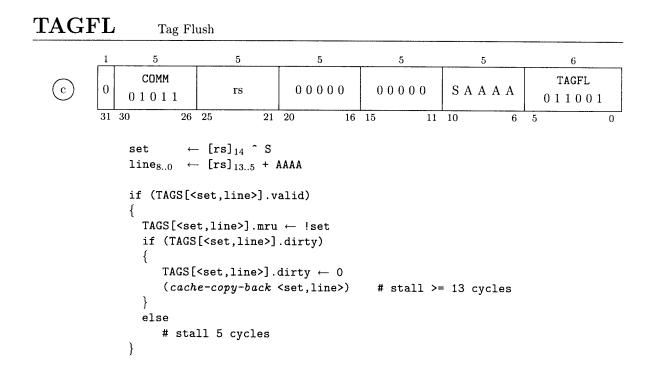

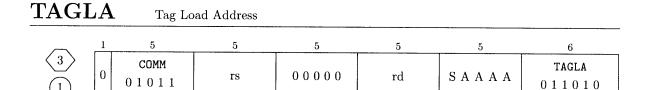

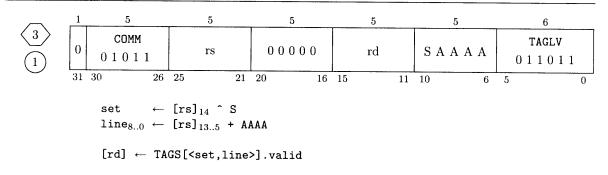

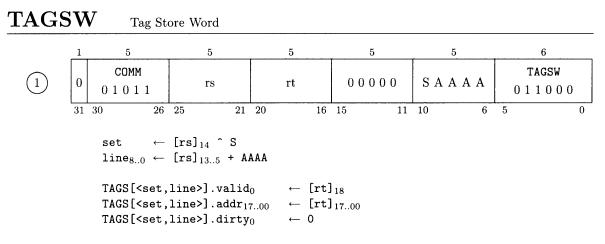

|   |            | B.1.3 Cache Management in Raw and RawH       | 229 |

|   | B.2        | Semantic Helper Functions                    | 233 |

|   | B.3        | Opcode Maps                                  | 235 |

|   |            | B.3.1 High-Level ("Opcode") Map              | 235 |

|   |            | B.3.2 SPECIAL Submap                         | 235 |

|   |            | B.3.3 FPU Submap                             | 236 |

|   |            |                                              | 236 |

|   |            | B.3.5 REGIMM Submap                          | 236 |

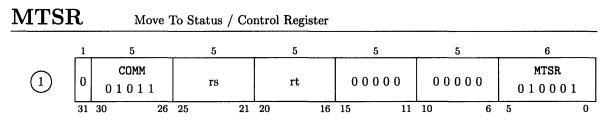

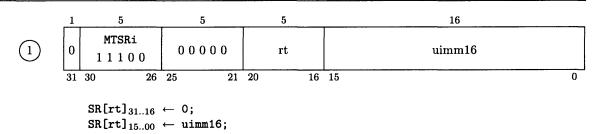

|   | <b>B.4</b> | Status and Control Registers                 | 237 |

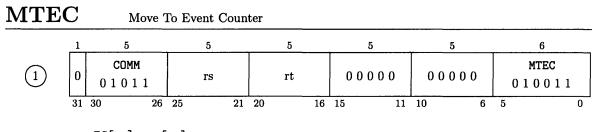

|   | B.5        | Event Counting Support                       | 243 |

|   | <b>B.6</b> | Exception Vectors                            | 246 |

|   | B.7        | •                                            | 247 |

|   |            |                                              | 247 |

|   |            | -                                            | 248 |

|   |            |                                              | 249 |

|   |            |                                              | 249 |

|   |            |                                              | 249 |

|   |            |                                              |     |

### Acknowledgments

My ten years at MIT have been a fruitful decade. For me, time is marked not in days but by the people that I meet and the systems that I work on. I've met many great people and worked on many great systems at MIT. However, as these acknowledgements will reflect, the story and the thanks start before I arrived at MIT.

### **Advisors and Thesis Committee**

First, I'd like to thank my advisor, Anant Agarwal, for providing me with the responsibility and autonomy that I was looking for, and for providing the Raw group with the resources and mandate to build great systems. I also thank Saman Amarasinghe, co-leader of the Raw project, who was a co-advisor to me and offered both technical advice and many words of support over the years. Finally, I thank Tom Knight, the third member of my committee, who inspires me to do creative research and has patiently presided over several of my MIT exams over the years. In high school, I read Steven Levy's *Hackers*, which chronicles, among other things, Tom's arrival at MIT in the mid-sixties as a teenager. Little did I know that he would end up on my thesis committee! Tom's feedback greatly strengthened the "Related Work" section of this document.

#### Pre-MIT

The earliest credit must go to my family. My brother was truly my earliest computer collaborator; I still remember us pulling long hours hacking *Escape from Old Khazan* on our dad's timesharing system. My mom and dad were avid supporters of my education and interests and helped me when times were rough.

When I was in Lakeville, Rodney Page, my computer science teacher, forgave me for hacking his network and fueled my interests with his remarkable enthusiasm. There, I also met my long-time friend, Douglas S. J. DeCouto, Hacker Mac, the man with five names, who ultimately brought me to MIT. Later, Doug worked in the same office one floor below me in 545 Tech Square. Quite rudely, he started his PhD after I started and finished it years before I did. His advice and friendship has truly kept me on course through the years. In Lakefile, I also met two of my good friends, Alex and Jason Ferries, erstwhile Macintosh hackers and great friends who I later roomed with while I was in Hanover and Boston.

In Denver, I learned a lot from Jeffrey Swartz, an engineer at StorTek, who combed through

my x86 code, line by line, and hacked with me on a variety of projects. From him, I learned many valuable lessons about software engineering and other things. Amazingly, almost all of this was done over the telephone or through email.

At Dartmouth, I met Scott Silver, with whom I spent many days hacking happily. We worked on many great projects together. He and I learned much about hacking together; but from him I also learned many things about life and about *chutzpah*. Scott and I journeyed to Silicon Valley together twice and had many adventures there. Through Scott, I also met Joy Silver, who is a constant source of enthusiasm and advice. At Dartmouth, I was indebted to my educators David Kotz, Dennis Healy, Samuel Rebelsky, Thomas Cormen, and Daniela Rus, who all invested a lot of time outside of class teaching me about research and computer science.

While in Silicon Valley, I had the pleasure of working with Tim Craycroft, Bruce Jones, Eric Traut, Jorg Brown, and Chad Walters – passionate software engineers and PowerPC coders who I learned many things from.

#### MIT

Not surprisingly given my tenure here, the list of people who impacted me at MIT is the longest.

Jonathan Babb, whose Virtual Wires research inspired the Raw project, was a frequent partnerin-crime. Among other things, we created Russian chess robots, argued over the Raw project, and compared our wildly intersecting libraries – microprocessors and VLSI, yes, but helicopter physics, space mission design, propaganda about propaganda, and ...? Jonathan is distinguished by an ability to inspire people to seek greatness and to realize that what they thought was big could be even bigger. Beyond that, Jonathan and I had many entertaining adventures - car accidents while drag racing, teaching streetwalkers to play chess at 3 am at Dunkin' Donuts, twilight Bova Bakery runs, and of course, screening the essential and formative works in the important emerging japanese medical horror film genre.

Walter Lee, whose parallelizing compiler was used for many of the results in this thesis, was my officemate for many years. We spent countless hours hacking on elegant systems that will never see the light of publication. We both enjoyed taking engineering problems, no matter how mundane sounding, and crafting the most amazing solutions for them. Somehow, after all of the projects and papers we've worked on, I consider Walter's characterization of me as a perfectionist (in his dissertation, no less!) as a badge of honor rather than an insult.

David Wentzlaff was involved in practically every aspect of the Raw hardware prototype. Walt and I had ear-marked him as our officemate from the beginning, and it was a great choice. In addition to his brilliant ideas, enthusiasm, and technical alacrity, he provided us with no end of entertainment with his inexorable annexation of office territory through the gradual sprawl of his acquisitions from reuse@mit. I always look forward to running into Dave somewhere in Cambridge to have a five hour discussion about something interesting. Matthew Frank, who was instrumental in the founding discussions of the Raw project (and indeed, authored the original 1997 Raw paper), was a compassionate counselor for many members of the Raw group. He was always there to appreciate my latest software hack (and vice versa) and provide thoughtful and motivating words.

Finally, Jonathan Eastep, my last office-mate at MIT, impressed me with his quick assimilation of practically everything about the Raw project. His enthusiasm for technology – out-gadgeting perhaps even Saman - is peerless and inspiring.

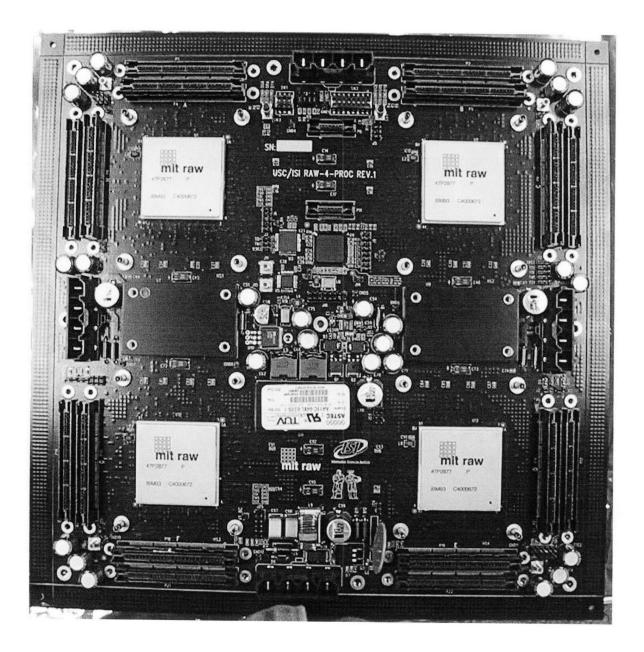

The contributions of the many members of the Raw group are obviously great and would be difficult to enumerate. No part of Raw was done in isolation. Without the effort of so many talented people, it would never have happened. To be comprehensive is impossible, but rather than just list names, I will list a few things that come to mind for each person – in all cases, a subset of what each person did. Jason Kim and I had frequent trips to Toscanini's to discuss Raw microarchitecture. We also supported each other through several week-long sessions, locked in various windowless rooms at IBM, learning that Einstimer truly was our friend. I still remember an episode with a certain Burger King hallucinogenic milkshake. IBM's ASIC team was a constant help as we iterated on the Raw ASIC design. USC ISI contributed essential software tools, benchmarks, and board design expertise. Jason Miller was my steady counterpart in pushing the Raw processor through the IBM tools; the Raw system could not have happened without his solid and unwavering engineering energy. Jason also designed the software i-caching system and was instrumental in developing the Raw motherboards. Andras Moritz examined the impact of different grain sizes in the Raw architecture. Rajeev Barua contributed MAPS, part of the Raw parallelizing compiler. Mark Seneski, master of logic emulation, ushered the Raw design through the SpecInt benchmark suite. Sam Larsen hacked on many parts of the Raw system, exuding quiet competence in every part of the toolchain he touched. Hank Hoffman and Volker Strumpen developed the Stream Algorithms for Raw, among other things. Albert Ma lent his extensive chip-building experience to the project and taught me about implementing datapaths. Jae-Wook Lee and I worked together to design the Raw placement methodology. Jae also found several pre-tapeout bugs in the design. Paul Johnson found more bugs in the Raw RTL than any other person and supported our software distribution efforts. Chris Kappler lent his extensive industry experience during the early stages of microarchitecture development. Devabhaktuni Srikrishna contributed his patient thoughtfulness to many interesting discussions. Mark Stephenson and Michael Zhang hacked on early versions of the Raw system; as roommates, our collaboration on a massive Allston party brought cops from all over. Russ Tessier offered the wisdom that comes from spending too long at MIT.

Arvind Saraf perfected the physical design for Raw's integer multiplier. Ben Greenwald contributed his fountain of knowledge and well-principled taste for elegant software engineering to many parts of the Raw infrastructure. Fac Ghodrat offered her chip-building expertise and was often there with an upbeat and persevering attitude during the long process of building the chip and struggling with the tools. Nathan Shnidman, whose research focused on software radio for Raw, gave great, thoughtful advice and was a fantastic traveling companion through Europe. With Ian Bratt, I had many frequent discussions about high-performance compilation for Raw. James Donald, a summer visitor, and now graduate student at Princeton, hacked on a number of projects with Walter and I.

Saman Amarasinghe's Commit group members were eager collaborators and provided the StreamIt infrastructure and results, which are also featured in this thesis. In particular, the efforts of Bill Thies, Mike Gordon, Jasper Lin, and Rodric Rabbah were instrumental in the Raw results.

Outside of the Raw group, I enjoyed interacting with the members of Martin Rinard's programming systems group. Martin Rinard, Karen Zee, Viktor Kuncak, Patrick Lam, Brian Demsky, and Alex Salcianu all contributed to an intellectual office camaraderie that MIT is all about. Karen Zee also designed the logo that graces the Raw microprocessor's package. I found Maria-Cristina's friendship, unique perspective and insights invaluable to me over the years. I also enjoyed brainstorming with Enoch Peserico, whose principled perspective on both computer architecture and life was refreshing.

I also thank the MIT Scale group, including Krste Asanovic, Chris Batten, Ronny Krashinsky, Mark Hampton, Jessica Tseng, Ken Barr, Seongmoo Heo, and Albert Ma, for many interesting discussions about microprocessor design.

John Redford and Doug Carmean, top-notch microprocessor designers at Chipwrights and Intel, provided me with much helpful advice and insight over time. I ran into Carmean in the hotel bar the night before my first-ever talk (at Hotchips) and his encouraging feedback more or less got me through it.

Mario Serna and Andy Kim, my roommates at Edgerton, offered many interesting conversations about military theory and materials science, as well as fresh baked bread and a hilarious escapade involving a turkey, a bike rack, and a bout of litigation. Another one of my roommates, Kirsten Ferries, was frequently a source of outside perspective and advice. Tsoline Mikaelian, a fellow Sidney and Pacific resident, was a welcome source of brainstorming and lively debate during my thesis grind at MIT.

The staff at MIT are often underappreciated but deserve the utmost credit; in my time at MIT, I've enjoyed the support, humor and advice of Marilyn Pierce, Cornelia Colyer, Anne McCarthy, Jennifer Tucker, Simone Nakhoul and Mary McDavitt.

I would like to thank those who supported my expensive tour of duty at MIT: the American Taxpayer (through the auspices of DARPA and NSF), ITRI, Intel's PhD Fellowship program, and the Michael B. Taylor Distinguished Presidential Doctoral Fellowship Program, which financed my last year of MIT tuition.

#### **Post-MIT**

At UCSD, I've also benefited from the advice and encouragement of my colleagues; Sorin Lerner and Ranjit Jhala for their discussions on gravitas; Matthias Zwicker, who sympathized on the imperfections of taxonomy, and Steve Swanson, a fellow hawker of tiled architectures. Mohammed Al-Fares, a graduate student in my CSE 240B class, implemented a class project that led the way to the collection of the 5-tuple number for the Power 4 machine. Finally, I thank my graduate students, who provide a constant source of inspiration.

#### **Major Stakeholders**

I thank all of the members of my immediate family – my mom, my dad, John, Cliff, Ingrid, Lars, and Lauren – who have all helped me through MIT in many more ways than one.

Finally, I would like to thank Karen, one of the few remaining speakers of the ancient dialect of High Taylorian, who has gone beyond the call of duty again and again and has sustained me over the years. She is one in 18, 446, 744, 073, 709, 551, 616.

MBT February 2, 2006

## Chapter 1

# Introduction

Over the last thirty-five years, microprocessor designs have constantly been re-adapted to accommodate enormous advances in the properties of integrated circuit (IC) implementation technology. The most famous of these advances, referred to as Moore's Law, is the exponential growth of the number of transistors that can be placed on an integrated circuit. In 1971, the first microprocessor, the Intel 4004, employed 2,300 transistors. In 2005, the Intel Pentium 670 used 169,000,000.

*Microprocessor scalability* refers to the ability of a microprocessor design to exploit changing technology properties to gain additional performance or energy efficiency. Over time, it has become difficult to exploit these properties and to scale microprocessor designs effectively with existing centralized microprocessor organizations. This dissertation proposes that these scalability problems can be overcome by structuring microprocessors in a *tiled* fashion. Accordingly, microprocessors structured in this way are termed *tiled microprocessors*.

This chapter motivates the approach as follows. First, it examines the many scalability problems that centralized microprocessor designs encounter as a result of growth in IC resources and the increasing importance of wire delay (Section 1.1). Second, the chapter argues that these scalability challenges can be overcome by implementing *physically scalable* microprocessors (Section 1.2). Third, the chapter introduces seven key criteria for attaining this physical scalability. Finally, the chapter details how tiled microprocessor designs fulfill the seven criteria and enable future microprocessor scalability (Section 1.3). The chapter concludes with an overview of the thesis and its contributions.

### 1.1 Emerging Issues in Microprocessor Design

### 1.1.1 VLSI Resources

Since the days of the first microprocessor, the Intel 4004, the central drive of microprocessor research has been the adaptation of microprocessor designs to improvements in semiconductor fabrication technology. The most significant of these improvements have been the exponential increases in the quantities of three types of VLSI resources: *transistors*, *wires*, and *pins*. However, with these improvements have come the negative effects of *wire delay*. This thesis will refer generally to these changes as the VLSI scaling properties.

**Transistors** The number of transistors that can be integrated onto a VLSI chip has been increasing exponentially for 40 years. This trend is referred to as Moore's Law [83]. This trend is evident in Table 1.1 which contrasts the 2,300 transistor 1971-era Intel 4004 microprocessor [55, 54, 32] against the 169,000,000 transistor 2005-era Intel Pentium 670.

| Intel              | Feature               | Transistors              | Frequency               | Pins                 | Wire           | Wire           |

|--------------------|-----------------------|--------------------------|-------------------------|----------------------|----------------|----------------|

| Microprocessor     | Size                  |                          |                         |                      | Bandwidth      | Delay (Est.)   |

|                    | (nm)                  |                          | (MHz)                   |                      | (Est., Tracks) | (clk cycle/cm) |

| 4004 (1971)        | 10000                 | 2,300                    | 0.750                   | 16                   | 190            | 1/1000         |

| Pentium 670 (2005) | 90                    | 169,000,000              | 3,800                   | 775                  | 125,000        | 4              |

| Improvement        | $\sim 100 \mathrm{x}$ | $\sim 75,000 \mathrm{x}$ | $\sim 5,000 \mathrm{x}$ | $\sim 50 \mathrm{x}$ | $\sim 660x$    | 1/4000x        |

Table 1.1: Microprocessor Properties in 1971 and in 2005

The size reduction of transistors carries with it side effects, a phenomenon that MOSFET (metaloxide-semiconductor field effect transistor) scaling theory [25, 24] attempts to elucidate for integrated circuits. The transistor size reduction brought on by each successive process generation<sup>1</sup> brings proportionally lower delay and smaller power consumption per transistor; however, it also presents a greater burden of difficulty in designing the circuits that exploit these properties. Table 1.1 shows the great improvement in frequency of the Pentium 670 versus the Intel 4004. A significant portion of this (100x out of 5000x) comes from the lower delay due to transistor scaling.

Wires and Pins Of course, VLSI (very large scale integration) chips do not include just transistors; they include *wires*, for connecting the transistors within the chip, and *pins*, for connecting the integrated circuit to the outside world. The quantity of these resources available to the microprocessor designer have also increased substantially over the years. The pin-count increase for microprocessors is also evident in Table 1.1.

Wire Delay One of the properties which has not improved as favorably with successive process generations has been wire delay [13, 79]. Wire delay has stayed mostly constant (in  $\frac{cm}{s}$ , for instance) across process generations. Historically, wires were so fast relative to transistors that they appeared to provide an almost instantaneous connection between their endpoints. Unfortunately, as transistor frequencies have improved with each process generation, the relative speed of the wires (measured in terms of transistor delay) has worsened exponentially. While they once barely impacted processor

<sup>&</sup>lt;sup>1</sup>The semiconductor industry tries to scale the minimum feature size of transistors by approximately .7 every two to three years. The term *process generation* is used to refer to the group of VLSI parameters that is employed to create integrated circuits of a given minimum feature size.

operating frequencies, wires now consume a significant fraction of the cycle time in the critical paths of current microprocessors. Wire delay has become a central concern for microprocessor designers [2], and significant effort has been expended by the semiconductor community to mitigates its effect through better materials (such as copper wires and low-K dielectrics) and better computer aided design (CAD) tools. There is evidence that wire delay will worsen in coming process generations because of complications in manufacturing wires [45], and because the wires are becoming small relative to the mean-free path of electrons in conductors.

### 1.1.2 Putting VLSI Resources to Use

The exponentially increasing availability of transistors, pins and wires according to VLSI scaling drives us to create microprocessors that put these resources to effective use.

In the early days of microprocessor design, many of these additional resources were expended to make microprocessors more usable; for instance, extending datapaths to accommodate reasonable address and data widths, adding floating points units to facilitate scientific calculation, and incorporating operating system protection mechanisms. Today, relatively few transistors are expended on improving microprocessor usability. Architects, recognizing that many features are better left implemented in C than in silicon, have focused on expending these additional resources to improve performance.

This focus led to the incorporation of microarchitectural innovations which exist only for performance reasons, such as caching, dynamic branch predictors, pipelining, wider memory interfaces, and superscalar and out-of-order execution. These microarchitectural approaches have the positive aspect that they improve performance without exposing to the programmer or compiler the fact that the microprocessor is utilizing exponentially more resources.

### 1.1.3 Problems with Addressing Scalability through Microarchitecture

Unfortunately, addressing scalability solely through microarchitectural mechanisms has led to a number of problems:

**Problem 1. Diminishing Performance Returns on VLSI Resources** Microarchitectural approaches have reached the point of diminishing returns. Today's wide-issue microprocessor designers have found it increasingly difficult to convert burgeoning silicon resources into usable, general-purpose functional units. The percentage of transistors that are performing actual programmer-specified computation has been steadily declining in successive versions of these modern designs. An extreme example of this can be found by comparing the 2004-era Intel 32-bit Xeon 4M to the 1989-era 32-bit Intel 80486. The Xeon has 238 times more transistors than the 80486 [51] but can sustain only three general purpose operations per cycle versus the 80486's one operation per cycle.

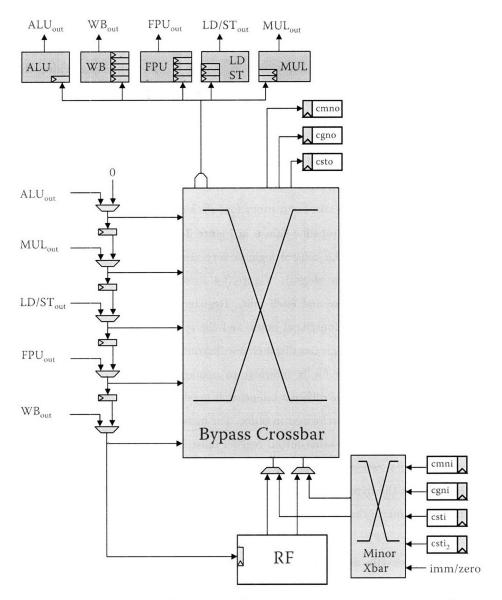

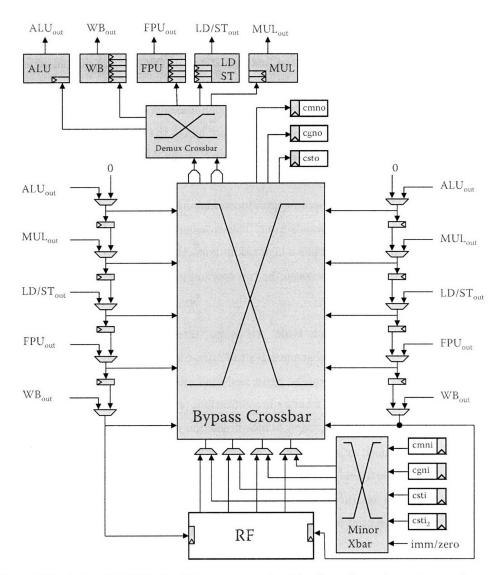

At the root of these difficulties are the centralized structures responsible for orchestrating operands between the functional units. These structures grow in size much faster asymptotically than the number of functional units. The prospect of microprocessor designs for which functional units occupy a disappearing fraction of total area is unappealing but tolerable. Even more serious is the poor frequency-scalability of these designs; that is, the unmanageable increase in logic and wire delay as these microprocessor structures grow [2, 92, 91, 121]. A case in point is the Itanium 2 processor, which sports a zero-cycle fully-bypassed 6-way issue integer execution core. Despite occupying less than two percent of the processor die, this unit spends half of its critical path in the bypass paths between the ALUS [85].

Scalability issues in microprocessors extend beyond the components responsible for functional unit bypassing. Contemporary processor designs typically contain unscalable, global, centralized structures such as fetch units, multi-ported register files, load-store queues, and reorder buffers. Furthermore, future scalability problems lurk in many of the components of the processor responsible for naming, scheduling, orchestrating and routing operands between functional units [92].

**Problem 2.** Large and Growing Design and Validation Effort Microarchitectural approaches to scalability have led to exponentially increasing design complexity. Intel's Pentium 4 required on the order of 500 people to design, and consisted of over 1 million lines of RTL code [12]. Of those people, 70 worked on verification. 7,855 bugs were found in the design before silicon and 101 errata were detected in the released product [11]. The number of pre-silicon bugs has approximately tripled for each of the last three significant microarchitectural revisions of the Intel IA32 architecture (from Pentium to Pentium Pro to Pentium 4) [97]. Correspondingly, the number of post-silicon errata continues to rise with each major release [49, 52, 53], despite advances in verification methodology and the use of larger verification groups.

**Problem 3. Low Power Efficiency** Microprocessor designers have recently found that the rising thermal dissipation of high performance microprocessors has affected these systems' applicability even in non-mobile environments. High thermal dissipation delayed the introduction of early Itanium II and Pentium 4 processors in dual-processor 1U rack-mount configurations. Heat production also affects the cost of these systems: the price of an appropriate cooling solution increases drastically with rising microprocessor temperatures. These power concerns led the Pentium 4 architects to include a thermal monitor and a mechanism to stop the processor's clock in order to prevent overheating [39].

Current wide-issue superscalar processor designs use large, centralized microarchitectural structures to extract parallelism from serial instruction streams. These microarchitecture features are inherently energy-inefficient because they add overhead to the execution of every instruction. Furthermore, these designs have undesireable power density properties – because they tend to cluster like components together (such as the execution units), which causes high power consumption components to be situated near to each other. Complex microarchitectures also prove a difficult challenge for energy optimization through clock-gating because they consist of many interdependent components, each of which must be examined carefully to determine the cases in which the component is not required for correct operation. Additionally, in cases where large structures, such as multiported register files or instruction scheduling windows are not being fully used, it adds significant complexity to add the ability to "partially" shut them off. Finally, because superscalar processors do not exploit parallelism efficiently and scalably, they are not well-equiped to save power by trading off frequency (and thus voltage and energy through voltage-scaling) with parallelism.

**Problem 4. Lack of Performance Transparency** The increase in microarchitectural complexity has resulted in the loss of *performance transparency* which confounds the ability of the programmer or compiler to generate code that runs efficiently on a microprocessor. Unlike in the past, the execution time (and order) of a program on modern-day microprocessors cannot be determined simply from instructions and their register dependences. One of the biggest culprits has been the introduction of various forms of hidden state in the processor, such as reorder buffers, dynamic branch predictors, way predictors, memory dependence predictors, branch target buffers, prefetch engines, and hierarchical TLBs. This state can significantly impact performance, and in general, may be left as a trade secret by the designers. To the end goal of overcoming these transparency problems, Intel has written an optimization guide for the Pentium 4 [50]. Even at 331 pages, the guide is incomplete; for instance, it fails to mention the presence of the P4's L1 data cache way-predictor [15] and its related performance effects.

In fact, the performance of applications is so much an emergent property that the Pentium 4 underwent a late revision that introduced an infrequently-invoked *cautious mode*, which overrides one of the predictors in order to address a performance problem on an important Windows application. This problem only manifested itself on 2 other traces out of 2200 [15]. Of course, these transparency problems are not limited to the Pentium 4; however due to its high profile, more data has emerged. A recent MIT thesis [69] noted a number of similar performance transparency issues in the Ultrasparc.

**Problem 5. Limited Design Adaptivity** One desirable characteristic of a microprocessor design is that it be easy to modify to accommodate different levels of VLSI resources and different operating constraints. This allows the design to target a greater market, which helps amortize the large initial design cost. Current microprocessor designs are relatively fixed for a given amount of VLSI resources. For instance, it is typically extremely difficult to add more general purpose functional units to a given microprocessor design. Because current microprocessor designs are not easily changed to more and fewer resources, they can not be easily adapted for use in other operating environments with different cost, power and size budgets. For example, most desktop superscalar designs like the Pentium 4 could not be made suitable for use in the MP3, handheld or mobile

telphone market. Even when these designs are deployed in the server and laptop markets, adaptations are limited, for instance, to cache configurations, bus interfaces and sleep functionality.

Furthermore, the complexity of these designs makes them brittle to technology changes. For instance, Intel had to write off its investment in the Pentium 4 architecture far earlier than planned because of the emerging energy limitations of the latest VLSI process generations.

### 1.2 Addressing Scalability through Physically Scalable Microprocessor Designs

This thesis examines the idea of using a *physically scalable microprocessor* design to overcome these five problems. A physically scalable microprocessor is one that can be modified in a straightforward manner to accommodate more or fewer underlying VLSI resources (such as transistors, wires, and pins), thereby providing proportionally more or fewer gainfully employable computational resources to the user. Such a design would address the problems described in the previous section. It solves Problems 2 (design and verification complexity) and 5 (design adaptivity) because it by definition can be easily modified to accommodate different levels of resources. It solves Problems 1 (diminishing returns) and 3 (power efficiency) because it provides usable processing resources proportional to the underlying resources. Finally, Problem 4 (performance transparency) can be addressed if VLSI resources are exposed through programmer-visible architectural structures rather than through hidden microarchitectural mechanisms.

### 1.2.1 Seven Criteria for a Physically Scalable Microprocessor Design

What properties would a physically scalable microprocessor design have? Surprisingly, a physically scalable microprocessor combines elements of existing microprocessor designs with elements traditionally found in scalable multiprocessor systems. In a sense, scalable microprocessors generalize existing microprocessors by incorporating multiprocessor design principles. Inherited from microprocessors is the concept that scalable microprocessors should be optimized for the communication of scalar values between the computational logic elements, or ALUs, and that they need to support traditional mechanisms such as interrupts, branches, and caching. At the same time, these scalable microprocessors must, like multiprocessors, be *frequency scalable* and *bandwidth scalable*, and manage exceptional conditions such as *deadlock and starvation* that arise from being implemented in a distributed fashion. We would also like them to offer *usage-proportional resource latencies* and to support the *exploitation of locality*. These properties ("The Seven Criteria For Physical Scalability") are discussed next.

**CRITERION 1 ("C1"): Frequency Scalability** Frequency scalability describes the ability of a design to maintain high clock frequencies as the design is adapted to leverage more VLSI

resources. In other words, we do not want the frequencies of these designs to drop as they get bigger. When an unpipelined, two-dimensional VLSI structure increases in area, speed of light limitations dictate that the propagation delay of this structure must increase asymptotically at least as fast as the square root of the area. More practically speaking, the increase in delay is due to both increased interconnect<sup>2</sup> delay and increased logic levels. If we want to build larger structures and still maintain high frequencies, a physically scalable design must pipeline the circuits and turn the propagation delay into pipeline latency. Scalability in this context thus refers to both individual components ("intra-component") and to collections of components ("inter-component") within a microprocessor.

Intra-component frequency scalability As the issue width of a microprocessor increases, monolithic structures such as multi-ported register files, bypassing logic, selection logic, and wakeup logic grow linearly to cubically in size. Although extremely efficient VLSI implementations of these components exist, their burgeoning size guarantees that intra-component interconnect delay will inevitably slow them down. Put another way, these components have an asymptotically unfavorable growth function that is partially obscured by a favorable constant factor. As a result, physically scalable microprocessors cannot contain monolothic, unregistered components that grow in size as the system scales. The Itanium 2 is an example of a microprocessor that is pushing the limits of frequency scalability: it has twice the number of general-purpose functional units as the Pentium 4 but the cycle-time is twice as great.

Inter-component frequency scalability Frequency scalability is a problem not just within components, but between components. Components that are separated by even a relatively small distance are affected by the substantial wire delays of modern VLSI processes. This inherent delay in interconnect is a central issue in multiprocessor designs and is now becoming a central issue in microprocessor designs. Two recent examples of commercial architectures addressing inter-component delay are the Pentium IV, which introduced two pipeline stages that are dedicated to the crossing of long wires between remote components; and the Alpha 21264, which has a one cycle latency cost for results from one integer cluster to be used by the other cluster. Once interconnect delay becomes significant, high-frequency systems must be designed out of components that operate with only partial knowledge of what the rest of the system is doing. In other words, physically scalable microprocessors need to be implemented as a collection of distributed processes. If a component depends on information that is not generated by a neighboring component, the architecture needs to assign a time cost for the transfer of this information. Non-local information includes the outputs of physically remote ALUs, stall signals, branch mispredicts, exceptions, and the existence of memory dependencies.

CRITERION 2 ("C2"): Bandwidth Scalability While many frequency scalability problems

$<sup>^{2}</sup>$ We use this term loosely to refer to the set of wires, buffers, multiplexers and other logic responsible for the routing of signals within a circuit.

can be addressed by distributing centralized structures and pipelining paths between distant components, there remains a subclass of scalability problems which are fundamentally linked to a microprocessor's underlying architectural algorithms. These *bandwidth scalability* problems occur when the amount of information that needs to be transmitted and processed grows disproportionately with the size of the system.

Physically scalable microprocessors inherit the bandwidth scalability challenge from multiprocessor designs. One key indicator of a non-bandwidth scalable architecture is the use of broadcasts that are not directly mandated by the computation. For example, superscalars often rely on global broadcasts to communicate the results of instructions to consuming reservation stations. Because every functional unit's result must be processed by every reservation station, the demands on an individual reservation station grow as the system scales. Although, like the Alpha 21264, superscalars can be pipelined and partitioned to improve frequency scalability, this is not sufficient to overcome the substantial area, latency and energy penalties due to poor bandwidth scalability.

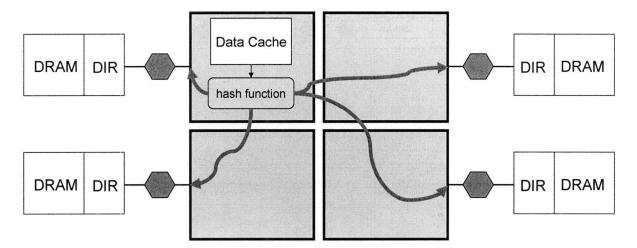

To overcome this problem, physically scalable microprocessors must employ a method of decimating the volume of messages sent in the system. Directory-based cache-coherent multiprocessors provide insight into a potential solution to this problem: employing directories to eliminate the broadcast inherent in snooping cache systems. Directories are distributed, known-ahead-of-time locations that contain dependence information. The directories allow the caches to reduce the broadcast to a unicast or multicast to only the parties that need the information. The resulting reduction in necessary bandwidth allows the broadcast network to be replaced with a point-to-point network of lesser bisection bandwidth<sup>3</sup>.

A directory scheme is one candidate for replacing broadcasts in a scalable microprocessor's SON and achieving bandwidth scalability. The source instructions can look up destination instructions in a directory and then multicast output values to the nodes on which the destination instructions reside. In order to be bandwidth scalable, such a directory must be implemented in a distributed, decentralized fashion. This thesis will show one such implementation, and examines some alternatives.

**CRITERION 3 ("C3"): Usage-Proportional Resource Latencies** The ability to provide usage-proportional resource latencies is a subtle but fundamental criteria for physically scalable microprocessors. Architectures with *usage-proportional resource latencies* offer inter-resource latencies that are proportional to the amount of resources used in a computation rather than the total quantity of resources in the system. Without this property, as the design is scaled up, existing programs with small amounts of parallelism would slow down due to increased latencies. More generally, this

$<sup>^{3}</sup>$ We define bisection bandwidths with a sequence of definitions. First, a *cut* of the network is a separation of the nodes of the network into two equal sized groups. The *min cut* is the cut which minimizes the sum of the edge weights of edges that connect the two groups. Finally, the *bisection bandwidth* is the edge weight sum corresponding to the min cut of network graph in which the edges weights correspond to the bandwidths of individual links.

criteria allows the compiler to make tradeoffs between using fewer resources at a lower average latency (e.g., a subset of the machine), or greater numbers of resources at a higher average latency. In general, dancehall-style resource topologies cannot provide usage-proportional resource latencies, while those with recursively substructured (such as trees or meshes) resource topologies are more easily able to.

**CRITERION 4 ("C4"): Exploitation of Locality** In addition to providing usage-proportional resource latencies, physically scalable architectures should connect resources via interconnect which offers communication latencies that reflect the underlying physical communication costs (i.e., wire delay) in the implementation substrate. To complement these networks, physically scalable microprocessors must provide architectural mechanisms that allow the program to exploit positional<sup>4</sup> locality between the program's virtual objects (e.g., data, instructions, operations, operands) in order to minimize latency and transport occupancy. Hardware or software mechanisms must be provided to enable related objects (e.g., communicating instructions) to be placed close together in order to avoid paying worst-case costs for communication.

**CRITERION 5 ("C5"): Efficient Inter-node Operation-Operand Matching** The most fundamental criteria for any microprocessor is that it perform *operation-operand matching*. Operationoperand matching is the process of gathering operands and operations to meet at some point in space to perform the desired computation. In the context of a physically scalable microprocessor, *operationoperand matching* must be performed across distributed ALUs, which can be more challenging than for standard centralized designs.

Efficient inter-node operation-operand matching is what distinguishes a physically scalable microprocessor from other types of distributed systems, such as multiprocessors, which have relatively high overheads for inter-node operation-operand matching.

This thesis introduces the term *scalar operand network* ("SON") to refer to the set of mechanisms in a microprocessor that implement operation-operand matching. These mechanisms include the physical interconnection network used to transport the operands (referred to as the *transport network*) as well as the operation-operand matching system (hardware or software) which coordinates these values into a coherent computation. This choice of definition parallels the use of the word "Internet" to include both the physical links and the protocols that control the flow of data on these links.

SONs have evolved as microprocessors have evolved – from early, monolithic register file interconnects to more recent ones that incorporate point-to-point mesh interconnects. Section 2.4.1 examines this evolution in detail.

This thesis examines SONs in depth, as they are the central component of any physically scalable

$<sup>{}^{4}</sup>$ I would use the term spatial locality, but the semantic nuances of the term (as currently employed in the context of caches) are different.

microprocessor.

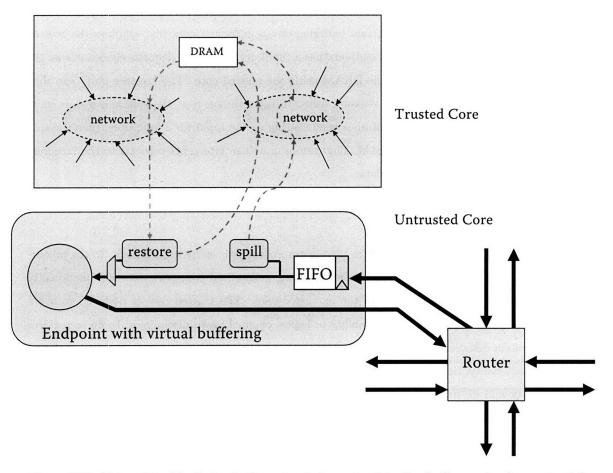

**CRITERION 6 ("C6"): Deadlock and Starvation Management** Superscalar SONs use relatively centralized structures to flow-control instructions and operands so that internal buffering cannot be overcommitted. With less centralized SONs, such global knowledge is more difficult to attain. If the processing elements independently produce more values than the SON has storage space, then either data loss or deadlock must occur [29, 102]. This problem is not unusual; in fact some of the earliest large-scale SON research – the dataflow machines – encountered serious problems with the overcommitment of storage space and resultant deadlock [6]. Alternatively, priorities in the operand network may lead to a lack of fairness in the execution of instructions, which may severely impact performance. Transport-related deadlock can be roughly divided into two categories; endpoint deadlock, resulting from a lack of storage at the endpoints of messages, and in-network deadlock, which is deadlock inside the transport network itself. Because effective solutions for innetwork deadlock have already been proposed in the literature, endpoint deadlock is of greater concern for SONs.

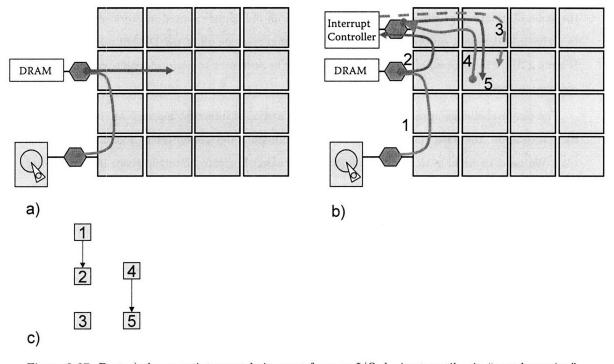

**CRITERION 7 ("C7"): Support for Exceptional Events** Exceptional events, despite not being the common case, play a prominent role in microprocessor design. The introduction of new architectural mechanisms, such as those likely to be found in physically scalable microprocessor designs, will carry with them the need to devise strategies for handling these exceptional events. Microprocessors of all types must be able to support events like cache misses, interrupts, memory dependencies, branch mispredictions, and context switches. The design of these items is a challenging task for any microprocessor, but is especially challenging for physically scalable microprocessors due to the necessity that they be implemented in a distributed manner.

### **1.3 Tiled Microprocessors:**

### A Class of Physically Scalable Microprocessor

How do we design physically scalable microprocessors? In this thesis, we examine *tiled microprocessors*, which are microprocessors that have the property of being physically scalable by construction. The central idea is to compose the microprocessor out of three core architectural entities – *tiles*, *networks*, and I/O ports – which are in correspondence with the three classes of VLSI resources described in Section 1.1.1: transistors, wires and pins. This correspondence is shown in Table 1.2. The computation and storage abilities of on-chip transistors are exposed through the tile abstraction. The communication capabilities of on-chip wires are exposed through the network abstraction. Finally, pin connections to the off-chip world are exposed through the I/O port abstraction.

Each tile occupies a rectangular region of the silicon area and is sized so that its width and

| VLSI Resource | Architectural Entity |

|---------------|----------------------|

| Gates         | Tiles                |

| Wires         | Networks             |

| Pins          | I/O Ports            |

Table 1.2: Correspondence of VLSI resources and architectural entities in Tiled Microprocessors

height are approximately the distance that a signal can travel in a single cycle. In addition to computational resources, a tile contains an incremental portion of the network – the network links that connect to the nearby neighbors and the router that controls those links. These point-to-point, pipelined on-chip network links contain at least one register between neighbor tiles. The I/O ports are connected to the periphery of the network.

Systems are scaled up or down by changing the number of tiles and I/O ports in accordance with the amount of die array and the number pins available, rather than by changing the contents of the tiles themselves. A latency, proportional to the distance between tiles, is assigned for communication between tiles.

### 1.3.1 Tiled Microprocessors Meet the Physical Scalability Criteria

We develop the definition of a tiled microprocessor by examining how they fulfill the seven criteria of physical scalability:

- 1. Frequency Scalability Tiled microprocessors meet the frequency scalability criteria because they do not have wires or structures that grow in size as the system is scaled up. In particular, because network wires are registered at tile boundaries, we know that wire lengths in the system do not grow as the system is scaled up by adding more tiles.

- 2. Bandwidth Scalability Tiled microprocessors implement all inter-tile networks using pointto-point rather than broadcast networks. Furthermore, all protocols implemented on these networks will be implemented using point-to-point communication patterns rather than broadcast. This includes protocols for performing both operation-operand matching as well as those that manage memory accesses and control operations. This way network congestion and latency will be solely a function of the computation being performed and not the number of tiles in the system.

- 3. **Proportional (non-uniform) Resource Latency** Tiled microprocessors are implemented with point-to-point networks that have latencies proportional to the distances between tiles. Furthermore, the programmer has the choice of determining how many tiles will be used to implement the computation. Thus, as microprocessors with more resources become available, the option still remains to use fewer tiles in order to minimize latency.

- 4. Exploitation of Locality Tiled microprocessors provide architectural interfaces for software and hardware mechanisms to control the placement of instructions, data objects, and I/O connections so that communication in the system can be localized.

- 5. Efficient Inter-node Operation-Operand Matching Of course, in order to be a microprocessor at all, the functional units have to be connected by a scalar operand network. Tiled microprocessors contain a scalar operand network that performs operation-operand matching both within and between all tiles<sup>5</sup>.

- 6. Deadlock and starvation management Tiled microprocessors, like the greater class of physically scalable microprocessors, must handle deadlock and starvation inside tiles and in all inter-tile networks, such as the SON. Later sections of this dissertation will describe some ways that tiled microprocessors can attain this.

- 7. Support for Exceptional Events Tiled microprocessors implement the same class of functionality as conventional microprocessors, such as interrupts, memory requests, branches and context switches. This requirement extends to functionality implemented over the inter-tile networks, e.g. the tiled microprocessor must be able to context switch even in the presence of inter-tile network traffic.

### 1.3.2 Tiled Microprocessors Overcome Microarchitectural Scalability Limitations

Tiled microprocessors overcome the limitations inherent in modern-day microprocessors that attempt to employ the microarchitectural approach to scalability. We examine in turn each of the issues discussed in Section 1.1.3 ("Problems with addressing scalability through microarchitecture"):

- a. Proportional returns on VLSI resources Tiled microprocessors expose transistor resources through a proportional number of tiles. They expose the VLSI wiring resources through the on-chip networks. Finally, they expose the VLSI pin resources via the I/O port abstraction. These tiles, networks and I/O ports are in turn exposed to the programmer, providing proportional programmable resources.

- b. Constant Design and Validation Effort Because systems are built by replicating the same basic tile and I/O port design, the system require only marginally more design and validation effort as more VLSI resources are employed.

- c. **Power Efficiency** Tiled systems are easy to optimize for power and are inherently powerefficient. First, tiling provides an easy way to power down portions of the chip when they

$<sup>{}^{5}</sup>$ In this thesis, we examine a system that is composed of only one type of tile, however we do not preclude the possibility of having a heterogeneous tiled system composed out of multiple types of tiles.

are unneeded [62]. For instance, individual tiles can be powered down by gating the clock coming into the tile. Second, tiled systems can easily implement frequency and voltage scaling to tradeoff parallelism for energy because they can exploit parallelism with little overhead. Third, because tiles do not grow in complexity as the system scales, the designer only has to optimize the power consumption of a single tile and the power gains will be realized across all of the tiles and thus throughout the microprocessor. Furthermore, because the processing resources available to the programmer are proportional to the underlying amount of VLSI resources, i.e., because the system overhead does not grow as more ALUs are added, the system does not experience the same declining efficiency found in successive generations of modern-day microprocessors. Finally, tiled systems can be implemented with short wires and simple, fixed-sized VLSI structures which makes them inherently power-efficient.

- d. **Performance Transparency** Since the central way in which the processor transforms VLSI resources into improved performance is exposed to the programmer via the number of tiles available, the user has a clear picture of the performance model. Furthermore tiles tend to be simple, because the mechanism for improving successive generations of processors is not through adding microarchitectural mechanisms, but by adding tiles.

- e. Design Adaptivity Tiled microprocessors are eminently design adaptable, because the designer can easily vary the number of tiles to accommodate different operating environments. Furthermore, because the system is composed out of a replicated element, it is easy to adapt tiled systems to new technology parameters simply design a new tile, and the rest of the system is a few copy commands away.

### 1.3.3 The Raw Tiled Microprocessor Prototype

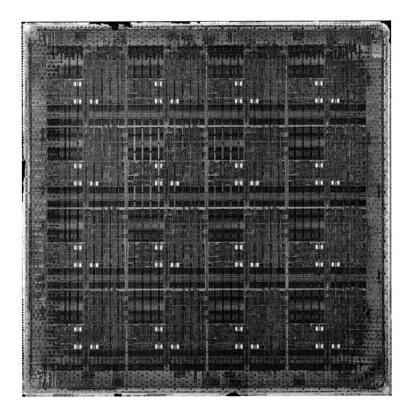

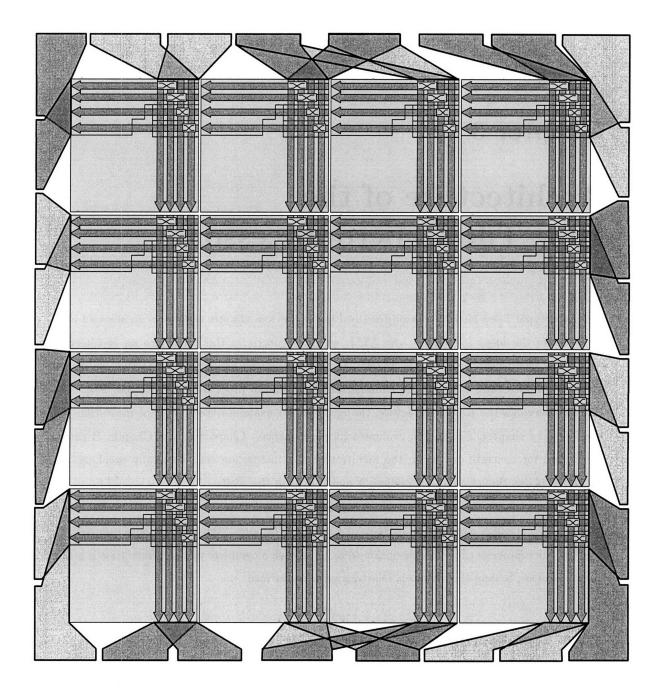

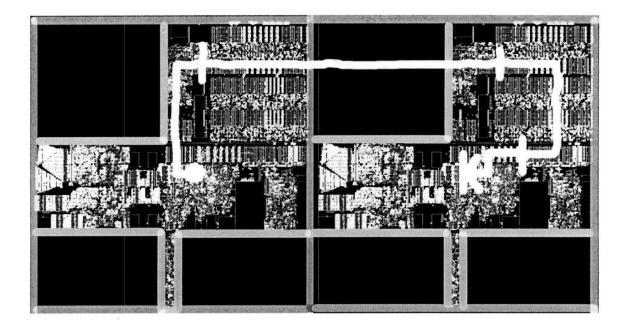

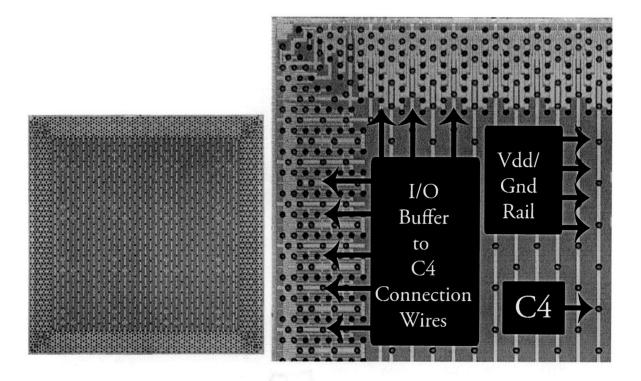

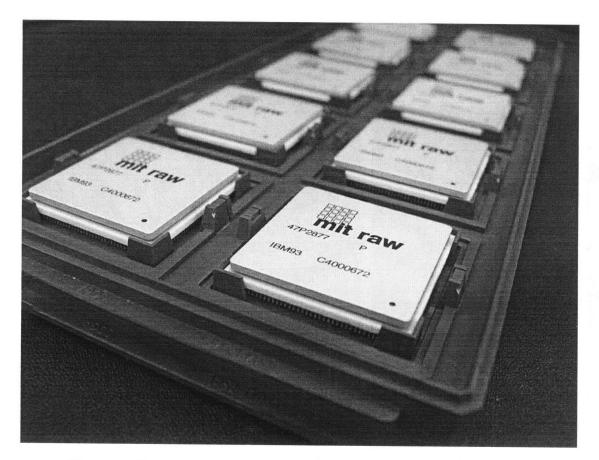

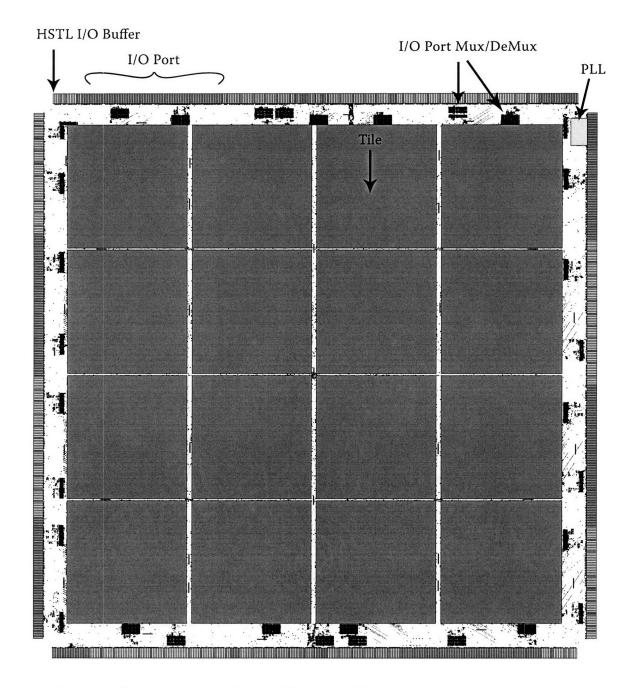

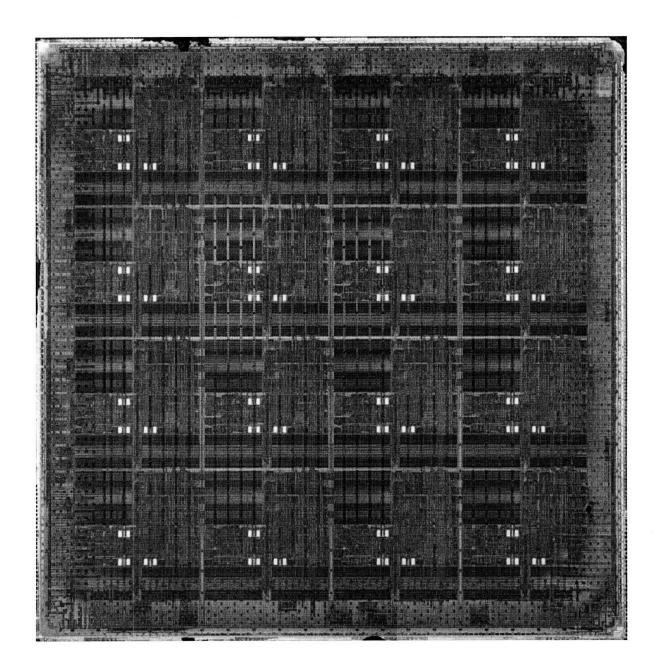

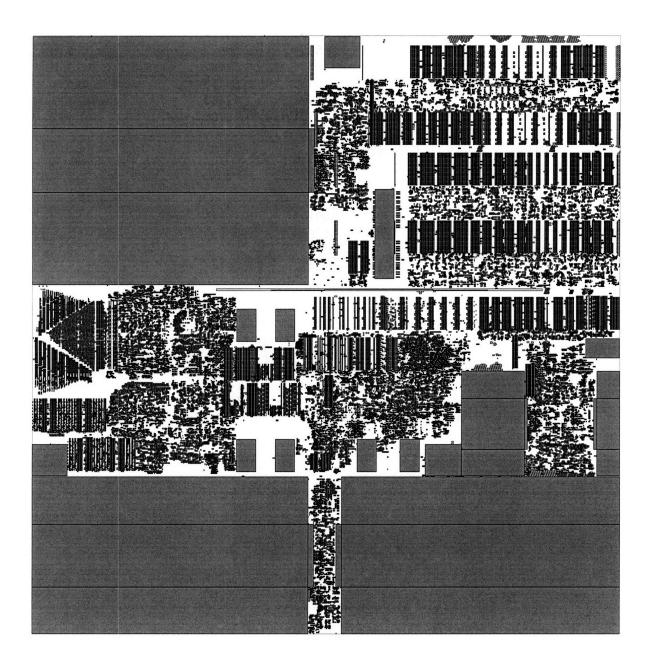

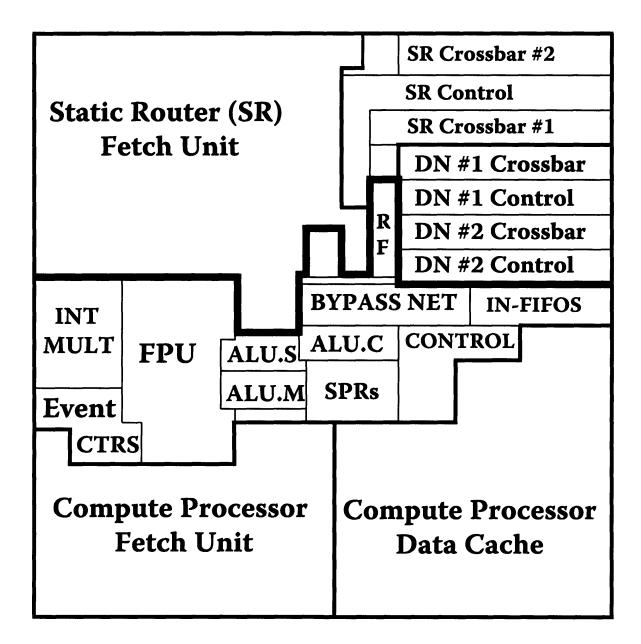

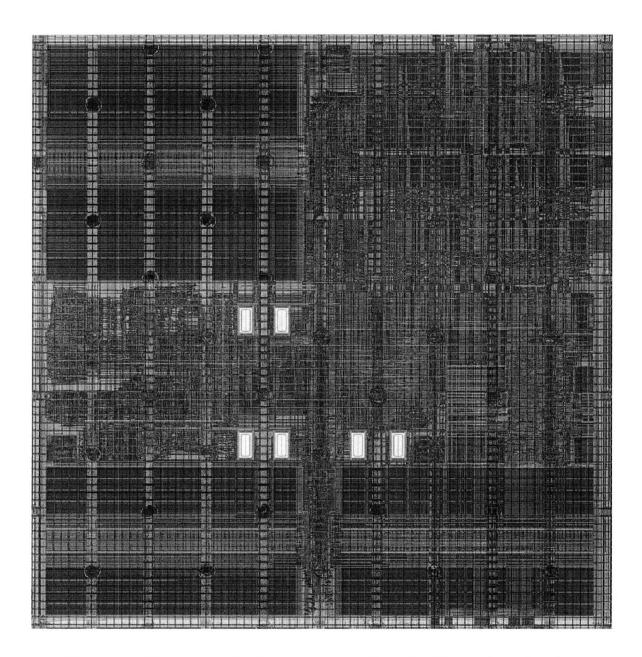

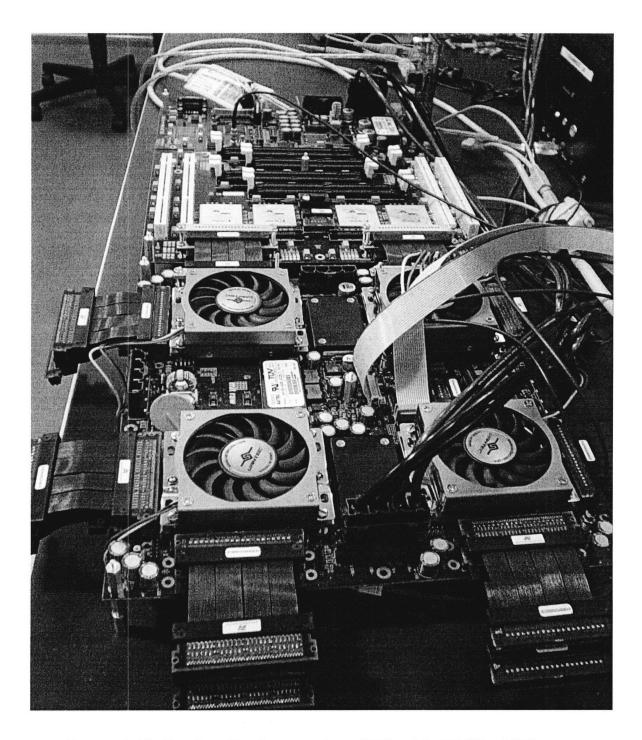

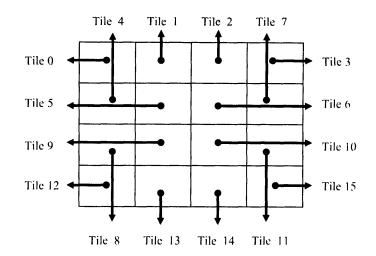

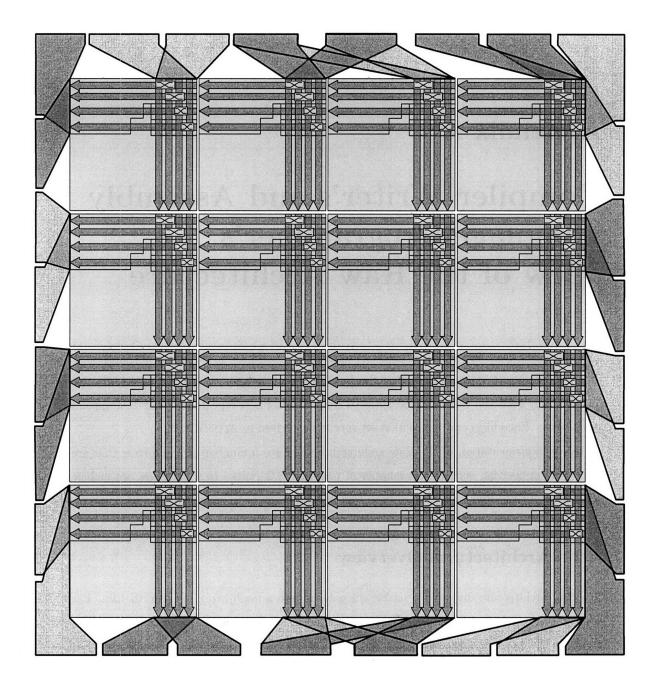

In order to investigate tiled microprocessors further, we designed and built a full tiled microprocessor prototype in 180 nm technology. We call this microprocessor the Raw microprocessor, in reference to the direct correspondence between VLSI resources and architectural entities in the architecture. A photomicrograph of the Raw microprocessor is shown in Figure 1-1. The 330  $mm^2$  chip attains 16-issue, greater than any Intel microprocessor in the same process generation.

### 1.3.4 Contributions

The contributions of this thesis (and the underlying research) focus around the formulation, formalization, and evaluation of tiled microprocessors as a way of attaining physically scalable microprocessors. To this end, the thesis proposes and examines seven criteria for physical scalability in microprocessor designs. It uses the ATM, an archetypal tiled microprocessor, to illustrate the design considerations that arise in realizing the seven criteria. One of these criteria leads to the introduction

Figure 1-1: Photomicrograph of the scalable 16-tile Raw microprocessor.

and formalization of a new class of network, Scalar Operand Networks, which are the core communication mechanism inside scalable microprocessors. Finally, the thesis describes and evaluates a complete 180 nm prototype tiled microprocessor implementation, the Raw microprocessor.

### 1.3.5 Thesis Overview

This thesis continues as follows. Chapter 2 employs an archetypal tiled microprocessor, labeled the Archetypal Tiled Microprocessor, to explore the key issues in designing tiled microprocessors. Chapter 3 and Appendices A and B describe the Raw architecture, a concrete tiled microprocessor implementation. Chapter 4 examines the Raw prototype and Raw VLSI implementation. Chapter 5 evaluates the Raw prototype and describes the various programming systems that were designed at MIT to program it. Chapter 6 examines related work, and Chapter 7 concludes.

## Chapter 2

# The Archetypal Tiled Microprocessor

In the introduction, we discussed the favorable characteristics of a tiled microprocessor. However, concretely, what are the essential architectural components of a tiled microprocessor? How does a tiled microprocessor function? In what ways is a tiled microprocessor different than conventional microprocessors? How does the tiled microprocessor address the seven criteria for physically scalable microprocessors discussed in Section 1.2.1? These are the questions which this chapter addresses.

In order to do this, we discuss a prototypical tiled microprocessor which we call the *Archety*pal Tiled Microprocessor, or ATM. As with the Raw prototype, the ATM has the essential characteristics that we would expect of a tiled microprocessor; however, at the same time, it allows us to abstract away from the nitty-gritty characteristics which may vary from design to design. It also allows us to generalize some of the findings that resulted from our experience with the Raw prototype.

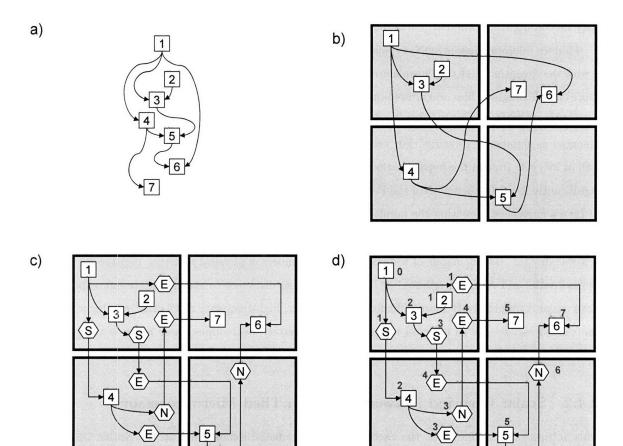

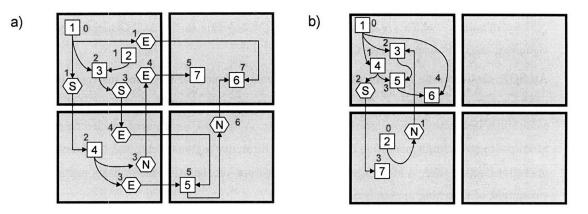

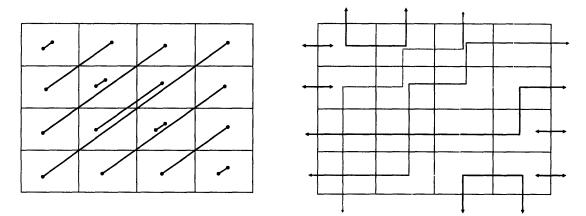

### 2.1 Basic Elements of a Tiled Microprocessor

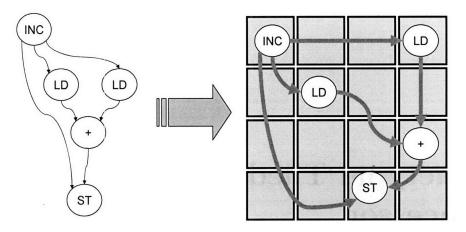

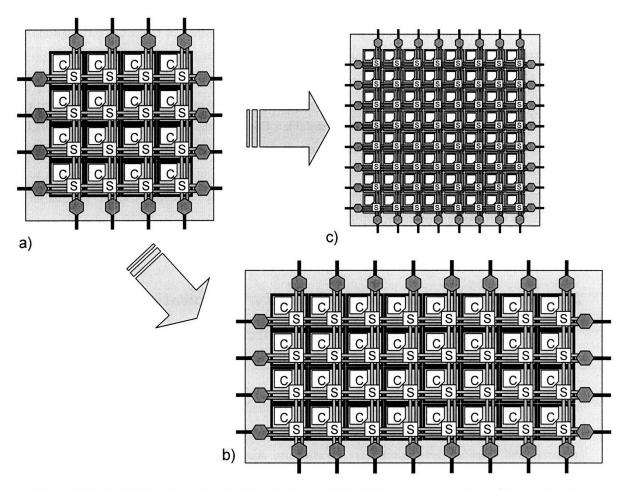

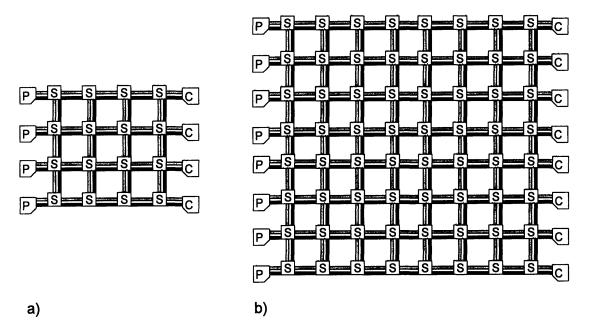

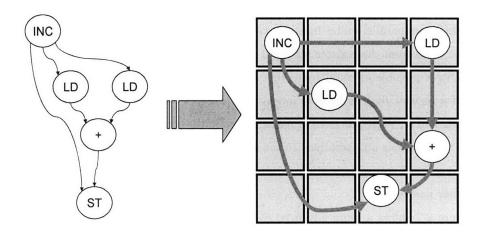

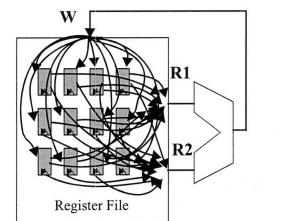

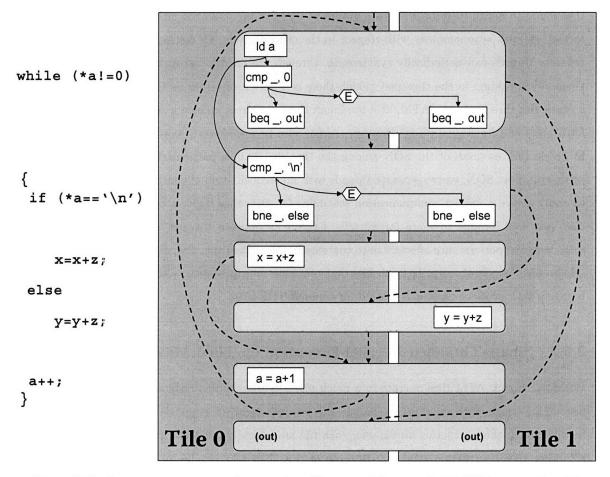

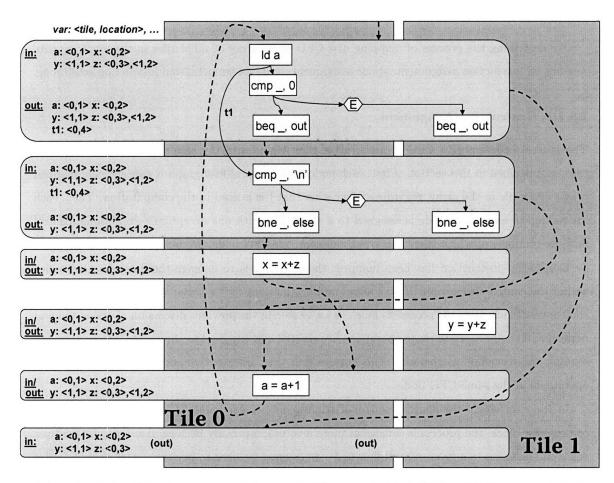

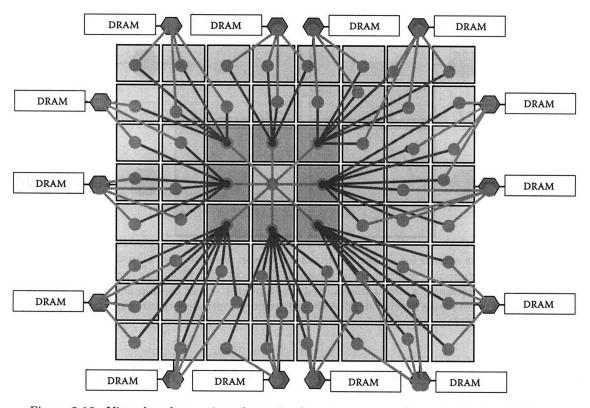

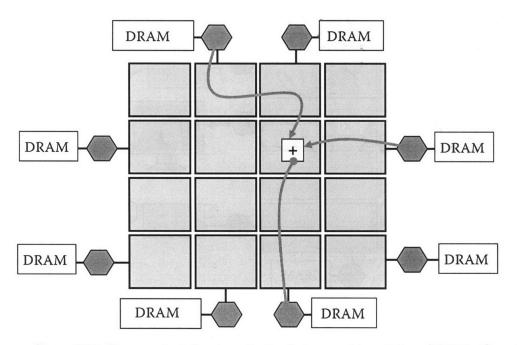

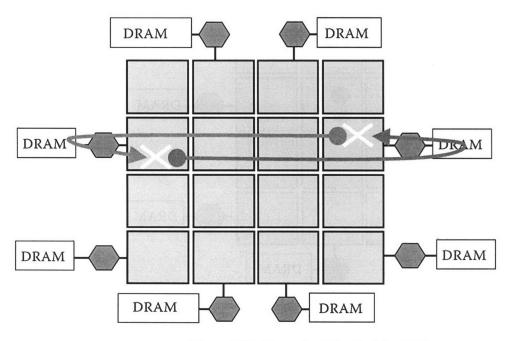

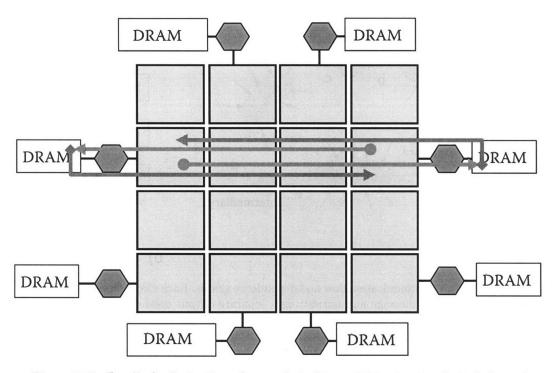

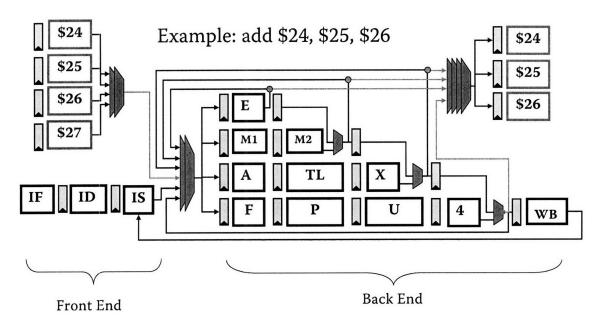

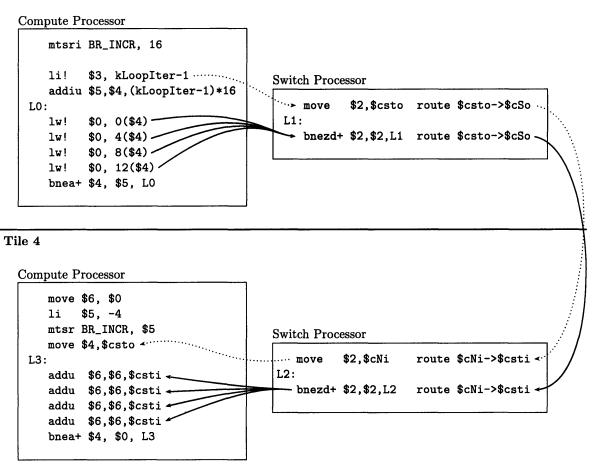

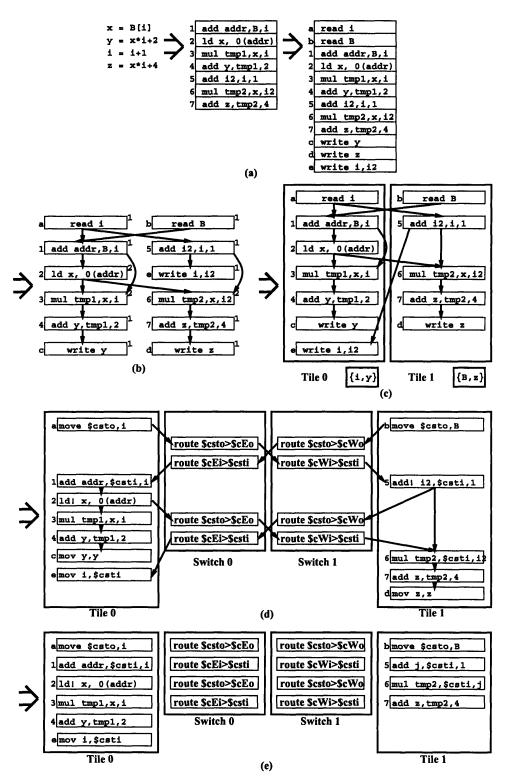

Fundamentally, the purpose of a tiled microprocessor is to execute programs in a parallel fashion. To do this, tiled microprocessors are comprised of an array of *tiles*. Each tile contains a number of functional units. Using their functional units, the tiles work together to collectively execute the instructions of a single program. The basic idea is to take the individual instructions of a program and assign them to different tiles, so that they can execute in parallel. Figure 2-1 shows an example program sequence and the mapping of instructions to an array of tiles.

Given a mapping of instructions to different tiles, tiled microprocessors must provide a way to transport the outputs of an instruction to the inputs of one or more dependent instructions. For this purpose, tiled microprocessors employ a class of on-chip networks called *scalar operand networks* ("SON") that is specialized for exactly this purpose. We call them scalar operand networks because

Figure 2-1: The goal of a tiled microprocessor: parallel execution of a program's instructions across an array of tiles. The figure depicts a program graph being mapped to an array of tiles.

they are a type of network optimized for transporting scalar operands between physically distributed functional units.

Furthermore, we want these tiles to operate autonomously; so a tile will contain a fetch unit that sequences a unique program counter ("PC") through an instruction stream. Tiles will also contain a data and instruction cache so that they can take advantage of instruction and data locality much like conventional microprocessors.

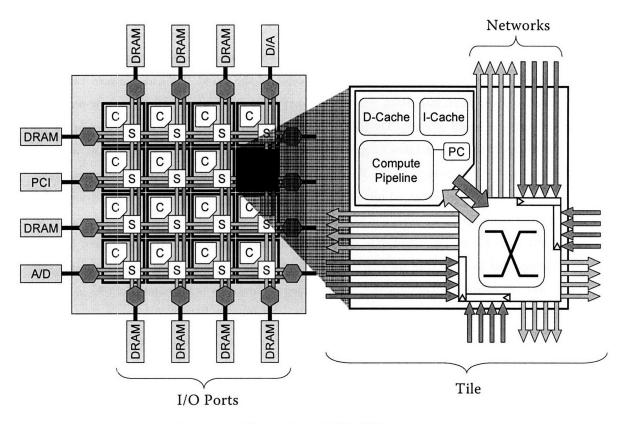

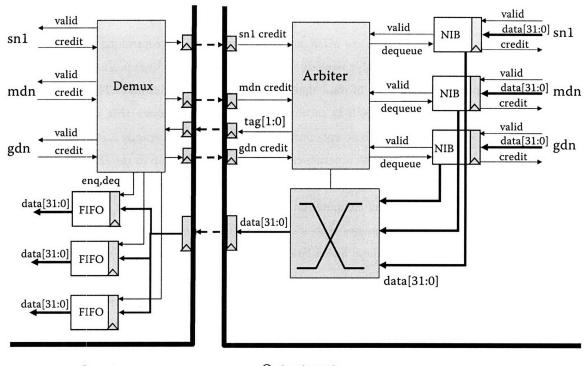

Finally, programs need to have inputs; and the instruction and data caches need to be backed by a larger pool of memory. For this purpose, we add two components. First, we will add a class of on-chip networks that is intended for generalized data transport, including cache misses. The tiles can use these networks to communicate between each other (for instance, to share their cache memory) and with the outside world; we'll call these the generalized transport networks ("GTN"). In some cases, these may be the same network as the SON. Furthermore, we want to ensure that our on-chip networks are also able to communicate with the outside world. To do this, we surround the array of tiles with a number of I/O ports, which interface the on-chip networks at the array edges with the pins of the VLSI package. These pins in turn are connected to off-chip devices like DRAM's, A/D converters, and PCI slots. Using these I/O ports, not only can tiles communicate with I/O devices, but the I/O devices can use the on-chip networks to communicate with each other.

### 2.2 Attaining Frequency Scalability (C1)

At this point, we have touched upon the basic components of a tiled microprocessor. However, as is often the case with parallel systems, one of our goals in designing the tiled microprocessor is to attain *scalability*. In this context, we seek *physical scalability*, which is the ability to create designs that exploit the VLSI processes made available with subsequent generations of Moore's law. To first

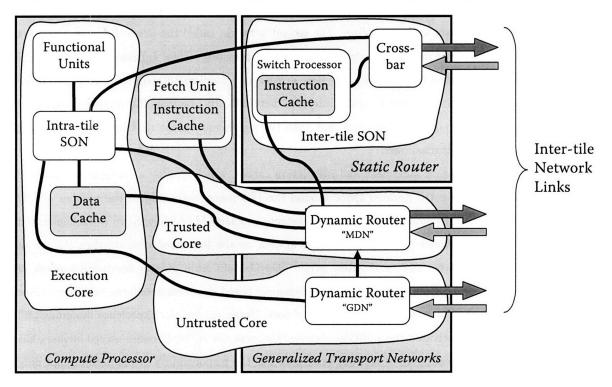

Figure 2-2: The Archetypal Tiled Microprocessor.

order, the tiled microprocessor as we've described it has a straight-forward path to doing this. As Moore's law provides more transistors, we can add more tiles. As Moore's law provides more pins, we add more I/O ports. Finally, as Moore's law provides more wiring resources, we can provide more network links.

However, physical scalability is more subtle then simply adding more tiles, networks links and I/O ports. Ultimately it is the way that these elements are tied together which determines this scalability. Much of the discussion in this thesis centers upon the architectural mechanisms that emerge from the desire to achieve scalability. In this section, we focus on attaining *frequency scalability*, the first of our seven criteria for physically scalable microprocessors.

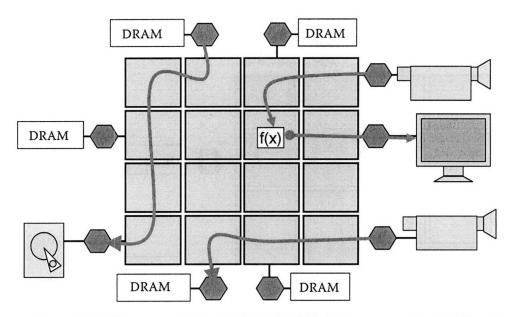

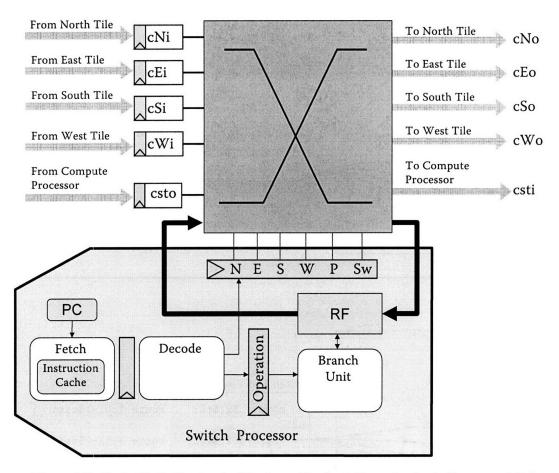

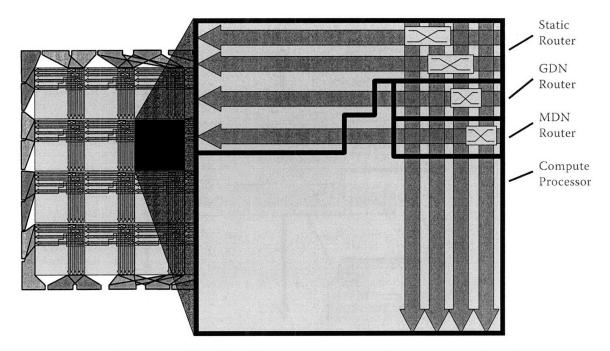

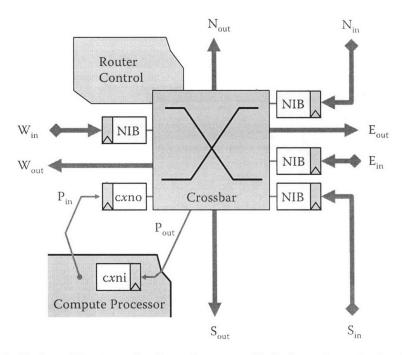

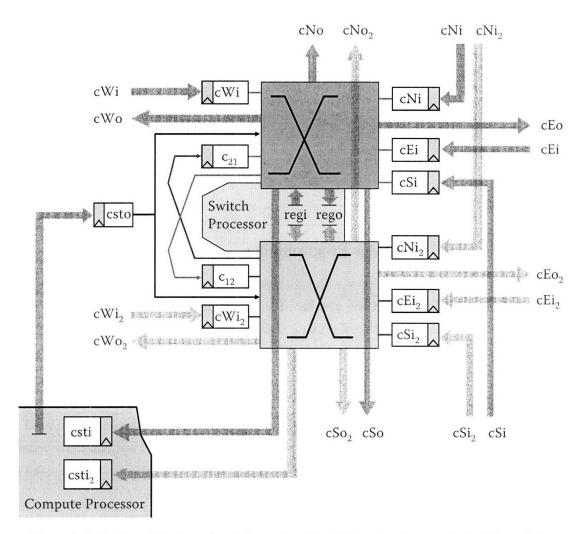

To further the discussion on frequency scalability, we are ready to introduce the Archetypal Tiled Microprocessor. The Archetypal Tiled Microprocessor is an example of a physically scalable microprocessor based upon a set of engineering principals that help ensure scalability. The ATM is depicted in Figure 2-2. On the left hand side, we see an array of identical tiles, which are connected to their nearest neighbors via a number of point-to-point networks. At the periphery of the array of the tiles, the network links are connected to the I/O ports, which are in turn connected to the pins of the chip and to off-chip devices, such as DRAMs, I/O buses, and A/D converters.

Depicted on the right side of Figure 2-2 is the tile. A tile is comprised of computing resources

(including caches), routers (indicated by the crossbar "X" symbol), and a set of network links, which span the tile and connect the tile to its four neighbors. These network links are registered on input. Because the network links are the only wires (except for the clock) that run between tiles, this configuration gives us an important guarantee – that the longest wire in the system is no longer than the width or height of a tile. The idea is that the cycle time of the tiled microprocessor should be approximately the time it takes a signal to pass through a small amount of logic (e.g., a simple router) and across one inter-tile link. We call these inter-tile links *point-to-point interconnections* because there is a single sender on one end and a single receiver on the other. The advantage of using nearest neighbor point-to-point links is that the wire lengths of the architecture do not grow as we add more tiles. The alternative communication mechanism, shared global buses, has the disadvantage that as more tiles are added to the bus, the bus gets longer, has more contention and has greater capacitance. All of these result in degraded performance as the number of tiles increases. None of these negative effects occur with the ATM's point-to-point links.

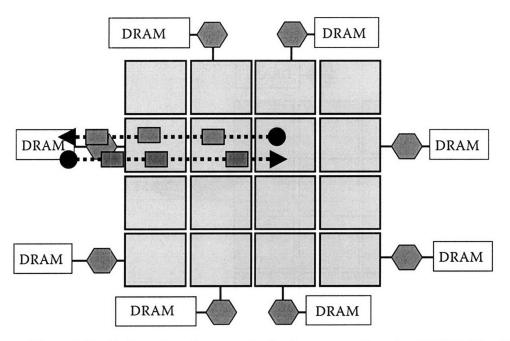

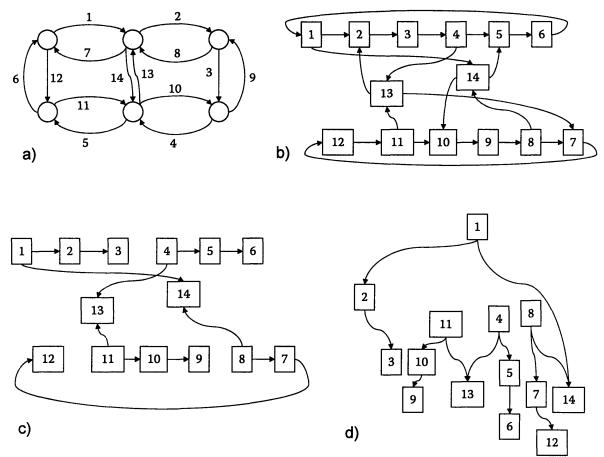

To make the issue of frequency scalability more concrete, let's examine graphically what happens when we attempt to scale the ATM design. In Figure 2-3a, we have depicted the baseline ATM design. In one scenario, we might anticipate using the same process generation, but with a more expensive and bigger die, as well as a more expensive package with more pins. This is shown in Figure 2-3b. As is evident from the diagram, although we have increased the number of tiles in order to exploit the larger transistor budget, none of the architectural wire lengths have changed. Thus, we can reasonably expect that the new design will have a frequency similar to the original design. In Figure 2-3c, we have pictured a implementation of the ATM in a VLSI process two generations of Moore's law later. The amount of on-chip resources has roughly quadrupled. As a result, in the same space, we are able to fit four times as many tiles and network links. In this new process, transistors are twice as fast, but the wire delay, per mm, is about the same. Thus, for a sensible design, the wire lengths need to be approximately half the original length. Because the ATM has only local wires, the wire lengths have shrunk with the tiles, and are a factor of two shorter. As a result, wire delay should not impact the design's ability to exploit the faster transistors and run at twice the frequency as the original ATM.

The design discipline for ensuring short wires is an important step towards frequency scalability. Today, it can take ten to twenty cycles for a signal to travel from corner to corner of a silicon die. As a result, wire delay has the potential to decrease the frequency of a chip by a factor of twenty or more in comparison to its frequency if wire delay were not considered. By ensuring that the architecture has no wires that increase in size as the number of tiles increases, tiled microprocessor designs can attain high frequencies and scale to future process generations even if wire delay worsens.

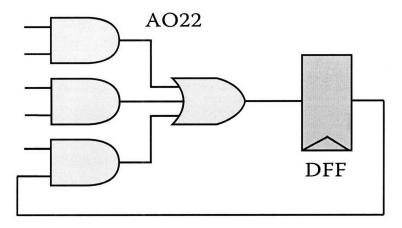

Wire delay is not the only potential problem area for frequency scalable systems – logic delay is also an important consideration. As VLSI structures – such as FIFO buffers, memories, bypass paths

Figure 2-3: Scalability Scenarios for The Archetypal Tiled Microprocessor. Part a) is the baseline ATM. Part b) depicts an ATM implemented in the same VLSI process, but with a bigger die size and a higher pin-count package. We can expect that this ATM will have a frequency similar to the original ATM, because wire lengths have not changed. Part c) depicts an ATM implemented two VLSI process generations later. In this new process transistors are twice as fast; but the wire delay, per mm, is about the same. For a sensible design, the wire lengths need to be approximately half the original size. Because the ATM has only local wires, the wire lengths have shrunk by a factor of two; as a result, wire delay should not impact the design's ability to exploit the faster transistors; the design should run at twice the frequency as the original ATM.

and out-of-order issue logic – grow in size, they also get slower. This is a key problem in today's superscalar processor designs. As the issue-width of superscalars increases, their micro-architectural structures grow in size, and the frequency of the design drops. As a result, superscalars are often characterized as either "brainiacs" – lower-frequency designs that are wide issue – or "speed-demons" – high-frequency designs that are narrow issue [40]. One example of a brainiac is the Itanium 2, which is a 6-way issue microprocessor. Its frequency is significantly lower than 3-way issue superscalars like the Pentium 4.

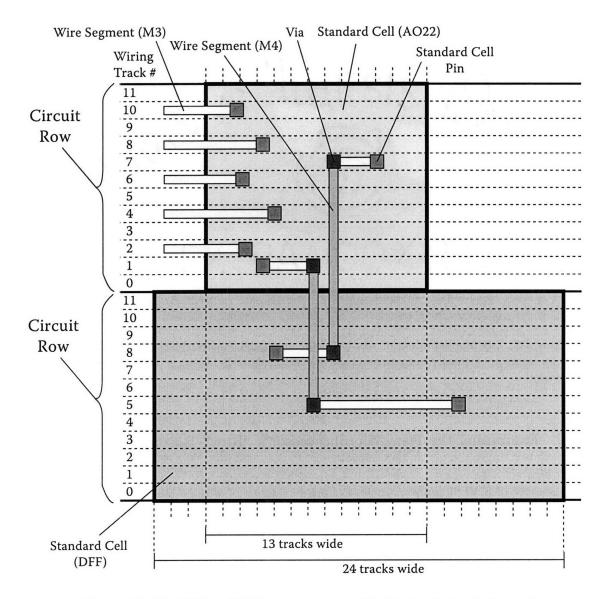

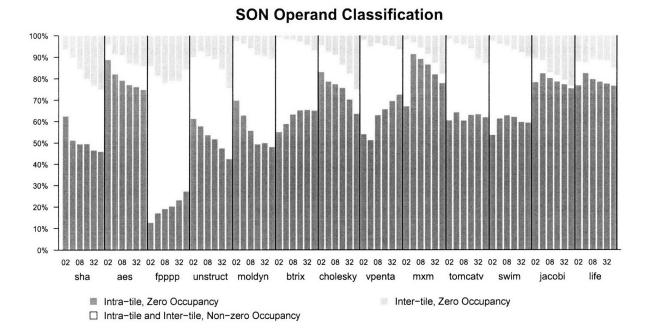

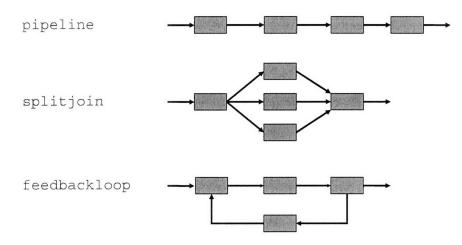

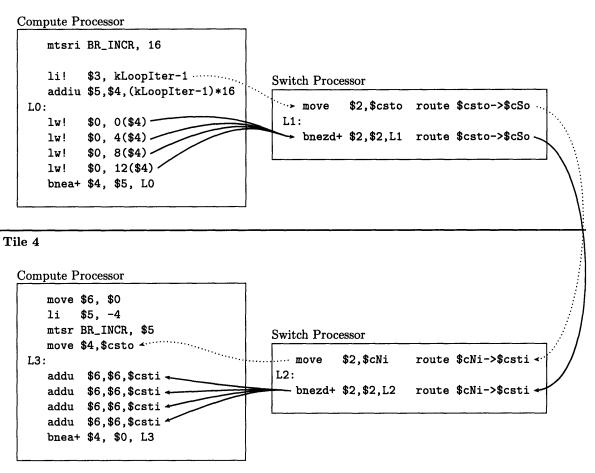

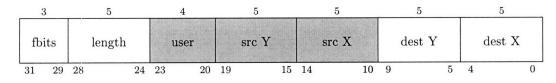

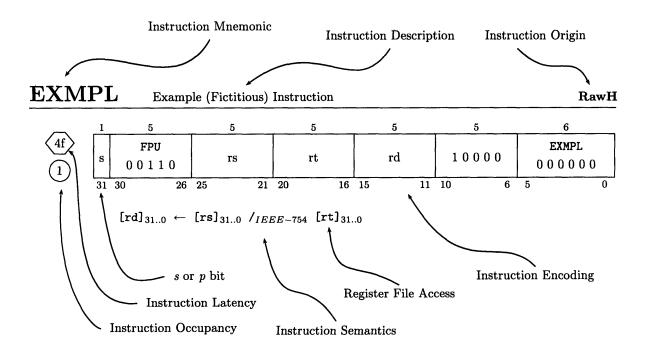

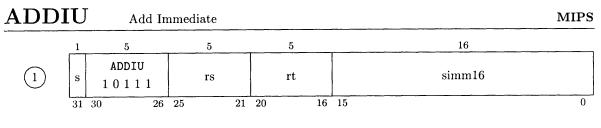

By increasing the capabilities of a machine by adding more tiles, rather than by increasing the size of micro-architectural structures, tiled microprocessors can be both "speed-demons" and "brainiacs" at the same time. By using the same tile design regardless of the scale of the system, tiled microprocessors ensure that frequency is not adversely impacted by the size of the system.