# SiGe-On-Insulator (SGOI) Technology and MOSFET Fabrication

### Zhiyuan Cheng, E. A. Fitzgerald, and D. A. Antoniadis

Abstract – In this work, we have developed two different fabrication processes for relaxed Si<sub>1-</sub> <sub>x</sub>Ge<sub>x</sub>-on-insulator (SGOI) substrates: (1) SGOI fabrication by etch-back approach, and (2) by "smart-cut" approach utilizing hydrogen implantation. Etch-back approach produces SGOI substrate with less defects in SiGe film, but the SiGe film uniformity is inferior. "Smart-cut" approach has better control on the SiGe film thickness and uniformity, and is applicable to wider Ge content range of the SiGe film. We have also fabricated strained-Si n-MOSFET's on SGOI substrates, in which epitaxial regrowth was used to produce the surface strained Si layer on relaxed SGOI substrate, followed by large-area n-MOSFET's fabrication on this structure. The measured electron mobility shows significant enhancement (1.7 times) over both the universal mobility and that of co-processed bulk-Si MOSFET's. This SGOI process has a low thermal budget and thus is compatible with a wide range of Ge contents in  $Si_{1-x}Ge_x$  layer.

*Keywords* – strained-Si, SiGe, SiGe-on-Insulator, SGOI, SOI, MOSFET, mobility, bonding, etch-back, etch-stop, smart-cut, hydrogen implantation.

#### I. INTRODUCTION

Relaxed  $Si_{1-x}Ge_x$ -on-insulator (SGOI) is a very promising technology, as it combines the benefits of two advanced technologies: the conventional SOI technology and the SiGe technology. SiGe-based devices have shown advantageous dc and rf performance using the enhanced electronic properties associated with strain engineering and heterojunction energy barriers. For example, it has been shown that enhanced carrier transport makes strained Si on relaxed SiGe a promising candidate for improving the performance of CMOS technology [1]. It is also of interest to develop SiGe-based devices in an SOI configuration,

The authors are with Massachusetts Institute of Technology, Microsystems Technology Laboratories, Cambridge, Email: cheng@MTL.MIT.EDU

advantages obtaining associated with an insulating substrate, such as reduced parasitic capacitances, improved isolation, and reduced short-channel-effect. In addition, relaxed SGOI is very promising for low power RF application in 10 to 30 GHz region, as the insulating substrate results in less signal crosstalk and less power loss while still enhances the tradeoff of speed-power product. Relaxed SGOI is also a versatile substrate that can be used to integrate various device structures, such as strained-Si and strained-SiGe FETs, and III-V optoelectronics. Several research groups have reported work on a relaxed Si<sub>1-x</sub>Ge<sub>x</sub>on-insulator structure [2-8]. Much of this work has concentrated on relaxed Si<sub>1-x</sub>Ge<sub>x</sub>-on-insulator substrates fabricated using the separation by implantation of oxygen (SIMOX) technology [2-4]. In that process, a high dose oxygen implant is used to bury high concentrations of oxygen in a  $Si_{1-x}Ge_x$  layer, which is then converted into a buried oxide (BOX) layer upon annealing at high temperature (for example, at 1350 °C). The quality of the resulting  $Si_{1-x}Ge_x$  film and the buried oxide layer is a concern in such processes. segregation addition, Ge during high In temperature annealing also limits the maximum Ge composition to a low value [2-4]. Another method reported [5-8] is to deposit an initially strained Si<sub>1-x</sub>Ge<sub>x</sub> layer on an ultra-thin SOI substrate and then transfer the strain to the underlying thin Si layer at high temperature. In this case the SOI substrate was used as a "compliant substrate".

In this work, we have investigated SGOI substrate fabrication via two different approaches: etchand "smart-cut" back [9] [10]. We also demonstrate strained-Si n-MOSFET's on relaxed Ge) with electron SGOI (25%) mobility of approximately enhancement 1.7 times compared to unstrained Si control devices [9].

#### **II. SGOI SUBSTRATE BY ETCH-BACK**

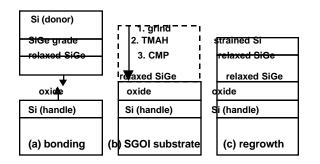

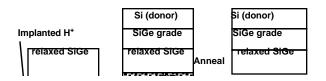

SGOI substrates were fabricated via two differenct approaches, etch-back and smart-cut. The substrate fabrication process is shown schematically in Fig. 1 and Fig. 2 respectively. In the etch-back approach, starting with a 4-inch Si (100) donor wafer, high quality relaxed SiGe was grown at 900 °C by UHVCVD using a graded Si<sub>1-x</sub>Ge<sub>x</sub> buffer technique [11]. The Ge content *x* was graded from zero to 25% with a grading rate of 10% Ge/µm. A 2.5 µm-thick undoped, relaxed Si<sub>0.75</sub>Ge<sub>0.25</sub> cap layer was deposited, as shown in Fig. 1(a). The slow grading rate and high growth temperature result in a completely relaxed cap layer with threading dislocation densities of ~10<sup>5</sup> cm<sup>-2</sup> [12].

The as-grown relaxed  $Si_{1-x}Ge_x$  layer has a surface roughness of around 11 to 15 nm, due to the underlying strain fields generated by misfit dislocations at the graded layer interfaces. Thus chemical-mechanical polishing (CMP) was used to smooth the surface. After a cleaning step to render the surface highly hydrophilic, the doner wafer was fliped over bonded to an oxidized Si handle wafer at room temperature, and then annealed at at 850 °C for 1.5 hrs, as schematically shown in Fig. 1 (a). The bonded pair was then ground to remove the donor wafer substrate, as shown in Fig. 1(b). The wafer was then subjected to a TMAH solution to etch away the SiGe graded layer until SiGe with 20% Ge was exposed. A key factor in this wet etch process is the use of 20% SiGe as a natural etch stop. It has been shown that  $Si_{1-x}Ge_x$  with Ge content greater than 20% is an excellent etch stop for various etchants (KOH, TMAH, and EPD), with selectivity better than the conventional  $p^{++}$  etch stop [13]. The structure was further thinned by CMP to expose the relaxed  $Si_{0.75}Ge_{0.25}$  layer, and a relaxed SGOI substrate results.

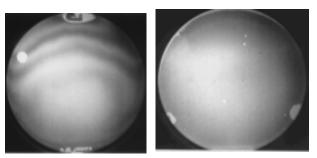

Fig. 3(a) shows the infrared image of a typical SGOI substrate with 25% Ge content. The fringes in the infrared image reflect the non-uniformity of the SiGe film. The non-uniformity results mainly from the two CMP steps in the process.

#### **III.SGOI SUBSTRATE BY "SMART-CUT"**

The "smart-cut approach" is shown schamatically in Fig. 2. Before bonding, hydrogen ions (50~200 keV, 5E16~1E17  $H^{+}/cm^{2}$ ) was implanted into the relaxed SiGe cap layer of the donor wafer. The implanted hydrogen creates micro-bubbles in a certain depth determined by the implantation energy, Fig. 2(a). After bonded to an oxidized Si handle wafer, it was annealed at 400~600°C. During the anneal, the bonded pair split at the buried hydrogen-rich layer, leading to the desired layer transfer of relaxed SiGe. A final 850°C anneal improved the

bond strength. Fig. 3(b) shows a 4-inch SGOI substrate prepared by "smart-cut" approach.

To investigate the surface of the as-transferred **SGOI** substrate, transmission electron microscopy (TEM) and atomic force microscopy (AFM) were used. The TEM cross-section view in Fig. 4(a) shows that a  $\sim 640$  nm thick Si<sub>0.75</sub>Ge<sub>0.25</sub> layer was transferred onto the top of a 550 nm thick buried oxide (BOX) in a typical SGOI substrate. Surface damage is also shown clearly at the splitting surface. Fig. 4(b) shows a surface roughness of 11.3 nm in an area of 5x5  $\mu$ m<sup>2</sup> by AFM for the as-transferred SGOI, which is similar to the surface roughness reported for as-transferred silicon film by "smart-cut" processes [15-16]. The TEM and AFM results suggest that a top layer of about 100 nm should be removed by a final touch CMP step.

advantage of "smart-cut" The approach, compared to etch-back approach, is that the thickness and uniformity of the transferred SiGe film can be controlled well. Nevertheless, the "smart-cut" approach tends to give higher defect density on the SiGe film, typically in the range of 20/cm<sup>2</sup>. We have observed one new faceted defects on SiGe film by "smart-cut" approach, which show characteristics of having ractangle crystal graphic shape and large size in the several hundred µm range. These defects were not observed in both the co-processed Si-on-insulator films using same "smart-cut" process and the coprocessed SiGe-on-insulator films using etch-back process. This suggests that these new defects may originate from the epi defects present in SiGe growth and the formation of these new defects is "smart-cut" related to the process. Detail investigation is under progress. Growing an oxide laver on the SiGe donor wafer before implantation and bonding, could be one possible solution to reduce those defects.

#### IV. MOSFET'S FABRICATION ON SGOI

Large-area ring structure strained-Si *n*-MOSFET's were fabricated on the SGOI substrate prepared by etch-back approach. First, 100 nm p-type (doping  $10^{16}$  cm<sup>-3</sup>) relaxed Si<sub>1-x</sub>Ge<sub>x</sub> was grown on the SGOI substrate at 850 °C, followed by 8.5 nm-thick undoped strained-Si layer grown at 650°C, as shown in Fig. 1(c). Large-area, ring structure *n*-MOSFET's were then fabricated utilizing a short-flow one-mask MOSFET process developed in this lab [14]. The gate stack consists of 300 nm LTO deposited via LPCVD at

400°C, and 50 nm of poly-Si deposited at 560°C. This large thickness of LTO gate dielectric facilitates the one-mask process, as described below. Capacitors fabricated with LTO in this lab have demonstrated interface state densities on par with thermal oxides ( $\sim 5_{10}^{10}$  cm<sup>-2</sup> eV<sup>-1</sup>) [14]. The measured fixed oxide charge density is about  $2.4 \times 10^{11}$  cm<sup>-2</sup>. The gate stack was then patterned and etched into ring MOSFET structures in the only lithography step. A key step is the use of buffered oxide etchant (BOE) to undercut the gate polysilicon, forming a large "T-gate" geometry. Arsenic ion implants (35 keV, total dose  $1 \times 10^{15}$  cm<sup>-2</sup>) were performed to dope both source/drain and gate regions at the perpendicular directions with a 7° tilt to extend the S/D region under the T-gate structure. The dopant was activated via RTA at 1000°C for 1 s. Because the strained-Si layer was in equilibrium, no relaxation via misfit dislocation introduction occurred. Blanket Ti/Al metallization was then performed e-beam deposition via at perpendicular incidence. Due to the extreme geometry of the "T-gate" FET structure and large gate LTO thickness, breaks occur in the metal which isolate the source, gate, and drain regions without further lithography. Two control structures were also co-processed: conventional bulk Si MOSFET's and strained-Si MOSFET's on relaxed bulk SiGe substrates which are identical to the donor wafer shown in Fig. 1(a).

The TEM photograph in Fig. 5 shows the structure of the finished strained-Si, surface channel *n*-MOSFET's on the relaxed SGOI substrate.

## V. DEVICE CHARACTERIZATION AND ELECTRON MOBILITY ENHANCEMENT

Some pieces of the finished wafer were used to conduct Triple-axis X-ray Diffraction Scans and EPD (etch pit density) experiments. The results show that both transferred and regrown SiGe films on SGOI were completely relaxed and the dislocation density was less than 8x10<sup>5</sup> /cm<sup>2</sup>, in the range of the bulk SiGe buffer. The EPD experiment showed no visible misfit dislocation between the top Si film and the relaxed SiGe layer, suggesting that the top Si film was strained.

The large square ring structure *n*-MOSFET's (L =200  $\mu$ m, ring perimeter = 4 x 250  $\mu$ m) were used to evaluate the electron mobility as a function of vertical field. The effective electron mobility  $\mu_{eff}$ was extracted from the linear regime device current,  $\mu_{eff} = (L_{eff}/W_{eff}) I_{DS} / [C_{ox}(V_{GS}-V_T)V_{DS}],$ where  $V_{DS} = 0.1$  V. Taking into consideration the transistor's ring geometry,  $(W_{eff}/L_{eff})$  was replaced by the appropriate geometry factor G = 0.138, obtained by numerical solution of the Laplace equation using MEDICI [14]. The oxide capacitance  $C_{ox} = \varepsilon_{ox} / t_{ox}$  was obtained from C-V measurements on the same device, and the oxide thickness  $t_{ox} = 326$  nm was also extracted. The effective vertical field  $E_{eff}$  is given by  $E_{eff} = (Q_b + Q_{inv}/2)/\varepsilon_s$ Because of the uncertainties in the strained-Si/Si<sub>0.75</sub>Ge<sub>0.25</sub> doping, the bulk depletion charge  $Q_b$  was not computed from the usual  $N_A x_{d,max}$  approximation. Instead,  $Q_b$  was extracted from  $E_{ox} \varepsilon_{ox} = Q_{inv} + Q_b$ , where  $E_{ox}$  is the electric field in the gate oxide. As a result, the effective field can be approximated by  $E_{eff} = [E_{ox}\varepsilon_{ox} - Q_{inv}/2] / \varepsilon_s$ . The inversion charge  $Q_{inv}$  was taken as  $C_{ox}(V_{GS}-V_T)$ .  $E_{ox}$  was assumed to be equal to  $V_{GS}/t_{ox}$ , which holds under the conditions of strong inversion and  $V_{GS} >> V_{DS}$ , when the potential difference between the strongly-inverted Si surface and the S/D regions is negligibly small compared with the large potential drop across the thick gate oxide.

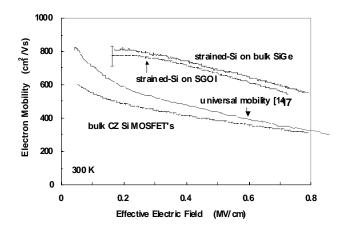

The measured  $\mu_{eff}$  as a function of  $E_{eff}$  is shown in Fig. 6. The mobilities of two controls are also shown in the figure for comparison. Since all three devices have the same geometry and were processed simultaneously, possible errors due to factors such as the extraction of the ring geometry factor, and approximations in  $E_{eff}$ do not evaluation impact the relative of the comparison electron mobility characteristics. In addition, the measured mobility for the CZ Si control device is close to the universal mobility curve [17]. The measured electron mobility enhancement for strained Si MOSFETs fabricated on SGOI, compared to the mobility of co-processed bulk Si MOSFET's is significant (~1.7 times). In addition, the electron mobilities are comparable for devices fabricated SGOI and bulk relaxed SiGe on layers, superior demonstrating that the mobility performance introduced by the strained-Si channel is retained in this SGOI structure. This enhancement factor of 1.7 is consistent with

previously reported experimental and theoretical values for strained-Si *n*-MOSFETs on bulk relaxed SiGe films [18].

### **V. CONCLUSION**

In summary, we have demonstrated fabrication of 4-inch diameter relaxed SiGe-on-insulator (SGOI) substrates, using a combination of UHVCVD Si<sub>1-x</sub>Ge<sub>x</sub> heteroepitaxial growth and hydrogen-induced layer transfer by delamination or etch-back utilizing 20% SiGe layer in the grade buffer as a natural etch stop. We also have demonstrated long-channel strained-Si MOSFET's fabricated in SGOI with a high Ge content of 25%. The measured electron mobility for strained-Si n-MOSFET's fabricated on SGOI is significantly higher than both the universal mobility and that of co-processed bulk Si MOSFET's. In contrast to the SIMOX process, where the high annealing temperature limits the Ge content to a low level, this new SGOI process has a low thermal budget and thus is compatible with a wide range of Ge contents in  $Si_{1-x}Ge_x$  layer.

#### ACKNOWLEDGMENT

One of the authors, Z. Cheng, is grateful to the advise from Prof J. L. Hoyt from MIT. He would also like to acknowledge the collaboration and useful discussion with Dr. M. T. Currie, C. W. Leitz, G. Taraschi, A. Pitera, M. L. Lee, Dr. T. A. Langdo and Mr. M. Frongillo. This work was funded by the Singapore-MIT Alliance program and the DARPA HGI program, and made use of facilities in the MIT Microelectronics Technology Laboratory and the NSF-funded MIT CMSE shared facilities.

#### **REFERENCES:**

- [1] K. Rim, J. L. Hoyt, and J. F. Gibbons, "Fabrication and analysis of deep submicron strained-Si n-MOSFET's", *IEEE Trans. Electron Devices*, Vol. 47, No. 7, pp. 1406-1415, 2000.

- [2] T. Mizuno, S. Takagi, N. Sugiyama, H. Satake, A. Kurobe, and A. Toriumi, "Electron and hole mobility enhancement in strained-Si MOSFET's on SiGe-oninsulator substrates fabricated by SIMOX technology", *IEEE Electron Device Letters*, Vol. 21, No. 5, pp. 230-232, 2000.

- [3] Y. Ishilawa, N. Shibata, and S. Fukatsu, "SiGe-on-insulator substrate using SiGe alloy grown Si(001)", *Applied Physics Letters*, Vol. 75, No. 7, pp. 983-985, 1999.

- [4] S. Fukatsu, Y. Ishilawa, T. Saito, and N. Shibata, "SiGe-based semiconductor-oninsulator substrate created by low-energy separation-by-implanted-oxygen", *Applied Physics Letters*, Vol. 72, No. 26, pp. 3485-3487, 1998.

- [5] F. Y. Huang, M. A. Chu, M. O. Tanner, K. L. Wang, G. D. U'Ren and M. S. Goorsky, "High-quality strain-relaxed SiGe alloy grown on implanted silicon-on-insulator substrate", *Applied Physics Letters*, Vol. 76, No. 19, pp. 2680-2682, 2000.

- [6] K. Brunner, H. Dobler, G. Abstreiter, H. Schafer and B. Lustig, "Molecular beam epitaxy growth and thermal stability of Si<sub>1-x</sub>Ge<sub>x</sub> layers on extremely thin silicon-oninsulator substrates", *Thin Solid Films*, Vol. 321, pp. 245-250, 1998.

- [7] A. R. Powell, S. S. Iyer, and F. K. LeGoues, "New approach to the growth of low dislocation relaxed SiGe material", *Applied Physics Letters*, Vol. 64, No. 14, pp. 1856-1858, 1994.

- [8] F. K. LeGoues, A. Powell, and S. S. Iyer, "Relaxation of SiGe thin films grown on Si/SiO<sub>2</sub> substrates", *Journal of Applied Physics*, Vol. 75, No. 11, pp. 7240-7246, 1994.

- [9] Z. Cheng, M. T. Currie, C. W. Leitz, G. Taraschi, E. A. Fitzgerald, J. L. Hoyt, and D. A. Antoniadis, "Electron Mobility Enhancement in Strained-Si n-MOSFET's Fabricated on SiGe-on-Insulator (SGOI) Substrates", *IEEE Electron Device Letters*, Vol. 22, No. 7, pp. 321-323, 2001.

- [10] Z. Cheng, G. Taraschi, M. T. Currie, C. W. Leitz, M. L. Lee, A. Pitera, T. A. Langdo, E. A. Fitzgerald, J. L. Hoyt, and D. A. Antoniadis, "Relaxed Silicon-Germanium on Insulator Substrate by Layer Transfer", *Journal of Electronic MaterialsPhysics*. accepted to publish in Oct, 2001.

- [11] E. A. Fitzgerald, Y.-H. Xie, M. L. Green, D. Brasen, A. R. Kortan, J. Michel, Y.-J. Mii, and B. E. Weir, "Totally relaxed  $Ge_xSi_{1-x}$  layers with low threading dislocation densities grown on Si substrates", *Appl. Phys. Lett.* 59, No. 7, pp. 811-813, 1991.

- [12] C.W. Leitz, M.T. Currie, A.Y. Kim, J. Lai,E. Robbins, E.A. Fitzgerald, and M.T. Bulsara, "Dislocation Glide and Blocking

Kinetics in Compositionally Graded SiGe/Si", submitted to Journal of Applied Physics.

- [13] K. Wu, "Novel Etch-Stop Materials for Silicon Micromachining", M.Eng. Thesis, Massachusetts Institute of Technology, 1997.

- [14] M. A. Armstrong, "Technology for SiGe Heterostructure-Based CMOS Devices". Ph.D. Thesis, Massachusetts Institute of Technology, 1999.

- International SOI Conference, pp. 178-179, (1995).

- [16] C. Maleville, et al., in Silicon-on-Insulator Technology and Devices VII. Electrochemical Society Proceedings, Vol. 96-3, pp. 34-46, (1995).

- [17] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part Ieffects of substrate impurity concentration", IEEE Trans. Electron Devices, vol. 41, No. 12, pp. 2357-2362, 1994.

- [18] S. Takagi, J. L. Hoyt, J. J. Welser and J. F. Gibbons, "Comparative study of phonontwo-dimensional limited mobility of electrons in strained and unstrained Si MOSFETs", Journal of Applied Physics, Vol 80, pp 1567-1577, 1996.

[15] M. Bruel, et al., Proceedings 1995 IEEE Fig. 2. SGOI fabrication processes via "smartcut" approach.

(a) by etch-back

(b) by "smart-cut"

Fig. 3. 4-inch SGOI substrates fabricated via (a) etch-back appoach, and (b) "smart-cut" approach

Fig. 4. As-transferred relaxed Si<sub>0.75</sub>Ge<sub>0.25</sub>-oninsulator substrate by "smart-cut" approach: (a) TEM cross-section view, and (b) AFM image, showing a surface roughness of 11.3 nm in an area of  $5x5 \ \mu m^2$ .

Fig. 1. SGOI fabrication processes via etch-back approach and relaxed-SiGe/strained-Si regrowth.

Fig. 5. TEM photograph of the finished strained-Si surface channel MOSFET's fabricated on relaxed  $Si_{0.75}Ge_{0.25}$ -on-insulator (SGOI) substrate.

Fig. 6. Measured effective electron mobility vs. effective electric field. The error bar represents the variation among devices. The universal mobility from [17] is also shown for comparison.

|         | Zhiyuan Cheng obtained B.          |

|---------|------------------------------------|

|         | Eng in Electronic Engineering in   |

|         | 1990 from Tsinghua University and  |

| Picture | Ph.D. in Electrical Engineering in |

|         | 1999 from National University of   |

|         | Singapore. He is now a post-doc in |

|         | MIT, working on SiGe technology.   |

|         |                                    |

|         |                                    |