# Monolithic Electronic-Photonic Integration in State-of-the-Art CMOS Processes

by

Jason S. Orcutt

M.S. Electrical Engineering

Massachusetts Institute of Technology, 2008

B.S. Electrical Engineering

Columbia University, 2005

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### FEBRUARY 2012

©2012 Massachusetts Institute of Technology. All rights reserved.

| Signature of Author: |                                                                           |

|----------------------|---------------------------------------------------------------------------|

|                      | Department of Electrical Engineering<br>February 3, 2012                  |

| Certified by:        |                                                                           |

|                      | Rajeev J. Ram<br>Professor of Electrical Engineering<br>Thesis Supervisor |

| Accepted by:         |                                                                           |

|                      | Leslie Kolodziejski                                                       |

|                      | Professor of Electrical Engineering                                       |

Chair, Committee for Graduate Students

# Monolithic Electronic-Photonic Integration in State-of-the-Art CMOS Processes

by

Jason S. Orcutt

Submitted to the Department of Electrical Engineering and Computer Science on February 3, 2012 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### **ABSTRACT**

As silicon CMOS transistors have scaled, increasing the density and energy efficiency of computation on a single chip, the off-chip communication link to memory has emerged as the major bottleneck within modern processors. Photonic devices promise to break this bottleneck with superior bandwidth-density and energy-efficiency. Initial work by many research groups to adapt photonic device designs to a silicon-based material platform demonstrated suitable independent performance for such links. However, electronic-photonic integration attempts to date have been limited by the high cost and complexity associated with modifying CMOS platforms suitable for modern high-performance computing applications.

In this work, we instead utilize existing state-of-the-art electronic CMOS processes to fabricate integrated photonics by: modifying designs to match the existing process; preparing a design-rule compliant layout within industry-standard CAD tools; and locally-removing the handle silicon substrate in the photonic region through post-processing. This effort has resulted in the fabrication of seven test chips from two major foundries in 28, 45, 65 and 90 nm CMOS processes. Of these efforts, a single die fabricated through a widely available 45nm SOI-CMOS mask-share foundry with integrated waveguides with 3.7 dB/cm propagation loss alongside unmodified electronics with less than 5 ps inverter stage delay serves as a proof-of-concept for this approach. Demonstrated photonic devices include high-extinction carrier-injection modulators, 8-channel wavelength division multiplexing filter banks and low-efficiency silicon germanium photodetectors. Simultaneous electronic-photonic functionality is verified by recording a 600 Mb/s eye diagram from a resonant modulator driven by integrated digital circuits. Initial work towards photonic device integration within the peripheral CMOS flow of a memory process that has resulted in polysilicon waveguide propagation losses of 6.4 dB/cm will also be presented.

Thesis Supervisor: Rajeev J. Ram

Title: Professor of Electrical Engineering

# **ACKNOWLEDGMENTS**

Many people have contributed in various ways to the creation of this thesis. Most directly, my colleagues at MIT over the years have been a pleasure to work alongside. Ranging from formal collaborations to more random exchanges of ideas and favors, the MIT research community as a whole has exceeded any expectations for approachability and camaraderie. Outside of campus, friends and family have made the experience enjoyable throughout tapeouts, trials and tribulations.

From the various corporate partners who have served as fabrication facilities, intermediaries or collaborators, there are many people to whom I owe many thanks for information and assistance that directly led to the ability to execute on the ideas in this thesis. At Texas Instruments, Dennis Buss gave us the first kind ear to figure out what we were trying to do and why we were trying to do it. He provided key technical insights and put us in touch with the right people to get the details of their state-of-the-art-fabrication processes and how a submitted design truly gets transferred into silicon. Tom Bonifield was one of the key people who provided guidance in many of the judgment calls that had to be made on early design framework integration choices that I had been making with way too little information. At IBM Foundry Design Services, Bill Smith, Kurt Tallman and Joanne Newman have been invaluable in their assistance not only for their information, but also for their patience. To get to them in the first place as well as everything practical that goes into submitting a CMOS design for fabrication under tight deadlines and high stress, Joe Meinhardt and James Gay have provided much appreciated assistance. Recently, through our collaboration with Micron Technology it has been a great pleasure to work with Roy Meade, Zvika Sternberg, Ofer Tehar-Zahav, Reha Bafrali, Gurtej Sandhu and many other people within their organizations. Sanh Tang, Steve Kramer and Nishant Sinha deserve special thanks for our first test fabrication run before the launch of the full POEM program. In aggregate, they have provided me with an absolute deluge of information on what it actually takes to make CMOS work from the STI to the OSG and back to the ULC.

Funding for this work has largely stemmed from Dr. Jagdeep Shah of the Defense Advanced Research Project Agency (DARPA) through a variety of programs. The full alphabet soup of DARPA programs that have contributed to funding the work of this thesis through seedlings or programs is from last to first: POEM, APS, CiPHER, PICO, LEAP, UNIC, GHOST and EPIC. Graduate fellowship funding from the NSF enabled me to pursue ideas that were further afield than existing funded programs at the start of this research.

The intrachip photonics team has consisted of many influential members over the years. Milos Popovic has provided me with extremely insightful information on high index contrast and resonant photonic device design the entire time that I have known him. All that I needed to know about fabrication when Trey Holzwarth was around was that he would somehow make it work. Once he left, Jie Sun and Hanqing Li have led many new projects in campus fabrication post-processing efforts. Anatoly Khilo provided many insights and novel photonic designs during his time with our project in the first few process generations. Erman Timurdogan and Jeff Shainline are continuing excellent photonic design work for novel tuning and modulation devices. I have spent more sleepless nights than I

care to remember to meet design deadlines working alongside a great team of circuit designers in Michael Georgas, Ben Moss, Jonathan Leu and Chen Sun.

The contribution of expertise and time from many different faculty members from Professors Hank Smith, Karl Berggren and Judy Hoyt on the fabrication front helped shape our early discussions to be more productive. Prof. Franz Kaertner led the EPIC team that kick started our efforts as well as served on my thesis committee. His insights are always helpful and he has taught me through his example that there is no problem too big to be solved by scribbling estimates of relevant physics on a scrap of paper to factor of two precision. Prof. Ippen helped clarify initial project ideas and has graciously loaned us the use of his broadband laser for years over the course of this project. Prof. Mike Watts, who is a recent addition to the team, has brought with him extensive experience in silicon photonics and I have greatly benefitted from discussions with him and his students.

I have had the great benefit of working closely with Prof. Vladimir Stojanovic, who has served as the project lead on this effort, for nearly 6 years. The rate at which he picks up new topics and becomes an expert has been fun to watch. A significant fraction of the ideas of this thesis down to the nittiest, grittiest, all-nighter-in-lab-with-the-students details have been jointly his or resulted from the continual process of bouncing ideas off of him. He has also steadfastly pursued the goal of getting this project to work one way or another.

Prof. Rajeev Ram has provided me with an ideal academic home among wide variety of different research topics in the Physical Optics & Electronics Group. I do not have a clue where else I could have had the breadth of interaction with interesting people and projects from thermodynamics to anything you can do with PDMS. Rajeev has served as a valuable advisor over the years by providing deep insight into many areas, unique opportunities and unusual freedom to take charge of my own research. He is also an extremely friendly person who has been a pleasure to get to know over my time here. Harry Lee, Peter Mayer and Tom Liptay provided the senior expertise when I joined the lab. All three helped me figure out what it meant to do research. They have also turned out to be lasting friends after graduation. Kevin Lee and Reja Amatya were great wire-to-wire lab companions with whom I shared between 1300 and 1500 lunches. Kevin managed to not accidentally kill me and along the way enhanced my love of the kludge. Reja has always been a friendly voice of reason and provided a constant example of not getting worked up over the little things in research and in life. Parthi Santhanam has added a unique viewpoint on thinking about problems both theoretical and practical that I have increasing been able to understand and appreciate over the years. Dodd Gray and Joe Summers were great colleagues to have around both in lab and over a barbeque. Karan Mehta has already proven his ability to unconfuse me on any number of topics and has been a welcome addition the project and our office.

My friends and family have provided a much needed counterweight to this thesis. There was never the lack of a worthwhile distraction when one was needed. Throughout it all, from rolling deadlines that just kept rolling to the minor victories, it was unexpected and wonderful to share my time in grad school with my wife Kelly. It has been a fun journey and far more interesting than I expected when I started at MIT back in 2005 without knowing what I was getting myself into.

| 1. I | ntro        | duction                                                | 12 |

|------|-------------|--------------------------------------------------------|----|

| 1.1. | A S         | urvey of Electronic-Photonic Integrated Circuits       | 14 |

| 1.2. | Oth         | er Examples of Zero-Change CMOS Integration            | 15 |

| 1.3. | CM          | OS Process Overview                                    | 16 |

| 1.4. | DR          | AM Process Comparison                                  | 22 |

| 1.5. |             | ndard Process Integration Methodology                  |    |

| 1.   | 5.1.        | Waveguide Core Formation in Standard CMOS              |    |

| 1.   | 5.2.        | Localized Substrate Removal                            |    |

| 1.   | <i>5.3.</i> | DRAM process integration                               | 27 |

| 1.6. | Alte        | ernative Approaches to Electronic-Photonic Integration | 29 |

| 1.   | 6.1.        | Thick-SOI                                              | 29 |

| 1.   | 6.2.        | Backend, On-CMOS processing                            |    |

| 1.   | 6.3.        | Hybrid Integration                                     | 32 |

| 1.7. | Inte        | egrated Optical Components                             | 34 |

| 1.   | 7.1.        | High-Index-Contrast Waveguides                         | 35 |

| 1.   | 7.2.        | Fiber-to-Chip Couplers                                 |    |

|      | 7.3.        | Wavelength Division Multiplexing Filters               |    |

|      | 7.4.        | Modulators                                             |    |

| 1.   | 7.5.        | Detectors                                              | 60 |

| 1.8. | Sur         | nmary                                                  | 65 |

| 2. ( | ore-        | to-Memory Links for Multicore Processors               | 67 |

| 2.1. | Tar         | get System                                             | 68 |

| 2.2. | Fut         | ure scaling of electrical core-to-memory links         | 70 |

| 2.   | 2.1.        | Channel Bandwidth                                      | 70 |

| 2.   | 2.2.        | Channel Density                                        | 71 |

|      | 2.3.        | Energy Efficiency                                      |    |

| 2.   | 2.4.        | Conclusions and Outlook                                | 73 |

| 2.3. | Mo          | nolithic Photonic Interconnect                         | 73 |

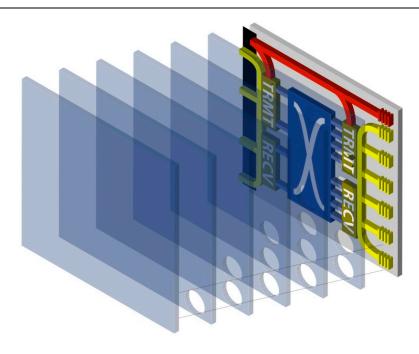

| 2.   | 3.1.        | Packaging platform                                     |    |

|      | 3.2.        | Wavelength Division Multiplexing                       |    |

|      | 3.3.        | Channel locking and thermal stabilization              |    |

| 2.   | 3.4.        | Modulators                                             | 84 |

| 2.3.5.        | Detectors                                           |     |

|---------------|-----------------------------------------------------|-----|

| 2.3.6.        | On-chip electrical link energy                      | 91  |

| 2.3.7.        | Optical loss budget                                 |     |

| 2.3.8.        | Optical power supply                                | 93  |

| 2.4. Fut      | ure Core-to-DRAM Photonic Networks                  | 96  |

| 2.4.1.        | Memory Module Architecture                          | 97  |

| 2.4.2.        | Wavelength-Routed Architecture                      |     |

| 2.4.3.        | Survey of Current and Future Architecture Work      |     |

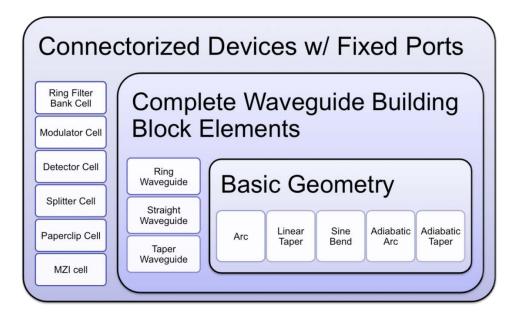

| 3. Found      | dry Design Environment Integration                  | 102 |

| 3.1. A C      | omparison to Photonic-Specific Foundries            | 102 |

| 3.2. CM       | OS Foundry Design Environment                       | 103 |

| 3.2.1.        | The Designer's Perspective                          | 104 |

| 3.2.2.        | Determining Process Parameters                      | 105 |

| 3.2.3.        | Design Rule Checking                                | 108 |

| 3.2.4.        | Data Preparation and Mask Manufacture               |     |

| 3.3. Des      | ign Environment Integration                         | 110 |

| 3.3.1.        | Full-Custom Layout of Photonic Structures           | 110 |

| <i>3.3.2.</i> | Design Layer Overview                               |     |

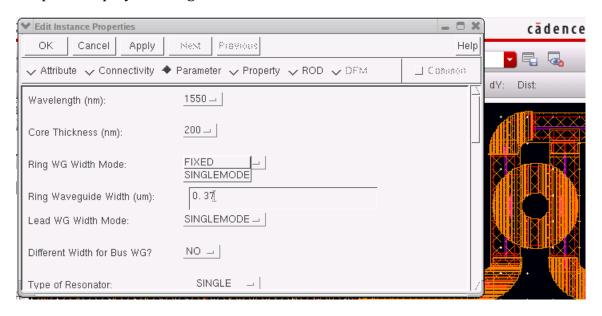

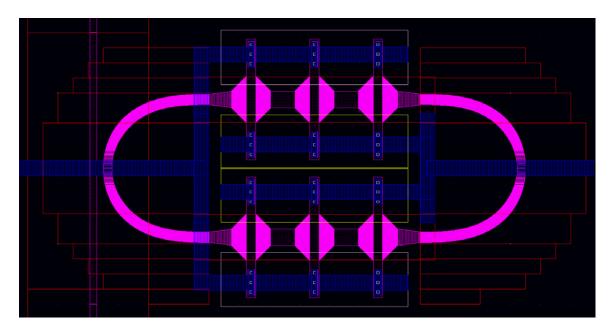

| 3.3.3.        | Efficient Photonic Device Layout on Design Layers   | 113 |

| 3.3.4.        | Hierarchical Parameterized Cell Design              | 114 |

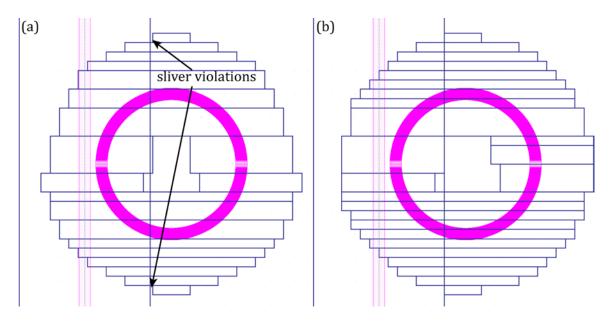

| 3.4. Des      | ign Rule Compliance                                 | 117 |

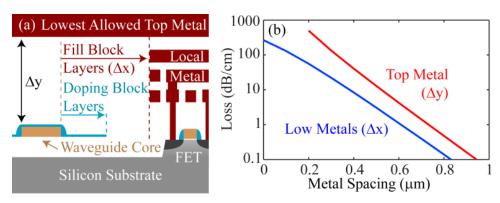

| 3.4.1.        | Exclusion of Lossy Materials from Local Environment | 118 |

| 3.4.2.        | Minimum/Maximum Geometry Design Rules               | 121 |

| 3.4.3.        | Device Functionality Design Rules                   | 124 |

| 3.5. Sun      | nmary of Photonic Integration CMOS Test Chips       | 124 |

| 3.5.1.        | AURORA (EOS1) – Texas Instruments 65nm bulk-CMOS    | 124 |

| <i>3.5.2.</i> | EOS2 – Texas Instruments 28nm bulk-CMOS             | 125 |

| <i>3.5.3.</i> | EOS3 – IBM 90nm bulk-CMOS (9sf)                     | 126 |

| <i>3.5.4.</i> | EOS4 - IBM 45nm SOI-CMOS (12soi)                    |     |

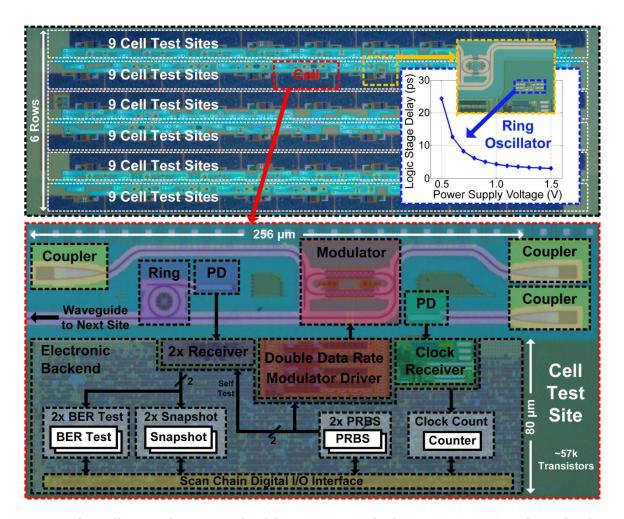

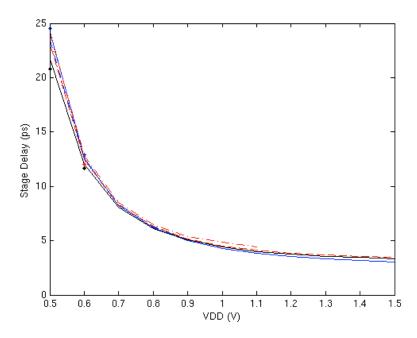

| 3.5.5.        | EOS6, EOS8 and EOS10 – IBM 45nm SOI-CMOS (12soi)    | 128 |

| <i>3.5.6.</i> | EOS12 – IBM 45nm SOI-CMOS (12soi)                   | 129 |

| 3.6. Con      | clusions and Future Work                            | 130 |

| 4. Wave       | guides and Passive Devices                          | 133 |

| 4.1. Hig      | h-Index Contrast Photonic Design Tools              | 133 |

| _             | veguide Design                                      |     |

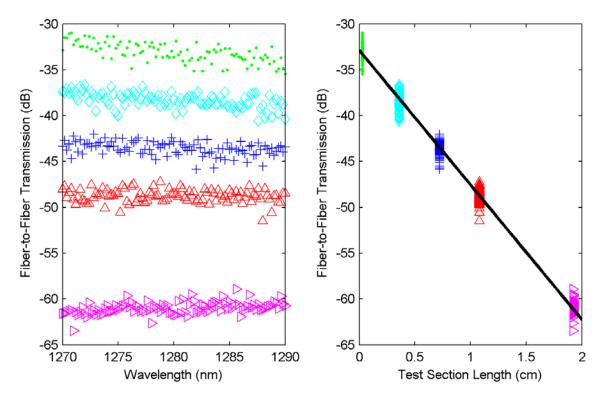

|               | veguide Loss Test Structures                        |     |

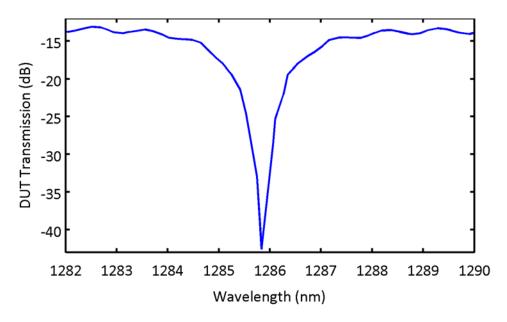

| 4.3.1. "Pa    | perclip" Waveguides                                | 139 |

|---------------|----------------------------------------------------|-----|

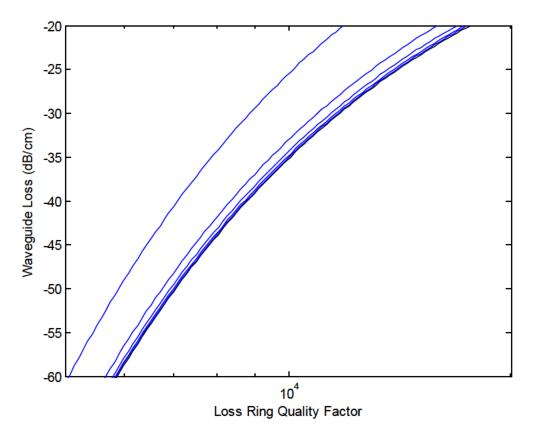

|               | ss Rings                                           |     |

| 4.4. Measure  | ed Waveguide Performance                           | 143 |

| 4.4.1. Sin    | gle-Crystalline Silicon Waveguides                 | 143 |

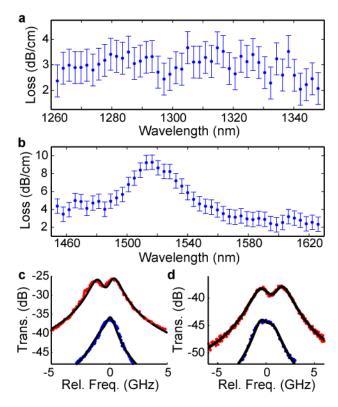

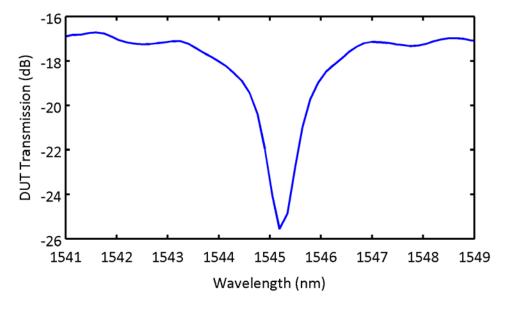

| 4.4.2. Zer    | o-Change Polysilicon Waveguides                    | 145 |

| 4.4.3. Opt    | timized Polysilicon Waveguides                     | 148 |

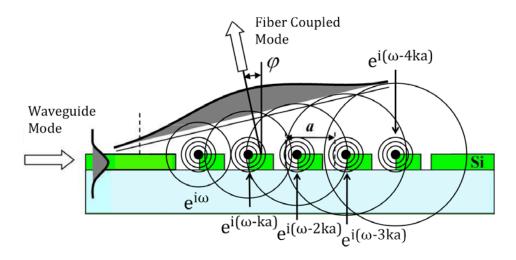

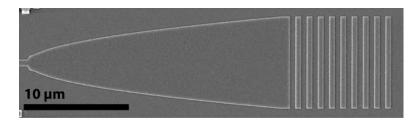

| 4.5. Vertical | Grating Couplers                                   | 164 |

| 4.6. Waveler  | ngth Division Multiplexing Filters                 | 176 |

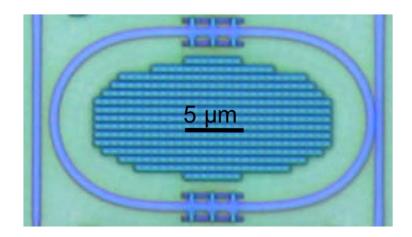

| 4.6.1. Fir.   | st-Order Ring Resonator Filters                    | 176 |

|               | ond-Order Ring Resonator Filters                   |     |

| 4.6.3. The    | ermal Tuning                                       | 181 |

| 4.7. Future V | Vork                                               | 185 |

| 5. Active De  | vices                                              | 187 |

| 5.1. Modelin  | g Framework                                        | 188 |

| 5.2. Electron | nic-Photonic Integration Platform                  | 189 |

| 5.3. CMOS In  | itegrated Modulators                               | 193 |

| 5.3.1. CM     | OS Process Constraints and Material Parameters     | 193 |

| 5.3.2. Sla    | b Contact Geometries                               | 194 |

| 5.3.3. Rib    | Contact Geometries                                 | 204 |

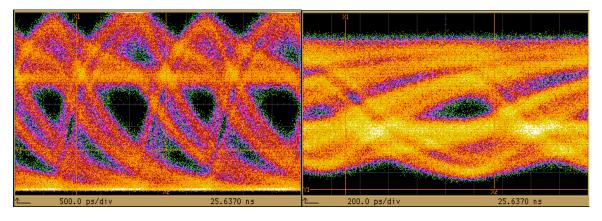

| 5.3.4. Hig    | rh-Speed Measurements                              | 208 |

| 5.3.5. Into   | egrated Driver Results                             | 211 |

| 5.4. DRAM M   | Iodulators                                         | 213 |

| 5.5. CMOS Si  | licon Germanium Photodiodes                        | 215 |

| 5.5.1. CM     | OS Process Constraints and Material Parameters     | 215 |

| 5.5.2. Ele    | ctrical Junction Design                            | 217 |

| 5.5.3. Bul    | k-CMOS Detectors                                   | 219 |

| 5.5.4. Thi    | n-SOI CMOS Detectors                               | 225 |

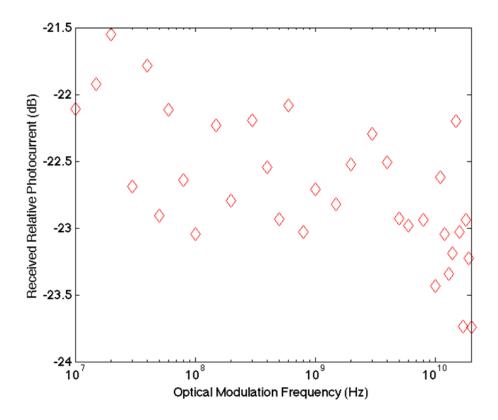

| 5.6. DRAM P   | hotodetectors                                      | 239 |

| 5.7. Conclus  | ion and Future Work                                | 241 |

| 6. Conclusio  | ns and Future Work                                 | 243 |

| 6.1. Core-to- | Memory Photonic Networks                           | 244 |

|               | Vork                                               |     |

|               | kaging                                             |     |

|               | velopment of Memory Photonic Integration Platform  |     |

|               | eroperability and Network Protocol Standardization |     |

| 6     | 2.4. Photonic-Friendly CMOS Foundry Process Modules                                                                         | 251 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|       | ppendix A: Testing of Vertically-Coupled Optoelectronics:                                                                   | 252 |

|       | 6μm                                                                                                                         |     |

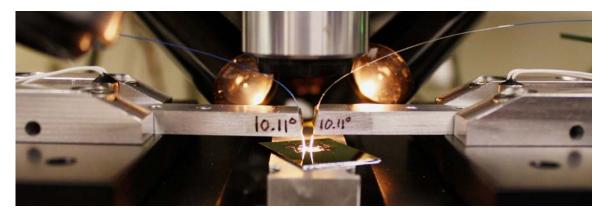

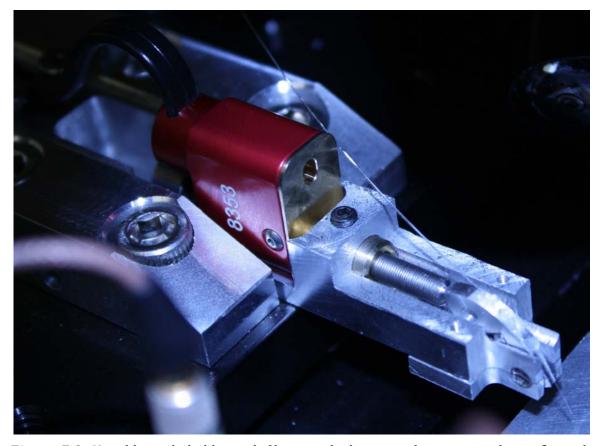

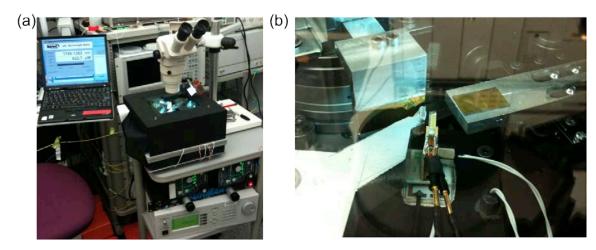

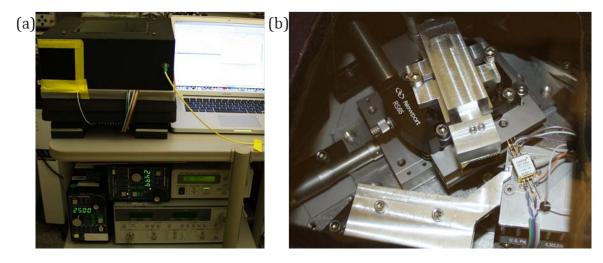

| 7.1.  | Vertical-Coupling Test Requirements                                                                                         |     |

|       | 1.1. Positioning Mechanics and Imaging Paths1.2. Compact, Variable-Angle Fiber Mounts                                       |     |

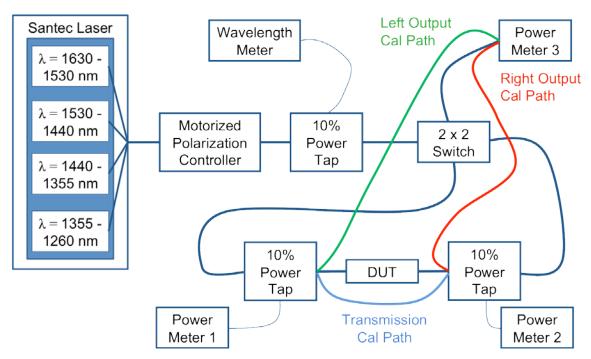

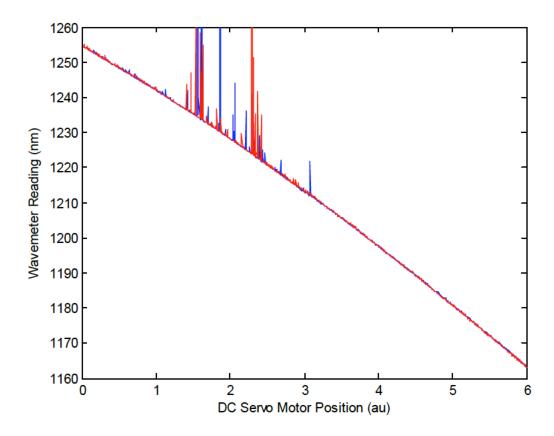

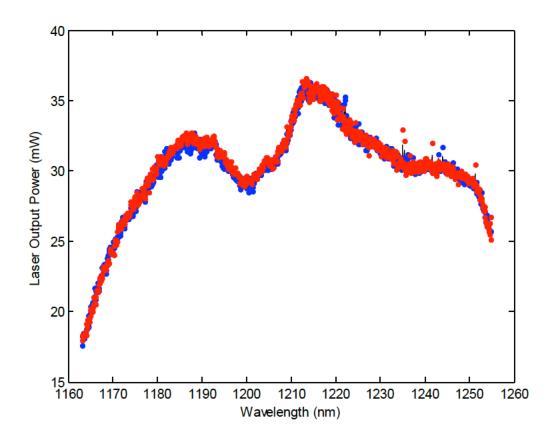

| 7.2.  | Calibrated Optical Measurement from 1260 nm to 1630 nm                                                                      | 258 |

| 8. A  | ppendix B: Post-Processing                                                                                                  | 261 |

| 8.1.  | Localized Substrate Removal                                                                                                 | 261 |

| 8.2.  | Full Substrate Removal                                                                                                      | 264 |

| 8.3.  | Substrate Transfer                                                                                                          | 265 |

|       | ppendix C: Design and Testing of an External Cavity Laser                                                                   | 260 |

|       | usly Tunable from 1150 nm to 1260 nm                                                                                        |     |

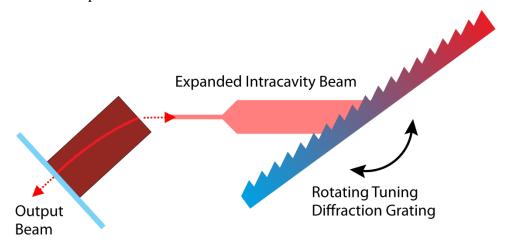

| 9.1.  | Theory of Operation                                                                                                         |     |

| 9.2.  | Cavity Optical Components                                                                                                   |     |

| 9.3.  | Cavity Construction                                                                                                         |     |

| 9.4.  | Cavity Alignment                                                                                                            |     |

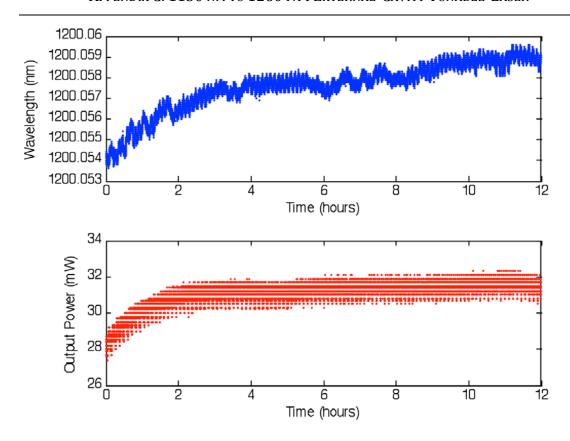

| 9.5.  | Measured Performance Characteristics                                                                                        | 274 |

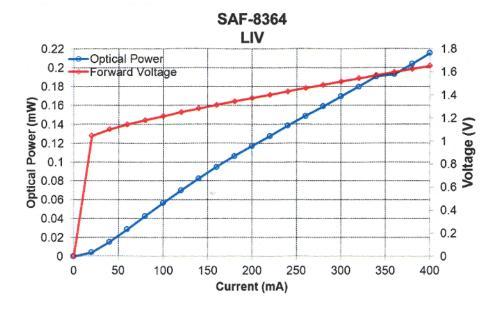

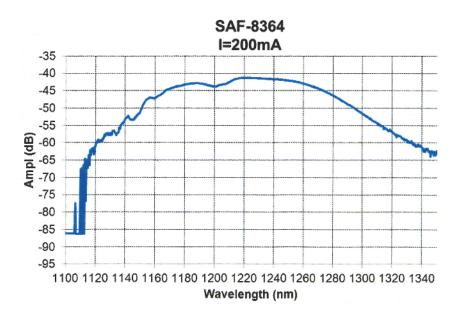

| 9.6.  | Manufacturer-Supplied Gain Media Test Data                                                                                  | 276 |

| 10. A | ppendix D: Code Reference                                                                                                   | 279 |

| 10.1. | Matlab Code                                                                                                                 | 279 |

| 10    | 0.1.1. first_order_ring_bank_32channel.m                                                                                    | 279 |

|       | 0.1.2. first_order_ring_single_depletion_modulator.m                                                                        |     |

|       | 0.1.3. calc_vertcoupl_fiber_coupling_omnisim_generated_fields.m<br>0.1.4. fit_omnisim_calculated_resonator_coupling_coeff.m |     |

|       | 0.1.5. paperclip_plot_loss_1280.m                                                                                           |     |

|       | 0.1.6. tmatrix_complex_anyangle.m                                                                                           |     |

|       | 0.1.7. tmatrix_complex_anyangle_MonteCarlo.m                                                                                |     |

| 10.2. | Sentaurus TCAD Scripts                                                                                                      | 301 |

|       | 0.2.1. Modulator (Generic) Junction Implant Process Simulation                                                              |     |

|       | D.2.2. Carrier Profile as a Function of Bias Device Simulation                                                              |     |

|       | Sentaurus Raphael Parasitic Calculation Scripts                                                                             |     |

| 10    | 0.3.1. Electromagnetic Calculation (RC2)                                                                                    | 303 |

| 10.3.2.    | Field Plotting (dplot)                                 | 304        |

|------------|--------------------------------------------------------|------------|

| 10.4. Cad  | ence Virtuoso P-Cell Photonic Layout CodeCommunication | 304        |

| 10.4.1.    | Global Functions                                       | 304        |

| 10.4.2.    | Shape Discretization Functions                         | 317        |

|            | Basic Geometry P-Cell Examples                         |            |

|            | Waveguide-Level Routing P-Cell Examples                |            |

|            | Simplified Top-Level User-Environment Cell Example     |            |

| 10.4.6.    | Component Description Language P-Cell UI Formatting    | Example373 |

| 10.4.7.    | Automatic P-Cell Layout Position Setting Script        | 375        |

| 10.5. Aut  | ofill Generation Scripts                               | 376        |

| 10.5.1.    | Generic Calibre Location Identification Script         | 376        |

|            | SKILL Fill Cell Array Insertion and Deletion Scripts   |            |

| Bibliograp | hy                                                     | 387        |

### 1. Introduction

Over the course of this thesis, I will present a design, layout and fabrication methodology to integrate nanophotonic devices within the three largest and most important electronics manufacturing processes: bulk CMOS, silicon-on-insulator (SOI) CMOS and DRAM. Importantly, the addition of the nanophotonic elements should not reduce the performance of the integrated transistors or require specialized processing in the CMOS cases that would limit the traditional foundry model of the industry. Integration within these processes not only extends the economies of scale present in the electronics industry to the ultraprecise fabrication required for nanophotonic devices, but also enables new classes of electronicphotonic integrated circuits (EPICs). Since the frequencies of operation of the transistors within these silicon-based processes are exceeding 300 GHz, it is a suitable platform for very high speed application specific functionality that has historically only been achievable with specialized III-V semiconductor based technologies. Additionally, although the lithographic precision is comparable to state-of-the-art nanophotonics fabrication results achieved by electron beam lithography, the lithographic throughput of CMOS is seven billion times higher. This offers the opportunity to dramatically lower the cost associated with such systems.

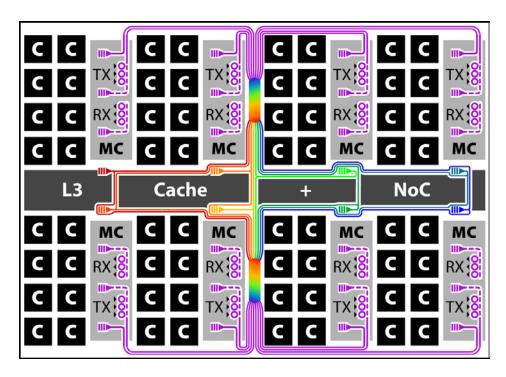

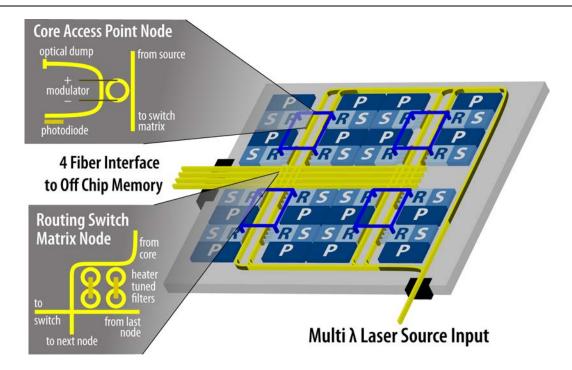

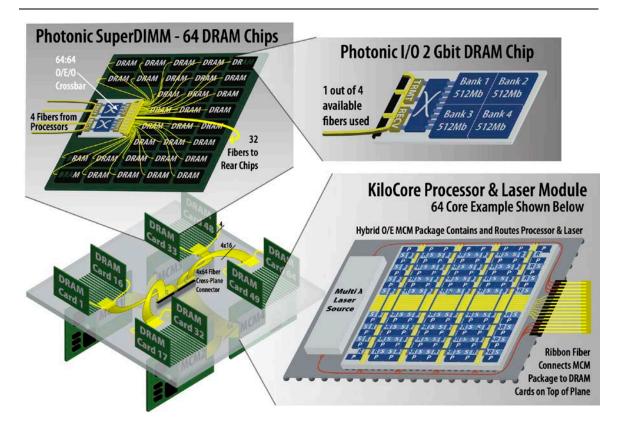

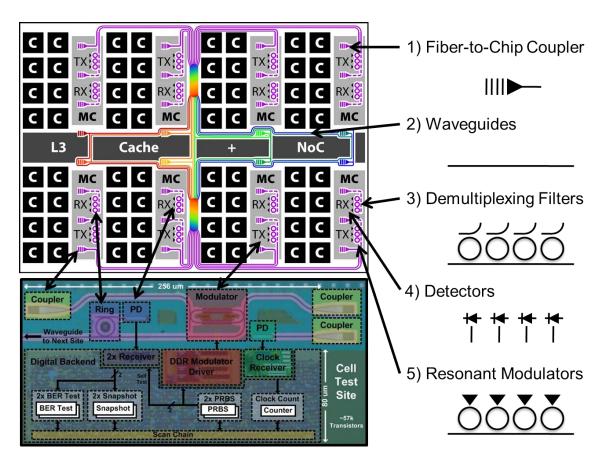

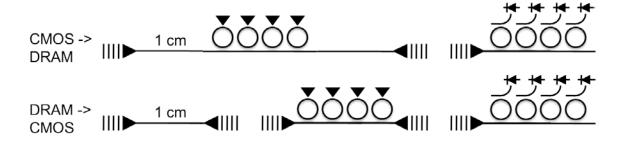

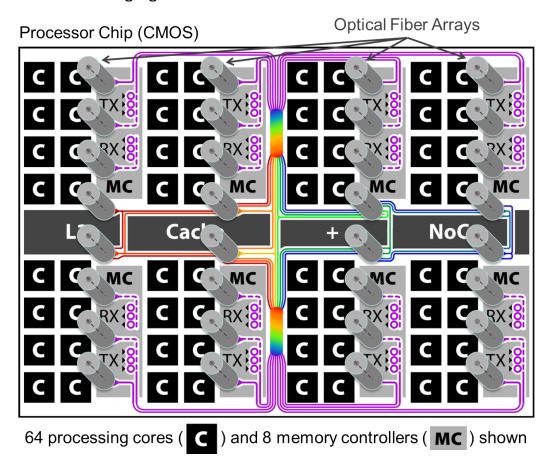

The application area that is the focus of much of this thesis is the integration of photonic links between the processing cores on a multicore CPU fabricated in either a bulk or SOI CMOS process and the main memory chips. The chief metrics of this system are energy efficiency and bandwidth density. This technology enables the communication interface to processing elements within future computing systems to fit within the required thermal budget and physical real estate footprint [1-4]. The required components are those of a typical wavelength division multiplexing (WDM) data link: modulators, receivers, add-drop filters and coupling interfaces. For all systems considered in this thesis, the laser source will remain off-chip and will not be integrated. Designs and initial test results for all of these components will be presented. The passive components are discussed in Chapter 4 and the active components will be discussed in Chapter 5. A detailed study of the microprocessor core-to-memory link application to set device specifications as well as to further motivate this work is included in Chapter 2.

The design and fabrication challenge for monolithic integration of photonics within an existing process is to identify a suitable set of layers that provide enough flexibility to produce all of the required devices. Due to the general-purpose model of CMOS foundries, the fabrication process steps are standardized for all users. Instead, the sole flexibility is in the design of the masks used to pattern these existing layers. This constraint has required the structures used to implement all of the photonic components to be rethought and adapted to fit inside the existing process box. There are two exceptions to this general principle. First, the layer structure of the electronic processes does not allow for the formation of a sufficiently thick low index under-cladding for the photonic devices in the standard process. To address this problem, a post-process localized substrate removal technology has been developed that does not affect electronic performance or compromise the foundry model. Second, the DRAM process manufactures a single product and therefore process technology is optimized to that purpose. This specificity allows for process tweaks and additions to integrate photonic devices with optimized processes by introducing steps compatible with the existing process flow. These changes do not present the problem they would in CMOS since there is no DRAM foundry system that forces process uniformity.

Another important aspect of the development of this platform is to integrate the layout of the photonic devices within the industry standard electronic design tools. In addition to enabling co-design of the photonic and electronic blocks, photonic device design preparation that is consistent with standard electronic layout is required for the foundry to accept the design for fabrication. Since the processing mask set for a state-of-the-art electronics process cost between two and five million dollars [5-7], it is necessary for small projects to join together to share this expense. This is common practice in the electronics industry. Therefore if the photonic designs can be produced such that they are indistinguishable from electronic designs, nanophotonics can piggyback on the much larger industry. Additionally, since the processing conditions are optimized for a specific set of design parameters, geometric rules must be verified to be within an acceptable range for successful fabrication. Since the on-wafer processing is shared with other customers, compliance with these rules is mandatory. Furthermore, the complexity associated with a mature fabrication platform results in between 40,000 and 60,000 rules that must be automatically verified in a process known as design rule checking (DRC) [8-11]. Care must be taken in the layout of the non-traditional, photonic

structures to ensure compliance. The details of the computer-aided design infrastructure that was developed to enable the fabrication of photonic devices using the standard electronic design infrastructure will be presented in Chapter 3.

For the remainder of this introductory chapter, further background and information relevant to the thesis work will be presented. The first sections will review prior platforms for opto-electronic integration. Next, a process overview of the CMOS electronics processes used for photonic integration will be presented. The general approach taken for fabricating photonic devices within these processes will be discussed next. The final section of the introduction will present a brief overview of each type of photonic device required for an integrated photonic link.

# 1.1. A Survey of Electronic-Photonic Integrated Circuits

The oldest optoelectronic platforms are based upon the periodic table group III-V element heterostructures such as InGaAsP. This platform has robust functionality including optical emission devices and high speed transistors. The semiconductor materials themselves have significant advantages to silicon such as high electron and hole carrier mobilities and direct bandgaps. The direct bandgap enables photon-mediated electron-hole interactions without requiring a phonon as in the case of indirect bandgap materials such as silicon. The higher equilibrium-state absorption and excited-state gain enables the creation of efficient lasers, modulators and detectors.

Indium phosphide photonic integrated circuits (PICs) have achieved complex functionality such as 40-wavelength 40-Gbps transmitters to enable 1.6 Tbps from a single chip using hundreds of integrated components [12-14]. Engineering of the epitaxial material stackup has allowed the same III-V wafers to be used for both electronic and photonic devices [15-17]. The compromises in the epitaxial stackup design has resulted in lower maximum frequency operation of the transistors with the highest demonstrated  $f_{\text{max}}$  operation of 150 GHz [16].

The chief difference from the silicon platforms that are the focus of this thesis is that III-V-based material systems are not used for large scale electronic circuits. The scale of integration is dramatically less than the billion-transistor-scale present in the silicon electronics industry. With device yields of  $\sim 95\%$  in GaAs ICs, the circuit yields for > 100 integrated transistors are unacceptable [18]. As such, it is not a suitable platform for the creation of computer systems that require the best-available integration scale [19-21]. Ongoing work for III-V logic transistor

demonstration has not enabled significant VLSI circuit production in that material system [22, 23].

The difficulties facing the high-yield production of III-V electronic integrated circuits has required electronic-photonic integrated circuits that require large numbers of integrated transistors to focus on silicon-based material platforms. Fundamentally, the first challenge is that light-emission and absorption in silicon is a significantly less efficient process than is available in III-V material systems. Some groups have tried to engineer light emission from silicon by the introduction of defect states [24, 25]. Others have focused on building lasers using materials that may be epitaxially grown on a silicon substrate [26-28]. The final option for laser source integration has been to bond direct band gap layers to the silicon wafer to integrate gain materials where required [29, 30]. For the most part, however, most silicon-based optoelectronic integration platforms have instead relied upon non-integrated laser sources as will be the case in this work.

Silicon electronic-photonic integrated circuit platforms have been demonstrated in other work by modifying the fabrication processes of older CMOS electronic foundries [31-34]. These platforms have been able to demonstrate integration scales of similar numbers of photonic devices as III-V PICs while including orders of magnitude more transistors [35]. Since the CMOS processing technology used has lagged at least five years behind the state-of-the-art, these platforms still do not provide a suitable method to fabricate photonic links monolithically integrated into microprocessors and memory.

# 1.2. Other Examples of Zero-Change CMOS Integration

To enable access to state-of-the-art CMOS processing technology, compliance with the existing process is required to leverage the economies of scale already present in the industry. Since billions of dollars are required to develop state-of-the-art CMOS processes, it is prohibitively expensive to develop customized processes. Significant research effort has already been performed with the goal of integrating non-standard devices within CMOS processes without requiring changes to the infoundry processing. At the outset of this thesis work, the demonstrated device set was limited to photodiodes operating above the silicon bandedge [36-47]. Although impressive performance in this application space, 1.24 A/W and multi-gigabit operation at 850 nm [47], had been achieved, no waveguides, modulators or photodiodes operating below the silicon bandedge had been demonstrated. At the

time of this writing, a zero-change CMOS demonstration with a metal-clad waveguide was reported [25]. Light emission and detection were observed between two proximate diodes in the silicon substrate. The demonstrated platform differs dramatically from the work in this thesis and does not have comparable scalability.

The first successful optical integration topology that did not require modifications to the CMOS processing was the bonding of parallel optics modules of VCSELs and photodiodes on top of separately fabricated silicon VLSI chips [48-53]. The applications for the technology has varied from neural network implementation [54], to chip-to-chip interconnect [55, 56] and to short-distance data communication within servers [50]. It is unclear, however, how such an approach can be scaled to enable the scale of optical connectivity required for the computer systems discussed in Chapter 2.

Alternatively, continued deposition and patterning of optical components on top of normally fabricated CMOS chips has been demonstrated [19]. This approach provides a viable alternative to the work presented in this thesis, but does have some drawbacks. The fundamental challenge in the demonstration of optical integration in this method is that the maximum processing temperature is limited to less than 450 °C. A photodetector with dark current below 1  $\mu$ A has not been demonstrated in this platform [19]. Additionally, since the inserted photonic devices do not share any processing steps with the electronic devices, the final solution may be significantly more expensive to manufacture. Other tradeoffs including increased thermal impedance are discussed in Section 1.6.

Instead, the goal of this project is to monolithically fabricate the photonic devices using the existing front-end process alongside the transistors in a state-of-the-art CMOS foundry. A similar approach has been taken by the MEMS community in prior work [57-62]. The actual devices to sense either sound or acceleration are fabricated in the standard process steps. After complete fabrication in the CMOS foundry, additional "post-CMOS" processing is often required to allow the sensor suspension. A similar approach has been followed for photonic integration and will be presented over the course of this thesis.

#### 1.3. CMOS Process Overview

Due to the high cost of the tools required to produce state of the art electronics, standardization and collaboration have produced significant consistency across CMOS foundries. The customer may select from a small menu of standard options

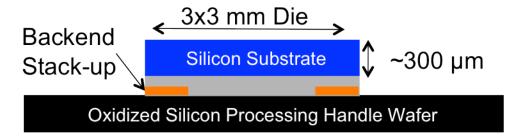

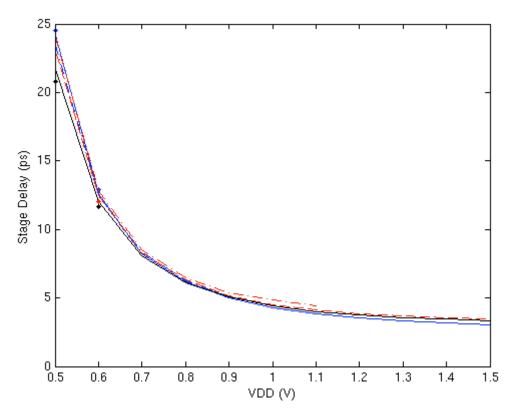

such as the number of metal layers, presence of specific passive components and transistor optimizations. Beyond this flexibility, the process is completely fixed in production processes due to the high cost of modifications. CMOS foundries are divided into two main groups depending on the starting substrate used. In the bulk CMOS process, which represents 92% of the market, the active device layer is fabricated directly on this silicon wafer. In the SOI CMOS market, the active device layer is a separate 50-200 nm silicon thick layer that is separated from the handle wafer by a 100-300 nm thick SiO<sub>2</sub> layer. Although this structured starting wafer has a higher cost, typically \$1000 as compared to a \$300 bulk wafer [63], the reduced transistor capacitance and altered device physics offers a 20-35% performance increase [64].

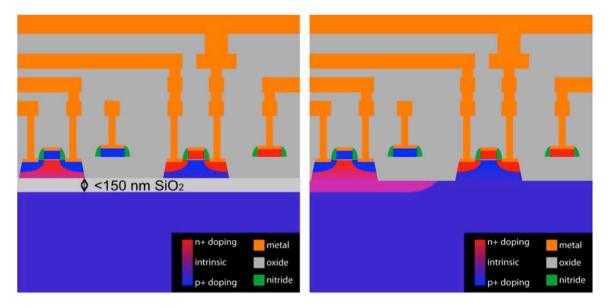

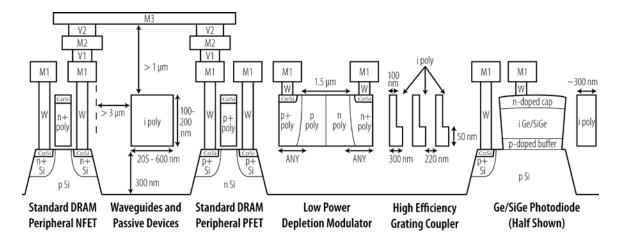

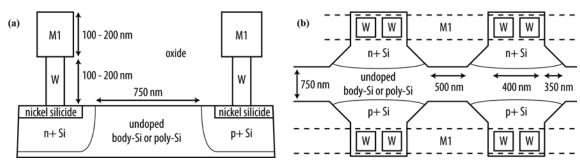

**Figure 1.1** Cross section cartoons for (a) the SOI CMOS process and (b) the bulk CMOS process.

The buried oxide (BOX) layer of the SOI wafer does present a slight tradeoff by increasing the thermal impedance of the wafer. The ability to fabricate a large number of transistors in a small area has resulted in most large circuits such as microprocessors operating in a thermally-limited regime. The total power that may be dissipated on a single chip is therefore limited to approximately 100 W today. Since the thermal conductivity of silicon dioxide is  $\sim \! 100$  times lower than silicon, replacing 200 nm of silicon with oxide is roughly equivalent to increasing the substrate thickness by 20  $\mu$ m. Considering an average silicon thickness after back-

grinding of approximately 300  $\mu$ m, the addition of the SOI layer results in less than a 7% reduction in substrate thermal conductivity. Since almost 50% of the power is dissipated through the metallization instead of the substrate, the total impact of the BOX layer on the effective thermal impedance for the circuits should be less than 5%. Similar to these concerns of the impact of the SOI wafer, any modification of the CMOS process must also consider the impact on the total thermal impedance. Reductions to the effective thermal conductivity will directly impact the total power that may be dissipated on-chip and therefore reduce the total number of transistors that may be integrated together to form complex circuits.

At the highest-level, the CMOS fabrication process is divided into two halves, the front and back ends. The field effect transistors (FETs), diodes and all other semiconductor devices are fabricated in the front-end and metal interconnections are fabricated in the back-end. The chief differences between the two are the temperatures and materials used. In the front end, high temperatures, in excess of 1050 °C, are common, but the available materials are restricted to a select set that are known to yield high quality electronics. The back end processing is relatively free of material restrictions, but the maximum allowable processing temperature is restricted to approximately 450 °C to prevent diffusion of the metal layers. A brief overview of these flows, focusing on aspects relevant for photonic devices will be presented below. Further details can be found from any number of introductory electronics books [65, 66].

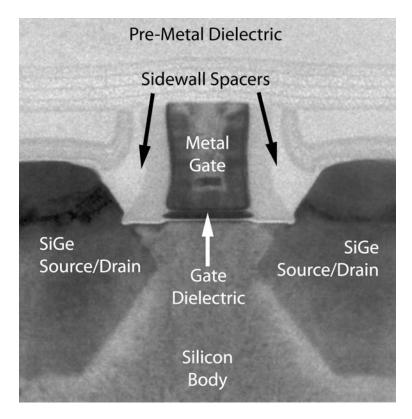

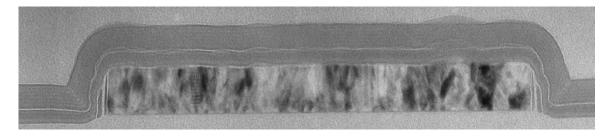

The field effect transistor (FET) at the heart of the front end process consists of a heavily doped polysilicon gate separated from the doped single-crystalline silicon channel by a 1-2 nm dielectric layer. The silicon channel is abutted by oppositely doped source and drain regions. A cross-sectional TEM of an advanced FET as would be found in a current microprocessor chip is shown in **Figure 1.2**. Each transistor is separated from its neighbors by a oxide-filled trench known as shallow trench isolation (STI) as shown in **Figure 1.1**. The front-end processing to define the transistors utilizes precise projection lithography to mask a large number of deposition and implant steps. The alignment between the transistor gate and the implants that define the source/drains is controlled by a dielectric spacer. The spacer of nitride and oxide is formed by the isotropic deposition of layers that are anisotroptically etched to leave material only on the sidewall of the transistor gates. By implanting both before and after spacer formation, the complex doping profiles for advanced transistors can be realized.

Figure 1.2 Scanning TEM of a bulk-CMOS 45nm scaled p-type FET transistor. Source: Intel.

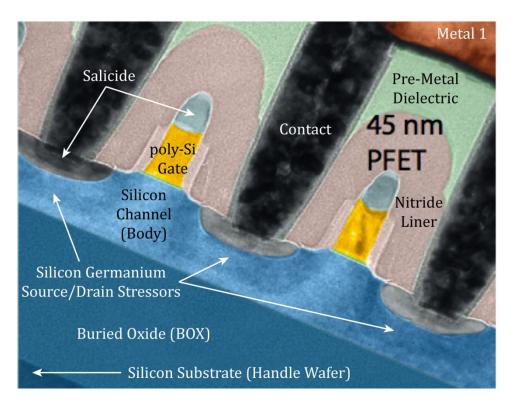

A relatively new addition to CMOS front end processing is the epitaxial growth of low mole fraction silicon germanium source/drains in p-type FETs. The SiGe is intended for transistor stress engineering, but also provides the photonic device designer with material that has a smaller bandgap than silicon for photodiode formation. The Ge mole-fraction is typically between 25% and 30% to produce a thin coherently strained layer that imparts compressive stress on the silicon channel to increase hole mobility [67]. The SiGe stressor regions are visible in both **Figure 1.2** and **Figure 1.3**.

The material sheet and contact resistances are reduced by the formation of a silicon-metal composite known as a silicide. Since the STI separates the transistors from each other and the sidewall spacers separate the transistor gate from the source/drains, all silicon transistor contacts are separated by dielectric layers. As a result, a self-aligned process can be used to metalize the silicon. A metal such as nickel or cobalt is blanketly deposited on the wafer. The wafer is then annealed between  $500\,^{\circ}\text{C}$  and  $600\,^{\circ}\text{C}$  to react the metal and the silicon. The unreacted metal is then etched away to form isolated silicide regions on all transistor contacts. The

self-aligned nature of this process has resulted in the term salicide as a short-hand for self-aligned silicide.

Next, a nitride liner is deposited to encapsulate the front-end transistors as shown in **Figure 1.3**. The first reason that the nitride layer was added to the front-end process was to provide a diffusion barrier to isolate the transistors from any contamination that may diffuse out of the back-end process. Since the stress of the layer is determined by deposition conditions, the nitride layer can also be used for further transistor stress engineering. This is typically used to provide tensile strain to the n-channel transistors to improve electron mobility.

**Figure 1.3** Scanning TEM of a SOI-CMOS 45nm scaled p-type FET transistor with surrounding. Source: IBM.

Once the transistors are defined, the process progresses to the back-end processing by depositing a thick layer of dielectric, typically phospho-silicate glass (PSG). This planarizes the wafer for further processing and isolates the sensitive device layer from contamination by materials used in the back-end. At this point, narrow square plugs are etched to make electrical contact to the devices in the silicided region and filled with a refractory metal, typically tungsten. The cross-section of a finished front-end process is shown in **Figure 1.3**. These initial contact

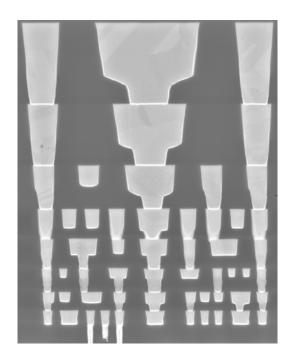

points then need to be wired together to create the final circuit by the copper dual-damascene process. To define each interconnection layer, a dielectric is deposited and then etched to pattern the desired planar wires. Then a thin diffusion barrier metal, typically TaN, is deposited and the copper is uniformly plated. The copper is then chemically-mechanically polished to form the wires and planarize the stackup. In order to ensure uniform thickness across the wafer, strict pattern density rules are enforced such that a consistent ratio of metal to oxide is maintained. A cross-section of such a finished stack-up is shown in **Figure 1.4**. To provide the necessary data and power connections to the increasingly dense device layer, as many as 13 of these back-end wiring layers are currently required. The total interconnect thickness in modern processes is greater than 8 µm.

**Figure 1.4** Cross sectional scanning electron micrograph showing the interconnecting metal layers in the backend stackup of a finished microprocessor. Source: Intel.

The external interfaces to the package are then formed on top of the copper wiring in either a wirebond or area array configuration. In the wirebond case, gold wires are bonded to aluminum pads at the perimeter of the circuit to the package connections. In the area array, or flip-chip, case, C4 solder balls are deposited on top of the aluminum pads that are arranged into a 150  $\mu$ m pitch array to mate to a matching array in the package. In both cases, the finished CMOS chip is encapsulated

in a 5  $\mu$ m thick polymer layer consisting of some combination of BCB and polyamide with openings only over the aluminum interface pads. The final in foundry step is to cut the wafers into individual die containing only each customer's design by a dicing saw.

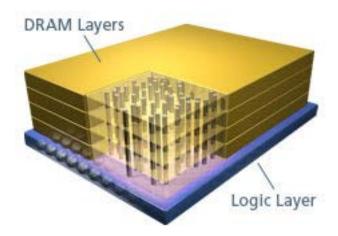

# 1.4. DRAM Process Comparison

DRAM memory modules are divided into two main sections: the storage array and peripheral access devices. The storage banks are comprised of a 2D arrays of capacitors isolated from many shared access wires, known as bit lines, by individual access transistors. The presence or absence of charge on the capacitors, which range in value between 15 fF and 50 fF depending on technology generation, stores either a data '1' or '0'. A single capacitor per bit line is then accessed for reading or writing data by raising or lowering the gate voltage of the connecting transistors that share a common word line across the bank. Data from all of the bit lines is then read out by sense amplifiers. These sense amplifiers and all circuitry to control the bit and word lines are the peripheral access devices located outside the storage array. Further peripheral circuitry provides data I/O to connect the DRAM to external components such as a memory controller or CPU. The peripheral circuitry resembles the bulk-CMOS process that has already been discussed. The storage array devices requires significantly different processes to fabricate the capacitors that are frequently known as containers. The total process flow must then be shared between these two regions and jointly optimized for acceptable performance for both circuit types.

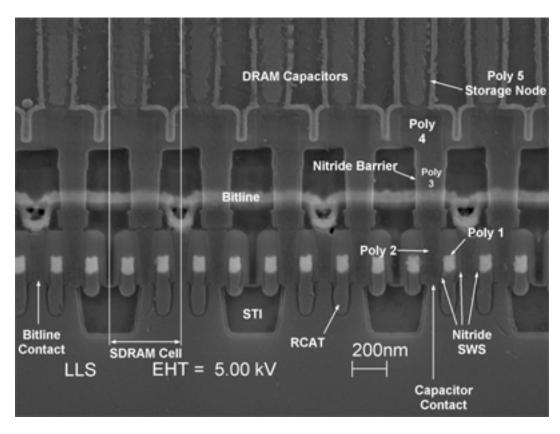

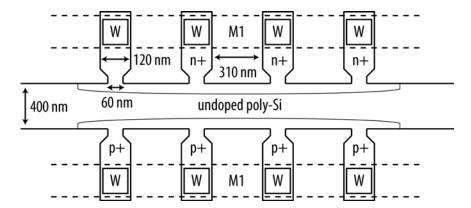

Although the general process flow and required tools of the DRAM manufacturing process greatly resembles that of CMOS, there are several key differences, both technical and logistical, worth noting here. As a primary constraint, the low cost model of memory manufacturing prohibits the use of the expensive starting substrates that are required for SOI-based processes. Instead, the memory process utilizes similar starting silicon substrates to bulk-CMOS processes. Technically, high density capacitors are fabricated in the pre-metal dielectrics separating the transistors from the metal layers. The capacitors themselves and the connections to them are constructed by up to five different polysilicon layers to create a front end process of far greater complexity than that found in traditional CMOS processes as shown in **Figure 1.5**. In contrast, the back end is much simpler containing only two or three metal layers due to the simpler circuit topologies.

Finally, due to low off-current requirements, transistor performance metrics such as saturated current drive and maximum switching frequency are reduced by approximately two process generations compared to CMOS.

**Figure 1.5** Cross sectional scanning electron micrograph showing the Samsung 45 nm DRAM front end process with stacked DRAM capacitors above the transistor layer. Source: EE Times.

Since the business model of the memory manufacturers differs greatly from the foundry model common in the CMOS industry, the integration constraints differ greatly. First, processing masks are never shared among different projects. Second, the processing steps are customized for optimal performance of every product. These factors enable process modifications to optimize photonic devices. The chief challenges are to minimize the additional cost of integration and to prevent modifications of electronic device characteristics. Any additional processing steps required for photonic integration should then be designed as the minimum number of simple modules that can be inserted into the existing memory process without shifting transistor characteristics.

## 1.5. Standard Process Integration Methodology

For many important EPIC systems, electronic performance and density are paramount. As has been discussed, previously proposed integration platforms compromise these desirable features that exist today within state-of-the-art electronic processes. To eliminate these barriers, we have developed a monolithic integration platform that neither alters the dominant business models present in the CMOS and DRAM industries nor degrades electronic performance.

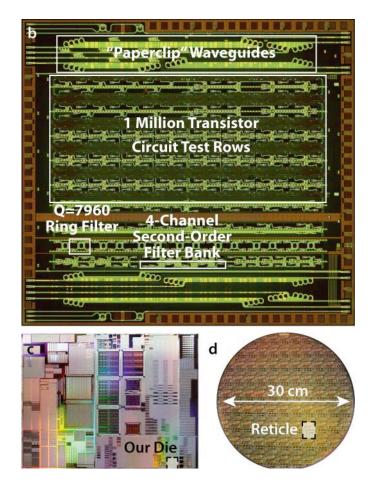

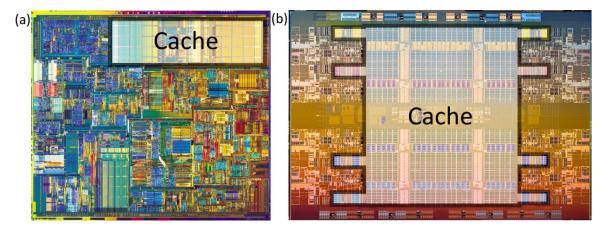

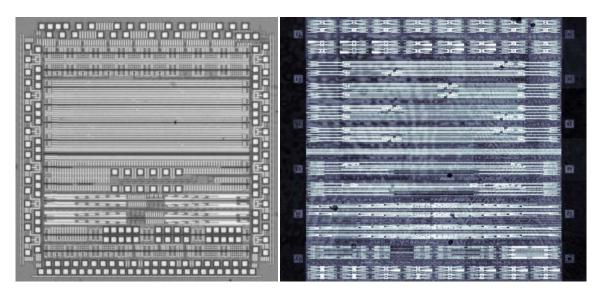

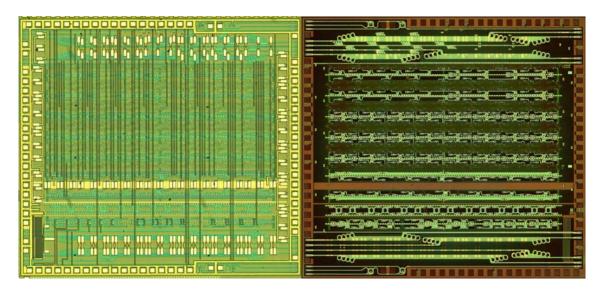

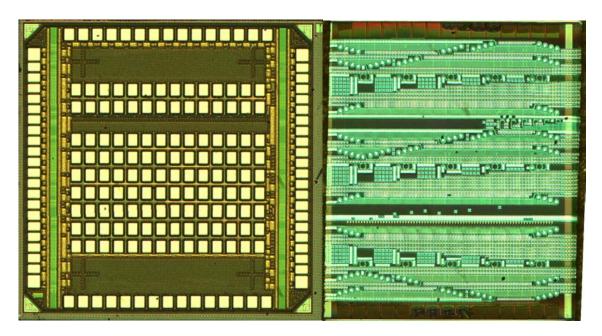

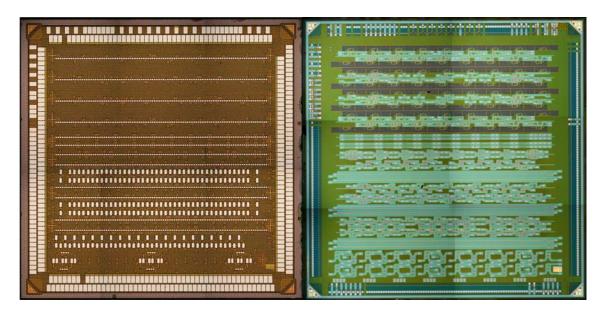

**Figure 1.6** (a) Integrated photonic-electronic die produced in a 32 nm bulk CMOS process. Die shared a (b) mask set with a full reticle of standard electronic projects submitted by other customers. All in foundry fabrication steps were performed in the standard electronic process on (c) a 30 cm wafer.

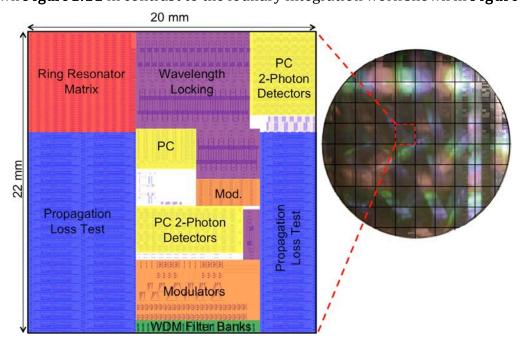

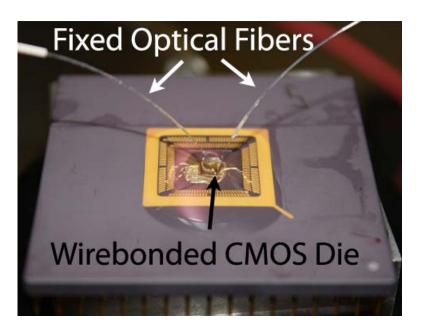

For CMOS integration, we have acted as a standard multi-project electronics customer at Texas Instruments and IBM, requiring zero in foundry process changes. Our integrated electronic photonic designs share mask sets and all in foundry

processes with standard electronics customers as shown in **Figure 1.6**. This approach allows us to leverage the existing infrastructure and economies of scale established by the \$250B yearly revenue silicon semiconductor electronics industry. For DRAM integration, we have worked closely with Micron Technology to insert photonic device layers within the existing manufacturing flow that do not degrade performance and cause minimal product cost increases. In contrast to the CMOS case where the work took place on the production manufacturing lines, we have pursued a short-flow methodology with DRAM integration to test the photonic devices in a less expensive process representative of the full production line.

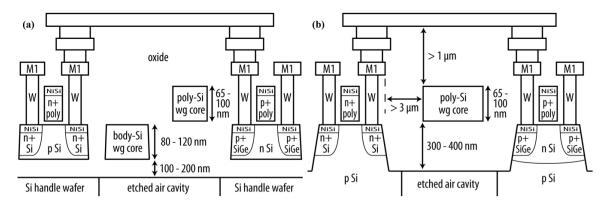

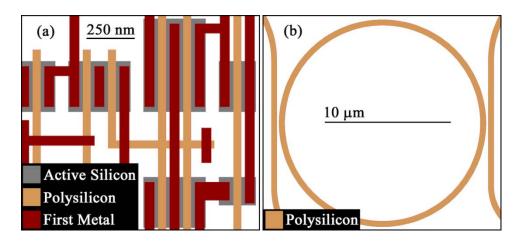

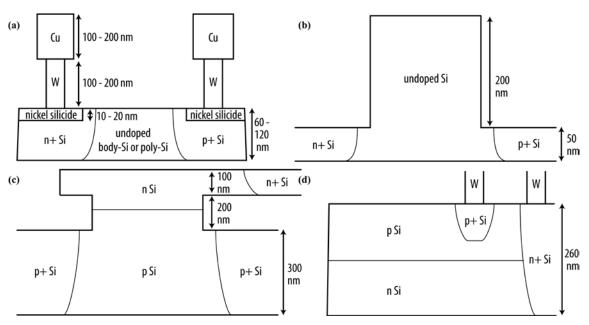

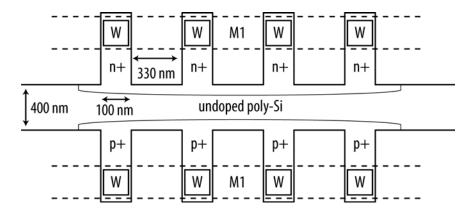

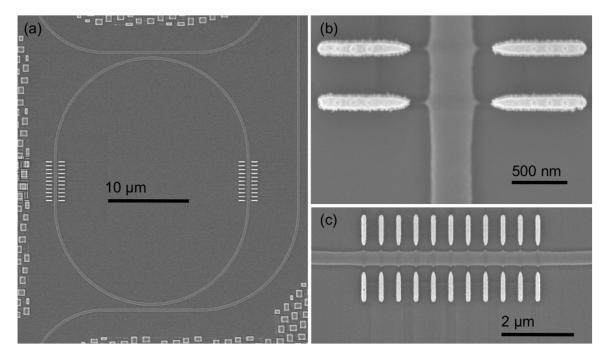

## 1.5.1. Waveguide Core Formation in Standard CMOS

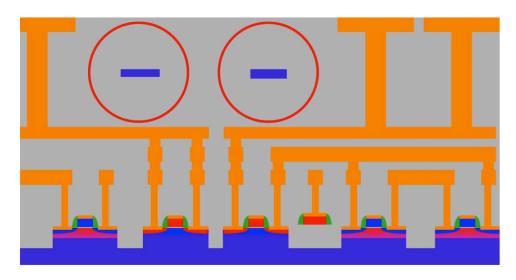

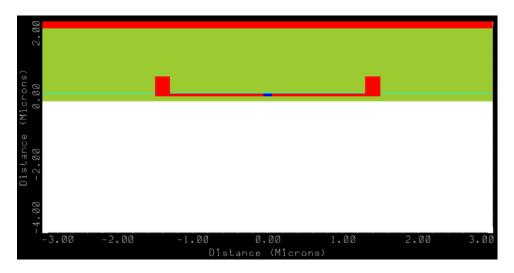

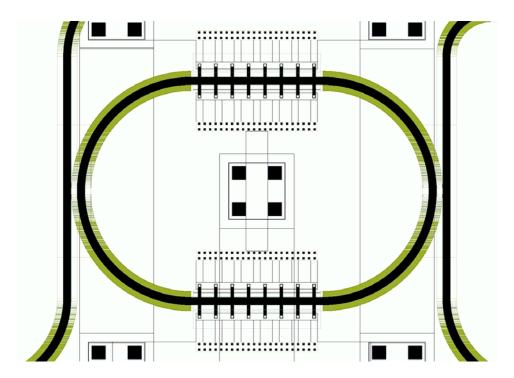

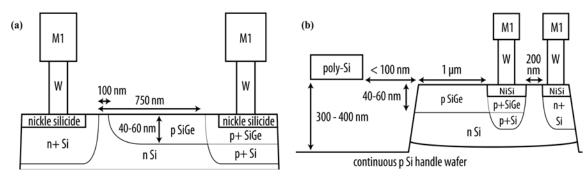

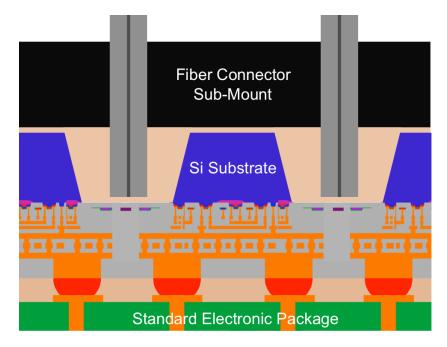

In our monolithic integration platform, the waveguide cores are implemented in the patternable front-end silicon layers. In the SOI-CMOS process, there are two such available layers: the single-crystalline silicon transistor body layer further referred to as the body-Si layer, and the polycrystalline silicon transistor gate layer further referred to as the poly-Si layer. In the bulk-CMOS process, the transistor body is fabricated directly in the handle wafer leaving only the poly-Si layer available as the waveguide core. By configuring the surrounding material stack-up using available design layers [7], the EPIC platform cross-sections, shown in **Figure 1.7**(a) and **Figure 1.7**(b) for the SOI- and bulk-CMOS processes respectively, are available in standard electronic foundries.

**Figure 1.7** Monolithic EPIC cross-sections integrated within (a) sub-65 nm node SOI-CMOS and (b) bulk-CMOS processes.

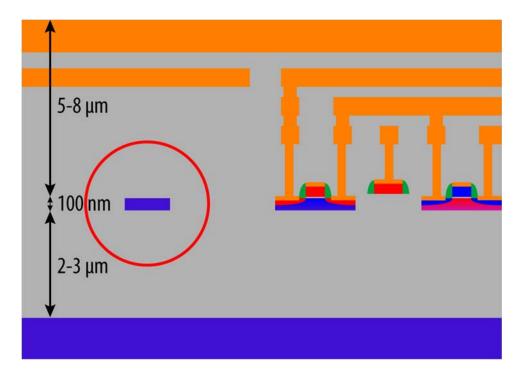

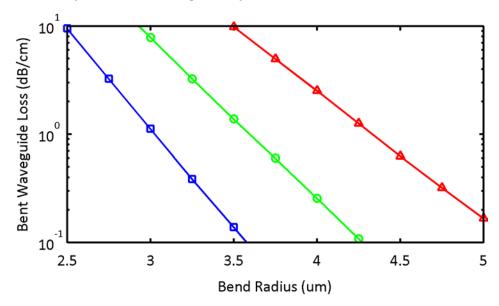

Utilizing the existing layers constrains the waveguide core thicknesses to values chosen to be optimal for transistor design at the current process generation. Instead of the ~220 nm thickness currently used in silicon photonic projects, the body-Si layer thickness ranges from 80-120 nm and the poly-Si layer thickness ranges from 65-100 nm depending on process generation. For passive photonic devices, this limits the minimum allowable bend radius for a given operating wavelength. SOI processes offer the designer flexibility to vertically stack the body-Si and poly-Si layers, separated only by a nanometer-scale oxide, for tighter bends where necessary. Results demonstrating high performance passive photonic devices fabricated in this platform will be presented in Chapter 4.

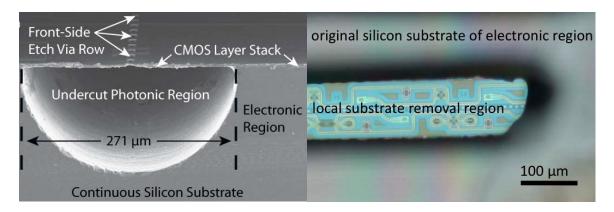

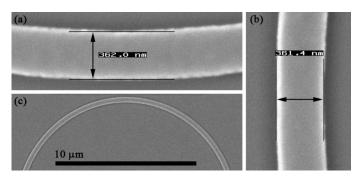

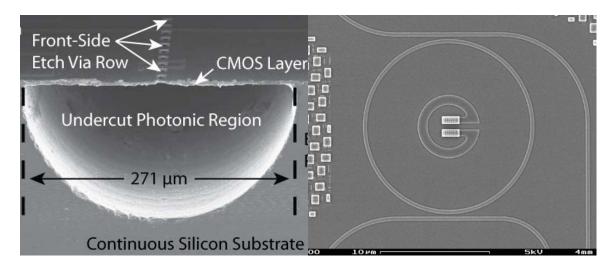

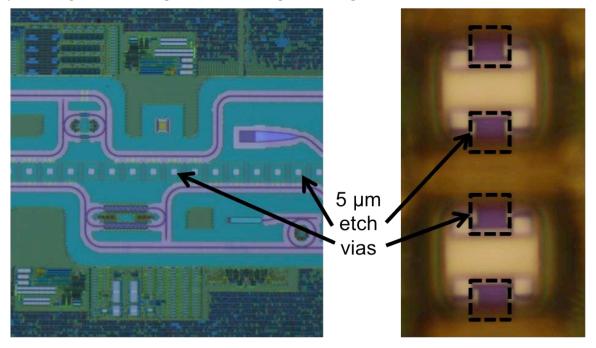

**Figure 1.8** (a) Cross-sectional scanning electron micrograph (SEM) of a 28nm bulk-CMOS die after localized substrate removal in the photonic region [70]. Total undercut width of 271  $\mu$ m is more than 3x the largest design width to demonstrate film stability and planarity. (b) Optical micrograph of back-side etched local substrate removal region of a 45nm SOI-CMOS die.

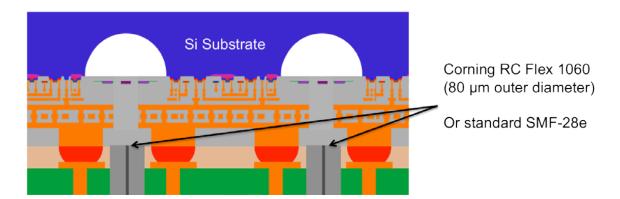

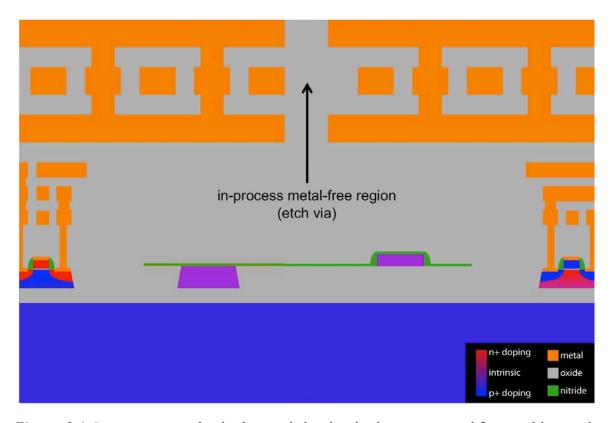

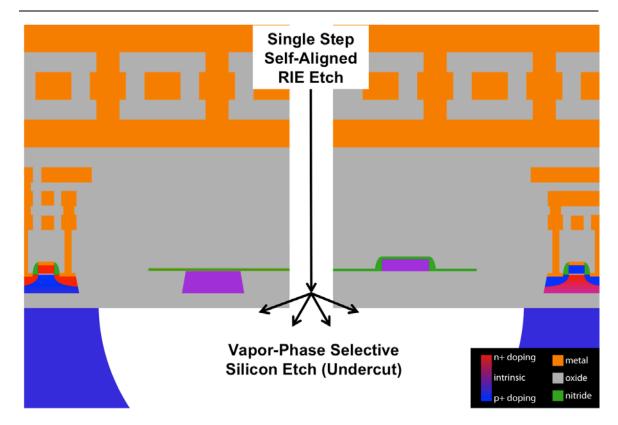

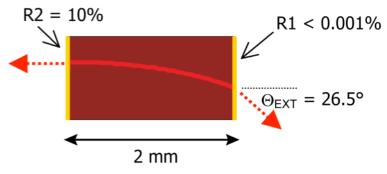

#### 1.5.2. Localized Substrate Removal

The oxide layers below the polysilicon layer in a modern bulk process, known as the shallow trench isolation (STI), and the BOX below the single crystalline silicon layer in a modern SOI process are all thinner than 300 nm. These thin oxide layers would cause propagation loss greater than 500 dB/cm due to the leaky optical mode [68]. To prevent this problem without process modification or the use of specialized starting substrates, a scalable, post-process front side localized substrate removal technology has been developed [69]. The end result of this process is an air pocket under the photonic regions and an unmodified local environment in the electronic regions as shown in **Figure 1.8**. Alternatively, back-side local substrate removal can

be used achieve the same end goal as also shown in **Figure 1.8**. Further details on required post-processing techniques are provided in Appendix B.

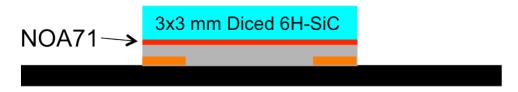

## 1.5.3. DRAM process integration

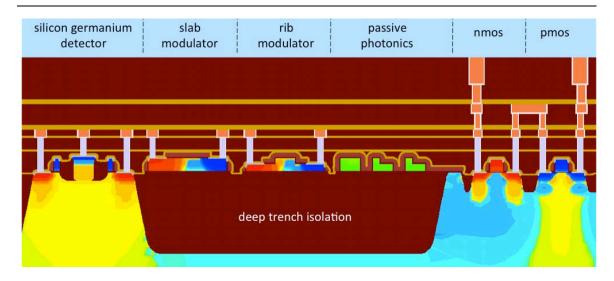

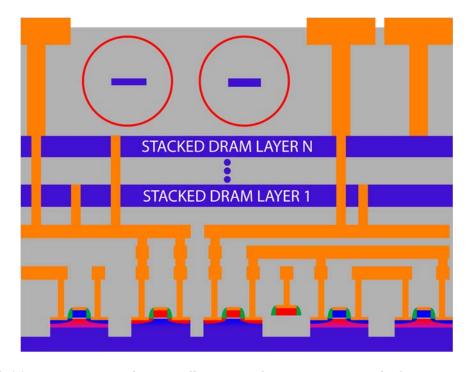

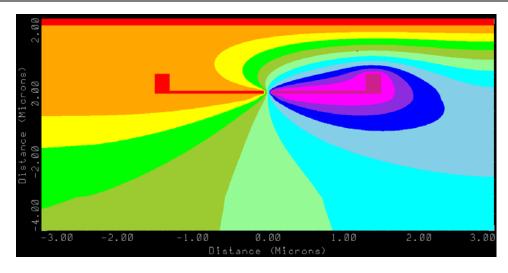

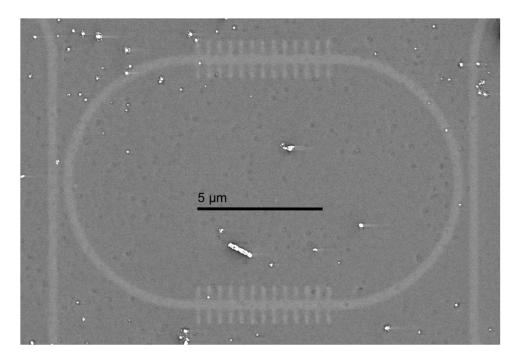

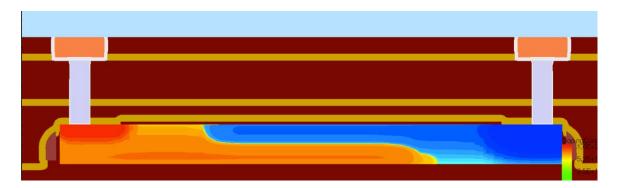

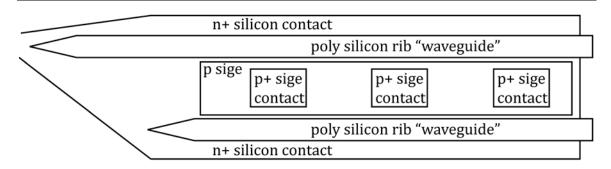

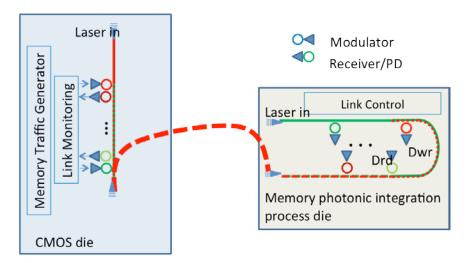

The flexibility of the process development available within DRAM enables a slightly different process integration methodology. Similar to a bulk-CMOS process, the polysilicon used for the transistor gate formation is used as the high index waveguide core. Additional process modules can be added to aid in device creation. For example, instead of requiring local substrate removal, deep trench isolation may optionally be added to the process to eliminate the requirement of further post-processing to enable optical functionality. Further functionality for device creation can be added by adding a partial etch to enable two thicknesses of the waveguide core. A basic set of the required photonic devices that must be integrated in the process is shown in **Figure 1.9**.

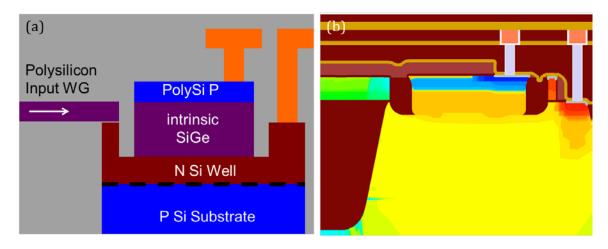

**Figure 1.9** Monolithic DRAM photonic cross-sectional integrated device proposal.

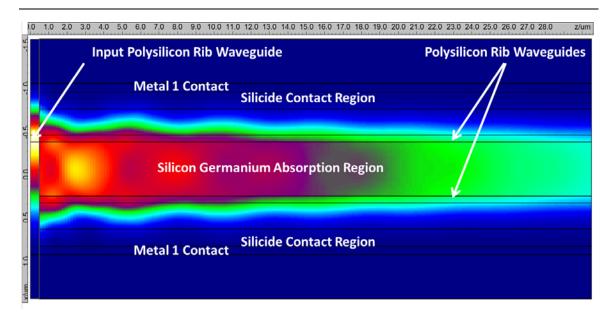

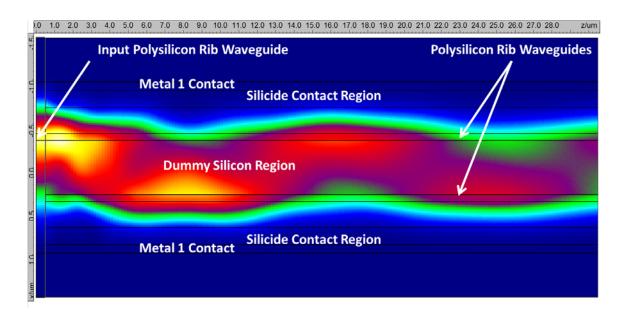

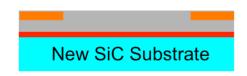

To test the required processes and demonstrate monolithic integration, a modified memory process has been developed by adding photonics-specific processing modules into an existing product manufacturing line. To simplify the fabrication during process development, all steps associated with the memory array process are not part of the integration flow. Instead, only the steps associated with the peripheral transistor process are explicitly performed. A technology computer aided design (TCAD) simulation of the complete proposed process is shown in **Figure 1.10**.

**Figure 1.10** Monolithic DRAM integration process TCAD simulation.

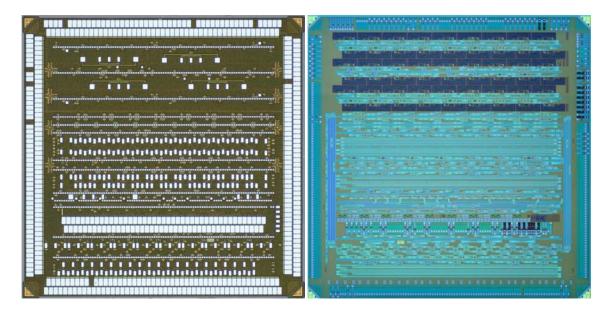

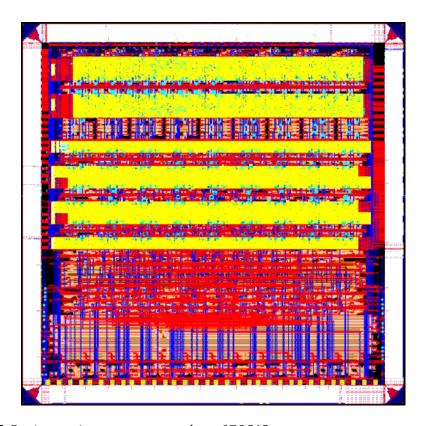

The requirement to develop a new fabrication process requires dedicated masks instead of being able to share masks with other projects as is in a CMOS foundry. The design size on silicon has ranged from 20mm x 22mm to 26mm x 33mm. The dramatically increased area relative to the ~9mm<sup>2</sup> CMOS test chips enables a more thorough study of process parameters as well as parametric design variation. An example project consisting of a complete reticle set and resulting processed wafer is shown **Figure 1.11** in contrast to the foundry integration work shown in **Figure 1.6**.

**Figure 1.11** Labeled design environment screen shot from the design environment and finished wafer identifying the stepped reticle fields.

## 1.6. Alternative Approaches to Electronic-Photonic Integration

Due to the widely-recognized value of integrating silicon-based electronic and photonic devices, several alternative integration platforms have been previously proposed in the literature. These approaches can be broken down into three main subgroups that I will address individually.

#### 1.6.1. Thick-SOI

The first approach is to modify the starting substrates and in foundry processes to integrate photonic devices within the CMOS front end [33, 68, 71-79]. Successful implementations of this approach include the modified 130 nm SOI-CMOS process line at Freescale that was developed in cooperation with Luxtera [31, 80-82]. The chief drawback with any approach that requires specialized processing is that modifications isolate photonics process development from the standard electronics foundry infrastructure. This requires the photonics developers to fully support the cost of the process line as well as individual production masks. The process development work to modify the wafer-level fabrication steps then occur not only the non-recoverable engineering cost of the modifications, but also an opportunity cost of occupying a fabrication line that may be used for high-volume manufacturing of electronic circuits.

To date, front-end monolithic integration has required non-standard silicon-on-insulator (SOI) starting wafers in which the buried-oxide (BOX) thickness is an order of magnitude thicker than is used in electronic SOI-CMOS processes. The resulting cross section is illustrated in **Figure 1.12**. The thicker BOX may degrade the performance of nanoscale transistors via drain-induced barrier lowering (DIBL) [83, 84]. Additionally, the thermal impedance of the thicker BOX impacts the circuit performance and requires the recalibration of many wafer-level processes [85]. Increasing the buried oxide thickness from under 200 nm to above 2  $\mu$ m increases the total thermal impedance of the substrate by an order of magnitude. First of all, the higher thermal impedance reduces the allowable power dissipation per unit area of the integrated circuits for a maximum transistor operation temperature. This may limit the scale of the integrated circuits as many important application areas such as microprocessors operate in a thermally-limited regime today [86, 87]. Second, the higher thermal impedance increases the thermal time constant for the individual transistors. This would therefore increase the relative importance of

thermal history effect and increase the difficulty of designing reliable circuits [88]. Finally, the increased thermal impedance may require a recalibration of on-wafer processing steps [89]. A hybrid approach that utilizes non-uniform buried oxide thickness across the wafer may resolve some to these constraints that currently limit the usefulness of such a platform [90]. Although this platform has been demonstrated in an academic setting, further process development is required in an industrial setting as this approach requires a radical change to the initial front-end process of a CMOS fabrication line.

**Figure 1.12** Cross-section schematic illustrating the thick-SOI CMOS platform.

Many high-performance silicon photonic devices have been demonstrated in a thick-SOI monolithically integrated platform. Integrated waveguide loss in the single-crystalline silicon layer of 1.7 dB/cm has been reported [75]. Epitaxially grown germanium photodiodes have demonstrated 0.85 A/W with a 26 GHz bandwidth [91]. The lowest power reported ring-resonator modulator achieved  $\sim$ 3 fJ/bit efficiency at 12.5 Gbps operation [92].

#### 1.6.2. Backend, On-CMOS processing

The second approach is to introduce new steps into the backend of the CMOS process to fabricate photonic devices on top of the existing stackup as shown in **Figure 1.13** [19, 93-97]. This offers some benefit for standard foundry compatibility as some process development for this approach may be done as post-processing on existing electronic designs. Additionally, no processing modifications are required in the performance critical front end of line as in the previous approach. However, long-term usefulness of such a platform still remains in question. Since no processing is shared with the existing electronic devices, many additional steps will be required, potentially increasing the product cost. This additional processing needs to also reverse the standard CMOS trend of reduced backend precision. Beyond a convenience issue of reducing process complexity, the lithographic imaging environment far from the silicon wafer surface is degraded by the topology and non-uniform reflections introduced by the underlying material stackup. This may present a significant technological barrier to manufacturing fabrication sensitive nanophotonic devices with high yield in this manner. Additionally, the thermal budget of the electronics may be reduced since this approach still requires the formation of additional thick layers in the top thermal path. Finally, this approach would still represent a significant process customization that would require a large photonics user base to support the development and share mask costs.

**Figure 1.13** Cross-section schematic illustrating the backend integration platform.

The backend photonic platform is composed of the least mature set of photonic devices. All wafer-level processes must have peak temperatures below 450 °C to prevent diffusion of the back end metal layers. This constraint places strict limits on allowable processing technologies. Either low temperature nitride or amorphous silicon waveguides are available. Amorphous silicon waveguides with  $\sim 1.2$  dB/cm propagation loss have been demonstrated [98]. Low temperature nitride waveguides have achieved similar waveguide losses [99, 100]. In addition to siliconbased modulators, electro-optic polymer modulators are also available since the thermal budget of the process is dramatically reduced. Nitride ring resonators with 8 dB extinction ratios at 20 Gbps that require 6 V drive signals have been demonstrated [100]. Assuming that laser-crystallization can enable polysilicon modulators, the best literature results include a 2.5 Gbps modulator with 10 dB extinction and 950 fl/bit energy dissipation [101]. The biggest missing component is a suitable photodetector. Defect-state polysilicon resonant photodetectors achieving 0.15 A/W may be integrable [102]. Otherwise, polycrystalline germanium MSM Shockley-barrier photodetectors are an available option, but suffer from large dark currents. The lowest leakage current reported for such devices is 77 μA [103].

## 1.6.3. Hybrid Integration

The final major proposed approach for photonic device integration is a modification of the thick-SOI platform. Since the modifications required to integrate photonics in the CMOS front end reduce the density and performance of integrated electronics, a layer stacking approach in which a separately fabricated largely photonic layer would be bonded to the standard state-of-the-art high density electronics CMOS layer as shown in **Figure 1.14** [104-108]. Two variations of this approach are differentiated by whether or not the photonic layer includes drive transistors or relies on transistors in the standard CMOS chip. If drivers are not included in the photonic layer, the additional parasitic of 20-25 fF in state-of-the-art face-to-face bonding demonstrations [107] would roughly triple the intrinsic capacitance of the modulator and photodiode components [108] and decrease link energy efficiency. If drivers are included in the photonic layer, the two layers could efficiently communicate with each other, as well as perhaps additional electronic layers bonded in the stack, through copper vias fabricated using 3D integration technology. Both approaches eliminate the high cost of modifying state-of-the-art electronics processes. However, as a result, the photonics designer no longer has

access to include such state-of-the-art transistors in the photonic layer. Additionally, the presence of the additional layer bonded in the top thermal path of the electronics reduces the allowable thermal budget even more than the backend integration approach. The largest problem with this approach is still the high costs associated with 3D integration which result from several well known issues: the separate fabrication of the two active layers, the additional complicated equipment and processing required for the bonding, and the coupling of the yield of the two chips and the bonding process.

**Figure 1.14** Cross-section schematic illustrating the 3D integration platform.

Since the 3D integration platform enables separate optimization of the photonic components from electronic functionality, best-in-class photonic results are available. Waveguide losses in shallow-ridge-etch silicon waveguides are as low as 0.274 dB/cm [80]. Ring resonator modulators achieve 12.5 Gbps operation and enable 135 fJ/bit energy efficiency with hybrid-integrated CMOS drivers [109]. Integrated germanium photodiodes achieve >20 GHz bandwidth with 1.05 A/W at 1550nm [110]. These results that were all demonstrated in similar waveguide cross-sections at Kotura represent the highest performance photonic platform available.

The electrical interface to all of these photonic components must also be considered as well. To accurately compare any interconnect topology, the total link from clocked, logic-level latch on one chip to clocked, logic level latch on the other must be considered. Further details on the implications of this requirement and introduction to the circuit design concepts required to understand the tradeoffs will be discussed in Chapters 2 and 5. For initial discussion of integration approaches, it is sufficient to first generally consider the important aspects of the connections between the photonic and electrical devices. For devices that require the driving voltage to switch billions of times a second, as is the case for the modulators considered for this thesis, the total capacitance of the switching node largely determines the energy dissipation. As such the connection parasitics, or stray wiring capacitance, must be minimized. To first order, this means that the physical distance between the driving circuits and active photonic components must be minimized. Further, this same stray capacitance directly impacts the sensitivity of the photoreceiver circuit. Since the photodetector transduces the absorbed photons into current, the initial signal to be sensed is a finite charge per data bit. In CMOS circuitry, the measureable signal can always be expressed as a voltage, or voltage difference on specific transistor gates. Since the transistor gate, as well as the wiring parasitics and the photodetector itself, can be modeled to first order as a capacitor, minimizing the total capacitance maximizes the effective signal resultant from the received optical bit. The stray capacitance therefore impacts the net sensitivity of the optical link as well as the energy efficiency. These constraints therefore dictate that the magnitude of parasitics present at the connections between the electronic and optical devices is an important figure-of-merit for an integrated optical link fabrication platform.

# 1.7. Integrated Optical Components

Waveguides, fiber couplers, filters, modulators and detectors have all been demonstrated over the course of this thesis. No effort towards integrated laser sources was undertaken or is anticipated as a system need for interchip communication. Since optical fibers are connected to provide the chip-to-chip communication link, optical power delivery can be provided from an off-chip source. There appears to be no technical benefit for laser source integration in such a system. Although the fiber coupling losses may be avoided on-chip, higher efficiency may be achieved off chip while avoiding numerous technical hurdles including

cavity isolation, power delivery and thermal stability of an integrated source. In contrast, other systems such as tightly integrated microwave photonic circuits or intrachip-only photonic links that do not explicitly optical fiber connections to the electrical die may benefit dramatically from such laser integration.

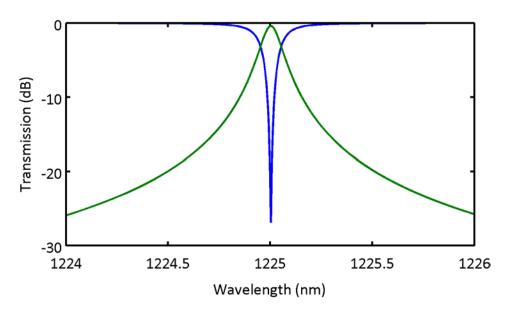

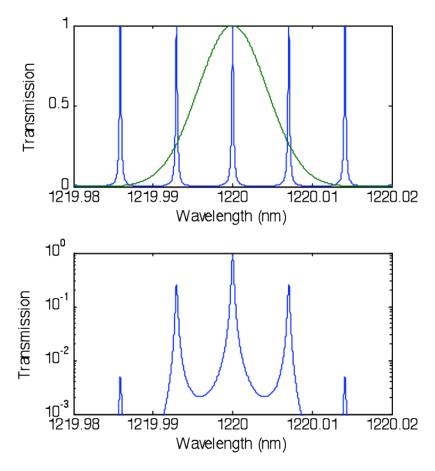

The nominal operation wavelength for integrated photonic devices will be focused in the 1.2 µm to 1.3 µm window for use with the integrated silicon germanium photodetectors. For the primary system application of photonic links in a processor to memory network, there is no requirement to adhere to standard telecommunication bands near the fiber loss minima of 1.55 µm. Further, from a purely technical laser perspective, it is in fact preferable to operate at shorter wavelengths. In nearly every parameter – threshold current [111], output power [111], efficiency [112], temperature dependence [111, 113], and reliability [114] better laser performance has been achieved near 1.3 µm as compared to 1.55 µm. Scaling to yet shorter wavelengths is limited by the silicon bandgap of 1.12 eV at which point low-loss silicon-core waveguides are impossible. Many photonic devices in this work are also designed for the 1.55 µm window due to the availability of higher quality test equipment at that wavelength in our labs. Additionally, since the scaling of various phenomena such as propagation loss as a function of wavelength provides insights to the underlying physics, device performance has been characterized over a wider wavelength range than is necessary to implement a given system.

#### 1.7.1. High-Index-Contrast Waveguides

At a basic level, the integrated waveguides consist of an undoped, unmetalized silicon or polysilicon strip that is surrounded by at least a micron of low-index, low-optical-loss material in all directions. Total internal reflection at the interface of the high-index silicon and low-index cladding such as silicon dioxide provides optical confinement. The geometries and materials for transistor formation, combined by the localized substrate removal post-processing where required, provide the necessary flexibility to remove extrinsic loss sources such as metals and other high-index layers from the proximity of the well localized mode.

Fundamentally, the waveguides formed for this work strongly resemble the silicon photonic waveguides that have been used by many research groups in previous work. The main differences in this work are the exact silicon layer thickness and the operating wavelength. Most silicon photonic work has previously

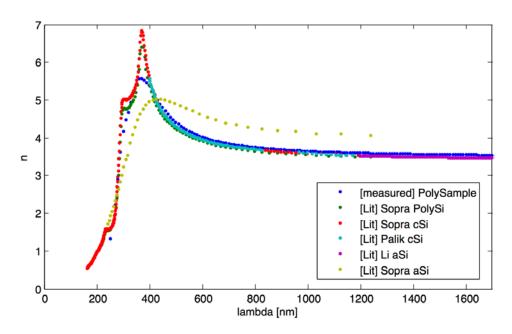

relied on 200-300 nm silicon layer thickness and operated at a wavelength of 1550nm. In this work, the operating wavelength is significantly shorter, between 1200nm and 1300nm and the layer thicknesses for integrated waveguides have ranged from 65nm to 225nm. DRAM emulation process, the target polysilicon thickness of approximately 200nm matches well with previous silicon photonic work. For the scaled-CMOS processes, the layers used to fabricate the transistors are significantly thinner.

To date, the best published propagation loss values for similar strongly-confined silicon waveguides formed by photolithography and dry-etching have remained in the 2 dB/cm to 3 dB/cm range [68, 71, 115]. Since the dominant loss mechanism is the sidewall scattering of the waveguides, specialized techniques such as the masked oxidation of silicon to form the waveguides has resulted in waveguide losses down to 0.3 dB/cm [116, 117]. Alternatively, shallow ridge etches using standard processing techniques have also demonstrated reduced waveguide losses down to 0.2 dB/cm [118].

**Figure 1.15** Mode solving simulations for the first-order (solid lines) and second-order (dashed lines) modes for wavelengths of 1200nm (blue), 1250nm (green) and 1300nm (red). The second-order mode's effective index is compared to the oxide cladding with a 1.45 refractive index.

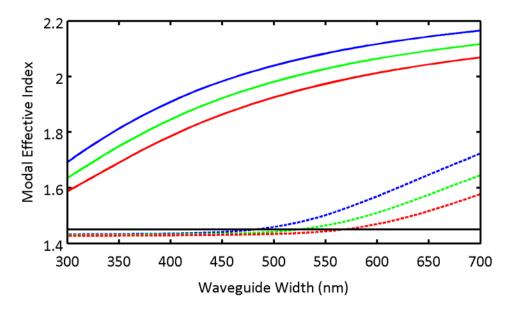

To examine waveguide characteristics in the thin-core silicon layers, we will focus on the geometry found in partially-depleted silicon-on-insulator (PD-SOI)

CMOS processes. Using layer thicknesses for such a standard wafer from SOITEC, 145 nm BOX and 80 nm silicon thicknesses, the properties of a strongly-confined singlemode waveguide can be simulated as is discussed in further detail in Chapter 4. First, the effective indices of the first and second order modes are simulated as a function of waveguide width as shown in Figure 1.15. Since the boundary conditions of the simulation domain artificially permit higher order modes when they would be physically forbidden, the cutoff of the second-order mode is taken to be the intersection of the solved effective index with that of the n=1.45 oxide cladding.

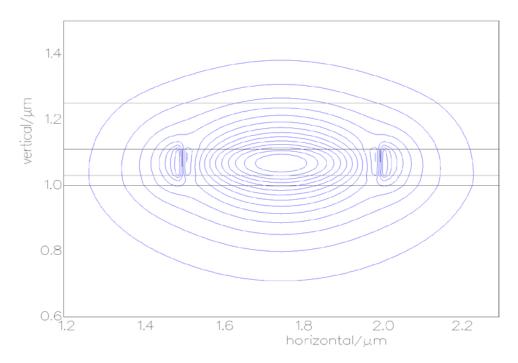

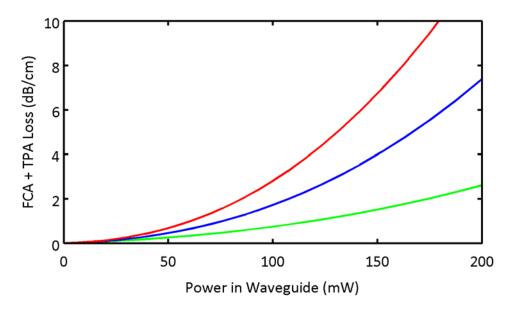

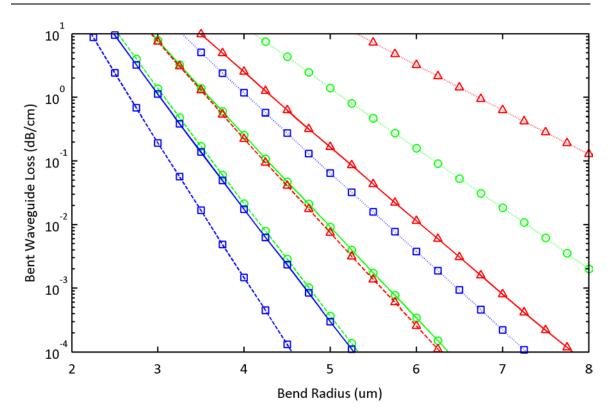

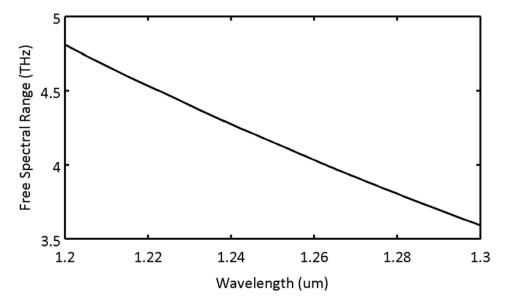

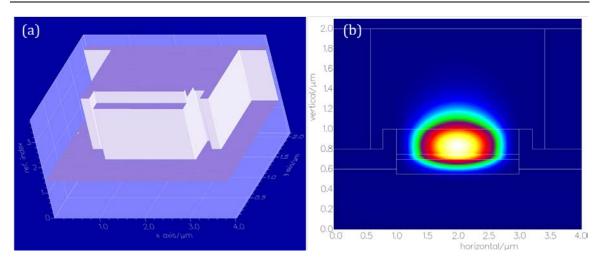

For the described layers of the PD-SOI wafer, a silicon core size of 80nm by 500nm represents the strongest confined singlemode waveguide in the 1200nm to 1300nm wavelength range and will be used for the purposes of generic integrated device simulation for the rest of this thesis. The resulting optical mode, shown in Figure 1.16, confines the guided light to a small cross-sectional area of 0.159  $\mu m^2$ . The small mode area is advantageous for high-density on-chip routing, but does increase the relative importance of non-linear phenomena. The optical power that is able to be guided by such an integrated waveguide is therefore limited to approximately 30mW.

**Figure 1.16** Optical mode simulation for 500nm wide single mode waveguide with an effective index of 1.98 and a group index of 3.4 at 1250nm. Optical mode area is 0.159  $\mu$ m<sup>2</sup> with a fill factor of 41% and a confinement factor of 70%.

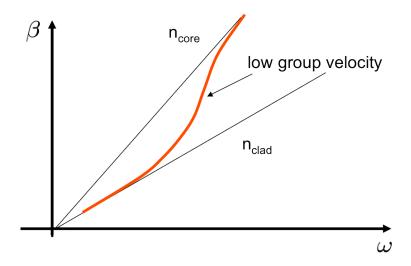

The strongly-confined mode of such a high-index-contrast waveguide results in the increased importance of other linear phenomena that are often neglected in low-index contrast photonic devices. Due to the high index contrast difference between the core and cladding materials, the effective index is a strong function of the relative confinement between the silicon and oxide regions. Since this confinement can be changed by either the wavelength or a change in dimensions, in addition to the exact properties being strongly dependent on fabrication, the waveguides are strongly dispersive. The effective geometric dispersion is also maximized in the strongly-confined single-mode region of greatest interest for the integrated photonic devices. This can be schematically understood by plotting the modal wavevector as a function of optical frequency as shown in Figure 1.17. As the waveguide enters the strong-confinement region as a function of frequency, the modal effective index changes from following the cladding dispersion relation towards following the core dispersion relation.

**Figure 1.17** Dispersion diagram for an optical mode of a strong-confinement waveguide.

The wavevector dispersion relation as a function of electro-magnetic field frequency,  $\beta(\omega)$ , determines several important waveguide characteristics. First, the phase velocity is given by:

$$v_{\phi} = \frac{\omega}{\beta} \tag{1.1}$$

Since the modal effective index is then the speed of light in vacuum divided by the phase velocity, this strong dispersion is evident in the simulated modal effective

indices for the various wavelengths of the 500nm wide waveguide mode shown in Figure 1.15. The velocity of power transfer may then vary from this phase velocity in such a dispersive system. Since the single-frequency representation of the electromagnetic field is non-causal, the power transfer velocity can be obtained by considering the velocity of a wave packet. The envelope function of the wavepacket then processes at the constructive interference condition of the multiple frequencies that compose the pulse. This velocity of power transfer, known as the group velocity, is then given by the inverse of the slope of the dispersion relation:

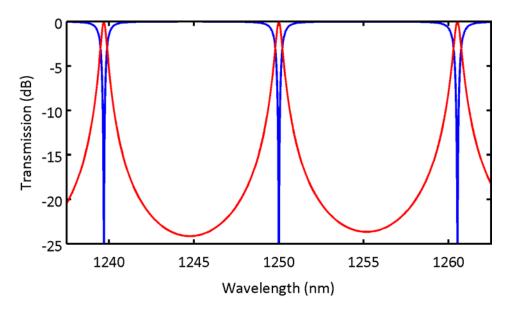

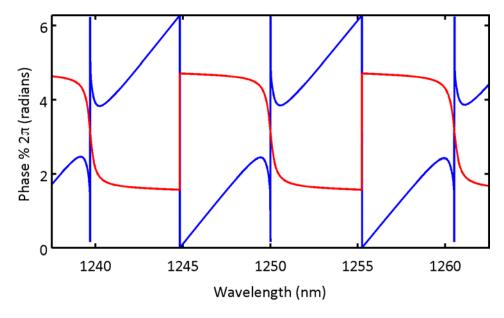

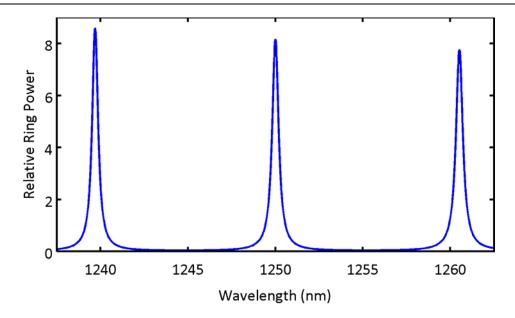

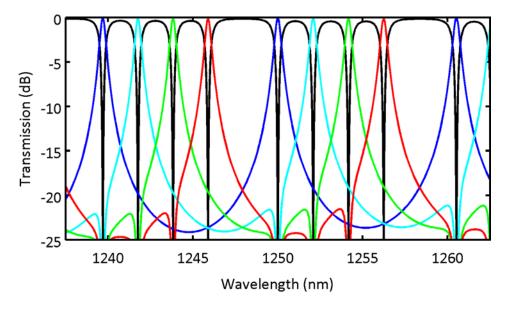

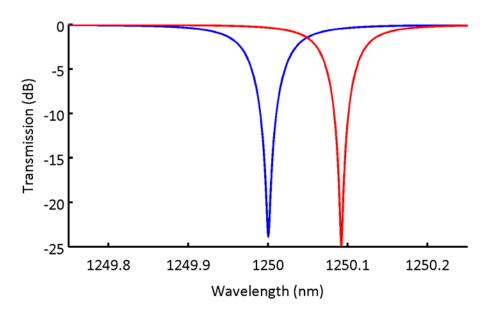

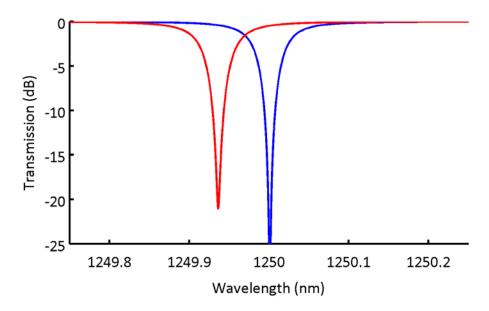

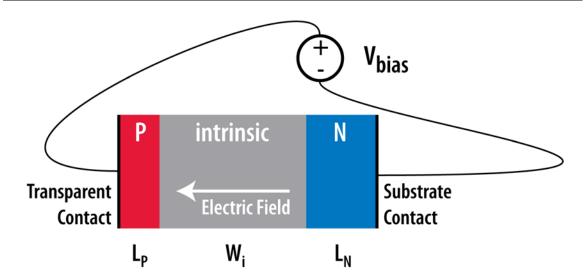

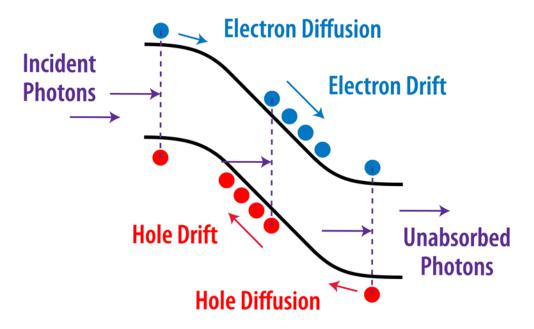

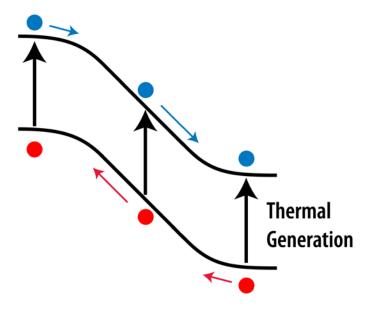

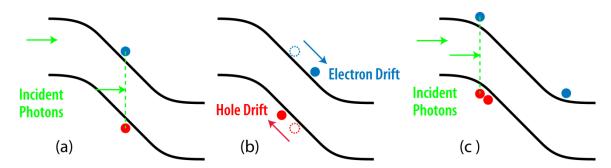

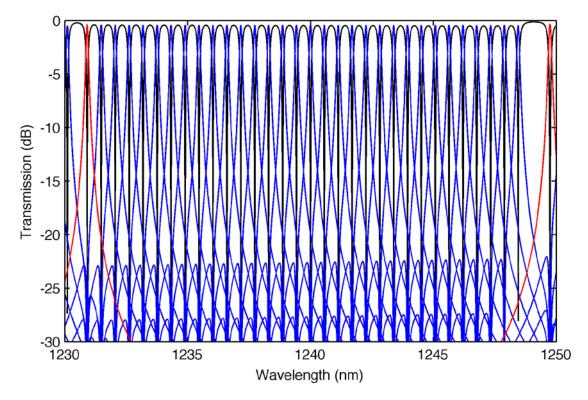

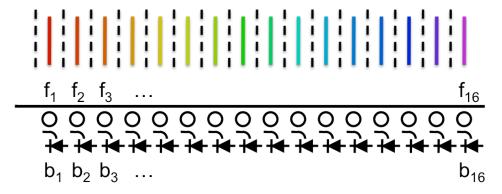

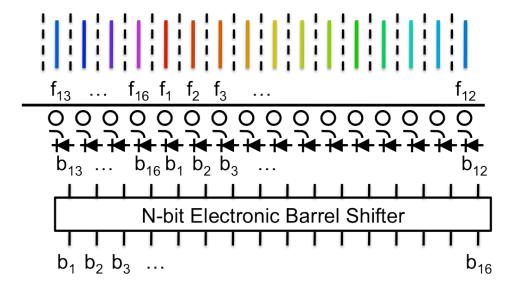

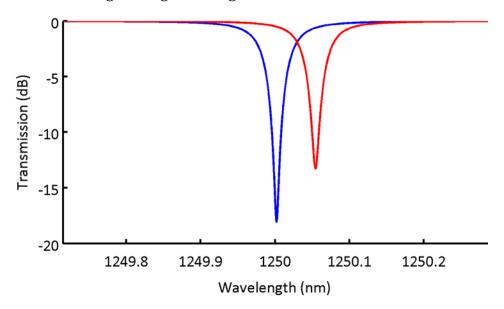

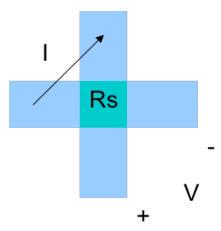

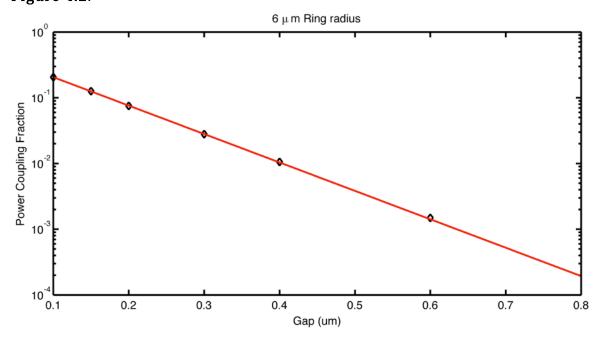

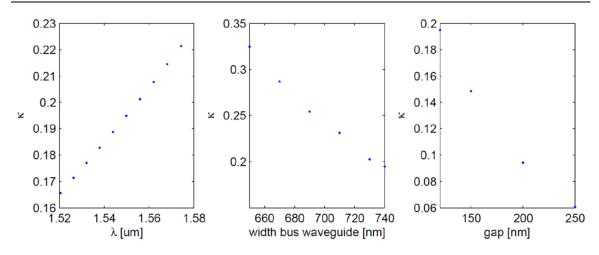

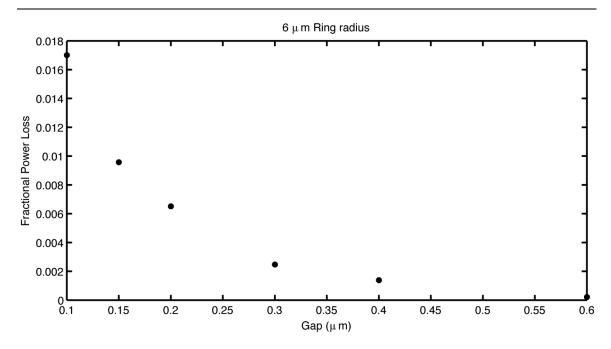

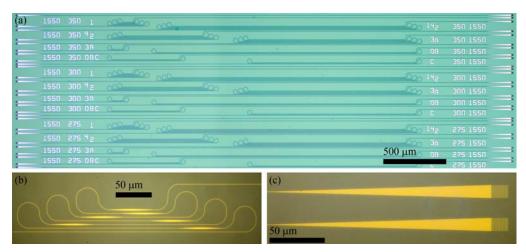

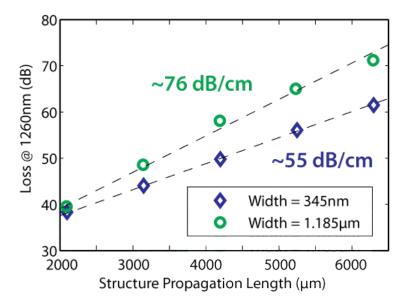

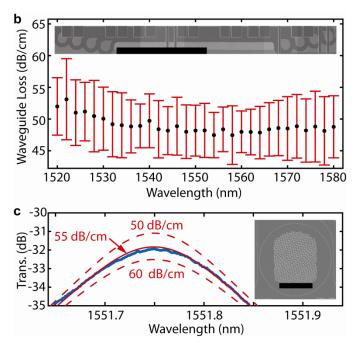

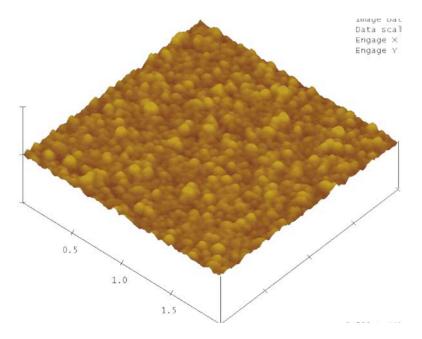

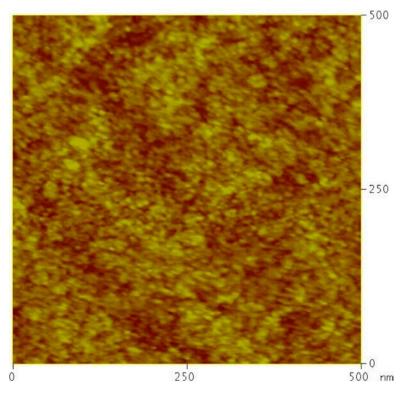

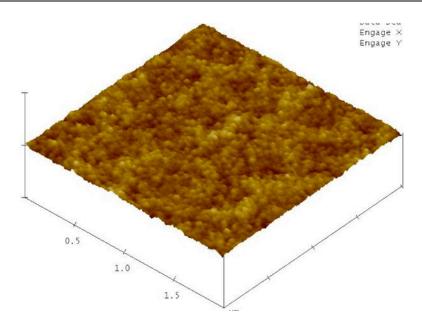

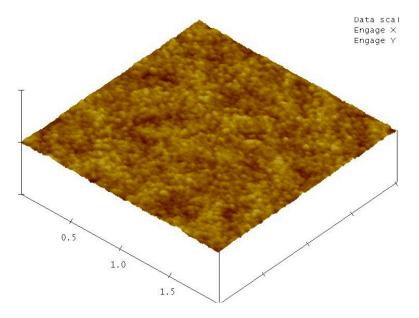

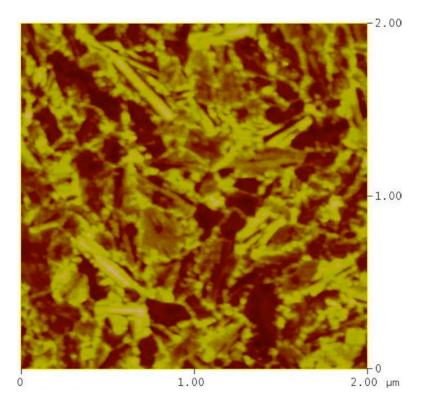

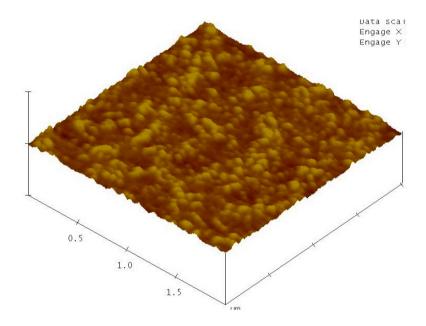

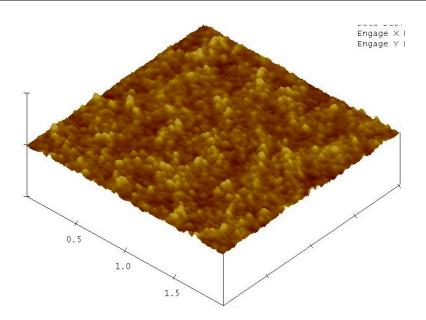

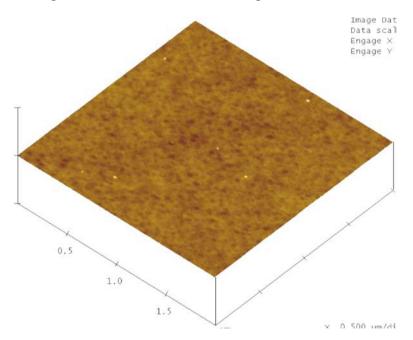

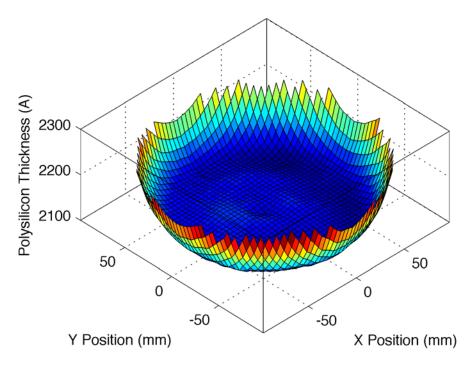

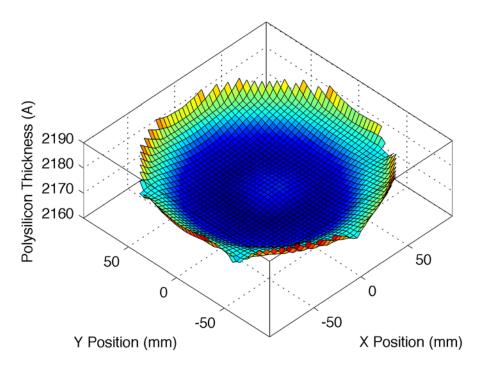

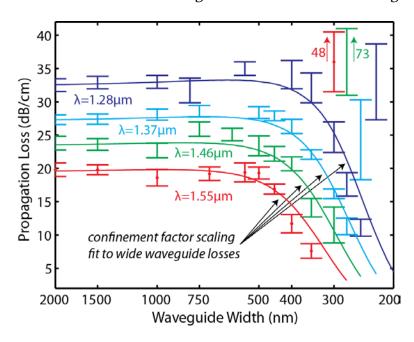

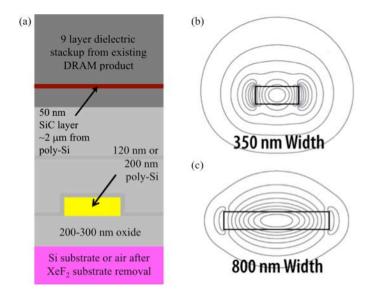

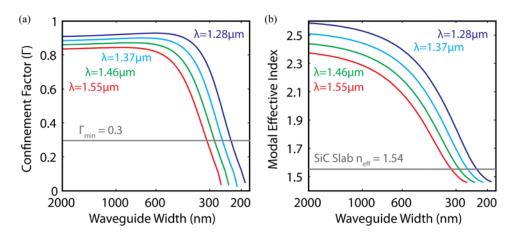

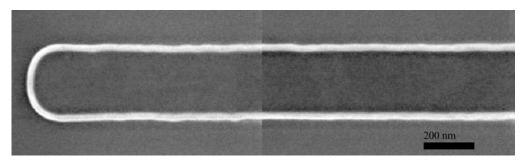

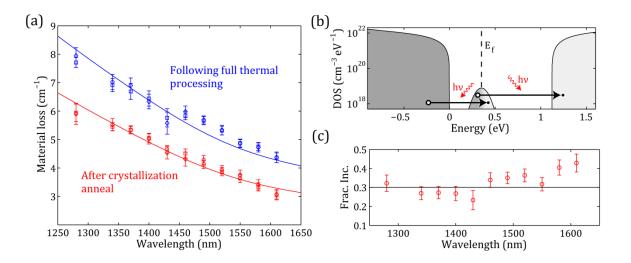

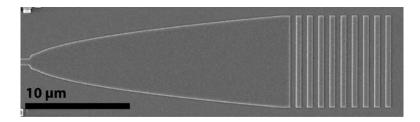

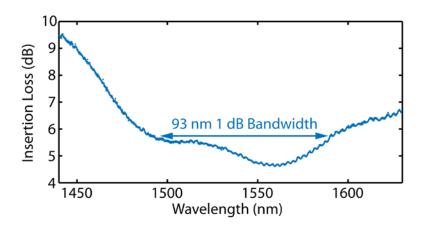

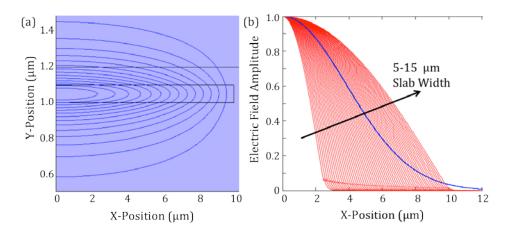

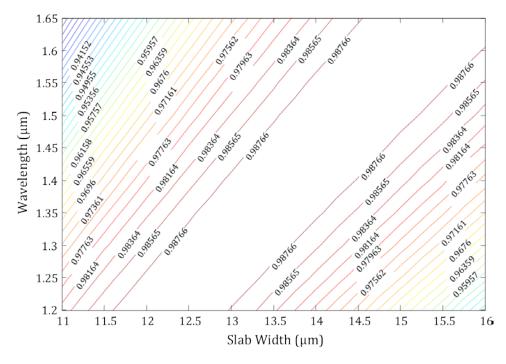

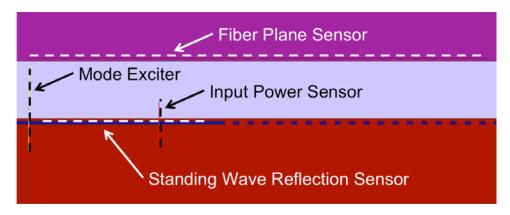

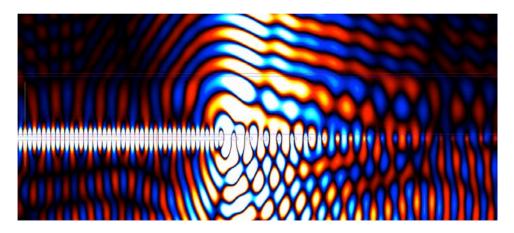

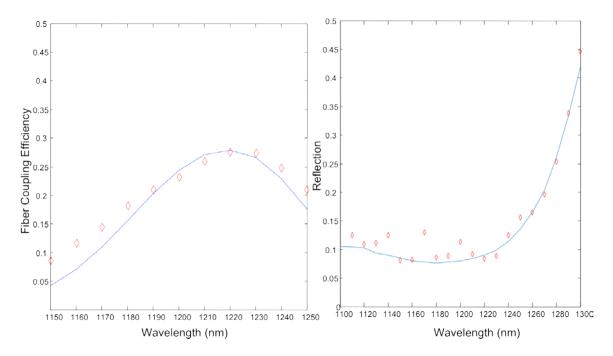

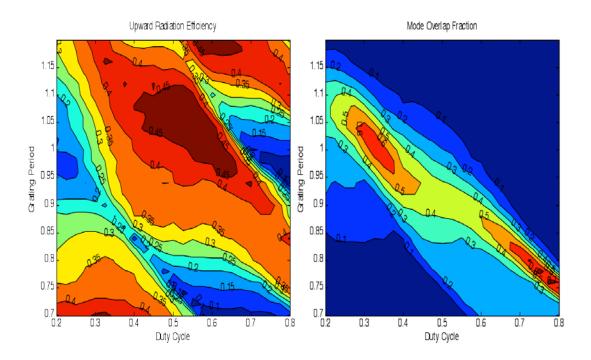

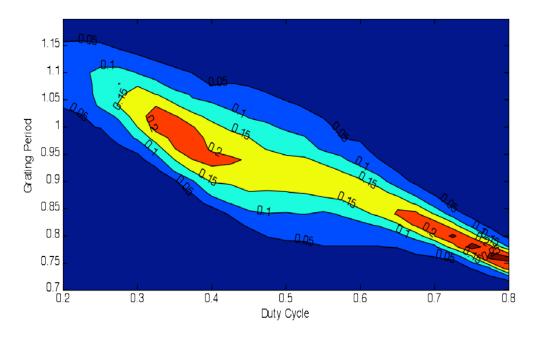

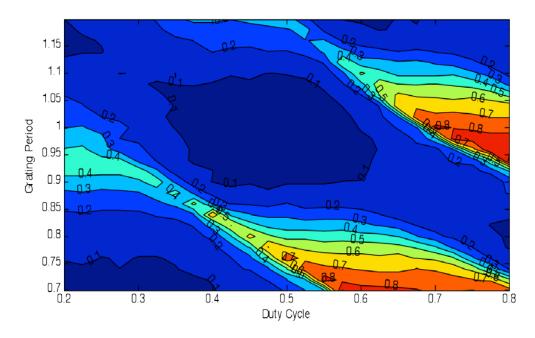

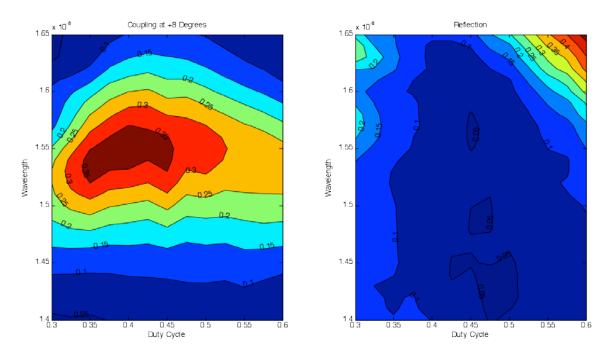

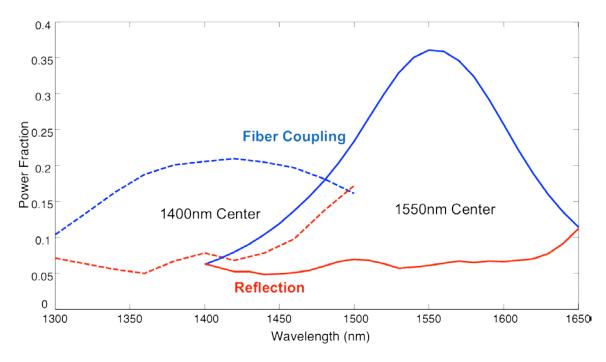

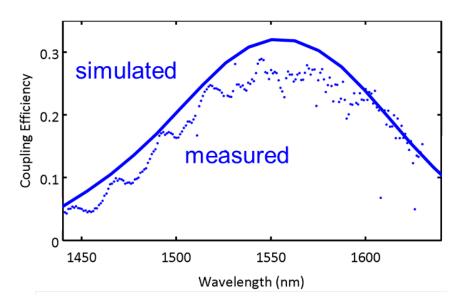

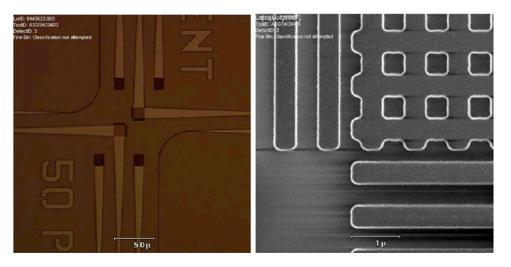

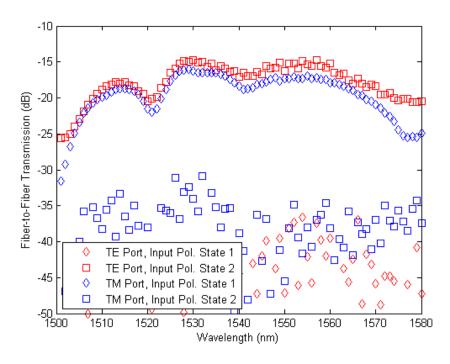

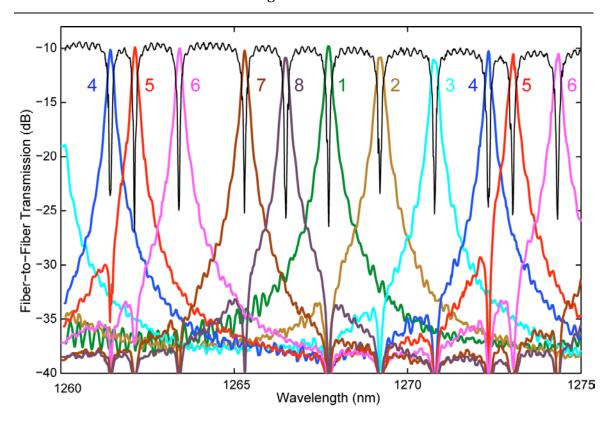

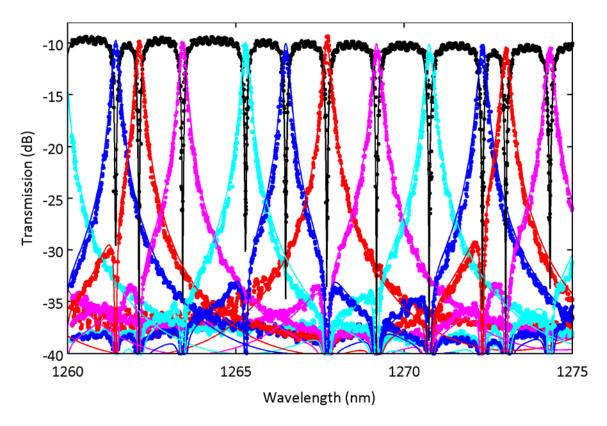

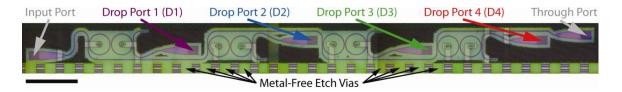

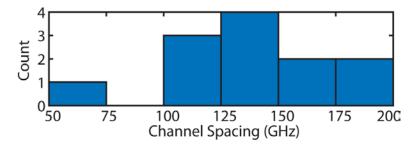

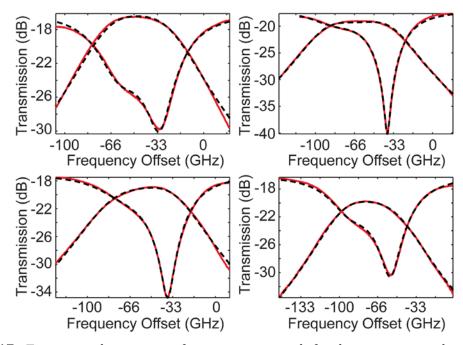

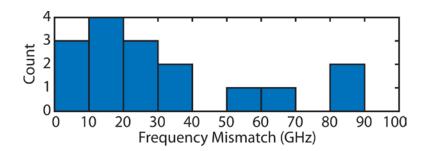

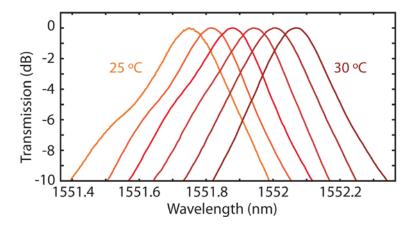

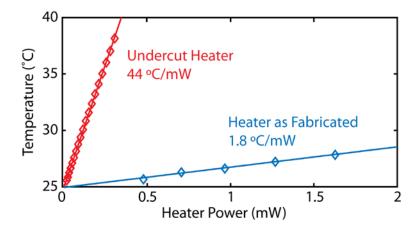

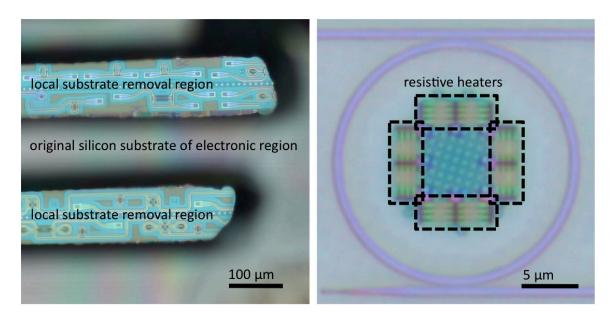

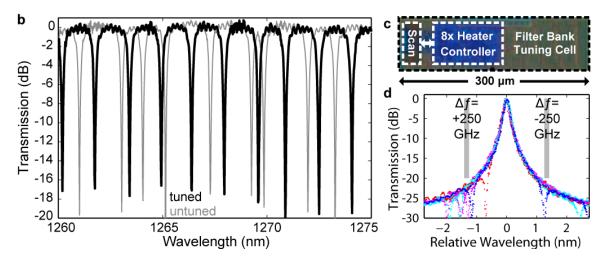

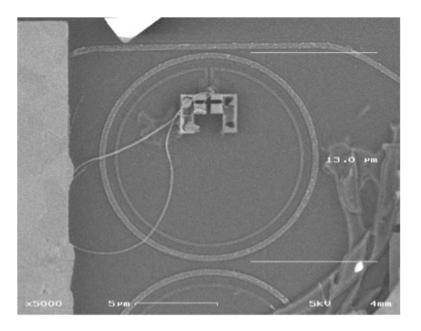

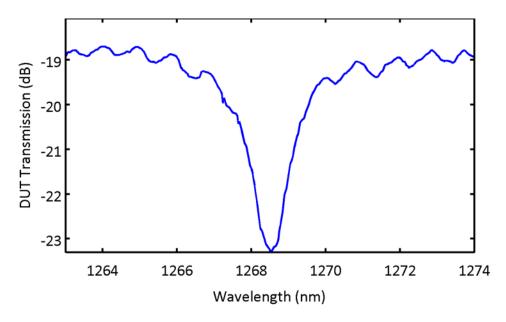

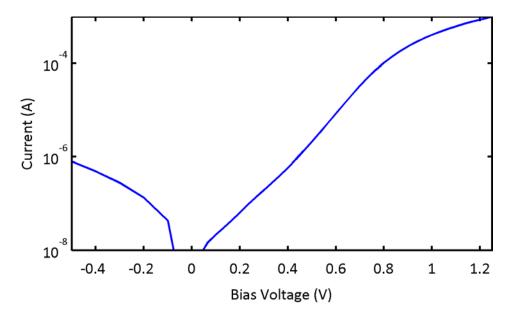

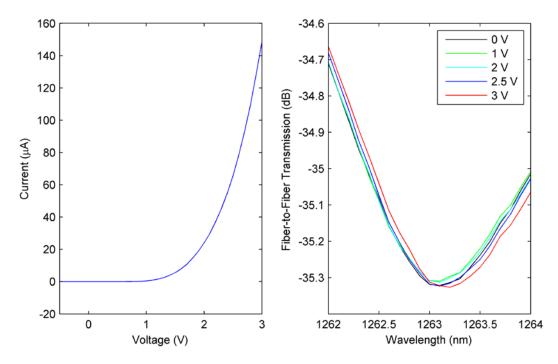

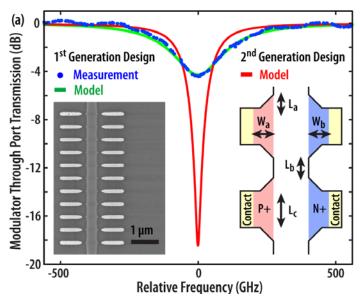

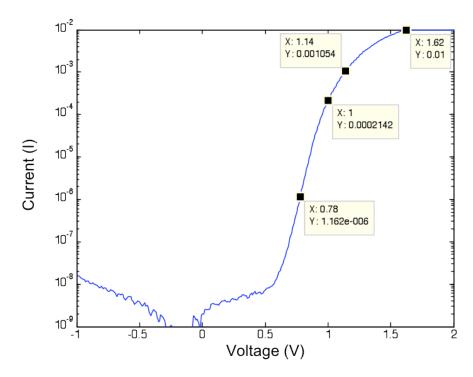

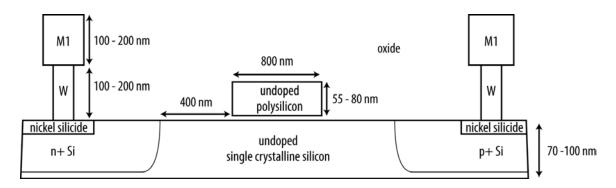

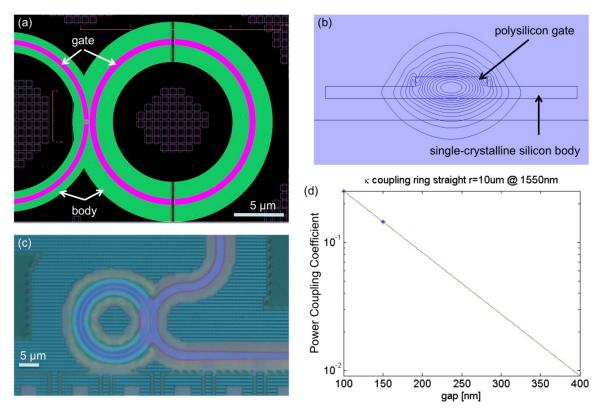

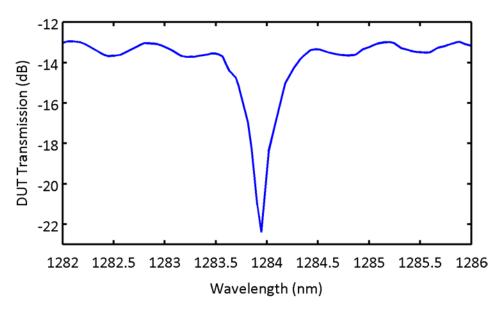

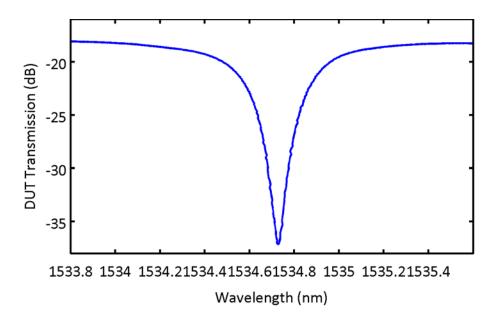

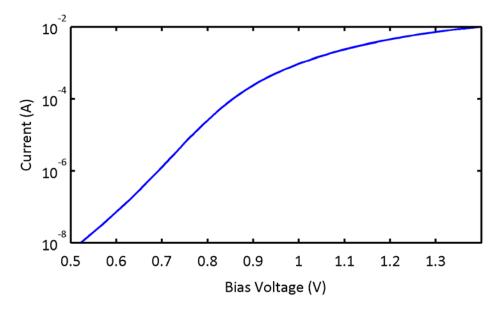

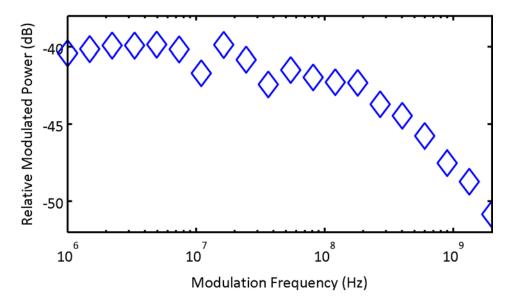

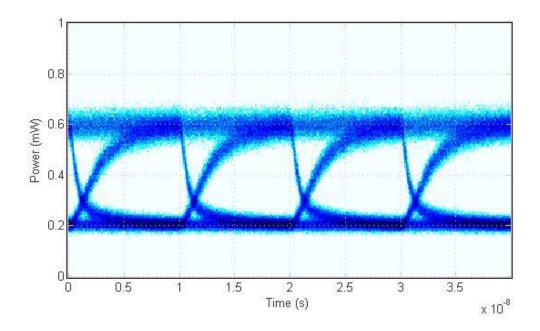

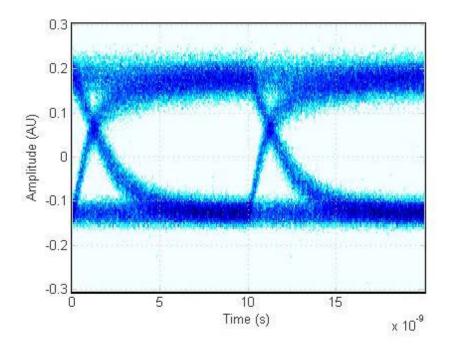

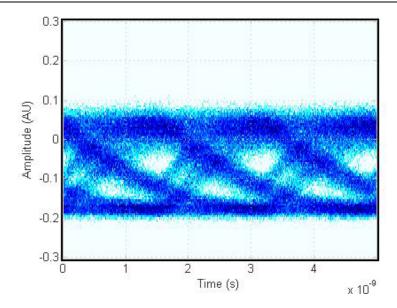

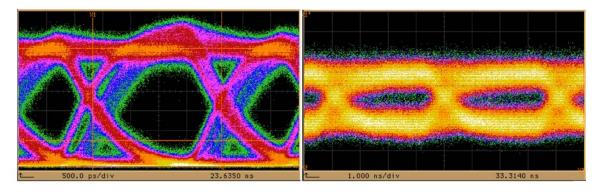

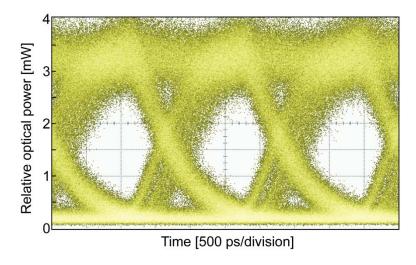

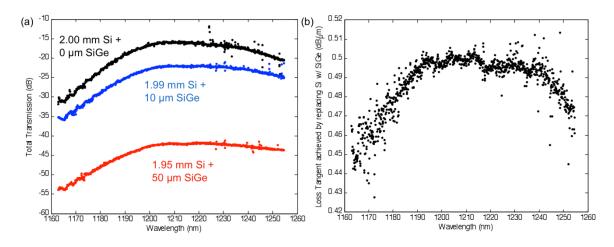

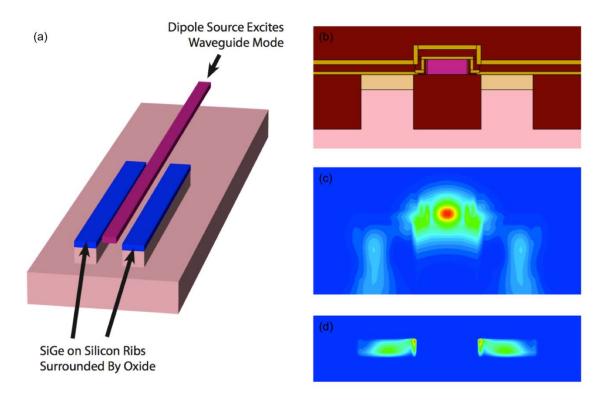

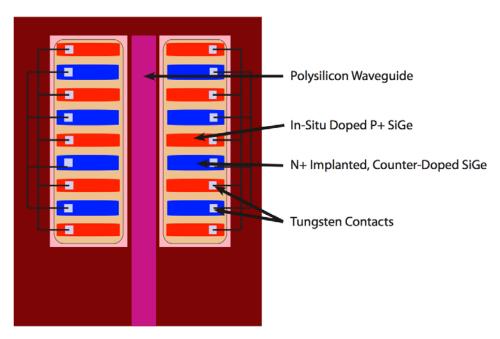

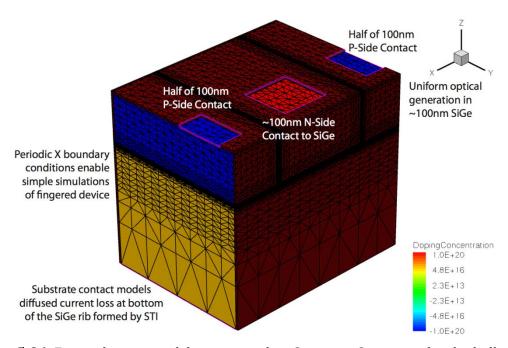

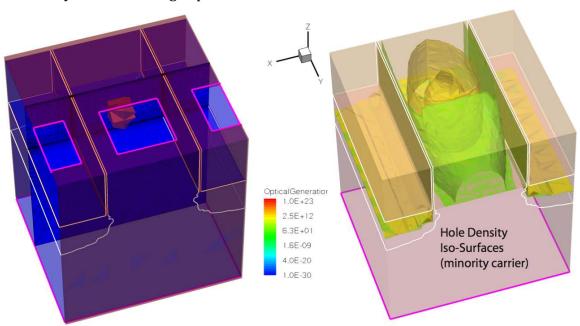

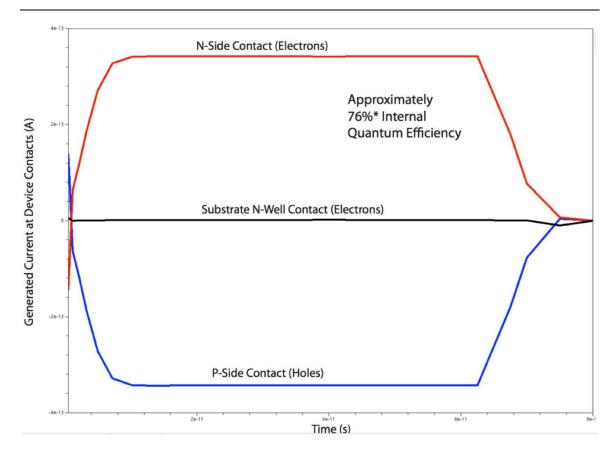

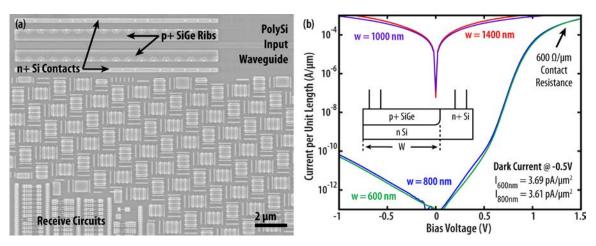

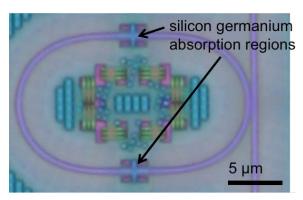

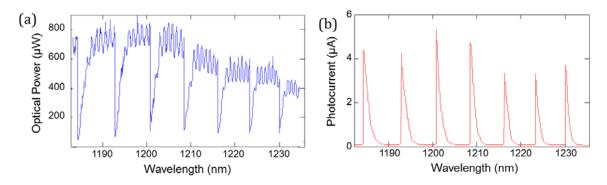

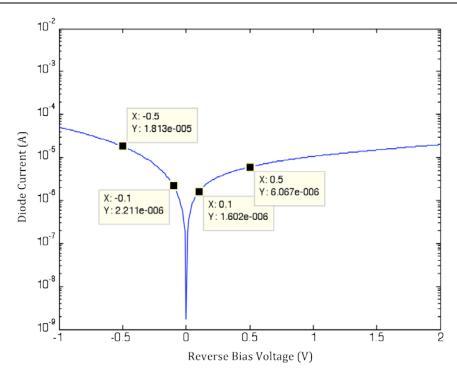

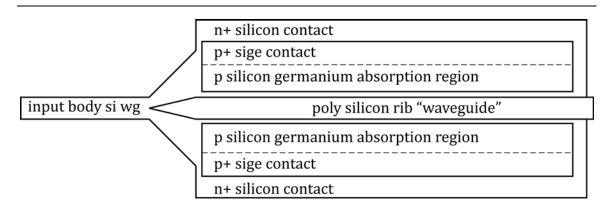

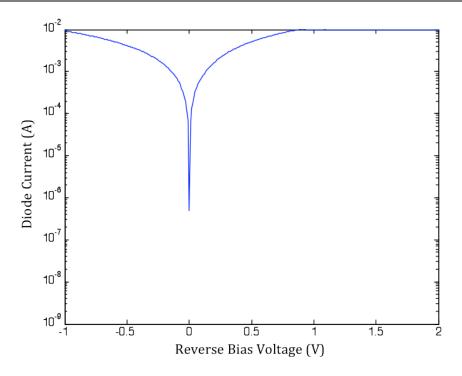

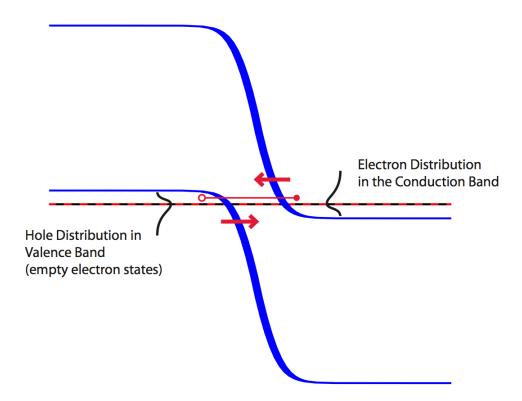

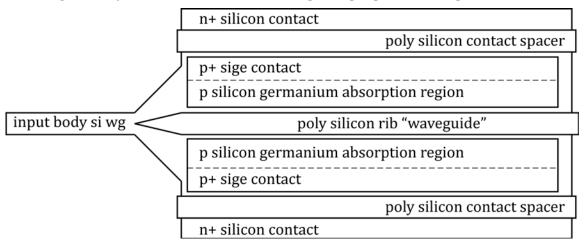

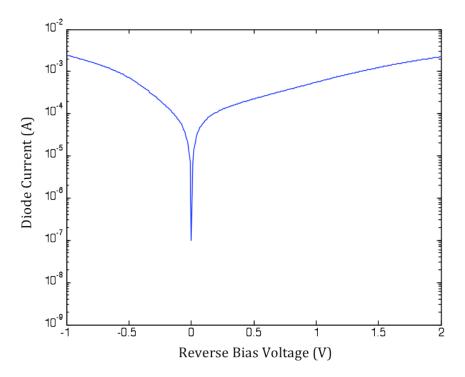

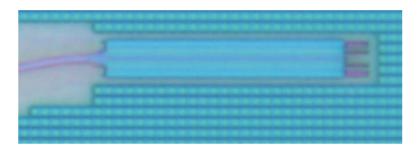

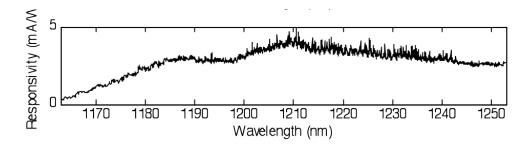

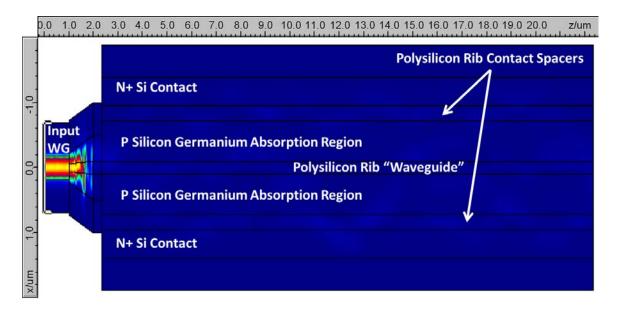

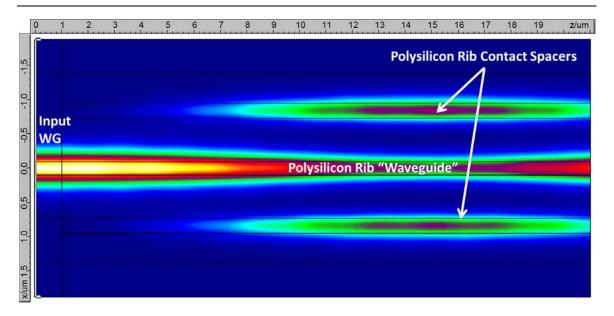

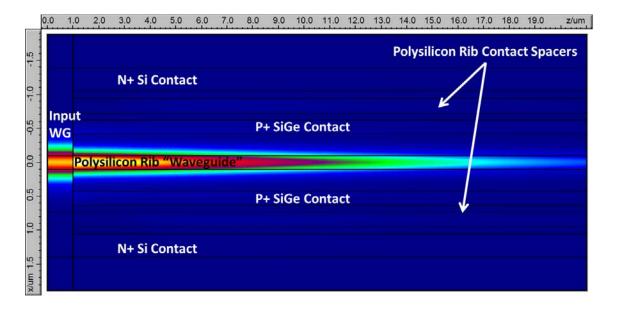

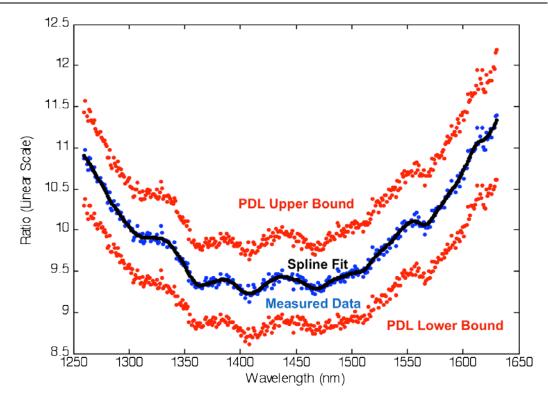

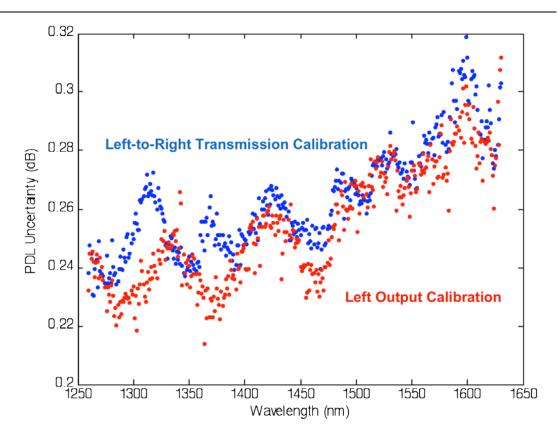

$$v_{g} = \frac{d\omega}{d\beta} \tag{1.2}$$