## Energy Efficient Reconfigurable SRAM Using Data-Dependency

by

Chuhong Duan

B.S., Electrical Engineering, University of Virginia (2013)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### September 2015

© Massachusetts Institute of Technology 2015. All rights reserved.

Certified by ..... Anantha P. Chandrakasan Joseph F. and Nancy P. Keithley Professor of Electrical Engineering Thesis Supervisor

Accepted by ..... Leslie A. Kolodziejski Chair, Department Committee on Graduate Students

## Energy Efficient Reconfigurable SRAM Using Data-Dependency

by

Chuhong Duan

Submitted to the Department of Electrical Engineering and Computer Science on Aug 28, 2015, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

The binary values processed and stored at the intermediary stages of an algorithm are often highly correlated. Motivated in part by this observation and the ever-increasing challenge of power density for Integrated Circuit (IC) systems, a novel reconfigurable memory framework is proposed in this thesis which builds upon traditional low power techniques such as voltage scaling in order to achieve up to 31% power savings for targeted applications. The general strategy underlying the presented low power memory innovation is to leverage global and local data correlation in order to make predictions so that the overall switching activity on the read bit-lines of the Static Random Access Memory (SRAM) is reduced with minimal area overhead. Additionally, multiple prediction schemes are incorporated into this framework wherein statistical data features are used to optimally configure each column of the proposed SRAM. Analysis tools for developing this type of reconfigurable low-power memories are provided.

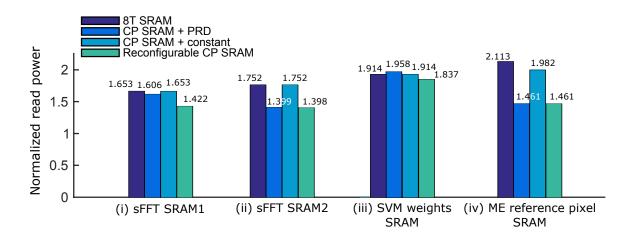

An example reconfigurable CP SRAM adhering to the proposed framework is presented which includes the novel designs of a 10-transistor (10T) bit-cell, a predictionbased conditional pre-charge scheme, and a column-wise reconfigurable dual prediction mode architecture. A 16kbit SRAM incorporating these innovations is implemented in a test chip using a 28nm FD-SOI CMOS process. Using post-layout simulations, the proposed SRAM is found to provide 14%-20%, 4%, and 31% reductions in read power as compared with a conventional 8T SRAM for three targeted applications: the coefficient SRAMs in a sparse Fast Fourier Transform (sFFT) implementation, the Support Vector Machine (SVM) weights SRAM in an objection detection system, and the Motion Estimation (ME) reference pixel SRAM in a video coding system, respectively.

Thesis Supervisor: Anantha P. Chandrakasan Title: Joseph F. and Nancy P. Keithley Professor of Electrical Engineering

## Acknowledgments

This thesis and the work it entailed would not have been possible without the guidance and support of my advisor, Professor Anantha Chandrakasan. Anantha, thank you for giving me the opportunity to join your group and providing me with incredible resources to learn and grow while undergoing this challenging yet exciting long-distance run. Aside from the technical lessons I learned from you, your passion and dedication to education and the circuit community have been an inspiration to me. I am deeply grateful for the enlightening discussions and warm encouragements you've shared throughout.

I am grateful to have had the opportunity to learn from some of the most brilliant, dedicated, and down-to-earth people I have ever met while in Ananthagroup. I would like to thank my colleagues and friends in Ananthagroup for their generous support in solving technical problems of all sorts. Specifically, I'd like to thank Avishek and Yildiz for welcoming me to the SRAM family and helping me ramp up when I first joined. They taught me countless things and were always willing to share more. I feel fortunate to have had them as mentors. I'd like to thank Arun, Mehul, Michael, and Phil for always answering my calls for help and generously sharing their insights and experience. I'd like to thank my current or former group mates: Bonnie, Chiraag, Dina, Dongsuk, Frank, Gilad, Georgios, Hyung-Min, Nachiket, Nathan, Omid, Preet, Priyanka, Rahul, Sirma, and Sungjae. I'd also like to thank the kindest and simply best admin, Margaret, for all of her assistance. It is a privilege to be a member of this group and I have greatly enjoyed my residency thus far.

I would like to thank a few wonderful individuals I have been fortunate enough to collaborate with during this thesis. I'd like to thank Mahmut for being an amazing mentor during my summer internship. I learned a lot from that experience and from the many other colleagues at NVIDIA. I'd like to thank Amr and Omid for the meetings, email discussions, and efforts in helping me understand the applications essential to this thesis. I'd like to thank Avishek, Arun, and Mehul for patiently analyzing and debugging detailed circuit diagrams with me in the lab, on the plane, at ISSCC, or remotely over the phone. I'd like to thank Tarek for his help in preparing the final manuscript and matlab programming. I would also like to thank DARPA and NSF for funding support and STMicroelectronics for their generous support with chip fabrication.

To all my friends, thank you for your care and support and for encouraging me to be who I am. I will forever cherish all the joy and laughter we have shared.

I would like to thank Tarek, my best friend and my soul mate, for being the most effective dose of caffeine in getting me to work and the greatest support when things go wrong. I admire you and have learned so much from you. Thank you for being so generous and wonderful.

Finally, I'd be remiss if I didn't thank my Mom Weilai Zhong, Dad Bin Duan, and family for their endless support and unconditional love. Thank you for believing in me and providing me with the best to be who I am today. It is your love that keeps me moving forward and I am forever grateful to you.

## Contents

| 1        | Intr | oduct   | ion                                                                 | 15 |

|----------|------|---------|---------------------------------------------------------------------|----|

|          | 1.1  | Motiv   | ation                                                               | 15 |

|          |      | 1.1.1   | Designing for energy constrained applications and systems $\ . \ .$ | 15 |

|          |      | 1.1.2   | Application specific considerations                                 | 17 |

|          | 1.2  | Summ    | nary of contributions                                               | 18 |

| <b>2</b> | A s  | urvey   | of low power SRAMs                                                  | 21 |

|          | 2.1  | Overv   | iew of low power techniques                                         | 22 |

|          | 2.2  | The d   | ata dependent approach                                              | 23 |

| 3        | Ene  | ergy-ef | ficient reconfigurable memory                                       | 27 |

|          | 3.1  | A gen   | eral framework                                                      | 27 |

|          | 3.2  | Condi   | tional pre-charge SRAM                                              | 29 |

|          |      | 3.2.1   | Proposed bit-cell design                                            | 29 |

|          |      | 3.2.2   | Conditional pre-charge                                              | 30 |

|          | 3.3  | Evalu   | ation of memory models and prediction schemes                       | 33 |

|          |      | 3.3.1   | Prediction scheme                                                   | 36 |

|          |      | 3.3.2   | Power dependency on data statistics                                 | 38 |

|          |      | 3.3.3   | Model evaluation                                                    | 39 |

|          | 3.4  | Propo   | sed reconfigurable memory design                                    | 42 |

|          |      | 3.4.1   | Two modes of read operation                                         | 42 |

|          |      | 3.4.2   | Proposed column circuit design                                      | 43 |

| 4        | Implementation of the reconfigurable CP SRAM |                                                             |                                                                       | 45 |

|----------|----------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|----|

|          | 4.1                                          | System architecture and physical design in 28nm FD-SOI CMOS |                                                                       | 46 |

|          |                                              | 4.1.1                                                       | Memory array architecture                                             | 46 |

|          |                                              | 4.1.2                                                       | Macro architecture                                                    | 47 |

|          |                                              | 4.1.3                                                       | Test chip architecture                                                | 51 |

|          | 4.2                                          | Post-l                                                      | ayout results                                                         | 52 |

|          |                                              | 4.2.1                                                       | Functional verification                                               | 53 |

|          |                                              | 4.2.2                                                       | Power simulations                                                     | 55 |

| <b>5</b> | App                                          | olicatio                                                    | on-specific power results                                             | 59 |

|          | 5.1                                          | Statis                                                      | tical data measures                                                   | 59 |

|          | 5.2                                          | Target                                                      | ted applications and achieved power                                   |    |

|          |                                              | saving                                                      | S                                                                     | 62 |

|          |                                              | 5.2.1                                                       | Sparse FFT: collision resolution                                      | 63 |

|          |                                              | 5.2.2                                                       | Video coding: motion estimation                                       | 73 |

|          |                                              | 5.2.3                                                       | Object detection: support vector machine classification $\ . \ . \ .$ | 81 |

|          |                                              | 5.2.4                                                       | Summary of power results                                              | 88 |

|          | 5.3                                          | Furthe                                                      | er comments on data mapping                                           | 89 |

| 6        | Cor                                          | nclusio                                                     | ns                                                                    | 91 |

|          | 6.1                                          | Recon                                                       | figurable memory framework                                            | 92 |

|          | 6.2                                          | Recon                                                       | figurable CP SRAM design in 28nm FD-SOI CMOS                          | 93 |

|          | 6.3                                          | Future                                                      | e directions                                                          | 95 |

# List of Figures

| 1-1               | Bit-cell and $V_{MIN}$ scaling trend of SRAM from major semiconductor manufacturers. Figure adapted from ISSCC 2014 Trends                                                                                                                                                                                                                                                              | 17             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2-1<br>2-2<br>2-3 | The conventional 8T bit-cell                                                                                                                                                                                                                                                                                                                                                            | 23<br>24<br>25 |

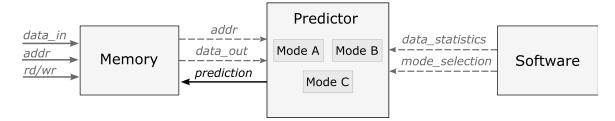

| 3-1               | An illustration emphasizing the communication between software and<br>memory hardware via the predictor in the proposed reconfigurable<br>memory framework.                                                                                                                                                                                                                             | 28             |

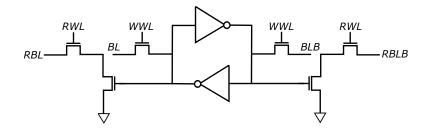

| 3-2               | The proposed 10T bit-cell consisting of two cross-coupled inverters, two access NMOS transistors for the write bit-lines BL and BLB, and two read ports connected to the read bit-lines RBL and RBLB                                                                                                                                                                                    | 30             |

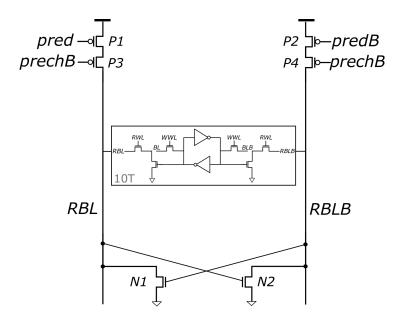

| 3-3               | Column architecture of the proposed Conditional Pre-charge SRAM (CP SRAM). One of the read bit-lines is pulled high depending on the current prediction values (pred, predB) via the associated pair of pre-charge PMOS transistors. The other read bit-line is kept low by one of the cross-coupled NMOS transistors N1 and N2                                                         | 32             |

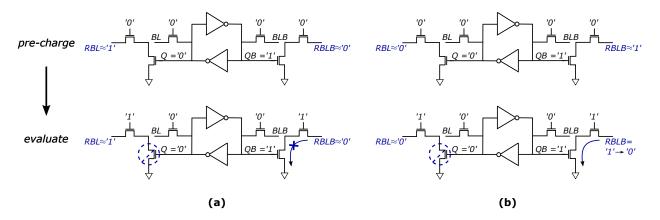

| 3-4               | (a) Correct and (b) incorrect prediction cases during a read operation<br>with the CP SRAM. The conditionally pre-charged read bit-line remains<br>high if the prediction is correct and is discharged to low if the prediction<br>is wrong                                                                                                                                             | 32             |

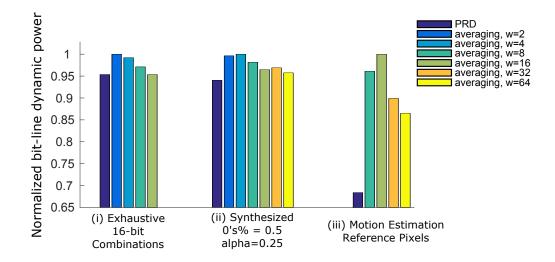

| 3-5               | Normalized read bit-line power consumption of CP-SRAM using predic-<br>tion scheme PRD vs arithmetic averaging for various average window<br>sizes (w). Three data sets are used: (i) $2^{16}$ 16-bit binary number com-<br>binations, (ii) synthetic data with $\alpha_{0\to 1} = 0.25$ and $\rho = 0.5$ , and (iii)<br>$1080 \times 1920$ highly compressed ME reference frame pixels | 35             |

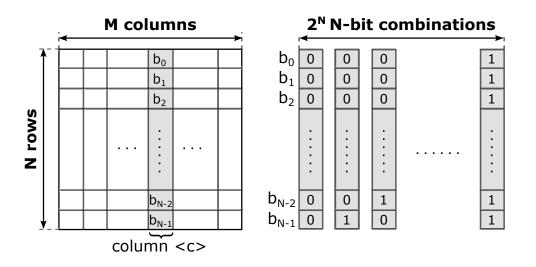

| 3-6               | Organization of the input data set (i). The exhaustive collection of $2^N$<br><i>N</i> -bit binary number combinations cover all possible patterns of the data stored in column $\langle c \rangle$ in an SRAM of size $N \times M$ .                                                                                                                                                   | 36             |

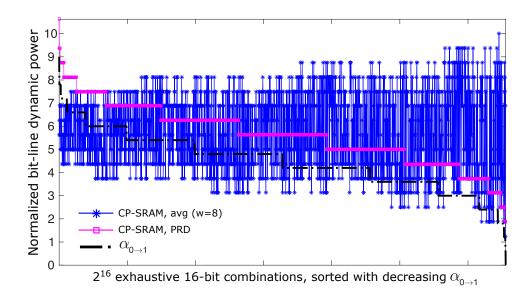

| 3-7               | Normalized read bit-line power consumption of CP-SRAM for every<br>16-bit binary number combination for prediction scheme PRD and<br>arithmetic averaging ( $w = 8$ ). The indexing corresponds to decreasing                                                                                                                                                                           |                |

|                   | $\alpha_{0\to 1}$ for the exhaustive data set                                                                                                                                                                                                                                                                                                                                           | 37             |

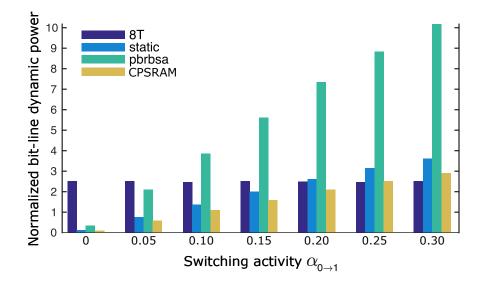

|                  | Normalized read bit-line and prediction-line power of various memory<br>models for synthesized data sets with various switching activity factors                                                                                                                                |               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 3-9 ]            | $\alpha_{0\to 1}$ . All data sets have $\rho = 0.5$                                                                                                                                                                                                                             | 38            |

| 3-10 ]           | data sets have $\alpha_{0\to1} = 0.15$                                                                                                                                                                                                                                          | 39<br>line) : |

| (<br>3-11 .<br>1 | (a) 1 : 1 : 2.5 and (b) 1 : 2.5 : 2.5                                                                                                                                                                                                                                           | 40<br>43      |

| 3-12 '           | column                                                                                                                                                                                                                                                                          | 43            |

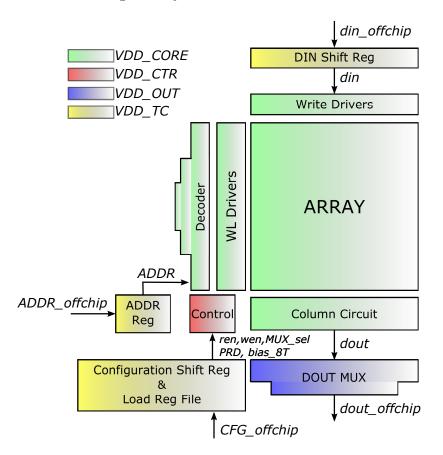

| ן<br>י           | A diagram of the system architecture for the 16kbit memory array. The memory consists of $256 \times 64$ 10T memory cells, row drivers for RWL and WWL, write drivers for BL/BLB, and a column circuit for RBL/RBLB                                                             |               |

| 4-2 (            | variation sensing, prediction generation, and mode configuration<br>General structure of the custom 10T bit-cell. This diagram does not<br>show the actual or any scaled version of the bit-cell layout. The<br>approximate placements of NWELL, p and n active regions, polys, | 47            |

| 4-3 .            | contacts, and METAL2/METAL3 routings are shown in the diagram.<br>Architecture diagram of the system macro. The macro consists of the<br>memory array, an 8-to-256 two-stage address decoder and a timing                                                                       | 48            |

| 4-4              | control unit                                                                                                                                                                                                                                                                    | 49            |

| 4-5 _            | highlighted in blue                                                                                                                                                                                                                                                             | 50            |

| 4-6              | are highlighted in the same color                                                                                                                                                                                                                                               | 51            |

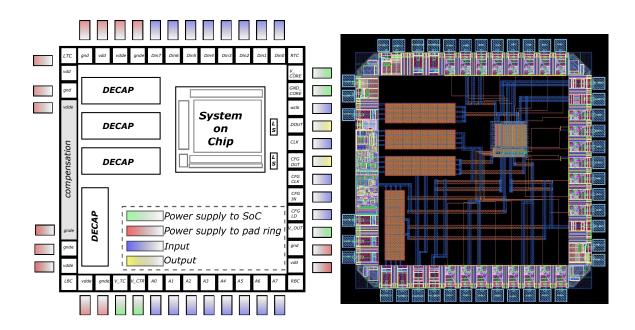

| 4-7              | Right: completed layout of the test chip                                                                                                                                                                                                                                        | 53            |

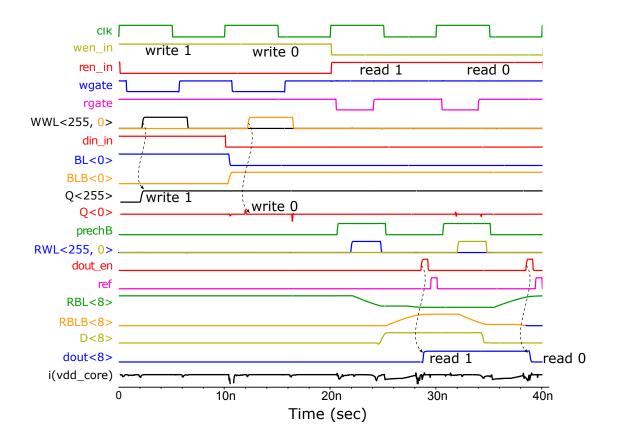

|                  | $V_{dd} = 0.65V, f = 100MHZ$ , and at the SS corner                                                                                                                                                                                                                             | 54            |

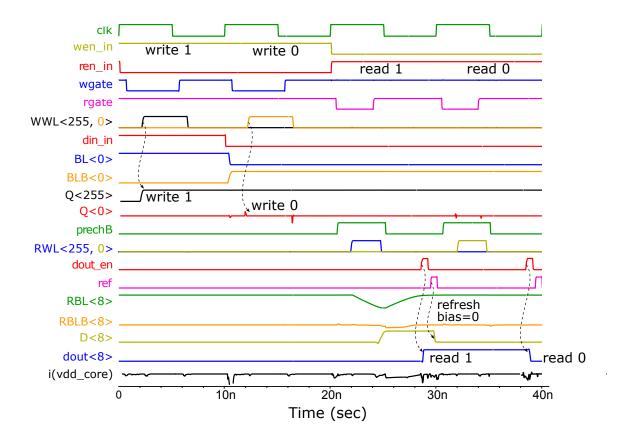

=

| 4-8  | Simulation waveforms of the extracted reconfigurable CP SRAM oper-<br>ated in constant mode (prediction = 0). The sequence of operations<br>performed are: (i) writing a 1 in row 255, (ii) writing a 0 in row 0, (iii)<br>reading the 1 from row 255, and (iv) reading the 0 from row 0. The<br>simulation is run with $V_{dd} = 0.65V$ , $f = 100MHZ$ , and at the SS corner. | 55 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

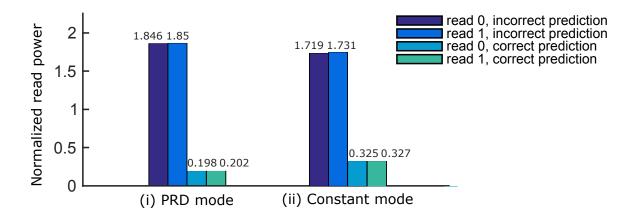

| 4-9  | Simulated read power consumption of the reconfigurable CP SRAM operated in PRD and constant prediction modes for various scenarios. Specifically, four scenarios are simulated for each mode: reading 0 with an incorrect prediction, reading 1 with an incorrect prediction, reading 0 with a correct prediction, and reading 1 with a correct prediction.                     | 56 |

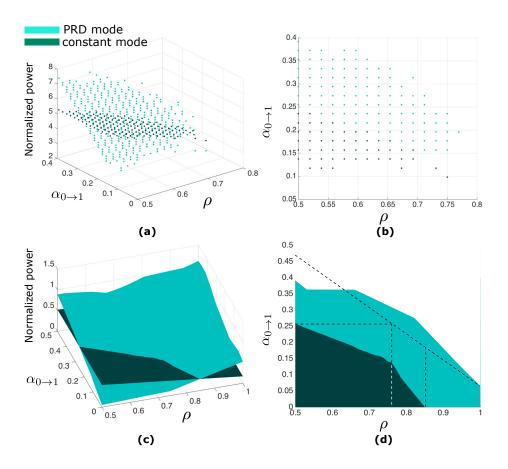

| 4-10 | Mode selection analysis for randomly generated statistical measure<br>pairs $(\rho, \alpha_{0\to 1})$ . Extrapolated data from (a) are shown in (c) and (d).<br>The prediction mode corresponding to the higher power consumption<br>is plotted in the plane views in (b) and (c).                                                                                              | 57 |

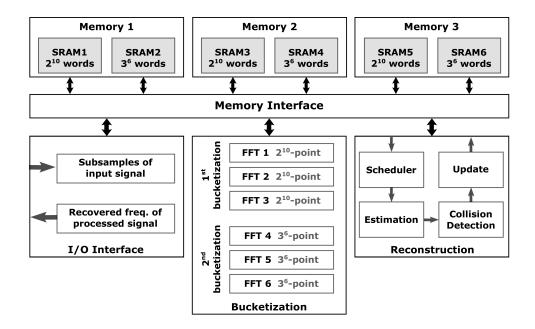

| 5-1  | Architecture of the sFFT system [1]. Three memory modules are implemented to enable the efficient operation of a three-stage pipelined sFFT system.                                                                                                                                                                                                                             | 66 |

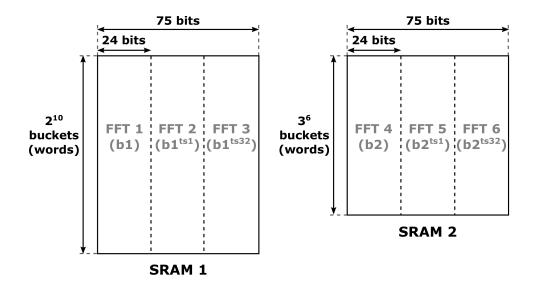

| 5-2  | Architecture design of the two FFT coefficient SRAMs in the sFFT system. SRAM1 (left) stores the output of the three 2 <sup>10</sup> -point FFT modules in the first bucketization group; SRAM2 (right) stores the output of the three 3 <sup>6</sup> -point FFT modules in the second bucketization group.                                                                     | 67 |

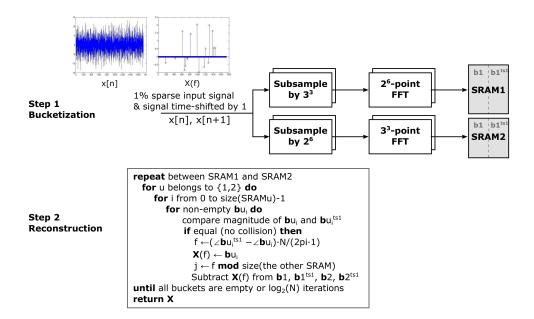

| 5-3  | Architecture and pseudo code of a custom program that simulates<br>data progression in the FFT coefficient SRAMs. Step 1 generates the<br>SRAMs' input data and step 2 simulates the SRAMs' data progression<br>during collision resolution.                                                                                                                                    | 68 |

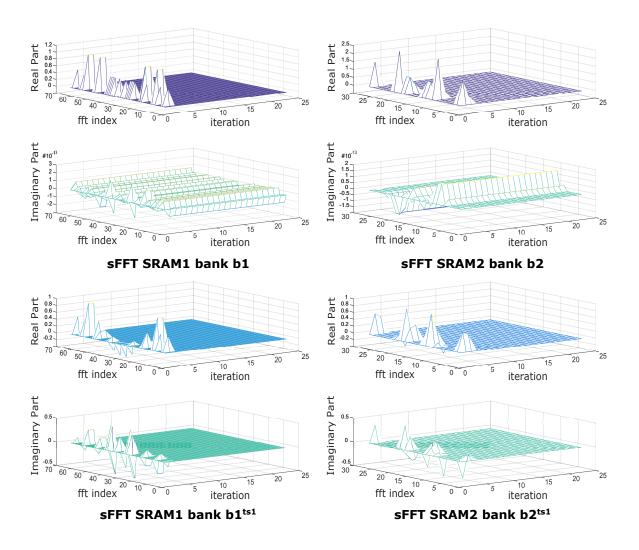

| 5-4  | Storage data in different SRAM banks in the collision resolution stage $(2^6 * 3^3 \text{ input size}, 1\% \text{ sparse in frequency})$ . Real and imaginary parts of the FFT coefficients are plotted separately as they occupy different columns of the SRAM.                                                                                                                | 69 |

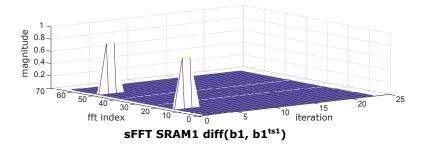

| 5-5  | Magnitude differences between the FFT coefficients in SRAM banks $b1$<br>and $b1^{ts1}$ in a simulation of the sFFT collision resolution process                                                                                                                                                                                                                                | 70 |

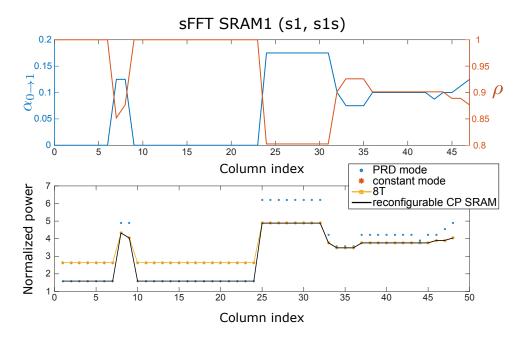

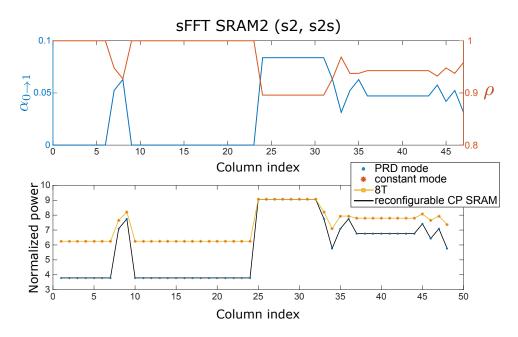

| 5-6  | (Top) The statistical measures $\rho$ and $\alpha_{0\to 1}$ , respectively computed in accordance with (3.1) and (3.2), as a function of each column of the data set associated with SRAM1 in an sFFT implementation. (Bottom) The normalized power for each column of the same data set for each of the listed memory models.                                                  | 71 |

| 5-7  | (Top) The statistical measures $\rho$ and $\alpha_{0\to 1}$ , respectively computed in accordance with (3.1) and (3.2), as a function of each column of the data set associated with SRAM2 in an sFFT implementation. (Bottom) The normalized power for each column of the same data set for each of                                                                            |    |

|      | the listed memory models                                                                                                                                                                                                                                                                                                                                                        | 71 |

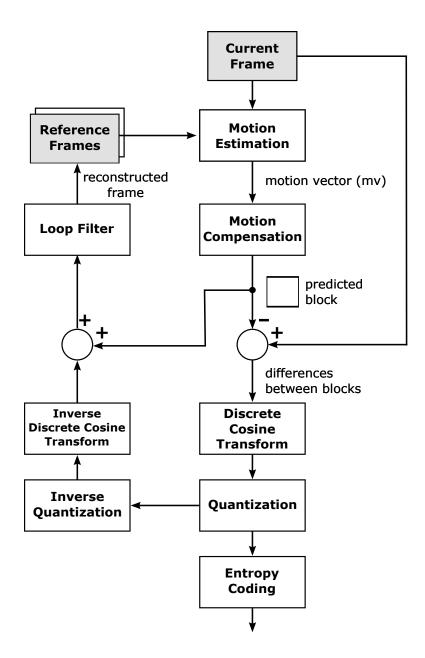

| 5-8  | Block diagram of an example video encoding system with ME and MC engines. Motion estimation identifies motion vectors which are then used by motion compensation to retrieve predicted blocks in the reference frame. Processed differences between the predicted and the current blocks are transmitted to the decoder system which is not shown here. A current frame is also reconstructed at the encoder side which becomes the new reference. | 74 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

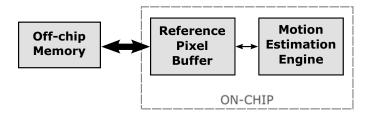

| 5-9  | Off-chip memory and on-chip buffer for the ME engine. The engine consecutively accesses on-chip pixel buffer with a read to write ratio greater than three.                                                                                                                                                                                                                                                                                        | 76 |

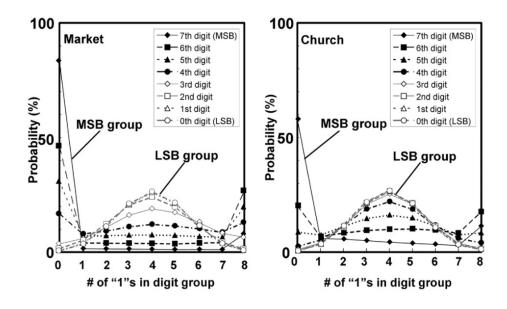

| 5-10 | Statistical analysis of video frame pixels in H.264 HDTV test sequences<br>'Market' (left) and 'Church' (right). For each sequence, the probability<br>of having different numbers of 1s is plotted for each digital group. Figure<br>adapted from [8].                                                                                                                                                                                            | 77 |

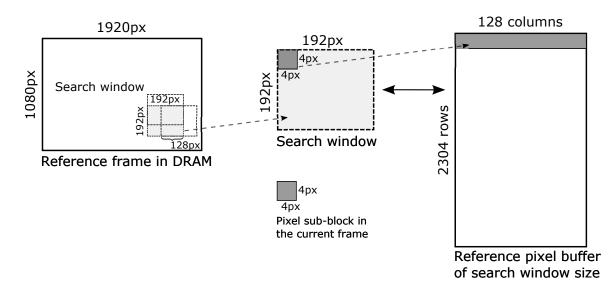

| 5-11 | Diagram showing the data-to-memory mapping scheme. Pixels in each $192 \times 192$ search window within the reference frame are retrieved from an off-chip DRAM and stored in an on-chip pixel buffer implemented as a $2304 \times 128$ SRAM                                                                                                                                                                                                      | 78 |

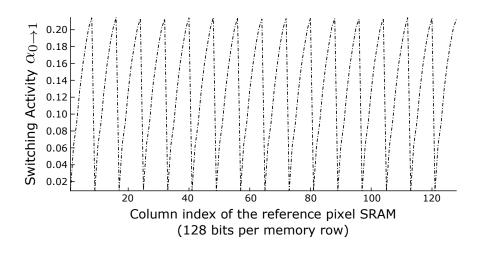

| 5-12 | Switching activity in each column of the reference pixel SRAM. Pixels<br>in a $1080 \times 1920$ highly compressed reference frame from the 'Park<br>Scene' video sequence are stored in this SRAM which has sixteen 8-bit<br>pixels per row, i.e. 128 bits per row. The MSBs of these pixels have<br>much higher local correlation than the LSBs                                                                                                  | 79 |

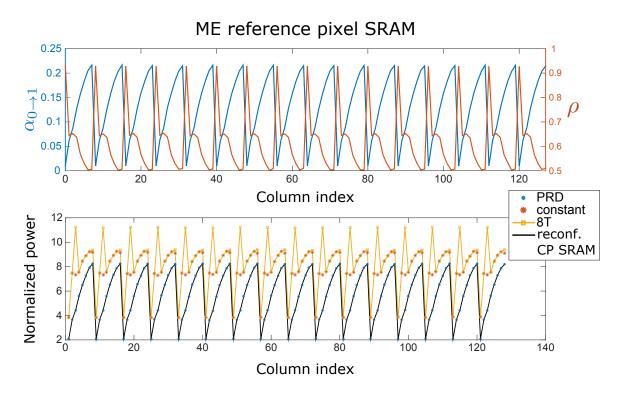

| 5-13 | (Top) The statistical measures $\rho$ and $\alpha_{0\to 1}$ , respectively computed in accordance with (3.1) and (3.2), as a function of each column of the data set associated with the ME reference pixel SRAM. (Bottom) The normalized power for each column of the same data set for each of the listed memory models.                                                                                                                         | 81 |

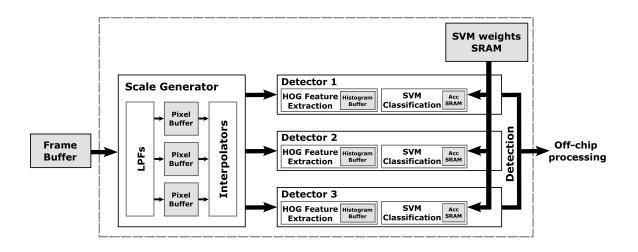

| 5-14 | The core architecture of an example SVM based object detection system [32]. This system supports multi-scale detection and uses three detectors in parallel. Each detector performs HOG feature extraction and SVM classification for the inputted frames by accessing trained optimal SVM weights from an on-chip SRAM.                                                                                                                           | 83 |

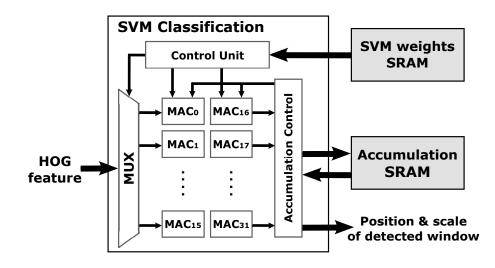

| 5-15 | Architecture of the SVM classifier used in the object detection system<br>in [32]. Thirty-two Multiply-And-Accumulation (MAC) modules and<br>an accumulation SRAM are used to realize on-the-fly SVM classification.                                                                                                                                                                                                                               | 84 |

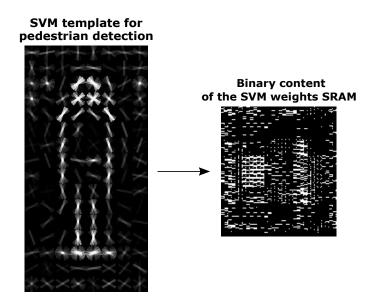

| 5-16 | Visualization of SVM coefficients trained for pedestrian detection and their binary representations stored in the SVM weights SRAM                                                                                                                                                                                                                                                                                                                 | 85 |

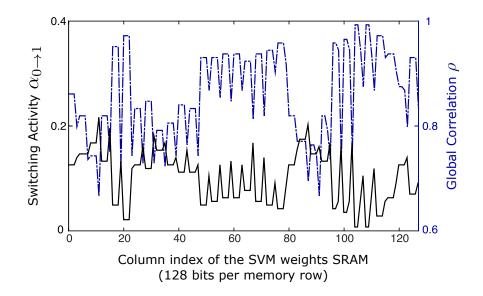

| 5-17 | Column-wise correlation statistics of the SVM weights SRAM. Columns with low switching activity $\alpha_{0\to 1}$ (black) tend to have high global correlation $\rho$ (blue).                                                                                                                                                                                                                                                                      | 86 |

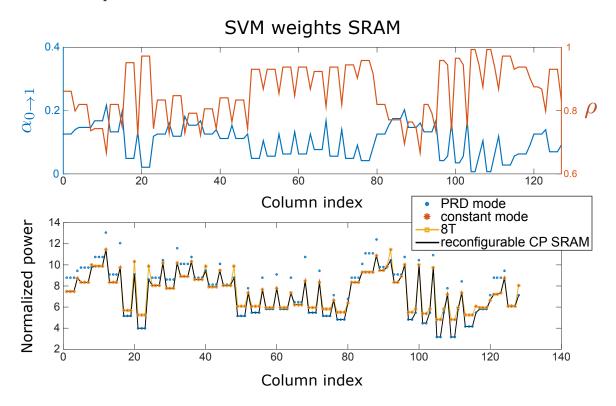

| 5-18 | (Top) The statistical measures $\rho$ and $\alpha_{0\to1}$ , respectively computed in accordance with (3.1) and (3.2), as a function of each column of the data set associated with the SVM weights SRAM in an object detection |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5-19 | system implementation. (Bottom) The normalized power for each                                                                                                                                                                   | 88 |

|      | models listed.                                                                                                                                                                                                                  | 89 |

| 6-1  | Hierarchy of the main thesis contributions.                                                                                                                                                                                     | 94 |

## Chapter 1

## Introduction

## 1.1 Motivation

Continuous process scaling, driven by the exponential growth of the semiconductor industry as famously predicted by Moore's law [18], has led to innovation in the area of integrated circuit (IC) design and has primarily resulted in increased functionality, lower fabrication and production costs, and continuously shrinking form factors. This trend of transistor feature size reduction, however, has also introduced challenges including increased power density and heat dissipation which are undesirable to small, energy-constrained mobile devices that rely on limited battery and/or self-harvested energy.

## 1.1.1 Designing for energy constrained applications and systems

The power consumed by a digital circuit is dominated by two components: dynamic power  $(P_{dynamic})$  and leakage power  $(P_{leakage})$ . Specifically, dynamic power consumption is attributed to capacitive logic switching, i.e. the charging and discharging of capacitors. When a circuit node goes from low (0) to high (1), current is drawn from the power

supply to fully charge the capacitor(s) attached to that node. Dynamic power is typically given by

$$P_{dynamic} = \alpha_{0 \to 1} C V_{dd}^2 f \tag{1.1}$$

where  $\alpha_{0\to1}$  is the activity factor, C is the switching capacitance,  $V_{dd}$  is the supply voltage, and f is the clock frequency. On the other hand, leakage power is attributed to the undesired leakage current that flows between power sources, intermediary nodes, and ground as a result of the fact that transistors are not completely off in their off state. Leakage power is typically given by

$$P_{leakage} = I_{leakage} V_{dd} \tag{1.2}$$

where  $I_{leakage}$  is the leakage current.

While the switching capacitance C scales proportionately with process technology, digital circuits at advanced nodes are designed to have more functionality per chip, more gates and therefore more switching nodes per unit area, and faster clock frequencies. As a result, the ever-increasing challenge is power density for IC systems. Additionally, leakage power in scaled processes is increased due to, for example, lower threshold voltages  $(V_T)$  and thinner gate oxides. For the reasons stated above, the exploration of low-power techniques for IC systems remains an active research area.

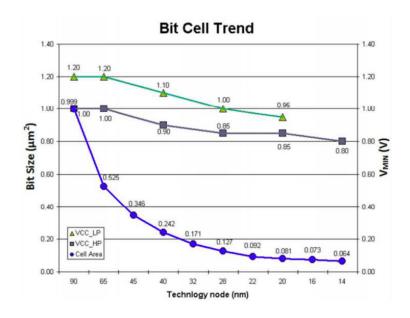

Embedded Static Random Access Memories (SRAMs) are critical components in modern system-on-chips (SoCs). As the capabilities of many digital electronic devices continue to improve at roughly exponential rates, the need for both large and low-power on-chip storage grows in parallel [4]. In IC implementations for various applications, SRAMs occupy a disproportionate amount of both the total die area and the total power consumption [37]. While recent progress has allowed the digital blocks of a system to be operated at lower supply voltages, robust SRAM operations still require a high supply voltage in order to guarantee reliability under worst-case process, temperature, and voltage conditions. Figure 1-1 shows the scaling trend of SRAM bit-cell sizes and SRAM power supply voltages  $V_{MIN}$  (minimum  $V_{dd}$  at which an SRAM works reliably) over process nodes. Observe that SRAM supply voltage scales much slower than the bit-cell size due to the stability challenges mentioned above. Consequently, SRAM has recently become the bottleneck of further power reduction in many systems and thus necessitates creative energy and area-efficient solutions.

Figure 1-1: Bit-cell and  $V_{MIN}$  scaling trend of SRAM from major semiconductor manufacturers. Figure adapted from ISSCC 2014 Trends.

#### 1.1.2 Application specific considerations

In order to develop a new dimension of energy savings, application-specific data features have been explored in addition to conventional techniques such as voltage scaling, read-/write-assist circuitry, and variation-tolerant sensing schemes. Highly correlated data, defined in [26] as data with repeated or similar values in consecutive cycles or more specifically with low switching activity  $\alpha_{0\to 1}$ , has been leveraged to help memory make predictions, reduce bit-line switching, and ultimately save energy wasted on reading redundant and/or predictable information. Existing data-dependent designs, however, are limited by their narrow applicability as well as significant overhead in area and/or latency. In this work, we propose an alternative 10-transistor (10T) bit-cell and a novel conditional pre-charge column circuit to save read power while simultaneously minimizing the overhead introduced by generating predictions. In addition, we develop a framework for *reconfigurable* memory in which data features are used to select an optimal prediction scheme per column of the proposed SRAM, making it well-suited for various energy-constrained applications with a wide range of data features.

## **1.2** Summary of contributions

This thesis focuses on the design of energy-efficient, data-dependent SRAMs equipped with reconfigurable prediction schemes and the methods by which application data statistics may be utilized to identify optimal configurations. The key contributions of this work are twofold. First, we propose a general framework and the associated analysis tools for developing reconfigurable low-power memories that take into account application-specific information provided by software. Second, an example reconfigurable CP SRAM adhering to the proposed framework is presented which includes the novel designs of a 10T bit-cell, a prediction-based conditional pre-charge scheme, and a column-wise reconfigurable dual prediction mode architecture. Incorporating these innovations, a 16kbit SRAM test chip is developed in a 28nm Fully-Depleted Silicon-on-Insulator (FD-SOI) Complementary Metal-Oxide Semiconductor (CMOS) process. Using its post-layout simulations, the proposed SRAM is found to provide 14%-20%, 4%, and 31% reductions in read power as compared with a conventional 8-transistor (8T) SRAM for three targeted applications: the coefficient SRAMs in a sparse Fast Fourier Transform (sFFT) implementation, the Support Vector Machine (SVM) weights SRAM in an objection detection system, and the Motion Estimation (ME) reference pixel SRAM in a video coding system, respectively.

## Chapter 2

## A survey of low power SRAMs

Key metrics of on-chip SRAM designs include power and/or energy, performance, area, and robustness. These metrics often imply critical design tradeoffs for which careful analysis and creative thinking may lead to an acceptable balance by taking into account the targeted application. This thesis focuses in particular on the design of low-power SRAMs for energy-constrained systems using this approach.

The total power consumption of SRAM consists primarily of power incurred during read and write accesses and leakage power wasted during data retention. This thesis emphasizes on SRAMs active operations for which average dynamic power, corresponding to per unit time energy consumed for charging and discharging capacitive loads, is regarded as the critical metric. The majority of SRAM dynamic power dissipation occurs during the switching of its highly capacitive bit-lines. In particular, the power consumed by bit-line switching can be written as

$$P = \alpha_{0 \to 1} C_{BL} V_{dd}(\Delta V) f, \qquad (2.1)$$

where  $\alpha_{0\to 1}$  is the activity factor,  $C_{BL}$  is the bit-line capacitance,  $V_{dd}$  is the supply voltage,  $\Delta V$  is the minimum amount of voltage development required on the bit-line for the sensing circuit to correctly resolve the read value, and f is the frequency of operation.

This thesis considers applications in which the total number of data accesses is high and read operations occur much more frequently than write operations. Hence, our design effort is primarily spent on the reduction of dynamic power dissipated on the read bit-lines.

## 2.1 Overview of low power techniques

The conventional 6-transistor (6T) SRAM is the most common type of on-chip memory due to its merit of high density [12]. However, in its most primitive form, 6T is inherently energy-inefficient. Power is consumed on its bit-lines during every read operation irrespective of the specific data being read. In this sense, 6T SRAM has 'dynamic' read operations in that every data evaluation is contingent on a bit-line pre-charge activity which always consumes a considerable amount of power. This implies that the combined  $\alpha_{0\to 1}$  in Eq. 2.1 corresponding to both bit-lines is at its maximum (= 1) for 6T read operations.

In the literature, much work has focused on reducing power via voltage scaling, i.e. to lower the supply voltage  $V_{dd}$  or  $V_{min}$  as it is sometimes referred to in SRAMs. By lowering  $V_{dd}$  both leakage and dynamic power are saved [5]. However, operating SRAM at low voltages is generally challenging in that it requires a significant amount of design effort to deal with issues such as increased soft error rate, degraded read static noise margin, and reduced write margin due to the exponential impact of intensified  $V_T$  variations (e.g., [34, 23]). To guarantee SRAM's reliability and robustness under all operating conditions is a critical task and a research area of its own. We refer readers to [24] for a rigorous and complete development of this subject. Other approaches, for example minimizing  $\Delta V$  by designing low-offset or offset-compensated sense amplifiers (e.g., [30]), have been undertaken. However, due to increased device variations at

Figure 2-1: The conventional 8T bit-cell.

reduced  $V_{dd}$ , worst-case  $\Delta V$  approaches  $V_{dd}$  in value.

## 2.2 The data dependent approach

As a consequence of the previously discussed limitations associated with voltage scaling, SRAM designers have looked into new ways of reducing memory power. One such way is to minimize switching activity  $\alpha_{0\to1}$  of bit-lines using or introducing correlation in stored data. Data stored in an SRAM often has particular properties that can be leveraged for application-specific designs. An example of an application-specific SRAM is presented in [8]. This work recognizes the inherent data dependency of 8T SRAM, a bit-cell of which is depicted in Fig. 2-1. Referring to this figure, 8T SRAM's pre-charged read bit-line **RBL** is only discharged when reading a 0 (or a 1 if the single read port is connected to Q). By using majority logic and data-bit inverting, this design maximizes the number of 1s stored in the SRAM resulting in minimized total power consumption. This scheme works well for heavily skewed data. However, when the percentage of 1s is close to 50%, 8T SRAM consumes at least half of the read power of a 6T SRAM.

New bit-cells as well as architectural designs have helped in leveraging data correlation. For example, [26] and [7] respectively designed a prediction-based 10T SRAM and a priority-based 6T/8T hybrid SRAM to maximize total power savings in

Figure 2-2: PB-RBSA bit-cell. Figure adapted from [26].

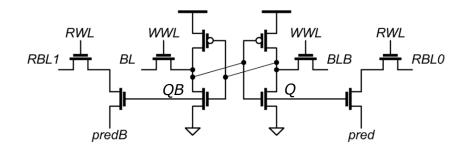

real-time video applications. The prediction-based reduced bit-line switching activity (PB-RBSA) SRAM design, as presented in [26], reduces bit-line switching activity by using correlation present in video data and a bit-cell topology that uses a bit-wise prediction provided by a separate arithmetic averaging block. As illustrated by the PB-RBSA bit-cell diagram in Fig. 2-2, the footer nodes of the two read ports are not connected to ground but two prediction lines **pred** and **predB**. With a correct prediction, i.e. **pred** = **Q** and **predB** = **QB**, both read bit-lines **RBL0** and **RBL1** stay at  $V_{dd}$  during a read evaluation. A major drawback of this design is the highly capacitive prediction lines **pred** and **predB** that span the entire height of the array. Therefore, driving and changing predictions creates a significant power overhead and introduces critical tradeoffs between the prediction accuracy and the power consumption of prediction lines.

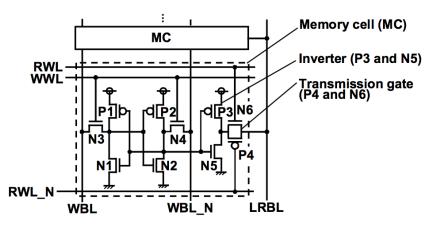

Alternative SRAM models may also benefit from utilizing data correlation. For instance, the work in [21] eliminates the pre-charge phase entirely by using a 10T bit-cell with a statically driven read bit-line. A depiction of this bit-cell design is provided in Fig. 2-3. When reading the same or similar data between cycles, this *static* SRAM has minimal switching on its read bit-lines. However, both latency and area are major concerns of this approach.

In Table 2.2 we compare our approach against the previously mentioned relevant data-dependent memory models. As is evident in our discussion this far, previous

Figure 2-3: 10T non-precharge-type two-port memory cell. Figure adapted from [21].

| Work              | Design Idea                               | Targeted Application(s) |

|-------------------|-------------------------------------------|-------------------------|

| Noguchi '07 [21]  | A non-precharge 10T SRAM for reduc-       | video applications      |

|                   | tion in bit-line switching activity       |                         |

| Fujiwara '08 [8]  | An 8T SRAM using majority logic and       | video applications      |

|                   | data-bit reordering for reduction in bit- |                         |

|                   | line switching activity                   |                         |

| Chang '11 [7]     | A priority-based 6T/8T hybrid SRAM        | video applications      |

|                   | for aggressive voltage scaling            |                         |

| Sinangil '14 [26] | A 10T PB-RBSA SRAM using out-             | video coding            |

|                   | put prediction for reduction in bit-line  |                         |

|                   | switching activity                        |                         |

| This work         | A conditional pre-charge 10T SRAM         | sFFT, object detection, |

|                   | using reconfigurable prediction schemes   | video coding            |

|                   | for reduction in bit-line switching ac-   |                         |

|                   | tivity                                    |                         |

Table 2.1: Comparison with relevant data-dependent SRAM models

work has identified opportunity in a data-dependent SRAM approach. However, room for improvement exists in that no one has fully developed a generic model that would work well across various applications. Toward this end, this thesis aims to leverage these ideas by incorporating a wide range of data features into the design of a single SRAM. Both circuit- and architectural-level techniques are explored in order to realize dynamic power savings with minimal area overhead. In Section 3.3.3, we compare our proposed SRAM against the models mentioned in this section.

## Chapter 3

# Energy-efficient reconfigurable memory

#### 3.1 A general framework

In this chapter, we present our reconfigurable memory framework in which application specific information such as data statistics are generally obtained via software in order to dynamically configure our memory hardware. Two statistical measures are repeatedly considered in the analysis in this thesis, namely the global correlation measure  $\rho$  and the local correlation measure  $\alpha_{0\to 1}$ , equivalently referred to as the switching activity factor. The global correlation measure shows how biased a data sequence is in its bit values. It is generated by

$$\rho \triangleq \frac{M}{N},$$

(3.1)

where M is the number of occurrences of the majority bit in a given data sequence of length N. For example, 1 is the majority bit in the sequence 1111111100 since there are eight 1s out of the total ten bits. In this case, M = 8, N = 10, and therefore  $\rho = 0.8$  or 80%. On the other hand, the local correlation measure shows how often a  $0 \rightarrow 1$  bit-level change occurs in a given data set. It is generated by

$$\alpha_{0\to 1} \triangleq \frac{\text{number of } 0 \to 1 \text{ transitions}}{N-1}.$$

(3.2)

With these definitions in place, we comment that the local and global correlation measures respectively satisfy  $\alpha_{0\to 1} \in [0, 0.5]$  and  $\rho \in [0.5, 1]$  while not all  $(\rho, \alpha_{0\to 1})$ pairs in  $[0.5, 1] \times [0, 0.5]$  are obtainable since the measures are correlated themselves. We refer to correlated data in what follows as a data sequence with high global and/or local correlation, i.e. a large  $\rho$  and/or a small  $\alpha_{0\to 1}$ .

As illustrated by Fig. 3-1, statistical parameters such as  $\rho$  and  $\alpha_{0\to 1}$  are passed from software to the prediction generation block, i.e. the *predictor*, which communicates directly with the memory array. The software program specifically takes the profiled data set for a targeted application and passes to the predictor a number of computed statistical measures. Equipped with this information as well as other inputs from the memory, the predictor identifies the optimal prediction mode from which prediction values for each memory read operation are generated and provided to the memory unit. In this sense, the memory in this framework is reconfigurable since a number of prediction modes are available for selection. Equipped with this infrastructure and knowledge of application-specific statistics, the proposed memory can support low-power data access for various classes of applications with distinct data features.

Figure 3-1: An illustration emphasizing the communication between software and memory hardware via the predictor in the proposed reconfigurable memory framework.

This thesis in part focuses on the exploration and design of a compact architecture

which endorses reconfigurability as previously described. In addition, pertinent questions involving the selection of appropriate prediction schemes and the identification of sufficient statistics to discern which scheme is best suited to a particular application are addressed. In the remainder of this chapter, we present our design at different hierarchical levels and address the above questions by means of simulation using a number of novel and existing memory designs. We conclude this chapter with an example SRAM adhering to the presented framework which constitutes our final design.

## 3.2 Conditional pre-charge SRAM

#### 3.2.1 Proposed bit-cell design

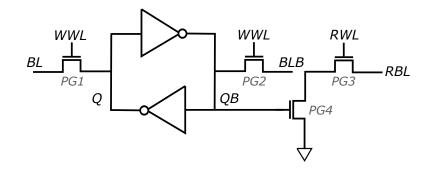

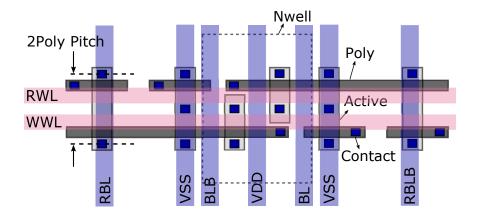

Figure 3-2 shows our proposed bit-cell design. The 10T bit-cell depicted subsumes a standard 6T bit-cell, i.e. two cross-coupled inverters and two access NMOS transistors, and two additional read ports. Read operations are decoupled from write operations in this memory cell since separate word lines (RWL and WWL) and bit-line pairs (RBL/RBLB and BL/BLB) are used for read and write control and accesses, respectively. Equipped with separated read ports, the 10T bit-cell is exempt from read stability issues as is the conventional 8T memory cell. Additionally, it may be used to construct two-port SRAMs wherein simultaneous read and write bit-line accesses are allowed. This design avoids the prediction line power overhead observed in the 10T bit-cell design in [26] by grounding the sources of the two bottom read port devices. Alternatively, prediction signals are passed to the memory via pre-charge circuitry as is discussed in Section 3.2.2.

Figure 3-2: The proposed 10T bit-cell consisting of two cross-coupled inverters, two access NMOS transistors for the write bit-lines BL and BLB, and two read ports connected to the read bit-lines RBL and RBLB.

#### 3.2.2 Conditional pre-charge

The column architecture of the proposed 10T memory array is provided in Fig. 3-3. Write operations are handled using the conventional 6T portion of the bit-cell. In particular, BL and BLB are driven to the desired values of the input and its complement, and then, with the WWL asserted, values on these bit-lines get passed to the bit-cell storage nodes Q and QB and overwrite their original values. Read operations in this design selectively utilize one of the read ports depending on the current prediction value. The general idea is to always pre-charge the bit-line on the side that is predicted to store a 0, a scheme we henceforth refer to as *conditional* pre-charge. In particular, two PMOS transistors (P1 and P2) in the pre-charge circuit are controlled by a pair of prediction signals, specifically, by the prediction **pred** and its complement predB. When the pre-charge enable signal prechB is asserted, one of the read bit-lines is charged through the turned-on PMOS stack while the other read bit-line's connection to the power supply is cut off. A pair of crossed-coupled NMOS transistors (CNN) keeps the unselected read bit-line low while the selected one is pre-charged high. Hereon, we refer to this design as the Conditional Pre-charge SRAM (CP SRAM).

Figure 3-4 illustrates two example cases for a read operation. Suppose the bit-cell nodes have the values Q = 0 and QB = 1. Figure 3-4(a) depicts a correct prediction,

i.e. pred = 0. In this case, RBL is charged high in the pre-charge phase while RBLB is kept low. During evaluation, the discharge path is open thus RBL stays high for the next read cycle. Figure 3-4(b) depicts an incorrect prediction. In this case, pre-charged RBLB discharges through the turned-on PMOS transistors during evaluation. Making correct predictions for the CP SRAM leads to reduced total pre-charge activity and consequently decreases the total energy consumed on the bit-lines.

It should be noted that the above arguments are valid if off-state leakage current is small as compared with the total on-state current. This is generally the case for regular threshold voltage (regular  $V_T$ ) devices in technologies such as FD-SOI [15]. If leakage current is significant and the evaluation phase is sufficiently long, the pre-charged read bit-line will leak from  $V_{dd}$  to a low logic value even when the prediction is correct and the associated PMOS transistors are turned off. This would result in an incorrect read output. In the development of a prototype test chip using regular  $V_T$  devices in a FD-SOI technology, we further ensure the functionality of the presented read scheme by using fixed-width timing controls as is discussed in Chapter 4. Secondary effects including leakage current are considered in the post-layout simulations presented in Section 4.2.

As expected, the prediction sequence directly affects the amount of power savings achievable in prediction-based SRAMs. Arithmetic averaging is a suitable scheme for the PB-RBSA SRAM since changing prediction from cycle to cycle causes significant power overhead and therefore should be balanced by using a larger prediction generation window. For CP SRAM, however, updating the prediction value has a negligible cost overhead due to the embedded prediction devices P3 and P4 in the pre-charge circuitry. Making a prediction complementary to the current output invariably causes switching in the following pre-charge phase and in the evaluation phase if the updated prediction is incorrect (e.g., due to signal noise). In order to minimize these types of unnecessary switchings when data is sufficiently correlated, we propose the Previous-Read-Data

Figure 3-3: Column architecture of the proposed Conditional Pre-charge SRAM (CP SRAM). One of the read bit-lines is pulled high depending on the current prediction values (pred, predB) via the associated pair of pre-charge PMOS transistors. The other read bit-line is kept low by one of the cross-coupled NMOS transistors N1 and N2.

Figure 3-4: (a) Correct and (b) incorrect prediction cases during a read operation with the CP SRAM. The conditionally pre-charged read bit-line remains high if the prediction is correct and is discharged to low if the prediction is wrong.

(PRD) prediction scheme where the data value currently being accessed is used to generate the next prediction. Our analysis shows that for a broad range of data profiles, PRD is a better option as compared with arithmetic averaging in terms of area, simplicity, and power savings with correlated data. Consistent with this remark, a simulation-based analysis of various prediction schemes is presented in Section 3.3.1. There are, of course, corner cases where PRD does not result in power saving, e.g., when  $\alpha_{0\to1} = 0.5$ . These cases will be examined in detail and handled by selecting a different prediction mode of the reconfigurable SRAM. Finally, it should be noted that more complex and application-specific prediction generation designs can easily be incorporated into the framework. However, since this work serves as a proof of concept and demonstration of a simple generic system, we henceforth focus our attention to only PRD and arithmetic averaging with variable length average window sizes.

## 3.3 Evaluation of memory models and prediction schemes

We proceed to evaluate the tradeoffs amongst various memory models and their associated performance capabilities for different data sets using a custom dynamic power simulation program wherein the total read power consumption of applicationspecific and synthetic data alike is computed for each model. In high density arrays, bit-line switching activity accounts for the majority of total power consumption during read accesses [26]. Therefore, for the sake of tractability, we focus our evaluation to power consumption on read bit-lines. The custom program design specifically allows for flexibility in the sense of parameterized bit-line and prediction-line capacitances as well as bit-line voltage swing.

We respectively propose and consider the following designs:

- (i) *CP-SRAM* : conditional pre-charge SRAM

- (ii)  $\delta T$ : conventional  $\delta T$  SRAM wherein the bottom gate of the read port is connected to Q

- (iii) *static* : non-precharge static SRAM

- (iv) *PB-RBSA* : prediction-based reduced bit-line switching activity SRAM

where (ii)-(iv) are as previously mentioned and listed here for completeness.

The justification of these designs for energy-constrained systems is twofold. First, by using separated read port(s), resulting in high read stability, these memories have the potential to support aggressive voltage scaling. Second, the read power consumption of each design depends critically upon data statistics such as  $\alpha_{0\to1}$ , as was discussed previously. Further power savings can be achieved by leveraging the data-dependent capability of each memory design thus motivating a careful analysis of these dependencies via the custom program.

The simulation program takes as an input SRAM data in one of three ways: specified by the user, synthesized using correlation parameters such as  $\alpha_{0\to 1}$  and  $\rho$ , or profiled from an application. For a given data array, the simulator first populates the corresponding prediction array for each of the prediction-based SRAMs (CP-SRAM and PB-RBSA) for the prediction schemes indicated by the user. Then, for each memory type, it identifies the power-incurring switching activities associated with reading data out the array in a sequential order. Bit-line power, as described in Eq. 2.1, is incurred on the bit-line(s) during pre-charge activity for 8T, PB-RBSA and CP-SRAM and during *1-after-0* data accesses for static SRAM. For PB-RBSA, switching the **pred** and **predB** lines contributes additional power consumption, which we henceforth regard as similar in cost to the power incurred on the bit-lines for simplicity. Loosely speaking, this implies that  $C_{PL} \approx C_{BL}$ . Lastly, adhering to Eq. 2.1, the total power consumption for each column of the memories considered, parameterized using the bit-line capacitances ( $C_{BL}$  and  $C_{PL}$ ) and bit-line voltage swing ( $\Delta V$ ), is computed.

Sensing networks are a critical peripheral circuit in an SRAM. The choice of utilizing small signal sensing by employing Sense Amplifiers (SA) to amplify small signal variations on the bit-lines into full swing output signal, or large signal sensing directly affects the minimum value of  $\Delta V$ . Other contributing factors include the implementation technology as well as the process, voltage and temperature variation effects. Generally, a  $\Delta V$  value of 0.1V is achievable with  $V_{dd} = 1$ V. However, considering worst case process variations when operated at a lower  $V_{dd}$  and/or the power overhead of offset compensation circuit, we assume that the  $\Delta V$  associated with small signal sensing is approximately  $\frac{2}{5}$  of the  $\Delta V$  associated with large signal sensing which is itself approximately equal to  $V_{dd}$ . The bit-line(s) of PB-RBSA and 8T SRAM are often evaluated with SAs whereas the bit-line of static SRAM and the prediction lines of PB-RBSA require full-swing operations. We summarize this assumption as

$$\Delta V \approx \begin{cases} V_{dd}, & \text{for static, PB-RBSA prediction-line} \\ \frac{2}{5}V_{dd}, & \text{for 8T, PB-RBSA} \end{cases}$$

(3.3)

We consider CP-SRAM with both small and large signal sensing networks. We next comment on the read power simulations for each of the three data types under the assumptions established in this subsection.

Figure 3-5: Normalized read bit-line power consumption of CP-SRAM using prediction scheme PRD vs arithmetic averaging for various average window sizes (w). Three data sets are used: (i)  $2^{16}$  16-bit binary number combinations, (ii) synthetic data with  $\alpha_{0\to 1} = 0.25$  and  $\rho = 0.5$ , and (iii)  $1080 \times 1920$  highly compressed ME reference frame pixels.

Figure 3-6: Organization of the input data set (i). The exhaustive collection of  $2^N$  N-bit binary number combinations cover all possible patterns of the data stored in column <c> in an SRAM of size  $N \times M$ .

#### 3.3.1 Prediction scheme

The normalized total read power consumption of CP-SRAM is depicted in Fig. 3-5 for both PRD and arithmetic averaging prediction schemes where the average window size  $w = 2^k$  ranges from k = 1 to k = 6. The results reported correspond to three input data sets: (i) an exhaustive collection of  $2^N$  N-bit binary number combinations for N = 16, (ii) a randomly synthesized data set with statistics  $\alpha_{0\to 1} = 0.25$  and  $\rho = 0.5$ , and (iii) 1080 × 1920 highly compressed Motion Estimation (ME) reference pixels extracted using the scheme discussed in Section 5.2.2. In regard to data set (i), the organization of the data set into memory is illustrated by Fig. 3-6 for an SRAM of size  $N \times M$ . Referring to an arbitrary column <c>, the bit values are read sequentially, i.e.  $b_0 \rightarrow b_{N-1}$ . As is indicated on the right, the exhaustive nature of (i) ensures that all possible patterns of data that can be stored in a column are considered. Furthermore, we comment that the mapping of an N-bit binary sequence to a  $(\rho, \alpha_{0\to 1})$  pair is not unique and so this approach facilitates the analysis of all possible  $(\rho, \alpha_{0\to 1})$  pairs achievable by a binary sequence of length N. For the purpose of demonstration and consistent with a wide range of values of N, the results displayed in Fig. 3-5 use

Figure 3-7: Normalized read bit-line power consumption of CP-SRAM for every 16-bit binary number combination for prediction scheme PRD and arithmetic averaging (w = 8). The indexing corresponds to decreasing  $\alpha_{0\to 1}$  for the exhaustive data set.

N = 16. We remark that our analysis and conclusions do not rely critically upon the specific value of N and in this sense we proceed taking N = 16 hereon for consistency.

Observe in Fig. 3-5 that only the applicable average window sizes are simulated for data sets (i) and (iii). Nonetheless, common to all three input data sets, PRD-based prediction results in the lowest total bit-line power consumption. This advantage of PRD is most evident for ME reference pixels which, on average, have a higher local correlation measure (a lower  $\alpha_{0\to 1}$ ) than the 16-bit binary number combinations.

In order to compare the performance of these prediction schemes more rigorously, the read power consumption is computed for each data sequence in the exhaustive set of 16-bit binary number combinations. The normalized power consumption of these sequences, sorted according to decreasing switching activity, shows that power consumption of CP-SRAM with PRD decreases monotonically with  $\alpha_{0\to1}$  whereas arithmetic averaging is not smoothly related to  $\alpha_{0\to1}$  (Fig. 3-7). For low values of  $\alpha_{0\to1}$  (toward the right-hand side of the plot) PRD incurs less power for most cases and on average as compared with arithmetic averaging. This result is consistent with our previous discussion, in particular that PRD is a better scheme in terms of power savings when the data is locally correlated which manifest itself as a low  $\alpha_{0\to 1}$  value. Subsequently, we proceed in our presentation by pairing the CP SRAM design with the PRD prediction scheme and henceforth refer to their joint use as CPSRAM.

Figure 3-8: Normalized read bit-line and prediction-line power of various memory models for synthesized data sets with various switching activity factors  $\alpha_{0\to 1}$ . All data sets have  $\rho = 0.5$ .

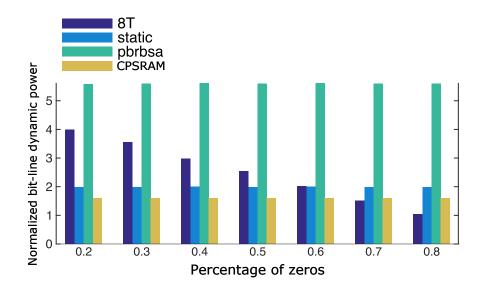

### 3.3.2 Power dependency on data statistics

As was previously mentioned, a built-in subroutine of the custom simulation program allows synthetic SRAM data to be generated for a prespecified pair ( $\rho$ ,  $\alpha_{0\to1}$ ). This capability allows us to explore the data-dependent features of each memory design in great detail. For instance, as shown in Fig. 3-8, the read power of both predictionbased and static SRAM is seen to scale appropriately with increasing  $\alpha_{0\to1}$  while  $\rho$ , or specifically here the percentage of 0s of each data set, is held constant at 0.5. The read power of 8T, however, remains relatively constant with respect to switching activity. Figure 3-9 plots the read power of the selected memory models using data

Figure 3-9: Normalized read bit-line and prediction-line power of various memory models for synthesized data sets with various percentages of 0s. All data sets have  $\alpha_{0\to 1} = 0.15$ .

sets with constant  $\alpha_{0\to 1} = 0.15$  and increasing percentage of 0s. Observe that 8T's read power decreases as the number of 0s in the data set increases while the others' remain relatively constant.

### 3.3.3 Model evaluation

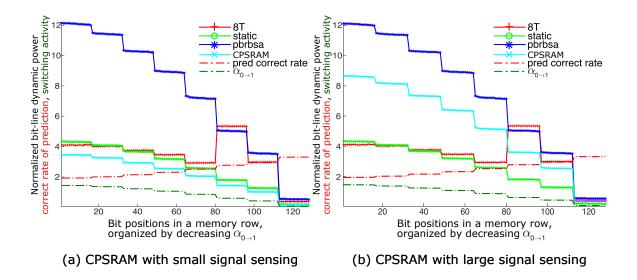

Pixel values from a  $1080 \times 1920$  video frame, extracted from the 'Park Scene' video sequence belonging to the Joint Collaborative Team on Video Coding (JCT-VC) common test conditions [3], have been pre-profiled into an array structure, in mimicry of the block-based retrieval pattern found in High Efficiency Video Coding (HEVC) motion search. This is further discussed in Section 5.2.2. Figure 3-10 illustrates the normalized read power consumption of the video frame pixels for all four memory models. Referring to this figure, CPSRAM with both small (a) and large (b) signal sensing networks are considered. In particular, (a) assumes that  $\Delta V(8T, PB-RBSA)$ :  $\Delta V(CPSRAM) : \Delta V(static, PB-RBSA prediction-line) = 1 : 1 : 2.5$ , i.e. the minimum

Figure 3-10: Normalized read bit-line and prediction-line power of various memory models for pixels in a highly-compressed HEVC ME reference frame. Bit positions are organized by decreasing  $\alpha_{0\to 1}$ . Voltage swing ratio  $\Delta V(8T, \text{PB-RBSA})$ :  $\Delta V(\text{CPSRAM})$  :  $\Delta V(\text{static, PB-RBSA prediction-line}) = (a) 1 : 1 : 2.5 and (b)$ 1 : 2.5 : 2.5.

amount of voltage development on the bit-line(s) of 8T, PB-RBSA, and CPSRAM is  $\frac{2}{5}$  of that on the static SRAM read bit-line and the PB-RBSA prediction-lines. This assumption is only valid if 8T, CPSRAM, and PB-RBSA SRAMs are designed with small signal sensing circuits. On the other hand, if CPSRAM makes use of large signal sensing, then the second ratio of  $\Delta V(8T, PB-RBSA) : \Delta V(CPSRAM) :$  $\Delta V(static, PB-RBSA prediction-line) = 1 : 2.5 : 2.5$  should be used for power computation as is the case in (b).

Observe from (b) that static SRAM is strictly better than CPSRAM in terms of bitline power consumption when their switching costs are assumed to be equal. Loosely speaking, for any data profile CPSRAM has greater or equal  $\alpha_{0\to1}$  as compared with static SRAM. However, a key disadvantage of static SRAM is that it is considerably slower in read operations as compared to the other SRAMs considered. Since the targeted applications in this thesis require real-time speeds, we proceed without further consideration of static SRAM. Correct resolution of read data in static SRAM requires full bit-line voltage swing whereas the penalty of switching CPSRAM's bit-lines can be reduced by using sense amplifiers as shown in (a). We again call attention to the fact that the assumed  $\Delta V$  ratios here are conservative. The actual amount of power that is saved by using sense amplifiers is often insignificant due to the large bit-line capacitance and number of bit-cells per bit-lines and therefore increased SA sensitivity to process variation, device mismatches, etc. [29, 31, 39]. Additionally, adding sense amplifiers to the CPSRAM design causes significant overhead in area. For the obvious reasons, we proceed with large signal sensing for CPSRAM.

For each column in Fig. 3-10(b), either 8T or CPSRAM has the lowest read power consumption depending on the data statistics of that column. For the specific case shown (average  $\rho \approx 0.58$ ), CPSRAM consumes less power for columns with  $\alpha_{0\to1} < 0.126$ . This observation suggests that combining these two memory models into the design of a dual prediction mode SRAM would help reduce total power. Note that reading from an 8T SRAM is equivalent to reading from a CP SRAM using a *constant* prediction scheme, i.e. to always predict 0 or 1 for each column depending on which value constitutes the majority and consistently pre-charge the bit-line associated with the 0 prediction. In fact, CP SRAM with this bit-wise constant prediction scheme introduces the majority logic described in [8] to each column and would perform better than a data agnostic 8T SRAM. Thus, the hardware complexity associated with integrating two distinct SRAM models can be reduced by combining the two prediction schemes (PRD and constant) into the design of a single reconfigurable CP SRAM.

## 3.4 Proposed reconfigurable memory design

### 3.4.1 Two modes of read operation

In order to make accurate and low-power memory predictions for various data statistics, we propose in this thesis a conditional pre-charge SRAM with reconfigurable prediction modes wherein one of the two previously discussed prediction modes (PRD and constant) is selected for each SRAM column based on that column's data statistics. By independently operating each column in the preferred mode, i.e. finding and connecting the lowest points on the simulated power curves in Fig. 3-10 (b), we can achieve the maximum total read power savings for various applications and systems.

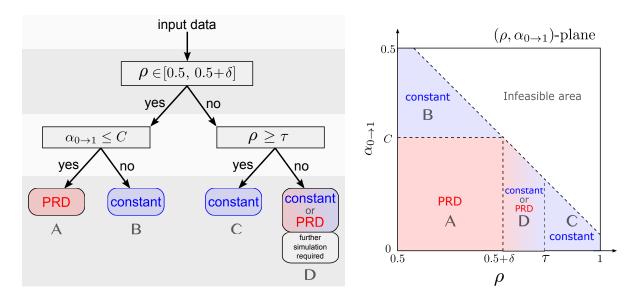

To this end, Fig. 3-11 shows an example decision tree on the left and an equivalent decision plane on the right. The depicted tree illustrates the procedure by which prediction modes are selected for each memory column. The presented decision tree is simplified in anticipation of the discussions in Chapter 5 surrounding three example applications and how, for each of them, the preferable SRAM configuration is identified in accordance with the decision branches. Referring to the figure, the red and blue coloring respectively indicate PRD and constant mode decisions. If the column's input data has a low global correlation, i.e.  $\rho$  is in the vicinity of 0.5 meaning the density of 0s and 1s are comparable, then we proceed to the left-hand branch to examine the local correlation coefficient  $\alpha_{0\to 1}$ . If  $\alpha_{0\to 1}$  is sufficiently small, then PRD is recommended for that column (label A); otherwise, constant should be selected to reduce bit-line switching activity (label B). If the input data set is sufficiently biased, i.e. if  $\rho$  is larger than some  $0.5 + \delta$  for some  $\delta$ , then we proceed to the right-hand branch. It should be noted that if the data set has a sufficiently high global correlation (label C) then its local correlation is also high by definition. An extreme example of this is a series of purely 0s or 1s. In this extreme case, the two modes perform equally well. However, constant mode is preferred due to its superior stability in the presence of

noise. For example, if one 0 value appears in the middle of a sequence of 1s, constant mode has equal or fewer discharging activities than PRD mode. Further simulations are required for data with no distinctive global or local correlation (label D). The parameters C,  $\delta$  and  $\tau$  are essential to the decision rule presented and are determined later in Section 4.2.2 via post-layout simulation.

Figure 3-11: A decision tree (left) and an equivalent decision plane (right) illustrating the procedure by which prediction modes are configured for each SRAM column.

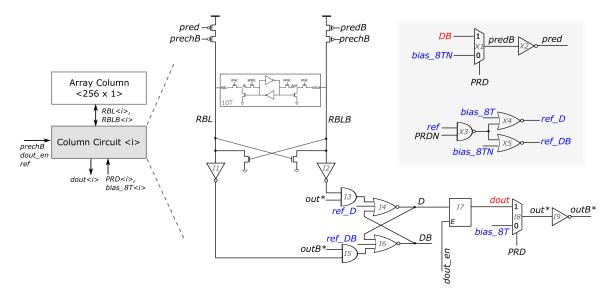

### 3.4.2 Proposed column circuit design

Figure 3-12 presents the column circuit for the reconfigurable CP SRAM. By adding a number of basic logic gates, e.g., multiplexers (MUX) and inverters, two prediction paths are introduced at the circuit-level. In particular, two inverters I1 and I2 are designed with skewed sizing to speed up the bit-line sensing. An And-Or-Invert (AOI) logic based Set/Reset (SR) latch takes the outputs of I1 and I2 along with the current prediction as inputs to resolve the read value. If one of the bit-lines stays high, meaning the prediction is correct, the SR latch holds the current values of D and DB; otherwise the SR latch inverts the values of D and DB reflecting that the read value is complementary to the prediction. Once the latch outputs settle and one of the bit-line is pre-charged high according to the next prediction, an enable signal dout en is asserted and a second latch, I7, latches D as the read output dout.

Figure 3-12: The proposed column circuit design which supports column-wise mode selection between PRD and constant prediction schemes. PRD signals are highlighted in red and constant signals are highlighted in blue.

While both prediction modes follow the above procedure for read operations, PRD and constant have separate prediction generation paths that are controlled by a mode selection signal PRD in MUXes I8 and X1. When PRD mode is selected, i.e. PRD is set to high, the value of DB is selected to generate the new prediction and dout is passed to the SR latch as the prediction feedback out\*. In constant mode, a DC bias control bias\_8T indicating the majority bit of the column is sent to the prediction generation and feedback paths. Additionally, since constant mode invariably predicts 0 or 1 and pre-charges the same bit-line, it requires a reset in the SR latch every read cycle by using a control signal ref.

## Chapter 4

# Implementation of the reconfigurable CP SRAM

Consistent with the general framework outlined in Chapter 3, a 16kbit, 28nm CMOS test chip was developed using CP SRAM utilizing the 10T bit-cell illustrated in Fig. 3-2, the prediction-based conditional pre-charge scheme discussed in Section 3.2, and the reconfigurable column circuit depicted in Fig. 3-12. The primary focus of this chapter is to present the associated memory array and system architectures, discuss the implementation of the test chip, and provide a number of selected results from post-layout simulations. To begin, we discuss in Section 4.1 the specific architectures implemented at the array, macro system and chip levels as well as associated physical design considerations. In Section 4.2, post-layout simulation results are presented including functional verification of the system across process corners and power measurements for various operation modes and data sequences.

## 4.1 System architecture and physical design in 28nm FD-SOI CMOS

### 4.1.1 Memory array architecture

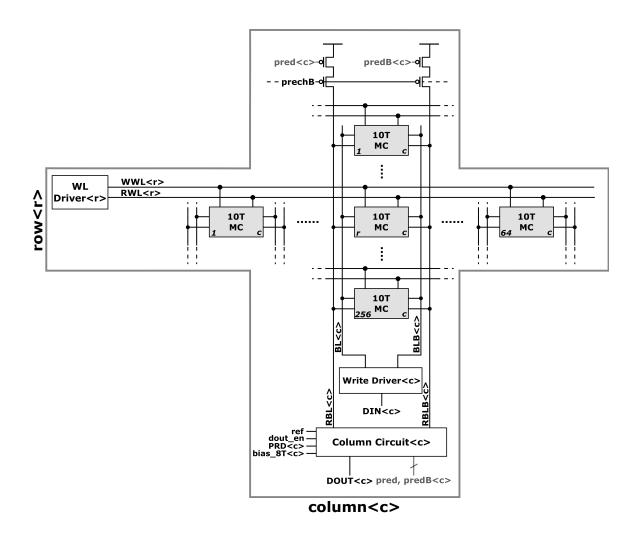

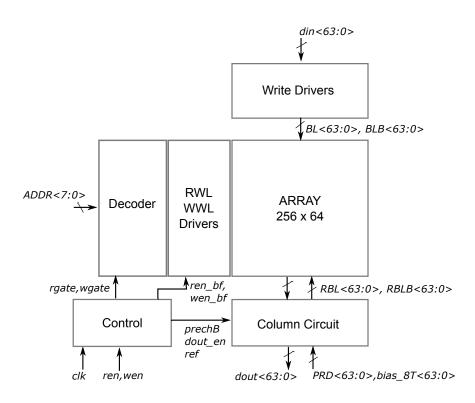

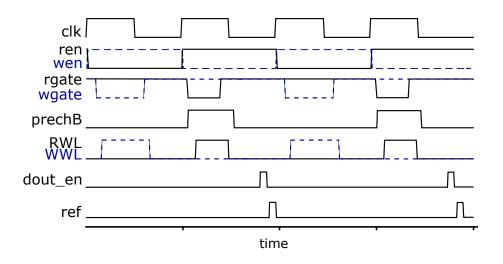

The SRAM array architecture is depicted in Fig. 4-1; the array is 16kbit in size and contains 256 rows and 64 columns of 10T memory cells along with row and column peripheral circuits. Specifically, memory cells in the same row share a Write Word Line (WWL) and a Read Word Line (RWL). During an active read/write cycle, one of these word lines is driven high through a word line driver depending on the specific operation performed. On the other hand, memory cells in the same column share a pair of write bit-lines (BL/BLB) and a pair of read bit-lines (RBL/RBLB). During a write operation, BLs and BLBs are driven to the desired bit values of input DIN by 64 write drivers. Each pair of RBL/RBLB is connected to pre-charge circuitry that consists of two PMOS transistors controlled by a global timing signal prechB and two other PMOS transistors controlled by a pair of column-specific prediction signals is generated internally in a column circuit which also facilitates output sensing and configuration of prediction mode.