# A Wide Dynamic Range CMOS Imager With Parallel On-Chip Analog-to-Digital Conversion

by

# Steven John Decker

B.S., The Ohio State University (1988) S.M., Massachusetts Institute of Technology (1991)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 1997

© Massachusetts Institute of Technology 1997

Signature of Author

Department of Electrical Engineering and Computer Science September 3, 1997

Certified by

Charles G. Sodini Professor of Electrical Engineering and Computer Science Thesis Supervisor

Accepted by

Arthur C. Smith

Chair, Department Committee on Graduate Students

# A Wide Dynamic Range CMOS Imager With Parallel On-Chip Analog-to-Digital Conversion

by Steven John Decker

Submitted to the Department of Electrical Engineering and Computer Science on September 5, 1997, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

# **Abstract**

The imager is the front-end of any machine vision system. Traditional machine vision systems have used CCD video cameras with a single analog output channel, which results in several limitations. The single output channel is generally designed for human vision, around 30 frames/sec, which is much slower than desirable for some machine vision tasks. The imager dynamic range is low compared to the scene dynamic range, which can be as much as 100,000:1 for automotive applications. The analog output format is incompatible with digital processing chips, requiring additional chip(s) for correlated double-sampling, gain control, and analog-to-digital conversion.

This thesis describes the theory, design, and characterization of a prototype  $256 \times 256$  CMOS active pixel sensor (APS) array which addresses these problems. Array output is column-parallel, allowing a high frame rate. Dynamic range is increased using a technique which varies the lateral overflow gate voltage over the integration period. The compression curve is digitally controlled and user-adjustable. Fixed-pattern noise (FPN) is partially removed by a switched-capacitor circuit. Imager output is digitized on-chip by cyclic analog-to-digital converters.

The prototype imager was manufactured in a 0.8  $\mu$ m CMOS process with linear (poly - n<sup>+</sup>) capacitors. The imager was characterized at 30 frames/sec, although operation was verified for frame rates between 30 and 400 frames/sec. The saturation level was 1.69 V, and random noise was 0.57 mV (1  $\sigma$ ), producing a dynamic range of 3000 for the linear imaging mode. The wide dynamic range imaging technique increases dynamic range by 20× with good image quality, and by approximately 160× with reduced image quality. The static power dissipation was 52 mW. Pixel FPN for a dark frame was 3.9 mV (1  $\sigma$ ), and column FPN was 1 mV (1  $\sigma$ ).

Thesis Supervisor: Charles G. Sodini

Title: Professor of Electrical Engineering and Computer Science

# **Dedication**

This thesis is dedicated to my parents, Ronald and Shirley Decker.

# Acknowledgements

Funding for this work was provided through the National Science Foundation and the Advanced Projects Research Administration under contract MIP-9423221.

I wish to thank my advisor, Professor Charles Sodini, for suggesting the thesis topic. His technical guidance, positive attitude, and ability to see the fundamental issues have been extremely valuable. I deeply appreciate his steady support for the project, and for me, over the past several years.

Kevin Brehmer hosted me for a month at National Semiconductor Corporation in Santa Clara, and provided the chip fabrication. His hospitality and technical input have been invaluable. I would like to thank my thesis readers, Dan McGrath and Hae-Seung (Harry) Lee, for freely sharing their knowledge and experience, and for taking the time to read and comment on the thesis. Professor John Wyatt provided valuable insight into the operation of the wide dynamic range pixel, and invested enormous effort in forming and leading the MIT Vision Group. Ichiro Masaki has continued the effort, and ensured continued funding so that this project could be completed.

Jen Lloyd and Jeff Gealow invested an enormous amount of time in bringing up the CAD tools used in this project. Their effort, and their willingness to help with all types of computer trouble, are deeply appreciated. I would like to thank them and my other colleagues, including Joe Lutsky, Chris Umminger, Ignacio McQuirk, Michael Ashburn, Dave Martin, and Andy Karanicolas, for providing insights, discussion, and friendship. My UROP, Steve Kim, is also owed a debt of gratitude for his efforts in producing a working camera.

Finally, I would like to thank my family for their constant understanding and support.

# **Contents**

| 1 | Intr | oducti | on                             | 14 |

|---|------|--------|--------------------------------|----|

| 2 | Bac  | kgroun | ıd                             | 17 |

|   | 2.1  | Image  | r Performance Characterization | 18 |

|   |      | 2.1.1  | Quantum Efficiency             | 18 |

|   |      | 2.1.2  | Conversion Gain                | 18 |

|   |      | 2.1.3  | Random Noise                   | 18 |

|   |      | 2.1.4  | Saturation Level               | 19 |

|   |      | 2.1.5  | Fixed-Pattern Noise            | 19 |

|   |      | 2.1.6  | Image Lag                      | 20 |

|   |      | 2.1.7  | Smear                          |    |

|   |      | 2.1.8  | Crosstalk                      |    |

|   |      | 2.1.9  | Anti-Blooming                  |    |

|   | 2.2  | CCD I  | Imagers                        |    |

|   |      | 2.2.1  | CCD Pixels                     |    |

|   |      | 2.2.2  | CCD Architectures              |    |

|   |      | 2.2.3  | CCD Performance                |    |

|   | 2.3  | MOS I  | Imagers                        |    |

|   |      | 2.3.1  | MOS Array Architecture         |    |

|   |      | 2.3.2  | Charge Output Pixel            |    |

|   |      | 2.3.3  | Current Output Pixel           |    |

|   |      | 2.3.4  | Voltage Output Pixel           |    |

|   | 2.4  |        | arison of CCD and CMOS Imagers |    |

|   |      | 2.4.1  | Quantum Efficiency             |    |

|   |      | 2.4.2  | Conversion Gain                |    |

CONTENTS 6

|   |     | 2.4.3                                                                 | Random Noise                                                                                                                                                                                                                             | 63                                           |

|---|-----|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   |     | 2.4.4                                                                 | Saturation Level                                                                                                                                                                                                                         | 64                                           |

|   |     | 2.4.5                                                                 | FPN                                                                                                                                                                                                                                      | 64                                           |

|   |     | 2.4.6                                                                 | Image Lag                                                                                                                                                                                                                                | 65                                           |

|   |     | 2.4.7                                                                 | Crosstalk                                                                                                                                                                                                                                | 65                                           |

|   |     | 2.4.8                                                                 | Anti-Blooming                                                                                                                                                                                                                            | 66                                           |

|   |     | 2.4.9                                                                 | System Integration                                                                                                                                                                                                                       | 66                                           |

|   | 2.5 | Dynar                                                                 | mic Range Expansion                                                                                                                                                                                                                      | 67                                           |

|   |     | 2.5.1                                                                 | Nonlinear Imaging Element                                                                                                                                                                                                                | 67                                           |

|   |     | 2.5.2                                                                 | Multiple Integration Periods                                                                                                                                                                                                             | 72                                           |

|   | 2.6 | Comp                                                                  | arison of Compressive Imaging Techniques                                                                                                                                                                                                 | 76                                           |

|   | 2.7 | Comp                                                                  | arison of On-Chip ADC Architectures                                                                                                                                                                                                      | 76                                           |

|   |     | 2.7.1                                                                 | Delta-Sigma Converter                                                                                                                                                                                                                    | 78                                           |

|   |     | 2.7.2                                                                 | Flash Converter                                                                                                                                                                                                                          | 79                                           |

|   |     | 2.7.3                                                                 | Dual-Slope Converter                                                                                                                                                                                                                     | 79                                           |

|   |     | 2.7.4                                                                 | Algorithmic Converters                                                                                                                                                                                                                   | 80                                           |

| 3 | The | Wide                                                                  | Dynamic Range Pixel                                                                                                                                                                                                                      | 82                                           |

|   | 3.1 | Introd                                                                | uction                                                                                                                                                                                                                                   | 82                                           |

|   | 3.2 | Barrie                                                                | r Waveform and Compression Curve: Continuous-Time                                                                                                                                                                                        | 84                                           |

|   |     | 3.2.1                                                                 | Physical Modeling                                                                                                                                                                                                                        | 84                                           |

|   |     | 3.2.2                                                                 | Forward Problem                                                                                                                                                                                                                          | 87                                           |

|   |     | 3.2.3                                                                 | Reverse Problem                                                                                                                                                                                                                          | 80                                           |

|   | 3.3 |                                                                       | Reverse Problem                                                                                                                                                                                                                          | UJ                                           |

|   |     | Barrie                                                                | r Waveform and Compression Curve: Stepped Barrier                                                                                                                                                                                        |                                              |

|   |     | Barrie 3.3.1                                                          |                                                                                                                                                                                                                                          | 90                                           |

|   |     |                                                                       | r Waveform and Compression Curve: Stepped Barrier                                                                                                                                                                                        | 90<br>91                                     |

|   |     | 3.3.1                                                                 | r Waveform and Compression Curve: Stepped Barrier                                                                                                                                                                                        | 90<br>91<br>91                               |

|   | 3.4 | 3.3.1<br>3.3.2<br>3.3.3                                               | r Waveform and Compression Curve: Stepped Barrier                                                                                                                                                                                        | 90<br>91<br>91                               |

|   |     | 3.3.1<br>3.3.2<br>3.3.3                                               | r Waveform and Compression Curve: Stepped Barrier                                                                                                                                                                                        | 90<br>91<br>91<br>92                         |

|   |     | 3.3.1<br>3.3.2<br>3.3.3<br>Nonide                                     | r Waveform and Compression Curve: Stepped Barrier                                                                                                                                                                                        | 90<br>91<br>91<br>92<br>94<br>94             |

|   |     | 3.3.1<br>3.3.2<br>3.3.3<br>Nonide<br>3.4.1                            | r Waveform and Compression Curve: Stepped Barrier  Forward Problem                                                                                                                                                                       | 90<br>91<br>91<br>92<br>94<br>94             |

|   |     | 3.3.1<br>3.3.2<br>3.3.3<br>Nonide<br>3.4.1<br>3.4.2                   | r Waveform and Compression Curve: Stepped Barrier  Forward Problem  Reverse Problem  Comparison Between Stepped-Time Barrier and Continuous-Time Barrier ealities  Charge Integration Nonlinearity  Clock Feedthrough                    | 90<br>91<br>91<br>92<br>94<br>94<br>95       |

|   |     | 3.3.1<br>3.3.2<br>3.3.3<br>Nonide<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | r Waveform and Compression Curve: Stepped Barrier  Forward Problem  Reverse Problem  Comparison Between Stepped-Time Barrier and Continuous-Time Barrier ealities  Charge Integration Nonlinearity  Clock Feedthrough  Optical Crosstalk | 90<br>91<br>91<br>92<br>94<br>94<br>95<br>97 |

| CONTENTS | 7 |

|----------|---|

|          |   |

•

|     | 3.5.2                           | Barrier Current Noise                                                                                                                                                                                   |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                 | Thermal Noise                                                                                                                                                                                           |

| 3.6 | Fixed-                          | Pattern Noise                                                                                                                                                                                           |

| Exp | erime                           | ntal Chip Design 106                                                                                                                                                                                    |

| 4.1 | Outpu                           | t Circuit                                                                                                                                                                                               |

|     | 4.1.1                           | Op-Amp                                                                                                                                                                                                  |

|     | 4.1.2                           | ADC Architecture                                                                                                                                                                                        |

|     | 4.1.3                           | ADC Nonidealities                                                                                                                                                                                       |

|     | 4.1.4                           | CDS Circuit                                                                                                                                                                                             |

|     | 4.1.5                           | Output Multiplexer and Pad Driver                                                                                                                                                                       |

| 4.2 | Row S                           | elect and Barrier Generation                                                                                                                                                                            |

| 4.3 | Pixel A                         | Array                                                                                                                                                                                                   |

|     | 4.3.1                           | Wide Dynamic Range Pixel                                                                                                                                                                                |

|     | 4.3.2                           | Settling Time                                                                                                                                                                                           |

| 4.4 | Imager                          | Operation                                                                                                                                                                                               |

| 4.5 | Bias C                          | ircuit                                                                                                                                                                                                  |

| Exp | erimen                          | ntal Results 149                                                                                                                                                                                        |

| -   |                                 | ip Test Structures                                                                                                                                                                                      |

|     | 5.1.1                           | Pixel                                                                                                                                                                                                   |

|     | 5.1.2                           | Analog-to-Digital Converter                                                                                                                                                                             |

|     | 5.1.3                           | Correlated Double-Sampling Circuit                                                                                                                                                                      |

| 5.2 | Image                           | Frames                                                                                                                                                                                                  |

|     | 5.2.1                           | Saturation Level                                                                                                                                                                                        |

|     | 5.2.2                           | Dark Response                                                                                                                                                                                           |

|     | 5.2.3                           | Optical Crosstalk/Blooming                                                                                                                                                                              |

|     | 5.2.4                           | Transfer Characteristic                                                                                                                                                                                 |

|     |                                 | Fixed-Pattern and Random Noise                                                                                                                                                                          |

|     |                                 | Sample Frames                                                                                                                                                                                           |

|     |                                 | Imager Power Dissipation                                                                                                                                                                                |

|     |                                 | Performance Summary                                                                                                                                                                                     |

|     | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Experiment 4.1 Output 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 4.2 Row S 4.3 Pixel A 4.3.1 4.3.2 4.4 Imager 4.5 Bias C  Experiment 5.1 On-Ch 5.1.1 5.1.2 5.1.3 5.2 Image 5.2.1 5.2.2 5.2.3 5.2.4 5.2.5 5.2.6 5.2.7 |

,

| CONTENTS | 8 |

|----------|---|

|----------|---|

| 6            | Con | aclusions                    | 173 |

|--------------|-----|------------------------------|-----|

|              | 6.1 | Summary                      | 173 |

|              | 6.2 | Contributions                | 175 |

|              | 6.3 | Conclusions                  | 176 |

|              | 6.4 | Future Work                  | 178 |

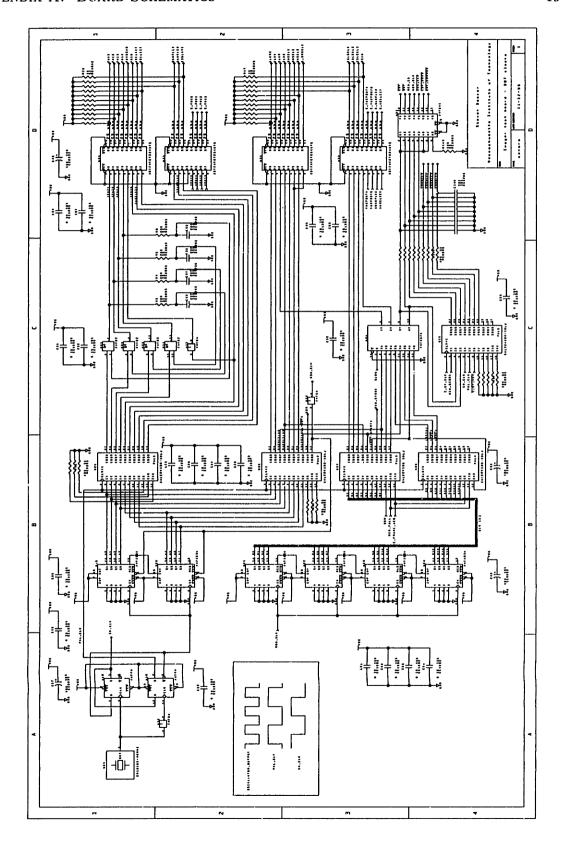

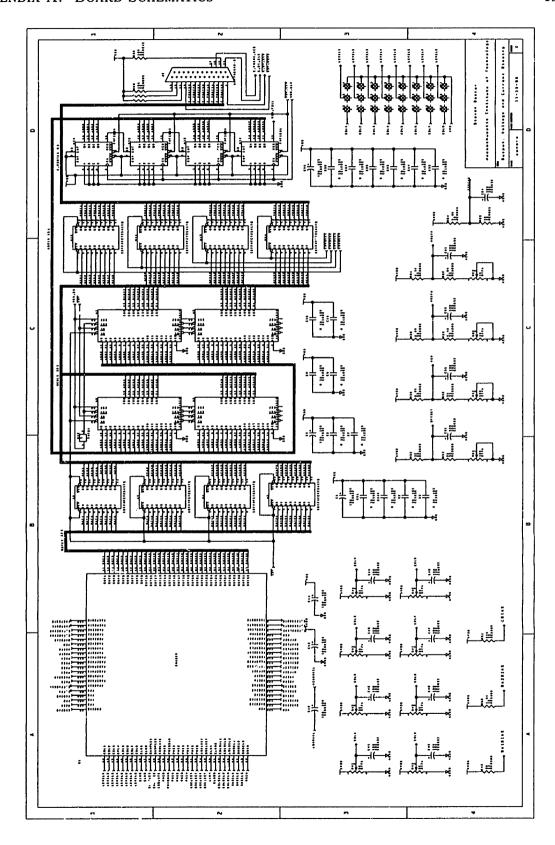

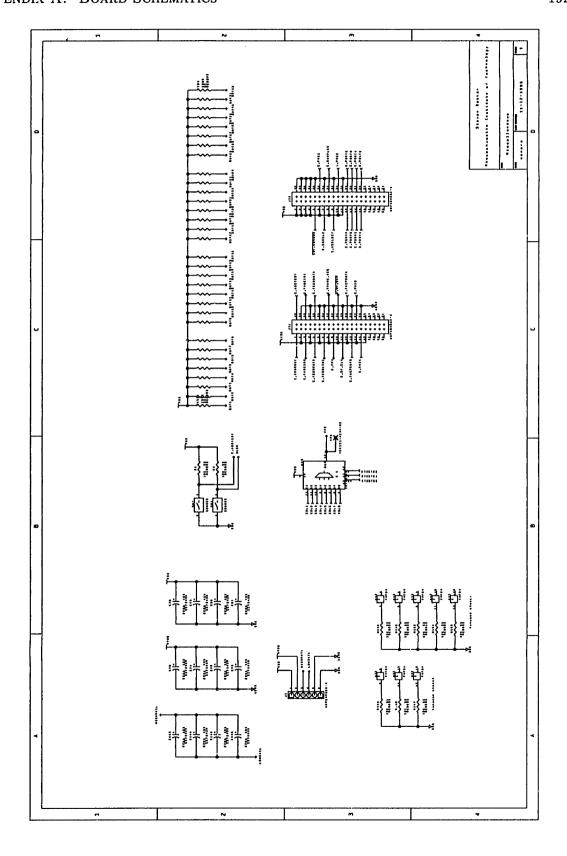

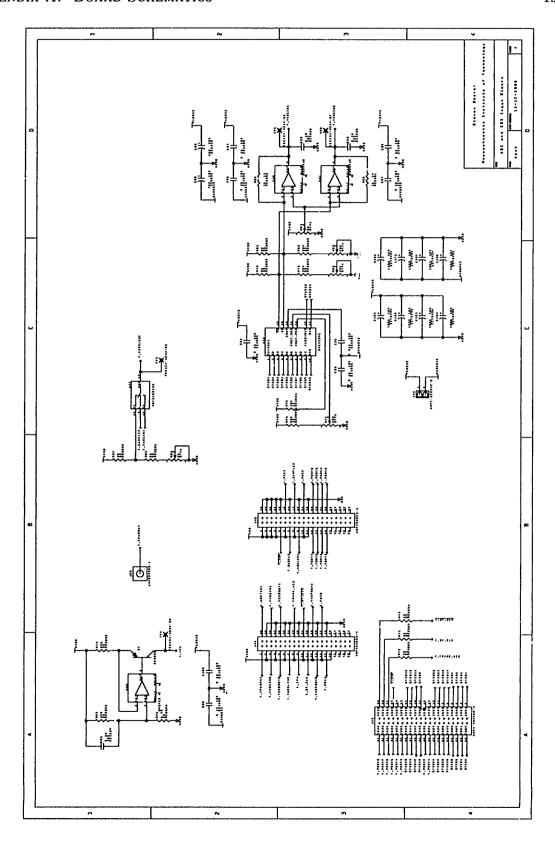

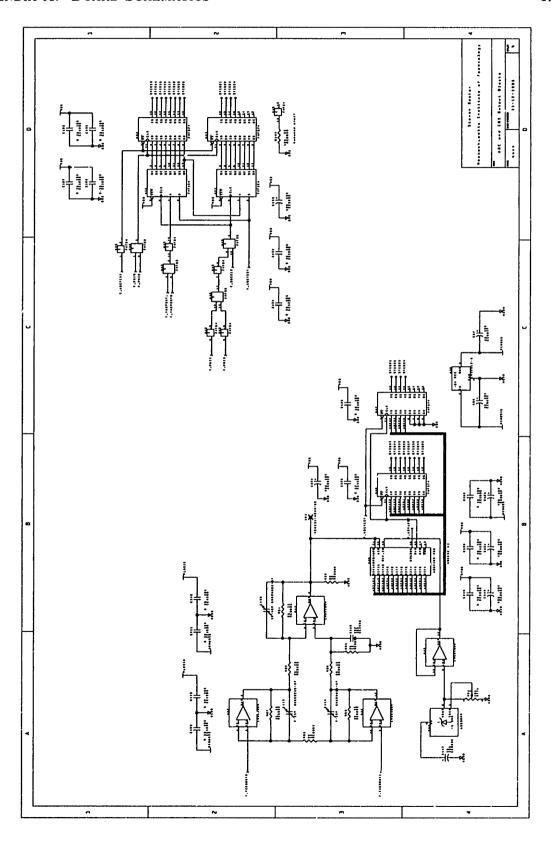

| A            | Boa | ard Schematics               | 180 |

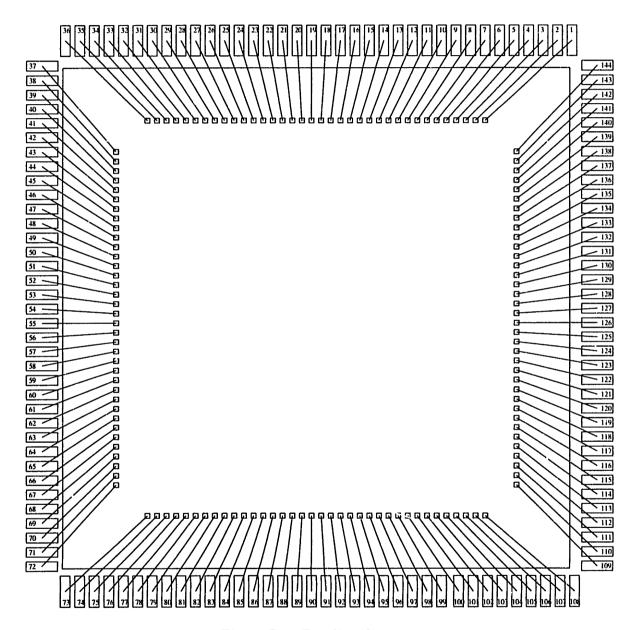

| $\mathbf{B}$ | Chi | p Pinout and Bonding Diagram | 195 |

# List of Figures

| 1-1  | Block diagram of a machine vision system                                  | 14 |

|------|---------------------------------------------------------------------------|----|

| 2-1  | MOS capacitor structure                                                   | 21 |

| 2-2  | Buried-channel potential profile                                          | 22 |

| 2-3  | CCD charge transfer sequence                                              | 23 |

| 2-4  | Photogate and photodiode CCD pixels                                       | 24 |

| 2-5  | Frame transfer (FT) CCD array                                             | 25 |

| 2-6  | Interline transfer (IT) CCD array                                         | 26 |

| 2-7  | Frame interline transfer (FIT) CCD array                                  | 27 |

| 2-8  | Output source follower for CCD imager                                     | 28 |

| 2-9  | Random noise in CCD imaging array.                                        | 29 |

| 2-10 | MOS imaging array architecture                                            | 32 |

| 2-11 | Charge readout pixel cross-section and plan view                          | 33 |

| 2-12 | Equivalent circuit and timing diagram for charge readout pixel            | 34 |

| 2-13 | Random noise model for amplifier                                          | 35 |

| 2-14 | Random noise model for charge readout output circuit                      | 35 |

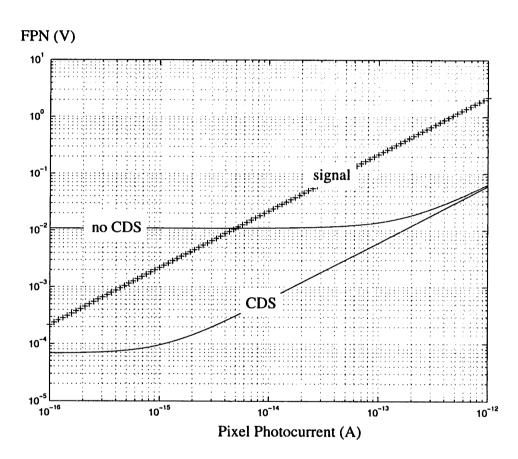

| 2-15 | FPN, charge readout pixel                                                 | 38 |

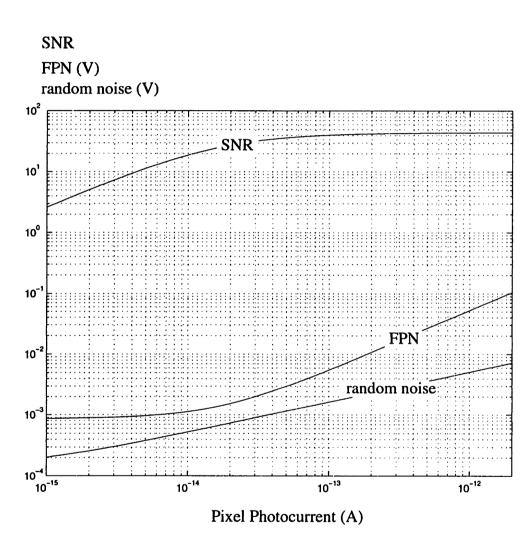

| 2-16 | SNR, charge readout pixel                                                 | 39 |

| 2-17 | Substrate noise induced during readout                                    | 41 |

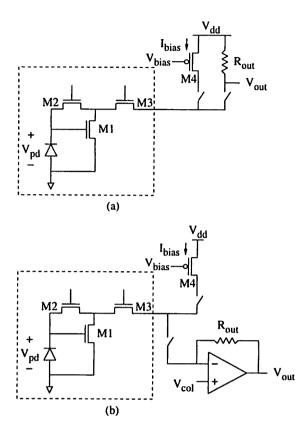

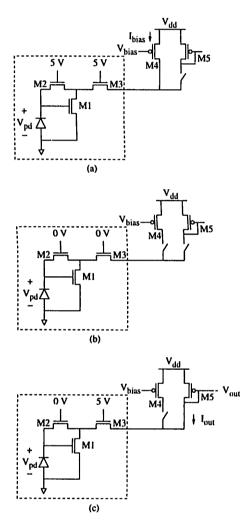

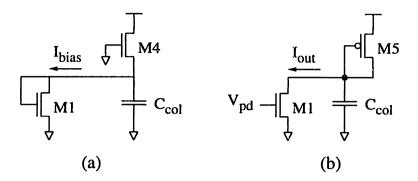

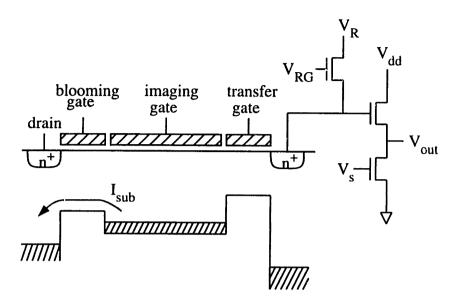

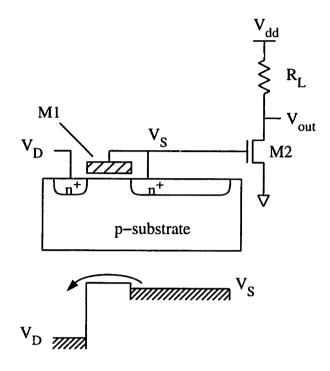

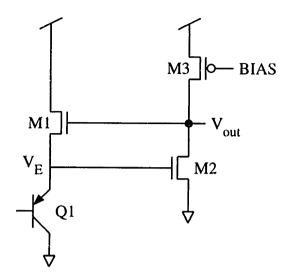

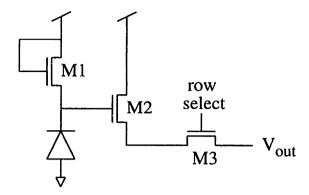

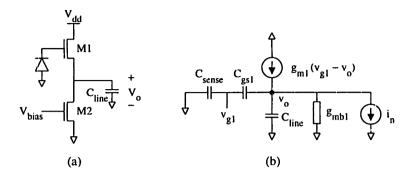

| 2-18 | Alternative output circuits for current output pixel                      | 43 |

| 2-19 | Current output pixel                                                      | 44 |

| 2-20 | Noise models for current readout pixel. (a) Reset phase. (b) Sample phase | 46 |

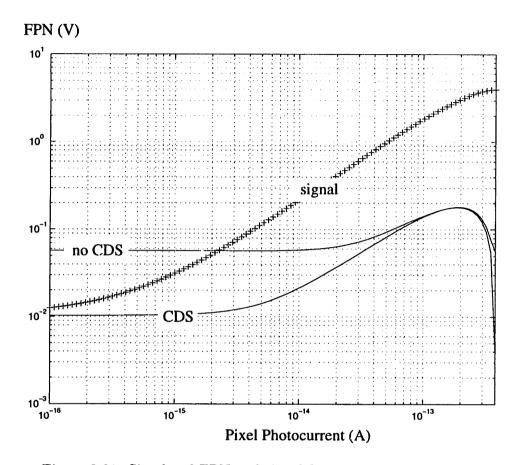

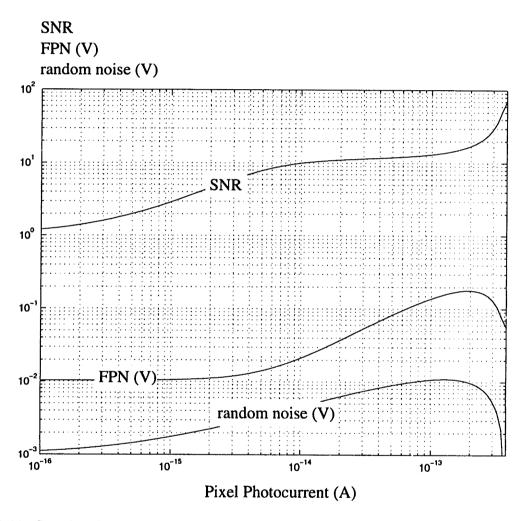

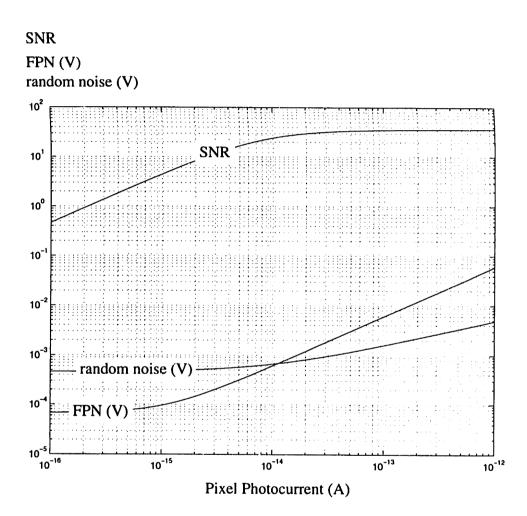

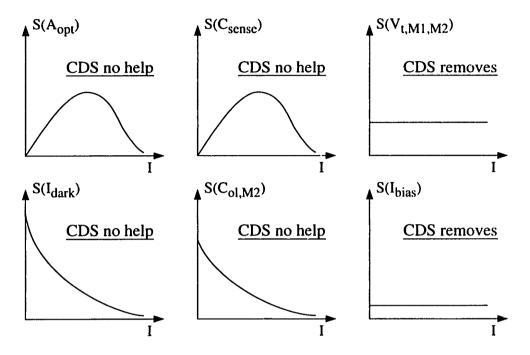

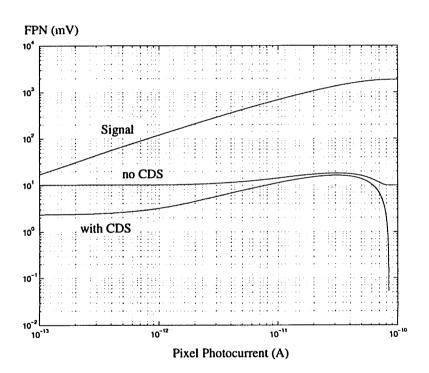

| 2-21 | FPN, current output pixel                                                 | 50 |

| 2-22 | SNR, current output pixel                                                 | 51 |

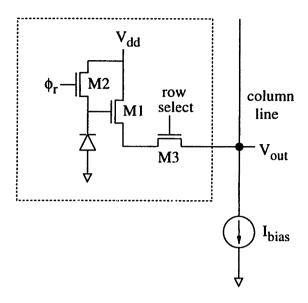

|      | Voltage output pixel                                                      |    |

| 2-24 | FPN, voltage readout pixel                                                | 57 |

LIST OF FIGURES 10

| 2-25       | SNR, voltage readout pixel                                                 | 58  |

|------------|----------------------------------------------------------------------------|-----|

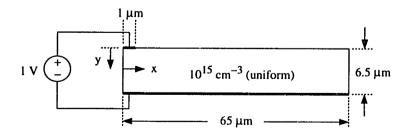

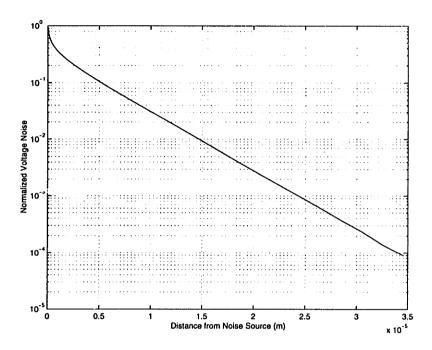

| 2-26       | (a) Plan view of column line and pixels. (b) Cross-sectional view          | 61  |

| 2-27       | Simulation structure for crosstalk                                         | 61  |

| 2-28       | Attenuation of voltage disturbance along silicon surface                   | 62  |

| 2-29       | Compressing photodetector with fixed lateral overflow gate                 | 68  |

| 2-30       | DALSA DYNASENSOR pixel                                                     | 69  |

| 2-31       | Silicon retina photoreceptor                                               | 70  |

| 2-32       | Subthreshold-mode MOS pixel                                                | 71  |

| 2-33       | Area-based nonlinear CCD pixel                                             | 72  |

| 2-34       | Nonlinear CCD pixel using switched-capacitor resistor                      | 73  |

| 2-35       | Timing-based nonlinear CCD pixel                                           | 75  |

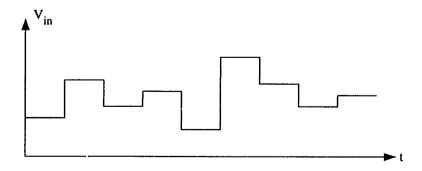

| 2-36       | Typical signal waveform from pixel array                                   | 77  |

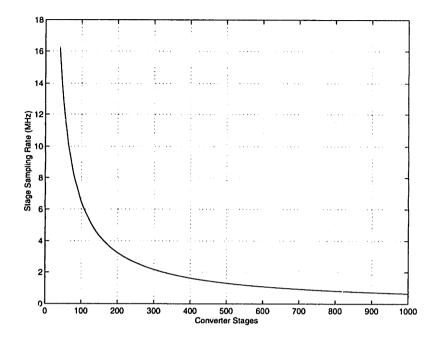

| 2-37       | Sampling rate in oversampled $\Delta - \Sigma$ converter                   | 79  |

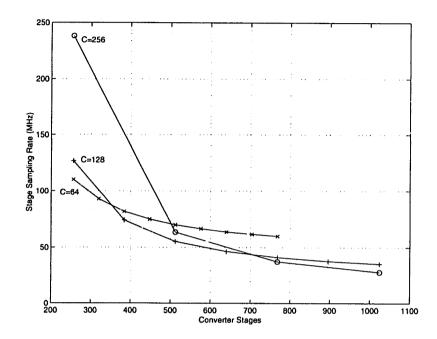

| 2-38       | Stage sampling rate for algorithmic converter                              | 81  |

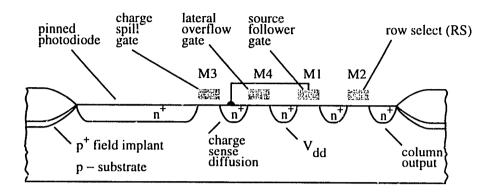

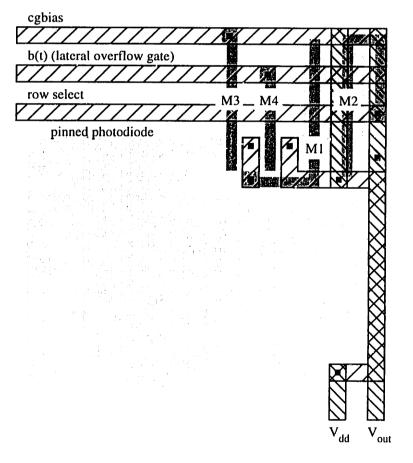

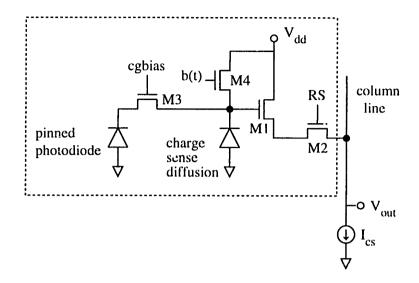

| 3-1        | Pixel cross-section                                                        | 0.0 |

| 3-1        | Plan view of wide dynamic range pixel.                                     |     |

| 3-3        |                                                                            |     |

| 3-4        | Equivalent circuit for wide dynamic range pixel                            |     |

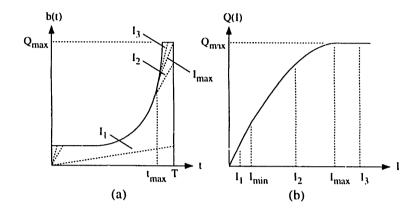

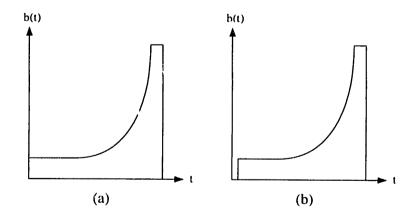

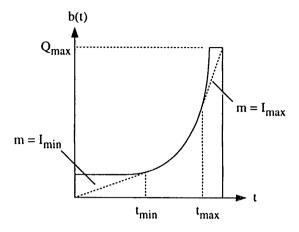

| 3-5        | Barrier waveforms                                                          |     |

| 3-6        | Breakpoints in compression curve.                                          |     |

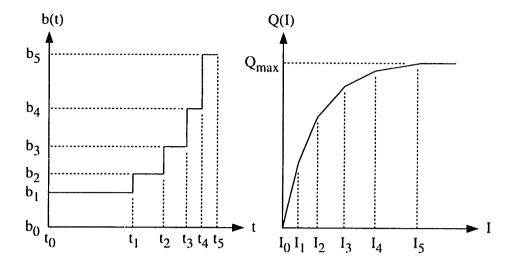

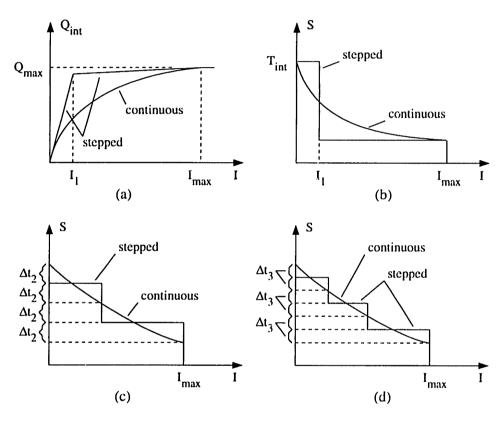

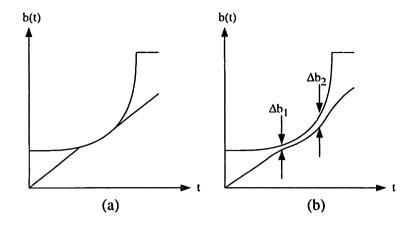

| 3-0<br>3-7 | Stepped barrier curve and compression curve                                |     |

| 3-8        | Comparison of stepped-time and continuous-time compression curves          |     |

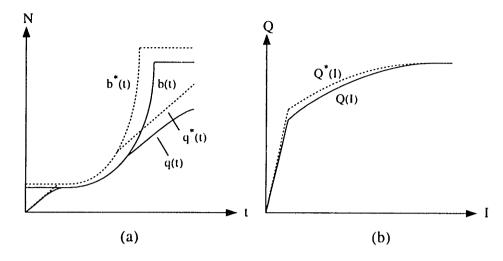

| 3-9        | Effect of charge integration nonlinearity on compression curve             |     |

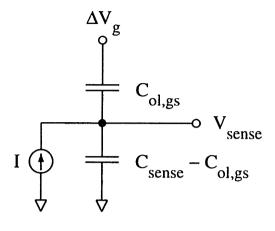

|            | Equivalent circuit for analyzing feedthrough capacitance                   |     |

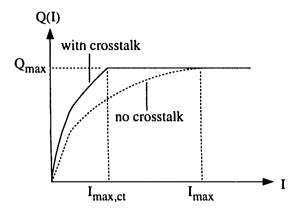

|            | Compression curve shift with optical crosstalk.                            |     |

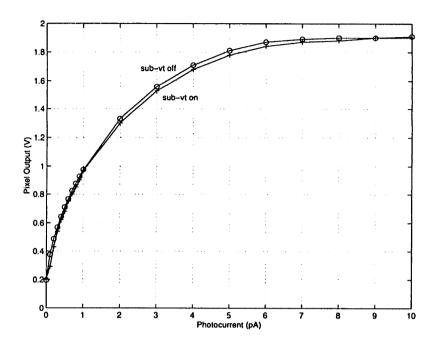

|            | Effect of subthreshold conduction on compression curve                     |     |

|            | Simulation of compression curve - subthreshold conduction                  |     |

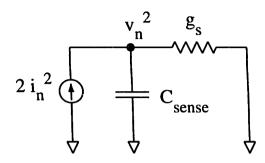

|            | Barrier current noise model                                                |     |

|            | Pixel noise model for thermal noise in source follower and current source. |     |

|            |                                                                            |     |

| 0-10       | FPN sensitivities for various mismatch sources in wide dynamic range pixel | 104 |

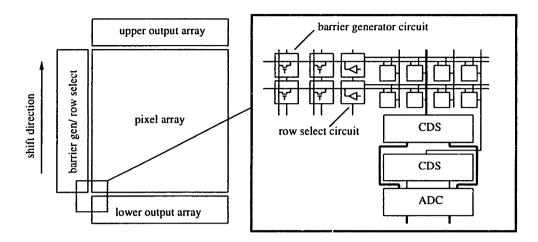

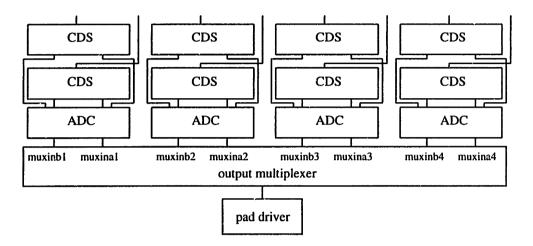

| 4-1        | Imager block diagram                                                       | 107 |

| 4-2        | Die photograph of imager                                                   | 108 |

| 4-3        | Output block diagram for one output pad                                    |     |

LIST OF FIGURES

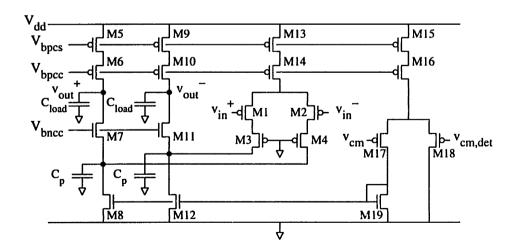

| 4-4  | Folded cascode op-amp core                                     |

|------|----------------------------------------------------------------|

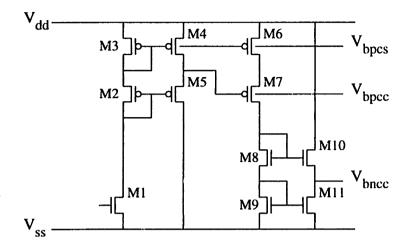

| 4-5  | Bias circuit for folded cascode op-amp                         |

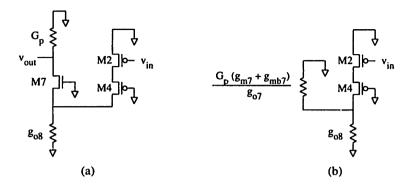

| 4-6  | Small-signal model for evaluation of op-amp dc gain            |

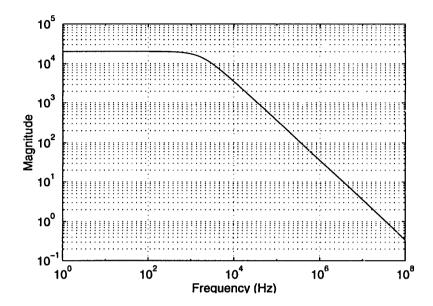

| 4-7  | Simulated op-amp differential mode response                    |

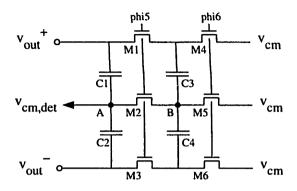

| 4-8  | Common-mode detector                                           |

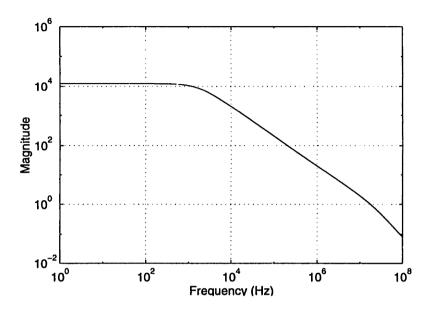

| 4-9  | Simulated op-amp common-mode response                          |

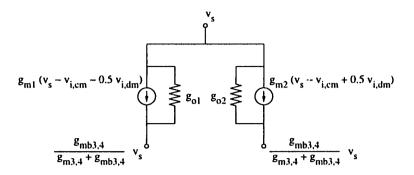

| 4-10 | Small-signal model for input pair mismatch                     |

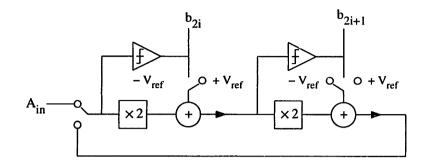

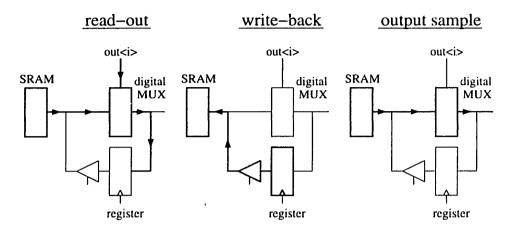

| 4-11 | Simplified cyclic converter schematic                          |

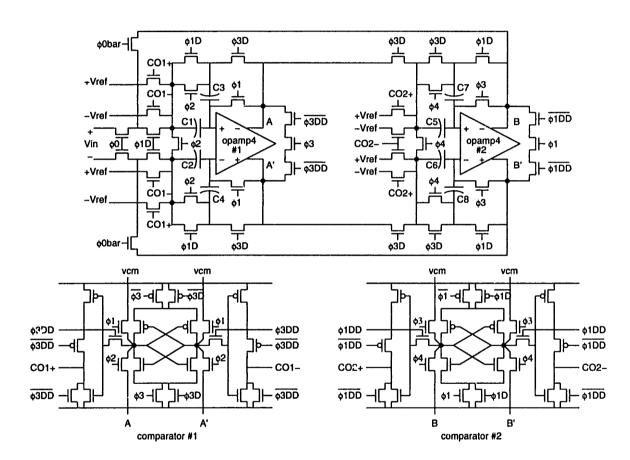

| 4-12 | Complete cyclic ADC schematic                                  |

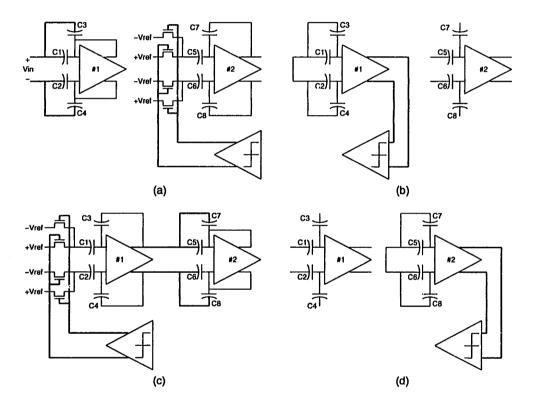

| 4-13 | Simplified cyclic ADC schematic                                |

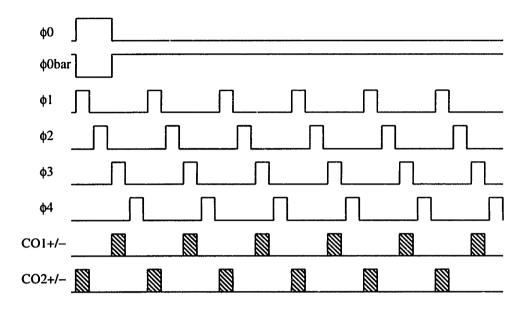

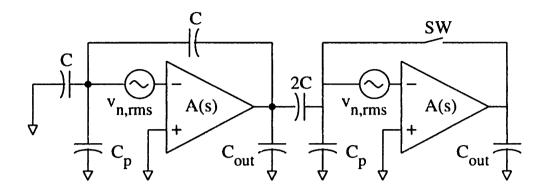

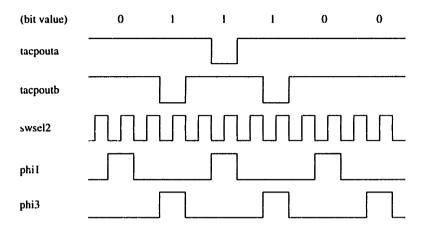

| 4-14 | Timing for cyclic ADC                                          |

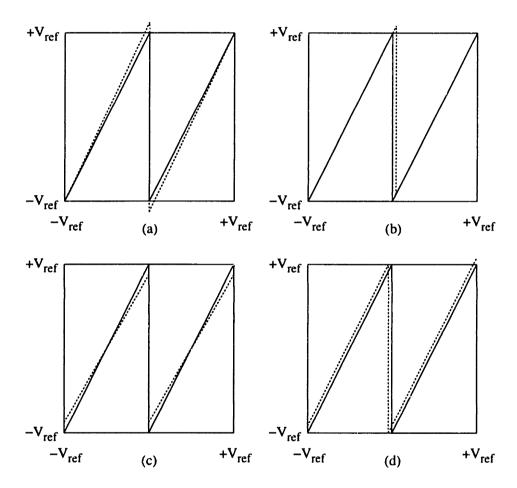

| 4-15 | Residue plots for various nonidealities                        |

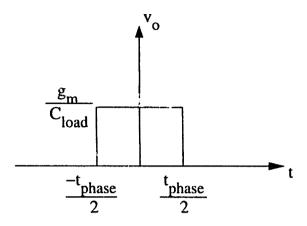

| 4-16 | Impulse response of op-amp and capacitive load                 |

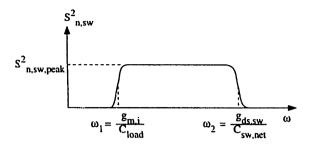

| 4-17 | Input-referred noise spectrum for switch resistance            |

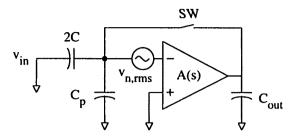

| 4-18 | Noise sampling operation for first sample (single-ended)       |

| 4-19 | Noise sampling operation for subsequent samples (single-ended) |

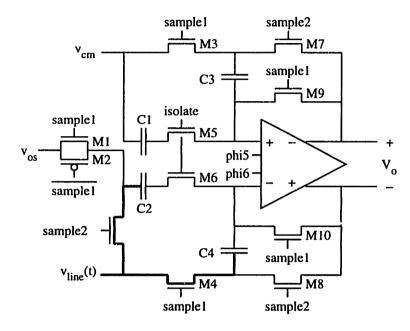

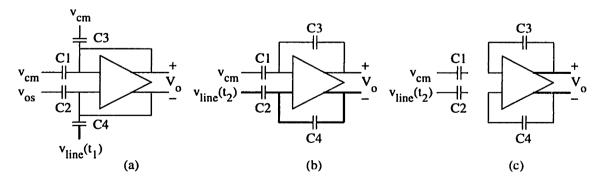

| 4-20 | Complete CDS circuit schematic                                 |

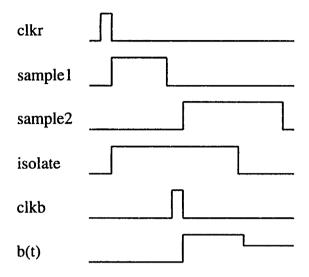

| 4-21 | CDS clocking sequence                                          |

| 4-22 | CDS circuit timing diagram                                     |

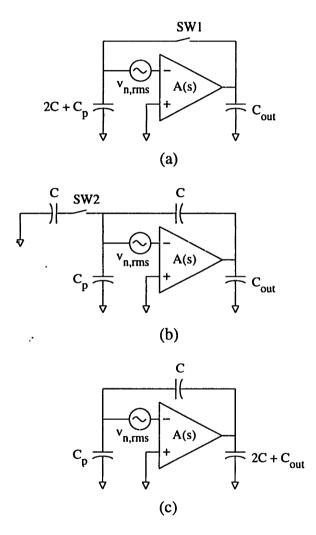

| 4-23 | CDS noise model                                                |

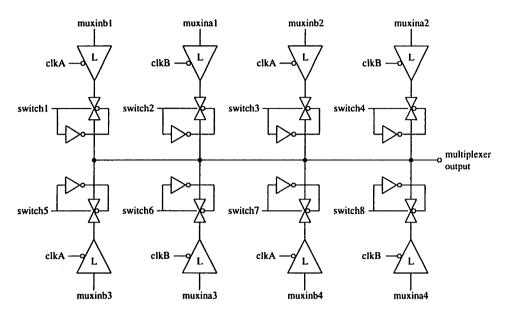

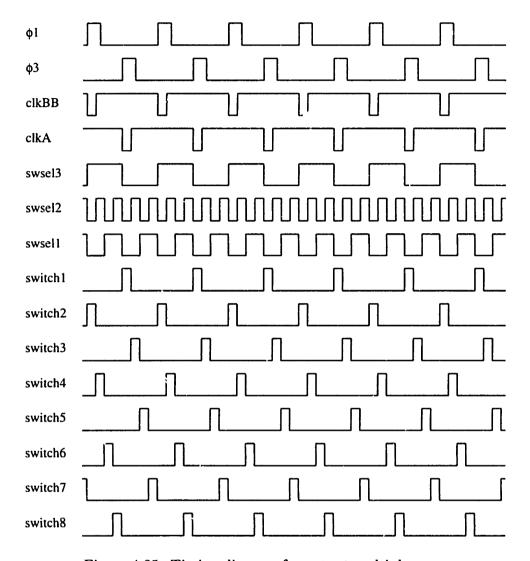

| 4-24 | Output multiplexer schematic                                   |

|      | Timing diagram for output multiplexer                          |

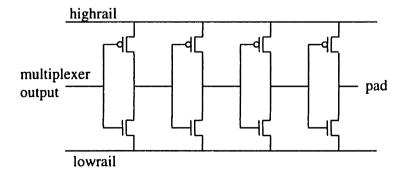

| 4-26 | Pad driver schematic                                           |

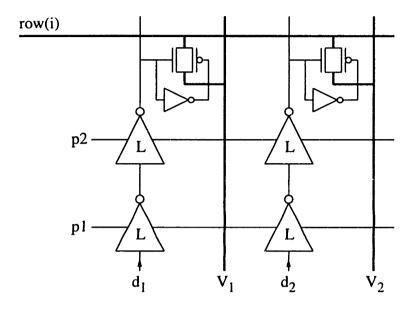

| 4-27 | Two bits of the the barrier generation circuit for one row     |

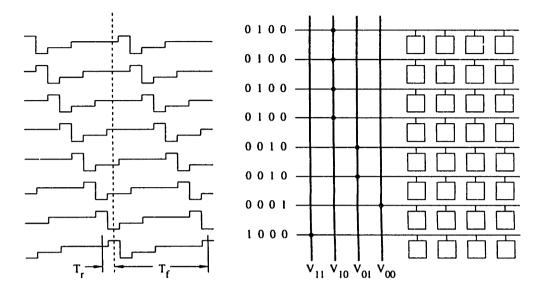

| 4-28 | Staggered readout example                                      |

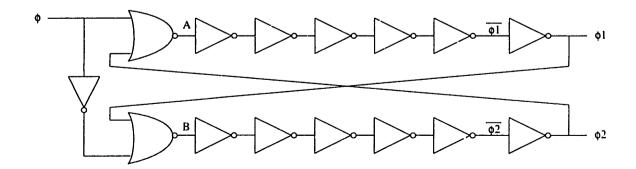

| 4-29 | Nonoverlapping clock generator                                 |

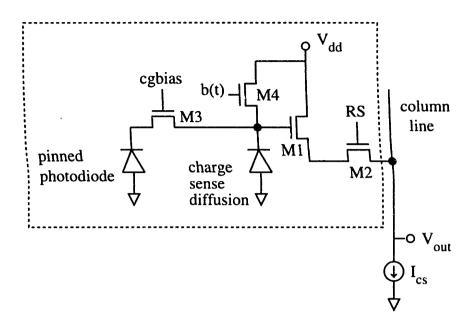

| 4-30 | Pixel equivalent circuit                                       |

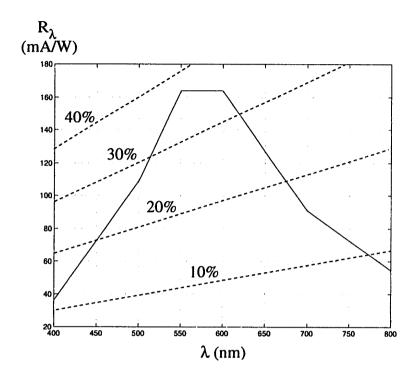

| 4-31 | Spectral responsivity for $n^+$ -p photodiode                  |

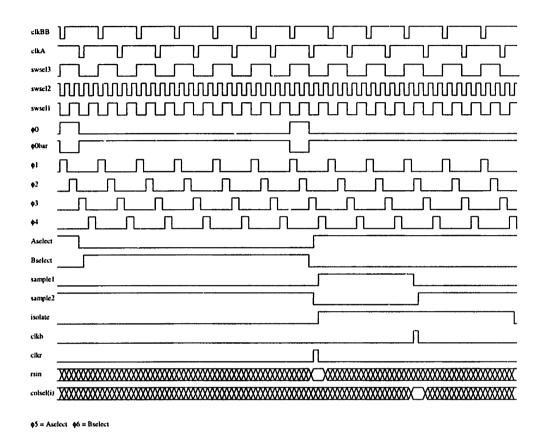

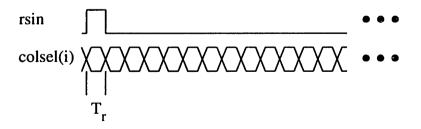

| 4-32 | Complete timing diagram for one row time                       |

| 4-33 | Frame timing diagram                                           |

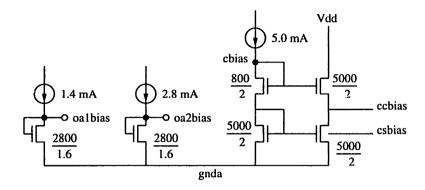

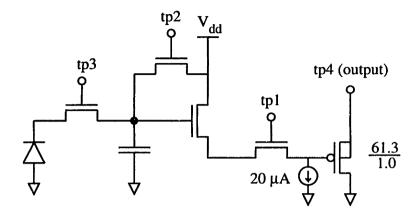

| 4-34 | Bias circuit for test chip                                     |

| 5-1  | Schematic diagram of on-chip individual test pixel             |

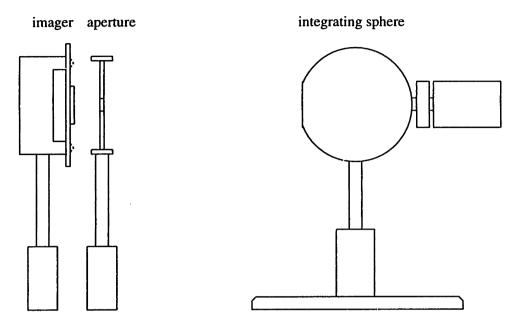

|      | Test setup for measuring pixel responsivity                    |

|      |                                                                |

LIST OF FIGURES 12

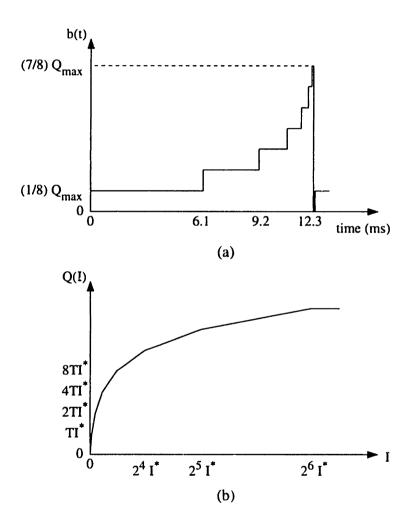

| 5-3  | Theoretical barrier and compression curves for pixel compression test                 |

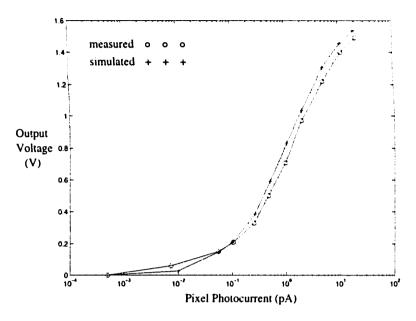

|------|---------------------------------------------------------------------------------------|

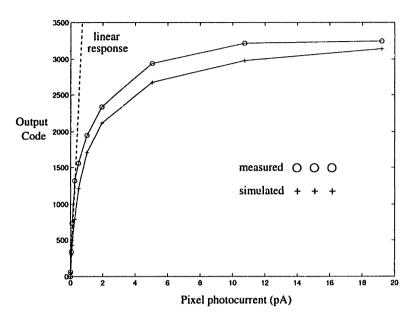

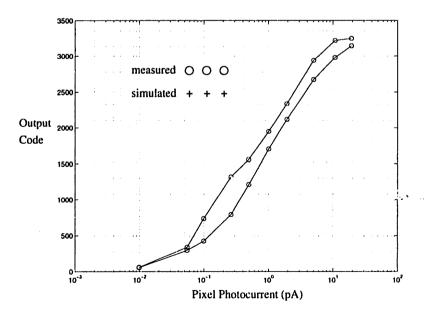

| 5-4  | Simulated and measured pixel output using quasi-logarithmic compression curve. 155    |

| 5-5  | Measured pixel output and barrier curve for low illumination                          |

| 5-6  | Measured pixel output and barrier curve for medium illumination                       |

| 5-7  | Measured pixel output and barrier curve for high illumination                         |

| 5-8  | ADC test circuit                                                                      |

| 5-9  | Timing for test analog-to-digital converter                                           |

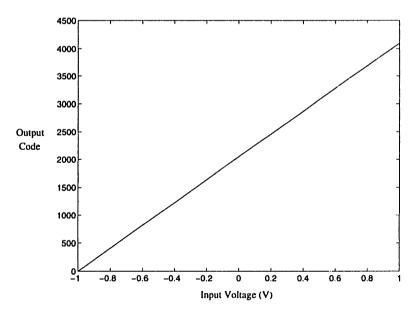

| 5-10 | Transfer characteristic for on-chip analog-to-digital converter                       |

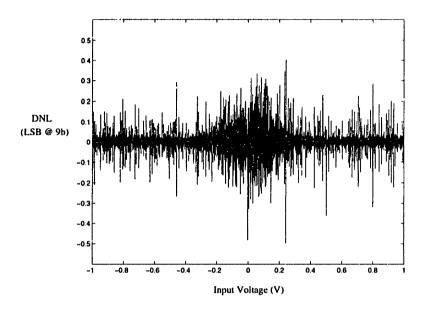

| 5-11 | Differential nonlinearity plot for on-chip analog-to-digital converter 160            |

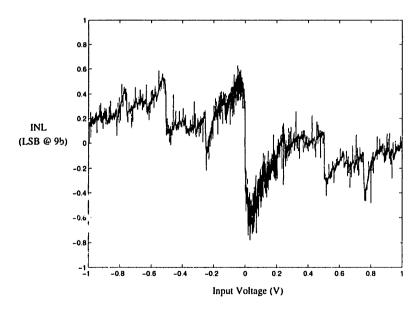

| 5-12 | Integral nonlinearity plot for on-chip analog-to-digital converter                    |

| 5-13 | CDS test circuit                                                                      |

| 5-14 | Blooming test performed with fluorescent lamp and newspaper. The horizontal           |

|      | bright line is a crease in the newspaper                                              |

| 5-15 | Blooming test performed with laser                                                    |

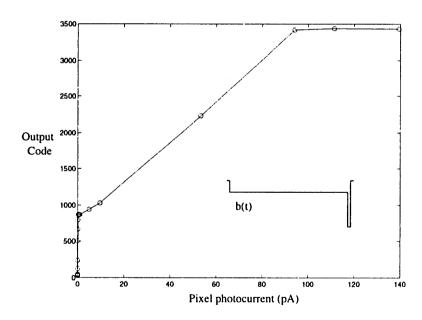

| 5-16 | Measured transfer characteristic for linear imaging mode                              |

| 5-17 | Transfer characteristics for compressive imaging mode (linear plot) 166               |

| 5-18 | Transfer characteristics for compressive imaging mode (log plot) 166                  |

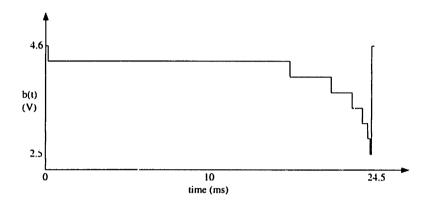

| 5-19 | Barrier curve for compressive imaging mode                                            |

| 5-20 | Compression curve and barrier curve (inset) for high dynamic range expansion. $.167$  |

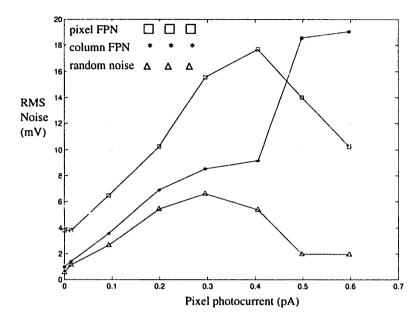

| 5-21 | Measured random and fixed-pattern noise for imager operating in linear mode. $$ . 168 |

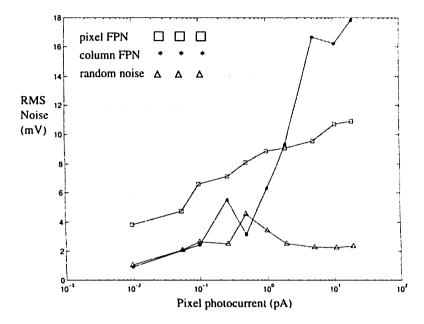

| 5-22 | Measured random and fixed-pattern noise for imager operating in compressive           |

|      | imaging mode                                                                          |

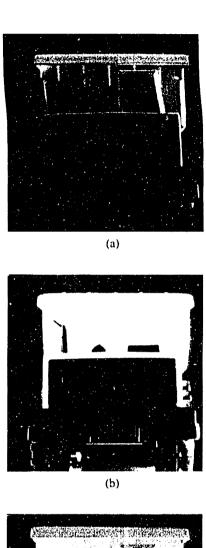

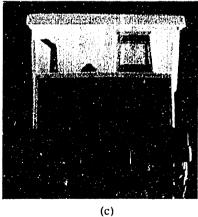

| 5-23 | Sample frames demonstrating wide dynamic range feature                                |

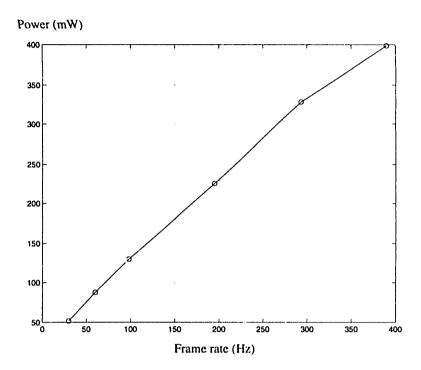

| 5-24 | Frame rate vs. imager power dissipation                                               |

| 6-1  | Implementation of real-time data reformatter                                          |

| B-1  | Bonding diagram                                                                       |

# List of Tables

| 2-1 | Comparison of CCD pixel specifications       | 0 |

|-----|----------------------------------------------|---|

| 2-2 | FPN sources for a charge readout pixel       | 7 |

| 2-3 | FPN sources for a current readout pixel      | 9 |

| 2-4 | FPN sources for a voltage readout pixel      | 6 |

| 2-5 | Comparison of CCD and CMOS Imaging           | 6 |

| 2-6 | Comparison of compressive imaging techniques | 7 |

| 3-1 | FPN sources in wide dynamic range pixel      | 4 |

| 4-1 | Summary of Operational Amplifier Design [1]  | 7 |

| 5-1 | Responsivity of photodiode array             | 2 |

| 5-2 | Summary of imager performance                | 2 |

| B-1 | Pin list, pads 1 - 72                        | 6 |

| B-2 | Pin list, pads 73 - 144                      | 7 |

| B-3 | Output bit order                             | 8 |

| B-4 | Imager columns converted at each output      | 8 |

# Chapter 1

# Introduction

Solid-state imaging is now an integral part of modern life. For example, camcorders, digital still cameras, surveillance cameras, electronic news gathering, and machine vision systems use solid-state imagers frequently or exclusively. These applications have very different requirements for resolution, frame rate, output signal format, and so on, which impose different design challenges for the imager. In this thesis, an imager for machine vision is developed.

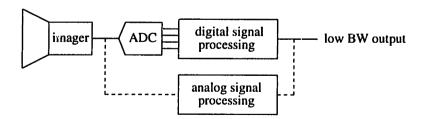

A machine vision system, shown in Fig. 1-1, consists of an imager and either an analog signal processor or an analog-to-digital converter (ADC) and digital processor. The imager is typically a CCD imager with a single analog output, a dynamic range between perhaps 100:1 and 1000:1, and a low (~30 Hz) frame rate. The imager is a limitation for applications which require high frame rate, such as assembly line inspection systems, or applications which require high dynamic range, such as automotive vision systems. In addition, it is desireable to integrate the system to reduce its power, size, and cost.

The MIT Machine Vision Group [1] has been exploring systems which use analog signal processing and varying levels of integration. Several chips designed in the course of this project

Figure 1-1: Block diagram of a machine vision system. A given system will use either analog or digital signal processing.

have integrated the imager with an analog processor using full 2-D connectivity [2, 3, 4]. The benefits include a wide data path between imager and processor, elimination of the ADC, and reduced system size. Impressive results have been achieved for certain machine vision tasks; for example, one chip is capable of locating the center of mass and orientation of an object at 5000 fps [2]. One drawback of this architecture is the conflict between making a good imager and making a highly functional processor. As the processor area increases, the light-collecting area of the pixel decreases, decreasing quantum efficiency. Since each pixel is generally placed next to a processing element, the pixel array is spread out over the entire chip, requiring an expensive large-format lens. Another drawback is that the output from the imager can only be used by the processor on that chip.

Quantum efficiency and pixel array size are improved by physically separating the pixel array from the processing circuits. Integrated systems employing this architecture include a focus-of-expansion chip [5] and a 2-D discrete cosine transform chip [6]. In both cases, the analog processor has limited flexibility, and pixel array output is available only to the on-chip processor.

In some systems, the analog processor is on a different chip from the pixel array [7, 8]. The advantages are that more area is available for both pixel array and processor, and pixel array output is available for multiple processors. The disadvantage is decreased integration. A programmable analog processing element tends to be large; a recent design required 700  $\mu$ m × 270  $\mu$ m [8] per processing element in a 0.8  $\mu$ m CMOS process.

Digital processing allows higher accuracy, and larger processing arrays on a chip [9]. This requires analog-to-digital conversion, which could be performed on a separate chip, the digital processor chip, or the imaging chip. Using a separate chip decreases system integration. Column-parallel conversion on the processing chip requires multiple analog channels between the imager and processor, and maintaining low crosstalk between adjacent channels is a potential drawback. Conversion on the imager chip mostly avoids the crosstalk problem, and is the more common choice. For example, Paul [10] has described a charge-based converter which produces serial digital output from a CCD pixel array. Column-parallel approaches have also been described [11, 12] using single-slope converters and sigma-delta converters. A focal-plane, column-parallel cyclic converter was chosen for the present work.

In addition to on-chip data conversion, the usefulness of this imager is improved by the use of a technique which increases the dynamic range. Low dynamic range is seen in the image as clipping in the dark and/or bright regions. The wide dynamic range technique used in this thesis has several advantages over other previously described schemes [13, 14, 15, 16, 17, 18, 19, 20, 21].

It is capable of approximating any compressive imaging characteristic. The compression curve  $(Q_{int})$  vs. Irradiance) is user-adjustable, and can be effectively turned off if desired. Pixel area is the same as for an ordinary active pixel sensor (APS) pixel because it uses a transistor which doubles as the reset transistor.

The main contribution of this thesis is a practical method of employing the wide dynamic range pixel in an area array. The pixel itself has been previously described in a CCD version, but no method has been described for generating a uniform lateral overflow gate waveform without requiring charge storage in the array. A further contribution of this thesis is the fully-differential signal processing chain for correlated double-sampling and column-parallel analog-to-digital conversion.

This thesis describes many advancements in the state of APS design. Although the dynamic range enhancement technique is not original with this thesis, it is shown that the continuous-time barrier described by previous authors can be replaced by a stepped barrier function with good results. A general mathematical relationship between the compression curve and barrier function is derived. A practical pixel array architecture which avoids dynamic range degradation due to optical crosstalk is developed.

The thesis is organized as follows. Chapter 2 covers background material on CCD and CMOS imaging, previously described techniques for dynamic range enhancement, and techniques for focal plane analog-to-digital conversion. Chapter 3 discusses the continuous-time and stepped-time theory behind the dynamic range enhancement technique. Chapter 4 covers the design of the prototype imager. Chapter 5 presents test data from the prototype. Chapter 6 summarizes the results and presents suggestions for future work and enhancements.

# Chapter 2

# Background

A pixel array transduces light to an electrical quantity (charge, current, or voltage) over a two-dimensional scene. Nearly all visible-light solid-state imagers are based on the principle of carrier photogeneration. Photons entering a semiconductor generate electron-hole pairs if the photon energy exceeds the bandgap energy. An electric field separates the holes and electrons; typically, the electrons are collected in a potential well and the holes are discarded. The major differences between imager types are related to how the electrons are converted to an output signal and how the array is scanned out.

Two technologies for imaging arrays were considered for this project. The charge-coupled device (CCD) array has been the dominant solid-state imager since its invention in 1970 [22]. CCD arrays make excellent imagers. Read noise as low as 3 e<sup>-</sup> per pixel has been achieved [23]. Pixel sizes as small as  $2.4 \,\mu\text{m} \times 2.4 \,\mu\text{m}$  can be achieved in currently available technologies [24]. Fixed-pattern noise (FPN) in the dark is so low that it is seldom reported; FPN in a recent CCD imager was reported to be 10 e<sup>-</sup> while using a dark current reduction technique [25].

Several MOS imagers were built before 1970 [26] and MOS imagers have recently experienced a resurgance of interest. Compared to CCD imagers, MOS imagers generally have higher read noise, higher fixed-pattern noise, and larger pixels. However, they can be built in readily available CMOS processes, and thus they can take advantage of the constant advances in minimum feature size. Digital and analog circuitry are more easily integrated with the imager. The CMOS imager has other advantages for wide dynamic range imaging which will be explained later.

This chapter begins by defining several imager parameters. CCD imaging arrays are discussed next. The principle of CCD operation is explained. Photogate and photodiode CCD

pixels are described, and the common pixel array architectures are reviewed. MOS pixels and architectures are described. CCD and CMOS technologies are compared for imaging applications. Several techniques for increasing the effective pixel dynamic range are discussed. Finally, several analog-to-digital converter architectures will be compared for focal-plane data conversion.

# 2.1 Imager Performance Characterization

Imagers are commonly characterized by quantum efficiency, conversion gain, random noise, FPN, lag, smear, saturation level, anti-blooming, and dynamic range. These terms will be defined below.

# 2.1.1 Quantum Efficiency

Quantum efficiency is the probability that a photon incident on the pixel creates a hole or electron that is collected in the pixel's potential well. Quantum efficiency depends on several parameters, including the reflection coefficient of the optical stack on the pixel, the fraction of the pixel area which is light-shielded, the fraction of the pixel area where photocharge goes elsewhere than the photosite, the photon wavelength, the bulk and surface carrier lifetimes, the depth of the potential well, and the volume and shape of the depletion regions. It is useful to think of quantum efficiency as the product of optical aperture, which is the fraction of pixel area which is optically active, optical stack transmission, which is the fraction of photons incident on optically active areas which reach the silicon surface, and collection efficiency, which is the fraction of photogenerated electrons that get collected.

## 2.1.2 Conversion Gain

The image data starts as charge and is usually converted to voltage. For an imager with a linear charge-to-voltage characteristic, the ratio of output signal to collected charge is a constant, referred to as the conversion gain. It is usually expressed in units of  $\mu V/e^-$  and is equal to the reciprocal of the charge sense capacitance, times any system gain.

## 2.1.3 Random Noise

An imager with a constant scene should produce identical output from frame to frame. In practice, the output from a given pixel will vary over time due to thermal noise, charge trapping,

and 1/f noise in the devices which comprise the imager. Photonic shot noise is usually not included in this quantity, although this also contributes to noise at the output. Random noise is typically stated in terms of input-referred equivalent electrons, *i.e.*, the root mean square (rms) output voltage noise divided by the conversion gain.

# 2.1.4 Saturation Level

Pixel saturation occurs when the pixel stores the maximum amount of charge. If more charge is added, it simply spills into the substrate or adjacent pixels. It is usually expressed in terms of electrons, although it is sometimes referred to the output as a voltage. It can also be stated in terms of the illumination required to produce the saturation charge. Depending on design, the output circuit can saturate before the pixel saturates. In this case, the saturation level is set by the output circuit.

#### 2.1.5 Fixed-Pattern Noise

Fixed-pattern noise (FPN) is the fixed (constant in time) variation between pixel outputs under spatially uniform illumination. Fixed-pattern noise is typically due to random or mask-induced mismatches in device parameters such as threshold voltage, trap density, parasitic capacitance and transistor  $\beta$ . FPN is usually a function of illumination, and can be written as the sum of a gain term and an offset term for an imager with a linear response characteristic. Offset FPN is constant over illumination, and gain FPN is proportional to illumination.

FPN consists of components that describe variation between columns, and variation between pixels in a single column. Column FPN is the standard deviation of the column-average pixel output values in a time-average, uniformly illuminated frame.

FPN (column) =

$$\sqrt{\frac{\sum_{j}(\overline{P}_{j} - \overline{P})^{2}}{j-1}}$$

, (2.1)

where  $\overline{P}_j$  is the average pixel value in column j and  $\overline{P}$  is the average pixel value in the frame. Since a column FPN calculation requires multiple columns, j > 1. Pixel FPN is the standard deviation of pixel output values after column FPN has been removed. In order to calculate pixel FPN, multiple pixels are required, so  $i \cdot j > 1$ .

FPN (pixel) =

$$\sqrt{\frac{\sum_{i,j}(P_{i,j} - \overline{P}_j)^2}{i \cdot j - 1}}$$

. (2.2)

# 2.1.6 Image Lag

Image lag refers to the persistance of one frame in successive frames. An imager demonstrates lag when, for example, a strong illuminant is suddenly turned off but the imager output does not immediately return to the black level. Lag is usually caused by incomplete charge reset. It is informally characterized by whether or not it is visible on a video display.

#### 2.1.7 Smear

In a CCD imager, pixel charge is clocked out through a shift register. A charge packet passing by a region of high illumination accumulates additional charge due to optical crosstalk, creating vertical stripes in the reconstructed image. Smear is characterized by the charge accumulated by a potential well passing by a column of pixels 10% the total column height, with the pixels illuminated by the saturation illumination. For example, assume a  $1000 \times 1000$  pixel interline CCD imager. The imager is completely in the dark, except for 100 rows which are illuminated with the saturation illumination. An empty potential well in the vertical shift register, starting at the top of the shift register, will acquire charge  $Q_{smear}$  by the time it reaches the bottom. Smear is expressed in dB as the ratio of the saturation charge to  $Q_{smear}$ .

Charge readout CMOS imagers can exhibit the same behavior. A column line can easily collect stray charge from a highly illuminated pixel, corrupting the readout of all pixels in that column.

## 2.1.8 Crosstalk

Crosstalk is any contamination of one pixel's signal by another pixel's signal. Smear is an example of optical crosstalk. Examples of electrical crosstalk include ground bounce and capacitive coupling.

# 2.1.9 Anti-Blooming

Blooming is the spread of charge from *saturated* pixels into surrounding potential wells. It differs from optical crosstalk in that all photogenerated charge, not just a small fraction, spreads out into the surrounding pixels/shift registers. Most pixels contain some means for shunting excess charge to a drain in order to preserve the information in nearby non-saturated pixels. Anti-blooming characterizes the effectiveness of the technique used to drain excess charge. It is expressed as the ratio of the illumination required to produce blooming to the illumination

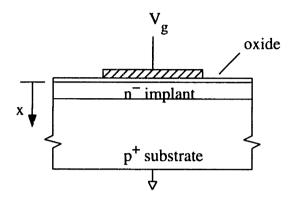

Figure 2-1: MOS capacitor structure.

required to saturate the pixel. For example, a pixel with no anti-blooming protection would have 1× anti-blooming.

# 2.2 CCD Imagers

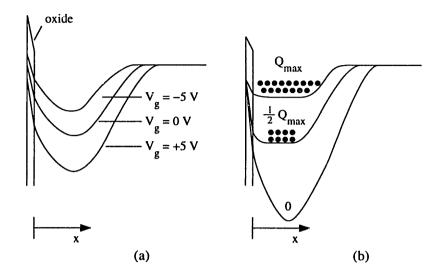

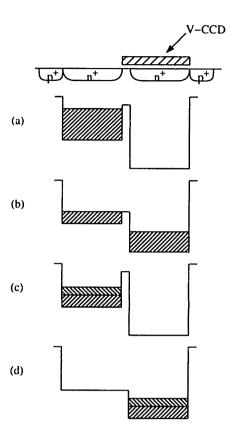

The CCD is the most common solid-state imager. The basis of this imager is the ability to completely transfer charge between adjacent MOS capacitors by applying overlapping clocks to their gates. The MOS capacitor with buried-channel implant is shown in Fig. 2-1. The buried-channel implant is a lightly n-doped region that can be fully depleted; it keeps the charge packet away from the SiO<sub>2</sub> interface, reducing charge loss in the interface traps and creating fringing fields to allow higher transfer speed. Figure 2-2(a) shows the potential profile for several different gate voltages with a fully depleted buried-channel implant. In practice, the gate voltage is set to one of two voltages: high to store charge and low to remove all charge. A third level is sometimes used to enable charge transfer through an alternate path. Figure 2-2(b) shows the potential profile for a fixed (high) gate voltage and various amounts of stored charge [27]. Free charge is indicated by a flat region at the bottom of the potential profile. The potential well is full when charge spills into adjacent pixels or through an overflow drain, or when the flat region extends to the silicon surface, since the MOS capacitor becomes a surface-channel device at that point.

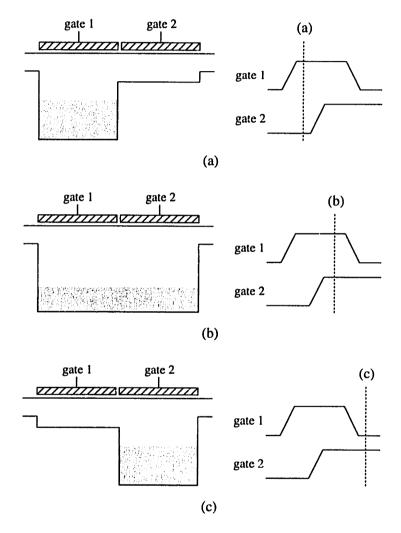

Charge is transfered between adjacent MOS capacitors by applying overlapping clocks to their gates. The concept is demonstrated by Fig. 2-3, which shows two adjacent MOS gates and their corresponding potential energy diagrams. The potential energy diagrams are shown using the fluid model of the CCD, where the y-axis is electron potential energy, and charge is thought of as a fluid that flows to the state of lowest potential energy. In Fig. 2-3(a), the charge

Figure 2-2: (a) Buried-channel potential profiles for zero charge. (b) Buried-channel profile for fixed gate voltage and varying charge.

is entirely under gate 1. In (b), the voltage on gate 2 is high so that charge is shared evenly between the two gates. In (c), the voltage on gate 1 goes low, transfering all charge under gate 2. Note that as voltage on a gate increases, the bottom of its potential energy well is lowered. This happens because potential energy diagrams are usually drawn for electrons, which have negative charge.

#### 2.2.1 CCD Pixels

The CCD pixel is an integrating type, *i.e.*, charge is accumulated over the integration time and sent to the output circuit at the end of the integration period. In its simplest form, a pixel is just a potential well and a transfer gate. The potential well can be created by either a photogate or a photodiode.

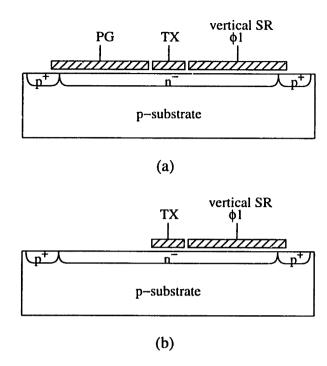

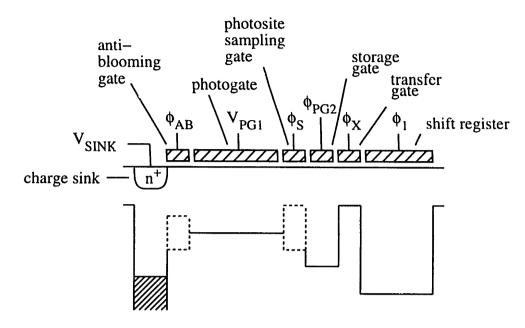

A photogate pixel, shown in Fig. 2-4(a), uses a MOS capacitor to create a potential well. During integration, the transfer gate (TX) voltage is low and the photogate (PG) voltage is high. Charge is transfered out of the pixel by raising the transfer gate and lowering the photogate. The vertical shift register phase  $\phi 1$  is high, creating a potential well to receive the charge. Photogate pixels tend to have a high saturation level due to the large gate capacitance. They also tend to have poor quantum efficiency, especially in the shorter wavelengths, due to absorption in the polysilicon gate.

A simple photodiode pixel is shown in Fig. 2-4(b). Operation is similar to the photogate

Figure 2-3: (a) All charge under gate 1. (b) Charge evenly divided between gate 1 and gate 2. (c) All charge under gate 2.

Figure 2-4: (a) Photogate CCD pixel. (b) Photodiode CCD pixel.

pixel. During integration, the transfer gate isolates the charge packet from the vertical shift register. At the end of the integration period, TX and  $\phi 1$  go high, skimming the integrated charge in the photodiode into the vertical shift register. Then TX goes low, starting another integration period. Readout of a photodiode pixel is relatively slow since transfer of the last few electrons takes place solely by diffusion. Quantum efficiency will be relatively high since no photogate blocks the short wavelengths.

## 2.2.2 CCD Architectures

Charge packets in the pixels must be transferred to the output circuit(s). The unique feature of CCD's is that this transfer occurs through a sequence of complete transfers between adjacent MOS capacitors. The details of the transfer process are specified by the architecture. Common CCD area imager architectures include the frame transfer (FT), interline transfer (IT), and frame interline transfer (FIT) designs [28].

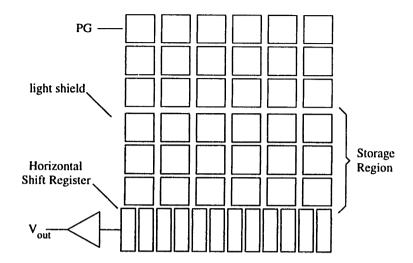

A frame transfer array is shown in Fig. 2-5. At the end of the integration period, charge is rapidly transferred directly through the array to a light-shielded storage area. The frame is then read out from the storage area. Smear is a problem for this architecture, and the transfer speed is limited due to the large length of a pixel compared to the length of the transfer gate in

Figure 2-5: Frame transfer (FT) CCD array.

a typical CCD shift register. Optical aperture is excellent, approaching 100% in some imagers. This is somewhat misleading, however, as the channel stops and polysilicon photogates have poor optical response. A storage area, roughly equal in size to the imaging area, is required to store the frame until it can be read out.

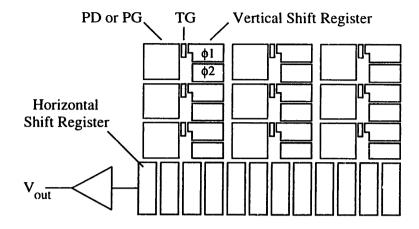

An interline transfer (IT) array is shown in Fig. 2-6. A vertical shift register is placed between each column of pixels. At the end of the integration period, the transfer gate (TG) in the pixel and  $\phi 1$  go high. Pixel charge spreads under those gates. As the transfer gate and photogate go low, the remainder of the charge is transfered under the  $\phi 1$  gates. As soon as TG goes low, the pixel can start another integration period. Meanwhile, the charge packets in the vertical shift register are shifted down towards the horizontal shift register. When a new set of packets is shifted into the horizontal shift register, the vertical shift register halts until all of the charge in the horizontal shift register is transfered to the output circuit, where the packets are converted into voltages. The shift registers are usually timed so that it takes exactly one integration period to clock out all of the pixels in the array, so that by the time one frame has been read out, the next frame is ready to be read out.

The IT array suffers somewhat in optical aperture since the vertical shift register is light shielded, and is therefore optically inactive. However, smear is low compared to a frame transfer array operated at the same frame rate, since the charge is not shifted through optically active regions.

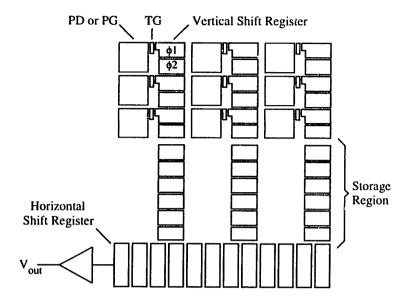

The FIT architecture combines the IT and FT architectures, as shown in Fig. 2-7. The advantages are the photodiode capability and very low smear. The disadvantages are reduced

Figure 2-6: Interline transfer (IT) CCD array.

optical aperture due to the vertical shift register and an approximate doubling of the required silicon area because of the storage region.

## 2.2.3 CCD Performance

# Quantum Efficiency

Optical aperture is strongly dependent on architecture type. An FT imager can have nearly 100% optical aperture. An IT or FIT imager has lower optical aperture since the shielded interline shift registers block at least some of the incident light. Shift register area is a largely a matter of design, subject to design rule limitations. For example, consider a photogate IT imager which uses the same buried-channel implant for integrating well and four-phase shift register. If it is necessary for the shift register to handle the full pixel capacity, the shift register area must be twice the photogate area, limiting optical aperture to 33%. If a photodiode is used, the integrating well capacitance decreases, allowing a small shift register and higher optical aperture. If pixel capacity is limited by a lateral overflow gate or vertical anti-blooming, the shift register can again be reduced. Shift register capacity can be increased by increasing the buried channel implant. In any case, the shift register can be no smaller than that allowed by minimum design rules.

Collection efficiency is determined by pixel geometry and doping profile. CCD pixels usually have carefully tailored doping profiles which can optimize collection efficiency given other design constraints, such as vertical anti-blooming or surface pinning [29].

Figure 2-7: Frame interline transfer (FIT) CCD array.

#### Random Noise

Random noise includes photonic noise, dark current noise, charge transfer noise, switch noise, and amplifier noise. These components are added in quadrature to find the total random noise.

Photonic and dark current noise refer to the shot noise of the photocurrent and dark current, respectively. The noise for these sources is

$$N_{e,shot,rms} = \sqrt{\frac{1}{q}(Q_s + Q_d)}, \tag{2.3}$$

where  $Q_s$  is the signal charge and  $Q_d$  is the dark charge. Charge transfer noise [30] is due to a similar shot noise process; when a charge packet is transfered between potential wells, each electron has a probability  $\epsilon$  of making the transfer. The total noise in the charge transfer is

$$N_{e,ct,rms} = \sqrt{2(1-\epsilon)N_sN_t},\tag{2.4}$$

where  $N_s$  is the number of signal electrons and  $N_t$  is the number of transfers. Switch noise is caused by resetting the output diffusion. It has magnitude

$$N_{e,switch,rms} = \sqrt{\frac{kT}{q^2}C_{sense}},\tag{2.5}$$

where  $C_{sense}$  is the capacitance of the output diffusion. The source-follower amplifier has inputreferred 1/f and thermal noise. Switch noise and amplifier 1/f noise can be mostly removed

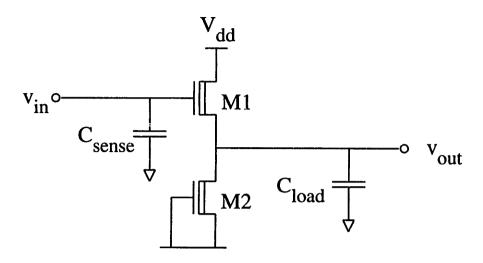

Figure 2-8: Output source follower for CCD imager.

using correlated double-sampling (CDS), but the source follower thermal noise is actually doubled by CDS. Source-follower thermal noise can be estimated from Fig. 2-8. Only one stage is shown, although in some cases, multiple source-follower stages are used. The thermal noise at the output is

$$N_{e,thermal} = \frac{C_{eff}}{qG_{sf}} \sqrt{\frac{8}{3} \frac{kT}{G_{out}^2} (g_{m1} + g_{m2}) \Delta f}$$

$$= \frac{C_{eff}}{qG_{sf}} \sqrt{\frac{8}{3} \frac{kT}{G_{out}^2} (g_{m1} + g_{m2}) \frac{G_{out}}{2\pi C_{load}} \frac{\pi}{2}}$$

$$C_{eff} \sqrt{\frac{8}{3} \frac{kT}{G_{out}^2} (g_{m1} + g_{m2}) \frac{G_{out}}{2\pi C_{load}} \frac{\pi}{2}}$$

(2.6)

$$= \frac{C_{eff}}{qG_{sf}}\sqrt{\frac{2}{3}\frac{kT}{G_{out}C_{load}}}(g_{m1}+g_{m2})$$

$$\tag{2.8}$$

$$= \frac{C_{eff}}{qG_{sf}} \sqrt{\frac{2}{3} \frac{kT}{G_{out}C_{load}}} (g_{m1} + g_{m2})$$

$$= \frac{C_{eff}}{qG_{sf}} \sqrt{\frac{2}{3} \frac{kT}{(g_{mb1} + g_{m1} \frac{C_{sense}}{C_{sense} + C_{gs1}})} (C_{load} + \frac{C_{sense}C_{gs1}}{C_{sense} + C_{gs1}})} (g_{m1} + g_{m2})$$

(2.8)

$$\approx \frac{C_{eff}}{q} \sqrt{\frac{kT}{C_{load}} \frac{g_{m1} + g_{m2}}{g_{mb1} + g_{m1} \frac{C_{sense} + C_{gs1}}{C_{sense} + C_{gs1}}}},$$

(2.10)

where  $C_{eff}$  is given by

$$C_{eff} = C_{sense} + C_{gs1}(1 - G_{sf}),$$

(2.11)

and  $G_{sf}$  is the source follower gain.

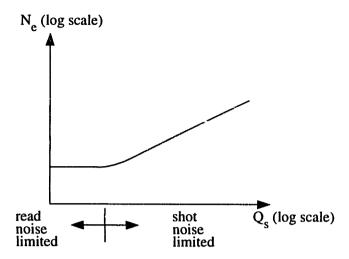

The sum of the signal-independent noise sources is called read noise. Read noise varies from about 3 e<sup>-</sup> to 200 e<sup>-</sup> [23]. Shot noise has a square-root dependence on signal; above a certain irradiance, random noise is dominated by photon shot noise (charge transfer noise also

Figure 2-9: Signal dependence of random noise in a CCD imaging array.

has a square-root dependence on signal, but should be much lower than the photonic noise). Figure 2-9 shows the general noise dependence on signal level.

## **Saturation Level**

The pixel saturation level is proportional to the integrating well capacitance, size, and voltage swing. The saturation level for a pixel in a CCD imager is usually in the range of 1000 to 3000  $e^{-}/\mu m^{2}$ .

## **FPN**

Fixed-pattern noise is usually negligible for CCD imagers, except for defective pixels. Defective pixels are defined as those having gain and/or offset FPN exceeding specified limits. CCD imagers are sorted into different grades, depending on the maximum number and type of defects allowed in specified regions of the array (see, for example, [31]). Typically, no more than a handful of defective pixels are tolerated in any grade.

Offset FPN occurs through pixel dark current  $I_d$ . Gain FPN arises from variation in pixel optical aperture  $A_{opt}$ , or any source of quantum efficiency mismatch. Gain FPN can become a problem as the aperture size becomes comparable to the polysilicon grain size. The net FPN is

$$FPN = T_{int} \left( \Delta I_d + I_s \frac{\Delta A_{opt}}{A_{opt}} \right), \qquad (2.12)$$

where  $I_s$  is the pixel photogeneration current.

Table 2-1: Comparison of CCD pixel specifications.

| Pixel Size $(\mu m^2)$ | $Q_{sat}$ (e <sup>-</sup> ) | ${ m e^-/\mu m^2}$ | Smear (dB) | Architecture | Reference       |

|------------------------|-----------------------------|--------------------|------------|--------------|-----------------|

| $6.0 \times 12.6$      | 70 000                      | 930                | 80         | FT           | bosiers94a[32]  |

| $7.3 \times 7.3$       | 80 000                      | 1500               | 77         | TI           | nichols92[33]   |

| $9.6 \times 5.4$       | 100 000                     | 1900               | 140        | FIT          | yamashita94[34] |

| $5.1 \times 5.1$       | 60 000                      | 2300               | 75         | FT           | bosiers94b[35]  |

| $12 \times 12$         | > 300 000                   | 2100               | NA         | TDI          | agwani95[36]    |

## **Image Lag**

Photogate CCD's usually have no visible image lag, since pixel charge is fully transfered into the vertical shift register. Possible sources include bulk trapping and insufficient readout time. The most problematic bulk traps are those with time constants greater than the pixel readout time but less than the integration time. These traps fill during bright frames but do not discharge during readout. In a subsequent dark frame, the traps discharge without being refilled, adding charge which is indistinguishable from photogenerated charge. The bulk trap density is generally low enough that this is not a significant problem. Insufficient readout time causes lag by turning off the transfer gate before all integrated charge has been removed. This is seldom a problem because the time constants for charge transfer are usually quite small, and transfer time is relatively unconstrained.

Lag can be a significant problem in a photodiode CCD. Because charge transfer occurs by subthreshold conduction through a MOS transistor, the photodiode is never completely reset. Any residual charge in one frame appears in the following frame.

#### **Smear**

Smear is determined by the doping profiles of the integrating well and shift register, the proximity of the shift register to the aperture, and the configuration of the light shield over the vertical shift register. Smear is typically 70 - 80 dB (3.5 - 4 orders of magnitude) in an IT imager, although it can be much better in an FIT architecture. Table 2-1 lists the smear and saturation level for several recent CCD imagers.

#### Crosstalk

The CCD imager is robust against electrical crosstalk since voltage fluctuations in the substrate do not affect the number of carriers stored in a potential well. The vertical overflow drain (VOD), a common structure in CCD's, produces a potential barrier which inhibits injected

electrons from entering a pixel. Also, the epi-substrate interface has a high defect concentration, which tends to recombine injected electrons.

Optical crosstalk results from light entering one pixel which adds charge to another pixel's charge packet. One form is pixel-to-pixel crosstalk, which is present in all pixel arrays. This is relatively benign since it seldom occurs between pixels with widely varying intensities. Smear is a more serious form, as it limits the scene dynamic range, especially for FT and IT architectures. Smear can be greatly reduced by an FIT architecture, but this requires approximate doubling of the silicon area.

# 2.3 MOS Imagers

An MOS imager is any pixel array which uses MOSFET transistors to convey the signal from the pixels to the output circuit(s). Signal transfer occurs over a wire, and the signal can be charge, current, or voltage. Pixel output can be either continuous-time or integrated.

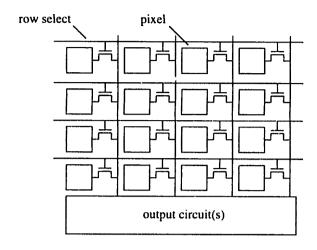

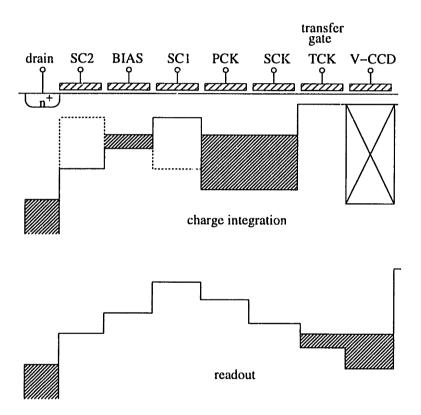

# 2.3.1 MOS Array Architecture

A typical MOS array architecture is shown in Fig. 2-10. The MOS array differs from the CCD array in that the column line can only carry one signal at a time, and must therefore be time multiplexed between all the pixels in a column. This requires a row select device in the pixel; when a row is read out, all other rows are disconnected from the column line. The outputs from all pixels in a row become available simultaneously. If only one output circuit is available for the entire array, the output columns must be multiplexed to one output.

The transduced signal is initially charge. MOS pixels can be classified according to the form of the signal between the pixel and the output circuit(s). The usual choices are charge, current, and voltage. The output circuit converts that signal to either an analog signal (normally a voltage) or a bit stream, and drives the signal off-chip.

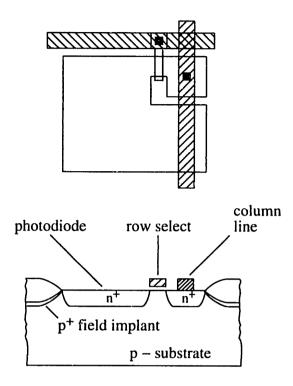

# 2.3.2 Charge Output Pixel

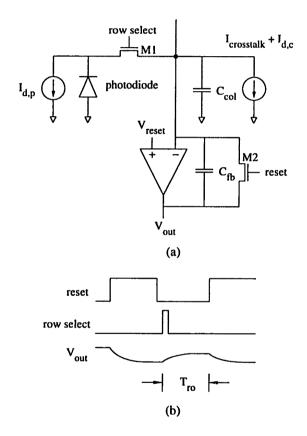

Figure 2-11 shows a plan view and cross-section of a charge readout pixel. A photogate implementation is also possible; it would give a higher saturation charge but lower quantum efficiency. Figure 2-12 shows the equivalent circuit and timing diagram for a pixel and output circuit. The crosstalk current source represents the optical crosstalk current from other pixels on the same column line. The line capacitance is due to parasitic capacitances between the column

Figure 2-10: MOS imaging array architecture.

line to the substrate, column line to row select lines, and output diffusion to substrate.

To read out a charge packet, the feedback capacitor  $C_{fb}$  is reset. The row select line is turned on and off, dumping the pixel charge onto the line. Since the column line capacitance is much greater than the pixel capacitance, nearly all of the imaged charge shifts onto the column line. This operation also resets the pixel. The pixel charge moves onto  $C_{fb}$  via the feedback action of the op-amp, producing a nominal output voltage of

$$V_{out} = V_{reset} - \frac{Q_{int}}{C_{fb}}. (2.13)$$

## Quantum Efficiency

The charge readout pixel has only one transistor, two wires, and two contacts, resulting in a relatively high optical aperture. The wires and transistor can be minimum size due to the small currents they pass.

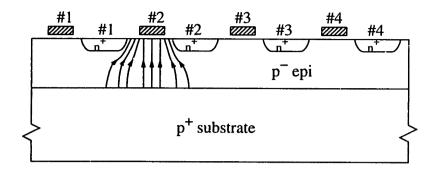

Collection efficiency depends largely on doping profile. An enhanced CMOS process with additional implants could achieve collection efficiencies comparable to a CCD pixel. In a digital CMOS process, the choices are limited. Available photodiodes include the n<sup>+</sup> – p-well diode, p<sup>+</sup> – n-well diode, and n-well – substrate diode. Diffusion – well photodiodes will have relatively poor blue response because degenerate doping increases the defect density near the silicon surface; carriers generated near the surface tend to recombine before reaching the potential well. Red response is also compromised due to the limited space charge layer depth. The n-well photodiode avoids both of those problems, and should therefore produce good collection efficiency [37].

Figure 2-11: Charge readout pixel cross-section and plan view.

## Conversion Gain

The conversion gain is  $C_{fb}^{-1}$ . There is no benefit in making the feedback capacitance greater than that which results in a full-scale swing for a saturation charge packet. Lower feedback capacitance results in higher conversion gain but limits the saturation charge.

#### Random Noise

Random noise sources include photonic noise, dark current shot noise, switch noise from the row select device, and amplifier noise. Photonic noise is a fundamental noise source for all imagers, and is caused by the Poisson statistics of the incoming photons. The resultant number of noise electrons is equal to the square root of the total number of imaged electrons. Dark current behaves the same as photogeneration current, and has the same shot noise characteristics. The main difference between these noise sources is that photonic noise increases with illumination, while dark current noise is independent of illumination.

Switch noise is the well known kTC noise caused by any switching operation onto a capacitor. The relevant capacitance in this case is the series combination of the pixel capacitance and the column line capacitance. Since the pixel capacitance is much less, the noise charge is very close

Figure 2-12: (a) Equivalent circuit for charge readout pixel and output circuit.  $I_{crosstalk}$  is the optical crosstalk current from all pixels close to the column line. (b) Timing diagram for charge readout pixel.  $T_{ro}$  is the readout time.

Figure 2-13: Random noise model for amplifier.

Figure 2-14: Random noise model for charge readout output circuit.

$$Q_{n,sw,rms} = \sqrt{kTC_{pixel}}. (2.14)$$

It is desirable to keep the pixel capacitance as low as possible for noise reasons. Switch noise is independent of illumination. Note that the reset device M2 also produces switch noise, but it can be ignored because CDS mostly removes it.

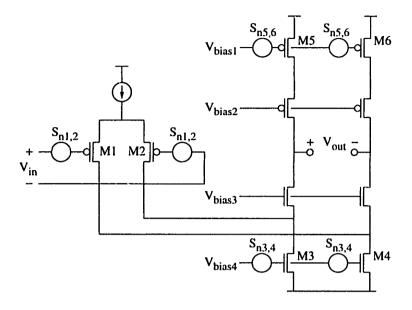

The noise model for the amplifier (assumed to be a folded cascode design) is shown in Fig. 2-13. The input-referred noise spectral density is

$$S_n = 2\left(S_{n1,2} + S_{n3,4} \left(\frac{g_{m3,4}}{g_{m1,2}}\right)^2 + S_{n5,6} \left(\frac{g_{m5,6}}{g_{m1,2}}\right)^2\right). \tag{2.15}$$

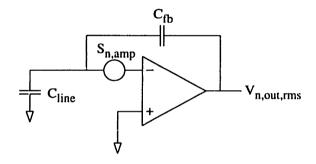

The noise model for the entire readout circuit is shown in Fig. 2-14. The input-referred amplifier noise is multiplied by the closed loop gain of the system and limited by the system bandwidth. The noise, referred back to pixel charge, is

$$Q_{n,amp,rms} = C_{col} \sqrt{S_n \cdot \text{BW (Hz)} \cdot \pi/2}, \qquad (2.16)$$

where BW is the closed-loop bandwidth of the system. This quantity is related to the readout time  $T_{ro}$ . The bandwidth should be just enough to allow settling in the readout time.

$$T_{ro} = N\tau = \frac{N}{2\pi \cdot \text{BW (Hz)}},\tag{2.17}$$

where N settling times are assumed. For 10 bit settling,  $N \approx 7$  is required to get within one lsb of the value at  $t = \infty$ . Amplifier noise decreases as  $T_{ro}$  increases. Readout time is usually limited by a minimum frame rate requirement.

The noise for a voltage readout pixel has a similar expression, where the noise source is the source follower device instead of the op-amp input devices. The noise is much lower for the voltage readout pixel because the corresponding capacitance is the pixel capacitance  $C_{pd}$  rather than the column line capacitance  $C_{col}$ . This noise is signal-independent.

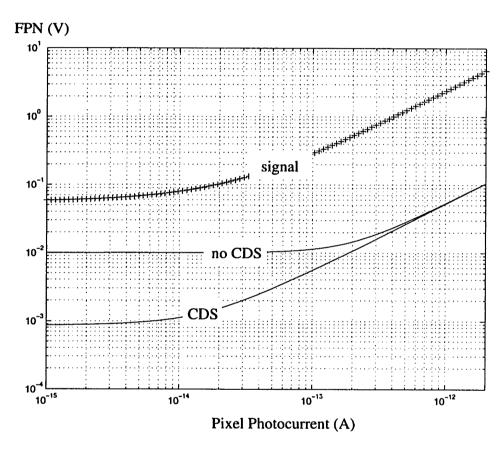

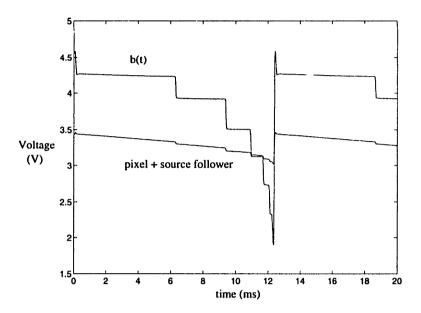

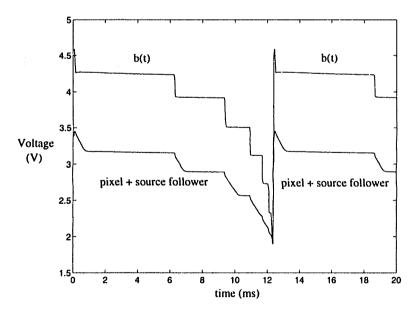

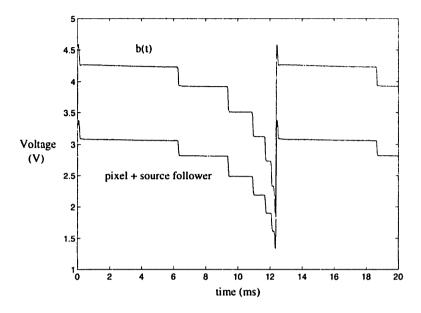

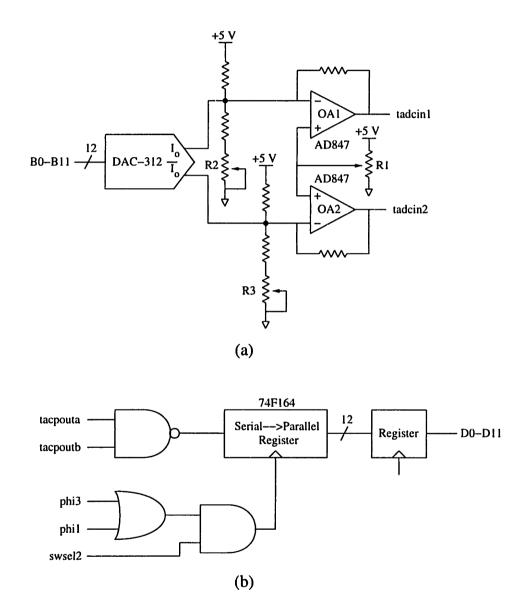

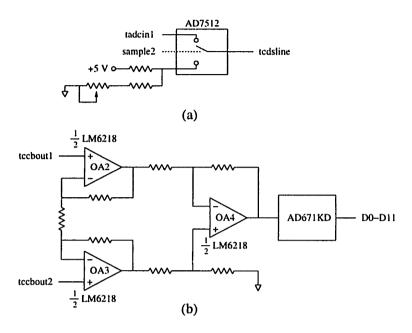

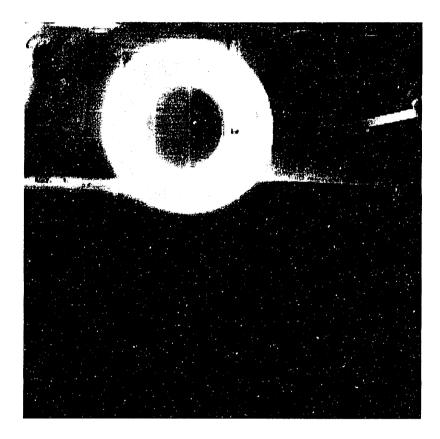

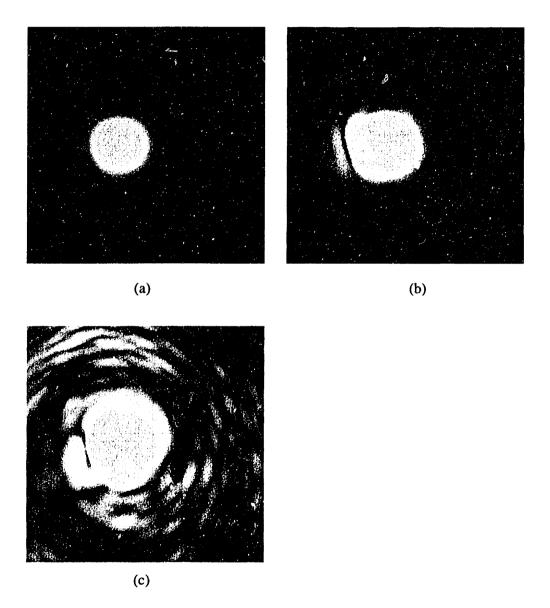

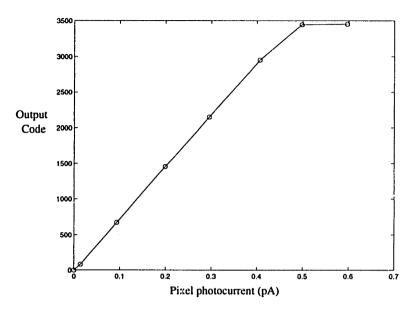

# **Saturation Level**