#### DESIGN OF A CRYOTRON COMPUTER

by

#### FRED HERZFELD

# SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF BACHELOR OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June, 1958

### Signature Redacted

| Signature of. | Author                                     |

|---------------|--------------------------------------------|

|               | Signature Redacted                         |

| Certified by  | Signature Redacted Thesis Supervisor       |

| Accepted by   | Chairman, Departmental Committee of Theses |

#### DESIGN OF A CRYOTRON COMPUTER

by

#### FRED HERZFELD

Submitted to the Department of Electrical Engineering on May 26, 1958 in partial fulfillment of the requirements for the degree of Bachelor of Science.

#### ABSTRACT

The work reported in this thesis is the development of the logical and associated circuitry of a general purpose digital computer employing cryotrons.

Following a discussion of the basic switching functions in two forms of realizations, and a discussion of a pulse detector with complementary output, the general organization of the cryotron computer is presented.

Diagrams of the computer logical circuitry and the associated terminal equipment are given. A read-out amplifier for the low-level cryotron output was designed, constructed, and tested in a cryotron circuit. Proper operation of the read-out amplifiers in conjunction with cryotron circuits was achieved. A method of building the cryotron computer in plugin modules is presented. Coupling between modules is magnetic.

Thesis Supervisor: Dr. Dudley A. Buck

#### **ACKNOWLEDGMENT**

I wish to express my deepest appreciation to Dr. Dudley A. Buck for suggesting the topic of this thesis, for the patient guidance and supervision of the work, and for editing and criticising the completed thesis.

I also wish to thank Mr. Arthur J. Schneider, Mr. Kenneth R. Shoulders, and Mr. Merle L. Wetherell for the many helpful discussions, and Allan F. Pacela for his aid in the construction.

I am indebted to Professor Ewan W. Fletcher for providing the laboratory facilities, and to the Lincoln Laboratory Division 6 Document Room for reproducing the thesis.

#### TABLE OF CONTENTS

|                                      |            |         |                                     | page           |

|--------------------------------------|------------|---------|-------------------------------------|----------------|

| Abstract Acknowledgme Table of Conte |            |         |                                     | i<br>ii<br>iii |

| List of Illustra                     |            |         |                                     | V              |

| CHAPTER I                            | INTR       | ODUCTI  | ON                                  |                |

|                                      | 1.1        | Histor  | 'y                                  | 1              |

|                                      | 1.2        | Object  | •                                   | 2              |

| CHAPTER II                           | BASI       | C CRYO  | TRON SWITCHING CIRCUITS             |                |

|                                      | 2.1<br>2.2 |         | ingle Cryotron                      | 3              |

|                                      | ۷. ۷       |         | asic Circuits Circuits and Notation | 3              |

|                                      |            |         |                                     | 4              |

|                                      |            | 2.22    | The OR Circuit The AND Circuit      | 6              |

|                                      |            |         | The NOT Circuit                     | 6              |

|                                      |            |         | The INHIBIT Circuit                 | 6              |

|                                      |            |         | The Flip-Flop                       | 8              |

|                                      |            |         | The DELAY                           | 8              |

|                                      |            |         | The Pulse Detector                  | 8              |

| CHAPTER III                          | GENE       | ERAL OF | RGANIZATION                         |                |

|                                      | 3.1        | Specif  | ications                            | 13             |

|                                      | 3.2        |         | Sequence                            | 18             |

|                                      |            |         | The Instruction Cycle               | 18             |

|                                      |            | 3.22    | The Execution Cycle                 | 20             |

| CHAPTER IV                           | THE        | COMPU'  | TER CIRCUIT                         |                |

|                                      | 4.1        | The M   | lemory Unit                         |                |

|                                      |            |         | The Memory                          | 26             |

|                                      |            | 4.12    | Memory Selection Matrix             | 28             |

|                                      | 4.2        | The P   | rint Unit                           |                |

|                                      |            | 4.21    | The Print Register                  | 28             |

|                                      |            | 4.22    | The Ten Position Switch             | 28             |

|                                      |            | 4.23    |                                     | 3.2            |

|                                      |            | 4.24    |                                     | 32             |

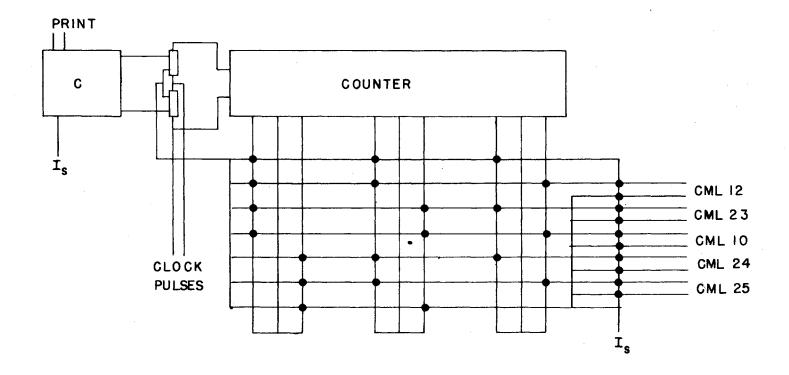

|                                      | 4.3        | ~       | Speed Fast Access Counter           | 35             |

|                                      | 4.4        |         | ccumulator Unit                     | 2.0            |

|                                      |            | 4.41    | The A Register                      | 38             |

|                                      |            | 4.42    | The M Register                      | 40             |

|             |      |          |                            | -iv-           |

|-------------|------|----------|----------------------------|----------------|

|             |      | 4.43     | The B Register             | 41             |

|             |      |          | The Adder                  | 41             |

|             | 4.5  | The Bus  | Register                   | 41             |

|             | 4.6  | The Inst | truction Counter           | 43             |

|             | 4.7  | The Cor  | ntrol                      | 43             |

|             | 4.8  | The Ins  | truction Selection Matrix  | 43             |

|             | 4.9  | The Clo  | ck                         | <del>4</del> 5 |

|             | 4.10 | The Clo  | ck Gates                   | 45             |

|             | 4.11 | The Ove  | erflow Register            | 48             |

|             | 4.12 | Product  | Sign Digit Register        | 48             |

|             | 4.13 | Comma    | nd Line Selection Matrices |                |

|             |      | 4.13-1   | Addition                   | 51             |

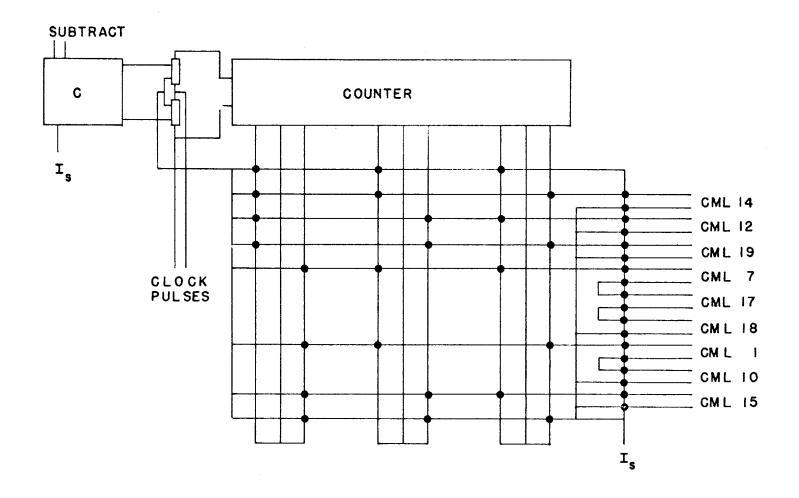

|             |      | 4.13-2   | Subtraction                | 51             |

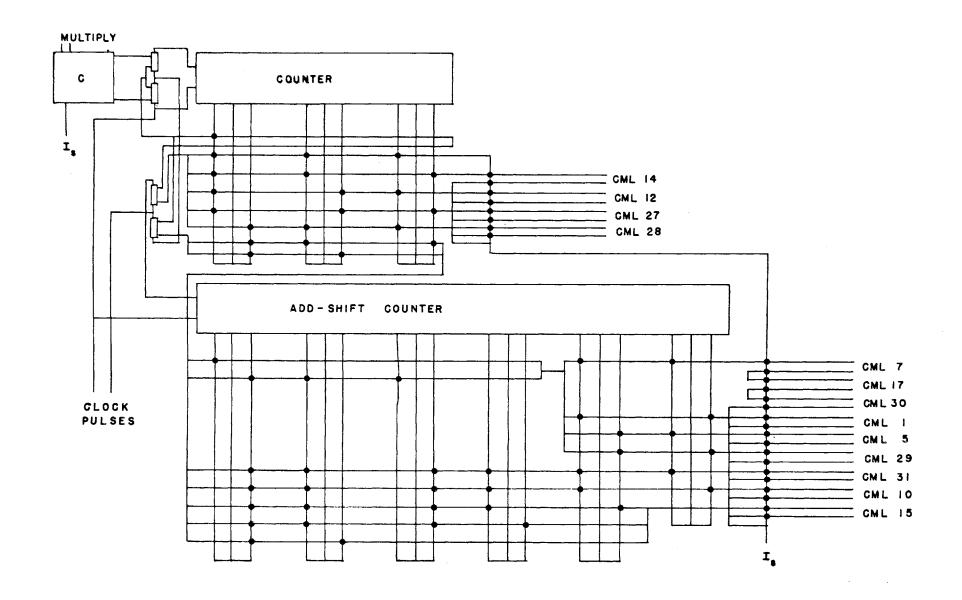

|             |      | 4.13-3   | Multiplication             | 54             |

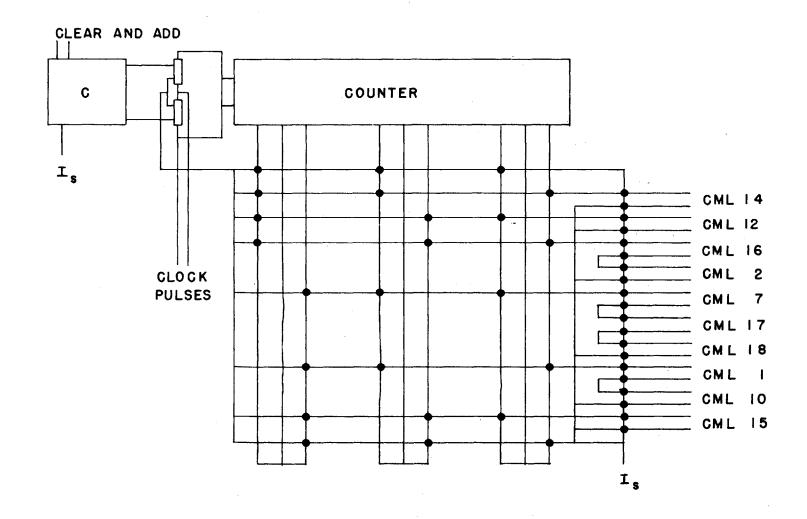

|             |      | 4.13-4   | Clear and Add              | 54             |

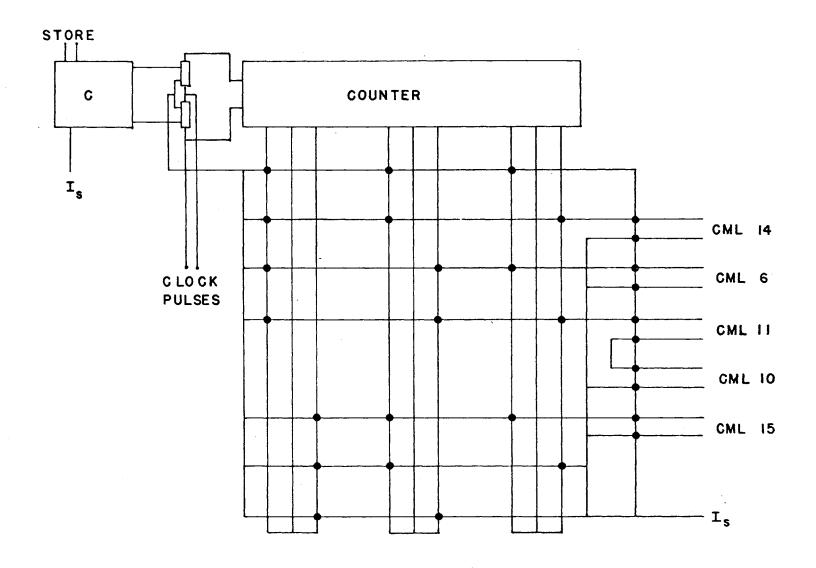

|             |      | 4.13-5   | Store                      | 54             |

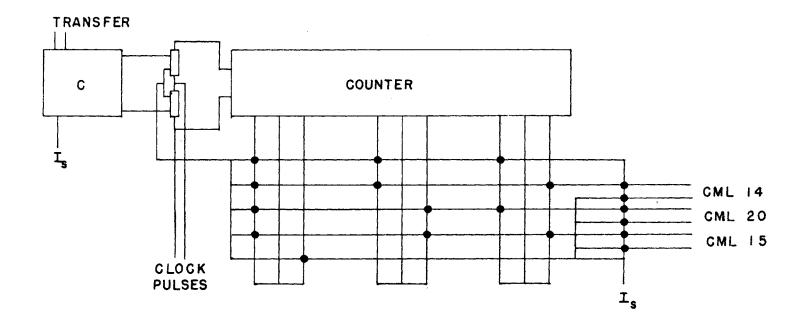

|             |      | 4.13-6   | Transfer                   | 58             |

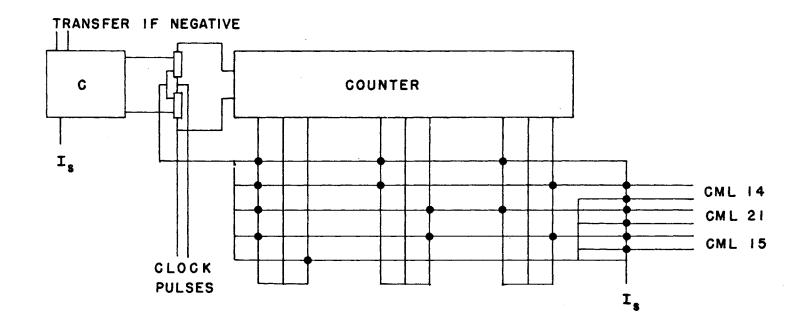

|             |      | 4.13-7   | Transfer if Negative       | 58             |

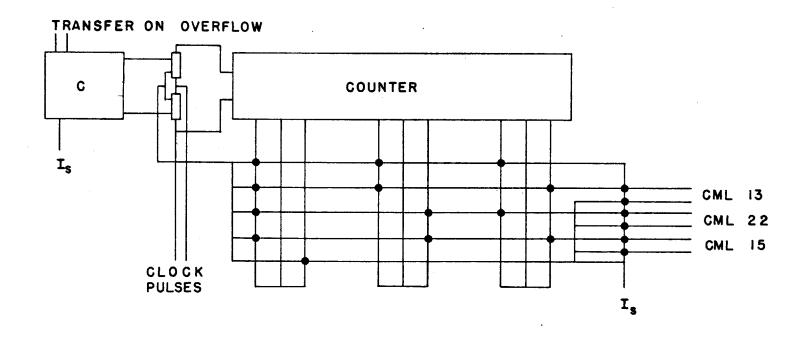

|             |      | 4.73-8   | Transfer on Overflow       | 58             |

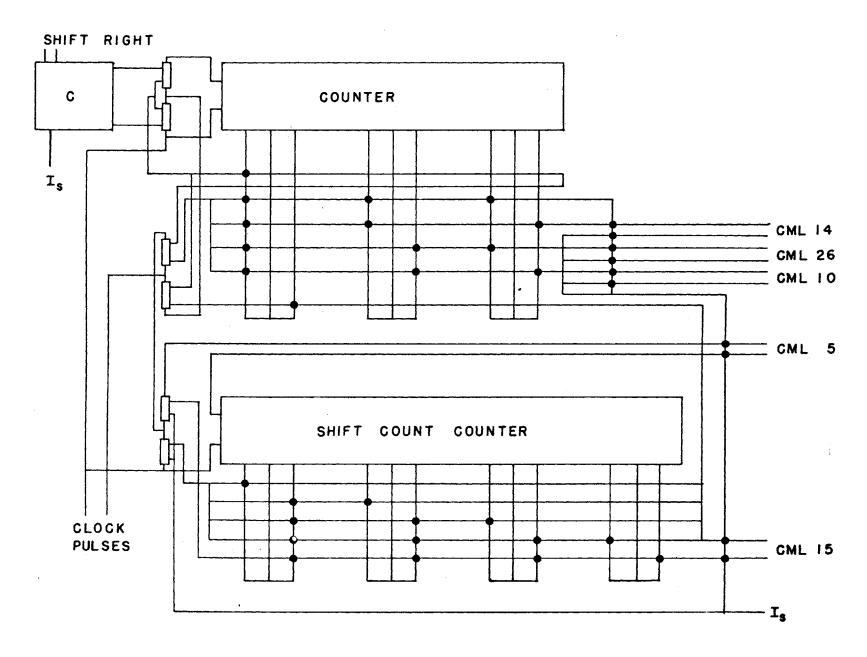

|             |      | 4.13-9   | Shift Right                | 58             |

|             |      | 4.13-10  | Shift Left                 | 62             |

|             |      | 4.13-11  | Print                      | 62             |

|             | 4.14 | The Rea  | id-In Unit                 | 65             |

| CHAPTER V   | TERA | IINAL EQ | UIPMENT                    |                |

|             | 5.1  | Output   | r .                        | 71             |

|             | 5.2  | Input    |                            | 75             |

| CHAPTER VI  | CONS | TRUCTIO  | N OF CRYOTRON CIRCUITS     |                |

|             | 6.1  | Superco  | nductive Joints            | 76             |

|             | 6.2  | -        | Construction               | 76             |

| CHAPTER VII | CONC | LUSIONS  |                            |                |

|             | 7.1  | Summar   | ·y                         | 78             |

|             | 7.2  | Suggest  | ions for Further Research  | 79             |

| APPENDIX I  | COMN | MAND LIN | IES                        | 80             |

| BIBLIOGRAPH | Y    |          |                            | 81             |

#### LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                            | Page |

|------------------|--------------------------------------------------|------|

| 1                | General OR Circuit                               | 5    |

| 2                | General AND Circuit                              | 5    |

| 3                | Inhibit Gate                                     | 7    |

| 4                | Cryotron Flip-Flop Circuit                       | 9    |

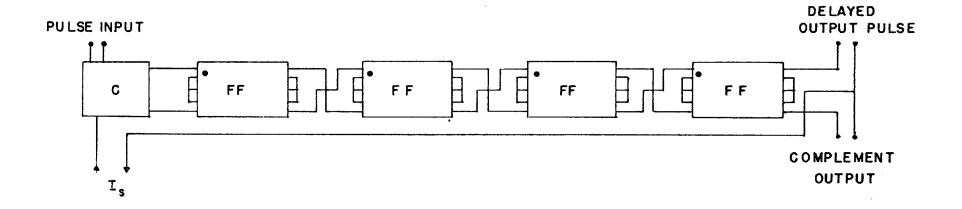

| 5                | Cryotron Delay Circuit                           | 10   |

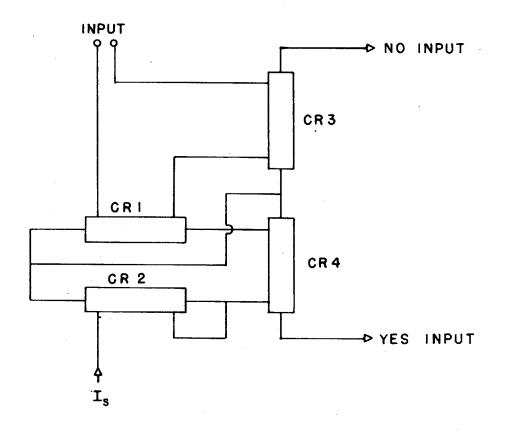

| 6                | Complementation Circuit                          | 12   |

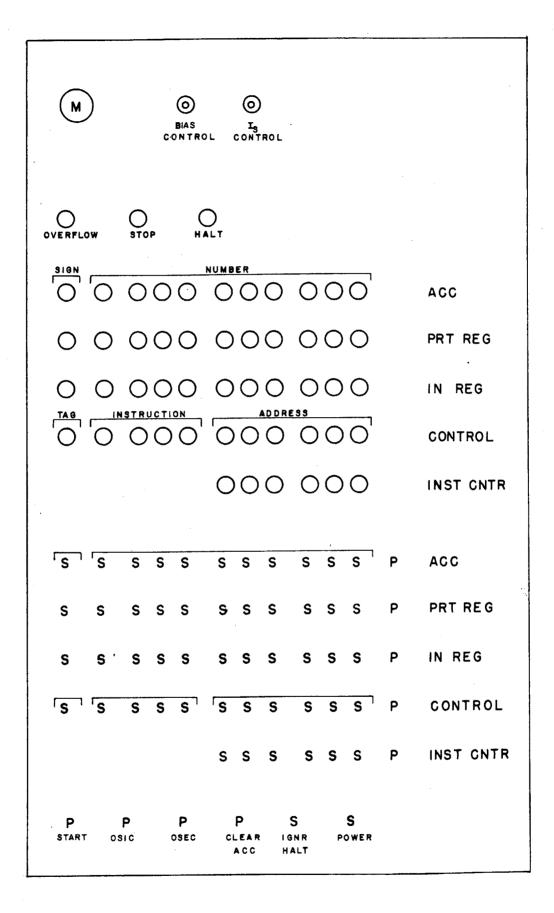

| 7                | Computer Panel                                   | 17   |

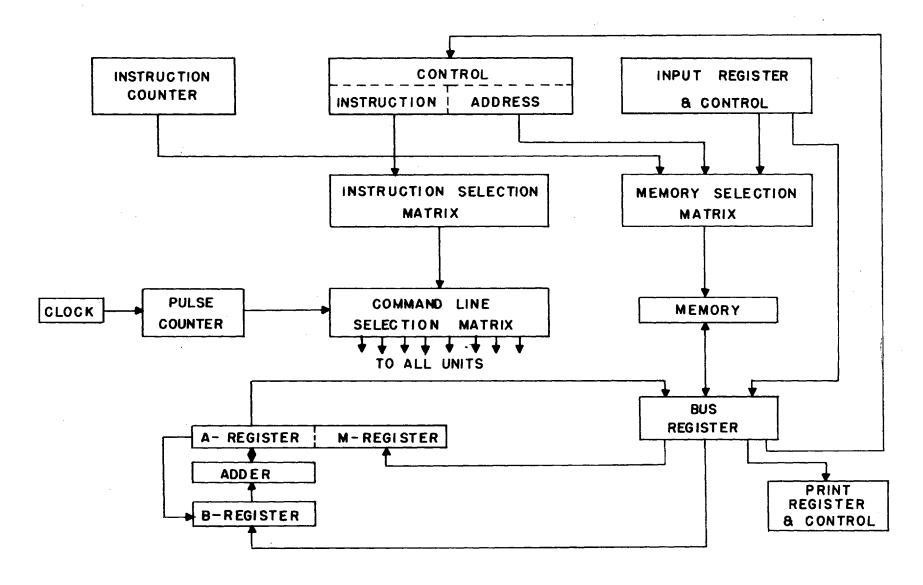

| 8                | Block Diagram of Cryotron Computer               | 19   |

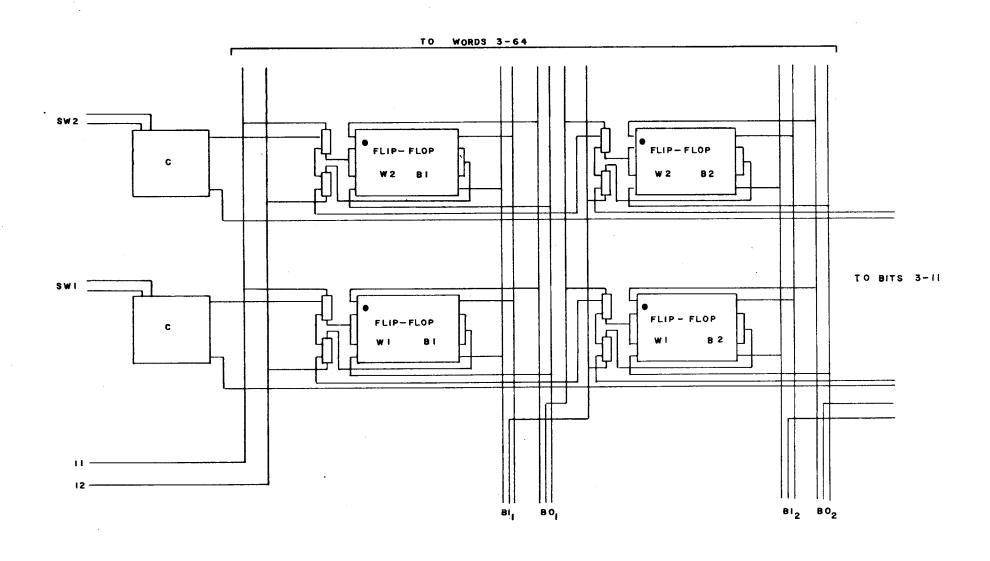

| 9                | Cryotron Flip-Flop Memory                        | 27   |

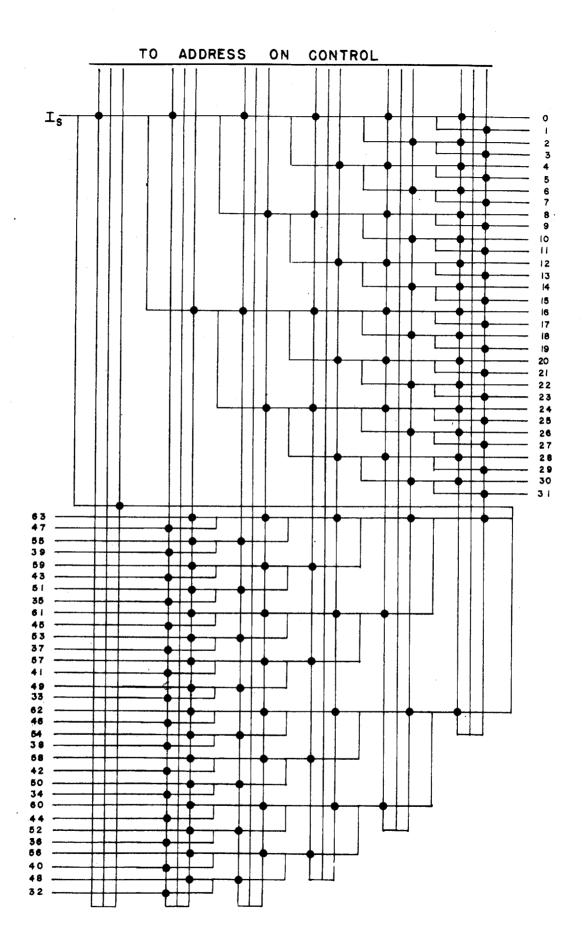

| 10               | Memory Selection Matrix Tree                     | 29   |

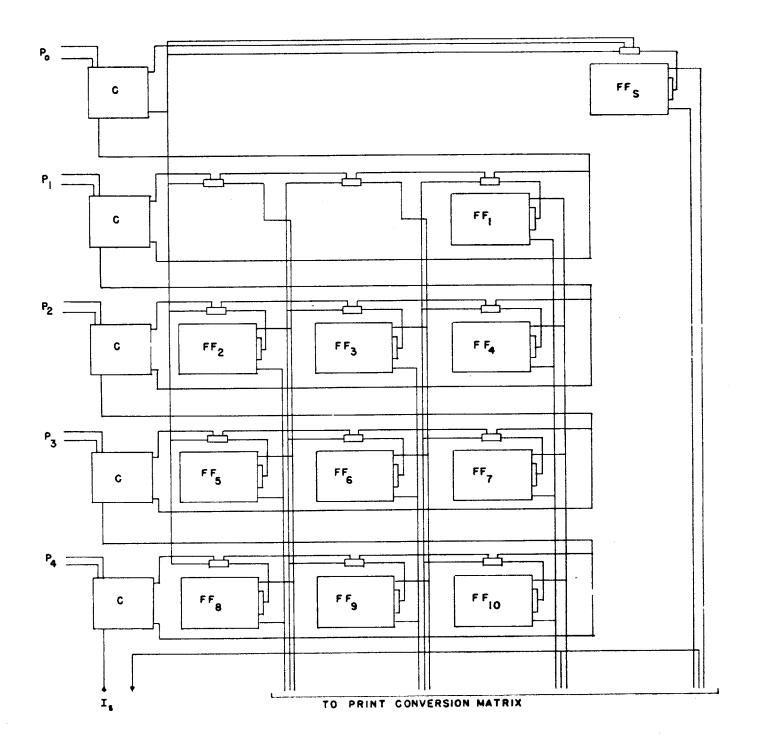

| 11               | Print Register                                   | 30   |

| 12               | Ten position switch for Print Translation Matrix | 31   |

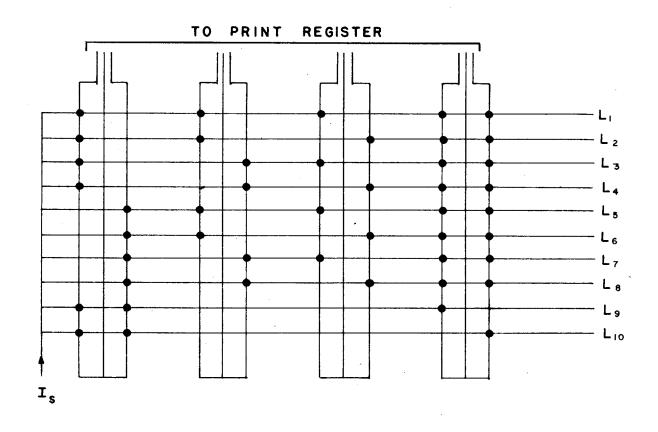

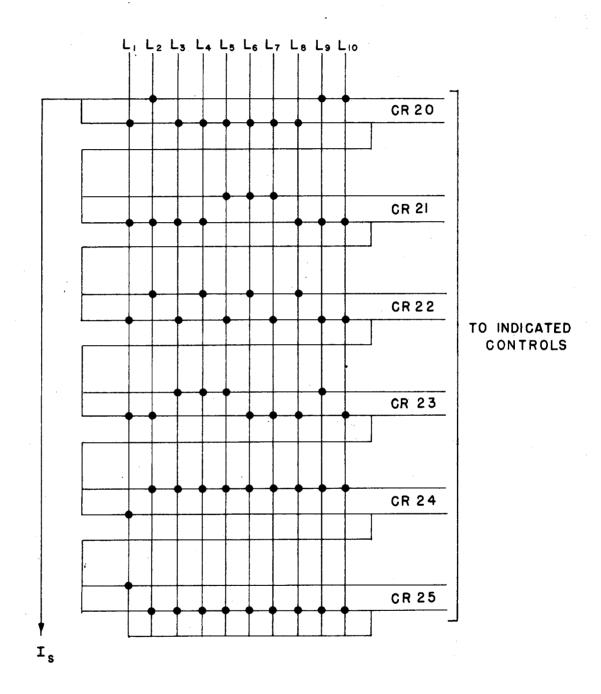

| 13               | Print Translation Matrix                         | 33   |

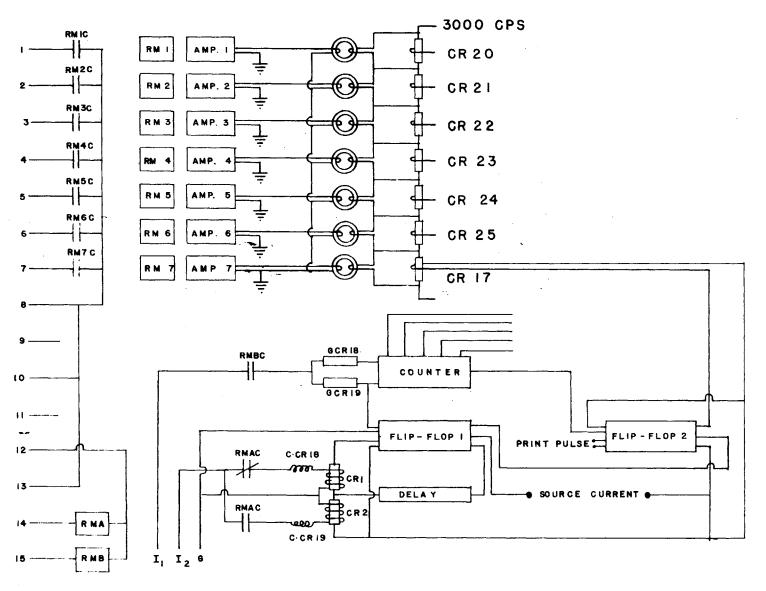

| 14               | Flexowriter Print Routine Circuit                | 34   |

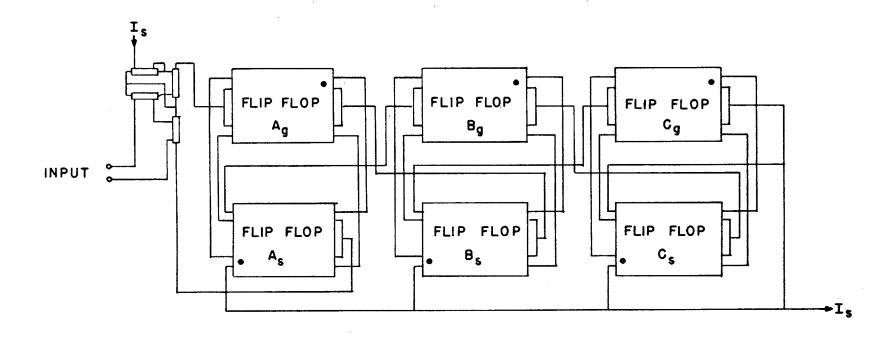

| 15               | High Speed Fast-Access Counter                   | 37   |

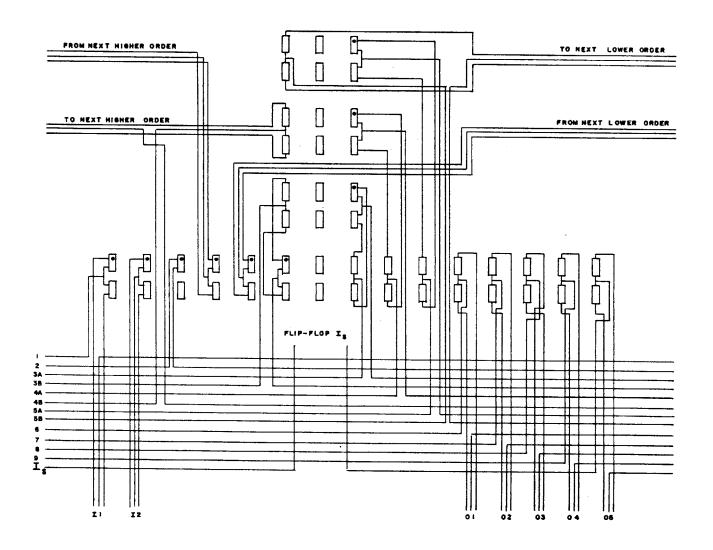

| 16               | Single Order Cryotron A Register                 | 39   |

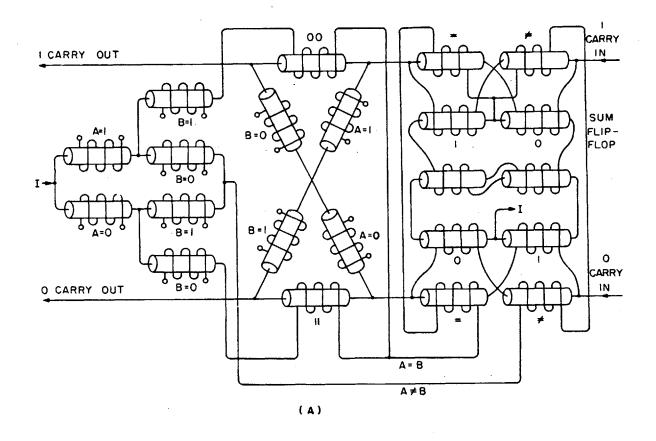

| 17               | Adder with End-Around-Carry Network              | 42   |

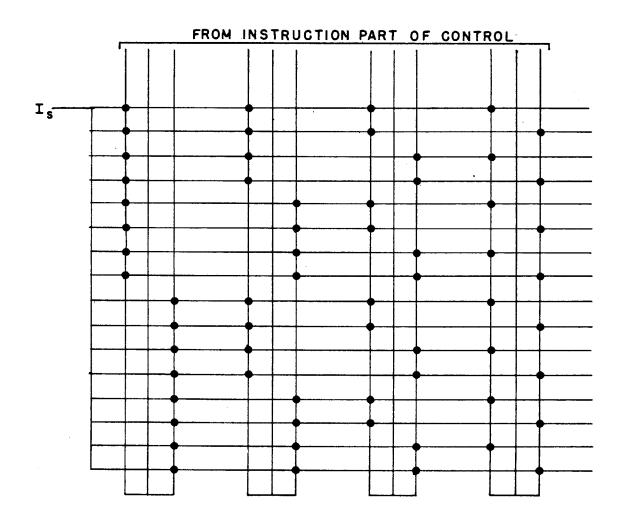

| 18               | Instruction Selection Matrix                     | 44   |

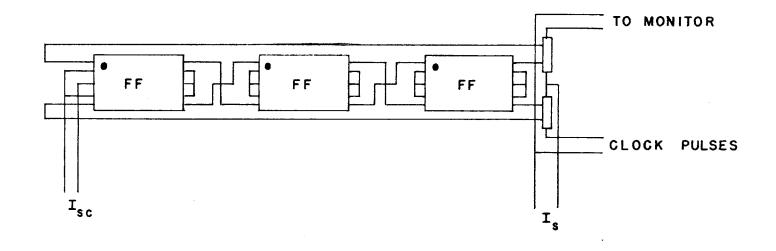

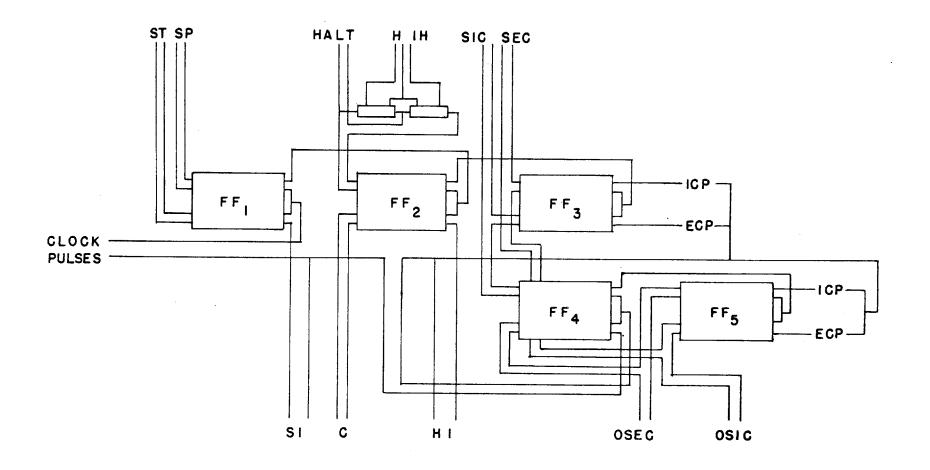

| 19               | Cryotron Clock                                   | 46   |

| 20               | The Clock Gates                                  | 47   |

| 21               | The Overflow Storage and checking Register       | 49   |

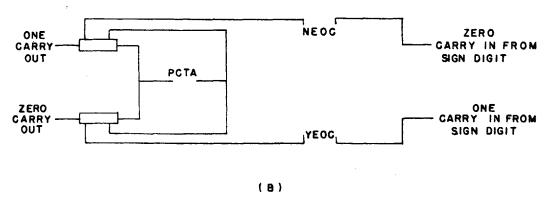

| 22               | Product Sign Digit Register                      | 50   |

| 23               | Command Line Selection Matrix for Addition       | 52   |

| 24               | Command Line Selection Matrix for Subtraction    | 53   |

| 25               | Command Line Selection Matrix for Multiplication | 55   |

| 26               | Command Line Selection Matrix for Clear and Add  | 56   |

### LIST OF ILLUSTRATIONS (continued)

| Figure<br>Number | Title                                                  | Page |

|------------------|--------------------------------------------------------|------|

| 27               | Command Line Selection Matrix for Storage              | 57   |

| 28               | Command Line Selection Matrix for Transfer             | 59   |

| 29               | Command Line Selection Matrix for Transfer if Negative | 60   |

| 30               | Command Line Selection Matrix for Transfer on Overflow | 61   |

| 31               | Command Line Selection Matrix for Shift Right          | 63   |

| 32               | Command Line Selection Matrix for Print                | 64   |

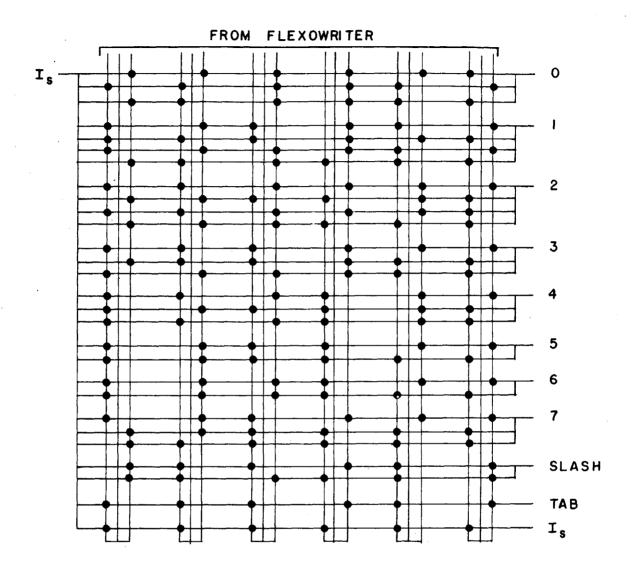

| 33               | Flexowriter Translation Matrix 1                       | 66   |

| 34               | Flexowriter Translation Matrix 2                       | 67   |

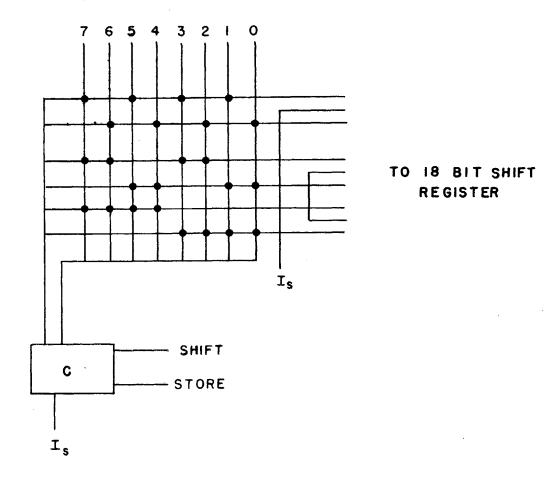

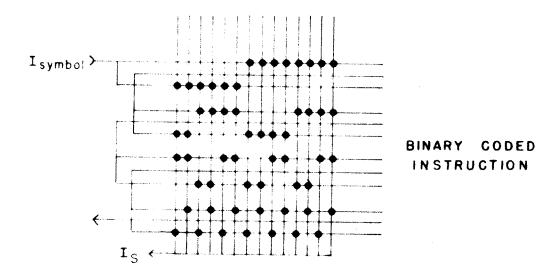

| 35               | Number-Symbol Selection Matrix                         | 68   |

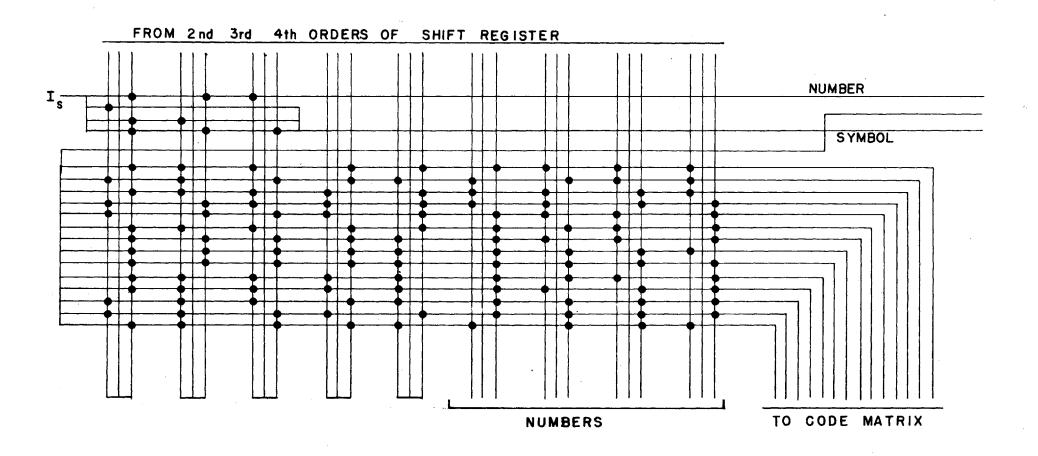

| 36               | Code Matrix                                            | 69   |

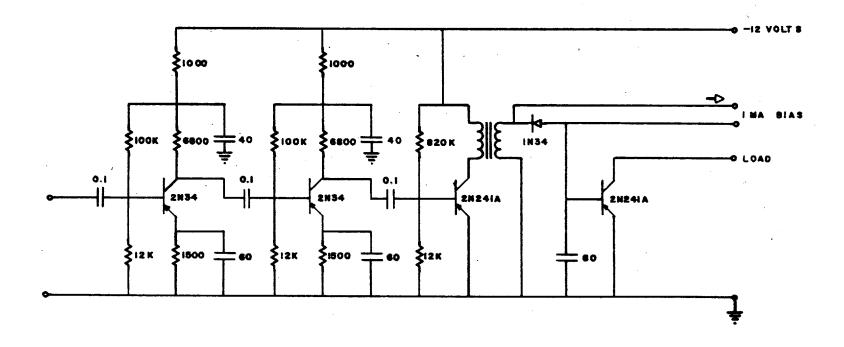

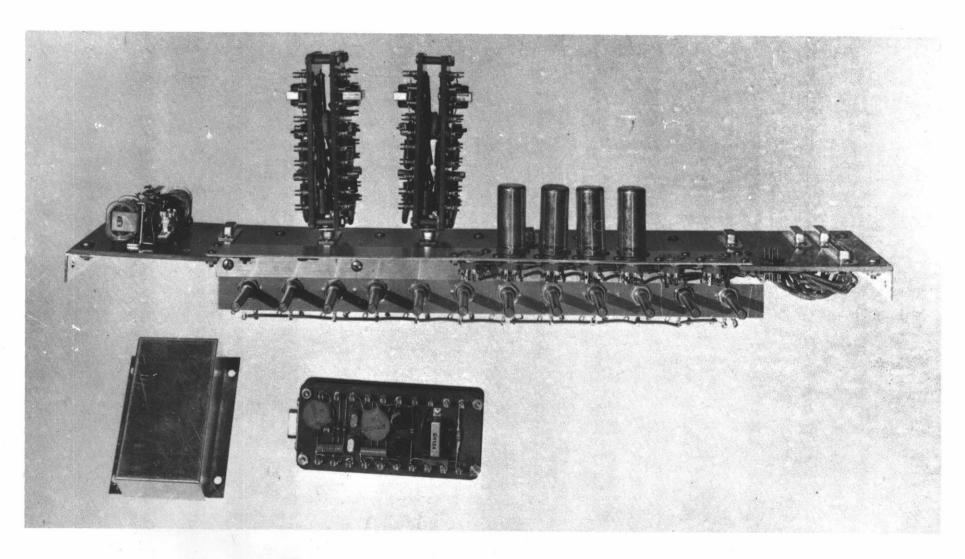

| 37               | Read-out Amplifier                                     | 72   |

| 38               | Read-out Amplifiers and Plug Board                     | 74   |

#### CHAPTER I

#### INTRODUCTION

#### 1.1 HISTORY

In the evolution of science and technology the trend toward more complex systems has forced a continual search for means to miniaturize, to investigate and apply the various phenomena of solid-state devices.

In the computer field there has been the ever more important search for methods which will increase the speed of operation of the computer. There are three solutions to the combined problem of attaining small size and high speed. First, new circuitry which will permit the present relatively slow components to function more efficiently, as for example, an otherwise slow counter employing high speed carry propagation. Second, the development of new components which are inherently applicable as high speed devices. Along with these two solutions there is the possibility of reduction in size through smaller construction and packaging. The third and perhaps most important region in which we hope to find solutions to the problem is in a combination of new circuitry with new components which are not only fast but small. This then is the problem: Find a new component which is inherently small and develop the associated new circuitry. In this thesis we will be dealing mainly with the circuitry of a newly developed component.

The development of the cryotron by D. A. Buck has opened another path along which we may hope to achieve both high speed and microminiaturization. The cryotron consists of a super-

<sup>1.</sup> Superscripts refer to references listed in the Bibliography.

conductor whose superconductive state may be destroyed by the application of a magnetic field. It is a two-state device operating in the temperature region near absolute zero; dissipating power only during the transition period; easily fabricated in extremely small size; and whose upper switching frequency limit has been estimated between 100 and 1,000 megacycles.

Operation at this low temperature implies not only that the device has a very low noise level, but also that it will have an extremely long life. Its two-state nature implies simple circuitry for a binary system. Dissipation of power during the switching transition only means less formidable requirements on the power source. The small size in which the cryotron may be fabricated means that larger systems can be packaged into a smaller space. Along with these advantages there is the possibility of extreme speed as the cryotron becomes physically smaller.

#### 1.2 OBJECTIVE

There are four parts that will be considered. First, the design of a small general purpose stored program digital computer using cryotron circuitry. Second, the design of reliable read-out amplifiers. Third, the construction of both the computer and the associated terminal equipment. Last and most important, the testing of the computer to determine the reliability of the cryotron in a large system. We will proceed from the discussion of the capabilities of the cryotron itself to the analysis of the Block Diagram logic, through the circuitry of the individual blocks and the problems of construction.

#### CHAPTER II

#### BASIC CRYOTRON SWITCHING CIRCUITS

#### 2.1 THE SINGLE CRYOTRON

The basic component of the computer, the cryotron, is a device which depends on the destruction of superconductivity by a magnetic field. The behavior of the cryotron is somewhat like an electromechanical relay, and yet between them there is a distinct difference in the number of "contacts" and in "contact resistance". A single electromechanical relay can have any number of contacts or contact pairs, while a single cryotron can have only normally closed contacts, and in the usual wire-wound form of construction has only one normally closed (superconductive) contact. The resistance of the open contact on an electromechanical relay is essentially infinite, preventing current flow. The cryotron gate (contact), on the other hand, presents approximately 0.001 ohm when resistive, thus as a series type switch it introduces only a small resistance which has little or no effect on the current flow. The closed contacts of the electromechanical relay present only a very small resistance, while the gate resistance of the superconductive cryotron is exactly zero. Useful switching with the cryotron can be accomplished by introducing the very small gate resistance into a path in which is flowing, and at the same time providing an alternate superconductive path for the current; that is, using it as a parallel switch.

#### 2.2 THE BASIC CIRCUITS

#### 2.21 CIRCUITS AND NOTATION

In the design of digital computers there are a number of basic circuits from which any functional relationship may be synthesized. In particular there are the OR, AND, NOT, and INHIBIT circuits.

The FLIP-FLOP and the DELAY are also of great importance as individual circuits although they may be constructed through the use of the simpler basic circuits. A PULSE DETECTOR of importance when the input signal is not in complementary form had to be developed.

Throughout the discussion we will make use of the TRANSMISSION rather than the HINDRANCE notation, and the duality that exists between the two systems will be particularly noted in a comparison of the OR and the AND circuits.

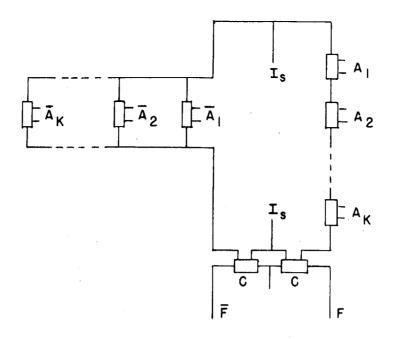

#### 2.22 THE OR CIRCUIT

The two general equations which specify the OR circuit may be written as:

$$F = \stackrel{\kappa}{\Sigma} A_{k}$$

$\overline{F} = \stackrel{\kappa}{\Pi} \overline{A}_{k}$  (1a, b)

where the  $A_k$ 's and the  $\overline{A}_k$ 's are the complementary inputs. F and  $\overline{F}$ represent the complementary outputs. While it is usual to consider only Equation la for the OR function, it was stated that an alternate shunt path for the current must be provided, and this is given in equation form by the dual of Equation la, namely 1b. The realization of these switching functions in terms of cryotron hardware is shown in Figure 1. This is only a typical circuit, and it must be recognized that many other circuit realizations of the functions (la, b) are possible. For the condition F= 0 we note that the source current I must flow through the control of cryotron C2. The gate of C2 must therefore be resistive, and that of  $\mathbf{C}_1$  superconductive. For any other input condition we have F= 1 and there are one or more gates on the F side which will be resistive, and one or more gates on the  $\overline{F}$  side which will be superconductive. The source current  $I_s$  must therefore flow through the control of cryotron  $C_1$ . The outputs may be determined by sensing the gates of C, and C2.

FIGURE 1

GENERAL OR CIRCUIT

FIGURE 2

GENERAL AND CIRCUIT

#### 2.23 THE AND CIRCUIT

We have previously mentioned the hindrance and transmission notations of Boolean Algebra as applied to switching circuits, the two systems being mathematical duals. Thus we may notice that the general equations for the AND circuit given by Equations 2a, b are the duals of Equations 1a, b.

$$F = \overset{\kappa}{h} A_{k}$$

$\overline{F} = \overset{\kappa}{\Sigma} \overline{A}_{k}$  (2a, b)

Except for an exchange in variables, 2a, b and la, b are identical and all that is required is an exchange of input lines and an exchange of output interpretation. This is shown in Figure 2. This duality is of particular importance in cryotron circuitry since the shunt or dual path must be present, and complementary inputs and outputs are also usually necessary.

#### 2.24 THE NOT CIRCUIT

The NOT circuit performs an inversion of the input variable. Thus for cryotron circuitry, since both the variable and its complement are usually present, the NOT circuit may be realized by an interchange of the output lines. If however the input is not present in complementary form the reader is referred to section 2.28 where a method of obtaining the complement is given.

#### 2.25 THE INHIBIT CIRCUIT

The INHIBIT function may be stated as:

$$F = X \cdot \overline{Y}$$

$\overline{F} = \overline{X} + Y$  (3a, b)

where Y is the inhibitor and X and Y any variables or function of variables. Figure 3 is a simple form of this function as realized without the use of dual X inputs although complementary Y inputs are required, and is a GATING TYPE realization. The INHIBIT circuit may also be realized by a proper choice of inputs to the AND circuit.

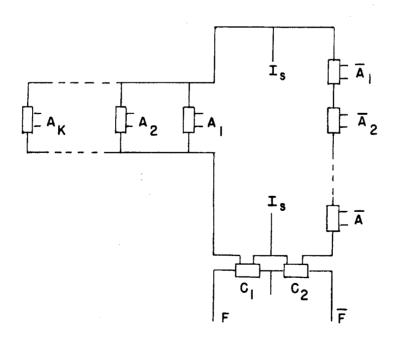

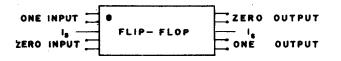

#### 2.26 THE FLIP-FLOP

A simple form for the FLIP-FLOP was shown to be that given in Figure 4a, with the block symbol representing it shown in Figure 4b. If we consider the source current  $I_s$  flowing through the gate of  $C_1$ , the gate of  $C_2$  being resistive, then it must also flow through the gate of  $C_3$  and through the controls of  $C_4$  and  $C_6$ . In flowing through the control of  $C_4$  it will prevent itself from flowing through the gate of  $C_2$ . The inputs are no longer required and the source current will remain in the same path. If an input is now applied to the control of  $C_1$ , the current will decay in the first path and build up in the alternate one and the FLIP-FLOP WILL change its state, which may be sensed by testing the output gates of cryotrons  $C_5$  and  $C_6$ . For such switching to occur the magnitude of the current  $I_s$  is given by Equation 4, and further details on the switching may be found in reference 4.

$$I_{c} \langle I_{s} \langle 2I_{c} \rangle$$

(4)

where  $I_c$  is the magnitude of the current at the threshold of switching.

#### 2.27 THE DELAY

A digital time delay may be achieved by interconnecting a series of FLIP-FLOPS in such a manner that a pulse travels down the line, flipping one after the other, as shown in Figure 5. Input and output gates may be combined thus requiring only four cryotrons per delay time plus two output cryotrons. By using only four cryotrons it is also possible to get short unit delay times.

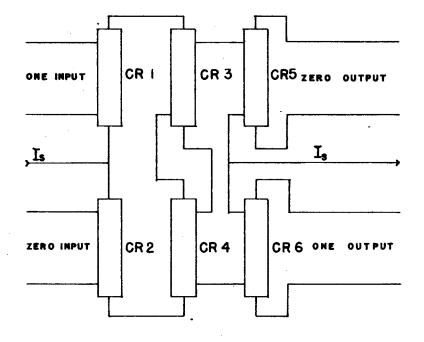

#### 2.28 COMPLEMENTARY-OUTPUT PULSE DETECTOR

It is pointed out above that the cryotron lends itself best to complementary circuitry. There are however times when compplementary inputs are not readily available, as for example in pulse detection, and it is necessary to use a circuit which will convert the presence or absence of a pulse into complementary outputs, one

(A)

(B)

indicating that a signal is present and the other indicating that there is no signal. The circuit diagram of such a pulse detector is shown in Figure 6.

When there is no input pulse, cryotrons  $\mathbf{C}_1$  and  $\mathbf{C}_3$  have no current flowing in their control windings. The gates of  $\mathbf{C}_1$  and  $\mathbf{C}_3$  are therefore superconductive. The source current  $\mathbf{I}_s$  has only one path available through which it may flow, namely through the control of  $\mathbf{C}_2$  and the gate of  $\mathbf{C}_1$ . This is the only superconducting path since there is a resistance in series with the other, produced by the gate of  $\mathbf{C}_2$  through the control of which the source current must always flow. This method of producing the resistance is used in order that the magnitude of the resistance is approximately that of any normal gate; however any resistance of proper magnitude may be substituted. Thus the current must choose the path which is entirely superconductive.

If there is a pulse present,  $\mathbf{C}_1$  and  $\mathbf{C}_3$  have current flowing in their control windings. The gates of  $\mathbf{C}_1$  and  $\mathbf{C}_3$  are therefore resistive. The source current  $\mathbf{I}_s$  now has two parallel resistive paths in which to flow, and the current in the control of  $\mathbf{C}_4$  is determined by the ratio of the two resistances. Assuming that the resistances are equal, the current in the control of  $\mathbf{C}_4$  will be less than  $\mathbf{I}_c$ , the transition current (the restriction on  $\mathbf{I}_s$  is again given by Equation 4.) and the gate of  $\mathbf{C}_4$  will be superconductive, while the gate of  $\mathbf{C}_3$  is resistive.

As shown in the diagram the source current  $I_s$  may be applied to the gates of  $C_3$  and  $C_4$  to sense their state and the outputs thus obtained labeled NO INPUT and YES INPUT.

#### CHAPTER III

#### GENERAL ORGANIZATION

#### 3.1 SPECIFICATIONS

The design of a computer must start with a decision as to what the computer is to be capable of performing. Since the purpose of this thesis is to develop the logical and associated circuitry of a general purpose digital computer using cryotrons for all of the switching elements, it is of importance to decide which functions or commands will best illustrate the use of cryotrons in a large system and provide a means for evaluating the performance of the system. For this purpose we have chosen to design a single address machine which has the 14 instructions listed in Table 1. While these 14 are only a few of the many instructions which could be built into the computer they will serve to illustrate the design principles. The number of digits in a word determines the precision with which the computer can handle numbers, and for the cryotron computer a word length of 11 binary digits was arbitrarily chosen. If one of these 11 is used for the sign digit (or the Tag for instructions) the number of digits for the address part of an instruction is fixed at 6 and the number of words in storage at 64. With 64 storage locations it will be possible to operate the computer with several program loops for long-time operation evaluation.

The computer panel was designed to provide as much flexibility as could reasonably be expected. The panel layout is shown in Figure 7. It provides visual observation of the data in the ACCUMULATOR, INPUT and OUTPUT registers, the INSTRUCTION COUNTER and the CONTROL register. For each of these there is a set of switches, (S), provided for manually correcting or setting the data at any of the mentioned units at a computer HALT POINT, and a push button, (P), for transfering the information

TABLE I

| INSTRUCTION   | SYMBOL | CODE | DESCRIPTION                                                                                                                                         |

|---------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop          | STP    | 0000 | Computer stops regardless of information in address part of instructions. Indicates STOP on panel.                                                  |

| Add           | ADD    | 0001 | The number stored at the indicated address is added to the contents of the accumulator, and the sum remains in the accumulator.                     |

| Subtract      | SUB    | 0010 | The number stored at the indicated address is subtracted from the contents of the accumulator and the difference remains in the accumulator.        |

| Multiply      | MUL    | 0011 | The number stored at the indicated address is multiplied by the contents of the accumulator. The eleven least significant remain in the M register. |

| Clear and Add | CLA    | 0100 | The accumulator is reset to zero and the number stored at the indicated address is placed in the accumulator.                                       |

| Store                | STR | 0101 | The number in the accumulator is placed in the indicated storage location; previous content of the storage location is discarded, and the contents of the accumulator remain unchanged.                                        |

|----------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transfer             | TRA | 0110 | The next instruction is taken from the address indicated.                                                                                                                                                                      |

| Transfer if Negative | TRN | 0111 | The next instruction is taken from the address indicated if the sign of the accumulator is negative, otherwise the next instruction is taken in normal sequence. Zero is interpreted as negative.                              |

| Transfer on Overflow | TRO | 1000 | The next instruction is taken from the address indicated if an overflow occured on the previous operation, otherwise the next instruction is taken in normal sequence. Overflow register reset; accumulator remains unchanged. |

| Shift Right          | SHR | 1001 | The number in the accumulator is shifted to the right by the number of places indicated in the address part of the instructions. Sign remains unchanged. Shifted digits enter the M register.                                  |

| Shift Left | SHL | 1010 | The number in the accumulator is shifted to the left by the number of places indicated in the address part of the instructions. Digits shifted to the left of the tenth order are discarded. Sign remains unchanged. |

|------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Print      | PRT | 1011 | The word at the indicated address is placed in the PRINT register and printed by the Flexowriter as a SIGN plus four octal digits.                                                                                   |

| Halt Point | HLT | 1100 | Computer comes to a halt. All registers remain unchanged. Computer will start with the next instruction in sequence when exrestarted. Indicates HALT on panel.                                                       |

| Read In    | RDN | 1101 | The number in the input register is placed in the memory at the location specified by the address part of the instructions. Previous contents of the memory location are discarded.                                  |

stored in the switches to the respective register. Visual indication is provided for the OVERFLOW, PROGRAM STOP and HALT POINT. Switches are provided for PROGRAM START, OPERATE SINGLE INSTRUCTION CYCLE, OPERATE SINGLE EXECUTION CYCLE, CLEAR ACCUMULATOR, CLEAR INSTRUCTION REGISTER, and IGNORE HALT POINT.

A meter and two potentiometers are provided to monitor the source current and properly set the level of the read-out amplifiers.

#### 3.2 PULSE SEQUENCE

From the basic Block Diagram of the cryotron computer, Figure 8, the sequence of pulses necessary for the various instructions was determined. To minimize the number of such pulses for a given instruction, the sequence was arranged so that a given pulse could perform several functions simultaneously. The generation of the pulses and the switching networks which distribute them are discussed in detail in Chapter IV of this thesis; in this section the pulse sequences for each of the various instructions are determined. Each sequence is divided into two distinct cycles - the instruction cycle and the execution cycle.

#### 3.21 THE INSTRUCTION CYCLE

One of the pulses of every command either advances the instruction counter by ONE or, if it is a transfer command, places the transfer address in the instruction counter. The last pulse from any of the execution matrices routes the clock pulses to the instruction cycle selection matrix. If the computer is being started manually the instruction counter is set to the address of the first instruction (usually zero) and the clock pulses are diverted from both the instruction cycle and the execution cycle matricies until the START

FIGURE 8 BLOCK DIAGRAM OF CRYOTRON COMPUTER

button is depressed. The pulse sequence to the various command lines for performing the INSTRUCTION CYCLE is given in Table 2.

#### 3.22 THE EXECUTION CYCLE

The pulse sequence during the operation of the EXECUTION CYCLE is also determined from the Block Diagram. Since one of the instructions allows a TRANSFER ON OVERFLOW, the first pulse in every sequence with the exception of the PRINT is a test for overflow. The pulse sequence for the various commands during the execution cycle is given in Table III. Having determined the sequence of pulses that is required for the various arithmetic operations we turn to the design of the individual units.

#### TABLE II

**OPERATION**

| ·              |                                  |

|----------------|----------------------------------|

| $P_0$          | Cut off command lines            |

| P              | Read Memory into Bus             |

| P <sub>2</sub> | Read Bus into Control            |

| P <sub>3</sub> | Switch clock to execution cycle. |

|                |                                  |

PULSE NUMBER

#### TABLE III

| PULSE NUMBER   | OPERATION                                                                       |

|----------------|---------------------------------------------------------------------------------|

| ADDITION       |                                                                                 |

| P <sub>0</sub> | Cut off command lines                                                           |

| Pl             | Test for overflow                                                               |

| P <sub>2</sub> | Read Memory into Bus                                                            |

| P <sub>3</sub> | Read Bus into B register                                                        |

| P <sub>4</sub> | Read A register into Adder<br>Read B register into Adder<br>Pulse Carry to Add  |

| P <sub>5</sub> | Read sum into A register<br>Advance Instruction counter                         |

| P <sub>6</sub> | Switch clock to instruction cycle                                               |

| SUBTRACTION    |                                                                                 |

| $P_{0}$        | Cut off command lines                                                           |

| P              | Test for overflow                                                               |

| P <sub>2</sub> | Read Memory into Bus                                                            |

| $P_{3}$        | Read Bus into B register                                                        |

| P <sub>4</sub> | Read A register into Adder<br>Read B register into Adder<br>Pulse Carry to Add. |

| P <sub>5</sub> | Read sum into A register<br>Advance Instruction counter                         |

| P <sub>6</sub> | Switch clock to instruction cycle.                                              |

#### STORE

P Cut off command lines

P, Test for overflow

P Read A register into Bus

Pa Read Bus into Memory

Advance Instruction Counter

P<sub>4</sub> Switch clock to instruction cycle

#### TRANSFER

P Cut off command lines

P, Test for overflow

P Read Address into Instruction counter

P<sub>3</sub> Switch clock to Instruction cycle

#### TRANSFER IF NEGATIVE

P. Cut off command lines

P. Test for overflow

P Read address into Instruction counter

if sign of A register is negative

P<sub>2</sub> Switch clock to Instruction cycle

#### TRANSFER ON OVERFLOW

$\mathbf{P}_{0}$  Cut off command lines

Pusle TRANSFER ON OVERFLOW line

P<sub>2</sub> Switch clock to Instruction cycle

#### STOP

Pulse to STOP flip-flop of clock

#### MULTIPLY

| P <sub>0</sub>               | Cut off command lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P <sub>1</sub>               | Test for overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P <sub>2</sub>               | Read Memory into Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P <sub>3</sub>               | Read A register into B register via<br>complement if necessary<br>Read Bus into M register via complement<br>if necessary<br>Store sign in SIGN storage register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P <sub>4</sub>               | ZERO set A register<br>ZERO set Adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P <sub>5</sub>               | Read A register into Adder Read B register into Adder Pulse carry to Add if right hand order of M register is ONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P <sub>6</sub>               | Read sum into A register if right hand order of M register is ONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P <sub>7</sub>               | Shift Right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P <sub>8</sub>               | Zero set sign order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| The sequence of pulse        | $^{\circ}$ |

| of ten times in the above se | quential order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P <sub>45</sub>              | Complement A register if necessary via sign storage register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

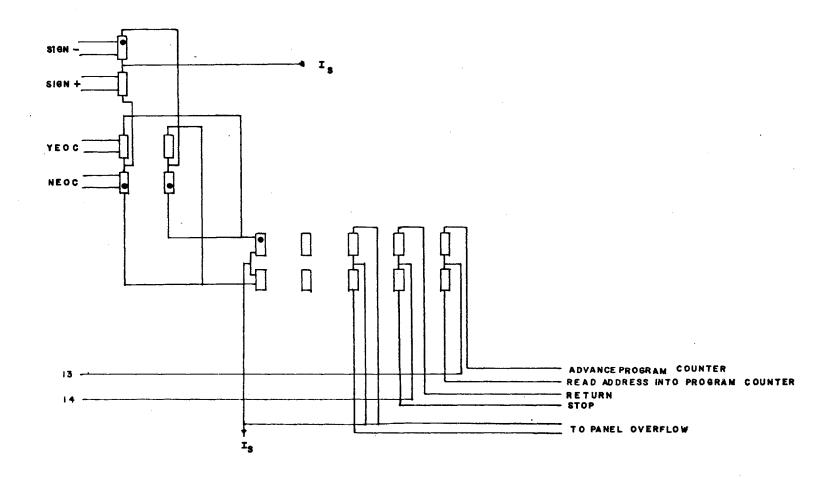

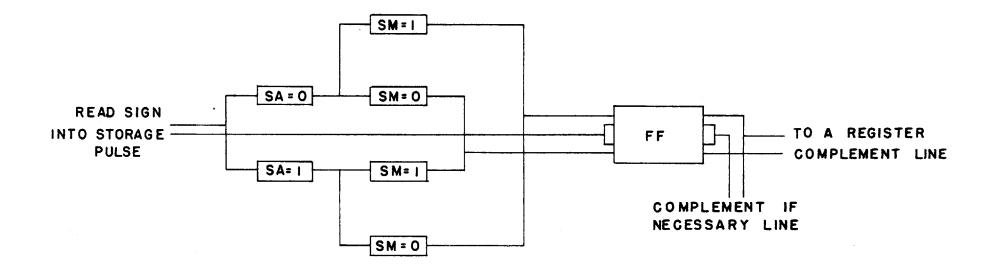

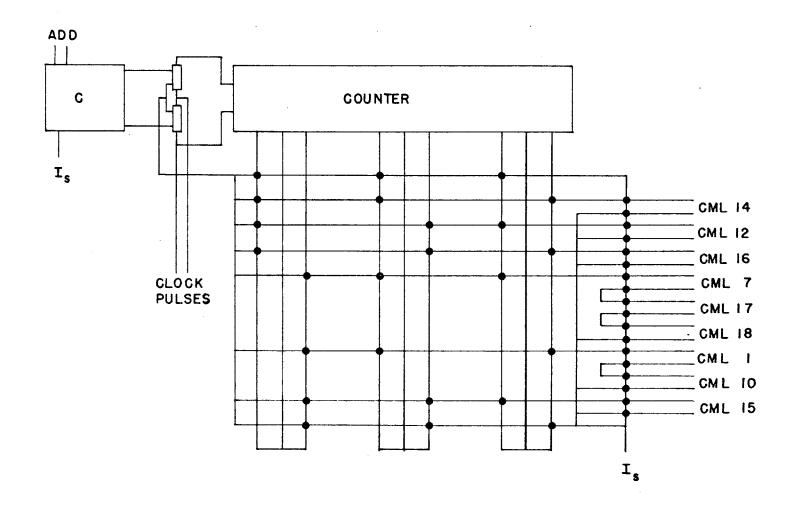

| P <sub>46</sub>              | Advance Instruction counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |