### WMM: a Resilient Weak Memory Model

by

Sizhuo Zhang

B.E., Tsinghua University (2013)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2016

© Massachusetts Institute of Technology 2016. All rights reserved.

January 27, 2016

Certified by ...... Arvind Johnson Professor of Computer Science and Engineering Thesis Supervisor

Accepted by ..... Leslie A. Kolodziejski

Chair, Department Committee on Graduate Students

#### WMM: a Resilient Weak Memory Model

by

#### Sizhuo Zhang

Submitted to the Department of Electrical Engineering and Computer Science on January 27, 2016, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

A good memory model should have a precise definition that can be understood by any computer architect readily. It should also be *resilient* in the sense that it should not break when new microarchitecture optimizations are introduced to improve singlethreaded performance. We introduce WMM, a new weak memory model, which meets these criteria. WMM permits all load-store reorderings except a store is not allowed to overtake a load. WMM also permits both *memory dependency speculation* and *load-value prediction.* We define the operational semantics of WMM using a novel conceptual device called *invalidation buffer*, which achieves the effect of out-of-order instruction execution even when instructions are executed in-order and one-at-a-time. We show via examples where memory fences need to be inserted for different programming paradigms. We highlight the differences between WMM and other weak memory models including Release Consistency and Power. Our preliminary performance evaluation using the SPLASH benchmarks shows that WMM implementation performs significantly better than the aggressive implementations of SC. WMM holds the promise to be a vendor-independent stable memory model which will not stiffe microarchitectural innovations.

Thesis Supervisor: Arvind Title: Johnson Professor of Computer Science and Engineering

### Acknowledgments

I would like to thank my advisor, Prof. Arvind, for his support and guidance that made this project possible. I also want to thank Prof. Daniel Sanchez for his help and advice on simulation experiments. Finally I want to acknowledge Muralidaran Vijayaraghavan for discussing many technical details with me.

# Contents

| 1        | Inti                 | roduction                                          | 13        |

|----------|----------------------|----------------------------------------------------|-----------|

|          | 1.1                  | Summary of Contributions                           | 15        |

|          | 1.2                  | Thesis Organization                                | 15        |

| <b>2</b> | $\operatorname{Rel}$ | ated Work                                          | 17        |

|          | 2.1                  | Sequential Consistency                             | 17        |

|          | 2.2                  | Weak Memory Models                                 | 17        |

|          | 2.3                  | Describing Memory Models                           | 18        |

| 3        | Def                  | ining Memory Models                                | <b>21</b> |

|          | 3.1                  | Abstracting the Instruction Set                    | 21        |

|          |                      | 3.1.1 Instantaneous Instruction Execution $(I^2E)$ | 22        |

|          | 3.2                  | Operational Semantics                              | 23        |

|          | 3.3                  | SC Model                                           | 24        |

|          | 3.4                  | TSO Model                                          | 24        |

| 4        | WN                   | /IM Model                                          | 29        |

|          | 4.1                  | Structure of WMM                                   | 29        |

|          | 4.2                  | Operational Semantics of WMM                       | 30        |

|          | 4.3                  | Reordering Axioms of WMM                           | 32        |

|          |                      | 4.3.1 Summarizing Reordering Axioms                | 34        |

|          | 4.4                  | Synchronization Instructions                       | 35        |

|          | 4.5                  | Well-synchronized Programs                         | 36        |

| <b>5</b> | $\mathbf{WN}$        | IM Processor Implementation                   | 37 |

|----------|----------------------|-----------------------------------------------|----|

|          | 5.1                  | Reorder Buffer (ROB)                          | 37 |

|          | 5.2                  | Store Buffer                                  | 39 |

| 6        | $\operatorname{Sep}$ | arating Memory Model from Cache Coherence     | 41 |

|          | 6.1                  | Specification of PCM                          | 41 |

|          | 6.2                  | Mapping Real Memory Systems to PCM            | 44 |

| 7        | Cor                  | nparison with other Weak Memory Models        | 47 |

|          | 7.1                  | Comparison with Release Consistency           | 47 |

|          |                      | 7.1.1 Comparing understandability             | 48 |

|          |                      | 7.1.2 Comparing implementation                | 50 |

|          |                      | 7.1.3 Summary                                 | 50 |

|          | 7.2                  | Comparison with Power                         | 50 |

| 8        | Cor                  | nparing Performance with Strong Memory Models | 53 |

|          | 8.1                  | Evaluation Methodology                        | 53 |

|          | 8.2                  | Evaluation Results                            | 55 |

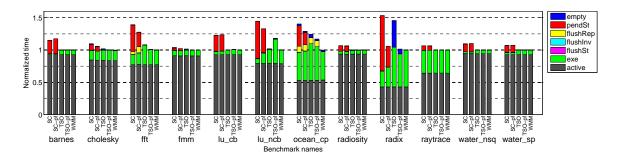

|          | 8.3                  | Performance: WMM <i>versus</i> SC             | 56 |

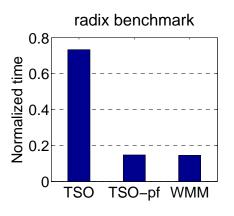

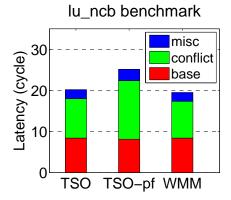

|          | 8.4                  | Performance: WMM <i>versus</i> TSO            | 56 |

| 9        | Cor                  | nclusion                                      | 59 |

# List of Figures

| 3-1 | General model structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3-2 | SC operational semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24 |

| 3-3 | TSO model structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 |

| 3-4 | TSO operational semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26 |

| 3-5 | Rule for dequeuing store buffer in PSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 |

| 4-1 | WMM model structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29 |

| 4-2 | WMM operational semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

| 4-3 | Dekker's algorithm in SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

| 4-4 | Dekker's algorithm in WMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33 |

| 4-5 | Message passing in SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 |

| 4-6 | Message passing in WMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |

| 4-7 | Load buffering in WMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 |

| 4-8 | Rule for execution of $RMW$ in WMM $\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hddots\hdddt\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\hdots\$ | 36 |

| 4-9 | Spin lock implementation for WMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

| 5-1 | Behavior by memory dependency speculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

| 5-2 | Behavior by load-value prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40 |

| 5-3 | Behavior by reordering loads to the same address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

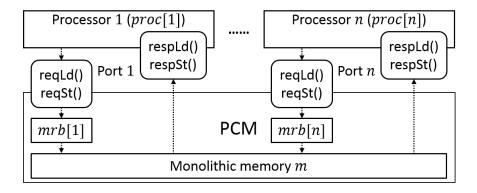

| 6-1 | PCM interface and structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

| 6-2 | PCM operational semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

| 7-1 | IRIW in SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 |

| 7-2 | IRIW in WMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 |

| IRIW in RC: wrong tagging                                         | 49                          |

|-------------------------------------------------------------------|-----------------------------|

| IRIW in RC: correct tagging                                       | 49                          |

| Normalized execution time and its breakdown at the commit slot of |                             |

| ROB                                                               | 55                          |

|                                                                   |                             |

| Stalls due to full store buffer                                   | 57                          |

|                                                                   | IRIW in RC: correct tagging |

# List of Tables

| 8.1 | Multiprocessor system configuration | 54 |

|-----|-------------------------------------|----|

| 8.2 | Core configuration                  | 54 |

# Chapter 1

## Introduction

The importance of memory models is difficult to deny; how can one specify an Instruction Set Architecture (ISA) if the meaning of load (Ld) and store (St) instructions is not precise. How can one give the semantics of a multithreaded programming language without specifying the behavior of shared writeable variables? Yet it is a topic that most architecture and language researchers, except those who work on the topic, want to avoid. Purely from a pragmatic point of view if the programmer or the compiler writer totally ignores the memory model issues, he or she is unlikely to pay a price for it; memory-model bugs are ephemeral and other bugs in parallel programming, such as races and deadlocks, manifest themselves much more readily [32]. Further to attribute a bug to the violation of a memory model is problematic because precise and understandable definitions of memory models are lacking [6, 42, 33]. This thesis presents WMM, a new weak memory model, with the goal of providing a vendor-independent memory model which is easy to understand and which is resilient to microarchitectural innovations.

It is important to recognize on the onset that unlike ISA, memory models were never "designed" by architects. Every ISA contains Ld and St instructions whose meaning is quite obvious in a uniprocessor setting or for a single-threaded program; Ld *a* returns the value stored by the most recent store to the address *a*. Every optimization in a uniprocessor preserves this abstraction. Instructions can be executed speculatively and out of order, store buffers and caches can be introduced, as long as the data dependencies are observed by the Ld and St instructions in a thread. None of these architectural mechanisms are visible to the user program. Another condition imposed by almost all general purpose ISAs is that the interrupts are *precise*, i.e. instructions are retired in order even if they are executed out of order. Precise interrupts are needed for the implementation of virtual memory and many other operating system services. It would be pretty messy to implement a system if it allowed stores to be retired out of order.

Unfortunately, the simple load-store abstraction breaks down in a system where multiple threads share a common global memory because a load in a thread can read the value written by a store in some other thread. So it is no longer sufficient to talk about simple data dependencies within a single thread. The earliest specification of a memory model was Sequential Consistency (SC) which specified how threads were allowed to interact with each other. SC specified that the program behavior must appear as if the instructions of various threads were executed one-by-one in an interleaved manner. It was clear from the earliest days that enforcing SC at the microarchitecture level downgraded performance unless aggressive speculation techniques requiring significant extra hardware cost were employed [22, 40, 27, 24, 17, 48, 14, 45, 30, 26. Worse yet, some of this cost had to be paid even when a program ran in a single-threaded mode. Currently most manufacturers expose weaker memory models than SC and provide instructions to enforce SC as needed. In spite of all the advances in implementation, the performance advantage of weaker models over SC is enough that the manufacturers are unlikely to give up on weaker memory models any time soon.

Ideally we want a memory model to have the following properties:

- Resilience: At the implementation level, the model should permit microarchitectural optimizations such as out-of-order execution, memory dependency speculation and load-value prediction [31, 21, 39, 38].

- 2. Simple description: The description of Ld and St instructions should be specified in terms of *instantaneous instruction execution* (I<sup>2</sup>E) using monolithic multi-

ported memory. So far such descriptions exist only for SC and Total Store Order (TSO).

- 3. Vendor independent: The memory model, like SC, should not depend upon the peculiarities of an ISA.

- 4. Completeness: Model should include *read-modify-write*, *memory fences* and other memory instructions needed to write parallel programs.

### 1.1 Summary of Contributions

The main contributions of this thesis are:

- 1. WMM, a new memory model that meets the above goals;

- 2. A novel technique for describing out-of-order execution using a conceptual device called *invalidation buffer* which achieves the effect of out-of-order instruction execution even when instructions are executed in-order;

- 3. Formal separation of memory model and cache coherence issues using *purely* coherent memory (PCM) abstraction;

- 4. A preliminary quantitative evaluation that shows that WMM implementation performs up to 33% and on average 14% better than the aggressive implementation of SC.

### 1.2 Thesis Organization

In Chapter 2 we discuss other weak memory models and the techniques used to describe them. We also survey aggressive implementations of SC. In Chapter 3 we explain Instantaneous Instruction Execution ( $I^2E$ ) and use it to describe SC and TSO. WMM is introduced in Chapter 4 where we give its operational semantics, and explain it further via programming examples. In Chapter 5, we show that WMM semantics are not violated even under very aggressive out-of-order and speculative implementations. In Chapter 6 we separate memory model issues from cache coherence. In Chapter 7 we analytically compare WMM against other weak memory models including Release Consistency and Power. In Chapter 8 we present our preliminary quantitative evaluation of WMM implementation on SPLASH-2x benchmarks [49, 1, 2] and contrast its performance with SC and TSO implementations with and without store prefetch. We finally offer some conclusions in Chapter 9.

## Chapter 2

## **Related Work**

### 2.1 Sequential Consistency

Sequential Consistency (SC) [29] is obviously the most intuitive memory model and has been used since nineteen sixties, even before the existence of multiprocessors (see Dijkstra [19]). However naive implementations of SC suffer from poor performance because the strong instruction ordering required by SC invalidates almost all optimizations for uniprocessor designs. Gharachorloo et al. [22] proposed load speculation and store prefetch to enhance the performance of SC. As the understanding of out-of-order and speculative microarchitectures has improved over the years, researchers have proposed more and more aggressive techniques to preserve SC [40, 27, 24, 17, 48, 14, 45, 30, 26]. Perhaps because of their hardware complexity and performance gap, no commercial microprocessor has adopted these techniques. Manufacturers have chosen instead to present a weaker memory model than SC as the memory interface.

### 2.2 Weak Memory Models

During the nineteen nineties a plethora of weak memory models emerged to characterize the memory systems of multiprocessor systems. SPARC architecture manual [46] specified Total Store Order (TSO), which relaxed the ordering between a younger load and an older store, and Partial Store Order (PSO), which further relaxed the ordering between two stores. Goodman [25] proposed Processor Consistency (PC), in which "the order of stores by two processors as observed by them and by a third processor may be different". Dubious et al. [20] defined Weak Consistency (WC), which required the shared variables in a program to be classified into synchronizing variables and non-synchronizing variables, and it only enforced ordering with respect to accesses to synchronizing variables. Gharachorloo et al. [23] presented Release Consistency (RC), a model closely related to WC but in which synchronization accesses were further partitioned into *acquire* and *release* accesses. Based on the type of the synchronization access (i.e. acquire or release), RC can further relax the ordering between the synchronization access and some other accesses. The memory models of Power [28] and ARM [11] as specified in the manuals were similar to WC, but orderings were enforced by fences (instead of synchronization accesses). The manual stated additional conditions such as "dependent loads will not be reordered", and such conditions have turned out to be both vague and imprecise. The tutorial by Adve et al. [3] and the tutorial by Maranget et al. [36] provide introductions to and relationships among above models.

### 2.3 Describing Memory Models

The lack of clarity in the definition of weak memory models has generated two types of research efforts to fix the problem. One type of effort has tried to develop a detailed *axiomatic semantics* to characterize a specific commercial memory model accurately [6, 8, 5, 33, 9]. Although the accuracy of the models has improved in the sense it conforms to empirical observations, often the models themselves have become too complicated to reason about. The second type of effort has been to describe the model by specifying its *operational semantics* [43, 42, 41, 7]. Namely, the model itself is described as an abstract machine, and the legal behaviors of the memory model had to be observable by executing programs on this abstract machine. The success of this approach depends upon the simplicity of the abstract machine. For example, the abstract machine for x86 includes a store buffer and results in an easyto-understand semantics [43]. In fact, Owens et al. prove the equivalence of the axiomatic and operational semantics of TSO [37]. We also define the semantics of WMM in a similar way by introducing a novel conceptual device called invalidation buffer.

Instead of describing memory models directly, Adve et al. [4] define a synchronization model called Data-Race-Free-0 (DRF0), which software programs should obey. In their proposal, the behavior of such programs is contained in SC. However, the model cannot specify the behavior of programs that do not obey DRF0. Our semantics do not require any labelling of memory access and is valid for all programs including the pathological ones.

A large amount of research has also been devoted to specifying and formalizing the memory models of high level languages: C++ [15, 13], Java [35, 16, 34], etc. This remains an active area of research because a widely accepted memory model for high-level parallel programming is yet to emerge.

There are also several other proposals on weak memory models: Shen et al. [44] introduce a model called Commit-Reconcile & Fences (CRF), in which loads and stores affect only the local cache, and **Commit** and **Reconcile** instructions are used to control the movement of values between local caches and the global memory. Arvind and Maessen [12] propose a weak memory model which is a combination of instruction reordering and monolithic memory. It specifies precise conditions for preserving store atomicity in program execution even when instruction reordering is permitted. In contrast, the WMM model presented in this thesis does not insist on the atomicity of stores at the program level.

# Chapter 3

## **Defining Memory Models**

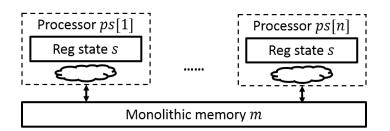

We will model multiprocessor systems as shown in Figure 3-1 to define memory models. The state of the system with n processors is defined as  $\langle ps, m \rangle$ , where m is an n-ported monolithic memory which is connected to the n processors and ps[i] $(i = 1 \dots n)$  represents the state of the  $i^{th}$  processor. Each processor contains a register state s, which represents all architectural registers, including both the general purpose registers and special purpose registers, such as PC. Specific memory models may add additional state elements, e.g. a *store buffer*, to each processor.

Figure 3-1: General model structure

### 3.1 Abstracting the Instruction Set

Memory model is always part of the ISA. However, we want our definitions of the memory models to be as generic as possible. For this reason, we introduce the concept of *decoded instruction set* (DIS). A *decoded instruction* contains all the information

of an instruction after it has been decoded and has read all source registers. To begin with our DIS has the following three instructions.

- (Nm, op, regs): instructions that do not access memory, such as ALU or branch instructions. op is the type of operation performed by the instruction, and regs represents all the necessary source register values and destination register names.

- $\langle Ld, a, dst \rangle$ : a load that reads memory address a and updates the destination register dst.

- $\langle \mathsf{St}, a, v \rangle$ : a store that writes value v to memory address a.

Later we will extend the DIS with fence and atomic read-modify-write instructions as needed.

Next we explain how we get to decoded instructions from the source or raw instructions.

#### 3.1.1 Instantaneous Instruction Execution (I<sup>2</sup>E)

To define memory models we restrict ourselves to the  $I^2E$  model where each instruction is executed instantaneously and the register state of each processor is by definition always up-to-date. Therefore we can define the following two methods to manipulate the register state s of a processor:

- decode(): fetches the next raw instruction and returns the corresponding decoded instruction based on the current register state s.

- execute(dIns, ldRes): updates the register state s (e.g. by writing destination registers and incrementing PC) according to the current decoded instruction dIns. The Ld instruction requires a second argument ldRes which should be the loaded value.

One limitation of  $I^2E$  is that it cannot be used to describe the semantics of an instruction set where the meaning of an instruction may depend upon a future store instruction. The memory models we discuss do not permit stores to overtake loads in execution.

After introducing our notation for operational semantics, we will give  $I^2E$  definitions of SC and TSO, and follow it by introducing our weak memory model WMM in Chapter 4.

### **3.2** Operational Semantics

The operational semantics is a set of *rules* that describe how the state of the processor and memory evolves as execution progresses. Each rule takes the following form:

$\frac{predicates (based on the current state)}{actions (to modify the current state)}$

If all *predicates* of a rule are *satisfied* then it can *fire* and atomically update model states according to the specified *actions*.

A predicate is either a *when* statement or a *pattern matching* statement. For example, when(b.empty()) means that the rule requires buffer b to be empty in order to fire. The *pattern matching* statement has the following form:

$$pattern = expression$$

For example, if we want to match the instruction returned by the decode() method to be a Nm instruction, we can write  $\langle Nm, op, regs \rangle = ps[i].s.decode()$ . Free variables op and regs will be assigned to appropriate values if the matching is successful.

We use " $\Leftarrow$ " to assign a new value to a state, and use semicolon ";" to separate statements written on the same line. If multiple rules can fire then our semantic model selects any one of those rules to execute. The final outcome may depend on the choice of rule selection, i.e. the rules are not necessarily "confluent".

To better understand the notation introduced above, we use it to specify two well-known strong memory models, i.e. SC and TSO.

### 3.3 SC Model

In SC model, a processor contains only the register state s. The operational semantics of SC is shown in Figure 3-2. The three rules correspond to the *instantaneous execution* of the three types of decoded instructions. In each rule, the decode() method first fetches and decodes a new instruction, and then the instruction is immediately executed and committed. Loads and stores in SC directly access the monolithic memory. For example, the SC-Ld rule executes a load by reading the monolithic memory. The three rules are disjoint, i.e. only one of them can be ready to fire. However, in a multi-processor setting there is still a choice regarding which processor we select for execution. The order of firing rules gives a total order of all loads and stores that is consistent with the program order on each processor. Even though SC permits different global Load-Store reorderings, it can be shown formally that reordering loads and stores on a single processor can take us out of the set of permitted behaviors.

**SC-Nm rule** (Nm execution).

$$\frac{\langle \mathsf{Nm}, op, regs \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{Nm}, op, regs \rangle)}$$

SC-Ld rule (Ld execution).

$\frac{\langle \mathsf{Ld}, a, dst \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{Ld}, a, dst \rangle, m[a])}$

SC-St rule (St execution).

$\frac{\langle \mathsf{St}, a, v \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{St}, a, v \rangle); \ m[a] \leftarrow v}$

Figure 3-2: SC operational semantics

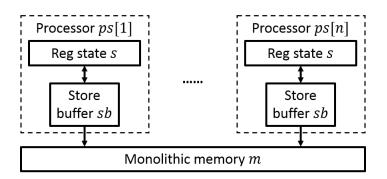

### 3.4 TSO Model

Figure 3-3 shows the states and structure of TSO model. In addition to register state s, each processor now contains a store buffer sb. sb is an unbounded buffer of (address, value) pairs, each representing a pending store. The following methods are

defined on sb:

- empty(): returns True when *sb* is empty.

- exist(a): returns True if address a is present in sb.

- getYoungest(a): returns the store data of the youngest store to address a in sb.

- enq(a, v): enqueues the (address, value) pair  $\langle a, v \rangle$  into sb.

- deq(): deletes the oldest store from sb, and returns its (address, value) pair.

Notice that the above deq() method not only updates the state of sb, but also returns a value. For this kind of *action-value* method, we use " $\leftarrow$ " to assign its return value to a free variable. For example,  $\langle a, v \rangle \leftarrow sb.deq()$  assigns the return value of deq() to pair  $\langle a, v \rangle$ .

Figure 3-3: TSO model structure

In order to enforce instruction ordering in accessing the newly added store buffer, we extend our instruction set with the memory fence instruction called **Commit** which flushes the local store buffer.

Figure 3-4 shows the operational semantics of TSO. The first four rules are instantaneous execution of four types of decoded instructions, while the last rule handles the interaction between the store buffer and the monolithic memory.

According to the TSO-Ld rule, Ld a first tries to read the youngest store to address a in the local store buffer, and if sb does not contain a then it reads the monolithic memory m. TSO adds new behavior to SC because buffering stores in sb essentially

**TSO-Nm rule** (Nm execution).

$$\frac{\langle \mathsf{Nm}, op, regs \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{Nm}, op, regs \rangle)}$$

**TSO-Ld rule** (Ld execution).

$\begin{array}{l} \langle \mathsf{Ld}, a, dst \rangle = ps[i].\mathsf{decode}() \\ v = & \mathbf{if} \ ps[i].sb.\mathsf{exist}(a) \ \mathbf{then} \ ps[i].sb.\mathsf{getYoungest}(a) \\ & \mathbf{else} \ m[a] \\ \hline & ps[i].s.\mathsf{execute}(\langle \mathsf{Ld}, a, dst \rangle, v) \end{array}$

**TSO-St rule** (St execution).

$$\frac{\langle \mathsf{St}, a, v \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{St}, a, v \rangle); \ ps[i].sb.\mathsf{enq}(a, v)}$$

**TSO-Com rule** (Commit execution).

$$\frac{\langle \mathsf{Commit} \rangle = ps[i].\mathsf{decode}(); \ \mathsf{when}(ps[i].sb.\mathsf{empty}())}{ps[i].s.\mathsf{execute}(\langle \mathsf{Commit} \rangle)}$$

**TSO-DeqSb rule** (dequeue store buffer).

$$\frac{\mathsf{when}(\neg ps[i].sb.\mathsf{empty}())}{\langle a,v\rangle \leftarrow ps[i].sb.\mathsf{deq}(); \ m[a] \leftarrow v}$$

Figure 3-4: TSO operational semantics

allows a load to be executed before an older store accesses the monolithic memory. Namely, TSO permits a load to overtake a store. The **Commit** instruction forces older stores to be flushed from store buffer into monolithic memory before any following instructions can execute. It should be noted that store atomicity [12] is broken at program level due to the store buffer even though all accesses on the monolithic memory are atomic.

**Enable Store-Store reordering:** We can introduce Store-Store reordering in TSO to form the related model known as Partial Store Order  $(PSO)^1$ . Only the TSO-DeqSb rule should be changed such that the store buffer can commit the oldest store of any address, instead of the oldest one of all stores, to the monolithic memory. Specifically, we use the following two methods instead of deq() to delete entries from store buffer sb:

<sup>&</sup>lt;sup>1</sup>The PSO model described here is somewhat different from SPARC PSO [46, 47] regarding fences.

- getAnyAddr(): returns any store address present in sb. If sb is empty, it returns

ε.

- removeOldest(a): deletes the oldest store to address a from sb, and returns its store data.

Thus we can dequeue stores for different addresses from the same store buffer to monolithic memory out of order, namely reordering stores. The substitute of the TSO-DeqSb rule is the PSO-DeqSb rule shown in Figure 3-5

| <b>PSO-DeqSb rule</b> (dequeue store buffer).                                                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------------|--|

| $\frac{a = ps[i].sb.getAnyAddr(); \text{ when}(a \neq \epsilon)}{v \leftarrow ps[i].sb.removeOldest(a); \ m[a] \leftarrow v}$ |  |

Figure 3-5: Rule for dequeuing store buffer in PSO

Comparing operational semantics and reordering axioms: I<sup>2</sup>E operational semantics with monolithic memory simply and accurately define a memory model and one can prove all the reordering axioms induced by the operational semantics. The converse is not true, given a set of reordering axioms it is quite difficult to know if all the relevant aspects of the operational semantics have been captured. For example, the reordering axiom of TSO (i.e. loads overtaking stores) cannot capture the subtlety in TSO operational semantics that a load may bypass data from the older store to the same address even if it overtakes the store. A lot of difficulty in understanding weak memory models arises from their complex axiomatic descriptions.

# Chapter 4

# WMM Model

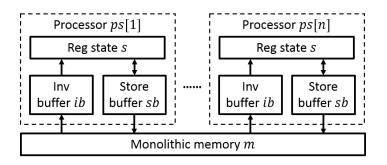

WMM, the weak memory model we are proposing, additionally allows Load-Load reordering compared to PSO. Despite the new reordering, we still want to describe WMM using I<sup>2</sup>E and monolithic memory for simplicity and independence of vendors. When two loads appear to be reordered, the younger one should read a stale value when it is executed in the I<sup>2</sup>E description. To model this behavior, we introduce a conceptual device called *invalidation buffer* to each processor, which holds stale values observable by the processor.

### 4.1 Structure of WMM

Figure 4-1: WMM model structure

The structure and states of WMM are shown in Figure 4-1. The change from PSO to WMM is to add an invalidation buffer ib to each processor. ib is an unbounded

buffer of  $\langle \text{address}, \text{value} \rangle$  pairs, each representing a stale memory value for an address that can be observed by the processor. The following methods are defined on *ib*:

- insert(a, v): inserts (address, value) pair (a, v) into *ib*.

- getRand(a, m): returns either a random stale value for address a present in *ib* or monolithic memory value m[a]. The choice is arbitrary.

- clear(): removes all contents from *ib* to make it empty.

- removeAddr(a): removes all (stale) values for address a from *ib*.

The insert function is used to store stale values into *ib*, and the getRand function allows loads to access stale values and get reordered with older instructions. The clear and removeAddr functions are called when ordering needs to be enforced.

Similar to the introduction of **Commit** fences in TSO, we extend our instruction set with the memory fence instruction called **Reconcile**, which flushes the local invalidation buffer (i.e. invoke *ib.clear()*), to enforce ordering by preventing younger loads from accessing stale values.

### 4.2 Operational Semantics of WMM

Figure 4-2 shows the operational semantics of WMM. The first five rules describe the instantaneous execution of the decoded instructions, while the last one commits stores from store buffer to the monolithic memory.

According to the WMM-Ld rule, a load first attempts to read from the local store buffer in the same way as TSO-Ld rule does. If this attempt fails, the load reads either a random stale value for address a from the local invalidation buffer or the monolithic memory m[a]. The stale value from the invalidation buffer enables the load to be reordered with older instructions. The choice between invalidation buffer and monolithic memory is arbitrary in order to enable reordering of loads on the same address, which will be discussed in detail in Chapter 5.1. In the WMM-Rec rule, the **Reconcile** fence flushes the invalidation buffer. WMM-Nm rule (Nm execution).

$\frac{\langle \mathsf{Nm}, op, regs \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{Nm}, op, regs \rangle)}$

WMM-Ld rule (Ld execution).

$\begin{array}{l} \langle \mathsf{Ld}, a, dst \rangle = ps[i].\mathsf{decode}() \\ v = & \mathbf{if} \ ps[i].sb.\mathsf{exist}(a) \ \mathbf{then} \ ps[i].sb.\mathsf{get}\mathsf{Youngest}(a) \\ & \mathbf{else} \ ps[i].ib.\mathsf{get}\mathsf{Rand}(a,m) \\ \hline & ps[i].s.\mathsf{execute}(\langle \mathsf{Ld}, a, dst \rangle, v) \end{array}$

WMM-St rule (St execution).

$\frac{\langle \mathsf{St}, a, v \rangle = ps[i].\mathsf{decode}()}{ps[i].s.\mathsf{execute}(\langle \mathsf{St}, a, v \rangle); \ ps[i].sb.\mathsf{enq}(a, v)}$

WMM-Com rule (Commit execution).

**WMM-Rec rule** (Reconcile execution).