# An Analysis of Network Routing and Communication Latency

| ARCHIVES |  |

|----------|--|

|----------|--|

by

# Yihao Lisa Zhang

MASE WERE BE ITS INSTITUTE OF THOMNOLOGY

JUN 25 1997

LIBRARIES

B.A. Wellesley College, Wellesley, MA (1993)

Submitted to the Department of Mathematics in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1997

| (C) | Massachusetts | Institute of | Technology | 7 1997. | All rig | ghts reserved | d. |

|-----|---------------|--------------|------------|---------|---------|---------------|----|

|-----|---------------|--------------|------------|---------|---------|---------------|----|

| Author                                                |

|-------------------------------------------------------|

| Department of Mathematics                             |

| May 9, 1997                                           |

| Certified by                                          |

| Frank Thomson Leighton                                |

| Professor of Applied Mathematics                      |

| Thesis Supervisor                                     |

| Accepted by                                           |

| Hung Cheng                                            |

| Chairman, Applied Mathematics Committee               |

| Accepted by                                           |

| Richard Melrose                                       |

| Chairman, Departmental Committee on Graduate Students |

| • |  | • |  |   |  |  |

|---|--|---|--|---|--|--|

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

| • |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  | • |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

|   |  |   |  |   |  |  |

# An Analysis of Network Routing and Communication Latency

by

## Yihac Lisa Zhang

Submitted to the Department of Mathematics on May 9, 1997, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

### **Abstract**

The thesis is divided into two parts. In the first part we describe methods for mitigating the degradation in performance caused by high latencies in parallel and distributed networks. For example, given any "dataflow" type of algorithm that runs in T steps on an n-node ring with unit link delays, we show how to run the algorithm in O(T) steps on any n-node bounded-degree connected network with average link delay O(1). This is a significant improvement over prior approaches to latency hiding, which require slowdowns proportional to the maximum link delay. In the case where the network has average link delay  $d_{\text{ave}}$ , our simulation runs in  $O(\sqrt{d_{\text{ave}}}T)$  steps using  $n/\sqrt{d_{\text{ave}}}$  processors, thereby preserving efficiency. We also show how to efficiently simulate an  $n \times n$  array with unit link delays using slowdown  $\tilde{O}(d_{\text{ave}}^{2/3})$  on a 2-dimensional array with average link delay  $d_{\text{ave}}$ . Lastly, we present results for the case in which large local databases are involved in the computation.

In the second part of the thesis we design schedules that provide per-packet delay guarantees in connection-oriented networks. We consider a network with arbitrary topology on which a set of sessions is defined. For each session i, packets are injected at a rate  $r_i$  to follow a predetermined path of length  $d_i$ . Due to limited bandwidth, one packet at a time may advance on a link. Packets therefore may experience end-to-end delays while traversing from their sources to their destinations. For the first time, we present an asymptotically-optimal schedule that achieves a delay bound of  $O(1/r_i + d_i)$  for every session-i packet, as long as the total rates add up to less than 1 on each link. An additional bonus is that only constant queues are needed at the switches. We also describe a simple distributed algorithm that, with high probability, delivers every session-i packet to its destination within  $O(1/r_i + d_i \log(m/r_{\min}))$  steps of its injection where  $r_{\min}$  is the minimum session rate, and m is the number of links in the network.

Thesis Supervisor: Frank Thomson Leighton Title: Professor of Applied Mathematics

# Acknowledgements

I am grateful to many people who have made this thesis possible. First, I would like to thank my advisor Professor Tom Leighton for the all the time and effort that he has devoted to my graduate study. Tom has been a source of intriguing problems and brilliant ideas, and he has never stopped being positive and encouraging, even during setbacks in my research. The discussions with him have been invaluable to me. I feel truly fortunate to have been his student. I would also like to thank Professors Michel Goemans and Dan Kleitman to serve on my thesis committee.

The work in this thesis is joint with several other people, including Matthew Andrews, Antonio Fernandez, Mor Harchol-Balter, Tom Leighton and Takis Metaxas. Thanks to them for their kind permission to put our joint results into my thesis. I also had the fortune to collaborate with Bill Aiello, Yonatan Aumann, Michael Bender, Sandeep Bhatt, Michel Goemans and K. R. Krishnan, although the work is not included here.

I am indebted to a graduate fellowship from the National Science Foundation that funded me during the past three years and an Applied Mathematics Fellowship from MIT that funded my first year. Additional support was provided by ARMY grant DAAH04-95-1-0607 and ARPA contract N00014-95-1-1246. I would also like to thank Takis for kindly sharing his Brachman-Hoffman research fellowship with me.

True friends are those who share good and bad times with me. I would like to thank Scott and Linda Dynes, Yue Hu and Juan Sanchez, Bin Hu, and Michael Bender for their friendship over the years. The Holdsworths, my adopted American family, deserve a special word of thanks. They have provided a warm, comfortable home and many memorable holidays in this foreign land. I shall always cherish their love and hospitality.

Many special thanks go to Matthew Andrews, my best friend and frequent coauthor. Together we have spent numerous weekends and late nights cranking out papers and catching deadlines. It is wonderful to collaborate with someone who is modest about himself, charitable to others and full of creative ideas. I have benefited greatly

from his intelligence, good humor, and unfailing support.

Finally, I owe my deepest gratitude to my close and loving family. My Jie-Jie is the best sister and a steady source of comfort. Without her love and understanding I would not have enjoyed my time in America as much. My father and late grand-mother have always been dedicated to my well-being. Their sacrifice ensured the best education for me in China, and their vision brought me to Wellesley and then to MIT. Their love will continue to give me strength through every stage of my life. I dedicate this thesis to them.

# To My Father and Grandmother

# **Contents**

| 1 | Int | roduction                                               | 13 |

|---|-----|---------------------------------------------------------|----|

|   | 1.1 | Hiding Latency for Parallel and Distributed Computation | 14 |

|   | 1.2 | Dynamic Packet Routing with Delay Guarantees            | 17 |

| I | Hi  | iding Latency                                           | 23 |

| 2 | Ove | erview                                                  | 25 |

|   | 2.1 | Model and Problem                                       | 25 |

|   | 2.2 | Results                                                 | 28 |

|   | 2.3 | A Related Scheduling Problem                            | 29 |

| 3 | Dat | aflow Model – Linear Arrays                             | 31 |

|   | 3.1 | Average Delay - An Upper Bound                          | 31 |

|   | 3.2 | A Better Upper Bound                                    | 33 |

|   | 3.3 | A Matching Lower Bound                                  | 35 |

|   | 3.4 | Simulating Linear Arrays on General Networks            | 36 |

| 4 | Dat | aflow Model – Two-Dimensional Arrays                    | 39 |

|   | 4.1 | An Analogue of the One-Dimensional Case                 | 39 |

|   | 4.2 | Improved Bounds for Worst-Case Delays                   | 43 |

|   |     | 4.2.1 Removing Useless Processors                       | 43 |

|   |     | 4.2.2 The Embedding                                     | 45 |

|   |     | 4.2.3 Bounding Monotone Path Length                     | 47 |

|    |     | 4.2.4   | Bandwidth                                      | 48  |

|----|-----|---------|------------------------------------------------|-----|

|    | 4.3 | Impro   | ved Bounds for Randomly-Arranged Delays        | 50  |

|    |     | 4.3.1   | Shortcuts and Edge Coloring                    | 51  |

|    |     | 4.3.2   | Large Delays                                   | 52  |

|    |     | 4.3.3   | Small Delays                                   | 54  |

| 5  | Dat | tabase  | Model                                          | 57  |

|    | 5.1 | A Spe   | cial Case                                      | 58  |

|    | 5.2 |         | thm OVERLAP                                    | 60  |

|    |     | 5.2.1   | Removing Useless Processors                    | 60  |

|    |     | 5.2.2   | Assigning Databases                            | 62  |

|    |     | 5.2.3   | The Simulation                                 | 63  |

|    |     | 5.2.4   | Bandwidth                                      | 67  |

|    |     | 5.2.5   | Improvements                                   | 67  |

|    | 5.3 | Simula  | ating Linear Arrays on General Networks        | 68  |

|    | 5.4 |         | ating 2-Dimensional Arrays on General Networks | 69  |

|    | 5.5 |         | Bounds                                         | 70  |

|    |     |         |                                                | ••• |

| II | D   | ynam    | ic Packet Routing                              | 75  |

| ^  | •   | •       |                                                |     |

| 6  |     | rview   | ° D. 11                                        | 77  |

|    | 6.1 |         | and Problem                                    | 77  |

|    | 6.2 |         | Bounds                                         | 78  |

|    | 6.3 |         | S,                                             | 79  |

|    | 6.4 | Genera  | dization to the Leaky-Bucket Injection Model   | 81  |

| 7  | Pre | liminar | ries                                           | 83  |

|    | 7.1 | Token   | Sequences                                      | 83  |

|    | 7.2 | Lemma   | as for Probabilistic Analysis                  | 86  |

|    | 7.3 | A Simp  | ple Centralized Scheduler                      | 88  |

|    |     | 7.3.1   | Template Size                                  | 88  |

|    |      | 7.3.2   | Token Placement                                    | 89  |

|----|------|---------|----------------------------------------------------|-----|

|    |      | 7.3.3   | Smoothing                                          | 90  |

|    | 7.4  | A Sim   | ple Distributed Scheduler                          | 91  |

| 8  | Out  | line of | the Optimal Result                                 | 95  |

|    | 8.1  | A Bou   | and of $O(c+d)$ for Static Routing                 | 95  |

|    | 8.2  | A Bou   | and of $O(1/r_i+d_i)$ for Dynamic Routing          | 97  |

|    | 8.3  | Param   | neter Definitions                                  | 101 |

| 9  | The  | Exist   | ence of an Optimal Schedule                        | 105 |

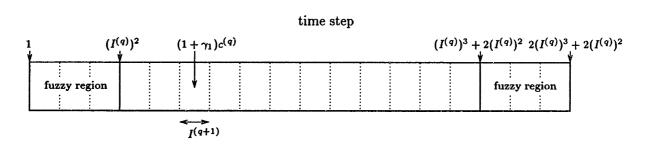

|    | 9.1  | An Ini  | tial Schedule $\mathcal{S}^{(0)}$                  | 105 |

|    | 9.2  | Frame   | -Refinement for Schedule $\mathcal{S}^{(q)}$       | 106 |

|    |      | 9.2.1   | A Useful Lemma                                     | 107 |

|    |      | 9.2.2   | The First Refinement Step for $\mathcal{S}^{(q)}$  | 109 |

|    |      | 9.2.3   | The Second Refinement Step for $\mathcal{S}^{(q)}$ | 111 |

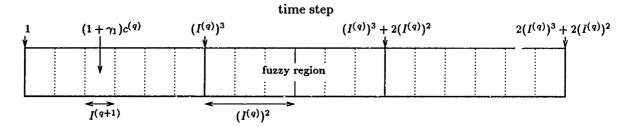

|    | 9.3  | Conve   | rsion for Schedule $\mathcal{S}^{(q)}$             | 115 |

|    |      | 9.3.1   | Discretization                                     | 116 |

|    |      | 9.3.2   | Delay Insertion                                    | 117 |

|    | 9.4  | Termin  | nation at Schedule $\mathcal{S}^{(\zeta)}$         | 120 |

|    | 9.5  | A Sche  | edule for the Original Network                     | 123 |

| 10 | The  | Const   | ruction of an Optimal Schedule                     | 127 |

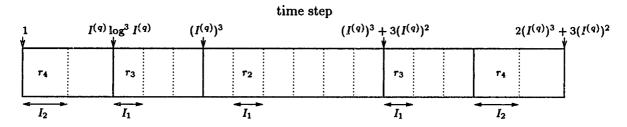

|    | 10.1 | Refine  | ment                                               | 128 |

|    |      | 10.1.1  | High Level Ideas                                   | 129 |

|    |      | 10.1.2  | One Iteration of Delay Assignment                  | 130 |

|    |      | 10.1.3  | Schedule $\mathcal{S}^{(1)}$                       | 133 |

|    |      | 10.1.4  | Schedule $\mathcal{S}^{(2)}$ , etc                 | 135 |

|    | 10.2 | Conve   | rsion                                              | 137 |

| 11 | Con  | clusion | 18                                                 | 141 |

|  |  | · |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

# Chapter 1

# Introduction

Recent technology advances have motivated a great deal of research in the fields of computation and communication. One general problem is network *latency*, i.e. the delay experienced by information as it travels from one location to another. Since latency has a direct impact on performance, we investigate this issue in two contexts. First, we study how to hide the effect of communication delay in high performance computing. Second, we present methods that ensure fast information delivery in communication networks.

Much effort is directed towards satisfying the increasing demands of parallel and distributed computing. One line of research is devoted to massively parallel processors (MPPs) that are dedicated to parallel computing, e.g. CRAY supercomputers and Connection Machines. Networks of workstations (NOWs) provide another platform for high performance computing [3]. The idea here is to connect desktop computers that are designed for small interactive jobs over a network. In this way, NOWs are capable of acting as a distributed supercomputer. Among various other issues such as job scheduling and load balancing, communication latency determines the efficiency of computing, especially when a NOW is involved. In Part I of this thesis, we devise methods for mitigating the impact of communication latency in parallel and distributed computing.

Many experts believe that the communication networks of the future will be based on Asynchronous Transfer Mode (ATM) technology, which will enable the integration of traffic with a wide range of characteristics within a single communication network [28]. A central problem in the design of ATM networks is that of providing quality-of-service (QoS) guarantees, such as the guarantees on bandwidth, delay, jitter and packet loss. These issues are particularly important if the networks support real-time traffic such as voice and video. Good scheduling algorithms can ensure fairness among the traffic streams and the efficient use of the network resources. In Part II of this thesis, we study the scheduling disciplines for connection-oriented packet-switched networks, e.g. ATM. We design schedules that efficiently deliver packets to their destinations, thereby providing end-to-end delay guarantees.

# 1.1 Hiding Latency for Parallel and Distributed Computation

In Part I of this thesis, we devise methods for mitigating the impact of latency in parallel and distributed computing. We focus on a model of processors interconnected by a bounded-degree fixed-connection network. The network may be either well-structured (such as an array) or unstructured (such as an arbitrary binary tree), and it may be either real or virtual. We assume that each link (or edge) in the network has a delay which models the latency associated with using the link. We also assume that the links have sufficient bandwidth and can be pipelined.

Most papers describing algorithms for parallel or distributed computation assume a model of computation in which all the links have unit delay. Such a model is nice to work with and it is realistic for some parallel machines, but not for most. In reality, there are often substantial delays associated with some or all of the links. These delays can be caused Ly long wires, links that are realized by paths that go through one or more intermediate switches, wires that are required to go off-chip or off-board, communication overheads, and/or by the method which is used to prepare a packet for entry into the network. Link delays are an even greater concern for distributed machines and NOWs. This is because some latencies can be very high (due to the

fact that some processors can be far apart physically) and also because the variation among latencies can be high (since some processors may be very close or even part of the same tightly-coupled parallel machine).

## **Traditional Approaches**

Since communication latency is an important factor in the performance of a parallel or distributed algorithm, several methods have been devised in an attempt to compensate for latency. The simplest of these methods is to slow down the computation to the point where the latency is accommodated. This approach is most commonly used at the circuit level, where the clock speed is set to be slow enough so that all of the data has time to reach its destination before the next step begins. This means that the circuit needs to be slowed down to accommodate the highest latency. Such an approach is clearly less than desirable in the context of a NOW with high-latency links.

An alternative approach is to organize the network in a hierarchical fashion so that the latencies are consistent with the hierarchy. For example, the CM-5 [1, 36] is organized into a fat tree and the KSR consists of two levels of nested rings. In both cases, the highest latency links are segregated into the top levels of the network hierarchy. This type of architecture works well for applications in which most of the computation is local since local computation can proceed using the low-level low-latency links. Only rarely, it is hoped, would the high latency links be needed. Thus, only certain steps of the computation would be slow. Unfortunately, this approach is not suitable for scenarios where the network is unstructured (which is often the case for a NOW) or when the underlying application requires frequent communications through the high-level links.

Redundant computation is another approach that has been used in the past [12, 30, 35] to hide the effects of latency. Here the idea is to avoid latency by recomputing data locally instead of waiting to receive it through a high-latency link.

Probably the most generally applicable method of hiding latency is the approach known as complementary slackness. The idea behind this approach is to load each

processor with enough work so that it stays productive while waiting for data to be supplied by the network. There are many implementations and incarnations of this method. For example, each processor in the CRAY YMP C-90 keeps busy by operating on a pipeline of 128 64-bit words. Processors on the HEP machine [53] swapped between unrelated threads while waiting for the data. The CM-1 and CM-2 were designed to simulate much larger virtual machines so that a single processor would perform the computation of many virtual processors [8, 57]. The technique also forms a critical component of Valiant's bulk synchronous model of parallel computing [59, 60] and it has been employed in several algorithms papers [5, 26, 30, 37, 50].

Unfortunately, in all of the preceding examples, it is incumbent on the programmer to provide the slackness or pipelining needed or to determine what part of the computation must be redundantly duplicated and by which processors to overcome the latencies in the network. Even in the scenario where a large virtual network is being simulated on a small parallel machine, it is incumbent on the programmer to find the parallelism necessary to efficiently implement the algorithm on a (potentially very large) virtual network.

### **Our Goal and Results**

The goal of our research is to devise automatic methods for hiding latency. Our approach falls within the broad class of methods based on complementary slackness, but does not require the programmer to provide slackness, pipelines, or greater parallelism in order to hide the latency. Rather, our methods attempt to find the slackness automatically. By automatically finding the slackness, we hope to allow the programmer to assume that there are uniform delays on each link of the network, thereby easing the task of writing code. Moreover, our methods will enable us to automatically convert a program that was written for a well-structured unit-delay machine into a program that will run with minimal degradation in performance on a network with potentially large and variable latencies, at least for certain classes of networks.

In this thesis, we devise automatic methods for latency hiding on rings, linear arrays and 2-dimensional arrays. These are the simplest networks for parallel algo-

rithms. Nevertheless, they support a rich class of interesting and important parallel algorithms. A large number of examples can be found in [34]. We consider the problem of implementing any "dataflow" type of algorithm that is designed for an n-processor guest ring with unit-delay links on an n-processor host ring with arbitrary link delays. A priori, it would seem that any such implementation would require slowdown  $d_{\text{max}}$  where  $d_{\text{max}}$  is the largest delay in the host. Indeed, this is the delay that would be incurred by many prior approaches. Among other things, we show how to accomplish a slowdown of  $O(\sqrt{d_{\text{ave}}})$ , where  $d_{\text{ave}}$  is the average delay. Efficiency is preserved here if we use only  $n/\sqrt{d_{\text{ave}}}$  processors to carry out the computation. The improvement is particularly impressive in the case when  $d_{\text{max}} \gg d_{\text{ave}}$ , which is often the case for NOWs. We also consider the problem of simulating an  $n \times n$  array with unit-delay links on an  $n \times n$  array with arbitrary delays, and achieve a slowdown of  $\tilde{O}(d_{\text{ave}}^{3/2})$ . When large databases are involved in the computation we use the method of redundant computation for latency hiding. We postpone the detailed description of the computation models and our results to Chapter 2.

# 1.2 Dynamic Packet Routing with Delay Guarantees

In Part II of this thesis we study scheduling disciplines for packet-switched networks. Modern integrated services networks, such as broadband integrated services digital networks (B-ISDN), carry a wide range of traffic types over a single communication network. Traffic streams with different characteristics have different requirements. For example, file transfer requires absolute accuracy, but it can tolerate relatively high end-to-end delay, i.e. the transfer time. On the other hand, for real-time services such as audio, video and interactive multi-player games, it is crucial to provide quality-of-service (QoS) guarantees such as minimum delay and jitter.

The choice of an appropriate scheduling discipline is key to achieving performance bounds. Mitra and Ziedins [39] note that a good scheduling scheme satisfies both fairness and efficiency constraints. The former guarantees a given grade of service to each application while the latter ensures the network resource is not underused. Keshav points out some common performance parameters in [28], including bandwidth, end-to-end delay, delay-jitter and loss. A bandwidth bound requires that each network user receives a minimum bandwidth from the network. End-to-end delay (or delay for short) is the total time from the packet injection until it is delivered to the desired destination. A delay bound requires fast delivery of the packets, which is particularly important for real-time services. A delay-jitter bound requires that the difference between the largest and the smallest delay is small. Finally, a loss bound requires that not many packets are lost. In practice, most current integrated-service networks provide only a bandwidth bound.

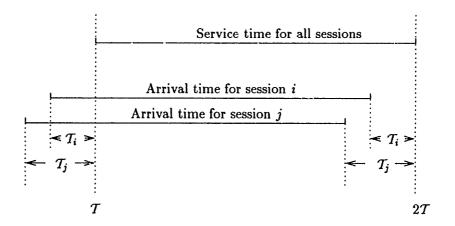

We concentrate on bounding the delay with no packet loss for connection-oriented networks, e.g. Asynchronous Transfer Mode networks (ATM). By connection oriented, we mean that a set of connections is predefined on the network, where each connection is specified by a route connecting a source node and a destination node. A user requests a share of a particular connection and injects a stream of packets along this connection continually. When traveling from its source towards its destination, a packet goes through a set of switches along its predetermined route. More than one packet may contend for the same switch simultaneously. Due to limited processing power, some packets may have to queue up at the switches while others are being serviced. In this way, packets experience end-to-end delay. Apart from delay bounds, we are also concerned with queue size at each switch due to limited buffer size.

In order to bound the delay and the queue size, it is necessary to impose certain usage restriction on the users. We can view the relationship between the users and the scheduler as a contract. As long as the users generate the traffic within the agreed-upon rates, the scheduler can in return meet the users' performance requirements, e.g. providing the delay guarantee. Leaky-bucket regulated traffic is one popular method to

<sup>&</sup>lt;sup>1</sup>We note the following. First, choosing routes for network connections is not a problem that we consider here. We focus on scheduling the motion of the packets once the routes are fixed. Second, we refer to our routing problem as *dynamic* since packets are injected over time. In contrast, in a *static* routing problem all packets are present initially.

restrict the users [14, 15, 58]. Here, a traffic stream is characterized by two parameters, a maximum burst size (or bucket size) and an average arrival rate. (Some papers characterize the traffic with one additional parameter, the maximum arrival rate.) Leaky-bucket regulated traffic is widely used in the literature, e.g. [18, 38, 48, 46, 47].

### Related Work

The design of scheduling disciplines so as to minimize the end-to-end delay is well studied. In this section we discuss some related work.

GPS and GPS-Based Schemes One simple scheme is called Generalized Processor Sharing (GPS), a generalization of the uniform Processor Sharing (PS) [29]. With PS, there is a separate FIFO queue for each contending user at a switch. During any time interval, a switch serves all the nonempty queues simultaneously at the same rate. This means that packets are serviced in infinitesimally small amounts by PS, i.e. it assumes a fluid model. GPS allows different users to have different service shares. A switch serves its nonempty queues in proportion to the service shares of the corresponding users. Since GPS uses an idealized fluid model that cannot be realized in the real world, various packet approximation algorithms of GPS have been proposed.

One simple emulation of GPS, proposed by Nagle, is called Weighted Round Robin [40]. In this approach, each of the nonempty queues is serviced in a round robin fashion proportional to the weight of the queue. Each time a queue is serviced a whole packet at the head of the queue is transmitted. Related work on round robin includes [23, 52].

Weighted Fair Queueing (WFQ), first proposed by Demers, Shenker and Keshav, is one of the best-known approximation schemes of GPS [17]. The intuition behind WFQ is to compute the times packets would complete service had GPS been used, and then serve packets in the order of these finishing times. Demers, et al. demonstrate the fairness of WFQ in [17]. A few congestion control algorithms are designed based on WFQ, e.g. [27, 51]. Some variants of WFQ are also studied. For example, Worst-case

Fair Weighted Fair Queueing by Bennett and Zhang [7], Self-Clocked Fair Queueing by Davin and Heybey [16] and Golestani [19].

Packet-by-packet Generalized Processor Sharing (PGPS), identical to WFQ, was proposed independently by Parekh and Gallager [46, 47]. They provide delay bounds for leaky-bucket regulated traffic streams. The first paper [46] proves that the delay bound of PGPS is within one packet transmission time of the bound of GPS on a single switch. The second paper [47] establishes end-to-end delay bounds for the case of multiple switches. In particular, if the *i*th connection has  $d_i$  switches and a packet arrival rate of  $r_i$ , then each packet injected along this connection can be delivered to its destination within  $2d_i/r_i$  steps. These results are among the best known on the subject. (See Chapter 6 for more details.)

Other related disciplines include the *Virtual Clock Multiplexing* by Zhang [61], Frame-based Fair Queueing by Stiliadis and Varma [55, 56] and Stop-and-Go Queueing by Golestani [20, 21, 22].

Delay-Insertion-Based Schemes An entirely different technique based on "delay-insertion" is also used to bound the end-to-end delay. The intuition here is that if each packet receives a large random delay initially, then the packets are sufficiently spread out so that they only need to wait a small number of steps at each successive switch. Rabani and Tardos [49] and Ostrovsky and Rabani [41] prove delay bounds that are essentially the sum of the minimum injection rate and the maximum number of switches per connection. Their schemes also allow a packet loss probability. (See Chapter 6 for more details.)

Many techniques for analyzing delay-insertion-based schemes are introduced by Leighton et al. in [31, 32] in the context of static routing, where all the packets are present in the network initially. We shall summarize some of these techniques in Chapter 8.

### **Our Results**

In this thesis we show, for the first time, how to design a schedule that guarantees asymptotically-optimal delay bounds for all connections. In particular, if the *i*th connection has  $d_i$  switches and a packet arrival rate of  $r_i$ , then each packet injected along this connection can be delivered to its destination in  $O(d_i + 1/r_i)$  steps. Our result presents two main improvements upon previous work. First, the multiplicative bound of Parekh et al. is enhanced to an optimal additive bound. Second, the bound expressed in terms of  $1/r_{\min} + d_{\max}$  due to Rabani et al. is enhanced to a connection-based delay guarantee of  $O(1/r_i + d_i)$  for each connection *i*. An additional bonus of our work is small queues for all edges. We defer the detailed description of our model and results to Chapter 6.

|  | ÷ |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

# Part I Hiding Latency

# Chapter 2

# **Overview**

### 2.1 Model and Problem

We consider the problem of simulating a network G with unit-delay links on a network H with arbitrary delays on its links. We refer to G as the guest and H as the host. Let  $g_1, g_2, \ldots$  be the processors of G and  $g_1, g_2, \ldots$  be the processors of H. We shall use pebbles to record the computations performed by the guest processors. In particular, pebble (i, t) represents the tth step of computation by processor  $g_i$ . In a simulation of G, H carries out the same step-by-step computation as G. In other words, H simulates G by computing every pebble created by G in an order that preserves the "dependency" of the pebbles. Our goal is to provide methods that would allow H to simulate G with a minimum amount of slowdown when G is used in a general purpose way. Two computation models are studied here, the dataflow model and the database model.

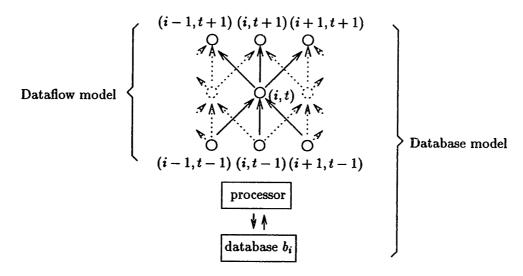

## **Dataflow Model**

In the dataflow model, each computation solely depends on the computation of the previous step. Creating a pebble (i,t) involves two time units. The first time unit is for communication, where  $g_i$  obtains pebbles of the form (j,t-1) from all its neighbors  $g_j$ . The second time unit is for computation, where  $g_i$  performs computation based

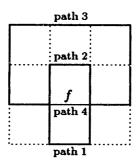

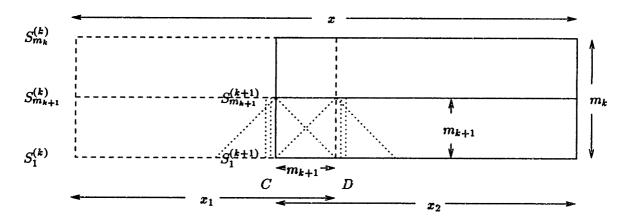

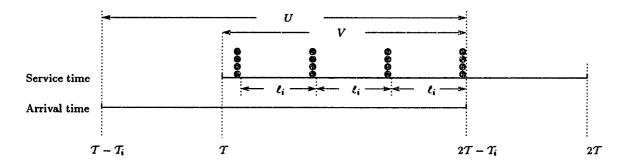

on pebbles (j, t-1) and records the result in pebble (i, t). Take an example of an n-node guest linear array. In 2T time steps, G creates  $n \times T$  pebbles, where pebble (i, t), for 1 < i < n and  $1 < t \le T$ , depends on pebbles (i - 1, t - 1), (i, t - 1) and (i + 1, t - 1). (See Figure 2-1.) Any host processor p can compute pebble (i, t) as long as p has the information in pebbles (i - 1, t - 1), (i, t - 1) and (i + 1, t - 1) either by directly computing these pebbles or by receiving them from neighboring processors.

The dataflow model is applicable to many computations such as matrix operations, Fourier transform, sorting, algorithms for computational geometry, etc. A large number of examples can be found in [34].

Figure 2-1: The computation pebbles created by a guest linear array.

### **Database Model**

In the database model each guest processor  $g_i$  has a potentially large local memory that may be accessed and updated by  $g_i$  during each step. We refer to the local memory of  $g_i$  as the database,  $b_i$ . Each computation not only depends on the computation of the immediate past but also the state of the database. For example, let G be a linear array. To create pebble (i,t),  $g_i$  first communicates with its neighbors, then performs computations based on pebbles (i-1,t-1), (i,t-1) and (i+1,t-1) and the current state of database  $b_i$ . Lastly,  $g_i$  updates database  $b_i$ . Hence, creating a pebble involves two time units as in the dataflow model, one for communication and

one for computation and recording.

In the database model, a pebble not only records the result of a computation but also the *changes* to the database incurred by this computation. To emphasize, a pebble does not contain a snapshot of the whole database but rather the changes incurred by one computation. Therefore, a pebble has small size and can be passed along links.

In order to simulate G on H, we assume that the initial contents of each database can be copied before the computation begins (thereby allowing redundant computations), but that the large size of a database makes it impractical to transmit a  $co_{\Gamma}y$  of a database through the network during the computation. Suppose processor p of H copies databases  $b_i$  and  $b_j$ , then p only has access to  $b_i$  and  $b_j$  and hence can only compute pebbles of the form (i,t) and (j,t) for  $t \geq 1$ . Moreover, if both processors p and p decide to copy p, then p and p each maintains a copy of p, and each looks up and updates its own copy. If p is to compute pebble (i,t) then p needs an updated copy of the database that includes all the changes incurred by the computations (i,t') for all t' < t. Hence, p must either have directly computed all the pebbles (i,t') or else have received the information from its neighbors.

Unlike the dataflow model, the database model captures a scenario where the computation performed by a processor depends on the state of a local memory or where part of the computation performed by a processor is to update its local memory. These situations could be critical in some applications involving a network of workstations.

### Bandwidth

The guest network G has unit bandwidth on each link. This allows each pebble to be passed along a unit-delay link of G in one time step. In our simulation we assume that the link bandwidth of the host network H is w. That is, P pebbles can be passed along a d-delay link of H in  $d + \lceil \frac{P}{w} \rceil - 1$  steps by pipelining. In many cases of our study, it is sufficient to assume that the host and the guest have comparable link bandwidth, i.e. w is a constant. However, in certain situations the bandwidth needs

to be  $\tilde{O}(\log n)$ . Otherwise, we pay an extra factor of  $\tilde{O}(\log n)$  in the slowdown. The details are discussed in Sections 4.2.4 and 5.2.4.

## 2.2 Results

Table 1 summarizes our results. In the table, n is the size of the guest,  $d_{ave}$  is the average delay of the host and "Bd-deg" stands for bounded-degree. The ratio of n and the slowdown is the size of the host since all the simulations are work efficient, i.e. it takes the guest and the host the same amount of work to compute the same result, where work is the product of the number of processors used and the running time.

|   | Guest             | Host           | Model    | Order of Slowdown                                   |

|---|-------------------|----------------|----------|-----------------------------------------------------|

| 1 | Ring/Linear Array | Bd-deg Network | Dataflow | $\sqrt{d_{ m ave}}$                                 |

| 2 | Ring/Linear Array | Bd-deg Network | Database | $\sqrt{d_{ m ave}}\log^3 n$                         |

| 3 | 2-D Array         | 2-D Array      | Dataflow | $d_{\mathrm{ave}}^{2/3} \log^{5/3} n$               |

| 4 | 2-D Array         | Bd-deg Network | Dataflow | $n^{1/4}(\sqrt{d_{\text{ave}}} + n^{1/4})$          |

| 5 | 2-D Array         | Bd-deg Network | Database | $n^{1/4} \log^3 n(\sqrt{d_{\text{ave}}} + n^{1/4})$ |

Table 1: Result Summary.

The first two results in Table 1 are proved in terms of linear arrays. An n-node unit-delay ring is essentially the same as an n-node unit-delay linear array, since the latter can simulate the former with a slowdown of 2 [34]. Result 1 is asymptotically optimal in some cases. In addition, we also have a constant-approximation algorithm for simulating rings and linear arrays in the dataflow model. Results 2 and 3 are optimal up to a polylogarithmic factor in some cases. Result 3 is for a worst-case model. When the delays on the host are randomly arranged, the bound can be improved to  $O(d_{\text{ave}}^{2/3})$ . Results 4 and 5 are easy generalizations of Results 1 and 2 respectively. Chapters 3 and 4 present latency hiding methods for the dataflow model. Chapter 5 concentrates on the database model.

The methods for latency hiding in the two computation models are substantially different. For example, we make heavy use of redundant computation in the database model, whereas redundancy is apparently not useful for the dataflow model.

Our bounds indicate that hiding latency in the database model is more difficult than in the dataflow model. Intuitively, this is because computation in the dataflow model is processor independent, and hence can be done by any processor with the information of the previous computation. In the database model computation can only be done by the processors with the right databases. One cannot afford to pass large databases across the links with limited bandwidth, because this will cause high slowdown. One also cannot afford to keep many copies of the databases, because memory is expensive and keeping every copy of the databases updated is difficult.

In Chapter 5, we also establish limits on the degree to which the high latency can be mitigated when each database is allowed a small number of copies. For example, if each database has only one copy, we show that the slowdown can be as much as  $d_{\text{max}}$  even if  $d_{\text{ave}}$  is a constant and the best simulation is used. When each database has at most two copies and each host processor copies a constant number of databases, we give an example of a host whose average delay is a constant, but for which the slowdown has a lower bound of  $\Omega(\log n)$ . These results demonstrate that it is easier to overcome latencies in dataflow types of computations than in computations that require access to large local databases.

# 2.3 A Related Scheduling Problem

The problem of latency hiding in the dataflow model can be viewed as the following scheduling problem. The pebbles created by the guest network together with their dependencies form a directed acyclic graph (dag), whose nodes represent computational tasks of equal execution time, and whose arcs represent precedence. All these tasks are to be computed by the processors in a given host network. If the same host processor computes two tasks of direct dependence, no communication cost is incurred. Otherwise, there is a communication cost between the two host processors

that compute these two tasks, and this cost is equal to the total delay between the processors in the host network. The goal here is to schedule the dag (with possible repetitions of the nodes) using the given host processors so as to minimize the makespan, i.e. the total time taken to execute all the tasks.

A variation of the above scheduling problem has been studied. Here, we are given any task dag (not necessarily created by a guest network in the dataflow model). All the arcs in the dag are associated with a fixed quantity that indicates the communication cost. Note that, unlike our problem, the communication cost here is the same for any processor-pair. In [44] Papadimitriou and Ullman studied an  $n \times n$  grid dag (which they called a diamond dag). They showed a nontrivial time-communication tradeoff and gave an asymptotically-optimal schedule. Their result was similar to the special case of our Result 1 stated in Section 2.2 where all the link delays in our host network are the same. In [45] Papadimitriou and Yannakakis presented a 2-approximation algorithm for general dags where an unlimited number of processors could be used. For well-known families of dags such as the full binary tree, the diamond dag and the fast Fourier transform, only a finite number of processors were needed and their approximation algorithms were optimal (or near-optimal). Redundant computation was used in [45].

Dag scheduling has been studied in other papers, including [2, 11, 13, 24, 25, 42, 43]. Some variations of the problem include the cases in which the dags are limited to certain topologies, the task nodes require different execution time, arcs require different communication times and/or processors have different processing powers.

# Chapter 3

# Dataflow Model – Linear Arrays

We begin our presentation with the methods for hiding latency in linear arrays. Our basic approach is to transfer a process that involves a two-way communication to a process that involves one-way communication only. (This idea is also essential for simulating 2-dimensional arrays in Chapter 4.) We present an asymptotically tight bound on the slowdown for linear arrays. All the results for linear arrays are applicable to rings.

# 3.1 Average Delay – An Upper Bound

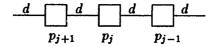

Let the network G be an n-processor guest linear array with unit delay on all the edges. Let the network H be an n-processor host linear array with arbitrary delays, where  $d_i$  is the delay on the ith edge of H. As discussed in Section 2.1, in 2T time steps G creates  $n \times T$  pebbles, where pebble (i,t), for 1 < i < n and  $1 < t \le T$ , depends on pebbles (i-1,t-1), (i,t-1) and (i+1,t-1). We first present algorithm STRIPE in which H simulates G with a slowdown of  $O(d_{ave})$ , where  $d_{ave} = \sum_{k=1}^{n-1} d_k/(n-1)$  is the average delay of H.

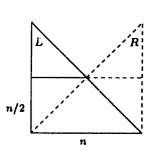

Consider the first n/2 rows of pebbles created by G. Let L be the triangle formed by pebbles (i,t), where  $i+t \leq n+1$ . Let R be the triangle formed by pebbles (i,t), where  $i \leq t$ . (See Figure 3-1.) In STRIPE, H first simulates the bottom half of L and then the bottom half of R. At this point every pebble in the first n/2 rows is

Figure 3-1: (Left) Triangles L and R. (Right) Algorithm STRIPE. Each slanted stripe is simulated by one processor of H. Arrows correspond to communications. Dashed lines correspond to the delays  $d_i$  encountered by communications.

simulated. If the entire computation of G is partitioned into groups each of which consists of n/2 rows of pebbles, then H can repeat the process and simulate every group in a similar manner.

To simulate the bottom half of L, the computation pebbles of G are divided into n slanted stripes, and each processor of H simulates one stripe. (See Figure 3-1.) In particular, processor  $p_i$  of H simulates a stripe consisting of pebbles (i-t+1,t), for  $1 \le t \le i$  and  $t \le n/2$ . Note that in the original computation by G, processor  $g_i$  depends on both  $g_{i-1}$  and  $g_{i+1}$ . However, in the simulation by H  $p_i$  depends on  $p_{i-1}$  and  $p_{i-2}$ . Hence, STRIPE transforms a process that involves two-way communication into a process that involves only one-way communication.

**Lemma 3.1.1** Processor  $p_i$   $(1 \le i \le n)$  is able to compute pebble (i-t+1,t) at step  $t + \sum_{k=1}^{i-1} d_k$ .

**Proof:** We use induction on i. The base case for  $p_1$  is obvious. Pebble (i-t+1,t) depends on pebbles (i-t,t-1), (i-t+1,t-1) and (i-t+2,t-1), which are computed by processors  $p_{i-2}$ ,  $p_{i-1}$  and  $p_i$  respectively. By induction these three pebbles are computed at step  $(t-1) + \sum_{k=1}^{i-3} d_k$ ,  $(t-1) + \sum_{k=1}^{i-2} d_k$  and  $(t-1) + \sum_{k=1}^{i-1} d_k$  respectively. It follows that (i-t+1,t) can be computed at step  $t+\sum_{k=1}^{i-1} d_k$ .  $\square$

Hence, pebbles (i+1,n/2), for  $0 \le i \le n/2$ , are computed at steps  $n/2 + \sum_{k=1}^{i+n/2-1} d_k$ , and so the bottom half of L is simulated in  $n/2 + \sum_{k=1}^{n-1} d_k$  steps by

H. The bottom half of R is simulated in a similar manner after processor  $p_n$  passes pebbles (n-t+1,t), for  $1 \le t \le n/2$ , to appropriate processors. Note that the intersection of R and L is only computed once. Thus, H has completed simulating the first n/2 rows of pebbles created by G. The next n/2 and every subsequent n/2 rows of pebbles can be simulated in a similar manner. Therefore, the slowdown is upper bounded by,

$$s = 2 \frac{n/2 + \sum_{k=1}^{n-1} d_k}{n} = O(d_{\text{ave}}).$$

# 3.2 A Better Upper Bound

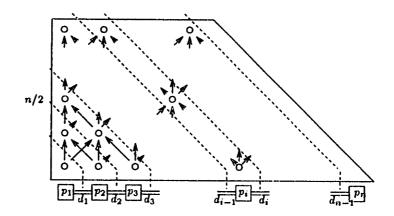

To get a better upper bound on the best achievable slowdown, we use the idea of "complementary slackness" in our new algorithm called FATSTRIPE. Each host processor is loaded with enough work to balance out the communication time. Suppose FATSTRIPE uses an interval of m processors to carry out the simulation. For simplicity, assume that this interval consists of processors  $p_1, \ldots, p_m$ . The bottom half of L is divided into m slanted stripes, each of which has width  $\ell = n/m$ . Again,  $p_i$  computes every pebble in stripe i. (See Figure 3-2.) Within each stripe i,  $p_i$  first computes all the pebbles in the bottom row and then moves up.

Figure 3-2: Algorithm FATSTRIPE. Processor  $p_i$  simulates stripe i which has width  $\ell = n/m$ . (In the figure,  $\ell = 4$ .) All the pebbles in stripe i are computed by time step  $\ell n/2 + \sum_{k=1}^{i-1} d_k$ .

**Lemma 3.2.1** Processor  $p_i$  finishes simulating stripe i by step  $\ln/2 + \sum_{k=1}^{i-1} d_k$ .

**Proof:** We inductively show that  $p_i$  can compute the pebbles in the xth row of stripe i by time step  $\ell x + \sum_{k=1}^{i-1} d_k$ . The base of the induction holds trivially for i=1 and x=1, since processor  $p_1$  does not depend on other processors and pebbles in the first row do not depend on other pebbles. Let us consider the pebbles on the (x+1)st row of stripes i+1, for  $x \geq 1$  and  $i \geq 1$ . These pebbles could only depend on pebbles on the xth row of stripe i-1, i and i+1, which can be computed by processors  $p_{i-2}$ ,  $p_{i-1}$  and  $p_i$  by steps  $\ell x + \sum_{k=1}^{i-3} d$   $\sum_{k=1}^{i-2} d_k$  and  $\ell x + \sum_{k=1}^{i-1} d_k$  respectively by induction. Hence,  $p_i$  is able to receive all the information necessary to compute its (x+1)st row by step  $\ell x + \sum_{k=1}^{i-1} d_k$  and therefore finish computing the (x+1)st row by step  $\ell (x+1) + \sum_{k=1}^{i-1} d_k$ . Since each stripe contains at most n/2 rows,  $p_i$  finishes simulating stripe i by step  $\ell n/2 + \sum_{k=1}^{i-1} d_k$ .

Hence, the slowdown is  $O(n/m + \sum_{k=1}^{m-1} d_k/n)$  in simulating the first n/2 rows of pebbles. All the subsequent n/2 rows can be simulated in a similar manner. To minimize the slowdown, FATSTRIPE uses the interval I (with  $m_I$  processors and  $d_I$  average delay) that minimizes the quantity  $n/m_I + d_I m_I/n$ . Therefore,

**Theorem 3.2.2** FATSTRIPE achieves a slowdown of  $\min_{\text{intervals } I} O(n/m_I + d_I m_I/n)$ .

In the case when  $\sqrt{d_{\text{ave}}} \leq n$ , there exists an interval I with  $M_I = n/\sqrt{d_{\text{ave}}}$  processors and average delay  $d_I \leq d_{\text{ave}}$ . Theorem 3.2.2 implies that the slowdown is  $O(\sqrt{d_{\text{ave}}})$  when  $M_I$  simulates G. In the case when  $\sqrt{d_{\text{ave}}} > n$  a single host processor is used to carry out the simulation, which incurs a slowdown of  $n = O(\sqrt{d_{\text{ave}}})$ . The simulation is work-efficient in both cases. Therefore,

Corollary 3.2.3 FATSTRIPE efficiently simulates G on H and achieves a slowdown of  $O(\sqrt{d_{ave}})$ , where  $d_{ave}$  is the average delay of H.

Bandwidth Let us consider the effect of bandwidth on the slowdown. In FAT-STRIPE as long as the stripe width is at least 2, then pebbles cross the edges one at a time by using pipelining. In STRIPE (i.e. FATSTRIPE with stripe width 1) at most two pebbles may cross an edge at the same time. Therefore, it is sufficient for the host bandwidth to be twice as large as that of the guest bandwidth. Otherwise, we pay another factor of 2 in the slowdown.

## 3.3 A Matching Lower Bound

We proceed to show that the upper bound,  $\min_I O(n/m_I + d_I m_I/n)$ , in Theorem 3.2.2 is asymptotically tight by showing that  $\min_I \max\{n/2m_I, d_I m_I/2n\}$  is a lower bound on the best achievable slowdown even if we allow redundant computation. Note that with redundant computation, a pebble may be computed by several host processors. This technique makes it more likely for the host to simulate the guest efficiently. However, we show below that redundancy does not help in this case.

**Lemma 3.3.1** The top pebble, (1,n) of triangle L, cannot be computed at a time step earlier than

$$\tau = \min_{\text{intervals } I} \max\{n^2/2m_I, d_I m_I/2\}.$$

**Proof:** We consider how the pebbles in L are computed in some simulation of G by H. In particular, we build a ternary tree T to keep track of the processors that have "effectively" computed the pebbles in L. The top pebble (1, n) has to be computed by some processor of H. Call this processor q. (If more than one processor of H has computed (1, n), then we pick any one of them to be q.) We label the root of tree T with  $q^{(1,n)}$ . Let u be a processor that has computed (1, n-1) and has passed this information to q, and v be a processor that has computed (2, n-1) and has passed this information to q. (Note that other processors may compute (1, n-1)and (2, n-1). We are only concerned with processors that pass information to q.) Now label the children of  $q^{(1,n)}$  with  $u^{(1,n-1)}$  and  $v^{(2,n-1)}$ . We proceed to construct the children of  $u^{(1,n-1)}$  and  $v^{(2,n-1)}$ . In general, node  $a^{(i,t)}$  in T has children  $b^{(i-1,t-1)}$ ,  $c^{(i,t-1)}$  and  $d^{(i+1,t-1)}$  if the following holds. Processors a, b, c and d compute pebbles (i,t), (i-1,t-1), (i,t-1) and (i+1,t-1) respectively, and a receives the values ef (i-1,t-1), (i,t-1) and (i+1,t-1) from b, c and d before a is able to compute (i,t). The leaves of T are nodes of the form  $p^{(i,1)}$ . The important observation is the following. If  $p^{(i,t)}$  is a node in T, then information has to be passed from processor p to q in H. The total delay from p to q lower bounds the number of steps in the simulation.

Let J be the smallest interval that contains all the processors appearing in tree T. If processors x and y are at the two ends of J, then there exist two nodes of the form  $x^{(i_x,t_x)}$  and  $y^{(i_y,t_y)}$  in T. Hence, information has to be passed from x and y to q in H. This takes at least  $d_J m_J/2$  steps, and pebble (1,n) therefore cannot be computed at a step earlier than  $d_J m_J/2$ . By a work argument, (1,n) cannot be computed before step  $n^2/2m_J$ . Hence, (1,n) cannot be computed at a step earlier than  $\tau = \min_I \max\{n^2/2m_I, d_I m_I/2\}$ .

It follows that the slowdown in simulating triangle L is lower bounded by  $\tau/n$ . By a similar argument to Lemma 3.3.1 none of the pebbles (i,n), for  $1 \le i \le n$ , can be computed at a time step earlier than  $\tau$ . By repeating this argument the first kn rows of G cannot be simulated in time less than  $k\tau$ . Therefore, we obtain,

**Theorem 3.3.2** The slowdown of any simulation of an n-node guest linear array G by a host linear array H is lower bounded by  $\min_I \Theta(n/m_I + d_I m_I/n)$ , where I is a subarray of H and has  $m_I$  processors and average delay  $d_I$ . Hence, FATSTRIPE is optimal up to a constant factor.

# 3.4 Simulating Linear Arrays on General Networks

We now consider simulating a linear array G on a general n-node network H with average delay  $d_{ave}$ . We first embed a linear array  $\mathcal{H}$  in H and then use  $\mathcal{H}$  to carry out the simulation of G.

**Lemma 3.4.1** Let H be a connected n-node network with arbitrary topology. Then an n-node linear array H can be one-to-one embedded in H such that every edge of H is used at most twice in H.

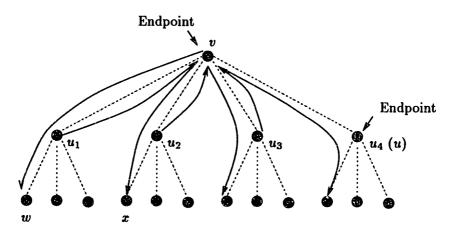

**Proof:** Our proof follows the approach of Theorem 3.15 in [34, page 470]. It is sufficient to embed a linear array  $\mathcal{H}$  in a spanning tree of  $\mathcal{H}$ . The proof proceeds by induction on the height of the tree with the following inductive hypothesis. For any child u of the root v, there is a one-to-one embedding of a linear array in the tree such that v and u form two endpoints of the array, the edge uv is used at most once

and all other edges of the tree are used at most twice. (Note that we treat all the edges as undirected.)

Let T be any spanning tree of H. The base of the induction in which T is a single node, i.e. the height is 0, is trivial. Otherwise, let v be the root of T and u be any child of v. We label the children of v as  $u_1, \ldots, u_d$ , and assume  $u = u_d$  without loss of generality. We place the first node of the linear array at v, and place the second node of the array at any child w of  $u_1$  (if any) using edges  $vu_1$  and  $u_1w$ . Next, we inductively place the nodes of the array in each node of the subtree of T rooted at  $u_1$ , making sure that the last node is placed at  $u_1$ , the edge  $u_1w$  is used at most once and that all other edges in the subtree are used twice. Therefore, edge  $u_1w$  is used at most twice in total.

We place the next node of the linear array at any child x of  $u_2$  (if any), using edges  $u_1v$ ,  $vu_2$  and  $u_2x$ . Again, we inductively place nodes of the linear array in the subtree rooted at  $u_2$  such that  $u_2$  and x are endpoints. We continue in this fashion. At the last subtree rooted at u, we enter this subtree at a child of u (if any) and exit at u. This completes the embedding of the linear array. Our lemma follows from the observation that the linear array has endpoints v and u, edges  $vu_1$ , ...,  $vu_{d-1}$  are used twice and  $vu_d$  is used once. (See Figure 3-3.)

Figure 3-3: Embed a linear array one-to-one in a tree such that each tree edge is used at most twice. The dotted lines indicate tree edges and the solid lines indicate array edges.

Since H has n nodes and degree  $\delta$ , H has at most  $\delta n/2$  edges and therefore the total delays on all edges of H is at most  $\delta d_{\text{ave}}n/2$ . By Lemma 3.4.1,  $\mathcal{H}$  uses each edge of H at most twice. Hence, the total delays on all edges of  $\mathcal{H}$  is at most  $\delta d_{\text{ave}}n$ , and the average delay of  $\mathcal{H}$  is at most  $\delta d_{\text{ave}}$ . By Corollary 3.2.3,  $\mathcal{H}$  can simulate G with a slowdown of  $O(\sqrt{\delta d_{\text{ave}}})$ . When H has bounded degree, i.e.  $\delta = O(1)$ , we have,

**Theorem 3.4.2** A bounded-degree host network with average delay  $d_{ave}$  can efficiently simulate an n-processor guest linear array with a slowdown of  $O(\sqrt{d_{ave}})$ .

Theorem 3.4.2 does not hold when H has unbounded degree. Consider the following example. Let H be a linear array of  $\sqrt{n}$  cliques, in which each clique contains  $\sqrt{n}$  nodes. If a clique edge has delay 1 and an edge connecting two adjacent cliques has delay n, then H has  $d_{ave} < 4$ . Suppose m connected cliques are used to simulate n steps of G. Lemma 3.3.1 implies a slowdown of  $\min_m \max\{\sqrt{n}/2m, m/2\}$  in simulating every n steps of computation by the guest. The first term follows from a work argument, since  $m\sqrt{n}$  processors are in m cliques. The second term comes from the communication delay, since a linear array embedded in these m connected cliques has a total delay of at least mn. Hence, the slowdown is at least  $\min_m \max\{\sqrt{n}/2m, m/2\}$ , which is  $\Omega(n^{1/4})$ , whereas the average delay is a constant.

# Chapter 4

## Dataflow Model –

# Two-Dimensional Arrays

In this chapter we present methods for hiding latency in 2-dimensional arrays. The analysis here is substantially more complex than that for the 1-dimensional case. We focus on simulating a 2-dimensional array on a 2-dimensional array. Section 4.1 generalizes the approach for the linear arrays. Section 4.2 introduces some new mechanism to improve the bound. Section 4.3 discusses the case when the delays are randomly arranged.

## 4.1 An Analogue of the One-Dimensional Case

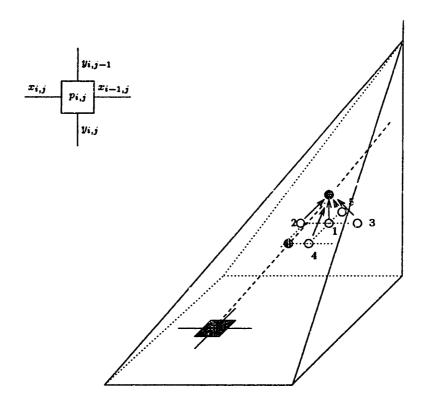

Let the guest network G be an  $n \times n$  2-dimensional array with unit delay on all the edges. Let the host network H be an  $n \times n$  2-dimensional array with arbitrary delays. Let  $x_{i,j}$  be the delay between processors  $p_{i,j}$  and  $p_{i+1,j}$  of H for  $1 \le i \le n-1$  and  $1 \le j \le n$ , and let  $y_{i,j}$  be the delay between  $p_{i,j}$  and  $p_{i,j+1}$  of H for  $1 \le i \le n$  and  $1 \le j \le n-1$ . The tth step of computation by processor  $g_{i,j}$  of G is recorded in pebble (i,j,t). In 2T steps, G creates  $n \times n \times T$  pebbles, where pebble (i,j,t), for 1 < i,j < n and  $1 < t \le T$ , depends on (i-t+1,j-t+1,t-1), (i-t,j-t+1,t-1), (i-t+2,j-t+1,t-1), (i-t+2,j-t+1,t-1).

Consider the first n/2 steps of computation by G. We define four pyramids  $P_1$ ,  $P_2$ ,

$P_3$  and  $P_4$  analogous to the left and right triangles in the linear array case. All four pyramids have the square, defined by vertices (1,1,1), (1,n,1), (n,1,1) and (n,n,1), as their bases. The top vertices of  $P_1$ ,  $P_2$ ,  $P_3$  and  $P_4$  are (1,1,n), (1,n,n), (n,1,n) and (n,n,n) respectively. Note that the bottom half of the four pyramids contain all the pebbles created by G for the first n/2 steps of computation.

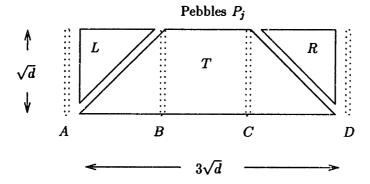

Algorithm 2D-RAY is a 2-dimensional analogue of STRIPE. To simulate the first n/2 steps of computation of G, 2D-RAY simulates  $P_1$ ,  $P_2$ ,  $P_3$  and  $P_4$  one by one. Pyramid  $P_1$  is divided into  $n^2$  rays, each of which is simulated by one processor of H. In particular, processor  $p_{i,j}$  of H simulates ray  $R_{i,j}$ , consisting of pebbles (i-t+1,j-t+1,t), for  $1 \le t \le \min\{i,j,n/2\}$ . (See Figure 4-1.) When every pebble for the first n/2 steps of computation of G is simulated, 2D-RAY repeats the process and simulates the next n/2 steps of computation. In the following we bound the slowdown in terms of the total delay on monotone paths, where a monotone path travels in two directions, up and right. Let the length of a path be the total delay on the path, and let  $D_{i,j}$  be the length of the longest monotone path from processor  $p_{1,1}$  to  $p_{i,j}$  in H. We have,

**Lemma 4.1.1** Processor  $p_{i,j}$  of H is able to compute pebble (i-t+1, j-t+1, t) at step  $D_{i,j} + t$ .

**Proof:** We use induction on the indices (i,j) of the processors. The base of the induction for  $p_{1,1}$  is obvious. Pebble (i-t+1,j-t+1,t) depends on pebbles (i-t+1,j-t+1,t-1), (i-t,j-t+1,t-1), (i-t+2,j-t+1,t-1), (i-t+1,j-t,t-1) and (i-t+1,j-t+2,t-1), which are computed by processors  $p_{i-1,j-1}, p_{i-2,j-1}, p_{i,j-1}, p_{i-1,j-2}$  and  $p_{i-1,j}$  respectively. (See Figure 4-1.) By induction, these five pebbles are computed at steps  $D_{i-1,j-1}+(t-1), D_{i-2,j-1}+(t-1), D_{i,j-1}+(t-1), D_{i-1,j-2}+(t-1)$  and  $D_{i-1,j}+(t-1)$  respectively. It follows that pebble (i-t+1,j-t+1,t) can be computed at step  $\max\{D_{i-1,j}+x_{i-1,j},D_{i,j-1}+y_{i,j-1}\}+t=D_{i,j}+t$ .

Hence, 2D-RAY simulates pyramid  $P_1$  in  $D_{n,n} + n$  steps. Since  $P_2$ ,  $P_3$ , and  $P_4$  can be simulated similarly, 2D-RAY simulate the first n/2 steps of computation of G in

Figure 4-1: Algorithm 2D-RAY. In pyramid  $P_1$  the dashed line represents the ray of pebbles computed by processor  $p_{i,j}$  (which is shown in the upper left corner). Two of those pebbles, computed at times t and t-1, are shown shaded. The five numbered pebbles are those that (i-t+1, j-t+1, t) depends on.

$O(D_{n,n}+n)$  steps. The simulation is repeated for every n/2 steps of computation of G. Therefore,

**Lemma 4.1.2** Algorithm 2D-RAY achieves a slowdown of  $O(D_{n,n}/n)$ , where  $D_{n,n}$  is the length of the longest monotone path in H.

Unfortunately,  $D_{n,n}$  can be large compared with  $d_{ave}$ , the average delay of H. In the worst case  $D_{n,n}$  can be  $\Theta(n^2d_{ave})$ , implying a slowdown of  $\Theta(nd_{ave})$ . We introduce algorithm FATRAY, a two-dimensional analogue of FATSTRIPE, to achieve a slowdown that is often better than  $O(D_{n,n}/n)$ . Pyramid  $P_1$  is divided into  $m^2$  rays, each of which has size  $\ell \times \ell = \frac{n}{m} \times \frac{n}{m}$ . FATRAY uses an  $m \times m$  contiguous subarray of processors in H to carry out the simulation. For simplicity, assume FATRAY uses processors  $p_{i,j}$   $(1 \le i, j \le m)$ . Again,  $p_{i,j}$  computes every pebble in ray  $R_{i,j}$ , and  $p_{i,j}$  first computes all the pebbles on the bottom plane and then moves up. The follow lemma is analogous to Lemma 3.2.1.

**Lemma 4.1.3** Processor  $p_{i,j}$  finishes simulating ray  $R_{i,j}$  by step  $\ell^2 n/2 + D_{i,j}$ .

**Proof:** As in Lemma 3.2.1 we can inductively show that  $p_{i,j}$  can compute all the pebbles in the xth plane in ray  $R_{i,j}$  by time step  $\ell^2 x + D_{i,j}$ . Since each ray contains at most n/2 planes of pebbles,  $p_{i,j}$  finishes simulating ray  $R_{i,j}$  by step  $\ell^2 n/2 + D_{i,j}$ .

This implies a slowdown of  $O(n^2/m^2 + D_{m,m}/n)$ . To minimize the slowdown, FATRAY uses the contiguous subarray S that minimizes  $n^2/m_S^2 + D_S/n$ , where  $m_S \times m_S$  is the size of S and  $D_S$  is the length of the longest monotone path in S.

**Theorem 4.1.4** FATRAY achieves a slowdown of min<sub>subarrays</sub>  $SO(n^2/m_S^2 + D_S/n)$ .

Unfortunately, the slowdown can still be big compared with  $d_{ave}$ . For example, suppose that H has n edges of delay n which are spread out evenly in the network and has unit delay on all other edges. The slowdown is  $\min_S \Theta(n^2/m_S^2 + D_S/n) = \Theta(n^{1/3})$  whereas  $d_{ave}$  is a constant. Matters are better, however, when all the delays are the same, as we show in the following theorem.

**Theorem 4.1.5** In the case where all the delays in H are d, FATRAY efficiently simulates G on H and achieves a slowdown of  $\Theta\left(\min\{d^{2/3}, n^2\}\right)$ . The slowdown is optimal up to a constant factor.

**Proof:** When  $d \leq n^3$  FATRAY uses a subarray of size  $\frac{n}{d^{1/3}} \times \frac{n}{d^{1/3}}$ . Theorem 4.1.4 implies a slowdown of  $O(d^{2/3})$ . We show that the slowdown is asymptotically tight as follows. Consider pebble  $(i, j, d^{1/3})$ , and suppose processor q computes it in a simulation. Let A be the set the pebbles of the form (i', j', t), for  $1 \leq t < d^{1/3}$ , on which  $(i, j, d^{1/3})$  depends, i.e.  $(i, j, d^{1/3})$  cannot be computed until after (i', j', t) is computed. If every pebble in A is computed by q then it takes at least  $|A| = \Omega\left((d^{1/3})^3\right) = \Omega(d)$  time steps to simulate A. Otherwise, a processor  $p \neq q$  computes some pebble in A and passes this information to q. The delay from p to q is at least d. Hence, the slowdown on simulating the first  $d^{1/3}$  steps is  $d^{2/3}$ . The same argument applies for the slowdown in the next  $d^{1/3}$  steps.

When  $d > n^3$  FATRAY uses a single host processor for the simulation and achieves a slowdown of  $O(n^2)$ . This slowdown is asymptotically tight for the same reason as

in the previous case. We consider pebbles (i, j, n) instead of  $(i, j, d^{1/3})$ . In both cases the simulation is work-efficient.

Theorem 4.1.5 can be generalized to any k-dimensional array, for  $k \geq 1$ .

**Theorem 4.1.6** Suppose G is an  $n \times ... \times n$  k-dimensional array with unit-delay edges, and H is an  $n \times ... \times n$  k-dimensional array with delay-d edges, then H can efficiently simulate G with a slowdown of  $\Theta(\min\{d^{k/k+1}, n^k\})$ . The slowdown is optimal up to a constant factor.

## 4.2 Improved Bounds for Worst-Case Delays

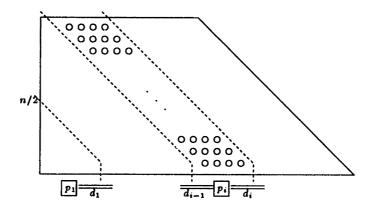

In order to improve the slowdown, we observe that not all the host processors are useful. If a host processor is surrounded by high delays, then the benefit to be gained by using its computing power is nullified by the communication cost. We first describe criteria of removing such host processors. We then embed guest processors to the unremoved host processors. Suppose that guest processor  $g_{i,j}$  is mapped to host processor p, then p computes the pebbles in ray  $R_{i,j}$  in the 2D-RAY algorithm. For any arrangement of the delays in H, we show how to embed G on H such that, for any monotone path in G, its image in H has length of  $O(d_{ave} \log^{5/2} n)$ . As a result, Lemma 4.1.2 implies a slowdown of  $O(d_{ave} \log^{5/2} n)$  as long as only O(1) guest processors are mapped to each host processor. By applying the idea used in FATRAY, we improve the slowdown to  $O(d_{ave}^{2/3} \log^{5/3} n)$  and achieve work-efficiency at the same time.

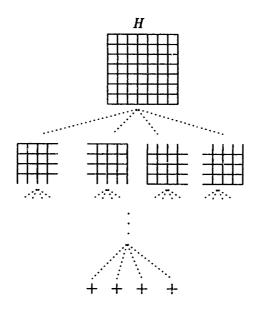

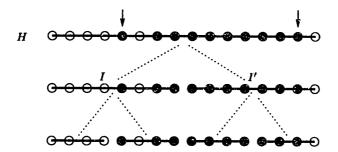

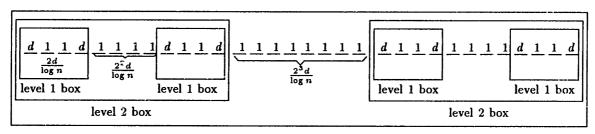

#### 4.2.1 Removing Useless Processors

We first recursively represent H using a quad-tree, in which each node corresponds to a subarray of H. The root represents the entire  $n \times n$  array. The four children of the root represent the four  $\frac{n}{2} \times \frac{n}{2}$  subarrays, etc. In general, a node at depth k of the quad-tree corresponds to an  $\frac{n}{2^k} \times \frac{n}{2^k}$  subarray of H. We refer to this subarray as a depth-k array. The leaves represent the individual processors of H. (See Figure 4-2.)

Figure 4-2: The quad-tree that represents H.

We describe a 2-stage procedure to remove "useless" processors of H. A processor is removed if it is surrounded by high delays (stage 1) or few unremoved processors (stage 2). (When a processor is removed, its incident edges remain in the network.) For each depth k, we define two quantities  $D_k$  for "delay threshold" and  $m_k$  for "survival threshold". Note that  $D_k$  is larger than the average delay on a row/column in a depth-k array by a factor of  $\Theta(\log n)$ , and  $m_k$  is smaller than the number of processors in a depth-k array by a factor of  $\Theta(\log n)$ .

$$D_k = (c \log n) \left( \frac{n}{2^k} d_{\text{ave}} \right) \tag{4.1}$$

$$m_k = \left(\frac{1}{c \log n}\right) \left(\frac{n^2}{4^k}\right) \tag{4.2}$$

A constant c is specified later. We also define a maximum depth  $k_{\text{max}}$  such that when  $k = k_{\text{max}}$  the survival threshold  $m_k$  becomes 1.

$$k_{\text{max}} = \log n - \frac{1}{2} \log c - \frac{1}{2} \log \log n.$$

(4.3)

• Stage 1 From depth  $k = k_{\text{max}}$  down to depth 0, if the total delay on a row/column of a depth-k array exceeds the threshold  $D_k$ , then all the  $\frac{n}{2^k}$  pro-

cessors on that row/column are removed.

• Stage 2 From depth  $k = k_{\text{max}}$  down to depth 0, if the number of unremoved processors in a depth-k array is smaller than the threshold  $m_k$ , then all the processors in that array are removed. Moreover, we also remove processors so that the number of remaining processors in any depth-k array is an integer multiple of  $m_k$ .

#### **Lemma 4.2.1** At most $2n^2/c$ processors are removed in stage 1.

**Proof:** The total delay of H is  $2n^2d_{ave}$ . At most  $\frac{2n2^k}{c\log n}$  depth-k rows and columns can have delay more than  $D_k$ . Since each depth-k row/column contains  $\frac{n}{2^k}$  processors, at most  $\frac{2n^2}{c\log n}$  processors are removed at depth k. There are  $\log n$  depths, and so the lemma follows.

**Lemma 4.2.2** At most  $n^2/c$  processors are removed at stage 2.

**Proof:** Since there are  $4^k$  depth-k arrays, at most  $\frac{n^2}{c \log n}$  processors are removed at depth k.

We label each array with the number of unremoved processors contained in it. By Lemmas 4.2.1 and 4.2.2, at most  $3n^2/c$  processors of H are removed. Therefore, H is labeled with  $c_1n^2$ , where  $c_1 \geq 1 - (3/c)$ . Any constant c > 3 works for our argument.

#### 4.2.2 The Embedding

For clarity of presentation, we create an intermediate 2-dimensional array  $\mathcal{G}$  that has size  $\sqrt{c_1}n \times \sqrt{c_1}n$  and unit-delay edges only. We describe an algorithm EMBED that maps the processors of  $\mathcal{G}$  one-to-one to the unremoved processors of H. The goal is to show that for any monotone path in  $\mathcal{G}$  its image in H under EMBED has length  $O(d_{\text{ave}}n\log^{5/2}n)$ . As a result, H can simulate  $\mathcal{G}$  with a slowdown of  $O(d_{\text{ave}}\log^{5/2}n)$ . Obviously  $\mathcal{G}$  can simulate G with constant slowdown.

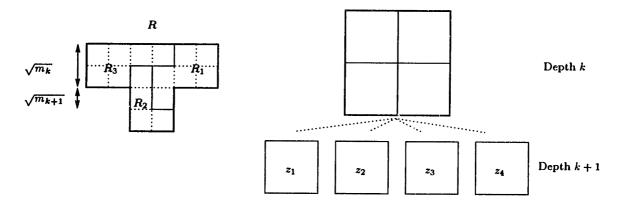

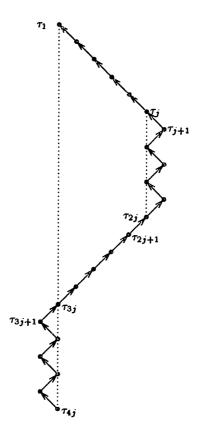

EMBED partitions  $\mathcal{G}$  into regions recursively, and each depth-k region of  $\mathcal{G}$  corresponds to a depth-k array of H. The depth-0 region is the entire network  $\mathcal{G}$ . By

the construction of stage 2,  $c_1n^2$  (the number of processors in  $\mathcal{G}$ ) is a multiple of  $m_0$ . Hence,  $\mathcal{G}$  can be viewed as a collection of contiguous squares of size  $\sqrt{m_0} \times \sqrt{m_0}$ . We inductively assume that each depth-k region consists of contiguous squares of size  $\sqrt{m_k} \times \sqrt{m_k}$ , where  $m_k$  is defined in Equation (4.2). Each depth-k region R is partitioned into four depth k+1 regions  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$  as follows. First, each  $\sqrt{m_k} \times \sqrt{m_k}$  square of R is divided into four squares of size  $\sqrt{m_{k+1}} \times \sqrt{m_{k+1}}$ , where  $\sqrt{m_{k+1}} = \sqrt{m_k}/2$ . Suppose that  $R_i$  corresponds to a depth k+1 square of  $R_i$  that has  $r_i$  unremoved processors, then  $r_i$  has size  $r_i$ . By the construction of stage 2,  $r_i$  is a multiple of  $r_i$ . Hence,  $r_i$  can be formed as a collection of contiguous squares of size  $\sqrt{m_{k+1}} \times \sqrt{m_{k+1}}$ . Note that if  $r_i$  is 0, the the corresponding  $r_i$  is empty. (See Figure 4-3.)

At depth  $k_{\text{max}}$ , each depth- $k_{\text{max}}$  region consists of contiguous squares of size  $1 \times 1$ . EMBED maps the processors in a depth- $k_{\text{max}}$  region of  $\mathcal{G}$  to the unremoved processors in the corresponding depth- $k_{\text{max}}$  array of H in an arbitrary one-to-one manner. Thus, we have a one-to-one mapping from the processors of  $\mathcal{G}$  to the unremoved processors of H.

Figure 4-3: (Left) Depth-k region R and depth k+1 regions  $R_1$ ,  $R_2$  and  $R_3$  of  $\mathcal{G}$ . (Right) Depth-k and k+1 arrays of H. Depth k+1 region  $\mathcal{K}_i$  has size  $z_i$ , where  $z_i$  is the number of unremoved processors in the corresponding array of H. In this figure,  $z_4=0$ , and  $R_4$  is therefore empty.

We also define the depth-k boundaries in  $\mathcal{G}$  to be the borders of depth-k regions of  $\mathcal{G}$ . Note that the depth-k boundaries are at least  $\sqrt{m_k}$  apart in both horizontal and vertical directions.

#### 4.2.3 Bounding Monotone Path Length

In this section we bound the total delay on the image of P in H, where P is any monotone path in G. Suppose a and b are two neighboring processors in G, then their images  $a_H$  and  $b_H$  in H are connected by a 1-bend route as follows. First,  $a_H$  is routed along its row to  $b_H$ 's column and then routed to  $b_H$  along the column. We define a and b (resp.  $a_H$  and  $b_H$ ) to be k-related if k is the largest integer such that a and b (resp.  $a_H$  and  $b_H$ ) are in a same depth-k region (resp. depth-k array). We also define  $a_H$  and  $b_H$  to be peers of each other. Note that each unremoved host processor can have 4 peers.

**Lemma 4.2.3** Let P be any monotone path in G. The image of P in H has a total delay of  $O(d_{ave}n \log^{5/2} n)$  under EMBED.

**Proof:** Let a and b be two neighboring processors on P and let  $a_H$  and  $b_H$  be their images. Suppose a and b (resp.  $a_H$  and  $b_H$ ) are k-related. We first bound the length of the 1-bend route from  $a_H$  to  $b_H$ . By the construction of stage 1, the total delay on a depth-k row/column that contains  $a_H$  or  $b_H$  is at most  $D_k$ . Hence, the distance from  $a_H$  to  $b_H$  is at most  $2D_k$ .

We now bound the number of neighboring a's and b's that can be k-related. If  $k < k_{\text{max}}$ , P must cross some depth k+1 boundary of  $\mathcal{G}$  in traveling from a to b. Since P is monotone and the depth-k boundaries are  $\sqrt{m_k}$  apart in both horizontal and vertical directions, P can cross the depth-k boundaries at most  $\frac{2n}{\sqrt{m_k}}$  times. Hence, at most  $\frac{2n}{\sqrt{m_{k+1}}}$  neighboring a's and b's on P can be k-related. This implies that the total delay incurred by k-related peers on the image of P is at most  $2D_k \frac{2n}{\sqrt{m_{k+1}}}$ , for  $k < k_{\text{max}}$ . Obviously, at most 2n neighboring a's and b's can be  $k_{\text{max}}$ -related. Summing over all depths, we conclude that the total delay on the image of P is at most  $2D_{k_{\text{max}}} \cdot 2n + \sum_{k < k_{\text{max}}} 2D_k \frac{2n}{\sqrt{m_{k+1}}}$ , which is  $O(d_{\text{ave}} n \log^{5/2} n)$  by the definitions of  $D_k$ ,  $m_k$  and  $k_{\text{max}}$ .

Hence, we can embed G on H such that O(1) guest processors are mapped to each host processor and that the image in H of any monotone path in G has length  $O(d_{ave}n\log^{5/2}n)$ . Lemma 4.1.2 implies that H can simulate G with a slowdown

of  $O(d_{ave} \log^{5/2} n)$ . To improve the slowdown and achieve efficiency, we apply the idea of complementary slackness and use an  $m \times m$  contiguous subarray of H for simulation as in FATRAY. Theorem 4.1.4 and Lemma 4.2.3 imply a slowdown of  $O\left((d_{ave}m \log^{5/2} m)/n + n^2/m^2\right)$ . By choosing m to be  $\max\left\{nd_{ave}^{-1/3} \log^{-5/6} n, 1\right\}$ , we have,

**Theorem 4.2.4** Network H with average delay  $d_{ave}$  can efficiently simulate G with a slowdown of  $O\left(d_{ave}^{2/3}\log^{5/3}n\right)$ .

#### 4.2.4 Bandwidth

The preceding analysis focuses entirely on the issue of latency and ignores bandwidth constraints. This does not present any problems if the link bandwidth available on the host array is  $\Omega(\log^{3/2} n)$  times larger than that on the guest array. If the bandwidth of the host and guest arrays are comparable, however, and if the guest array is fully utilizing the bandwidth on its links then congestion becomes an issue. In this case, we may need to slow down the simulation by an additional factor of  $O(\log^{3/2} n)$ .

In Section 4.2.3, peers  $a_H$  and  $b_H$  are connected by a 1-bend route in H. To address the congestion issue, we present a more sophisticated method of connecting  $a_H$  and  $b_H$  such that each edge in H has  $O(\log^{3/2} n)$  routes going through it and that the distance between  $a_H$  and  $b_H$  remains unchanged asymptotically.