# Abacus: A Reconfigurable Bit-Parallel Architecture for Early Vision

by

### Michael Bolotski

B.A.Sc. Electrical Engineering, University of British Columbia (1988) M.A.Sc. Electrical Engineering, University of British Columbia (1990)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 1996

© Massachusetts Institute of Technology 1996. All rights reserved.

|              | artment of Electrical Engineering and Computer Science                      |

|--------------|-----------------------------------------------------------------------------|

|              | September 6, 1996                                                           |

|              |                                                                             |

|              |                                                                             |

| Certified by | Thomas F. Knight, Jr<br>Senior Research Scientist of Electrical Engineering |

|              | Thomas F. Knight, Jr                                                        |

|              | Senior Research Scientist of Electrical Engineering                         |

|              | Thesis Supervisor                                                           |

|              |                                                                             |

|              |                                                                             |

Accepted by .....

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Frederic R. Morgenthaler Chairman, Committee on Graduate Students

OCT 1 5 1996 -

**ARCHIVES**

LIBRARIES

|  | • |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

# Abacus: A Reconfigurable Bit-Parallel Architecture for Early Vision by Michael Bolotski

Submitted to the Department of Electrical Engineering and Computer Science on September 6, 1996, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Abstract**

Many important computational problems, including those of computer vision, are characterized by data-parallel, low-precision integer operations on large volumes of data. For such highly structured problems, this thesis develops Abacus, a high-speed reconfigurable SIMD (single-instruction, multiple-data) architecture that outperforms conventional microprocessors by over an order of magnitude using the same silicon resources.

Earlier SIMD systems computed at relatively slow clock rates compared to their uniprocessor counterparts. The thesis discusses the problems involved in operating a large SIMD system at high clock rates, including instruction distribution and chip-to-chip communication, presents the solutions adopted by the Abacus design.

Although the chip was implemented in a 1989-era VLSI technology, it was designed to contain 1024 processing elements (PEs), operate at 125 MHz, and deliver 2 billion 16-bit arithmetic operations per second (GOPS). The PE and chip architecture are described in detail, as well as the results of testing the chip at 100 MHz.

Despite this high performance, the Abacus one-bit ALU is not the optimal point in the design space. An analytical model is developed for performance as a function of ALU width and off-chip memory bandwidth. Intuition provided by the model leads to the conclusion that an eight-bit ALU is an optimal choice for the current technology.

Finally, using the analytical model, area and time parameters from the Abacus chip, and some lessons learned from the chip implementation, a design is presented for a 320 GOPS low-cost single-board system.

Thesis Supervisor: Thomas F. Knight, Jr.

Title: Senior Research Scientist of Electrical Engineering

## Acknowledgements

I would like to thank my thesis advisor, Tom Knight, for his support and encouragement over the past six years. To me, he truly personifies the nature of creative intellectual inquiry. An off-hand quote of his has been hanging on my wall since the month of my arrival at MIT: "the goal, of course, is to learn everything."

I owe a debt to everyone who worked on the Abacus chip, especially Tom Simon who was responsible for every off-chip interface circuit, and without whose attention to detail the chip would have never worked. The chip also includes contributions from Carlin Vieri and Raj Amirtharajah. Fred Drenckhahn did an outstanding job on the package design.

This page is too short to express the debt I owe to my friends at MIT: Maja Mataric, Phillip Alvelda, Carlin Vieri, Tony Gray, and Jim Goodman. They have made my stay here a wonderful experience. I would also like to thank Lisa Kozdiy for tolerance and understanding throughout the trying time of the thesis defense.

Other departed members of the Lab have also contributed to this thesis, through discussion, guidance, and friendship: Ian Horswill, Karen Sarachik, Carl de Marcken, Paul Viola, Patrick Sobalvarro, Tom Breuel, and Saed Younis.

My housemates throughout the years have tolerated my late hours and sleep-deprived behavior. Thanks go to Pablo Policzer, Sue Nissman, and Pam Sawyer.

Finally, I want to thank my parents, Peter and Frida Bolotski, for their support, love, and unending confidence in my abilities.

This research is supported in part by the Defense Advanced Research Projects Agency under contract DABT63-92-C-0039

# Contents

| 1 | Intr | coducti | ion                                     | 17 |

|---|------|---------|-----------------------------------------|----|

| 2 | Pre  | vious a | and Related Work                        | 21 |

|   | 2.1  | Archit  | ectural Design                          | 21 |

|   | 2.2  | High-S  | Speed SIMD Issues                       | 24 |

|   | 2.3  | Recon   | figurable Architectures                 | 25 |

|   | 2.4  | Archit  | ectural Studies                         | 27 |

|   |      | 2.4.1   | Normalized Analysis                     | 27 |

|   |      | 2.4.2   | Simulation-Based Performance Evaluation | 28 |

|   |      | 2.4.3   | Dynamic Concatenation                   | 29 |

|   |      | 2.4.4   | Phase-Specific Reconfiguration          | 30 |

| 3 | Aba  | acus C  | hip                                     | 31 |

|   | 3.1  | Abacu   | s PE Architecture                       | 31 |

|   | 3.2  | Proces  | ssing Element Core                      | 33 |

|   |      | 3.2.1   | Memory                                  | 33 |

|   |      | 3.2.2   | ALU                                     | 34 |

|   |      | 3.2.3   | Network                                 | 37 |

|   |      | 3.2.4   | Data and I/O Planes                     | 39 |

|   |      | 3.2.5   | Global OR Operation                     | 40 |

|   |      | 3.2.6   | Layout Summary                          | 40 |

|   | 3.3  | On-Ch   | nip Signal Distribution                 | 41 |

|   |      | 3.3.1   | Load Equalization                       | 41 |

|   |            | 3.3.2    | Layout Issues: The Trench                  | 42     |

|---|------------|----------|--------------------------------------------|--------|

|   |            | 3.3.3    | Timing                                     | 42     |

|   | 3.4        | Exter    | nal Interfaces                             | 43     |

|   |            | 3.4.1    | System Synchronization                     | 43     |

|   |            | 3.4.2    | Instruction Distribution                   | 44     |

|   |            | 3.4.3    | Inter-Chip Mesh Communication              | 47     |

|   |            | 3.4.4    | External Memory Interface                  | 48     |

|   |            | 3.4.5    | Image I/O Interface                        | 48     |

|   | 3.5        | Chip I   | Floorplan and Control Logic                | 49     |

|   |            | 3.5.1    | Timing Generator                           | 49     |

|   |            | 3.5.2    | Pad Ring Summary                           | 51     |

|   |            | 3.5.3    | Instruction Decode                         | . , 51 |

|   |            | 3.5.4    | TAP Control                                | . 51   |

|   | 3.6        | Design   | n Style                                    | . 52   |

|   | 3.7        | Testing  | g the Chip                                 | . 54   |

|   |            | 3.7.1    | Test Board                                 | . 54   |

|   |            | 3.7.2    | Test Process                               | . 55   |

|   |            | 3.7.3    | Test Results                               | . 55   |

|   |            | 3.7.4    | Testing Summary                            | . 58   |

| 4 | Aba        | acus-1 S | System-Level Design                        | 63     |

|   | 4.1        |          | ncer , , , , , , , , , , , , , , , , , , , | . 64   |

|   | 4.2        |          | pard                                       |        |

|   | 4.3        |          | oards                                      |        |

| 5 | Δbs        | oug.1 1  | Performance Evaluation                     | ~.     |

| J | 5.1        |          |                                            | 71     |

|   | 5.2        |          | Arithmetic Algorithms                      |        |

|   | 0.2        |          | nunication Operations                      |        |

|   |            |          | Scans                                      |        |

|   | <b>5</b> 2 |          | General Routing                            |        |

|   | 5.3        | Dasic \  | Vision Algorithms                          | 77     |

|   | 5.4  | The DARPA IU Benchmark         | 7   |

|---|------|--------------------------------|-----|

|   | 5.5  | Performance Summary            | 8   |

| 6 | Ana  | alytical Modeling              | 8   |

|   | 6.1  | RBP Performance Model          | 8   |

|   | 6.2  | Optimal Bit Width Analysis     | 8   |

|   |      | 6.2.1 Ideal Model              | 8   |

|   |      | 6.2.2 Amdahl's Law             | 8   |

|   |      | 6.2.3 Off-Chip Data            | 9   |

|   |      | 6.2.4 Background Loading       | 90  |

|   |      | 6.2.5 Conclusions              | 99  |

|   | 6.3  | Future Work                    | 100 |

| 7 | Aba  | cus 2: The Next Generation     | 103 |

|   | 7.1  | Lessons of Abacus-1            | 104 |

|   | 7.2  | Abacus-2                       | 106 |

|   |      | 7.2.1 Pipelining Analysis      | 106 |

|   |      | 7.2.2 Improvements To Abacus-1 | 108 |

|   |      | 7.2.3 Physical Characteristics | 111 |

|   | 7.3  | Beyond SIMD: A Family of Abaci | 112 |

| 8 | Disc | ussion                         | 115 |

| A | Aba  | cus-1 Instruction Format       | 118 |

|   | A.1  | Regular Instructions           | 119 |

|   | A.2  | Special Instructions           | 120 |

|   |      | A 2.1 Timing Information       | 100 |

# List of Figures

| 1-1  | CPU and SIMD System Comparison   | 18   |

|------|----------------------------------|------|

| 2-1  | SIMD System Block Diagram        | . 22 |

| 2-2  | RBP Organization                 | . 26 |

| 3-1  | Processing Element Block Diagram | . 32 |

| 3-2  | Network cell                     | 32   |

| 3-3  | Three Func                       | 36   |

| 3-4  | Network Types                    | 37   |

| 3-5  | Network Configurations           | 38   |

| 3-6  | Network Block Diagram            | . 38 |

| 3-7  | Network Accelerator              | 39   |

| 3-8  | PE Layout                        | 40   |

| 3-9  | Memory read and write path       | 43   |

| 3-10 | Abacus PE Timing                 | . 44 |

| 3-11 | DLL Arbiter                      | 45   |

| 3-12 | Instruction Pad                  | 46   |

| 3-13 | Chip Photograph                  | 50   |

| 3-14 | Time Ring Unit                   | 51   |

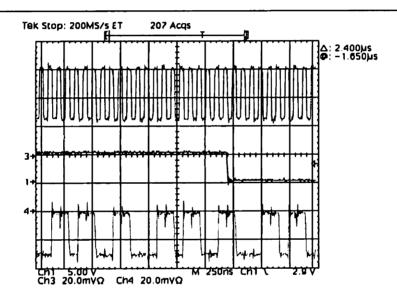

| 3-15 | Read Clock Monitor               | 56   |

| 3-16 | TAP Interface                    | 57   |

| 3-17 | I/O Burst                        | . 57 |

|      | DP Shift                         |      |

|      | DRAM toggle at 80                |      |

| 3-20 | I/O Toggle                                                                             | )  |

|------|----------------------------------------------------------------------------------------|----|

| 3-21 | Mesh Shift                                                                             | L  |

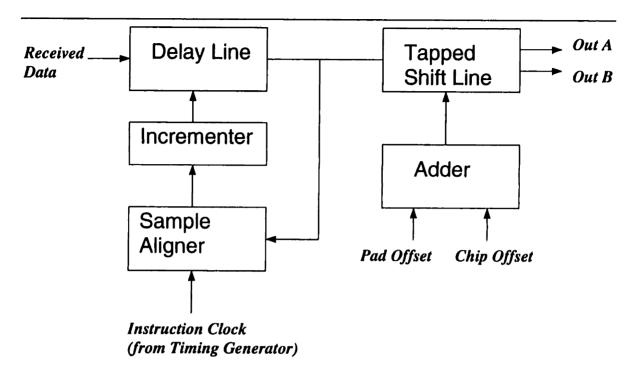

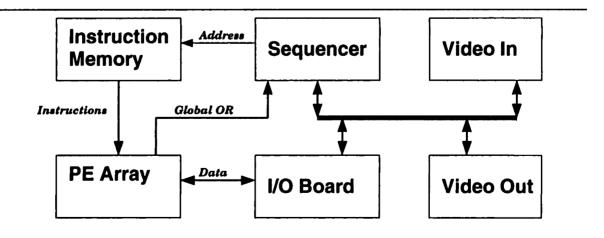

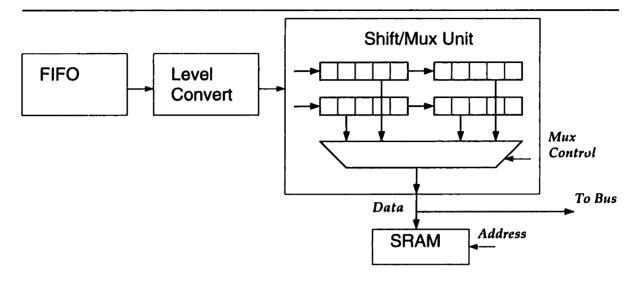

| 4-1  | System Block Diagram                                                                   | }  |

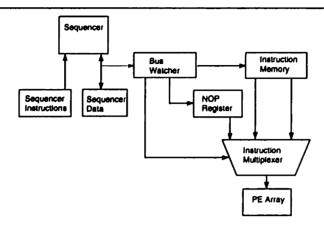

| 4-2  | Sequencer Block Diagram                                                                | 5  |

| 4-3  | Interleaved scalar and parallel code                                                   | j  |

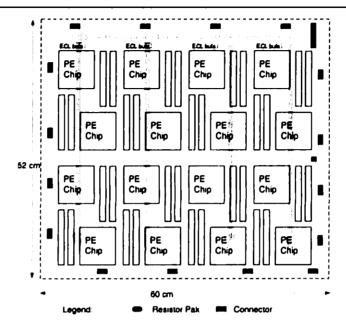

| 4.4  | PE Board                                                                               | 7  |

| 4-5  | Reformatting Circuitry Block Diagram                                                   | )  |

| 5-1  | Logical Shift Right                                                                    | 2  |

| 5-2  | Accumulate                                                                             | 2  |

| 5-3  | Addition                                                                               | }  |

| 5-4  | Compare                                                                                | Į  |

| 5-5  | A +-reduce operation                                                                   | 5  |

| 5-6  | Optical Flow Example                                                                   | 3  |

| 5-7  | Optical Flow Field                                                                     | 3  |

| 5-8  | K-curvature definition                                                                 | )  |

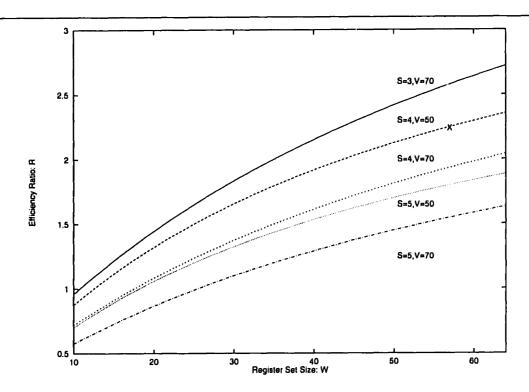

| 6-1  | Silicon Efficiency Ratios                                                              | 1  |

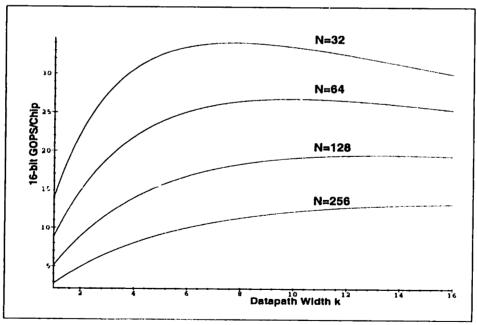

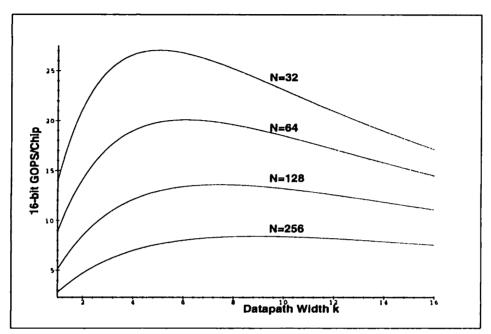

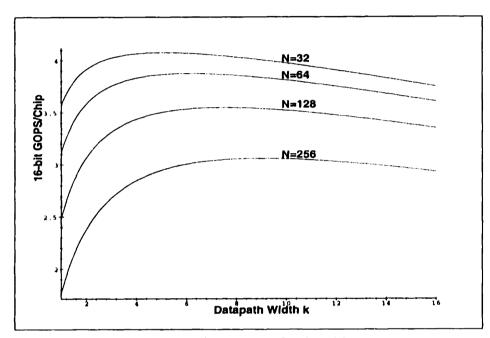

| 6-2  | Ideal Performance as a function of $k$                                                 | 3  |

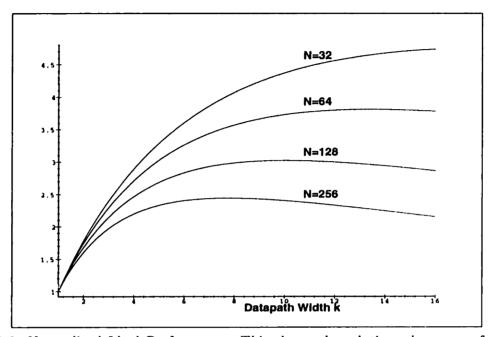

| 6-3  | Normalized Ideal Performance                                                           | 7  |

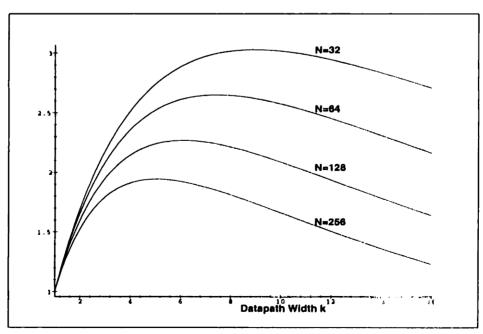

| 6-4  | Amdahl-corrected quality values                                                        | )  |

| 6-5  | Normalized Amdahl-corrected quality values                                             | )  |

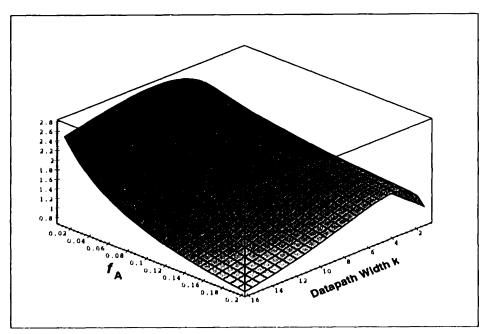

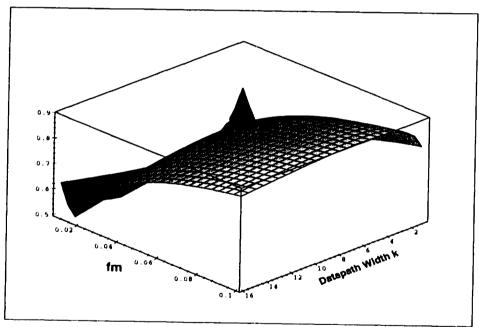

| 6-6  | Normalized quality vs $k$ and $f_A$                                                    | )  |

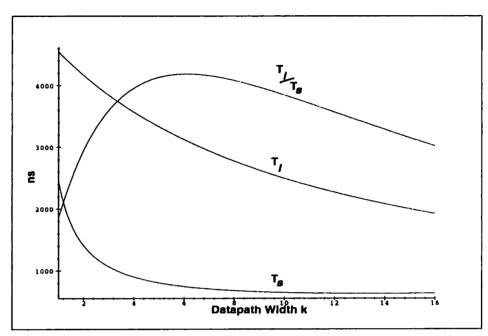

| 6-7  | Load Time Compared to Load Period                                                      | }  |

| 6-8  | I/O-derated Quality Metrics                                                            | į  |

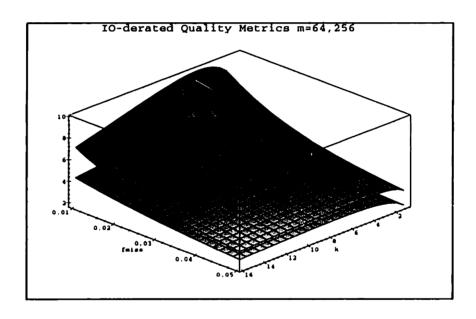

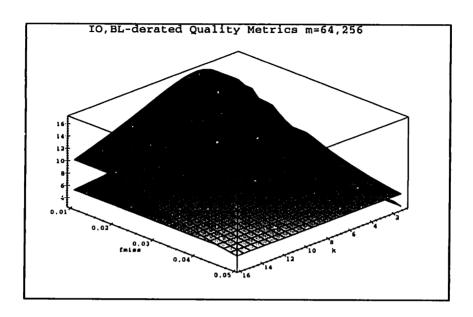

| 6-9  | I/O-derated Quality Metrics (m=64,256))                                                | 5  |

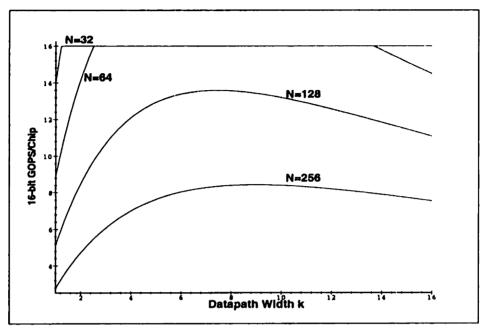

| 6-10 | Performance improvement due to background loading                                      | j  |

| 6-11 | Absolute performance, background loading                                               | 7  |

| 6-12 | Prefetching-derated quality metrics                                                    | 3  |

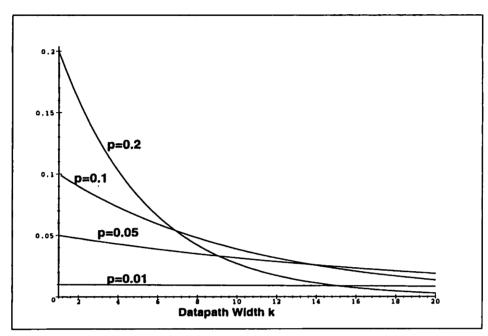

| 6-13 | Probability of hi sequence of length $k$                                               | .) |

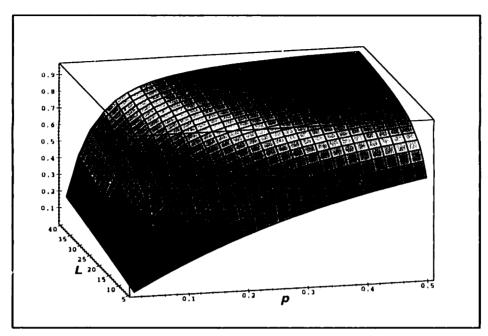

| 6-14 | Effective latency vs latency due to background loading as a function of $L$ and $p100$ | )  |

| 7-1 | Abacus-2 Carry Interconnection | 107 |

|-----|--------------------------------|-----|

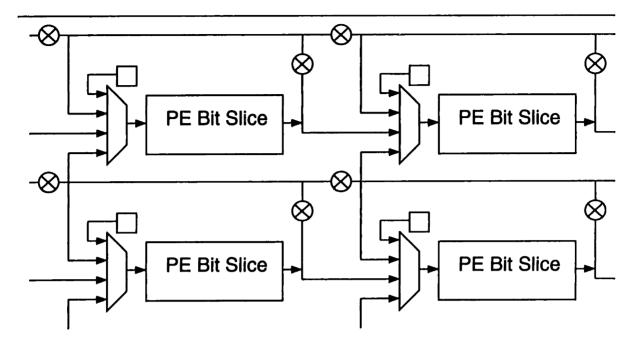

| 7-2 | Abacus-2 Mesh Network          | 110 |

# List of Tables

| 2.1 | Architectural performance comparison                    |

|-----|---------------------------------------------------------|

| 3.1 | Single vs Double Bank Design                            |

| 3.2 | Number of cycles in horizontal mode                     |

| 3.3 | PE Area Resources                                       |

| 3.4 | Chip Area by Subsystem                                  |

| 3.5 | Pin Requirements                                        |

| 3.6 | Board Stackup                                           |

| 3.7 | Testing Summary                                         |

| 4.1 | Board Level Parts Count                                 |

| 4.2 | Reformatter Part Count                                  |

| 5.1 | Single Chip Arithmetic Performance                      |

| 5.2 | Vision Algorithm Performance Summary                    |

| 6.1 | Analytical Model Parameters                             |

| 6.2 | Fraction of Operation Costs Affected by Data Path Width |

| 6.3 | Fraction of Operation Costs Affected by Data Path       |

| 6.4 | Contemporary Memories                                   |

| 6.5 | Latencies of Memories                                   |

| 7.1 | Abacus 2 Pin Budget                                     |

| 7.2 | Abacus-2 PE Area                                        |

| 7.3 | Abacus-2 Chip Spec                                      |

| A.1 | Microinstruction Types  | 120 |

|-----|-------------------------|-----|

| A.2 | DRAM Timing Information | 122 |

# Chapter 1

## Introduction

Computer vision, the understanding of images by a computer, is both an exciting component of artificial intelligence and a daunting computational task considered as one of the Grand Challenge problems of parallel processing. The scope of the challenge becomes apparent when the computational requirements of early vision are considered. A moderately sized image contains approximately 65,000 pixels, each of which may be used a hundred times in a computation. A single vision algorithm may require ten iterations per image, and as many as fifty algorithms may be required to extract essential information such as depth, motion, shapes, and shadows. All of this processing must be repeated thirty times per second to sustain real time response. The aggregate sustained computing power is therefore on the order of 100 billion operations per second (GOPS).

Hundreds of parallel system designs have been proposed to attain this level of performance. These systems can be broadly categorized as Single-Instruction Multiple Data (SIMD) machines that consist of identical processing elements (PEs) executing the same instructions in lockstep, and Multiple-Instruction Multiple-Data (MIMD) machines, whose PEs execute independent programs and use explicit communication to synchronize operations. Historically, SIMD machines have been built with large numbers of simple PEs, while MIMD machines relied on a small number of complex PEs.

Currently, the most prevalent parallel architectures are MIMD machines consisting of collections of workstation-class RISC processors. Indeed, only one major SIMD vendor, MasPar, still exists, while there are many MIMD vendors, including Cray, Convex, IBM, and Intel. This overwhelming commercial success is due to the constant improvement in microprocessor performance, driven by marketplace pressure and fueled by enormous investment.

Parallel MIMD machines are excellent general-purpose computing and development platforms, since they come equipped with the software inherited from their workstation heritage. As with the uniprocessors on which they are based, these machines excel at computations with irregular and unpredictable instruction streams. Unfortunately, the price of this flexibility is reduced performance. On problems with a data-parallel, highly regular structure, such as image processing, these processors continue to be unnecessarily flexible at every instruction step. The MIMD model incurs enormous overhead for every functional unit that actually manipulates data. This overhead consists of silicon area required to store the program (a 10K word program of 32 bits each corresponds to 1.8 million transistors!), instruction decoding, addressing, and control circuitry. The overhead can easily be a factor of ten larger than the functional unit actually processing the data.

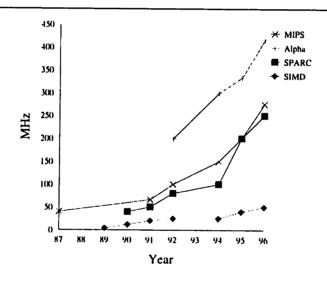

Despite this apparently inherent advantage, there are few SIMD systems in existence. The reason for the lack of widespread adoption of SIMD machines becomes obvious when the clock rates of RISC and SIMD systems are compared. Figure 1-1 compares the improvement in clock rate within several families of RISC processors to (mostly academic) SIMD designs.

Figure 1-1: CPU and SIMD System Comparison

The advent of VLSI technology gave SIMD systems a substantial advantage over their discrete-component based uniprocessor competition. With time, this advantage disappeared as SIMD machines failed to incorporate high-speed circuit techniques and therefore retained unnecessarily low clock rates. This work aims to substantially improve the clock rates of SIMD and microprocessor systems and thereby regain the performance lead. Experience obtained through the detailed design shows that the clock rate barrier is largely illusory.

Thesis. The thesis of this dissertation is that for the problem domain of early vision, parallel computers based on a SIMD architecture can outperform those based on conventional processors by over an order of magnitude using the same silicon resources.

The overall research approach is to:

Design, implement, and test a VLSI chip containing Abacus processing elements. A

working chip will unearth any inaccurate assumptions about high speed SIMD operations.

- Complete a system-wide design to ensure that there are no unexpected system-level bottlenecks.

- Develop an analytical performance model based on the chip parameters. The existence of a concrete instantiation of the architecture allows empirical evaluation of the costs and benefits of reconfiguration.

- Use the chip implementation experience and the analytical model to develop a design for a second generation architecture.

The contributions of this work can be grouped under three categories: implementational, analytical, and cultural. A successful implementation has demonstrated a SIMD chip with the highest clock rate to date and forced the development of system interfaces generally ignored in the academic field. The collection of high-speed techniques forms a framework for future SIMD designs.

The analytical model allows the selection of an optimal point in implementation space as technology parameters vary. For example, novel high-bandwidth devices such as Rambus memory components may allow reduction in the amount of on-chip memory. The model will allow quantification of these tradeoffs.

An operational chip will also have several positive cultural effects. It will provide a convincing demonstration of the effectiveness of SIMD processing. Important applications of SIMD technology are near but may be hampered by the unconvincing performance and architectural deficiencies of existing SIMD processor arrays. Vision-related tasks, such as MPEG coding, OCR, paper document processing, digital picture manipulation, medical imagery, face recognition, vehicle collision avoidance, and automatic vehicle guidance all provide important practical applications which can be solved on SIMD machines. Finally, the project will demonstrate that high performance design can be done in a university environment.

An existing system design will allow the construction of a cheap tera-op level supercomputer for vision research. Such a platform will allow important image, signal, and text processing applications to be prototyped. A successful design will encourage research on specialized architectures, which has been decreasing recently due to the success of RISC-based MIMD machines.

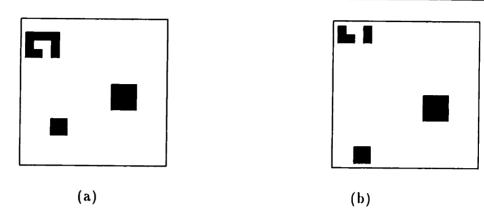

Abacus. The Abacus architecture can be classified as a reconfigurable bit-parallel (RBP) machine. The key idea of a RBP design is to provide programmable interconnect to link multiple PEs into a single Processing Site (PS) that can operate on several bits of a data word simultaneously. Reconfiguration allows word width to be matched to the need of each algorithm. Even more significantly, on-chip memory capacity at each processing site can also be adjusted by changing the number of PEs in a PS. Since off-chip memory references can be a factor of 20 slower than on-chip accesses, decreasing the miss rate at the cost of ALU capacity may lead to substantial performance increases for many algorithms.

Reconfigurable processors provide a smooth transition between the two extremes of a slow, small bit-serial PE and a complex, fast bit-parallel PE. The tradeoff between the two is that simple one-bit PEs are capable of arbitrary precision and can run at a high clock speed,

but require many cycles per operation. Hardware bit-parallel PEs require few cycles, but run slower and waste valuable silicon when computing with data narrower than their ALU width. RBP designs retain bit-serial flexibility and bit-parallel performance.

Organization Chapter 2 presents an overview of the substantial body of previous work relating to the topics of this thesis, from SIMD machines to modern architectural alternatives: the SRC PIM chip, Berkeley's PADDI-2 DSP, and FPGA based computing platforms. After demonstrating the the SIMD approach is competitive if the clock speed can be raised above previous levels, the discussion turns to issues of high-speed SIMD system designs. The chapter concludes with a review of related architectural performance evaluations.

Chapter 3 describes the implementation of the Abacus-1 chip at a fairly detailed level, as well as chip test results. Chapter 4 describes the system-level design of the Abacus machine, including the approach to issues of high-speed SIMD operation.

Chapter 5 is the performance evaluation. It introduces the benchmark algorithms used to evaluate the architectural tradeoffs and evaluates architectural tradeoffs such as local memory size, ALU width, off-chip memory bandwidth and network bandwidth, based on instruction traces from the parallel algorithms.

Chapter 6 develops an analytical model for the performance of SIMD chips, based on parameters from the Abacus implementation.

Chapter 7 describes the lessons learned from the design of the Abacus-1 architecture, and the set of changes required to produce a smaller yet more powerful design. Looking farther ahead, it introduces modifications that allow a redesigned Abacus element to function in multiple-SIMD mode, as a systolic processor, or to emulate random logic circuits effectively.

Chapter 8 concludes with the implications of what has been learned from the design and suggests avenues for future research.

# Chapter 2

# Previous and Related Work

Many systems have been developed to perform vision and image processing. The performance of the Abacus-1 design must be considered in the context of other major approaches. When the clock rate is boosted with aggressive design, SIMD machines are more than competitive with other approaches. A survey of previous work on the challenges of high-speed SIMD design indicates that an effective high speed design has not yet been worked out. Once such a design is developed, the processor/memory bottleneck becomes apparent. Dynamic reconfiguration may be used for tuning on-chip memory size to the needs of a particular algorithm at run-time. After analyzing previous reconfigurable machines it is clear that none of them have been optimized for this sort of reconfiguration.

## 2.1 Architectural Design

There has been a considerable amount of research on architectures for image processing and image understanding. A variety of processor designs and interconnection networks have been proposed (but few have been implemented). This review concentrates on SIMD designs and on alternate approaches with comparable performance.

Early examples of machines designed for image processing include Goodyear's MPP(Potter 1985), NCR's GAPP (Cloud 1988), and ICL's DAP (Parkinson & Litt 1990). The most widely produced SIMD machine was Thinking Machines' CM-2. A contemporary commercial product was produced by MasPar (Blank 1990), and recently upgraded to the MP-2 (Tuck & Kim 1993).

There are also several research designs which have not been put into commercial production. These designs explored different aspects of SIMD architectures. For example, IBM's polymorphic torus (Li & Maresca 1989) concentrated on adding connection autonomy by the addition of locally reconfigurable network switches. The MCNC Blitzen project (Blevins, Davis, Heaton & Reif 1988) updated the original MPP design for VLSI technology by adding on-chip RAM, local modification of addresses, and an X-grid 8-neighbor interconnect. A unique Some/None network intended for associative processing was stressed in the CAAAP

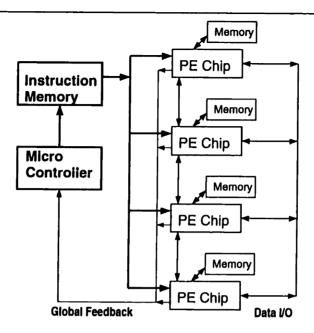

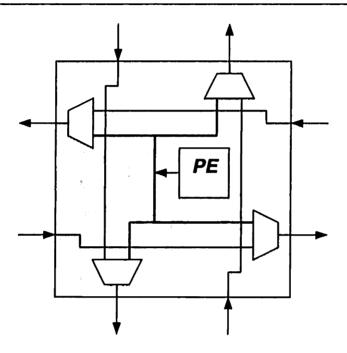

Figure 2-1: SIMD System Block Diagram. The five interfaces shown are: local memory, instruction distribution, global feedback, inter-chip communication, and data input/output. Although the PEs are shown arranged in an array, most architecture organize them in a 2-dimensional mesh.

architecture (Shu, Nash & Weems 1989) developed at the University of Massachusetts at Amherst. As in the polymorphic torus, network switches were locally controlled, but groups of processors could be electrically connected. This feature allowed efficient connected components and global statistics algorithms.

A number of recent research efforts promise to achieve substantially higher performance than these early designs. A 256-element SIMD array driven by an on-chip RISC-like processor has been designed at the University of Sheffield (Thacker, Courtney, Walker, Evans & Yates 1994). The performance is reasonable, given the number of processors, but is limited by the instruction issue rate of the RISC controller, the low I/O bandwidth, and the lack of off-chip memory support. The Supercomputer Research Center has developed a processor-in-memory chip which augments a 128 Kbit SRAM array with bit-serial processors at each row (Gokhale, Holmes & Iobste 1995). The performance of this design is rather low due to the small number of PEs and modest clock rate.

An alternate processor-in-memory MIMD/SIMD architecture has been developed by IBM (Kogge, Sunaga, Miyataka, Kitamura & Retter 1995). The Execube chip incorporates 8 16-bit PEs, each with 64 KB of DRAM memory, and can be operated in SIMD mode from a global instruction bus. The performance is again rather low due to the long cycle time of DRAM and because instructions are stored in the same memory as data.

An integrated micro-MIMD chip, integrating 48 16-bit processors and an interconnection

network on each chip has been designed at UC Berkeley (Yeung & Rabaey 1995). The IC delivers an impressive 2.4 GOPS on a variety of DSP algorithms and is designed to communicate efficiently with other chips. However, since each PE's instruction memory is only 8 words deep, with no provision for expansion, the architecture is not suitable for more complex algorithms.

A class of DSP chips, most notably the Texas Instruments C40 and the Analog Devices SHARC processors, have been designed to support efficient execution over data arrays and inter-processor communication. These appear more promising than the RISC based systems, but still lack performance.

Another technology that delivers comparable performance to Abacus and PADDI is the use of reconfigurable logic as exemplified by Field Programmable Gate Arrays. An array of programmable logic can be used to configure applications specific hardware and thereby obtain excellent performance. For example, research at DEC Paris have implemented algorithms ranging from Laplace filters to binary convolutions (Bertin, Roncin & Vuillemin 1993). If the per-chip performance is computed as aggregate performance divided by the number of FPGA chips in the system, each Xilinx chip delivers approximately 500 million 16-bit operations per second.

| Machine          | Performance | Clock | I/O BW | Men      | Mem BW   |       |

|------------------|-------------|-------|--------|----------|----------|-------|

|                  | 16-bit MOPS | MHz   | MB/sec | Internal | External | $\mu$ |

| TMC CM-2         | 8           | 8     | 8      | 32       | 16       | 1.5   |

| SRC TeraSys      | 20          | 10    | 5      | 80       | 5        | 1     |

| IBM EXECUBE      | 50          | 25    | 300    | 400      | 0        | .8    |

| TI C40           | 50          | 50    | 200    | 0        | 200      | .8    |

| MasPar MP-2      | 133         | 12.5  | 45     | 1600     | 45       | 1     |

| HP8000           | 200         | 200   | 800    | 0        | 960      | .5    |

| Sheffield DIP    | 320         | 40    | 160    | 2560     | 0        | 1     |

| Xilinx XC3090    | 500         | 20    | NA     | NA       | NA       | 1     |

| Berkeley PADDI-2 | 2400        | 50    | 800    | 14400    | 0        | 1     |

| MIT Abacus-1     | 2000        | 125   | 1000   | 32000    | 512      | 1     |

Table 2.1: Architectural performance comparison

It is unfair to directly compare the 16-bit performance of Abacus compared to the wider-width Execube and MasPar PEs, as they incorporate floating-point support. However, even granting a factor of five in area, their performance still lags Abacus. Both of these designs make the mistake of using single-ported register files. The implication of requiring three cycles to perform a single instruction is that three times the area could have been allocated to triple-porting the memory, and the performance per unit area would have remained constant. In this case, the area refers to the *entire* silicon area, including communication pads and support circuitry.

The only architecture comparable in performance is the Berkeley PADDI-2 chip, and it is not suitable as a general computing element as it can only store eight instructions per PE. Of course, when the computation task can be expressed as piping data through a systolic array, the PADDI is an ideal high-performance, low chip-count solution.

No other research SIMD machine in the literature even approaches the Abacus design in terms of performance per silicon area on low-precision integer operations. The advantage occurs for a variety of reasons, including an aggressive clock rate of 125 MHz, made possible by careful custom design, high density manual circuit layout, and the inherent advantage of RBP operations.

## 2.2 High-Speed SIMD Issues

Recently a number of researchers have started to address system-level high-speed SIMD design issues (Rockoff 1993, Allen & Schimmel 1995, Weems 1994). The consensus problems are clock distribution, instruction generation and broadcasting, non-local data access.

Clock Distribution Since the clock skew budget is typically less than 10% of the clock period, a 200 MHz SIMD array must maintain skew below 500 picoseconds. To overcome this problem, Weems (Weems 1994) proposes a loosely synchronized SIMD processor. This degree of complexity is somewhat surprising since commercial chip sets with tunable delay times are easily available, and the salphasic (Chi 1994) clock distribution scheme has been used to provide a 160 MHz clocks to 60 system boards with less than 200 psec of skew across a 10-foot-long system.

Instruction Broadcasting Rockoff (Rockoff 1993) believes that distribution of finely synchronized instructions to hundreds of PE chips is a fundamental limitation on the clock rate due to transmission skew. His doctoral thesis is based on the idea of using instruction caches internal to each PE chip to allow operation faster than the transmission limit. The approach appears to be a complex solution to a non-problem, since sufficiently frequent registers along the transmission path can resynchronize the instruction stream.

The cost of this retiming is increased latency in instruction distribution. Allen analyzes a tree-structured transmission and retiming model to determine an optimal number of stages. The model is mostly theoretical as it uses RC delays and clock rate as limitations instead of the actual transmission-line effects encountered at high speeds. Further, there is no good reason for different stages to have identical fanout factors, since there are differences both between inter-board and on-board wire delays, and between the receiving circuitry.

The Abacus system design presents a method for synchronized instruction distribution along widely varying transmission paths that adds programmable delay elements to the instruction pads on each chip and retimes the signals on a pin-by-pin basis. This scheme allows propagation variations on the order of several cycle times with a skew equal to the clock skew.

<sup>&</sup>lt;sup>1</sup> Mention Pixel-Planes 5!

Instruction Generation Another suggested bottleneck in SIMD performance is instruction generation. The traditional SIMD model is that instructions for operations such as 16-bit addition are sent from the host to the sequencer, where they are converted to a sequence of microinstructions to be executed by the PE array. Weems claims that between 20 and 50 RISC-like instructions are required to transform a single array instruction. The system design chapter presents three instruction generation techniques that in combination reduce the ratio of sequencer/array cycles to 1. In contrast, Weems proposes to solve the problem by substantially increasing the complexity of each PE chip to allow on-chip expansion of broadcast instructions.

Data Cache As in mainstream conventional microprocessors, high-speed implementations widen the gap between processor speed and main memory speed. The common approach is to insert a medium-speed memory between the small fast register file and the large slow main memory. SIMD machines are inherently cache-unfriendly, since any cache miss by any PE will cause the entire machine to stall, and with a large enough machine, such a miss is virtually guaranteed. Allen observes that as long as PEs are allowed only direct memory accesses, all PEs will either miss or hit at the same time, and therefore proposes direct-only-data caches. This is an interesting approach, but many vision and image processing algorithms are oblivious in the sense that their execution does not change as a function of data, and therefore the memory access patterns are known at compile time. As a result, the compiler can optimally manage the slower memory without using additional hardware at run-time.

High Latency Issues Allen points out that one of the costs of instruction synchronization via pipelined distribution is the increased latency of the array response to a sequencer command. This is an important issue, especially in the Abacus-1 design, which has a 10-stage pipeline. However, since the global OR computation already requires about 5 or 6 cycles, the extra two cycle cost of instruction pipelining is negligible, especially when the controller runs at least two (and possibly four) times slower than the parallel array. For any reasonable implementation, the pipeline cost is either zero or one one extra stall cycle per compare.

In the pathological case of a very tight loop, there is a software technique for reducing the effect of a pipeline stall. Most iterative code does not damage the solution if it executes an extra iteration or two. Our proposed solution is to unroll the loop, checking for completion only once every 3 or 4 iterations. Since iterative code usually executes for at least dozens of iterations, the extra two or three iterations at the end are reduced to a 10% cost.

## 2.3 Reconfigurable Architectures

The basic idea of RBP is the concatenation of several processing elements into a processing site. The advantages of the technique can be viewed from several angles. First, if an algorithm requires many data bits per pixel, then the silicon area of the ALU is small compared

with total data area, and therefore adding a few more ALUs will improve performance linearly, with a tiny increase in total area. This interpretation assumes that all data is kept on chip and physically near the ALU.

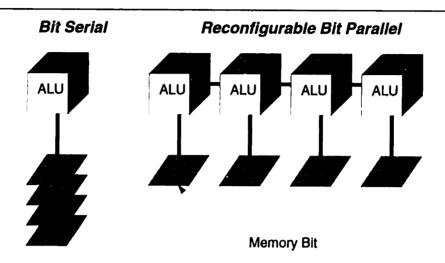

Figure 2-2: A bit-serial organization compared to a reconfigurable bit-parallel one. Each of the RBP processors is also capable of acting as a bit-serial unit, if appropriate.

Alternately, RBP may be viewed as a method of adding the appropriate number of registers to a processing site to minimize the frequency of expensive off-chip accesses. The improvement in performance is due mostly to decreased stall time rather than additional ALU bits.

The idea of dynamically changing the data path width to better match the algorithm requirements has been around since the earliest days of SIMD computing. The Illiac-IV, initiated in 1965 and completed in 1975 (Barnes, Brown, Kato, Kuck, Slotnick & Stokes 1968), had 64 64-bit PEs that could be partitioned as 128 32-bit PEs or as 512 8-bit PEs. Three years before its completion, work started in Britain on the Distributed Array Processor (DAP) (Parkinson & Litt 1990), a bit-serial machine whose PEs could be configured together with a ripple-carry path to perform 64-bit arithmetic. This capability was not central to the architecture and operated with one eighth the throughput of the bit-serial mode. A prototype was produced in 1976 and a commercial model in 1980.

The first VLSI-era member of the class, the reconfigurable processor array (RPA) (Rushton 1989) was developed between 1985 and 1989 at the University of Southampton. Although a chip was designed and fabricated, a full scale computer was not completed. The RPA uses a mixed approach to reconfigurability. Although each PE processes two bits at a time and a data word is shared among several PEs, considerable hardware resources are devoted to supporting bit-slice operations. As a result, each PE is quite complex for a fine-grained machine.

A substantially finer-grain architecture, Silt (Barman, Bolotski, Camporese & Little 1990),

was designed at the University of British Columbia between 1988 and 1990. The design took a minimalist path, exploring the approach of minimal area and high clock speed. The Silt chip led to the Abacus design presented in this thesis. Work on Abacus began in 1991, and a full-scale chip was fabricated in 1995.

In 1992, a reconfigurable processor, MGAP, was developed at the Pennsylvania State University. Its key distinction was the orientation towards a fully-redundant radix-4 arithmetic system. A second generation design, the MGAP-2, was completed in 1996.

Mainstream processors have recently rediscovered and fully embraced reconfigurable processing. Driven by multimedia applications with similar characteristics to image processing, Sun's UltraSparc, Hewlett-Packard's PA-RISC, and Intel's MMX chips all support the partitioning of the 64-bit data path into 8 independent byte-wide processors.

### 2.4 Architectural Studies

SIMD machines are an attractive class of architectures to study since the effects of data path enhancement can be easily isolated from issues of control circuitry or cache organization improvements. A number of studies have been done, especially for vision applications.

#### 2.4.1 Normalized Analysis

A methodology for comparing parallel computer performance was described by Holman and Snyder (Holman & Snyder 1989, Ho & Snyder 1990). They introduced the distinction between three types of analysis:

- cost-free analysis, where absolute performance is the relevant metric, and the amount

of consumed resources is not relevant. For example, cache studies are typically costfree analyses since the comparison metric is absolute performance, neglecting the

resource cost of the caches.

- 2. budget-constrained analysis, where different systems are compared under the constraint that they use identical amounts of hardware.

- 3. normalized analysis, where an improvement in a PE is compared to using the same hardware as the original PE, but using more processors.

The approach is based on the generally true observation that "There are two ways to improve any parallel architecture using additional hardware - by speeding up the processor elements or by adding more processor elements."

There are clearly situations in which neither approach is very effective and indeed can be counterproductive. For example, in memory-bandwidth or communication-limited designs, speeding up the PE is not going to have a substantial effect on performance. Similarly, if the computation is already fully parallelized, with one PE per data item, adding PEs cannot improve the performance.

The curious part of the work is that while analyzing optimal data path size, due to a fraction inversion error, the authors drew the exact opposite conclusion from the data. Specifically, analysis assumed that any area applied to making a PE more powerful could instead be applied to create a larger number of simple PEs, and that the resulting speedup is linear. Similarly, the area cost is linear in the size of the register file and ALU, and quadratic in the size of the shifter.

The machine composed of many simple elements is termed the XPE machine, and the machine composed of fewer complex elements is the IPE machine. The basic unmodified architecture is the BA (base architecture) machine. They derive the following performance metrics for execution time, assuming SU is the speedup provided by the enhancement, fis the fraction of instructions affected by the enhancement, and c is the chip area of the respective machines.

$$T_{IPE} = T_{BA} \left( 1 - f + \frac{f}{SU} \right)$$

$$T_{XPE} = T_{BA} \frac{c_{BA}}{c_{IPE}}$$

(2.1)

$$T_{XPE} = T_{BA} \frac{\dot{c}_{BA}}{c_{IPE}} \tag{2.2}$$

Combining the two yields

$$SU_{eff} = \frac{T_{XPE}}{T_{IPE}} = \frac{c_{BA}}{c_{IPE}} \left( 1 - f + \frac{f}{SU} \right)^{-1}$$

(2.3)

To choose an example from the paper, consider a 4-bit PE and a 32-bit PE, with area ratio approximately 1:8. The Batcher implementation has f = 0.75, leading to su = 0.36 (the paper computed 0.41). This is as expected, since the area penalty was a factor of 8, while the performance improvement was only a factor of 3. Nevertheless, the authors conclude that "the best performance is obtained with a 32-bit data path".

Chapter 6 shows that the determining factor in this design choice turns out to be the amount of silicon area dedicated to the memory, and the memory access patterns of the algorithm. The Holman/Snyder model does not account for the diminished storage capacity of each simplified PE. If the algorithm needs to access 16 32-bit words per pixel for one iteration, and only 2 32-bit words are available, the machine will perform a large number of memory spills. With the growing gap between processor and memory speeds, this effect becomes critical.

#### Simulation-Based Performance Evaluation 2.4.2

A simulation approach to SIMD performance evaluation was taken by Herbordt (Herbordt 1994). His trace compilation technique compiled traces generated on an abstract virtual machine for a specific target architecture. The technique can be two orders of magnitude faster than a detailed simulation. This flexibility allows quick evaluations of different architectural parameters, such as register file size or communication latency.

Although the centerpiece of his dissertation is the trace compilation methodology, the tool was used to perform a number of architectural studies, and resulted in some interesting conclusions. For example, some studies showed that increasing ALU width substantially improved performance only up to a width of 8 bits. After that, performance improved only slightly.

The simulator is an excellent tool for evaluating system performance. It allows the architect to experiment with different virtualization ratios, datapath width, register file size, and off-chip memory latency. The potential danger is the unknown effect of the trace compiler quality on performance. The other inherent problem with the methodology is that algorithms were not optimized on a per-case basis: the same address trace was used for a wide variety of system parameters. Algorithms designed for the virtual machine are not necessarily optimal for a large memory or narrow datapath variant. Similarly, the virtual machine compiler generated code for a uniform memory access model, which is almost guaranteed to be suboptimal for a contemporary machine with a high disparity between on-chip and off-chip access times.

Nevertheless, many of the results in Herbordt's work can be used directly as a starting point for selecting good concatenation factors for reconfigurable architectures.

### 2.4.3 Dynamic Concatenation

The performance advantages of reconfigurable architectures due to memory limitations were first evaluated by Audet et al (Audet, Savaria & Houle 1992), who referred to reconfiguration as the Dynamic Concatenation Approach. The goal of the research was to determine the optimal number of PEs to be grouped into a processing site (PS), given particular hardware and algorithmic parameters. This number is called the concatenation factor, w.

Although the critical issue of off-chip memory traffic minimization was addressed, the published work contained some shortcomings. For example, a particularly strange pipelining model was chosen, and execution times were scaled by factors based on pipelining effects. The method of deriving these parameters is based on arbitrary assumptions about compilers and hardware implementation. Quantifying pipelining effects applies more to a VLIW-style system where multiple functional units can be triggered by a single instruction. The model appears to apply to multi-cycle, relatively complex functional units, which are not usually present in simple, small SIMD PEs.

The model assumes a static type of register assignment: the most frequently used variables are placed into registers, and the rest into memory locations. Algorithms that use one variable frequently in the first half of operation, and use another during the second half, would be forced to assign different registers even if their use did not overlap in time. As the methodology used UNIX-based C profiling tools to determine the often referenced variables, it is not clear whether the compilation was optimized for the right number of registers, or whether loop unrolling optimizations were made.

Virtualization requirements were not considered and program segments appear trivially short. Further, the only program example shown in detail is of a systolic type. Short

computation chains between virtual PE synchronizations could lead to a large number of register save and restore operations. Virtualization could play a large role due to the time involved in restoring context.

## 2.4.4 Phase-Specific Reconfiguration

Unlike earlier comparisons that maintained the same concatenation factor (CF) throughout an algorithm, this work broke vision algorithms into phases, and evaluated the performance of a particular CF on each phase (Ligon & Ramachandran 1994). They found that changing CF between phases could improve performance by approximately 25%.

# Chapter 3

# **Abacus Chip**

This chapter describes the design, implementation, and testing of the Abacus-1 chip in considerable detail. After reading this section, the reader should understand the issues involved in the design of a high-speed SIMD computer. The discussion focuses on the implementation, assuming that the broad architectural issues were previously decided. Of course in reality the design did not proceed unidirectionally from architecture to implementation; low level issues significantly affected the architecture.

The design goals of the Abacus-1 chip were not simply to obtain the highest possible performance, but more importantly to investigate issues of high-speed SIMD computers. Therefore, performance improvements at the cost of higher complexity and lower clock rate are less desirable than those due to a higher clock rate. Further, the high speed must transfer over to the system level, so the chip design must handle inter-chip synchronization effectively. Proceeding up the hierarchy, the lessons learned from the design must apply to practical systems. A critical requirement of real systems is the capability of expanding the memory allocated to each processing element. Finally, the system must support high speed (at least real-time) I/O of image data.

A large collection of on-chip subsystems is required to satisfy these goals. The subsystems can be divided into three broad categories: the processing element core that performs the computation; the off-chip interface that delivers network, instruction, and data streams to the core; and the control logic that binds the two together. This chapter addresses each of these categories in turn.

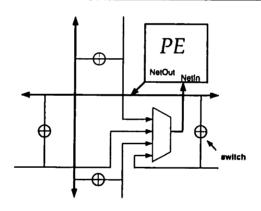

### 3.1 Abacus PE Architecture

The Abacus processing element (PE) consists of 64 1-bit registers organized into two banks. There are two 3-input ALUs, each of which takes two inputs from its memory bank and one input from the other bank. The four available data bits allow complex boolean functions, and two result bits can be written in each cycle, one bit to each bank.

Figure 3-1: Processing Element Block Diagram.

A PE also has a 1-bit network interface and background I/O interface. Seven of the registers are used for control, leaving 57 general-purpose registers.

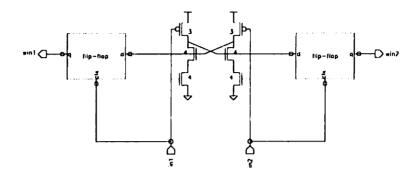

Figure 3-2: Network

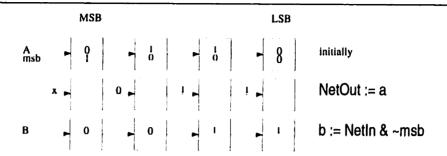

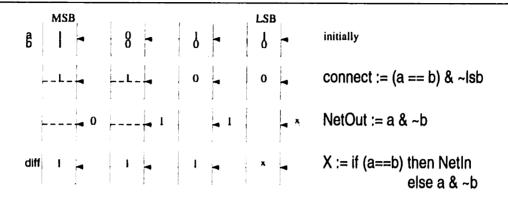

Activity Register Conditional execution of an if (cond) then ... else ... sequence on SIMD arrays operates by disabling those PEs for which cond is true, executing the true branch, disabling the other set of PEs, and executing the false branch. One of the Abacus PE registers serves as the activity bit which, when cleared, disables computation by inhibiting the write of the result to the destination register.

The ability of the ALU to serve as a multiplexer greatly reduces the use of the activity register. For example, the sequence if A then  $B \Leftarrow C$  incurs two cycles of overhead if implemented with the activity register. Alternately, the operation can be expressed as  $B \Leftarrow$

$\max(A,C|B)$ , eliminating all overhead.

Network The reconfiguration network serves for both bit-slice interconnection and interword communication. The network is a wired-OR reconfigurable mesh. As in a conventional mesh topology, each PE listens to the output node of one its four mesh neighbors. Each PE is provided with a configuration register that specifies which neighbor to listen to. Unlike a mesh, each PE-can connect its output node to the selected neighbor's output node. Shorted nodes behave as a wired-OR bus: if any PEs in a connected chain send a 1, all PEs listening to the chain receive a 1.

Background I/O Each PE contains a data plane (DP) register, used for background off-chip data transfers. The DP registers of PEs in a column of the array form a 32-bit shift register. At the edge of the PE array, the 32 shift registers are connected to an off-chip memory port. These registers can be shifted without interfering with PE computation. Although the DP register is not used in arithmetic operations it is essential in hiding the latency of external memory accesses.

### 3.2 Processing Element Core

#### 3.2.1 Memory

Design Processor memory size is a critical design parameter as it is the main determinant of the overall processor size and therefore the number of PEs per chip. Too little on-chip memory, and machine performance becomes limited by off-chip memory bandwidth; too much memory and the amount of processing power on a chip drops. Thus, the memory size should be carefully chosen based on extensive simulations.

In the case of the Abacus-1 chip, the choice was mostly guided by intuition. There are only a few feasible sizes, ranging between 32 and 1024 bits. The low end of the range is inefficient as much of the memory is consumed by configuration and temporary bits. The 32-bit configuration, in vertical mode, cannot perform any algorithm that requires more than two 16-bit data items. The 1024-bit configuration, in horizontal mode, allocates 1 Kword per pixel site, which is far more memory than needed. Two other disadvantages of larger memories are a longer access time, and more address bits, which translates directly into higher instruction bandwidth, already one of the more challenging board-level design tasks. The Abacus-1 design has 64 bits of memory per PE.

Implementation The 64-bit register file is arranged as two banks of eight rows and four columns. Each cell is a standard six-transistor SRAM cell. The bit and bit lines are used single-ended to provide two read ports, allowing four bits to be read and two written in each cycle.

The bitlines are precharged to  $V_{dd} - V_T$  to speed pulldown time and reduce power dissipation. Precharging is done through the column select transistors, further reducing power by charging only those bitlines that are about to be read.

The SRAM cell is susceptible to false writes, especially because the bitlines are typically not charged to opposite values. Thus, the high-capacitance bitlines, charged to opposing values during the read phase, can act as a line driver, overwriting cells not selected by the column selects. This problem is avoided by shorting the bit and bit lines during the precharge interval, even if those lines are charged. In other words, all bitline pairs are shorted, but only the ones to be read are charged.

One of the key space-saving ideas was the integration of the five control registers and the network interface into the SRAM array. The initial design included fully static master-slave flip-flops, multiplexers to connect them to read busses, and separate control wires. This auxiliary circuitry substantially increased the non-ALU PE area. In the current implementation, edge cells in the SRAM array, together with buffers that isolate the internal data storage node, are used as control registers. In the case of the network and data plane registers, the multiplexing occurs inside the SRAM cell.

#### 3.2.2 ALU

Design The main design issue of the ALU is its range of computations. The initial ALU design was a 4:1 multiplexer that could compute all 16 two-input one-output functions. Computation of a full binary one-bit addition therefore required five cycles, emulating all five 2-input gates.

The limited complexity is due to available data sources and sinks. A single-ported memory bank can produce only two bits for reading, and can absorb only a one bit result. If operations such as addition are required, the extra input bit must come from another source such as an auxiliary register or the communication network.

Previous bit-serial computers incorporated dedicated adders and carry registers. Abacus does not follow this approach because of the additional area and because the circuitry is only useful in vertical mode. A dedicated full adder circuit would be useful in horizontal mode, assuming its outputs could be steered appropriately, but it requires three input bits while the memory only produces two per cycle. The Abacus design's solution was based on the realization that the memory required much more area than the ALU. Splitting the memory into two banks doubles the memory bandwidth and adding another ALU doubles the peak computing power. If the ALU requires one tenth of the memory area, the twin-bank, twin-ALU (TBTA) design occupies 1.1 times the area, but has 2.0 times the performance, for an overall advantage of 1.8 over the single ALU.

A significant penalty occurs because the chip is pad-limited. The inner pad-ring is arranged in a 56 by 44 rectangle. Without the 20 extra instruction bits (corresponding to 10 double-cycled pads) the pad ring could be reduced to a 51 by 44 rectangle. Assuming a 170 micron pad pitch, the area decrease is 6.4 mm<sup>2</sup>. Since the entire PE array occupies 38.4 mm<sup>2</sup>, the extra instruction bits cost an additional 17% overhead. As long as the design remains pad

|                  | SBSA |               | TBTA |           |

|------------------|------|---------------|------|-----------|

| Circuit Element  | 1 AL | 1 ALU, 1 bank |      | U, 2 bank |

|                  | Qty  | Area          | Qty  | Area      |

| Метогу Аггау     | 1    | 205           | 2    | 102       |

| Column Mux       | 8    | 20            | 8    | 20        |

| Read/Write Logic | 1    | 18            | 2    | 36        |

| Aux Logic        | 1    | 64            | 1    | 64        |

| ALU              | 1    | 38            | 2    | 76        |

| Network          | 1    | 52            | 1    | 52        |

| Total            |      | 397           |      | 452       |

Table 3.1: Silicon area requirements of the single-banked, single-ALU and the twin-banked, twin-ALU designs. As expected, silicon area increases by only 15%.

limited, this effect will grow worse as technologies scale down, mostly because the pad size stays constant while the PE density improves. Thus, any design decision that increases the number of chip pads should be considered carefully. This is an important example of how architectural analysis must be done at all levels of design in order to be accurate.

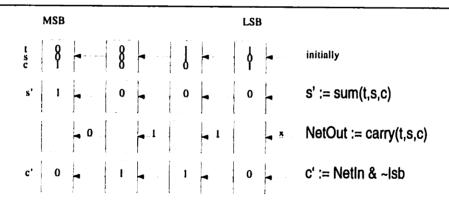

The algorithmic advantage is more difficult to quantify. Each 3-input ALU can perform an arbitrary 3-input operation each cycle, which could take a 2-input ALU at least 3 (and as many as 5) cycles. To see this, consider the an arbitrary function of three boolean variables Z = f(A,B,C). Using the Shannon expansion, Z can be expressed as

$$Z = \overline{A} \cdot f_{A=0}(B,C) + A \cdot f_{A=1}(B,C)$$

(3.1)

where the two subfunctions are obtained from the truth table entries corresponding to the cases where A is 0 and 1 respectively. Most useful functions are actually simpler. For example, consider the the multiplexing operation Z = (!A & B) | (A & C). For this function,  $f_{A=0}(B,C)$  is simply B, and steps 1 and 3 of Figure 3-3 can be eliminated.

Converting to two 3-input ALUs improves the peak bit-manipulation performance by a factor of ten, but several effects limit this improvement. First, the addressing is limited to sharing certain bits between the two banks. Second, these five-cycle operations are relatively rare. Third, data dependencies require waiting for bits to arrive from the network.

Table 3.2 shows the number of cycles required per arithmetic operation, including reconfiguration overhead. The ratio is about 1.75. Of course, the proper instruction mix for real applications should be evaluated for true improvements, but this analysis suffices to bound performance improvement in the range of 1.25 to 2.1.

There is another subtle effect of a more complicated ALU. A 2-input ALU can require up to two temporary storage locations to evaluate most 3-input functions. When operating near

<sup>&</sup>lt;sup>1</sup>This function is used frequently when some bits must be conditionally updated. The idiom is Z := mux(flag, Z, newZ).

T1 = f0(B,C) T1 = T1 & !A T2 = f1(B,C) T2 = T2 & A Z = T1 + T2

Figure 3-3: Evaluation of an arbitrary 3-input function by a two-input ALU. Two auxiliary memory locations are required.

| Operation  | SBSA     | ТВТА     |

|------------|----------|----------|

|            | (cycles) | (cycles) |

| Add        | 9        | 4        |

| Shift      | 4        | 3        |

| Grid Move  | 7        | 6        |

| Accumulate | 10       | 4        |

| Average    | 7.5      | 4.3      |

Table 3.2: Number of cycles required for common operations in horizontal mode. The count includes reconfiguration cost.

the memory capacity, two memory spills can have a substantial effect on performance.

We can now evaluate the overall advantage of the twin ALU design. The area cost is dominated by the pad ring increase, and is a factor of 1.35. The performance improvement is 1.75. Thus, the overall advantage of the design is only about 30%. This advantage will increase slightly as compiler technology improves and as memory accesses become more expensive.

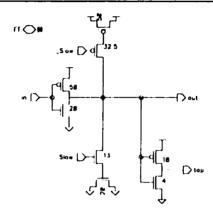

Implementation. Each ALU is implemented as a precharged 8-to-1 multiplexer that uses three data bits to select one of eight instruction bits. Initial design used predecoded cells but this was slower and larger due to the non-regularity. This design does have four transistors in the pulldown path, but the timing and capacitances are designed to minimize the body effect and reduce charge-sharing problems.

Immediate Constant. The ALU also incorporates an additional circuit that allows the architecture to support effective constant distribution. Without this feature, there is no clean method of distributing a run-time value generated in the scalar unit to the array. Indeed the only way of transferring such a value would be to send it via the image I/O interface.

Instead, the output of the left ALU passes through a NAND gate controlled by a global

wire common to each column of PEs. In normal operation, these 32 global "literal" wires are held at 1. When a constant is to be loaded, the instruction decoder generates a set ALU op code, and loads the literal bus with the logical inverse of the constant. Thus, in every column whose bus is at 1, the result will be forced to a 0, as desired.

#### 3.2.3 Network

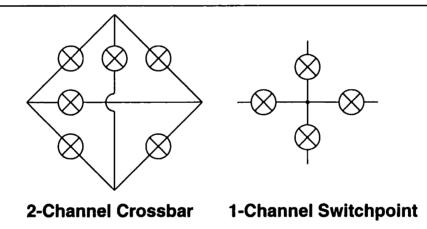

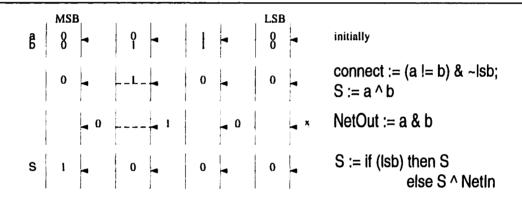

Design The two questions in network design are where the PE obtain its network data and how does it route data around itself. Two alternatives of routing data are shown in Figure 3-4. The first, the two-channel crossbar, allows messages to pass in a wide variety of directions. For example, the PE can connect the north port to the east port while simultaneously connecting the west port to the south. The second is far less flexible, and can only make one connection.

The original network design used four independent switches in a mesh topology. Each switch had a dedicated control register. The independent switch control allowed many cluster configurations.

Figure 3-4: Various network types. The Abacus type is of the single channel, but even more restrictive in that each PE can turn on only one switch.

The price of this flexibility is additional registers and increased reconfiguration time. If a register is allocated to each switch, the four registers represent 5% of the total addressable registers. More importantly, reconfiguration time doubles. Even with dual ALUs (which were added primarily to speed reconfiguration), two cycles are required to change topology. Since reconfiguration may be required after each arithmetic operation, and since most operations require only two or three cycles, the additional 1 cycle penalty is a performance hit of approximately 20%.

Reconfiguration time can be reduced at a slight loss in flexibility. Since information flow in arithmetic operations is usually along the MSB/LSB path, configuration in a line is usually

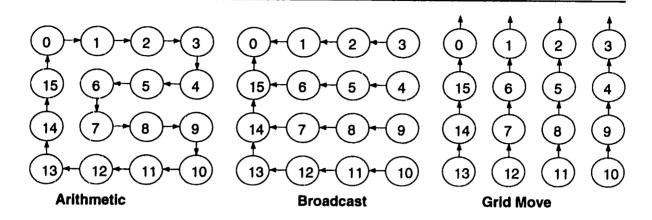

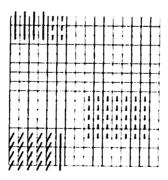

Figure 3-5: Various network configurations. Arithmetic, bit broadcast, and mesh move modes are shown. For example, broadcast of a bit to all 16 cluster elements can be done with only 8  $(2\sqrt{N})$  switch delays if the cluster is configured as a tree with fanout of 4.

sufficient. The design implemented in Abacus-1 incorporates a decoder to select only one of the four switches, and a *connect* configuration bit that controls whether any of the switches are activated at all. The addressing cost of the two approaches is not substantially different: three registers instead of four. But now, changing reconfiguration directions requires only one cycle, and conditional bypass, another frequent operation, also requires only one cycle instead of two.

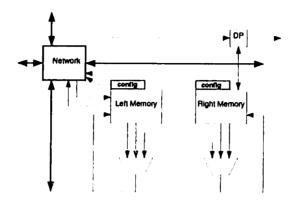

Figure 3-6: Network Block Diagram. Magnified view and mesh view.

Implementation. The on-chip communication network consists of a precharged output node and four isolating switches. The node is a simple precharged inverter whose input is driven by the network output register. The four switches are NMOS transistors driven by

#### a 2:4 precharged decoder.

Communication with signaling times longer than a cycle period is performed by controlling network precharge via software. As long as precharge is turned off, processors connected to a bus node continue to discharge it.

Propagation delay across a series of pass transistors is usually quadratic in the number of devices. This delay is greatly reduced by a local accelerator circuit at each node which regeneratively pulls a node to ground as soon as the node voltage drops by a transistor threshold. The circuit is a dynamic NORA style circuit and is well suited to the precharged operation of the network. We found it to be several times faster than an implementation based on a complementary inverter. At the nominal process corner, simulations show that a bit propagates through 18 switches and long network wires in one 8 ns cycle.

Figure 3-7: Network accelerator in the NORA circuit style.

This circuit has a noise margin of  $V_T$ , so careful layout was done to reduce coupling capacitance to the pre-discharged node. Further, the chip is provided with on-chip bypass capacitance and over 200 power and ground pins to reduce dI/dt noise.

#### 3.2.4 Data and I/O Planes

The architecture supports a background loading mechanism for both the external memory data and image data. Data is shifted through the PE array without interfering with computation. One memory location in each PE is dedicated as the data plane (DP) registers. All DP registers in a column are connected in a 32-element shift register. This shift register is clocked by a global signal. The PE addresses the DP register as a normal SRAM cell, and is not aware of the alternate write path.

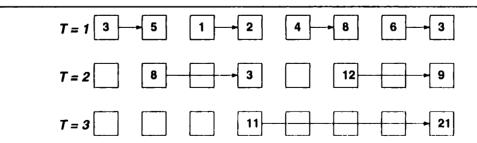

#### 3.2.5 Global OR Operation

The global OR (GOR) mode is used to signal completion of some computation by the entire PE array to the sequencer. Off-chip, the GOR is computed by dedicated logic. On-chip, the GOR can be computed with the multiple-writer capability of the network. In this mode, all PEs connect their network nodes into one chip-wide node. The shortest propagation path is obtained by connecting all PEs in a row to the left-most PE of that row, and then connecting all left-edge PEs together vertically, as in Figure 3-5. The on-chip evaluation time is five cycles in the worst case.

#### 3.2.6 Layout Summary

The simplicity of each PE resulted in a compact, 83 micron by 453 micron implementation in a 2.6 micron contacted metal pitch technology.

| Subsystem  | Агеа                             | Percentage |

|------------|----------------------------------|------------|

| <u></u>    | $\left(\mathrm{K}\mu^{2}\right)$ |            |

| Memory     | 22.9                             | 61.0       |

| ALU        | 6.3                              | 16.8       |

| Network    | 6.2                              | 16.6       |

| Misc PE    | 1.2                              | 3.1        |

| Data Plane | 1.0                              | 2.6        |

Table 3.3: PE Area resources

This data differs from the earlier table in that configuration registers are now allocated to the resource they serve instead of to the memory array. For example, there are four control registers (2 select, 1 connect, 1 data) dedicated to the network. Similarly, two are dedicated to the I/O and data planes.

Figure 3-8: PE Layout with the second layer of metal removed. ADD OVERLAYS

## 3.3 On-Chip Signal Distribution

A previously unanticipated design task was the challenge of distributing control signals to the PEs. As discussed in Section 3.3.3, there are four phases in the clock cycle, and each phase must complete before the other can begin. For example, all word lines in the register file must be unasserted while bitlines are being precharged, and any overlap may cause memory cells to be overwritten. This nonoverlap is guaranteed by separating the clock phases sufficiently to account for the worst case rise/fall times. Signal transitions that occur in the same phase but must follow each other are separated by inserting an inverter or two as delay elements.

There are two problems with this approach. Given 8 ns cycle time of the PE, each of the four phases has only 2 ns to rise, stay level, and fall. This means that even if the level time is 1 ns long, each rise/fall time must be 500 ps or less. This is an aggressive RC product, given the long and narrow signal wires and the high gate loading of the wire. The usual technique of simply widening the signal wires cannot be used due to the wire density. The second problem is that even if the four phases can be safely separated, non-overlap within the cycle by using inverters as delay elements may not work because the variation in wire loading may dwarf inverter delays. Both of these problems can be addressed by local buffering of the global signals.

#### 3.3.1 Load Equalization

Local buffering both reduces the load on each wire and decreases the variation between signal arrival times due to unequal loads. This section describes the calculations used to obtain the load values, wire widths, and row buffer sizes.

In addition to reducing the capacitive load by local buffering, the RC product was improved by reducing wire resistance by widening the signal traces. Although the wire capacitance increases, the lowered resistance decreases the effect of the load capacitance, as shown in Equation 3.2.

$$\tau = RC = (R_{\text{wire}} + R_{\text{driver}}) (C_{\text{wire}} + C_{\text{driver}})$$

(3.2)

The equation can be made more rigorous to account for the distributed wire loads and the lumped driver load, but those calculations do not capture the most difficult characterization: the variation in wire capacitance due to fringing fields and to the material underlying the wires. Further, the wire pitch, and therefore width and spacing, undergoes different constraints in different parts of the circuit. Instead of obtaining an analytical solution for the wire width, spreadsheet models were developed for common wiring situations and driver configurations, and used to determine case-specific trace widths.

#### 3.3.2 Layout Issues: The Trench

The Abacus-1 design had to deliver 76 signals across a 1 cm chip with very little skew even though the array is tolerant of gradual signal skew across the part since communication is purely local. Problems arise in two cases: intra-PE signal skew and interfaces to logically synchronous zones at at the pad ring. The task was decomposed into two parts: delivering the signals to the horizontal row drivers and then their outputs. Vertical signal delivery was not an issue due to the low resistivity of the metal 3 layer. The design easily tolerated high uniform latency in instruction distribution so the row buffers could be composed of several scale-up stages. As a result, the loads presented to the vertical wires were that of minimum sized inverters, and therefore dwarfed by wiring capacitance. The vertical wires were metal-3, 3.2 microns wide, and spaced by 3.3 microns. The nominal capacitance of a 7 mm vertical wire is 2.5 pF, and the nominal resistance is 75 ohms. The distributed RC delay of this wire is only 184 picoseconds.

The problem arises after the signals have been delivered on the vertical wires. The row buffers are rather large, and there are 152 of them packed into one PE height, 76 for each side. This occupies a significant area, and spans 1.1 mm! Fully one-sixth of the core area is dedicated to these buffers. To connect a row buffer at the extreme edge of the trench to the vertical wire requires a horizontal wire of 500 microns. This horizontal load almost doubles the signal capacitance, and therefore skew. Also, a little bit of horizontal skew is introduced, as the row buffer output wires end up differing in length, depending on the buffer position.

#### 3.3.3 Timing

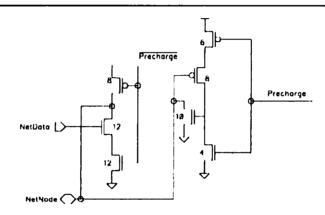

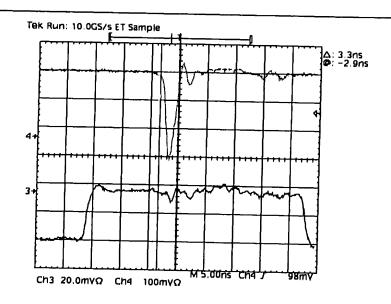

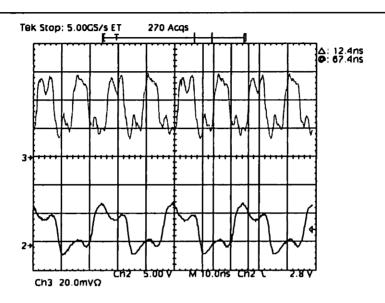

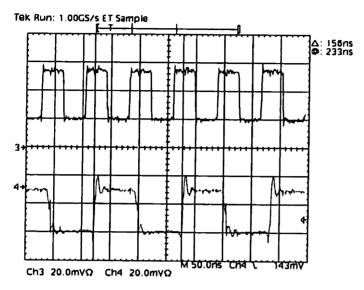

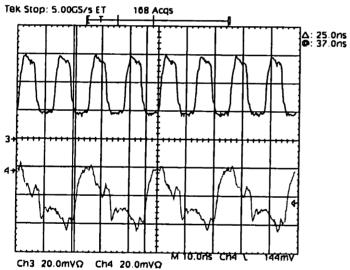

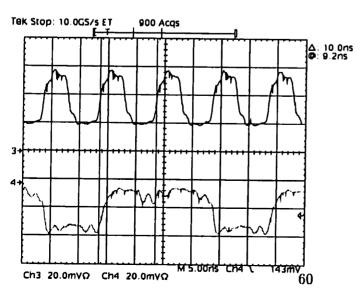

The processor timing is driven by the basic design choice of double-cycling the register file to perform a read and a write operation in one cycle. The cycle starts with the instruction clock, which clocks out the decoded instruction bits. At the same time, the word lines are gated off to avoid overwriting memory cell contents in the upcoming precharge interval. After the word lines are safely off,, the bitline precharge signal is asserted. This signal enables precharge transistors onto the A and B busses, charging them, and the bitlines that are about to be read. The column selects must therefore be stable at their read phase values during this phase. A circuit diagram of the memory system is shown in Figure 3-9.