## **Low Power Scalable Encryption For Wireless Systems**

by

## James R. Goodman

B. ASc. Electrical Engineering University of Waterloo, Canada, 1994

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY August 28, 1996

© 1996 Massachusetts Institute of Technology All rights reserved.

| Author      | •••••                       | *************************************** |

|-------------|-----------------------------|-----------------------------------------|

|             | Department of Electrical Er | gineering and Computer Science          |

|             | -                           | August 28, 1996                         |

| Certified b | ру                          |                                         |

|             |                             | Anantha Chandrakasan                    |

| A           | nalog Devices, Inc.Career   | Development Assistant Professor         |

|             |                             | Thesis Supervisor                       |

| Accepted 1  | by                          |                                         |

| •           | •                           | F. R. Morgenthaler                      |

|             | Chairman, Debartment        | Committee on Graduate Students          |

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

ARCHIVES

OCT 1 5 1996

| • |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

## **Low Power Scalable Encryption For Wireless Systems**

by

#### James R. Goodman

Submitted to the Department of Electrical Engineering and Computer Science on August 28, 1996, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering.

#### **Abstract**

Secure transmission of information is critical for many wireless applications. Wireless transmission imposes constraints not found in typical wired systems such as low power consumption, tolerance to high bit error rates, and scalability. A variety of cryptographic algorithms have been analyzed for their suitability to low-power wireless systems, and low power techniques have been developed to reduce their power consumption. Several test chips were designed, fabricated, and tested to verify the results proposed within this work. in addition, a model for error propagation in block ciphers is proposed and verified through experimentation.

Thesis Supervisor: Anantha Chandrakasan

Title: Analog Devices, Inc. Career Development Assistant Professor

## Acknowledgements

First and foremost I'd like to say thank you to my advisor Anantha Chandrakasan who's sense of humour, patience, and constant drive (not to mention funding...) helped me finally get this damn thing done!

Thanks also to the members of "ananthagroup" for all of their help over the last two years: to Raj "Oh my god! You're on fire!" Amirtharajah for reminding me that everyone suffers here in Hell, to Vadim "Cadence is broken...." Gutnik for being a well of knowledge that I frequently drank from, to Abram "Where does he find time to be a father?!" Dancy for suffering with me through the TSMC experience, to Wendi "It's only 5 flights of stairs..." Rabiner for being the only one of us sane enough to stay away from chip design, to Duke "the XOR man" Xanthopolous for catching my mistakes when I was too tired to notice them myself, and Tom "I'm off to make real money." Barber for his constant friendship and transport to and from Analog Devices.

I'd also like to thank my roommates Phillip "It only started 20 minutes ago." Alvelda for the bad movies and great friendship, and Misha "The Anti-christ of Driving." Bolotski for being a Cadence god, and all around great friend. And let us not forget Tony, the long-lost brother that I never knew I had until I showed up for hockey that first month here at MIT. I owe you a lot my friend, you kept me going through the rougher spots of my stay.

Lastly I'd like to thank my family whom I owe everything: my sister Lisa and her husband Cory for pretending to recognize me when I came home every Christmas, my "Dad" Milt who is a gentleman in every sense of the word and more of a father to me than anyone else in this world, and my mother Cathy who I only wish were still here to share this with me. I miss you so very much Kate, there isn't a day that goes by that I don't think about you -- I love you very much.

For Kate,

# **Table of Contents**

| 1 | Introduction                                                     | 14 |

|---|------------------------------------------------------------------|----|

|   | 1.1 Low Power Design Basics                                      | 15 |

|   | 1.2 Cryptography For Wireless Systems and Thesis Scope           | 18 |

|   | 1.3 Driver Application                                           | 19 |

| 2 | Introduction to Basic Cryptography                               | 22 |

|   | 2.1 General Classification of Algorithms                         |    |

|   | 2.1.1 Asymmetric Algorithms                                      |    |

|   | 2.1.2 Symmetric Algorithms                                       |    |

|   | 2.2 Block Cipher Algorithms                                      |    |

|   | 2.3 Stream Cipher Algorithms                                     |    |

|   | 2.3.1 Design Criteria for Keystream Generators                   |    |

|   |                                                                  |    |

|   | 2.4 Quadratic Residue Generator                                  |    |

|   | 2.5 Comparison of Algorithms (Block Ciphers vs. Stream Ciphers)  |    |

|   | 2.5.1 Figh Bit Error Rates and Error Propagation                 |    |

|   | 2.5.3 Buffering Requirements                                     |    |

|   | 2.5.4 Decoupling the Encryption Function                         |    |

|   | 2.6 Scalability                                                  | 35 |

|   | 2.7 An Existing System - the Group Special Mobile (GSM) Standard | 37 |

| 3 | LFSR-Based Stream Cipher Systems                                 | 40 |

|   | 3.1 Shrinking Generator                                          | 40 |

|   | 3.2 Self-Shrinking Generator                                     | 42 |

|   | 3.3 Alternating-Stop-and-Go Generator                            | 44 |

|   | 3.4 Proposed GSM Cipher (A5)                                     | 45 |

|   | 3.5 Estimating the Power Consumption                             |    |

|   | 3.6 Reducing the Power Consumption                               |    |

|   | 3.6.1 Conventional Supply Scaling                                |    |

|   | 3.6.2 Parallelizing the LFSRs                                    | 50 |

|   | 3.7 Stream Cipher Test Chip Design                               | 52 |

|   | 3.8 Preliminary Test Results                                     | 57 |

| 4 | QRG-Based Stream Cipher Systems                                  | 62 |

|   | 4.1 Some Basic Number Theory                                     | 62 |

|   | 4.2 Security of the QRG                                          | 64 |

|   | 4.3 Perio  | od of the QRG                                        | 65  |

|---|------------|------------------------------------------------------|-----|

|   | 4.4 Effi   | ciency of the QRG                                    | 67  |

|   | 4.5 Mod    | dular Multiplication Algorithms                      | 67  |

|   | 4.5.1      | Chinese Remainder Theorem                            |     |

|   | 4.5.2      | Morita's Algorithm                                   | 69  |

|   | 4.5.3      | Orup and Kornerup's Algorithm                        | 70  |

|   | 4.5.4      | Takagi's Algorithm                                   | 70  |

|   | 4.6 Red    | ucing Power Consumption                              | 72  |

|   | 4.6.1      | Conventional Supply Scaling                          | 74  |

|   | 4.6.2      | Pipelining and Parallelizing the Computation         | 74  |

|   | 4.6.3      | Variable Supply Voltage                              | 74  |

|   | 4.6.4      | Load Averaging                                       | 77  |

|   | 4.7 Scal   | lability                                             | 80  |

|   | 4.8 Test   | t Chip Design                                        | 82  |

|   | 4.9 Prel   | iminary Testing                                      | 87  |

| 5 | Conclusion | ons and Future Work                                  | 90  |

|   | 5.1 Futu   | ıre Work                                             | 91  |

|   | 5.1.1      | Low Power Hybrid System                              |     |

|   | 5.1.2      | Key Exchange and Authentication                      |     |

|   | 5.1.3      |                                                      |     |

|   | 5.1.4      | Modular Multiplication Algorithm Development and Imp |     |

| R | eferences  |                                                      | 94  |

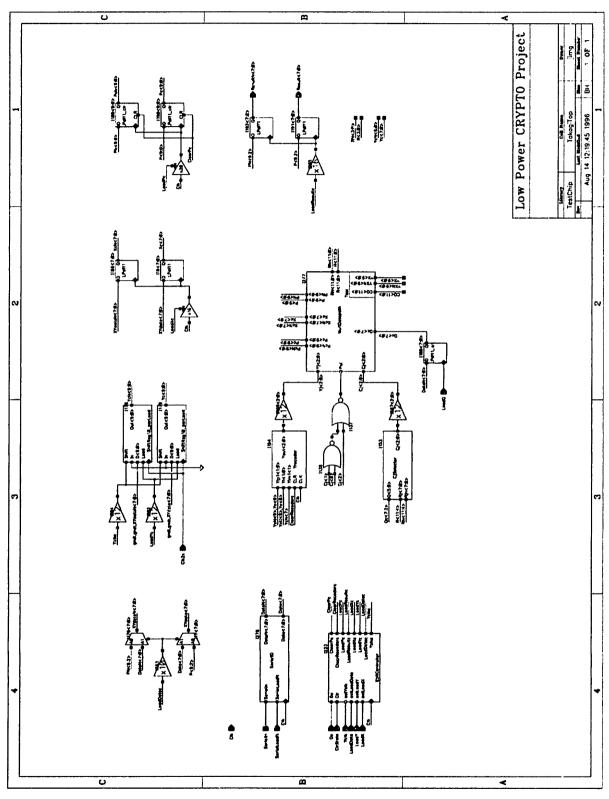

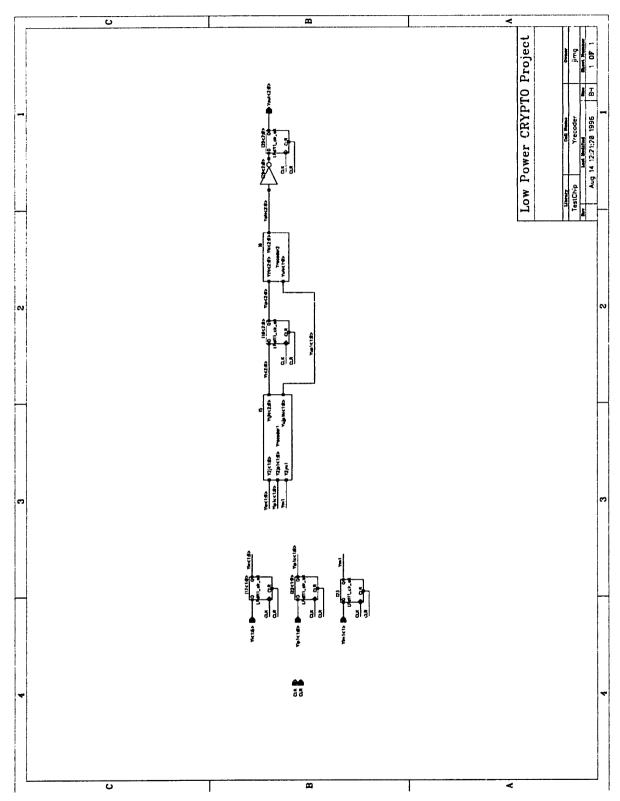

| A | Stream C   | ipher Schematics                                     | 98  |

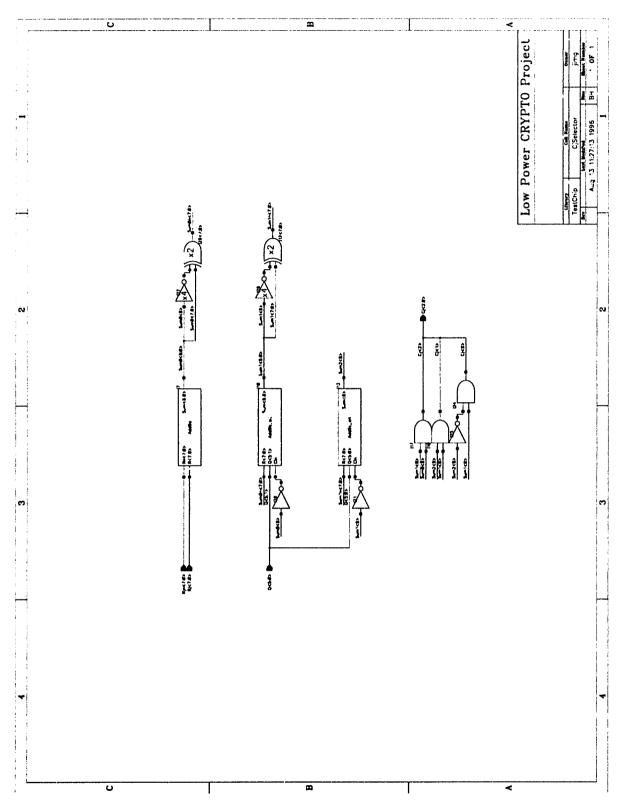

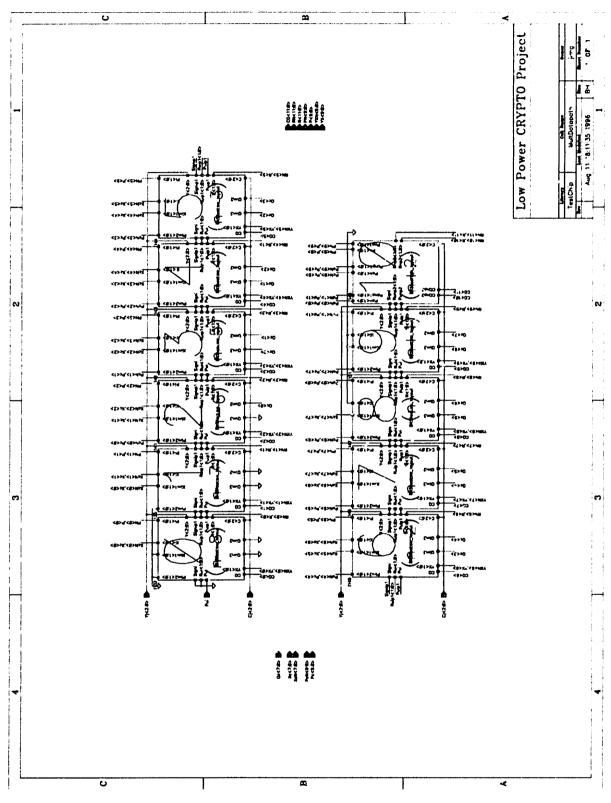

| В | Modular l  | Multiplier Schematics                                | 106 |

# **List of Figures**

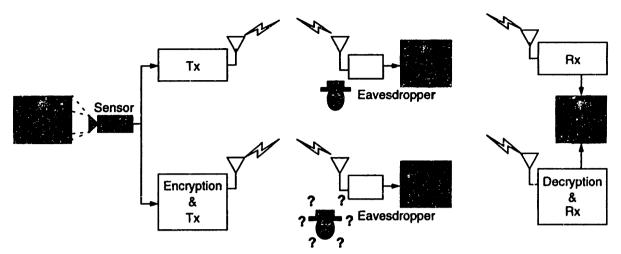

| Figure 1-1: Wireless Network Encryption/Decryption Example                      | 15     |

|---------------------------------------------------------------------------------|--------|

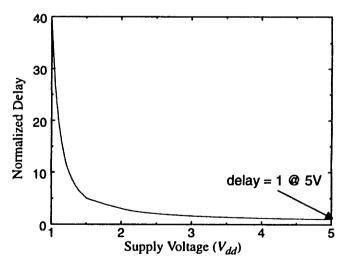

| Figure 1-2: Normalized Delay vs. Supply Voltage                                 | 16     |

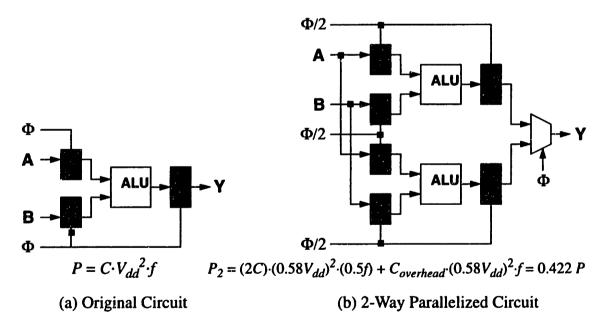

| Figure 1-3: Parallelization Example: an ALU                                     | 17     |

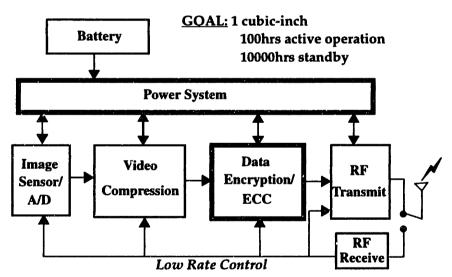

| Figure 1-4: MIT Wireless Sensor Project                                         | 20     |

| Figure 2-1: Product Cipher Construction                                         | 24     |

| Figure 2-2: Block Cipher Operating Modes                                        | 25     |

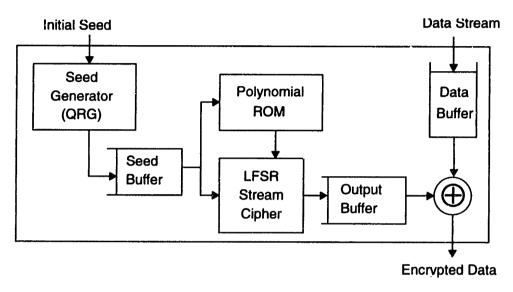

| Figure 2-3: Stream Cipher - Keystream Generator Construction                    | 26     |

| Figure 2-4: Output Feedback Mode                                                | 26     |

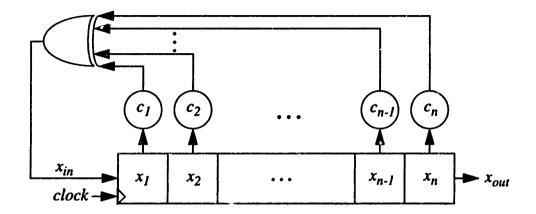

| Figure 2-5: An n-bit LFSR.                                                      | 28     |

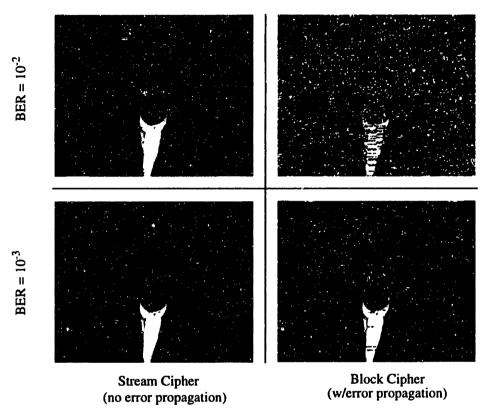

| Figure 2-6: Effects of Error Propagation on an Uncompressed Video Image         | 30     |

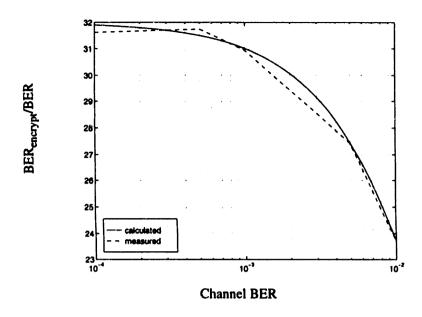

| Figure 2-7: Theoretical BER for Block Size = 64 bits                            | 31     |

| Figure 2-8: Error Propagation Ratio                                             | 32     |

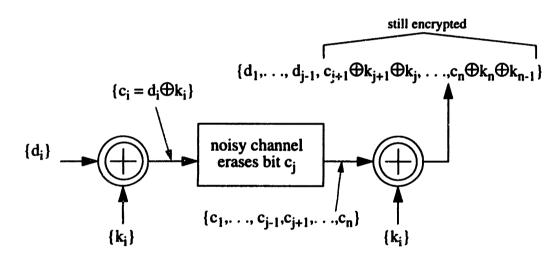

| Figure 2-9: Effects of De-Synchronization on Block Ciphers                      | 33     |

| Figure 2-10: Effects of De-Synchronization on Stream Ciphers                    | 33     |

| Figure 2-11: Comparison of Decoupling in Block and Stream Ciphers               | 35     |

| Figure 2-12: Amount of Computation Required for Factoring Using the GNFS        | 37     |

| Figure 2-13: Distribution of Security Features in a GSM Network                 | 38     |

| Figure 2-14: GSM Security Protocol                                              | 38     |

| Figure 3-1: Shrinking Generator                                                 | 41     |

| Figure 3-2: Time to Accumulate Keystream Bits for Linear Cryptanalysis of Shrin | nking  |

| Generator                                                                       | 42     |

| Figure 3-3: Seif-Shrinking Generator                                            | 43     |

| Figure 3-4: Alternating Stop & Go Generator                                     | 44     |

| Figure 3-5: GSM Cipher (i.e., A5)                                               | 46     |

| Figure 3-6: Normalized Power Consumption as a Function of LFSR Length           | 49     |

| Figure 3-7: Comparison of Power Consumption (Estimate vs. Powermill Simulati    | ons)50 |

| Figure 3-8: 2-way Parallel Shift Register                                       | 51     |

| Figure 3-9: Degree of Parallelism vs. Normalized Power Consumption for Shift    |        |

| Registers                                                                       | 51     |

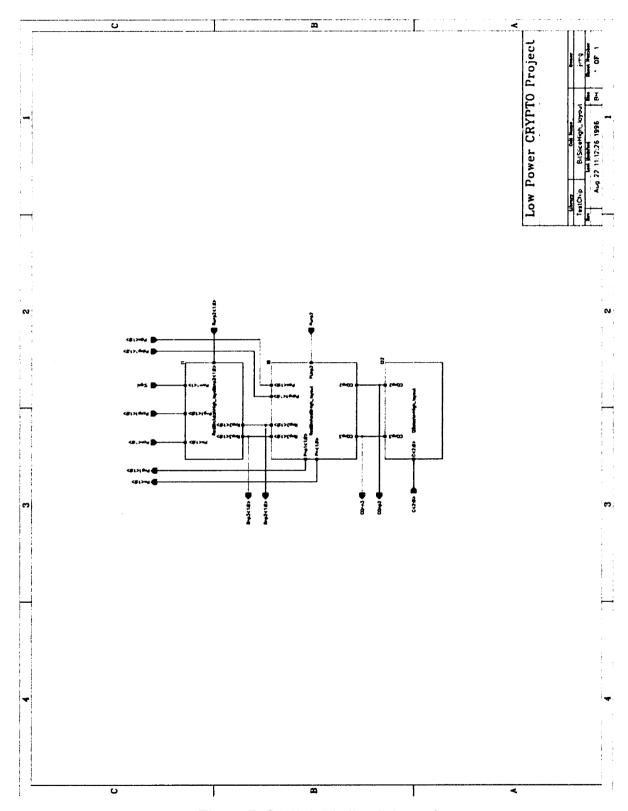

| Figure 3-10: 2-way Parallelized LFSR                                                     |

|------------------------------------------------------------------------------------------|

| Figure 3-11: Variable Length LFSR Block Diagram53                                        |

| Figure 3-12: Variable Length Shift Register Block Diagram53                              |

| Figure 3-13: Programmable Feedback Tree Block Diagram                                    |

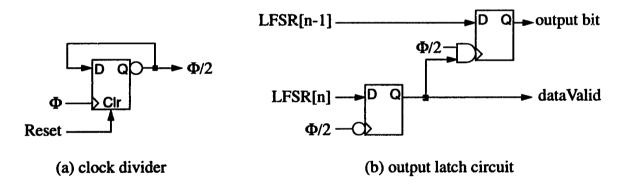

| Figure 3-14: Shrinking Generator Output Latching54                                       |

| Figure 3-15: Clock Gating55                                                              |

| Figure 3-16: Self-Shrinking Generator Output Circuit55                                   |

| Figure 3-17: A5 Clock Control Circuit                                                    |

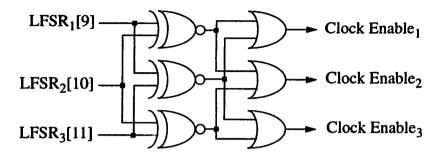

| Figure 3-18: Stream Cipher Test Chip Layout57                                            |

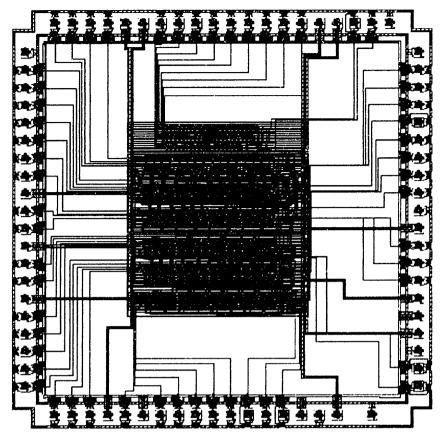

| Figure 3-19: Measured Power Consumption of the 4 LFSR-based Stream Ciphers58             |

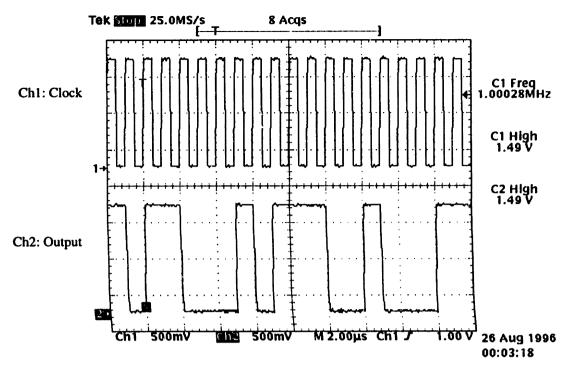

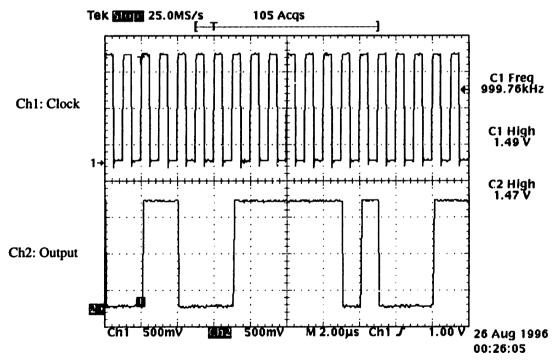

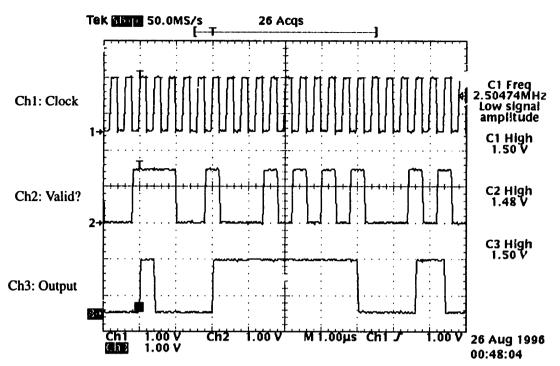

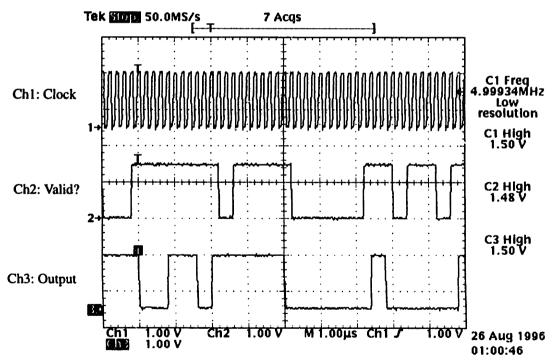

| Figure 3-20: A5 Stream Cipher Operation @Vdd = 1.5V59                                    |

| Figure 3-21: ASG Stream Cipher Operation @Vdd = 1.5V59                                   |

| Figure 3-22: SG Stream Cipher Operation @Vdd = 1.5V60                                    |

| Figure 3-23: SSG Stream Cipher Operation @Vdd = 1.5V60                                   |

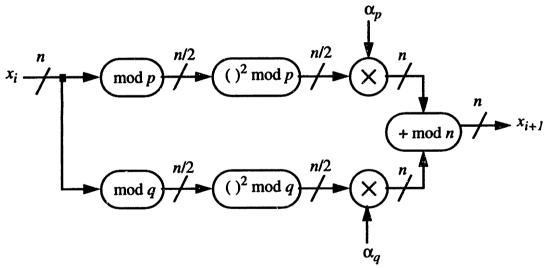

| Figure 4-1: Parallelization of Chinese Remainder Algorithm                               |

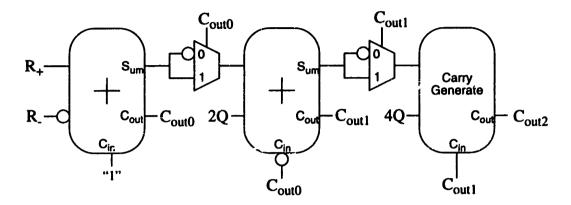

| Figure 4-2: Takagi's Algorithm71                                                         |

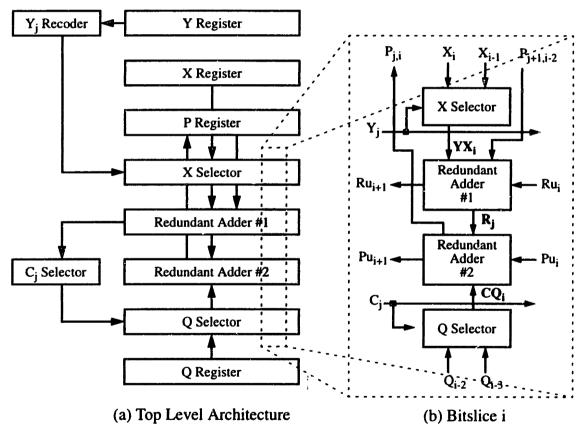

| Figure 4-3: Architecture of Takagi's Multiplier72                                        |

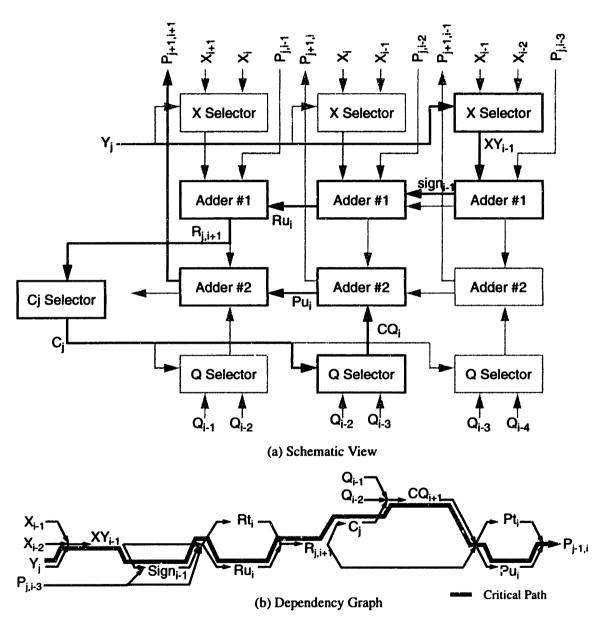

| Figure 4-4: Critical Path of Takagi's Multiplier73                                       |

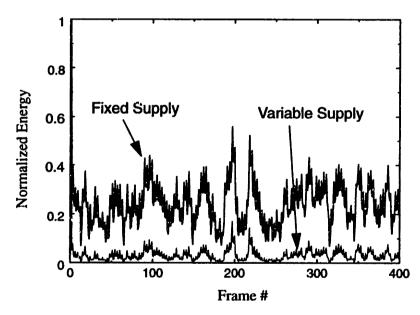

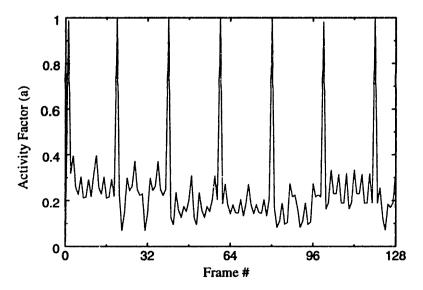

| Figure 4-5: Activity Factor per Frame                                                    |

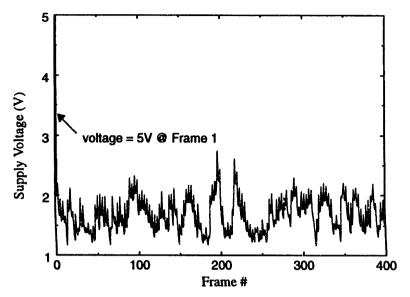

| Figure 4-6: Supply Voltage per Frame76                                                   |

| Figure 4-7: Normalized Energy Consumption per Frame76                                    |

| Figure 4-8: Activity Factor per Frame (bursty data)                                      |

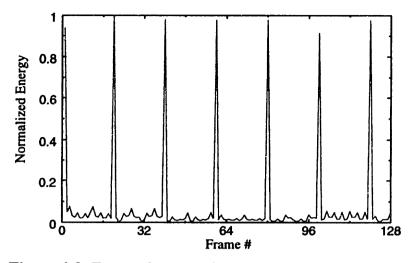

| Figure 4-9: Energy Consumption per Frame (bursty data)78                                 |

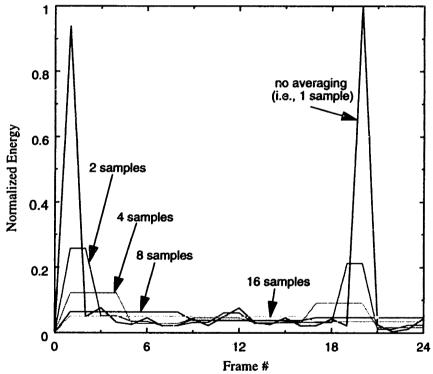

| Figure 4-10: Energy Consumption per Frame for Varying Sample Sizes78                     |

| Figure 4-11: Energy Reduction Factor for Varying Sample Sizes Relative to a Fixed Supply |

| Scheme79                                                                                 |

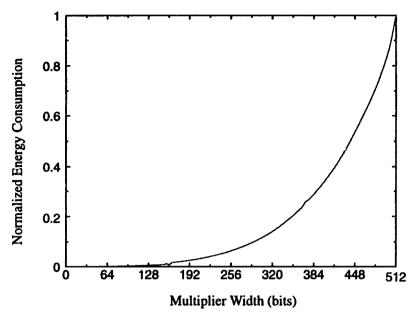

| Figure 4-12: Energy Consumption for Varying Multiplier Widths81                          |

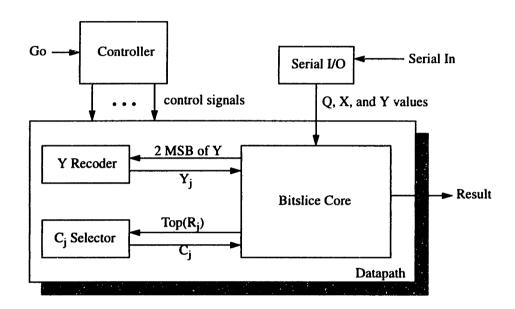

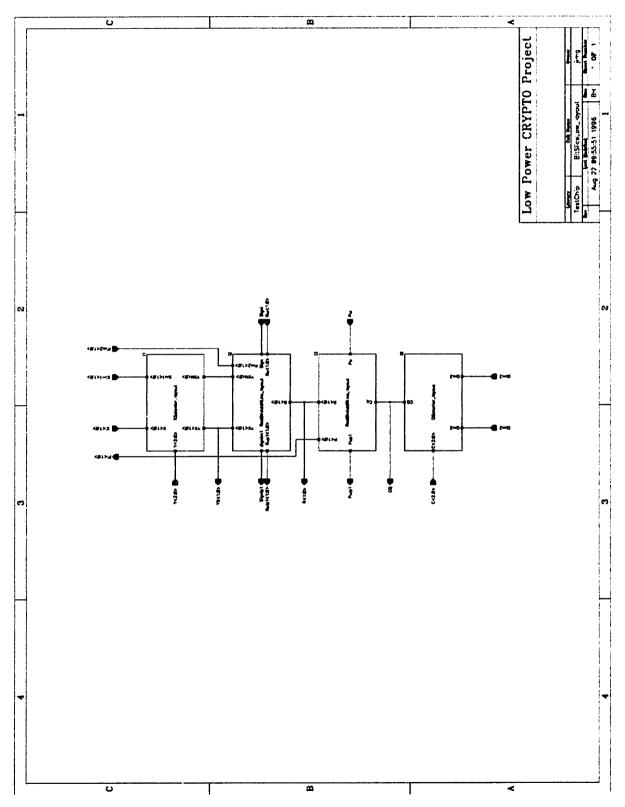

| Figure 4-13: Modular Multiplier Test Chip Top Level Block Diagram82                      |

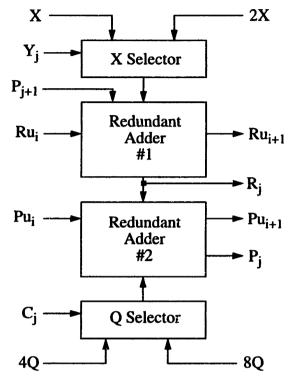

| Figure 4-14: Bitslice Core Block Diagram83                                               |

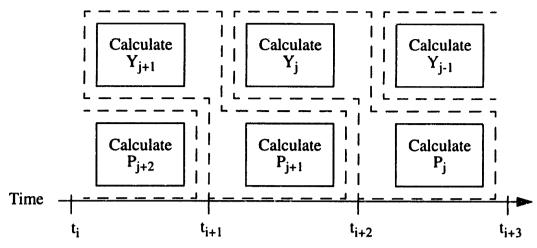

| Figure 4-15: Pipeline Flow of Y Recoder84                                                |

| Figure 4-16: Cj Selector Block Diagram85                                                 |

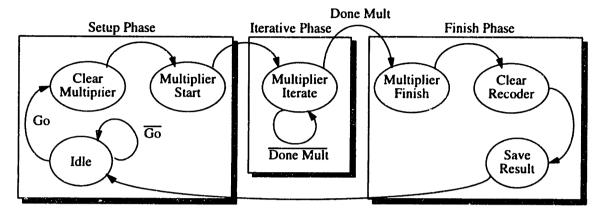

| Figure 4-17: Controller State Diagram                                    | 86  |

|--------------------------------------------------------------------------|-----|

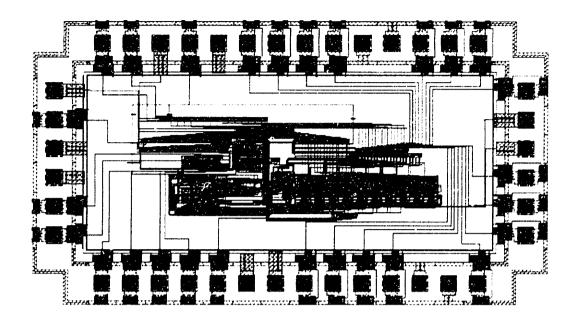

| Figure 4-18: Modular Multiplier Test Chip Layout                         | 87  |

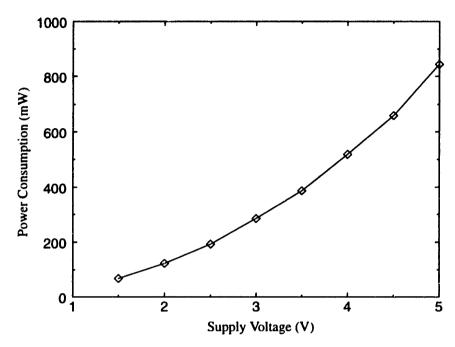

| Figure 4-19: Estimated Power Consumption of QRG Based on 8-bit Test Chip | 88  |

| Figure 5-1: Proposed Low Power Encryption System                         | 92  |

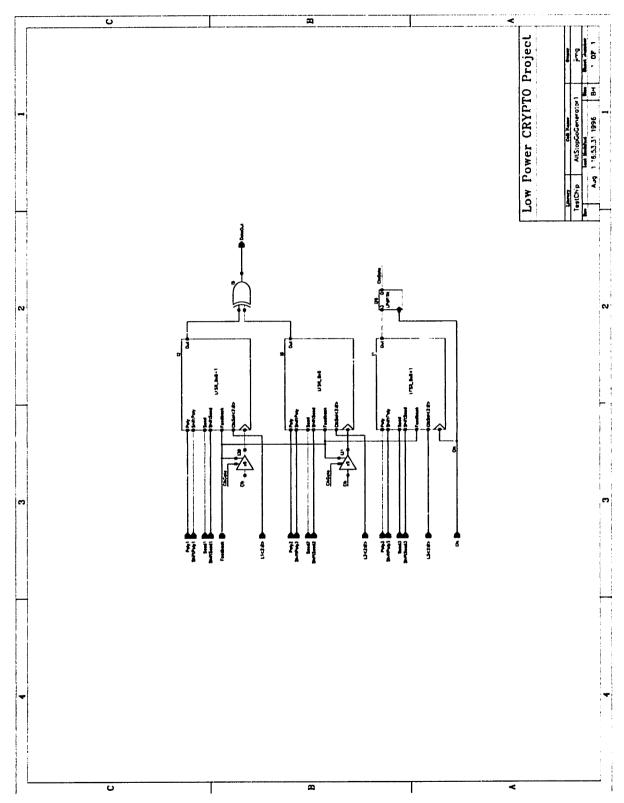

| Figure A-1: Alternating Stop & Go Generator Schematic                    | 99  |

| Figure A-2: Shrinking Generator Schematic                                | 100 |

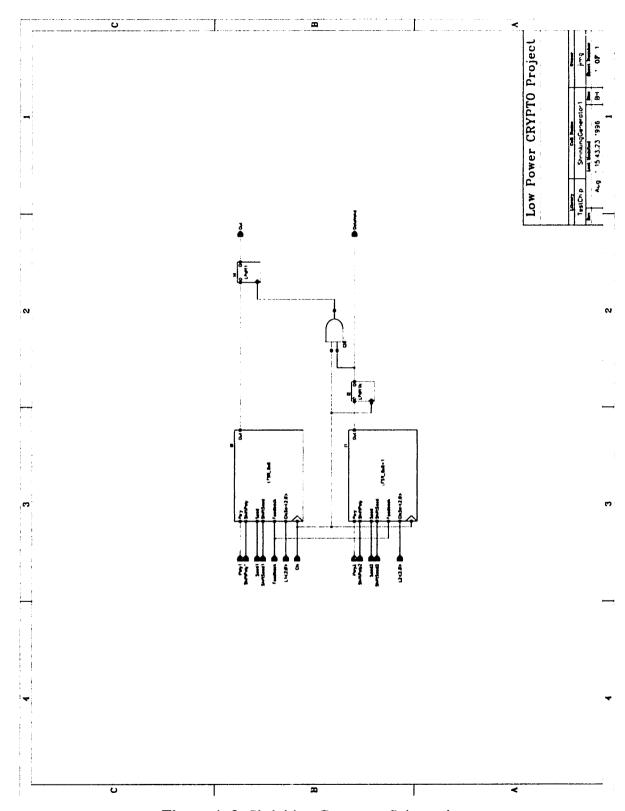

| Figure A-3: Self-Shrinking Generator Schematic                           | 101 |

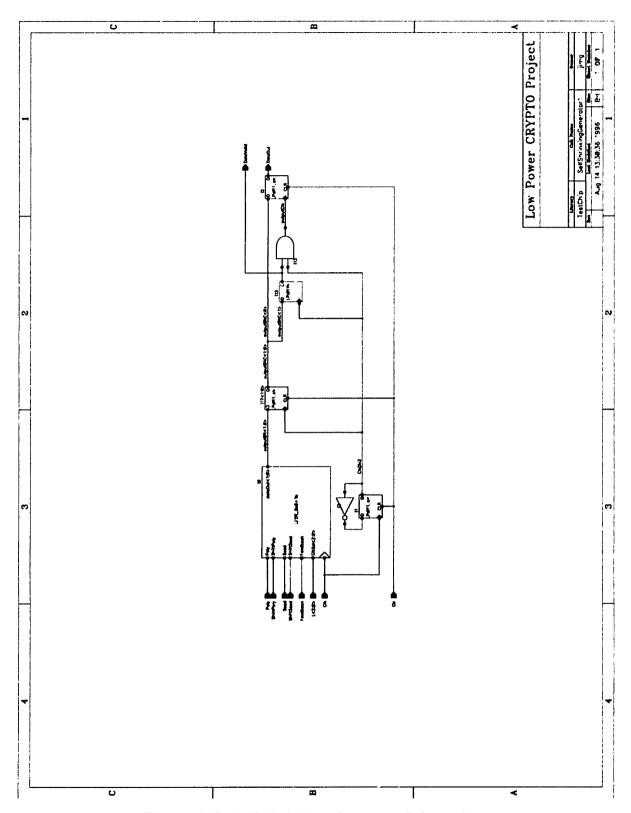

| Figure A-4: Proposed GSM Cipher (A5) Schematic                           | 102 |

| Figure A-5: 65-bit Variable Length Programmable LFSR Schematic           | 103 |

| Figure A-6: 64-bit Variable Length Programmable LFSR Schematic           | 104 |

| Figure A-7: 63-bit Variable Length Programmable LFSR Schematic           | 105 |

| Figure B-1: Top Level Modular Multiplier Schematic                       | 107 |

| Figure B-2: Controller Logic Schematic                                   | 108 |

| Figure B-3: Serial I/O Interface Schematic                               | 109 |

| Figure B-4: Cj Selector Schematic                                        | 110 |

| Figure B-5: Yj Recoder Schematic                                         | 111 |

| Figure B-6: Modular Multiplier Datapath Schematic                        | 112 |

| Figure B-7: Low Bitslice Schematic                                       | 113 |

| Figure B-8: High Bitslice Schematic                                      | 114 |

## **List of Tables**

| Table 1-1: Various sensor applications and their data characteristics                            | 21 |

|--------------------------------------------------------------------------------------------------|----|

| Table 2-1: Algorithm Parameters for Several Factoring Algorithms                                 | 36 |

| Table 3-1: Clocking function for the GSM Cipher                                                  | 48 |

| Table 3-2: Power Consumption Estimates                                                           | 49 |

| Table 3-3: Layout Statistics for Stream Cipher Test Chip                                         | 56 |

| Table 3-4: Estimated and Measured Power Consumption of the 4 LFSR-based Stream Ciphers at 1 Mbps | 58 |

| Table 4-1: Activity Factors and Power Reduction Factors for 3 Video Sequences                    | 75 |

| Table 4-2: Power Reduction Factor Using a Variable Supply Relative to a Fixed Supply             | 76 |

| Table 4-3: Power Reduction Factors Using Averaging Relative to a Fixed Supply Scheme             | 79 |

| Table 4-4: Power Reduction of Complimentary Scheme Relative to a Fixed Supply Scheme             | 80 |

| Table 4-5: Priority assignment for scalability example                                           | 81 |

| Table 4-6: Decoding of Carry-out Bits in Cj Selector                                             | 85 |

| Table 4-7: Test Data for Maximum Clock Frequency Based on Measurements at Vdd = 2V               | 89 |

|                                                                                                  |    |

# Chapter 1

# Introduction

Two of the biggest trends in computing today are mobile computing and global networking. The popularity of the Internet is an example of the drive towards a "wired world" in which all computers exist within a global web that allows them to communicate and share information with other systems located around the world. At the same time the current trend in computing hardware is towards portable, battery-operated nomadic computing systems. Thus the average power consumption of the system must be minimized in order to maximize the battery lifetime and minimize the battery size/weight. The popularity of wireless networks is a direct result of these two trends as people strive to remain connected to the global web without having to be tied down to a wired link.

Unfortunately wireless networks are notorious for their susceptibility to tampering and eavesdropping. In a wired network, information is transmitted within protected physical links (wires), offering the user some measure of security. Wireless networks have no such protection and it is a simple manner to eavesdrop or interfere with a transmission (e.g., the top link from Figure 1-1). In the cellular phone network, for example, scanners can be purchased that allow an attacker to steal cellular phone identification codes that are then used to defraud the cellular service provider. Estimates place annual losses due to fraud for cellular phone service providers and their customers at over \$500 million ([1], [2]). The need for secure wireless transmission becomes even more apparent when one considers the gradual migration of conventional commerce, electronic banking, and other sensitive applications to the Internet; a trend that will continue to wireless networks.

These wireless security schemes will require low power hardware encryption modules as building blocks upon which to build safe and reliable protocols to provide end users with a secure wireless link (e.g. the bottom link of Figure 1-1).

Figure 1-1: Wireless Network Encryption/Decryption Example

## 1.1 Low Power Design Basics

In modern integrated static CMOS circuits, the power consumption is dominated by the dynamic switching component that results from the charging/discharging of parasitic load capacitances. This power consumption can be modeled by the following expression:

$$P_{switching} = \alpha \cdot C \cdot V_{dd}^{2} \cdot f \tag{1-1}$$

where C is the physical capacitance,  $V_{dd}$  is the supply voltage and f is the clock frequency.  $\alpha$  represents the activity factor of the circuit which is the probability that C will be charged on any given cycle. This models the fact that most capacitances are not being charged on every given cycle.

To minimize the power consumption of the circuit, the designer should minimize the variables of EQ 1-1. Techniques for minimizing the switched capacitance and supply voltage are described below.

#### Minimizing the Switched Capacitance

Minimization of the switched capacitance can be done at several levels of the design hierarchy [3]. At the highest level, the designer can perform algorithmic optimizations that minimize the number of operations, as well as select a specific data representation that minimizes the bit switching activity (e.g., using sign-magnitude vs. 2's complement encoding of operands in a multiplier). At the circuit/logic level, the designer can optimize

the logic implementation and transistor sizing, as well as utilize power-down techniques to minimize the switched capacitance within the circuit.

## Minimizing the Supply Voltage -- Conventional Supply Scaling

The switching component of the power consumption of a digital CMOS circuit scales with the square of the supply voltage. By minimizing  $V_{dd}$  the designer can quadratically reduce the power dissipation of the circuit. Unfortunately propagation delays in CMOS integrated circuits increase as the supply voltage is reduced according to the first order model:

$$T_{delay} = \frac{k \cdot V_{dd}}{\left(V_{dd} - V_{l}\right)^{2}} \tag{1-2}$$

where k is a process dependent constant,  $V_{dd}$  is the supply voltage, and  $V_t$  is the MOSFET threshold voltage. Figure 1-2 shows the normalized delay vs. supply voltage characteristic for a 0.6  $\mu$ m process. This dependence limits the amount that the supply voltage can be reduced as the circuit must satisfy its throughput requirements. Hence the supply voltage is reduced until the critical path of the circuit is the same as the clock period required for the given throughput and architecture.

Figure 1-2: Normalized Delay vs. Supply Voltage

#### Minimizing the Supply Voltage -- Parallelizing and Pipelining the Computation

One technique for reducing the supply voltage involves parallelizing the computation to increase the effective cycle time of the circuitry for a fixed throughput. By increasing the

effective cycle time, the circuit delays can be increased and hence the supply voltage can be reduced. The cost of parallelizing the computation is the area overhead in creating parallel implementations of the circuitry and the increase in the switched capacitance due to the additional multiplexing and routing required. However the additional reduction in supply voltage will result in lower overall power consumption. As an example, consider the 2-way parallelization of an ALU (Figure 1-3). The parallel implementation datapath features twice the switched capacitance of the original, half the switching frequency and 0.58 times the supply voltage. The routing/muxing overhead is equivalent to 0.255 times the original switched capacitance and operates at the original switching frequency and 0.58 times the supply voltage. The overall normalized power consumption of the parallel implementation is thus:

$$P_2 = 2C \cdot (0.58V)^2 \cdot \frac{f}{2} + 0.255C \cdot (0.58V)^2 \cdot f = 0.422 \cdot CV^2 f = 0.422P$$

which consumes 2.37 times less power than the original implementation [3].

Figure 1-3: Parallelization Example: an ALU

In the general case, the power reduction factor for an n-way parallelization can be approximated using the following model assuming that the total switched capacitance scales with n plus some correction factor that is a function of the parallelism,  $\gamma(n)$ . If

delays scale according to EQ 1-2, then the supply voltage  $(V_{dd})$  can be calculated from the delay  $(T_d)$  using the expression:

$$V_{dd}(T_d) = \left(\frac{1}{2} + \frac{V_t T_d}{k} + \sqrt{\frac{V_t T_d}{k} + \frac{1}{4}}\right) \cdot \frac{k}{T_d}$$

(1-3)

If we ignore  $V_t$  (i.e.,  $V_t = 0$ ), the supply voltage scales inversely with the delay of the circuit. Thus for an n-way parallelized circuit, the supply voltage can be reduced by a factor of n (as delays increase by a factor of n). Hence the power consumption of the circuit is reduced by a factor of:

reduction factor

$$=\frac{P_1}{P_n} = \frac{C \cdot V^2 \cdot f}{nC(1+\gamma(n)) \cdot \left(\frac{V}{n}\right)^2 \cdot \left(\frac{f}{n}\right)} = \frac{n^2}{1+\gamma(n)}$$

Pipelining can be utilized in a similar manner to reduce the supply voltage by partitioning the calculation into n discrete steps, each of which needs to be completed in the original clock period. Thus delays can be increased by a factor of n and hence the supply voltage can be decreased by a factor of n. The cost of pipelining is the additional pipeline registers that must be added to the circuit.

## 1.2 Cryptography For Wireless Systems and Thesis Scope

There are three basic research areas that need to be addressed in the design of a security system for a wireless communications channel: authentication, key exchange, and encryption/decryption. In all of the explanations presented below it is assumed that two parties (i.e., sender and receiver) wish to communicate in the presence of an external observer (i.e., the attacker), who is attempting to eavesdrop, over an insecure channel using digital transmission techniques.

#### Authentication

Authentication is the means by which the sender and receiver verify their identities to one another at the beginning of a communication. This is particularly difficult in digital communications systems as each party is only able to see easily-forged binary messages at the

output of the communication channel. The parties must therefore utilize some form of protocol which guarantees that a party can demonstrate irrefutable proof of identity even in the presence of tampering. Typically this is done by requesting that the other party demonstrate knowledge of a piece of information that only the intended recipient could know and then verifying that their reply is valid.

#### **Kev Exchange**

Usually the sender and receiver need to share a piece of secret information called the key for the purposes of encrypting and decrypting the data traffic between them. In some of these applications both parties are assumed to already have a copy of the key. In others the key must be decided upon and then shared over an insecure link. Hence there must be some means by which the sender and receiver can agree upon and exchange the key in the absence of any shared information and a secure link. Algorithms and protocols exist by which a key can be generated and exchanged. These are for the most part very computationally intensive and unsuitable for a low-power wireless application.

## **Encryption/Decryption**

Once the keys have been established the sender and receiver now need to encode and decode the data that is to be transmitted over the channel. The encryption algorithms must be chosen such that the amount of work required for an attacker to decrypt the data is prohibitively high. There is a wealth of good encryption/decryption algorithms available to the wireless systems designer. However the complexity and security of these algorithms vary widely. Care must be taken to select an algorithm that provides a satisfactory level of security at an acceptable level of complexity. A trade-off that is made all the more critical by the low-power requirements of a typical mobile wireless system.

While all three of the above areas are equally important, scope limitations allow only the encryption/decryption aspect to be studied here. Authentication and key exchange will be considered as future work.

## 1.3 Driver Application

The research described within this body of work is driven by the Ultra Low Power Wireless Sensor Project at MIT. The goal of this project is to design, fabricate, and characterize

a wireless image sensor (Figure 1-4) capable of operating over a wide range of data rates (e.g., 1 bps - 1 Mbps). The sensor features an imager, reconfigurable A/D converter, DSP core (which includes video compression and an encryption module) and a transmitter. The sensor electronics are intended to be generic in the sense that the imager can be removed and another form of sensor input can then be utilized with the same programmable A/D / DSP / RF transmitter core. The core must therefore be capable of operating at a variety of data rates and resolutions, as outlined in Table 1-1. The system features a variable voltage power supply for dynamic adjustment of the supply voltage. The sensor features a low bandwidth return channel from the base station to the sensor for control information, such as transmitter power control and Automatic Repeat Requests (ARQ) acknowledgments for a low data rate sensor configuration (e.g., temperature sensing).

The design specifications of the sensor require its size to be no greater than 1 in<sup>3</sup>, with a battery operated lifetime of 1000 hours of active operation and 10,000 hours of stand-by operation. The power budget of the sensor system is approximately 50 mW.

Figure 1-4: MIT Wireless Sensor Project

Sensor Type

A/D Resolution (bits/sample)

Data Rate

Video (compressed)

8 bits

≤ 1Mbps

Audio (uncompressed)

20

~ 800 kbps

Temperature

20

20 bps

Table 1-1: Various sensor applications and their data characteristics

# Chapter 2

# Introduction to Basic Cryptography

## 2.1 General Classification of Algorithms

Cryptographic algorithms involve performing various operations on a given input to produce an encoded output, based on the value of a secret control input called the key. The security of a cryptographic algorithm is dictated by the difficulty of deducing the input given the output and the encoding algorithm with the exception of the key. Thus the security of the algorithm rests solely in the secrecy of the key and the computational complexity of deducing its value. At the topmost level, cryptographic algorithms can be partitioned into two classes depending on the symmetry of the encryption/decryption algorithms and keys.

## 2.1.1 Asymmetric Algorithms

Asymmetric algorithms require no exchange of secret information between the sender and the receiver, as they do not utilize the same keys for encryption and decryption (i.e., the keys are asymmetric). The receiver generates the encryption and decryption keys and then publicly distributes the encryption key. This allows anyone to encode a message so that only the receiver can decode it. The idea of using an asymmetric algorithm was first proposed by Whitfield and Diffie [4] and has since come to be known as Public Key Cryptography.

The security of asymmetric algorithms relies on the difficulty of solving hard numbertheoretic problems, such as computing discrete logarithms over a field (e.g., ElGamal [5]), or factoring large composite numbers (e.g., RSA [6]). As an example of the difficulty of such problems, consider that the estimated effort to factor a 512 bit composite number is  $3x10^4$  MIPS-years<sup>1</sup> [7]. Unfortunately, the complexity of these problems makes asymmetric algorithms much too computationally demanding for wireless applications where

<sup>1.</sup> a MIPS-year is the number of calculations performed by a machine capable of performing 10<sup>6</sup> instructions per second, running non-stop for a full year

power budgets are strictly limited. They do however find applications in wireless networks for such operations as authentication and key exchange (e.g., [8] and [9]).

#### 2.1.2 Symmetric Algorithms

Symmetric algorithms differ from asymmetric algorithms in that the sender and receiver must share a secret key that is used for both encryption and decryption. This implies that the keys can be exchanged through some secure channel, or can be installed within the encryption/decryption units during fabrication, thereby avoiding the whole key exchange process.

The security of a symmetric algorithm is based on the amount of computation that is required to determine the value of the secret key. This can be parameterized by defining an equivalent keylength that represents the number of values that must be checked in order to determine the secret key value. This set of possible key values is denoted as the keyspace of the algorithm.

Symmetric algorithms are in general much more efficient than asymmetric systems as the security of the algorithm is based on the secrecy of the key and not the computational complexity of the algorithm. Hence they are the algorithm of choice for power-limited wireless applications.

## 2.2 Block Cipher Algorithms

Block cipher algorithms are symmetric algorithms that operate on blocks of data, n bits at a time, to generate an m bit output that forms the encrypted message. Obviously m must be greater than n in order to have an invertible mapping that can be decrypted and, for the purposes of wireless communication networks where bandwidth is very limited, typically is restricted to m = n. As a result a block cipher can be thought of as a memoryless n bit permutation of the inputs under the influence of the secret key.

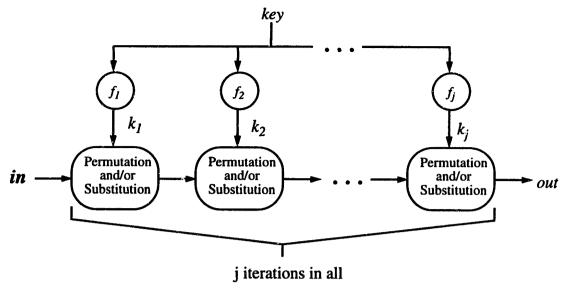

Most practical block cipher implementations are constructed using a cascade of simple bitwise permutations and substitutions under the influence of a function of the secret key (Figure 2-1). Each stage contributes to the overall security of the cipher. This construction is known as a product cipher and serves as the basic structure of most popular block ciphers in use today (e.g., DES [10], IDEA [11], BLOWFISH [12], and RC5 [13]).

Figure 2-1: Product Cipher Construction

The idea can be extended to the cascading of multiple block ciphers to create a more secure cipher. The security of the overall system is not guaranteed to be n times as difficult to crack if n ciphers are cascaded together. The only guarantee is that the system will be at least as difficult to crack as the weakest algorithm used in the cascade [14].

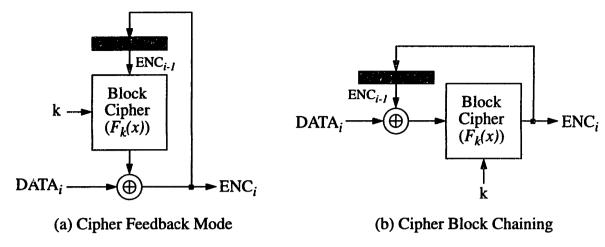

The lack of memory in the block cipher results in the weakness that given the same input (x) and key (k), the block cipher will always output the same value,  $y = F_k(x)$ . This weakness can be overcome by utilizing the block cipher with external memory and feedback in one of the following operating modes (Figure 2-2):

- Cipher Feedback (CFB): data is XORed with the encryption of the previous block's output (i.e.,  $ENC_i = DATA_i \oplus F_k(ENC_{i-1})$ ).

- Cipher Block Chaining (CBC): data is first XORed with the previous block's output and the result is then encrypted (i.e.,  $ENC_i = F_k(DATA_i \oplus ENC_{i-1})$ ).

CFB can use a varying amount of feedback by only using j bits of ENC<sub>i</sub> in the feedback loop. The contents of the feedback register are shifted j bits to the left and the j bits of ENC<sub>i</sub> are then loaded into the least significant j bits of the feedback register.

Figure 2-2: Block Cipher Operating Modes

By introducing feedback into the encryption/decryption process, the system designer has also introduced error propagation. If so much as a single bit is in error at the decryption process input, it will decrypt to random values. These random values will then be used in the decryption of subsequent blocks, causing numerous errors to propagate across multiple blocks. In environments where bit errors are very likely (e.g., a wireless communications channel), this can lead to catastrophic error propagation. A detailed analysis of this problem is given in Section 2.5.1.

## 2.3 Stream Cipher Algorithms

Stream ciphers differ from block ciphers as they contain internal state that makes their output a time-dependent function, thereby avoiding the replay weakness that haunts block ciphers. In addition, a stream cipher operates on a data stream, typically one bit wide, rather than a block of data.

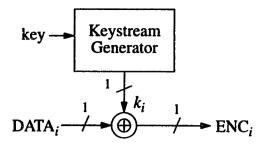

Stream ciphers are commonly modelled as a sequence generator that produces a time-varying pseudo-random sequence (i.e., the keystream) that is then XORed with the data stream to produce the encrypted data stream (Figure 2-3). Decryption is performed by using an identical keystream generator which is synchronized to the data stream. Its output is XORed with the encrypted data stream, removing the influence of the original keystream (i.e.,  $(k_i \oplus d_i) \oplus k_i = d_i$ ).

Figure 2-3: Stream Cipher - Keystream Generator Construction

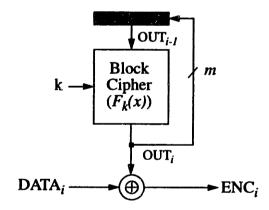

Note that it is possible to construct a stream cipher using a block cipher by operating the block cipher in an Output Feedback Mode (OFB) configuration (Figure 2-4). In this configuration the block cipher is never used to directly encrypt the data, rather it is given an initial starting vector that it then repeatedly encrypts. On any iteration m bits of  $OUT_i$  are shifted into the least significant m bits of the feedback register, whose contents are then encrypted to generate  $OUT_{i+1}$ .

Figure 2-4: Output Feedback Mode

A very thorough discussion concerning the construction and analysis of stream ciphers is given by Rueppel in [15].

## 2.3.1 Design Criteria for Keystream Generators

Several stream cipher design criteria have been proposed that serve as necessary, but not sufficient conditions for obtaining a secure keystream generator [15]. These criteria are: sufficiently long period, sufficiently large linear complexity and uniformly distributed output sequence statistics.

The period of a keystream must be greater than the length of the data being encrypted. If not, the attacker can XOR two encrypted data bits to remove all influence of the key (i.e.,  $(a_i \oplus k_i) \oplus (a_{i+T} \oplus k_{i+T}) = a_i \oplus a_{i+T}$  as  $k_i = k_{i+T}$ ). It is then a simple matter to decrypt the resulting data stream using simple statistical techniques<sup>2</sup>.

The linear complexity (LC) of a keystream is a measure of the length of an equivalent LFSR that generates the keystream. The length of the equivalent LFSR and its feedback polynomial can be determined from 2·LC keystream bits using the Berlekamp and Massey algorithm [16]. Thus the linear complexity must be made sufficiently long that the attacker never sees enough keystream bits to mount such an attack.

In addition to a long linear complexity and period, the keystream must also exhibit signal statistics that appear indistinguishable from a uniform distribution. Any deviations could be utilized by an attacker to create a next bit predictor for the keystream that could then be used to crack the system.

While satisfying all of the aforementioned design criteria is a necessary condition for a secure keystream generator, it is by no means sufficient. In general, the designer must analyze any proposed algorithm to discover its weaknesses and quantify its strength to known attacks.

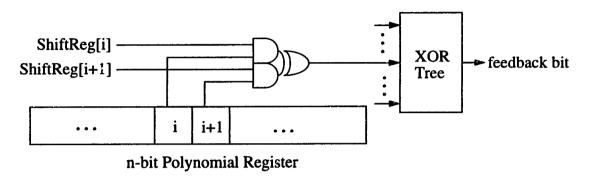

#### 2.3.2 Linear Feedback Shift Register Based Stream Ciphers

Linear feedback shift registers (LFSRs) consist of a shift register whose input is computed using a linear recursion based on the current state of the shift register:

$$x_{1}(t+1) = \sum_{i=1}^{n} c_{i} \cdot x_{i}(t)$$

(2-1)

Alternatively, the feedback expression can be thought of as an *n*th degree feedback polynomial given by the expression:

$$f(x) = c_n x^n + c_{n-1} x^{n-1} + \dots + c_1 x^1 + 1 = 0$$

(2-2)

<sup>2.</sup> For detailed examples of statistical cryptanalysis based on the statistics of English see Section 1.2 of [36].

where both  $c_i$  and x are binary values. The above summations are performed modulo-2 and can be implemented using simple XORs, thus resulting in a very simple and efficient circuit (Figure 2-5).

Figure 2-5: An *n*-bit LFSR

An *n* bit LFSR can be in any of  $2^n$  states and can cycle through any of  $2^{n-1}$  states (the all 0 state will cause the LFSR to become stuck). Any LFSR that cycles through all  $2^{n-1}$  non-zero states is said to be a maximal length LFSR and its output is called an m-sequence. The LFSR's feedback polynomial must be irreducible (i.e., there is no polynomial of degree 0 < k < n that divides f(x)) in order to generate an m-sequence. There are a total of  $\phi(2^{n-1})/n$  (see Section 4.1 for a definition of  $\phi$ ) primitive polynomials for an *n* bit LFSR. For large values of *n*, the number of primitive polynomials approaches  $2^n$ .

One interesting property of a maximal length LFSR is that its output exhibits a uniform distribution in terms of the number of 1's and 0's, making it appear to be an excellent candidate for use as a stream cipher keystream generator. Unfortunately LFSRs are completely insecure as any n-bit LFSR can be cracked after observing 2n output bits using the Berlekamp and Massey Algorithm. However, due to their simplicity and excellent output statistics, LFSRs are typically used as building blocks in more complicated stream cipher systems. Such systems utilize multiple LFSRs, that are clocked irregularly and whose outputs are combined using non-linear functions, to yield more cryptographically secure outputs.

## 2.4 Quadratic Residue Generator

The Quadratic Residue Generator (QRG) is a cryptographically-secure pseudo-random bit generator based on the difficulty of determining quadratic residues modulo a large composite modulus. The QRG was originally proposed by Blum, Blum, and Shub [17].

The QRG operates by performing repeated modular squarings:  $x_i = x_{i-1}^2 \mod N$  and extracting the least significant  $log_2(log_2(x_i))$  bits from each result to generate the keystream sequence. The modulus N must be the product of two large prime numbers P and Q, where P and Q are both congruent to 3 modulo 4. The initial seed  $(x_0)$  must be a quadratic residue modulo N.

## 2.5 Comparison of Algorithms (Block Ciphers vs. Stream Ciphers)

Given that both stream ciphers and block ciphers are computationally efficient enough to be utilized in a low-power wireless application, it remains to be seen which is ultimately the most suitable. There are many considerations that must be studied, as outlined in the following sections.

## 2.5.1 High Bit Error Rates and Error Propagation

Block ciphers are designed so that inputs differing by so much as a single bit generate widely varying outputs. This property, while being highly desirable for security reasons, leads to the phenomenon of error propagation in block ciphers. Error propagation is the generation of multiple errors from a single error due to inter-bit dependencies and correlations in the data path. For wireless communication channels, one must be especially concerned with error propagation as BERs can be on the order of 10<sup>-2</sup>. When these large BERs are combined with signal processing algorithms, which are typically intolerant to even single bit errors (e.g., video compression algorithms), the need for forward Error Correction Coding (ECC) becomes obvious. However, ECC requires the introduction of redundancy into the data stream which consumes part of the transmission bandwidth. Thus it is desirable to minimize the amount of ECC that is required.

If raw pixel values are transmitted or the video compression algorithm is able to tolerate errors (e.g., pyramid vector quantization [18]), then error propagation analysis is extremely important as the increased BER translates into image degradation. Figure 2-6 shows the effects of error propagation for a stream cipher and 64-bit block cipher. As seen

from the figure, a single bit error will become a large burst of errors for the block cipher due to error propagation. Note that if the compression algorithm is intolerant to even single bit errors (e.g., huffman encoding [19]), error propagation is not an issue as it only involves the propagation of existing errors. Since an error has already occurred, the frame will be lost regardless of how many other errors are generated due to error propagation.

Figure 2-6: Effects of Error Propagation on an Uncompressed Video Image

Assuming that channel bit errors can be modeled as independent, identically distributed events with some probability P<sub>e</sub>, then the channel BER for a block of length B bits can be expressed as:

$$BER = \frac{1}{B} \cdot \sum_{i=1}^{B} \left( i P_e^i (1 - P_e)^{B - i} {B \choose i} \right) = P_e$$

(2-3)

Now assume that a block cipher is used to encrypt the data before it is transmitted over the channel. The block cipher operates on blocks of length B, and exhibits excellent diffusion characteristics such that even a single bit error will affect all other bits within the block with probability 1/2. Hence a single bit error in the encrypted block will decrypt to a block with on average B/2 bit errors. Under these assumptions, the BER for a block of length B bits that is encrypted before being transmitted and then decrypted at the output of the channel (i.e., BER<sub>encrypt</sub>) can be expressed as:

$$BER_{encrypt} = \frac{1}{B} \cdot \sum_{i=1}^{B} \left( \left( \frac{B}{2} \right) P_e^i \left( 1 - P_e \right)^{B-i} \left( \frac{B}{i} \right) \right)$$

(2-4)

Figure 2-7 shows the resulting BER<sub>encrypt</sub>, assuming a typical block length of 64 (e.g., IDEA and DES algorithms) for channel BER values ranging from 10<sup>-1</sup> to 10<sup>-5</sup>.

Figure 2-7: Theoretical BER for Block Size = 64 bits

Experiments were conducted using a 100-frame video sequence. The channel BER was varied from  $10^{-2}$  to  $10^{-4}$  and the 64-bit IDEA block cipher was used for encryption/decryption. Figure 2-8 shows the multiplicative effects of error propagation for both the simulation and that predicted by EQ 2-4.

Figure 2-8: Error Propagation Ratio

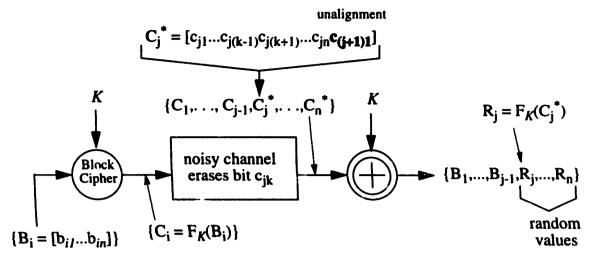

#### 2.5.2 Synchronization Effects

Wireless systems can experience deep fades due to obstructions in the communication channel. The result of these deep fades can be a loss in synchronization between the sender and receiver. In such cases the receiver will detect erasures in the transmitted data stream.

Both block and stream ciphers require constant synchronization between sender and receiver. When synchronization is lost in a block cipher system, the decryption block becomes unaligned resulting in random data (Figure 2-9). Similarly, when stream cipher keystream generators become unsynchronized the results are fatal as well. Recall that the data stream is XORed with the pseudo-random keystream to generate the encrypted data stream. Decryption requires that the encrypted data stream be XORed again with the synchronized keystream in order to remove the effects of the key (i.e.,  $A \oplus B \oplus A = B$ ). If the two generators ever become unsynchronized, the second XORing will not decrypt the data, rather it will re-encrypt it with the offset keystream (Figure 2-10).

Figure 2-9: Effects of De-Synchronization on Block Ciphers

Figure 2-10: Effects of De-Synchronization on Stream Ciphers

One way to reduce the effects of synchronization loss is to force a periodic re-synchronization of the keystream generator with new seeds and feedback polynomials. If a sufficiently secure pseudo-random generator is used to generate the new seeds/polynomials, the attacker must start all over again in their attempt to crack the system. This makes the system very computationally expensive to crack and reduces the amount of information leaked for any given successful attack.

Another way to combat the effects of synchronization loss is to use a self-synchronizing cipher. A cipher is said to be self-synchronizing if the output depends on previous output values. Given a self-synchronizing system whose output is a function of the previous n

outputs, a missing output value will only affect the next n output values. Hence, any correct continuous sequence of n output values is sufficient to resynchronize the system. Compare this to a non-self-synchronizing system in which any one missing output value will cause all subsequent values to be incorrect until the system is re-initialized. The cost of using such a system is error propagation, as any incorrect output will affect n other values. Given the high bit error rates of wireless systems (e.g.,  $10^{-2}$ ), this can prove to be prohibitively expensive in terms of the overhead of additional error correction coding.

In summary, both block ciphers and stream ciphers suffer from catastrophic error propagation in the presence of synchronization loss.

## 2.5.3 Buffering Requirements

Block ciphers require that their inputs be fixed-size n-bit blocks of data. If less than n bits need to be encrypted then either the data can be buffered up until a full block is ready to be encrypted or the incomplete data block can be padded to create a full block. In applications where latency requirements don't allow for indefinite buffering delays, padding is the only option. However, padding reduces the efficiency of the algorithm, as the same amount of work is being performed to encrypt fewer bits. In an application where the data rate is widely varying, this inefficiency can result in significant additional power consumption.

On the other hand, stream ciphers require a minimal amount of buffering as they have an effective block size of a single bit. Hence, they are perfectly efficient in that no additional work needs to be performed.

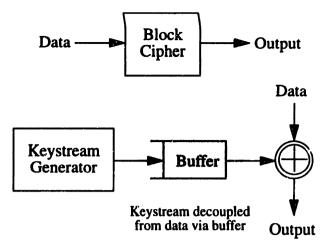

#### 2.5.4 Decoupling the Encryption Function

Block ciphers cannot be decoupled from the data stream as the outputs on any given cycle must be generated directly from the inputs (Figure 2-11). Stream ciphers, however, can be decoupled from the data stream since the encryption function involves XORing the data stream with the keystream, which can be precomputed and stored until it is required. This decoupling property allows stream ciphers to utilize additional power reduction techniques that are not possible with block cipher systems.

Figure 2-11: Comparison of Decoupling in Block and Stream Ciphers

## 2.6 Scalability

The scalability of a cryptographic algorithm can be defined as the measure of how the security of the cipher scales with some fundamental parameter associated with the algorithm. For LFSR-based ciphers, this parameter is typically the register lengths; while for the QRG it is the size of the modulus.

An LFSR-based stream cipher is cracked by reconstructing the contents and feedback polynomial of its constituent LFSRs. Knowing this information, an attacker can fully reconstruct the entire keystream and hence decrypt the data. As previously stated, an n-bit maximal-length LFSR can be in any of  $2^n$ -1 states and has any of  $\phi(2^n$ -1)/n possible feedback polynomials, for a total of  $(2^n$ -1) $\phi(2^n$ -1)/n possible key values. However, not every key value needs to be tried as weaknesses in the algorithm allow the attacker to reduce the size of the keyspace to something significantly smaller. The size of this reduced keyspace determines the effective key length of the algorithm, which is the measure of the true difficulty to crack an LFSR-based stream cipher. Hence, the security of an LFSR-based stream cipher scales exponentially with the effective key size (i.e., security is  $O\left(2^{n_{eff}}\right)$  where  $n_{eff}$  is the effective key length of the algorithm). The relationship between the actual key size and the effective key size of an LFSR-based stream cipher varies from algorithm to algorithm and must be evaluated on a case-by-case basis.

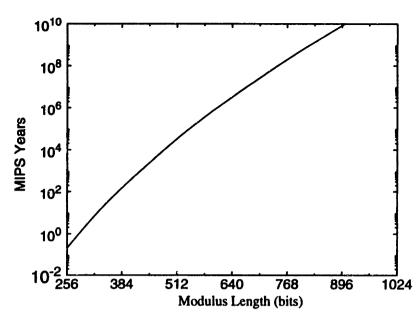

The security of the QRG is based on the difficulty of factoring large integers and as such, its security varies with the difficulty of factoring its modulus. This in turn scales

with the size of the modulus. There are numerous algorithms for factoring large integers (e.g., the Number Field Sieve [20] and Quadratic Sieve [21]), the running time of which all have the general form  $L(N,\nu,a+o(1)) = \exp((a+o(1))\cdot(\ln N)^{\nu}\cdot(\ln \ln N)^{(1-\nu)})$ , where a and  $\nu$  are algorithm-specific constants (e.g., Table 2-1) and N is the n-bit integer to be factored. The o(1) term is difficult to calculate and is eliminated from the analysis by approximating the time to factor N given the known time to factor some integer M using the expression:

$$T_N = T_M \cdot \frac{L(N, \nu, a)}{L(M, \nu, a)} \tag{2-5}$$

Practice has shown this to be a reasonable approximation [7]. The current best known algorithm for factoring large integers is the General Number Field Sieve (GNFS). A variant of the GNFS is the Special Number Field Sieve (SNFS) that can be used with integers of the form  $(a^k \pm b)$  where a and b are small (typically a = 2, b = 1). Using the current version of the GNFS it is predicted that it will require  $3x10^4$  MIPS-years to factor a 512 bit number. In general the difficulty of factoring is exponentially related to the length of the number being factored and hence the security of the QRG scales exponentially with the size of the modulus used (i.e., security is  $O\left(e^{n^V(\ln(\ln 2) + \ln 2 \cdot \log_2 n)^{1-v}(\ln 2)^V}\right)$  where n is the length of the modulus). Figure 2-12 shows how the amount of computation scales with modulus length for the GNFS algorithm.

| Algorithm                  | а                     | ν   |

|----------------------------|-----------------------|-----|

| General Number Field Sieve | (64/9) <sup>1/3</sup> | 1/3 |

| Special Number Field Sieve | $(32/9)^{1/3}$        | 1/3 |

| Quadratic Sieve            | 1                     | 1/2 |

Table 2-1: Algorithm Parameters for Several Factoring Algorithms

Figure 2-12: Amount of Computation Required for Factoring Using the GNFS

# 2.7 An Existing System - the Group Special Mobile (GSM) Standard

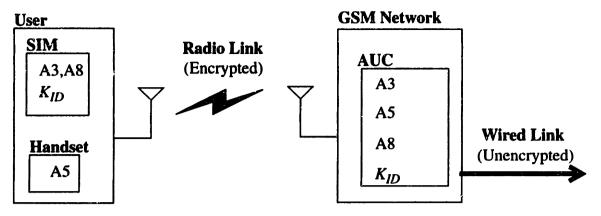

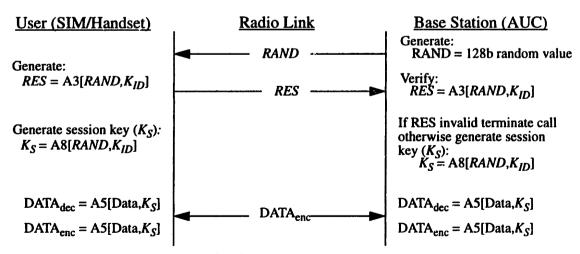

GSM is the third-generation cellular telecommunications standard currently being introduced in Europe and represents the most secure cellular telecommunications standard in existence today. The provision for radio link encryption/decryption is defined in the standard itself [22] and goes far beyond the primitive security standards of the Advanced Mobile Phone Standard (AMPS) system that is currently in place in North America. GSM utilizes three separate algorithms for performing authentication, temporary key generation and actual data encryption/decryption:

- A3: a 128-bit to 64-bit one-way hash function used for performing user authentication

- A5: a symmetric 64-bit key stream cipher used for data encryption/decryption

- A8: a 128-bit to 64-bit one-way hash function used for generating temporary session keys

The protocol relies on the existence of a unique secret subscriber ID key  $(K_{ID})$  that is stored within a Subscriber Identification Module (SIM) [23] carried by the user and within the Authentication Center (AUC) [24] of the GSM network (Figure 2-13). Encryption is performed only over the wireless link. Once inside of the wired portion of the network it is transmitted in an unencrypted format.

Figure 2-13: Distribution of Security Features in a GSM Network

At the start of a call, the network sends a 128 bit random value (RAND) to the user who in turn hashes this value under the influence of  $K_{ID}$  to generate a 64 bit response ( $RES = A3[RAND,K_{ID}]$ ) which it returns to the network. The network compares this value with the expected value (determined by applying A3 to its copy of RAND and  $K_{ID}$ ) and if the two match, it concludes that the user is in fact who they claim to be (as only they would know the value of  $K_{ID}$ ) and allows the call to continue. If encryption is required, the user generates a temporary session key ( $K_S$ ) by applying A8 to RAND under the influence of  $K_{ID}$ . All data transfers are then encrypted/decrypted using A5 keyed with  $K_S$ . This protocol is shown in Figure 2-14.

Figure 2-14: GSM Security Protocol

The GSM protocol demonstrates several features that are essential to a usable wi eless communication system and which should be considered by a wireless security systems designer:

- No secret information is ever allowed onto the unsecure radio link, it is always stored away inside of the SIM or AUC, both of which are assumed to be secure from tampering by an attacker.

- Data encryption keys are generated for each session, thereby forcing an attacker to start each attack from scratch.

- Users must authenticate themselves via a challenge-response protocol in which the

network forces the user to generate a value that can only be calculated with knowledge of some secret information that is assumed to be known only by the intended

receiver.

- There is no need for a complicated key exchange protocol as both the user and the network have copies of the secret key  $(K_{ID})$  that is distributed with the SIM given to the user when they register with the network.

# **Chapter 3**

# LFSR-Based Stream Cipher Systems

The simplicity of LFSRs make LFSR-based stream ciphers a very attractive alternative for hardware implementations. Numerous LFSR-based stream cipher designs have been proposed and subsequently broken due to weaknesses in their construction (e.g., the Stop and Go Generator [25], the Geffe Generator [26], and the Jennings Generator [27]). Here several LFSR-based stream ciphers that appear to be secure, to the limits discussed within each description, are discussed. The power consumption of each algorithm is then estimated and various techniques for reducing the power consumption are described. Finally a test chip implementation of the algorithms is described and the test results are presented.

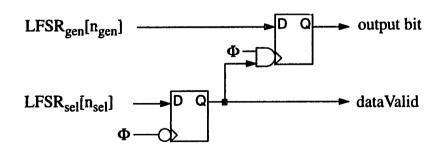

# 3.1 Shrinking Generator

The Shrinking Generator was first proposed by Coppersmith et. al. [28] as an efficient and reasonably secure (i.e., no obvious weaknesses) pseudorandom bit generator for use in stream cipher systems. The generator is based on the idea of a variable decimation of a pseudorandom sequence.

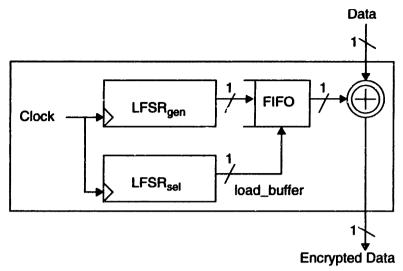

The Shrinking Generator utilizes a selection LFSR (LFSR<sub>sel</sub>) to determine whether the output of the generating LFSR (LFSR<sub>gen</sub>) is to be used within the keystream (Figure 3-1). If the output of LFSR<sub>sel</sub> is a "1" then the output of LFSR<sub>gen</sub> is added to the keystream, if not, then the output of LFSR<sub>gen</sub> is discarded. The output of the generator represents a varying decimation of LFSR<sub>gen</sub>, as governed by LFSR<sub>sel</sub>.

Figure 3-1: Shrinking Generator

Assuming that both LFSR<sub>sel</sub> and LFSR<sub>gen</sub> are maximal length and their periods are relatively prime (i.e.,  $gcd(T_{sel},T_{gen}) = 1$ ), then the linear complexity and period of the Shrinking Generator are given by the expressions:

$$LC > |G| \cdot 2^{|S|-2}$$

$$T = \left(2^{|G|} - 1\right) \cdot 2^{|S|-1}$$

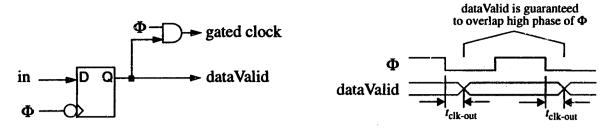

where |G| and |S| are the lengths of LFSR<sub>gen</sub> and LFSR<sub>sel</sub> respectively. Assuming a data rate of 1 Mbps and choosing |S| = 44 and |G| = 41, the attacker will have to wait at least 10 years to obtain enough output values to mount an attack based on the linear complexity or period. The exponential dependance of both the linear complexity and period on the length of the selection register implies that LFSR<sub>sel</sub> should be as long as possible.

One obvious shortcoming of the Shrinking Generator is that it does not guarantee a keystream bit will be output on any given clock cycle. Hence the generator must utilize a higher clock frequency and an output buffer to ensure that there is always a keystream bit available. Kessler and Krawczyk proposed a model [29] for determining the required clock rate and buffer length in order to guarantee a certain miss probability and also proposed an empirical expression for estimating the miss probability given a certain buffer length (B) and clock rate multiplier  $(\alpha)$ :

$$M(\alpha, B) \approx e^{-6.779 - 1.335\alpha B + 1.731\alpha^2 + 2.554B}$$

(3-1)

For large buffer sizes (e.g., 1024 bits) and modest clock rate increases (e.g., 2x), the miss probability can be effectively forced to zero (M(2,1024) =  $3x10^{-52}$ ).

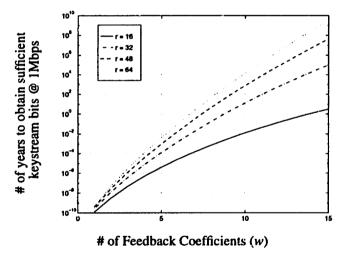

Currently the best known attack on the Shrinking Generator reduces its effective key length to ISI or 2ISI if the feedback polynomials are programmable. Another attack, based on Linear Cryptanalysis, was inferred by Golic [30]. Such an attack would require approximately  $40(6.28 \cdot r/w)^w$  keystream bits to detect a weakness that could then be exploited, where r is the length of LFSR<sub>gen</sub> and w is one less than the number of non-zero feedback polynomial coefficients of LFSR<sub>gen</sub>. Figure 3-2 show the infeasibility of such an attack assuming a keystream generator output rate of 1 Mbps. For a modestly sized LFSR<sub>gen</sub> (r = 32 bits) with only 10 non-zero feedback polynomial coefficients, it would require approximately 13.6 years to observe a sufficient amount of keystream bits to mount an attack.

Figure 3-2: Time to Accumulate Keystream Bits for Linear Cryptanalysis of Shrinking Generator

# 3.2 Self-Shrinking Generator

The Self-Shrinking Generator [31] is a modification of the Shrinking Generator to reduce the hardware requirements by incorporating both LFSR<sub>sel</sub> and LFSR<sub>gen</sub> into one LFSR (Figure 3-3). On each clock cycle, the most significant bit of the LFSR is examined and if it is a "1" the second most significant bit of the LFSR is added to the keystream. The shift

register is then clocked twice and the whole process is repeated with the two new most significant bits.

Figure 3-3: Self-Shrinking Generator

If the LFSR is a maximal length LFSR, the linear complexity and period of the Self-Shrinking Generator are given by the expressions:

$$T \ge 2^{\lfloor n/2 \rfloor}$$

$$LC > 2^{\lfloor n/2 \rfloor - 1}$$

where n is the length of the LFSR. Meier and Staffelbach have conducted experiments [31] where they have discovered that for all n such that 3 < n < 20 the period is always maximal (i.e.,  $2^n - 1$ ) given a maximal length LFSR. In addition, the linear complexity was found to be very close to maximal (i.e.,  $2^{n-1} - 1$ ) for n < 16. Continuing the assumption of a data rate of 1 Mbps and choosing n = 101 bits, an attacker will require approximately 32 years to obtain enough output values to mount an attack using either the linear complexity or period of the Self-Shrinking Generator.

Early cryptanalytic results provided in [31] demonstrate that the Self-Shrinking Generator has an effective key length of  $2^{0.375n}$  with a fixed feedback polynomial and  $2^{0.875n}$  with a variable feedback polynomial. This compares favourably with the effective key

length of the Shrinking Generator which is approximately  $2^{0.5(nsel + ngen)}$ . However, it must be emphasized that these are preliminary results -- the algorithm is still too new to have had a thorough cryptanalytic analysis. Only time and scrutiny will tell just how secure the Self-Shrinking Generator really is.

One obvious drawback of the Self-Shrinking Generator is that the LFSR must be clocked at twice the rate of the Shrinking Generator, which in turn is operating at some multiple of the data rate. This higher clock rate will directly affect the power consumption of the algorithm.

# 3.3 Alternating-Stop-and-Go Generator

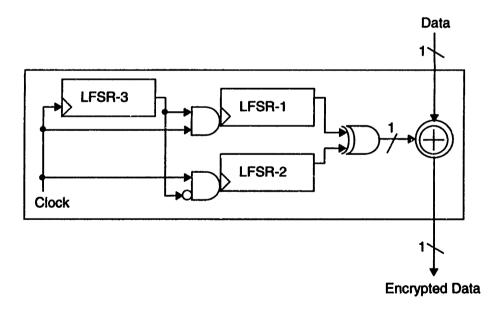

The Alternating Stop and Go Generator [32] utilizes two clock-controlled LFSRs whose outputs are XORed together to produce the keystream. The clock control is performed using a third LFSR whose output determines which of the two LFSRs is to be clocked on any given cycle (Figure 3-4).

Figure 3-4: Alternating Stop & Go Generator

Assume that the LFSR<sub>1</sub>, LFSR<sub>2</sub>, and LFSR<sub>3</sub> are maximal length LFSRs of lengths  $n_1$ ,  $n_2$ , and  $n_3$  respectively and the periods of LFSR<sub>1</sub> and LFSR<sub>2</sub> are relatively prime. The period and linear complexity of the generator are then given by the expressions:

$$T_{ASG} = T_{LFSR3} \cdot T_{LFSR2} \cdot T_{LFSR1} \approx 2^{n_1 + n_2 + n_3}$$

$$LC > (n_1 + n_2) \cdot (2^{n_3} - 1)$$

With a 1 Mbps data rate and LFSRs of length 29, 31, and 47 bits respectively an attacker will require over 7 years to obtain enough output values to attack using either the linear complexity or period.

The best known attack on the Alternating Stop & Go Generator is a correlation attack on LFSR<sub>3</sub> [32] that effectively reduces the number of keys that must be searched to its third root (i.e., the length of LFSR<sub>3</sub>), assuming that all LFSRs are of similar length. This attack can be overcome by choosing a sufficiently large value for  $n_3$ .

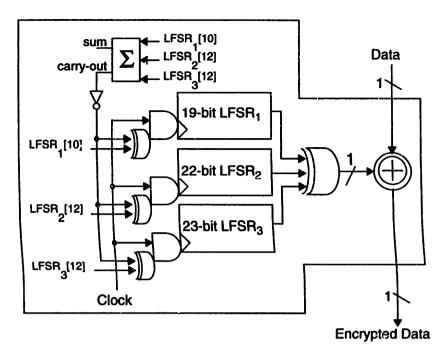

# 3.4 Proposed GSM Cipher (A5)

The proposed stream cipher algorithm (A5) used in the GSM cellular network standard is somewhat of a mystery and still officially remains a secret. However, several noted cryptographers have speculated as to its design and have proposed the construction described below ([33], [34]) based on information that they have gleaned from various sources. A5 utilizes three fixed-length LFSRs (LFSR<sub>1</sub>, LFSR<sub>2</sub>, and LFSR<sub>3</sub>) with fixed feedback polynomial connections (Figure 3-5). The clock control function of the registers is derived by XORing the inverted carry-out bit from the summation of the three LFSRs' middle bits with that register's middle bit. This ensures that at least two of the three registers are clocked on any given cycle.

Since A5 is not yet officially released, the linear complexity and period of the cipher have yet to been quantified. However, some analysis of the security of the cipher has led to the conclusion that it is far from secure due to its relatively short LFSRs and the fact that the feedback connections are fixed. A simple attack was proposed by Dr. Ross Anderson [34] that reduces the effective key length to just 41 bits by guessing the contents of LFSR<sub>1</sub> and LFSR<sub>2</sub>, determining the contents of LFSR<sub>3</sub> from examination of the keystream and then continuing on to determine if the guesses were in fact correct. Other attacks are said to exist but they are still awaiting publication.

Figure 3-5: GSM Cipher (i.e., A5)

According to Schneier, the basic structure and underlying construction of A5 look very promising [33]. However, to be truly effective, the LFSRs must be made longer and the feedback polynomials must be made programmable. In its current form A5 provides only a marginal level of security.

# 3.5 Estimating the Power Consumption

The various LFSR-based ciphers differ in terms of their power consumption as dictated by their clock-control schemes and non-linear combining functions. The basic hardware circuit in all of the aforementioned ciphers is the LFSR, whose power consumption is represented as a function of their length (i.e., P(n)) and the probability that they will be clocked on any given cycle (i.e.,  $\alpha$ ). A first order approximation of the power consumption of each scheme can be estimated and compared using these building blocks. Note that the ciphers must be normalized in terms of their security to provide a meaningful comparison.

The Alternating Stop and Go (ASG) Generator utilizes LFSR<sub>3</sub> to control the clocking of LFSR<sub>1</sub> and LFSR<sub>2</sub>, whose outputs are then XORed to produce the keystream. On any given cycle, the probability of clocking LFSR<sub>1</sub> is 1/2 and the probability of clocking LFSR<sub>2</sub> is 1/2 as well. However, only one of the two can ever be clocked on any given

cycle, hence  $\alpha_1 = \alpha_2 = 1/2$ , and  $\alpha_3 = 1$ . The combining function is the XOR of the outputs of LFSR<sub>1</sub> and LFSR<sub>2</sub>, both of which are assumed to be equally likely a 1 or 0, therefore  $\alpha_{\text{out}} = 1/2$ . Combining these results, a preliminary power estimate for the ASG is given by the expression:

$$\begin{split} P_{ASG} &= \alpha_1 \cdot P(l_1) + \alpha_2 \cdot P(l_2) + \alpha_3 \cdot P(l_3) + \alpha_{out} \cdot P(xor) \\ &= \frac{1}{2} (P(l_1) + P(l_2)) + P(l_3) + \frac{1}{2} P(xor) \end{split}$$

where  $l_1$ ,  $l_2$ , and  $l_3$  are the lengths of LFSR<sub>1</sub>, LFSR<sub>2</sub>, and LFSR<sub>3</sub> respectively.

The Shrinking Generator utilizes  $LFSR_{sel}$  to determine whether or not the output of  $LFSR_{gen}$  is to be used in the output keystream. Since there is no guarantee that a valid output will occur on any given cycle, the clock rate of the generator must be increased and an output buffer utilized to ensure that the probability of not having a valid output bit being output on any given cycle is sufficiently low. This increased clock rate is indicated by the multiplication factor k. Note that the power consumption of the output buffers are not accounted for in this analysis as all of the generators will implicitly require output buffering in order to decouple them from the data stream. The estimated power consumption of the Shrinking Generator is given by the expression:

$$P_{SG} = k \cdot \alpha_{sel} \cdot P(l_{sel}) + k \cdot \alpha_{gen} \cdot P(l_{gen})$$

=  $k(P(l_{sel}) + P(l_{gen}))$

where  $l_{sel}$  and  $l_{gen}$  are the lengths of LFSR<sub>sel</sub> and LFSR<sub>gen</sub> respectively.

The Self-Shrinking Generator requires only a single LFSR whose clock rate must be double that of the Shrinking Generator. The power consumption of the output buffers is once again ignored. The estimated power consumption of the Self-Shrinking Generator is:

$$P_{SSG} = 2 \cdot k \cdot \alpha \cdot P(l)$$

= 2 \cdot k \cdot P(l)

where l is the length of the LFSR.

The GSM Cipher uses 3 LFSRs (LFSR<sub>19</sub>, LFSR<sub>22</sub>, and LFSR<sub>23</sub>) whose clock control is derived from the summation of the middle bits of the LFSRs. The clocking probabilities of all 3 LFSRs is  $\alpha = 3/4$ , as derived using Table 3-1 and the output is the XOR of the three LFSRs' outputs. Using these results the power consumption of the GSM Cipher can be estimated to be:

$$P_{SG} = \alpha_{19} \cdot P(19) + \alpha_{22} \cdot P(22) + \alpha_{22} \cdot P(23) + \alpha_{out} \cdot P(xor3)$$

$$= \frac{3}{4} (P(19) + P(22) + P(23)) + \frac{1}{2} P(xor3)$$

| Middle Bits        |                    |                    | Clock Enable       |                    |                    |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|

| LFSR <sub>19</sub> | LFSR <sub>22</sub> | LFSR <sub>23</sub> | LFSR <sub>19</sub> | LFSR <sub>22</sub> | LFSR <sub>23</sub> |  |

| 0                  | 0                  | 0                  | 1                  | 1                  | 1                  |  |

| 0                  | 0                  | 1                  | 1                  | 1                  | 0                  |  |

| 0                  | 1                  | 0                  | 1                  | 0                  | 1                  |  |

| 0                  | 1                  | 1                  | 0                  | 1                  | 1                  |  |

| 1                  | 0                  | 0                  | 0                  | 1                  | 1                  |  |

| 1                  | 0                  | 1                  | 1                  | 0                  | 1                  |  |

| 1                  | 1                  | 0                  | 1                  | 1                  | 0                  |  |

| 1                  | 1                  | 1                  | 1                  | 1                  | 1                  |  |

Table 3-1: Clocking function for the GSM Cipher

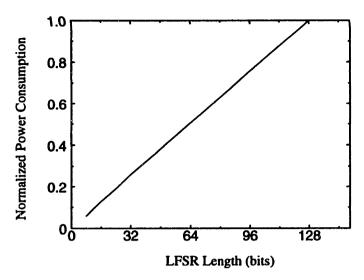

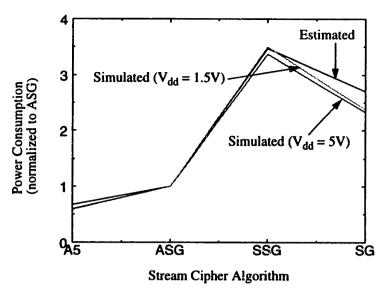

Experimentation using EPIC's Powermill power estimation tool has shown (Figure 3-6) that to a first order approximation, the power consumption for an LFSR is a linear function that scales directly with its length (i.e., z(P(x) + P(y)) = P(z(x + y))). Hence, the aforementioned power estimates can be directly compared to determine which is the most efficient algorithm. For the comparison, the effective key length was chosen to be 40 bits as it is the effective key length of A5. Since the effective key length of A5 is fixed and cannot be changed, all other algorithms were scaled accordingly.

Figure 3-6: Normalized Power Consumption as a Function of LFSR Length

Table 3-2 summarizes the results of this comparison and shows that A5 provides the most efficient implementation in terms of power consumption. Note that the power consumption of any output combining function XORs is minimal in comparison to the power consumption of the shift registers and hence it has been ignored.

| Algorithm                | Parameters                            | Estimated Power |  |

|--------------------------|---------------------------------------|-----------------|--|

| Alternating Stop & Go    | $l_1 = 31, l_2 = 32, l_3 = 41$        | P(72)           |  |

| Shrinking Generator      | $l_{gen} = 37, l_{sel} = 41, k = 2.5$ | P(195)          |  |

| Self-Shrinking Generator | l = 50, k = 2.5                       | P(250)          |  |

| A5                       |                                       | P(48)           |  |

**Table 3-2:** Power Consumption Estimates

Simulations on the fully extracted layouts of the 4 stream ciphers were performed using Powermill. They show that the above estimates are quite accurate (Figure 3-7), differing by at most 16%.

Figure 3-7: Comparison of Power Consumption (Estimate vs. Powermill Simulations)

# 3.6 Reducing the Power Consumption

#### 3.6.1 Conventional Supply Scaling

Analysis of the various LFSR-based stream ciphers leads to the conclusion that their critical path is short enough that they can satisfy the 1 Mbps data throughput requirement while operating at the minimum allowable supply voltage of 1.5V.

#### 3.6.2 Parallelizing the LFSRs

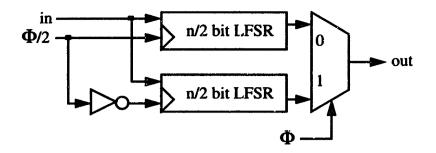

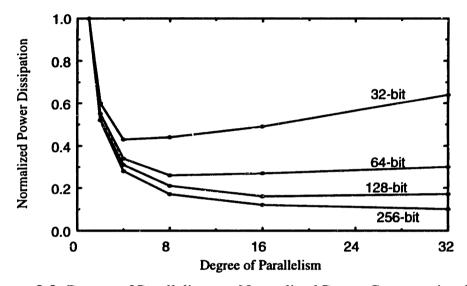

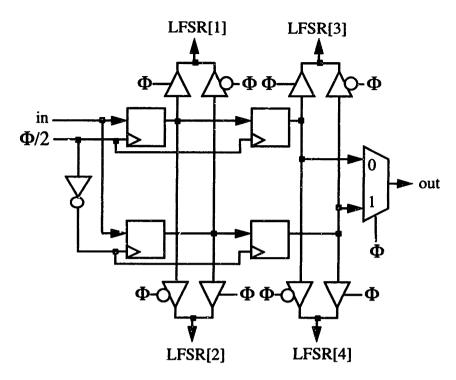

With the supply voltage minimized, the power consumption can be reduced further still by reducing the clock frequency of the LFSRs by parallelizing the shift registers used to construct them. An example of a 2-way parallel shift register implementation is shown in Figure 3-8. The parallel shift register utilizes a half rate clock but requires additional multiplexing and routing. Higher degrees of parallelism will also require control circuitry to generate multiple clock phases for each of the parallel registers. The multiplexor, routing and clock generation circuitry overhead is ultimately what determines the optimal degree of parallelization (Figure 3-9 [35]).

Figure 3-8: 2-way Parallel Shift Register

Figure 3-9: Degree of Parallelism vs. Normalized Power Consumption for Shift Registers

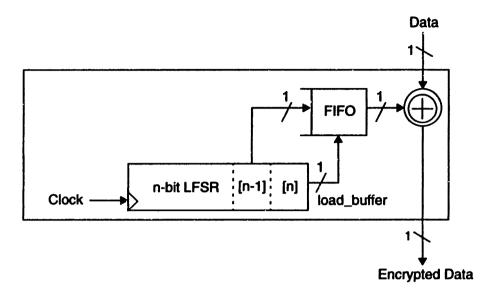

Parallelizing LFSRs is not quite so straightforward. The feedback tap positions must change their relative positions with time as the location of bit i within the LFSR changes from cycle to cycle. In general, for an n-way parallelized LFSR, the location of bit i can be any of n positions. The additional multiplexing required for the feedback taps increases the overhead dramatically (Figure 3-10), making the optimum parallelization quite different from that of the simple shift register. Analysis using 520-bit matched filters with 32 feedback taps showed that the optimal amount degree of parallelism is only 2 [35].

Figure 3-10: 2-way Parallelized LFSR

Unfortunately, it was not possible to implement parallel LFSRs during the layout of the Stream Cipher Test Chip due to time restrictions. A second-generation stream cipher test chip that will utilize the techniques described above is currently in development.

# 3.7 Stream Cipher Test Chip Design

The four aforementioned LFSR-based stream cipher designs are quite similar in design, consisting of multiple linear feedback shift registers with algorithmic-specific output-combiner and clock-control circuitry. The design details of the output combiner and clock-control circuitry are described in this section, along with the design of the variable length LFSRs with programmable feedback polynomials used in three of the four stream cipher designs.

A full set of schematics for all four LFSR-based stream ciphers can be found in Appendix A.

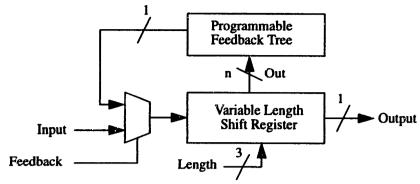

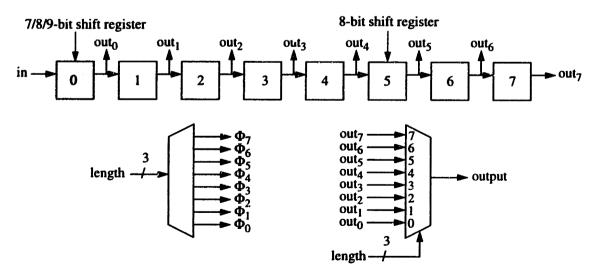

#### Variable Length LFSRs With Programmable Feedback

The basic building block of three of the four stream cipher designs is a variable length LFSR with programmable feedback. These LFSRs were constructed using a variable

length shift register and programmable feedback tree (Figure 3-11).

Figure 3-11: Variable Length LFSR Block Diagram