# Radiation Management, Avionics Development, and Integrated Testing of a Class-D Space-Based Asteroid X-ray Spectrometer

bу

#### Pronoy K. Biswas

B.S., Electrical and Computer Engineering

Carnegie Mellon University (2014)

Submitted to the Department of Aeronautics and Astronautics in partial fulfillment of the requirements for the degree of

Master of Science in Aeronautics and Astronautics

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2016

© Massachusetts Institute of Technology 2016. All rights reserved.

| Author       |                             | Signature red                       | acted             |

|--------------|-----------------------------|-------------------------------------|-------------------|

| indication   |                             | Department of Aeronautics           | and Astronautics  |

| Certified by | Signati                     | ure redacted                        | June 29, 2016     |

|              |                             | Rebe                                | ecca A. Masterson |

|              | Research                    | Engineer, Department of Aeronautics | and Astronautics  |

| Certified by |                             | Signature redacted                  | Thesis Supervisor |

| ·            |                             |                                     | Richard P. Binzel |

|              |                             | Professor of                        | Planetary Science |

|              |                             | Joint Professor of Aeronautics      |                   |

| Accepted by  | Sigr                        | nature redacted                     | Thesis Supervisor |

| 1            |                             |                                     | Paulo C. Lozano   |

| MASSACHU     | SETTS INSTITUTE<br>CHNOLOGY | Associate Professor of Aeronautics  | and Astronautics  |

| OF 12        | 0.6.2016                    | Chairman, Graduate Pro              | ogram Committee   |

#### **DISCLAIMER NOTICE**

Due to the condition of the original material, there are unavoidable flaws in this reproduction. We have made every effort possible to provide you with the best copy available.

Thank you.

The images contained in this document are of the best quality available.

## Radiation Management, Avionics Development, and Integrated Testing of a Class-D Space-Based Asteroid X-ray Spectrometer

by

#### Pronoy K. Biswas

Submitted to the Department of Aeronautics and

Astronautics on June 29, 2016 in partial fulfillment of the

requirements for the degree of Master of Science in

Aeronautics and Astronautics

#### **Abstract**

The Regolith X-ray Imaging Spectrometer (REXIS) is a student designed and built payload instrument aboard NASA's OSIRIS-REx asteroid sample return mission. The interplanetary target for this mission is a primitive asteroid known as Bennu that is believed to be relatively unchanged since the formation of the Solar System over 4.5 billion years ago. The primary goal of REXIS is to provide data to determine the elemental abundance composition of Bennu's surface through the measurement of X-ray fluorescence from Bennu's regolith. Achieving this goal requires the REXIS instrument to have an avionics system designed to operate the x-ray detectors, perform some preliminary processing of the x-ray events detected, and transfer this information to the main spacecraft computer for transmission to Earth. REXIS avionics accomplish these tasks using a mixture of commercial and spaceflight-grade hardware, reconfigurable Xilinx and Actel FPGAs, and a softcore MicroBlaze processor. Although the REXIS instrument is classified as a high-risk Class-D project by NASA, it must safely interface (in the manner of "do no harm") with the low-risk Class-B OSIRIS-REx spacecraft. Furthermore, REXIS must operate in the interplanetary space radiation environment of the OSIRIS-REx mission. This thesis details the REXIS avionics system and its novel features for collecting scientific x- ray data, interfacing safely with the OSIRIS-REx main spacecraft in spite of differing Class B/D risk postures, and robust operation in the interplanetary space radiation environment. Emphasis is placed on how the REXIS avionics design and radiation hazard mitigation features were implemented with significant budget and time constraints.

Thesis Supervisor: Rebecca A. Masterson

Title: Research Engineer, Department of Aeronautics and Astronautics

Thesis Supervisor: Richard P. Binzel

Title: Professor of Planetary Science, Joint Professor of Aeronautics and Astronautics

#### Acknowledgements

This work was supported by NASA Goddard Space Flight Center under NASA contract #NNG12FD70C (Origins Spectral Interpretation Resource Identification Security Regolith Explorer (OSIRIS-REx) REgolith X-ray Imaging Spectrometer (REXIS), Phases B/C/D). I gratefully thank the sponsors for their generous support that made this work possible.

I would like to thank Dr. Rebecca Masterson and Professor Richard Binzel for starting the REXIS project, guiding me through the project development, giving me encouragement, and helping me write this thesis. I am also thankful for Dr. Alvar Saenz-Otero and his advice and guidance that was essential for this thesis.

I enjoyed working with my REXIS team-mates and greatly appreciate their support, both throughout the project and for writing this document. I would not have been able to get started without the mentoring of Shuyi Chen and Mike Jones. I appreciate the practical advice and encouragement from Mark Chodas throughout the REXIS project. Finally, Conor McMenamin, Laura Bayley, and David Carte always made our office a fun and productive place to work.

I was extremely lucky to have support outside of MIT. The advice, guidance, and know-how of Ed Bokhour, Robert Grimes, Branden Allen, Jaesub Hong, Jonathan Boblitt, Dave Petrick, Eric Haggquist, and James Dailey made my contributions to REXIS possible and taught me so much about space systems engineering.

Finally, I am very thankful for my friends and family for their love, guidance, and unwavering support during the REXIS project. Their invaluable love, help, editing and encouragement has allowed me to complete this document.

## Contents

| Chapter 1 - Intro | oduction                                    | 13   |

|-------------------|---------------------------------------------|------|

| 1.1 Backgrou      | und and Motivation                          | 14   |

| 1.2 OSIRIS-I      | REx Spacecraft Overview                     | 16   |

| 1.2.1 OSIRIS      | IS-REx Spacecraft Bus                       | 17   |

| 1.2.2 Regoli      | ith Sample Acquisition and Delivery         | 18   |

| 1.2.3 OSIRI       | IS-REx Payload Instruments                  | . 19 |

| 1.3 REXIS In      | nstrument Overview                          | . 21 |

| 1.3.1 REXIS       | S Science Process and Data                  | . 22 |

| 1.3.2 REXIS       | S System Description                        | . 26 |

| 1.4 Thesis Ro     | Coadmap                                     | . 29 |

| Chapter 2 - Inter | eraction of Space Radiation and Electronics | . 31 |

| 2.1 Space Ra      | adiation Environment                        | . 31 |

| 2.2 Radiation     | n-caused Electrical Malfunctions            | . 38 |

| 2.2.1 Single      | Event Upset                                 | . 39 |

| 2.2.2 Single      | Event Transient                             | . 41 |

| 2.2.3 Single      | e Event Latch-up                            | . 41 |

| 2.2.4 Single      | e Event Gate Rupture                        | . 42 |

| 2.2.5 Total I     | Ionizing Dose                               | . 42 |

| 2.2.6 Total ?     | Non-Ionizing Dose                           | . 44 |

| 2.3 Techniqu      | ues for Radiation Risk Mitigation           | . 44 |

| 2.3.1 System      | m-wide Design for Radiation                 | . 46 |

| 2.3.2       | Radiation Hardened Parts                              |

|-------------|-------------------------------------------------------|

| 2.3.3       | Shielding53                                           |

| 2.3.4       | Latch-up protection circuitry                         |

| 2.3.5       | Error correction codes                                |

| 2.3.6       | Redundancy                                            |

| 2.4 S       | ummary of Radiation Effects and Mitigation Techniques |

| Chapter 3 - | REXIS Avionics Overview                               |

| 3.1 It      | ntroduction to REXIS Avionics                         |

| 3.1.1       | Avionics Functional Overview                          |

| 3.1.2       | Avionics Hardware Overview                            |

| 3.1.3       | Avionics Software and FPGA Core Overview              |

| 3.1.4       | Avionics Power Overview                               |

| 3.1.5       | Interface between REXIS Avionics and OSIRIS-REx       |

| 3.2 D       | Description of Software and FPGA Cores                |

| 3.2.1       | FSW Main Loop and Interrupt Service Routines 80       |

| 3.2.2       | Timekeeping  83                                       |

| 3.2.3       | Command Processing 84                                 |

| 3.2.4       | Radiation Cover Actuation 87                          |

| 3.2.5       | Image Processing • 90                                 |

| 3.2.6       | SXM Control and Data Processing 96                    |

| 3.2.7       | Housekeeping Data Acquisition 98                      |

| 3.2.8       | Telemetry Packaging 0 100                             |

| 3.2.9       | Function Upload                                       |

| 3.3 H       | lardware Description                                    | 103 |

|-------------|---------------------------------------------------------|-----|

| 3.3.1       | Main Electronics Board (MEB)                            | 104 |

| 3.3.2       | Interface Board •                                       | 116 |

| 3.3.3       | Video Board                                             | 118 |

| Chapter 4 - | Radiation Tolerant Design of REXIS Avionics.            | 119 |

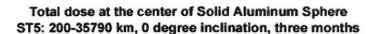

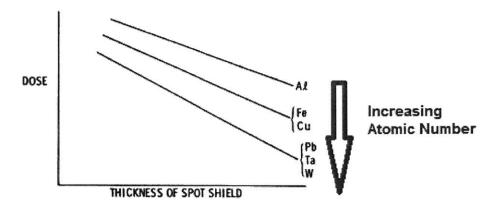

| 4.1 R       | EXIS Radiation environment overview                     | 120 |

| 4.2 D       | Design for Radiation Tolerance                          | 123 |

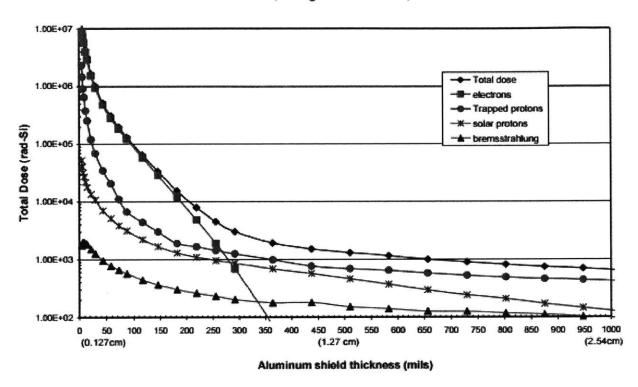

| 4.2.1       | Shielding                                               | 123 |

| 4.2.2       | Avionics Component Selection and Design                 | 124 |

| 4.3 N       | 1EB Design for Radiation                                | 129 |

| 4.3.1       | Xilinx Virtex5 FPGA                                     | 129 |

| 4.3.2       | NOR Flash                                               | 130 |

| 4.3.3       | SDRAM                                                   | 131 |

| 4.3.4       | Spacecraft Interface Hardware                           | 131 |

| 4.3.5       | Frangibolt Drive Circuitry                              | 132 |

| 4.3.6       | Analog to Digital Converters                            | 133 |

| 4.3.7       | SXM Circuitry                                           | 134 |

| 4.3.8       | Power System                                            | 136 |

| 4.4 D       | DE Design for Radiation                                 | 137 |

| 4.4.1       | Interface Board                                         | 137 |

| 4.4.2       | Video Board                                             | 140 |

| 4.5 S       | ummary of REXIS Avionics Mitigation of Radiation Hazard | 142 |

| Chapter 5 - | Lessons Learned and Conclusion                          | 145 |

| 5.1 Reconfigurability Facilita | ates Project Development         | 145 |

|--------------------------------|----------------------------------|-----|

| 5.1.1 FPGA Digital Logic Co    | ores                             | 146 |

| 5.1.2 Microblaze Processor     |                                  | 148 |

| 5.1.3 Image Processing         |                                  | 149 |

| 5.1.4 Importance of Avionics   | s Reconfigurability              | 151 |

| 5.2 Importance of keeping FS   | SW simple                        | 153 |

| 5.2.1 Software Development     | t with C Programming Language    | 153 |

| 5.2.2 Minimizing the Number    | er of Interrupt Service Routines | 154 |

| 5.3 Conclusion                 |                                  | 159 |

| Bibliography                   |                                  | 161 |

## List of Figures

|     | Figure 1-1: Pictures of the OSIRIS-REx Spacecraft                                           | 18   |

|-----|---------------------------------------------------------------------------------------------|------|

|     | Figure 1-2: OSIRIS-REx Remote Sensing Instruments                                           | 20   |

|     | Figure 1-3: REXIS X-ray Data Acquisition (Credit: Branden Allen and Niraj Inamdar)          | 23   |

|     | Figure 1-4: REXIS Coded Aperture Mask [3]                                                   | 24   |

|     | Figure 1-5: REXIS Scientific Data Products [10]                                             | 25   |

|     | Figure 1-6: REXIS Main Spectrometer and SXM Aboard OSIRIS-REx (Credit: Lockheed Martin)     | 26   |

|     | Figure 1-7: REXIS Spectrometer Physical Overview [3]                                        | 27   |

|     | Figure 1-8: REXIS SXM Physical Overview [8]                                                 | 28   |

|     | Figure 2-1: Origins of Space Radiation (Credit: NASA Space Environments and Effects Office) | . 32 |

|     | Figure 2-2: Dose-rate Comparison of Earth-based Radiation Sources and Space Radiation [18]  | . 33 |

|     | Figure 2-3: Abundances (a) and Energy Spectra (b) of Galactic Cosmic Radiation (GCR) [19]   | . 35 |

|     | Figure 2-4: Sunspot Count vs. SPE Occurrences with 100MeV Protons [15]                      | 36   |

|     | Figure 2-5: Structure of the Van Allen Belts (Idealized) [21]                               | . 37 |

|     | Figure 2-6: SRAM (a) and DRAM (b) Memory Cells                                              | . 39 |

|     | Figure 2-7: Radiation Hazard Mitigation Techniques                                          | . 45 |

|     | Figure 2-8: Perijove Passage through Jupiter's Radiation Environment [22]                   | . 47 |

|     | Figure 2-9: Degradation of the Input Bias Current vs TID Imparted to the LM311 Voltage      |      |

| Con | nparator for Various Dose Rates and Temperatures [26]                                       | . 48 |

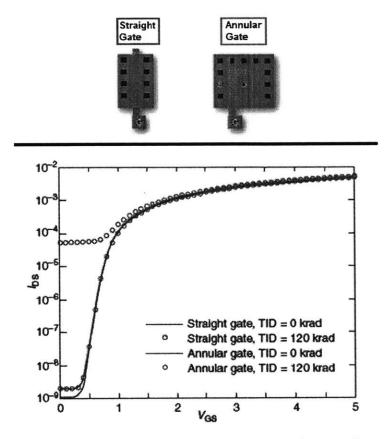

|     | Figure 2-10: Transistor Current vs. Control Voltage for a Radiation-tolerant Device [17]    | . 51 |

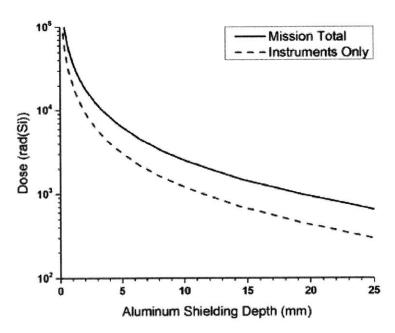

|     | Figure 2-11: Radiation Dose vs. Aluminum Shielding Thickness [26]                           | . 54 |

|     | Figure 2-12: Shielding Effectiveness of Various Elements [27]                               | . 55 |

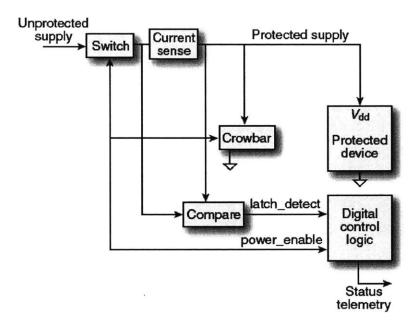

|     | Figure 2-13: Active SEL-protection Circuitry [17]                                           | . 56 |

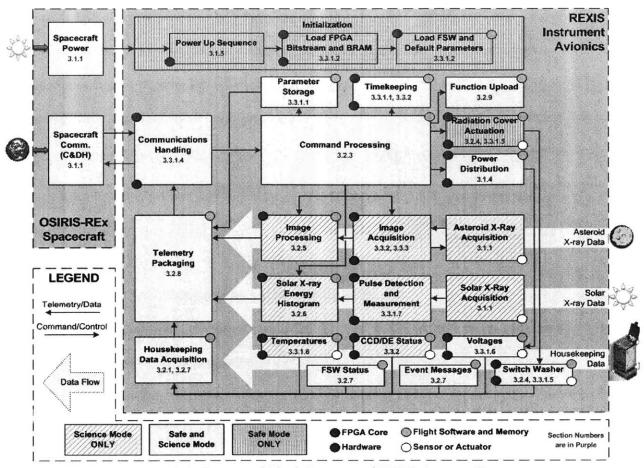

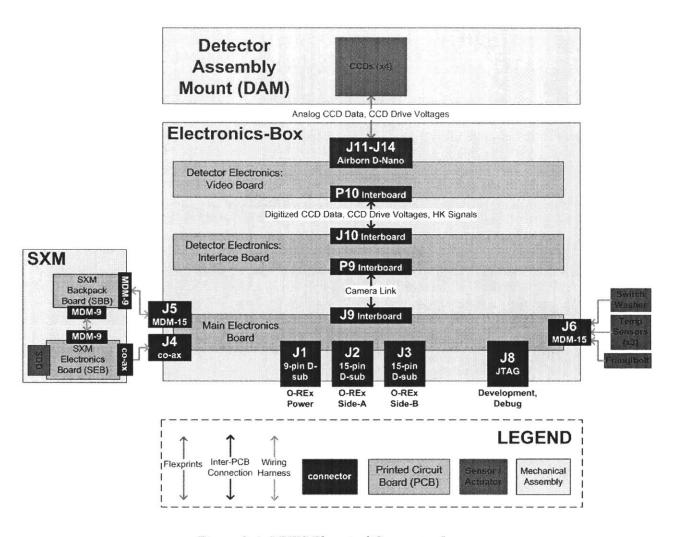

|     | Figure 3-1: Functional Block Diagram of REXIS Avionics System                               | . 63 |

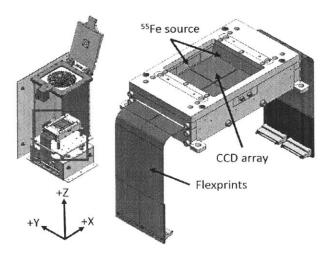

|      | Figure 3-2: REXIS CCD Sensors in the Detector Assembly Module (DAM) [3]                  | 65    |

|------|------------------------------------------------------------------------------------------|-------|

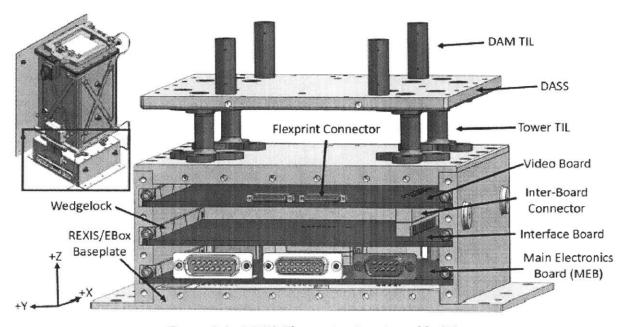

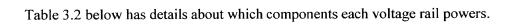

|      | Figure 3-3: REXIS Electronics Box Assembly [3]                                           | 66    |

|      | Figure 3-4: REXIS Electrical Connector Layout                                            | 67    |

|      | Figure 3-5: Renderings of the FM Solar X-ray Monitor                                     | 68    |

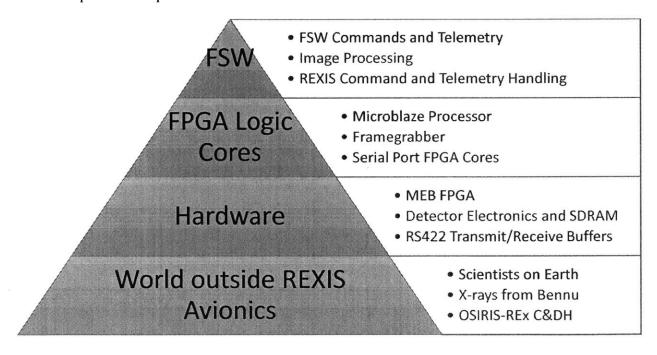

|      | Figure 3-6: FSW Support Structure                                                        | 69    |

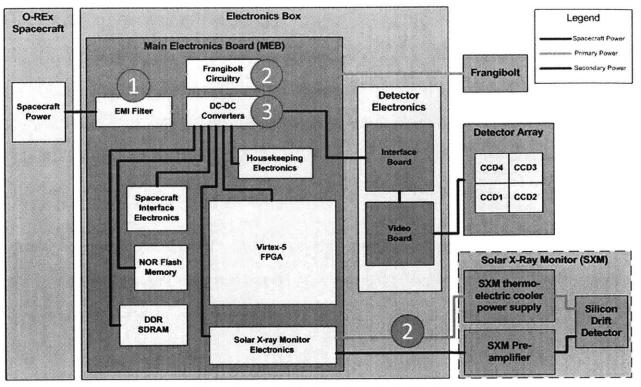

|      | Figure 3-7: REXIS MEB Power Distribution.                                                | 72    |

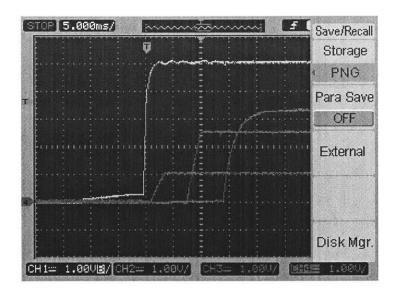

|      | Figure 3-8: REXIS Power Rail Ramp-up during System Power-up                              | 73    |

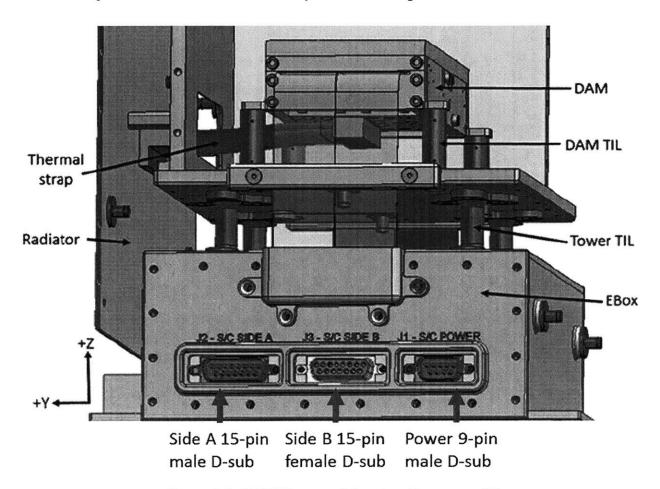

|      | Figure 3-9: REXIS/Spacecraft Interface Connectors [3]                                    | 76    |

|      | Figure 3-10: REXIS/Spacecraft Interface Connector Schematics for Commands and Telemetry  | 77    |

|      | Figure 3-11: REXIS FSW Main Loop                                                         | 80    |

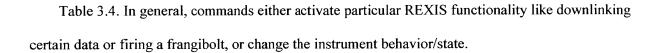

|      | Figure 3-12: Frangibolt Actuation State Diagram                                          | 88    |

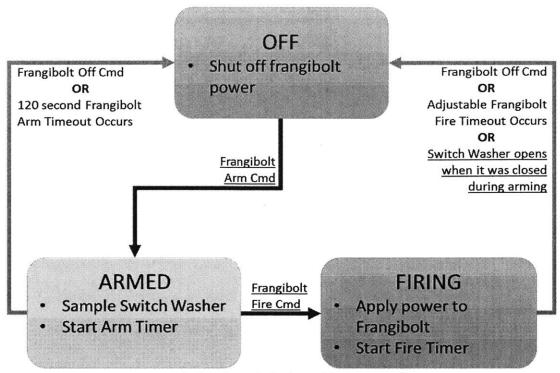

|      | Figure 3-13: Image Processing Block Diagram                                              | 91    |

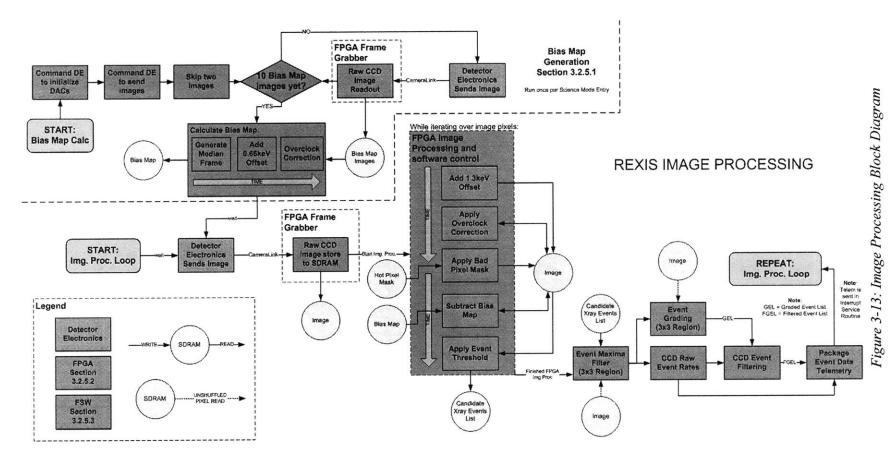

|      | Figure 3-14: X-ray Event Grades [11]                                                     | 95    |

|      | Figure 3-15: Housekeeping Data Flow                                                      | 98    |

|      | Figure 3-16: REXIS Telemetry Protocol and Packet Structure                               | . 100 |

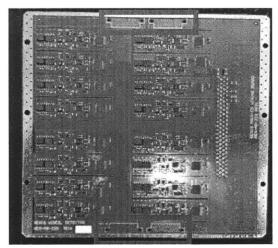

|      | Figure 3-17: Main REXIS PCBs                                                             | . 104 |

|      | Figure 3-18: FPGA cores that are implemented on the MEB FPGA                             | . 107 |

|      | Figure 3-19: Frangibolt Actuator and Switch Washer Sensor [3]                            | . 111 |

|      | Figure 3-20: Opto-coupler Based Circuitry to enable the Frangibolt DC/DC Converter       | . 112 |

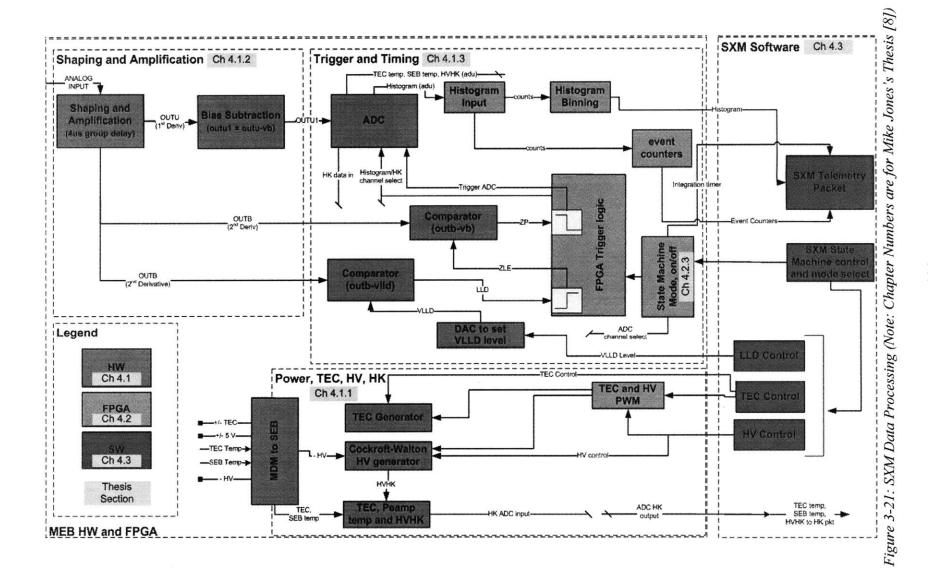

|      | Figure 3-21: SXM Data Processing (Note: Chapter Numbers are for Mike Jones's Thesis [8]) | . 114 |

|      | Figure 3-22: REXIS Video Board [28]                                                      | . 118 |

|      | Figure 4-1: Aluminum dose-depth curve for the OSIRIS REx Mission. The dashed line is the |       |

| inst | rument dose after 1,721 Days                                                             | . 121 |

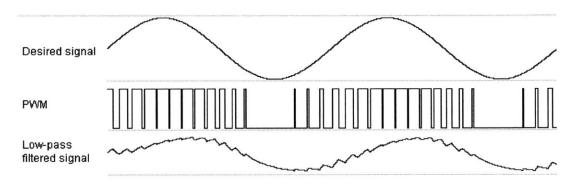

|      | Figure 4-2: Analog Voltage Generation with PWM                                           | . 139 |

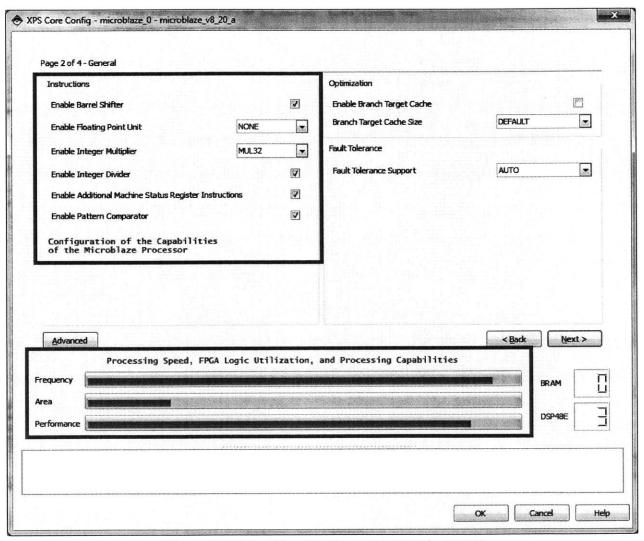

|      | Figure 5-1: Microblaze Configuration GUI for REXIS                                       | 149   |

## List of Tables

| Table 1.1: Scientific Payload Instruments aboard OSIRIS-REx [9]  | 21  |

|------------------------------------------------------------------|-----|

| Table 2.1: Radiation Hazard and Mitigation Technique Summary     | 59  |

| Table 3.1: REXIS Electrical Power Draw from OSIRIS-REx           | 71  |

| Table 3.2: Overview of the Secondary Power Voltage Rails         | 75  |

| Table 3.3: FSW Interrupt Service Routines                        | 82  |

| Table 3.4: REXIS Commands, Actions, and State Changes            | 86  |

| Table 3.5: Uploadable Functions within REXIS FSW                 | 101 |

| Table 4.1: Summary of REXIS Radiation Tolerance Features         | 120 |

| Table 4.2: REXIS Maximum TID                                     | 122 |

| Table 4.3: Rad-hard Parts aboard REXIS                           | 127 |

| Table 4.4: Summary of REXIS Avionics Radiation Hazard Mitigation | 144 |

| Table 5.1: Redesign Recommendations for ISRs                     | 156 |

#### Acronym List

ADC - Analog to Digital Converter

C&DH - Command and Data Handling

CCD - Charge Coupled Device

CDR - Critical Design Review

CMOS – Complementary Metal Oxide Semiconductor

Co-ax – Coaxial Cable

COTS - Commercial Off The Shelf

CXEL - Candidate X-ray Events List

DAC – Digital to Analog Converter

DAM – Detector Assembly Mount

DC - Direct Current

DE - Detector Electronics

DSN - Deep Space Network

E-box - Electronics Box

ECC – Error Correcting Codes

EDAC - Error Detection and Correction

EM – Engineering Model

EMC - Electromagnetic Compatibility

EMI - Electromagnetic Interference

ET - Event Threshold

FM - Flight Model

FOV - Field of View

FPGA - Field Programmable Gate Array

FSW - Flight Software

GaAs - Gallium Arsenide

GCR - Galactic Cosmic Ray

GNC - Guidance Navigation and Control

GPIO - General Purpose Input/Output

GSFC - Goddard Space Flight Center

GUI - Graphical User Interface

HDL - Hardware Description Language

JTAG - Joint Test Action Group

LDO - Low Dropout

LEO - Low Earth Orbit

LET - Linear Energy Transfer

MEB - Main Electronics Board

MicroMAS - Micro-sized Microwave Atmospheric Satellite

MIT – Massachusetts Institute of Technology

MPMC – Multi Port Memory Controller

MRO - Mars Reconnaissance Orbiter

NICER- Neutron star Interior Composition Explorer

NOR Flash - Not OR Flash

Op Amp – Operational Amplifier

PCB - Printed Circuit Board

PDR - Preliminary Design Review

PRT – Platinum Resistance Thermometer

Rad - Radiation Absorbed Dose

Rad Cover - Radiation Cover

Rad-hard - Radiation Hardened

RC – Resistor-Capacitor

REXIS - REgolith Imaging X-Ray Spectrometer

OSIRIS-REx - Origins, Spectral Interpretation, Resource Identification, Security Regolith Explorer

PWM – Pulse Width Modulation

TAGSAM – Touch and Go Sample Acquisition Mechanism

TESS - Transiting Exoplanet Survey Satellite

TID - Total Ionizing Dose

TNID - Total Non-Ionizing Dose

TVac - Thermal Vacuum

SBB - SXM Backpack Board

SDD - Silicon Drift Detector

SDRAM - Synchronous Dynamic Random Access Memory

SEB - SXM Electronics Board

SEL - Single Event Latch-up

SET – Single Event Transient

SEU - Single Event Upset

Si - Silicon

SPE - Solar Particle Event

SPI - Serial Peripheral Interface

SRAM - Static Random Access Memory

SRC – Sample Return Capsule

SSL - Space Systems Laboratory

ST - Split Threshold

STL – Spacecraft Test Laboratory

SXM – Solar X-ray Monitor

TID – Total Ionizing Dose

TIL - Thermal Isolation Layer

TVAC - Thermal Vacuum

ULD – Upper Limit Discriminator

VDC - Volts, Direct Current

XRF - X-Ray Fluorescence

## Chapter 1 - Introduction

The REgolith X-ray Imaging Spectrometer (REXIS) is one of the remote sensing instruments aboard the spacecraft of the NASA Origins, Spectral Interpretation, Resource Identification, Security, Regolith Explorer (OSIRIS-REx) mission. The OSIRIS-REx mission is designed to allow scientists to remotely study the asteroid Bennu, and return a sample from the asteroid's topsoil, or regolith, to laboratories on Earth. The goal of REXIS is to remotely acquire scientific data in the form of elemental composition of Bennu's regolith for the OSIRIS-REx mission.

REXIS is a high-risk and low-cost component of the OSIRIS-REx system. The most important requirements of the REXIS project are educating student engineers through practical spaceflight development experience and not damaging the OSIRIS-REx spacecraft. The low-cost nature of REXIS has caused the development and testing of the REXIS avionics system to be more time and budget constrained than a typical spaceflight project. These time/budget constraints and the REXIS's two high-level requirements take priority over the secondary requirement of acquiring scientific data from Bennu, thus allowing for higher risks to be taken with this data acquisition. Overall, this outlook can be summarized by the fact that REXIS-spacecraft interface is class-B (low-risk) but has other subsystems which are class-D (high-risk), like the science data collection, that are outside of the spacecraft-interface. Class B and Class D are further explained in section 1.1.

The REXIS avionics is the combination of electrical and software subsystems that enable the REXIS instrument to process commands, operate instrument subsystems, and generate both scientific and engineering telemetry. The high-risk and radiation-tolerant nature of the REXIS avionics system is presented as guide and example for the design and testing of similar resource-constrained high-risk space systems. This thesis presents the design of the electrical and software systems of the REXIS instrument, how these systems operate in spite of the space radiation hazard, and the development and testing of these

systems. Rationale behind design decisions and lessons learned from the REXIS avionics system are also detailed in order to guide future space system development.

The remainder of this chapter begins with the background and motivation for this thesis. Afterward, an overview of the OSIRIS-REx system and its scientific goals is presented. Next the REXIS instrument is presented as a scientific payload that contributes to the scientific return of the OSIRIS-REx mission. Finally, a thesis roadmap that details the layout and content of this entire document is presented.

#### 1.1 Background and Motivation

Humanity has realized many practical benefits through operating spacecraft both within and beyond Earth's orbit. Without these spacecraft, modern society's reliance on state-of-the-art space exploration, remote sensing, surface imaging, global tracking/positioning, and communications technology would be impossible. To continue realizing the benefits of these space-based technologies, there must be ongoing progress in the research, development and testing of new spacecraft.

A new spacecraft system requires the development, integration, and testing of the electronic subsystems. These electronics that are designed to operate in outer space are known as avionics, and they are provide electrical power, process commands from Earth, generate and send telemetry to Earth, and control the spacecraft and its mechanisms. Avionics have certain specially designed features that allow them to operate reliably without complications in outer space for long durations. When compared to the electronics on Earth, avionics require extra development and testing resources.

Spacecraft in general, and avionics in particular, are very expensive to develop in terms of time and money. Compared to operating conditions on Earth, avionics in space must endure an extreme temperature range, harsh vibrations from a rocket launch, constant radiation bombardment, and a hard vacuum. To operate in these extreme conditions, avionics require expensive components, and implementation of costly design, testing and optimization that increase the overall cost and development time. Testing an avionics design to determine if it works in these environments requires expensive array of equipment like thermal-vacuum chambers, vibration tables, radiation chambers, and particle

accelerators. Finally, because spacecraft typically cannot be repaired in space, there is a push to have these spacecraft operate for as many years as possible without servicing. Spacecraft longevity is accomplished through spending more resources to increase spacecraft reliability and fault tolerance. These factors combine together to make both spacecraft and their avionics extremely expensive to design, build, integrate, and test.

In recent years, there is a push for developing low-cost spacecraft and avionics. Entities with smaller budgets like small companies, universities, and technology demonstration projects are enabled by lower rocket-launch costs, new research and development goals, and state-of-the-art technology to develop spacecraft. The projects of these entities are typically allocated smaller budgets than the usual spacecraft programs from large companies and governments. An example of such spacecraft are CubeSats which are miniature satellites designed to utilize surplus payload capability aboard rockets. These spacecraft have limited capability and their stakeholders are more failure tolerant than traditional large-budget space systems.

Another low-cost and experimental project is the REXIS instrument. REXIS is classified as a Class D mission by NASA in contrast to the Class B designation of the whole OSIRIS-REx mission. Class D missions "have a lifecycle cost of less than \$250 million. They generally are less complex, have a streamlined reliability approach, and may have a shorter design life" [1]. Class B missions are the traditional high-cost space missions since they are "high priority" in terms of advancing NASA's scientific mission, have "high complexity", and have "high national significance" [2]. On the other hand, REXIS's Class D nature means that REXIS mission success provides valuable science data to enhance the OSIRIS-REx mission, but a failure of REXIS to provide this scientific data does not put the OSIRIS-REx's mission success, or NASA's overall space science mission, in jeopardy. Because of this directive, REXIS can take higher risks in the development and testing of its avionics system.

There is a lack of published literature and guidance for the successful development, testing and operation of such high-risk spaceflight missions [3]. There is no guide to designing, building, integrating, and operating a Class D subsystem that properly interfaces with a Class B system. For example, the

REXIS development team had very few guidelines or standards to follow when designing a robust avionics system that would not damage the OSIRIS-REx spacecraft and its asteroid sample recovery program, but operate within the allocated time and budget.

The design, development, and testing of the REXIS avionics system is presented as an example of low-cost high-risk design that interfaces with a high-cost low-risk spacecraft system. Successes and failures that occurred during the REXIS avionics project are presented and can be used as a learning guide for future missions.

#### 1.2 OSIRIS-REx Spacecraft Overview

The OSIRIS-REx is NASA's asteroid sample return mission. OSIRIS-REx's main component is a spacecraft that is scheduled to launch in September 2016 and will return a pristine sample from the asteroid Bennu's surface in 2023 [4] [5]. The OSIRIS-REx spacecraft is designed to launch from Earth, cruise to Bennu, remotely study this asteroid, acquire an asteroid regolith sample, and deliver this sample to Earth.

The OSIRIS-REx mission motto of "Exploring Our Past, Securing Our Future Through Pioneering Asteroid Science" summarizes the objective and purpose of the OSIRIS-REx scientific mission [6]. The acronym OSIRIS-REx is derived from the mission's scientific objectives and is further explained below:

- Origins Bennu is a carbonaceous asteroid that is believed to contain material left over from the formation of the solar system [4]. The asteroid topsoil, known as regolith, that OSIRIS-REx is designed to sample and return will allow scientists to understand the organic chemistry and geochemistry of Bennu, and consequently the early solar system as a whole [4].

- Spectral Interpretation The OSIRIS-REx spacecraft carries a suite of spectrometers that generate spectra of the photons emitted from Bennu. These spectra span a variety of wavelengths ranging from infrared, visible light, and x-ray, and they are used to determine the physical, mineralogical, chemical, and elemental composition of Bennu.

- Resource Identification The spectral information will also be acquired for specific areas on Bennu's surface. The preliminary data will be used to understand the geology and composition of Bennu, and ultimately help in finding the sampling site on Bennu's surface.

- Security Bennu is an asteroid 500 meters in diameter and has a 0.037% chance of impacting the Earth between the years of 2175 to 2196 [7]. OSIRIS-REx is designed to provide data for understanding the momentum change caused by the absorption and emitting of the sun's thermal energy on Bennu. Precise understanding of this orbital disturbance, known as the Yarkovsky Effect, further refines the current estimate of a 0.037% chance that Bennu and Earth will collide [8].

- Regolith Explorer OSIRIS-REx's remote sensing instruments and sample return mission will

currently focus on the topsoil, or regolith of Bennu.

The OSIRIS-REx spacecraft consists of the following subsystems to meet the previously described scientific objectives:

- A spacecraft bus that meets the structural, navigational, optical, thermal, electrical, and communications requirements imposed by the mission's remote-sensing instruments and sampleacquisition hardware

- A mechanism to acquire and deliver an asteroid regolith sample to Earth

- Remote Sensing instruments to fully characterize the asteroid Bennu in relation to other asteroids

The following sections provide an overview of each of these OSIRIS-REx spacecraft subsystems.

#### 1.2.1 OSIRIS-REx Spacecraft Bus

The spacecraft bus is both physically and functionally in the center of the OSIRIS-REx system. This central subsystem interacts with all the subsystems of the OSIRIS-REx system. The spacecraft bus consists of a chassis derived from the Mars Reconnaissance Orbiter (MRO) spacecraft that has mounting points for all the other spacecraft components. All spacecraft functionality such as power, propulsion,

avionics, communication, navigation, and scientific data acquisition are implemented with components that are mounted on the spacecraft bus. An Atlas-5 rocket is the launch vehicle for OSIRIS-REx since it places the spacecraft on an interplanetary trajectory to the asteroid Bennu [4].

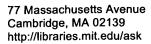

Figure 1-1: Pictures of the OSIRIS-REx Spacecraft1

The left side of Figure 1-1 shows technicians building the spacecraft chassis and gives an idea of spacecraft size. The black cylinder in the middle of this left image is a structural member that contains the main OSIRIS-REx propellant tank. Four gussets protrude radially from this structural cylinder and serve as the mounting surface for many spacecraft subassemblies. The four gussets and structural cylinder are capped with decks on both ends which provide mounting for remote sensing instruments, the sample return capsule (SRC), and main propulsion system. The left side of Figure 1-1 is the same spacecraft chassis with the addition of the mounted circular high-gain antenna and rectangular solar panels.

#### 1.2.2 Regolith Sample Acquisition and Delivery

The spacecraft bus provides the mounting for two key assemblies required for sample return from Bennu. These assemblies are the Touch and Go Sample Acquisition Mechanism (TAGSAM) and the Sample Return Capsule (SRC). TAGSAM is a robotic arm that allows OSIRIS-REx to acquire the asteroid sample, and SRC is a container that contains and protects the asteroid sample during its journey through Earth's atmosphere. Through commands from the ground, the spacecraft extends the TAGSAM

<sup>&</sup>lt;sup>1</sup> Taken from the blog of OSIRIS-REx Principle Investigator Dante Lauretta on 6/26/2016. URL: <a href="https://dslauretta.com/2015/11/13/osiris-rex-progressing-through-environmental-testing/">https://dslauretta.com/2015/11/13/osiris-rex-progressing-through-environmental-testing/</a>

arm and positions it near the asteroid. A puff of pure nitrogen gas is used to push Bennu's regolith dust into the TAGSAM head.

After the asteroid regolith sample is acquired, it needs to be measured and returned to Earth.

Immediately after sample acquisition, the spacecraft is commanded to do the following to verify the sample has been properly acquired [4]:

- 1. Take images of the sample-site on Bennu with remote sensing instruments

- 2. Determine the sample mass by measuring the change in the spacecraft's moment of inertia. By using small rocket thrusters to spin the spacecraft, and measuring the spin-rate with the spacecraft's Guidance Navigation and Control (GNC) sensors, the change in the spacecraft's moment of inertia due to the asteroid sample can be determined for estimating sample mass.

Once these steps are completed, the asteroid sample is ready to be stored.

After sample acquisition, The TAGSAM robotic arm is actuated to store the asteroid sample in an open SRC. Afterward, the SRC closes and is ready for its journey through Earth's atmosphere. OSIRIS-REx then leaves Bennu and takes a 2 year journey to Earth. Once this journey is complete, the spacecraft is commanded to release the SRC into Earth's atmosphere [5].

#### 1.2.3 OSIRIS-REx Payload Instruments

Prior to acquiring a sample of Bennu's regolith, an appropriate sampling site must be chosen. A sampling site is selected by analyzing data from the remote sensing instruments aboard OSIRIS-REx. These instruments are used to understand Bennu's physical, elemental, visual, and infrared composition. This holistic understanding of Bennu's surface provided by remote sensing instruments is essential for picking a sample site that is scientifically interesting and not hazardous for operating the TAGSAM mechanism.

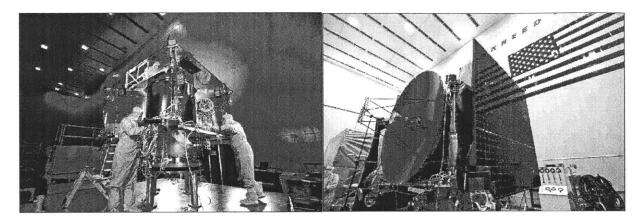

Figure 1-2: OSIRIS-REx Remote Sensing Instruments<sup>2</sup>

OSIRIS-REx has an instrument deck (Figure 1-2) which has a variety of scientific payload instruments and the SRC mounted to it. In order to collect scientific data, the spacecraft orients itself so that the instrument deck faces the asteroid. This maneuver is important because it allows all the scientific payload instruments to simultaneously collect data from the asteroid.

The scientific payload aboard OSIRIS-REx are the following remote sensing instruments (Table 1.1) used to determine the shape and composition of Bennu in terms of particles sizes, chemicals, minerals, and elements. The OSIRIS-REx Camera Suite (OCAMS) consists of three cameras that use the same imaging sensor to sense visible light at various ranges. PolyCam serves as both a telescope and microscope designed to acquire Bennu from long ranges and provide high resolution images of Bennu's regolith. MapCam is designed to image the entire surface of Bennu. SamCam is designed to take close-up images of the sample site and the TAGSAM mechanism. Next to OCAMS is the OSIRIS-REx Visible

<sup>&</sup>lt;sup>2</sup> Taken from the blog of OSIRIS-REx Principle Investigator Dante Lauretta on 6/26/2016. URL: <a href="https://dslauretta.com/2014/06/04/spacecraft-structure-the-bones-of-osiris-rex/">https://dslauretta.com/2014/06/04/spacecraft-structure-the-bones-of-osiris-rex/</a>

and Infrared Spectrometer (OVIRS), which is sensitive to light wavelengths of 0.4-4.3 micrometers and used to determine local and global concentrations of organic volatile compounds on Bennu's surface. Longer infrared wavelengths from 4-50 micrometers are sensed by the OSIRIS-REx Thermal Imaging Spectrometer (OTES) that provides thermal data about Bennu's surface. The instrument deck also hosts the OSIRIS-REx Laser Altimeter (OLA) that provides data used to create topographical maps of Bennu. The final instrument is the Regolith X-ray Imaging Spectrometer (REXIS) is designed to sense x-rays within the energy range of 0.5-7 keV emitted by Bennu. The x-ray spectra derived from REXIS data is used to determine the global and local elemental makeup of Bennu's regolith. The information produced by all of these instruments is used to determine the sample selection site [9].

Table 1.1: Scientific Payload Instruments aboard OSIRIS-REx [9]

| Instrument Name            | Abbreviation | Purpose                                                   |

|----------------------------|--------------|-----------------------------------------------------------|

| OSIRIS-REx Camera          | OCAMS        | Detect the asteroid visually, photograph the asteroid,    |

| Suite                      |              | detect satellites/outgassing around the asteroid, and     |

|                            |              | observe the asteroid sampling process                     |

| OSIRIS-REx Laser           | OLA          | Create a topographical map of the asteroid                |

| Altimeter                  |              |                                                           |

| OSIRIS-REx Visible and     | OVIRS        | Create visible/IR spectra for areas on the asteroid to    |

| Infrared (IR) Spectrometer |              | determine chemical composition of these areas             |

| OSIRIS-REx Thermal         | OTES         | Create a thermal IR spectrum for areas on the asteroid to |

| Emission Spectrometer      |              | determine mineral composition and particle size within    |

|                            |              | these areas                                               |

| Regolith X-ray Imaging     | REXIS        | Create an x-ray spectrum for areas on the asteroid to     |

| Spectrometer               |              | determine elemental composition of these areas            |

#### 1.3 REXIS Instrument Overview

The Regolith Imaging X-ray Spectrometer (REXIS) is a remote sensing payload instrument that flies aboard OSIRIS-REx and is used to determine the elemental composition of Bennu's regolith. Knowledge of the composition of Bennu's regolith aids in classifying Bennu amongst the different types of asteroids and determining an appropriate site for sampling Bennu's regolith. REXIS determines the composition of Bennu's regolith by sensing the x-rays emitted by Bennu's surface.

#### 1.3.1 REXIS Science Process and Data

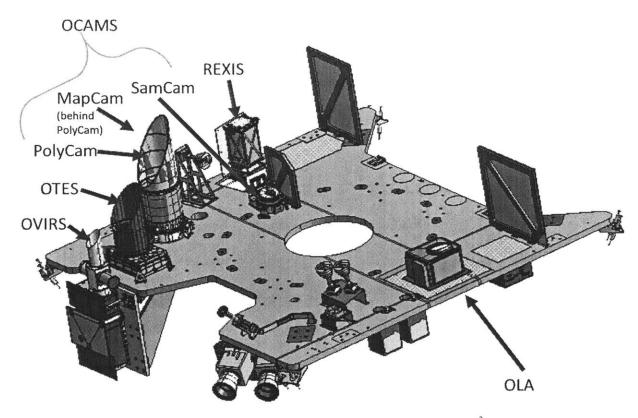

The REXIS instrument is designed to sense x-ray fluorescence (XRF) from Bennu's regolith. A schematic of this process is shown in Figure 1-3 where the Sun emits x-ray energy that excites the regolith of Bennu. The excitation caused by solar x-ray energy causes the regolith to emit its own x-rays – this is the XRF process. The energy of these x-rays depend on the regolith's elemental composition.

REXIS uses Charged Coupled Device (CCD) sensors to sense these x-rays originating from Bennu. Using data from the CCDs, the REXIS instrument produces scientific telemetry from Bennu that consists of x-ray energy, the position where x-rays intersect REXIS's sensor, and how the x-rays energize clusters of pixels within this sensor. In order to properly interpret x-ray energies and correctly derive elemental abundances in Bennu's regolith from the XRF, the solar x-ray spectrum at Bennu must be acquired at the same time as the XRF reading. REXIS has an auxiliary detector known as the Solar X-ray Monitor (SXM) that detects the solar x-rays while the CCD sensors are operating as shown in Figure 1-3 [10]. While the main CCD x-ray sensors provide data for x-ray spectra that correspond to local elemental abundances on Bennu, the SXM only provides the x-ray spectrum of the Sun as a whole.

Figure 1-3: REXIS X-ray Data Acquisition (Credit: Branden Allen and Niraj Inamdar)

REXIS uses a coded aperture x-ray imaging process to sense where on Bennu's surface an x-ray originated from. This process consists of encoding x-ray light from the asteroid with a coded aperture mask. A coded aperture mask is a metal sheet coded with a pattern that is opaque to x-rays at random points as shown in Figure 1-4 below. This pattern is randomly generated during REXIS design and used by scientists to transform REXIS scientific x-ray telemetry into elemental abundance maps of Bennu.

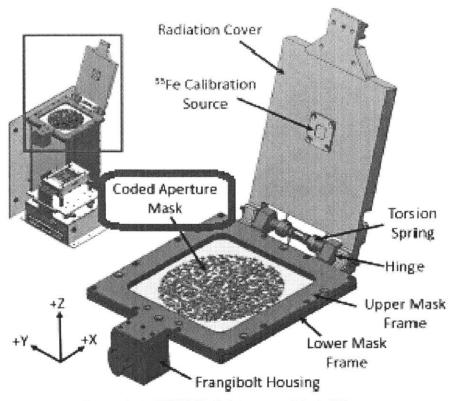

Figure 1-4: REXIS Coded Aperture Mask [3]

Consider a point source of x-ray light on Bennu's surface within the REXIS spectrometer's field of view. The x-ray light from this point source will create a particular shadow of Figure 1-4's coded aperture mask on the CCD detectors. This particular shadow depends on the position of the point source in the REXIS spectrometer's field of view. The pattern of photons that are not blocked by the coded aperture mask are sensed by the REXIS CCDs. The 2-dimensional image of these unblocked x-ray photons forms x-ray image telemetry that is transmitted to Earth. Scientists on Earth can perform a two-dimensional mathematical de-convolution of the coded mask pattern and CCD-derived x-ray image to recover the position of the x-ray point-source. Since all of the x-ray light from the asteroid can be broken down into a superposition of x-ray point-sources, this convolution technique can used to recreate an x-ray image of the asteroid [11].

#### **REXIS Science Data Stream** Data Product #1 Data Product #2 Data Product #3 Spectral Mode Collimator Mode **Imaging Mode** Globally averaged elemental Fine angular resolution Coarse angular resolution abundances of Bennu and its <50m scales of possible ~100m scales of possible analog meteorite classification. elemental abundance elemental abundance concentrations. concentrations. Increasing Spatial Resolution

Figure 1-5: REXIS Scientific Data Products [10]

Three different scientific products are produced from REXIS telemetry that indicate the composition of Bennu's regolith with varying spatial resolutions of Bennu's surface, as shown in Figure 1-5. As the spatial resolution of REXIS scientific products increases, the resolution of elemental concentrations decreases. This resolution decrease occurs because there are fewer photons for smaller areas of Bennu to make detailed spectral histograms. The Spectral Mode data in Figure 1-5 is generated by creating an x-ray energy histogram that includes all of the photons emitted by Bennu's regolith. This large quantity of photons from all of Bennu ensures a high resolution of elemental concentration values for the entire asteroid surface. Collimator mode data is produced by taking REXIS's 200 meter wide field of view (FOV) on the asteroid's surface into account. Photons from the same 200-m wide FOV footprints on Bennu are grouped into an image of Bennu's elemental abundances with a 200-m spatial resolution. However, collimator mode images have less elemental abundance resolution when compared to Spectral Mode data. Similarly, Imaging Mode uses coded aperture imaging to resolve areas within the 200 meter FOV footprints and determines elemental concentrations at finer spatial resolutions. High resolution elemental abundance data in Spectral Mode is used to classify Bennu among other asteroids in the Solar

System while high resolution spatial data from imaging mode may be used to help select a regolith sample site. Furthermore, high accuracy instruments on Earth will determine the elemental composition of the asteroid sample. This composition data will be compared to REXIS Imaging Mode science data to determine the effectiveness of XRF and coded aperture imaging at an asteroid [10].

#### 1.3.2 REXIS System Description

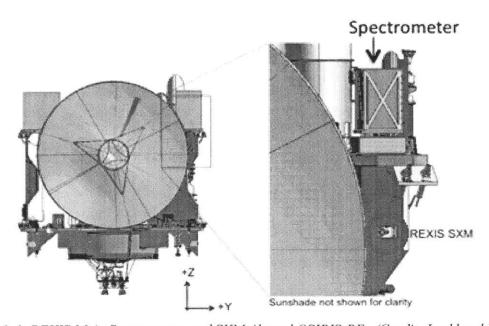

REXIS senses x-rays emitted by Bennu and the Sun with two separate mechanical assemblies known as the main spectrometer and the SXM. Figure 1-6 shows the placement of these REXIS components aboard the OSIRIS-REx spacecraft. The main spectrometer is aimed towards Bennu along with the other remote sensing instruments mounted on the instrument deck. The SXM is mounted so that it monitors the Sun whereas the main REXIS spectrometer monitors Bennu. These two assemblies are connected with wiring harnesses. The REXIS instrument uses another set of wiring harnesses to interface with the OSIRIS-REx spacecraft. These harnesses provide electrical power and conductors used for digital communication. This digital communication consists of sending commands to and receiving telemetry from the REXIS instrument.

Figure 1-6: REXIS Main Spectrometer and SXM Aboard OSIRIS-REx (Credit: Lockheed Martin)

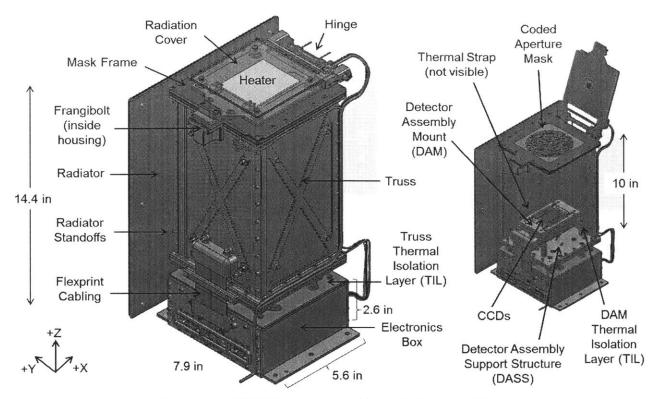

Figure 1-7: REXIS Spectrometer Physical Overview [3]

Figure 1-7 details the physical components that form the REXIS main spectrometer assembly. At the center of the instrument (seen within the cutaway model on the left of Figure 1-7) are the four Charge Coupled Device (CCD) sensors arranged in a 2x2 array. These CCDs are CCID-41 sensors that are an array of x-ray sensitive pixels. These pixels convert the energy of an x-ray photon into electrical current. The CCDs are sensitive to the soft x-ray range of 0.3 keV - 7.5 keV [12]. The REXIS system supports the CCDs with the following subsystems in order to produce quality scientific data:

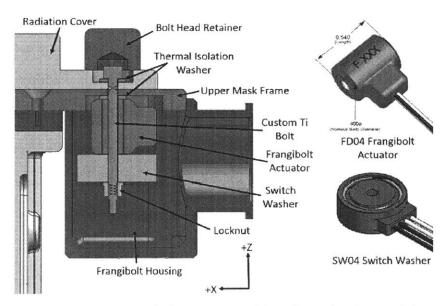

1. Radiation Cover and Shielding – Because the CCDs degrade with exposure to radiation, the aluminum mass of the REXIS truss and radiation cover are designed to reduce the total radiation dose the CCDs receive while flying through space. Once REXIS is arrives to image the asteroid Bennu, the radiation cover opens through the actuation of a TiNi Aerospace FD04 Frangibolt mechanism. When electrical current is applied to the Frangibolt by the avionics system, it is designed to fracture a bolt that holds the radiation cover closed. Once the bolt is fractured, torsion springs open the radiation cover and permanently hold it open [3].

- 2. Thermal Isolation and Passive Cooling The CCDs are mounted in a Detector Assembly Module (DAM) that is thermally isolated and radiatively cooled to reduce temperature-dependent noise in the CCD output signal. This thermal management system consists of two thermal isolation layers that prevent the avionics heat energy from flowing to the DAM and a passively operating radiator that dissipates the CCD sensor's heat energy into outer space through radiative heat transfer [13] [14].

- 3. Coded Aperture Mask The coded aperture mask is shown in Figure 1-4 and consists of a stainless steel sheet with a circular pattern of randomly placed holes. In total, these create a 50% open-fraction and there is a 0.15mm wide support grid that runs between each hole and opaque portion of the mask [10].

- 4. Electrical CCD Drive and Readout Electronics within the electronics box power the CCDs and read data from them. The REXIS electronics transmits CCD drive voltages and receive CCD pixel data through flexible printed circuit boards known as flexprints. This CCD-derived data is used to create the REXIS science telemetry.

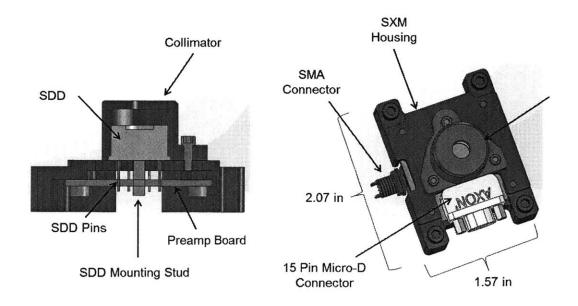

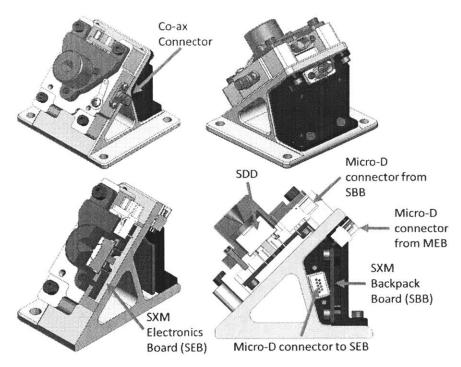

Figure 1-8: REXIS SXM Physical Overview [8]

The other component of the REXIS is the SXM. Similar to how the main spectrometer is built around the CCD sensors, the SXM is built around the Silicon Drift Detector (SDD) x-ray sensor as shown in Figure 1-8. The electronics that operate the SDD sensor are split between the main spectrometer's electronics-box and SXM assembly (Figure 1-8). The spectrometer electronics provide a high voltage bias voltage for the SDD, power for the SDD's preamplifier, and power for the SDD's built-in thermo-electric cooler (TEC). Unlike the CCD's passive cooling system, the TEC uses electrical power to keep the SDD at its operating temperature. The SDD converts x-rays that travel through the collimator (used to restrict the SDD's FOV) into electrical pulses. These pulses are amplified by the SXM's preamplifier circuit on an SXM Electronics Board (SEB), sent over a coaxial cable wiring harness, and counted/measured by the electronics within the REXIS electronics box. A coaxial cable is used to transmit the analog SDD pulses amplified by the SEB for its superior noise-rejection compared to normal wiring. The other electrical signals required to operate the SXM such as the high voltage bias, power, and ground, are provided through a separate wiring harness between the SXM and the main spectrometer.

#### 1.4 Thesis Roadmap

This chapter presents the background and motivation behind this thesis, an overview of the OSIRIS-REx system, and an overview of the REXIS system within OSIRIS-REx. The REXIS system has been introduced within the context of the larger OSIRIS-REx project and the need to share the experience and lessons learned from high-risk low-cost avionics design. The rest of this thesis will delve deeper into these ideas with the following chapters.

Chapter 2 introduces the space radiation hazard and how it affects avionics in general. Emphasis

is given to the adverse effects of space radiation and how avionics are typically designed to avoid

or mitigate these effects.

- Chapter 3 details the REXIS avionics system that is the main subject of this thesis. The functionality, hardware, software, and FPGA<sup>3</sup> design are explained in this chapter.

- Chapter 4 describes how the REXIS avionics system is designed to function as it is bombarded

with space radiation. REXIS's cost-saving designs for mitigating the radiation hazard are

highlighted.

- Chapter 5 concludes this thesis with lessons learned from designing, testing, and operating the

REXIS avionics system. These lessons can also be generalized to other avionics systems.

In short, this thesis presents the design, development, and testing of the REXIS avionics system.

Successes and failures that occurred during the REXIS avionics project are presented and can be used as a learning guide for future missions.

<sup>&</sup>lt;sup>3</sup> Field Programmable Gate Array – A microchip that contains an array of digital logic and computation hardware. This hardware and its interconnections can be reconfigured to implement digital computing functionality

## Chapter 2 - Interaction of Space

### Radiation and Electronics

The OSIRIS-REx mission imposes a 3-year operational lifetime on the REXIS instrument in the interplanetary space radiation environment because of the spacecraft's 2.5 year cruise to Bennu. Without proper precautions, radiation has a damaging and degrading effect on system performance. This chapter discusses the effects of space radiation on the operation of avionics. First, the space radiation environment is presented and compared to radiation sources found on Earth. Then, transient and permanent radiation-caused avionics malfunctions are discussed. Finally, techniques to mitigate this damage and prevent system malfunction are presented.

#### 2.1 Space Radiation Environment

Space radiation consists of highly energized subatomic particles and atomic nuclei. Radiation in outer space originates from a variety of sources ranging from normal stars to exploding supernovae. Radiation particles can also accumulate in planetary magnetic fields and become hazards for avionics operating within these areas. For Earth, such areas where radiation is trapped by the Earth's magnetic field are known as the Van Allen belts [15].

Figure 2-1: Origins of Space Radiation (Credit: NASA Space Environments and Effects Office<sup>4</sup>)

Radiation damages electronics by putting too much energy and charge into sensitive places within the electronics' physical micro-architecture. Space electronics designers must account for radiation coming from three different hazards shown in Figure 2-1. Two of these hazards that create space radiation are Solar Particle Events (SPEs) from our Sun, and Galactic Cosmic Rays (GCRs) from extra-solar sources such as supernova [16]. The third radiation hazard for spacecraft are planetary magnetic fields which trap and accumulate energetic charged subatomic particles originating from the previous two sources around planetary bodies. The radiation dose caused by these particles is measured in the unit of rad which is defined as one erg (10<sup>-7</sup> Joules) of energy absorbed by one gram of material. One rad may appear as a small amount of energy, but when such energy continuously accumulates within microchip circuits measured in atom-widths during the many years of a spaceflight mission, it can negatively affect operation and functionality.

Spaceflight missions usually have low radiation dose rates and high accumulated radiation doses compared to conditions found in Earth's laboratories. While Earth orbits outside the Van Allen belts can be characterized with low dose rates ranging from 10<sup>-4</sup> to 10<sup>-2</sup> rad/second, years of operation in these orbits can result in a high accumulated dose in the order of 10<sup>5</sup> rad [17]. The space radiation environment

<sup>&</sup>lt;sup>4</sup> Taken from URL: http://holbert.faculty.asu.edu/eee560/tiondose.html

is difficult to replicate on Earth due to constraints from time and available equipment. More specifically, it is impractical to test a newly developed spaceflight components at all possible orientations continuously for years on end.

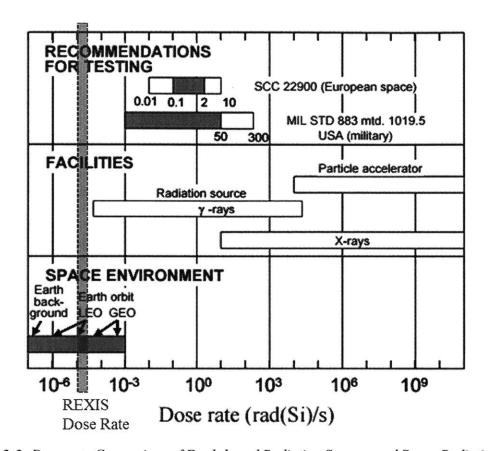

Figure 2-2: Dose-rate Comparison of Earth-based Radiation Sources and Space Radiation [18]

The difference in dose rates on Earth and space is shown in Figure 2-2 where the bottom third of the figure shows the low dose rate in space and the middle third shows the dose rates that are practically available through various testing facilities such as X-ray sources, gamma-ray sources, and particle accelerators. These facilities create dose rates notably higher than the space dose rates but have the benefit of allowing radiation testing to be completed in a reasonable timeframe of hours/days instead of years for a given component at a particular dose. However, high dose-rates are not representative of space so typically parts are over-designed and over-tested to ensure they continue to work reliably in the space environment [17].

Furthermore, radiation in space bombards components from all directions. This effect is usually simulated by rotating parts within radiation sources. Each new orientation requires a new part and this quickly adds time and cost to testing. New parts are needed for testing each orientation since allowing radiation dose to accumulate within a single continuously rotated part simultaneously tests the independent variables of dosage accumulation and sensitive to radiation angle-of-incidence. Thus, component degradation observed from testing cannot be conclusively attributed to dosage accumulation or radiation angle-of-incidence.

The time-wise and location-wise variation of the space radiation environment requires that a system or component be designed, optimized, and vetted to operate in specific conditions. Location-wise, the three radiation hazards have different energy distributions, fluxes, and are dominant in different areas of outer space. Time-wise, the 11-year period of the solar activity cycle causes the GCR flux and SPE flux to vary inversely. An example of the location-oriented radiation dose variation is within the various Earth orbits that intersect the trapped radiation regions of Earth's magnetic fields at varying levels. Lower energy radiation hazards such as SPEs and trapped ions are simulated with radioactive x-ray or gammaray sources while the testing high energy hazards like GCRs requires the use of particle accelerators. The following paragraphs describe these three sources of space radiation in detail.

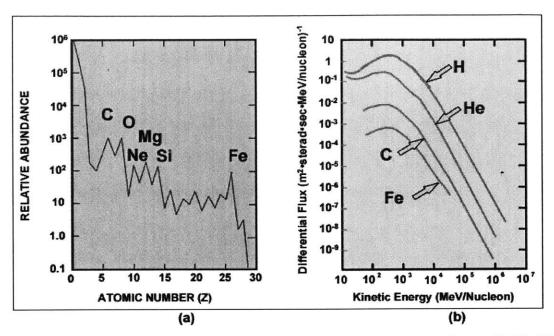

Figure 2-3: Abundances (a) and Energy Spectra (b) of Galactic Cosmic Radiation (GCR) [19]

Galactic Cosmic Rays - Spacecraft must contend with energetic charged particles that originate from sources beyond the solar system. These charged particles are known as the Galactic Cosmic Rays (GCRs) and consist of a variety of nuclei ranging from hydrogen to iron that originate from various supernovae. Figure 2-3 shows the distribution of atomic nuclei that form GCRs and the various energy distributions that these nuclei have [19]. GCRs are unique since they sometimes consist of very heavy atomic nuclei like Iron or Carbon while the vast majority of space radiation consists of energetic much lighter electrons and protons. Heavy nuclei from GCRs can only be simulated by particle accelerators on Earth and are particularly damaging to electronic semiconductors [17]. The high mass of GCR particles contributes to the overall high energy levels of GCRs when compared to SPEs. This excessively high energy makes it practically impossible to shield components from GCRs [20].

Figure 2-4: Sunspot Count vs. SPE Occurrences with 100MeV Protons [15]

The intensity of GCRs within the solar system is dependent on the 11-year solar cycle. The solar magnetic field also varies with the 11-year solar cycle and when the solar-cycle peaks, the solar magnetic field blocks GCRs. During periods of solar maximum, the flux, or number of ions per unit area, decreases by a factor of two [20].

Solar Particle Events - Solar Particle Events (SPE) are primarily emissions of protons and a few heavy ions from the sun. These energetic charged particles are emitted from solar flares during periods of high solar activity. Solar activity has lulls and peaks that follow an 11 year cycle [15]. Figure 2-4 shows solar activity for 22 years as a subset of the solar sunspot cycle with the number of visible sunspots plotted on the y-axis vs time on the x-axis. Major SPEs containing highly energetic protons (>100MeV) are marked with red circles. The greatest concentrations of the major SPEs align with periods of high solar activity or high sunspot counts. Typically SPEs have much lower energies than GCRs but their flux is much greater within the Solar System.

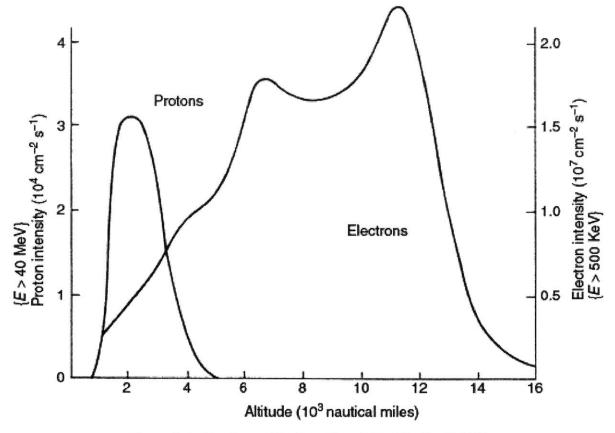

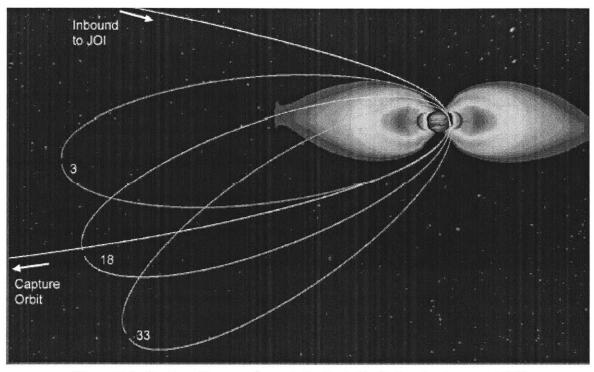

Figure 2-5: Structure of the Van Allen Belts (Idealized) [21]

Planetary Magnetic Fields - Energetic charged particles originating from the Sun such as protons, electrons, and other ions can be trapped by magnetic fields in the solar system. For example, the magnetic fields that surround the Earth and Jupiter trap these energetic particles and become radiation hazards for spacecraft. The Earth's magnetic field is of interest since the vast majority of spacecraft operate within it whereas Jupiter's magnetic field is notable because it traps many more solar charged particles than Earth's field. Since Jupiter has the strongest planetary magnetic field, it is a significant hazard to Jovian spacecraft [22].

The particle concentration of Earth's magnetic field is shown in Figure 2-5 while the location of these particles around Earth is shown in Figure 2-1. At altitudes within the upper end of Low Earth Orbit (LEO) beyond the 215 nautical mile altitude orbit of the International Space Station, the radiation environment is primarily trapped solar protons. As orbit altitude increases, trapped solar electrons become

the dominant radiation hazard. However, most satellites operate either in LEO or geostationary orbit which is much higher than the Van Allen belts in Figure 2-1 to avoid this radiation hazard.

## 2.2 Radiation-caused Electrical Malfunctions

Space radiation negatively affects the operation of space electronics by depositing charge and energy within the micro-architecture of integrated-circuit microchips. This transfer of energy causes malfunction through one of the following mechanisms [17]:

- Permanently changing the composition and structure of the semiconductors that comprise

electronic circuits

- 2. Causing transient voltage or current spikes within electronic circuitry

- 3. Creating unwanted state changes in computer memory elements

Depending on the semiconductor architecture and the magnitude/direction of the disruption, the electronics may recover from a temporary failure or become permanently damaged/degraded [17].

Radiation can either cause temporary or permanent malfunctions in radiation-tolerant electronics.

The persistence of a radiation-caused malfunction depends on the electronic/radiation interaction and electronic design. A permanent malfunction is characterized by an irreversible change in the electronic device's physical makeup that affects functionality. A transient malfunction will go away after waiting for a certain time period, power cycling, or invoking any other features that returns the device to its normal state. Examples of these features are automatic processor resetting after a fault occurs, correcting data corrupted by radiation, retaking radiation corrupted measurements, or switching to a back-up while the radiation-affected system recovers.

Transient effects that do not cause permanent damage to an appropriately designed avionics system are presented first in this subsection. These are collectively known as Single Event Effects (SEE) and only occur within electronics that are already powered and operational. The SEE category can be divided into Single Event Upsets (SEUs), Single Effect Transients (SETs), and Single Event Latch-up (SEL).

SEEs only affect electronics that are powered on. The final three topics are Single Event Gate Rupture (SEGR), Total Ionizing Dose (TID) and Total Non-Ionizing Dose (TNID) that permanently affect the operation of electronics that are both on or off.

## 2.2.1 Single Event Upset

Single Event Upsets (SEUs) occur when an energetic radiation particle is absorbed by a transistor and causes the transistor to change its state in a digital circuit. Transistors are either on or off in digital circuitry, and a SEU will undesirably toggle the transistor's state. The amount of energy a transistor must absorb for an SEU to occur depends on the transistor size, composition, angle of radiation incidence, and energy of the radiation particle. Digital circuitry in general is vulnerable to SEU-caused malfunctions since their transistors seldom operate between the on and off transistor states. For example, digital computer memories, which consist of transistors, are typically affected by SEUs. A SEU can persist in memory if the avionics system is not built to handle it. However, the SEU hazard can be resolved with appropriate algorithms to mitigate the malfunction.

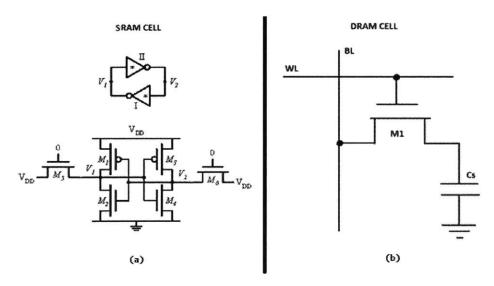

Figure 2-6: SRAM (a) and DRAM (b) Memory Cells

<sup>&</sup>lt;sup>5</sup> Diagram taken from "Ultra Low Power SRAM Design" by Huifang Qin and Jan M. Rabaey at the UC Berkeley Wireless Research Center. URL:

https://buffy.eecs.berkeley.edu/PHP/resabs/resabs.php?f year=2006&f submit=chapgrp&f chapter=5

<sup>6</sup> Diagram taken from "DRAM - An Intro". URL: https://allthingsvlsi.wordpress.com/tag/dram-cell/

The two types of radiation susceptible memory common in avionics systems are Static Random Access Memory (SRAM) and Dynamic Random Access Memory (DRAM). These computer memories are composed of many memory cells and the circuitry for reading/writing data to/from these cells. SRAM and DRAM memory cells both utilize transistors as shown in Figure 2-6. SRAM on the left can be thought of two interconnected inverter circuits that can take on two states – either V<sub>1</sub> is high and V<sub>2</sub> is low or vice versa. These two states correspond to one bit of digital data and can be read/written to with external circuitry. The bottom left of Figure 2-6 shows the transistor-based implementation of an SRAM cell. The right side of Figure 2-6 shows a DRAM cell stores the value of one digital bit in a capacitor, with transistor M1 reading/controlling the value of this bit.

If any of the transistors in these memory cells are disrupted by radiation, then the data stored in the memory cell can be corrupted. This failure is known as a SEU and could cascade into an avionics system malfunction depending on which memory cell is affected and the ability of the system to handle these failures. Energetic protons or heavy ions can deposit dangerously high levels of energy inside the transistors of an electronic memory circuits shown in Figure 2-6. This excess energy is dangerous because it corrupts data stored in digital memory by unwantedly causing the transistors in a digital memory cell to conduct electricity. This unwanted conduction of electricity causes the memory cell to change state and corrupts the digital data in the memory cell [12] [17]. Improperly designed space electronics that cannot detect and correct corrupt data can result in SEUs causing permanent issues.

SEUs can also corrupt the SRAM memory that is frequently used by microchips to store their internal configuration necessary to implement avionics functionality. This type of malfunction is known as Single Event Fault Interrupt (SEFI) and can prevent these microchips from operating correctly. An uncorrected SEFI will propagate through the operation of the microchip and could cause the wrong instructions to be executed by a microprocessor or corrupt reconfigurable digital logic circuitry within a Field Programmable Gate Array (FPGA) microchip [12].

## 2.2.2 Single Event Transient

The passage of a charged particle near an electrical circuit node can cause transient currents in that node. By interacting with other circuit components, these currents cause transient voltages [3]. This process is known as a Single Event Transient (SET). SET-caused voltage spikes can show up as noise within instruments and analog circuitry [17]. In the case of REXIS and other space-based instruments with analog electronics, SETs decrease the resolution of scientific telemetry due to the spurious signals it causes.

If a SET-caused voltage spike is clocked into digital circuitry without triggering a fault, the error can propagate through the system and cause permanent damage [17]. Higher clock speeds make a digital system more vulnerable to SET but design that detects and resolves radiation-caused faults ensures that SET cause transient malfunctions [23]. SETs cause transient voltages that can be erroneously interpreted by digital circuitry [17]. Higher clock speeds mean more of these interpretations and calculations per second, and thus increase the chances of SET errors [17].

## 2.2.3 Single Event Latch-up

Single Event Latch-up (SEL) occurs when radiation causes unwanted conduction and high currents in Complementary Metal Oxide Semiconductor (CMOS) transistors. The (CMOS) transistors used in space electronics have alternating layers of P-type and N-type silicon that form a parasitic thyristor<sup>7</sup>. SEL occurs when charge deposited from space radiation creates small but abnormal currents in the CMOS base layer. This current provides the initial energy to cause the MOSFET's parasitic thyristor to start conducting electricity though a positive feedback loop. Left unchecked, this SEL causes a damaging overcurrent event that overheats and destroys the small and sensitive electronics within microchips [23].

<sup>&</sup>lt;sup>7</sup> A thyristor is an electrical semiconductor component that allows small voltages at one terminal to control large currents at other terminals. The small voltage causes a positive feedback loop within the thyristor that facilitates the conduction of large currents.

Without built-in protection, SELs can cause permanent damage in circuitry. If the circuit undergoing SEL has no current limiting or the circuit is not shut off in time, then the high current caused by the latch up will cause permanent damage through overheating. Circuits with current limiters or over-current detectors will stop the heat build-up from SEL by limiting power to the SEL affected circuit. There will be a temporary lapse in functionality, but the circuit will not have permanent damage. For low-power circuitry, a current limiter could be a simple resistor on the supply line. Higher power circuitry requires more complex electronics that actively detect and cut power to remove the overcurrent fault.

## 2.2.4 Single Event Gate Rupture

Single Event Gate Rupture (SEGR) is caused by ionizing space radiation that deposits enough charge within certain transistors to permanently damage the control terminal of a transistor, known as the gate. Transistors affected by SEGR are the Metal Oxide Semiconductor Field Effect Transistors (MOSFET) that are used in modern digital electronics, where the gate is electrically isolated from the rest of a transistor with a non-conductive dielectric layer. Ionizing radiation can deposit enough charge on the dielectric layer to break it down. This breakdown causes a brief but damaging current flow that damages the MOSFET by electrically connecting the gate to the rest of the transistor. The damage mechanism is similar to charge building up in clouds, causing lightning but on the microscopic scale of a transistor. Using MOSFETs well below the voltage limits that it is rated for greatly reduces the chance of SEGR [17].

# 2.2.5 Total Ionizing Dose

Total Ionizing Dose (TID) is a measure of radiation dose accumulation caused by prolonged exposure to radiation in space that can cause permanent damage to electronics. While an electronic component is in outer space, ionizing radiation deposits charge that accumulates within semiconductors that form the component's circuitry [23]. This additional charge changes the composition of circuit components that in turn affects operation speed, threshold voltages, and overall functionality [17] [23].

This composition of circuit components is formally known as doping, and is defined as the concentration of charge within a volume of semiconductor. Modern integrated circuits consist of differently doped regions of a semiconductor like silicon or gallium arsenide that form interconnected transistors. As TID increases, the semiconductor doping changes and leads to poorly operating transistors.

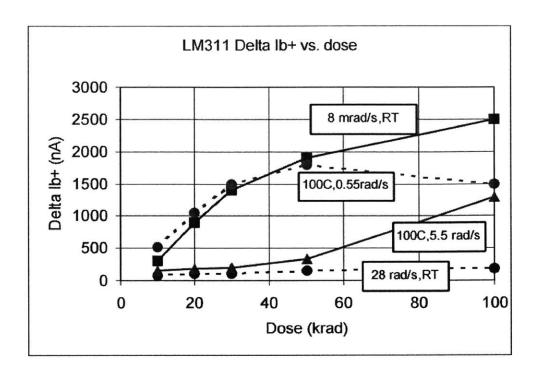

Low radiation dose rates cause more damage to electronics than the high dose rates that electronics are typically tested with on Earth. This susceptibility to low dose rates is known as Enhanced Low Dose Rate Sensitivity (ELDRS) and space-grade electronics are designed to be less susceptible to ELDRS. On a typical geostationary orbit space mission of several years, the TID accumulates to around 10<sup>5</sup> rad [17]. Typically devices are tested to levels of 10<sup>6</sup> rad with a higher dose rate on Earth than that experienced in outer space. This margin of an order of magnitude radiation dosage difference is needed because of the ELDRS vulnerability and impracticality of testing a component continuously for years. The underlying cause for the ELDRS vulnerability is unknown and an area of active research.

TID also has serious long term effects on analog electronics. Within analog circuitry, voltage thresholds, characteristic response, and current-voltage curves change from radiation exposure. Changing these parameters usually has negative effects on the power consumption, noise, accuracy, precision, and overall operation of analog electronics [17] [24]. These TID-caused circuitry changes are permanent so avionics designers must account for this gradual degradation over the circuitry's operational lifetime.

Unlike analog circuitry, once the TID radiation dose goes beyond a certain level, digital circuitry abruptly stops working [25]. Digital electronics quickly change status from operational to defective because their internal components are supposed to exist in distinct "on" or "off" states, and TID interferes with this neat categorization. The transition between these states is dictated by a voltage threshold. TID causes this threshold to drift over time. If the threshold changes slightly, the electronics would still function normally, but there could be increased current drawn since the circuit is slightly deviating from the operating point that it was designed for. However, once these TID-caused threshold changes become severe enough to violate the definitions of digital logic – the voltages defining the "on" and "off states – the digital electronic component will abruptly stop working. Degradation in digital electronics is different

from analog electronics since TID degradation in analog electronics is immediately evident because analog circuitry has a continuous range of operating voltages.

# 2.2.6 Total Non-Ionizing Dose

Another source of long-term radiation-caused damage similar to TID are high-energy neutrally-charged particles measured in terms of Total Non-Ionizing Dose (TNID). Exposure to non-ionizing radiation causes the crystalline structure of electronic semiconductors to become riddled with irregularities in contrast to TID that changes the charge of electronic semiconductors. These radiation-caused defects are known as displacement damage and they degrade the performance of CCDs, solar cells, and linear regulators [17]. Displacement damage will damage semiconductor crystal structures and permanently degrade the charge transfer efficiency [17]. This degradation negatively affects the pixel readout of CCDs, voltage output from voltage references, and power output from solar panels. Like damage from TID, displacement damage is always accumulating, even if the space electronics in question are turned off.

# 2.3 Techniques for Radiation Risk Mitigation

Avionics designers implement a variety of techniques to prevent radiation-caused malfunctions and gracefully recover the avionics system when these malfunctions occur. Collectively these techniques are known as avionics design for radiation (DFR). More specifically, design decisions that address and mitigate radiation-caused malfunctions fall within the category of DFR.

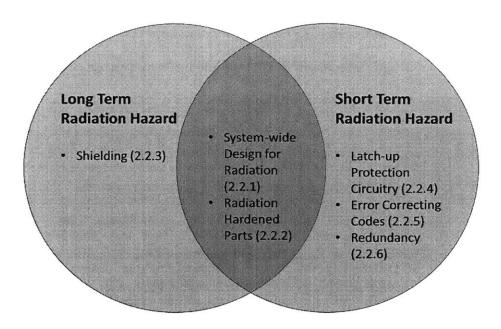

Figure 2-7: Radiation Hazard Mitigation Techniques

DFR techniques protect against both the long term effects of radiation like TID and displacement damage and short term transient effects created by SEEs. DFR methods add complexity to space system avionics but ensure that these circuits can function and allow the space system to meet its requirements. DFR techniques can be grouped using two criteria: the radiation hazard the technique addresses and the avionics complexity required to implement the technique. Mitigating and recovering from SEE-caused malfunctions and long term radiation-caused degradation require the implementation of different approaches in the electronics design as shown in Figure 2-7. Some of these approaches are effective against both long and short term radiation exposure. Furthermore, the implementation of radiation hazard mitigation techniques range from simple to complex. An example of a simple technique is using a current limiting resistor on a power supply line to prevent damaging currents from Single Event Latch-up (SEL) hazards. On the other hand, a complex technique is triplicating critical functionality to compare the three results for consistency and correctness [17].

It is important to realize that these groupings are convenient, but they are mainly superficial. A single technique cannot fall squarely in the simple or complex categories. For example, the implementation of current limiting resistors requires an electrical power system that can continuously

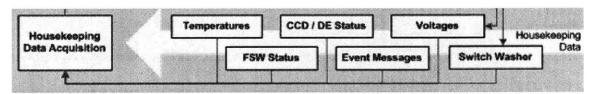

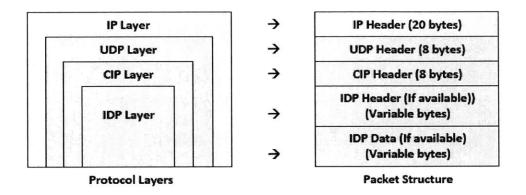

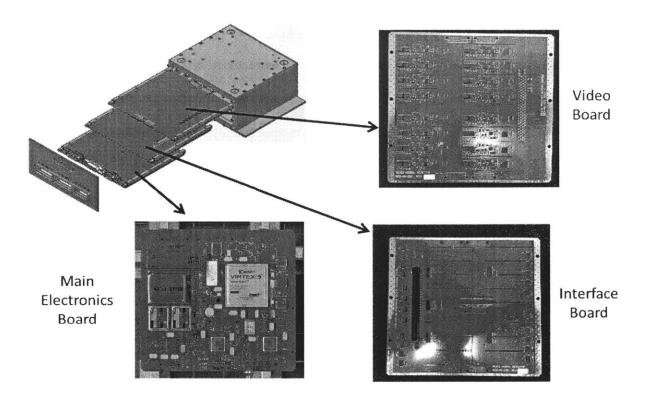

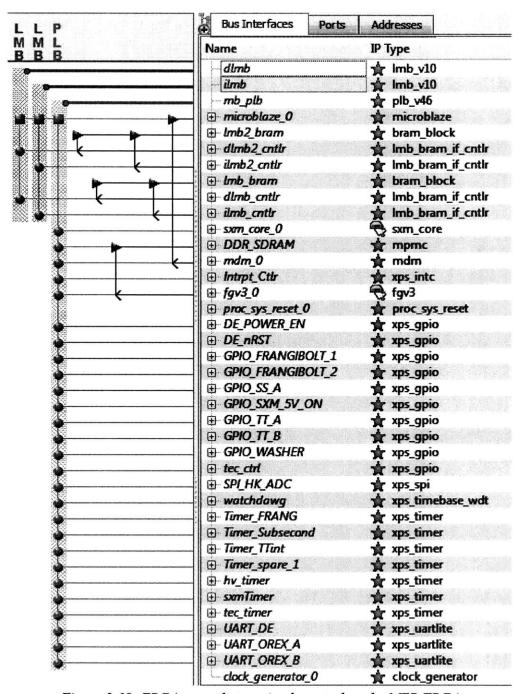

support the significantly increased current draw of a latched-up component until the component is shut down. For certain low-power electrical systems, accommodating this extra current on top of nominal power consumption can add further complexity. On the other hand, using triple modular redundancy to redundantly compute and compare values could be simple to implement in an FPGA-based design if there are enough digital logic resources available on the FPGA and the FPGA manufacturer provides a standardized way to triplicate functionality [17] [23].