## Creation, Validation, and Implementation of a Highly Accelerated Life Testing (HALT) Procedure to Improve the Reliability of Printed Circuit Boards

by

Abhishek Singh

Bachelor of Science in Mechanical Engineering National Institute of Technology -Trichy, 2013

Submitted to the Department of Mechanical Engineering in partial fulfillment of the requirements for the degree of

Master of Engineering in Advanced Manufacturing and Design

at the

MASSACHUSETTS INSTITUTE OF TECHNOLGOY

September 2016

© 2016 Abhishek Singh. All rights reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now known or hereafter created.

# Signature redacted

| Signature of Author:                    |                                   |                               |

|-----------------------------------------|-----------------------------------|-------------------------------|

| 7                                       |                                   | ent of Mechanical Engineering |

| Signature Signature                     | e redacted                        | August 05, 2016               |

|                                         | -                                 | David E. Hardt                |

| Rai                                     | lph E and Eloise F. Cross Profess | sor of Mechanical Engineering |

| Signatu                                 | re redacted                       | Thesis Advisor                |

| Accepted by:                            | ~                                 | <br>Rohan Abeyaratne          |

|                                         | Quentin B                         | Berg Professor of Mechanics & |

| MASSACHUSETTS IN OF TECHNOLOG SEP 13 20 | 16                                | ommittee of Graduate Students |

**ARCHIVES**

(This page is intentionally left blank)

Creation, Validation, and Implementation of a Highly Accelerated Life Testing (HALT)

Procedure to Improve the Reliability of Printed Circuit Boards

by

Abhishek Singh

Submitted to the Department of Mechanical Engineering On 15th August, 2016 in partial fulfillment of the

requirements for The Degree of Master of Engineering in Advanced Manufacturing and Design

Keywords: Reliability, HALT, PCBs, Vibration testing

Abstract

Highly Accelerated Life Testing (HALT) is a test methodology to evaluate the reliability of electronic and

electromechanical devices. This thesis aimed at the implementation of Highly Accelerated Life Testing

(HALT) on Printed Circuit Boards. A standard operating procedure for implementing Highly Accelerated

Life Testing (HALT) to increase the reliability of PCBs used in various Waters equipment is developed and

validated. For the creation of the standard operating procedure a very reliable Alliance PCB is selected that

acts as a benchmark for screening other boards. Extensive testing is done on the Alliance PCB by subjecting

it to thermal and vibration stresses through a Hot Step Stress profile, Cold Step Stress profile, Thermal

Cycling, Vibration Step Stress profile and Combined Cycle profile. For validation, the standard operating

procedure created is applied to a less reliable Acquity board to check whether the same standard operating

procedure is effective in precipitating and detecting failures on a variety of different boards that Waters

equipment uses. As expected the operating limits of temperature and vibration of the Acquity board are

found to be less than the Alliance board i.e. the Acquity experiences failure much earlier than Alliance

when subjected to the same stress profiles. This result is in direct correlation with the on field failure data

obtained for these two boards – the less reliable board has lesser operating limits.

Thesis Supervisor: Dr. David E. Hardt

Title: Ralph E and Eloise F. Cross Professor of Mechanical Engineering

3

(This page is intentionally left blank)

#### **ACKNOWLEDGEMENTS**

I take this opportunity to express my gratitude to the people who have been instrumental in the successful completion of this project. First, I would like to thank Professor David Hardt for guiding us through the entire period of this project work and pushing us to do our best. His valuable guidance and constant encouragement helped us greatly during the course of the project.

I would like to thank my wonderful teammates Chun Ming Zhang and Dexter Chew. We had a very cross functional team and each of us brought different skill set to the table, which was important for the success of this project. We gelled well as a team and I thoroughly enjoyed working with them for the last six months.

I would like to express my heartfelt gratitude to Mr. Jim McPherson, Mr. Gabriel Kelly and Mr. Gregory Puszko from Waters Corporation for their constant support, encouragement, and diligence in providing us the necessary tools and resources to be successful.

The guidance and support received from the employees at Reliability Engineering division, Testing Engineering division and Marketing division at Waters Corporation has been phenomenal and was vital for the success of the project. I am grateful for their constant support and help.

Special thanks to Mr. Jared Ouillette, Ian Klobucher and Brian from the Reliability Engineering Lab and Mr Antonio from the Testing Department for their enthusiasm and support during the implementation phases of this project.

Last and definitely not the least, I would like to thank my parents Mr. Yasbir Singh, Mrs. Neeta Singh, my brother Abhijeet Singh and my sister Priyanka Singh for being very supportive through the entire course of the project.

(This page is intentionally left blank)

## **Table of Contents**

| ABSTRACT                                                | 3         |

|---------------------------------------------------------|-----------|

| ACKNOWLEDGEMENTS                                        | 5         |

| LIST OF TABLES                                          | 11        |

| CHAPTER 1: INTRODUCTION                                 | 12        |

| 1.1 Background Information on Waters Corporation        | 13        |

| 1.2 Liquid Chromatography and Mass Spectrometry         | 14        |

| 1.2.1 High-Performance Liquid Chromatography (HPLC)     |           |

| 1.2.1 Ultra-Performance Liquid Chromatography (HPLC)    |           |

| 1.3 Motivation                                          |           |

| 1.4 Objective                                           |           |

| 1.5 Problem Statement                                   |           |

| 1.6 Task Division                                       |           |

| CHAPTER 2 : INTRODUCTION TO RELIABILITY ENGINEERING     | _         |

| 2.1 Background                                          |           |

| 2.2 Why is Reliability Important?                       |           |

| 2.3 Basic Reliability Concepts                          |           |

| 2.5 Reliability of PCBs at Waters                       |           |

| CHAPTER 3 – LITERATURE REVIEW                           |           |

| 3.1 Introduction to Highly accelerated life test (HALT) |           |

| 3.2 HALT Profiles                                       |           |

| 3.2.1 Temperature Homogeneity                           |           |

| 3.2.2 Cold Step Stress                                  |           |

| 3.2.3 Hot Step Stress                                   |           |

| 3.2.4 Thermal Cycling                                   |           |

|                                                         |           |

| 3.2.5 Vibration                                         |           |

| 3.2.5.1 Failure of PCBs due to Vibration                |           |

|                                                         |           |

| 3.2.5.3 HALT vibration chamber                          |           |

| 3.2.5.4 HALT vibration Profile                          |           |

| 3.2.4 Combined Vibration and Temperature                |           |

| 3.2.5 Failure Analysis and Corrective Actions           |           |

| 3.2.6 Benefits of HALT                                  |           |

| CHAPTER 4 – PREPARATION OF STANDARD OPERATING PROCEDURE |           |

| 4.1 Overview – The Methodology                          |           |

| 4.2 Functional Testing of the Alliance board            | <i>38</i> |

| 4.3 Data Acquisition and Equipment Used                 | 45        |

| 4.3.1 Temperature Measurement                           | 45        |

| 4.3.2 Vibration Response Measurement                    | 45        |

| 4.4 Experimental Step and Analysis                      | 47        |

| 4.4.1 Hot Step Stress                                   |           |

| 4.4.2 Cold Step Stress                                  |           |

| 4.4.3 Thermal cycling                                   |           |

| 4.4.5 Vibration                                         |           |

| 4.4.5.1 Vibration Fixture                               |           |

| 4.4.5.2 Response Characterization of the Fixture        |           |

| 4.4.5.2.1 Experimental Setup                            |           |

|   | 4.4.5.2.2 Location of Accelerometers.                                   | 53 |

|---|-------------------------------------------------------------------------|----|

|   | 4.4.5.2.3 Experimental Results                                          | 54 |

|   | 4.4.5.3 Vibration Step Stress                                           |    |

|   | 4.4.5.3.1 Vibration Step Stress Profile                                 |    |

|   | 4.4.5.3.2 Experimental Setup and Procedure                              | 59 |

|   | 4.4.5.3.3 Experimental Results                                          |    |

|   | 4.4.6 Combined Thermal Cycling and Vibration                            |    |

|   | 4.4.6.1 Combined Cycle Profile                                          |    |

|   | 4.4.6.2 Experimental Setup and Procedure                                |    |

|   | 4.4.6.3 Experimental Results                                            | 65 |

| C | HAPTER 5 – VALIDATION OF THE STANDARD OPERATING PROCEDURE               | 67 |

|   | 5.1 Introduction                                                        | 67 |

|   | 5.2 Selection of Acquity PCB                                            | 67 |

|   | 5.2.1 Ease of testing and root cause analysis                           | 68 |

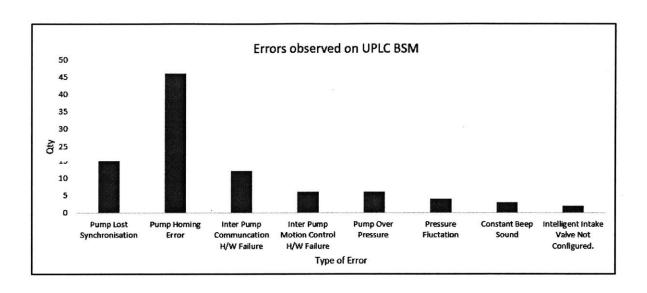

|   | 5.2.2 Field Failure Data                                                | 69 |

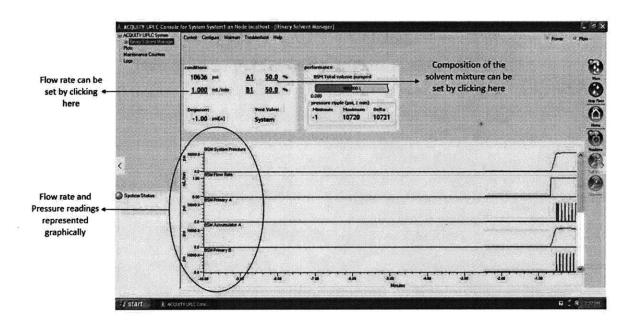

|   | 5.2 Functional testing of the Acquity PCB                               | 70 |

|   | 5.3 Experimental setup                                                  |    |

|   | 5.4 Experiments – Acquity PCB                                           | 74 |

|   | 5.4.1 Hot Step Stress                                                   | 74 |

|   | 5.4.2 Cold Step Stress                                                  | 77 |

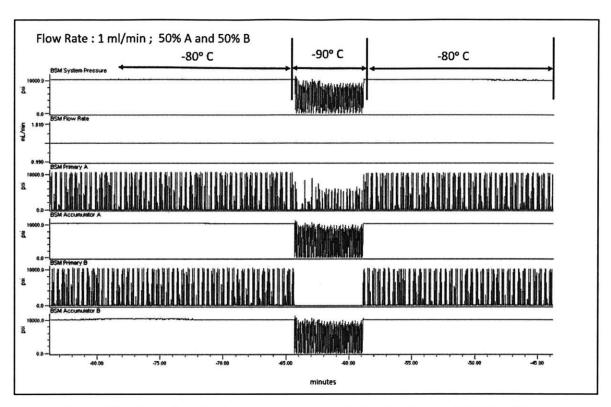

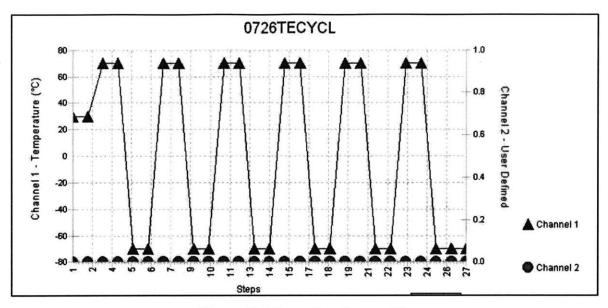

|   | 5.4.3 Thermal Cycling                                                   | 78 |

|   | 5.4.3 Vibration Step Stress                                             | 79 |

|   | 5.4.3.1 Vibration Step Stress Profile                                   | 79 |

|   | 5.4.3.2 Vibration Fixture                                               |    |

|   | 5.4.3.3 Experimental Results.                                           | 84 |

|   | 5.4.3.4 Vibrational step stress – 4 module configuration of the fixture |    |

|   | 5.4.5 Combined Cycle                                                    |    |

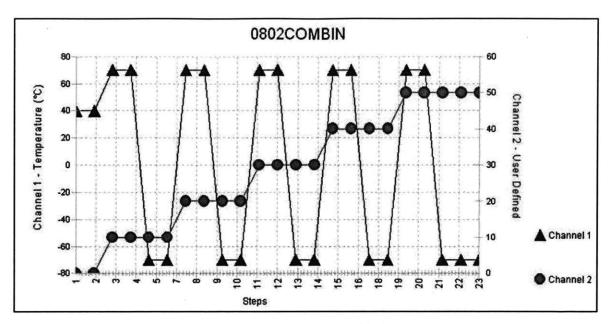

|   | 5.4.5.1 Combined Cycle Profile                                          |    |

|   | 5.4.5.2 Combined cycle experimental results                             |    |

| C | HAPTER 6: CONCLUSION AND FUTURE WORK                                    | 90 |

|   |                                                                         |    |

| к | IRLIOGRAPHY                                                             | 92 |

## **List of Figures**

| Figure 1: Waters Corporation, Milford, MA                                                                              | . 12 |

|------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2: Diversification of Waters Corporation in various fields                                                      | . 13 |

| Figure 3: The Bath tub curve: The green, red and cyan curves represent the infant mortality,                           |      |

| constant and wear out failures respectively, while the blue curve is a combined                                        |      |

| representation of the three individual failure rates                                                                   | . 23 |

| Figure 4: - Life Cycle of electronic components in the absence of burn-in test [10]                                    | . 25 |

| Figure 5- Ruptured Lead Wires due to Fatigue [16]                                                                      |      |

| Figure 6- Solder joint fatigue failure [17]                                                                            | . 31 |

| Figure 7- Solder joint crack initiation [17]                                                                           | . 32 |

| Figure 8- Acceleration vs Time graph as obtained from an accelerometer                                                 | . 33 |

| Figure 9- HALT Chamber                                                                                                 |      |

| Figure 10- HALT Vibration Profile                                                                                      | . 35 |

| Figure 11: Spending rate against time: cost reductions on HALT [12]                                                    |      |

| Figure 13- Alliance Plunger drive PCB                                                                                  |      |

| Figure 15- The Waters Alliance Separations module                                                                      |      |

| Figure 16- Functionality of Plunger Drive PCB.                                                                         |      |

| Figure 17- HyperTerminal functional test output                                                                        |      |

| Figure 18- The triaxial accelerometer used for monitoring vibration                                                    |      |

| Figure 19- Data acquisition device.                                                                                    |      |

| Figure 20- National Instruments DAQ.                                                                                   |      |

| Figure 21: LabVIEW output that measures vibration in X, Y & Z directions                                               |      |

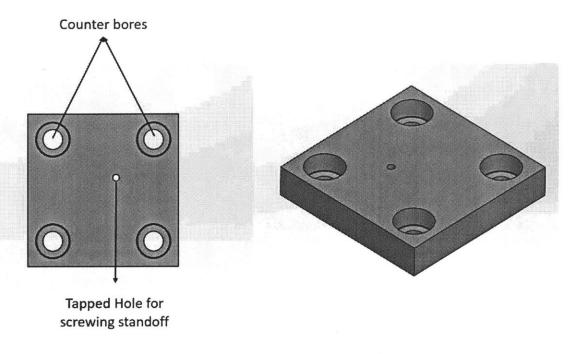

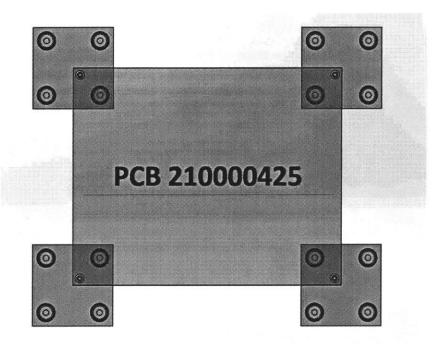

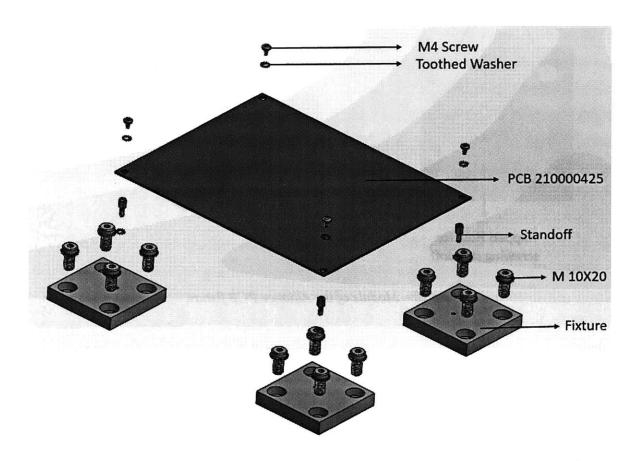

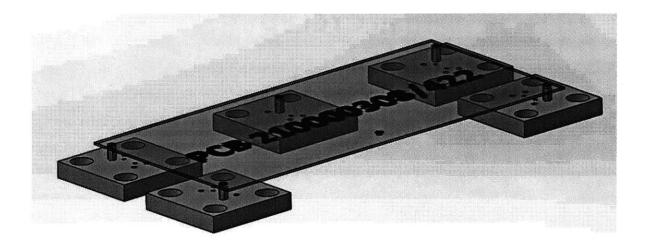

| Figure 22 – Module of the Alliance PCB fixture                                                                         |      |

| Figure 23 – Alliance fixture used for vibration step stress and combined cycle                                         |      |

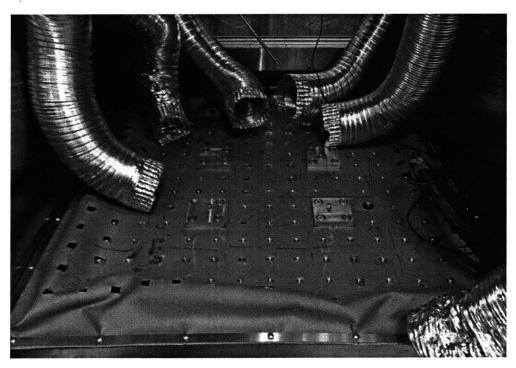

| Figure 24 – Exploded view of the vibration step stress arrangement                                                     |      |

| Figure 25 – Alliance fixture mounted on the HALT chamber vibration table                                               |      |

| Figure 26 – The triaxial accelerometer mounted on the Alliance                                                         |      |

| Figure 27 – Vibration Step Stress experimental setup                                                                   |      |

| Figure 28 - Vibration Simulation on the Alliance PCB                                                                   |      |

| Figure 29 – Locations for placing the accelerometers                                                                   |      |

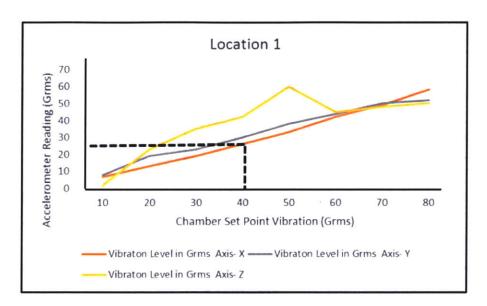

| Figure 30: Graphical representation of Vibrational variation at location 1 on the PCB                                  |      |

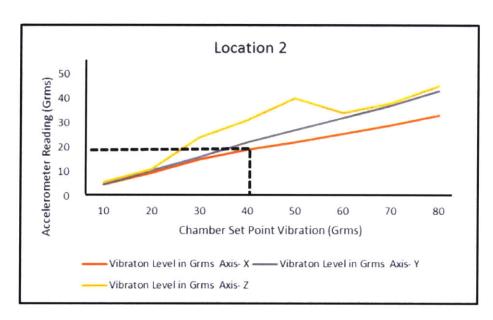

| Figure 31: Graphical representation of Vibrational variation at location 2 on the PCB                                  |      |

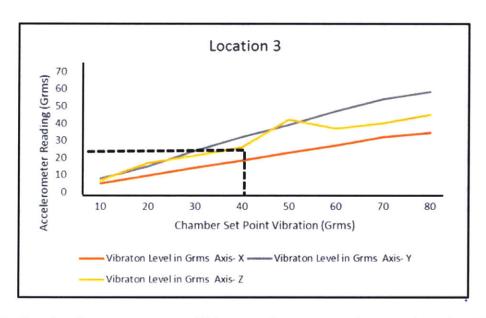

| Figure 32: Graphical representation of Vibrational variation at location 3 on the PCB                                  |      |

| Figure 33 – Vibration Step Stress Profile                                                                              |      |

| Figure 34 – Vibration step stress experimental setup                                                                   |      |

| Figure 35 – Vibration step stress experimental setup                                                                   |      |

| Figure 36 – Vibration Step Stress Profile                                                                              |      |

| Figure 37 – Error message observed during vibrational step stress                                                      |      |

| Figure 38 – Alliance PCB functional test fixture                                                                       |      |

| Figure 39 – Alliance PCB functional test fixture                                                                       |      |

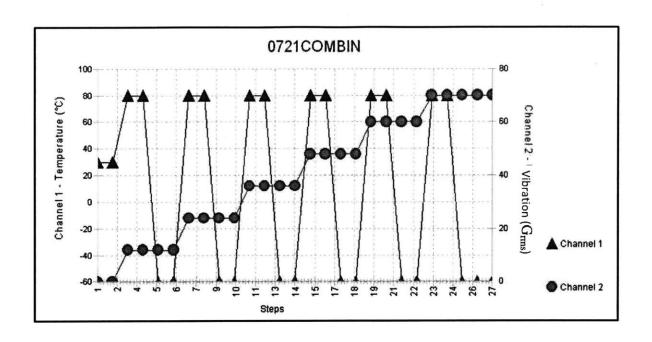

| Figure 40 – Combined Cycle HALT profile                                                                                |      |

| Figure 41 – Combined Cycle HALT profile                                                                                |      |

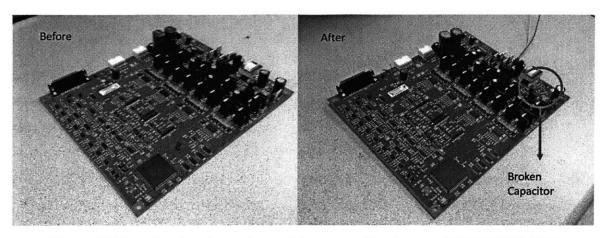

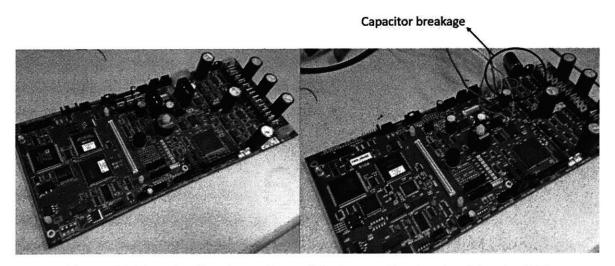

| Figure 41 – Combined Cycle HALT profile  Figure 42-Capacitor breakage observed during combined cycle of 2100000425 PCB |      |

| rigure 42-Capacitor breakage observed during combined cycle of 2100000423 PCB                                          | . 00 |

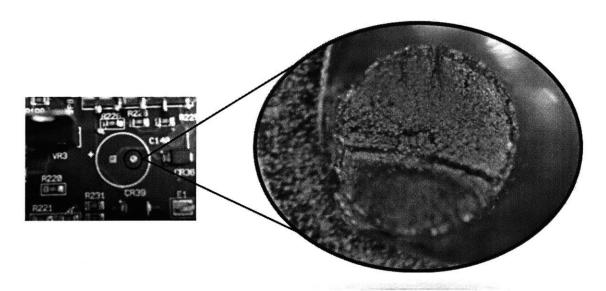

| Figure 43-Microscopic Image of the fractured surface                                                 | 66 |

|------------------------------------------------------------------------------------------------------|----|

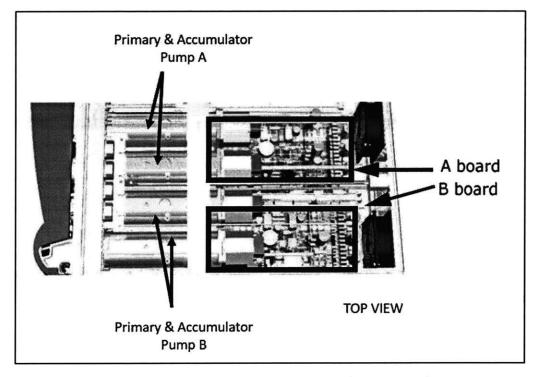

| Figure 46 – The Binary Solvent Manager that uses Acquity PCB                                         | 71 |

| Figure 47: Arrangement of Pumps and PCBs inside the Binary Solvent Manager                           | 71 |

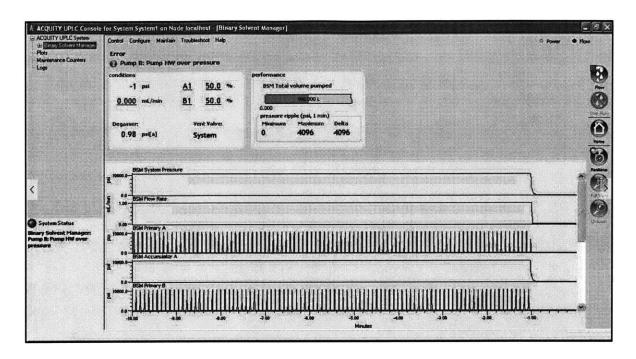

| Figure 48: Screen shot of the user interface of the Console                                          | 72 |

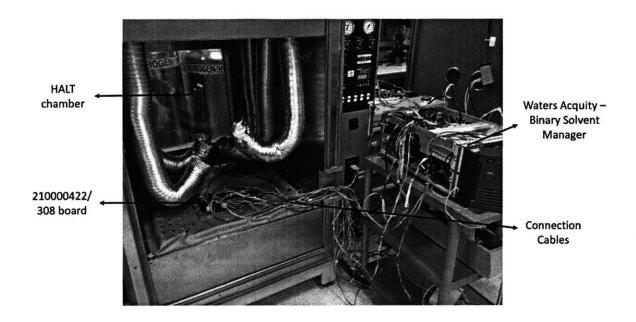

| Figure 49 – Experimental setup for testing Acquity board                                             | 73 |

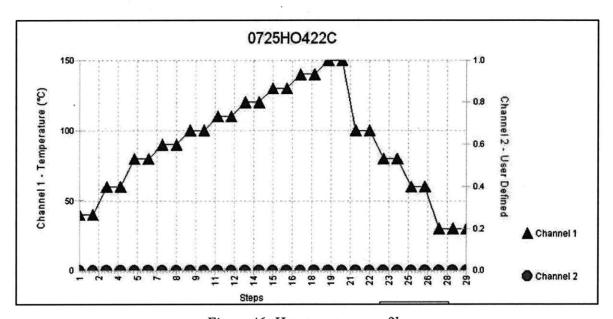

| Figure 50: Hot step stress profile                                                                   | 74 |

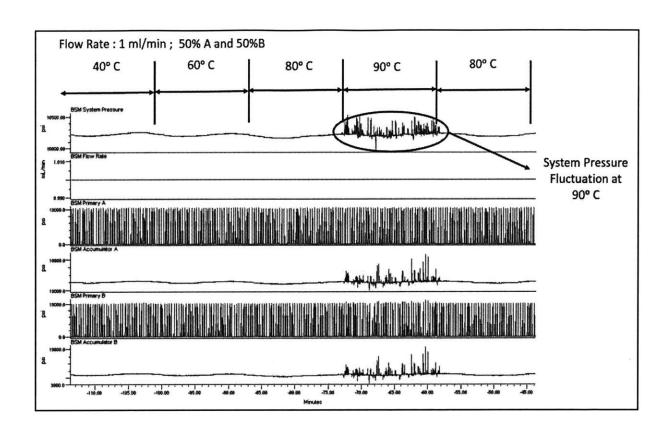

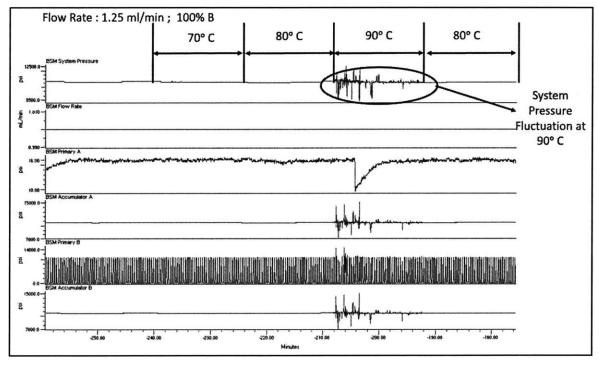

| Figure 51 – Console output showing pressure fluctuation during Hot Step Stress                       |    |

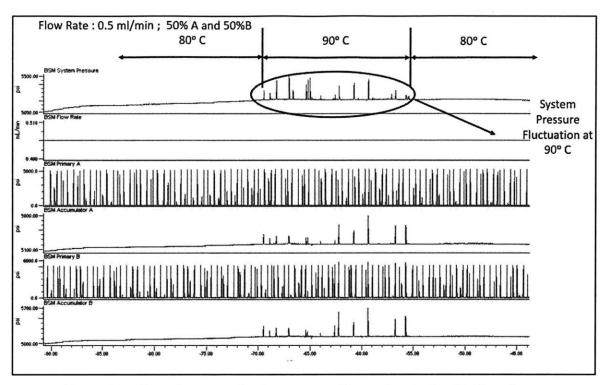

| Figure 52 – Console output showing pressure fluctuation during Hot Step Stress                       | 76 |

| Figure 53 – Console output showing pressure fluctuation during Hot Step Stress                       | 76 |

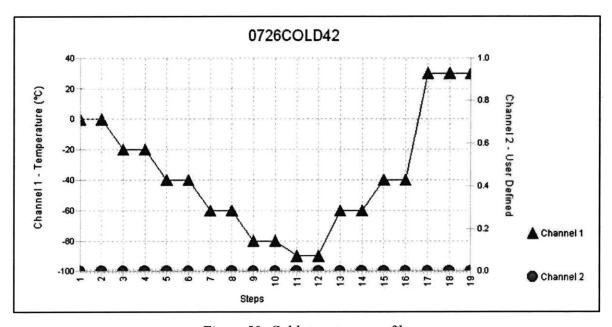

| Figure 54: Cold step stress profile                                                                  | 77 |

| Figure 55 – Console output showing pressure fluctuation during Cold Step Stress                      | 78 |

| Figure 56: Thermal cycling profile                                                                   | 79 |

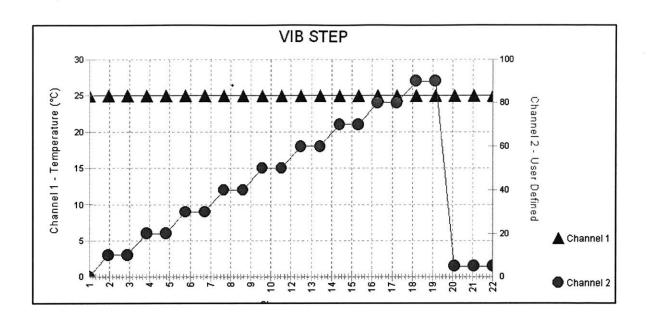

| Figure 57 – HALT profile for vibration step stress                                                   | 80 |

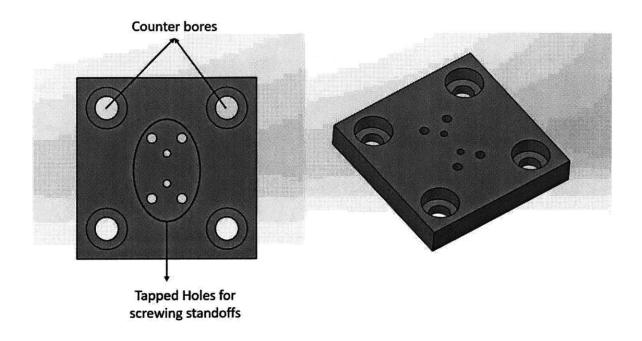

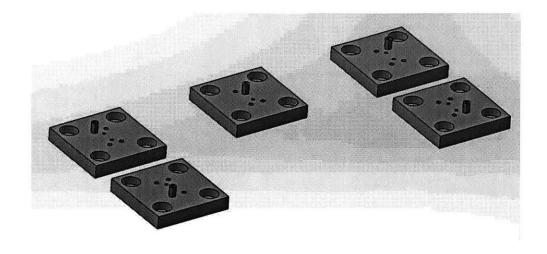

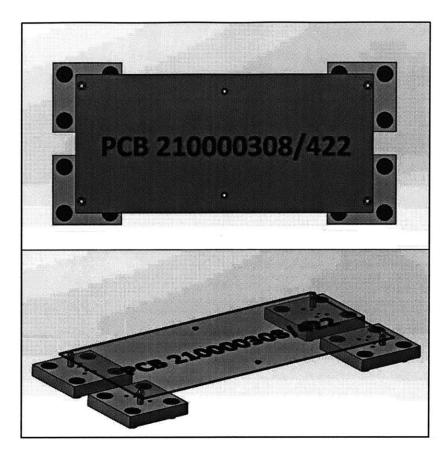

| Figure 58 – Module of the Acquity PCB fixture                                                        | 81 |

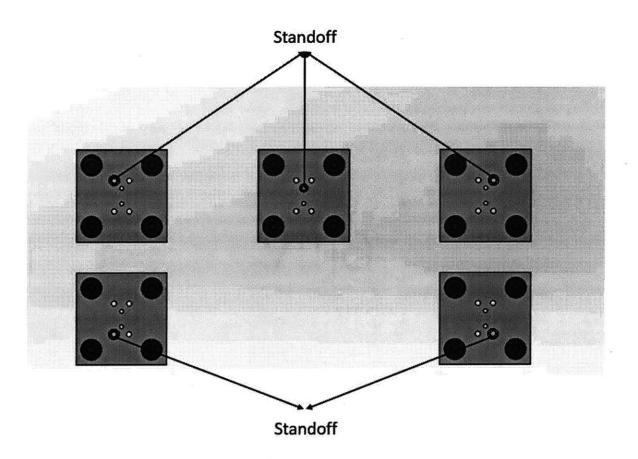

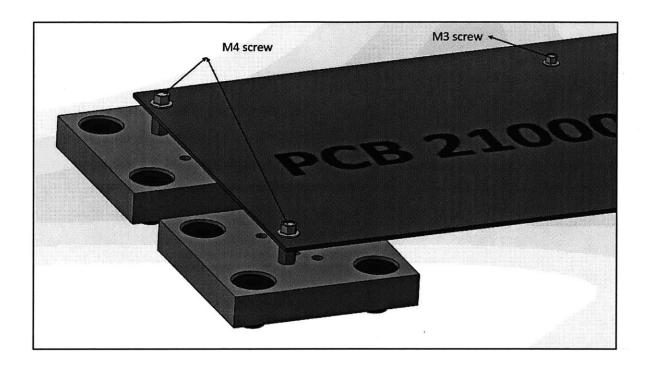

| Figure 59 – Standoffs provided on the Acquity fixture (five module configuration)                    | 82 |

| Figure 60 – Acquity PCB mounted on the fixture                                                       | 83 |

| Figure 61 – Acquity PCB mounted on the fixture                                                       | 83 |

| Figure 62 – M4 & M3 screws for mounting the PCB on the standoffs of the Acquity fixture              | 84 |

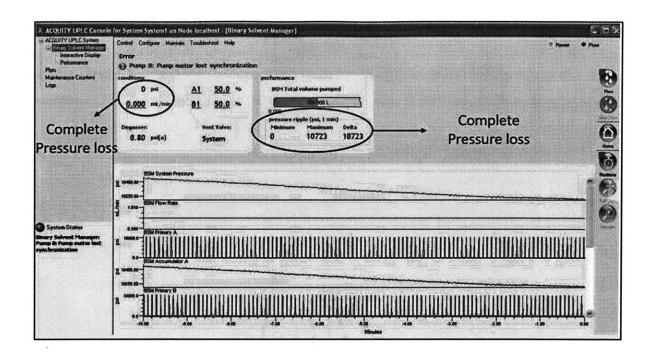

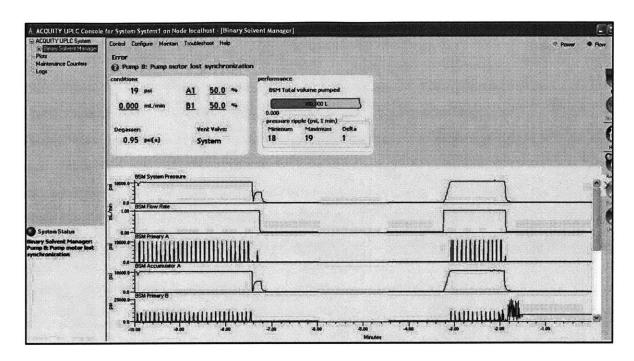

| Figure 63 – Console output showing operational failure of Acquity PCB during vibration step          |    |

| stress                                                                                               | 85 |

| Figure 64: 4 module configuration for vibration step stress                                          | 86 |

| Figure 65: Operational failure observed at 30 G <sub>rms</sub> for four module fixture configuration | 87 |

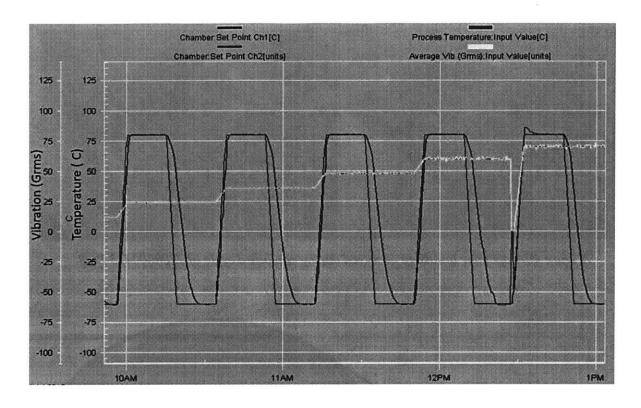

| Figure 66: Combined Cycle profile for Acquity                                                        | 88 |

| Figure 67: Error message observed during combined cycle Acquity                                      |    |

| Figure 68: Capacitor breakage observed during combined cycle of Acquity PCB                          | 89 |

## **List of Tables**

| Table 1 - Vibration set point of HALT chamber and the response of the Alliance PCB at location |

|------------------------------------------------------------------------------------------------|

| 154                                                                                            |

| Table 2 - Vibration set point of HALT chamber and the response of the Alliance PCB at location |

| 256                                                                                            |

| Table 3 - Vibration set point of HALT chamber and the response of the Alliance PCB at location |

| 357                                                                                            |

| Table 4 - List of PCBs for which both In circuit and functional test fixture were available 69 |

## **Chapter 1: Introduction**

This thesis concentrates on the creation and validation of a standard operating procedure (SOP) for implementing Highly Accelerated Life Testing (HALT) for increasing the reliability of PCBs. This thesis is based on an industrial project at Waters Corporation that designs, manufactures and services analytical laboratory instruments that are used by pharmaceuticals, industries, academic personnel and other laboratory applications. Their focus is liquid chromatography, mass spectrometry technology systems, and thermal analysis, which include consumable products such as columns and other support products. Its headquarters is at Milford, Massachusetts as shown in Figure 1. Currently, there is a need at Waters Corporation to implement and integrate a Highly Accelerated Life Testing procedure in the product development process. This chapter concentrates on providing background information on Waters Corporation, the motivation and the problem statement that this thesis seeks to address.

Figure 1: Waters Corporation, Milford, MA

#### 1.1 Background Information on Waters Corporation

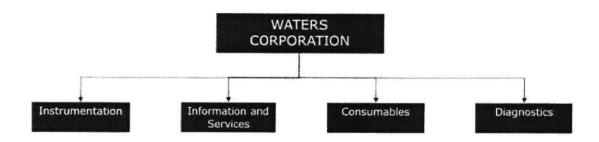

Waters Corporation was founded by James Logan Waters in 1958. Waters Corporation designs and manufactures analytical laboratory instruments that are used in pharmaceutical, industrial and other academic laboratories. The company has advanced in the field of analytical chemistry by producing breakthrough research and state of the art technological systems and has become a major player in the market. Their revenue for the year 2013 was \$1.9 billion. They have offices in 27 countries which also include 11 manufacturing facilities. On the road to becoming a major player in the analytical instruments industry, Waters has acquired a number of companies and thus expanded their business to even greater extents as shown in Figure 2.

Figure 2: Diversification of Waters Corporation in various fields

Waters has divided their products into two divisions: the Biochemical and Chemical Analysis Division, and the Physical Testing Division. The Biochemical and Chemical Analysis Division is based in Milford, MA and produces liquid chromatography instruments, while the Physical Testing Division is based in Manchester, England and Wexford, Ireland and produces mass spectrometry instruments. Thermal analysis and calorimetric instruments are also produced by their physical testing division. With customer success being the prime mission for Waters Corporation, they have a global network of authorized service centers that can install, repair and replace part services, thereby creating a strong bond between customers and the company. This thesis describes the implementation of Highly Accelerated Life Testing (HALT) on PCBs at Waters Reliability Engneering Lab, Milford, MA.

#### 1.2 Liquid Chromatography and Mass Spectrometry

One of the important tools in analytical chemistry is liquid chromatography. It was defined by the Russian botanist, Mikhail S. Tswett in the early 1900s. His studies focused on separating plant compounds by using a solvent and a column packed with materials [1]. This created a pathway for many scientists to use this technique to separate out the individual parts from the sample. The technique is based on the phenomenon that different compounds have different strengths of chemical attraction to particles. When the compound is made to flow using a solvent (mobile phase) in a column filled with particles (stationary phase), the individual parts are separated based on the chemical attraction to the particles in the column which creates different color bands. Based on these color bands, the individual parts of the compound can be identified.

#### 1.2.1 High-Performance Liquid Chromatography (HPLC)

In early liquid chromatography systems, high pressure of about 35 bar was used to generate the flow in packed columns. These systems were known as High-Pressure Liquid Chromatography or HPLC. The 1970s saw tremendous improvement in HPLC technology which could develop pressures up to 400 bar and incorporated improved injectors, detectors and columns. With continued advances in performance with technologies such as smaller particles and higher pressures the acronym remained the same but the name was changed to High-Performance Liquid Chromatography (HPLC). HPLC systems are one of the most powerful instruments used in analytical chemistry today as they can easily identify compounds in trace concentrations as low as parts per trillion (ppt). It has the ability to separate, identify, and quantitate the compounds that are present in any sample that can be dissolved in a liquid and find its application in many industries such as pharmaceuticals, food, cosmetics, environmental matrices, forensic samples and industrial chemicals

#### 1.2.1 Ultra-Performance Liquid Chromatography (HPLC)

In the last decade, advancement in instrumentation and column technology led to significant increase in resolution, speed, and sensitivity in liquid chromatography. A very high level of performance is achieved by using columns with particles as small as 1.7 microns and instrumentation with specialized capabilities designed to deliver mobile phase at about 1000 bar. This new system holistically created with updated capabilities is called Ultra-Performance Liquid chromatography (UPLC) technology. The UPLC system consists of 4 components - a solvent pump, a sample injector, a stationary phase or 'column' which allows the separation, and a detector to analyze the separating components.

#### 1.3 Motivation

Waters Corporation is a leading analytical instrument manufacturer of high-performance liquid chromatography (HPLC) systems and mass spectroscopy. In addition to the intricate mechanical components such as columns, pumps, syringes, and valves in the system, the electronic components such as power supply and printed circuit boards (PCB) that control all of the hardware also play a critical role in the instrument. As a matter of fact, it was reported that the field failure rate of electronic components is often higher than that of the mechanical components. Although efforts and design specification have been made and verified in reliability engineering during the product development process and testing engineering during post-production process, the unpredictability in shipment and end-user environment still incur some additional stresses that have led to premature failures of PCBs within the warranty periods. It is believed that the establishment of a generic Highly Accelerated Life Test (HALT) process could not only facilitate the communication between reliability engineering, R&D engineering, and testing engineering department to better assess the product design weakness within a shorter period during product development cycle, but also therefore increase product robustness and reduce warranty cost.

#### 1.4 Objective

The primary objective of this project is to create and establish a standard operating procedure (SOP) for implementing Highly Accelerated Life Testing (HALT). The objectives can be further categorized into three:

- (1) Creation of a standard operating procedure that will include the step by step process of carrying out the entire process of Highly Accelerated Life Testing (HALT), starting from fixture design all the way through obtaining a reliable product.

- (2) Validation of the standard operating procedure using a different PCB than the one used to create the HALT procedure.

- (3) A cost impact analysis that will include the cost of implementing Highly Accelerated Life Testing (HALT) on a PCB and will also delve briefly into the benefits of implementing HALT.

#### 1.5 Problem Statement

While design verification and instrument evaluation is embedded in Waters' product development process, the current design process does not utilize any generic HALT procedure to identify latent defects in the design or production of components that may not manifest until after years of field operation. Without a generic method in place, the current process requires specialized test plans and analysis developed specifically for the component or assembly. Although Waters already has a discrete approach toward post-production examination of the PCBs quality via In-Circuit Testing (ICT) or Functional Testing (FCT), to make sure the board is functioning properly, yet pre-mature failures still occur in the field. Implementation of a generic HALT procedure for various electronic components such as power supplies and PCBs would help identify these latent issues early on with minimum resources. Waters is looking for a HALT program that can help identify design issues before parts are approved to be used in instruments.

On the same note, possible issues may arise when discussing to what extent these components should be tested. There is often a trade-off that exists between production costs, testing costs, and cost of quality. For example, a new component could be introduced that meets the required functional specifications, and is a lower cost component, but if the failure rates of the component are higher compared to the old part, it may lead to a high cost of quality (the need for service engineers to replace the part) that outweighs the production cost savings. On the other hand, a component could be re-designed using the latest manufacturing techniques in order to improve quality and practically guarantee zero failures over the life of the component, but at a grossly increased production cost. There is a need to find the balance between production costs and cost of quality when it comes to the component, design, or production changes. A successful HALT program would facilitate efficient screening of these scenarios and provide data to augment design process.

#### 1.6 Task Division

This thesis is written in conjunction with the work done by Chun Ming Chang [1] and Dexter Chew [2], and several sections and descriptions in this thesis are written in common with their works. Each team member took the lead on one of three aspects of the HALT implementation. Dexter Chew was responsible for the Design and Fabrication of Fixtures used in HALT. Chung Ming Chang worked on conducting the Highly Accelerated Life Tests with a focus on Thermal stresses and the author of this thesis was responsible for conducting the Highly Accelerated Life tests with a focus on Vibration stresses.

## **Chapter 2: Introduction to Reliability Engineering**

Manufacturers and designers of electronic products are constantly facing new challenges while trying to cope with consumers and market's continuous demands of new features and improved performance in a smaller size. The component sizes, I/O (input/output) pitches and line widths of the printed circuit boards (PCBs) have been decreasing rapidly and the increasing packaging density is causing manufacturing and reliability challenges. Higher operating speeds require shorter interconnection distances to minimize propagation delays, resulting in the components becoming smaller and the number of electric contacts increasing. As a consequence, the components are brought even closer to the PCB with smaller interconnections, adding to the stresses and strains of the interconnections. While the smaller and more versatile components increase current densities and the number of I/Os, the enhanced performance creates thermal challenges due to the increased power densities.

It is a generally recognized fact that the reliability of electronics is to a large extent determined by the ability of electrical interconnections to withstand various loadings during product's operational lifetime. Reliability testing is needed to provide assurance that designs and products are reliable and durable in service, and due to modern day's tight time-to-market requirements and shortening product cycles, these tests should be conducted in a timely fashion. The reliability testing of the interconnections has been traditionally carried out with accelerated reliability tests, where the test units are used more frequently than usual or are subjected to higher than usual levels of accelerating variables like temperature or voltage. These tests can be grouped under two categories, single load tests, where only one loading type is used, and multiple loading tests, where two or more different loading types are used.

Today, the vast majority of accelerated tests are still conducted as single load tests, mainly because of simplicity and because the interaction effects of various combined loads are still not known or understood. There are, however, various potential advantages in multiple loading tests. Most modern products are designed to operate without failure for years and it has become more difficult, even with an accelerated single load test, to obtain a sufficient amount of failure data within a reasonable amount of time. Multiple loading tests have recently been employed as a means of

overcoming such difficulties. Multiple loading tests can also offer a much better representation of the actual use-environment strains and stresses since the components in actual products are rarely exposed to a single type of strain or stress.

This thesis focuses on single as well as multiple loading tests and, more specifically, on the combination of mechanical and thermal loads. The theory part of the thesis gives a review on the current status of the subject, while the experimental part attempts to combine two separate loads (namely vibration and temperature) into a single, more comprehensive and efficient concurrent reliability testing method.

#### 2.1 Background

Reliability engineering emerged as a separate engineering discipline during the 1950s but traces its roots to the Second World War. At the onset of the war, the essential ingredients of reliability engineering, statistics (theory of sampling) and mass production were well established and reliability engineering was ripe to emerge. Electronics played a critical role in the war but the increasing complexity of military electronic systems was generating failure rates which originated in greatly reduced availability and increased costs. During the war, the availability of American naval and army electronic equipment was approximately 70% and less than 40% respectively, while over 60% of airborne equipment shipped to the Far East arrived damaged [3]

During the 1950s the gathering pace of electronic device technology meant that especially the developers of new military systems were making increasing use of large numbers of new component types and involving new manufacturing processes, with the inevitable consequences of low reliability. The increasing complexity of military electronic systems was generating intolerable failure rates and greatly influenced the emergence of reliability engineering. As a consequence, several methods (such as the identification of root cause of field failure and determination of mitigating actions or the specification of quantitative reliability requirements) to achieve higher reliability were developed. A permanent committee (the Advisory Group on Reliability of Electronic Equipment, AGREE) was established to guide the emerging reliability discipline and the birth date of reliability engineering is often coincided with the committees

foundational report, published in 1957, that provided assurance that reliability could be specified, allocated and demonstrated. [4]

The most widely known and used reliability prediction handbook, MIL-HDBK-217, was first published in 1961. Although originally developed for military for aerospace applications, it became widely used for industrial and commercial electronic equipment applications throughout the world. The most recent revision, "Military Handbook, Reliability Prediction of Electronic Equipment", MIL-HDBK-217, Revision F, Notice 2, was released in February of 1995. The MIL-217 is an influential military standard by which reliability predictions are still performed. The reliability development in the western world was driven to a large extent by the customers and particularly by the US military. In order to improve reliability, several standards and procedures were set up, while the suppliers saw little motivation to improve, since they were paid for spares and repairs. By contrast, the Japanese had a different view on improving reliability. Guided by the doctrines of the late W. Edwards Deming, the Japanese industry had learned the fundamental connections between quality, productivity and competitiveness and their basic philosophy was that quality provided the key to greatly increased productivity and competitiveness. [5]

The inductive western approach on reliability led to inventions, breakthroughs and to greater reliance on systems for control of people and processes as opposed to the more deductive approach applied by the Japanese. The effectiveness of the deductive approach was shown in the way that many products, such as Japanese cars, machine tools or consumer electronic products won dominant positions in world markets in the last 40 to 50 years. The deductive approach seeks to generate continuous improvements across a broad front, and new ideas are subjected to careful evaluation. Furthermore, it allows a clearer view, particularly in discriminating between sense and nonsense, but it is not conducive to the development of radical new ideas. Obviously, these two philosophies are not exclusive, and elements of both can be seen in modern reliability engineering.

#### 2.2 Why is Reliability Important?

Today the reliability of electronics is an important factor of success in the highly competitive global markets. The modern consumer will not tolerate products that do not perform in a reliable

fashion, or as promised or advertised and if the manufacturer does not design its products with reliability and quality in mind, someone else certainly will. In addition, customer dissatisfaction with a product's reliability can have disastrous financial consequences to the manufacturer. A company's reputation is very closely related to the reliability of their products and while it takes a long time to build up a reputation for reliability, only one malfunctioning product can brand the whole company as unreliable. Furthermore, if a product fails to perform its function within the warranty period, in addition to the unwanted attention the replacement and repair costs can be substantial. Thus it is of utmost importance that a manufacturer knows the reliability of its product and continual assessment of new product reliability and ongoing control of the reliability of everything shipped are critical necessities in today's competitive business arena.

Besides Financial issues, reliability can be of paramount importance in some application areas. In today's technological world we depend upon the continued functioning of a wide array of complex equipment and machinery. Constantly more and more important operations are performed with automated equipment, whose failures have varying effects from minor nuisances to catastrophic results. It is clear that in critical fields and key applications, such as medical devices or avionic electronics, where failures can lead to life threatening situations, reliability should be of highest priority to avoid the catastrophic consequences of failure.

#### 2.3 Basic Reliability Concepts

This section introduces, defines and briefly discusses some basic concepts related to Reliability.

#### Reliability

An illustrative description of the meaning of reliability today is [6], (originally cited by an unknown reliability engineer): "Reliability - it is when the customer comes back, not the product". More formally reliability is commonly defined as the ability of a product or a component to operate without failure under a set of predetermined conditions over a specified period of time [7]. The definition contains several key requirements: functions of the products, their normal operation and

stated operating conditions as well as anticipated lifetime expectations must be specified. Predetermining these conditions makes the designing easier and the reliability considerations are much easier to implement.

#### Quality

Reliability should not be confused with quality or quality control since the two concepts are quite different. Reliability grew out of the need for a time-based concept of quality and it is the distinction of time that marks the difference between the traditional quality control and the modern approach to reliability. International Organization for Standardization (ISO) defines quality as "the totality of features or characteristics of a product or service that bear on its ability to satisfy stated or implied needs" [8]. The definition of quality refers to this totality at a particular instant of time, whereas reliability deals with the behavior of failure rate over a long period of performance.

#### **Failure**

Failure is an important concept in reliability, since the measure of reliability is the infrequency in which failures occur in time. Especially for all life tests, some time-to-failure information for the product is required since the failure of a product is the event we want to understand. Failure is generally defined as "the non-performance or inability of a component or system to perform its intended function for a specified time under specified environmental conditions" [9]. Once again, the intended function of the device and its operating conditions need to be specified.

#### **Bathtub Curve**

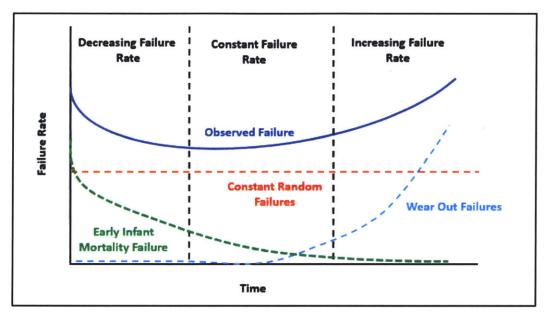

The so called bathtub curve (presented in Figure 3) is typically used to illustrate reliability over time and the three principal periods of product failure. The curve does not depict the failure rate of a single item, but describes the relative failure rate of an entire population of products over time. Although it is rare to have enough short- and long-term failure information to actually model a population of products with a calibrated bathtub curve, the curve is nonetheless a widely used

concept in the industry. The product's life cycle can be divided into three distinct periods based on the dominant failure mode as shown in figure 3.

Figure 3: The Bath tub curve: The green, red and cyan curves represent the infant mortality, constant and wear out failures respectively, while the blue curve is a combined representation of the three individual failure rates

The curve consists of the following three periods:

- **Infant mortality period** is characterized by a decreasing failure rate. These infant mortality failures are highly undesirable and are caused by defects and blunders.

- A constant and relatively low failure rate is a characteristic feature of the normal-life

period (also known as "useful life"). The failures during this period are considered as

random cases of stresses and strains exceeding the product strength.

- Wear-out period exhibits an increasing failure rate due to the fatigue or depletion of materials.

#### 2.4 Reliability of PCBs

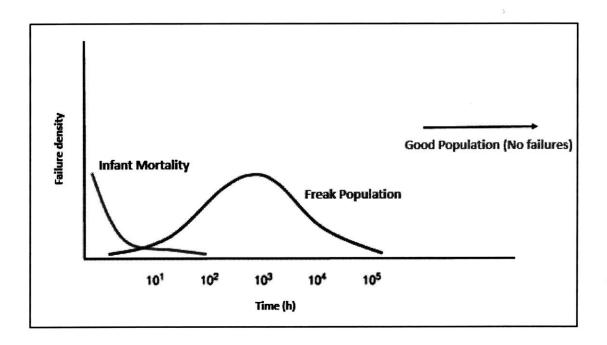

Unlike most non-electronic equipment, the electronic components' reliability is often difficult to be tested and verified since most of the time they are already encapsulated after production. In most of the cases, the PCBs are conformed to specification and are identified as good and can last throughout the life of the equipment. Secondly, the one that are defective will fail and be caught up when first tested under ICT or FCT and will be either fixed or removed, which therefore do not cause equipment failures. However, the culprit that is causing warranty cost are those that do not immediately fail during the traditional testing that will affect performance and result in the decrease of reliability. For example, a weak soldering point, silicon, oxide and conductor imperfections, impurities, inclusions and non-hermetic packages. These components are called "freaks". [10]

"Consider a typical failure mechanism in an electronic component: a weak mechanical bond of a lead-in conductor to the conducting material of the device. This may be the case in a resistor, a capacitor, a transistor or an IC. Such a device might function satisfactorily on test after manufacture and in all functional tests when built into a system. No practical inspection method will detect the flaw. However, because the bond is defective it may fail at some later time, due to mechanical stress or overheating due to a high current density at the bond. Several other failure mechanisms lead to this sort of effect, for example, flaws in semiconductor material and defective hermetic sealing. Similar types of failure occur in non-electronic systems, but generally they do not predominate.

The typical 'electronic' failure mechanism is a wear out or stress induced failure of a defective item. In this context, 'good' components do not fail, since the application of specified loads during the anticipated life will not lead to failure. While every defective item will have a unique life characteristic, depending upon the nature of the defect and the load(s) applied, it is possible to generalize about the nature of the failure distributions of electronic components. Taking the case of the defective bond, its time to failure is likely to be affected by the voltage applied across it, the ambient temperature around the device and mechanical loading, for example, vibration. Other failure mechanisms, say a flaw in a silicon crystal, may be accelerated mainly by temperature variations. Defects in devices can result in high localized current densities, leading to failure when

the critical value for a defective device is exceeded.

Of course, by no means all electronic system unreliability is due to defective components. Interconnects such as solder joints and wire bonds can be reliability 'weak links' especially in harsh environment applications (automotive, avionics, military, oil drilling, etc.). [10]

Figure 4: - Life Cycle of electronic components in the absence of burn-in test [10]

"Figure 4 shows the three categories of component that can be manufactured in a typical process. Most are 'good', and are produced to specification. These should not fail during the life of the equipment. Some are initially defective and fail when first tested, and are removed. They, therefore do not cause equipment failures. However, a proportion might be defective but nevertheless, pass the tests. The defects will be potential causes of failure at some future time. Typical defects of this type are weak wire bond connections, silicon, oxide and conductor imperfections, impurities, inclusions and non-hermetic packages. These components are called "freaks." [11]

#### 2.5 Reliability of PCBs at Waters

The Reliability engineering and Testing engineering Group at Waters are facing problems in identifying root causes of on field failure, especially for printed circuit boards (PCBs) that fail in the field but passes functional and ICT tests when brought back for testing. Although there were efforts in conducting the HALT procedure, resource issues and opposition from R&D Group in testing beyond products specifications results in a delayed implementation of HALT procedure. These issues resulted in an inconsistent screening process using the HALT chamber and inaccurate data collection process. The team also consulted reliability engineers in the group and found in consistencies in the way the current proposed HALT procedure is conducted as compared to industry practices. Although the HALT chamber has been around for more than 5 years, the inefficient use of the resource meant loss of potential savings [12] from a ruggedized product and depreciation of idle inventories that can otherwise turn into profit.

### Chapter 3 – Literature Review

#### 3.1 Introduction to Highly accelerated life test (HALT)

HALT is conducted to stimulate and replicate as many failure modes as possible to locate the design weaknesses in the early stage of product design and development process so as to improve the overall robustness of the product. As mentioned in chapter 2, many of the electronics flaw might be latent and cannot be detected via the traditional testing method like ICT (In-circuit testing) and FCT (functional testing). Unlike traditional environmental stress screening (ESS), HALT utilizes a series of thermal and vibrational steps to expose the intermittent failures or latent defects within a shorter period of time. After HALT process, the early failure rate could be reduced significantly and the product will become more mature and therefore not only the failures rate in the field will be reduced significantly but also the variation in quality will also be reduced.

#### 3.2 HALT Profiles

The HALT profiles can be categorized into two different sections, the temperature stressing and vibration stressing. Before proceeding to the discussion of the detailed profiles, some of the key matrix of measurement are explained and defined as the following:

- Lower operating limit (LOL): During the cold temperature stressing step, the system or

equipment might output an abnormality at this certain temperature but when returning back to

room temperature, the system should be able to go back to normal without the need of repairing.

It usually occurred because there is an intermittent failure, or the so-called soft failures.

- Lower destructive limit (LDL): Similar concept to LOL, but at this temperature, the system will not go back normal if simply returning back to room temperature. Some degrees of repair or replacement of components might be required. It is usually called the hard failure.

- Upper Operating Limit (UOL): During the hot temperature stressing step, the system or equipment might output an abnormality or not be functioning properly as it is intended to be

at this certain temperature. But when returning back to room temperature, the system will be able to go back to normal without the need of repairing. It usually occurred because of an intermittent failure, or the so-called soft failures.

- Upper Destruct Limit (UDL): Similar concept to UOL, but at this temperature, the system will not go back normal if simply returning back to room temperature. Some degrees of repair or replacement of components might be required. It is usually related to hard failure.

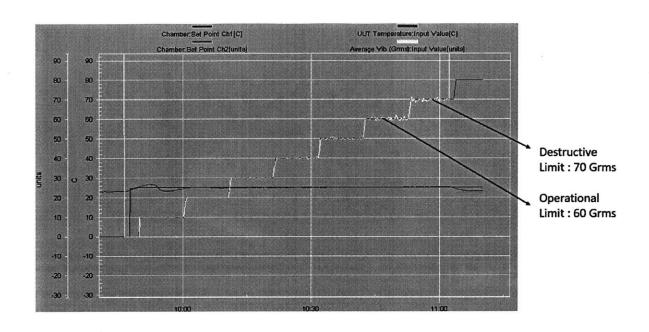

- Vibration Operating Limit (VOL): The point at which the product stops operating or a specification is no longer being met, but returns to normal after the vibration level is decreased.

- Vibration Destruct Limit (VDL): The point after which the product does not return the vibration level is decreased below the operating limit.

#### 3.2.1 Temperature Homogeneity

The temperature homogeneity test should be conducted in the beginning of the HALT to make sure that the ducting positions in the chamber are optimized and there is maximum airflow across the products so as to obtain the best thermal response. The actual product temperature was measured by several thermal couples across the boards and compared with and the chamber setpoint to adjust the air duct position in the chamber so as to maximize thermal energy transfer and uniformity on the board. [13]

#### 3.2.2 Cold Step Stress

During the cold step stress the temperature is lowered in increments less than or equal to 20°C. The test should be started at ambient temperature (which can be defined anywhere between 20°C and 30°C) and the dwell time on each temperature is a minimum of ten minutes or as determined by the temperature homogeneity step. The loading is continued until either the operational limit (OL) of the sample is determined or the chamber maximum is achieved. If the OL can be

determined, the test process should continue to the destruct limit (DL) or chamber maximum. However, since the sample will most likely not be operational beyond its OL, it will become necessary to return to a lower temperature (i.e. below the OL) after each additional dwell to determine whether the sample is still operational. It has been reported that cold temperature step is the least detrimental one and therefore was performed first. When irregularities and abnormalities occur, the temperature is then returned back to either the previous level or room temperature and functional test was conducted again to see whether it will go back to normal. If it will, then an LOL has been identified. However, if even after returning to room temperature and the equipment still will not work, then a LDL has been identified.

#### 3.2.3 Hot Step Stress

The hot step basically follows the same logic as the cold step stress. The hot step stressing will also begin at room temperature, and the temperature will be increased about 10~20°C per step until the UOL and UDL are identified.

#### 3.2.4 Thermal Cycling

Thermal cycle tests have been designed to simulate the thermal excursions experienced in regular operating conditions. The tests are conducted at wider temperature ranges and higher frequencies to induce failures in much shorter duration than in field use while still under the assumption that failure modes are identical to the ones observed in field use. The actual test process is straightforward: the test specimens are continuously exposed to alternating high- and low temperature extremes. The tests are typically conducted until a predetermined number of cycles are reached or a failure is detected. The test parameters are temperature range (maximum [Tmax] and minimum [Tmin] temperature), dwell time (time spent at both Tmax and Tmin) and ramptime (how fast the temperature changes from Tmax to Tmin and from Tmin to Tmax). The tests are conducted in specially designed environmental test chambers, which are typically equipped with one, two or three zones. In one zone configuration the specimens are heated and cooled in one chamber according to test specifications. Two zone configuration features hot and cold zones,

which can be controlled independently and a product carrier to move the test specimen between the zones. Three zone configuration utilizes a third, ambient zone between the hot and cold zones to enable a more constant change of temperature than in two zone chambers. Regardless of the configuration, the chambers are typically air filled and heating and cooling is achieved by convection. Typically the thermal cycling phase consists of a minimum of five thermal cycles (performed at the maximum attainable rate of change) that shall be performed unless a destructive failure is encountered prior to completion. The minimum thermal cycle temperature range should be within 10°C of both the lower and upper thermal operating limits as discovered during the temperature step stress phase. The minimum dwell time is ten minutes following stabilization of the sample at the set point as determined by the sample thermocouple response. The dwell time is increased to allow higher mass components to reach at least 80 percent of the thermal range. [14]

#### 3.2.5 Vibration

Vibration is one of the most important loading conditions in electronic components especially PCBs. The life cycle of electronic components includes vibration loading at different phases such as during transportation, handling, captive carry flight and free flight. Dynamic analysis of PCBs under vibration loading can be performed by three different approaches (i) analytical methods, (ii) finite element analyses and (iii) experimental studies. However, common practices in the industry is to employ experimental studies using a shaker. The trend is due to the complexity of today's electronic assemblies. The sophisticated structure of PCBs makes analytical modeling and Finite Elemental Analysis difficult and sometimes impossible. HALT has emerged as a promising method to improve the reliability of complex PCBs and includes vibration testing. [15]

#### 3.2.5.1 Failure of PCBs from Vibration

Excessive deformations and accelerations of PCBs results in damage to mounted components, solder joints and electrical interfaces, as well as the circuit board itself.

## Failure Mechanism due to vibration can be specified as follows

- Lead wire fatigue failure (see example shown in Figure 5)

- Connector contact fretting corrosion

- Structural fatigue failure

- Solder joint fatigue failure (see example shown in Figure 6)

- Excessive deflection

- · Loose hardware

Figure 5- Ruptured Lead Wires due to Fatigue [16]

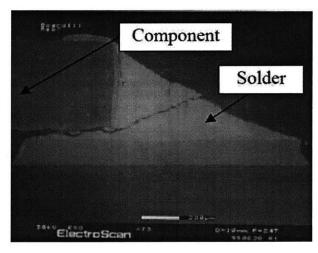

Figure 6- Solder joint fatigue failure [17]

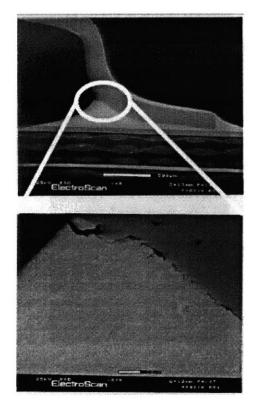

Soldering is inevitable during mounting processes of electronic components over printed circuit boards. High solder reliability is required since failures of solder joints and lead wires directly result in failure of systems. Main failure mode of solder joints under vibration loading is fatigue failure. High cycle fatigue causes crack growth in solder joints (Figure 7) and excessive stresses in lead wires.

Figure 7- Solder joint crack initiation [17]

#### 3.2.5.2 Random Vibration HALT

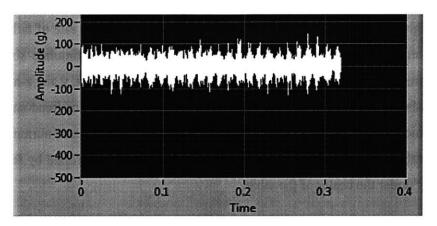

Random Vibration is measured in gravity root mean squared (G<sub>rms</sub>), the square root of the area under the acceleration spectral density (ASD) curve in the frequency or time domain. The acceleration spectral density curve can be obtained using an accelerometer. A typical real-time signal from an accelerometer mounted on a HALT table is shown in figure 8. The root mean square (rms) value of this signal can be calculated by squaring the magnitude of the signal at every point,

finding the average (mean) value of the squared magnitude, then taking the square root of the average value. The resulting number is the  $G_{rms}$  metric.

Figure 8- Acceleration vs Time graph as obtained from an accelerometer

The ASD or power spectral density (PSD) bandwidth in a HALT vibration system can extend from 20 Hz to 10 kHz. Unlike an electrodynamic shaker, the shape or frequency spectrum of the ASD input produced cannot be directly controlled in a typical multi-axis HALT vibration chamber, only its level of intensity can be expressed in G<sub>rms</sub>.

#### 3.2.5.3 HALT vibration chamber

Figure 9- HALT Chamber

The HALT chamber (Figure 9) uses pneumatic hammers to induce vibration. It is also referred to as repetitive shock (RS) system. HALT chambers provide multi-directional high pulse shock peaks that can be as high as ±10 sigma peak accelerations resulting in a higher rate of fatigue damage. These systems are multiple axis systems which can simultaneously stimulate six degrees of freedom, with three along the x, y and z-axes, and three rotational about x, y and z-axes. Because of this, HALT vibration is sometimes referred to as 6 DOF (six degrees of freedom). Generally, RS vibration in most HALT systems is highest in the z-axis, which is the axis normal to the plane of the vibration table. The vibration level in RS systems is typically controlled by feedback from an accelerometer under the center of the table.

#### 3.2.5.4 HALT vibration Profile

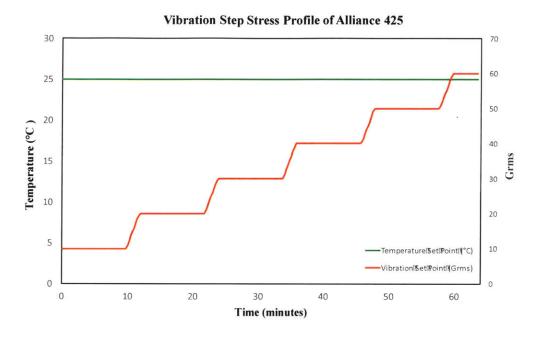

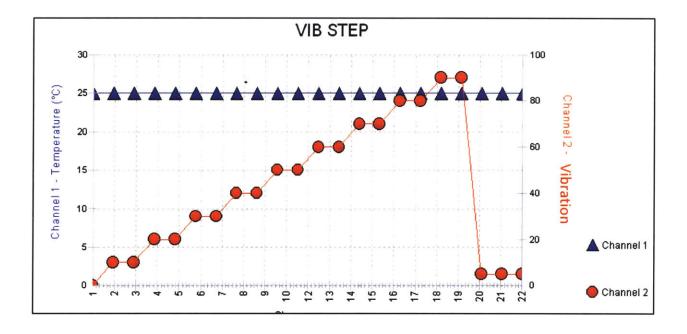

The HALT methodology involves inducing vibration loading in a stepped manner. Hence the HALT vibration testing is also called Vibration step stress. The vibration step stress profile consists of two parts – ramp and soak (dwell). The Vibration step stress test begins at a chamber set point of 5 to 10 G<sub>rms</sub> (or lowest stable chamber control set point), as measured over a 2 Hz to 10,000 Hz or greater bandwidth and is then increased (ramped) in 5 to 10 G<sub>rms</sub> increments (5 G<sub>rms</sub> recommended) upon completion of the soak (dwell) period and subsequent functional test. The minimum dwell time is ten minutes, with functional testing performed at the very least at the conclusion of the dwell. In the same way as in temperature step stress, the loading is increased until either the operational and destruction limits of the sample are determined or the chamber maximum is achieved. Figure 10 represents a typical vibration step stress profile.

Figure 10- HALT Vibration Profile

### 3.2.4 Combined Vibration and Temperature

The last step in ruggedizing a product during HALT is to combine all the stresses that were previously used. In this step, the product is basically subjected to the combination of the vibration and thermal cycling profiles. According to McLean [16] in sum, there should be five thermal cycles in conjunction with vibration and other stresses like power cycling, or humidity. For temperature, we will use the same profile that was used during rapid thermal transitions or to within 10°C of the thermal operating limits. For vibration, each step will be equal to the step stress operating limit divided by five. For example if we achieve a vibration operating limit of 50 G<sub>rms</sub>, each thermal cycle will have a vibration dwell of a multiple of 10 G<sub>rms</sub> for 15 minutes. The combination of thermal cycling and vibration stepping was found to be important because the vibration response of many products might change as the temperature varied. Cross-over effect might also take place and stimulate more otherwise cannot-be-seen failure modes. A new set of operating limit and destructive limit might be determined for this combined environment stimulus. [13]

#### 3.2.5 Failure Analysis and Corrective Actions

After identifying the operating limit or destructive limit in each of the aforementioned steps, failure analysis was conducted and the root-cause must be investigated and fixed whenever possible in order to keep going up to expose higher level of failures. If modifications could not be made because the failure was not easily correctable, the sensitive areas could be kept at a lower stress level than the rest of the product by for example, using thermal barrier material and epoxy to reduce the temperature and vibration response, respectively. In HALT, most of the failures could be fixed at low to no cost because they might simply be due to incorrect component or materials selection and design flows. [13] [16]

#### 3.2.6 Benefits of HALT

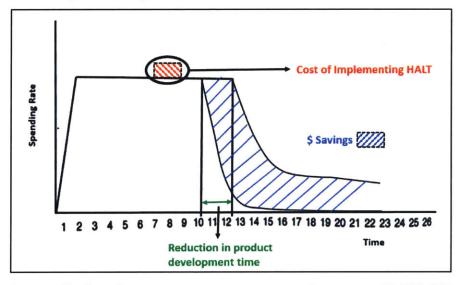

The benefits from increased product reliability during pre-production provides indirect cost savings by freeing up resources and competitive advantages. For instance, R&D engineers could focus on developing the next product instead of executing rework and design adjustments to an existing one. Figure 11 aptly illustrates cost savings in the long run and reduction in failure rates respectively. Figure 11 shows a step increase in spending rate in periods 7-9 because of HALT testing but products could be launched earlier and at lower costs because of the ability to have economies of scale much quickly due to the confidence of robust products. Long term savings is illustrated by shaded regions after period 10.

Figure 11: Spending rate against time: cost reductions on HALT [12]

# Chapter 4 - Preparation of Standard Operating Procedure

### 4.1 Overview - The Methodology

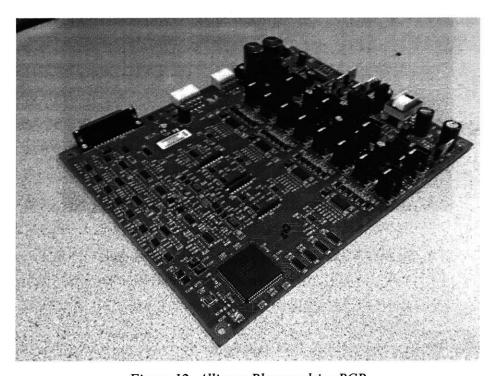

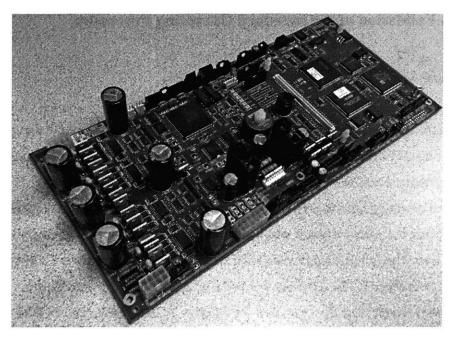

The basic approach towards establishing a HALT standard operating procedure for reliability testing of PCBs was to work with a very robust board and create a standard operating procedure that will serve as a benchmark for screening other PCBs. Waters uses over 200 different kinds of PCB boards in its various line of products. The robustness of the PCB board was characterized by analyzing the field failure data of various PCB boards. The aim was to find a board which has an extremely low failure rate (less than 1%). The board identified for creating the standard operating procedure was the plunger drive board 210000425 (figure 13) used in Waters Alliance equipment (figure 15). The field failure data for the Alliance depicts that the failure rate of the PCB is around 0.1%. In the subsequent chapters, this board will be referred to as the 'Alliance PCB'.

Figure 12- Alliance Plunger drive PCB

### 4.2 Functional Testing of the Alliance board

An important part of HALT is to establish the operating and destructive limits of the PCB with respect to both temperature and vibration and to do so it is imperative to know when i.e. at what stage during the HALT step did the PCB fail operationally and destructively. Hence it becomes very important to monitor the vitals of the equipment continuously during the entire HALT procedure. This is done by conducting functional tests – that monitor the performance and the functionality of the PCB.

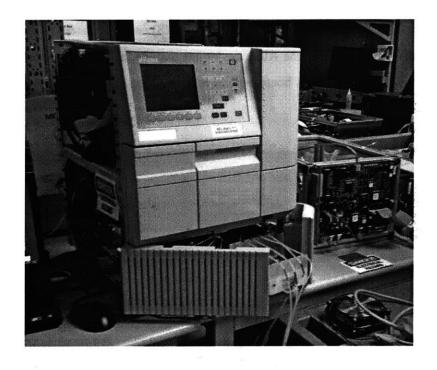

Figure 13- The Waters Alliance Separations module.

In the case of the Alliance Plunger drive PCB, this is done by connecting it using extended cables to its parent equipment which in this case is the Waters Alliance e2695 separations module (figure 15) and monitoring the essential functions controlled by the PCB through a Hyperterminal

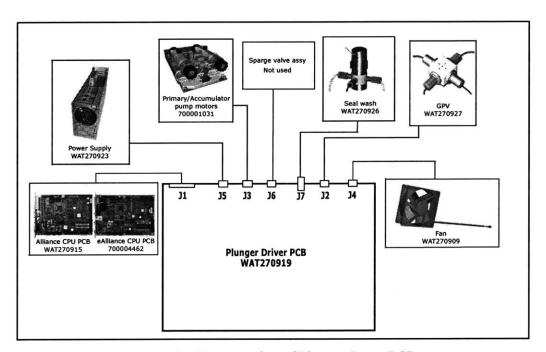

software. The main function of the Alliance PCB is to provide the drive electronics for controlling the following (figure 16)

- a two-step motor Pump (Primary and Accumulator)

- a four solvent Gradient Proportioning Valve

- a Plunger Seal Wash solenoid

- four Sparge Valves to provide Helium Sparging

- to provide Power to a 24 VDC Fan along with detecting Fan Failure by monitoring a Fan Tachometer signal.

The Pump Driver PCB Opto-Isolates all input and output control signals from the host. On board intelligence is provided in logic and state machines within the PLD. The Pump Driver PCB requires three power supplies with their grounds tied at the power supply. The required voltages are +24 VDC, +5 VDC (VCC) and an analog +5 VDC.

# 4.2.1 Functional theory of operation

Figure 14- Functionality of Plunger Drive PCB.

### 4.2.1.1 The pump, primary and accumulator motors

The Pump Driver PCB provides a micro-step drive to both the Primary and Accumulator step motors. Inherent in a micro-step drive are two phases being driven, one with a sine current wave form and the other with a cosine wave form. Change of direction is accomplished by inverting either the sine or cosine. The micro-step resolution is determined by the sine and cosine values sent. For example the full period (360 electrical degrees) of the sine and cosine represents four full motor steps, if you were to divide the 90 degrees (1 full step) by 10 and send the sine and cosine current values for every 9 degrees you would be executing a 1/10 micro-step. This is what is currently implemented in the 2690 and 690 products. However where the sine and cosine generation is done by the host, then any micro-step resolution may be performed within the bandwidth of data transmission. The other component of the sine and cosine is the current amplitude which is proportional to torque produced by the motor. With the current gain of the current sense circuit the maximum current amplitude is 4.13 amperes

### 4.2.1.2 The Gradient Proportional Valve (4)

There are two modes of operation on the GPV drive, Slam Mode used to open the GPV valve and Hold Mode used to hold the valve open. All four valves are normally closed with no power applied. The four solvent select signals which come from the host CPU go directly to four N channel FETS for each respective GPV valve A, B, C OR D. These signals also go to the PLD which contains logic to determine the proper time to slam or hold the valves. Slam is defined by applying 24 VDC to the selected valve until the current through it reaches 340 ma then the 24 VDC is removed and 5 VDC is applied in its place to hold it open. Therefore slam and hold modes are determined by which P channel FET is activated. This in turn determines what supply voltage is applied to top of the valve coils, +24 VDC or +5 VDC. There are two comparators that monitor current through the selected valve by measuring the voltage drop across a resistence. SLAMED is low when the valve current has reached 340 ma, while GPVFAIL is low only if the control logic has failed or the valve coil is shorted and the current is greater than 450 ma. The host or CPU commanding this board has

the responsibility of ensuring that only one GPV valve is commanded at a time and if GPVFAIL is low then any GPV actuation must be removed.

### 4.2.1.3 Plunger seal wash drive

The Plunger Seal Wash Drive utilizes two channels of an octal Darlington transistor Array driver chip. The activation signal SEAL\_WASH\_ON comes directly from the host CPU. The Darlington transistors close the circuit to the Seal Wash solenoid and the +24 VDC supply which activates the solenoid.

### 4.2.1.4 Four sparge valve drives

The Sparge Valve Drive uses four channels of an Octal Darlington Transistor Array driver chip. Each channel drives one Sparge Valve. The activation signals are SPARGE\_A, SPARGE\_B, SPARGE\_C and SPARGE\_D which come directly from the host CPU. The four valves are totally independent and may be selected in any combination. The Darlington transistors close the circuit to the Sparge Valve and the +24 VDC supply through a 300 OHM resistor which drops 12 volts. The Sparge Valves are 12 volt coils which are normally closed when no power is applied.

#### 4.2.1.5 Fan

The Fan has a tachometer output which is simply an open collector transistor which is capable of sinking 100 ma maximum. A normally operating fan emits a clock of 100 HZ. Should the fan slow down to less than 65 % (65 HZ) of its' normal speed or lock up, then a failure will be initiated. The failure signal returned to the host CPU is MTR\_FAIL high. This is a multiplexed signal which is used to identify one of three failures, Fan Fail, Primary Motor Failure or Accumulator Motor Failure. The host CPU should try to run thorough its failure diagnostics to determine which failure has occurred.

# 4.2.2 Failure Diagnostics using HyperTerminal software

There are two signals returned to the host CPU that identify failures, the first is GPV\_FAIL and the second is MTR FAIL.

#### 4.2.2.1 GPV failure

GPV\_FAIL is low when the current through one of the four GPV valves has exceeded 450 ma. This could happen if the control logic is not operational or if there is a short across the coil. If the signal GPV\_FAIL goes low the host CPU must remove any commanded GPV valve signals, SOL\_SELA, SOL\_SELB, SOL\_SELC or SOL\_SELD. Once the command signal is removed then the fail signal GPV\_FAIL should go inactive (High). If it doesn't this is a hard failure in the electronics. To determine if the control logic is at fault (all four valves not operating) or if a single valve is defective, the following diagnostic procedure may be implemented. If removing the commanded signal the failure signal GPV\_FAIL went high then the host CPU may activate each of the four GPV Valves, A, B, C or D one at a time. If only one of the valves causes GPV\_FAIL to go low then there is one shorted valve, however if more than one valve causes GPV\_FAIL to go low then a control logic problem may be assumed.

# 4.2.2.1 Primary motor, accumulator motor or fan failure

MTR\_FAIL is a high active signal that is multiplexed to represent three different failures, Primary Motor Fail, Accumulator Motor Fail or Fan Fail. If the Pump driver develops a motor drive problem (EX: shorted FET) on either the Primary or Accumulator Motor Drive then both motor drive circuits will be disabled. The host CPU detects this via encoder that the motors are no longer moving and MTR\_FAIL should be high. Because the motors stopped, this is known to be either a Primary or Accumulator Motor Failure, thus the Fan Fail has been ruled out because a Fan Fail doesn't stop the motors. Of course, if we have a dual failure all bets are off determining the failure status.

The motors stopping says we have a motor failure. The following diagnostic procedure may be used to determine which motor has actually failed. The signal from the host CPU MTR\_PWR should have been high if the motors were moving when the failure occurred. The Pump Driver PCB has taken control and disabled the motors. The pump Driver PCB PLD will give control of the motor which didn't fail to the host CPU after the host CPU toggles from high to low back to high the signal MTR\_PWR. Next the host CPU tries to move both motors the one that moves is fine and the other which doesn't move caused the failure. If neither moves then you can assume both failed. To determine a Fan Failure is simple, if you get MTR\_FAIL high and both motors are operational then a Fan Failure has occurred. In the case of a Fan Failure, the motors shouldn't be run and MTR\_PWR should be brought low, inactive.

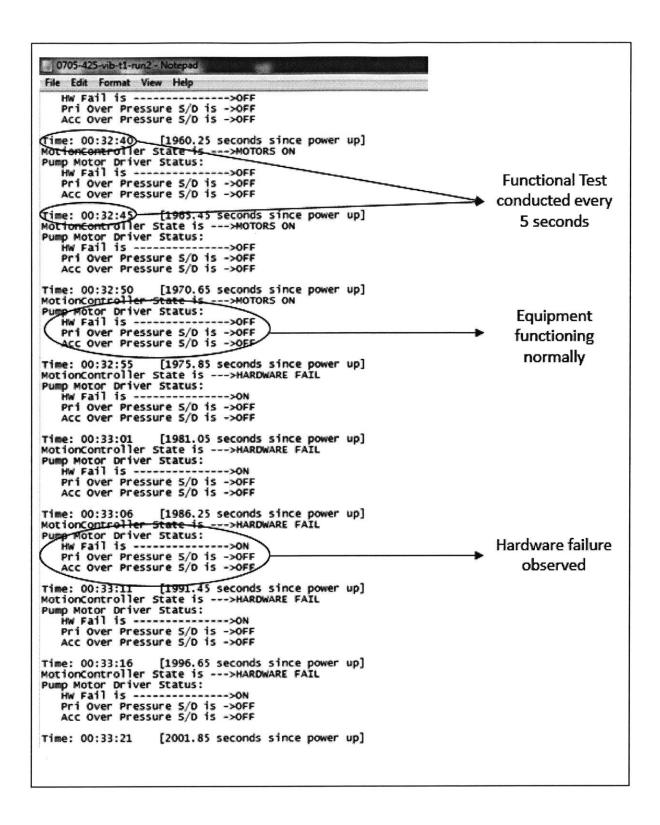

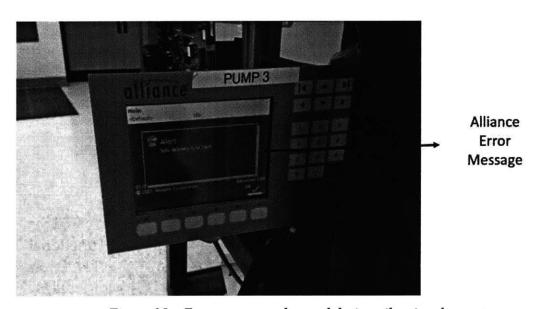

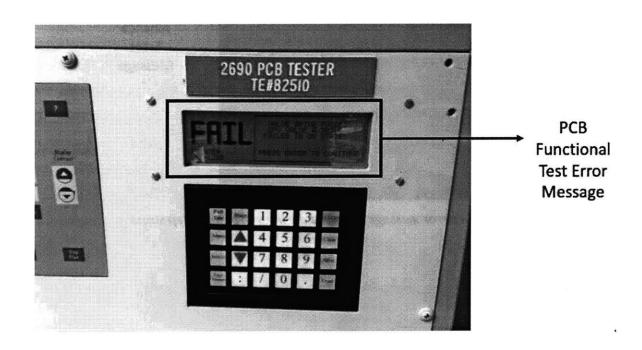

The diagnostics are run continuously throughout the entire HALT testing via hyper-terminal, connected using the serial communication port (RS232). The commands are sent from computer through the HyperTerminal continuously to the CPU board to activate the signal on plunger drive board. The Operational Limit was determined once the hyper-terminal communication outputs the sign "hardware failure" or if any specific functionality can no longer be activated. Figure 17 shows the screenshot of the hyper terminal software while it was performing the functional test.

Figure 15- HyperTerminal functional test output

# 4.3 Data Acquisition and Equipment Used

In order to execute the HALT process accurately, the following equipments were used in different settings so as to measure and optimize the product response.

# 4.3.1 Temperature Measurement

Within the HALT chamber, there are two thermal couples, one is in the shape of a cylindrical steel bar and it measures the process temperature, while the other measures the Device Under Test (DUT) temperature. For more details on the Temperature measurement setup refer to thesis by Chang [1]

#### 4.3.2 Vibration Response Measurement

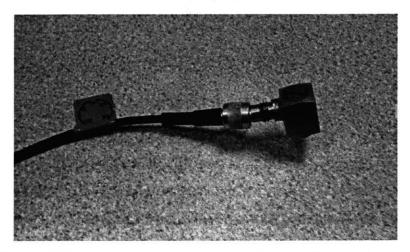

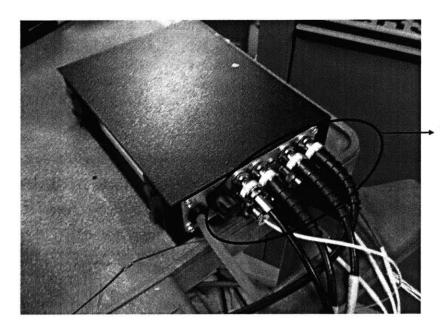

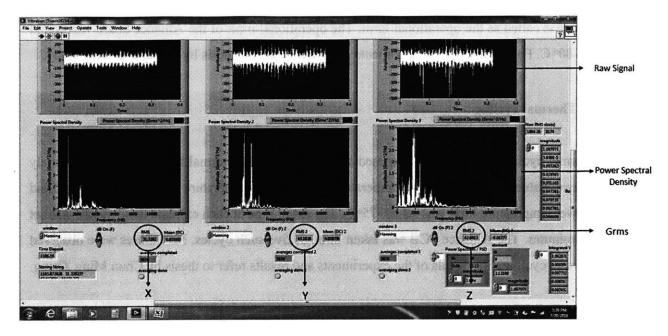

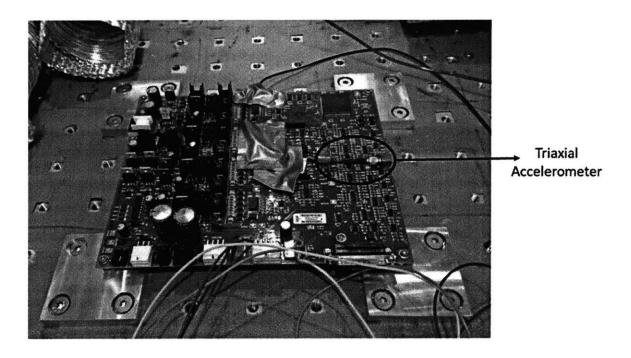

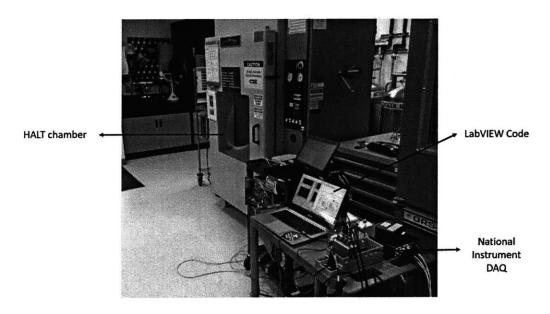

A triaxial accelerometer (Figure 18) was used to monitor the vibrational response of the fixture and also the vibrational response at various locations on the PCB (when mounted on the fixture). The signal from the accelerometer was processed by a DAQ (Data Acquisition) device (figure 19). The DAQ was connected to a National Instruments device (figure 20) to output the vibration levels in X, Y and Z direction on a computer through a LABVIEW code (figure 21).

Figure 16- The triaxial accelerometer used for monitoring vibration.

3 wires (X, Y & Z) from the tri-axial accelerometer connect to the DAQ

Figure 17- Data acquisition device.

3 wires (X, Y & Z) from the DAQ connect to the National Instrument DAQ

Figure 18- National Instruments DAQ.

Figure 19: LabVIEW output that measures vibration in X, Y & Z directions

# 4.4 Experimental Step and Analysis

In each experimental step, the operating limit and the destructive limit was identified.

# 4.4.1 Hot Step Stress

The hot step stress involved taking the Alliance PCB to extremely high temperatures in a stepped manner till operational failure was observed. The temperature at which the operational failure is observed is called as the operational limit. The operational limit of the Alliance board was found to be 140° C. For details of the experiments and results refer to thesis by Chun Ming Chang [1].

# 4.4.2 Cold Step Stress

The cold step stress involved taking the Alliance PCB to extremely low temperatures in a stepped manner till operational failure was observed. The temperature at which the operational failure was

observed is called as the operational limit. The operational limit of the Alliance board was found to be -80° C. For details of the experiments and results refer to thesis by Chun Ming Chang [1].

#### 4.4.3 Thermal cycling

In thermal cycling, the PCB was exposed to a series of rapid thermal transition from extremely high temperature to extremely low temperatures. The upper temperature limit was set as 75° C and the lower temperature limit was set as -75° C. The dwell time at each extreme temperature was set as 15 minutes. The Alliance PCB was taken through five such cycles. No failures were observed in thermal cycling. For details of the experiments and results refer to thesis by Chun Ming Zhang.

#### 4.4.5 Vibration

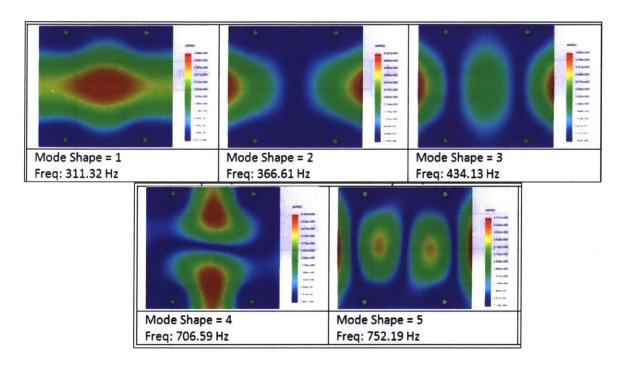

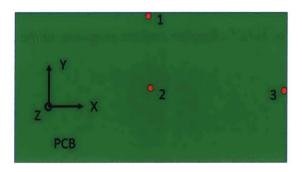

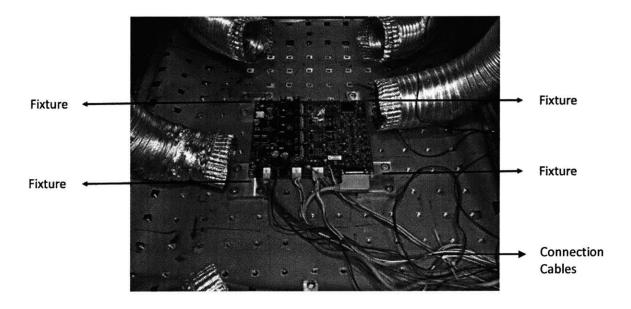

#### 4.4.5.1 Vibration Fixture