## Electrically Active Defects in Zinc Oxide

by

Thomas D. Chen

B.A., Physics University of California, Berkeley (1993)

Submitted to the Department of Materials Science and Engineering in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Materials Science and Engineering at the

Massachusetts Institute of Technology

June 1996

© 1996 Massachusetts Institute of Technology All Rights Reserved

| Signature of Author |                                                                    |

|---------------------|--------------------------------------------------------------------|

| _                   | Department of Materials Science and Engineering                    |

|                     | May 10, 1996                                                       |

| Certified by        |                                                                    |

|                     | Harry L. Tuller                                                    |

| Sumitor             | Electric Industries Professor of Ceramics and Electronic Materials |

| ,                   | Thesis Advisor                                                     |

| Accepted by         | -                                                                  |

| 1 /                 | Michael F. Rubner                                                  |

|                     | TDK Professor of Materials Science and Engineering                 |

|                     | Chair. Departmental Committee on Graduate Students                 |

MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

ARCHIVES

JUN 24 1996

#### Electrically Active Defects in Zinc Oxide

by

#### Thomas D. Chen

Submitted to the Department of Materials Science and Engineering on May 10, 1996 in partial fulfillment of the requirements for the degree of Master of Science in Electronic Materials

#### **Abstract**

Electrically active defects in semiconducting zinc oxide were studied in bulk single crystal form or in single crystal thick films deposited on r-plane sapphire. Electrically active defects in zinc oxide have been identified to be important factors in the description of the varistor grain boundary effect found in doped polycrystalline ceramics of zinc oxide. The goal of the study was to acquire information that would shed light on the nature of bulk defects as a function of heat treatment and doping. Bulk samples were purchased from a commercial supplier; thick film samples were fabricated using a vapor transport reactor which will have later use in zinc oxide bicrystal fabrication for single grain boundary studies of the varistor effect. Schottky contacts were fabricated on polished surfaces of zinc oxide, and the electrically active defects were evaluated with deep level transient spectroscopy (DLTS). The samples examined were either nominally undoped or, on the other hand, doped with cobalt, a relevant dopant used in commercial zinc oxide varistors. Heat treatments consisted of anneals in oxygen partial pressures of 1 atm and  $10^{-4}$  atm at  $1000^{\circ}$ C.

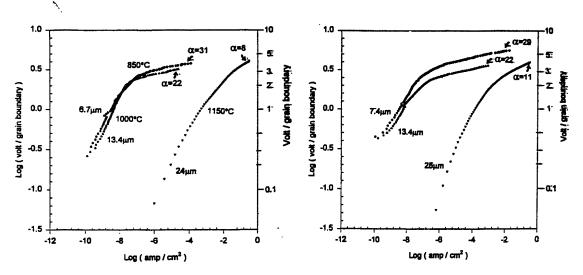

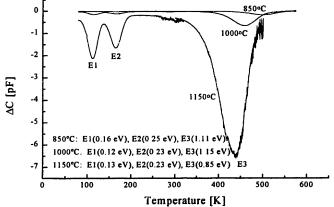

Simplified varistor systems of polycrystalline bismuth- and cobalt-doped zinc oxide were also studied. The goal of this research was to evaluate electrically active defects in an actual varistor system and perhaps correlate the findings to those on bulk samples. Furthermore, a previous study has shown that the distributions of bismuth segregation at the grain boundaries in such samples can be controlled by varying microstructure and heat treatment. Current-voltage and deep level transient spectroscopy measurements were done to evaluate the corresponding electrical and defect properties. Low leakage and  $\alpha$  values of  $\sim 30$  were attained, despite the nominal, two-component doping of these simplified varistors. Moreover, by using DLTS these samples show the signature defects that are found in many multi-dopant, commercial devices: two shallow bulk traps at  $\sim 0.14$  eV and  $\sim 0.24$  eV and one prominent interfacial trap at  $\sim 1$  eV.

Thesis Advisor: Dr. Harry L. Tuller

Title: Sumitomo Electric Industries Professor of Ceramics and Electronic Materials

## **Table of Contents**

| ABSTRACT                                                           | 2  |

|--------------------------------------------------------------------|----|

| TABLE OF CONTENTS                                                  | 3  |

| LIST OF ILLUSTRATIONS AND FIGURES                                  | 5  |

| LIST OF TABLES                                                     | 8  |

| ACKNOWLEDGMENTS                                                    | 9  |

| 1. INTRODUCTION                                                    | 10 |

| 1.1 GOALS OF THE THESIS                                            | 10 |

| 1.2 Organization of the Thesis                                     | 11 |

| 2. BACKGROUND                                                      | 12 |

| 2.1 ZNO VARISTOR FUNDAMENTAL ELECTRICAL PROPERTIES                 | 12 |

| 2.2 ZINC OXIDE SEMICONDUCTOR JUNCTIONS                             | 14 |

| 2.2.1 The Metal-Semiconductor (Schottky) Junction                  | 14 |

| 2.2.2 The Double Schottky Barrier Model for Grain Boundaries       | 16 |

| 2.3 DEEP LEVELS AT THE GRAIN BOUNDARIES                            | 18 |

| 2.3.1 Previous Studies Using DLTS on ZnO Grain Boundaries          | 19 |

| 2.4 GRAIN BOUNDARY SIMPLIFICATION: GEOMETRY AND CHEMISTRY          | 21 |

| 2.5 VAPOR PHASE GROWTH OF ZINC OXIDE                               | 23 |

| 2.5.1 Thermodynamics of Vapor Transport                            | 24 |

| 2.5.2 Literature Review of Vapor Phase Growth of Zinc Oxide        | 25 |

| 3. DLTS MEASUREMENT TECHNIQUE                                      | 29 |

| 3.1 REVIEW OF FUNDAMENTAL THEORY BEHIND DLTS                       | 29 |

| 3.1.1 Junction Capacitance                                         | 31 |

| 3.1.2 The DLTS Transient Signal                                    | 31 |

| 3.1.3 The DLTS Rate Window                                         | 33 |

| 3.2 APPLICATION OF DLTS TO GRAIN BOUNDARY JUNCTIONS                | 35 |

| 3.2.1 Zero Quiescent Bias Case                                     | 35 |

| 3.2.2 Negative Quiescent Bias Case                                 | 37 |

| 3.3 A-B TECHNIQUE: SIMULATED BOX-CAR METHOD WITH LOCK-IN AMPLIFIER | 38 |

| 3.3.1 In-phase and Quadrature Channels of the Lock-in Amplifier                                                | 39      |

|----------------------------------------------------------------------------------------------------------------|---------|

| 3.3.2 Rate Window Determination with the A-B Technique                                                         | 40      |

| 3.4 FOURIER LOCK-IN AMPLIFIER METHOD                                                                           | 42      |

| 4. EXPERIMENTAL APPROACH                                                                                       | 46      |

| 5. TRAPS IN ZINC OXIDE BULK CRYSTAL AND THICK FILMS                                                            | 47      |

| 5.1 EQUIPMENT DESCRIPTION AND GROWTH CONDITIONS FOR THICK FILMS                                                | 47      |

| 5.2 POLISHING AND METAL DEPOSITION FOR SCHOTTKY BARRIERS                                                       | 49      |

| 5.3 MEASUREMENT RESULTS                                                                                        | 50      |

| 5.3.1 Undoped Bulk Zinc Oxide Crystal (2 days at 1000 $^{\circ}$ C under 10 <sup>-4</sup> atm O <sub>2</sub> ) | 50      |

| 5.3.2 Undoped Bulk Zinc Oxide Crystal (2 days at 1000 °C under 1 atm O2)                                       | 52      |

| 5.3.3 Cobalt-Doped Zinc Oxide Crystal (5 days at 1000 °C under $10^{-4}$ atm $O_2$ )                           | 54      |

| 5.3.4 Undoped Bulk Zinc Oxide Film (as-grown)                                                                  | 56      |

| 6. SIMPLIFIED ZINC OXIDE VARISTORS                                                                             | 59      |

| 6.1 SAMPLE DESCRIPTION                                                                                         | 59      |

| 6.2 DC ELECTRICAL AND DLTS MEASUREMENT RESULTS                                                                 | 60      |

| 7. DISCUSSION                                                                                                  | 63      |

| 7.1 DEFECT LEVELS: DLTS MEASUREMENTS                                                                           | 63      |

| 7.1.1 Junction Quality: Current-Voltage Measurements                                                           | 64      |

| 7.1.2 Carrier Concentration: Capacitance-Voltage Measurements                                                  | 66      |

| 7.2 COMPARISON OF SINGLE AND POLYCRYSTAL MEASURED DEFECT LEVELS                                                | 67      |

| 8. SUMMARY                                                                                                     | 69      |

| 9. FUTURE WORK ERROR! BOOKMARK NOT D                                                                           | EFINED. |

| APPENDIX A: FOURIER ANALYSIS OF EXPONENTIAL TRANSIENT                                                          | 70      |

# List of Illustrations and Figures

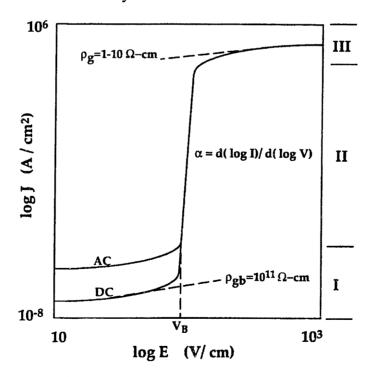

| FIGURE 2.1 A SCHEMATIC LOG I-LOG V CURVE OF A ZNO VARISTOR OVER A WIDE CURRENT DENSITY AND                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ELECTRIC FIELD RANGE. REGION I IS THE PREBREAKDOWN REGIME; REGION II IS THE BREAKDOWN                                                                                 |

| REGIME; AND REGION III IS THE UPTURN REGIME                                                                                                                           |

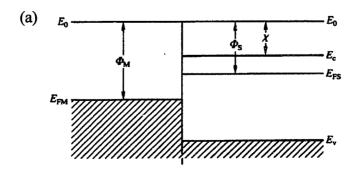

| FIGURE 2.2 ENERGY BAND DIAGRAMS FOR METAL-SEMICONDUCTOR CONTACT (A) BEFORE CHARGE                                                                                     |

| TRANSFER (NON-EQUILIBRIUM) AND (B) AFTER CHARGE TRANSFER (EQUILIBRIUM)1                                                                                               |

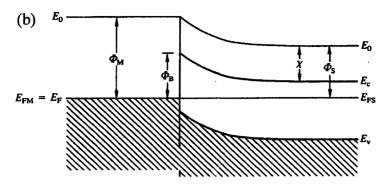

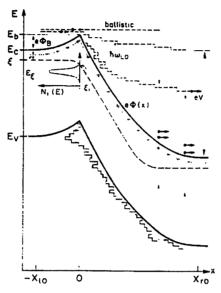

| FIGURE 2.3 ENERGY BAND DIAGRAM AND CHARGE DISTRIBUTION FOR A DOUBLE SCHOTTKY BARRIER AT AN                                                                            |

| ACTIVATED GRAIN BOUNDARY. $N_I\!(E)$ is the trap concentration at the interface. Typical zing                                                                         |

| OXIDE VARISTORS FEATURE A ZERO-BIAS $\Phi_B$ =1 eV, A DONOR LEVEL $E_0$ =50 MEV WITH                                                                                  |

| CONCENTRATION $N_0$ =10 <sup>18</sup> Cm <sup>-3</sup> , an interface state concentration $N_I$ *=10 <sup>12</sup> -10 <sup>13</sup> Cm <sup>-2</sup> ( $I$ =0, 1, 2) |

| AND $V_B \le 3.3-3.7 \text{ V.}$ (SEE REF. 4)                                                                                                                         |

| FIGURE 2.4 ENERGY BAND DIAGRAM FOR A DSB UNDER LARGE APPLIED BIAS, SHOWING HOLES BEING                                                                                |

| COLLECTED AT THE INTERFACE, CAUSING THE BARRIER TO COLLAPSE. [SEE REF. 8]1                                                                                            |

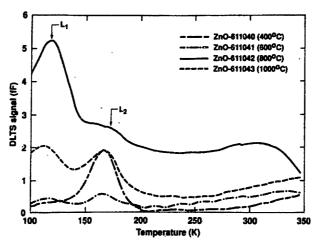

| FIGURE 2.5 DLTS SIGNAL VERSUS TEMPERATURE FOR SAMPLES WITH DIFFERENT ANNEALING                                                                                        |

| TEMPERATURES [Ref. 18]1                                                                                                                                               |

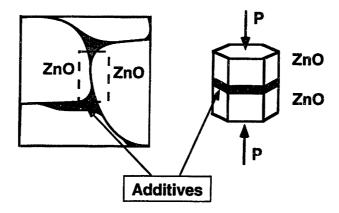

| FIGURE 2.6 LEFT: SCHEMATIC GRAIN-GRAIN INTERFACE IN A ZINC OXIDE VARISTOR; RIGHT: IDEALIZATION O                                                                      |

| THIS GRAIN-GRAIN VARISTOR INTERFACE BETWEEN TWO SINGLE CRYSTALS OF ZNO2                                                                                               |

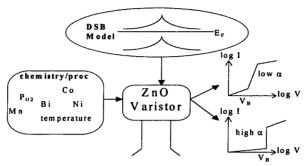

| FIGURE 2.7 CHEMISTRY AND PROCESSING NEED TO BE LINKED TO THE ELECTRICAL PROPERTIES.                                                                                   |

| UNDERSTANDING THE INTRINSIC AND EXTRINSIC DEFECT CHARACTERISTICS IN TERMS OF THE DSB                                                                                  |

| MODEL IS AN IMPORTANT LINK                                                                                                                                            |

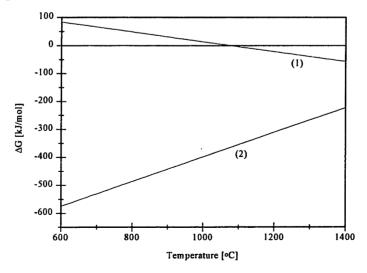

| FIGURE 2.8 $\triangle G$ VERSUS TEMPERATURE FOR REACTION (1) ZNO(S) + H <sub>2</sub> (G) = ZN(G) + H <sub>2</sub> 0(G) AND REACTION                                   |

| (2) $2ZN(G) + O_2(G) = 2ZNO(S)$ (SEE REF. 40)                                                                                                                         |

| FIGURE 2.9 SCHEMATIC FURNACE SETUP USED BY (A) NIELSEN [39], (B) PAS'KO ET AL. [41], AND (C)                                                                          |

| DODSON AND SAVAGE [40]20                                                                                                                                              |

| FIGURE 2.10 SCHEMATIC DIAGRAM OF OPEN TUBE SYSTEM FOR ZNO GROWTH ON SAPPHIRE USED BY (A)                                                                              |

| KASUGA AND ISHIHARA [45] AND (B) OHNISHI ET AL. [46]                                                                                                                  |

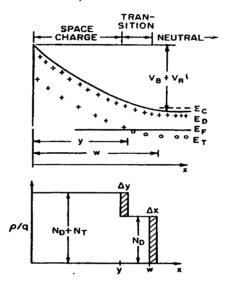

| FIGURE 3.1 SCHEMATIC DIAGRAM OF DEPLETION REGION AT METAL AND N-TYPE SEMICONDUCTOR                                                                                    |

| INTERFACE. A DEPLETION REGION HAS FORMED NEAR THE METAL/SEMICONDUCTOR INTERFACE                                                                                       |

| BECAUSE A CHARGE TRANSFER FROM THE SEMICONDUCTOR HAS OCCURRED TO ACHIEVE EQUILIBRIUM                                                                                  |

| HERE $V_{B}$ is the built-in voltage and $V_{R}$ is the applied reverse bias. A single majority                                                                       |

| CARRIER TRAP OF CONCENTRATION $N_T$ is depicted with energy $E_T$                                                                                                     |

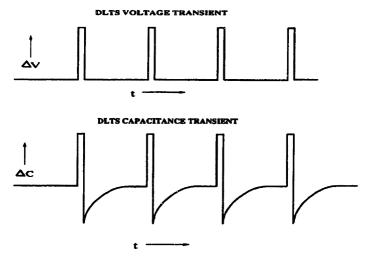

| FIGURE 3.2 TYPICAL TIME DEPENDENCE CURVES FOR APPLIED VOLTAGE AND CAPACITANCE TRANSIENT. THE                                                                          |

| VOLTAGE PULSE SHOULD SATURATE ALL THE TRAPS WITHIN A GIVEN SEGMENT OF THE DEPLETION                                                                                   |

| REGION. HERE, THE TRANSIENT SIGNAL IS NEGATIVE33                                                                                                                      |

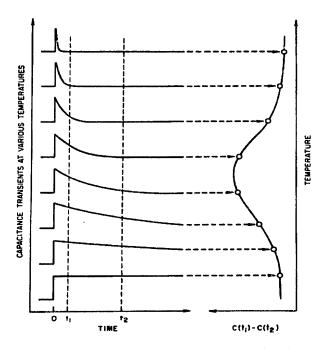

| FIGURE 3.3 SCHEMATIC ILLUSTRATION OF TEMPERATURE DEPENDENCE OF POSITIVE CAPACITANCE                           |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| TRANSIENT. A BOX-CAR AVERAGER SAMPLING WINDOW AT TIMES $T_I$ AND $T_2$ ARE INDICATED,                         |     |

| SHOWING HOW THE CHOICE OF THESE TIMES CAN RESULT IN A SPECTROSCOPIC PEAK IN THE CHANGE                        | IN  |

| CAPACITANCE $\Delta C(T) = C(T_1) - C(T_2)$ .                                                                 | .34 |

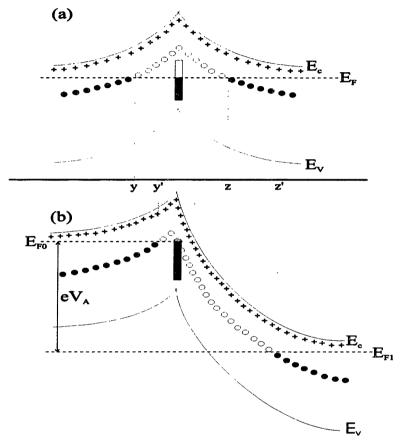

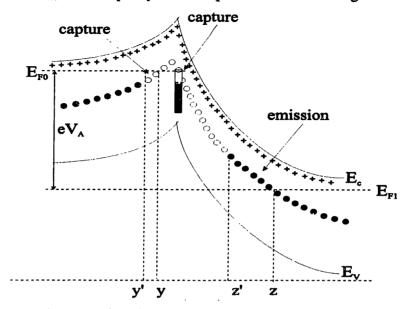

| FIGURE 3.4 (A) BAND DIAGRAM AT ZERO BIAS. INTERFACE STATES UP TO $E_F$ ARE FILLED. (B) BAND                   |     |

| DIAGRAM DURING FILLING PULSE AT BIAS $V_{\mathcal{A}}$ . Interface states up to $E_{F0}$ are filled, which is |     |

| SOMEWHAT HIGHER THAN $E_F$                                                                                    | .36 |

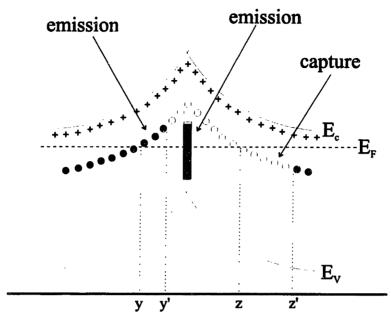

| FIGURE 3.5 INTERFACE STATES AFTER INJECTION PULSE ARE FILLED ABOVE THE FERMI LEVEL. CARRIERS I                | N   |

| THESE TRAPS WILL BE EMITTED TO THE CONDUCTION BAND.                                                           | 37  |

| FIGURE 3.6 CARRIERS ARE EMITTED FROM BULK TRAPS ONLY WHEN THE BIAS RETURNS TO THE QUIESCENT                   | •   |

| VALUE OF $V_A(<0)$ .                                                                                          | 38  |

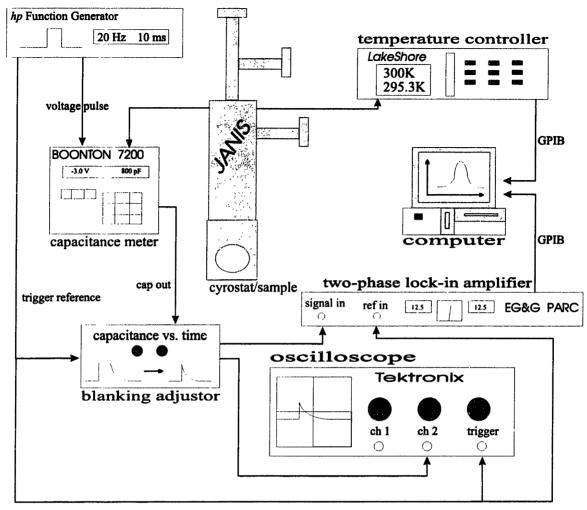

| FIGURE 3.7 PICTORIAL BLOCK DIAGRAM OF THE DLTS SYSTEM EMPLOYING A LOCK-IN AMPLIFIER. NOTE                     |     |

| DIRECTIONS OF ARROWS WHICH REPRESENT FLOW OF ELECTRONIC SIGNALS.                                              | 39  |

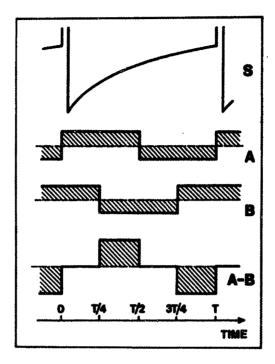

| Figure 3.8 A-B technique: signal $S$ is convolved with in-phase weighting function $A$ and                    |     |

| QUADRATURE WEIGHTING FUNCTION $\emph{B}$ AND SUBTRACTED. THIS IS EQUIVALENT TO CONVOLVING THE                 | ;   |

| SIGNAL S WITH EFFECTIVE WEIGHTING FUNCTION A-B.                                                               | 40  |

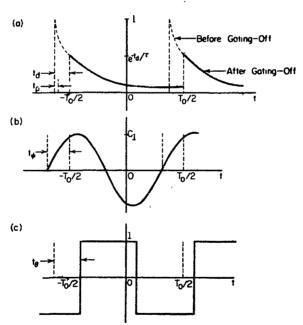

| FIGURE 3.9 DEFINITIONS OF SIGNAL AND REFERENCE RELATIONSHIPS: (A) NORMALIZED EXPONENTIAL                      |     |

| CAPACITANCE TRANSIENT BEFORE AND AFTER GATING OFF, (B) FUNDAMENTAL FOURIER COMPONEN                           | Γ   |

| OF SIGNAL IN (A), (C) LOCK-IN AMPLIFIER WEIGHTING FUNCTION FOR PHASE SETTING $\Theta$ . HERE, $T_{\theta}$ IS |     |

| MEASURED FROM THE SAME POINT $\mathcal{T}_D$ IS MEASURED FROM ABOVE                                           | 43  |

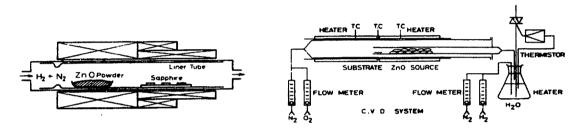

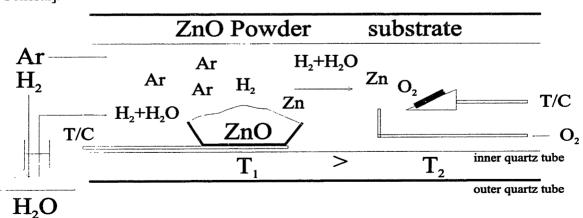

| FIGURE 5.1 SCHEMATIC DIAGRAM OF VAPOR TRANSPORT SETUP USED TO DEPOSIT ZINC OXIDE FILMS. THE                   |     |

| POWDER SOURCE IS KEPT AT TEMPERATURE $T_{I}$ , and the sapphire substrates are kept at                        |     |

| TEMPERATURE $T_2$ .                                                                                           | 47  |

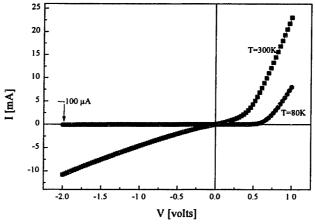

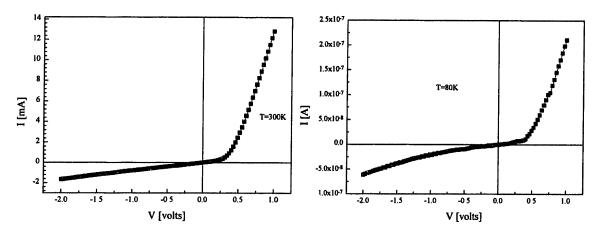

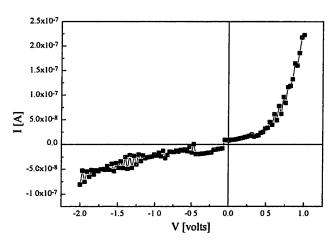

| FIGURE 5.2 I-V CURVES AT LOW AND ROOM TEMPERATURES FOR A SCHOTTKY BARRIER ON AN UNDOPED                       |     |

| BULK ZINC OXIDE CRYSTAL HEAT TREATED IN A REDUCING ATMOSPHERE.                                                | 51  |

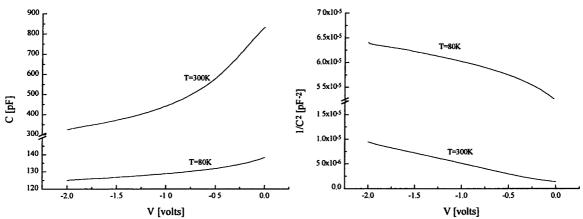

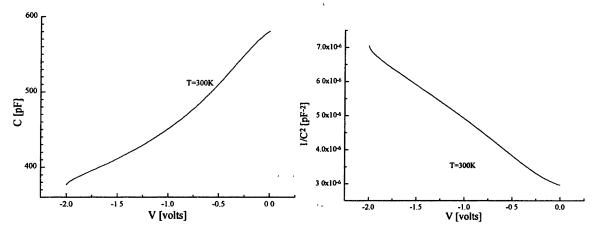

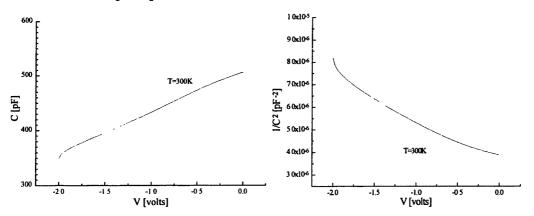

| FIGURE 5.3 LEFT: C-V PLOTS AT LOW AND ROOM TEMPERATURES FOR AN UNDOPED BULK ZINC OXIDE                        |     |

| CRYSTAL (REDUCED); RIGHT: MOTT-SCHOTTKY REPRESENTATION OF C-V DATA WITH SLOPE THAT                            |     |

| YIELDS $N_D \approx 6 \times 10^{16} \mathrm{CM}^{-3}$ .                                                      | 51  |

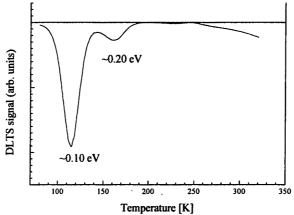

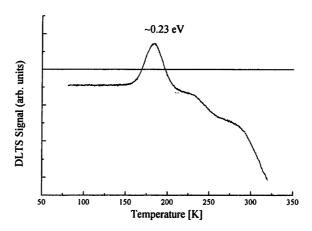

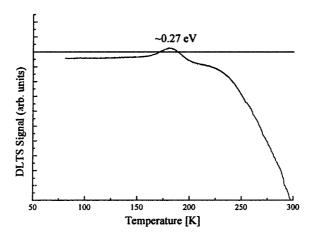

| FIGURE 5.4 DLTS CURVE FOR UNDOPED BULK ZINC OXIDE CRYSTAL (REDUCED) WITH $f=10$ Hz, $T=44.2$ ms               |     |

| GATING ( $T_D = 1.6 \text{ MS}, T_P = 1.5 \text{ MS}$ )                                                       | 52  |

| FIGURE 5.5 I-V CURVES AT LOW AND ROOM TEMPERATURES FOR A SCHOTTKY BARRIER ON AN UNDOPED                       |     |

| BULK ZINC OXIDE CRYSTAL HEAT TREATED IN AN OXIDIZING ATMOSPHERE                                               | 53  |

| FIGURE 5.6 LEFT: C-V PLOTS AT ROOM TEMPERATURE FOR AN UNDOPED BULK ZINC OXIDE CRYSTAL                         |     |

| (OXIDIZED); RIGHT: MOTT-SCHOTTKY REPRESENTATION OF C-V DATA WITH SLOPE THAT YIELDS                            |     |

| $N_D = 10^{17} \mathrm{CM}^{-3}$                                                                              | 53  |

| FIGURE 5.7 DLTS CURVE FOR UNDOPED BULK ZINC OXIDE CRYSTAL (OXIDIZED) WITH $f=50$ Hz, $T=10.2$ MS            | ;  |

|-------------------------------------------------------------------------------------------------------------|----|

| GATING ( $T_D = 1.6 \text{ Ms}, T_P = 1.5 \text{ Ms}$ )                                                     | 54 |

| FIGURE 5.8 I-V CURVES AT LOW AND ROOM TEMPERATURES FOR A SCHOTTKY BARRIER ON A COBALT-                      |    |

| DOPED BULK ZINC OXIDE CRYSTAL HEAT TREATED IN A REDUCING ATMOSPHERE.                                        | 55 |

| FIGURE 5.9 LEFT: C-V PLOTS AT ROOM TEMPERATURE FOR A COBALT-DOPED BULK ZINC OXIDE CRYSTAL                   |    |

| (REDUCED); RIGHT: MOTT-SCHOTTKY SLOPE YIELDS $N_D \approx 6 \times 10^{17} \text{ cm}^{-3}$                 | 55 |

| Figure 5.10 DLTS curve for as-grown zinc oxide film with $f$ =50 Hz, $\tau$ =10.2 ms gating ( $t_D$ =1.6 ms | s, |

| $T_P$ =1.5 MS)5                                                                                             | 56 |

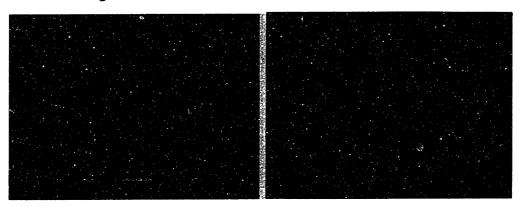

| FIGURE 5.11 LEFT: ESEM PICTURE OF AS-GROWN FILM; RIGHT: FILM AFTER POLISHED TO 0.3 MM                       | 56 |

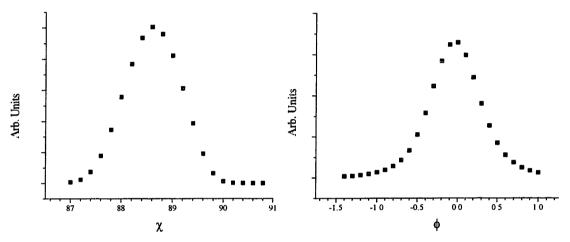

| Figure 5.12 x and $\phi$ rocking curve data for (1120) zinc oxide films grown on R-plane sapphire.          | 57 |

| Figure 5.13 I-V curves at room temperature for a Schottky barrier on an undoped, as-grown                   |    |

| BULK ZINC OXIDE FILM                                                                                        | 58 |

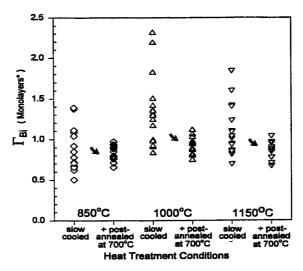

| FIGURE 6.1 BISMUTH SEGREGATION AT ZINC OXIDE GRAIN BOUNDARIES AS MEASURED BY STEM, SHOWING                  | ì  |

| A TIGHTENING OF THE SEGREGATION DISTRIBUTION WITH AN ADDED POST-ANNEAL BELOW THE $\mathrm{B_2O_3}$ -        |    |

| ZNO EUTECTIC. [61, 72]6                                                                                     | 60 |

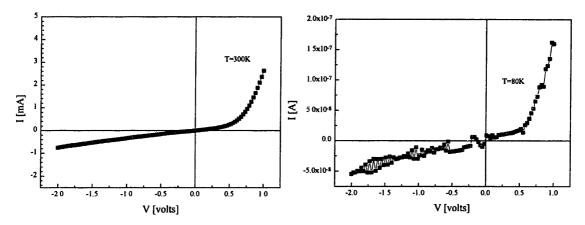

| FIGURE 6.2 I-V CURVES FOR SAMPLES (A) SLOW COOLED FROM THEIR INITIAL TEMPERATURE AND (B) SLOW               | ,  |

| COOLED WITH AN ADDITIONAL 700°C ARREST6                                                                     | 1  |

| FIGURE 6.3 DLTS CURVE OF SAMPLES SLOW COOLED FROM THEIR INITIAL ANNEALING TEMPERATURE                       |    |

| WITHOUT ANY OXIDATIVE POST-ANNEAL. (1=7.41 MS)6                                                             | 1  |

| FIGURE 6.4 DLTS CURVE OF SAMPLES SLOW COOLED FROM THEIR INITIAL ANNEALING TEMPERATURE WITH                  |    |

| An oxidative post-anneal at 700°C for 24 hours. ( $\tau$ =7.41 ms)6                                         | 2  |

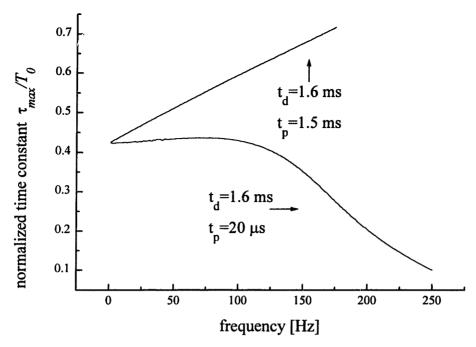

| FIGURE A.9.1 NORMALIZED TIME CONSTANT VERSUS FREQUENCY IN THE BIAS PHASE REFERENCE MODE FOR                 | L  |

| TWO CASES: (1) $T_D$ =1.6 MS AND $T_P$ =20 MS AND (2) $T_D$ =1.6 MS AND $T_P$ =1.5 MS7                      | 4  |

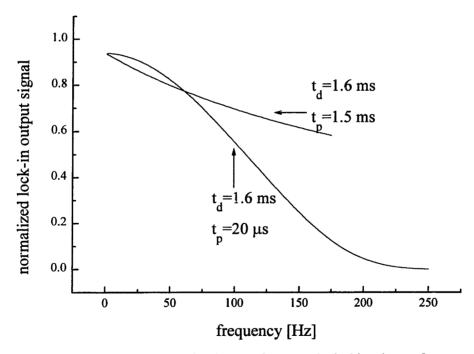

| FIGURE A.9.2 NORMALIZED OUTPUT SIGNAL VERSUS FREQUENCY IN THE BIAS PHASE REFERENCE MODE FOR                 |    |

| TWO CASES: (1) $T_D$ =1.6 MS AND $T_P$ =20 MS AND (2) $T_D$ =1.6 MS AND $T_P$ =1.5 MS. THE NORMALIZATION    | 1  |

| IS TO THE IDEAL CASE WHERE $T_D$ , $T_P = 0$                                                                | 4  |

## List of Tables

| TABLE 2.1 SUMMARY OF MAJORITY CARRIER TRAPS IN ZNO MEASURED BY VARIOUS RESEARCHERS ON A     |    |

|---------------------------------------------------------------------------------------------|----|

| VARIETY OF SAMPLES                                                                          | 20 |

| TABLE 3.1 DLTS RATE WINDOW TIME CONSTANTS FOR THE LOCK-IN AMPLIFIER WHEN USED UNDER THE A-  | В  |

| TECHNIQUE. THE PULSE WIDTH IS FIXED AT (1/5)T4                                              | 1  |

| TABLE 3.2 DLTS RATE WINDOW TIME CONSTANTS FOR THE LOCK-IN AMPLIFIER WHEN USED UNDER THE     |    |

| FOURIER METHOD AND BIAS PHASE REFERENCE MODE ( $T_D$ =1.6 MS AND $T_P$ =20 MS)4             | 4  |

| TABLE 3.3 DLTS RATE WINDOW TIME CONSTANTS FOR THE LOCK-IN AMPLIFIER WHEN USED UNDER THE     |    |

| FOURIER METHOD AND BIAS PHASE REFERENCE MODE ( $T_D$ =1.6 MS AND $T_P$ =1.5 MS)4            | 4  |

| TABLE 3.4 PULSE WIDTHS AND CORRESPONDING LOCK-IN PHASE SETTINGS FOR DLTS MEASUREMENTS       |    |

| TAKEN AT 10 Hz. THE TIME CONSTANT IS NOTED TO CHANGE SLIGHT; HENCE, A SLIGHT SHIFTING OF    |    |

| THE PEAK IS EXPECTED TO OCCUR4                                                              | 5  |

| TABLE 5.1 FLOW RATES AND OTHER EXPERIMENTAL PARAMETERS USED IN GROWING ZINC OXIDE FILMS. (* |    |

| 10% Oxygen/Argon gas mixture)4                                                              | 8  |

## Acknowledgments

I would like to mention first my deepest appreciation and gratitude to my thesis advisor Professor Harry L. Tuller. This thesis would never have come to fruition without his helpful and insightful guidance. His academic instruction is matched by his warm hospitality, extending his home to me during the holiday seasons.

I also thank the other members of the Tuller group for improving my laboratory skills. I am especially grateful for the collaboration and friendship of Jürgen Claus whose cross court backhand is only outdone by his exacting organizational skills. Furthermore, the administrative support of Alberto Balestrieri, who always has something interesting to say, was critical in ensuring a smooth ride during my last year on this thesis. Jonq-Ren Lee and Professor Yet-Ming Chiang are accredited for providing helpful discussions and some of the samples used in work presented herein. Also, the help of Imtiaz Majid in the x-ray measurements and Richard Pirelli of the CMSE Microfabrication Lab for help with the electron beam metal deposition are appreciated.

Special recognition goes to Eleanor Perrone, my piano teacher. Her encouragement and musical instruction have brought me to a deeper understanding of music. I would also like to thank the Brookline Music School for inviting me to play at their adult recitals, allowing me to gain practice in sharing the music I love.

Finally, I would like to recognize the most important support of my family and friends, beginning with my mother Theresa and my younger brother Eric. Despite the great distance between us, I have always felt their unwavering support and prayers. The sympathetic efforts of other family members like my grandmother, my uncle and his family, my cousin Janet and her family, and my second cousin Jane and her family are duly noted. Good friends who have supported me at MIT include Laura Giovane, Larry Foley, , Mary Ni, and Roy Rasera. Also appreciated are Jung Uk Yoon and the kind people at Berkland Baptist Church. Finally, an implicit acknowledgment goes to those I have not mentioned because of space limitations.

The financial support of the MIT Center for Materials Science and Engineering is greatly appreciated under contract NSF-DMR-022933.

#### 1. Introduction

Even though the word defect connotes something that is undesirable, defects play a key role in the engineering of many materials. Semiconductors rely on careful defect engineering to control their electrical conductivity and carrier type so that one is able to build functional devices and integrated circuits. Oxide ceramics, many of which are wide bandgap semiconductors, also rely on defect engineering to attain some of the unusual properties they exhibit. For example, many gas sensors use the defect properties of ceramics to detect potentially harmful emissions from cars or factories. Furthermore, the combination of grain boundaries and point defects has lead to interesting phenomena as found in ZnO varistors, (Sr,Ba)TiO<sub>3</sub>-based boundary layer capacitors, and positive temperature coefficient (PTC) thermistors. These phenomena are specific to the material's grain boundaries and are not exhibited in their single crystal counterparts.

## 1.1 Goals of the Thesis

The goal of this thesis is to investigate the nature of electrically active defects in zinc oxide, either in single crystal films or polycrystalline ceramics, as related to its peculiar grain boundary electrical characteristics. The motivation for understanding defects is to gain a deeper understanding of their fundamental roles as "grain boundary activators" in commercial varistors. Understanding the nature of defects and how they affect the grain boundaries is the first step in connecting the grain boundary chemistry with its electrical behavior. Because commercial varistors are often very complicated, consisting of secondary phases and multiple dopants, the work in this thesis centered on examining simpler systems that would yield useful information that could be extended to more complex systems. Single crystals were used to investigate the defect character of doping and processing, and chemically simple polycrystalline ceramics were used to investigate both defect character and I-V electrical properties. The work on single crystal growth of ZnO films was also developed in a way such that bicrystals with large, well-defined single boundaries could later be studied.

## 1.2 Organization of the Thesis

Having described the motivation for doing this work, the thesis is organized as follows. Chapter 2 gives necessary background information related to zinc oxide and zinc oxide varistors. It presents the accepted model of metal/ZnO and ZnO-ZnO interfacial junctions that is used in explaining the electrical characteristics, a review of the literature concerning deep levels in zinc oxide, and information on vapor transport. Chapter 3 discusses the deep level transient spectroscopy (DLTS) measurement technique as applied to Schottky barriers and electrically active grain boundaries, describing two techniques of using the lock-in amplifier as the DLTS rate window. Computations presented in the literature are extended to our system, and the results prove useful for computing a new set of time constants (detailed in Appendix A). The computations show an important distinction in the phase of the fundamental of the Fourier transform from those found in the literature. The experimental approach is outlined in Chapter 4. Chapter 5 considers vapor phase growth of zinc oxide, including the experimental setup and parameters used in the production of ZnO films on r-plane sapphire. X-ray data is presented as an evaluation of the film crystallinity. Also included are the results of I-V, C-V, and DLTS measurements. Chapter 6 provides a description of the simplified, "primitive" BiCo:ZnO varistors and recounts I-V and DLTS measurements attained on these samples. Chapter 7 discusses the results found in the previous two chapters, and Chapters 8 and 9 close this dissertation with a summary and suggestions for future work.

## 2. Background

## 2.1 ZnO Varistor Fundamental Electrical Properties

Since the late 1970's, doped polycrystalline zinc oxide has been known to exhibit a nonlinear current-voltage (I-V) characteristic. Because of this striking nonlinearity, this particular electroceramic has served as an overvoltage circuit protector which can sense and limit transient voltage surges repeatedly without being destroyed. The I-V curve resembles that of back-to-back diodes and, hence, limits current in both polarities. These devices can be designed to operate over the range of high voltages for usage in the power industry to low voltages for semiconductor applications. In addition, the speed of these devices and their high nonlinearity factors have made zinc oxide the dominant material for overvoltage applications, supplanting the previously dominant material, silicon carbide. Functionally, as shown in Figure 2.1, at biases below a characteristic breakdown voltage  $V_B$ , the device is essentially an insulator.

Figure 2.1 A schematic log I-log V curve of a ZnO varistor over a wide current density and electric field range. Region I is the prebreakdown regime; region II is the breakdown regime; and region III is the upturn regime.

Thus, connecting the device in parallel with a load does not disturb the load's normal operation. If, however, transient voltages above  $V_B$  were to occur, the resistivity of the device decreases precipitously, shorting the load to protect it from dangerous current levels. When the voltage settles back down below  $V_B$ , the device regains its insulator properties, ready for the next voltage surge. Such devices with voltage-dependent resistances have been dubbed "varistors." [1]

Three main regions of operation are evident from Figure 2.1: (I) the prebreakdown regime, (II) the breakdown regime, and (III) the upturn regime.  $V_B$  is engineered such that it is very close to the load's normal operating voltage. A normally operating varistor is kept just below  $V_B$  in the prebreakdown region and jumps into the breakdown region when a dangerous voltage surge occurs. The striking nonlinearity is a direct consequence of a space charge barrier breakdown located at the grain boundaries in the polycrystalline zinc oxide. Undoped polycrystalline zinc oxide does not manifest this nonlinearity. It is well-established that the nonlinearity can only be induced by the addition of key dopants that activate the boundaries. In general, the key ingredients that have been identified to lead to effective varistor action are: (a) deep donors (e.g. Co, Mn), (b) segregants (e.g. Bi, Pr), and (c) an oxidative anneal with slow cool. The combination of these three factors, either independently or synergistically, cause space charge barriers to form at the grain boundaries. Hence, the prebreakdown regime is dominated by the high resistance of the grain boundaries caused by the presence of electrostatic barriers, and the upturn regime is dominated by the grain resistance, as the grain boundary potential barriers have been overcome at large voltages (>V<sub>B</sub>). The degree of nonlinearity is quantified by a parameter called the  $\alpha$  value, where  $\alpha$  is the slope of the log I-log V curve in the breakdown region. The  $\alpha$  values can range from ~10 for poor varistors to ~100 for good varistors. Comprehensive reviews of zinc oxide varistors have been given by Gupta [1] and Levinson and Philipp [2].

The grain boundary phenomenon has been widely studied in terms of single boundary-type measurements. The most obvious correspondence of the varistor effect to individual zinc oxide grain boundaries lies in the breakdown voltage  $V_B$ . If one varistor is twice as thick as another identically processed one, the thicker varistor's breakdown volt-

age is two times higher than the thinner one's. This is so presumably because the thicker sample has twice as many grain boundaries between the electrodes. Individual measurements on single grain boundaries confirm their role as the determining factor in a device's nonlinearity.

#### 2.2 Zinc Oxide Semiconductor Junctions

Two types of zinc oxide semiconductor junctions are considered in this thesis. The first junction is the metal-semiconductor (Schottky) junction, where a high work function metal like palladium or gold is deposited onto an *n*-type single crystal semiconductor like zinc oxide or arsenic-doped silicon. The second type of junction is the graingrain homojunction found in polycrystalline materials. The varistor effect is a consequence of the significant band bending that occurs at a doped grain boundary in zinc oxide. Both types of junctions are taken advantage of in order to study electrically active defects in zinc oxide. The principles of these two junction types are presented below, and their application to measuring electrically active defects is explained in Chapter 3.

#### 2.2.1 The Metal-Semiconductor (Schottky) Junction

What follows is a discussion of the fundamentals concerning metal-semiconductor contacts, where the semiconductor is assumed to be defect-free and n-type, since zinc oxide is known to be n-type. The inclusion of defect levels will be covered in Chapter 3. For those who are familiar with pn-junctions, the Schottky junction can be viewed as a limiting case, resembling a p+n-junction, where the p+ side emulates a metal. The energy band diagrams for the metal and n-type semiconductor are shown in Figure 2.2.

Figure 2.2 Energy band diagrams for metal-semiconductor contact (a) before charge transfer (non-equilibrium) and (b) after charge transfer (equilibrium).

$E_0$  is the vacuum energy level, a reference point to indicate the amount of energy needed to remove an electron from the metal without any leftover kinetic energy. The difference between the vacuum energy level and the metal's Fermi level is called the work function  $\Phi_M$ . A similar work function quantity exists for the semiconductor,  $\Phi_S$ . The electron affinity  $\chi$  of a semiconductor is defined as  $E_0$ - $E_C$ .

The work function  $\Phi_M$  of a metal and the electron affinity  $\chi$  of a semiconductor are fundamental materials properties and do not change when constructing a junction. Furthermore, the Fermi level is constant when thermal equilibrium is achieved. (Here, the widely used misnomer of "Fermi level" is somewhat confusing because it is actually the chemical potential. Because it is an accepted misnomer, it will be used throughout this thesis.)3 This property of the Fermi level is a result of its thermodynamic properties. When a metal and semiconductor are brought together as in Figure 2.2a, the higher position of the Fermi level in the semiconductor indicates an excess charge amount relative to the metal. To establish the equilibrium of Figure 2.2b, electrons from the semiconductor must be depleted from the interface and transferred to the metal. Moreover, the fundamental properties  $\Phi_M$  and  $\chi$  cannot change. Thus, this charge transfer in the name of thermal equilibrium causes band bending in the semiconductor, whereby electrons in the metal see a potential barrier  $\Phi_B$  and electrons in the semiconductor see a potential barrier  $\Phi_{B-EC}$  (= $\Phi_{M^*}\Phi_S$ ), where  $E_C$  is the conduction band energy far from the junction.

The band bending at the metal-semiconductor interface indicates a depletion of electrons in the n-type semiconductor. This depletion of charge results in a depletion ca-

pacitance that will figure importantly in later discussions of measuring defect levels in the semiconductor. To evaluate the length of the depletion region, one usually assumes the "depletion approximation," whereby the depletion region is assumed to end after a finite distance W [cm] into the semiconductor and the semiconductor free carrier concentration is given by  $N_D$  [cm<sup>-3</sup>]. Using Poisson's Equation and the definition of the potential V [Volts],

$$\nabla^2 V = -\frac{\rho}{\varepsilon_S \varepsilon_0} \quad and \quad E = -\nabla V, \tag{2.1}$$

where  $\rho$  [C/cm<sup>-3</sup>] is the charge density,  $\varepsilon_S$  is the semiconductor's relative dielectric constant, and E [V/cm] is the electric field, one integrates from the interface over the depletion width (i.e. from x=[0,W]) to attain

$$E(x) = -\frac{eN_D}{\varepsilon_S \varepsilon_0} (W - x) \text{ for } x \in [0, W].$$

(2.2)

Arbitrarily choosing the metal to be at "zero potential" and integrating the electric field to obtain the potential as a function of distance

$$V(x) = V_{bi} - \frac{eN_D}{2\varepsilon_S \varepsilon_0} (W - x)^2 \text{ for } x \in [0, W],$$

(2.3)

where the built-in potential  $V_{bi}=eN_DW^2/2\varepsilon_s\varepsilon_o$  [V]. Using the expression for  $V_{bi}$ , the depletion width W [cm] is given by

$$W = \sqrt{\frac{2V_{bi}\varepsilon_{S}\varepsilon_{0}}{eN_{D}}} . {(2.4)}$$

For conditions under applied bias  $V_A$ , the barrier height related to  $V_{bi}$  is changed to  $V_{bi}$ - $V_A$ . Hence, during conditions of reverse bias (i.e.  $V_A < 0$ ), the bands in the semiconductor are shifted downward, increasing the barrier height accordingly, and the expression for the depletion width becomes

$$W = \sqrt{\frac{2\varepsilon_S \varepsilon_0}{eN_D} (V_{bi} - V_A)} . {(2.5)}$$

#### 2.2.2 The Double Schottky Barrier Model for Grain Boundaries

To understand the behavior of electrically active grain boundaries, the double Schottky barrier model (DSB) has found widespread acceptance as an archetype for the electronic potential near these interfaces. The DSB is essentially two back-to-back Schottky barriers. Figure 2.3 shows a schematic energy diagram of an electrically active interface. The potential barrier forms because electrons are trapped by the interface states. This trapping negatively charges the grain boundaries, inducing a local depletion of electrons in the adjacent grains and thereby effectively increasing the resistance of the grain boundary region. Greuter [4] has recently reviewed the key aspects of this model.

Figure 2.3 Energy band diagram and charge distribution for a double Schottky barrier at an activated grain boundary.  $N_i(E)$  is the trap concentration at the interface. Typical zinc oxide varistors feature a zero-bias  $\mathcal{O}_B=1$  eV, a donor level  $E_0=50$  meV with concentration  $N_0=10^{18}$  cm<sup>-3</sup>, an interface state concentration  $N_i^*=10^{12}-10^{13}$  cm<sup>-2</sup> (i=0, 1, 2) and  $V_B \le 3.3-3.7$  V. (see Ref. 4)

Many researchers have used the DSB model to describe quantitatively the transport of electrons across the barrier. For example, Pike and Seager [5] derived an expression for the thermionic emission current density in the prebreakdown regime:

$$J = A^* T^2 \exp(-\frac{\xi + \Phi_B}{kT}) \left[ 1 - \exp(-\frac{eV}{kT}) \right], \tag{2.6}$$

where  $\xi$  (= $E_C$ - $E_F$ ) is the bulk position of the Fermi level with respect to the conduction band,  $A^*$  is the effective Richardson constant, V is the applied bias, and  $\Phi_B$  is the grain boundary potential barrier height. This is analogous to the expression for the thermally

activated current density in metal-semiconductor barriers. Electrical breakdown in regime II occurs when the potential barrier collapses, allowing a huge increase in the current flow from regime I, and Equation 2.6 no longer applies. The mechanism of electrical breakdown is postulated as barrier height ( $\Phi_B$ ) lowering and/or formation of a significant tunnel current due to a strong applied bias [5, 6, 7]. Furthermore, impact ionization has been accepted as a critical mechanism by which the barrier collapses due to an influx of holes at the boundary, as shown in Figure 2.4 [8].

Figure 2.4 Energy band diagram for a DSB under large applied bias, showing holes being collected at the interface, causing the barrier to collapse. [see Ref. 8]

High energy electrons accelerated across the boundary by the large applied bias impact ionize atoms on the other side. Holes from the electron-hole pairs generated from the impact ionization drift and/or diffuse back toward the interface. A hole recombination process is computed to give a stable breakdown and high  $\alpha$  values that do not diverge. In essence, the generated holes travel to the interface and depopulate the interface traps which, in turn, cause the barrier to collapse.

## 2.3 Deep Levels at the Grain Boundaries

Deep level transient spectroscopy (DLTS) has been utilized to study bulk or thin film semiconductors. To an extent, it has also been applied to polycrystalline semiconductors. Defect levels in silicon [9, 10, 11, 12, 13], germanium [14], and gallium arsenide

[15, 16] have been identified in their polycrystalline or bicrystal forms with DLTS. Similar defects at grain boundaries in zinc oxide have been measured. In fact, because zinc oxide varistors can exhibit very large capacitances, DLTS is a natural technique that can be used in attaining grain boundary defect information. (see also Chapter 3)

#### 2.3.1 Previous Studies Using DLTS on ZnO Grain Boundaries

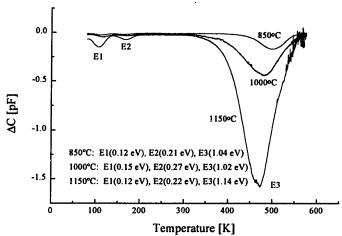

Shohata *et al.* [17] were one of the first to explore DLTS as means for characterizing zinc oxide varistors. They identified two defect levels, E1 (0.24 eV) and E2 (0.33 eV). They also noticed that the E1 signal saturated for large (presumably reverse) applied biases, which means that the E1 trap localized near the grain boundary depletion region. Rohatgi *et al.* [18] examined the defect levels they found in light of the heat treatments they performed on their samples. A figure showing DLTS signal versus temperature for samples with different annealing temperatures is shown in Figure 2.5.

Figure 2.5 DLTS signal versus temperature for samples with different annealing temperatures [Ref. 18]

They made some correlations between the relative heights of the L1 and L2 defect levels (as depicted) and varistor stability. This work is noteworthy for its attempts directly measuring and comparing defect information between samples in order to ascribe a DLTS peak with a specific defect. In this case, the authors ascribe the L2 peak with the zinc interstitial. Gambino *et al.* [19] did DLTS experiments on "simplified" varistors, doped only with bismuth and cobalt. They reported only one energy level between 0.6 and 0.7 eV and ascribed it to interface states caused by large segregated ions. As will be pre-

sented in Chapter 6, our results for a similar system show two more defect levels. Simpson and Cordaro [20] have researched the defect levels in barium-doped zinc oxide. In their study, they also investigated effects that cooling rate might have on the defect densities. Other studies have investigated defect energy levels and various other aspects of the zinc oxide varistor effect such as electrical degradation [21] and doping [22]. A selected list of energy levels identified throughout the literature is presented in Table 2.1.

Table 2.1 Summary of majority carrier traps in ZnO measured by various researchers on a variety of samples.

| Energy (eV) | Capture Cross-Section (cm <sup>2</sup> ) | Reference |

|-------------|------------------------------------------|-----------|

| 0.3         | 2.6×10 <sup>-14</sup>                    | 20        |

| 0.17        | 2.6×10 <sup>-17</sup>                    | 18        |

| 0.26        | 7.6×10 <sup>-17</sup>                    |           |

| 0.32        | 2×10 <sup>-14</sup>                      | 23        |

| 0.19        | 4×10 <sup>-16</sup>                      |           |

| 0.17        | 3×10 <sup>-12</sup>                      |           |

| 0.09        | -                                        | 21        |

| 0.16        | -                                        |           |

| 0.18        | 8×10 <sup>-18</sup>                      | 25        |

| 0.28        | 1.3×10 <sup>-17</sup>                    |           |

Researchers are interested in finding the important defect levels so that they can ascribe them to a particular chemical specie. In doing so, one is able to understand barrier formation and breakdown behavior (i.e. nonlinearity,  $\alpha$  value) of varistors better in terms of doping and heat treatment. Distinguishing between bulk and interface traps seems like a logical prerequisite in order to begin to clarify the origins of the energy levels that have been measured to date. Winston and Cordaro [24], as well as Tsuda and Mukae [25, 26], tried to distinguish between bulk and interface states in their studies. In fact, "reverting" back to single crystal zinc oxide to understand its bulk state behavior seems like a logical course of action; Simpson and Cordaro [27]found a single 0.3 eV trap in a hydrothermally grown, single crystal. Though they conjectured a connection with an oxygen vacancy defect, they did not investigate doping or heat treatment effects, nor they did not use a saturating filling pulse to ensure that all traps were being filled. Experiments that follow up on the findings of Simpson and Cordaro are the main thrust of this thesis.

#### 2.4 Grain Boundary Simplification: Geometry and Chemistry

In an effort to understand better the electronic structure of these doped interfaces and the double Schottky barrier, researchers have sought to isolate electrically active grain boundaries through various techniques. Olsson and Dunlop [28] used microcontacts to characterize individual grain junctions in sintered zinc oxide. Although they identified many different types of grain-grain junctions, their method is not ideal for studying electronic structure because of the complexities of the three-dimensional current network inherent in a polycrystalline matrix. Electrically active secondary phases and uncertain dopant concentrations further add to difficulties in studying specific grain boundaries. To lower the dimensionality of the problem, Schwing and Hoffmann [29] deposited an additive layer between two ZnO single crystals and annealed this construction at high temperatures (see Figure 2.6).

Figure 2.6 left: schematic grain-grain interface in a zinc oxide varistor; right: idealization of this grain-grain varistor interface between two single crystals of ZnO

By the very nature of the sample, current is confined to pass through a well-defined two-dimensional plane. Although this method successfully demonstrated I-V nonlinearity, the nonlinearity was caused by an artificial double heterojunction that forms between the ZnO crystals and the additive oxide (~microns thick) between them. Electron microscopy of typical varistor grain boundaries show that no micron-thick foreign oxide layer is normally present.

The movement toward better controlled interfaces has lead Yano et al. [30, 31] to fabricate thin film "sandwiches." Similar to the case of Schwing and Hoffmann, Yano

and co-workers constructed a double heterostructure which demonstrated a symmetrical I-V nonlinearity. Because they used sputtering to deposit poly-ZnO and PrCoO<sub>x</sub> films, they did not need high temperature anneals to hold their structures together, and no indiffusion was done. As mentioned previously, this double heterostructure is not representative of varistor boundaries.

Sukkar [32, 33] and Baek [34, 35] developed surface in-diffusion (SID) "sandwich" structures with poly-ZnO ceramics along the same lines. In appearance, these samples look very similar to those of Schwing and Hoffmann. Again, the current is isolated to pass through an electrically activated two-dimensional plane. In this case, however, the additive layer diffuses down the poly-ZnO grain boundaries into the bulk, leaving a thin area in the middle of the sandwich activated. Here, the heterojunction problem is somewhat alleviated because the additive layer actually diffuses into the bulk crystals. For these specimens, the high temperature sintering that was required to construct the sandwiches often changed the ZnO microstructure. Furthermore, the dopants which were introduced in pairs (e.g. Pr and Co) diffused at different rates, causing possible non-uniformity in the activated layer. This nonuniformity in coverage leads to characterization difficulties because the barrier height is lower in some spots.

Aside from a movement toward increased geometrical control, recent work by Lee and Chiang [36] has succeeded in controlling and quantifying the grain boundary chemistry in hot-pressed bulk BiCo-doped zinc oxide. In terms of the composition, these samples most resemble those of Gambino *et al.* [19]. By careful microanalysis and heat treatment, they have developed a method of controlling bismuth monolayer coverage along grain interfaces. As part of our collaboration with them, we have made correlations between the processing of these materials and their dc leakage currents and  $\alpha$  values.

Despite the foundations that have been laid to describe the process of electrical breakdown at grain boundaries and the efforts to apply this description to simplified grain boundary structures, a direct correlation between the chemistry of the boundary and its resultant electrical behavior has not been made. Greuter [4] has stated "The dominant parameters determining the potential barrier,  $\Phi_B$ , and its dependence,  $\Phi_B(V)$ , on applied bias are: (i) the doping,  $N_0$ ,  $N_t$ , of the ZnO grains, (ii) the total interface charge,  $Q_i$ , and (iii)

the actual distribution,  $N_i(E)$ , of the interface density of states." (see Figure 2.3) In other words, what kinds of dopants and subsequent processing steps need to be performed to achieve the proper values for  $N_0$ ,  $N_t$ ,  $Q_i$ , and  $N_i$  such that  $\Phi_B(V)$  can be predicted with some degree of certainty? As depicted in Figure 2.7, the connection between the chemistry/processing of varistors and their electrical properties is unclear.

Figure 2.7 Chemistry and processing need to be linked to the electrical properties. Understanding the intrinsic and extrinsic defect characteristics in terms of the DSB model is an important link.

A comprehensive understanding begins with knowledge of the intrinsic and extrinsic defect characteristics in ZnO. That is, knowing the energy level(s) of certain defects and understanding how they behave under various processing conditions allows one to apply directly the DSB model in order to understand the resultant electrical characteristics. Single crystal films of ZnO were grown in order to focus on understanding intrinsic and extrinsic defects. Moreover, the technique of growing single crystal films was conceived such that it could be extended to bicrystal growth in future studies.

## 2.5 Vapor Phase Growth of Zinc Oxide

Growth of zinc oxide from zinc vapor has been done since the late 1960's for its optical and piezoelectric properties. Initially, the interest was focused on the ability to grow high quality, free-standing single crystals. Gradually, interest shifted toward growing single crystal zinc oxide on suitable substrates to explore potential integrated circuit and waveguide applications. More recently, as mentioned in the previous section, zinc oxide films have been explored for electrically active grain boundary studies by Yano et al. [30, 31]. As applied to our work, single crystal zinc oxide was grown on r-plane sapphire so that we could use Schottky barriers and DLTS to investigate the nature of intrin-

sic and extrinsic defects. This section reviews some thermodynamic considerations when growing zinc oxide in an open tube system. Additionally, some previous work on ZnO growth is reviewed.

#### 2.5.1 Thermodynamics of Vapor Transport

In many of the studies encountered in the literature, growth of zinc oxide films focused on reducing zinc oxide powder with hydrogen gas to zinc vapor and water, subsequently transporting it over a negative temperature gradient to a cooler substrate, and then reoxidizing the vapor back to ZnO. Zinc is known to have a high vapor pressure, melting at a relatively low 420°C. Because of zinc's rather high vapor pressure, zinc oxide can be easily transported if it can first be reduced to zinc. The oxidation/reduction behavior of zinc and zinc oxide is summarized in the Ellingham diagram (or Richardson/Jeffes) [37]. The two reactions of interest are

$$ZnO(s) + H_2(g) = Zn(g) + H_2O(g)$$

(2.7)

$$2Zn(g) + O_2(g) = 2ZnO(s)$$

(2.8)

The first equation, reaction 1, is represented on the Ellingham diagram by the zinc line and the  $H_2/H_20$  ratio data. The second equation, reaction 2, would be represented on the Ellingham diagram as just the zinc line if the zinc were in the solid phase.

Comparing the free energies of these reactions in Figure 2.8, one readily sees that the reaction in Equation 2.8 is much more favorable.

Figure 2.8  $\triangle G$  versus temperature for reaction (1) ZnO(s) + H<sub>2</sub>(g) = Zn(g) + H<sub>2</sub>0(g) and reaction (2) 2Zn(g) + O<sub>2</sub>(g) = 2ZnO(s) (see Ref. 40)

The fact that oxygen is a potent oxidizer is a key consideration when designing a vapor transport system for zinc oxide. Moreover, one may incorrectly guess from Figure 2.8 that temperatures greater than  $T\approx1078^{\circ}C$  are necessary to reduce zinc oxide with hydrogen (i.e. to drive reaction 1 rightward). Though reaction 1 appears thermodynamically favorable only above  $T\approx1078^{\circ}C$ , one must inspect the equilibrium constant  $K_I$  to determine whether this reaction proceeds leftward or rightward.

$$K_1 = \frac{P_{Zn}P_{H_2O}}{P_{H_2}} \tag{2.9}$$

The Ellingham diagram takes account of the equilibrium constant by including the  $H_2/H_20$  ratio axis, and one sees that zinc oxide can be reduced for sufficiently high  $H_2/H_20$  ratios at temperatures below 1078°C. For example, to reduce zinc oxide at 900°C, one needs an  $H_2/H_20$  ratio greater than 100:1.

## 2.5.2 Literature Review of Vapor Phase Growth of Zinc Oxide

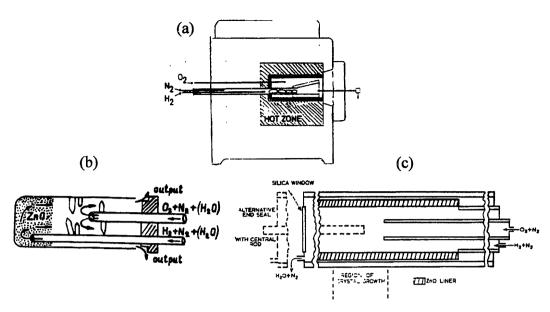

As stated earlier, zinc oxide's properties as a wide bandgap semiconductor and piezoelectric substance have generated interest in its bulk growth. One of the first to report vapor phase growth of zinc oxide was Scharowsky [38]. Small zinc oxide needles ~0.3 mm in diameter were reported to have grown on the furnace walls, when zinc metal vapor from a metal source at 600°C was carried by a nitrogen and hydrogen gas mixture into a furnace at 1150°C. Nielsen [39] performed a similar experiment but used sintered zinc oxide as the source. Nitrogen and hydrogen were fed into a source tube which contained the ZnO pellets. This end of the tube exited into a zinc oxide cone lining inside the furnace at ~1300°C; oxygen was fed separately into the furnace (see Figure 2.9a). Nielsen notes that the ZnO lining inside the furnace was advantageous to growing large, pure specimens.

Figure 2.9 Schematic furnace setup used by (a) Nielsen [39], (b) Pas'ko et al. [41], and (c) Dodson and Savage [40].

Nielsen also modified the setup to dope his as-grown crystals with copper. Dodson and Savage [40] along with Pas'ko *et al.* [41] used tube furnace setups that were conducive to the control and study of gas flow on crystal quality, as shown in Figure 2.9b and c. Both Dodson and Savage and Pas'ko *et al.* introduced hydrogen through one port and oxygen through another, with the expectation that the crystals would grow in the vicinity of the oxygen port. Furthermore, both use zinc oxide as a source, strategically placed in a manner that allows the hydrogen to have dominant flow over it, minimizing the source's interaction with the oxygen. Both groups featured temperatures in the 1200°C range. Pas'ko *et al.* even characterized the morphology of their specimens against flow rate of water vapor and hydrogen.

Not long after vapor growth of bulk zinc oxide was established, several investigators developed film growth techniques that borrowed many ideas from their bulk counterparts. Some early work on thin ZnO films was done by Channin *et al.* [42] for waveguide studies. Their process simply involved holding a (1102) sapphire substrate (*r*-plane) over a heated zinc oxide powder source (~850°C) in flowing hydrogen. Films of (1120) zinc oxide were produced, but no significant details concerning the growth process were given. Galli and Coker [43] used a chemically more complicated system which involved hydrogen and HCl. They deposited thick ZnO films on a number of sapphire

substrates which included the r-plane orientation. Though their films were of good crystalline quality, they found the film surfaces to be highly textured, sometimes with a 5  $\mu$ m surface roughness.

Open tube systems were later studied so that gas delivery would be simplified. Reisman and Landstein [44] studied the thermodynamics of such systems, though they did not focus on ZnO growth on sapphire substrates. Kasuga and Ishihara [45] flowed nitrogen, hydrogen, and water through a tube system to grow (1120) ZnO on *r*-plane sapphire, as depicted in Figure 2.10a. They kept their source at 1000°C and their substrates between 650-800°C. Their growth rates were on the order of microns per minute.

Figure 2.10 Schematic diagram of open tube system for ZnO growth on sapphire used by (a) Kasuga and Ishihara [45] and (b) Ohnishi *et al.* [46]

For the same film-substrate orientations, Ohnishi *et al.* [46] investigated the improvements that added water vapor and an intermediately sputtered ZnO layer had on the final films. Considerably more complicated than the system of Kasuga and Ishihara, the system of Ohnishi *et al.* bubbled hydrogen through water (~90°C) and added an oxygen gas inlet where the substrates were located, similar to the ideas found in bulk crystal growth. They did not observe film growth when oxygen was absent. They used a temperature of 900°C for both source and substrate. Hydrogen and oxygen were flowed at ~40 sccms, and nitrogen (carrier gas) was flowed at a considerably faster rate of ~300 sccms. Most significantly, Ohnishi *et al.* found that a thin (~13 nm) intermediately sputtered zinc oxide film improved the smoothness of the films. Apparently, the amorphous sputtered layer suppresses island formation which leads to uneven polycrystalline growth. Though the pre-sputtered film was amorphous, the subsequent film grown by CVD afterwards was found to be of high crystalline quality. Their film thicknesses ranged from 0.4 to 100 µm. They later compared their results with other chemical systems, namely ZnO-Br<sub>2</sub>-O<sub>2</sub> and ZnCl<sub>2</sub>-O<sub>2</sub> [47], and also tested their films as optical waveguides. [48]

The reactors of Kasuga and Ishihara as well as Ohnishi *et al.* were used as examples when we designed our own system for zinc oxide film growth. Substrate preparation with a thin, pre-sputtered ZnO layer was considered seriously, as the literature clearly indicates that higher quality, smoother films under well-controlled growth conditions are produced with this added step. Water was also considered an essential ingredient to slow the growth rate down. Because adatoms need enough time to find single crystal atomic positions to achieve smooth films of high crystallinity, slow growth rates and high temperatures were chosen to enhance surface mobility. Chapter 5 reviews the specific parameters used in our experiments.

## 3. DLTS Measurement Technique

Introduced in 1974 by Lang [49], deep level transient spectroscopy (DLTS) has rapidly become a standard evaluation tool for semiconductors. By using the depletion capacitance of a pn-junction or Schottky barrier (e.g. metal on n-type zinc oxide) to monitor the filling and emission of traps located within the depletion region, one is able to observe a corresponding capacitance transient that is related to the emission of holes into the valence band or electrons into the conduction band. This transient contains fundamental information about the nature of the trap such as (1) its energy level  $E_T$  [eV], (2) its capture cross-section  $\sigma_T$  [cm<sup>2</sup>], and (3) its concentration  $N_T$  [cm<sup>-3</sup>]. The heart of DLTS lies in analyzing a particular trap's capacitance transient as it changes over a temperature scan. Using the principle of detailed balance and some electronics that are set to give a maximum DLTS signal at a predetermined time constant  $\tau_{max}$ , a spectrum is produced with peaks that each identify a trap level. DLTS is sensitive to concentrations as low as  $10^9$  cm<sup>-3</sup>, where the detection limit is about  $10^{-5}$  times the bulk free carrier concentration.

Many ways of applying DLTS have been developed, and hence, proper analysis and interpretation of DLTS data requires specific understanding of a particular DLTS system. In this chapter, the basic physics of DLTS is reviewed for Schottky barrier and grain boundary (double Schottky barrier) junctions. A description of the two different DLTS methods used in this thesis are presented thereafter. Benton [50] has written an excellent summary of DLTS and has included some demonstrative applications. A thorough review is given by Miller *et al.* [51].

## 3.1 Review of Fundamental Theory behind DLTS

Because zinc oxide is naturally an *n*-type semiconductor and has not been known to exhibit *p*-type conductivity, discussion of metal/semiconductor junctions will be limited to *n*-type semiconductors. The fundamentals of junction device physics are covered extensively in standard text books [52, 53]. The discussion below is a review of the key concepts relevant to DLTS.

When a metal is brought into intimate contact with a perfect semiconductor surface, the semiconductor undergoes a free charge transfer to the metal such that the Fermi levels in the metal and semiconductor are equal. (see also Section 2.2.1) Due to the absence of majority carrier electrons in the semiconductor, the region adjacent to the metal contact contains a net charge density, and the valence and conduction bands bend upwards as shown in Figure 3.1. A typical approximation is to assume that this space charge in the semiconductor extends a finite distance W (given by  $\sqrt{\frac{2\varepsilon_S(V_{bi}-V_A)}{eN_D}}$ ) beyond which no space charge exists; this is called the depletion approximation. (W is computed through some elementary electrostatics; the terms are described below.)

Figure 3.1 Schematic diagram of depletion region at metal and n-type semiconductor interface. A depletion region has formed near the metal/semiconductor interface because a charge transfer from the semiconductor has occurred to achieve equilibrium. Here  $V_B$  is the built-in voltage and  $V_R$  is the applied reverse bias. A single majority carrier trap of concentration  $N_T$  is depicted with energy  $E_T$ .

As can be seen in Figure 3.1, the donor-like trap level crosses the Fermi level near the depletion region edge. Electron traps above the Fermi level  $E_F$  are empty and positively charged; those below are filled and neutral. One should note that the region of empty traps does not identically span the depletion width; it extends to about the point where the energy of the trap state crosses the Fermi level (y) which is a little before the depletion width edge.

#### 3.1.1 Junction Capacitance

An expression for the capacitance of this junction can be computed for space charge regions without traps by using the depletion approximation. Analogous to a parallel plate capacitor with a separation distance given by the depletion width W,

$$C = \frac{\varepsilon_s A}{W} = A \sqrt{\frac{e\varepsilon_s N_D}{2(V_{bi} - V_A)}},$$

(3.1)

where  $\varepsilon_s$  [F/cm] is the permittivity of the semiconductor (= $\varepsilon_r \varepsilon_0$ ), e [C] is the unit charge,  $V_{bi}$  [V] is the built-in (or flat-band) potential,  $V_A$  [V] is the applied voltage across the barrier (negative for a reverse bias),  $N_D$  [cm<sup>-3</sup>] is the donor density, and A [cm<sup>2</sup>] is the metal-semiconductor contact area. When considering the presence of traps, the previous equation becomes

$$C = \frac{\varepsilon_s A}{W} = A \sqrt{\frac{e\varepsilon_s (N_D + n_T)}{2(V_{bi} - V_A)}},$$

(3.2)

where  $n_T$  [cm<sup>-3</sup>] is the concentration of <u>filled</u> traps. Thus, filling of traps in the depletion region is detected by a capacitance change. As noted by Kimerling [54], one should remember that the effects of traps on junction capacitance can vary, depending on the frequency of the small signal capacitance; here, one is assuming that the frequency used to measure the small signal capacitance is much larger than the emission or capture rates of the trap. Equation 3.2 can be further rearranged into the Mott-Schottky relation

$$\frac{1}{C^2} = \frac{2(V_{bi} - V_A)}{e\varepsilon_s A^2 (N_D + n_T)},\tag{3.3}$$

such that  $1/C^2$  depends linearly on the applied (reverse) voltage  $V_A$ . Typically,  $N_D$  is much greater than  $n_T$ , and thus, the slope of this plot is proportional to the free carrier concentration  $N_D$ .

#### 3.1.2 The DLTS Transient Signal

In a DLTS experiment, the dynamic quantity is the number of traps actually filled with electrons,  $n_T(t)$ . The rate equation governing the occupancy of electron traps depends on the thermal capture rate for electrons and holes  $c_n$ ,  $c_p$  [s<sup>-1</sup>] and their corresponding thermal emission rates  $e_n$ ,  $e_p$  [s<sup>-1</sup>] (neglecting the optical emission rate):

$$\frac{dn_T(t)}{dt} = (c_n + e_p)(N_T - n_T) - (c_p + e_n)n_T.$$

(3.4)

The solution of this differential equation for traps initially filled with electrons in the depletion layer  $n_T(t=0)=N_T$  is

$$n_T(t) = N_T e^{-e_{n}t} = N_T e^{-t/\tau_n},$$

(3.5)

where  $N_T$  [cm<sup>-3</sup>] is the total number of electron traps, and  $\tau_n$  [s] is the characteristic time constant at which the trap empties. Hence, by establishing an initial state where traps in the depletion region are all filled, the capacitance will behave with the time dependence

$$C(t) = A\sqrt{\frac{e\varepsilon_s(N_D + n_T)}{2(V_{bi} - V_A)}} = A\sqrt{\frac{e\varepsilon_s(N_D + N_T e^{-t/\tau_n})}{2(V_{bi} - V_A)}}.$$

(3.6)

Taking  $N_D$  to be much greater than  $N_T$ ,

$$C(t) = A \sqrt{\frac{e\varepsilon_s N_D}{2(V_{bi} - V_A)}} \sqrt{1 + \frac{N_T}{N_D} e^{-t/\tau_n}} \approx A \sqrt{\frac{e\varepsilon_s N_D}{2(V_{bi} - V_A)}} (1 + \frac{N_T}{2N_D} e^{-t/\tau_n}). \quad (3.7)$$

By defining the baseline (quiescent reverse bias) capacitance  $C_{\infty}$  and the change in capacitance  $\Delta C(t)$ ,

$$C_{\infty} \equiv A \sqrt{\frac{e\varepsilon_s N_D}{2(V_{bi} - V_A)}}$$

(3.8)

$$\Delta C(t) \equiv C_{\infty} - C(t), \qquad (3.9)$$

equation 3.7 becomes

$$\frac{\Delta C(t)}{C_{\infty}} \equiv \frac{N_T}{2N_D} e^{-t/\tau_n}.$$

(3.10)

Hence, the change in capacitance  $\Delta C(t)$  under reverse bias is exponentially dependent on the time as depicted in Figure 3.2, where the voltage pulse establishes the initial condition of filling all the traps in a given segment of the depletion width.

Figure 3.2 Typical time dependence curves for applied voltage and capacitance transient. The voltage pulse should saturate all the traps within a given segment of the depletion region. Here, the transient signal is negative.

#### 3.1.3 The DLTS Rate Window

The time constant of the capacitance transient can be used to determine a trap's energy level  $E_T$ , its capture cross-section  $\sigma_T$ , and its concentration  $N_T$ . A donor-like trap in the bandgap emits electrons to the conduction band with an emission rate given by the principle of detailed balance:

$$e_n = \frac{1}{\tau_n} = \frac{\sigma_n \langle v_{th} \rangle N_C}{g} \exp\left(-\frac{E_C - E_T}{k_B T}\right), \tag{3.10}$$

where  $\sigma_n$  [cm<sup>2</sup>] is the capture cross-section for electrons of the defect state,  $v_{th}$  [cm/s] is the mean thermal velocity of electrons,  $N_C$  [cm<sup>-3</sup>] is the effective density of states in the conduction band, g is the trap degeneracy, and  $E_C$  [eV] is the energy of the conduction band edge. Because the emission rate  $e_n$  (=1/ $\tau_n$ ) is temperature dependent, so too is the capacitance transient by Equation 3.7. The temperature dependence of the transient is schematically illustrated in Figure 3.3. For low temperatures, carriers are not emitted for lack of thermal energy, and the transient is exceedingly slow. For high temperatures, carriers are emitted quickly, and the transient response is immediate.

Figure 3.3 Schematic illustration of temperature dependence of positive capacitance transient. A box-car averager sampling window at times  $t_1$  and  $t_2$  are indicated, showing how the choice of these times can result in a spectroscopic peak in the change in capacitance  $\Delta C(t) = C(t_1) - C(t_2)$ .

The heart of DLTS lies in defining a "rate window" with electronics that will output a maximum DLTS signal  $\Delta C$  for a specific transient time constant  $\tau_{max}$ . In other words, during a temperature scan, the capacitance transient will traverse a myriad of time constants  $\tau_n$ . At some peak temperature  $T_p$  at which  $\tau_n = \tau_{max}$ , the DLTS signal will max out. Changing  $\tau_{max}$  causes the DLTS signal maximum to shift to other values of  $T_p$ . For a given defect, values of  $\tau_n$  and  $T_p$  are tabulated for different settings of  $\tau_{max}$  to generate an Arrhenius graph of  $\ln(e_n/T_p^2)$  versus  $1/T_p$ , where the slope is proportional to the energy level  $E_T$  and the y-intercept is proportional to the capture cross-section  $\sigma_n$ . In the case of Figure 3.3, the rate window is set by sampling the capacitance signal at times  $t_1$  and  $t_2$  which defines a particular time constant  $\tau_{max}$ . ( $t_1$  and  $t_2$  are measured from the pulse edge.) Changing the values of  $t_1$  and  $t_2$  redefines the value of  $\tau_{max}$ . Mathematically speaking,  $\tau_{max}$  for a given  $t_1$  and  $t_2$  can be computed by maximizing the expression for  $\Delta C(t_1, t_2) = C(t_1) - C(t_2)$  (Equation 3.9) which can be done by taking its derivative with respect to  $\tau_n$  and setting it equal to zero. (Note that we are assuming that  $C_\infty \approx C(t_1)$ .) The result is

$$\tau_{max} = \frac{1}{e_{max}} = \frac{t_1 - t_2}{\ln(t_1 / t_2)}.$$

(3.11)

The concentration can be computed from the height of the DLTS peak  $\Delta C$ . Assuming that all the traps are filled by the pulse and that  $\Delta C \ll C_{\infty}$ , one can use Equation 3.10 with t=0 to get

$$N_T \approx 2N_D \frac{\Delta C}{C_m}. (3.12)$$

Here, the expression for  $N_T$  is given as an approximation because the filling pulse does not in practice cover the entire depletion width and the sampling window may not cover the entire transient.

## 3.2 Application of DLTS to Grain Boundary Junctions

Though originally conceived for use on asymmetric Schottky or *pn*-junctions, DLTS has found widespread use in characterizing energy levels at or near grain boundary junctions. DLTS can be used at electrically active grain boundaries, such as the one represented by the double Schottky barrier model, because there is a depletion capacitance associated with band bending. Furthermore, this band bending is bias-dependent so that one is able to populate and depopulate traps in a manner similar to that of a one-sided Schottky barrier. Grain boundaries generally have two kinds of traps: (i) bulk traps located in the adjacent grains and (ii) interface traps located at the grain boundary plane which are mainly responsible for the depletion regions. Because the discussion of the bulk states is identical to the one above for metal-semiconductor junctions, the discussion below will be limited to the application of DLTS to interface states.

#### 3.2.1 Zero Quiescent Bias Case

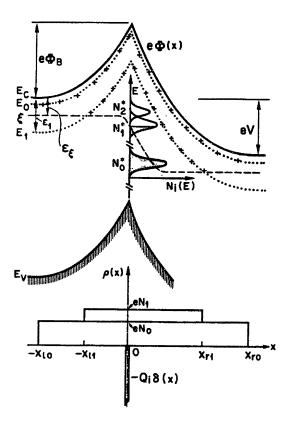

When the double Schottky barrier is at zero-bias, the Fermi level is flat. Traps below the Fermi level are filled; traps above the Fermi level are empty, including the interface traps. Referring to Figure 2.3, biasing the grain boundary causes the depletion region on one side to enlarge, dropping the Fermi level on that side, raising it on the other. DLTS on Schottky junctions usually involves holding the junctions at a reverse bias, and

pulsing them to near-zero bias for majority carrier filling. Because one wishes to observe emission from interface traps, a different pulsing arrangement is required. In the grain boundary case, referring to Figure 3.4a, if the bias is constantly held at the quiescent bias of zero, the equilibrium occupancy of the interface states is simply determined by the position of the Fermi level  $E_F$ .

Figure 3.4 (a) Band diagram at zero bias. Interface states up to  $E_F$  are filled. (b) Band diagram during filling pulse at bias  $V_A$ . Interface states up to  $E_{F0}$  are filled, which is somewhat higher than  $E_F$ .

During the pulse depicted in Figure 3.4b, the bias is increased to  $V_A(>0)$ , and the quasi-Fermi levels move in accordance to this new bias. Here, the interface states have a new equilibrium occupancy at  $E_{F0}$  which is higher than the quiescent  $E_F$ . Thus, during the pulse, the interface states between  $E_F$  and  $E_{F0}$  are filled. When the pulse ends and the bias returns to zero, carriers in the filled traps above  $E_F$  will be emitted to the conduction band, as illustrated in Figure 3.5. Thus, by changing the bias settings to move the Fermi level, one can sweep through a distribution of interface states. In analogy to Equation 3.2, the filling and unfilling of these interface traps can be monitored by the capacitance change of the grain boundary.

Figure 3.5 Interface states after injection pulse are filled above the Fermi level. Carriers in these traps will be emitted to the conduction band.

A word of caution must be included when interpreting the DLTS signal from grain boundary capacitances. An implicit assumption that bulks states on one side of the interface are identical to those on the other side has been made. As shown in Figure 3.5, the DLTS signal originates from potentially three different sources: (1) a capture signal from the filling of bulk traps on the negatively biased side of the grain boundary, (2) an emission signal from bulk traps on the positively biased side, and (3) the emission signal from the interface traps. Assuming the capture rate (which depends on the cross-section of the traps) to be fast compared to the emission rate (which depends mostly on the temperature), one still needs to discern between bulk and interface states. The next section discusses how a negative quiescent bias remedies this difficulty.

#### 3.2.2 Negative Quiescent Bias Case

The negative quiescent bias case simply involves pulling the dc offset of the pulse generator down so that the situation in Figure 3.4 is reversed. The junction is held as shown in Figure 3.4b at a bias  $V_A(<0)$  and pulsed to zero bias as shown in Figure 3.4a. (More accurately, the mirror image of Figure 3.4b is the result of a negative bias  $V_A$ , but

since the junction is symmetric, Figure 3.4b can still be used.) When the bias returns to its quiescent value of  $V_A$ , the occupancy of the traps are as shown in Figure 3.6.

Figure 3.6 Carriers are emitted from bulk traps only when the bias returns to the quiescent value of  $V_A(<0)$ .