## The Reliable Router: An Architecture for Fault Tolerant Interconnect

by

## Larry R. Dennison

B.S., Massachusetts Institute of Technology (1980) S.M., Massachusetts Institute of Technology (1991)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1996

| <b>©</b> | Massachusetts | Institute o | f Technology | 1996. | All rights | reserved |

|----------|---------------|-------------|--------------|-------|------------|----------|

|----------|---------------|-------------|--------------|-------|------------|----------|

| Author Departmen | t of Electrical Engineering and Computer Science |

|------------------|--------------------------------------------------|

| D open on on     | May 24, 1996                                     |

| Certified by.    | ************                                     |

| 1                | William J. Dally                                 |

|                  | Professor, Artificial Intelligence Laboratory    |

|                  | Thesis Supervisor                                |

| Accepted by      | *************                                    |

|                  | FR Morgenthaler                                  |

JUL 1 6 1996

Chairman, Departmental Committee on Graduate Students

MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

ARCHIVE8

## The Reliable Router: An Architecture for Fault Tolerant Interconnect

by Larry R. Dennison

Submitted to the Department of Electrical Engineering and Computer Science on May 24, 1996, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Abstract**

The Reliable Router advances the state-of-the-art in high-speed, fault-tolerant communication. It does so through novel ideas in the following areas: router architecture, fault-tolerant networks, interchip signalling, and data retiming (synchronization).

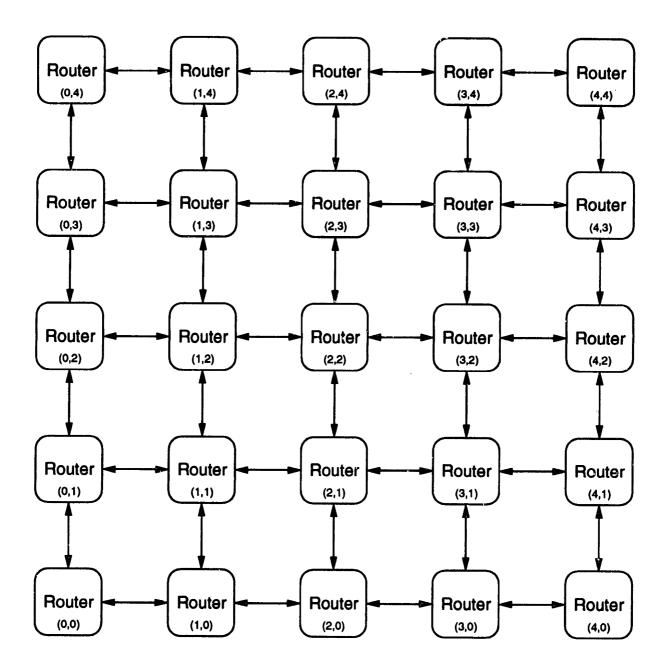

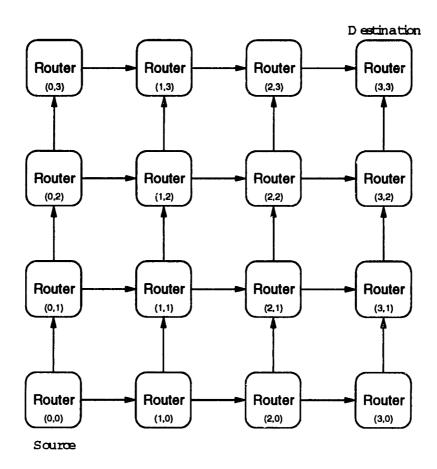

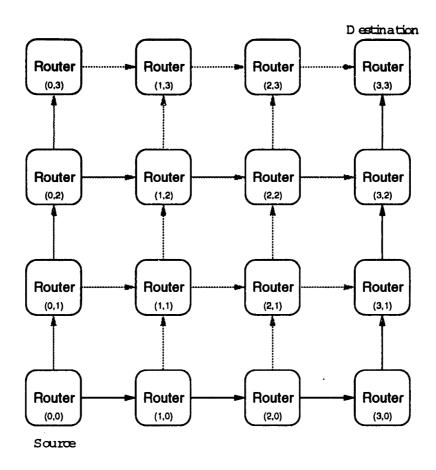

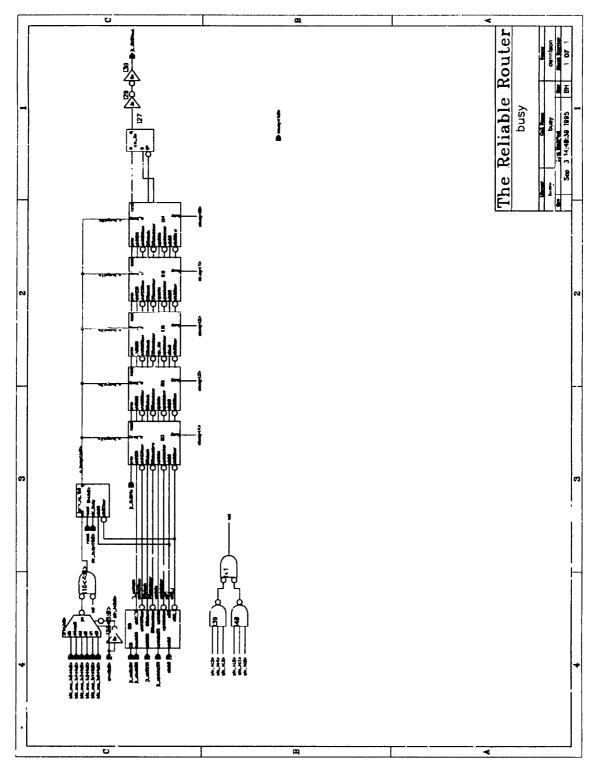

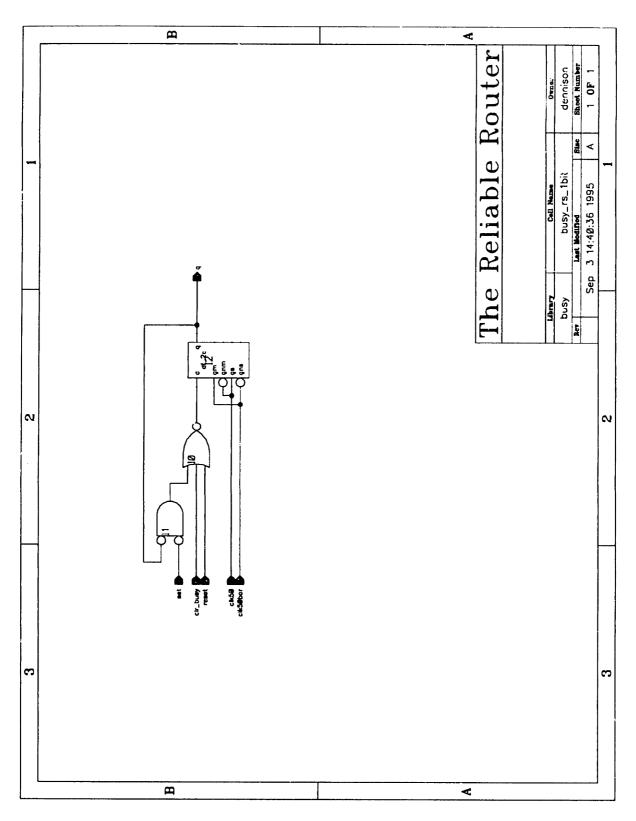

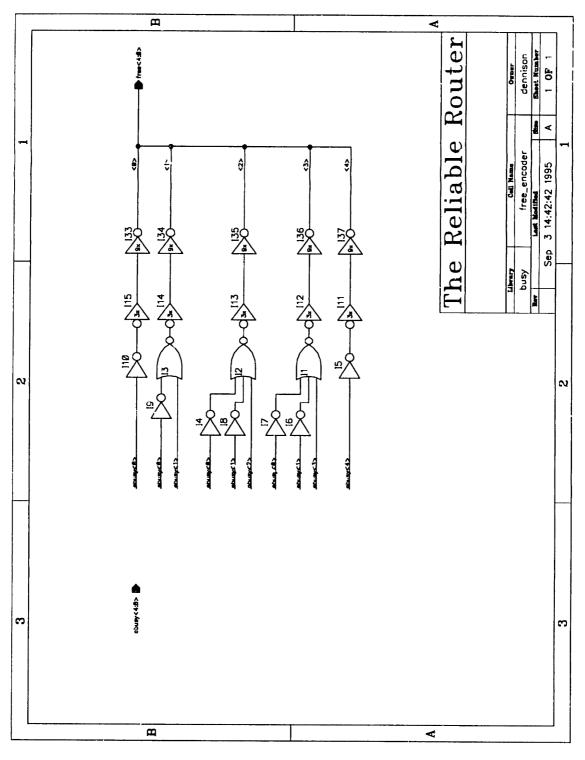

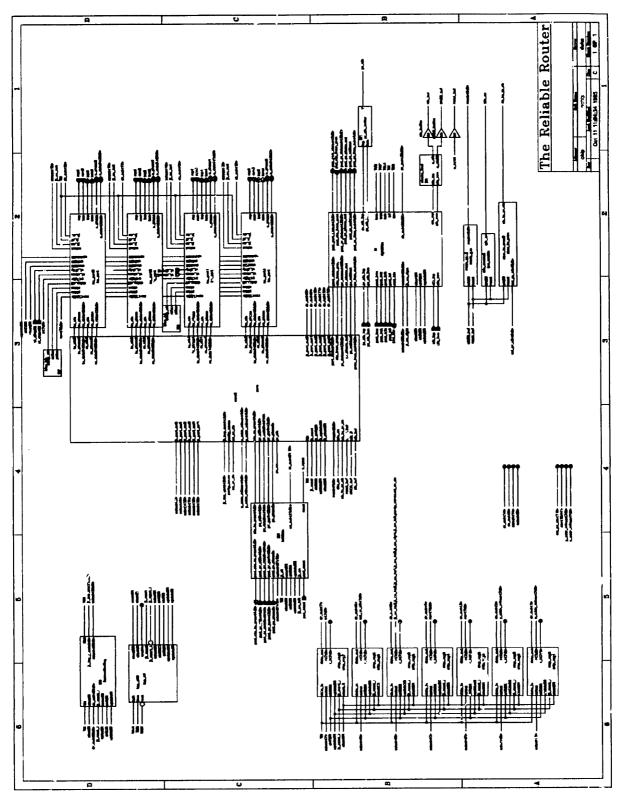

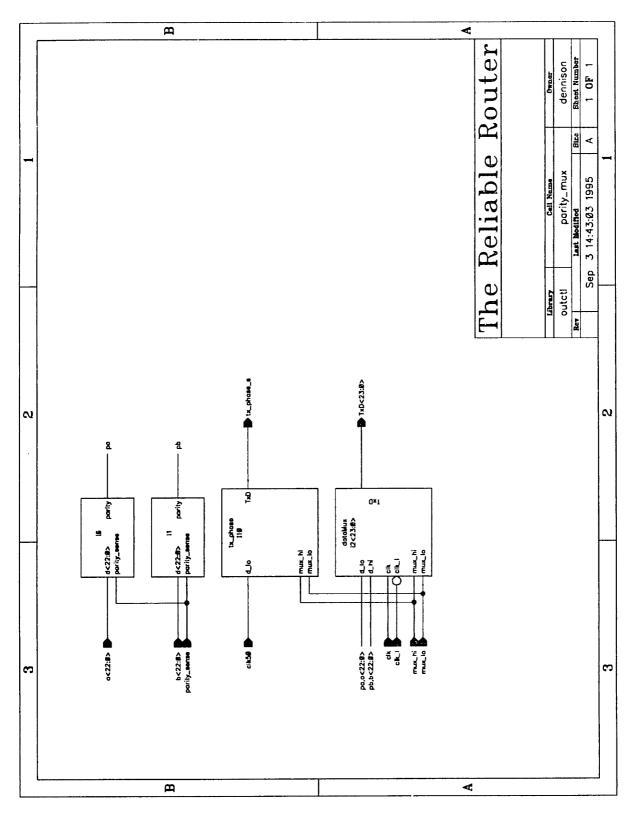

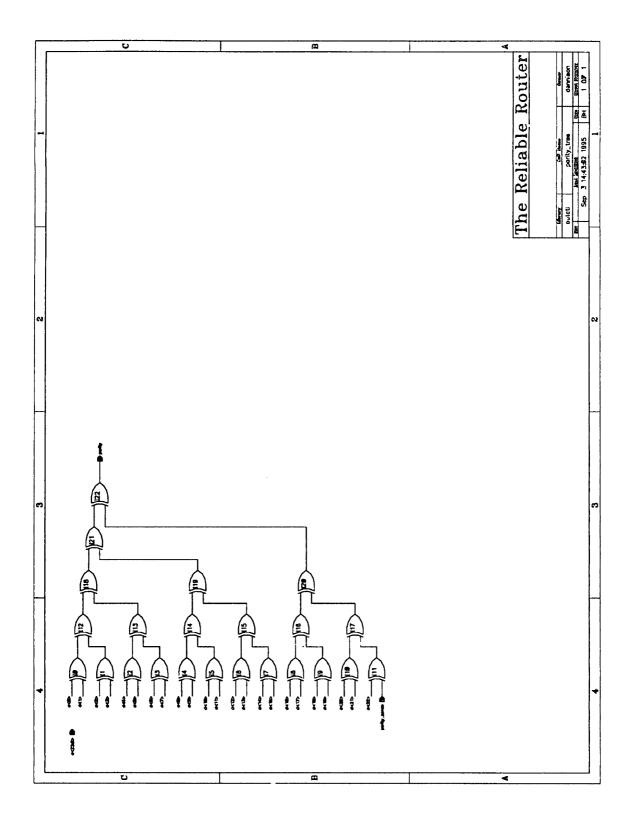

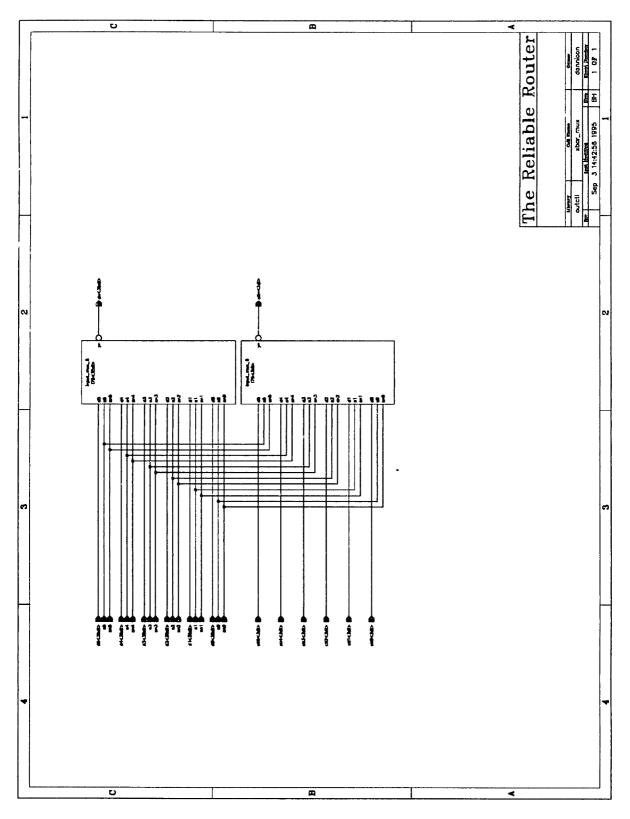

The Reliable Router is a VLSI device implementing a message-passing communication substrate for parallel computers and other micro-area networks. The network topology is a 2-dimensional mesh. It uses wormhole routing, 5 virtual channels per physical channel, 2 priority levels, minimally adaptive and one-fault-tolerant routing. Bandwidth between routers is 3.2Gbit/s, each way. Router latency is about 70ns. The router has been fabricated on a 13.5mm by 15mm die, packaged in a 463-pin PGA, and partial testing performed. A description of the architecture and schematics are given. The design methodology is presented.

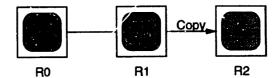

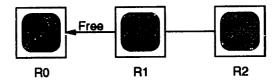

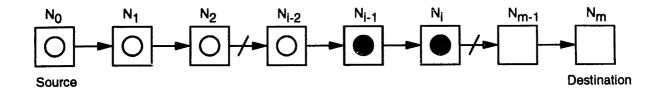

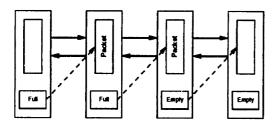

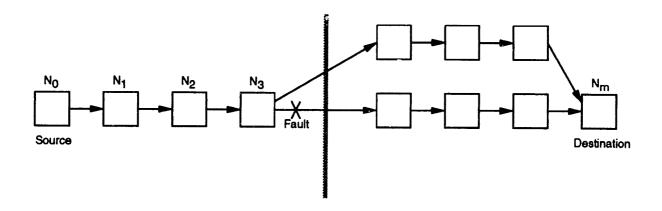

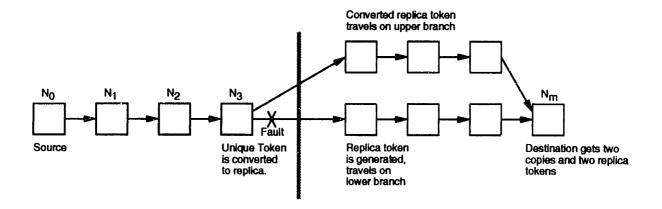

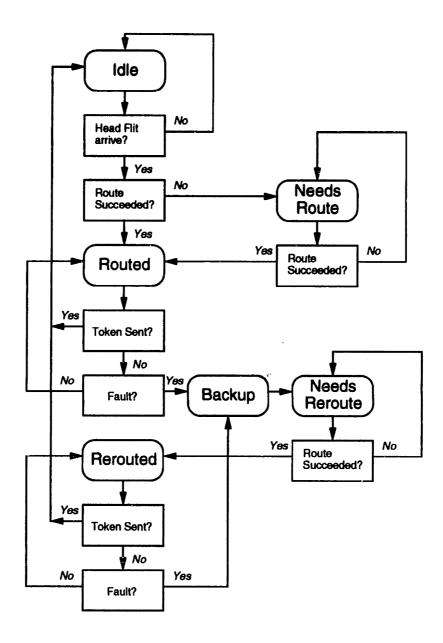

The Unique Token Protocol is used to provide fault-tolerance in the network. The protocol keeps two copies of a message in the network, obviating the need for source buffering. A token is used to determine the unique (exactly-once) delivery of a message, nearly completely eliminating the need for duplicate detection at the receiver. Details of the protocol under wormhole-routing are also provided.

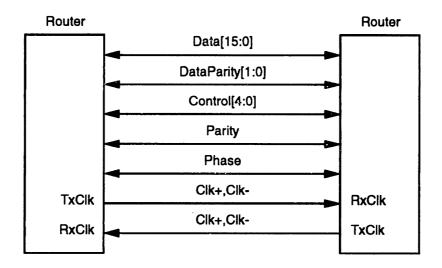

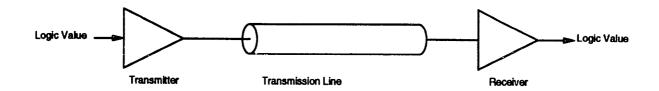

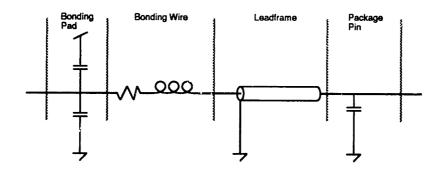

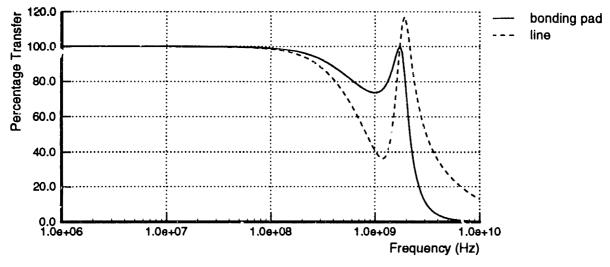

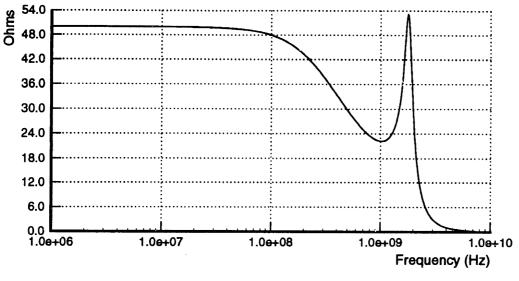

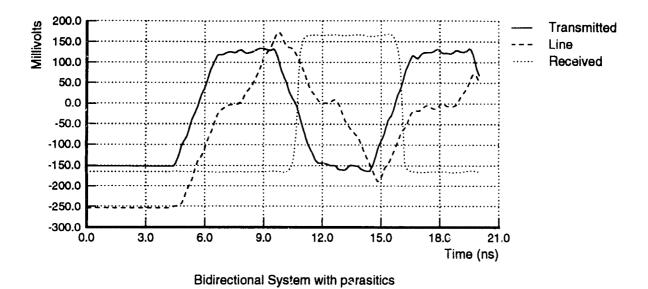

Simultaneous Bidirectional Signalling is used for high-performance interchip communication, 200Mbit/s each way per wire. A single wire carries full duplex communication concurrently through the use of waveform superposition. Circuits, noise-reduction techniques, and analysis are given.

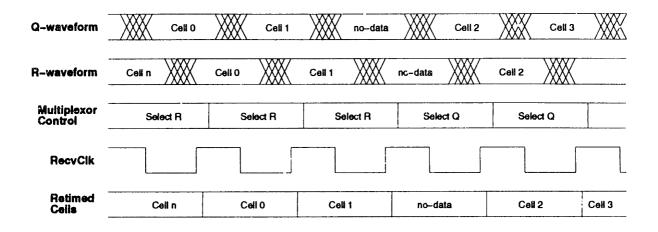

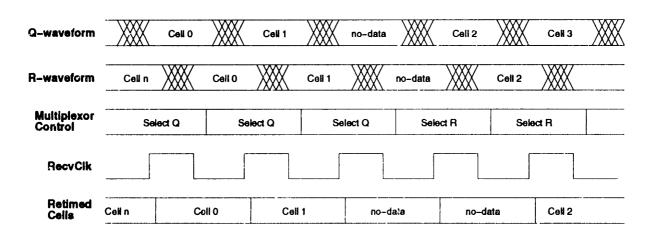

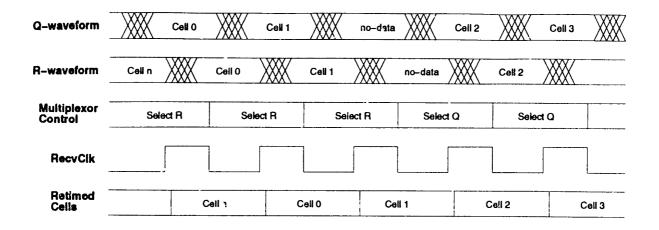

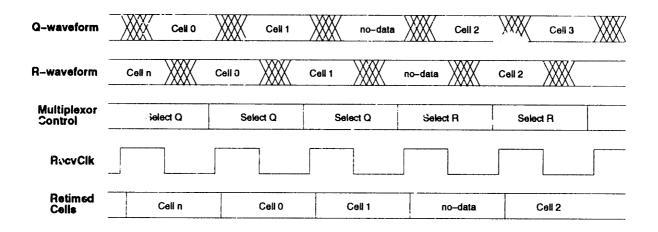

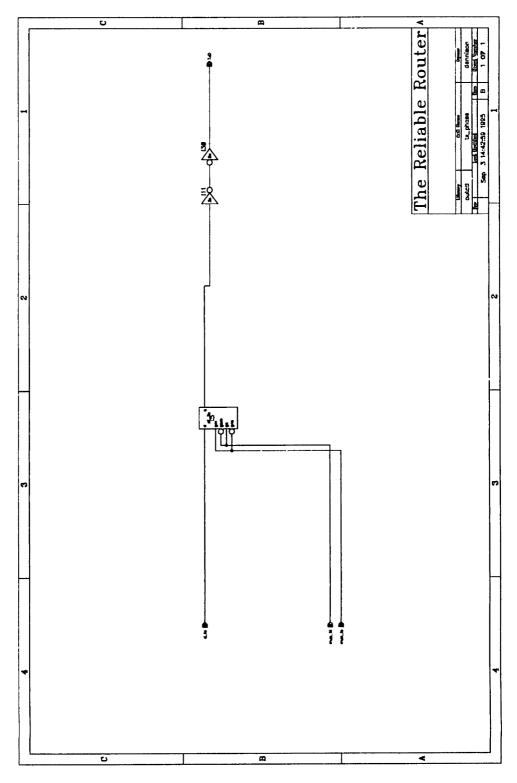

Low-Latency Plesiochronous Data Retiming is used for interchip communication. Each router operates in a separate clock domain. Latency is minimized by placing the synchronizer out of the data path. The basic retiming method is fully described, along with circuits and constraints for correct operation. Average latency is one-half a clock period. Extensions for integral subrates and cascaded timing circuits are given.

Thesis Supervisor: William J. Dally

Title: Professor, Artificial Intelligence Laboratory

## Acknowledgements

"It's a long hard climb, but I'm gonna get there."

from a Sesame Street song

I've relied on many people over the years. I would like to say thank you to the following people:

Bill Dally, for getting me started, for all his support along the way, and for bringing this project to a successful completion.

My thesis readers, Gill Pratt and Tom Knight, who supplied energy to a rather tired student.

Scott Furman, a great officemate.

The people who worked on the router over the years, Whay Lee, Kin Hong Kan, Ivan Oei, Jonathan Rosenberg, Dan Hartman, Jeff Bowers, and Dave Harris.

Eileen Neilson for getting the no-cost extensions through.

Tom Blackadar for understanding "I gotta get done."

The CVA group, for all their moral support.

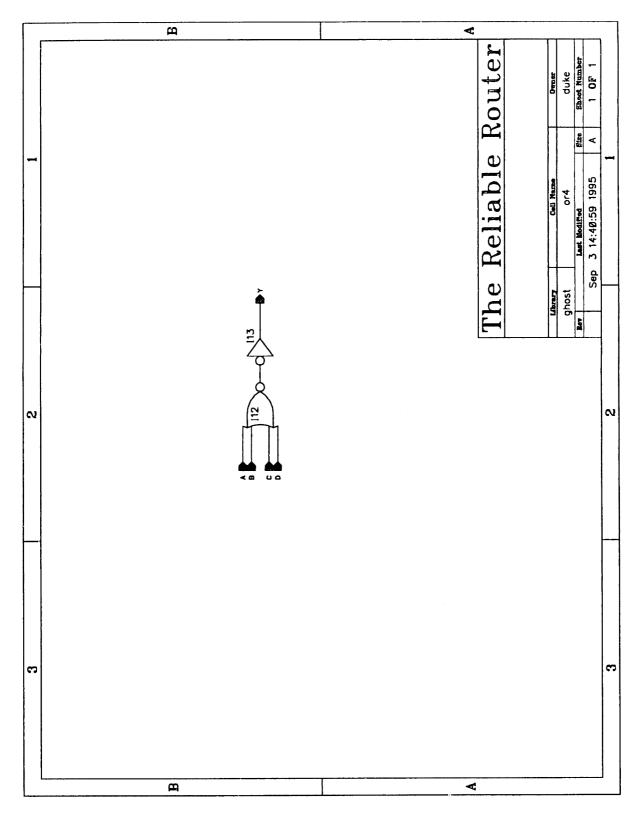

Duke Xanthopoulos, officemate, fellow router designer, and among the best of men.

My father and mother, Daniel and Dolores, who encouraged me to succeed by teaching me not to fear failure.

My father-in-law and mother-in-law, James and Lee Moses, for their support (and child-watching).

My children, Daniel, Kathryn, Larry, and Timothy, for their patience while Dad did this.

My wife Judy, who has done more for me than I ever had any right to ask and yet still loves me.

God in heaven, who watches over all I do.

For Judy, My one and only.

## Contents

| 1 | Int | roduction                                                           | 20 |

|---|-----|---------------------------------------------------------------------|----|

| 2 | Pri | or and Related Work                                                 | 23 |

|   | 2.1 | Fault Tolerance                                                     | 23 |

|   |     | 2.1.1 Routing Around Faults                                         | 23 |

|   |     | 2.1.2 Fault Tolerant Protocols                                      | 26 |

|   | 2.2 | Interchip Signalling                                                | 26 |

|   | 2.3 | Low-Latency Plesiochronous Retiming                                 | 26 |

|   | 2.4 | Router Architecture                                                 | 27 |

| 3 | Ove | erview of the Reliable Router                                       | 29 |

|   | 3.1 | Routing                                                             | 31 |

|   |     | 3.1.1 Minimally Adaptive Routing                                    | 31 |

|   |     | 3.1.2 Dimension-Ordered Routing                                     | 33 |

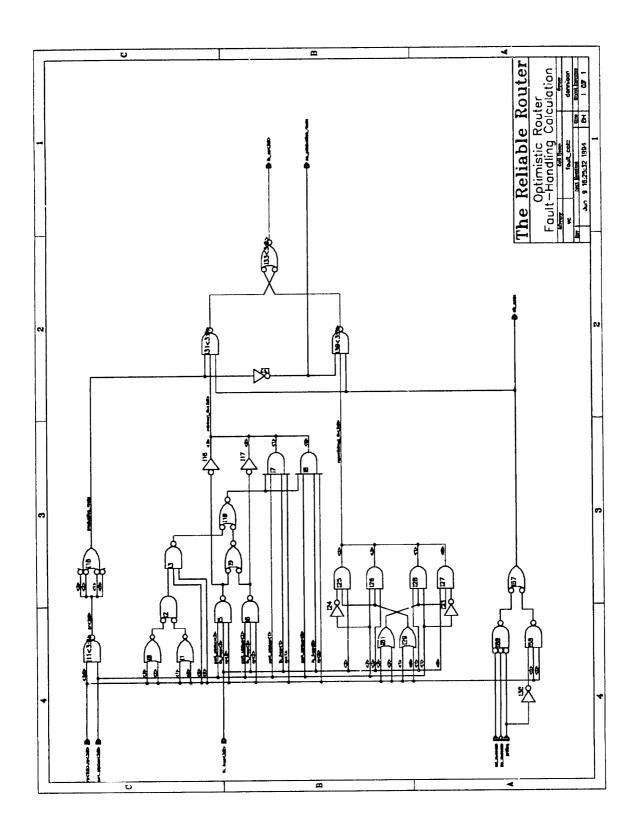

|   |     | 3.1.3 Fault-Handling Routing                                        | 34 |

|   | 3.2 | Network Construction                                                | 35 |

|   |     | 3.2.1 Messages                                                      | 36 |

|   |     | 3.2.2 Processor Port                                                | 37 |

|   | 3.3 | Summary                                                             | 38 |

| 4 | The | Unique Token Protocol                                               | 40 |

|   | 4.1 | Goals of Network-Level Fault Tolerance                              | 40 |

|   | 4.2 | Overview of the Unique Token Protocol                               | 41 |

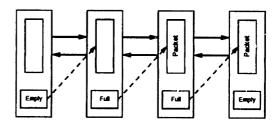

|   | 4.3 | Keeping Multiple Copies in the Network                              | 41 |

|   |     | 4.3.1 Correctness of the Flow-Control Algorithm                     | 41 |

|   |     | 4.3.2 The Unique Token Protocol Flow-Control Protocol Using Permits |    |

|   | 4.4 | The Token                                                           | 45 |

|   |     | 4.4.1 Correctness of the Token Passing Algorithm                    | 47 |

|   |     | 4.4.2 Token-Passing Pragmatics                                      | 49 |

|   | 4.5 | The Unique Token Protocol Using Wormhole Routing                    | 50 |

|   |     | 4.5.1 Packet Format and Reconstruction                              | 50 |

|   |     | 4.5.2 Flow Control                                                  | 51 |

|   |     | 4.5.3 Restarting a Message After a Fault                            | 51 |

|   |     | 4.5.4 Completing a Message After a Fault                            | 51 |

|   | 4.6 | Summary                                                             | 51 |

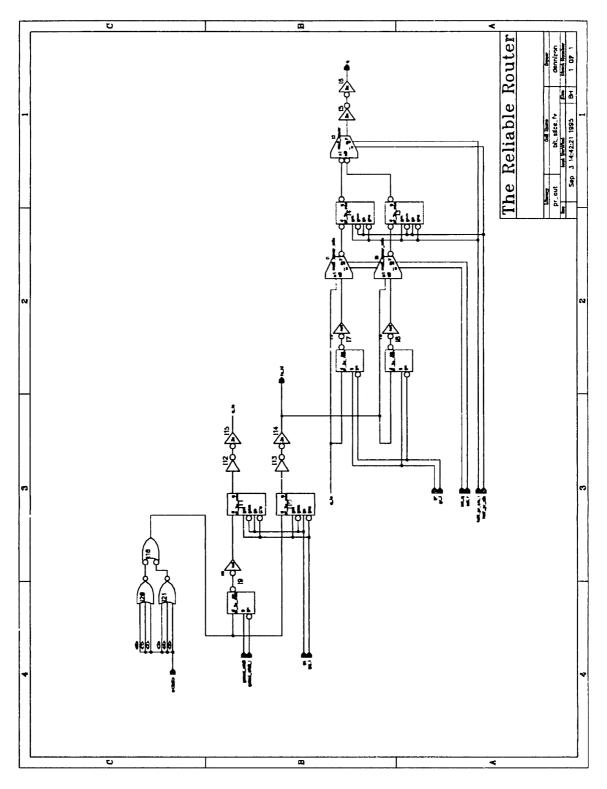

| 5 | Sim  |         | ous Bidirectional Signalling 5                            |

|---|------|---------|-----------------------------------------------------------|

|   | 5.1  | Funda   | mentals of Signalling                                     |

|   | 5.2  | Noise   | 54                                                        |

|   |      | 5.2.1   | Noise in the Interconnect                                 |

|   |      | 5.2.2   | Noise in the Transmitter 5                                |

|   |      | 5.2.3   | Noise in the Receiver                                     |

|   | 5.3  | Circui  | t Techniques                                              |

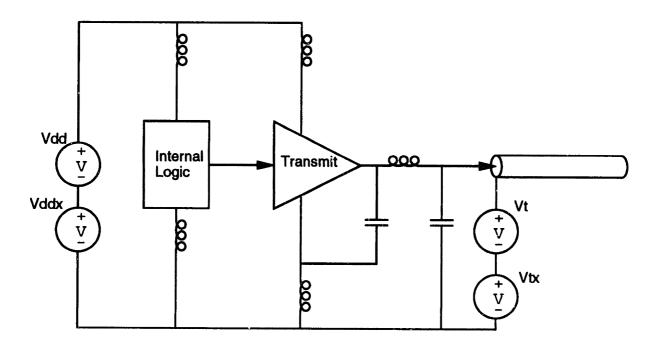

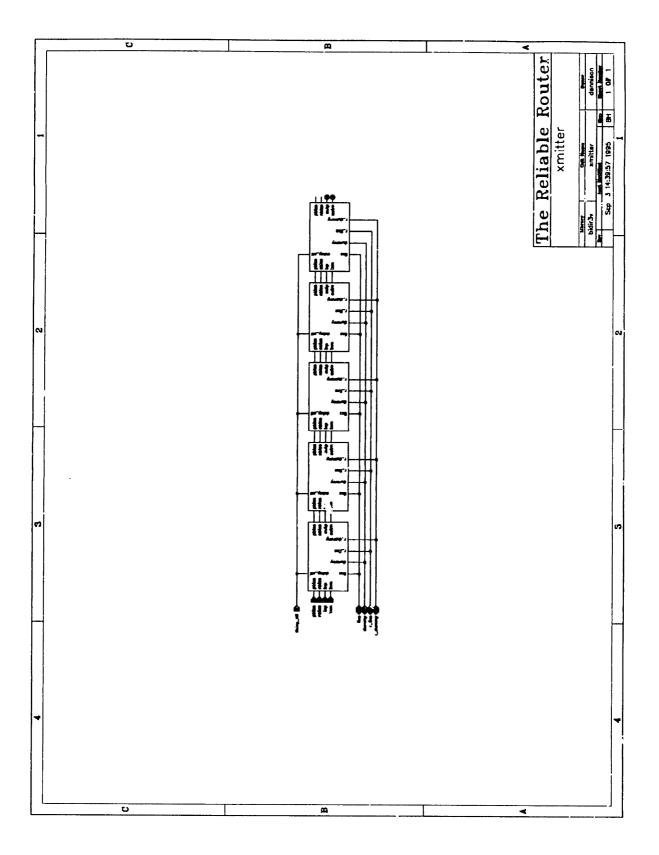

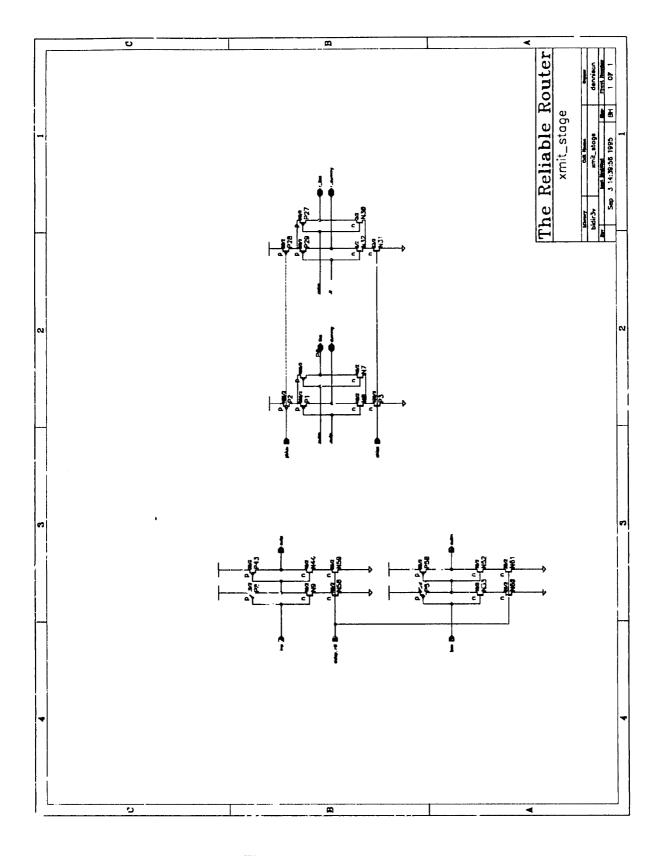

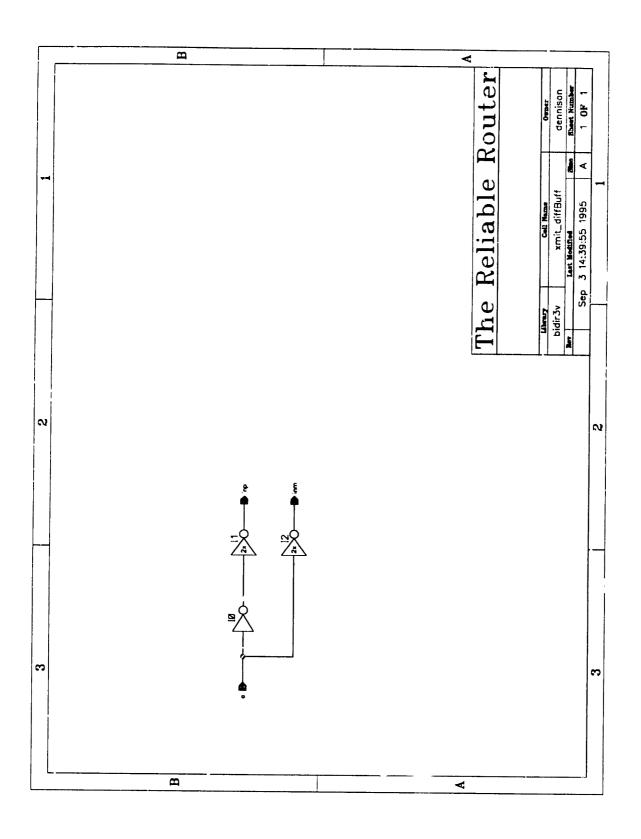

|   |      | 5.3.1   | Transmitter                                               |

|   |      | 5.3.2   | Transmission line and termination 68                      |

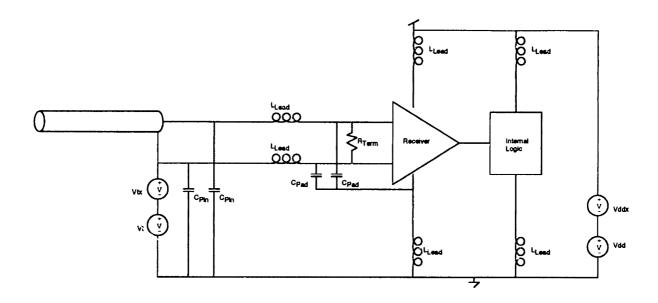

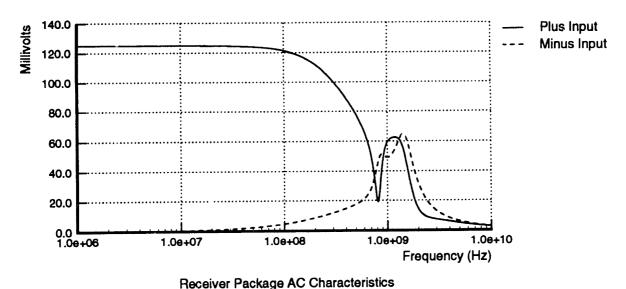

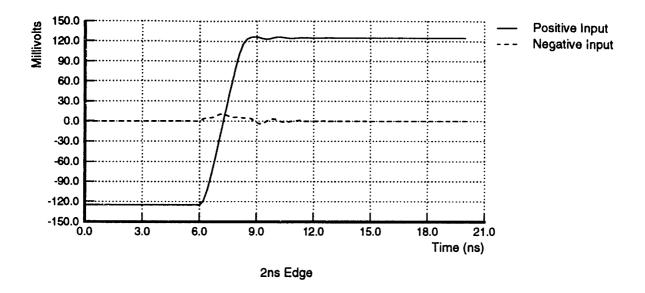

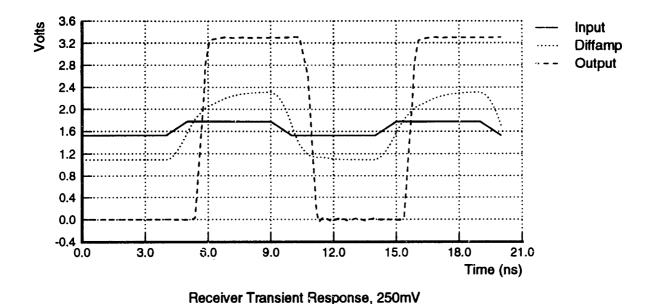

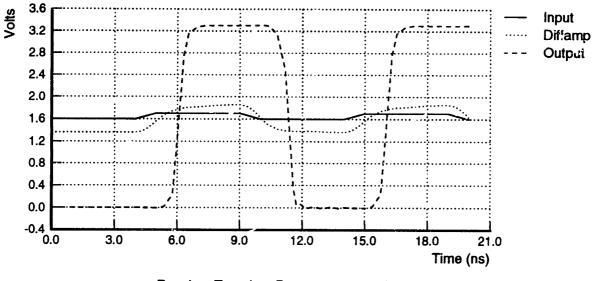

|   |      | 5.3.3   | Receiver                                                  |

|   |      | 5.3.4   | Undirectional Signalling Summary                          |

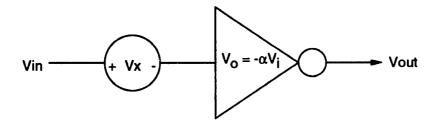

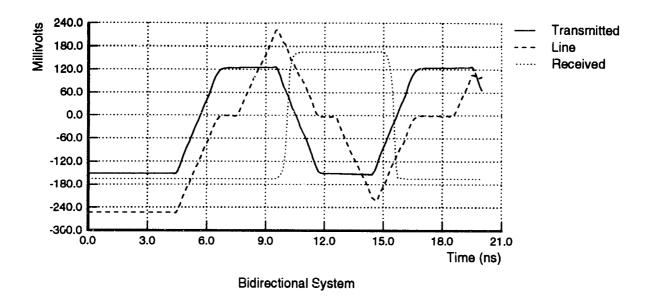

|   | 5.4  | Bidire  | ctional Signalling                                        |

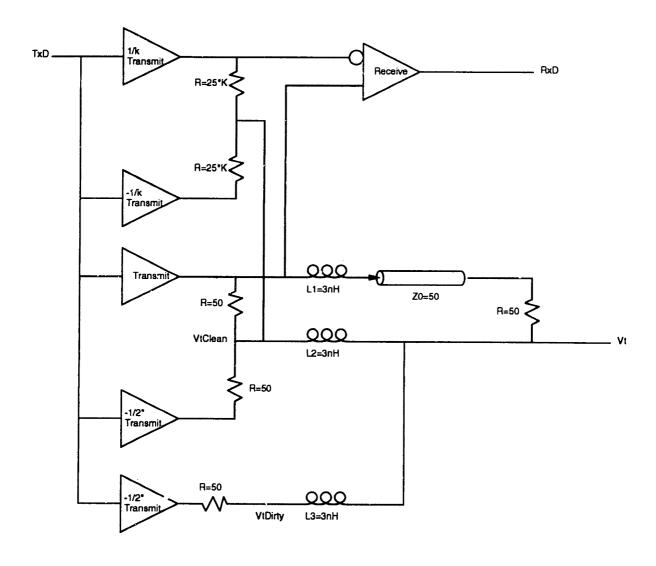

|   |      | 5.4.1   | Additional Bidirectional Noise Factors                    |

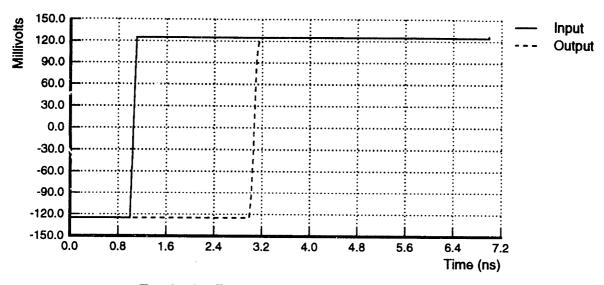

|   |      | 5.4.2   | Driver Output Impedance                                   |

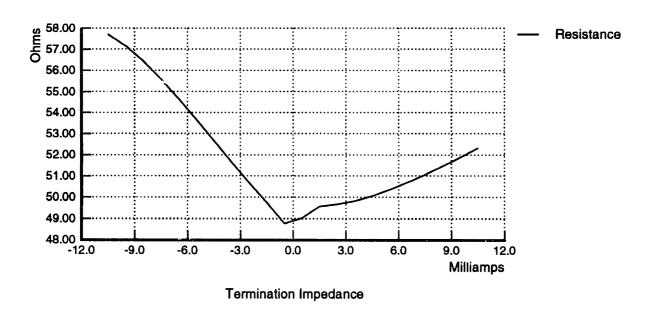

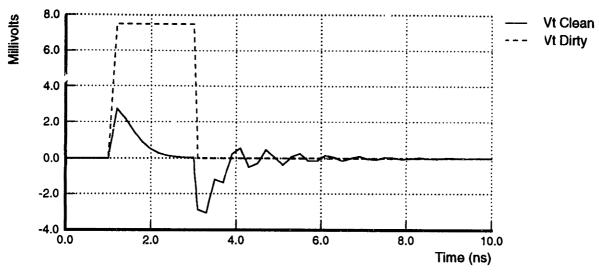

|   |      | 5.4.3   | Termination Nonlinearity                                  |

|   |      | 5.4.4   | Large Common-Mode Signal                                  |

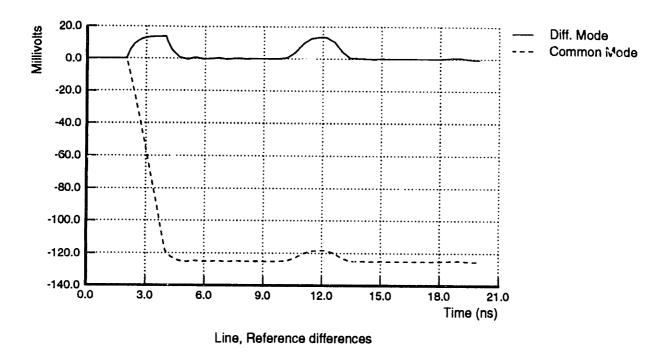

|   |      | 5.4.5   | Discrepencies between the line and reference waveforms 77 |

|   |      | 5.4.6   | Additional Noise Sources                                  |

|   |      | 5.4.7   | The Noise Margins                                         |

|   |      | 5.4.8   | Summary of Bidirectional Signalling 80                    |

|   | 5.5  | Summ    | ary                                                       |

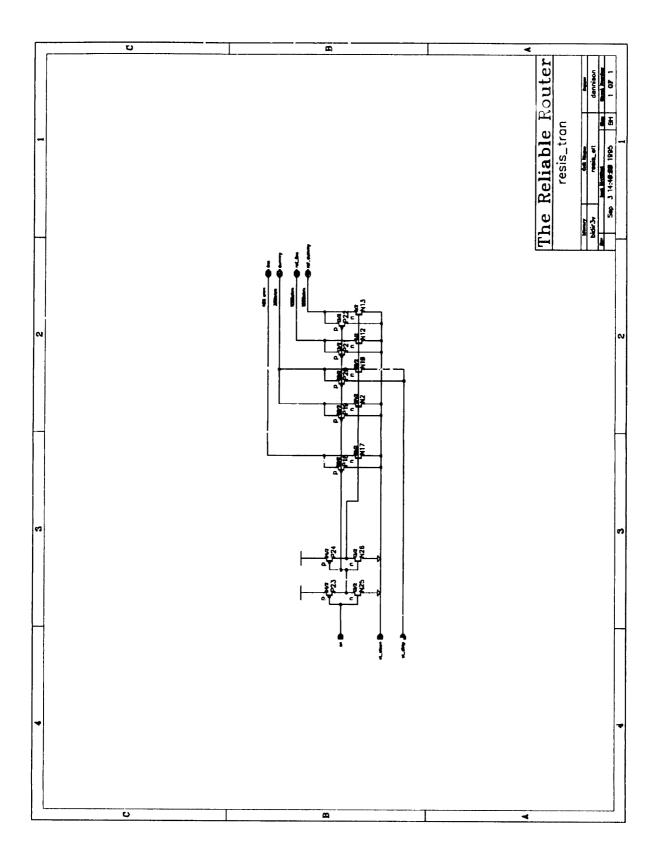

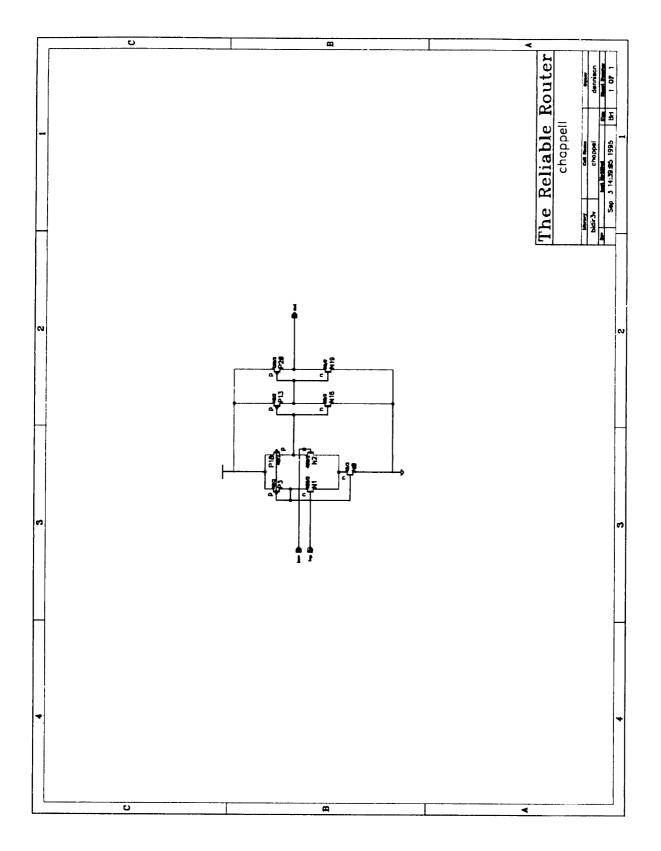

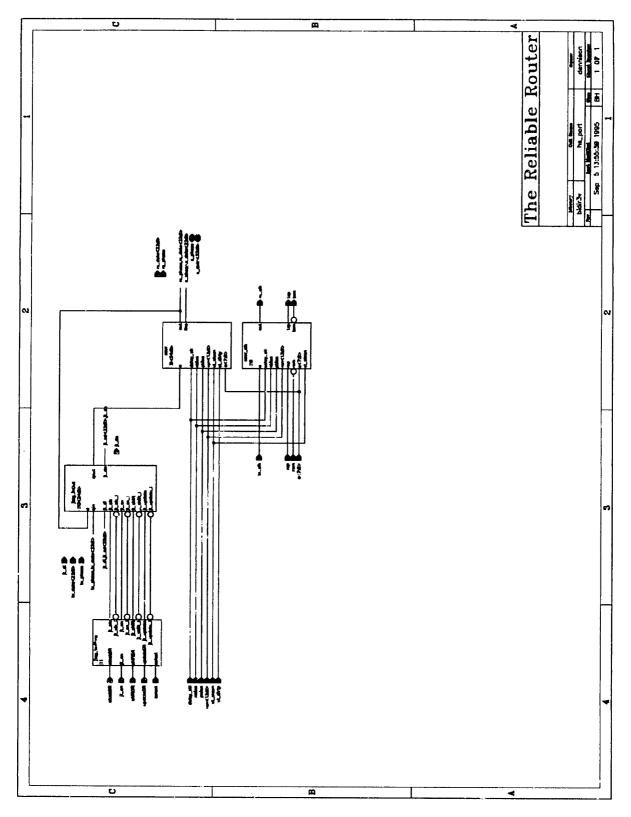

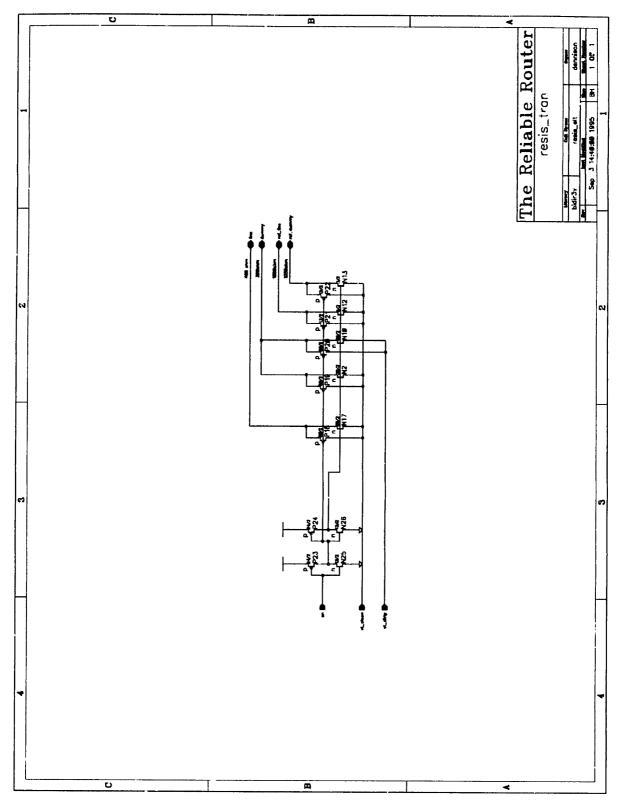

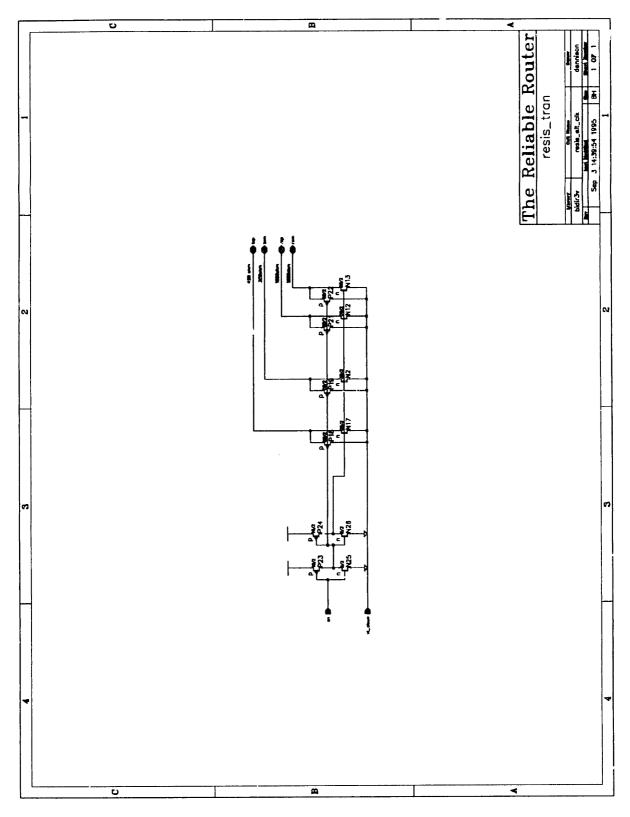

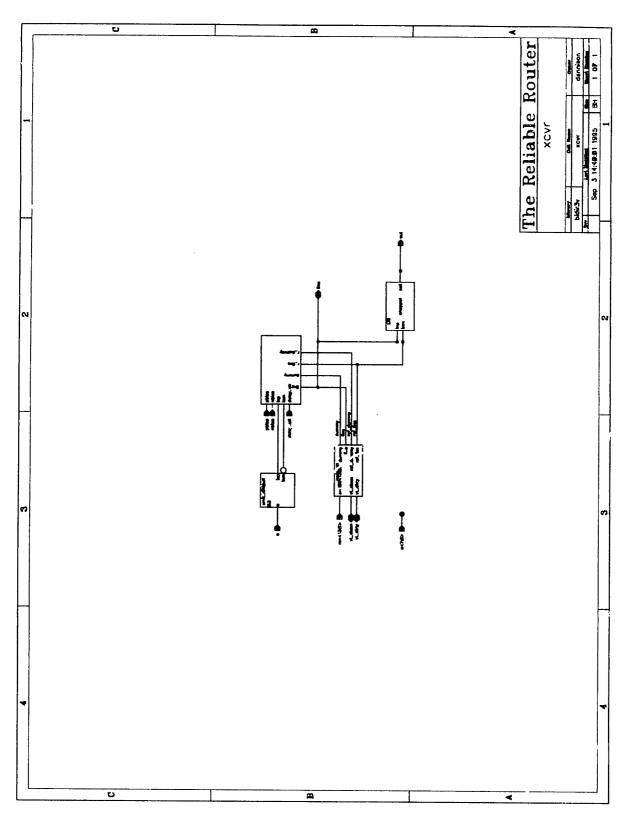

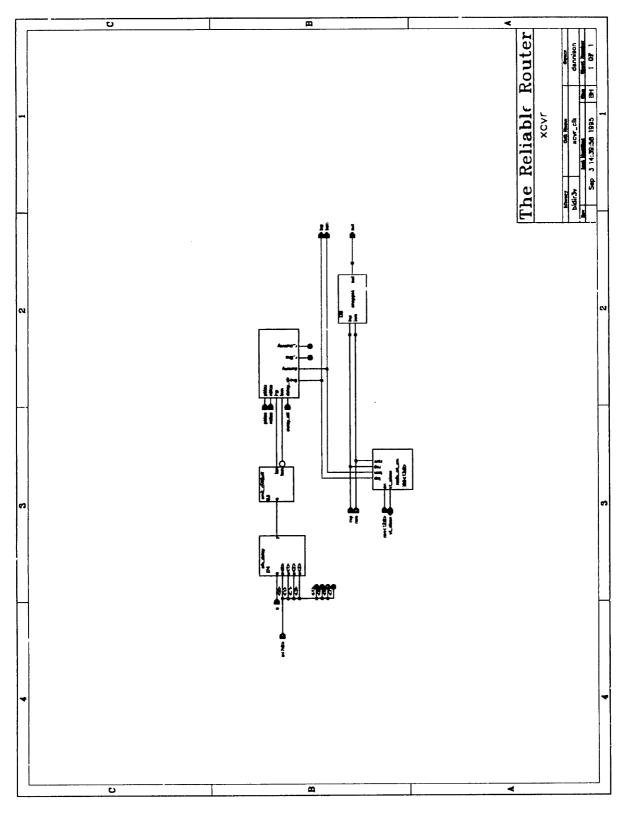

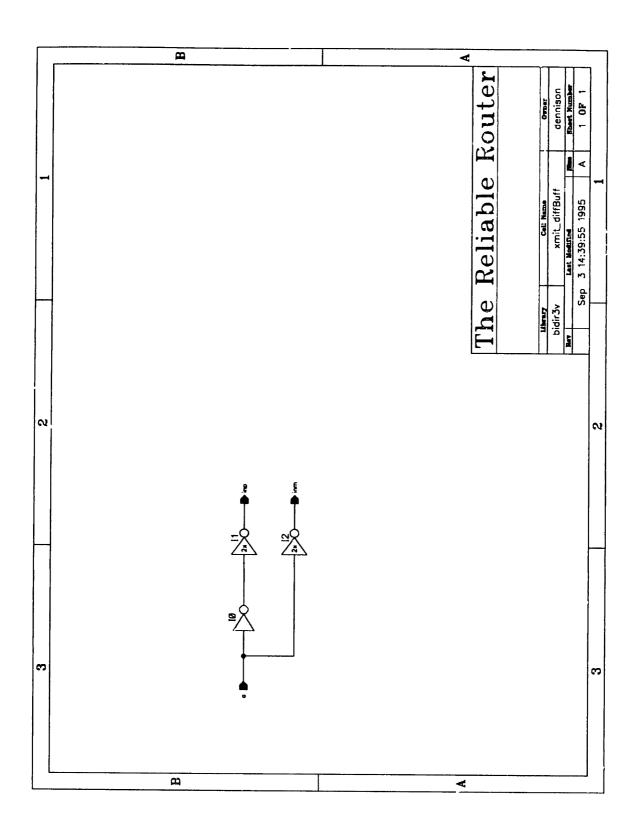

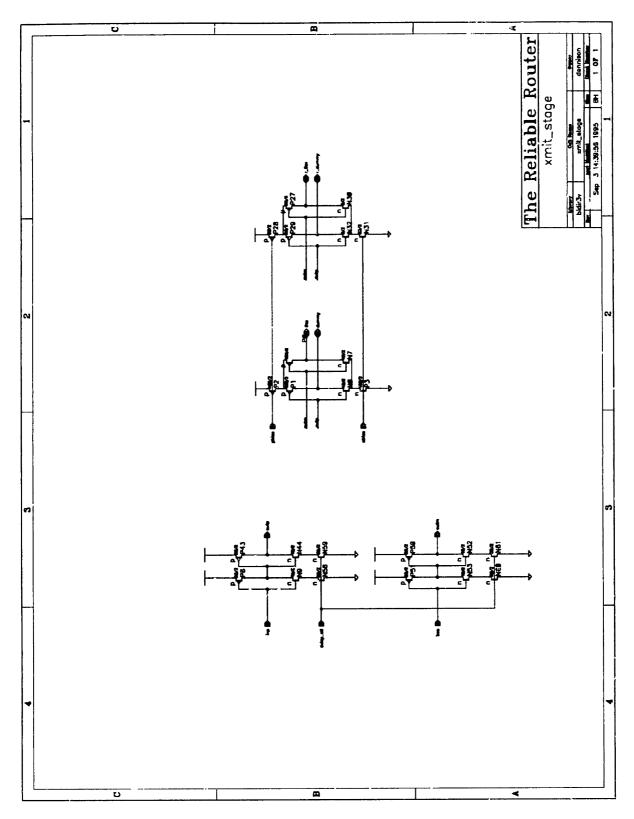

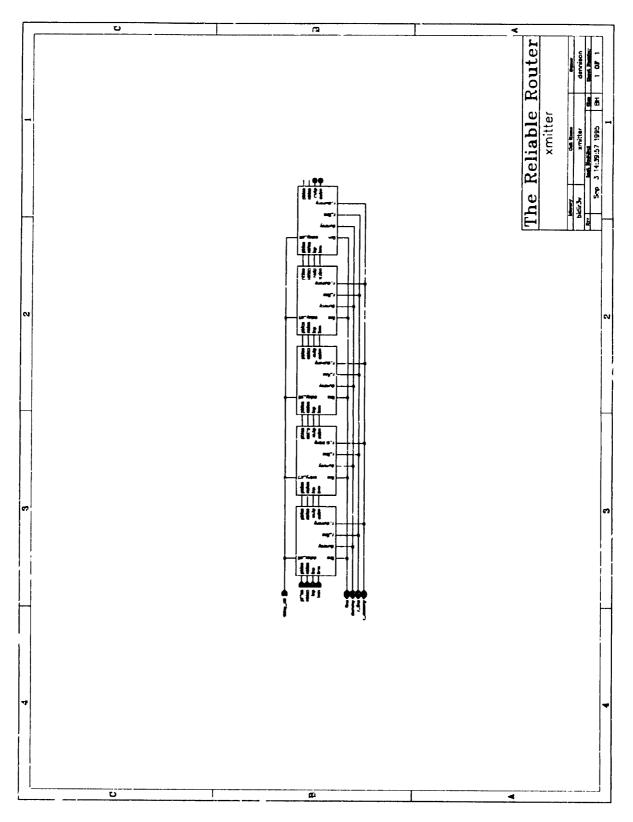

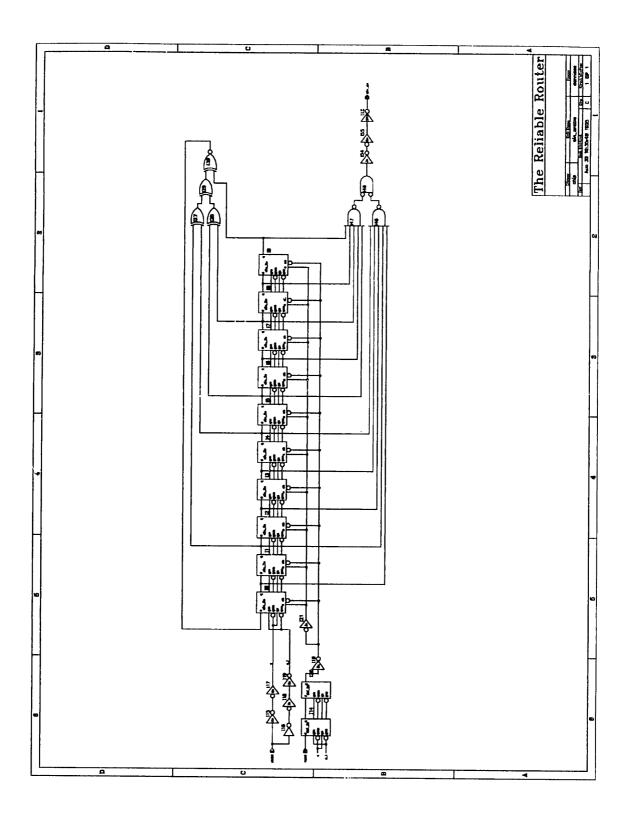

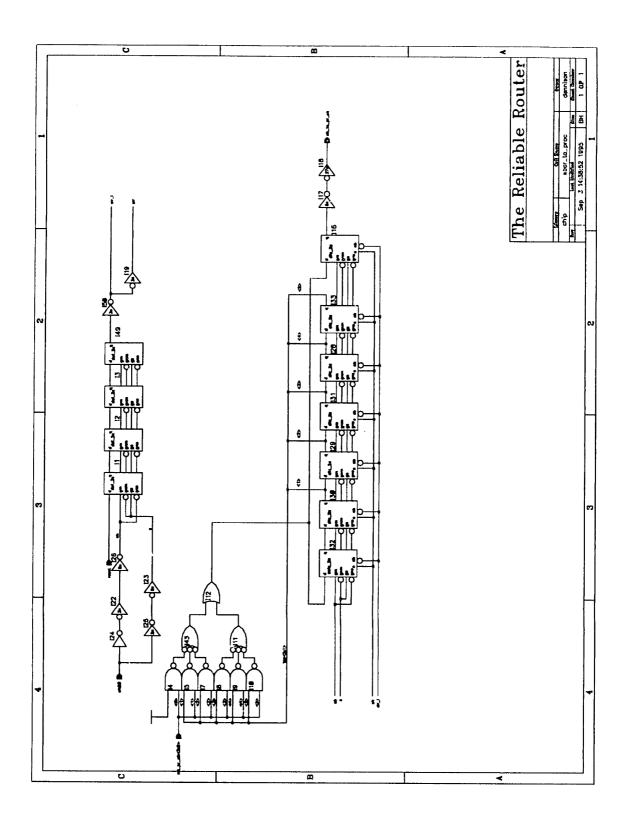

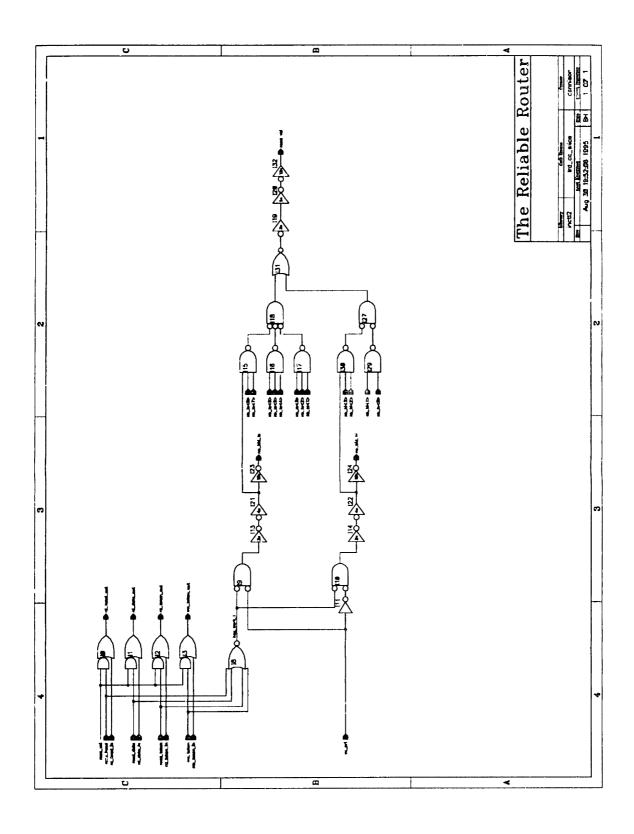

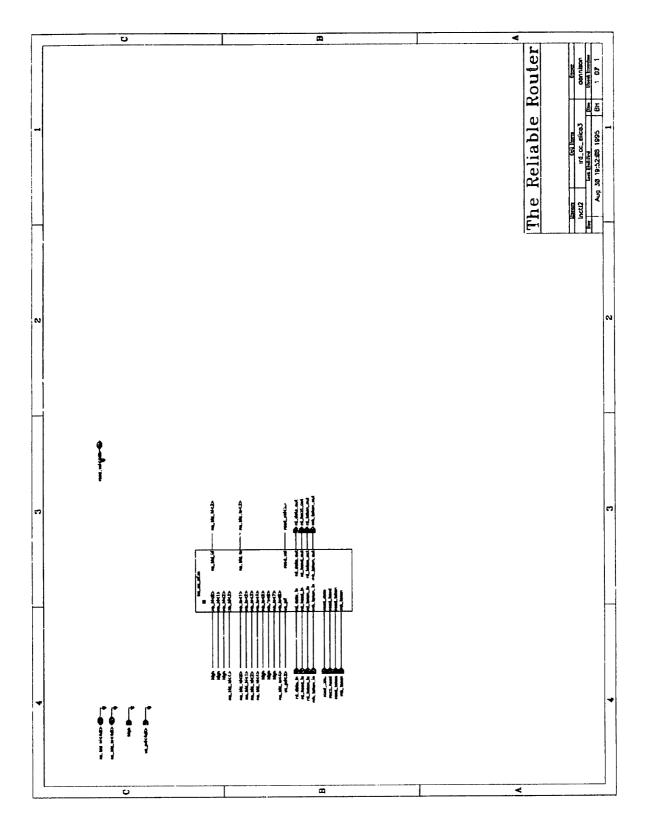

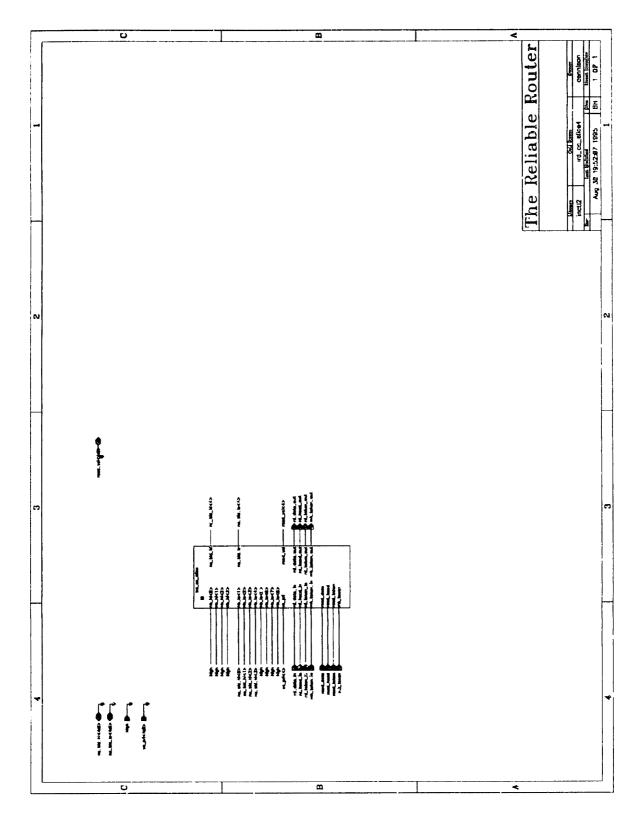

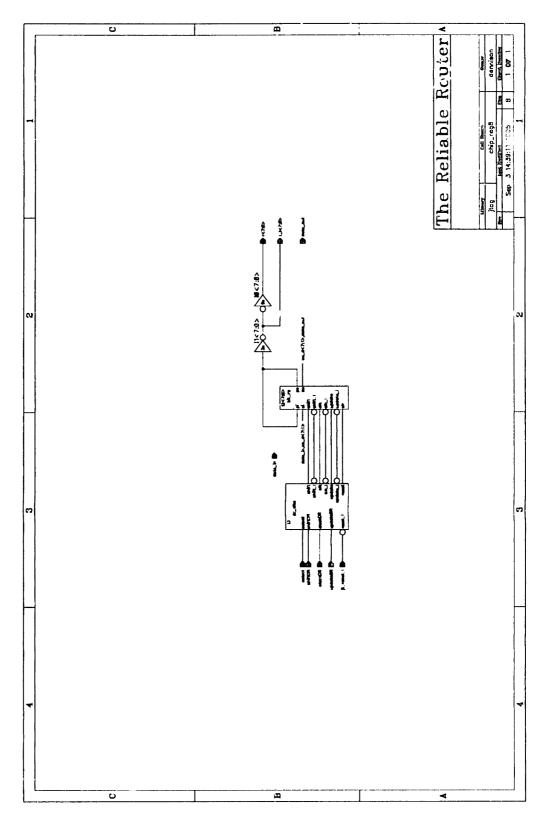

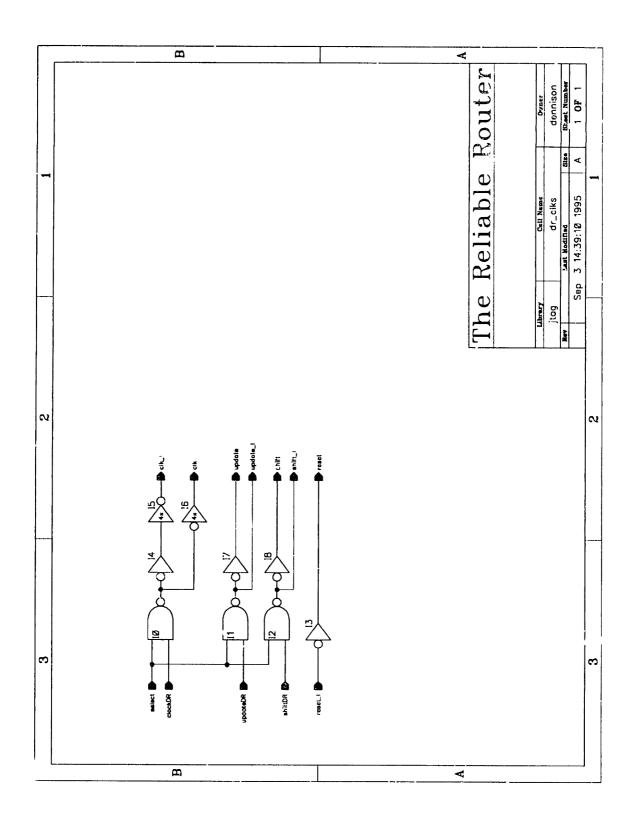

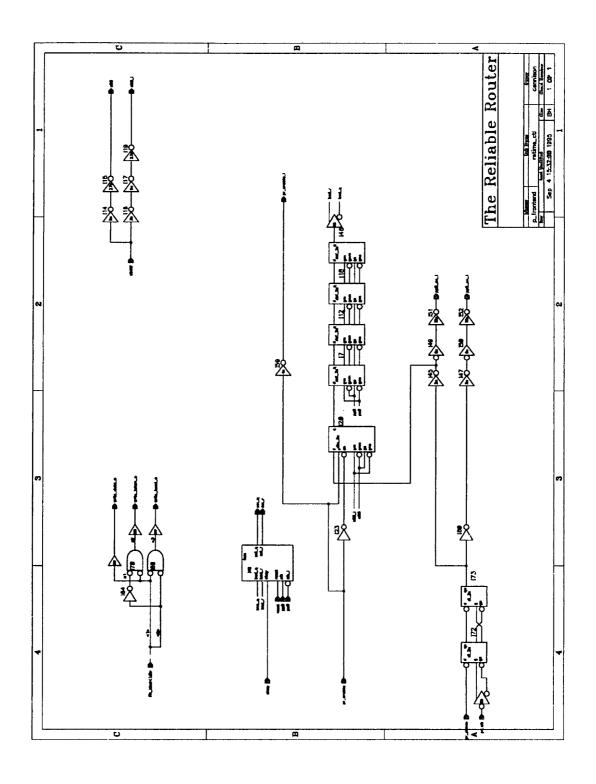

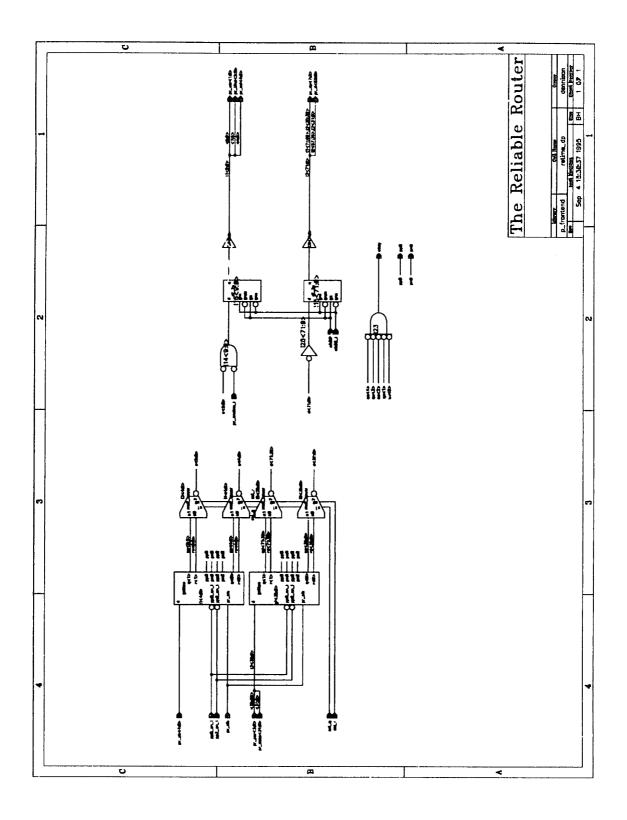

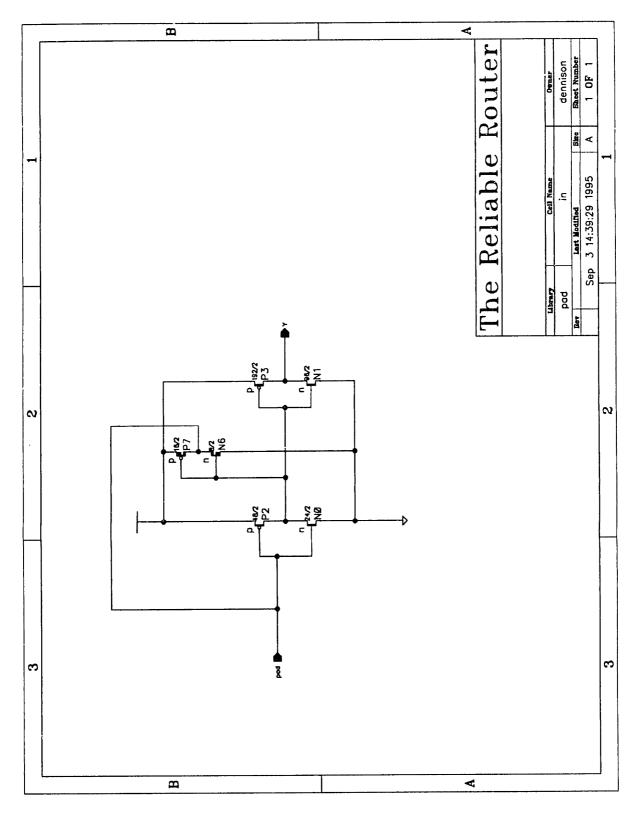

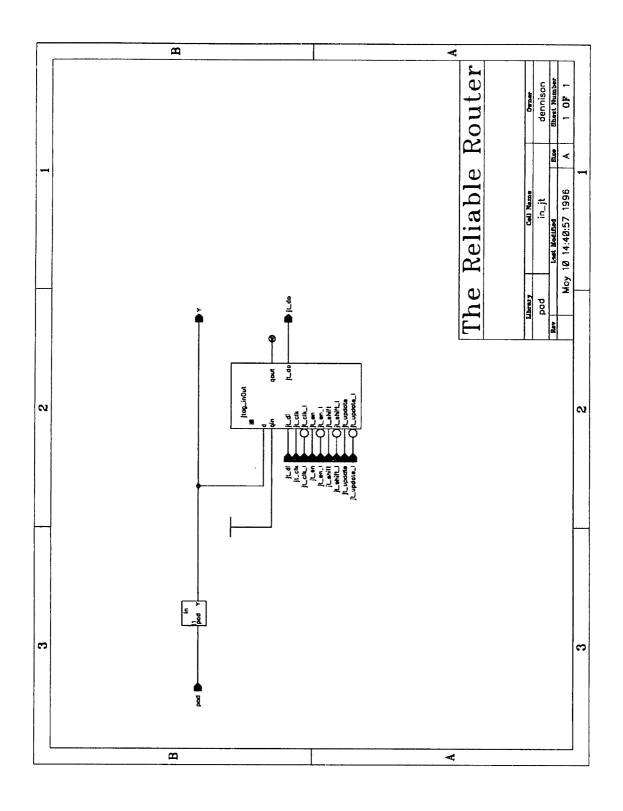

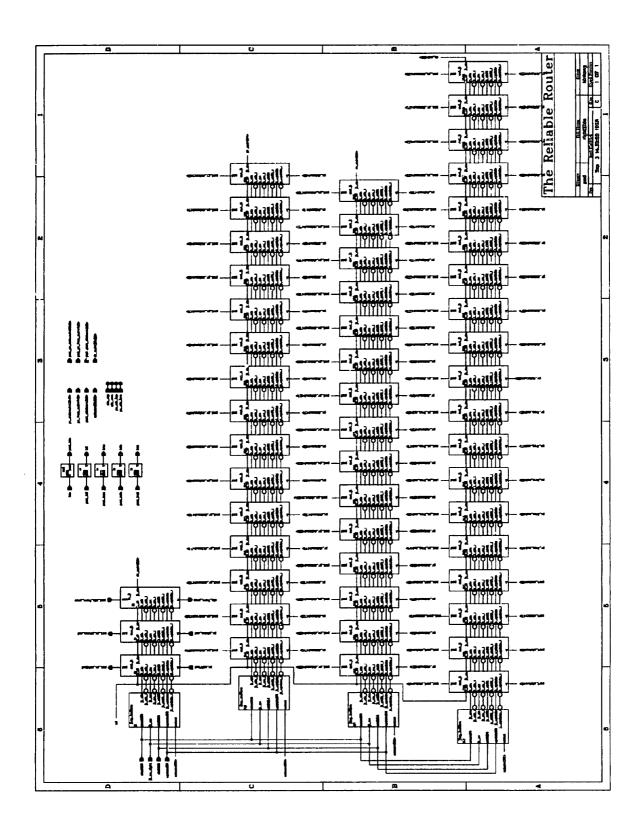

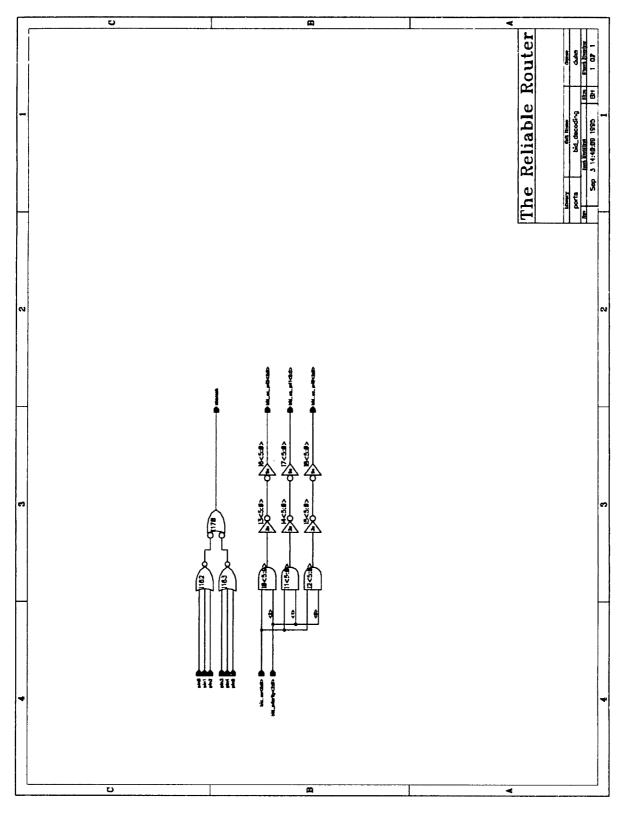

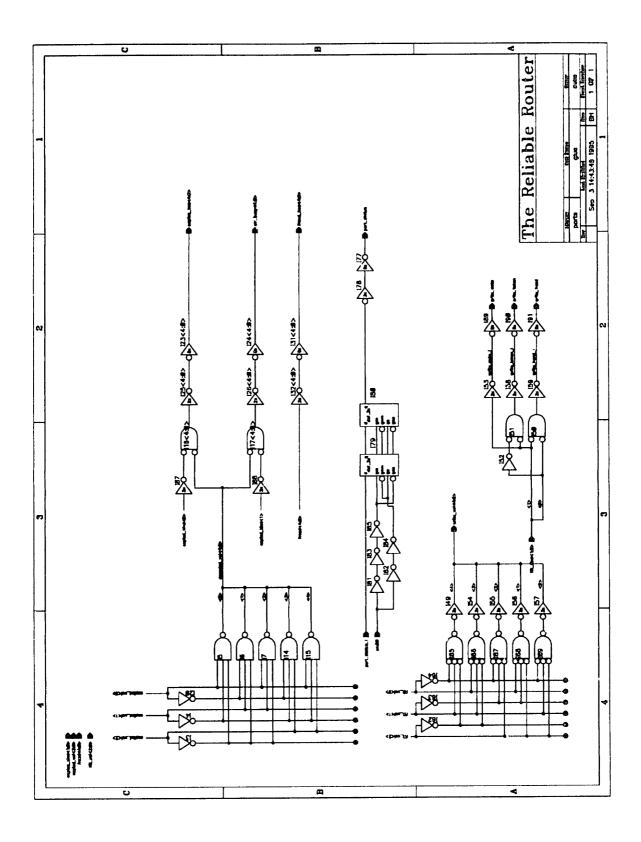

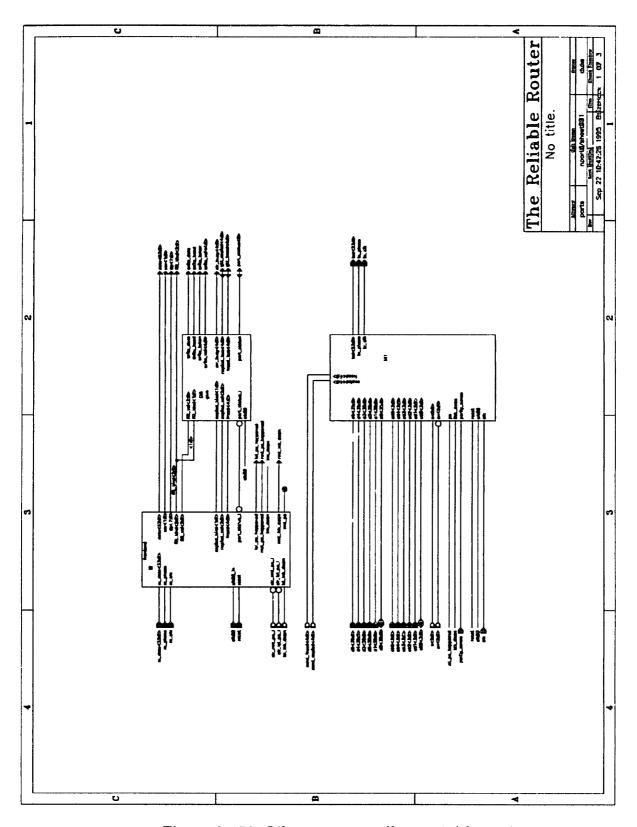

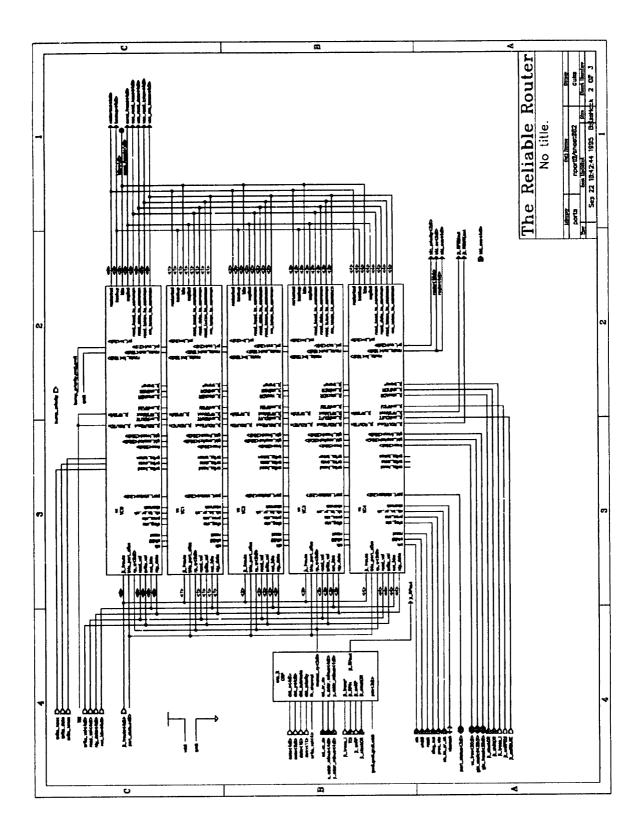

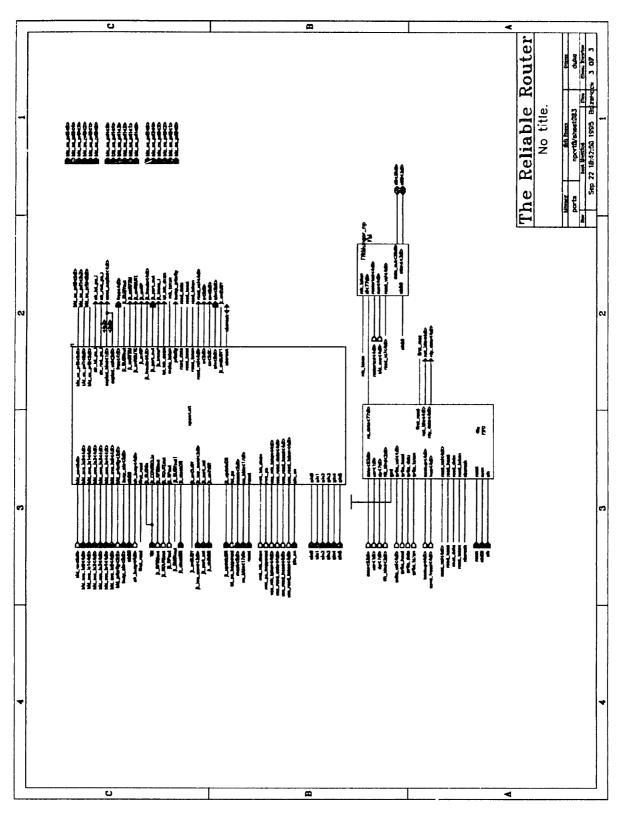

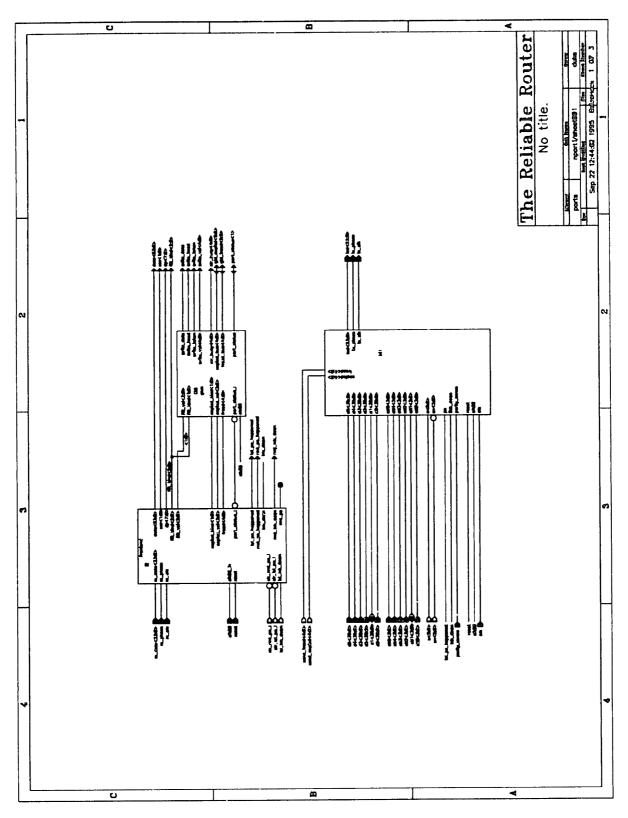

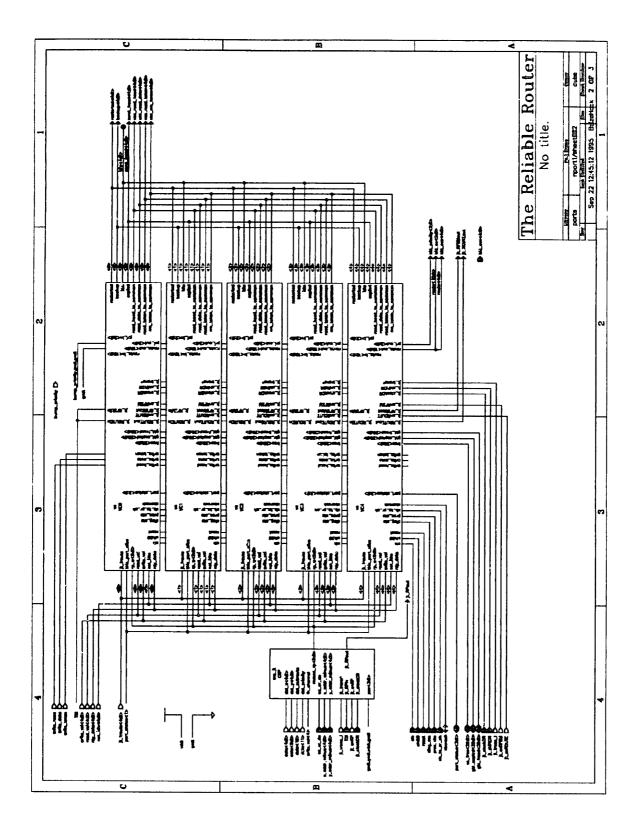

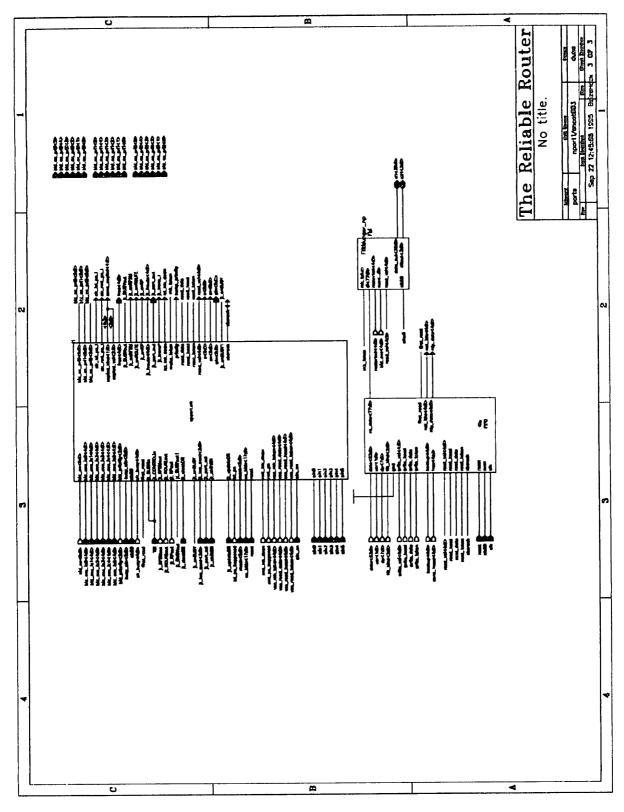

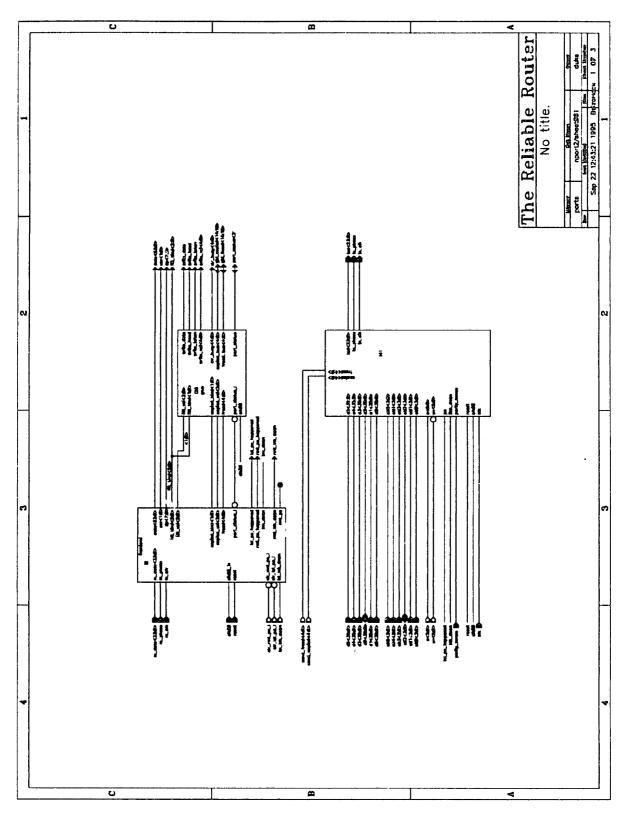

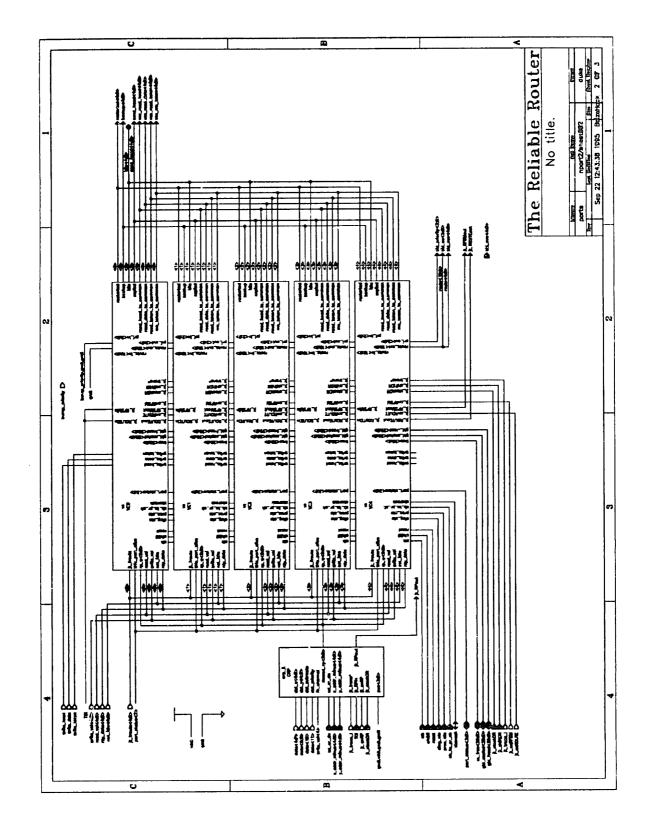

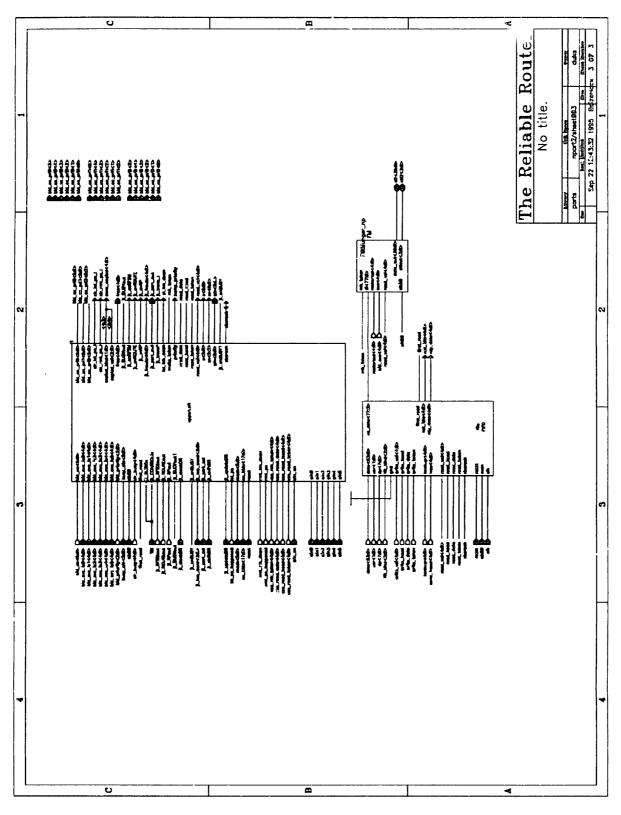

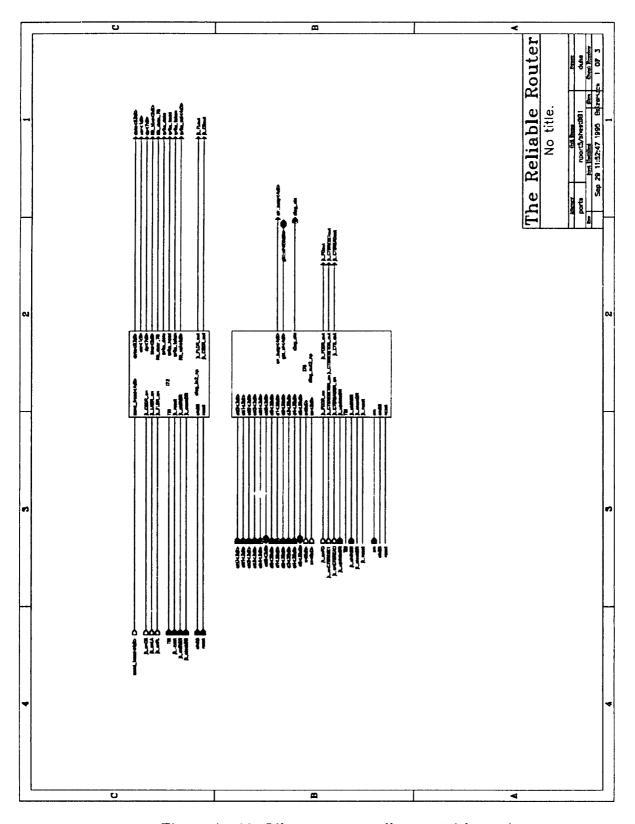

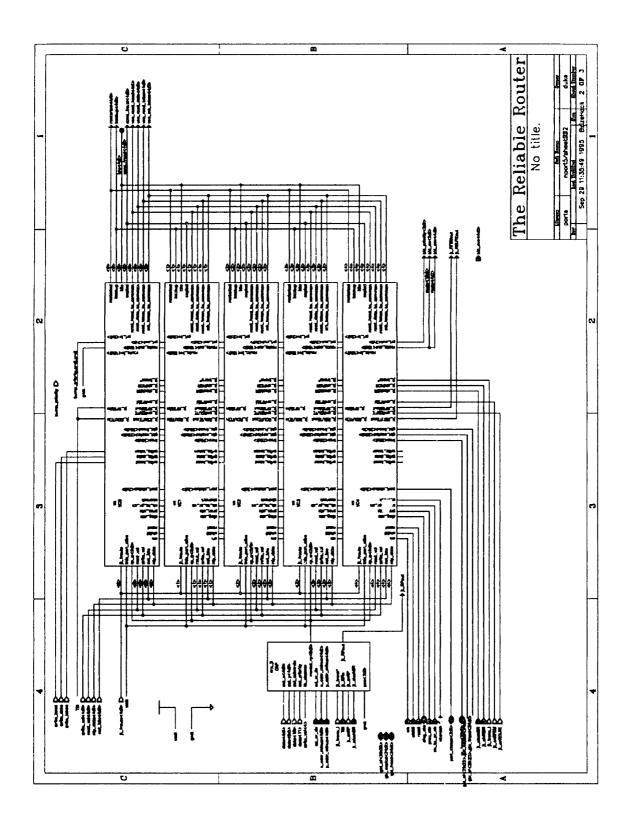

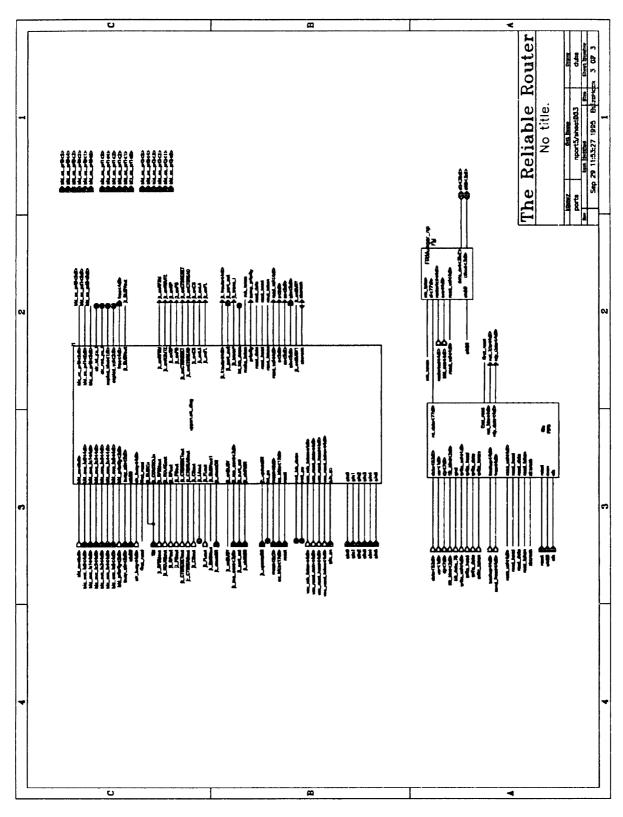

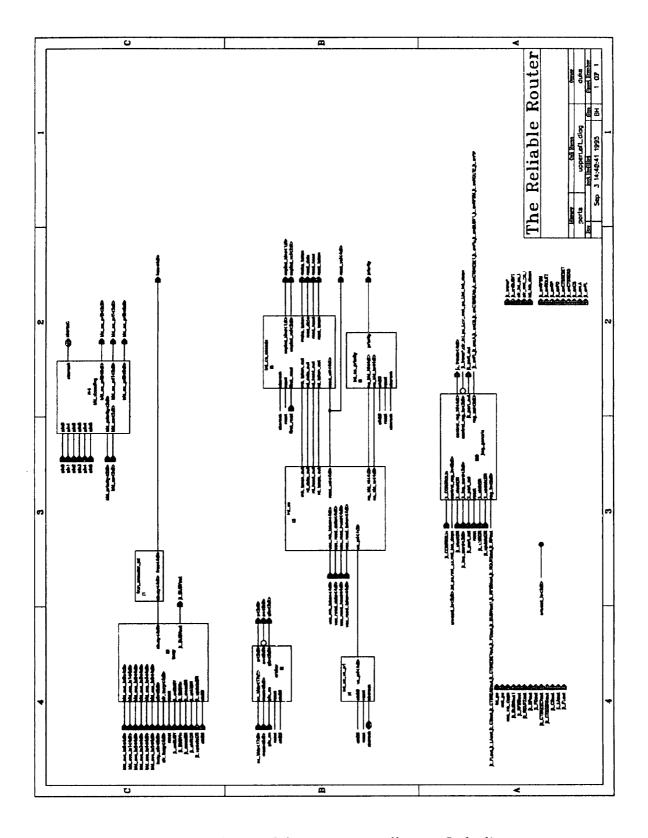

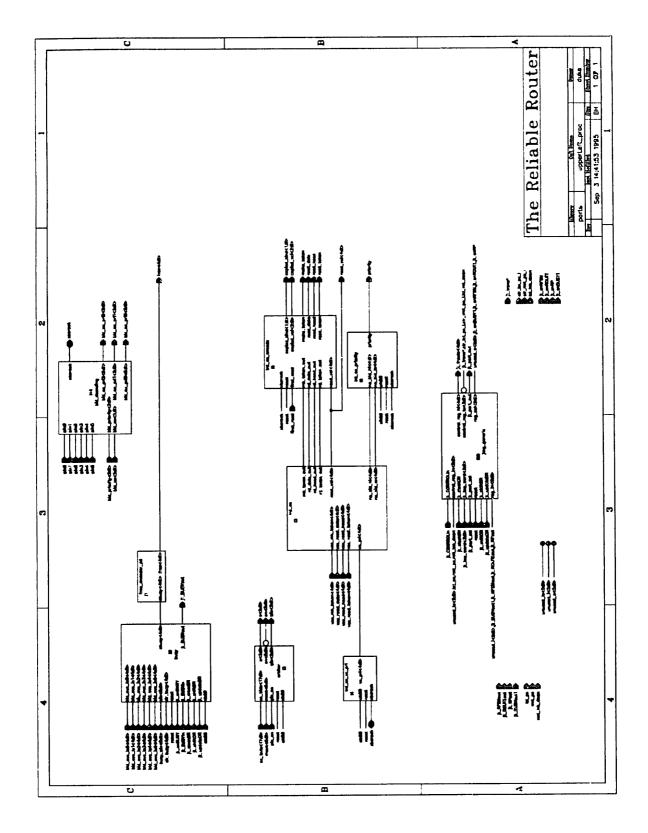

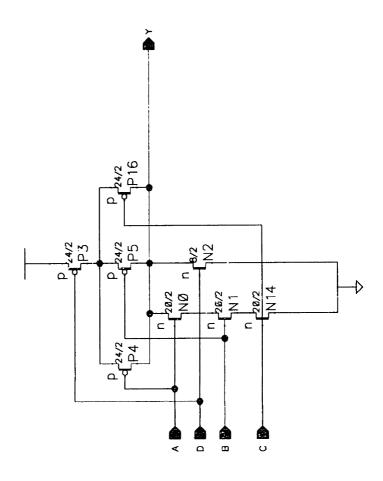

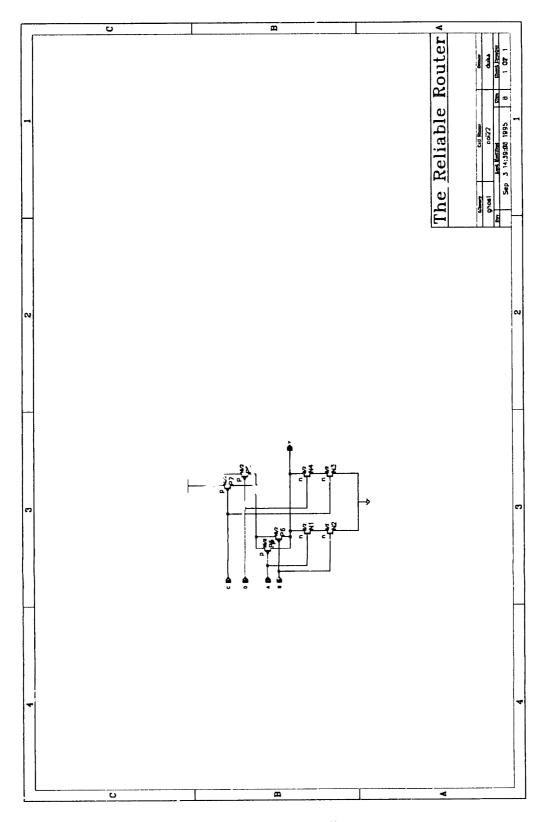

|   | 5.6  |         | atics                                                     |

|   |      |         |                                                           |

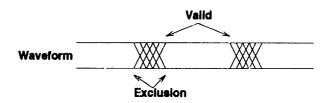

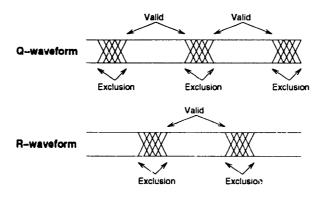

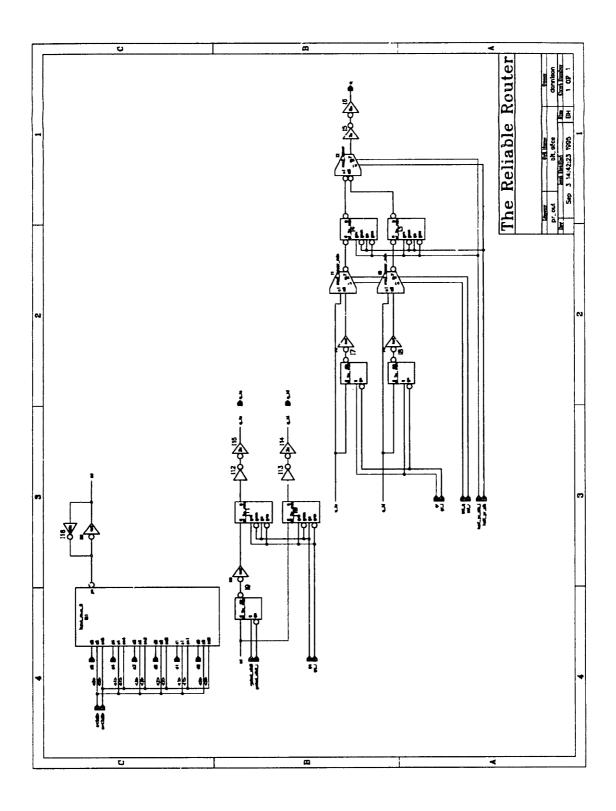

| 6 | Low  | /-Later | ncy Plesiochronous Data Retiming 88                       |

|   | 6.1  |         | round                                                     |

|   | 6.2  | Plesio  | chronous Requirements                                     |

|   | 6.3  |         | ing                                                       |

|   |      | 6.3.1   | Mesochronous Retiming                                     |

|   |      | 6.3.2   | Plesiochronous Retiming                                   |

|   |      | 6.3.3   | Correct Plesiochronous Retiming                           |

|   | 6.4  | Circui  | t Pragmatics                                              |

|   |      | 6.4.1   | Modeling Flip-Flops                                       |

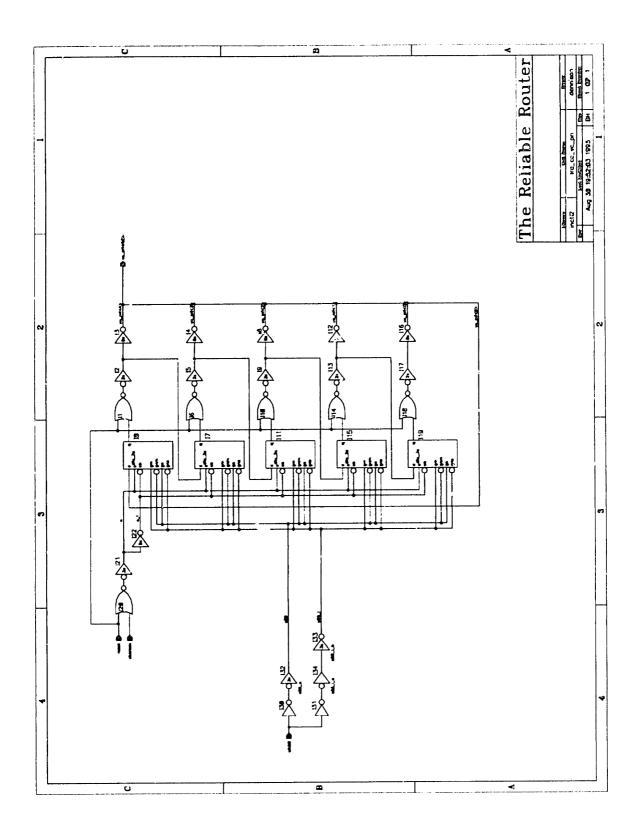

|   |      | 6.4.2   | Circuit Details                                           |

|   | 6.5  | Latend  | y                                                         |

|   | 6.6  | Non-D   | ata Transmission Rate                                     |

|   |      | 6.6.1   | Best Case Non-Data Transmission Rate 100                  |

|   |      | 6.6.2   | The Effect of Jitter                                      |

|   | 6.7  | Casca   | ling Plesiochronous Retiming Stages                       |

|   |      | 6.7.1   | The Need for Local Timing Requirements                    |

|   |      | 6.7.2   | The Source Data Rate                                      |

|   | 6.8  | Integra | al Subrate Extensions                                     |

|   | 6.9  |         | parison to Mesochronous Techniques                        |

|   | 6.10 |         | ary                                                       |

| 7 | Th   | e Microarchitecture of the Reliable Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106 |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

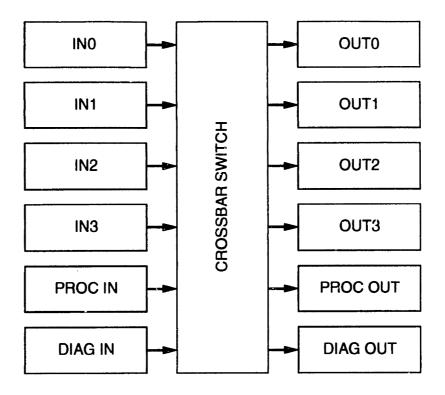

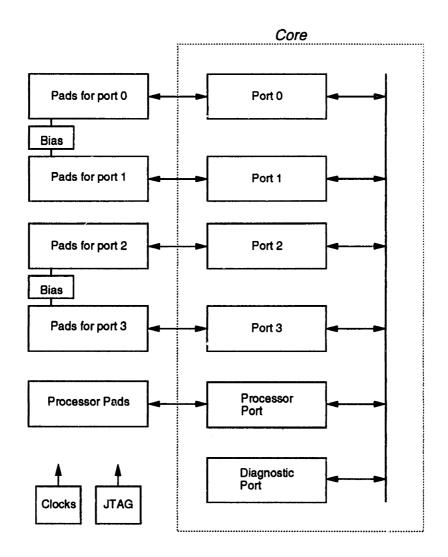

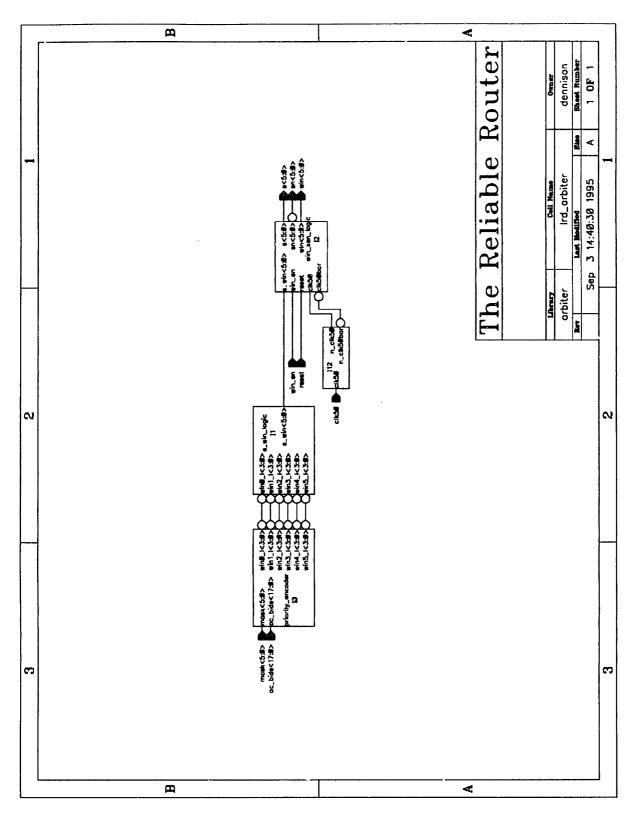

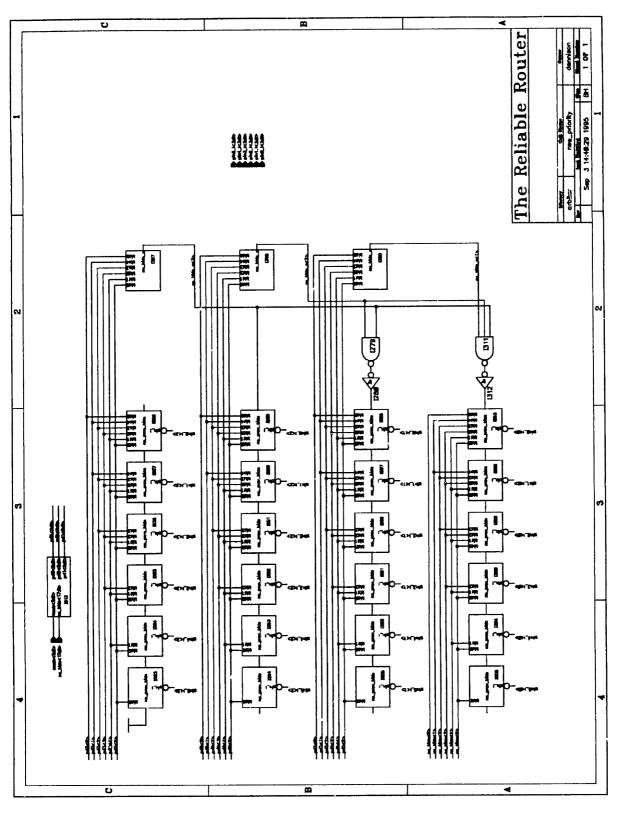

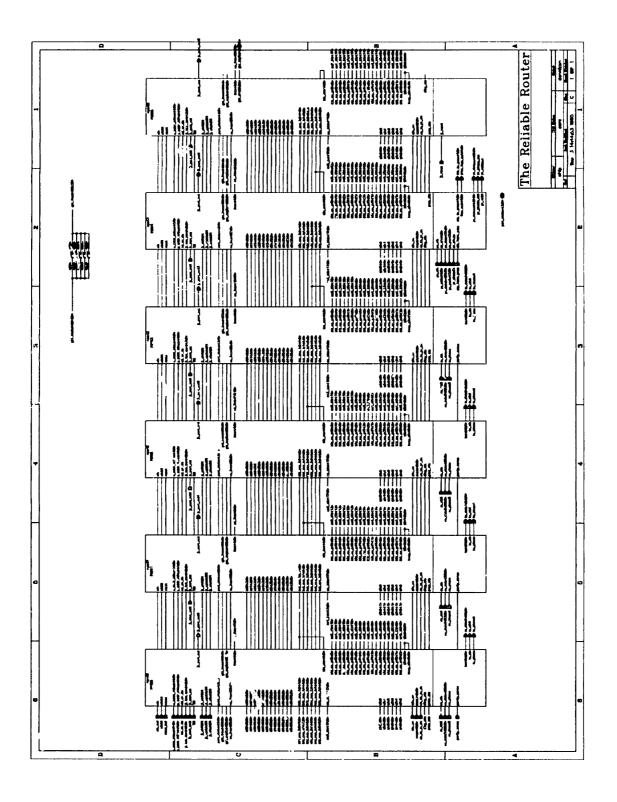

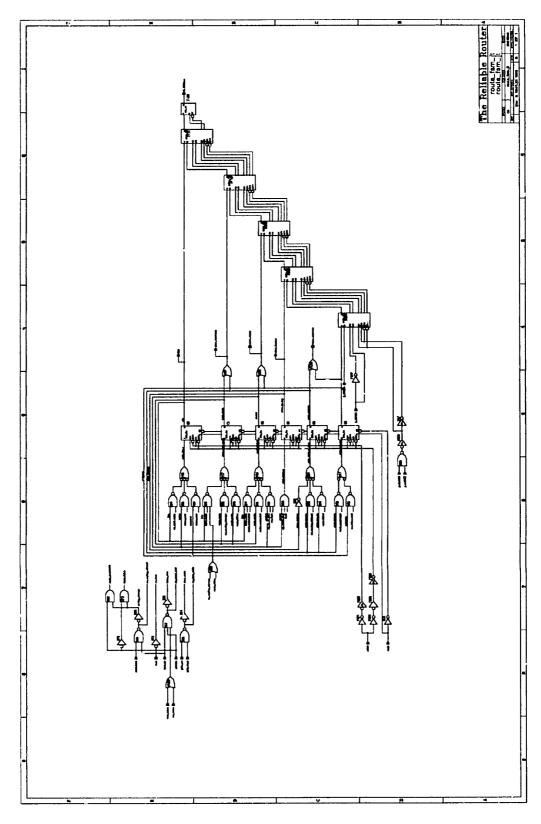

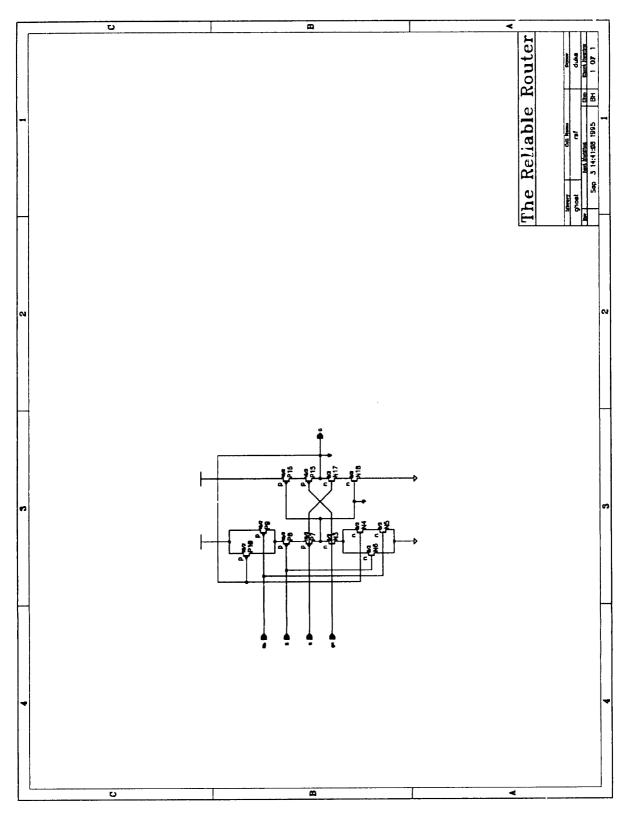

|   | 7.1  | Top Level Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106 |

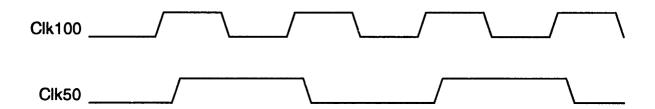

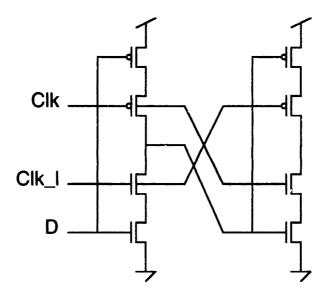

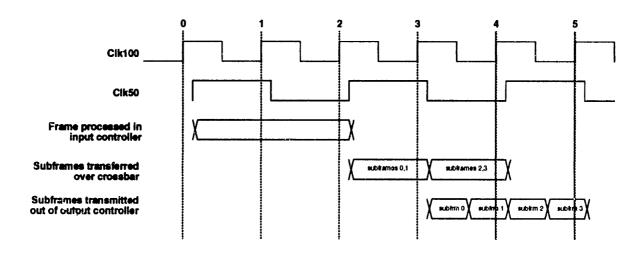

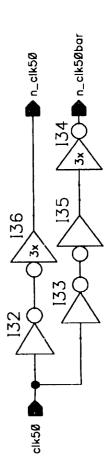

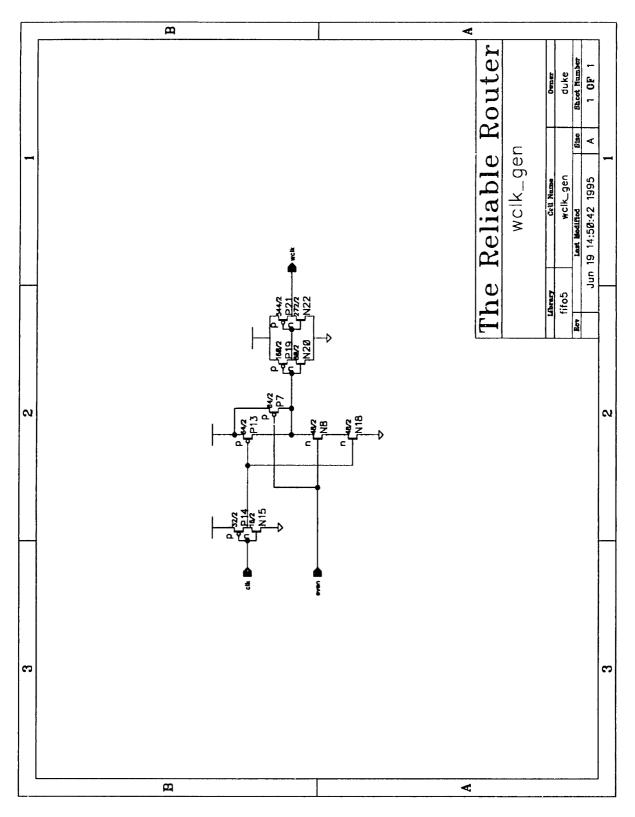

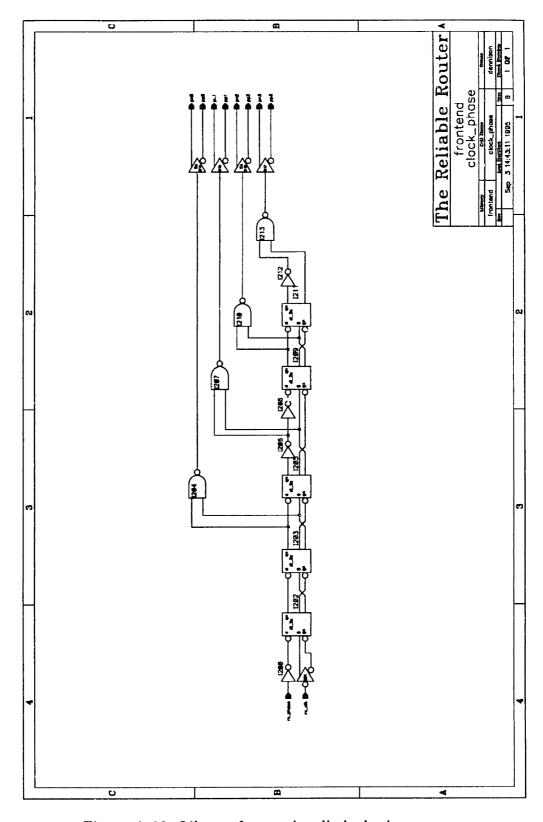

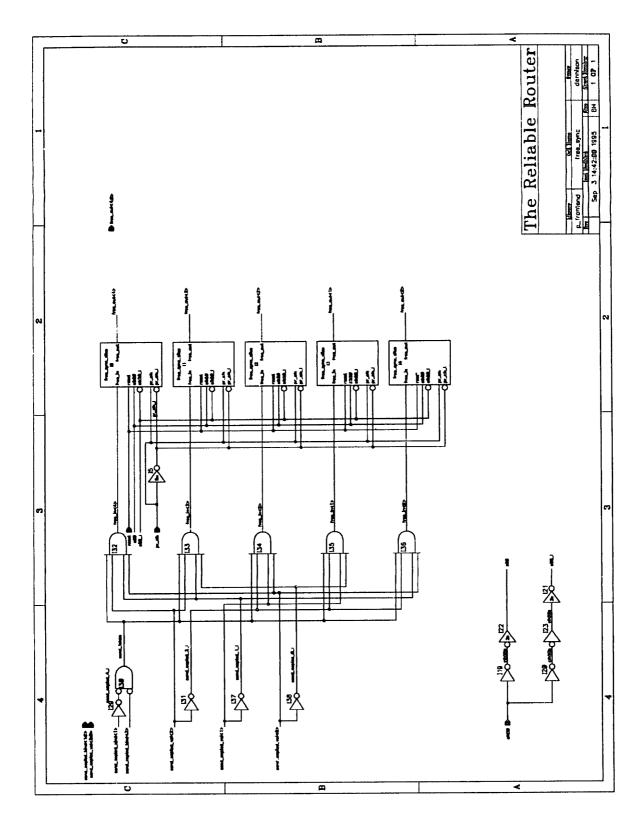

|   | 7.2  | Clocking and Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 108 |

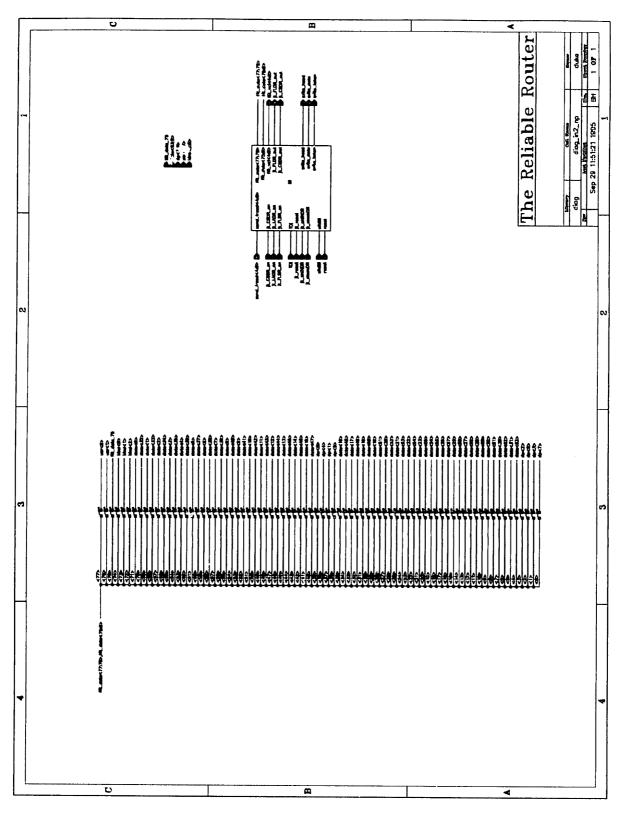

|   | 7.3  | Global Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110 |

|   |      | 7.3.1 General Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112 |

|   |      | 7.3.2 Routing Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112 |

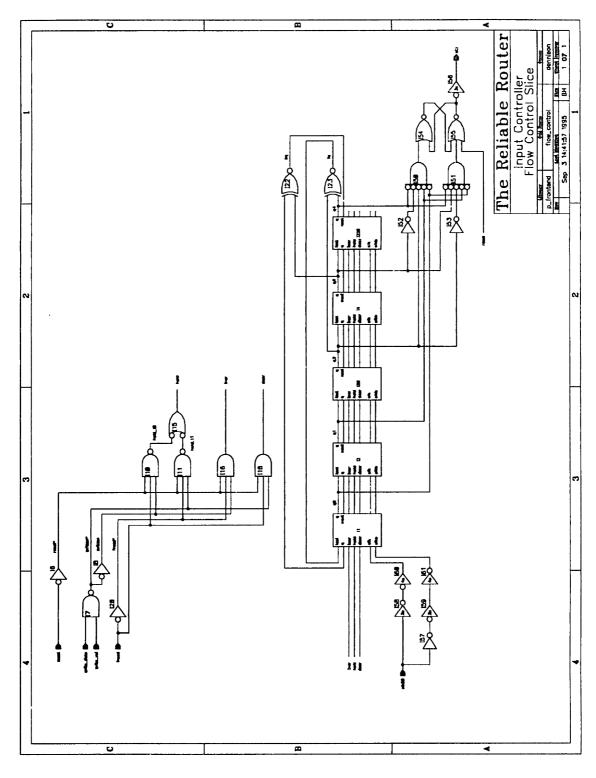

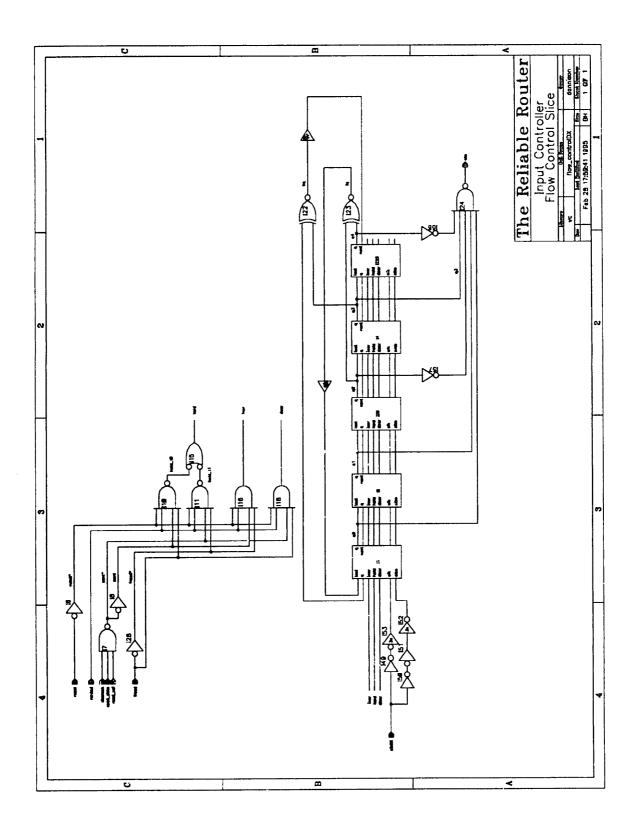

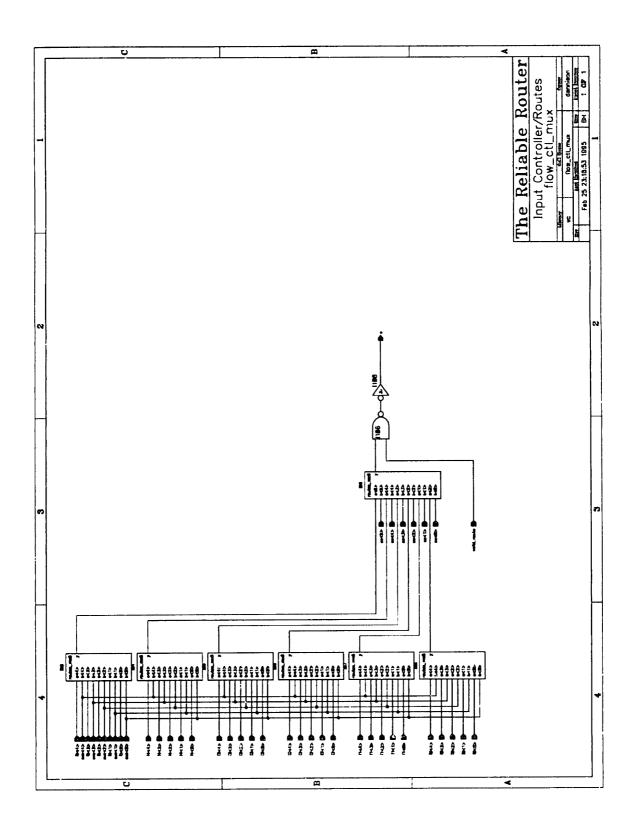

|   |      | 7.3.3 Flow Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 112 |

|   |      | 7.3.4 Crossbar Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113 |

|   | 7.4  | Top-level Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 115 |

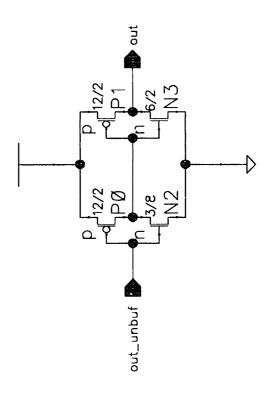

|   |      | 7.4.1 I/O Pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 115 |

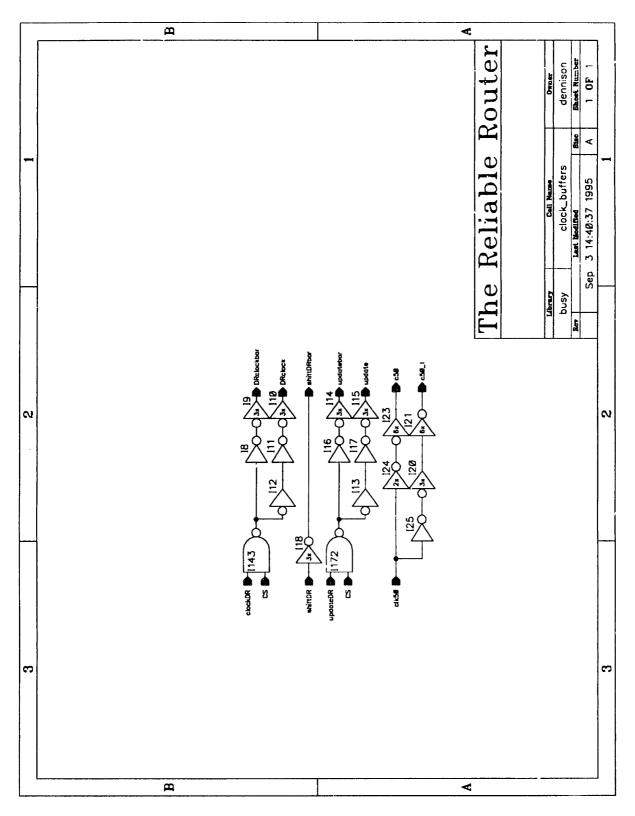

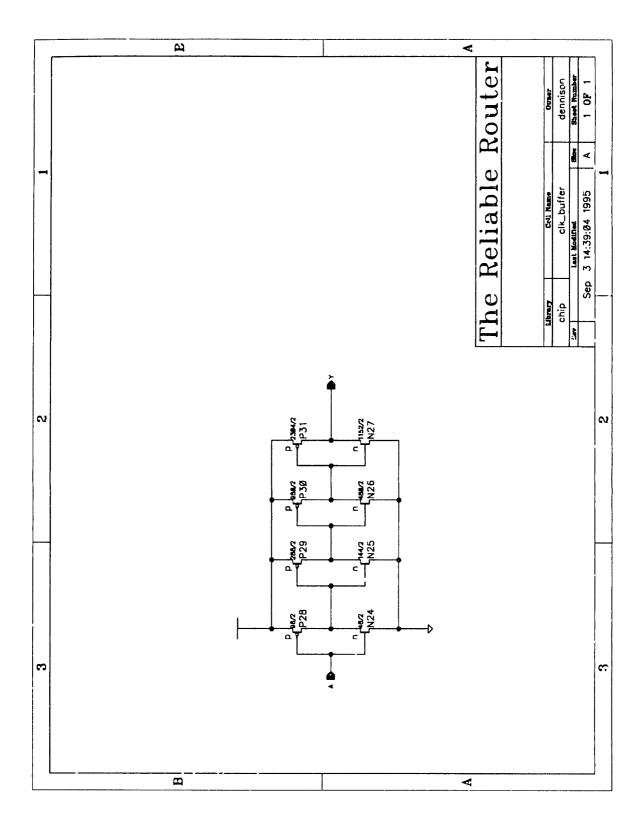

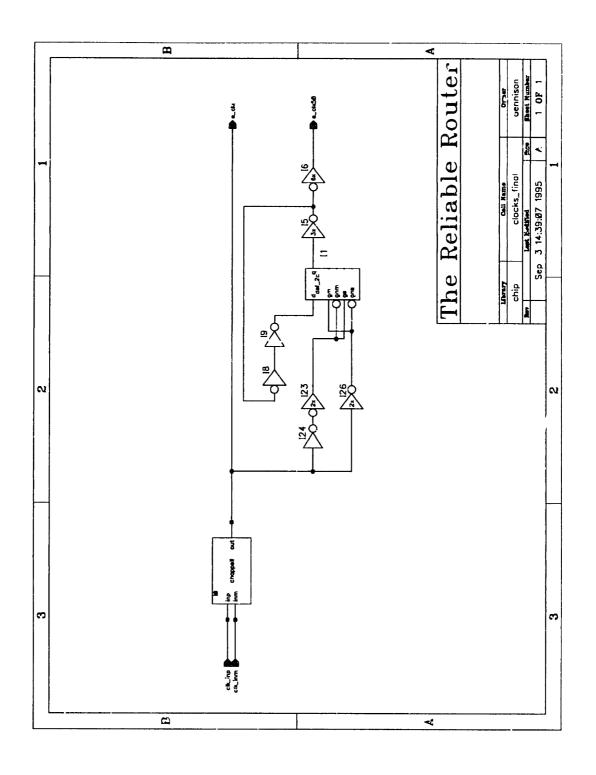

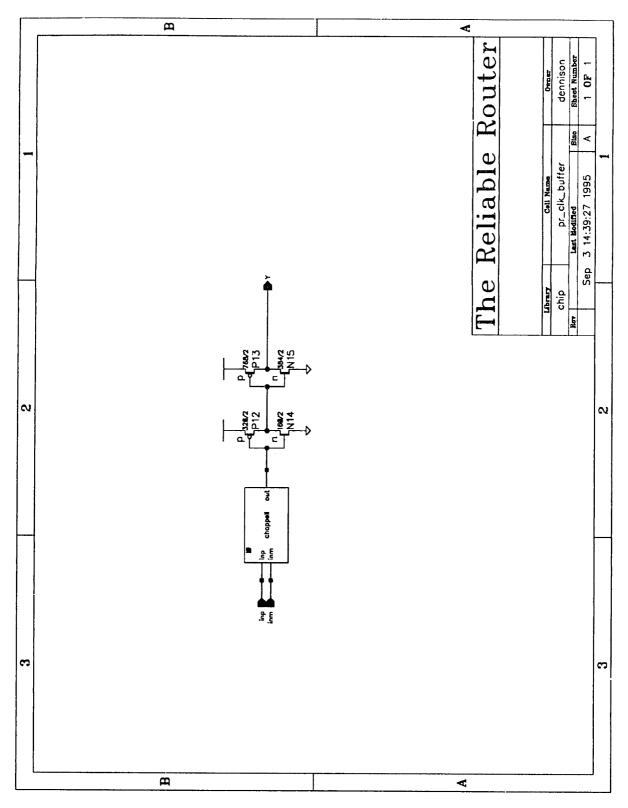

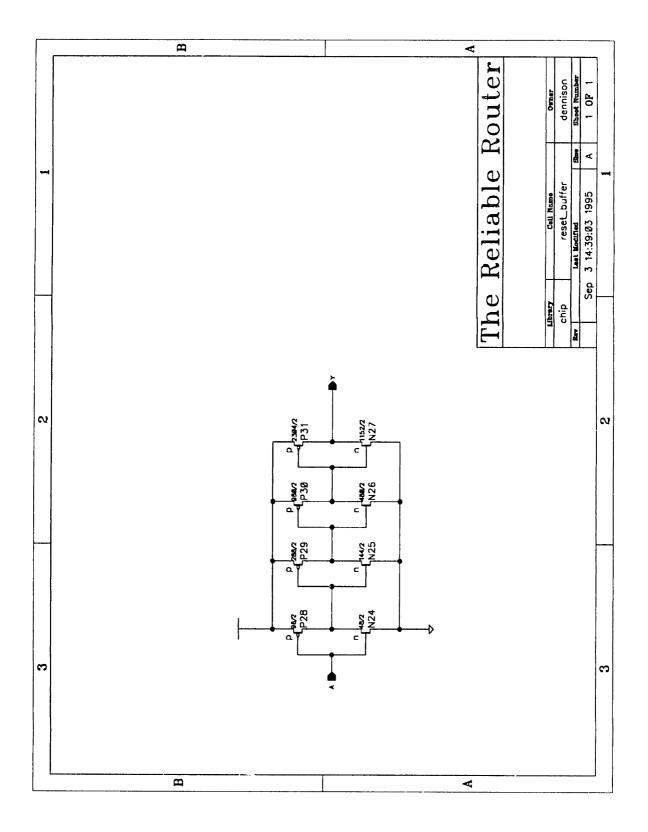

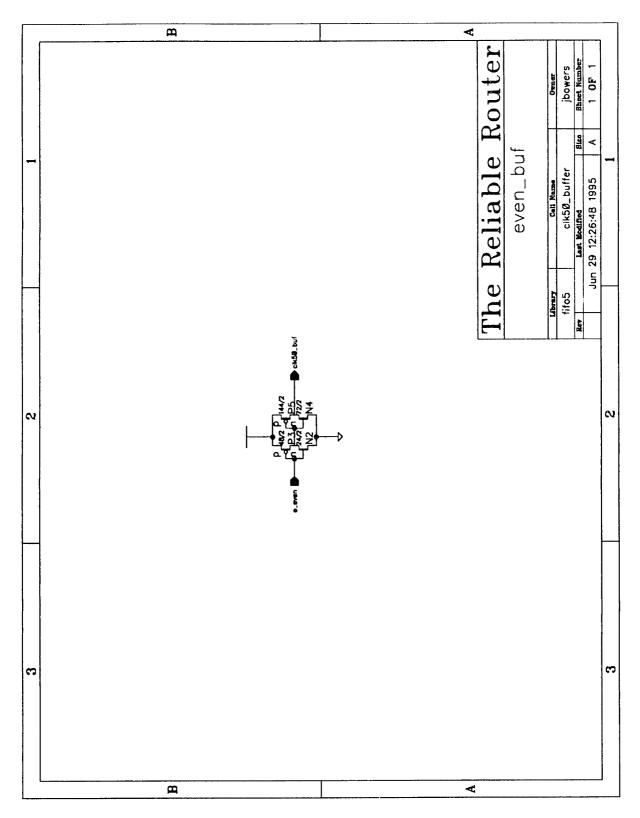

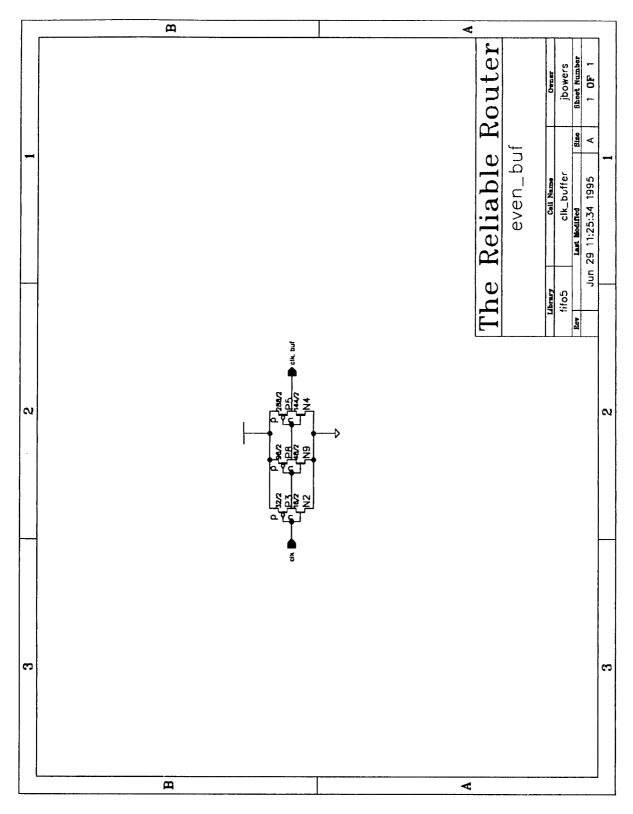

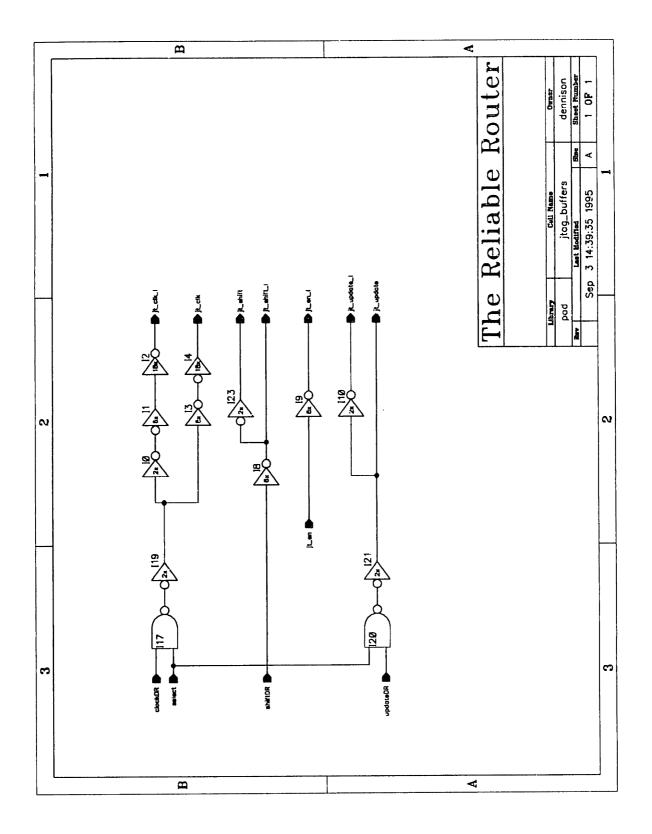

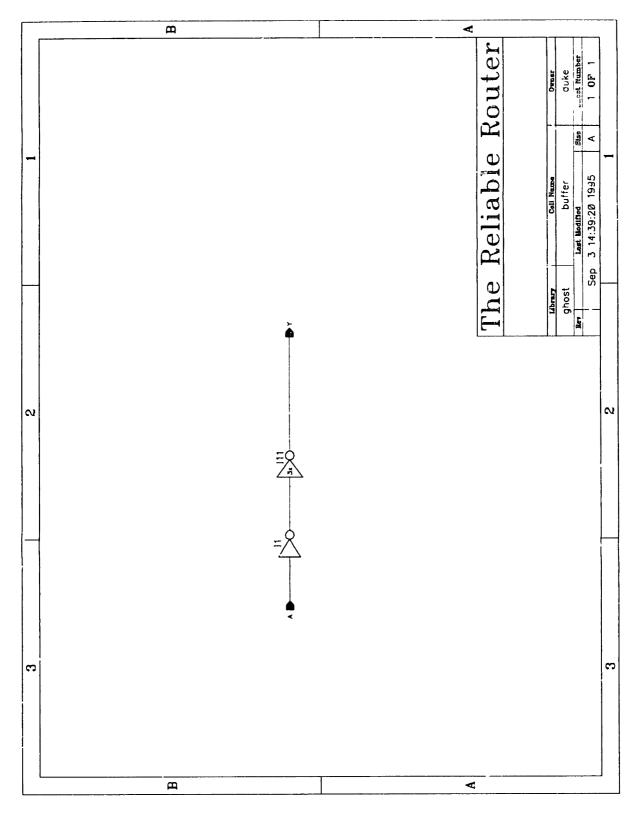

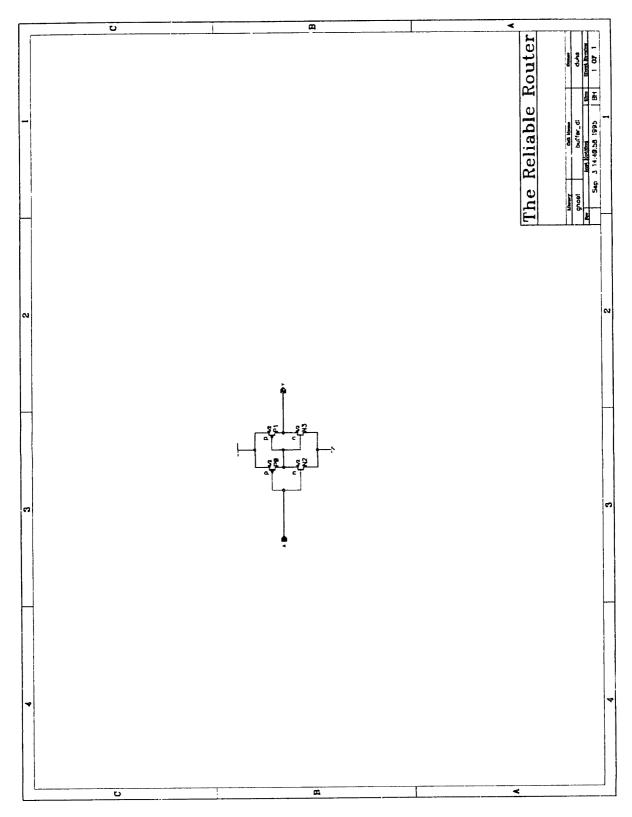

|   |      | 7.4.2 Clock Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 116 |

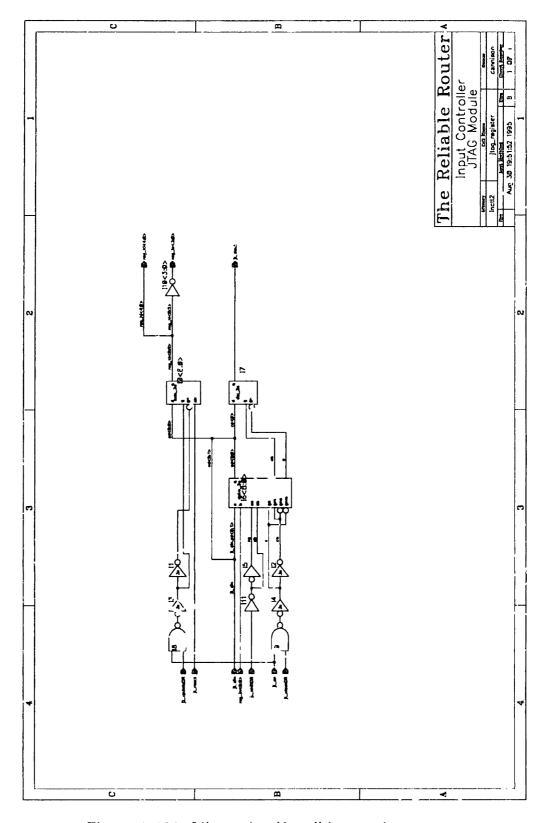

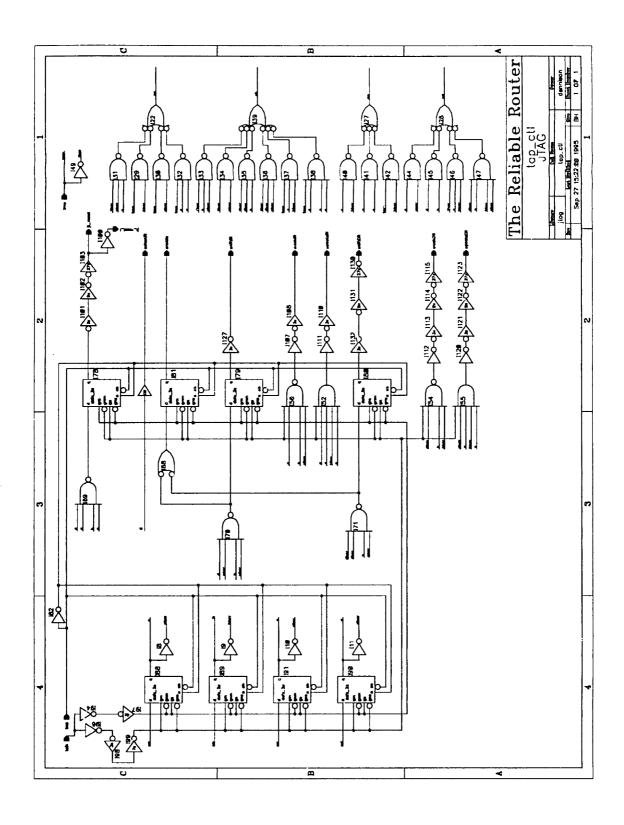

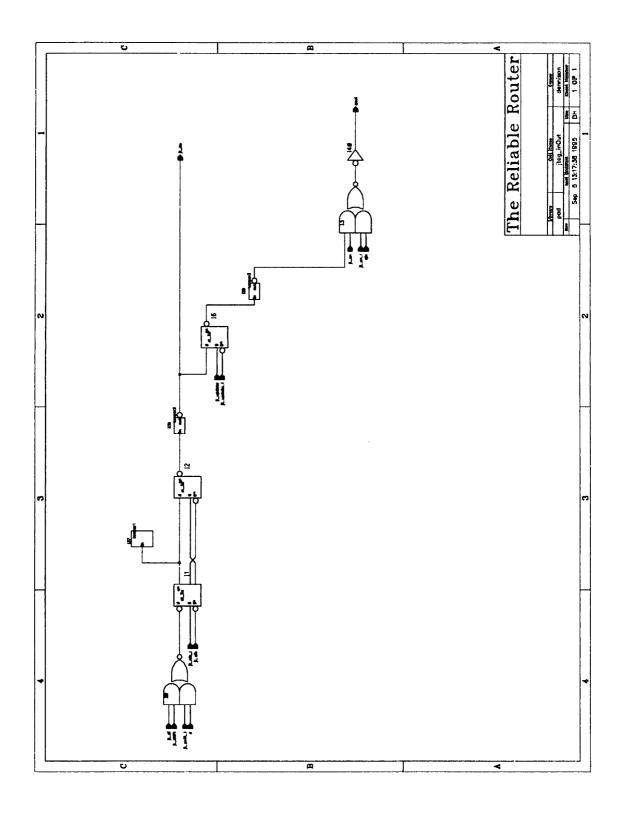

|   |      | 7.4.3 JTAG Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 116 |

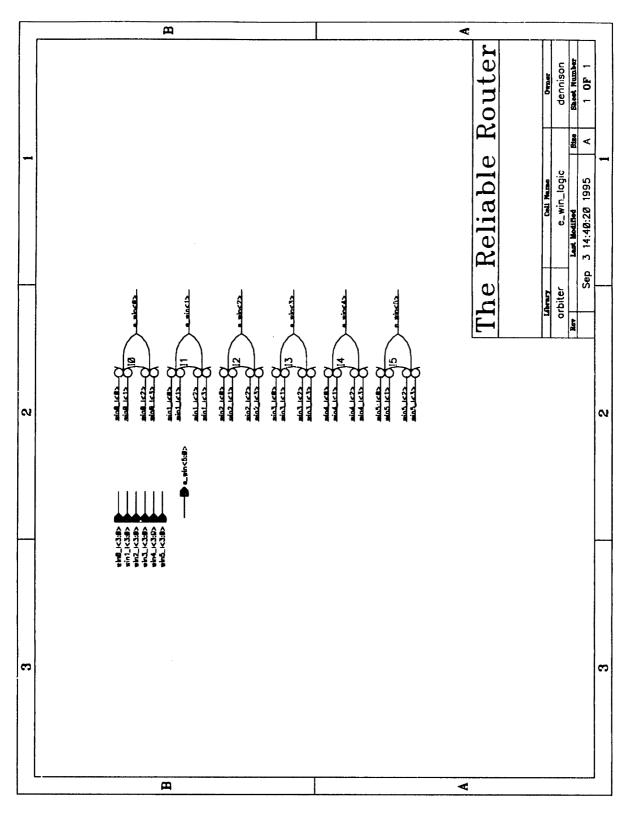

|   |      | 7.4.4 Mask Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 116 |

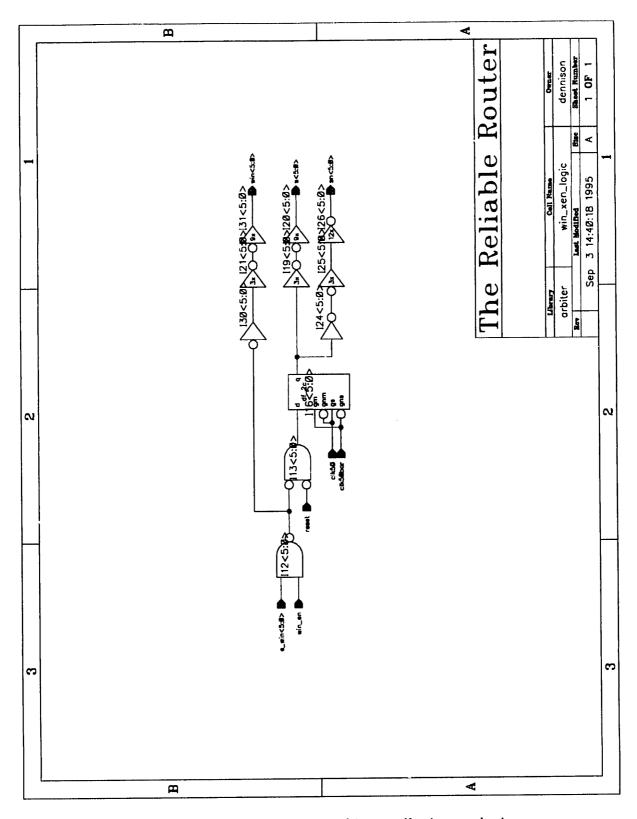

|   |      | 7.4.5 Win Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 117 |

|   |      | 7.4.6 Crossbar to Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117 |

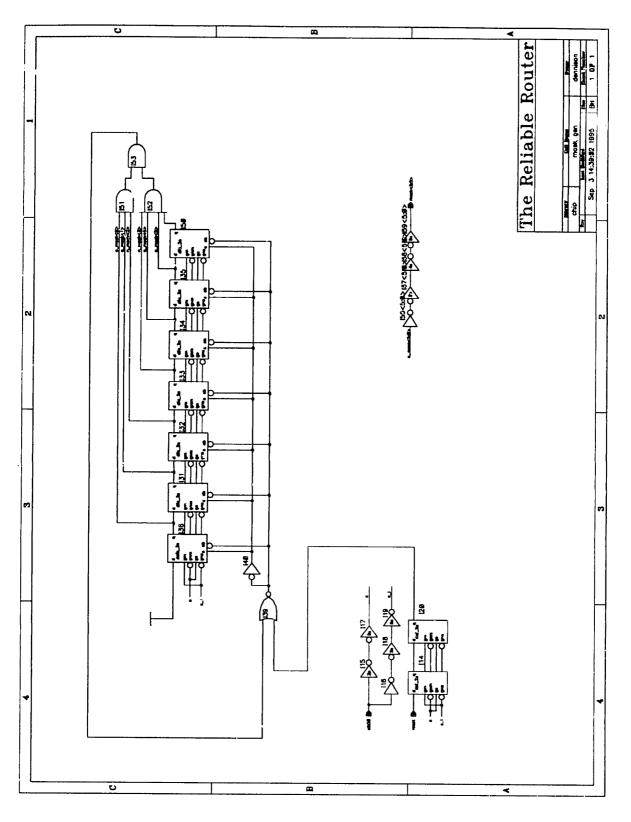

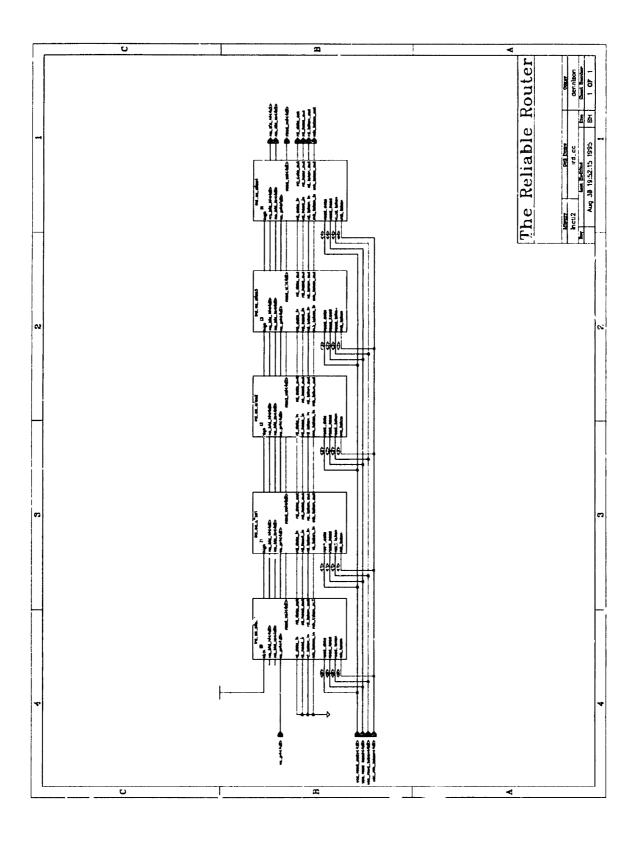

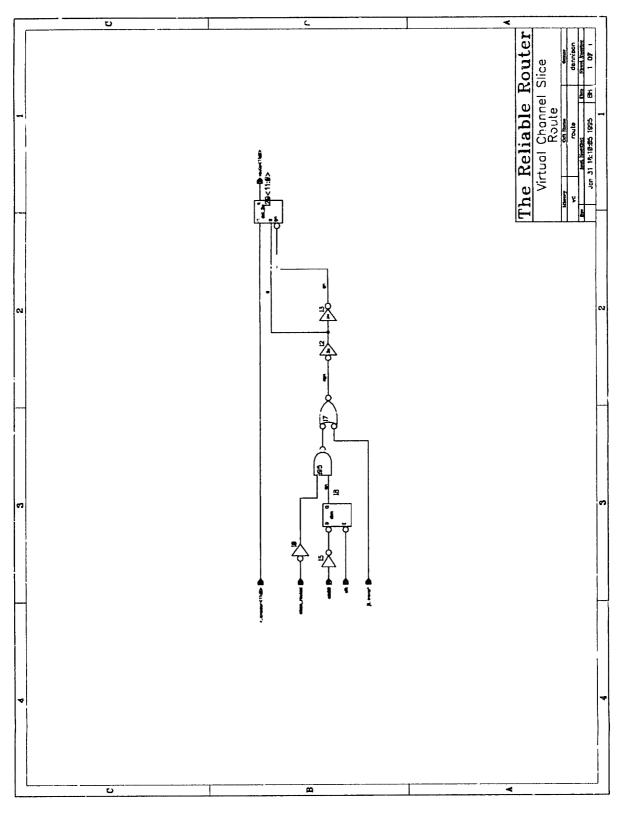

|   | 7.5  | Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 117 |

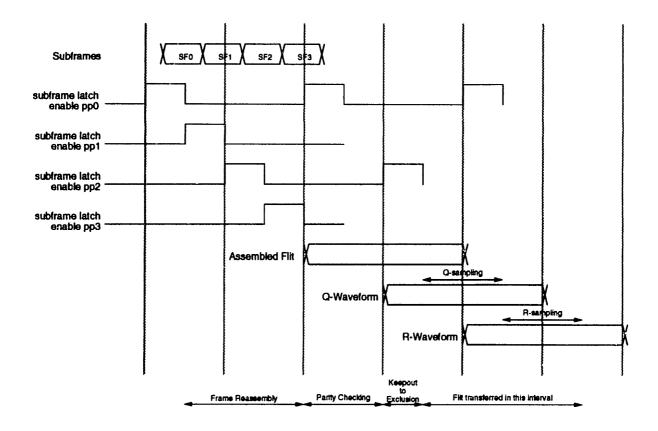

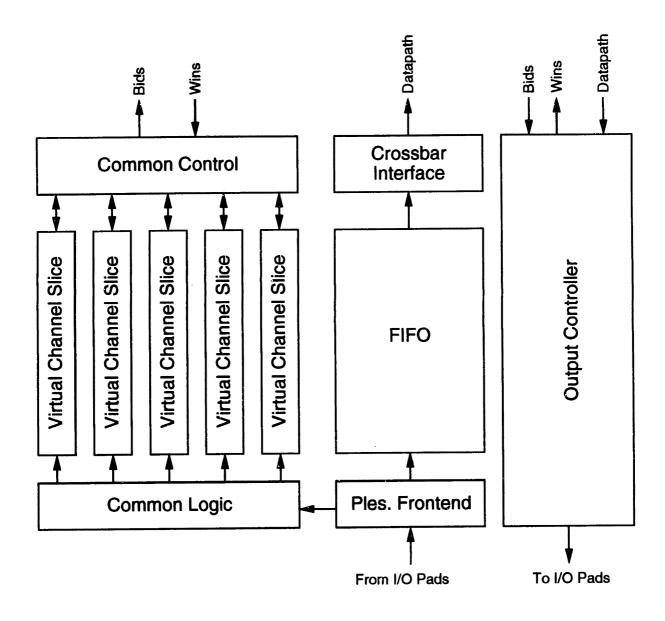

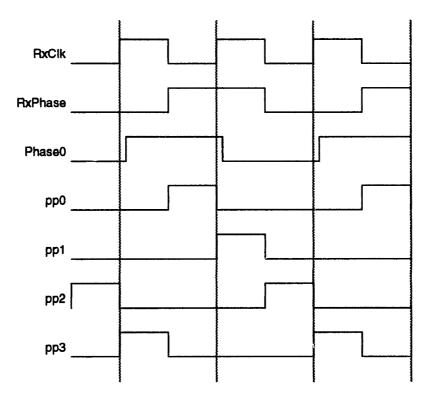

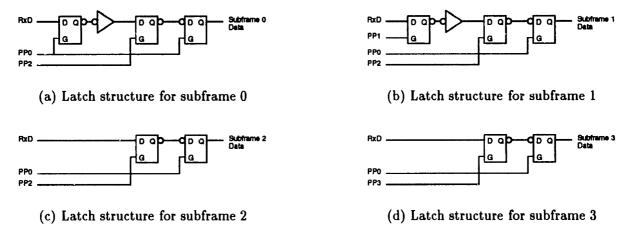

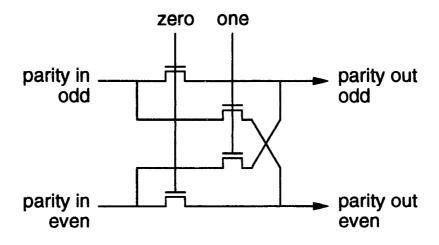

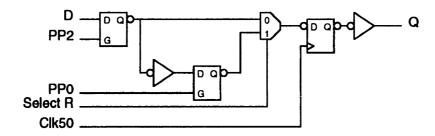

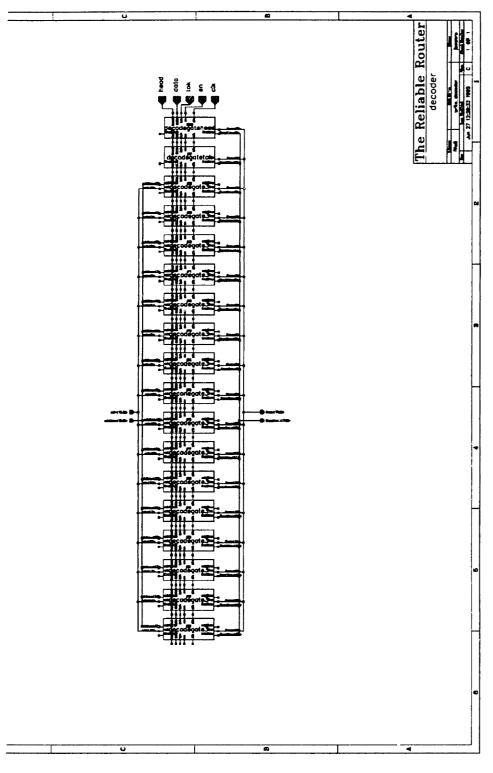

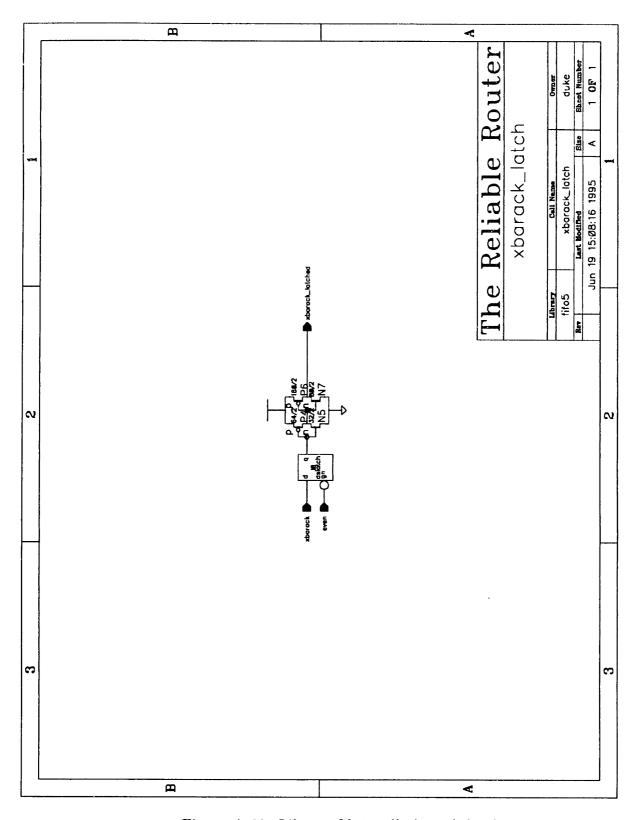

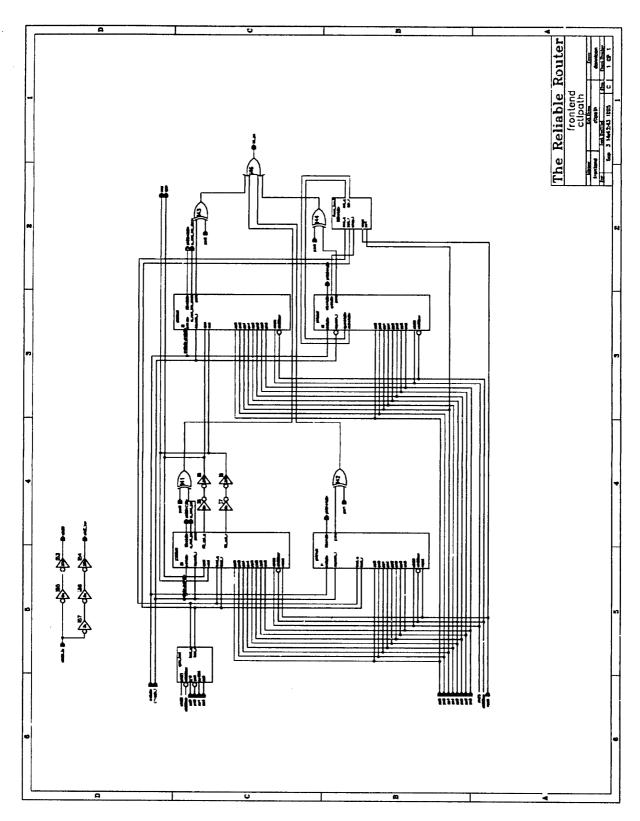

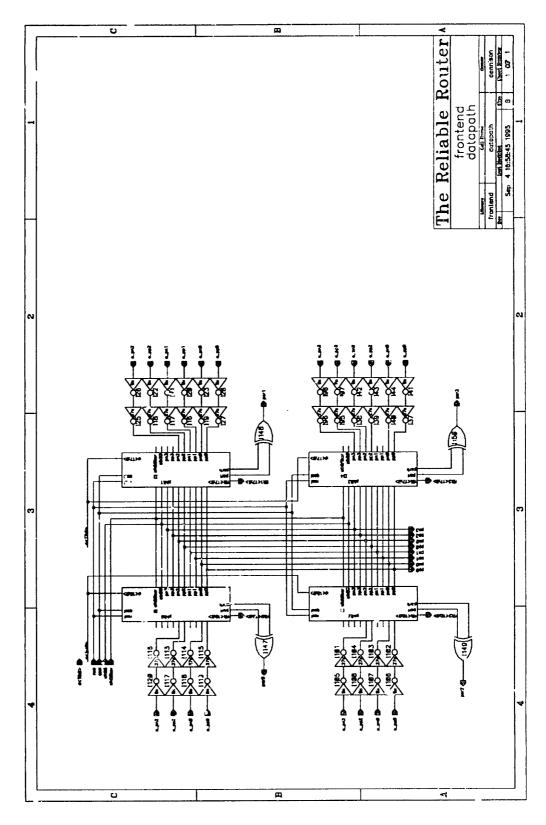

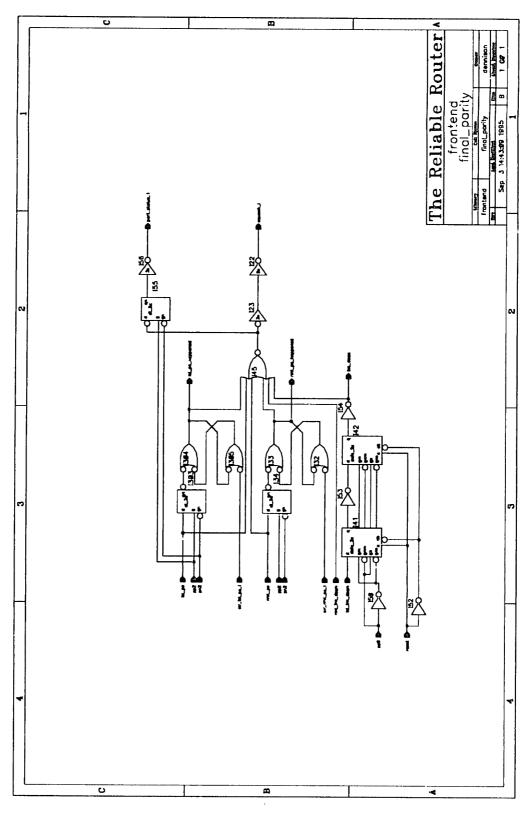

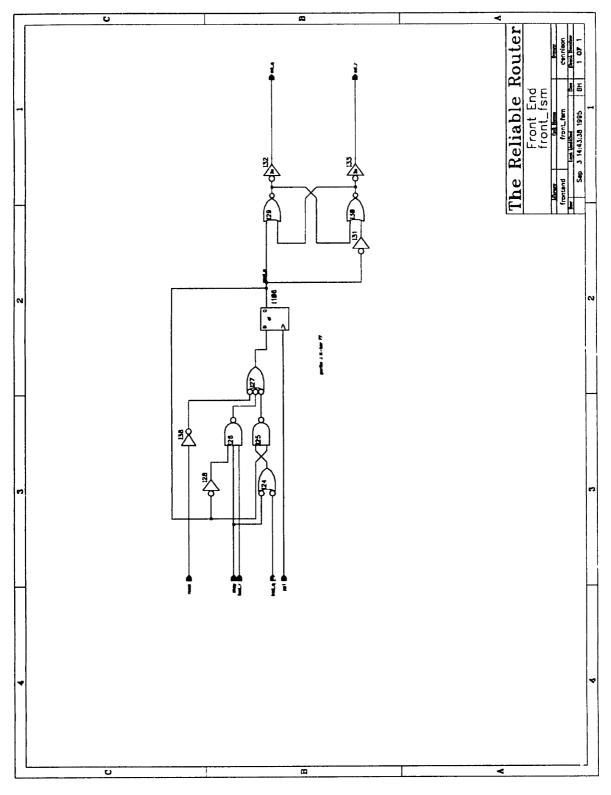

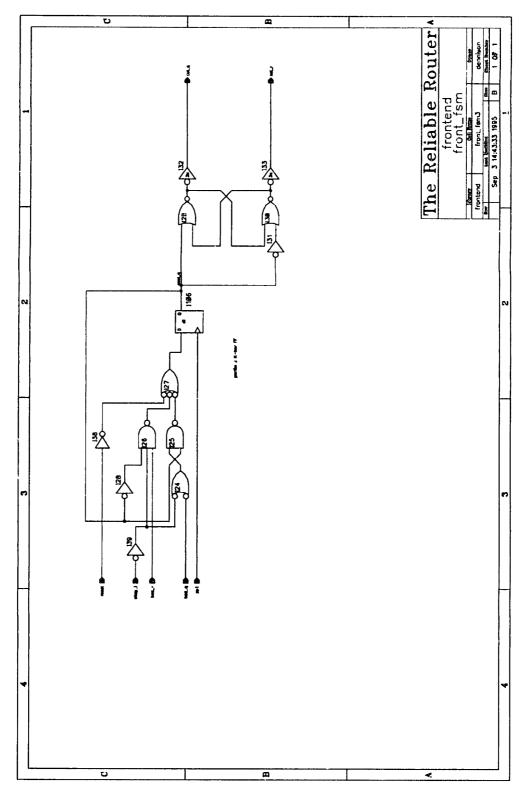

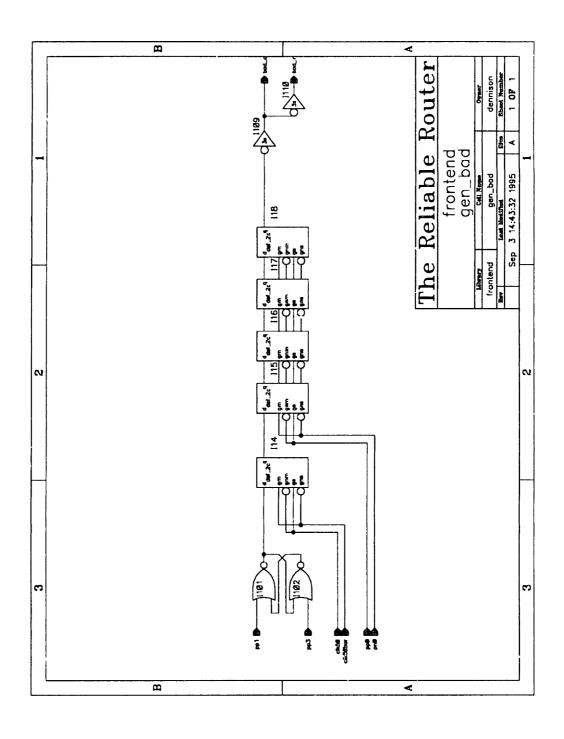

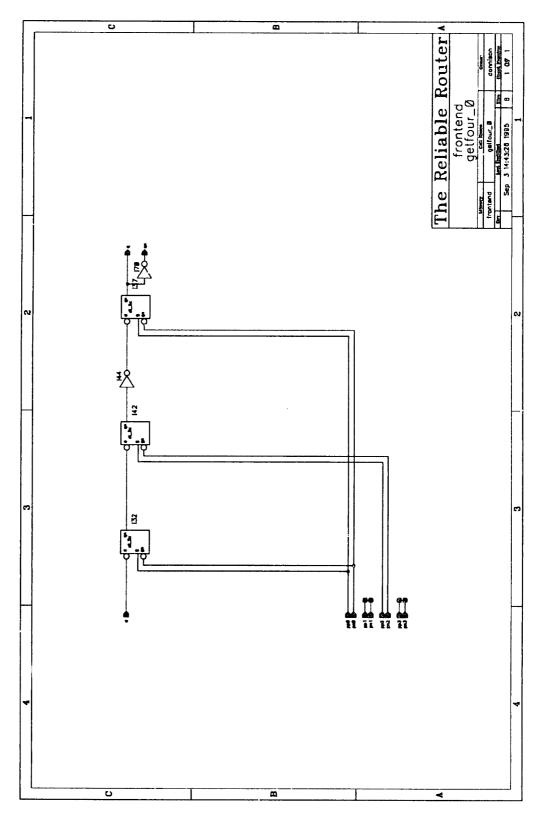

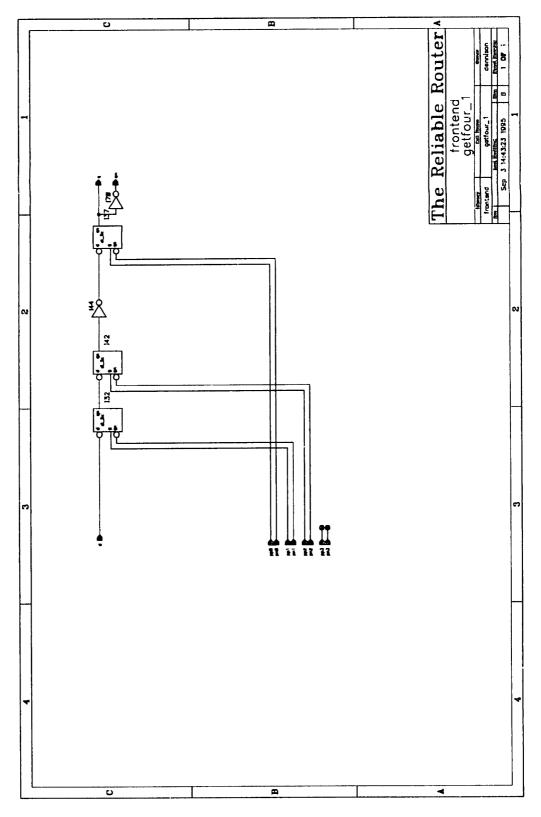

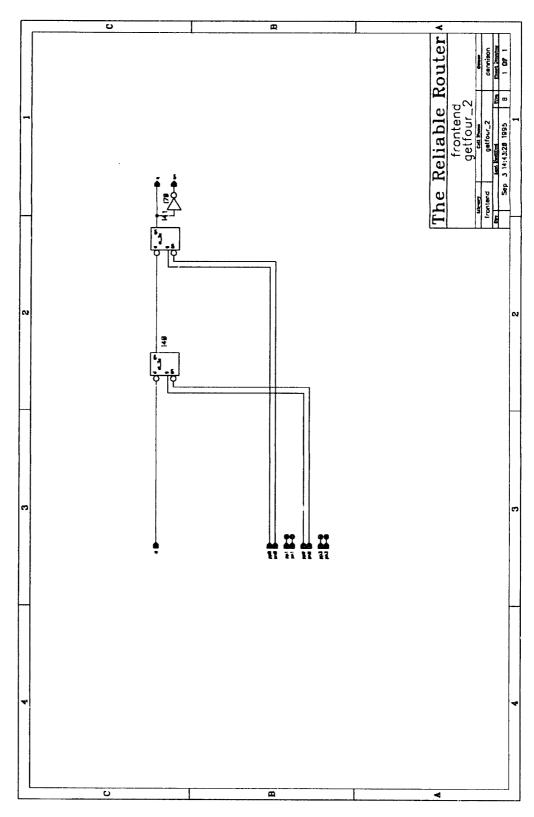

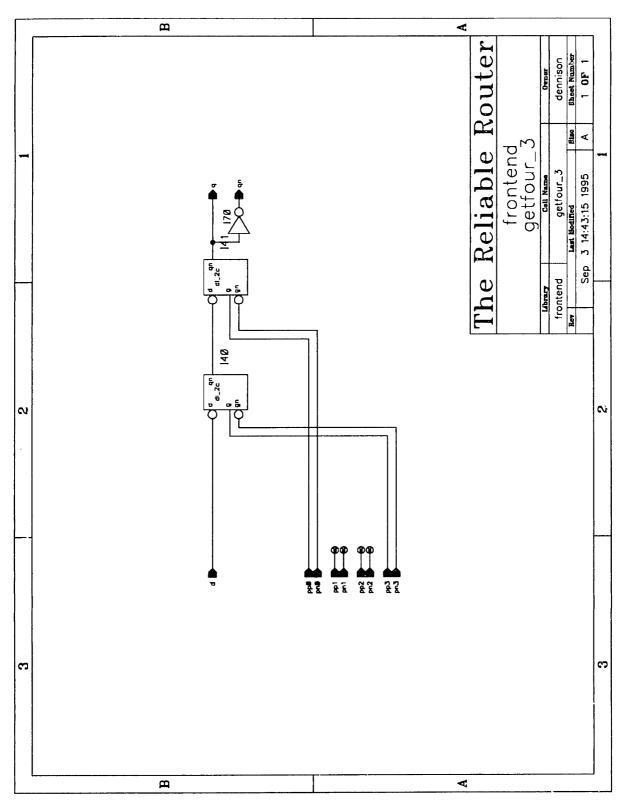

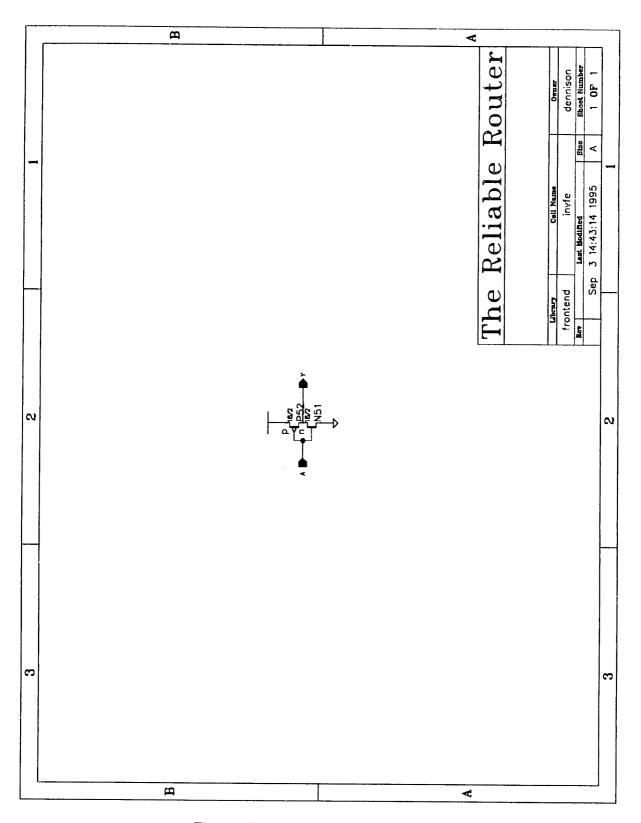

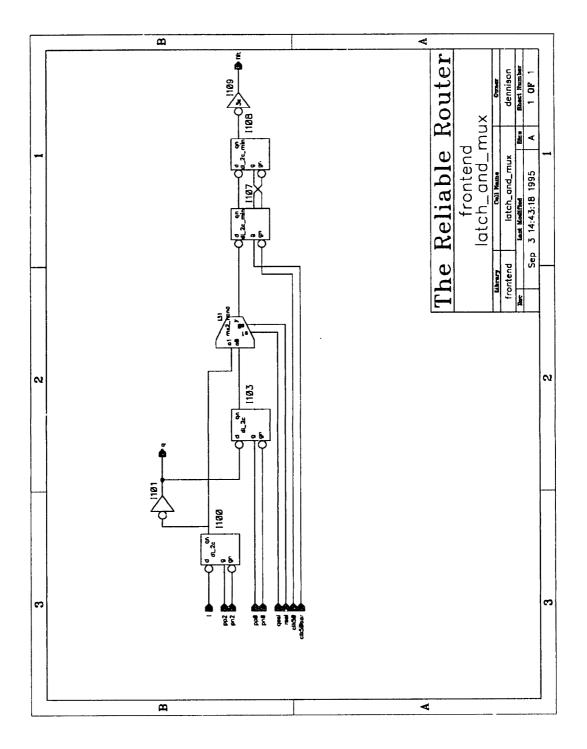

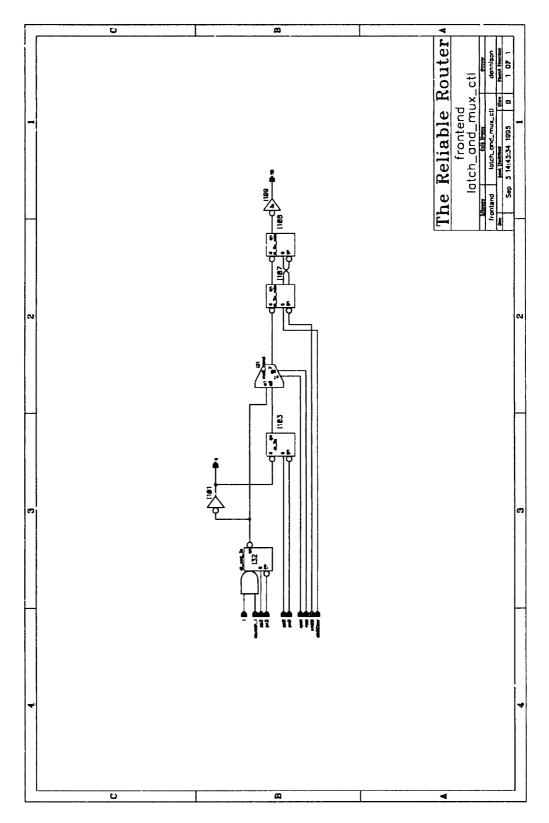

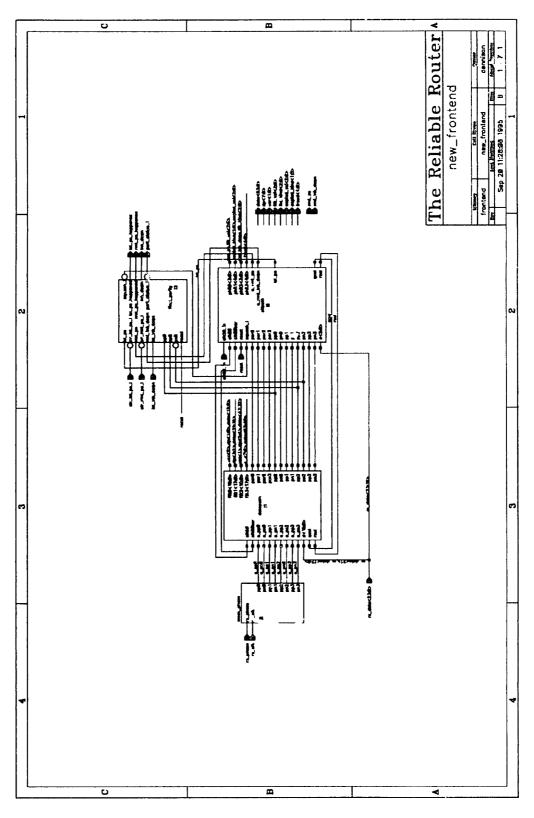

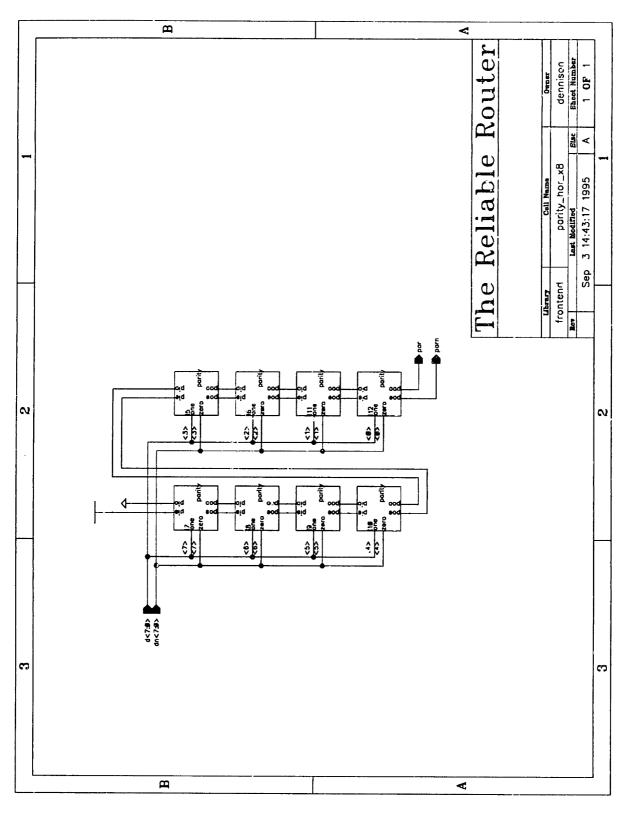

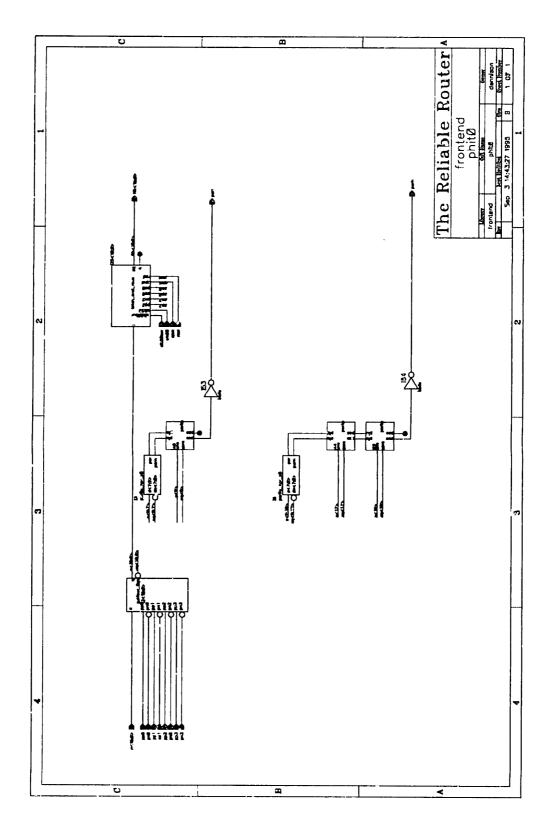

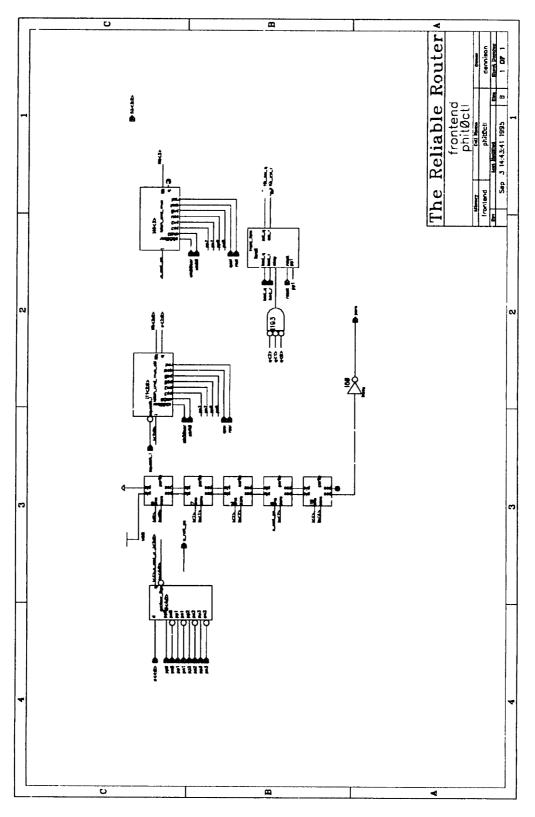

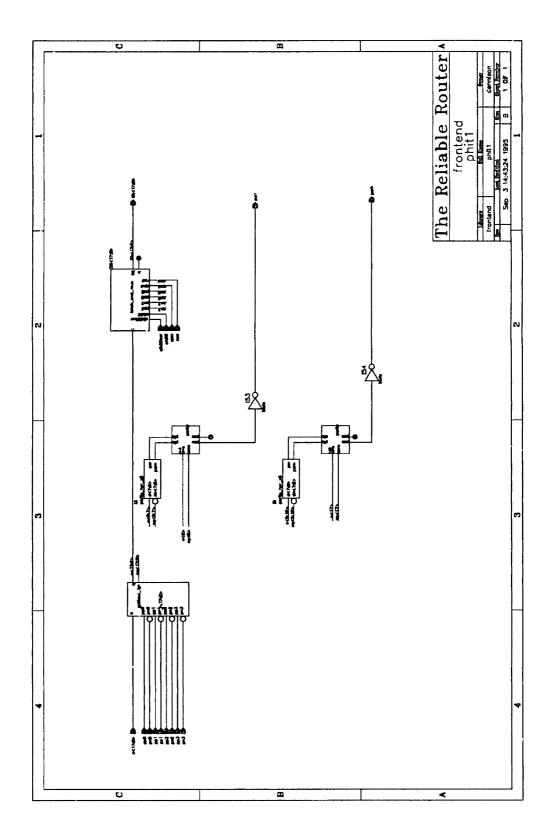

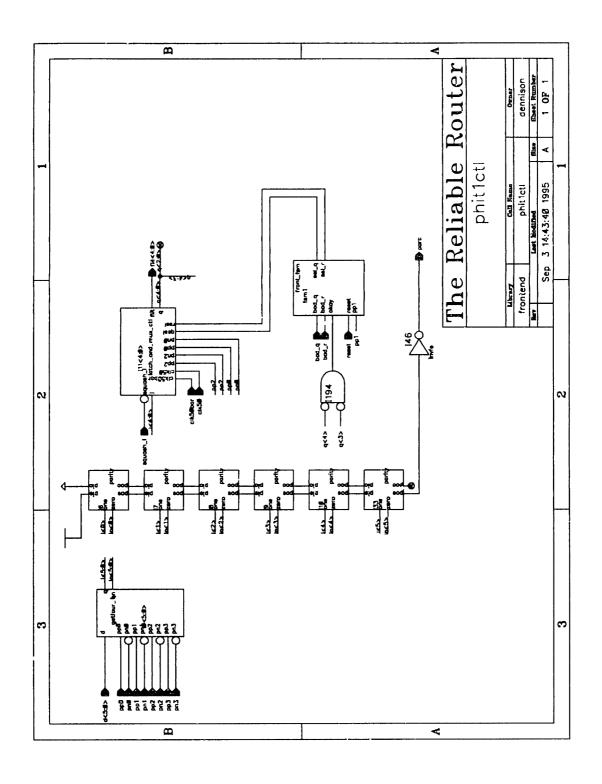

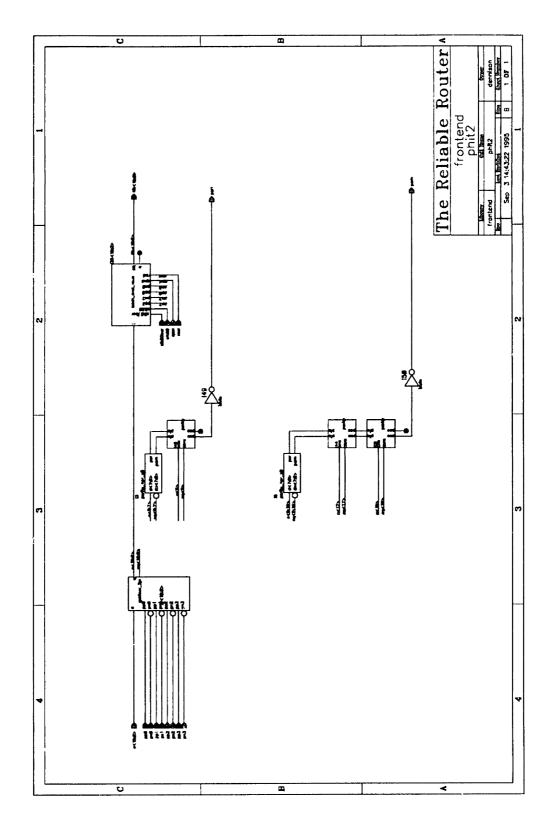

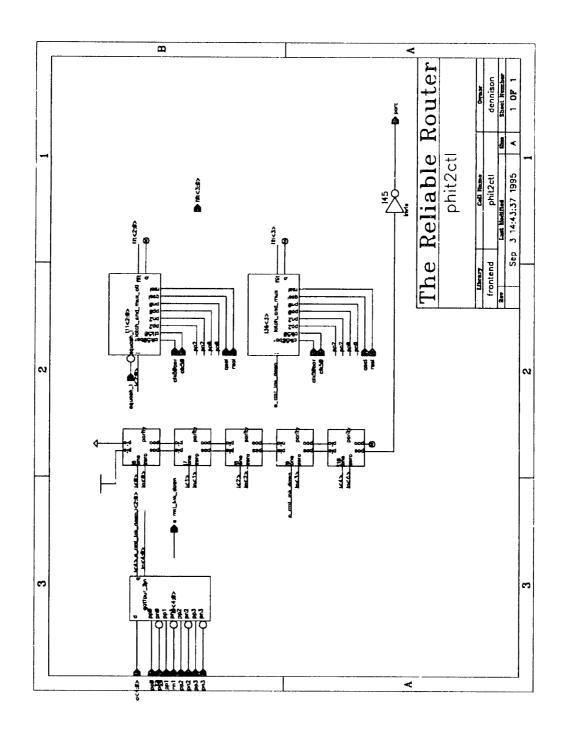

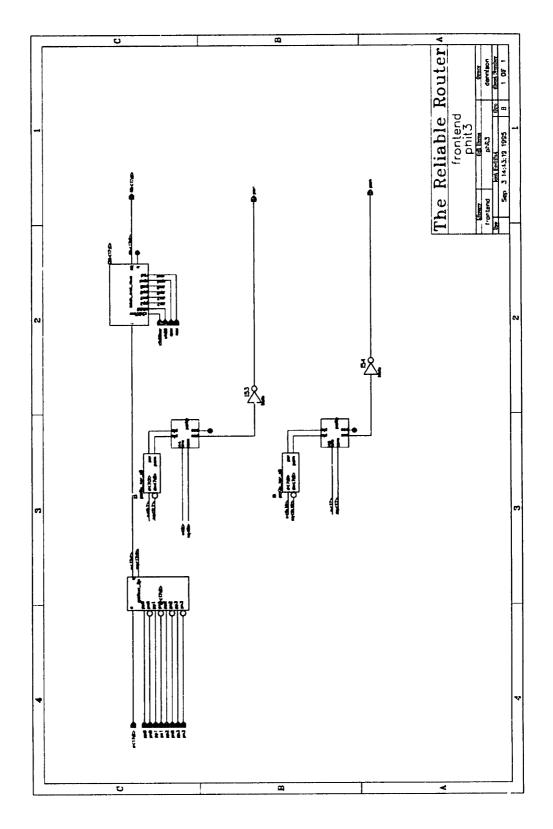

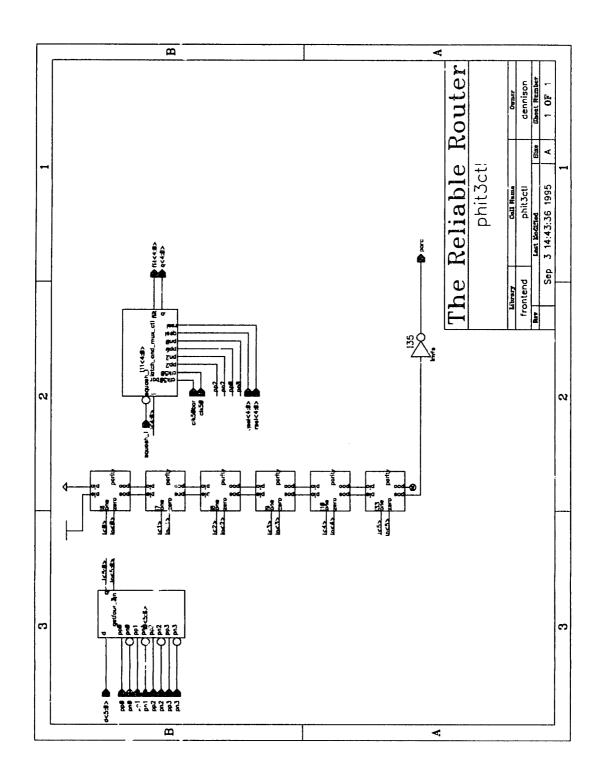

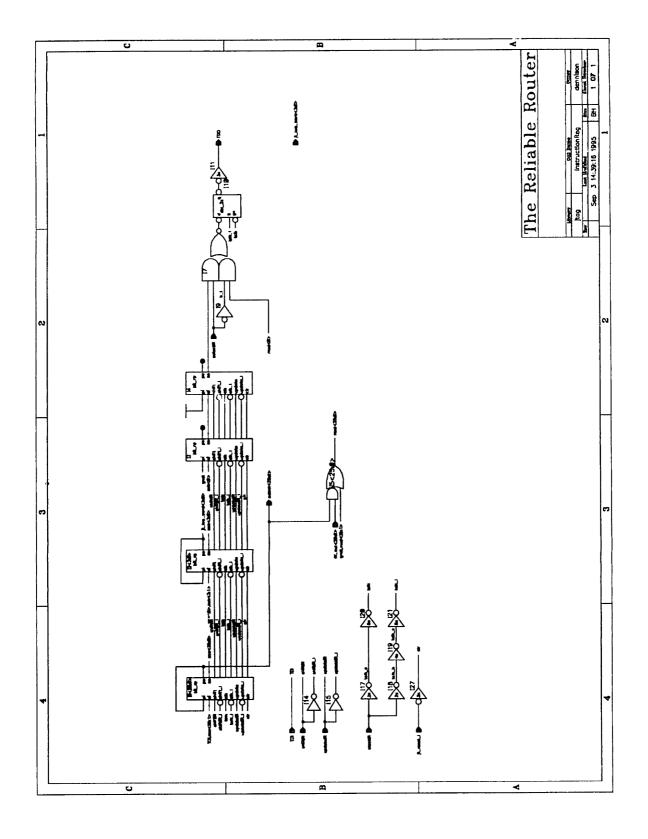

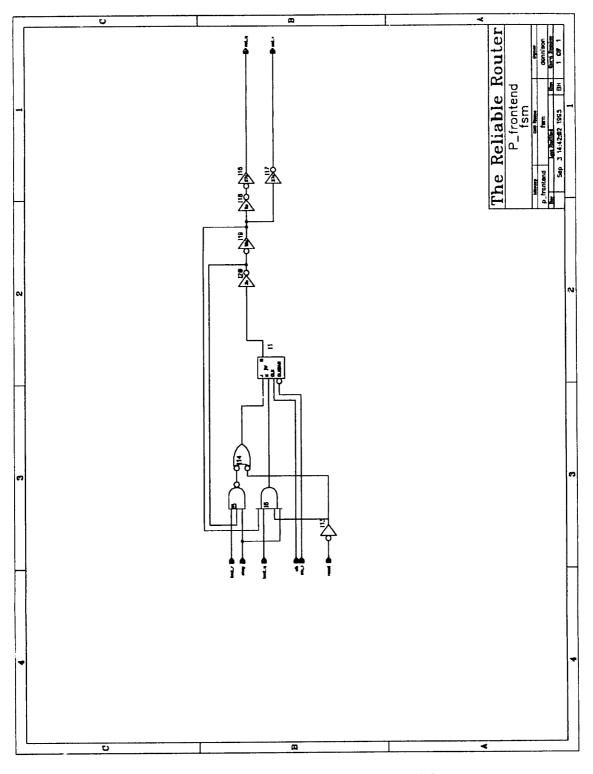

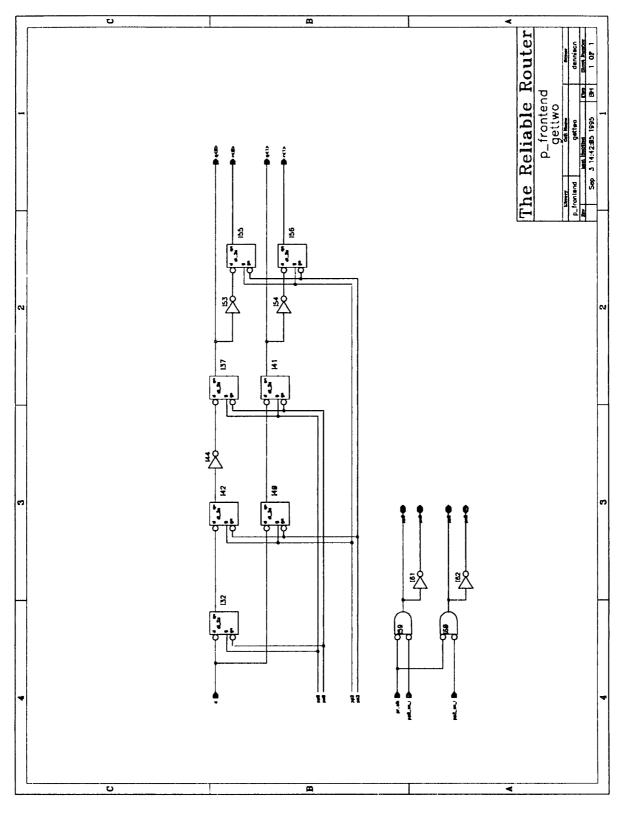

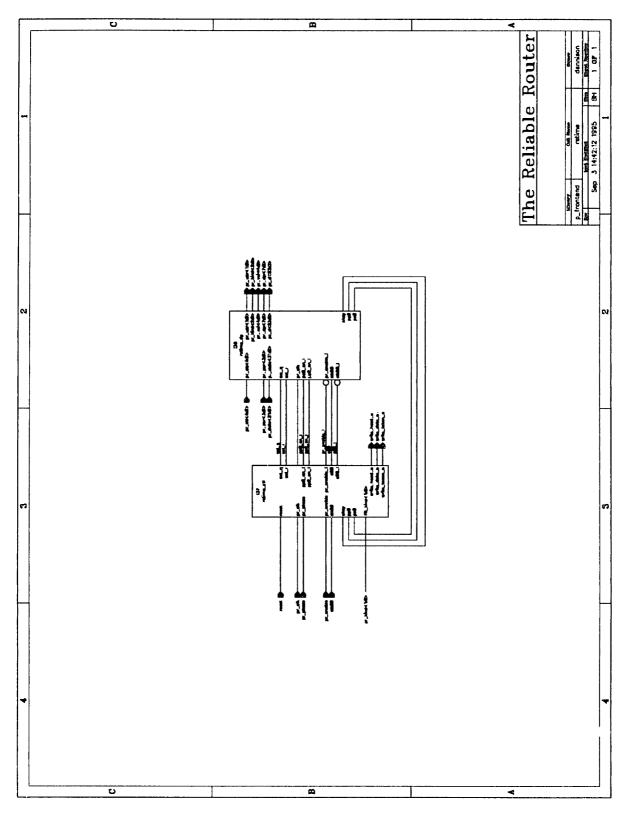

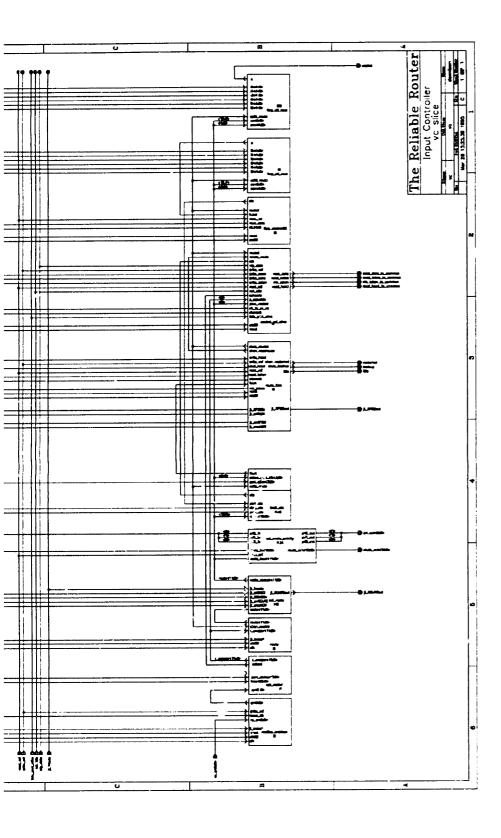

|   |      | 7.5.1 Frontend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 118 |

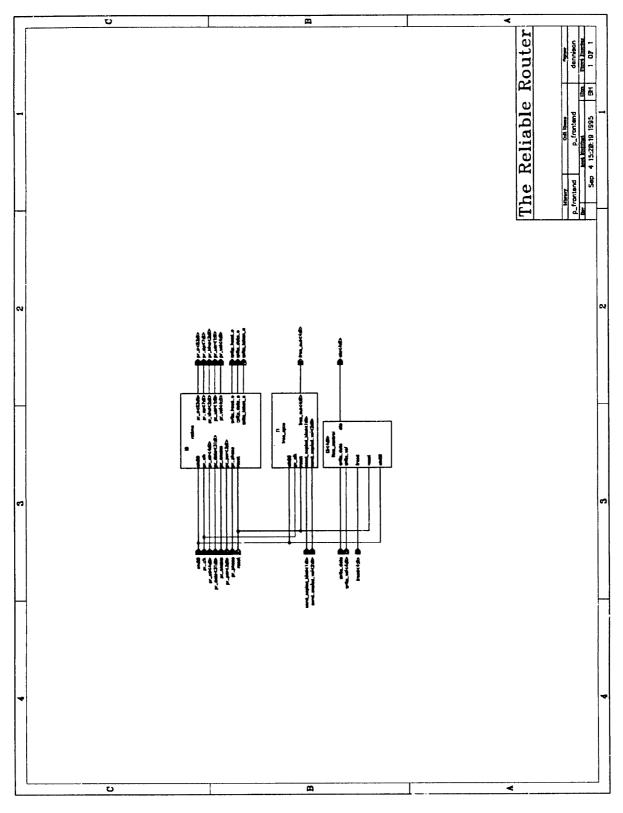

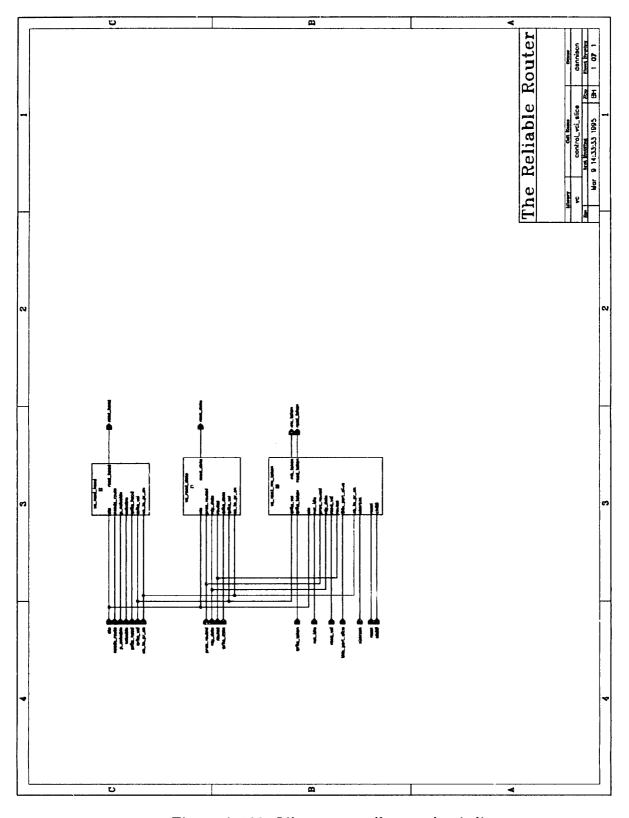

|   |      | 7.5.2 Glue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123 |

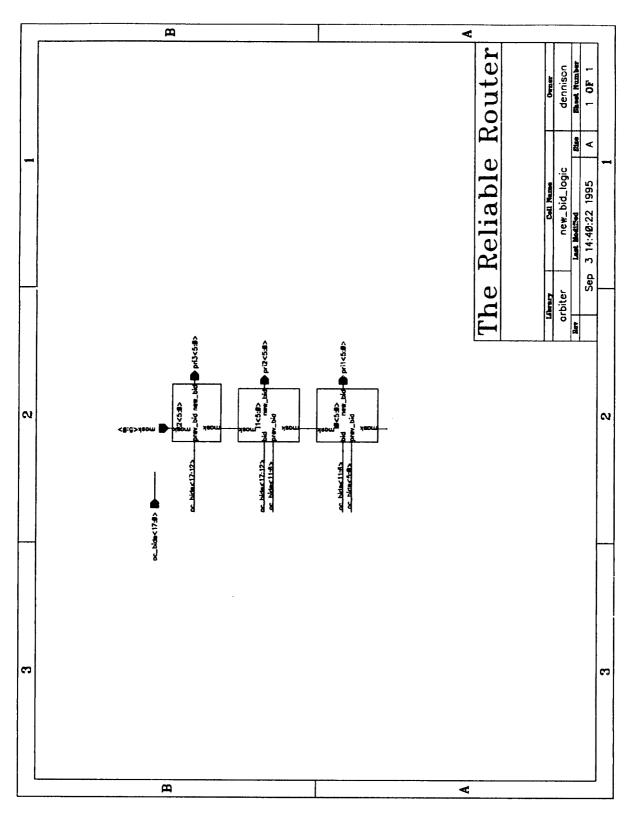

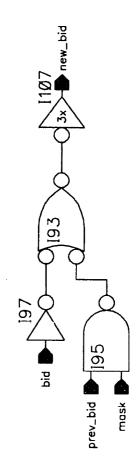

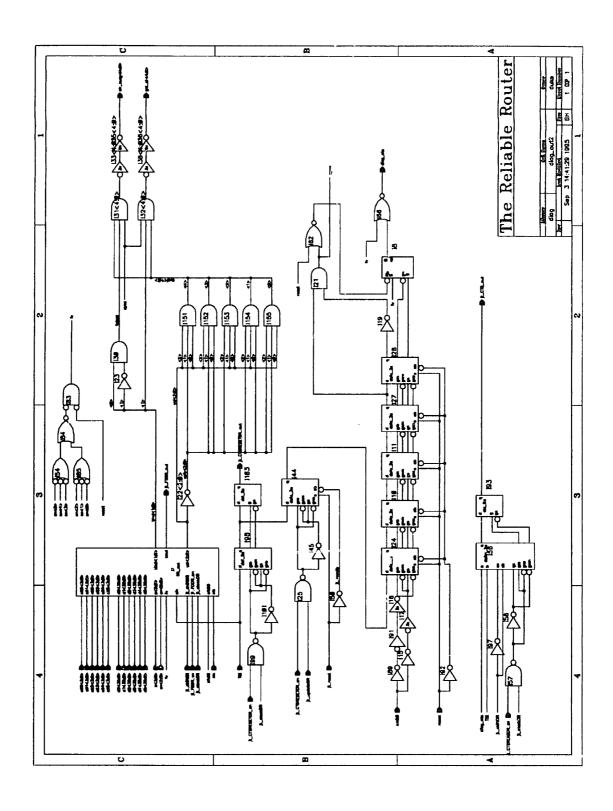

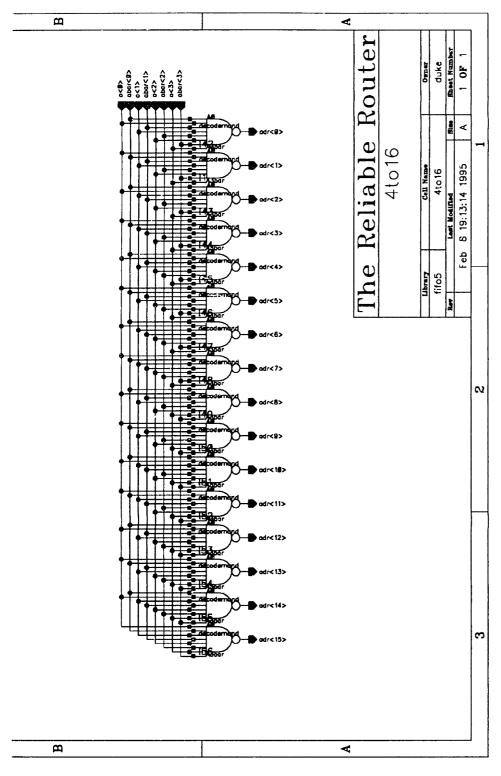

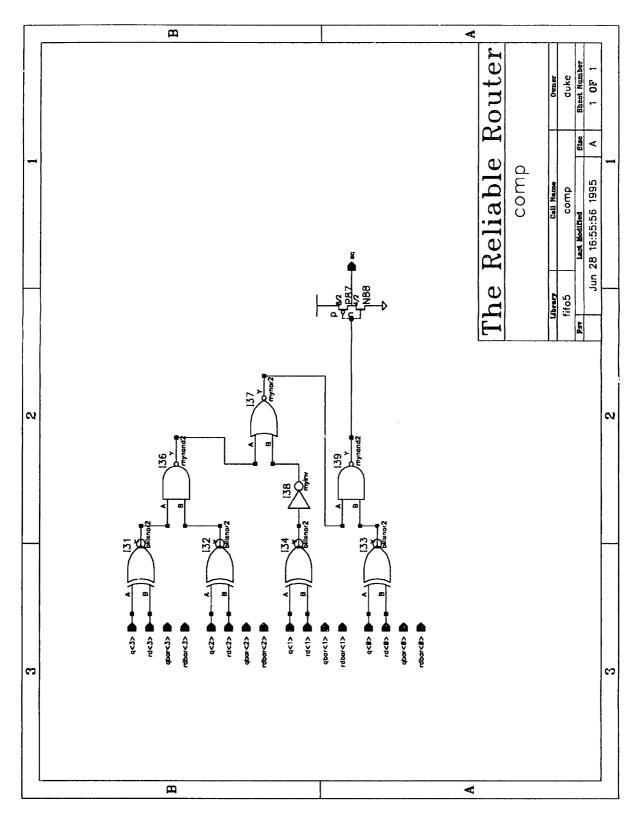

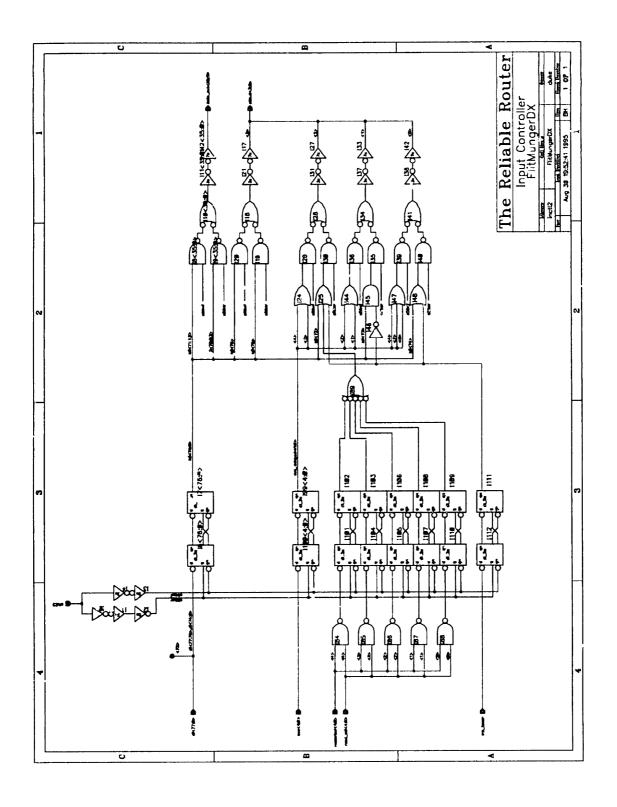

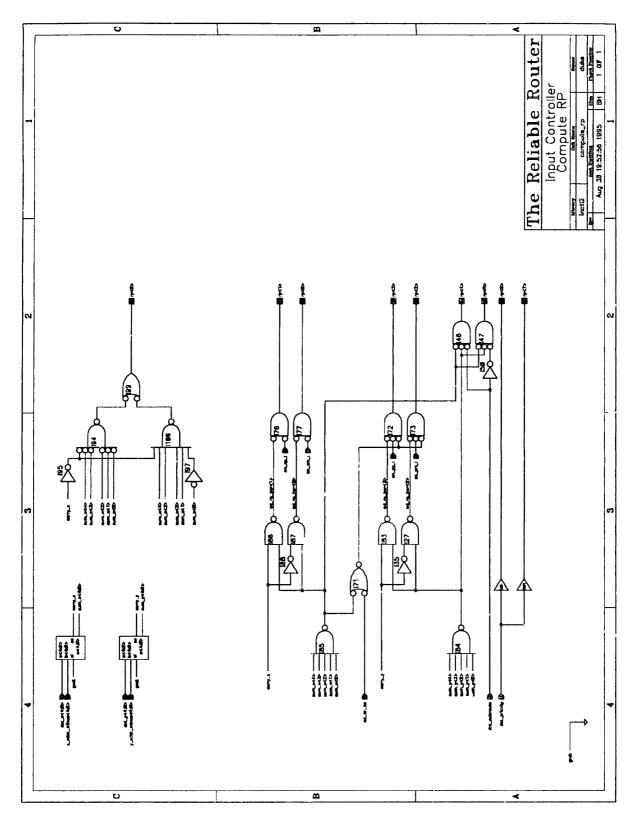

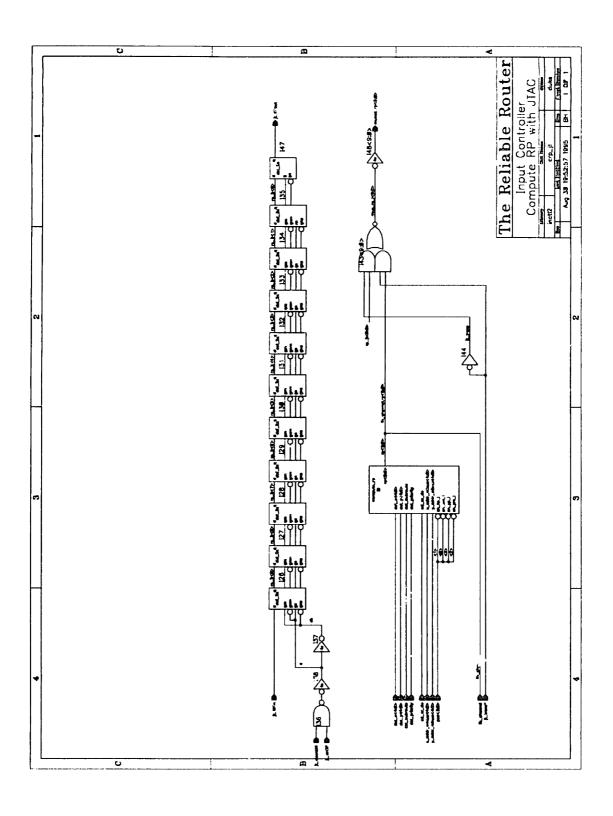

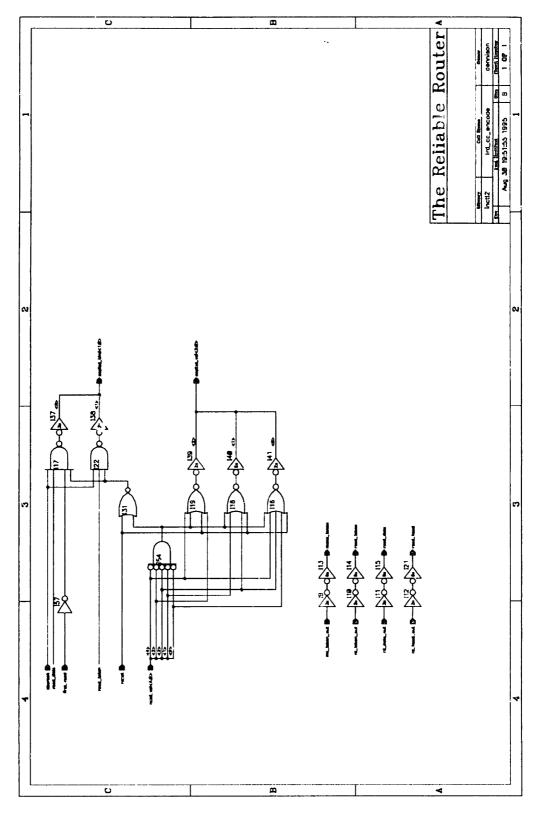

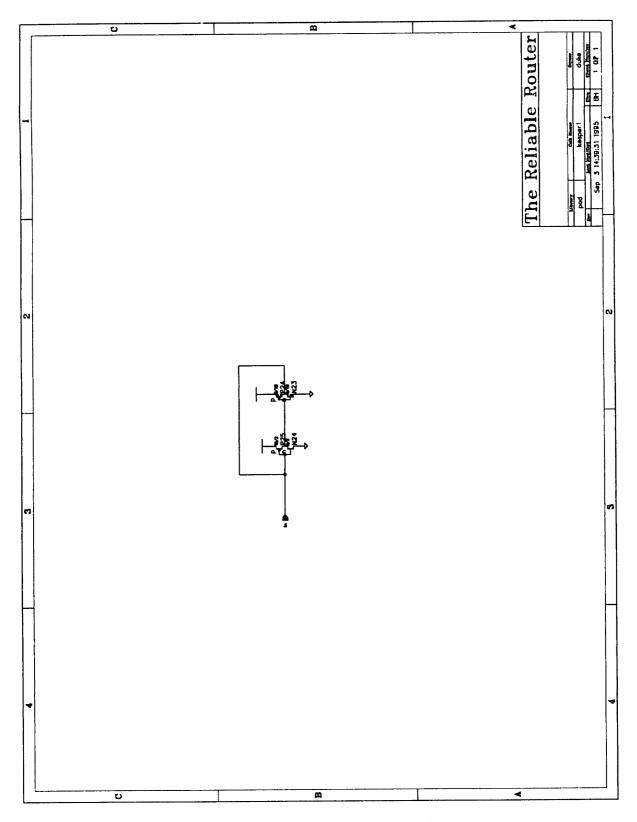

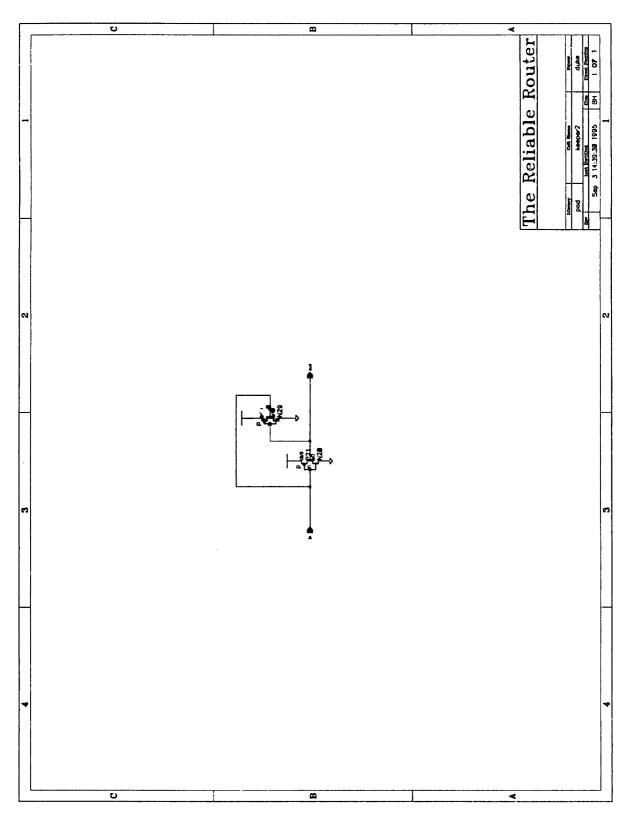

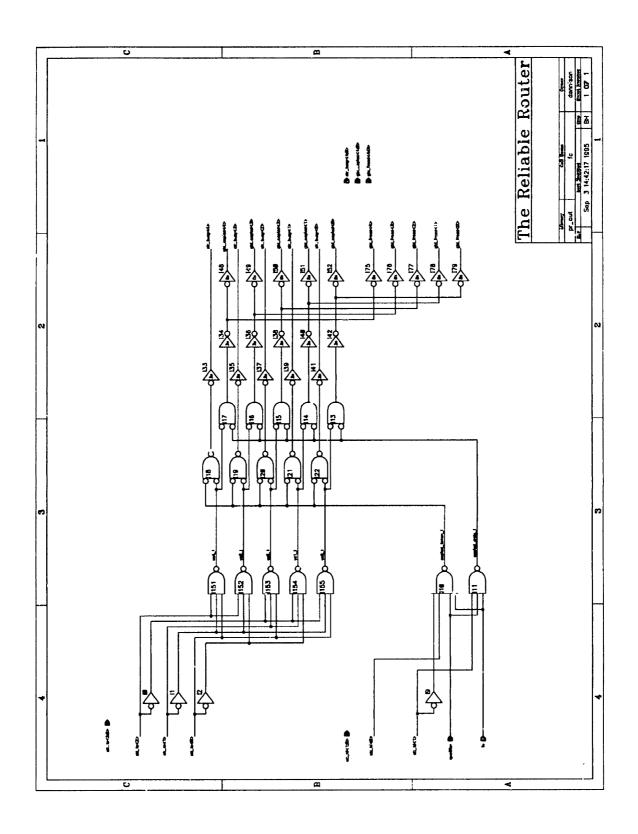

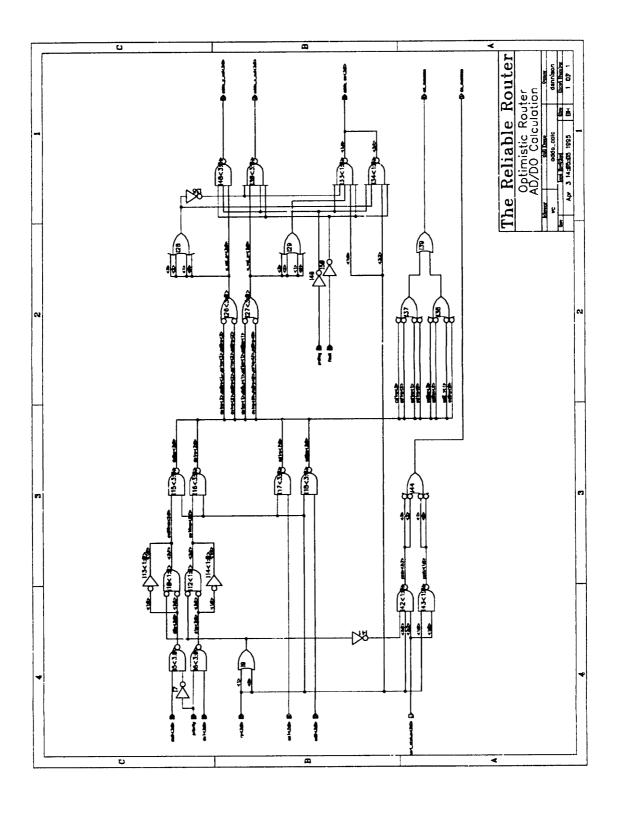

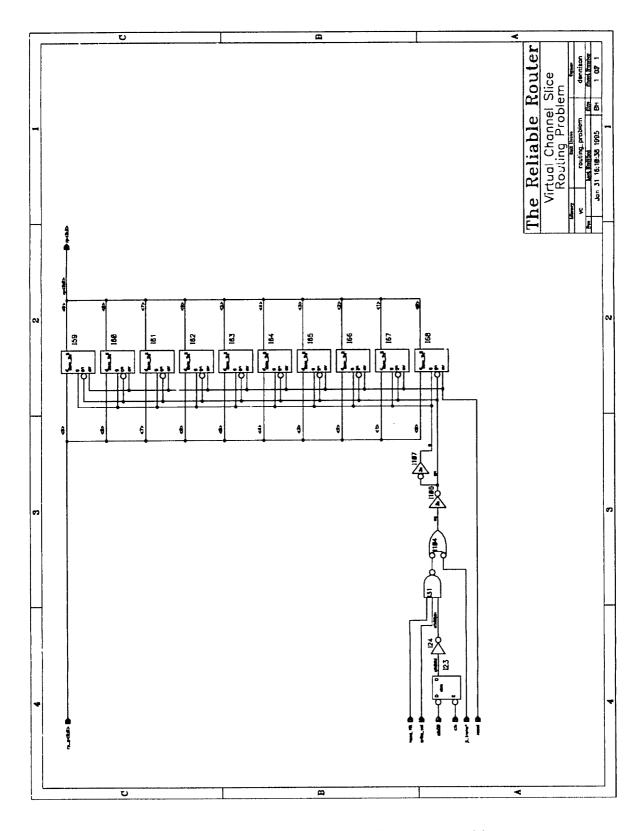

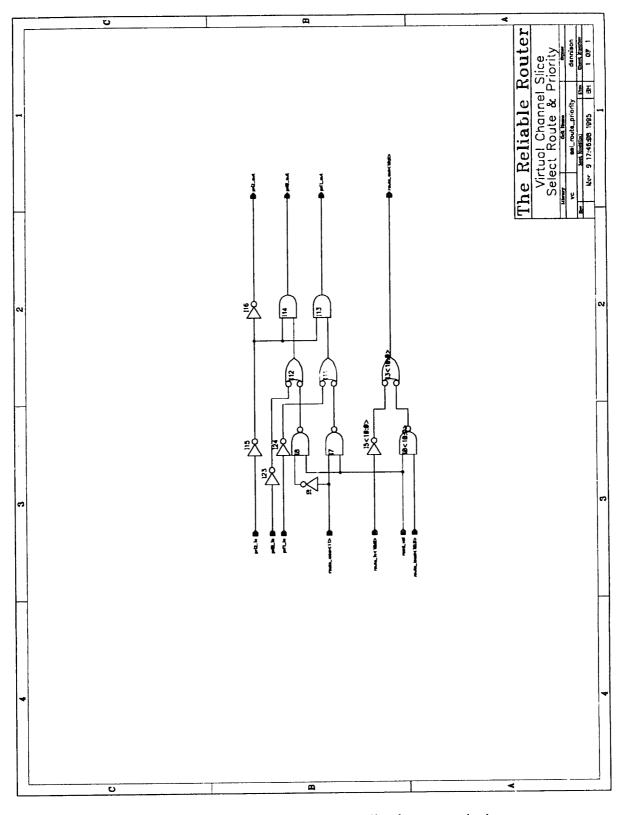

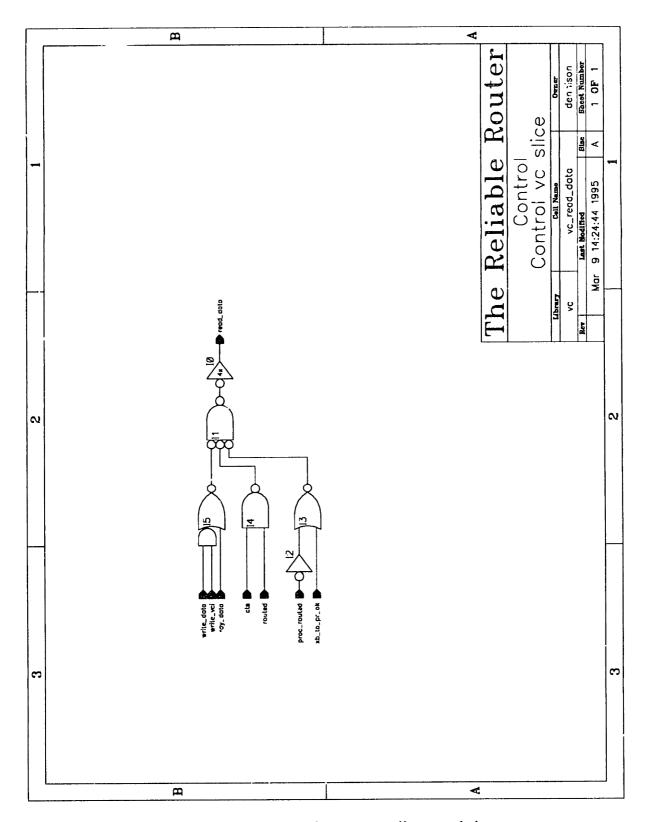

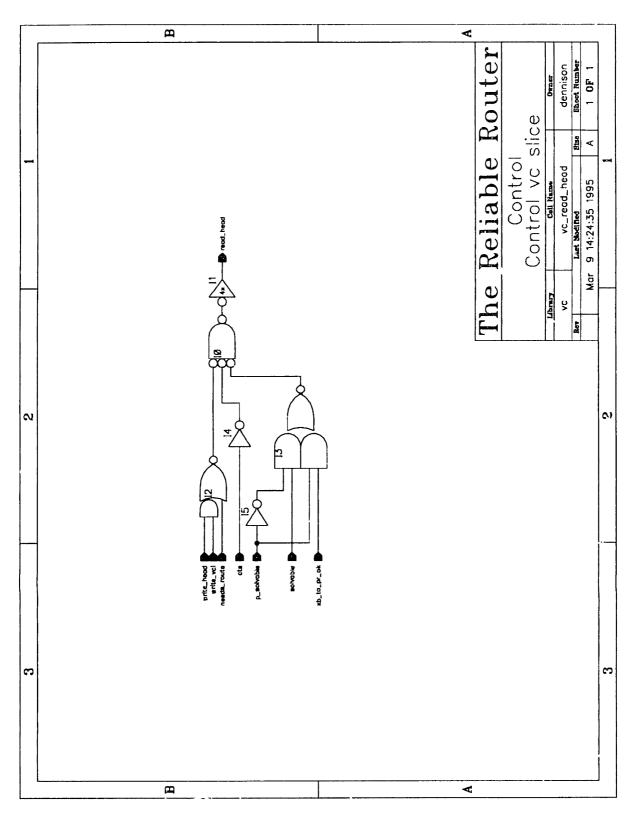

|   |      | 7.5.3 Compute Routing Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 123 |

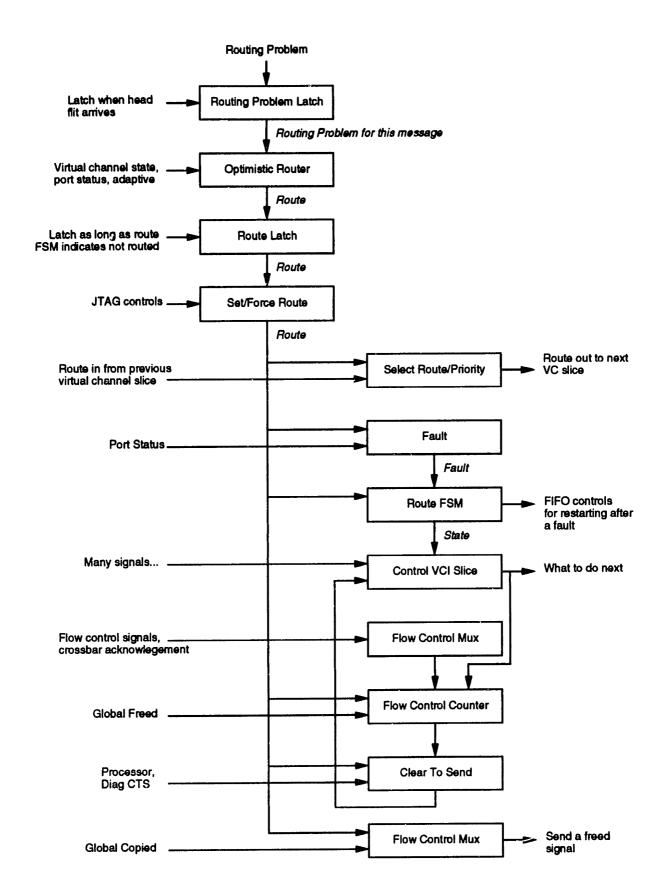

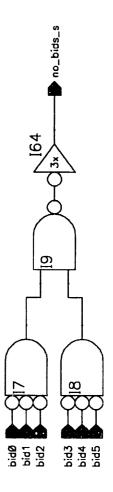

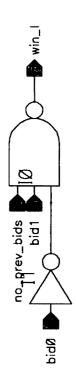

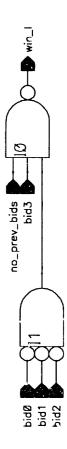

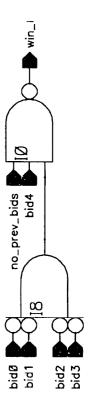

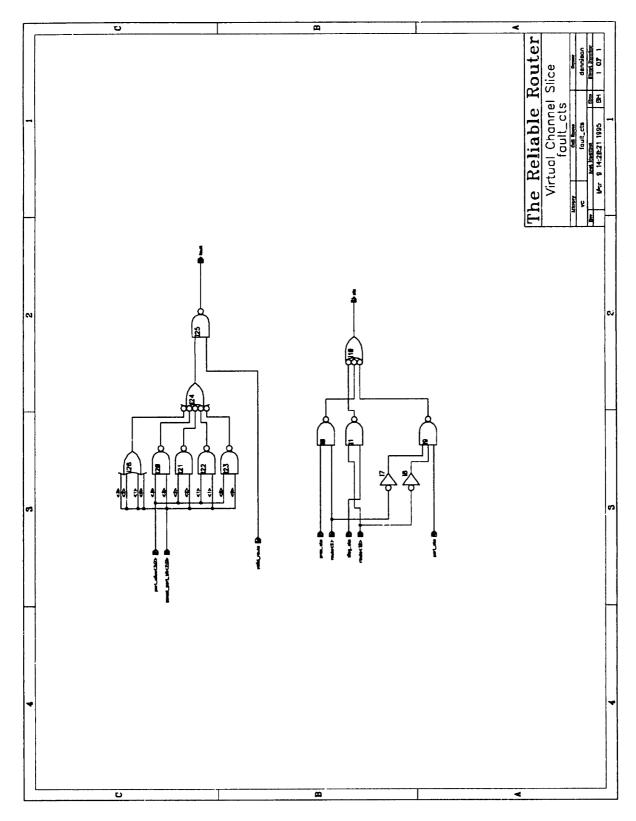

|   |      | 7 5 4 37' 4 3 60 1 600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 125 |

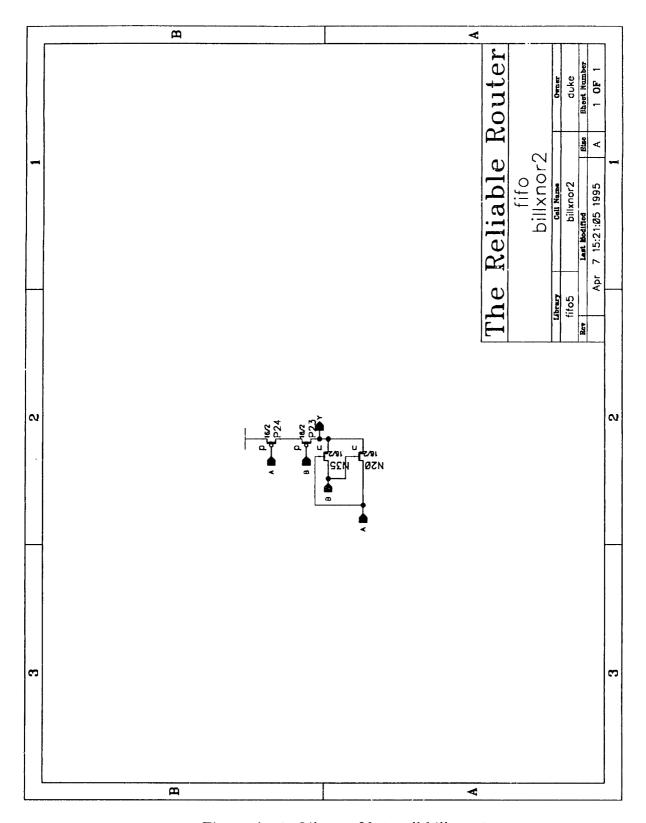

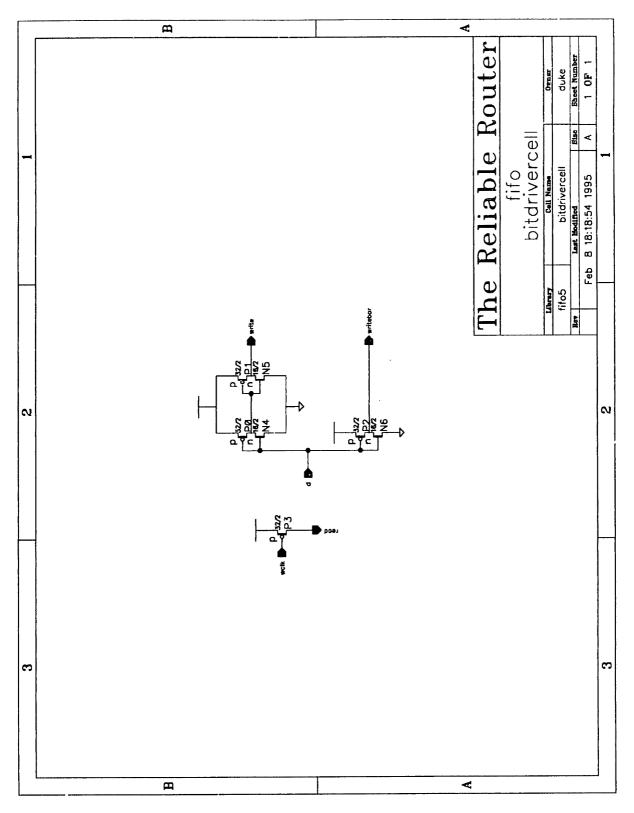

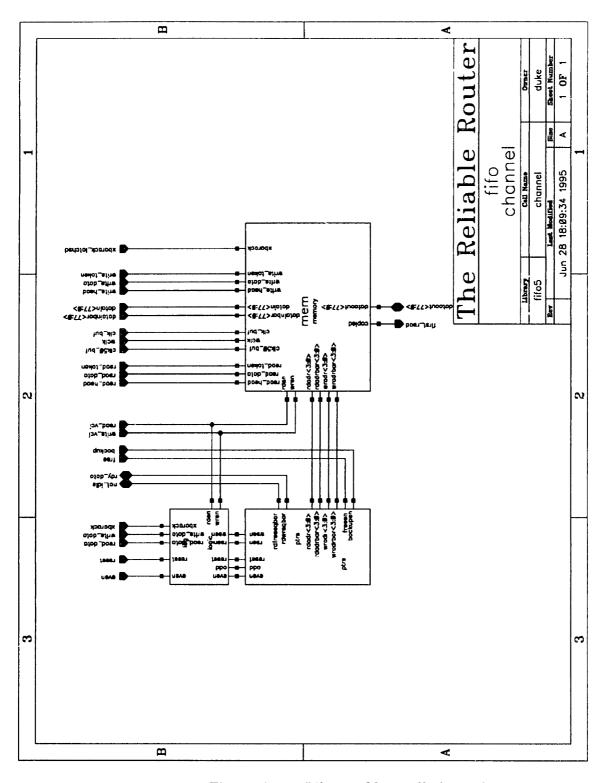

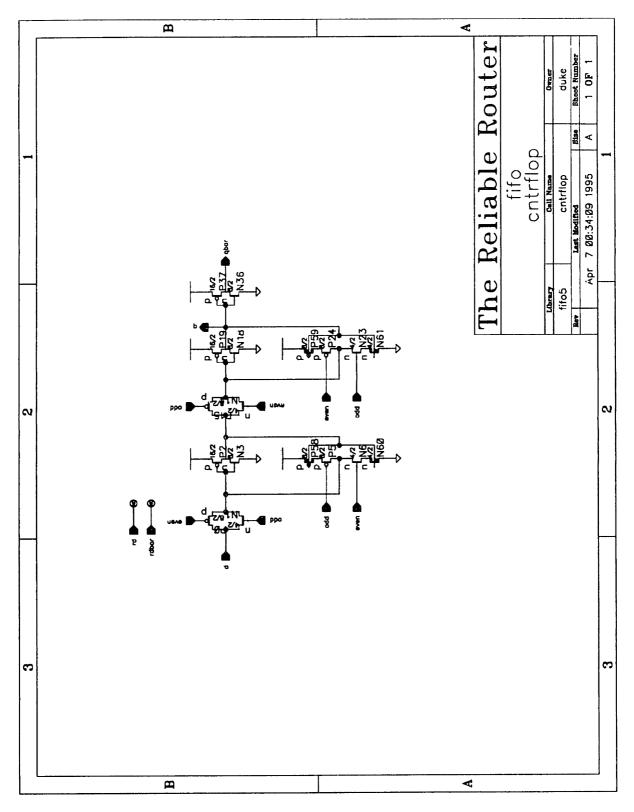

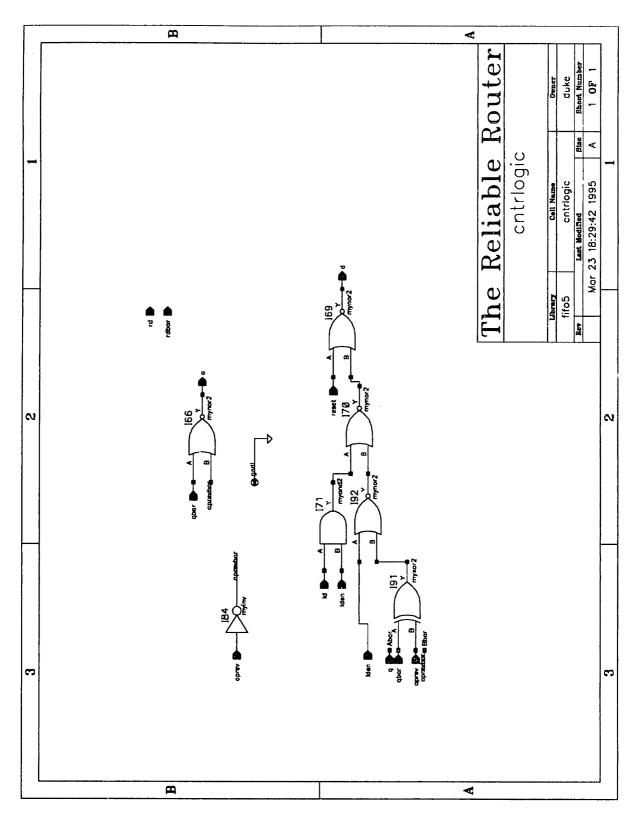

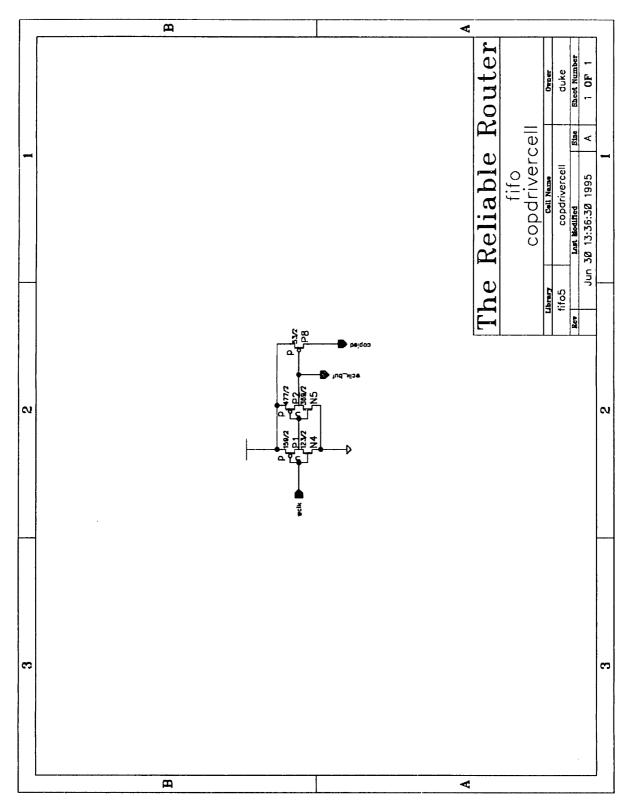

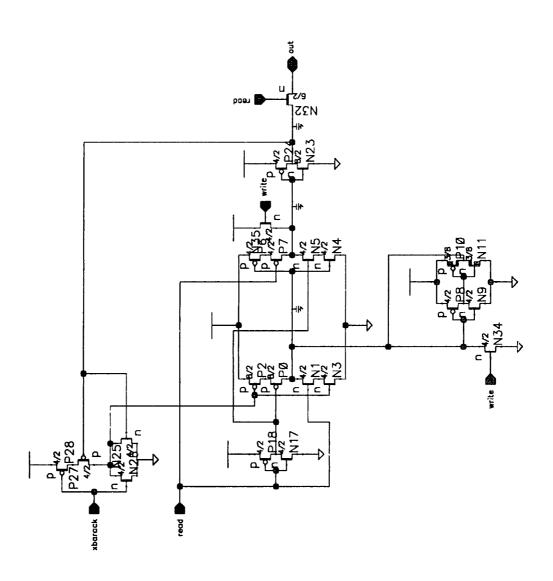

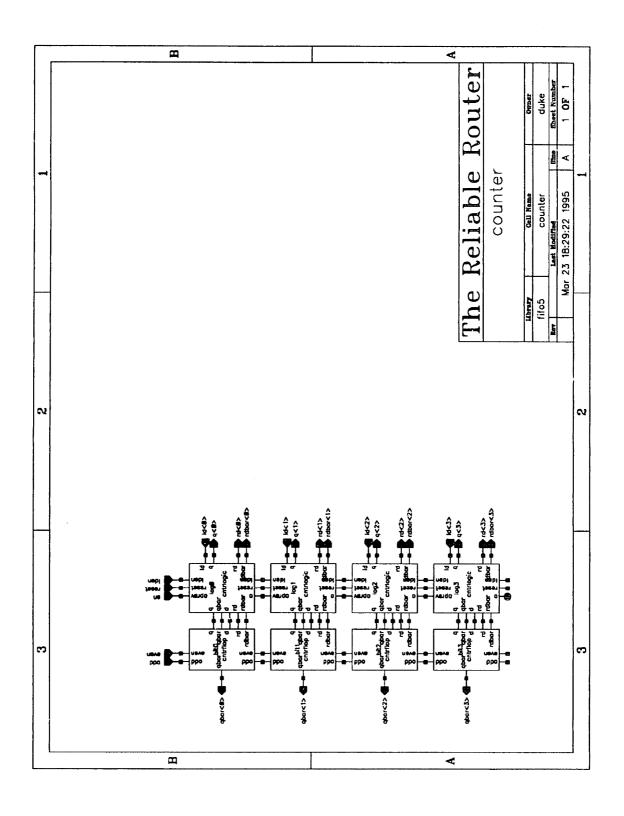

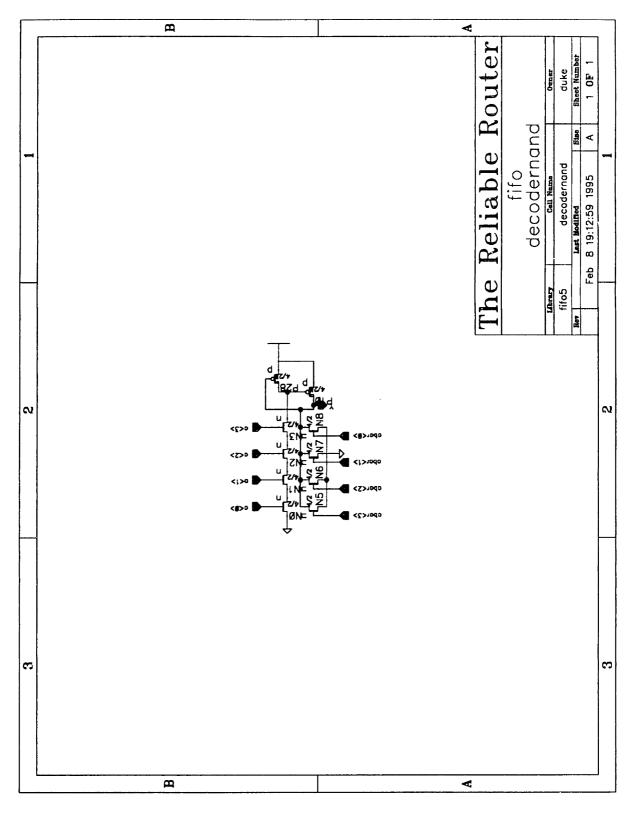

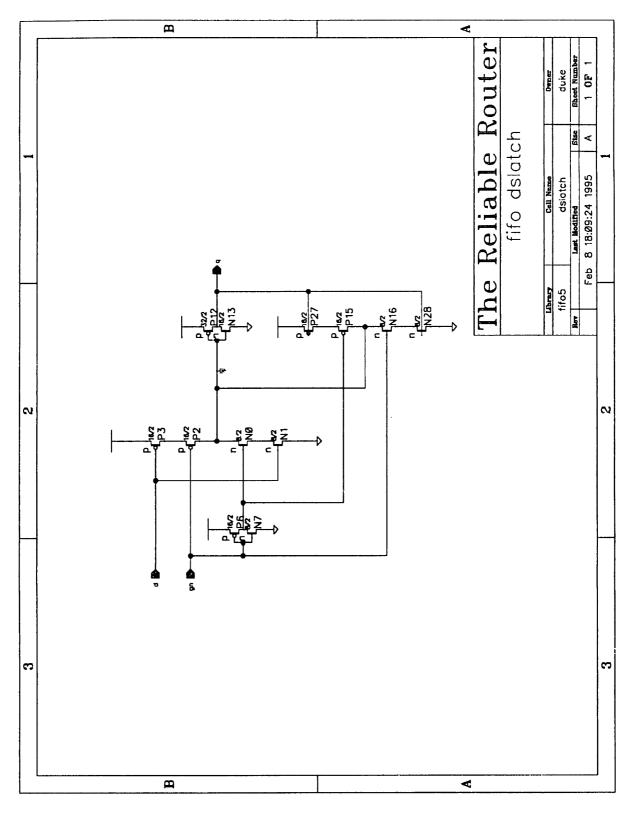

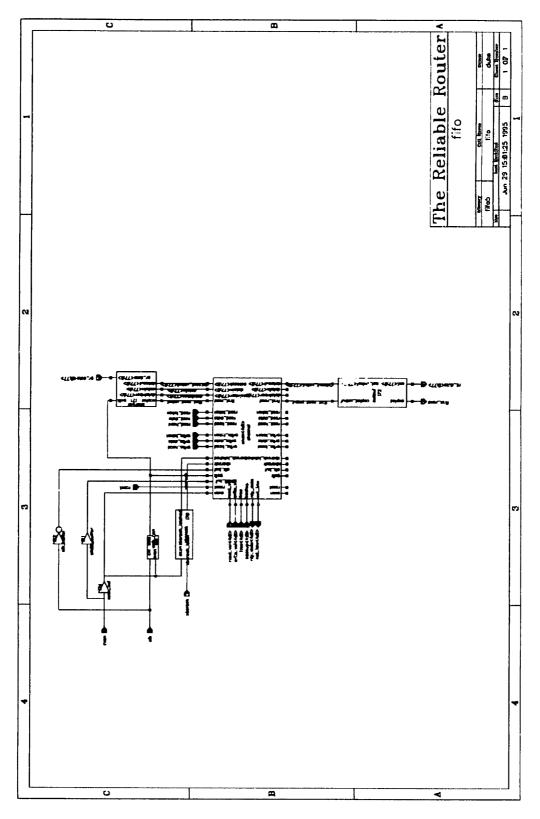

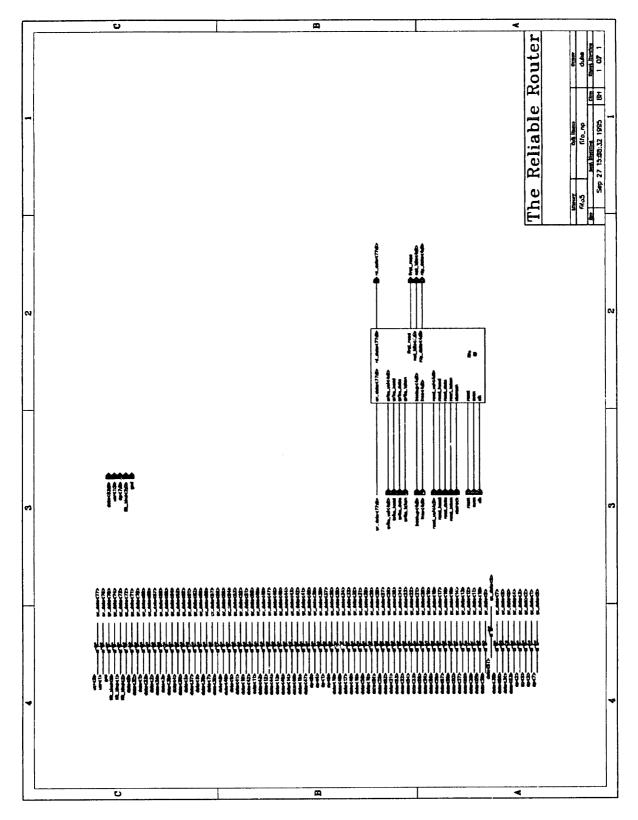

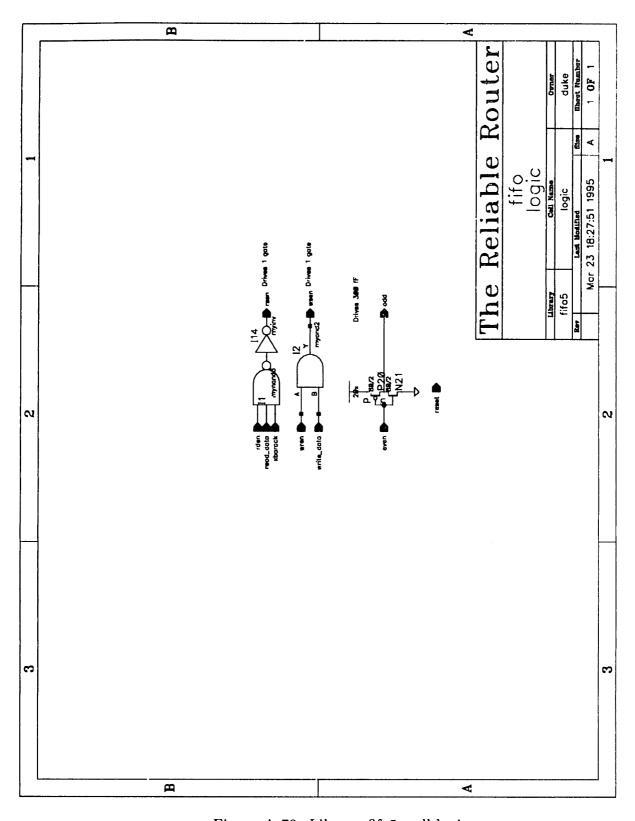

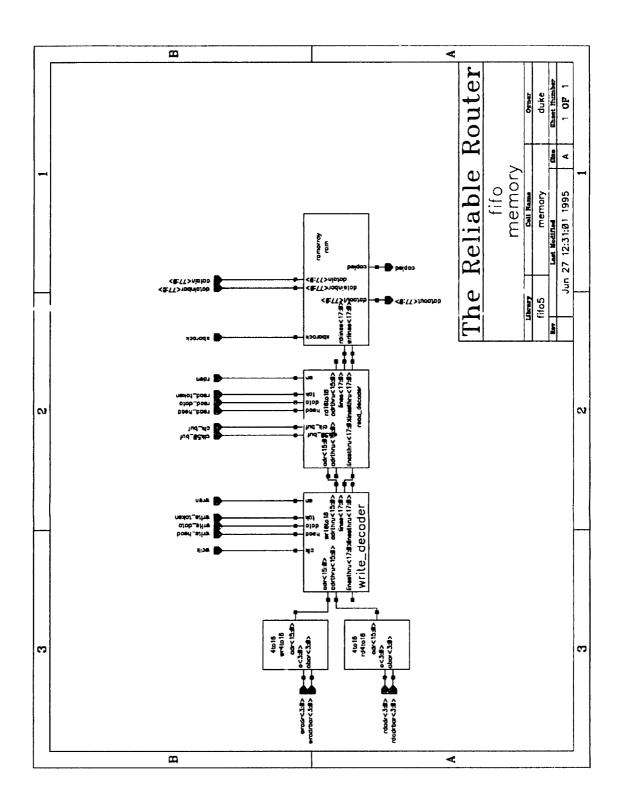

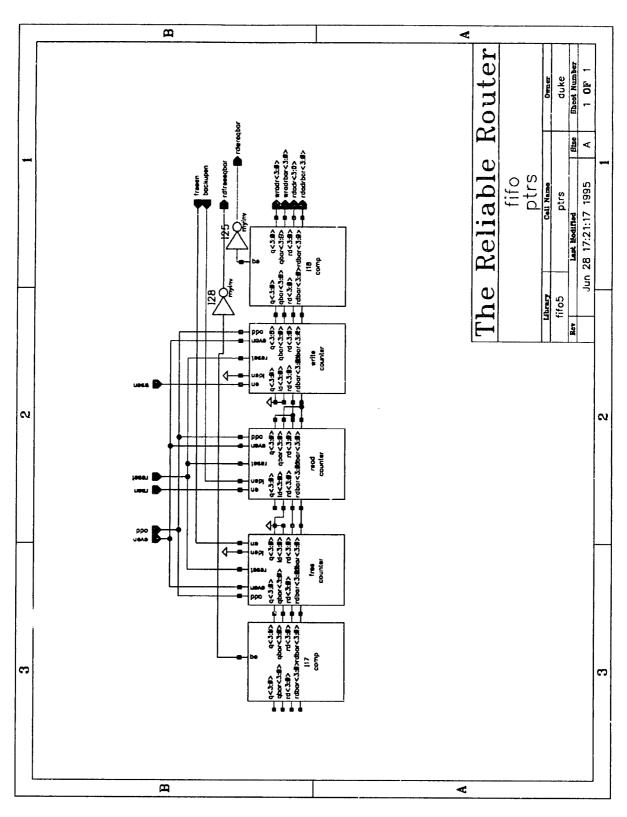

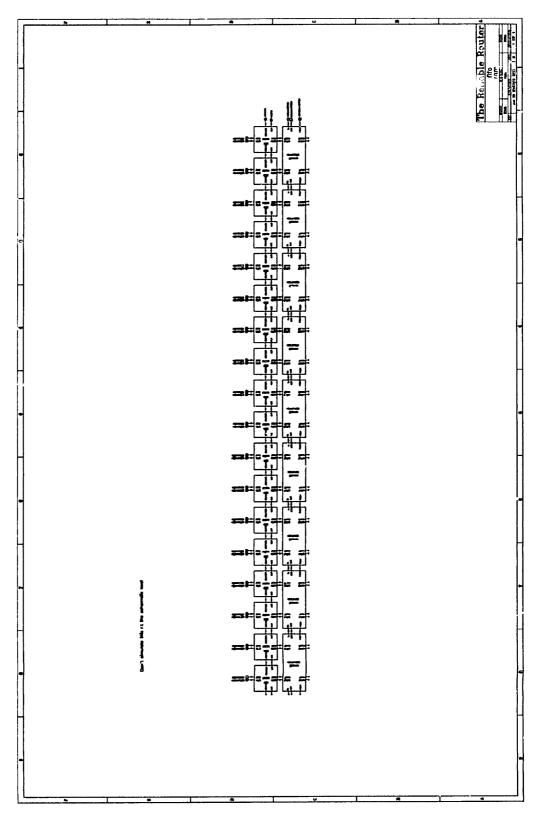

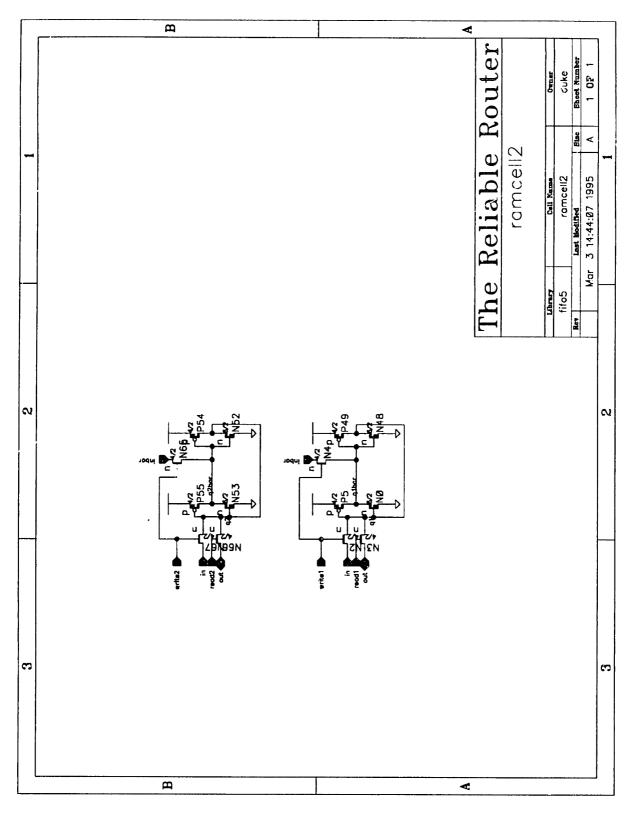

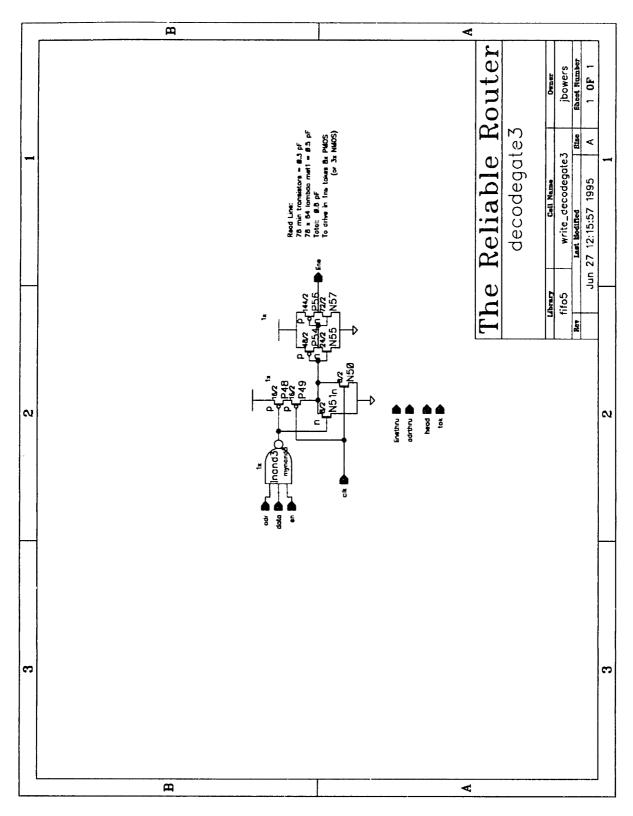

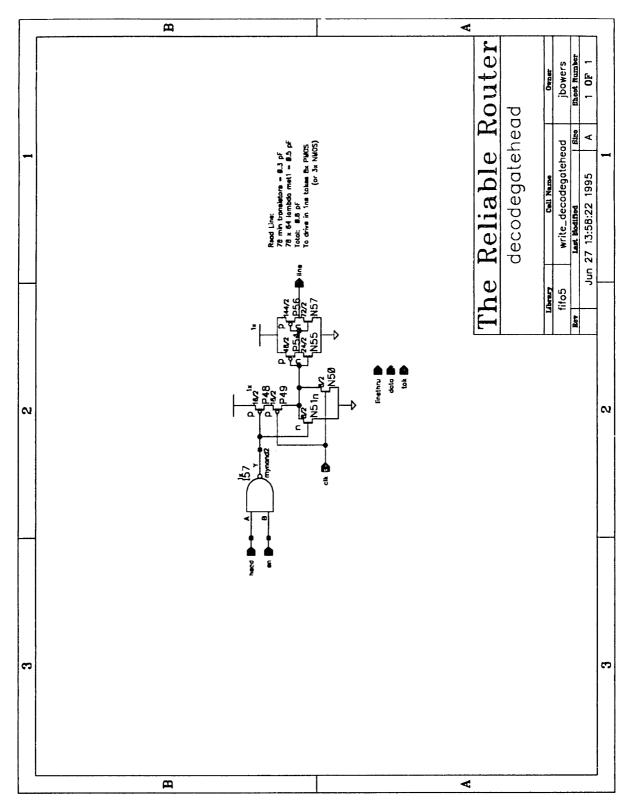

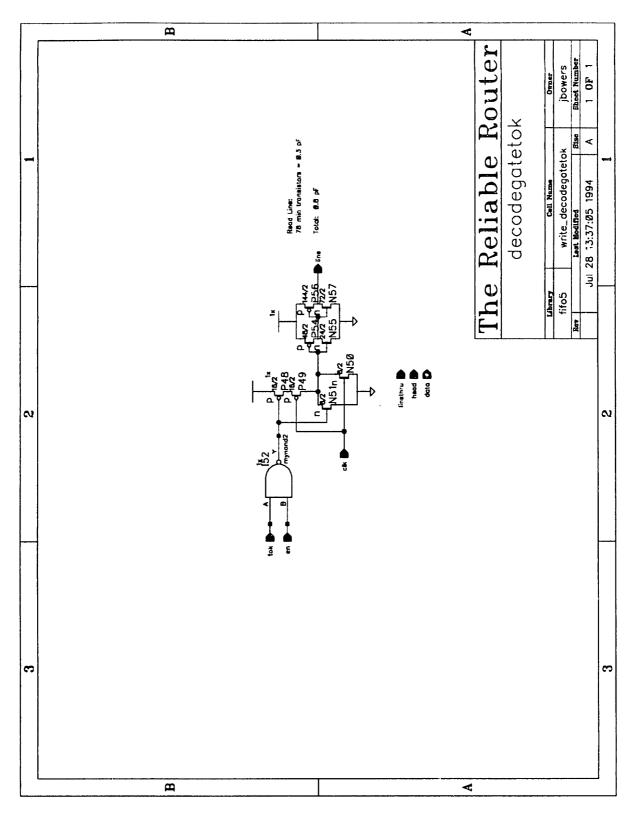

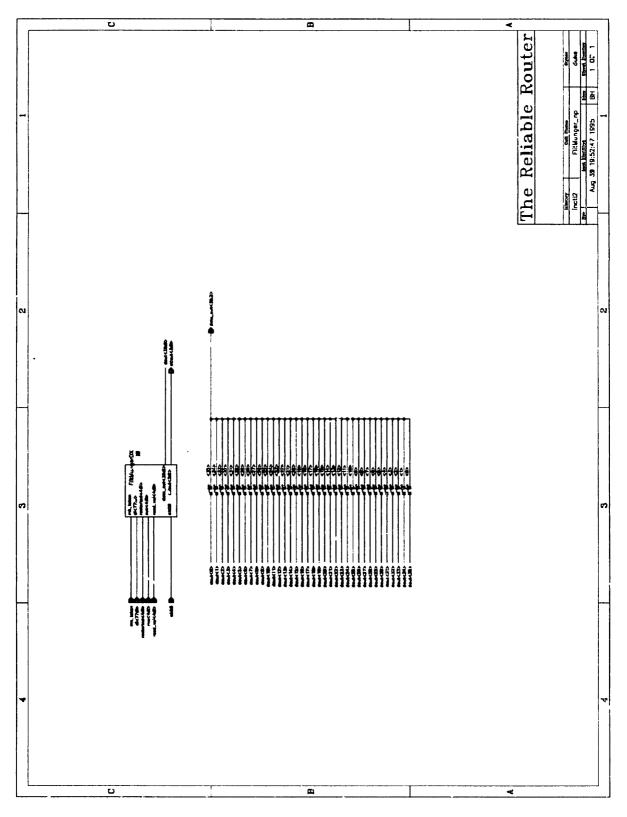

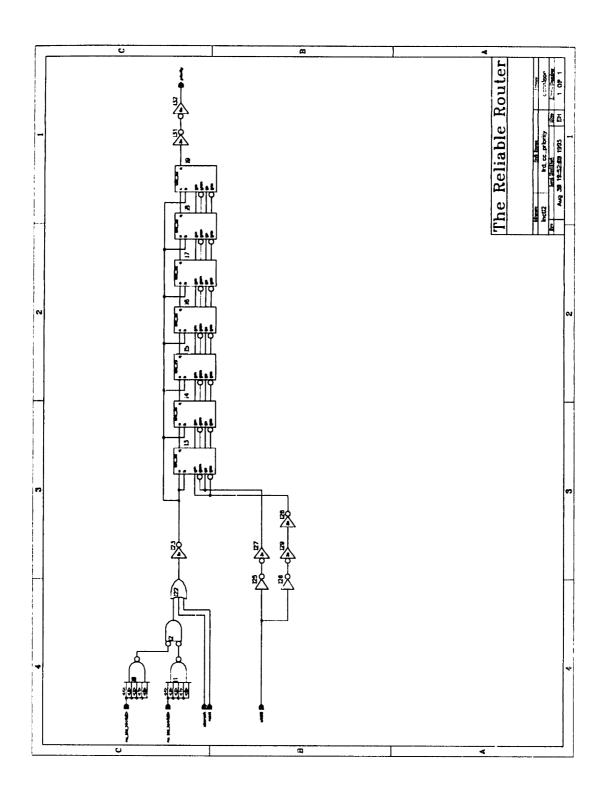

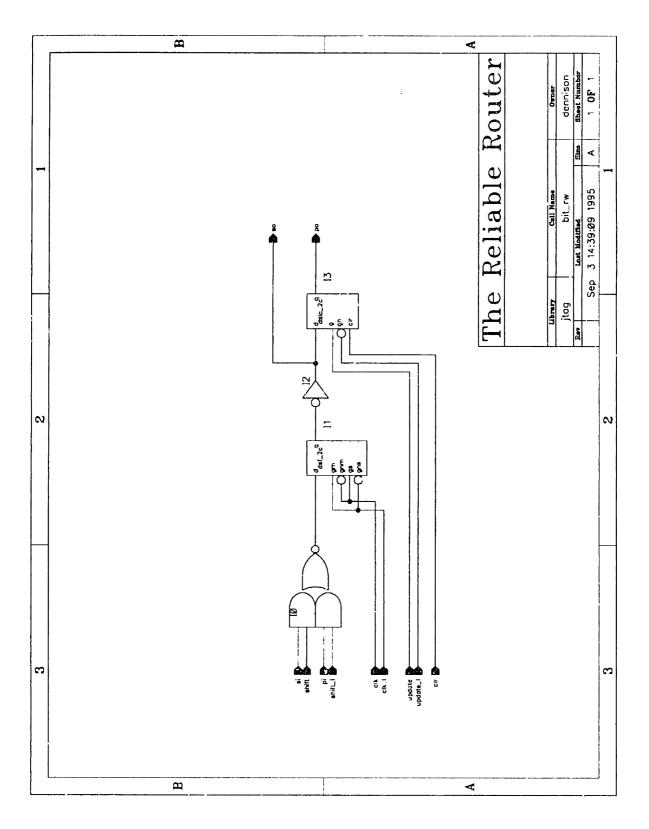

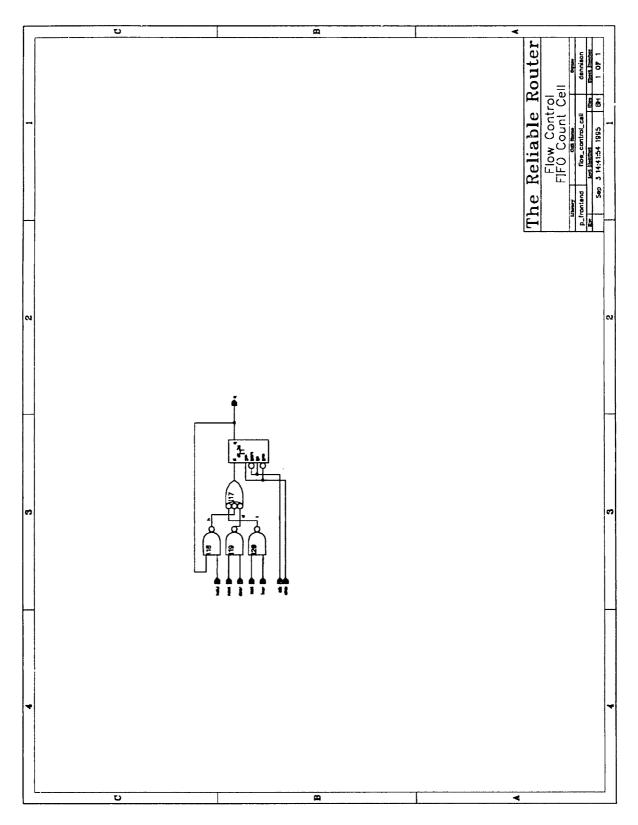

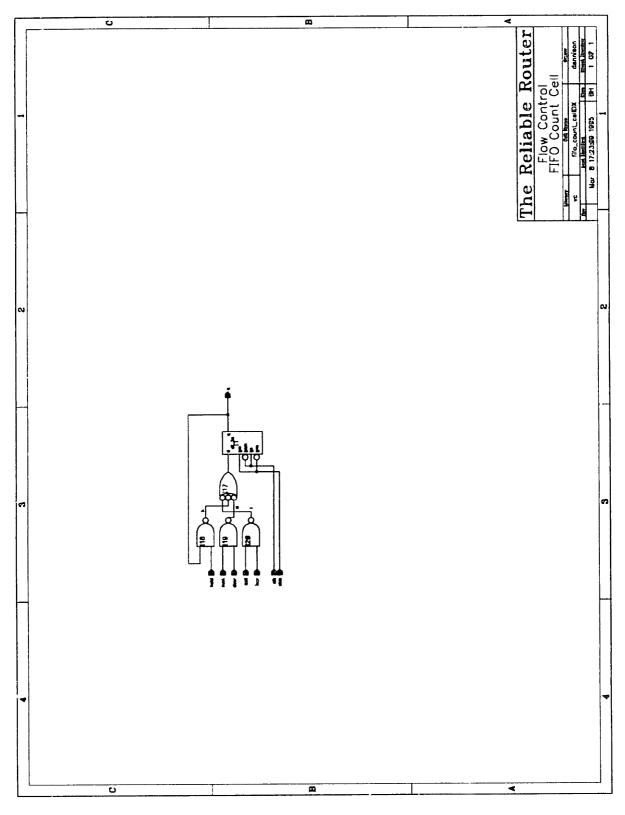

|   |      | 7 E E DIDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 130 |

|   |      | 7.5.6 FIFO Interface to the Crossbar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 131 |

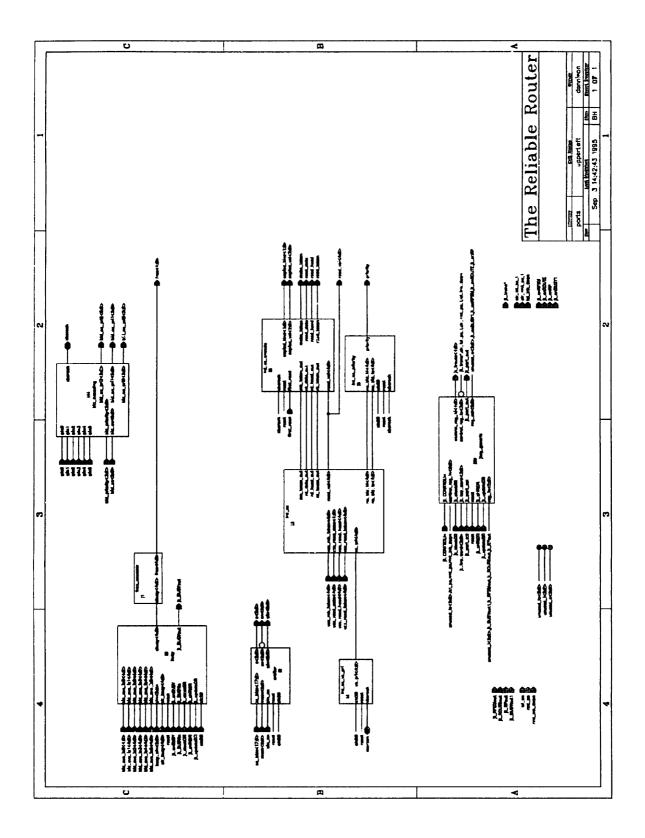

|   |      | 7.5.7 Upper Left                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 131 |

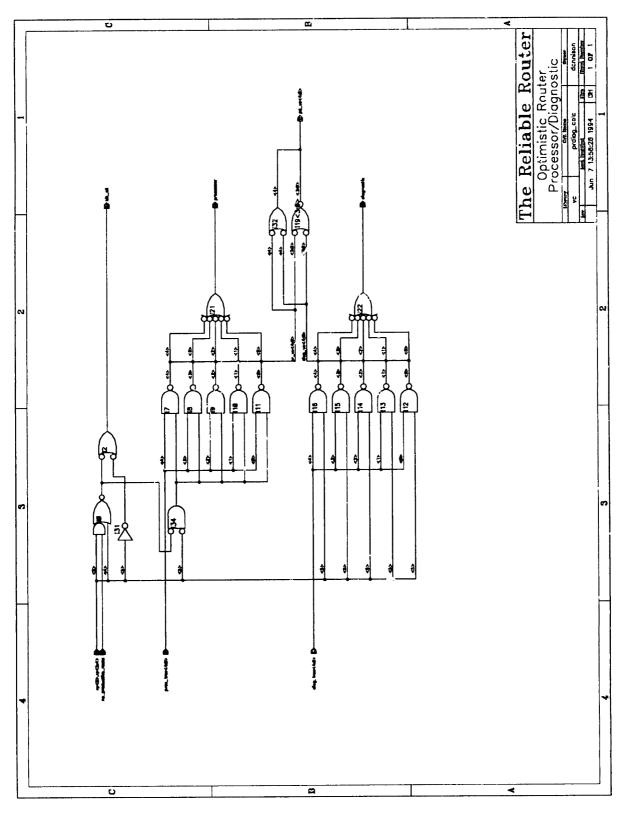

|   | 7.6  | Processor Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 133 |

|   |      | 7.6.1 D D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 133 |

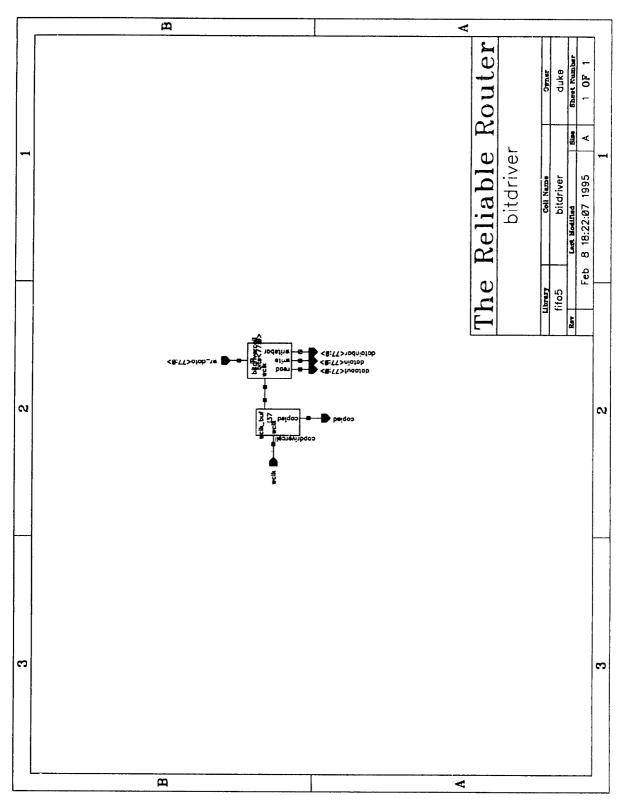

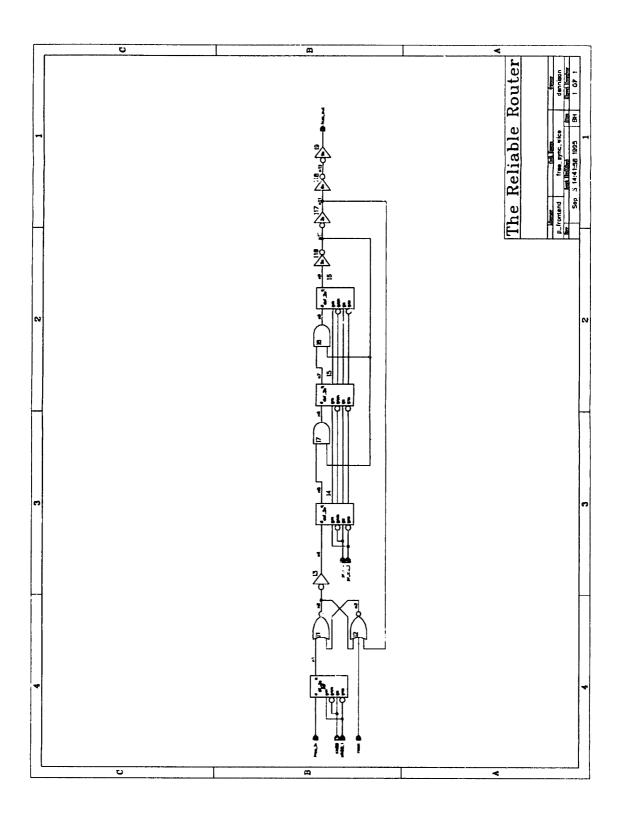

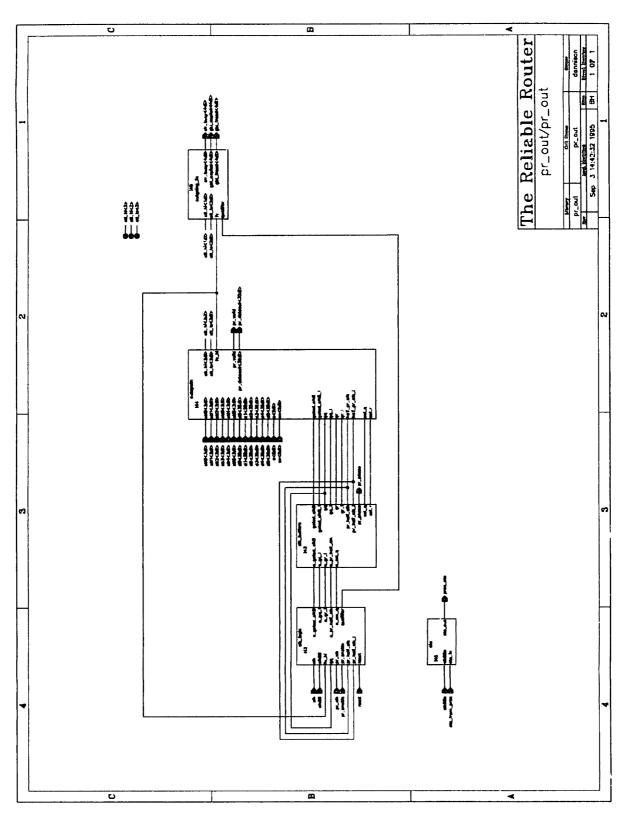

|   |      | 7.6.2 Processor Output Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 134 |

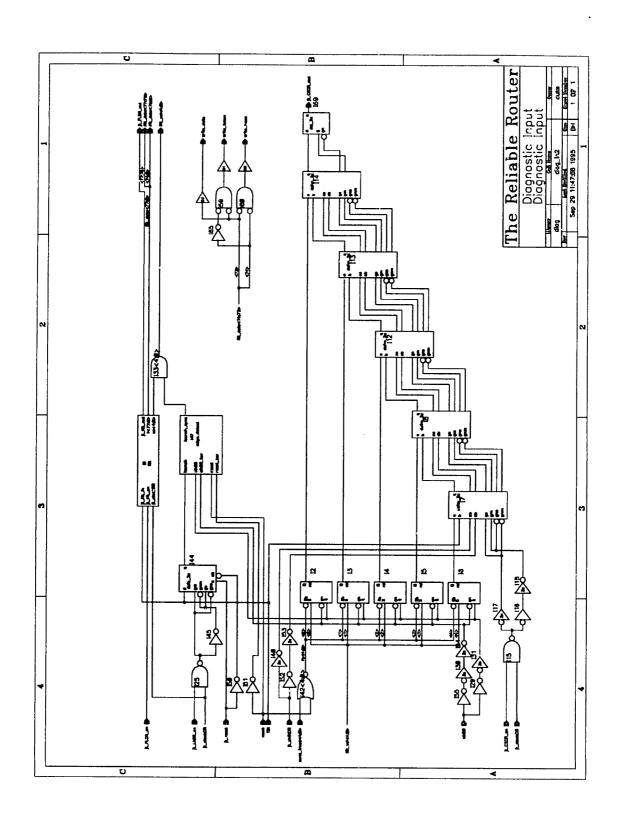

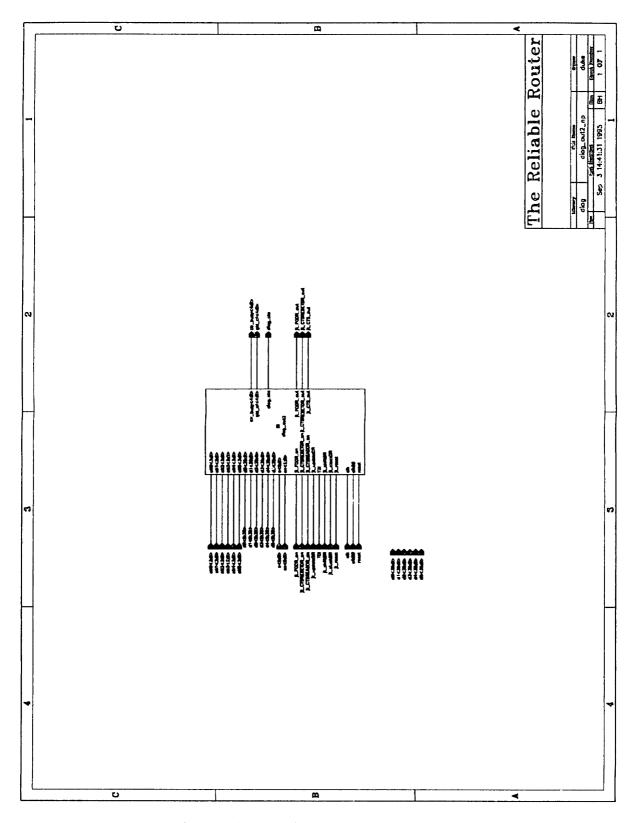

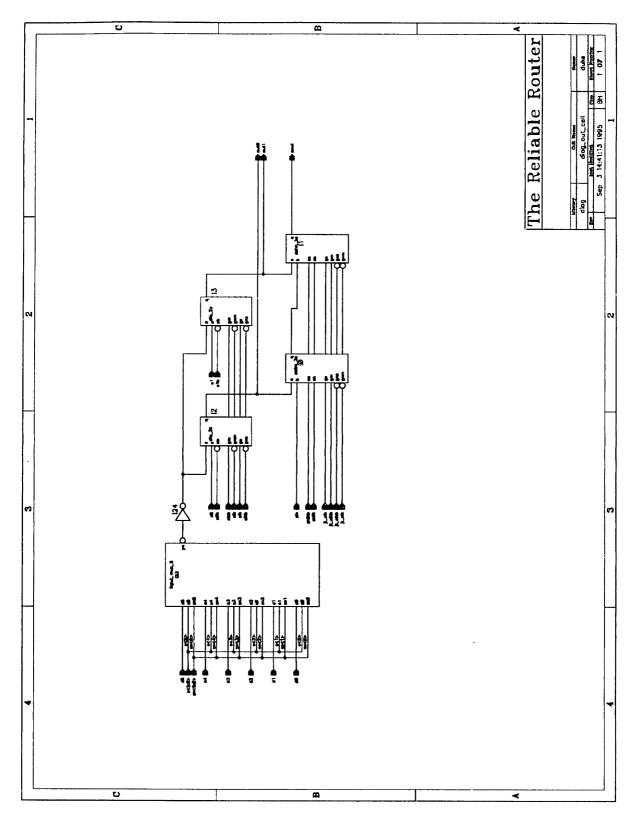

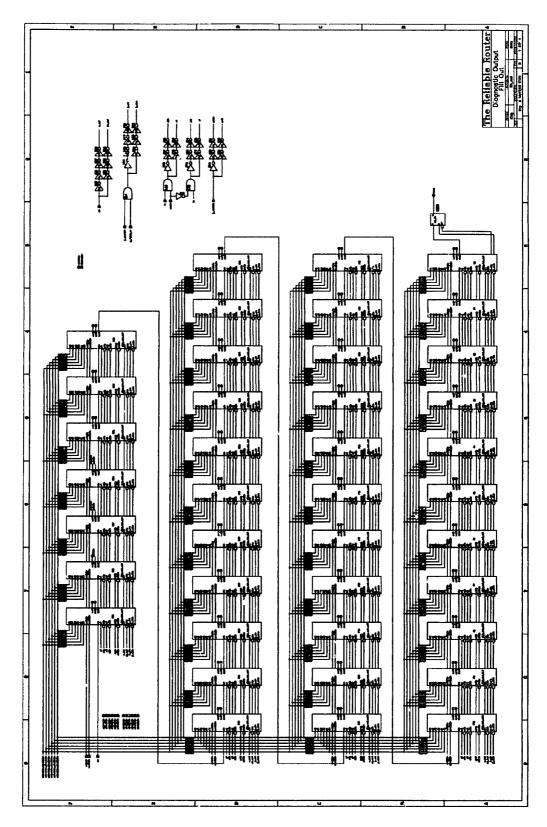

|   | 7.7  | Diagnostic Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 135 |

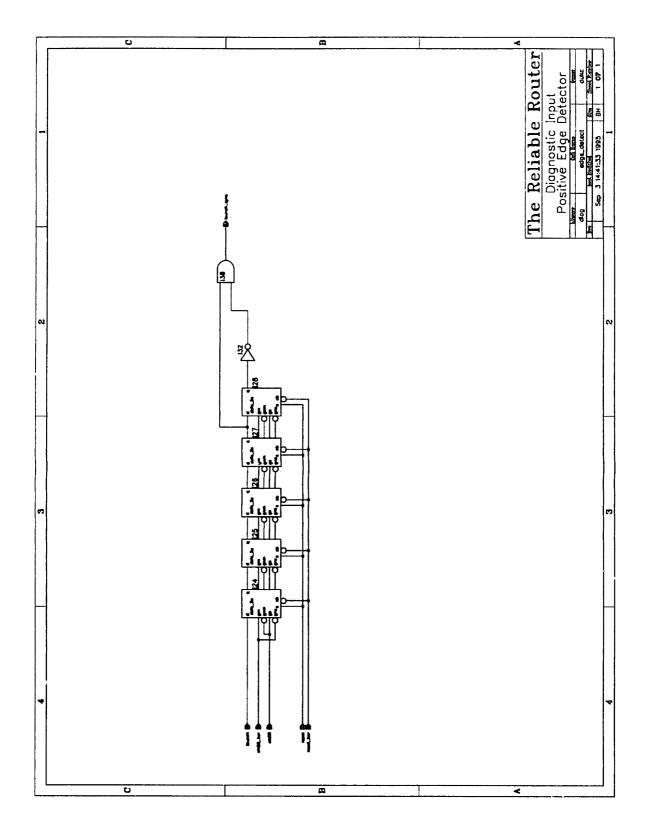

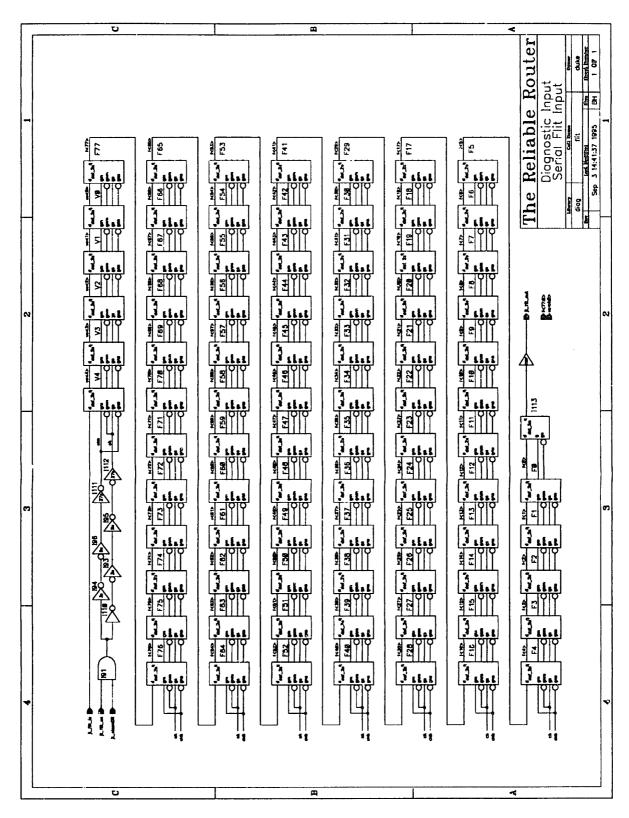

|   |      | 7.7.1 Diagnostic Frontend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 135 |

|   |      | 7.7.2 Diagnostic Output Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 135 |

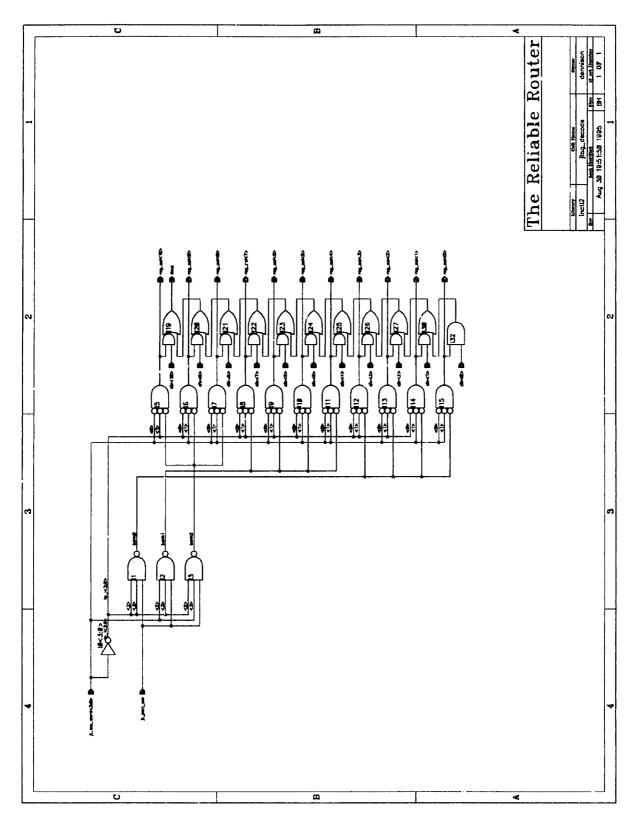

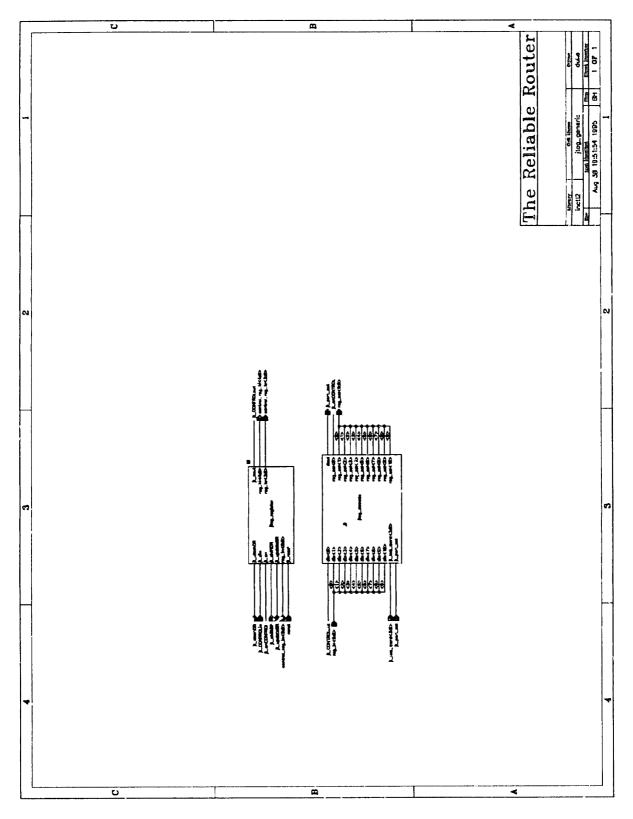

|   | 7.8  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 136 |

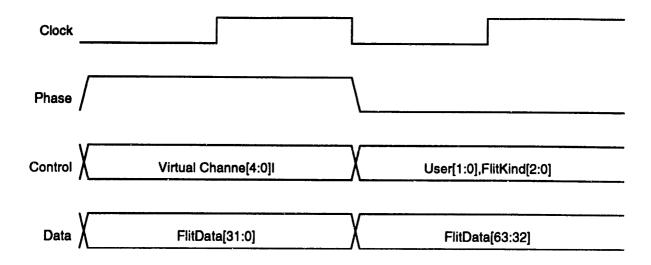

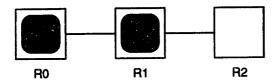

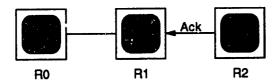

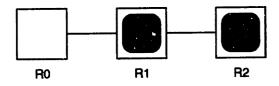

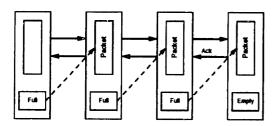

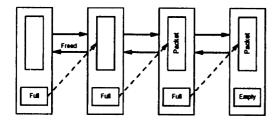

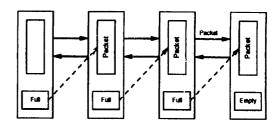

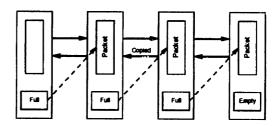

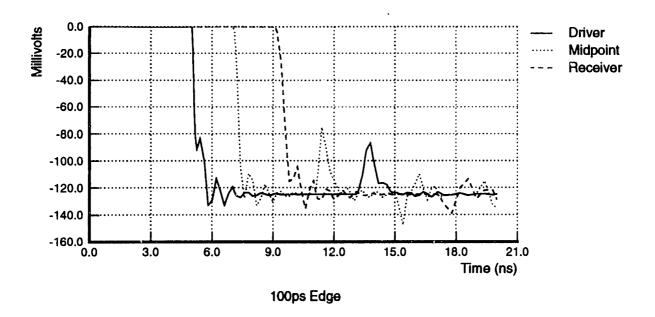

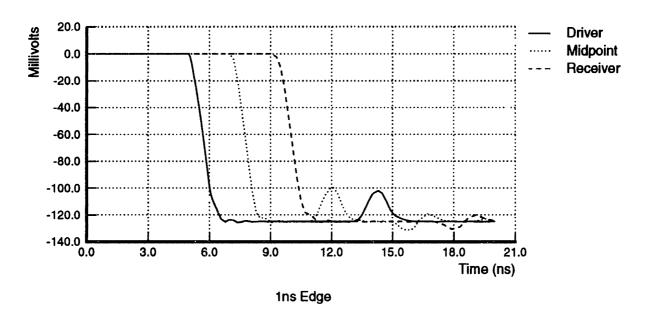

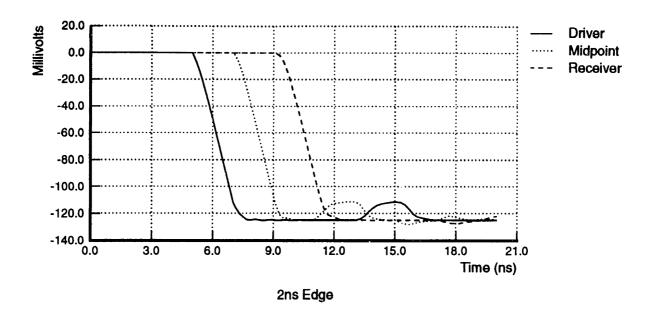

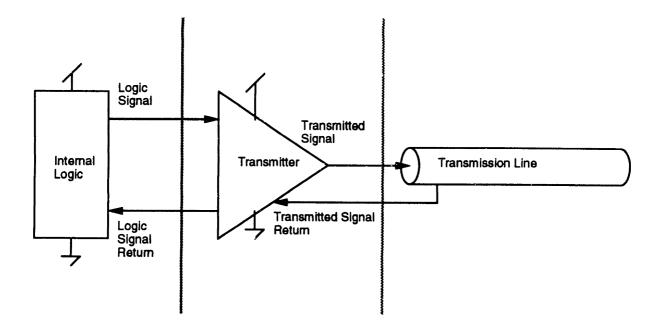

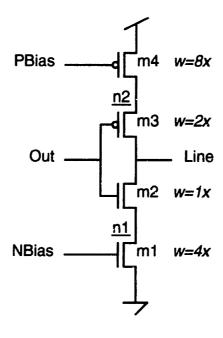

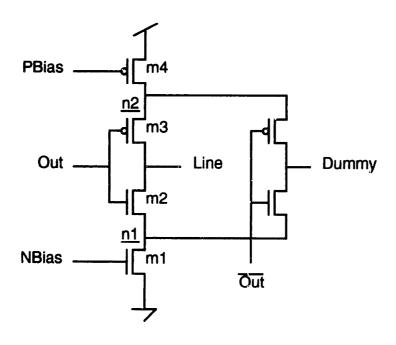

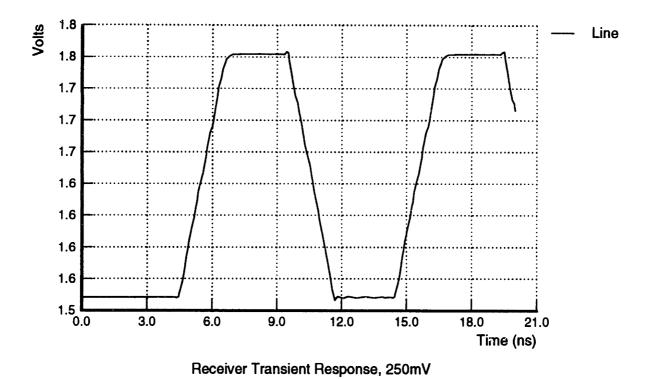

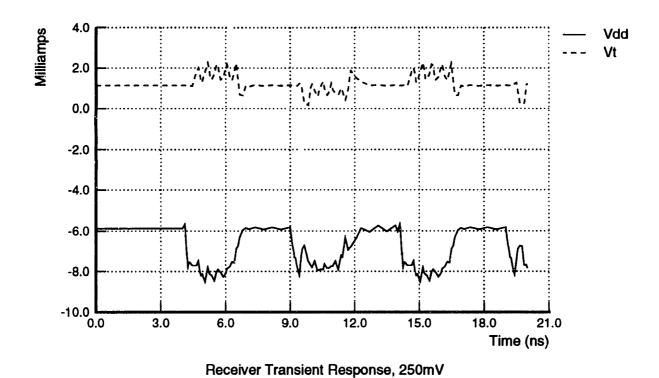

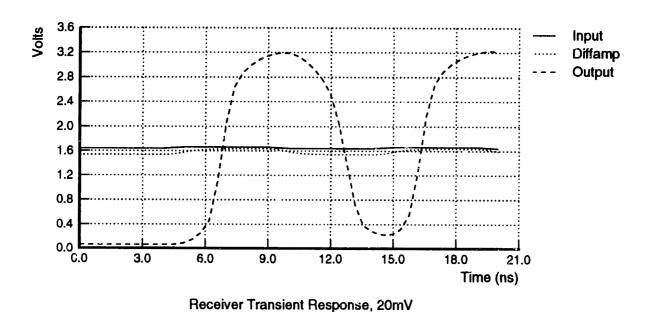

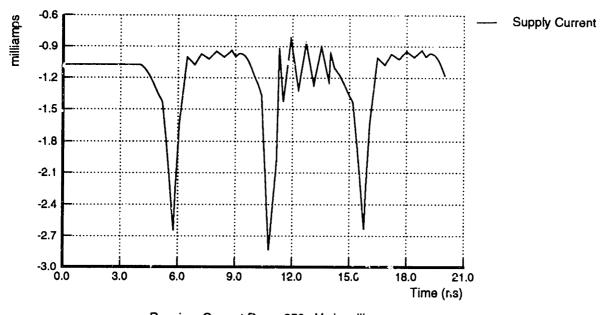

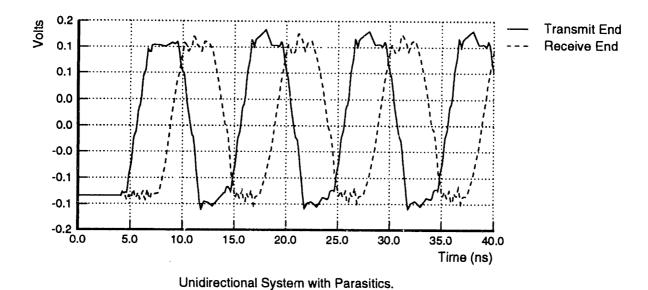

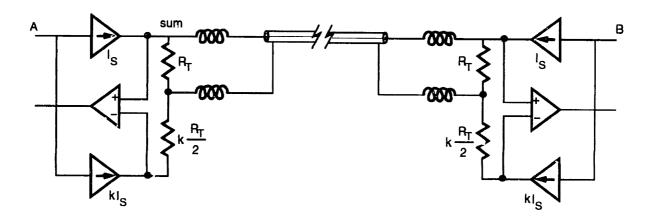

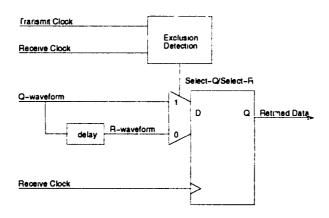

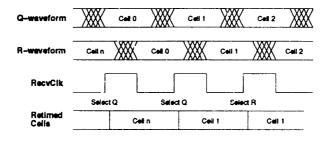

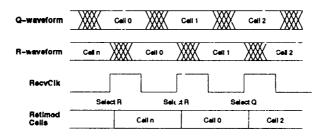

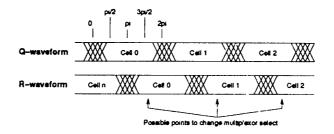

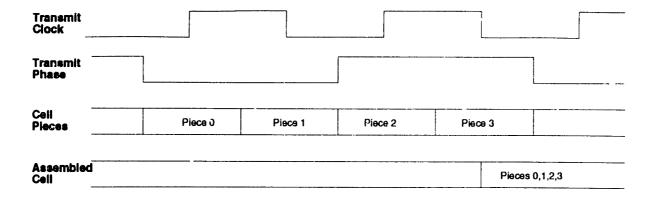

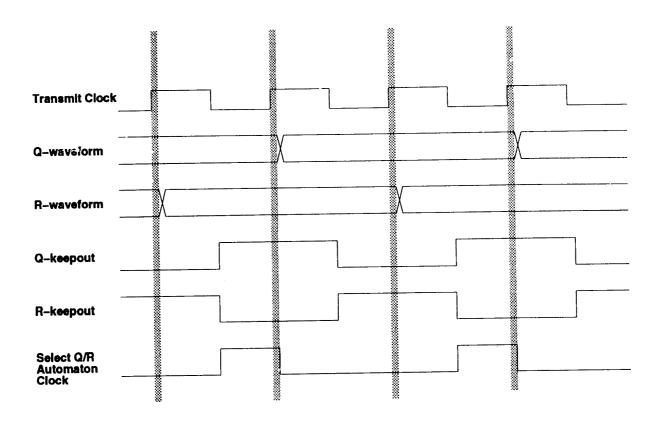

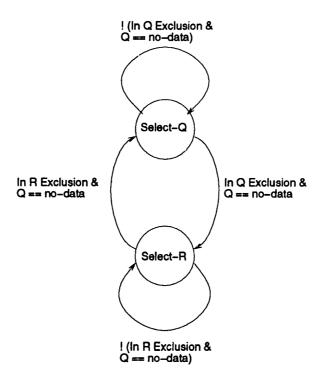

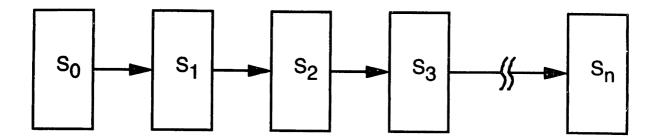

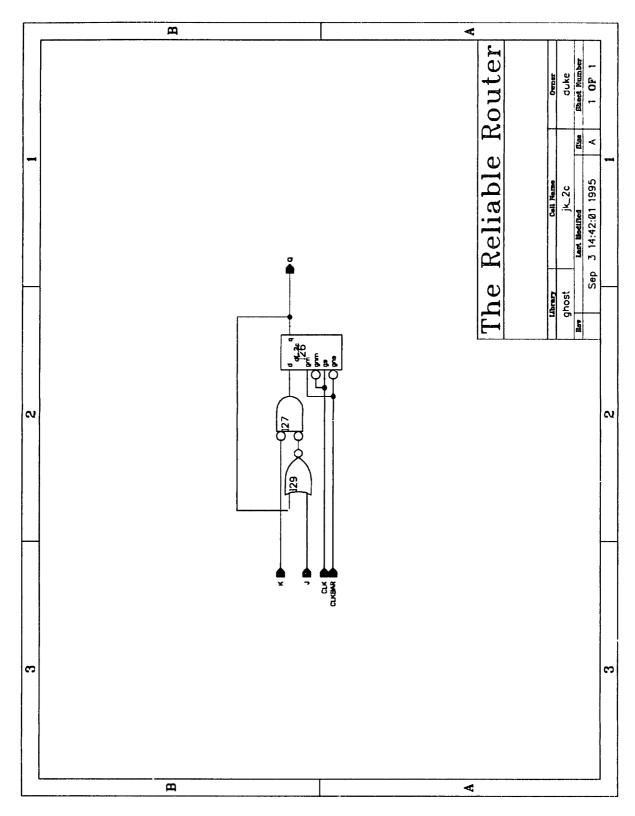

| 8 | Dasi |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |