#### Near Junction Thermal Management of GaN HEMTs via Wafer Bonding

by Robert M. Radway

B.S., E.E.C.S. M.I.T., 2016

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Master of Engineering in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology

February 2017

(c) Massachusetts Institute of Technology 2017. All rights reserved.

Author:

Department of Electrical Engineering and Computer Science February 3, 2017

Certified by: \_

Tomás Palacios, Professor February 3, 2017

Accepted by: .

Christopher Termam, Chairman, Masters of Engineering Theses Committee

### Near Junction Thermal Management of GaN HEMTs

### via Wafer Bonding

by

Robert M. Radway

Submitted to the Department of Electrical Engineering and Computer Science on February 3, 2017, in partial fulfillment of the requirements for the Degree of Master of Engineering in Electrical Engineering and Computer Science

### Abstract

Gallium nitride (GaN)-based high electron mobility transistors (HEMTs) offer excellent performance in power conversion and high frequency power amplification. However, device self-heating limits reliable output power to 1/8th of reported maximums. Device-level thermal management is therefore critical for reliable high power operation. This thesis proposes and examines wafer bonded GaN-on-SiC HEMTs as a thermally efficient alternative to growth structures. This work first compares the thermal properties of this novel structure to the state-of-the-art. It then develops suitable wafer bonding techniques to fabricate this structure. In addition, the bonded interface thermal conductivity is measured via time domain thermoreflectance. The results of these measurements are analyzed to determine the thermal performance of the structure. In all, this thesis shows that the proposed bonded technology is a promising method for the fabrication of the next generation of GaN HEMTs. These devices are expected to perform at a level equivalent to GaN-on-diamond devices, although further process development is needed to achieve high bonding yields.

Thesis Supervisor: Tomás Palacios Title: Professor

# Acknowledgments

I would like to acknowledge first and foremost my supervisor, Professor Tomás Palacios, for the insightful discussions we have had, as well as the wonderful opportunity to join his group and pursue this work. Tomás and the rest of his group make excellent colleagues and have made my Master's work very enjoyable.

In particular, I would like to thank Dr. Noelia Vico Triviño, for her mentorship and collaboration. Noelia was instrumental towards the end of my time in lab, aiding me in solving many of the issues that device processing can entail. In addition, I am extremely grateful to Sameer Joglekar, Daniel Piedra, Min Sun, Yuhao Zhou, Marek Hempel, Elaine McVay, and the other members of the Palacios group for their continual encouragement and aid. Beyond my group, I would especially like to thank the MTL research staff, particularly Kurt Broderick, Bob Bicchieri, Kristofor Payer, Donal Jamieson, Dave Terry and Dennis Ward. Likewise I am indebted to Ali Khalatpour, Andrew Paulson, and the other members of Prof. Qing Hu's group for aid with the lapping procedure.

I am grateful to my many collaborators. I would like to thank Dr. Richard Molnar (MIT Lincoln Labs) for growing the specialized GaN HEMT wafers used in this project. I am indebted to Kevin R. Bagnall (and his advisor Prof. Evelyn N. Wong) for our many discussions about GaN device modeling. Finally, I am thankful for thermal measurements done with Samuel Huberman and Laureen Meroueh (under advisor Prof. Gang Chen), without whom this project would have had no conclusion.

Finally, I am particularly grateful for the continual support, encouragement, and love of my family, friends, and Madeline. Without you, Maddie, I would not have been able to surmount the many failures I encountered. You have always been there during both my achievements and upsets, and I hope you will always be there in the future.

# Contents

| 1        | Introduction |                                                          |           |  |  |

|----------|--------------|----------------------------------------------------------|-----------|--|--|

|          | 1.1          | GaN HEMTs                                                | 14        |  |  |

|          |              | 1.1.1 Gallium Nitride Growth                             | 17        |  |  |

|          | 1.2          | Scope and Outline of Thesis                              | 19        |  |  |

| <b>2</b> | The          | ermal Properties of GaN Devices                          | <b>21</b> |  |  |

|          | 2.1          | Heat Generation in GaN Devices                           | 21        |  |  |

|          | 2.2          | Heat Dissipation in Multilayered Epitaxies               | 22        |  |  |

|          |              | 2.2.1 Thermal Conductivity of Materials                  | 23        |  |  |

|          |              | 2.2.2 Phonon Mean Free Path Suppression                  | 25        |  |  |

|          |              | 2.2.3 Thermal Boundary Conductivity                      | 26        |  |  |

|          |              | 2.2.4 Thermal Conductivities of Buffer Layers            | 28        |  |  |

| 3        | The          | ermally Efficient GaN-on-SiC Epitaxies via Wafer Bonding | 31        |  |  |

| 0        | 3.1          | Thermal Modeling of GaN Devices                          | 31        |  |  |

|          | 0.1          | 3.1.1 Analytical Method                                  | 32        |  |  |

|          | 3.2          | Performance of Current GaN Technologies                  | 33        |  |  |

|          | 0.2          | 3.2.1 GaN-on-SiC                                         | 33        |  |  |

|          |              | 3.2.2 GaN-on-Diamond                                     | 35        |  |  |

|          | 3.3          | GaN-on-SiC via Wafer Bonding                             | 38        |  |  |

|          |              | 3.3.1 GaN-SiC Direct Bonded Structure                    | 39        |  |  |

|          |              | 3.3.2 GaN-on-SiC Double-Bonded Structure                 | 39        |  |  |

|          | 3.4          | Performance of Wafer Bonded GaN-on-SiC HEMT              | 40        |  |  |

|          | -            | 3.4.1 Variations of Model Assumptions                    | 42        |  |  |

|          |              | 3.4.2 Thermal Performance of Double Bonded Structure     | 43        |  |  |

|          | 3.5          | Summary of Performance Characteristics                   | 44        |  |  |

|          | 3.6          | Discussion                                               | 45        |  |  |

| 4        | Gal          | N - SiC Wafer Bonding Technology                         | 47        |  |  |

|          | 4.1          | Principals of GaN-SiC Bonding                            | 48        |  |  |

|          | 4.2          | Thermal Mismatch During Bonding                          | 50        |  |  |

|          | 4.3          | Proposed Bonding Technique                               | 52        |  |  |

|          | -            | 4.3.1 Step 1: Sample Cleaning                            | 52        |  |  |

|          |              | 4.3.2 Step 2: Surface Activation                         | 53        |  |  |

|          |              | 4.3.3 Step 3: Preliminary Bonding                        | 53        |  |  |

|              |     | 4.3.4    | Step 4: Bond Annealing                                     | 54 |

|--------------|-----|----------|------------------------------------------------------------|----|

|              |     | 4.3.5    | Experimental Methodology                                   | 54 |

|              | 4.4 | Bondir   | ng Materials                                               | 55 |

|              | 4.5 | Bondir   | ng Results                                                 | 57 |

|              |     | 4.5.1    | Cleaning & Surface Activation Experiments                  | 57 |

|              |     | 4.5.2    | High Temperature Annealing                                 | 60 |

|              | 4.6 | High 7   | Cemperature Bonding Fixtures                               | 62 |

|              | 4.7 | Stress   | Relieving Etched Channels                                  | 63 |

|              | 4.8 | Final I  | Bond Annealing                                             | 64 |

|              | 4.9 | Bondir   | ng Discussion                                              | 66 |

| <b>5</b>     | The | rmal N   | Measurement of GaN-SiC Bonded Structure                    | 69 |

|              | 5.1 | Sample   | e Preparation                                              | 70 |

|              |     | 5.1.1    | Lapping of Si                                              | 70 |

|              |     | 5.1.2    | $SF_6$ RIE                                                 | 71 |

|              |     | 5.1.3    | GaN Etching                                                | 74 |

|              |     | 5.1.4    | GaN/AlGaN Selective Stop Etch                              | 75 |

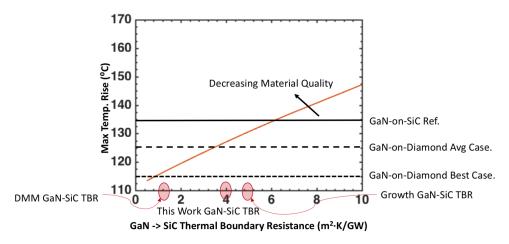

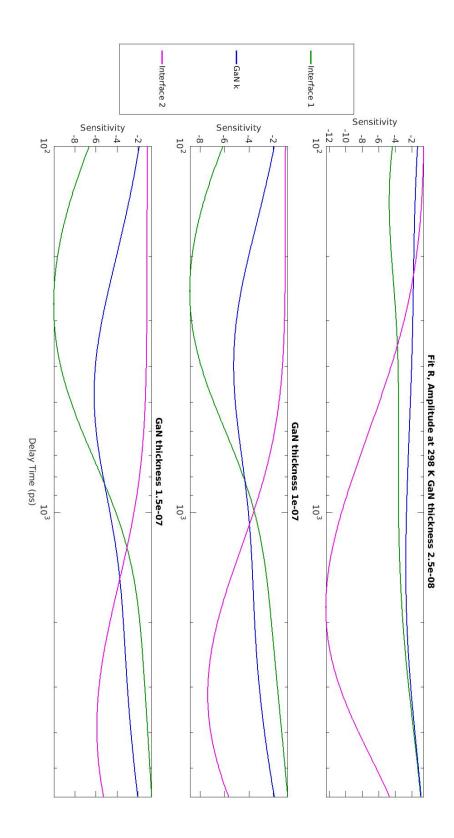

|              | 5.2 | Time I   | Domain Thermoreflectance Measurement of Bonded GaN-SiC TBR | 77 |

|              |     | 5.2.1    | Measurement Technique                                      | 78 |

|              |     | 5.2.2    | Sensitivity Analysis                                       | 79 |

|              |     | 5.2.3    | Samples Measured                                           | 81 |

|              |     | 5.2.4    | Measured Results                                           | 82 |

|              | 5.3 | Discus   | sion of Results                                            | 84 |

|              |     | 5.3.1    | Improved Backside Etching                                  | 85 |

| 6            | Con | clusion  | n and Future Work                                          | 87 |

| $\mathbf{A}$ | The | rmal N   | Modeling Method                                            | 91 |

| в            | Sen | sitivitv | Analysis for Time Domain Thermoreflectance Measure-        |    |

|              | men | Ũ        | v                                                          | 95 |

# List of Figures

| 1-1  | (a) Epitaxial structure for a generic HEMT (b) Band diagram around a AlGaN/GaN heterojunction                                             | 15 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1-2  | Epitaxial structure for (a) GaN-on-SiC and (b) GaN-on-Diamond HEMTs                                                                       | 16 |

| 2-1  | Generic epitaxial structure for thermal evaluation $\ldots \ldots \ldots \ldots$                                                          | 23 |

| 2-2  | Thermal boundary resistance (a) diffuse mismatch model (b) acoustic mismatch model                                                        | 26 |

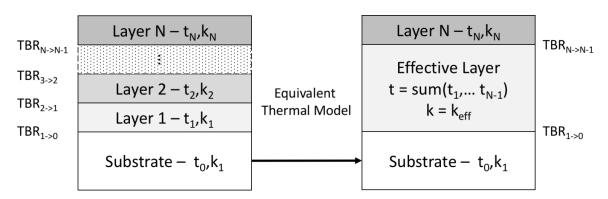

| 2-3  | Equivalent thermal models for a multi-layered structure                                                                                   | 29 |

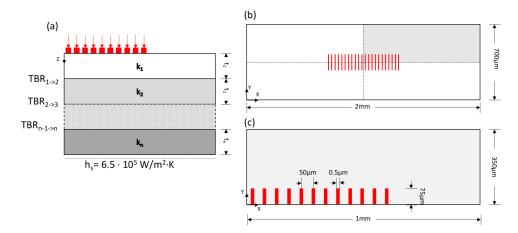

| 3-1  | Generic epitaxial thermal structure (a) side view (b) top view (c) symmetrically reduced top view                                         | 32 |

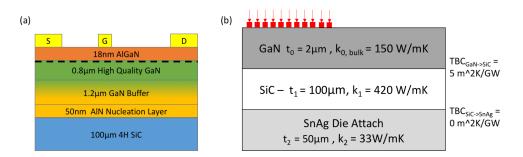

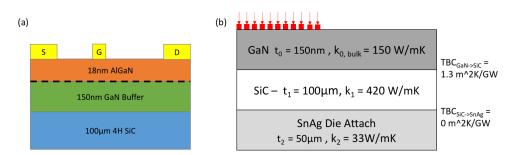

| 3-2  | Standard GaN-on-SiC HEMT (a) epitaxial structure (b) modeled struc-<br>ture with parameters listed.                                       | 34 |

| 3-3  | Standard GaN-on-SiC HEMT simulated temperature rise at 5W/mm power dissipation (a) under central heat source (b) on surface around        |    |

|      | central heat source                                                                                                                       | 34 |

| 3-4  | Max temperature rise in GaN-on-SiC HEMTs as a function of GaN buffer thickness                                                            | 36 |

| 3-5  | Standard GaN-on-Diamond HEMT epitaxial structure with model parameters listed.                                                            | 37 |

| 3-6  | Standard GaN-on-Diamond HEMT simulated temperature rise at 5W/mm<br>power dissipation (a) under central heat source (b) on surface around |    |

|      | central heat source                                                                                                                       | 37 |

| 3-7  | Wafer bonding process for GaN-on-SiC HEMTs                                                                                                | 38 |

| 3-8  | Double wafer bonding process for GaN-on-SiC HEMTs                                                                                         | 40 |

| 3-9  | Bonded GaN-on-SiC HEMT epitaxial structure with model parameters listed.                                                                  | 41 |

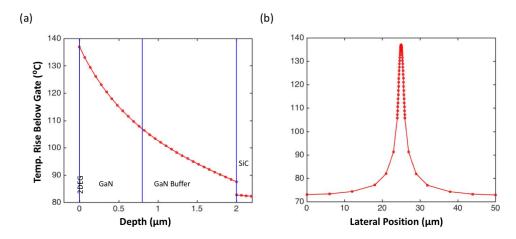

| 3-10 | Bonded GaN-on-SiC HEMT simulated temperature rise at 5W/mm power dissipation (a) under central heat source (b) on surface around          |    |

|      | central heat source                                                                                                                       | 41 |

| 3-11 | Max temperature rise in bonded GaN-on-SiC HEMTs as a function of GaN/SiC Thermal Boundary Conductivity                                    | 43 |

| 3-12 | Double bonded GaN-on-SiC HEMT epitaxial structure with model pa-                                                                          | -  |

|      | rameters listed.                                                                                                                          | 43 |

| 3-13   | Double bonded GaN-on-SiC HEMT simulated temperature rise at 5W/m power dissipation (a) under central heat source (b) on surface around central heat source | m<br>44 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|        |                                                                                                                                                            | 44      |

| 4-1    | Pictorial representation of the bonding chemistry                                                                                                          | 50      |

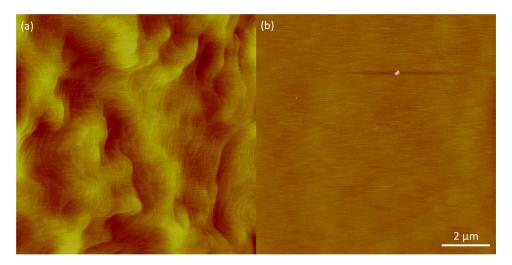

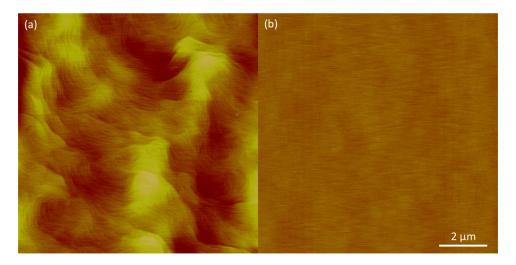

| 4-2    | AFM measurement of (a) GaN and (b) SiC samples                                                                                                             | 56      |

| 4-3    | AFM measurement of (a) GaN and (b) SiC samples after 24W Ar                                                                                                |         |

|        | plasma exposure                                                                                                                                            | 58      |

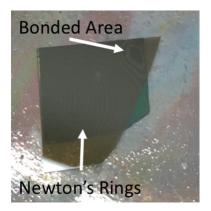

| 4-4    | Sample with small visible bonding region                                                                                                                   | 59      |

| 4-5    | Initial bond quality examined under IR camera                                                                                                              | 60      |

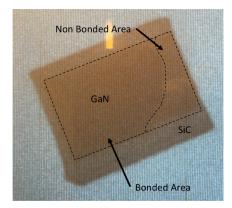

| 4-6    | After failed anneal at 1000C for 1hr (a) GaN degradation and (b) SiC                                                                                       |         |

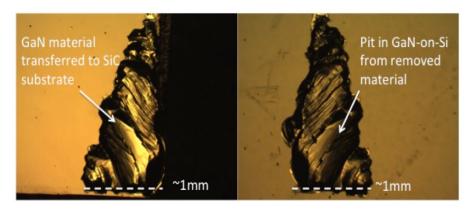

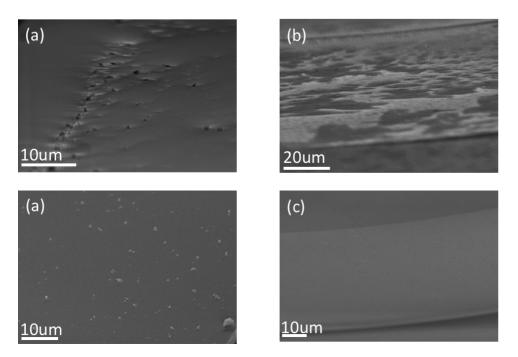

|        | surface under 5X magnification                                                                                                                             | 61      |

| 4-7    | Transferred GaN/Si material after annealing                                                                                                                | 61      |

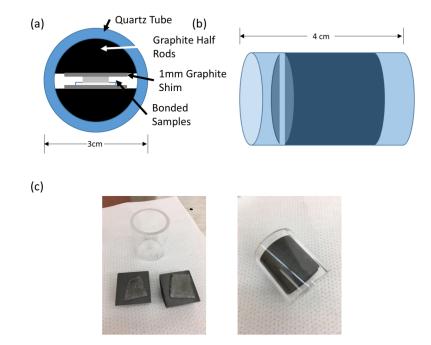

| 4-8    | Graphite bonding fixture                                                                                                                                   | 63      |

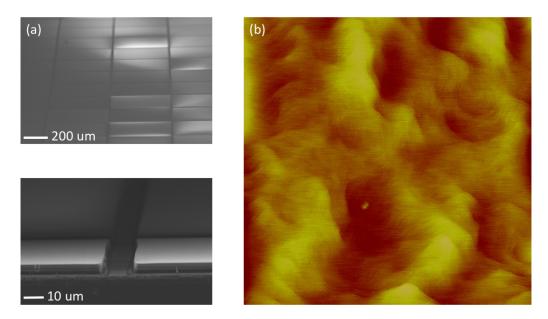

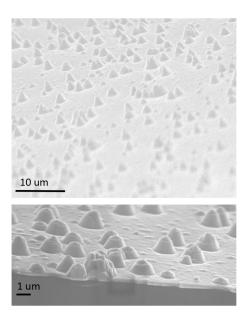

| 4-9    | Stress relieving channels etched into GaN (a) SEM Images (b) Surface                                                                                       |         |

|        | AFM after etch processing                                                                                                                                  | 64      |

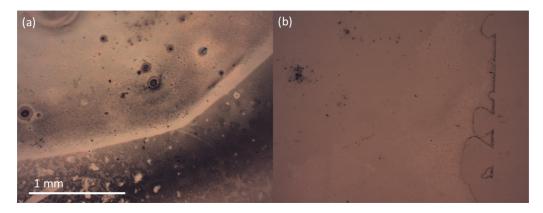

| 4-10   | GaN surface after failed anneal with stress-relieving channels, optical                                                                                    |         |

|        | microscope 5X mag                                                                                                                                          | 65      |

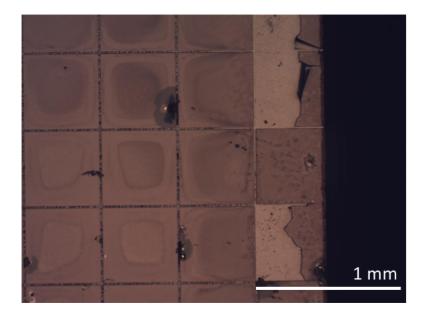

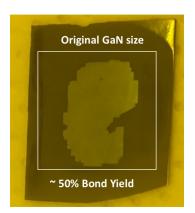

|        | Final bond yield on best sample                                                                                                                            | 65      |

| 4-12   | He+ ion microscopy imaging showing (a) void at scribed edge (b) side                                                                                       |         |

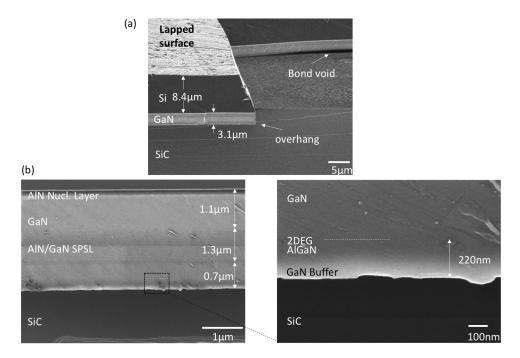

|        | view of bond interface                                                                                                                                     | 66      |

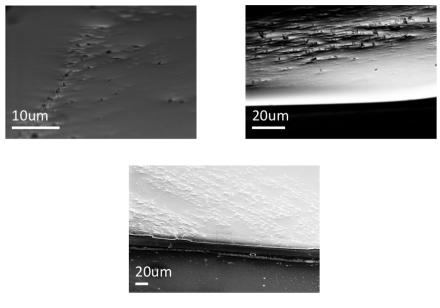

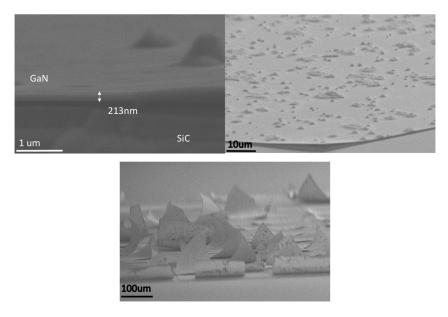

| 5-1    | The transferred film surface in various samples after removal of Si via                                                                                    |         |

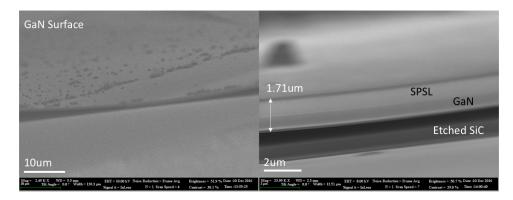

| -      | $SF_6$ with a 20% over etch $\ldots$                                                                                                                       | 72      |

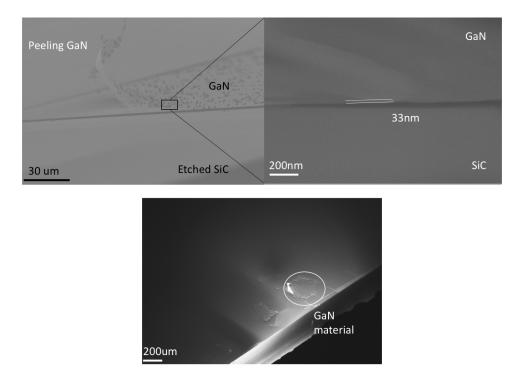

| 5-2    | GaN film peeling due to $SF_6$ etch seep $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                       | 73      |

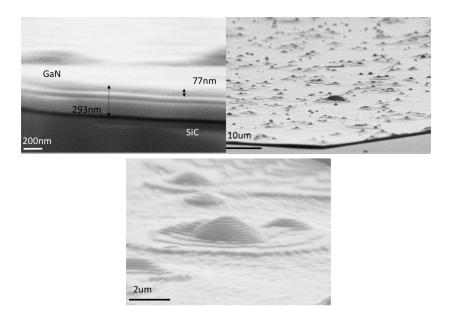

| 5-3    | GaN film surface (a) after Si removal (b) after additional 10 min Nanos-                                                                                   |         |

|        | trip clean (c) after additional HF dip                                                                                                                     | 74      |

| 5-4    | GaN film surface after 10 minutes of high power $Cl_2/BCl_3$ etch                                                                                          | 75      |

| 5-5    | GaN film surface after one hour of $Cl_2/BCl_3/CF_4$ etch chemistry                                                                                        | 76      |

| 5-6    | GaN film surface after 2.5 hours of $Cl_2/BCl_3/CF_4$ etch chemistry                                                                                       | 76      |

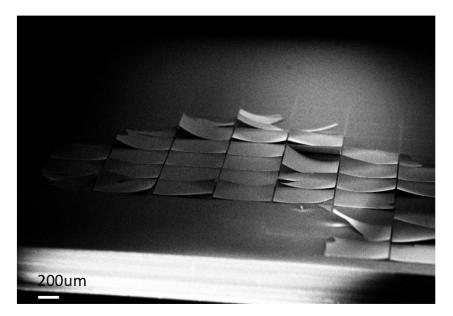

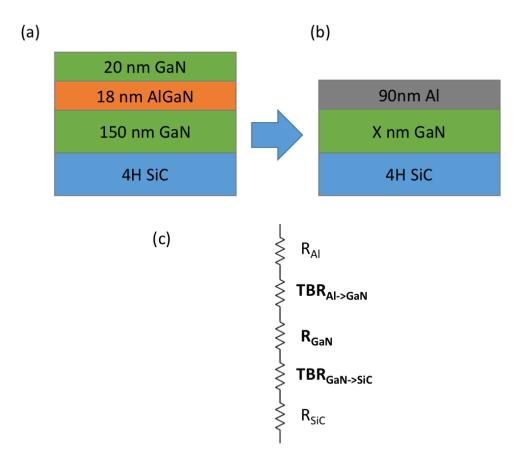

| 5 - 7  | Sample after 3hrs of selective etch                                                                                                                        | 77      |

| 5-8    | Structure (a) after original etch (b) with simplified epitaxy yielding (c)                                                                                 |         |

|        | five thermal resistor model                                                                                                                                | 80      |

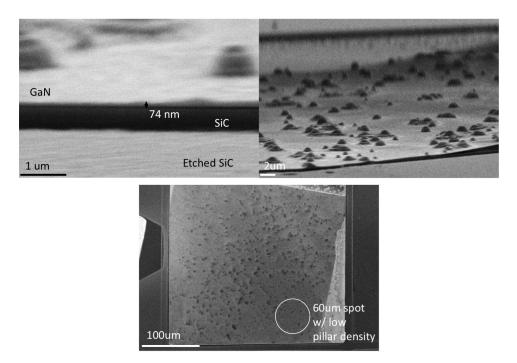

| 5-9    | Sample 1 for TDTR measurement                                                                                                                              | 81      |

| 5 - 10 | Sample 2 for TDTR measurement                                                                                                                              | 82      |

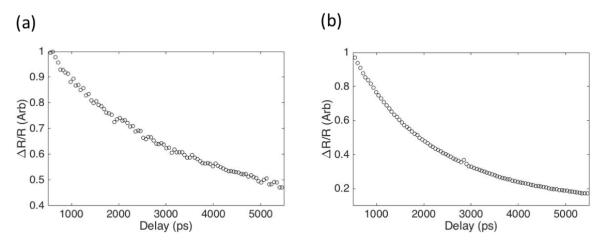

| 5-11   | Sample (a) 75nm (b) 33nm GaN measured thermoreflectance                                                                                                    | 82      |

| 5-12   | Sample 2 measured thermoreflectance with best fit                                                                                                          | 83      |

| 6-1    | Max temperature rise in bonded GaN-on-SiC HEMTs as a function of                                                                                           |         |

| 01     | GaN/SiC Thermal Boundary Conductivity                                                                                                                      | 89      |

|        |                                                                                                                                                            |         |

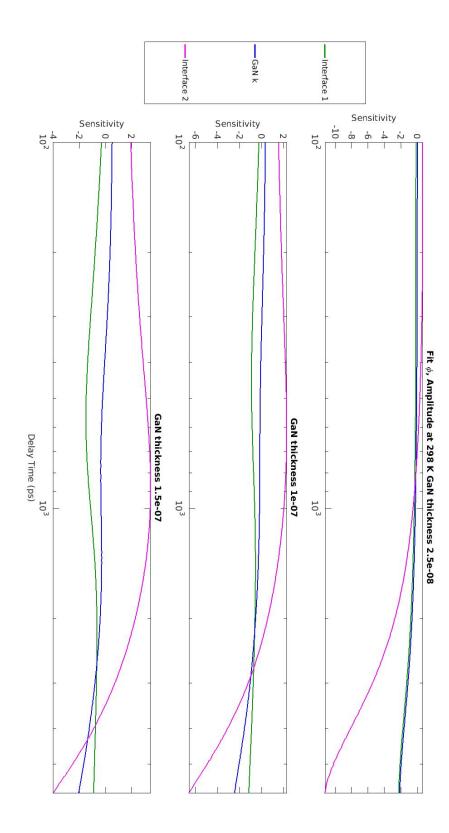

| B-1    | Sensitivity analysis, fit R in delay space                                                                                                                 | 97      |

| B-2    | Sensitivity analysis, fit $\Phi$ in delay space                                                                                                            | 98      |

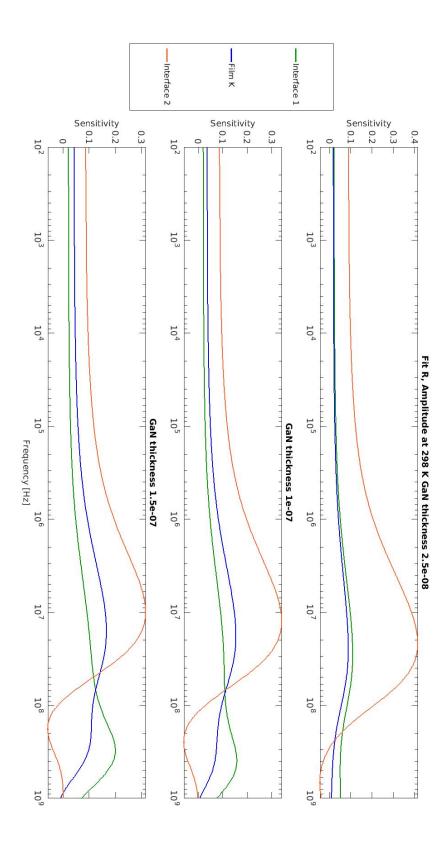

| B-3    | Sensitivity analysis, fit R in frequency space                                                                                                             | 99      |

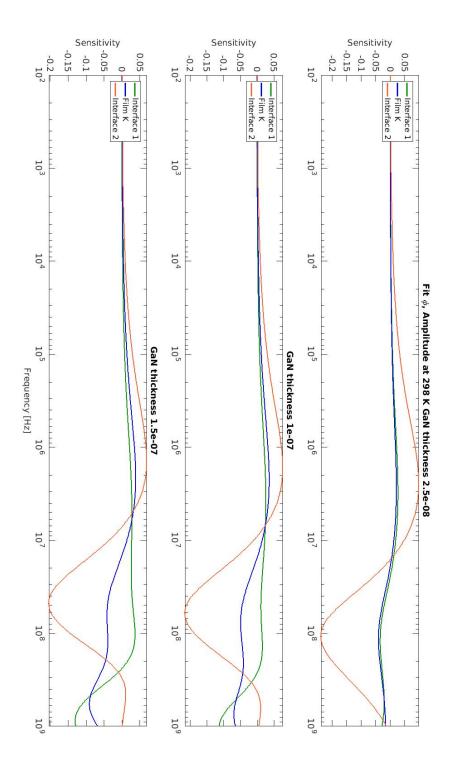

| B-4    | Sensitivity analysis, fit $\Phi$ in frequency space $\ldots \ldots \ldots \ldots \ldots$                                                                   | 100     |

# List of Tables

| $1.1 \\ 1.2$ | Crystal parameters of materials in GaN growth<br>Coefficients of thermal expansion (CTE) of materials in GaN growth      | 18 |

|--------------|--------------------------------------------------------------------------------------------------------------------------|----|

|              | at room temperature                                                                                                      | 18 |

| $2.1 \\ 2.2$ | Thermal Conductivities of Materials in GaN HEMTs (W/mK) TBR $(m^2 K/GW)$ for boundaries in GaN HEMTs calculated from DMM | 24 |

| 2.3          | TBR $(m^2 K/GW)$ for GaN-substrate interfaces measured in literature                                                     | 28 |

|              | (Growth signifies either substrate or GaN) $\ldots \ldots \ldots \ldots \ldots$                                          | 28 |

| 3.1          | GaN-on-SiC thermal resistance                                                                                            | 35 |

| 3.2          | GaN-on-Diamond thermal resistance                                                                                        | 38 |

| 3.3          | Bonded GaN-on-SiC thermal resistance                                                                                     | 42 |

| 3.4          | Double bonded GaN-on-SiC thermal resistance                                                                              | 44 |

| 3.5          | Makeup of total GaN-on-diamond thermal resistance                                                                        | 45 |

| 4.1          | Electronegativity differences for the possible GaN-SiC bond configura-                                                   |    |

|              | tions                                                                                                                    | 49 |

| 4.2          | Epitaxial growth structure used in wafer bonding experiments                                                             | 56 |

| 4.3          | Epitaxial growth structure for wafer bonding experiments                                                                 | 57 |

| 4.4          | Results of initial GaN-SiC bonding experiments                                                                           | 58 |

| 5.1          | TBR $(m^2 K/GW)$ for GaN-substrate interfaces measured in literature                                                     |    |

|              | (Growth signifies either substrate or GaN) $\ldots \ldots \ldots \ldots \ldots$                                          | 84 |

| 6.1          | TBR $(m^2 K/GW)$ for GaN-substrate interfaces measured in literature (Growth signifies either substrate or GaN)          | 89 |

# Chapter 1

# Introduction

Gallium nitride (GaN) is a wide bandgap semiconductor that has many uses in optical, radio, and power applications. GaN high electron mobility transistors (HEMTs) are commonly found in high-frequency power amplifiers (PAs) [1]. These amplifiers are a critical component in many broadcasting technologies including cellular communications and radar applications. GaN HEMTs are a particularly promising technology due to increased power density and efficiency over existing technologies such as silicon (Si) laterally diffused metal oxide semiconductor (LDMOS) transistors, silicon carbide (SiC) metal semiconductor field effect transistors (MESFETs), and gallium arsenide (GaAs) HEMTs [1,2]. This increased power density arises from the excellent material properties of GaN. Particularly, GaN has a wide bandgap, high breakdown field, high electron mobility, excellent charge density, and high thermal conductivity [1,3].

Due to these desirable characteristics, GaN HEMTs and GaN transistors in general have undergone significant academic and commercial development. GaN HEMTs have been reported with a maximum output power of 40 W/mm under active device cooling [4]. Large devices are also possible; CREE, Inc. has produced compact, high-power amplifiers with 521W of output and a record 72.4% efficiency at 3.55GHz [5]. The wide bandgap properties of GaN HEMTs make them particularly well suited for

reliable high temperature operation such as internal engine sensors [6]. GaN HEMTs have also been integrated in monolithic microwave integrated circuits (MMICs) for use in the L thru W-bands. With power outputs of 11W at 34 GHz, these devices meet the high level requirements of next generation radar and communication systems [7].

Overall, GaN HEMT technology has numerous benefits and uses in high power and high frequency regimes. However, commercially available technologies typically operate at reduced power densities of 3-6 W/mm [1,8]. This reduced power density is needed to mitigate device self-heating and thereby improve operational reliability and device lifetime. With the high voltages and high power densities required for efficient, scalable PAs, GaN HEMTs must be engineered with improved thermal dissipation to achieve reliable, widely commercial devices [9]. While both package-level and device level thermal engineering are required, the growth constraints of GaN present several opportunities to improve near junction thermal resistance through novel structures [8].

### 1.1 GaN HEMTs

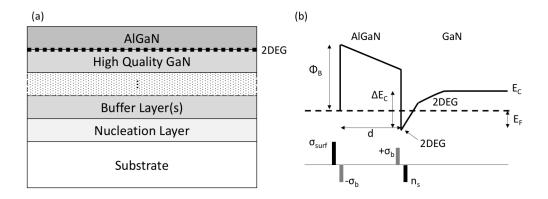

The structure of a generic GaN HEMT is shown Figure 1-1. The exact buffer layers depend greatly upon the substrate used, however, for all HEMTs the principal of operation is the same. Sufficient buffer material is needed to achieve a high quality GaN material with a smooth epitaxial surface (see subsection 1.1.1). After this is achieved, an  $Al_xGa_{1-x}N$  layer (usually with concentration x = 0.28) is grown [1,2].

Due to a difference in the spontaneous polarization fields of GaN and AlGaN, a two dimensional electron gas (2DEG) forms at the GaN/AlGaN material interface. While both N-face and Ga-face polarities can introduce a 2DEG, the Ga-face has been much more widely investigated [1,2,10]. The formation of the 2DEG is shown in the band diagram in Figure 1-1; the mode of operation is apparent as an applied gate voltage can lift the well above the Fermi level thereby turning off the device. However,

Figure 1-1: (a) Epitaxial structure for a generic HEMT (b) Band diagram around a AlGaN/GaN heterojunction

this means that GaN HEMTs are always-on – a key limitation for use in digital logic. While GaN HEMTs operate much as other HEMT devices, the major benefit is that no doping is needed to populate the 2DEG (as is required for GaAs HEMTs) [11]. Another benefit is that the native 2DEG carrier concentration is extremely high, greater than  $1 \times 10^{13} cm^{-2}$  [10], and high quality devices achieve channel mobilities of over  $2000 cm^2/Vs$  [1]. The level of confinement and concentration in the 2DEG can be tuned with the alloy concentration, as well as the thickness of the GaN and AlGaN layers. This dependence is described in Equation 1.1, where  $n_s$  is the 2DEG charge density,  $\sigma_B$  is the AlGaN polarity induced charge,  $\Phi_B$  is the gate metal work function, and  $\Delta E_c$  is the polarity induced band bending.

$$n_s = \frac{\sigma_B}{e} - \left(\frac{e\epsilon_0}{de^2}\right) \left[\Phi_B + E_F(n_s) - \Delta E_c\right]$$

(1.1)

To contact the 2DEG, ohmic contacts are formed through multi-layer metal depositions (usually a Ti/Ni/Al/Au stack). The wafer then undergoes a high temperature anneal to diffuse the contact metal through to the 2DEG. A Ni/Au Schottky gate is then deposited to control the channel. Usually, devices are isolated via a mesa etch. There are several other contact and gate methodologies: those that allow CMOS-

Figure 1-2: Epitaxial structure for (a) GaN-on-SiC and (b) GaN-on-Diamond HEMTs

compatible processing [12], the addition of  $Si_xN$  passivation [13, 14], and the use of field plates for increased breakdown voltage [4, 15, 16]. However, these complexities and the circuit design of PAs are beyond the scope of this work, see [1, 2, 17, 18] for in-depth review. Subsequently, this thesis will only consider GaN HEMTs of the basic design outlined above and depicted in Figure 1-1. It is also key to note that GaN RF PAs are usually found in a multi-fingered configuration [1]. This is important to consider in device simulation, and it is this type of mask layout which will be simulated in chapter 3.

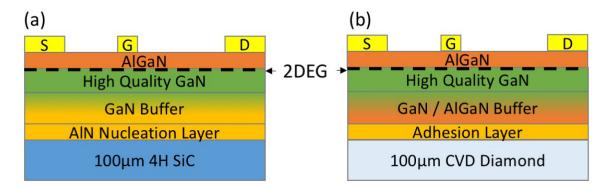

While GaN-on-SiC HEMTs have been the dominant structure in commercial applications, there is a growing interest in GaN-on-diamond devices [19–24]. The high thermal conductivity of synthetic diamond improves heat dissipation in the device, allowing for higher power density circuits [25]. Such a GaN-on-diamond structure is shown in Figure 1-2. There are two main processes for fabricating such a device. The first starts with a GaN-on-Si epitaxial wafer; a carrier wafer is then attached to the top surface via an adhesive. The original substrate is etched away, an adhesion interlayer is deposited, and a CVD diamond substrate is subsequently bonded to this interlayer [19,23]. The second method instead directly grows CVD diamond on the exposed GaN surface (after a nucleation layer is deposited) [21,22]. In general, GaN-on-diamond devices are state-of-the-art in terms of power density and thermal performance; however, they are significantly more expensive due to increased materials and processing costs [23,26]. These devices will be used as the point of comparison in chapter 3, as they achieve the highest published thermal performance.

#### 1.1.1 Gallium Nitride Growth

There has been significant work on hydride vapor phase epitaxy (HVPE), ammonothermal, and Na-flux methods for bulk GaN crystal growth. However, these methods are still not able to produce the large-area, uniform wafers needed for scalable GaN device fabrication [27–31]. Thus, GaN and associated AlGaN are generally grown heteroepitaxially via molecular beam epitaxy (MBE) and metal organic chemical vapor deposition (MOCVD) [1,32,33]. Three main substrates are used in commercial production: sapphire, Si, and SiC. In addition, AlN, ZnO2, bulk GaN and graphene have all been used as substrates for heteroepitaxial growth [34]. With many of these substrates, a nucleation layer is needed to induce growth of the GaN crystal. Although excellent end material quality is achieved for the GaN, AlGaN, and AlN layers via these growth methods [35,36], dislocation densities are still considerable. Commercial wafers are usually found to be in the  $10^7 cm^{-2}$  to  $10^9 cm^{-2}$  densities [37]. Nonetheless, both techniques grow the smooth and abrupt interfaces needed for high quality 2DEG formation with high electron mobility [1].

There are three main causes for these high dislocation densities. The first is that during the initial stages of GaN growth, grains form but eventually coalesce into a uniform material layer. This seeding effect can introduce lattice dislocations at the grain boundaries [38]. While AlN nucleation layers are needed to form these grains, they also induce threading dislocations in the nucleation layer itself [39]. In addition, growth methods suffer from complications due to lattice mismatch and thermal mismatch between the GaN and the substate. As Table 1.1 shows, there is significant lattice mismatch for GaN-on-Si, as well as smaller mismatch for GaN-on-

|                         | GaN     | Si    | SiC (4H) | Sapphire |

|-------------------------|---------|-------|----------|----------|

| Lattice Structure [40]: | Wurzite | FCC   | Wurzite  | Trigonal |

| a (Å) [40]:             | 3.190   | 5.431 | 3.073    | 4.785    |

| c (Å) [40]:             | 5.125   |       | 10.053   | 12.991   |

Table 1.1: Crystal parameters of materials in GaN growth

|                                  | GaN              |                 | ( /             |                  |

|----------------------------------|------------------|-----------------|-----------------|------------------|

| $CTE \ \alpha_a(K^{-1}) \ [40]:$ | $5.59 * 10^{-6}$ | $2.6 * 10^{-6}$ | $4.1 * 10^{-6}$ | $6.66 * 10^{-6}$ |

| $CTE \ \alpha_c(K^{-1}) \ [40]:$ | $2.17 * 10^{-6}$ |                 | $3.7 * 10^{-6}$ | $5 * 10^{-6}$    |

Table 1.2: Coefficients of thermal expansion (CTE) of materials in GaN growth at room temperature

sapphire and GaN-on-SiC.

Mismatched thermal expansion rates between GaN and the substrate can introduce significant dislocations and even cracking [41]. As GaN is grown at high temperature of over 1000°C, during cool down the different materials compress at significantly different rates. Often the stresses induced by this effect are on the order of  $10^9 Pa$  [41]. With a GaN-on-Si wafer, and an appropriate low temperature AlN nucleation layer, the GaN stress can be reduced to 0.15GPa [42]. Other stress relieving methods include graded AlGaN layers [43]. Often, a thick buffer layer of GaN is grown to reduce the dislocation density. This buffer is stress relieving, and reduces the effects of CTE mismatch [44, 45]. For GaN-on-Si epitaxies, a short-period superlattice (SPSL) of GaN and AlN layers is typically used to reduce dislocation counts as repeated material changes induce recombination of threading and spiral dislocation [46]. As with pure GaN buffers, a thick layer of material must be used to mitigate CTE and lattice mismatch.

In all, growing GaN for HEMT fabrication presents several problems with material quality, namely, a high dislocation density. While this dislocation density can be reduced to achieve a high-quality 2DEG, this requires thick nucleation and buffer layers, often of a total thickness greater than  $2\mu m$ . These buffer layers can consist

of many different material layers and are highly complex, as is the case with SPSLs for GaN-on-Si. The thermal problems associated with these structures are the main focus of this thesis.

### **1.2** Scope and Outline of Thesis

The overall theme of this thesis is to explore and develop novel GaN HEMT designs fabricated via wafer bonding. By bonding and transferring a GaN HEMT structure to a SiC substrate, the thermal conductivity from the heat source to sink is expected to improve by the elimination of thermally resistive buffer layers and thermal boundaries. This thesis evaluates structures first via simulation, and then by fabrication and measurement using time-domain thermal reflectance. This work required the development of novel wafer bonding techniques, as well as back etch processing to appropriately access the bonded device layers.

Chapter 1 gives background on GaN HEMTs, their operation, and the problems faced during growth. This serves as motivation for the development of novel structures fabricated via wafer bonding to overcome these problems.

Chapter 2 presents a discussion of heat generation and dissipation in GaN devices. Subsequently, the chapter reviews research into several thermal effects present in multilayered structures, and expands upon the impact these effects can have in GaN devices.

Chapter 3 proposes novel wafer bonded GaN HEMTs. First, this chapter explores state-of-the-art GaN HEMT structures grown on silicon carbide and transferred to diamond, to determine their dominant thermal resistances. The chapter then describes two novel wafer bonded designs, and compares their thermal performance to existing state-of-the-art technologies. The chapter concludes with a design optimization of the most promising structure, and gives a performance analysis of this design. Chapter 4 develops the required GaN-SiC wafer bonding techniques to realize the structures described in Chapter 3. The chapter goes over the many experiments conducted to determine appropriate surface activation techniques needed to bond GaN and SiC. The chapter expounds upon the conditions needed to achieve reliable bonding, particularly the development of specialized high-temperature bonding fixtures and stress-relieving channels needed to achieve covalent Ga-C bonds at 1000°C. The chapter also gives an analysis of the further refinements needed to improve bond yield.

Chapter 5 describes the experiments taken to measure the thermal boundary resistance of the GaN/SiC bonded interface. The chapter begins with a discussion of the back etch processes developed to prepare the samples. A time domain thermoreflectance sensitivity analysis of the structure is then performed. The chapter continues on to describe the samples measured and outlines the results and significance of those measurements.

Chapter 6 includes a discussion of the results of this thesis, the potential impact of those results, and future work to be undertaken to expand these results.

# Chapter 2

# Thermal Properties of GaN Devices

This chapter will discuss heat generation and dissipation in GaN HEMTs. Particular emphasis will be given to the various thermal effects which reduce thermal conductivity in the structures and thereby limit high power performance.

## 2.1 Heat Generation in GaN Devices

There have been several analysis of heat generation in GaN HEMTs [47–49]. As with other HEMTs the primary concern with active devices is Joule heating. While GaN HEMTs are not typically run in a steady state, most thermal analyses have looked at the steady state temperature rise in a device [50]. While understanding behavior during use is a primary goal, there is significant complexity in simulating a pulsed device and analyzing transient self-heating. As [50] found, multiple time constants are needed to describe the transient heating behavior. This thesis will therefore focus on steady state temperature rise, as this provides an single statistic, namely max device temperature, when comparing multiple device architectures. This approach has been used in several structural comparisons, particularly those concerned with GaN-on-diamond devices [20, 51, 52]. Using an Arrhenius equation to model failure rate, the device temperature rise also gives insight into device lifetime and reliability. The exact thermal modeling methods used in this work will be described in further detail in chapter 3.

Beyond the general modeling approach, a pressing concern is the shape and size of the heat source. While a multi-fingered HEMT of common size and configuration is modeled in chapter 3, there is still much uncertainty to the actual shape of the heat source in the literature [48]. While previous thermal analyses of devices have often assumed that the heat source is uniform and comparable to the gate length [47], several electro-thermal modeling works have found conflicting results. While there does seem to be agreement that the size of the heat source in devices is dependent upon both bias conditions and gate length, one work modeled the heat source as greater than the gate length |53|, while another has modeled the heat source as lesser |54|. In [48], the author goes into great detail discussing and analyzing the assumptions of uniformity of the heat source. In summary, it is clear that heat generation is highly localized in the channel on the drain side of the gate. However, there are many factors that determine the exact level of dispersion of heat generation, which cannot be determined without full 3D electro-thermal models. While understanding these effects is important, this thesis aims to compare structures on a basis of temperature rise and reliability. Using a uniform heat source in the 2DEG, with an appropriate flux based on the dissipated power density, should provide an appropriate comparison. This conclusion was also reached by the developers of the analytical methods used in this work [55, 56], as well as other thermal studies comparing GaN technologies [20].

## 2.2 Heat Dissipation in Multilayered Epitaxies

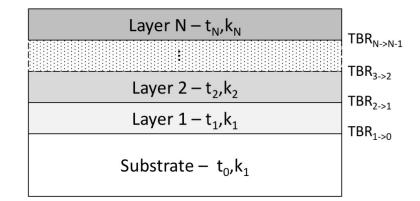

While the thermal conductivity in any given bulk material is usually well characterized, there are several important effects which must be considered when looking at the thermal conductivities of thin, multilayered epitaxies. The first is the bulk con-

Figure 2-1: Generic epitaxial structure for thermal evaluation

ductivity of a given material, which is highly depended on concentration (in alloyed cases) as well as material quality [37,57]. The second effect one must consider is the reduction of the material conductivities from their bulk values due to phonon mean free path suppression. This effect is critical in thin films, as the conductivities can be reduced by up to 90 percent from bulk values [58]. Finally, one must consider the interface effects due to change in material, namely the thermal boundary created therein. [59] These boundaries have a fixed resistance due to the material, and as such, they can significantly increase the overall resistance of an epitaxy. Figure 2-1 depicts a generic multilayered epitaxial structure which will be the basis for further analysis in this work. The next sections will go into detail on the thermal effects described in general above and depicted in the figure.

#### 2.2.1 Thermal Conductivity of Materials

Table 2.1, lists the bulk thermal conductivities of the materials that are considered in this work. It is important to note the relative magnitudes of these conductivities. As is expected, stiffer, harder materials (such as SiC and diamond) both have extremely high conductivity. The ranges of values given are usually due to material quality, these uncertainties will be discussed in detail below.

While the thermal conductivity of bulk GaN has been calculated from first prin-

| GaN                    | $Al_{0.27}Ga_{0.73}N$ | AlN                   | Si       |

|------------------------|-----------------------|-----------------------|----------|

| 150 [37] - 240 [60,61] | 30 [57]               | 285 [40]              | 130 [40] |

|                        |                       |                       |          |

| SiC (4H)               | Sapphire              | CVD Diamond           |          |

| 420 [40]               | 27 [40]               | 1200 [62] - 2000 [26] |          |

|                        |                       |                       |          |

Table 2.1: Thermal Conductivities of Materials in GaN HEMTs (W/mK).

cipals [60] there is still uncertainty about the thermal conductivity of any given GaN film, mainly due to the variable dislocation density introduced during growth. Dislocations cause diffuse scattering of heat carrying phonons, thereby impeding heat flow through the epitaxy. With several efforts taken to measure and calculate this effect [37, 61], the consensus seems that for most GaN epitaxies with a dislocation density around  $10^8 cm^{-2} - 10^9 cm^{-2}$ , a bulk conductivity near 150 W/mK is appropriate.

Along with dislocation density, it is key to consider the alloy concentration for  $Al_xGa_{1-x}N$  layers. As the concentration x, in  $Al_xGa_{1-x}N$ , goes from 0 to 1 there is initially a sharp drop off in thermal conductivity, reaching as low as 14 W/mK at a 20 percent Al concentration [63]. As the Al concentration increases, there is a sharp rise around 0.9 approaching the bulk value for AlN [57]. Thus, for  $Al_{0.27}Ga_{0.73}N$  layers in GaN HEMTs, a bulk thermal conductivity of 16-20 W/mK is appropriate [56, 63]. Besides alloyed impurities, doped impurities also reduce the thermal conductivity of materials. In many GaN epitaxies, C-GaN is often used as a stress relieving buffer layer, however, at a concentration of  $10^{17}to10^{18}$  the thermal conductivity of GaN is reduced to 86 W/mK [64]. Therefore, when modeling a given epitaxial structure, one must closely analyze the exact material composition and quality, as this can significantly impact the total thermal conductivity.

#### 2.2.2 Phonon Mean Free Path Suppression

Beyond material makeup and quality, phonon mean free path (MFP) suppression can significantly reduce the thermal conductivity of an epitaxial layer. The thermal conductivity of a material can be described as an accumulation function, where phonons of a given MFP contribute to the total thermal conductivity based on the material's MFP distribution [58]. This accumulation function is described in Equation 2.1, where L is the cumulative maximum MFP,  $\sigma$  is the phonon polarization,  $C_{\sigma}(l)dl$  is the volumetric heat capacity for a phonon of a given MFP, v(l) is the phonon speed, and l is the MFP of the phonon.

$$k_{accum}(L) = \frac{1}{3} \sum_{\sigma} \int_0^L C_{\sigma}(l) v(l) l dl$$

(2.1)

A material's MFP distribution is critical to understanding the thermal conductivity. There have been several works to determine the MFP distributions in a variety of materials [65–67], including GaN and AlN [58]. With phonon MFPs  $\leq 1\mu m$  the accumulated conductivity is  $\leq 50\%$  of bulk. At phonon MFPs  $\leq 30nm$  the accumulated conductivity is  $\leq 10\%$  of bulk [58]. When considering a thin epitaxial layer, the MFP distribution is changed from the bulk – interfacial scattering limits phonon mean free paths to below the material thickness. A thin epitaxial layer there has a reduced conductivity compared to the bulk value. Using the accumulated conductivity directly (even though this is measured in bulk material without interfacial scattering) is an appropriate model. Measured values of the thermal conductivity in Si membranes map well to expected conductivities from these MFP calculations [68]. Although this does not seem well known, particularly for nm-thin layers, this will be the approach used in this work.

This effect becomes quite important in designing thermally optimal structures. When considering a single material layer, reducing the material thickness would seem

Figure 2-2: Thermal boundary resistance (a) diffuse mismatch model (b) acoustic mismatch model

to always reduce the total thermal resistance. However, considering the impact of MFP suppression, a non-zero thermally optimal thickness exists. This is a critical effect which is ignored in thermal modeling and in design of GaN epitaxial structures [20, 56]. The rest of this thesis will use the measured accumulation functions found in [58], and further details on the values used can be found in chapter 3.

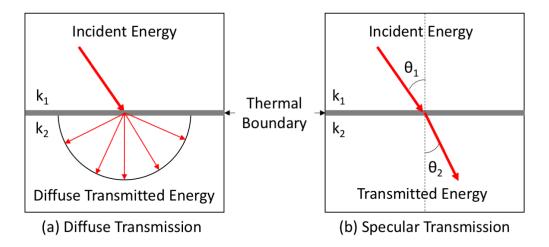

### 2.2.3 Thermal Boundary Conductivity

In addition to material interfaces suppressing the phonon MFP distribution, they also create an impedance to heat flow across the interface [69]. As two materials will have different phonon density of states, there is imperfect transmission of a heat carrying phonon across the interface. This effect has been well studied [52,59,69,70], and there are several analytical and experimental techniques used to calculate and measure the thermal boundary resistance between two materials. Two of the main models are depicted in Figure 2-2. Per its name, the diffuse mismatch model assumes that heat transport through the boundary is via diffuse scattering of incident heat carrying phonons. For the diffuse mismatch model the thermal boundary resistance is found to be [59]:

$$R_b = \left[\frac{k_b^4 \pi^2}{30\hbar^3} \left(\sum_j c_{1,j}^{-2}\right) \alpha_{1->2}\right]^{-1} T_2^{-3}$$

(2.2)

Where  $c_{i,j}$  is the phonon speed in the i'th material with the j'th polarity and

$$\alpha_{1->2} = \frac{\sum_{j} c_{2,j}^{-2}}{\sum_{j} c_{1,j}^{-2} + \sum_{j} c_{2,j}^{-2}}$$

(2.3)

is the thermal transmission coefficient between material 1 and 2.

The acoustic mismatch model assumes that each incident phonon transports heat across the boundary in a specular nature. As such, the transmission coefficient of a given phonon across the boundary is dependent upon its polarization and orientation to the interface. However, this model quickly becomes untenable unless simplifications are made. Under the assumptions of uniformity of phonon speeds in all directions, the transmission coefficient becomes [71]:

$$\alpha_{1->2} = \frac{4\frac{\rho_2 c_2 cos\theta_2}{\rho_1 c_1 cos\theta_1}}{(\frac{\rho_2 c_2}{\rho_1 c_1} + \frac{cos\theta_2}{cos\theta_1})^2}$$

(2.4)

where  $\rho_i$  is the density,  $\theta_i$  is the angle of incidence, and  $c_i$  is the isotropic phonon speed in the i'th material. And the thermal boundary resistance is then [59]:

$$R_b = \left[\frac{k_b^4 \pi^2}{15\hbar^3} \left(\frac{\int_0^{\sin^{-1}(c_1/c_2)} \alpha_{1->2} \sin\theta \cos\theta d\theta}{c_1^2}\right)\right]^{-1} T_2^{-3}$$

(2.5)

While measured TBRs for GaN HEMT interfaces are readily found, measured values include additional resistance due to interface layers. For example, the  $TBR_{GaN->diamond}$ in [52] includes the resistance of both AlN nucleation layers and the adhesive bonding layer. With novel structures, on must therefore use the theoretical models described above. However, measured values are still useful in determining a bound on a given TBR. While the theoretical models, neither is particularly accurate. However, the DMM is much more tenable to calculate and has been shown to give a good lower

| Source              | GaN  | $Al_{0.3}Ga_{0.7}N$ | AlN  | Si   | SiC $(4H)$ | CVD Diamond |

|---------------------|------|---------------------|------|------|------------|-------------|

| GaN                 |      | 0.5                 | 1.34 | 0.8  | 1.31       | 2.7         |

| $Al_{0.3}Ga_{0.7}N$ | 0.69 |                     | 1.34 |      |            |             |

| AlN                 |      |                     |      | 0.32 | 0.42       | 0.5         |

Table 2.2: TBR  $(m^2 K/GW)$  for boundaries in GaN HEMTs calculated from DMM

|              | SiC $(4H)$ | CVD Diamond           |

|--------------|------------|-----------------------|

| GaN (Growth) | 4-5 [51]   | 12-50 [72],17-41 [62] |

| GaN (Bonded) |            | 38-108 [70]           |

Table 2.3: TBR  $(m^2 K/GW)$  for GaN-substrate interfaces measured in literature (Growth signifies either substrate or GaN)

bound on the TBR at high temperatures [59,69]. Table 2.2 gives DMM calculated values and Table 2.3 lists measured interfaces in the literature.

#### 2.2.4 Thermal Conductivities of Buffer Layers

When looking at complicated buffer layers, the many effects outlined above result in a large reduction in the total conductivity of the layers. Many GaN HEMTs, particularly those grown on Si, use short period superlattices of alternating AlN and GaN layers as a method to reduce strain and eliminate dislocations [46,73]. Thus, there are many fixed thermal boundary resistances, along with reduced conductivities in each of the SPSL layers due to MFP suppression. Thus, when considering such a buffer, it can be modeled as a single layer, with a net thermal resistance of a lower conductivity material. This is depicted in Figure 2-3 While the exact structure can impact the conductivity significantly, a SPSL of 53nm of GaN and 4nm AlN has an effective conductivity roughly 1/10th of the bulk value of GaN at 17 W/mK [73]. This reduced conductivity buffer layer is quite resistive, and due to it's thickness the SPSL will dominate the total thermal resistance. As such, GaN-on-Si structures are rendered so thermally inefficient that they are not considered in this work.

Figure 2-3: Equivalent thermal models for a multi-layered structure

# Chapter 3

# Thermally Efficient GaN-on-SiC Epitaxies via Wafer Bonding

GaN HEMTs are a critical technology for high power RF amplification and many other uses. However, there are a variety of thermal problems in GaN HEMTs related to the limitations of growth technology. When analyzing such a device, there are also a variety of ways to thermally simulate a given structure. This chapter will discuss the specifics of the thermal modeling technique that was used to compare the thermal performance of several GaN HEMT technologies. This technique is a computationally efficient analytical method, which provides the same accuracy as numerical physics simulations. Subsequent sections focus on a given GaN design and components of the total thermal resistance are analyzed for each device. A novel GaN HEMT design is then presented, discussed, and analyzed; its thermal performance and reliability are compared to existing state-of-the-art HEMTs.

# 3.1 Thermal Modeling of GaN Devices

Finite element methods (FEM) are often used in simulating GaN devices [20, 48, 49, 69, 74]. While FEM give consistent and convergent results, the high aspect ratio of

Figure 3-1: Generic epitaxial thermal structure (a) side view (b) top view (c) symmetrically reduced top view

gate length as compared to chip structure can make meshing difficult. There have been several recent works to develop analytical methods to calculating temperature rise in a device [55,56]. This is the approach that is used in this work. This analytical method is highly accurate as compared to FEM, but requires a fraction of the runtime and calculation setup [56]. The author of this method was generous enough to share his Matlab framework, which was used as a foundation for the simulations described below.

#### 3.1.1 Analytical Method

The generic thermal structure to be modeled is shown in Figure 3-1. A 22 fingered HEMT mask is assumed, consistent with GaN PAs [56]. While the exact relation between gate length and heat source is still not fully understood, as this is a cross-design comparison, the exact choice is not that significant. A 0.5  $\mu m$  heat source was chosen for this simulation. This choice is consistent with several studies on thermal generation in GaN HEMTs [48, 54, 75]. Due to the exploitable symmetry, we can reduce our calculations to only consider a single quadrant, with symmetric (i.e. floating) boundary conditions at the edges. The total size of the die, along with the gate pitch and width is shown in Figure 3-1. Instead of choosing a specific bias

point, the power dissipation itself was chosen. Full electro-thermal simulations are needed to determine the exact heat dissipation for a given bias. As this work is simply focused on thermal performance of a given structure, the power dissipation is really all that matters. A dissipation of 5 W/mm was assumed; this implies a corresponding areal heat flux of  $10^{10}W/m^2$  for the sources. Beyond the layout, the technical details of the method are given in Appendix A. As was mentioned in section 2.2, when modeling a given structure, one must consider the interface conductivity between two materials. However, in some cases, the measured values found in literature are for an "effective" TBR which includes the resistance of an interlayer [51, 52, 70]. This does not present a problem for this method, as an interlayer can be dropped from the wafer stack and modeled solely by the effective TBR between the surrounding materials. As described in , determining the thermal conductivity of a thin layer is a non-trivial problem. The model used generally accepted value for the thermal conductivities; for thin GaN layers, phonon mean free path suppression was calculated as in [58].

# 3.2 Performance of Current GaN Technologies

Now that the modeling method has been described, it will be used to compare standard and state-of-the-art GaN HEMT structures. Particular focus is given on the impact of near junction resistances such as the GaN-substrate thermal interface.

#### 3.2.1 GaN-on-SiC

While GaN-on-Si devices are important for GaN integration into Si-based technologies, they have substantial thermal and structural limitations. GaN-on-SiC devices are the preferred design for high powered use (particularly for the simulated MMIC structures). This is due to their increased thermal efficiency resulting from SiC's high thermal conductivity. A GaN-on-SiC HEMT structure is shown in Figure 3-2

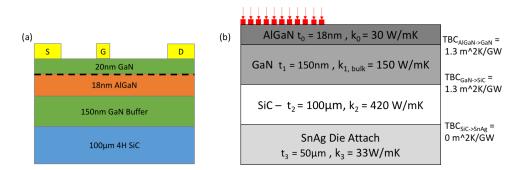

Figure 3-2: Standard GaN-on-SiC HEMT (a) epitaxial structure (b) modeled structure with parameters listed.

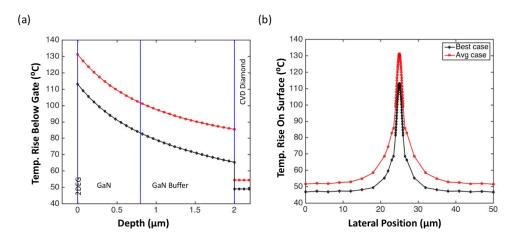

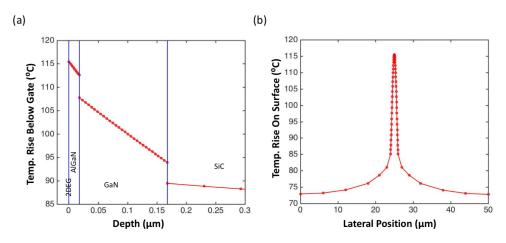

Figure 3-3: Standard GaN-on-SiC HEMT simulated temperature rise at 5W/mm power dissipation (a) under central heat source (b) on surface around central heat source

along with the simplifications made for simulation. Using the values as listed in the figure, the simulated temperature rise is shown in Figure 3-3. Note that the value of 150W/mK given for GaN is the assumed bulk conductivity. For a 2  $\mu m$  thick GaN layer, this implies a suppressed conductivity of roughly 90 W/mK. The best growth TBR reported is assumed for the GaN-SiC, at  $0.2GW/m^2K$  [51].

The max temperature rise in this device is 136.9C. Between devices, the surface cools to 72.86C. Within a micron of the heat source, the temperature drops over 31.2C. The contributions to the total thermal resistance are shown in Table 3.1. In general, heat is highly concentrated under the sources. The package makes up a considerable contribution to the total thermal resistance, as the relatively low GaN/SiC TBR and SiC substrate resistance are not a significant percentage of the total. The GaN

| Region:           | GaN Epi | GaN/SiC TBR | Substrate | Package |

|-------------------|---------|-------------|-----------|---------|

| Percent of Total: | 35.9%   | 3.7%        | 2.1%      | 58.3~%  |

Table 3.1: GaN-on-SiC thermal resistance

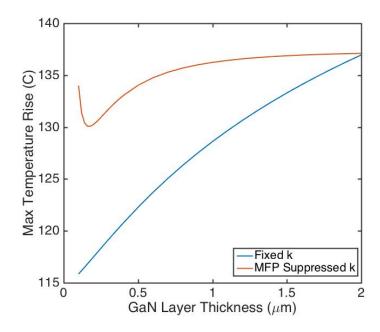

material is a significant portion of the near junction thermal resistance; ignoring the package, the GaN material is over 85% of the thermal resistance on the chip. As there is not much that can be done to reduce the growth TBR of GaN-SiC (the AlN nucleation layer is critical for GaN wetting and high quality growth), the simplest optimization would be to thin the GaN layer. If phonon MFP suppression is ignored, then simply reducing the GaN buffer thickness to close to 0 is optimal. However, when one models the MFP suppressed thermal conductivity, a true minimum arises at roughly 200nm. This relation is shown in Figure 3-4. If GaN growth could be terminated at that thickness, this would decrease the near junction thermal resistance by 15%. However, the high dislocation density would reduce 2DEG conductivity, and the net electrical performance would be much lower. However, if there were a way to reduce the GaN thickness without other performance loss, then the overall performance can be significantly improved.

#### 3.2.2 GaN-on-Diamond

As discussed in section 1.1, GaN-on-diamond technologies are seen as a promising method to improve thermal performance. Diamond substrates have the highest bulk thermal conductivity measured at up to 2000 W/mK theoretical maximum [62, 70], Therefore, replacing the SiC substrate in a GaN HEMT with diamond should yield an significant thermal performance improvement due to improved thermal spreading. As was discussed, both regrowth and wafer bonding methods have been approached. Each yields a different quality of GaN-diamond interface, as well as different diamond quality. For high quality growth interfaces, the diamond quality ranges from 800 to

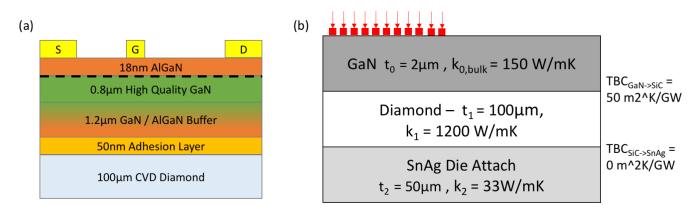

Figure 3-4: Max temperature rise in GaN-on-SiC HEMTs as a function of GaN buffer thickness

1600 W/mK realized conductivity, with TBRs reliably around 20  $m^2 K/GW$  [62,72]. Better diamond substrates (up to 1800 W/mK) are used in bonded devices, but the thermal interface is significantly worse, ranging from 36 to 100  $m^2 K/GW$  [70]. While the fabrication methods are different, both yield essential the same structure, the only thermal difference being in the GaN-diamond TBR and the conductivity of the diamond. A GaN-on-diamond HEMT structure is shown in Figure 3-5.When evaluating these structures, the question of what TBRs and conductivities to use is a pressing one. As a best case scenario, the simulation use the maximal conductivity achieved for diamond wafers (1800 W/mK), and the lowest TBR measured for GaNdiamond interfaces (20  $m^2 K/GW$ ). The more reasonable scenario assumed a 50  $m^2 K/GW$  TBR and a 1200 W/mK diamond conductivity. These scenarios are shown in Figure 3-6.

Both GaN-on-diamond devices offer a significant performance improvement over GaN-on-SiC. The max temperature rises are 131.1C and 113.0C for the average and best case scenarios. These devices have an even more compressed temperature dis-

Figure 3-5: Standard GaN-on-Diamond HEMT epitaxial structure with model parameters listed.

Figure 3-6: Standard GaN-on-Diamond HEMT simulated temperature rise at 5W/mm power dissipation (a) under central heat source (b) on surface around central heat source

tribution on the surface, with the minimum temperature significantly lower at 55.3C and 48.7C respectively. Again the main source of thermal resistance is in the GaN material and the GaN-diamond TBR. However, the TBR is now an extremely significant percentage of the total thermal resistance in the average case. Table 3.2 shows the distribution in the two cases. In general, GaN-on-diamond is an interface limited technology. If good material interfaces can be achieved (approaching the 3  $m^2k/GW$  DMM value) then these devices will have exemplary performance. However, for current technology, while still outperforming SiC, they do not achieve their full potential.

| Region:    | GaN Epi | GaN/SiC TBR | Substrate | Package |

|------------|---------|-------------|-----------|---------|

| Best Case: | 51.1%   | 5.6%        | 3.9%      | 39.4~%  |

| Avg Case:  | 35.6%   | 23.7%       | 4.8%      | 35.9%   |

Table 3.2: GaN-on-Diamond thermal resistance

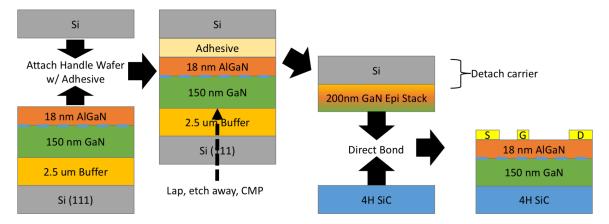

Figure 3-7: Wafer bonding process for GaN-on-SiC HEMTs.

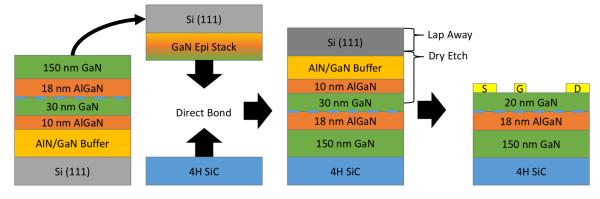

# 3.3 GaN-on-SiC via Wafer Bonding

After comparing the common GaN HEMT epitaxial structures there are several key conclusions. Reducing the thermally resistive buffer layers and having thermally conductive interfaces from GaN to the substrate is key. While both GaN-on-SiC and GaN-on-diamond HEMTs achieve some of these design ideals, neither is optimal, mainly due to the high TBRs because of nucleation and inter layers, as well as the thick GaN buffer layers needed for high material quality at the 2DEG. The goal is then to somehow achieve this reduced thickness, keep the GaN-substrate TBR low, and also maintain material quality and electrical performance. The subsequent sections propose and analyze two possible wafer bonding processes to achieve these goals. The main idea is to take a GaN-on-Si wafer, bond it to a new SiC substrate. Once that is done, the original Si and buffer material can be removed, thus leaving a thin, high quality transistor layer in good thermal contact with the carbide substrate. This will achieve two things. First, by direct bonding the GaN to the SiC, the thermal boundary resistance should be improved over growth interfaces. Second, the exact thickness of GaN material can be chosen to optimize the thermal performance of the structure.

#### 3.3.1 GaN-SiC Direct Bonded Structure

Beginning with a GaN-on-Si epitaxially grown HEMT, an additional 25nm - 200nm thick GaN cap is grown. This cap will become the new bonding buffer material. This wafer is then direct bonded to an SiC wafer, yielding the structure shown in Figure 3-7. The original Si substrate is the etched away, along with the nucleation and buffer layers, yielding from top down a thin GaN layer, with an AlGaN layer below that, and a final GaN buffer layer bonded to a SiC substrate. The total final thickness is <300nm of GaN material, and the GaN HEMT can be N-face contacted. Similar devices have been fabricated previously, although a Si substrate wafer was used, and a thick interlayer of SiO2 was used to achieve bonding [76]. The benefits of this bonded GaN-SiC structure are a highly conductive substrate, a reduced TBR between GaN and SiC (due to lack of interlayer in the bonding and the high quality of the bonded GaN surface) and most importantly, a reduced GaN buffer layer. Unfortunately, the AlGaN layer cannot be ignored, as it is now between the 2DEG (heat source) and the substrate (heat sink). The key to fabricating such a structure is developing appropriate wafer bonding techniques to create high quality interfaces. Back etch techniques are needed to remove the original Si substrate and GaN buffer layers. Although explored previously [76], there are still additional complications that could arise in such processing.

#### 3.3.2 GaN-on-SiC Double-Bonded Structure

A second wafer bonding structure could be fabricated in a manner similar to the GaN-on-diamond bonded structures. While using a more complicated process, this results in a simpler structure. A Si handle is attached to GaN-on-Si wafer surface via

Figure 3-8: Double wafer bonding process for GaN-on-SiC HEMTs.

an adhesive. Subsequently, the original substrate is removed and the GaN material is mechanically polished down till the GaN thickness is 300nm. After chemical mechanical polishing (CMP) this surface to achieve a smooth interface, this wafer is direct bonded to a polished SiC wafer. The carrier is then removed and devices can be fabricated on the surface. This structure has the benefit of both being a standard Gaface HEMT, with a high conductivity substrate, while removing substantial amounts of resistive buffer material. The key to fabricating such a structure is the CMP of the GaN material in order to bond the GaN and SiC. This structure will not be pursued much beyond an initial evaluation of its potential, as the extra processing required is well beyond the scope of this work.

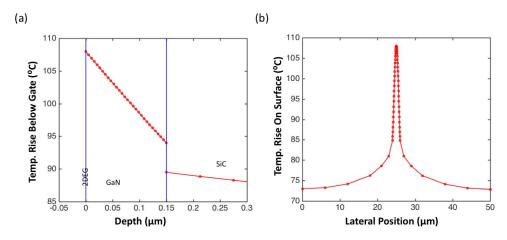

# 3.4 Performance of Wafer Bonded GaN-on-SiC HEMT

The key consideration when simulating this structure is the GaN-SiC TBR. While several values have been measured, they all include the resistance of AlN nucleation layer (see section 2.2). Thus, a analytical model must be used. From a DMM calculation, the value is  $1.31m^2K/GW$ . This value presents a strong upper bound on the interfacial conductivity, and the measured TBRs including nucleation layer present a good lower bound at  $4 - 5m^2K/GW$  [52]. For the TBR of the AlGaN/GaN interface,

Figure 3-9: Bonded GaN-on-SiC HEMT epitaxial structure with model parameters listed.

Figure 3-10: Bonded GaN-on-SiC HEMT simulated temperature rise at 5W/mm power dissipation (a) under central heat source (b) on surface around central heat source

we again appeal to a DMM; the value is  $1m^2K/GW$  as an upper bound. Finally, for the AlGaN layers a 30 W/mK conductivity was used [57]. As will be seen in the simulations below, varying these parameters beside the GaN-SiC TBR does not significantly affect the performance of these devices.

The max temperature in this device is 115.5C, which is significantly lower than a standard GaN-on-SiC structure, as well as the GaN-on-Diamond average case. Like the standard GaN-on-SiC, the bonded HEMT has a surface temperature minimum of 72.7C, with a similar peak sharpness. As is seen in Figure 3-10, the reduction in the GaN buffer significantly makes up for the increased resistance of the AlGaN layer when compared with GaN-on-diamond. The relative contributions to the total resistance

| Region: | GaN Epi | GaN/SiC TBR | Substrate | Package |

|---------|---------|-------------|-----------|---------|

|         | 18.6%   | 3.9%        | 18.4%     | 59.1 %  |

Table 3.3: Bonded GaN-on-SiC thermal resistance

are shown in Table 3.4. Now, the near junction thermal resistance is approaching its minimum. The SiC substrate is roughly 45% of the near junction, and the GaN epitaxy is the other 45% with the TBR making up the rest. Effectively, the only way to begin making more efficient devices is the second proposed bonding method.

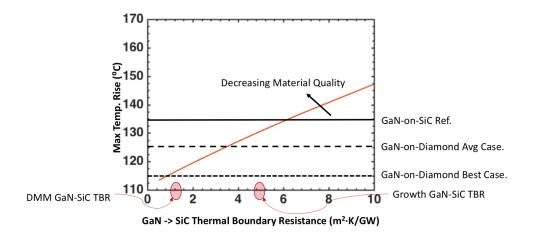

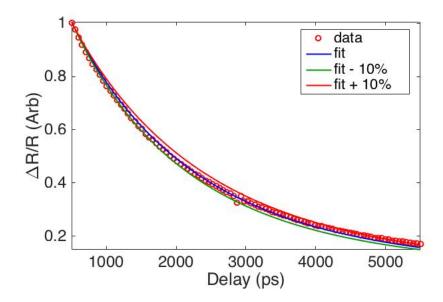

#### 3.4.1 Variations of Model Assumptions

As mentioned above, there are several assumptions made in modeling this structure, the key being the assumed TBR of a bonded GaN-SiC interface. If these assumptions are shifted, then several trends can be observed. Figure 3-11 shows the general trends, as well as the points of comparison evaluated in this structure. We see under all assumptions except for perfect interfacial thermal contact, the bonded GaN structure underperforms the best case diamond system. However, for an average diamond GaN HEMT, the bonded GaN-SiC structure has a lower temperature rise, assuming the TBR is no worse than the growth case. This is highly promising, as we expect a lower bonded TBR versus growth due to the lack of an interlayer. While not shown for clarity, varying the AlGaN or GaN conductivities by 10% did not have a significant effect on thermal performance. The key conclusions from this analysis are that the performance of this structure is highly dependent upon the thermal boundary at the bonded interface. While the structure pretty always outperforms a standard GaN-on-SiC HEMT, its performance relative to GaN-on-diamond devices is dependent upon the bond interface quality.

Figure 3-11: Max temperature rise in bonded GaN-on-SiC HEMTs as a function of GaN/SiC Thermal Boundary Conductivity

Figure 3-12: Double bonded GaN-on-SiC HEMT epitaxial structure with model parameters listed.

#### 3.4.2 Thermal Performance of Double Bonded Structure

In the double bonded GaN HEMT, the end structure is extremely simple. Effectively, this can achieve the optimal minimum found when considering variable GaN-on-SiC thicknesses. As the optimized thickness was 200nm, this value was chose for the final layer thickness. As with the above bonding case, the DMM was assumed for the GaN-SiC TBR yielding  $1.3 \ m^2 K/GW$ . Mean free path suppression was likewise assumed; the end model of this structure can be seen in Figure 3-12. The simulated temperature rise is shown in Figure 3-13. As to be expected, this is an ideally efficient GaN-on-SiC HEMT. The max temperature rise was only 107.9C, with a very low percentage of the thermal resistance found in the near junction. In a case like this, the only improvements which can be made are switching to higher conductivity materials.

Figure 3-13: Double bonded GaN-on-SiC HEMT simulated temperature rise at 5W/mm power dissipation (a) under central heat source (b) on surface around central heat source

| Region: | GaN Epi | GaN/SiC TBR | Substrate | Package |

|---------|---------|-------------|-----------|---------|

|         | 12.7%   | 4.2%        | 7.9%      | 75.0~%  |

Table 3.4: Double bonded GaN-on-SiC thermal resistance

# 3.5 Summary of Performance Characteristics

The following table summarizes the performance of the various devices considered in the above simulations. For each device, the power dissipation was modified until the max surface temperature reached 250C. The goal of this was to gain an understanding of the increase in power density achievable with these structural changes. Using an Arrhenius equation to model the mean time to failure, the growth GaN-on-SiC was used as a reference, and the energy of activation was assumed to be 1.0 Ev [77]. As one can see, the bonded Gan-SiC HEMT significantly outperforms average GaNon-diamond, and GaN-on-SiC devices. Under best case assumptions for GaN-ondiamond, the proposed structure is only marginally behind.

| Structure:             | TBR $(m^2 K/GW)$           | Max Temp. Rise (C)   |

|------------------------|----------------------------|----------------------|

| GaN-on-SiC:            | 5                          | 136.9                |

| GaN-on-Diamond (best): | 20                         | 113.0                |

| GaN-on-Diamond (avg):  | 50                         | 126.3                |

| Bonded GaN-on-SiC:     | 1.3                        | 115.5                |

| 2x Bonded GaN-on-SiC:  | 1.3                        | 107.3                |

|                        | Max Power Density $(W/mm)$ | Reliability Increase |

| GaN-on-SiC: 8.7        | ſ                          |                      |

| Gan-on-510: 8.7        | ref.                       |                      |

| GaN-on-Diamond (best): | ref.<br>11.2               | 335.2%               |

|                        |                            | $335.2\% \\ 93.5\%$  |

| GaN-on-Diamond (best): | 11.2                       |                      |

Table 3.5: Makeup of total GaN-on-diamond thermal resistance

# 3.6 Discussion

The goal of these simulations was to explore novel structures and use the results to optimize their design. The wafer bonded structures proposed in this chapter have high promise in therms of expected performance improvements. This suggests that experimental work should be undergone to realize and test these devices. The points of comparison were difficult to choose, as there are several variations of devices which have similar structures, but different thermal performance. The aim was to simply these aspects away, and create a more standard model as a point of comparison. To that end, the best values reported in the literature were used, and so the analysis is in the times with the literature. With the GaN-on-diamond case, while the idea TBR and diamond conductivities yielded the best device, to date no one has realized a 20  $m^2 K/GW$  or lower TBR while also achieving a 1800 W/mK diamond substrate. Part of this lies in the trade off between growth and bonding. With a bonding approach, a high quality substrate can be obtained, however the need for interlayers reduces the thermal boundary conductivity [52]. On the other hand, while optimizing the growth interface yields a lower TBR, the diamond quality is sacrificed, as grain formation during growth significantly reduces thermal conductivity [62]. In all, the proposed method yields improved results because it should have both a high quality substrate and a high interface conductivity. The approach taken herein has been novel in that several thermal effects are modeled in addition to the basic structure and bulk conductivities. Overall, this analysis has yielded fruitful results, and is hoped to inform future device design and optimization works.

# Chapter 4

# GaN - SiC Wafer Bonding Technology

A directly bonded GaN HEMT is of high promise due to expected thermal improvement over current designs. However, there is very little in the literature on bonding GaN and SiC. GaN and SiC had been previously bonded in a ultra-high vacuum, high temperature bonding system [78]. With this method, the authors were able to reliably bond a GaN layer grown on Si to a pristine 6H SiC wafer. As with any bonding process, rigorous cleaning was a necessity, and the system was highly temperature dependent; reliable bonding only occurred at 1000C. While this method is promising, there are several key differences between the proposed structure and that previously bonded. The first is that the substrate was 6H polytype SiC versus a 4H polytype. While both are wurtzite crystal structure, the 6H polytype has different periodicity and hexagonal symmetry. They also both have slight differences in their coefficients of thermal expansion; most notably, the 4H thermal expansion is more anisotropic than that of 6H SiC [79]. Secondly, the proposed epitaxial structure is significantly different than that previously bonded. Compared to the 0.5  $\mu m$  GaN layer with a 100nm AlN nucleation layer reported, the 3  $\mu m$  structure proposed consists of many AlN, GaN, and AlGaN layers. Each of these materials have a different thermal expansion and the internal stresses are drastically different.

Besides direct bonding, there are several examples of interlayer bonding of GaN to other substrates [23, 52, 76, 80, 81]. While the actual interlayers are not often published, particularly for the GaN-on-diamond technologies, they are only a few standard materials. When bonding to Si substrates,  $SiO_2$  is a well known adhesive interlayer, particularly when coated in the form of HSQ [76,82]. In addition to  $SiO_2$ ,  $Al_2O_3$ , also been used in interlayer bonding [83].  $SiN_x$  is used in GaN-on-diamond wafers where the diamond is deposited [72]; it is therefore a likely bonding interlayer as well. While metal-metal bonding and eutectic bonding are both well characterized and optimized processes, the high temperature annealing required for the creation of ohmic contacts render these techniques unusable. Overall, interlayer bonding is a promising candidate for this GaN-SiC system if simple bonding is required. However, with any interlayer comes an increased GaN-SiC TBR; the goal of this work is the development of thermally efficient devices. These indirect methods will therefore be ignored, and a direct bonding method is subsequently developed.

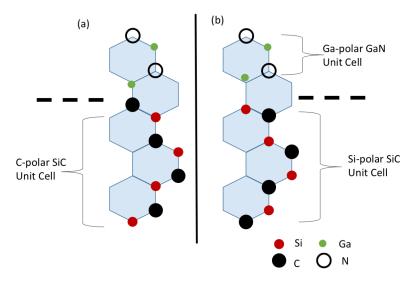

# 4.1 Principals of GaN-SiC Bonding