# SURFACE LAYER FORMATION ON Pb/Sn ALLOYS

by

Caroline S. Lee

S.B. Materials Science and Engineering Massachusetts Institute of Technology (May 1993)

Submitted to the Department of Materials

Science and Engineering in partial

fulfillment of the requirements for the Degree of

MASTER OF SCIENCE IN MATERIALS SCIENCE AND ENGINEERING

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1995

©Massachusetts Institute of Technology 1995 All rights reserved.

| Signature of Author | Department of Materials Science and Engineering                        |

|---------------------|------------------------------------------------------------------------|

|                     | May 12, 1995                                                           |

| Certified By        |                                                                        |

| •                   | Professor Thomas W. Eagar                                              |

|                     | POSCO Professor of Materials Science and Engineering Thesis Superviser |

| Accepted By         |                                                                        |

|                     | Professor Carl V. Thompson II                                          |

|                     | Professor of Electronic Materials                                      |

|                     | Chair, Departmental Committee on Graduate Students                     |

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

JUL 2 0 1995

LIBRARIES

#### SURFACE LAYER FORMATION ON Pb/Sn ALLOYS

by Caroline S. Lee

Submitted to the Department of Materials Science and Engineering on May 12, 1995, in partial fulfillment of the requirement for the department for

#### MASTER OF SCIENCE IN MATERIALS SCIENCE AND ENGINEERING

#### **ABSTRACT**

With recent advances in silicon technology, microprocessor performance is becoming limited by chip-to-package interconnections. Three primary assembly processes, Wirebonding (WB), Tape Automated Bonding (TAB) and Controlled Collapsed Chip Connection (C4), are used. Out of the three assembly processes, this study focuses on C4 technology where a chip is interconnected to a package by a matrix of solder bumps. C4 offers many advantages over WB or TAB, such as a high input/output density and better overall electrical performance.

Pb/Sn bumps are used as connectors in the C4 technology. Pb/Sn solder bumps produced by electroplating were extensively studied. The use of Pb/Sn electroplating process for C4 requires the ability to etch Ball Limiting Metallurgy (BLM) in the presence of Pb/Sn bumps. Therefore, the appropriate etchant needs to be selected. Upon etching, a surface corrosion layer is formed and an appropriate cleaning acid needs to be selected to remove this layer subsequently. This thesis examines surface layer formation on solder bumps, the morphology of the surface layer and surface layer composition.

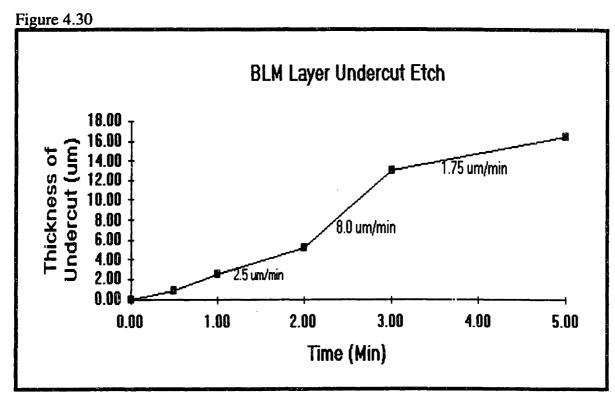

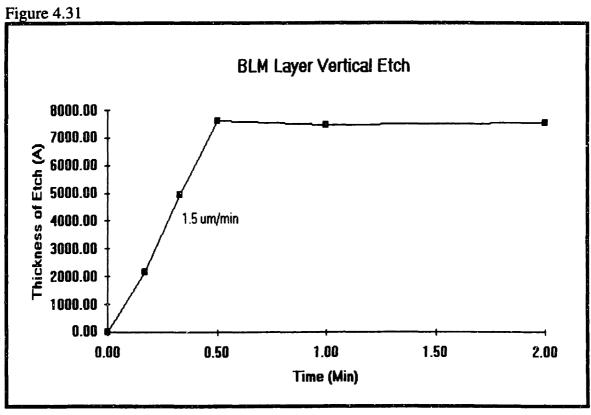

It was found that the morphology of the surface layer formed on the Pb/Sn Solder bumps is critically dependent on the concentration of the etchant, especially H<sub>2</sub>SO<sub>4</sub>. Using a gravimetric test, XPS and AES analysis, PbO containing Sn and S, was identified to be the primary component of the surface layer after the BLM etch. Moreover, the impact of the BLM etch bath on Pb/Sn solder bumps was investigated. The thickness morphology, composition and the growth rate of the layer are critically dependent on S from H<sub>2</sub>SO<sub>4</sub>. In H<sub>2</sub>O<sub>2</sub>-rich solution, the surface appears to be loosely packed and the growth rate on the surface of the bump was found to be reaction-rate limited; whereas, in H<sub>2</sub>SO<sub>4</sub>-rich solution, the diffusion rate is the controlling step in forming the surface layer on the solder bumps. Also, the layer was thin and dense. Moreover, from the AES scan and the concentration variation of the BLM etch studies, the optimal concentration was determined to be 86% H<sub>2</sub>SO<sub>4</sub> solution which results in very slow surface layer growth, limited by the diffusion rate. Using that concentration, BLM etch rates in vertical and lateral directions were studied. The overall etch rate in the lateral direction was determined to be 3 um/min; whereas, the vertical etch rate was about 1.5 um/min, thus the etch rate is anisotropic.

Further research needs to be focused on the BLM etch rate studies and on developing better methods for measuring thickness and solubility.

Thesis Supervisors: Professor Thomas Eagar, POSCO Professor of Materials Engineering Mr. Doug Crafts, Senior Engineer, Intel Corp., Santa Clara, CA

# Acknowledgements

Over a period of 7 months of research, engineering, writing resulted in this document. Without substantial help and support from others, this thesis would not been possible to complete. I would like to take this opportunity to thank those who have contributed much to the completion of my Master's thesis.

I wish to express my sincere thanks to my MIT adviser, Professor Thomas Eagar. Even though my experimental work was carried out at Intel, CA, he was always available for me to contact, and he provided critical guidance during this work. I appreciate his technical support, understanding and time spent in proofreading my thesis.

I greatfully acknowledge the support and the help of my Intel Supervisers, Mr. Doug Crafts and Dr. V. Murali. Their supports ranged from having "one-on-one" discussions to proofreading my thesis. I really appreciate their technical advices, encouragement and support. I would like to recognize Intel Inc. for the use of laboratories and libraries, as well as accepting me as part of the team. I would like to thank Peter Coon for helping me analyzing Spectroscopic data.

Thanks to Advanced Interconnects Technology Development (AITD) Group members at Intel Inc. for their kindness and emotional supports.

I would also like to thank my friends, Yukyong, Jung-Sul, Christine and Woojun for cheering me up and encouraging me in bad times.

Special thanks to my Parents and my sister Michelle, for their concern over the years. My attendance at MIT probably meant more to them than it did to me. Being able to study in America would have been impossible without the dedication and trust from my parents.

Most importantly, I want to thank God for being with me and keeping me strong in faith throughout the whole process.

The work for this thesis was carried out in the Summer and Fall semester of 1993 at Intel Corporation, Santa Clara, California as part of IIIB intership program at MIT. This document was written in the Fall term of 1993 at Intel and was revised in the Spring term of 1994 at MIT.

# **Table of Contents**

| Al | ract                                                                         | 2    |

|----|------------------------------------------------------------------------------|------|

| A  | nowledgement                                                                 | 3    |

| 1. | NTRODUCTION                                                                  | 10   |

| 2. | ACKGROUND                                                                    | 12   |

|    | 2.1. Motivation                                                              | 12   |

|    | 2.2. Methods of the bumping process in C4                                    | 18   |

|    | 2.3. Materials Selection                                                     | 25   |

|    | 2.4. Growth Kinetics and Order of Reactions - An Overview                    | 2.5  |

|    | 2.5. Electrochemical Principles of Pb/Sn Solders                             | 29   |

| 3. | XPERIMENTAL PROCEDURES AND METHODS                                           | 31   |

|    | 3.1. Thickness Morphology and Composition of the Surface Layer of Sold Bumps |      |

|    | 3.2. Gravimetric Test of Pb Compounds                                        | 35   |

|    | 3.3. BLM Layer Etch Rate Study                                               | 36   |

| 4. | ESULTS AND DISCUSSION                                                        | 37   |

|    | 4.1. Thickness Morphology and Composition of the Surface Layer of Sold       |      |

|    | 4.2. Gravimetric Test                                                        | 47   |

|    | 4.3. Reaction Mechanism for Surface layer growth studies of Solder Bumps     | . 51 |

|    | 4.4. BLM Layer Etch Rate Studies                                             | 61   |

| 5. | ONCLUSIONS AND RECOMMENDATIONS                                               | 67   |

| 5.1. Conclusions                                       | 67 |

|--------------------------------------------------------|----|

| 5.2. Recommendations                                   | 70 |

| APPENDIX I. Binding Energy of Pb compounds             | 71 |

| APPENDIX II. XPS Results of Pb Compounds               | 74 |

| APPENDIX III. Thermodynamic Properties of Pb Compounds | 77 |

| REFERENCES                                             | 78 |

# LIST OF FIGURES

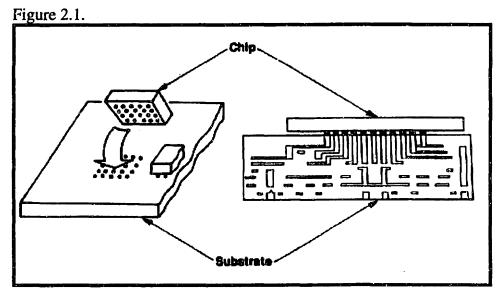

| Figure 2.1. Flip Chip                                                                | 12   |

|--------------------------------------------------------------------------------------|------|

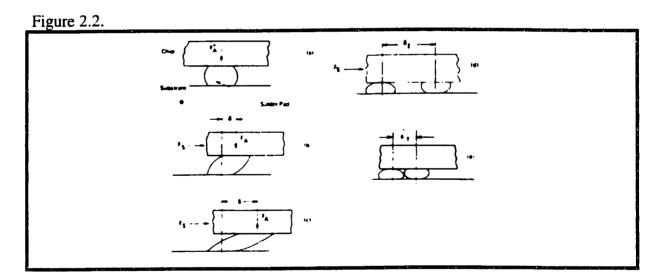

| Figure 2.2. Self-Alignment of Flip Chip                                              | 13   |

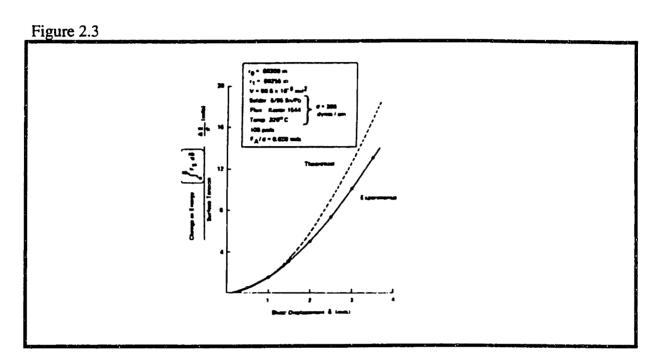

| Figure 2.3. Experimental Energy vs. Shear Displacement                               | 14   |

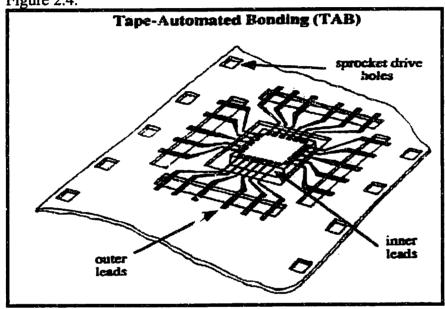

| Figure 2.4. Tape Automated Bonding (TAB)                                             | 15   |

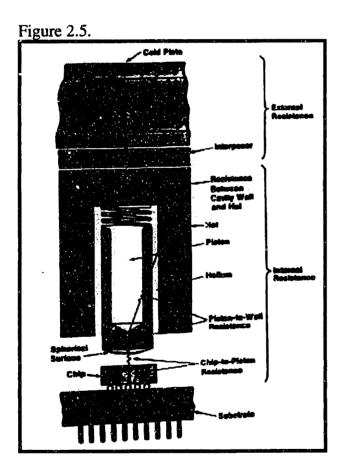

| Figure 2.5. IBM Thermal Conduction Module                                            | 16   |

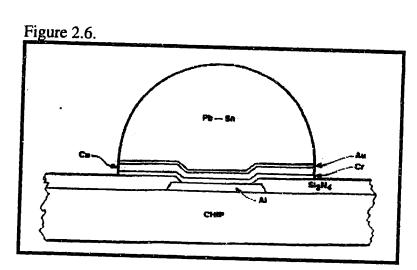

| Figure 2.6. A schematic Diagram of C4 bumps                                          | . 19 |

| Figure 2.7. Solder Bump Structures and procedures                                    | . 20 |

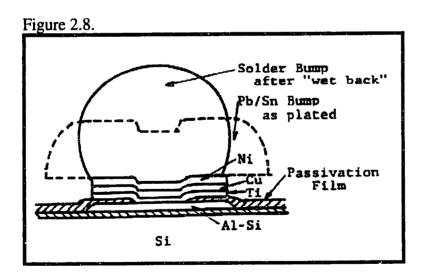

| Figure 2.8. BLM layers of C4 bumps                                                   | . 21 |

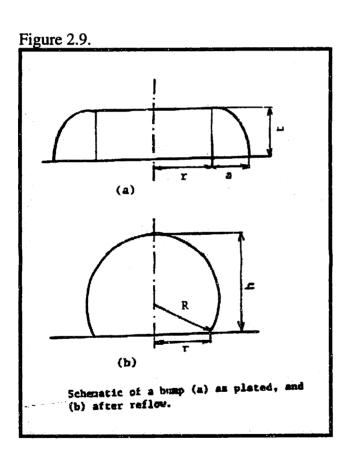

| Figure 2.9. Study on height of the bumps after reflow                                | 22   |

| Figure 2.10. Wet Etch technique for removal of BLM layers                            | 23   |

| Figure 2.11. Lift off technique for removal of BLM layers                            | 24   |

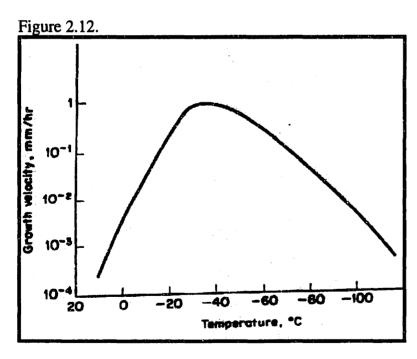

| Figure 2.12. Growth rate in the transformation of beta tin to alpha tin              | 26   |

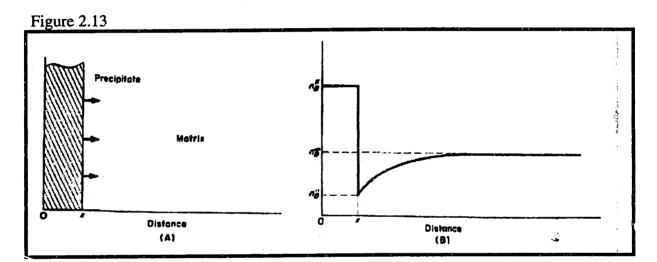

| Figure 2.13. Growth by diffusion                                                     | 27   |

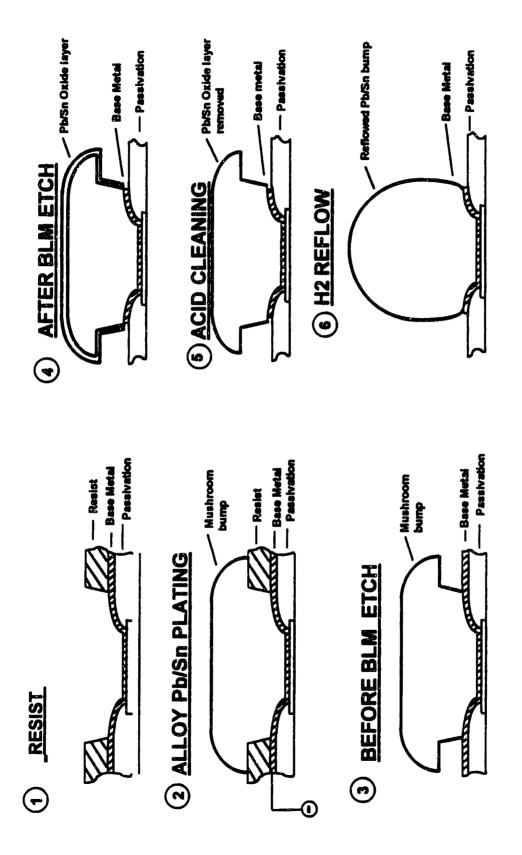

| Figure 3.1. Electroplating Process                                                   | 32   |

| Figure 4.1. The surface of Pb/Sn Solder bumps after high sulfuric concentration bath | 39   |

| Figure 4.2. The surface of Pb/Sn Soder Bumps after high sulfuric concentration bath  | 39   |

| Figure 4.3. The surface of Pb/Sn solder bumps after low sulfuric concentration bath  | 40   |

| Figure 4.4. 2000X Magnification                                                      | 40   |

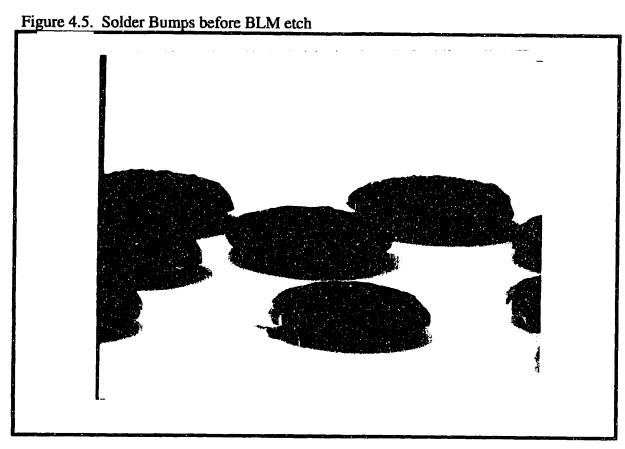

| Figure 4.5. Soder Bumps before BLM etch                                              | 41   |

| Figure 4.6. Solder Bumps before BLM etch                                             | 41   |

| Figure 4.7. S | Solder bumps after BLM etch                                                                      |

|---------------|--------------------------------------------------------------------------------------------------|

| Figure 4.8. S | Solder bumps after BLM etch                                                                      |

| Figure 4.9. S | Solder bumps after acid cleaning and after reflow                                                |

| Figure 4.10.  | Solder bumps after acid cleaning and after reflow                                                |

| U             | XPS scan on the cross section of Pb/Sn plated wafer after 86% H2SO4 Bath                         |

|               | The trend of solubility of PbO in the Pourbaix Diagram for Pb Comounds                           |

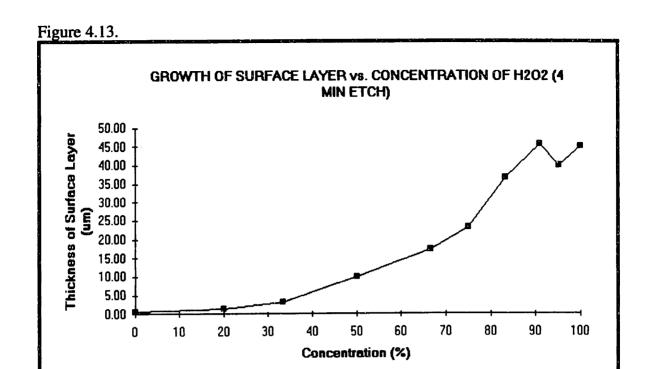

| Figure 4.13.  | Growth of Surface Layer vs. Concentration of H <sub>2</sub> O <sub>2</sub> (4 min. etch) 52      |

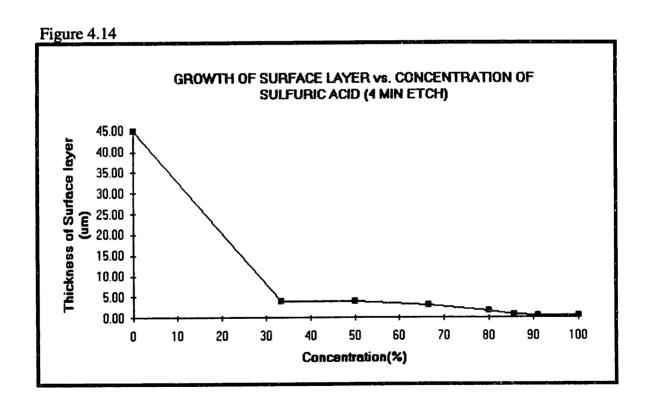

| Figure 4.14.  | Growth of Surface Layer vs. Concentration of Sulfuric Acid (4 min. etch)                         |

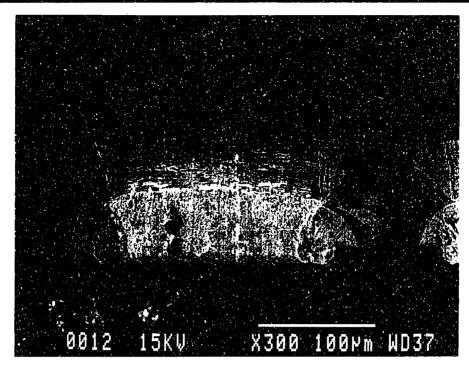

|               | Cross Section of Pb/Sn solder bumps after 90% H <sub>2</sub> O <sub>2</sub> bath (4 min. etch)   |

|               | Cross section of Pb/Sn solder bumps after 100% H <sub>2</sub> 0 <sub>2</sub> bath (4 min. etch)  |

| _             | Cross section of Pb/Sn solder bumps after 100% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch) |

| _             | Cross section of Pb/Sn solder bumps after 33% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)  |

| Figure 4.19.  | Cross section of Pb/Sn solder bumps after 50% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)  |

| Figure 4.20.  | Cross section of Pb/Sn solder bumps after 66% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)  |

| Figure 4.21.  | Cross section of Pb/Sn solder bumps after 80% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)  |

| Figure 4.22.  | Cross section of Pb/Sn solder bumps after 86% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)  |

| Figure 4.23.  | Cross section of Pb/Sn solder bumps after 91% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)  |

| Figure 4.24. | Cross section of Pb/Sn solder bumps after 100% H <sub>2</sub> SO <sub>4</sub> bath (4 min. etch)             | 58 |

|--------------|--------------------------------------------------------------------------------------------------------------|----|

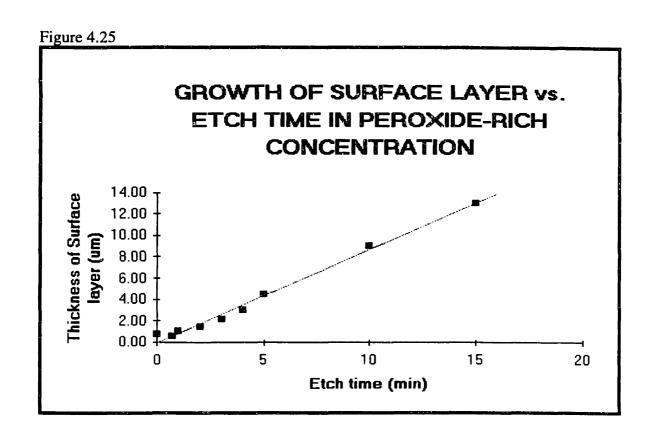

| Figure 4.25. | Growth of surface layer vs. etch time in peroxide-rich concentration                                         | 59 |

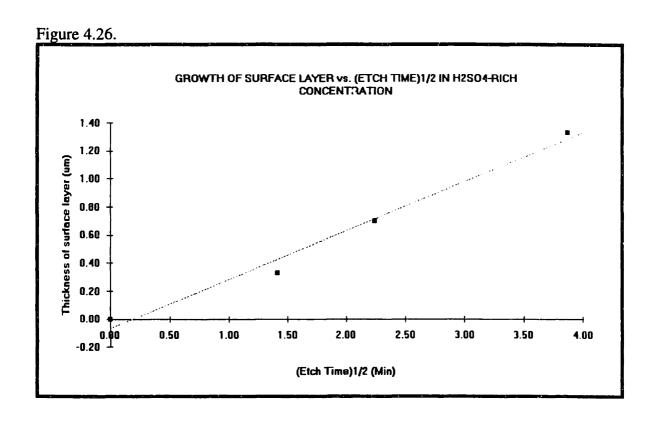

| Figure 4.26. | Growth of Surface layer vs. (etch time) <sup>1/2</sup> in H <sub>2</sub> SO <sub>4</sub> -rich concentration | 59 |

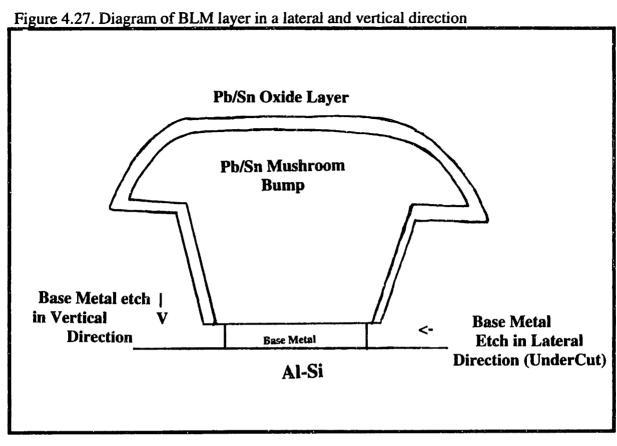

| Figure 4.27. | Diagram of BLM layer in a lateral and vertical direction                                                     | 62 |

| Figure 4.28. | The undercut of BLM layer after 86% H <sub>2</sub> SO <sub>4</sub> for 1 min                                 | 62 |

| Figure 4.29. | The undercut of BLM layer after 86% H <sub>2</sub> SO <sub>4</sub> for 3 min                                 | 63 |

| Figure 4.30. | BLM layer Undercut Etch                                                                                      | 64 |

| Figure 4.31. | BLM layer Vertical Etch                                                                                      | 64 |

# LIST OF TABLES

| Table 4.1. | Percentage composition of Surface analysis using AES | 38 |

|------------|------------------------------------------------------|----|

| Table 4.2. | Percentage composition of Surface analysis using XPS | 44 |

| Table 4.3. | Binding Energy of Pb oxides using NIST data          | 44 |

| Table 4.4. | Gravimetric test results for Pb oxides               | 49 |

| Table 4.5. | Solubility of PbO                                    | 50 |

# **CHAPTER 1. INTRODUCTION**

With recent advances in silicon technology, microprocessor performance is becoming limited by chip-to-package interconnections. The three primary assembly processes are: Wirebonding (WB), Tape Automated Bonding (TAB), and Controlled Collapsed Chip Connection (C4). Wirebonding is a method where semiconductor components are attached with very fine wire. These components interconnect with each other or with a package lead. TAB is the process to join silicon chips to patterned metal on polymer tape and then attaching silicon chips to a substrate or board by outer lead bonding [Tummala and Rymaszewski, 1989, pp. 1151-1154].

C4 is a technology where a chip is interconnected to a package by a matrix of solder bumps. This solder-bump interconnection was originated by IBM in the early 1960s to remove several problems of manual wirebonding, such as low productivity, high expense and unreliability due to mechanical connectors. TAB also has several disadvantages over C4, such as total input/output count limited by pitch, the high cost of high performance TAB tape and the complexity of the total process. C4 has several potential advantages over TAB and WB. First, C4 offers a high input/output density by placing solder bumps anywhere on the chip in an array. Second, interconnection by very small solder bumps lowers inductance, this enhancing the overall electrical performance. Finally, C4 allows for lower process complexity due to the relaxation of pitch requirements and the self-aligning property of C4 die attach.

This study focuses on C4 solder bumps to understand Pb/Sn surface layer formation kinetics, as well as analysis of layer composition and morphology of C4 bumps after base metal etch. In addition, the effect of using etchants for removing the surface layer to improve the solderability of solder bumps, and the etch rates of Ball Limiting Metallurgy (BLM) layer and its etch mechanism were studied.

Specifically, C4 was studied from three view points. First, the kinetics of reaction of the surface layer with sulfuric acid and H<sub>2</sub>O<sub>2</sub> etch were studied in depth. The thickness variation of the surface layer as well as its composition caused by the interaction of H<sub>2</sub>O<sub>2</sub> and sulfuric acid was studied by the rate of growth of the surface layer as a function of time. A model was developed to examine the rate limiting step in the formation of these layers. The composition and morphology of those layers were also analyzed using XPS, AES and SEM. Moreover, solubility testing was performed to confirm the spectroscopy data results. From these data, the optimal etchant composition which results in the thinnest surface layer and most efficient etch of BLM layer, and its etch time was determined.

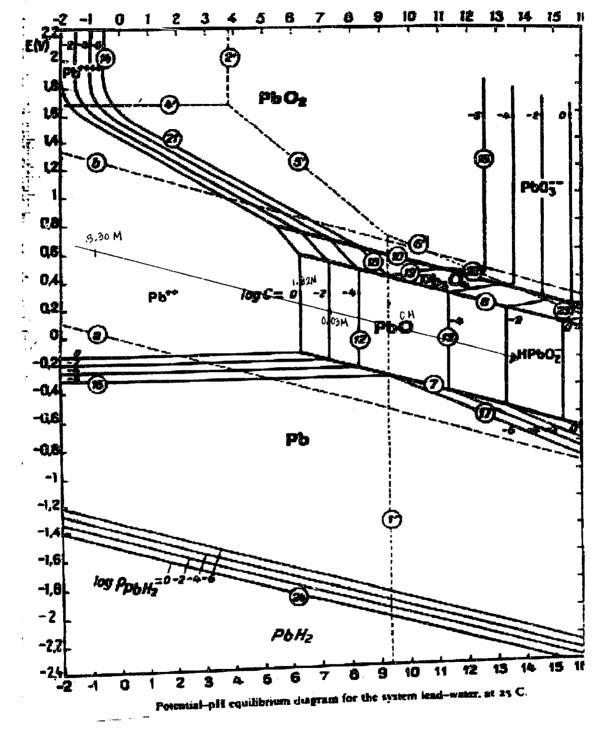

Second, removing the surface layer before reflow, using the right acid, is the most important step for good reflow and durability of solder bumps. The selection of acid can be determined using electrochemical principles of Pb/Sn solders and using the Pourbaix diagram of Pb compounds as explained in Section 2.4. The pH change of this acid was studied extensively and the solubility of the surface layer was observed.

Finally, the BLM layer etch rate in the lateral and vertical directions was studied to determine optimal etchant composition. Forming a thin layer on the surface using the correct composition of etchant is important, but it is equally important that the current composition completely etches the BLM layer around bumps after plating. SEM was used to take pictures of cross sections of bumps. The thermodynamics and kinetics of the etch rate will be discussed.

# **CHAPTER 2. BACKGROUND**

#### 2.1. Motivation

C4 Technology is important for chip-to-package interconnections and offers many advantages over TAB and WB. One advantage is the high input/output density of the C4 process, which enables bumps to be placed anywhere on the chip so that it is easier to make connections to the circuitry at those points [Jackson et. al., 1991, pp. 82-85]. Short solder bumps improve overall electrical performance and allow more control of the size of the chip. Moreover, the higher density of I/O per chip allows a higher degree of integration at the first packaging level than ones with edge-connect packages, such as WB or TAB.

C4 technology is also referred to as "Flip Chip" because the chip is self-aligned

[source:Tumala et. al., 1989, pp.366]

to the substrate (upside-down) and the surface tension of solder allows solder balls to form self-aligned metallurgical joints with the substrate as shown in Figure 2.1. The selfalignment feature allows high yields even when dealing with chips with very high pin counts. During chip joining, self-alignment automatically corrects relatively coarse chip placement during solder reflow. This is not possible for TAB or WB. Studies done by Goldman et. al. (1972) demonstrated self-alignment capability of a flip chip. These studies showed that within a certain limit, a misaligned chip self-aligns during reflow joining. The mechanical energy of a molten solder pad is made up of gravitational and surface energy, the joint always having the shape which minimizes total energy. Gravitational energy being negligible, for small balls (less than 1 mm in size), free surface area can then be viewed as a direct measure of the pad energy. Goldman discovered that the minimum distance of critical energy or touching is the maximum center-to-center mis-registration  $\delta_R$  which can be realigned as shown in Figure 2.2:

[source: Goldmann, 1972, pp.333]

$\delta_R = \min (\delta_E, \delta_T).$

where  $\delta_E$  is the minimum critical energy distance and  $\delta_T$  is the touching distance.

Goldman proved that for small displacements, the energy is close to his predicted value, but the experimental energy is increasingly less than the theoretical value for larger displacements (Figure 2.3). Therfore, the degrees of misregistration that can be realigned in solder-reflow chip joining is limited by the touching distance. Also,

[source: Goldmann, 1972, pp.336]

Goldman showed that a pad of interface radius (R) can have a center-to-center offset of at least the touching distance or three times the average interface radius [Goldmann, 1972, pp.332-339].

TAB processes use thermocompression bonding to attach silicon chip pads to patterned metal on polymer tape (Figure 2.4). This process is known as inner lead bonding (ILB). Following ILB, the chip is then encapsulated or tested. The individual die is subsequently removed from the tape and packaged using outer lead bonding (OLB) techniques.

The C4 process costs less than TAB and WB because of the bumping process, the simplified assembly processes and the improved cost performance ratio for C4 packages. The bumping process takes place instantaneously; whereas, WB makes each connection

1

from chip to package through a manual or automatic set of routes with wires. The cost of equipment, maintenance and downtime of C4 is lower because of its self-alignment capability; the greater the misalignment that can be corrected, the less accurate chip placement would be needed [Goldman, 1972, pp.332-339].

[source: Charles, 1989, p. 233]

Flip chips have more thermal advantages relative to back bonding where the package is placed on the top of the chip. In the past, a constraint with flip-chip bonding was the poor dissipation capability compared to backside bonding. Area array bumps, compared to pheripheral bumps, resulted in an increase in heat dissipation because area array bumps increased the number of joints and their greater closeness to the device. Heat dissipation is a crucial factor in flip-chip bonding because of a device's ability to eliminate heat greatly affects the maximum power capability. However, since the back of the flip-chip is mechanically and electrically free of delicate surface features, flip-chips are now competitive thermally with back-bonding by having a variety of heat sinks on the back of a chip. For example, the IBM Thermal Conduction Module, TCM (Figure

2.5), can dissipate 4 watts per chip and up to 300 watts for a 100 or a 118-chip module. This system has spring-loaded pistons transferring heat from the back of each chip to a water-cooled plate attaching a solder joint thermal path [Goldmann & Totta, 1983, pp. 91-97]. As an enhanced conduction path, Helium gas encapsulation has been developed for this conduction cooling machine because of its high thermal conductivity [Oktay & Kammerer, 1982, pp. 55-66].

[source: Goldmann & Totta, 1983, pp. 94]

This cooling and encapsulation concept depends on the used of spring-loaded "pistons" in contact with each chip. R.C. Chu et. al. (1982), did further studies on TCM modules and established that the TCM cooling concept is thermally superior to its Liquid-Encapsulated Module (LEM) predecessor. D.M. Cavanaugh (1975) compared flip-chip

thermally with wire-bonding. Two chip/substrate package configurations were tested for  $\theta$ j-a,  $\theta$ j-s and maximum power dissipation; one to study flip chip reflow die attachment and one to study chip-to-wire attachment. Here,  $\theta$  is a thermal resistance factor, defined as:

$\theta = \Delta T/P$  OC/Watt

where P = power and  $\Delta T = Tj$ - $T_0$  where Tj = Device Junction temperature and  $T_0 = temperature$  of heat sink or ambient if the atmosphere is the ultimate heat sink. Also,  $\theta j$ -a,  $\theta j$ -s stand for Thermal resistance from junction to ambient, from junction to substrate respectively. As a result, thermal resistance of the mounted flip was higher when compared to a chip- and-wire configuration. These advantages enabled us to choose C4 over TAB or WB.

Myers (1959) gave an overview of flip-chip die bonding. The potential advantages of IC flip-chip bonding are to eliminate wirebonds, to reduce assembly costs, and to improve reliability. Packaging costs are as much as 80% higher for wirebonds since each wire has to be bonded individually. The flip chip reduces the failures and costs associated with wirebonding. Also, the substrate materials along with the substrate interconnect pattern provide mechanical supports and act as a heat sink. The substrate-toconductor pattern interface metal serves as a thin film resistor in hybrid applications. Moreover, the metallurgical system between the silicon chip and the substrate used for the chip interconnection pattern-the bump, the substrate interconnection pattern, and interfacing and bonding between them- is the single most important variable in flip chip. These interfacing materials are required to improve mechanical adhesion and to join two noncompatible metals. Also, this bonding method provides joining between the bump and the conductor pattern, as well as, high strength and low resistence bond at low costs. Solder bonding offers several advantages such as lower temperature processing above the temperature of the molten solder required, rework capability and the simple soldering process [Myers, 1969, pp.131-144].

### 2.2. Methods of the bumping process in C4

There are two types of solder bump formation for Flip Chip Technology: evaporation and electroplating. In this chapter, these two processes and their advantages and disadvantages are discussed.

Flip chip technology was originally developed at IBM in the 1960s to resolve problems involving manual wirebonding. After passivation patterning, the under-bumpmetallization (UBM), such as chromium/copper/gold layers are sequentially deposited through holes of a metal mask using an evaporator. Chromium acts as an adhesion promoter and diffusion barrier metal layer which makes contact with Al-Si electrode pads. A layer of copper is then deposited, providing solder wettability. To prevent copper from oxidizing, a layer of gold is deposited above the copper layer. Finally, Pb/Sn solders are deposited sequentially through the same mask using another evaporator. These wafers are then placed in an H<sub>2</sub> ambient furnace at 365 <sup>O</sup>C for reflow to obtain spherical bump shape. The bumps melt and wet only at the Cr/Cu/Au areas. H2 reduces minor Pb/Sn oxides. The surface tension of the bumps results in a spherical shape after A schematic diagram of C4 bumps using the IBM method is reflow at about 365 <sup>O</sup>C. shown in Figure 2.6. This evaporation method is performed in a vacuum. Because the deposition process is continuous and the key layers are blended together, layers do not need to be separated from one another. Although the IBM method is well established, costs associated with the deposition process are high. Moreover, due to differences in the thermal expansion coefficient between the Si wafer and metal mask, as wafer size increases, good dimensional accuracy of bumps is very hard to obtain [Tumala & Rymaszewski, 1989, pp.366].

An alternate method for depositing solder bumps is electroplating. Blanket layers of metal or Ball Limiting Metallurgy (BLM) are sputtered on the wafer. Electroplating is a deposition of metallic coating onto a conductive object placed in an electrolytic bath.

Using the terminal as the anode, a DC current is passed through the solution affecting transfer of metal ions onto the cathodic surface.

[source: Nagesh, 1982, pp.10]

In the case of C4, this is the BLM layer. Photoresist is then applied on the BLM film coated wafer and the resist is patterned using the photolithography process. The wafer is then subjected to electoplating and Pb/Sn bumps are formed in the open vias in the patterned resist. After stripping the resist, using the bumps as a mask, the thin film metal layers are selectively etched to electrically isolate the bumps from each other. The electroplating method requires the right selection of a base metal stack because the solder is soluble in almost every acid and is vulnerable to the etching solutions of the base metal [Tumala & Rymaszewski, 1989, pp.378]. During this etch process, thin layers are chemically formed on the surface of the Pb/Sn bumps. These layers impact the solderability of the solder bumps and must be removed. Although the electroplating method seems to be easier and a more economical bumping process than IBM's original "metal mask" vacuum deposition method, the etching of base metal stacks, without etching away plated solder bumps, has remained a difficult problem.

Several studies have been conducted to fabricate bumps by electroplating. Studies done by Kawanobe et.al. (1981) summarized the past solder bump fabrication processes produced by plating (Figure 2.7). One of the fabrication by electroplating

Figure 2.7. Solder Bump structures and procedures

| Maker              | Structure                      | Procedure                                                                                                                              | NUEJ                                                          |

|--------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 186                | Solder<br>Cu<br>Al-Es          | 1.Ketal Mask Alignment 2.Ag/Cu/Cr Deposition 3.Metal Mask Alignment 4.En-Pb Deposition 5.Wet Back                                      | "Controlled<br>Collapse Inter-<br>connection"<br>ref. (1)     |

| Philips            | Solder Cu Ni Al                | 1.Ni/Al Deposition 2.Photoresist 3.Ni Etch 4.Photoresist 5.Sn-Pb/Cu Electro. Plate 6.Al Etch 7.Reflow                                  | "IC on Tape" ref. (3)                                         |

| Sanken<br>Electric | Solder                         | 1.Mi/Al Deposition<br>2.Photo-Etch<br>3.Passivation 4 Through-Hole<br>4.Metal Aparture Alignment<br>5.En-Pb Ball Placement<br>6.Reflow | zef. (4)                                                      |

| ***                | Solder<br>Ni<br>Ni<br>Al       | 1.Mi/Al Deposition 2.Photoresist 1.AU/Mi Electro. Plate 4.Mi,Al Etch 5.Solder Dip                                                      | Procedure is<br>speculated from<br>the structure.             |

| -3-                | Solder<br>Ag<br>Au<br>Cr<br>Al | 1.Au/Cr Deposition<br>2.Photoresist<br>1.Ag Electro. Plate<br>4.Au,Cr Etch<br>5.Solder Dip                                             | Procedure is appendiated from the structure.                  |

| •e•                | Solder<br>Mi<br>Mi<br>Cr<br>Al | 1.Mi/Cr Deposition 2.Photoresist 1.Mi Etch 4.Photoresist 5.Ma/Ag/Mi Electro Plate 6.Cr Etch 7.Wet Back                                 | Procedure is speculated from the structure.                   |

| Phileoford         | Solder<br>Hi-P<br>Hi<br>Ct     | 1.Hi/Cr Deposition 2.Photoresist 1.Hi,Cr Ztch 4.Hi Electroless Plats 5.Solder Dip                                                      | Structure is<br>speculated from<br>the procedure.<br>ref. (5) |

[Source: Kawanobe et. al., 1981, pp.150]

methods was to make nickel or silver spacers but bumping by dip soldering made it very difficult to build up higher solder bumps. Also, as shown in Figure 2.7, this bumping process is done by an electroplating method, but supplying plating current through thin and high resistent films result in a large thickness distribution on a wafer. The method used by Philips was electroplating. A corrodable Al layer for BLM was used. Knowing that the solder is very vulnerable to etching solutions of BLM, Kawanobe et. al. finally selected a Cu layer for a solder wettability barrier against the reaction between Al and solder and for the conductive layer. A TiW layer was used as an adhesive with Pb/Sn solders (Figure 2.8). These layers were then etched off without attacking the solder using EDTA, H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub>. Sn and Pb are plated separately to control only the Pb-Sn solder constitution. This study also determined the height of the bumps after reflow (Figure 2.9).

[source: Kawanobe et. al. 1981, pp.149]

The relation between the height and the plating thickness is an important criteria in determining the bump height. The volume after plated  $V_1$  is defined in the following:

$$V_1 = \pi \int [r + a/t \sqrt{t^2 - x^2}]^2 dx = \pi [r^2 t + \pi/2 art + 2/3 a^2 t]$$

The volume of bump after reflowed shape  $V_2$  is:

$$V_2 = \pi \int [R^2 - x^2] dx$$

where  $R = h^2 + r^2 / 2h$

=  $\pi/6 h[h^2 + 3r^2]$

In practice, the volume difference between  $V_1$  and  $V_2$  can be expressed as:

$$V_2 = \alpha V_1$$

where  $\alpha$  is a correction factor

$$h^3 + 3ph + 2q = 0$$

where

$$q = -3[r^2t + 1/2 \pi art + 2/3 a^2t] \alpha$$

$p = r^2$

[source: Kawanobe et. al., 1981, pp. 152]

Then using the last two equations:

$$h = 3\sqrt{-q} + \sqrt{q^2 + p^3} + 3\sqrt{-q} - \sqrt{q^2 + p^3}$$

This calculation concluded that bump height of 100 µm or more is necessary for controlled collapse solder interconnections. Also, approximately 50 µm or more "uniform thickness" is required after plating. This study showed that thickness uniformity distribution on a whole wafer depends on the current density, the flow rate of plating solution through the bath, and a cylindrical-shaped plating bath where a wafer and an anode are placed opposite to one another [Kawanobe et. al., 1981, pp.149-155]. Another study done by Wolf, J. et.al. (1993), demonstrated an electroplating method for the bumping process. Using TiW/Au /Cu BLM, Wolf achieved low processing costs and better resolution by two approaches of Pb/Sn solder bumping. In Figure 2.10, wet

Al-Chippad with Passivation

Sputteretch Al Sputter Ti : W(N)/Au (200 / 200 nm)

Spin-on Photoresist (1 ≥ 30 μm) Expose to yield steep walls

Electroplate Cu, Pb, Sn Strip Photoresist Al Sputter Ti : W(N)/Au (200 / 200 nm)

Wet etch Au, Ti:W(N)

Figure 2.10.

[source: Wolf et. al. 1993, pp. 143]

etch is used to remove BLM around solder bumps. Another method used is a lift off technique instead of wet etching steps. A lift off technique avoids wet etching steps by sputtering BLM layers onto a resist mask, followed by PVD of copper and also by a thick second photoresist layer to achieve PVD of lead and tin (Figure 2.11). Both methods

proved to be viable so that benefits of both techniques can be compared and used [Wolf et. al. 1993, pp. 141-152].

After these Pb/Sn solder bumps are plated, the BLM around the bumps is etched. Studies done by Kawanobe, T. et.al. (1981) indicated that a combination of hydrosulfuric acid and hydrogen peroxide etches the BLM layer. Combination of Sulfuric acid and H<sub>2</sub>O<sub>2</sub> are used to etch the base metal layer in this project. These acids create sulfur containing oxide layers on the surface of the bumps. These oxide layers on the surface serve as protection layers and as masks against other BLM etchants. After the base metal layer etch is applied, these oxide layers on the surface need to be eliminated from the bumps to allow for solderability of bumps during reflow.

1) 4) spin-on 2. photoresist (30-50 µm) Expose to yield steep walls 2) 1. photoresist  $(3 \mu m)$ deposited, patterned PVD Pb, Sn sputtering Ti:W(N)/Au (200 nm / 200 nm) Cu / Au (1-2) µm / 100 nm 3) 6) Lift-off Lift-off TI:W(N) / Au / Cu / Pb/Sn layer Au layer

Figure 2.11.

[source: Wolf et. al. 1993, pp. 146]

#### 2.3. Materials Selection

There are several reasons why Pb/Sn solders are chosen over other combinations of solders such as Pb/In, In/Sn and Cu/Pb. First, high-lead composition solder (97% Pb and 3% Sn) was selected because its melting point is about 315 <sup>O</sup>C, which prevents C4 bumps from remelting at the package-to-board level of assembly. Wafers are then placed in an hydrogen funrace at 360 <sup>O</sup>C for reflow [Tumala & Rymaszewski, 1989 pp.369]. The choice of BLM is important for these solders because these layers have to be good conductors for plating, minimizing the formation of intermetallics with Sn and forming a good protection layer for better adhesion and uniform plating. Studies done by Bowlby at Motorolla, indicated that Pb/Sn solder bumps ranging from 60/40 to 95/5 are preferred for the following reasons: improving storage and aging characteristics, and wetting characteristics of solder bumps.

#### 2.4. Growth Kinetics and Order of Reactions - An Overview

Since the growth kinetics of surface layer on Pb/Sn bumps was examined in this study, its overview is explained. Growth kinetics becomes important after the undeveloped embryo has exceeded a critical size and become a stable nucleus. The rate at which heat of fusion is removed largely controls the growth rate of new phase during solidification. Considering simple growth, where a new phase growing from another phase by simple transfer of atoms of a single component, an equation shown below describes the net rate of atom transfer from the matrix to a particle (being equal to the difference in the rate of atom movement toward and away from the particle):

$$I = Sve^{-\Delta g} a^{/kt} (1 - e^{-\Delta g \beta \alpha / kt})$$

Where S = number of atoms facing the surface, v = an atomic vibration frequency I = net number of atoms per second leaving the matrix to join the beta phase  $\alpha =$  matrix phase,  $\beta =$  embryo phase.

Assuming that when the atoms jump, they move through an average distance  $\lambda$ . The velocity of the boundary will be given by:

$$v = \lambda I / S$$

Where I/S = the average number of per atoms' jumps per second facing the boundary

$\lambda$  = the distance corresponding to each of these jumps.

Assuming  $\Delta g \alpha \beta \ll kT$  for a sufficiently small supercooling, the growth velocity becomes:

$$v \approx \lambda v (\Delta g \alpha \beta / kT) \exp(-\Delta g \alpha / kT)$$

For a large degree of supercooling, the velocity equation may be written as:

$$v \approx \lambda v \exp(-\Delta g \alpha / kT)$$

Figure 2.12 shows this growth rate in the transformation of beta tin to alpha tin [Reed-Hill and Abbaschian, 1973, pp. 498-501].

[source: Reed-Hill and Abbaschian, 1973, pp.501]

There is another type of growth where formation of a new phase occurs that is different from the composition of old phase. As shown in Figure 2.13, the growth is controlled by diffusion. According to Zener's theory, whenever, the growth is controlled by a simple diffusion process, the interface position varies with the square root of time and the growth velocity varies inversely as the square root of time.

$$x = a * \sqrt{Dt}$$

[source: Reed-Hill and Abbaschian, 1973, pp.502]

where x = thickness layer growth, D = diffusion coffients and  $a^* =$  parameter for dimensional growth. So if the reaction rate of two molecules forming growth is fast enough, then diffusion is the rate-limiting step. Otherwise, the growth rate can be controlled by the chemical reaction rate, where growth of thickness is directly proportional to time,

$$x = ct$$

where  $c = a constant$

Therefore, the rate of surface oxide layer growth in this study can determine the ratelimiting step. To determine the order of the reaction, the concentration of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> was varied as well since the rate-controlling step is determined by both concentration and time for those acids which react with Pb/Sn solders [Reed-Hill and Abbaschian, 1973, pp.501-506].

#### 2.5. Electrochemical Principles of Pb/Sn Solders

As mentioned earlier, removing the oxide layer on the surface of bumps is the most important step for reflow. The selection of acids can be explained by the Pourbaix diagram of Pb compounds which uses the relationship between electrode potential and pH equilibrium to show the region where the oxides are dissolved in aqueous solutions. Electrochemical reactions are different from chemical reactions in that an electrochemical reaction, instead of a chemical reaction, occurs at the interface between the metal and a solution of electrolyte. This interface enables us to measure the affinity of the reaction in magnitude and sign by the electrode potential. If the two potentials-- electrode potential E and equilibrium potential E<sub>0</sub> - are equal, the affinity is zero and the thermodynamic equilibrium state of the reaction is obtained; if the electrode potential is above the equilibrium potential, the affinity is positive and the reaction can take place only in the direction of oxidation. However, if the electrode potential is below the equilibrium potential, the affinity is negative and the reduction reaction is only the reaction that takes The electrode potentials and pH are the characteristics of a metal/solution place. interface, where the metal or solution is the site of electric currents or chemical changes [Pourbaix, 1974, pp. 53-55].

When a metallic electrode is placed into a solution containing ions of that metal, an equilibrium is established between the trend of the metal to enter solution as ions (1), and the opposing force for the ions to lose their charge and deposit on the metal (2):

$$M \rightarrow M^{n+} + ne^{-} \tag{1}$$

$$M^{n+} + ne^{-} \rightarrow M \tag{2}$$

For this equilibrium to be established, a charge separation will occur to determine whether ionization or deposition happens faster. In other words, faster ionization will result by metal becoming negatively charged relative to the solution and faster deposition will result by metal becoming positively charged relative to the solution. Such a resultant potential, between the metal and the solution, is called electrode potential. Here,

the Nernst equation is given to measure the magnitude of the potential between a metal and a solution of its ions:

$$E = E_0 + (0.059/n) \log a$$

where  $E_0$  is a constant characteristic of the material of the electrode, n=valence charge and a = activity of the metal ion [Lowenheim, 1978, pp.16-19]. Therefore, using these two characteristics, pH and Electrode potentials, a Pourbaix diagram of Pb compounds tells us to predict at which potential and pH of solution certain oxides can be dissolved as well as concentration of those oxides that have dissolved in a certain region. An example of a Pourbaix diagram is shown in the Results section of this thesis.

# CHAPTER 3. EXPERIMENTAL PROCEDURES AND METHODS

# 3.1. Thickness Morphology and Composition of the Surface Layer of Solder Bumps

To prepare a sample for the morphology and composition studies, the process for bumping by electroplating is described. Blanket layers of metal or Ball Limiting Metallurgy (BLM) were deposited by Physical Vapor Deposition(PVD) on the wafer. Photoresist was then applied and patterned on the wafer using photolithography. The wafer was then subjected to electroplating of Pb/Sn bumps which were formed in areas not convered by resist as shown in Figure 3.1. After the plated wafer was prepared, the wafer was cut into dice to perform the experiments for the morphology and composition studies. The BLM etch bath of H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub> was prepared; the dice with Pb/Sn soldered bumps were put in the bath and were agitated to etch the BLM layer; During the etch, a surface oxide layer was formed on the bump. The size of the etch bath was about eight gallons. The concentration of H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub> was varied as well as the etch time to study the surface layer as a function of concentration variation in BLM etchant. Scanning Electron Microscopy (SEM) was used to study the thickness, the morphology of the surface layer and the etch rates of BLM layer.

Standard precision cross-section SEM technique which showed the cross section of Pb/Sn bumps, was performed. After the dice were exposed to various etchant baths, each die was cut into 4 small pieces with a scribe. A mixture of hardner and resin was prepared for an epoxyresin and a drop of this mixture was applied to a cover glass. This cover glass with the epoxyresin was then placed on the top of the die. A sample holder was used to hold the die and the cover glass together, and this sample was heated on a hot plate till the color of the epoxyresin changed to an amber color, and the epoxyresin hardened between the cover glass and the die. Then the sample was polished and mounted to grind the corner of the die using SiC grit papers with a roughness ranging

Figure 3.1. Electroplating process.

from 400-1200 sequentially. Top view optical microscopy was used to stop polishing once the center of the bumps was reached. Then, alumina oxide papers with a grain size ranging from 12 um to 0.3 um were used successively for final polishing. Since the Pb/Sn solder bumps were very soft and were easily oxidized, they require very careful polishing. The microscope was used to observe the cross section throughout this polishing process. After making a cross section of the sample, it was put in a gold sputter system to produce a few angstroms of Au which would prevent charging when using the SEM. Finally, the morphology and thickness of the surface layers of the bumps were studied using SEM.

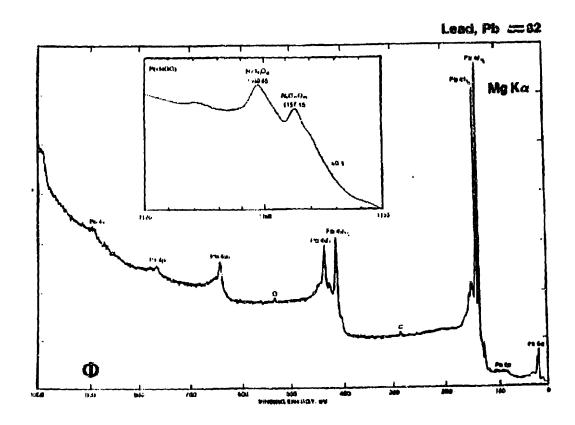

After those samples were prepared, several spectroscopic techniques were used to analyze the surface of the solder bumps. The spectroscopic techniques had several limitations. Auger Electron Spectroscopy (AES) is the energy analysis of Auger electrons produced when an excited atom relaxes after ionization by a high-energy electron [Wolf, S. and Tauber, R.N., 1986, pp. 604]. Auger Analysis was used because it is surface-sensitive with typical analysis depth of less than 50A, has a very small analysis area (5-10 um) and can detect very small elemental concentrations on the surface, about 0.1 atom %. However, AES does not give any information about the bonding state of the elements.

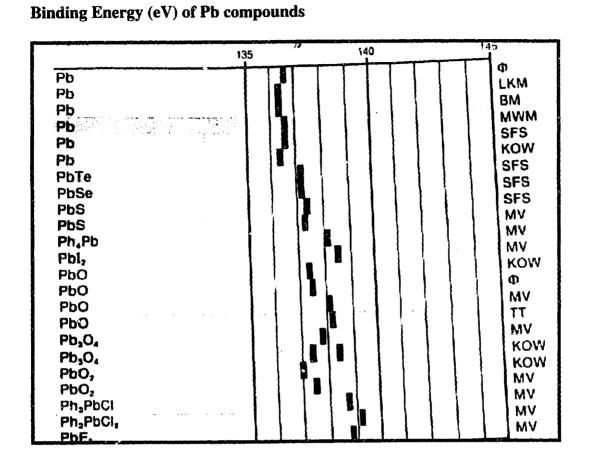

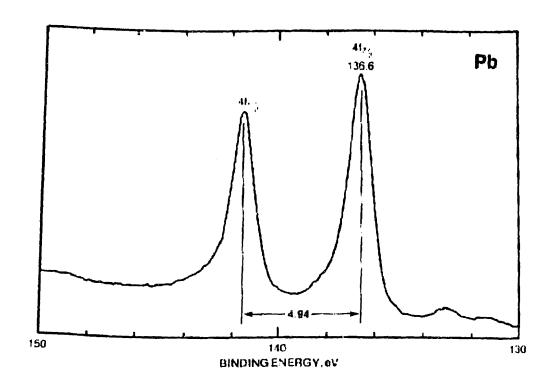

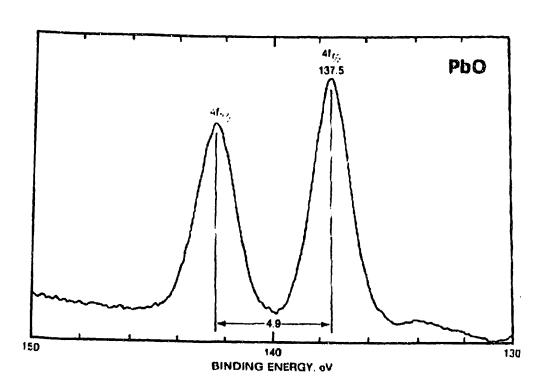

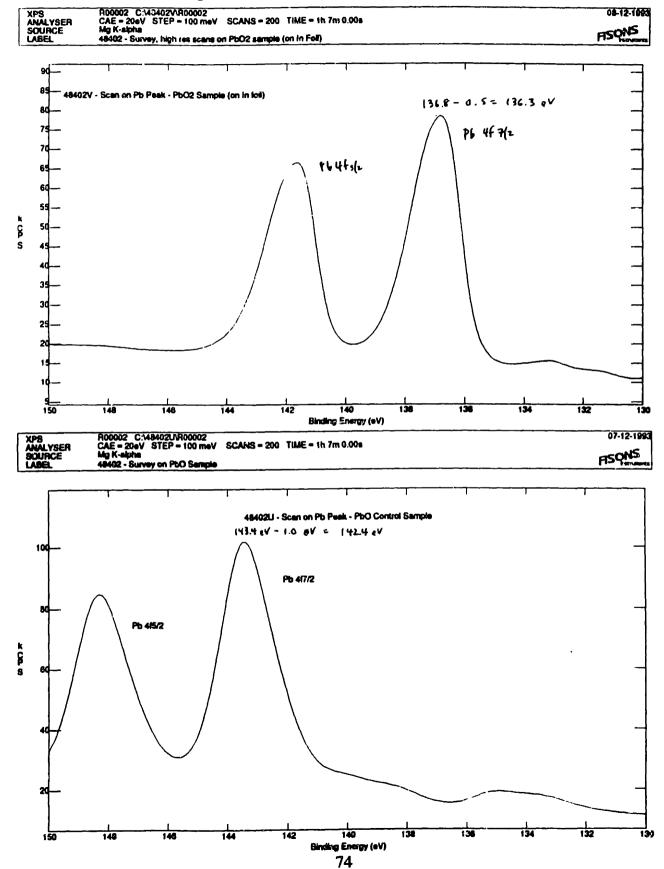

X-ray Photoemission Spectroscopy (XPS) uses low energy x-rays, such as the K-alpha line of aluminum to cause photoelectron emission. The emission of photoelectrons is different from Auger emission in that XPS analyzes the electron that is "knocked out" of the atom. This equipment was used because it is surface-sensitive like AES and shows information about the bonding state of the elements. The limitation with XPS is that the difference in binding energy between Pb<sup>2+</sup> and Pb<sup>4+</sup> is less than 1 eV (Appendix I). In addition, the charging effect causes peak shifts which make it harder to distinguish to which peak the surface layer corresponds.

Secondary Ion Mass Spectrometry (SIMS) uses a medium energy beam of primary ions to sputter a sample. The intensity and mass of the secondary ions can be

used to determine the elemental composition of a sample. This equipment has a very high sensitivity and most elements can be detected. However the surface of the solder bumps was too rough to obtain accurate depth profiling. Furthermore, SIMS uses  $O_2^+$  primary ions to sputter a sample. The molecular weight of the  $O_2^+$  primary ion is same as the molecular weight for S which can not be detected, and the other primary ions, such as  $Cs^+$ , required a very large spot size.

Energy Dispersive X-ray (EDX) was also used as EDX can detect elements with a thickness of more than 1 um without sputtering by looking at a polished cross section of the bumps, gives a bulk concentration of the elements and gives a visual image of the sample using SEM. EDX is used in conjunction with SEM and does not require sputtering a sample. However, EDX has limited ability to distinguish between two adjacent X-ray peaks. The Pb peak is very broad and overlaps the S peak. So Pb and S peaks cannot be distinguished.

X-ray Fluorescence (XRF) was used to detect the elements present by using an X-ray source to irradiate the sample with high-energy photons. However, this equipment is able to detect elements starting from Na (atomic number of 11) so that the lighter elements, such as O, can not be detected.

Atomic Force Microscopy (AFM) was used to measure the grain size of the surface, but the surface of the layer was too rough to get a stable image.

Rutherford Backscattering Spectrometry (RBS) was used as it gives information on both the composition and depth distribution of elements by the energy of the backscattered ions. After an energetic beam of He ions impinges on the target, the He ions backscatter from the near surface region of the sample and are collected by a solid state detector. The limitations with this equipment are the poor spatial resolution (1 mm) and low detection limits for low atomic number elements. Moreover, the surface of the layer was too rough to obtain accurate depth distribution of the elements [Wolf, S. and Tauber, R.N., 1986, pp. 604-611]. Therefore, based on the capabilities and limitations fo

various techniques listed above, AES, XPS and SEM were used as the primary techniques. In this study, VG 310F Microlab AES and XPS, and Joel 840 SEM were used. For XPS, a Mg X-ray source was used and Field Emission Electron source was used for AES. The composition of the surface layer on the solder bumps at the die level was examined using AES and XPS, whereas SEM was used to measure the thickness and the morphology of the surface layer.

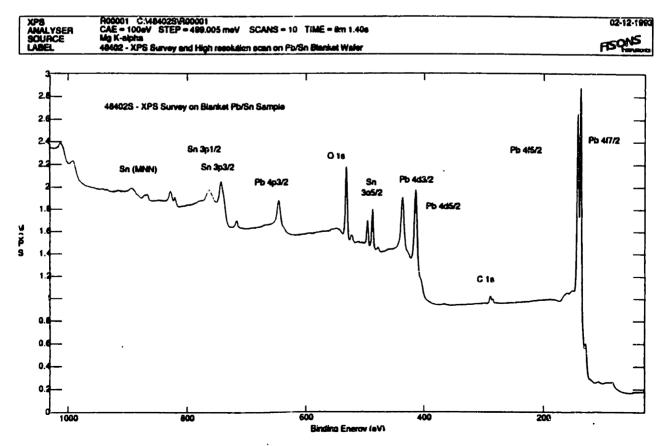

XPS and AES were performed on Pb/Sn solder bumps before and after BLM etch. From the Auger Analysis data, the percentage of each element in the layer was calculated to determine the dominant compound in the layer. For XPS analysis, since the spot size of XPS was larger than the bump size, a blanket wafer plated with Pb/Sn was used. The blanket wafer was agitated in an etch bath at elevated temperature for 10 minutes. The wafer was cleaved to scan across the layer using XPS.

## 3.2. Gravimetric Test of Pb Compounds

Solubility testing was used to verify the results. Solubility of different compounds was studied by dissolving them in the cleaning acid. First, each beaker was filled with 120ml of diluted 10% acid and the initial pH of the solution was measured using a pH meter. Then samples of 100% PbO, 97.4% PbO<sub>2</sub>, 96.6% Pb<sub>3</sub>O<sub>4</sub>, 100% PbSO<sub>4</sub> and 99.9% SnO (manufactured from Baker Analysis and Mallinckrodt) were weighed and were dissolved in separate beakers. Agitation was provided with a stirring bar, and the reaction temperature and the change in color of the solution were recorded. After the solution was agitated for approximately five minutes, the solution was filtered using a funnel. The precipitant on the filter paper was dried in an oven. Then the final mass left on the filter paper was weighed and the solubility was calculated using this data. The final pH of the solution that was filtered through the paper was measured and recorded. Also, diluted 10% acid was buffered to a different pH to study the solubility of

Pb compounds in the acid. Those pH and solubility results were compared to the data given in the published Pourbaix diagram.

#### 3.3. BLM Layer Etch Rate Study

To measure the etch rate of BLM layer in a lateral direction, a high sulfuric concentration of BLM etch bath was prepared at an elevated temperature in the 8 gallon bath. The dice were agitated in the bath for times ranging from 30 seconds to 5 minutes. A precision cross section of the corner of each die with different time intervals was performed through the middle of the bump to view the overetch of the BLM layer using SEM. This measured the undercut of the BLM layer underneath the bumps.

To obtain the etch rate in the vertical direction, blanket BLM layer deposited wafers were used. The wafers were premeasured on a RS55/tc Omnimap which is a device to measure the thickness of the wafer, to obtain initial thickness. The thickness of the blanket wafers were approximately 8000A. Then each wafer was agitated in the same bath as above for times ranging from 5 seconds to 2 minutes. The final thickness was measured using the Omnimap. The difference between initial and final thicknesses was calculated. A graph was constructed to show the difference between the initial and the final thickness as a function of time.

# **CHAPTER 4. RESULTS AND DISCUSSION**

### 4.1. Thickness Morphology and Composition of the Surface Layer of Solder Bumps

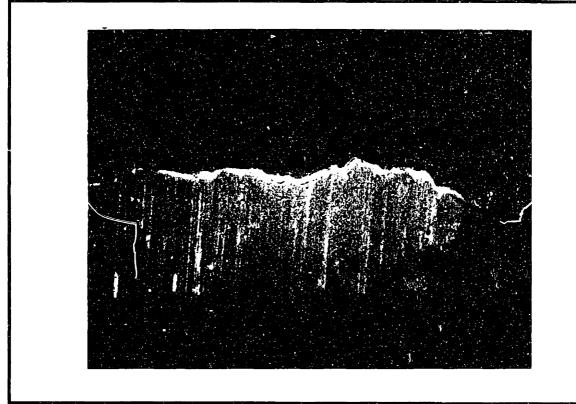

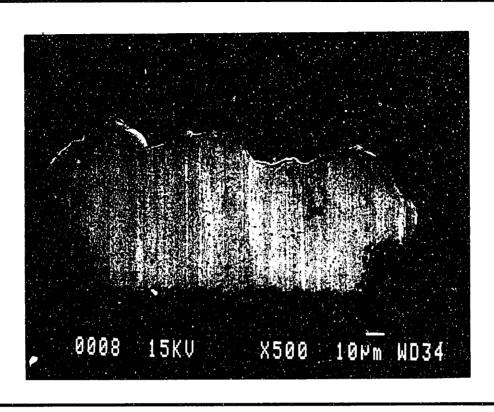

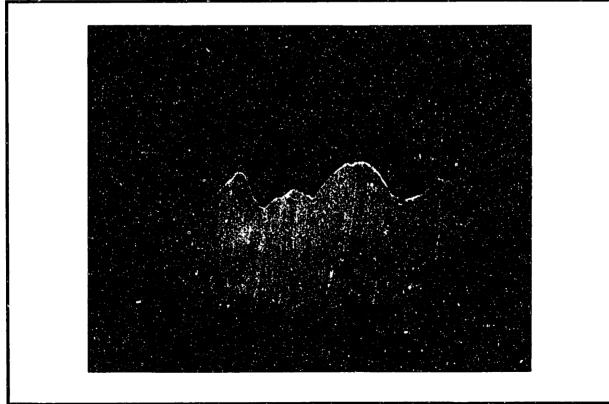

Precision SEM cross-sections were performed extensively to identify the thickness and morphology of the surface layer on Pb/Sn solder bumps. It was found that the morphology of the layer is critically dependent on the etchant concentration. H<sub>2</sub>O<sub>2</sub>-rich solutions caused a very thin and dense surface layer as shown in Figures 4.1 and 4.2. However, as the concentration of H<sub>2</sub>O<sub>2</sub> relative to H<sub>2</sub>SO<sub>4</sub> increased, the layer appeared to be more loosely packed and thicker as shown in Figures 4.3 and 4.4. The morphology was independent of the etch time although the thickness increased with time.

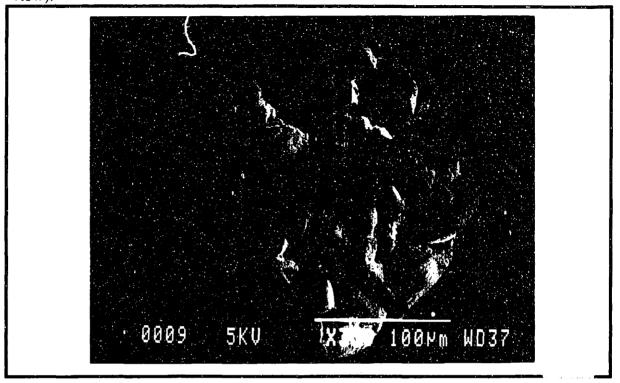

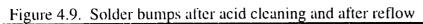

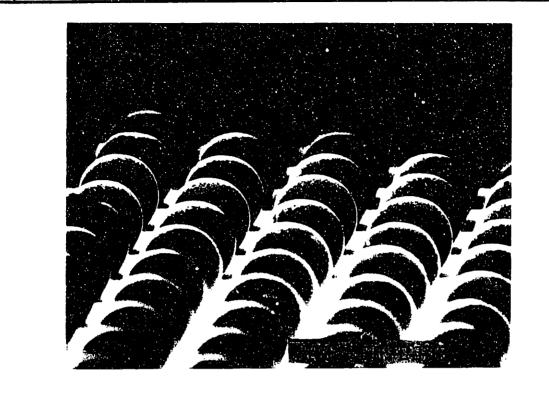

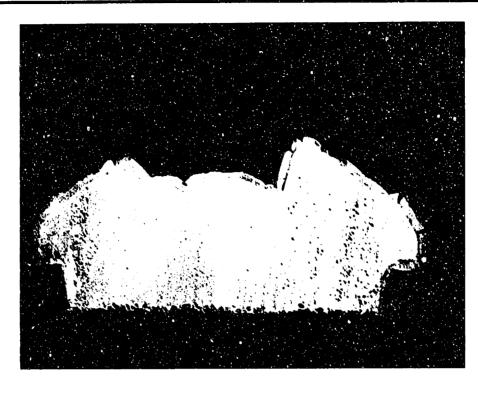

Auger Analysis was performed on the bumps that were dipped in the H<sub>2</sub>O<sub>2</sub>-rich solution of the BLM etch bath at an elevated temperature for 3 min and were reflowed in the furnace after they were cleaned with acid. SEM pictures of bumps are shown sequentially before dipping in the etch bath, after dipping in the bath, and after acid cleaning and reflow (see Figures 4.5-4.10). The composition of the surface of Pb/Sn bumps was obtained from the Auger analysis and is shown in Table 4.1. From this table, several observations can be made: Upon the exposure to the BLM etchant, S, Sn, Pb and O were found. The percentage of Pb increased after acid cleaning. This indicates that as the surface of the bump was cleaned with acid and reflowed, Pb was exposed. The level of Sn decreased after acid cleaning and reflow. During reflow, Sn formed an intermetallic layer with the BLM layer.

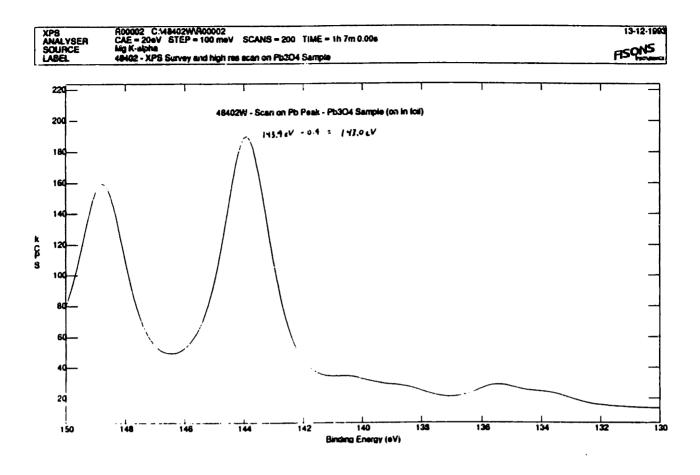

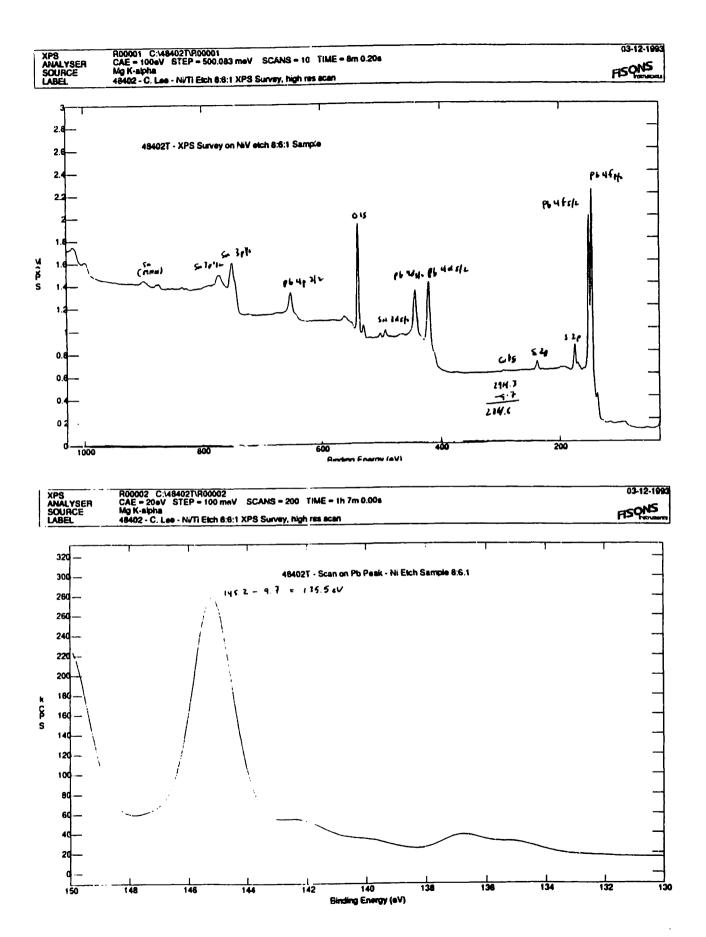

To find out about the bonding states of compounds, XPS was performed on the Pb/Sn plated blanket wafer with the same conditions as with the AES analysis. The limitation with XPS is that the difference in binding energy between Pb<sup>2+</sup> and Pb<sup>4+</sup> is less than 1eV. In addition, the charging effect causes peak shifts which make it harder to distinguish which peak the surface layer corresponds to (Tables for binding energy of

Table 4.1. Percentage composition of surface analysis using AES

| Element/      | Before BLM etch | After BLM etch | After acid cleaning |

|---------------|-----------------|----------------|---------------------|

| % Composition | (%)             | (%)            | and reflow (%)      |

| Pb            | 38.50           | 40.20          | 54.50               |

| Sn            | 15.80           | 3.01           | 8.47                |

| s             | 15.20           | 17.20          | 17.60               |

| o             | 17.00           | 27.60          | 19.39               |

| С             | 13.40           | 12.00          | 0.04                |

Pb compounds are listed in Appendix I). Samples of pure PbO, PbO<sub>2</sub> and Pb<sub>3</sub>O<sub>4</sub> were used to standardize and calibrate the peak of each compound for accuracy. These XPS results are shown in Appendix II. The binding energy peak on the surface layer produced with the 86% H<sub>2</sub>SO<sub>4</sub> etchant bath was close to the binding energy peak for PbO<sub>2</sub>. Moreover, the atomic concentrations (%) of each element, before and after agitating in an etchant bath, are shown in Table 4.2. These quantitative XPS results were obtained using Wagner Empirical Sensitivity Factors [Handbook of X ray photoelectron spectroscopy] and the curve-fitting area under the XPS data. From these results, the concentration of S on the surface of the bumps after dipping in the BLM etch bath seemed high. Also, the percentage of S on the surface of the bumps increased by 10% after high sulfuric concentration bath exposure compared to the percentage of S after low sulfuric concentration. The percentage of S could be the reason for the difference in morphology of the surface layer. Based on free energy of formation tables shown in Appendix III, PbSO<sub>4</sub> is more stable than any other Pb oxide compounds.

Figure 4.1. The surface of Pb/Sn solder bumps after high sulfuric concentration bath (top view).

Figure 4.2. The surface of Pb/Sn solder bumps after same condition as Figure 4.1.

Figure 4.3. The surface of Pb/Sn solder bumps after low sulfuric concentration bath.

Figure 4.4. 2000X magnification

Figure 4.8. Solder bumps after BLM etch

Figure 4.10. Solder bumps after acid cleaning and after reflow

The concentration of sulfur was found to be higher at the top of the surface layer (Figure 4.11). Therefore, this scan showed that if the sulfur-compound is present in the

Table 4.2.

| sample / % Composition           | Pb   | С    | S    | 0    | Sn  |

|----------------------------------|------|------|------|------|-----|

| Pb/Sn bumps before BLM etch bath |      | 20.6 | 0    | 47.9 | 3.4 |

| Pb/Sn bumps after BLM etch bath  | 19.4 | 2.3  | 28.9 | 49.2 | 0.2 |

surface layer, it is most likely to be on the top of the layer.

According to the XPS results, the binding energy peak for the sample was determined to be 135.5 eV and the energy peak for PbO<sub>2</sub> is 136.3 eV, for PbO is 142.4 eV and for Pb<sub>3</sub>O<sub>4</sub> is 143.0 eV. Therefore, the peak that is the closest to the peak of the sample is PbO<sub>2</sub> although the peak value is not within the given range as determined from the National Institute of Standards and Technology (NIST) data. The charging effect is the major reason for peak shifts and inaccuracies of peak values. The charging

Table 4.3

| Compounds         | Binding Energy (eV) |  |

|-------------------|---------------------|--|

| Pb                | 136.4 -136.9        |  |

| PbO               | 137.7-138.2         |  |

| PbO <sub>2</sub>  | 136.8-137.6         |  |

| PbSO <sub>3</sub> | 138.6               |  |

| PbSO <sub>4</sub> | 139.4-139.5         |  |

effects and peak shifts are calibrated by the binding energy peak for C. The C peak is relatively high on these XPS results as shown in APPENDIX II. Moreover, the presence

of large quantities of C indicates that a lot of organic residues were left on the surface of Pb/Sn bumps. These residues might have originated from the Pb/Sn plating solution itself since the plating solution is based on a carbon compound. The XPS results indicate that the surface layer is most likely PbO<sub>2</sub>, and the calculation of atomic concentration from percentages of 1Pb to 2O or 2Pb to 5O are shown in Table 4.2, also indicates that the layer is most likely PbO<sub>2</sub> or Pb<sub>2</sub>O<sub>5</sub>. However, the accuracy of this data is doubtful because of the charging effects and peak shifts in Bonding Energy peaks. Peak shifts occur due to charging and due to experimental environments. By looking at graphs of standardized peaks for Pb compounds, the C peak was found to be shifted more than 1 eV. So, the small binding energy peak difference between Pb<sup>2+</sup> and Pb<sup>4+</sup> makes it hard to distinguish between these peaks. Second, peaks between Pb compounds overlap to a certain extent according to the NIST data as shown in Table 3.4. A gravimetric test was then performed to verify these results.

#### 4.2 Gravimetric Test

The Pourbaix diagram for Pb in the literature (figure 4.11) indicated that there are different regimes for Pb oxides, depending on the pH and the electrode potential of the solution. A gravimetric test was performed to identify the surface layer and also to confirm the XPS results. With a detection limit of 0.1 g/l, this gravimetric test was performed by dissolving several chemicals, such as PbO, PbO2, PbSO4, Pb3O4 and SnO, in the diluted 10% acid which removed the surface layer for reflow. The pH of the acid before dissolving any oxide was approximately -0.53. As a result, no chemical except PbO seemed to be soluble in the acid. Table 4.4 indicates pH before and after these Pb compounds were dissolved in the acid. From this table, PbO showed dramatic pH change whereas the other compounds showed slight pH changes. This indicates that only PbO reacted with the acid, whereas the other Pb compounds did not. These observations were also consistent with visual inspection. Pb compounds, except PbO, just remained in the bottom of the beaker giving a clear liquid on the top and the reaction temperature did not change. However, PbO showed very high solubility. When orange powder-PbO was put in 120ml diluted acid, bubbles were formed initially and the colors turned to light yellow. Moreover, the temperature increased to 45°C, indicating an exothermic reaction. When the solution was filtered, the solubility was approximately 405.6 g/l which is 1.82M. After the solution saturated, the pH was about 6.03 whereas the initial pH of the solution without PbO was -0.53. The pH and concentration for PbO in the acid matches with those in a Pourbaix Diagram for Pb compounds (Figure 4.12). In the PbO region, 1 M solution of PbO is in the aqueous state with pH close to 6.5. This figure closely matches with the experimental values which are 1.82M of PbO with a final pH of 6.03. Moreover, the graph indicates a decrease in concentration of dissolved PbO as the final To demonstrate whether this is consistent with the pH becomes greater than 6.5. experimental values or not, the acid solution was buffered to an initial pH of 13.0.

Figure 4.12. The trend of solubility of PbO in the Pourbaix Diagram for Pb Compounds

[source: Atlas of Electrochemical Equilibria in Aqueous Solutions, 1974, pp. 489]

Table 4.4.

| compounds / pH                 | Initial pH (pH of 10% acid) | Final pH(after Pb compounds were dissolved) |

|--------------------------------|-----------------------------|---------------------------------------------|

| PbO                            | -0.53                       | 6.03                                        |

| PbO <sub>2</sub>               | -0.53                       | -0.39                                       |

| PbSO <sub>4</sub>              | -0.53                       | -0.28                                       |

| Pb <sub>3</sub> O <sub>4</sub> | -0.54                       | -0.28                                       |

| SnO                            | -0.53                       | -0.56                                       |

The Solution showed very small solubility of PbO in the acid with pH of 13.0 that it was very hard to weigh the difference using filter paper. At final pH of 6.67 at saturated solution, the solubility of PbO showed about 0.032M. This result is consistent with the Pourbaix diagram in that the order of magnitude change in concentration of PbO resulted as the pH increased. As the final pH is less than 6.50, there is an increase in solubility. The 50% concentrated acid was prepared to observe the solubility of PbO in the acid with initial pH of less than -0.53. This reaction gave off heat, increasing the temperature to 75 °C. PbO consumed acid, resulting in white blocks of crystals. The solubility seemed to be high but the solution was very dense during filtering through the funnel. The solubility of PbO in the acid with an initial pH of -1.02 was about 747.5 g/l or 3.35M at the saturated level. The trend of solubility is shown with an arrow in the Pourbaix diagram (Figure 4.12): The solubility of PbO is the highest at a pH of -1 and the solubility decreases gradually at other pHs. Therefore, the bulk gravimetric test indicates that the surface layer of Pb/Sn solder bumps is composed of PbO, having a solubility of 3.35M at a final pH of -1.02 at saturated level and the solubility of PbO is favorable till the final

pH reaches 6.03 with a saturated concentration of 1.82M. Solubility of PbO with different pH is summarized in Table 4.5.

From the table 4.4, PbSO<sub>4</sub> was not soluble and this result matches with the XPS analysis result; therefore, this solubility test confirms the absence or a very small concentration of PbSO<sub>4</sub> in the surface layer. The identification of the surface layer contrasts with the results from XPS in that PbO is the probable surface layer instead of PbO<sub>2</sub>. Because of several limitations and inaccuracies that XPS has in view of the

Table 4.5.

| Initial pH | Final pH | Conc. (M) | Observation                                  |

|------------|----------|-----------|----------------------------------------------|

| -1.02      | -1.02    | 3.35M     | 50% concentrated acid, white dense crystals  |

|            |          |           | formed and the temp. was 75 <sup>0</sup> C.  |

| -0.53      | 6.03     | 1.82M     | Solution turned to ivory yellowish color and |

| <u>.</u>   | ļ        |           | the temp. increased to 47 °C (10% acid).     |

| 0.77       | 6.66     | 0.032M    | Solution turned to white color with reaction |

|            |          |           | temperature of 55 °C (10% acid).             |

| 1.06       | 9.87     | 0         | PbO did not dissolve in the acid,            |

|            |          |           | maintaining its orange color at room         |

|            |          |           | temperature (10% acid).                      |

| 13.10      | 13.24    | 0         | same as above except that the color of PbO   |

|            |          |           | was heavy orange (10% acid).                 |

apparent solubility of PbO in acid, a bulk solubility test appears to be more accurate than the spectroscopic analysis. Therefore, S, Sn containing PbO, is believed to be the layer that has formed on solder bumps by reacting with H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub>.

### 4.3. Reaction Mechanism for Surface layer growth studies of Solder Bumps

To study surface layer growth with the concentration effects of H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub>, concentration of H<sub>2</sub>O<sub>2</sub> was varied with a constant ratio of H<sub>2</sub>O and H<sub>2</sub>SO<sub>4</sub>. The etch time was four minutes for each set of experiments. The thickness of the surface layer was measured by taking a cross section of the die (The result is shown in Figure 4.15). As shown in figure 4.13, as the concentration of H<sub>2</sub>O<sub>2</sub> increased, the surface layer thickness increased dramatically, proportional to the concentration level of H<sub>2</sub>O<sub>2</sub>. In the low concentration of H<sub>2</sub>O<sub>2</sub>, up to 35% of H<sub>2</sub>O<sub>2</sub> solution bath, the surface layer growth rate did not increase as fast as it did in the 35% or higher concentrations of H<sub>2</sub>O<sub>2</sub>. In the regions of 0 to 35% H<sub>2</sub>O<sub>2</sub> solution, 65-100 % H<sub>2</sub>SO<sub>4</sub> concentration is present. In that region, the thickness of the surface oxide layer was thin (less than 5 um). In the region of more than 35% H<sub>2</sub>O<sub>2</sub>, the growth of the layer grew at a faster rate, resulting in a very loose layer of up to 45 um as shown in Figure 4.15. These regions are not favorable although BLM gets etched fast. It is difficult to remove those thick oxide layers and a dramatic volume loss in bumps resulted. The rapid growth of the layers consumes the bump height by oxidation, and a faster growth rate of the surface layer will eventually result in uneven bump height which is not favorable from a processing point of view. Since this region forms loose layers where there is no sulfate layer on the top to prevent the layer from growing fast, the reaction rate is a lot slower than the diffusion rate. Therefore, the reaction rate is controlling the growth rate. At 100% H<sub>2</sub>O<sub>2</sub>, the surface layer thicknesss reached its peak at 50 um. As shown in the SEM picture (Figure 4.16), the layers are not noticeable because the layers remain loose and slough off when no H<sub>2</sub>SO<sub>4</sub> is present. Many layers got washed away during rinsing, resulting in a 50 um bump height reduction. Moreover, pure H<sub>2</sub>O<sub>2</sub> did not etch the BLM layers at all. Therefore, rich concentrations of H<sub>2</sub>SO<sub>4</sub> prevent a fast growth rate of surface layer formation and promote a BLM etch. From figure 4.13, at 95% of H<sub>2</sub>O<sub>2</sub>, the thickness of the layer dropped about 5 um, resulting in a drop in the bump height.

At that very high concentrated H<sub>2</sub>O<sub>2</sub> solution, the resulting thickness is very flaky and uneven, and it is difficult to measure accurate thicknesses of layers. An accurate thickness of the layers would be about 5 um higher. The right proportion of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> is necessary to etch a BLM layer completely around the bump and to form a thin surface layer at the same time.

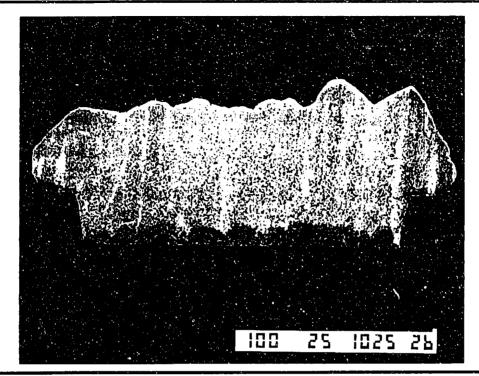

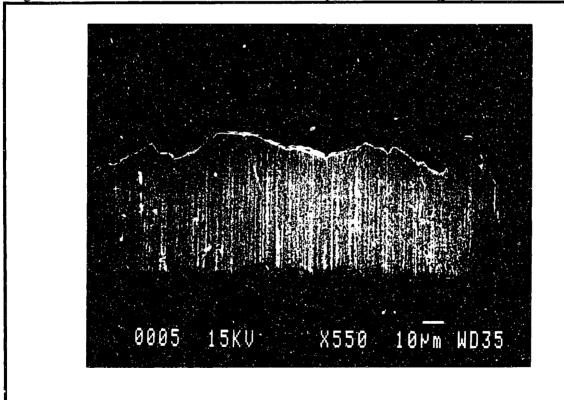

The previous studies in this paper showed the effect of concentration variation in H<sub>2</sub>O<sub>2</sub> by keeping the other ratios constant. The effect of concentration variation in H<sub>2</sub>SO<sub>4</sub> by keeping the other ratios constant was studied to further investigate the impact of H<sub>2</sub>SO<sub>4</sub> on surface layer growth. The exact conditions as described above was applied in these experiments. SEM pictures for cross sections at different concentrations are shown in Figures 4.17-4.24. Keeping these ratios constant, only the ratio of H<sub>2</sub>SO<sub>4</sub> varied with respect to the other two components. As shown in that figure (4.14), concentrations of 0-30 % H<sub>2</sub>SO<sub>4</sub> showed a dramatic decreasing trend in the thickness of the surface layer, resulting in a final thickness of 5 um at 30% H<sub>2</sub>SO<sub>4</sub> from the initial At 0% H<sub>2</sub>SO<sub>4</sub>, only oxidation of Pb/Sn solder bumps takes thickness being 45 um. As the percentage of H<sub>2</sub>SO<sub>4</sub> increased, the thickness of the surface layer decreased dramatically until the concentration of H<sub>2</sub>SO<sub>4</sub> reached around 35%. Then, the thickness of the layer seems to stabilize at an average of about 5um. Therefore, H<sub>2</sub>SO<sub>4</sub> plays a signicant role in making layers denser or thinner. Up to 35% of H<sub>2</sub>SO<sub>4</sub> concentration, the growth rate of the surface layer of the solder bumps are rapid through the diffusion of the BLM etchant. This rapid growth is limited by the reaction rate where the thickness growth is proportional to the time. However, more than 30% of the H<sub>2</sub>SO<sub>4</sub> concentration results in very low thickness of the surface layer, showing no dramatic change in thickness of layers. In that region, because the diffusion rate is the ratedetermining step, the growth of the layer is slow. The overall thickness of the surface layer after 35 % H<sub>2</sub>SO<sub>4</sub> concentration was approximately 5 um. The thickness difference between 30% and 100% H<sub>2</sub>SO<sub>4</sub> was less than 3 um as shown in Figure 4.26.

Figure 4.15. Cross section of Pb/Sn solder bumps after 90% H<sub>2</sub>O<sub>2</sub> bath (4 min etch)

Figure 4.16. Cross section of Pb/Sn solder bumps after 100% H<sub>2</sub>O<sub>2</sub> bath (4 min etch).

Figure 4.17. Cross section of Pb/Sn solder bumps after 100 % H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.18. Cross section of Pb/Sn solder bumps after 33% H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.19. Cross section of Pb/Sn solder bumps after 50% H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.20. Cross section of Pb/Sn solder bumps after 66% H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.21. Cross section of Pb/Sn solder bumps after 80% II<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.22. Cross section of Pb/Sn solder bumps after 86% H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.23. Cross section of Pb/Sn solder bumps after 91% H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

Figure 4.24. Cross section of Pb/Sn solder bumps after 100% H<sub>2</sub>SO<sub>4</sub> bath (4 min. etch)

At 35% concentration of H2SO4, the layer decreased from 5 um, eventually going down to 1 um at 100% H<sub>2</sub>SO<sub>4</sub>. From these studies, having a large percentage of H<sub>2</sub>SO<sub>4</sub> in solution will result in a zero order reaction where the thickness of the surface layer is less than 5 um. Also, having a thin layer will make it easier for the acid to remove so that these Pb/Sn bumps can be reflowed.

A combination of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> with high concentration of H<sub>2</sub>SO<sub>4</sub> is necessary, not only for the thin surface layer, but also for a fast BLM etch. Using these two figures, an optimal BLM etch solution concentration can be determined. 86% H<sub>2</sub>SO<sub>4</sub> region is the optimal etch concentration, where the BLM is completely etched around bumps after 4 minutes and the surface layer is about 1 um thick. At 86% sulfuric acid, the reaction of surface layer growth is limited by the diffusion rate, resulting in slow growth of the layer. Therefore, this concentration study suggests the optimal etch concentration.

In H<sub>2</sub>O<sub>2</sub>-rich solution, the surface layer of Pb/Sn bumps appeared to be loose and thick. Also, it was found that the surface layer grew linearly with time as shown in Figure 4.25. The growth rate of the surface layer was approximately 1.1 um/min. Since the growth rate of the layer is linearly proportional to time, this etch reaction is reaction-rate limited instead of diffusion-rate limited. Since the layer is loose and flaky, the etchant is diffusing quickly through the layer, promoting the growth of the layer. The concentration studies from figures 4.13 and 4.14, demonstrate this result. The reaction rate is the rate-determining step.

In sulfuric acid rich solutions, the morphology of the surface layer seemed to be dense and thin. It was found that the surface layer grew linearly with the square root of time as shown in Figure 4.26. Since the layer is dense and thin, this surface layer is preventing the etchants from diffusing through the layer quickly; so the layer growth is slow. This surface growth is diffusion-rate limited. From the results obtained, S seems to be the reason for the differences in thickness morphology and reaction mechanism.

Moreover, the increase in percentage of S in the surface layer (Table 4.2) in the sulfuricrich solution according to AES scan, suggests S being the source of these differences. Free energy tables (Appendix III) show PbSO<sub>4</sub> being stable over any other Pb oxide compounds, which also supports the impact of S on the surface layer. However, the gravimetric test showed that PbSO<sub>4</sub> is not soluble in the cleaning acid. Therefore, the surface layer is some type of sulfate compound where the most of the sulface layer is made of lead oxide with a very small percentage of non-uniform sulfate layer on the top of the bumps. Although the sulfate layer is not primarily taking part in the stoichiometry of the compound, the thickness and the density of the surface layer is controlled by the very small concentration of sulfate layer on the top of the bumps. Based on these results, the following reaction for the surface layer growth on the Pb/Sn solder bumps was proposed:

$$Pb + H_2O_2 \rightarrow PbO + H_2O$$

$PbO + H_2SO_4 \rightarrow Pb_xS_yO_z + O_2$

#### 4.4. BLM Layer Etch Rate Studies

So far, we have studied surface composition analysis of solder bumps in a BLM etch bath. To answer the question how fast are H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> etching the BLM layer, etch rates of BLM layer in a lateral and vertical direction was determined. It was found from the concentration variation studies that the 86% H<sub>2</sub>SO<sub>4</sub> etch bath creates a thin surface layer on Pb/Sn bumps and etches the BLM layer at a fast rate. During the time it takes to create a layer on Pb/Sn solder bumps, the BLM layer surrounding the bumps is etched off completely. To study the etch rate of the BLM layer in a lateral direction (Figure 4.27), a cross section of bumps, through the center of the bump, was studied using the SEM (Figure 4.28 and 4.29). The condition for the etch bath is 86% H<sub>2</sub>SO<sub>4</sub> with varying time. Since this etch reaction is isotropic, the etch rate in a vertical

Figure 4.29. The undercut of BLM layer after 86% H<sub>2</sub>SO<sub>4</sub> for 3 min.