## Digital Self-Calibration Techniques for High-Accuracy, High-Speed Analog-to-Digital Converters

bу

#### Andrew Nicholas Karanicolas

Bachelor of Science Electrical Engineering and Computer Science Massachusetts Institute of Technology (1987)

Master of Science Electrical Engineering and Computer Science Massachusetts Institute of Technology (1990)

Submitted to the Department of Electrical Engineering and Computer Science In Partial Fulfillment of the Requirements For the Degree of

Doctor of Philosophy

at the

Massachusetts Institute of Technology

February 1994

©Massachusetts Institute of Technology

All Rights Reserved

| Signature of Author | <u> </u>                                                  |

|---------------------|-----------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science |

|                     | 16 February 1994                                          |

| Certified By        |                                                           |

|                     | Hae-Seung Lee                                             |

|                     | Professor of Electrical Engineering and Computer Science  |

|                     | Thesis Supervisor                                         |

| Accepted By         |                                                           |

|                     | Frederic R. Morgenthaler                                  |

|                     | Chairman, Department Committee on Graduate Students       |

ARCHIVES

MASSACHUSETTS INSTITUTE

OF TECHNICIONS

JUL 13 1994

## Digital Self-Calibration Techniques for High-Accuracy, High-Speed Analog-to-Digital Converters

bу

#### Andrew Nicholas Karanicolas

Submitted to the

Department of Fiectrical Engineering and Computer Science

on 16 February 1994 in partial fulfillment of the requirements

for the Degree of Doctor of Philosophy

### **Abstract**

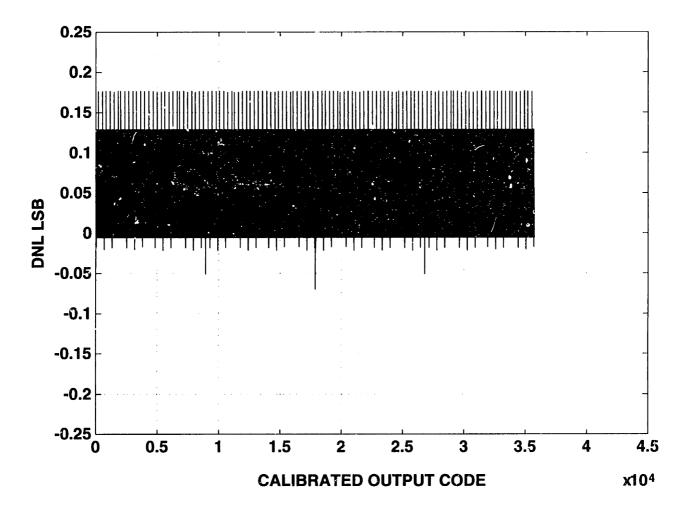

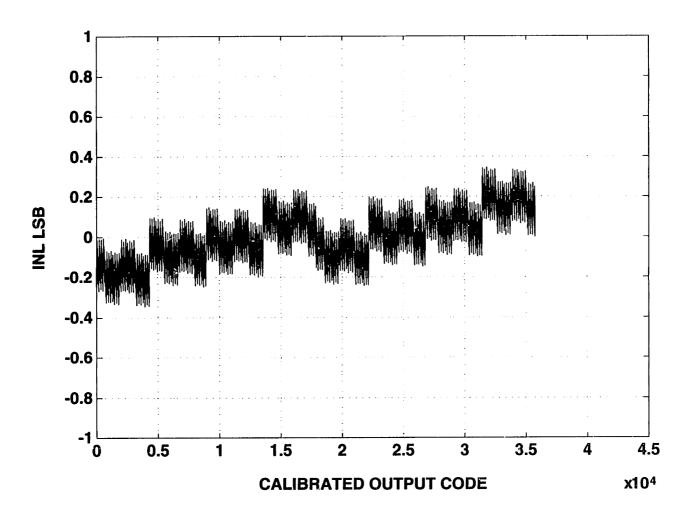

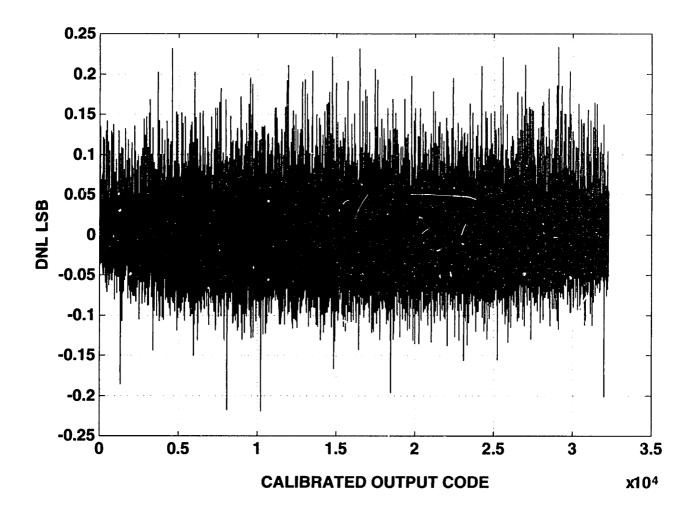

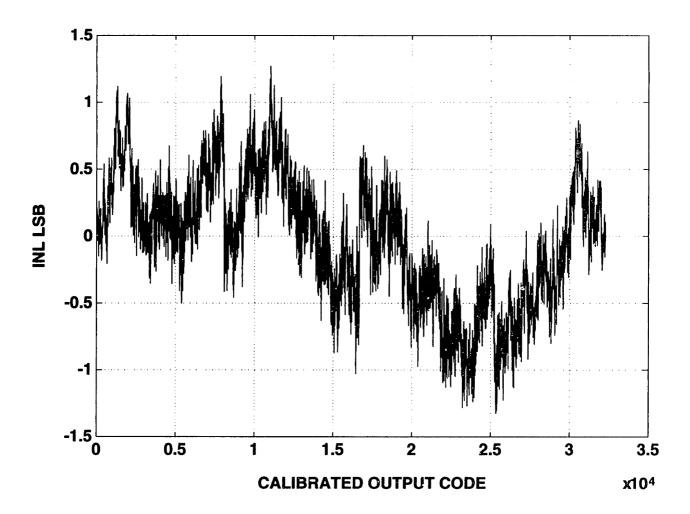

This thesis presents digital self-calibration techniques for high-accuracy, high-speed Analogto-Digital Converters (ADCs). The digital self-calibration addresses the traditional limitations to pipeline ADCs implemented in monolithic IC processes. The digital self-calibration reported here automatically accounts for capacitor mismatch, capacitor nonlinearity leading to Differential Nonlinearity (DNL), charge injection, finite op-amp gain and comparator offset. The errors are directly measured under the same conditions as during the run mode. Thus, DNL is not contributed by circuit nonlinearity. No external reference data converters are needed in the technique and no high-precision matched components are required. Since the calibration algorithm is all digital, no extra analog hardware is required for the calibration mode or the run mode. The digital self-calibration can attain 15-bits of linearity with component matching no better than 7-bits. The digital self-calibration performs a simple calibration algorithm in the digital domain alone. As a result of the algorithm simplicity, no multipliers, microprocessors or other complex arithmetic systems are required. The digital calibration presented here may be applied to pipeline or cyclic ADC architectures employing a 1-bit-per-stage or multi-bit-per-stage design. An important advantage of a pipeline architecture is that it exhibits linear hardware growth, as a function of resolution, compared to exponential hardware growth for flash ADC architectures. Successive approximation and delta-sigma oversampled ADCs have lower throughput than a pipeline ADC because of an increased number of clock cycles needed for conversion. Additionally, pipeline ADCs can acquire Sample-and-Hold Amplifier (SHA) data or multiplexed SHA data, unlike deltasigma oversampled ADCs. A 15-bit 1 MS/s switched-capacitor pipeline ADC prototype is investigated. The 1-bit-per-stage, radix 1.93 design incorporates digital self-calibration. Total Harmonic Distortion (THD) was measured as -90 dB up to a 100 kHz sine-wave input frequency at a 1 MS/s sampling rate. Maximum DNL of  $\pm 0.25$  LSB at 15-bits and maximum Integral Nonlinearity (INL) of  $\pm 1.25$  LSB at 15-bits were measured at 1 MS/s. The chip was fabricated in an 11 V, 4 GHz, 2.4  $\mu$ m BiCMOS process.

Thesis Supervisor: Prof. Hae-Seung Lee

Title: Professor of Electrical Engineering and Computer Science

## Acknowledgements

Upon reaching the destination of a fantastic journey, I would like to thank the incredibly diverse set of people who have been part of my endeavors at M.I.T. Having shared with them in the intense, cooperative and ultimately rewarding experiences at M.I.T. has taught all of us how to excel. Having helped each other through some difficult times has taught all of us how to accept each other and enjoy the wonderful times.

First, I want extend thanks to my thesis advisor, Prof. Hae-Seung Lee. His technical contributions have been invaluable in this work and it has been greatly rewarding to be part of his outstanding team in the Microsystems Technology Laboratory. His belief in me, and in my project, was instrumental to sustaining my drive in this project. It was an immense pleasure to have shared with him the excitement from the success of this work.

I am tremendously grateful to my thesis readers. Prof. Charles Sodini provided me important feedback during the evolution of my doctoral thesis. His advice in practical matters is greatly appreciated. As a teacher, and a professional role model, Prof. James Roberge was instrumental in my decision to pursue a doctoral thesis in the field of analog circuits.

There are many people at Harris Semiconductor who played a key role in the implementation of the chip in this work. Kanti Bacrania provided me the opportunity to design and layout the chip at Harris. His commitment to having the chips fabricated at Harris is greatly appreciated. Greg Fisher was helpful in explaining many aspects of the Fastrack design system. Thanks go to Akira Ito, who responded to my almost endless stream of process related questions. Mark Snowden was helpful in keeping the computer systems up and running. Thanks go to Deborah Michaud for helping me get Versatec plots. Jeanne Santell provided good conversation during her rounds as night watchman in the many early morning hours in Bldg. E11. Thanks also go to Dale Edwards for helping provide a great intern program at Harris.

Many people at Analog Devices were very helpful, and friendly, in arranging access to the P-CAD PCB layout tools. In particular, thanks go to Dave Robertson for providing me initial direction among the various PCB approaches. Peter Casparius was helpful, and patient, in explaining how to use the many features of the system necessary to complete the PCB. Thanks go to Stacy Ho and Hassan Malik for fun conversation. Additional thanks to Stacy for rides to Analog Devices on many cold, wet New England mornings. Mick Mueck was helpful in providing feedback on the PCB layout. I am grateful to Chris Mangelsdorf for informative conversations about ADCs and Analog Devices.

The students at MTL provided a great atmosphere to work in and were a lot of fun to be around. The many discussions with Kenneth O and Merit Hong spanned just about every topic possible. Many thanks go to Joe Lutsky, Shujaat Nadeem, Steve Decker and Jen Lloyd for the fun times. Additional thanks to Joe Lutsky for giving me rides home during terrible weather. Special thanks to Kathleen Early for sharing the TA experience and for being a fantastic friend. I enjoyed many conversations with Barry Thompson about audio, business and west coast life. Thanks go to David Martin and Paul Yu for interesting

conversations on a myriad of topics. Joe Kung and Chris Eugster provided a source of many colorful arguments about academics, business and music. Special thanks to Fritz Herrmann and Jeff Gealow for their outstanding computer expertise. Their efforts have been central to keeping our computers in both Harry's and Charlie's group up and running. Ken Szajda has been an interesting source of technical discussions, has provided a wide variance of humor and has been a great guy to talk to from the very beginning in this long path at M.I.T. John Bulzacchelli helped with his grasp on electrical engineering, and his patience in explaining some of it to me, as well as being a great friend. Special thanks to Tom Lee for many great conversations about technical matters and life, for great times as TAs up in the 5th floor lab of Bldg. 38 and for his excellence in teaching me about analog circuits. Many thanks to Craig Keast, and his wife Barbara, for providing a western outpost for many of my century bike rides that passed through Groton, Massachusetts, and to their Basset Hound, Burt, who no longer attacks me.

I want to thank Prof. Art Smith, Dean of Student Affairs, for giving me advice about a wide variety of issues that arise throughout a graduate student's life at M.I.T. Many thanks are due to Marilyn Pierce, Monica Bell, Alice Twohig and Lisa Bella in the EECS Graduate Administration offices who were always pleasant when asked a myriad of administrative questions. Special thanks go to Marilyn Pierce who was especially patient in explaining administrative deadlines, even when I forgot about them. Many thanks to Beth McDonald for always being cheerful to talk to. Special thanks to Kate Paterson for her excellent work in handling the SRC reviews.

Finally, I want to express my gratitude to some friends from my undergraduate years that I still stay in contact with at M.I.T. and across the U.S.A. Ivan Deutsch has been a great friend throughout my stay at M.I.T. and I thank him for listening to me when I was down, always remembering my birthday and being a lot of fun to do stuff with. Isako Hoshino has provided great conversation about everything possible and has been a lot of fun to be with. I would like to thank Bradford Tropea for an infinite source of great conversation and good times going all the way back to Atlantic City High School days. Many thanks to Anand Mehta for discussing the glories and trials of being undergraduate and graduate students at M.I.T. and for lots of good times, pizza and rides to movies. Last, but not least, special thanks go to George Xixis, Ken Ishii, Sheryl Shanks, Steve Rohall, Meilin Wong (Teela), John Rochlis, Chun The, Annette Leonard (Nemesis), Amy Lee, Carla Fermann (I'm Not Loud!), Paul Watts (Photon), Livia Jacunski, Karen Fu, Bill Gimbel and Andy Berlin.

This research was supported by the Semiconductor Research Corporation (91-SP-080) and by General Electric and Analog Devices. The prototype pipeline ADC was fabricated by Harris Semiconductor. MOSIS provided fabrication for the PCB used in the ADC evaluation. Some of the computer simulations were performed using the CRAY XMP resources at the M.I.T. Supercomputer Facility.

## **Dedication**

This work would not have been possible without the continuous love and support from my parents, Nicholas and Zoi Karanicolas, and from my sister, Anna Maria. Their hard work and devotion are the source of my inspiration. I owe all of my success to them.

## **Biography**

Andrew N. Karanicolas was born in Philadelphia, Pennsylvania, on July 28, 1965. He attended George Washington High School from 1979-1980 in Philadelphia. Upon moving to Atlantic City, New Jersey, he attended Atlantic City High School from 1980-1983. He received the S.B. degree from the Dept. of Electrical Engineering and Computer Science from the Massachusetts Institute of Technology, Cambridge, Massachusetts, in June 1987. The S.B. thesis was titled Feedback Control of Plasma Radius in the Versator Tokamak. From September 1987 to June 1988, he was a Teaching Assistant in the Dept. of EECS at M.I.T. for the undergraduate classes Electronic Devices and Circuits and Signals and Sustems. From June 1988 until February 1994, he has been a Research Assistant at the M.I.T. Microsystems Technology Laboratory under the direction of Prof. Hae-Seung Lee. He received the S.M. degree from the Dept. of EECS in September 1990. The S.M. thesis was titled A Switched-Capacitor Pipelined BiCMOS Analog-to-Digital Converter. He was a research intern at Harris Semiconductor, Melbourne, Florida, from July 1991 to December 1991. His present research interests include high-performance BiCMOS, CMOS and bipolar analog integrated circuits and systems. Since 1991, he has been a member of Sigma Xi and since 1985, a student member of the IEEE. He received the Schmeidler Foundation Scholarship from 1983-1987, the Papines Foundation Scholarship from 1983-1987, and the Rotary Club Scholarship during 1983.

## Contents

| 1 | Intr | oducti | on                                                                    | 16 |

|---|------|--------|-----------------------------------------------------------------------|----|

|   | 1.1  | Descri | ption of the Problem                                                  | 16 |

|   |      | 1.1.1  | Overview                                                              | 16 |

|   |      | 1.1.2  | Pipeline ADC Architecture                                             | 16 |

|   |      | 1.1.3  | Limitations to Switched-Capacitor ADCs                                | 17 |

|   |      | 1.1.4  | Digital Self-Calibration for Pipeline ADCs                            | 17 |

|   |      | 1.1.5  | Digital Error-Correction and Digital Self-Calibration                 | 18 |

|   | 1.2  | Applic | eation Realms                                                         | 18 |

|   |      | 1.2.1  | General High-Accuracy High-Speed Data Acquisition                     | 18 |

|   |      | 1.2.2  | Transducer Based Signal Processing Systems                            | 19 |

|   |      | 1.2.3  | Communication Systems                                                 | 20 |

|   |      | 1.2.4  | Control Systems                                                       | 20 |

|   |      | 1.2.5  | Ranging Systems                                                       | 20 |

|   | 1.3  | Organ  | ization of the Thesis                                                 | 21 |

| 2 | Bac  | kgrour | ad                                                                    | 22 |

|   | 2.1  | _      | ary of ADC Techniques                                                 | 22 |

|   |      | 2.1.1  | Flash ADCs                                                            | 22 |

|   |      | 2.1.2  | Subranging ADCs                                                       | 24 |

|   |      | 2.1.3  | Pipeline ADCs                                                         | 24 |

|   |      | 2.1.4  | Successive Approximation ADCs                                         | 27 |

|   |      | 2.1.5  | Delta-Sigma Oversampled ADCs                                          | 29 |

|   |      | 2.1.6  | Cyclic ADCs                                                           | 29 |

|   | 2.2  | Previo | ous Studies in Pipeline ADC Calibration Techniques                    | 31 |

|   |      | 2.2.1  | A 12 bit 600 kS/s Digitally Self-Calibrated Pipelined Algorithmic ADC | 31 |

|   |      | 2.2.2  | Digital-Domain Calibration of Multistep Analog-to-Digital Converters  | 32 |

|   |      | 2.2.3  | A 13 bit 2.5MHz Self-Calibrated Pipelined A/D Converter in 3μm        |    |

|   |      |        | CMOS                                                                  | 32 |

|   |      | 2.2.4  | Self-Calibrating Pipelined Subranging Analog-to-Digital Converter .   | 33 |

|   |      | 2.2.5  | Architecture for High Sampling Rate, High Resolution Analog-to-       |    |

|   |      |        | Digital Converter System                                              | 34 |

8 CONTENTS

|   |      | 2.2.6 Digital Error Correction System for Subranging Analog-to-Digital  Converters |

|---|------|------------------------------------------------------------------------------------|

|   | 2.3  | Converters                                                                         |

|   | 2.0  | Advantages of the Proposed Digital Bell Cambration                                 |

| 3 | Pipe | eline ADC Architecture 39                                                          |

|   | 3.1  | General Pipeline Subranging Structure                                              |

|   | 3.2  | Radix 2 1-Bit-per-Stage Pipeline Subranging ADC Algorithm                          |

|   | 3.3  | Radix 2 1-Bit-per-Stage Pipeline ADC Error Sources 47                              |

|   | 3.4  | Radix < 2 1-Bit-per-Stage Pipeline ADC Motivation                                  |

|   | 3.5  | Radix < 2 Pipeline ADC Properties                                                  |

| 4 | D:a  | tal Self-Calibration 51                                                            |

| 4 | 4.1  | Introduction                                                                       |

|   | 4.1  | Basic ADC Metrics                                                                  |

|   | 4.2  | <del>- 111 - 1 -                           </del>                                  |

|   |      |                                                                                    |

|   |      |                                                                                    |

|   |      | 4.2.3 Differential Nonlinearity                                                    |

|   |      | 4.2.4 Integral Nonlinearity                                                        |

|   |      | 4.2.5 Examples of DNL and INL 54                                                   |

|   | 4.3  | Principles of Digital Self-Calibration for Pipeline ADCs                           |

|   |      | 4.3.1 Introduction                                                                 |

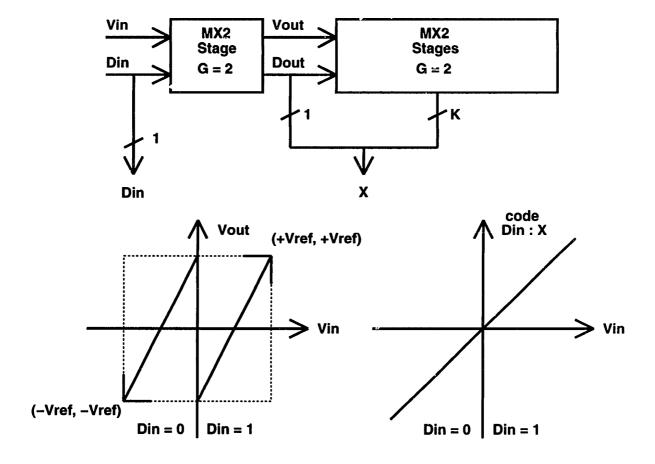

|   |      | 4.3.2 MX2 Stage with $G=2$                                                         |

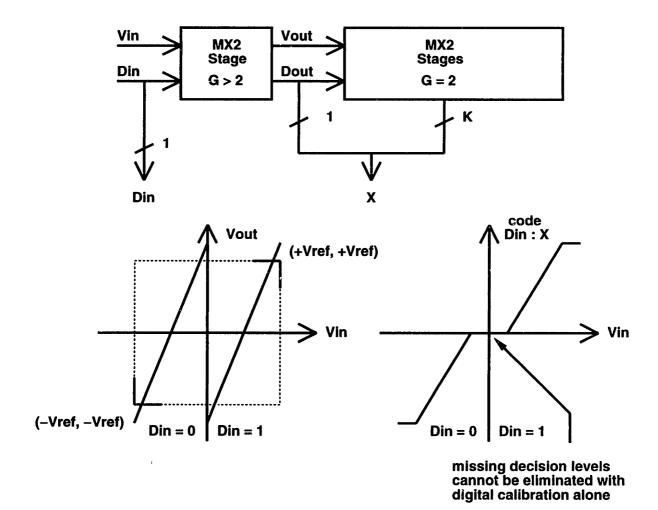

|   |      | 4.3.3 MX2 Stage with $G > 2$                                                       |

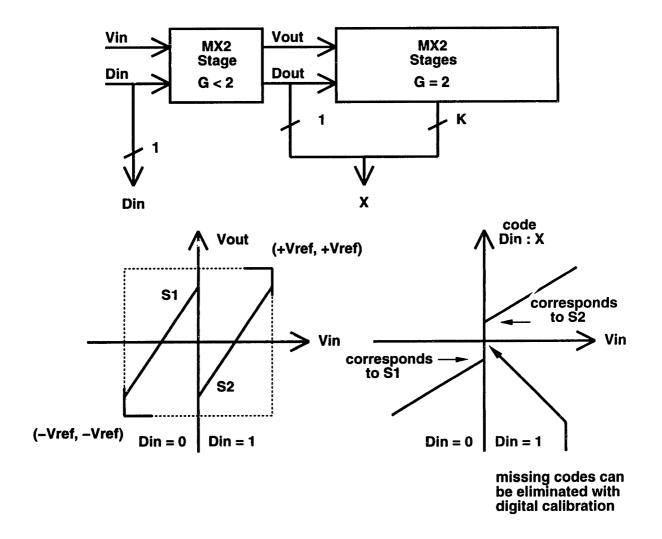

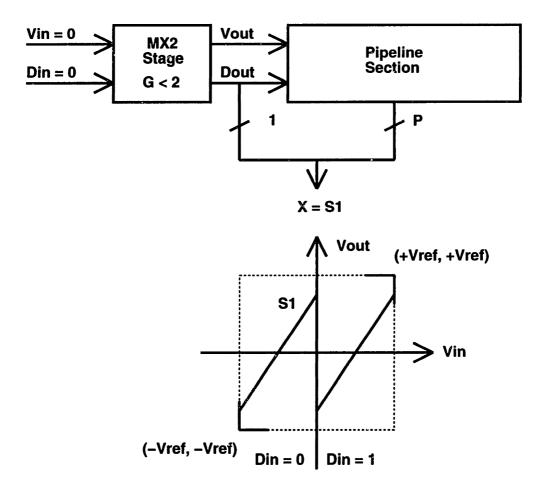

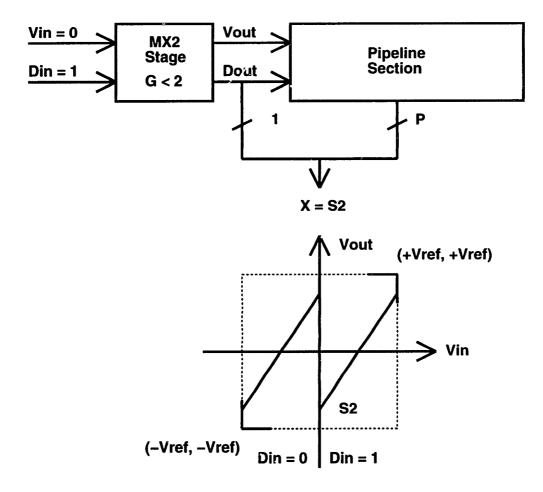

|   |      | 4.3.4 MX2 Stage with $G < 2$                                                       |

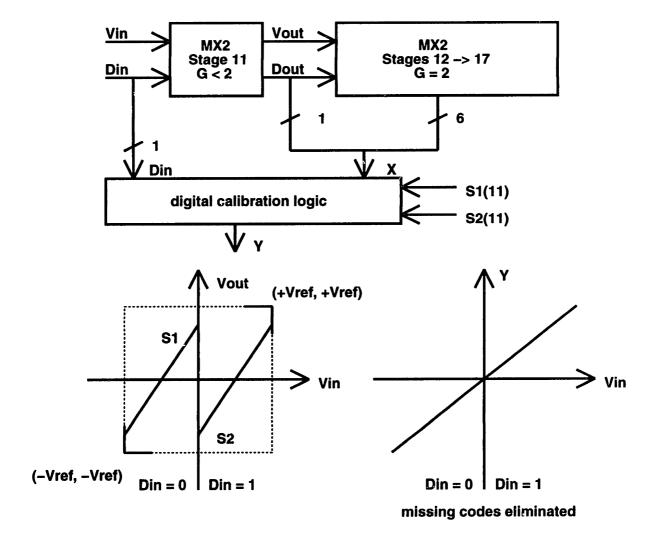

|   |      | 4.3.5 MX2 Stage with $G < 2$ and Digital Calibration Applied 60                    |

|   |      | 4.3.6 Interpretation of the Last K Stage Pipeline Section 60                       |

|   | 4.4  | Calibration Algorithm                                                              |

|   |      | 4.4.1 Introduction                                                                 |

|   |      | 4.4.2 Derivation of Algorithm                                                      |

|   |      | 4.4.3 Algorithm                                                                    |

|   | 4.5  | Comparator Offset                                                                  |

|   | 4.6  | Pipeline Synthesis                                                                 |

|   | 4.7  | Determination of the Calibration Constants $S_1$ and $S_2$                         |

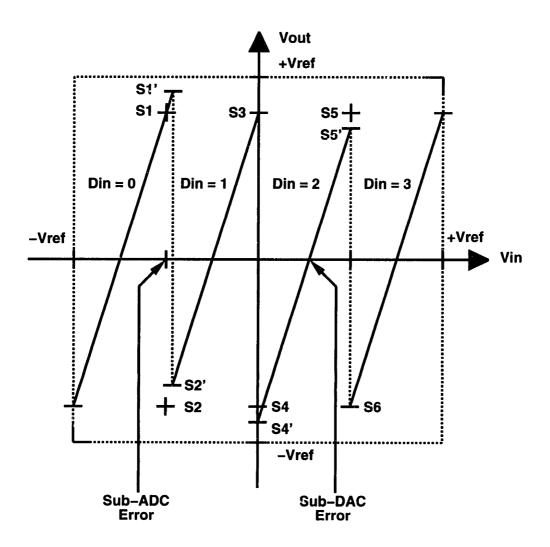

|   | 4.8  | Extension to Multi-Bit-per-Stage Pipeline ADCs                                     |

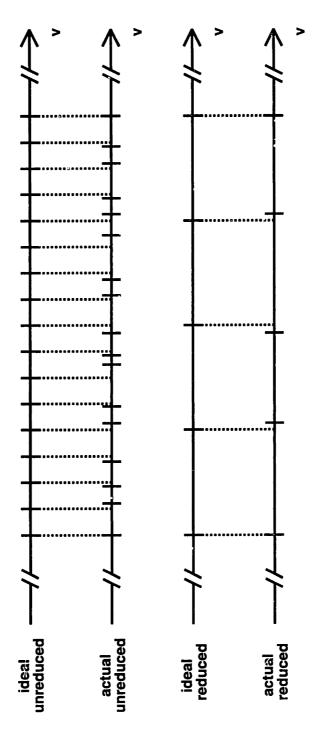

|   | 4.9  | ADC Digital Output Reduction                                                       |

|   | 4.10 | Properties of Digital Self-Calibration                                             |

|   | D:-: | tal Self-Calibration Simulator 77                                                  |

| 5 | _    |                                                                                    |

|   | 5.1  | Software Strategy                                                                  |

|   | 5.2  | Simulator Structure                                                                |

|   | 5.3  | Simulator Description                                                              |

|   | 5.4  | Simulation Results                                                                 |

|   |      | 5.4.1 MX2 Stage Gain $G = 1.9704$                                                  |

| CONTENTS | 9 |

|----------|---|

|          |   |

|   |     | 5.4.2  | MX2 Stage Gain $G = 1.9550$   |   |   |   |   |   |       |       |  | , <b>.</b> |   |   |   |   |   |   | 79  |

|---|-----|--------|-------------------------------|---|---|---|---|---|-------|-------|--|------------|---|---|---|---|---|---|-----|

|   |     | 5.4.3  | MX2 Stage Gain $G = 1.9324$   | • |   | • |   | • |       | <br>• |  | , •        | • | • | • | • | • | • | 79  |

| 6 | Swi | ched-  | Capacitor System Design       |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 86  |

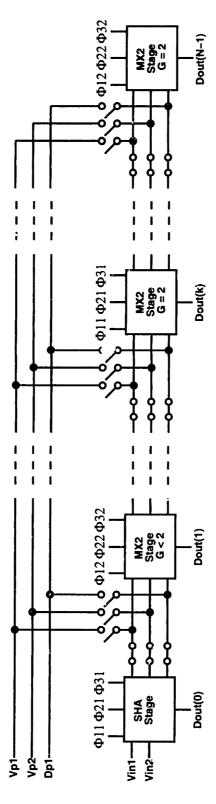

|   | 6.1 | SC Pi  | peline ADC                    |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 86  |

|   |     | 6.1.1  | Basic Structure               | • |   |   |   |   |       | <br>• |  |            |   |   |   |   |   | • | 86  |

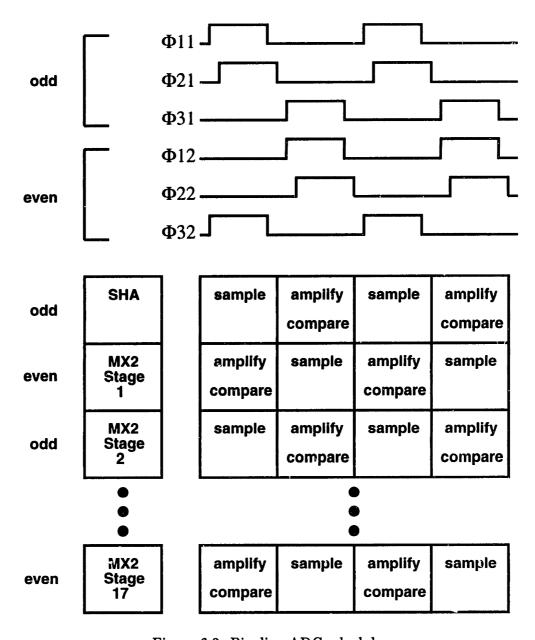

|   |     | 6.1.2  | Timing                        |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 88  |

|   | 6.2 | SC SH  | [A                            |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 88  |

|   |     | 6.2.1  | Sample Mode                   |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 88  |

|   |     | 6.2.2  | Amplify Mode                  |   |   |   |   |   |       |       |  |            |   |   | • |   |   | • | 88  |

|   | 6.3 | SC M   | X2                            |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 91  |

|   |     | 6.3.1  | Sample Mode                   |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 91  |

|   |     | 6.3.2  | Amplify Mode                  |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 91  |

|   | 6.4 | Limita | ations to the SC SHA and MX2  |   |   |   |   |   |       |       |  |            |   |   |   |   |   | • | 95  |

|   |     | 6.4.1  | Nonlinearity                  |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 95  |

|   |     | 6.4.2  | Residual Offset               |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 98  |

|   |     | 6.4.3  | Noise                         |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 99  |

|   |     | 6.4.4  | Settling Time and Accuracy .  |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 100 |

|   |     | 6.4.5  | Aperture Jitter               |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 100 |

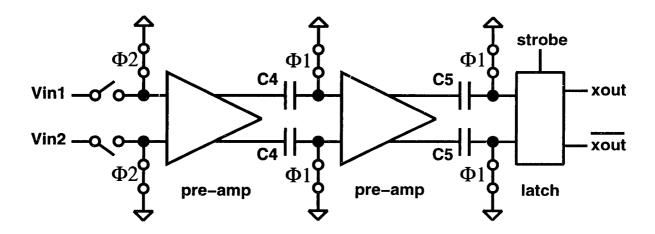

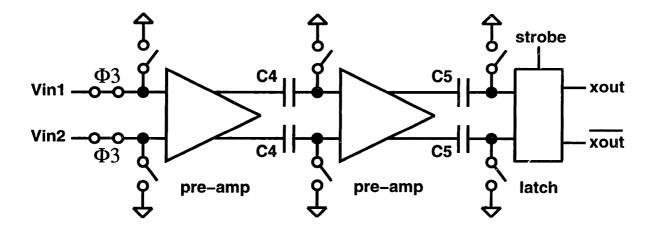

|   | 6.5 | SC Co  | omparator                     |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 101 |

|   |     | 6.5.1  | Basic Structure               |   | • |   |   |   |       |       |  |            |   |   |   |   |   |   | 101 |

|   |     | 6.5.2  | Reset Mode                    |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 101 |

|   |     | 6.5.3  | Amplify Mode                  |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 101 |

|   |     | 6.5.4  | Latch                         |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 101 |

|   | 6.6 | Limita | ations to the SC Comparator . |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 104 |

|   |     | 6.6.1  | Residual Offset               |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 104 |

|   |     | 6.6.2  | Noise                         |   | • |   | • |   | <br>• |       |  |            |   |   |   | • | • | • | 104 |

| 7 | Ana | log In | tegrated Circuit Design       |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 105 |

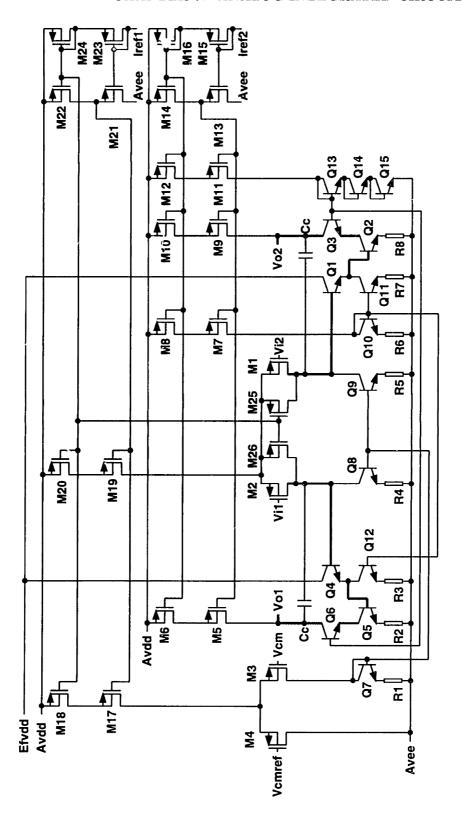

|   | 7.1 | Opera  | tional Amplifier              |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 105 |

|   |     | 7.1.1  | Op-Amp Overview               |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 105 |

|   |     | 7.1.2  | Frequency Response Issues .   |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 105 |

|   |     | 7.1.3  | Transient Response Issues     |   |   |   |   |   |       |       |  | • •        |   |   |   |   |   |   | 108 |

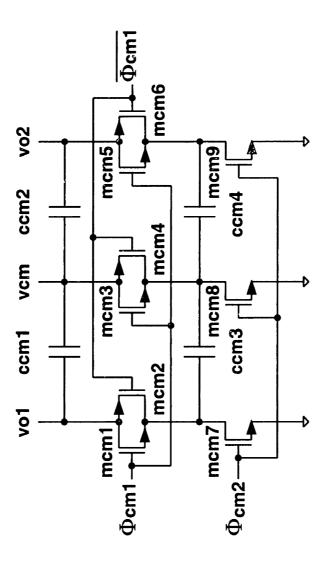

|   |     | 7.1.4  | Common Mode Feedback Netv     |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 109 |

|   | 7.2 | Comp   | arator Pre-Amplifier          |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 109 |

|   | 7.3 | _      | nic CMOS Latch                |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 111 |

|   | 7.4 | •      | Distribution Network          |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 111 |

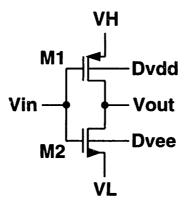

|   | 7.5 |        | l Output Buffer               |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 115 |

|   | 7.6 | _      | ation Results                 |   |   |   |   |   |       |       |  |            |   |   |   |   |   |   | 115 |

10 CONTENTS

| 8  | Mix  | ed-Signal System Layout Design                                    | 118 |

|----|------|-------------------------------------------------------------------|-----|

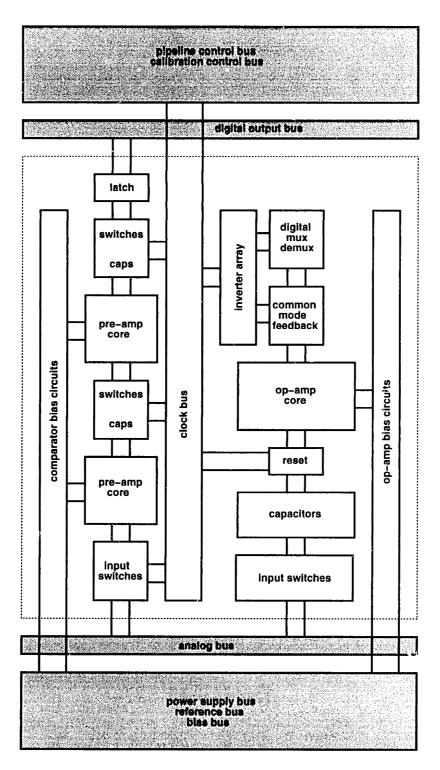

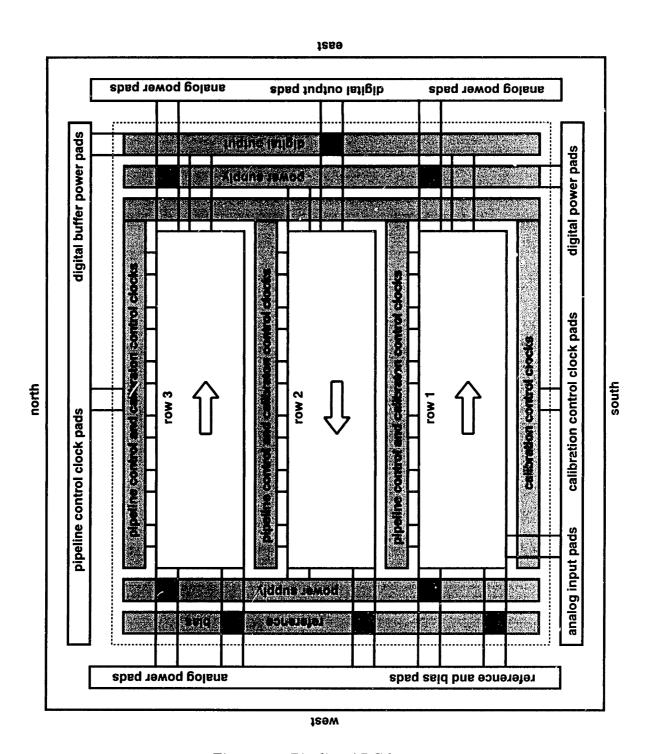

|    | 8.1  | Overall Layout Strategy                                           | 118 |

|    | 8.2  | SHA and MX2 Layout                                                | 119 |

|    | 8.3  | ADC Layout                                                        | 119 |

|    | 8.4  | Layout Verification                                               | 119 |

| 9  | Test | System                                                            | 123 |

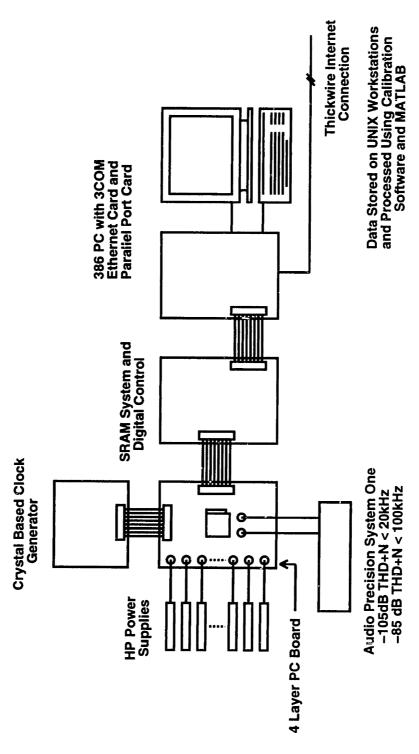

|    | 9.1  | Overall Test System Strategy                                      | 123 |

|    | 9.2  | Test System Structure                                             | 123 |

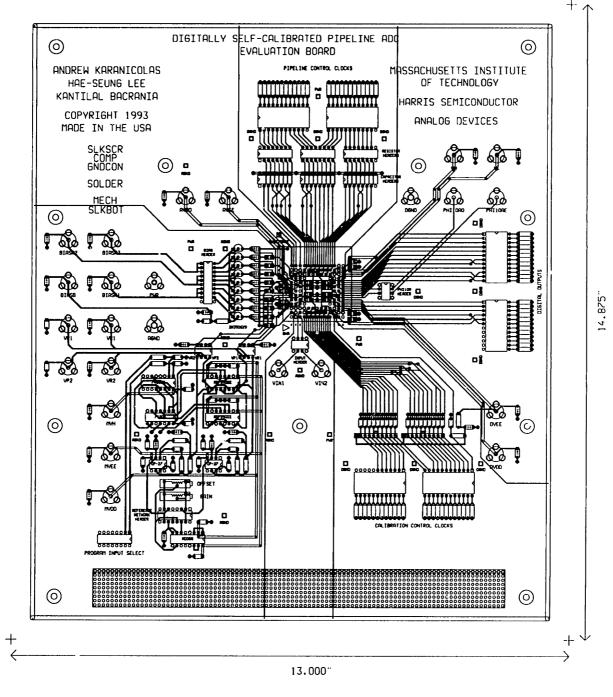

|    | 9.3  | PCB                                                               | 125 |

|    |      | 9.3.1 Overall Design                                              | 125 |

|    |      | 9.3.2 Ground Plane Design                                         | 127 |

|    | 9.4  | Analog Inputs                                                     | 127 |

|    | 9.5  | Pipeline Control Clocks                                           | 127 |

|    | 9.6  | Calibration Control Clocks                                        | 130 |

|    | 9.7  | Reference Voltage Circuit                                         | 130 |

|    | 9.8  | External Bias Circuit                                             | 132 |

|    | 9.9  | Analog and Digital Power Supplies                                 | 132 |

| 10 | Exp  | erimental Results                                                 | 135 |

|    | -    | Total Harmonic Distortion                                         | 135 |

|    |      | 10.1.1 Overview                                                   | 135 |

|    |      | 10.1.2 Sine-Wave Input, 9.87560 kHz, -2 dB FS                     | 135 |

|    |      | 10.1.3 Sine-Wave Input, 98.7560 kHz, -2 dB FS                     | 136 |

|    |      | 10.1.4 Sine-Wave Input, 198.7560 kHz, -2 dB FS                    | 136 |

|    |      | 10.1.5 Sine-Wave Generator Distortion Test                        | 136 |

|    | 10.2 | DNL and INL                                                       | 136 |

|    |      | Input Referred Noise                                              | 141 |

|    |      | Dielectric Relaxation                                             | 141 |

|    |      | Ambient Temperature                                               | 141 |

|    |      | Power Dissipation and Die Area                                    | 144 |

| 11 | Con  | clusions                                                          | 146 |

|    |      | Thesis Summary                                                    | 146 |

|    |      | Future Work                                                       | 145 |

| A  | Swi  | tched-Capacitor Thermal Noise Analysis                            | 143 |

|    | A.1  |                                                                   | 148 |

|    | A.2  | Direct and Sample-and-Held Thermal Noise                          | 149 |

|    | A.3  |                                                                   | 149 |

|    | A.4  |                                                                   | 149 |

|    | 41.7 | A.4.1 Power Spectrum Density of a Discrete Time Stochastic Signal | 149 |

|    |      | A.4.2 Undersampled Broad-Band Noise FT                            |     |

| CONTENTS | 11 |

|----------|----|

|          |    |

|              |            | A.4.3 Enumeration of Sample-and-Held Noise in SC Networks | 155 |

|--------------|------------|-----------------------------------------------------------|-----|

|              | A.5        | SHA Sample-and-Held Noise Analysis                        | 156 |

|              |            | A.5.1 Nonsampling Transmission Gate Contribution          | 156 |

|              |            | A.5.2 Op-Amp Contribution                                 | 156 |

|              |            | A.5.3 Reset Switch Contribution                           | 156 |

|              |            | A.5.4 Total Output Referred Sample-and-Held Noise         | 156 |

|              | A.6        | MX2 Sample-and-Held Noise Analysis                        | 157 |

|              | A.7        | Pipeline ADC Sample-and-Held Noise Analysis               | 158 |

|              | <b>A.8</b> | Signal-to-Noise Ratio                                     | 158 |

|              |            |                                                           |     |

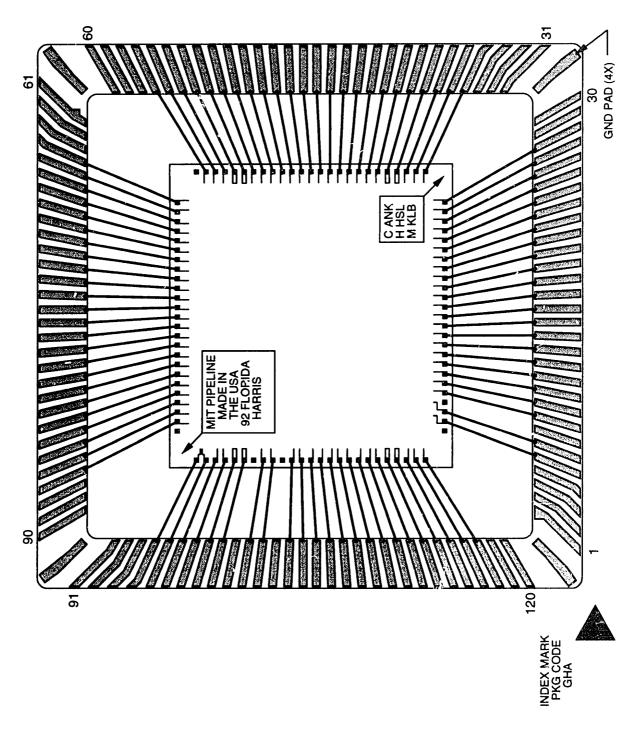

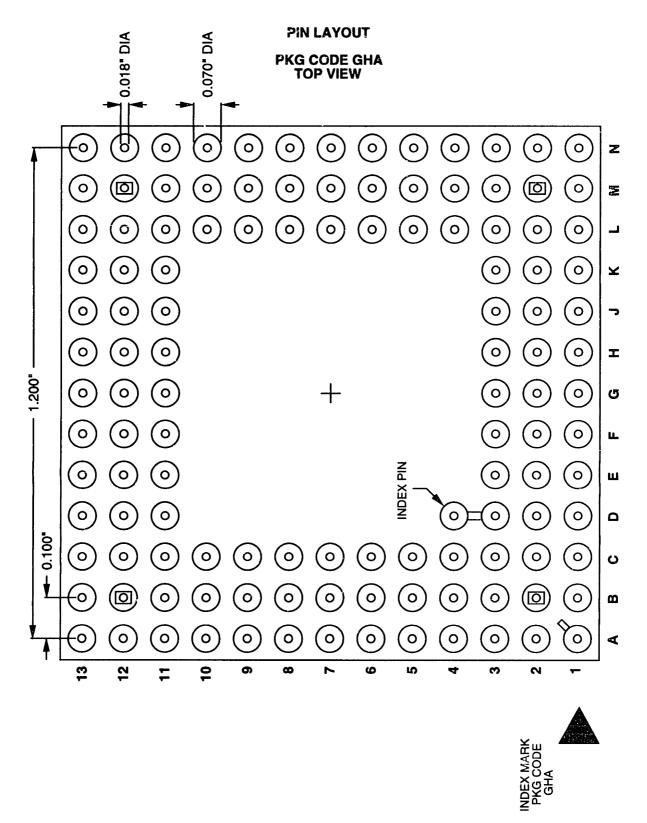

| $\mathbf{B}$ | Pip        | eline ADC Package                                         | 159 |

|              | <b>B.1</b> | Thermal Resistance                                        | 159 |

|              | <b>B.2</b> | Wire-bond Connection Diagram                              | 159 |

|              | <b>B.3</b> |                                                           | 159 |

|              | <b>B.4</b> | PGA Pin-out and Signal Table                              | 162 |

| C            | Dig        | ital Self-Calibration Simulator C Code                    | 166 |

|              | _          | header.h                                                  | 166 |

|              | <b>C.2</b> | main.c                                                    | 166 |

|              | <b>C.3</b> | setbit.c                                                  | 202 |

|              |            | testbit.c                                                 |     |

|              | _          |                                                           | 004 |

| D            |            | t System C Code                                           | 204 |

|              |            | acq.c                                                     |     |

|              | <b>D.2</b> | cal.c                                                     | 209 |

## List of Figures

| 2.1  | Flash ADC architecture                                                      |

|------|-----------------------------------------------------------------------------|

| 2.2  | One stage of a subranging ADC architecture                                  |

| 2.3  | Pipeline ADC architecture                                                   |

| 2.4  | Successive approximation ADC architecture                                   |

| 2.5  | Delta-sigma oversampled ADC architecture                                    |

| 3.1  | General pipeline subranging ADC                                             |

| 3.2  | General cyclic subranging ADC                                               |

| 3.3  | Radix 2 1-bit-per-stage pipeline subranging ADC 43                          |

| 3.4  | Radix 2 1-bit-per-stage ADC algorithm in the sample mode                    |

| 3.5  | Radix 2 1-bit-per-stage ADC algorithm in the amplify mode 45                |

| 3.6  | Residue plot of a MX2 stage in a radix 2 1-bit-per-stage pipeline ADC 46    |

| 3.7  | Residue plot of a 2-bit-per-stage MX4 stage                                 |

| 3.8  | Errors in radix 2 1-bit-per-stage ADCs. Missing codes and missing decision  |

|      | levels are present                                                          |

| 4.1  | Example of uniform decision level locations                                 |

| 4.2  | Example of nonuniform decision level locations                              |

| 4.3  | Example of DNL                                                              |

| 4.4  | Example of INL                                                              |

| 4.5  | Ideal residue and transfer characteristic of a pipeline ADC 5               |

| 4.6  | Residue and transfer characteristic of a pipeline ADC with missing decision |

|      | levels                                                                      |

| 4.7  | Residue and transfer characteristic of a pipeline ADC with missing codes 59 |

| 4.8  | Pipeline ADC with digital calibration applied to the eleventh stage 6       |

| 4.9  | Residue plot of a MX2 stage in a 1-bit-per-stage radix < 2 pipeline ADC     |

|      | with $d(i+1)-d(i)\approx 2\Delta$                                           |

| 4.10 | Residue plot of a MX2 stage in a 1-bit-per-stage pipeline ADC with $d(i +$  |

|      | $1)-d(i)\approx 0.$                                                         |

| 4.11 | Residue plot of a MX2 stage with comparator offset $V_{OS}$ 68              |

| 4.12 | Digital calibration of higher level stages                                  |

| 4.13 | Determination of calibration constant $S_1$                                 |

| 4.14 | Determination of calibration constant $S_2$                                 |

LIST OF FIGURES

| 4.15         | Residue plot of a 2-bit-per-stage MX4 stage. Sub-ADC an are indicated |      |     |       |   |       | 73          |

|--------------|-----------------------------------------------------------------------|------|-----|-------|---|-------|-------------|

| 4 16         | Comparison of decision level locations for the cases of unrec         |      |     |       |   |       |             |

| 1.10         | ADC digital output. Ideal and actual locations are shown              |      |     |       |   |       |             |

|              | cases                                                                 |      |     |       |   |       | 75          |

|              |                                                                       |      |     |       |   |       |             |

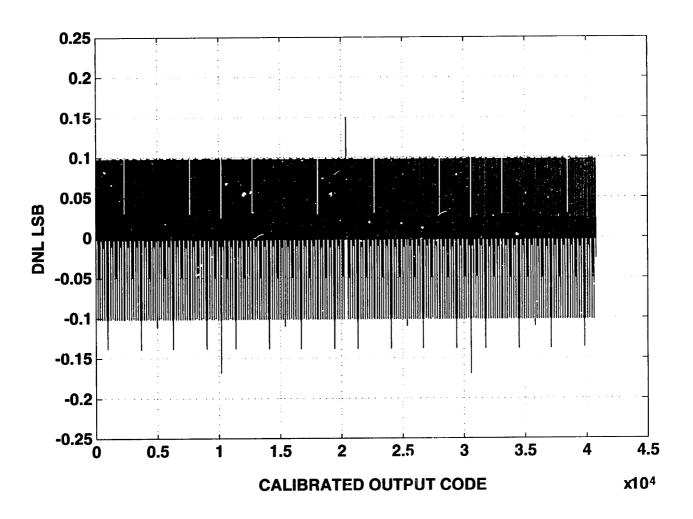

| <b>5</b> .1  | Simulated DNL, $G = 1.9704$ , $K = 6$                                 |      |     |       |   | <br>• | 80          |

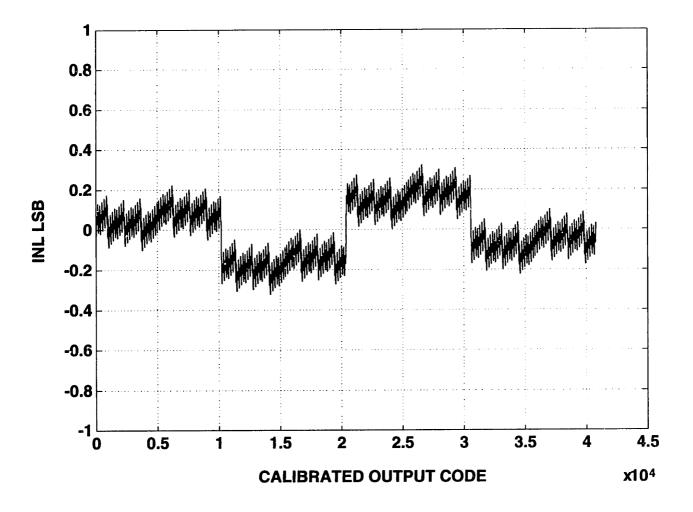

| 5.2          | Simulated INL, $G = 1.9704$ , $K = 6$                                 |      |     |       |   | <br>• | 81          |

| 5.3          | Simulated DNL, $G = 1.9550$ , $K = 6$                                 |      |     |       |   |       | 82          |

| 5.4          | Simulated INL, $G = 1.9550$ , $K = 6$                                 |      |     |       |   |       | 83          |

| 5.5          | Simulated DNL, $G = 1.9324$ , $K = 6$                                 |      |     |       |   |       | 84          |

| 5.6          | Simulated INL, $G = 1.9324$ , $K = 6$                                 |      |     |       |   |       | 85          |

|              |                                                                       |      |     |       |   |       | ۰.          |

| 6.1          | SC Pipeline ADC.                                                      |      |     |       |   |       | 87          |

| 6.2          | Pipeline ADC schedule                                                 |      |     |       |   |       | 89          |

| 6.3          | SHA in the sample mode                                                |      |     |       |   |       | 92          |

| 6.4          | SHA in the amplify mode                                               |      |     |       |   |       | 93          |

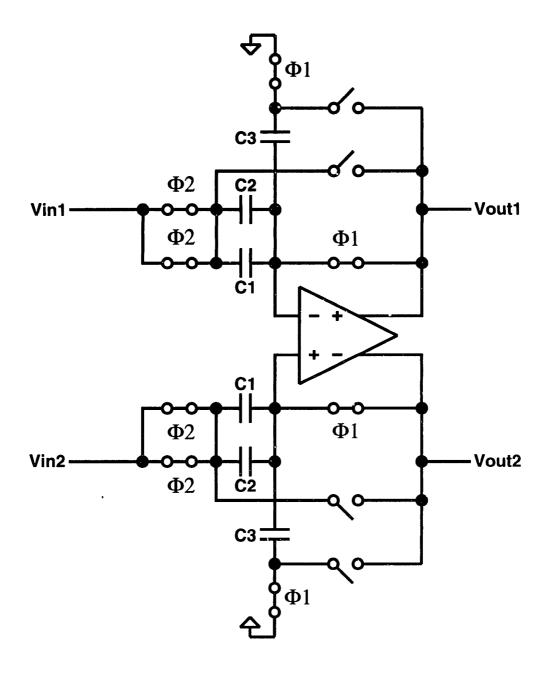

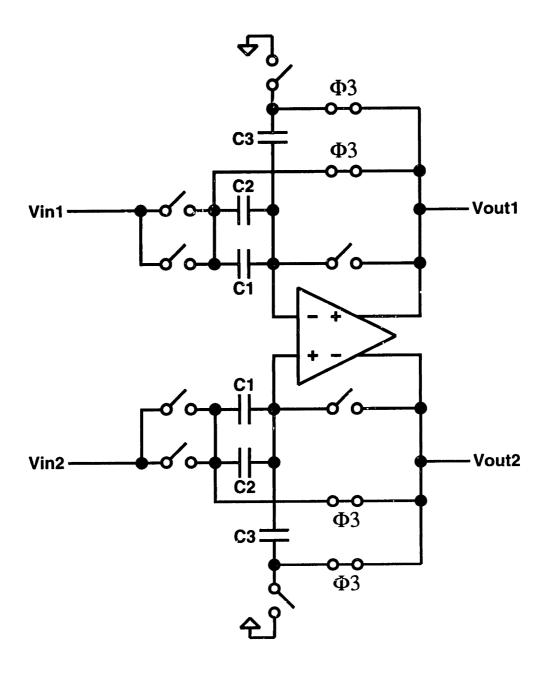

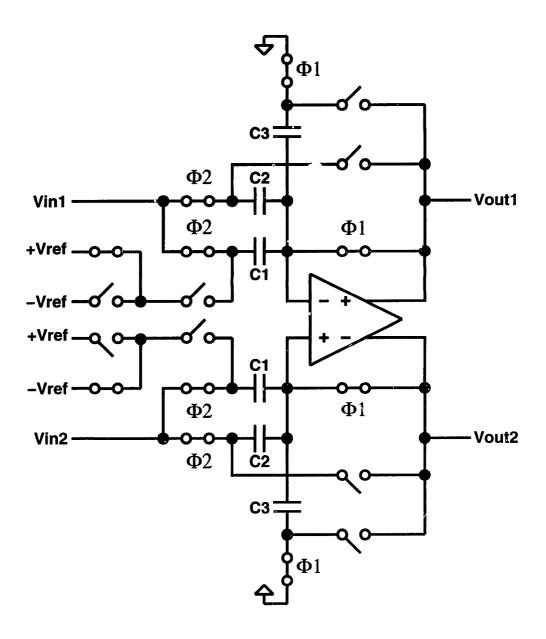

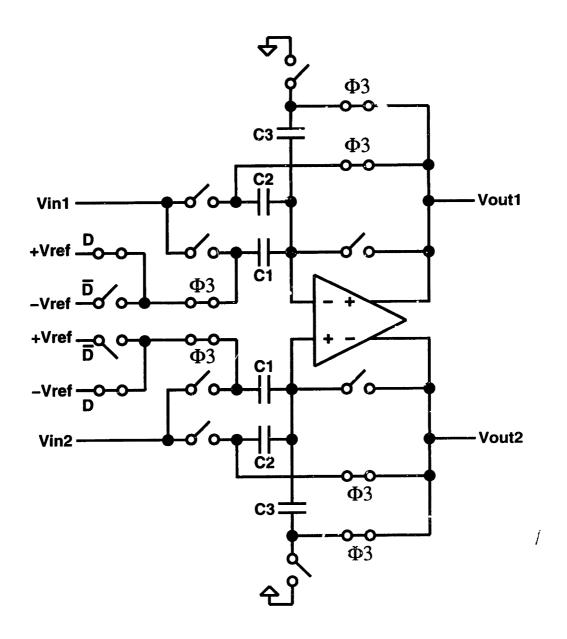

| 6.5          | MX2 in the sample mode                                                |      |     |       |   |       | 96          |

| 6.6          | MX2 in the amplify mode                                               |      |     |       |   |       | 97          |

| 6.7          | Comparator structure in the reset mode                                |      |     |       |   |       | 102         |

| 6.8          | Comparator structure in the amplify mode                              | •    |     | <br>• | • | <br>• | 103         |

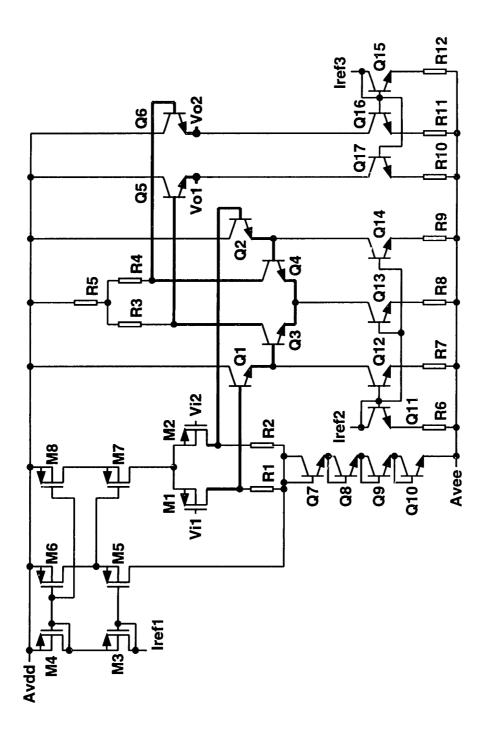

| <i>p</i> 7 1 | 0                                                                     |      |     |       |   |       | 106         |

| 7.1          | Operational amplifier                                                 |      |     |       |   |       | 110         |

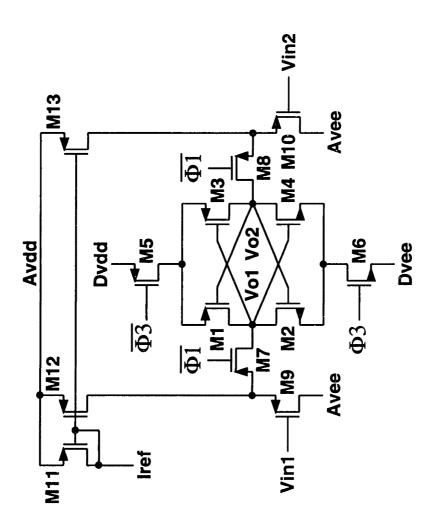

| 7.2          | Common mode feedback schematic                                        |      |     |       |   |       | 112         |

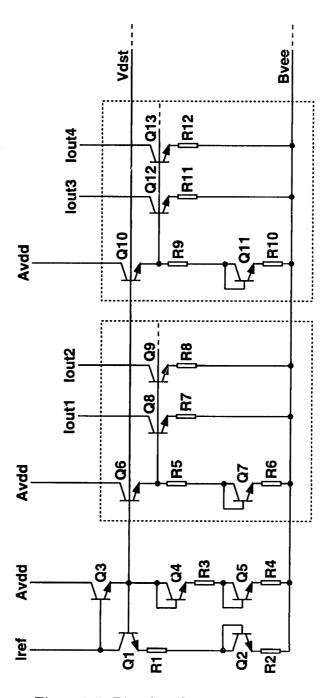

| 7.3          | Comparator pre-amplifier                                              |      |     |       |   |       | 113         |

| 7.4          | Comparator latch.                                                     |      |     |       |   |       | 114         |

| 7.5          | Bias distribution network                                             |      |     |       |   |       |             |

| 7.6          | Digital output buffer design                                          | •    | • • | <br>• | • | <br>• | 116         |

| 8.1          | Pipeline ADC stage layout                                             |      |     |       |   | <br>  | 120         |

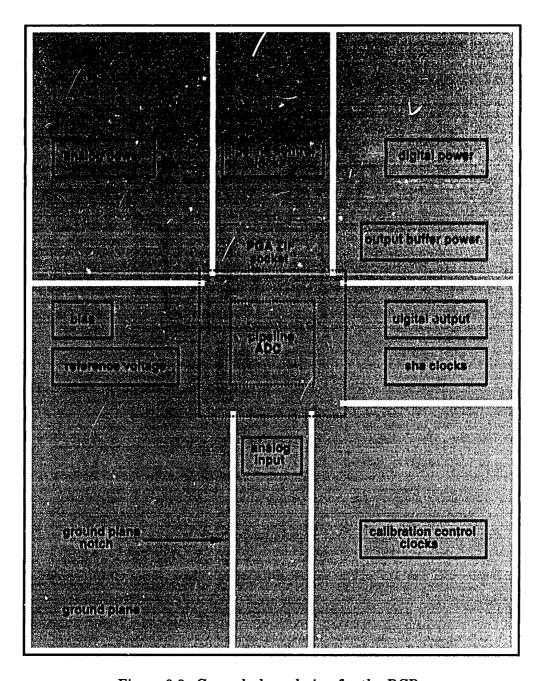

| 8.2          | Pipeline ADC layout                                                   |      |     |       |   |       | 121         |

|              |                                                                       |      |     |       |   |       |             |

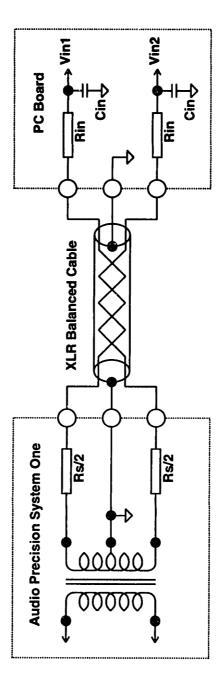

| 9.1          | Test setup for the pipeline ADC                                       |      |     |       |   |       | <b>12</b> 4 |

| 9.2          | Layout of the PCB                                                     |      |     |       |   |       | 126         |

| 9.3          | Ground plane design for the PCB                                       |      |     |       |   |       | 128         |

| 9.4          | Analog input circuit for the pipeline ADC                             |      |     |       |   | <br>  | 129         |

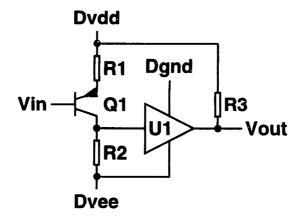

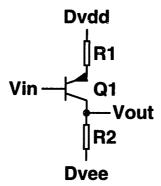

| 9.5          | Pipeline control clock driver circuit                                 |      |     |       |   | <br>  | 131         |

| 9.6          | Calibration control clock driver circuit                              |      |     |       |   | <br>  | 131         |

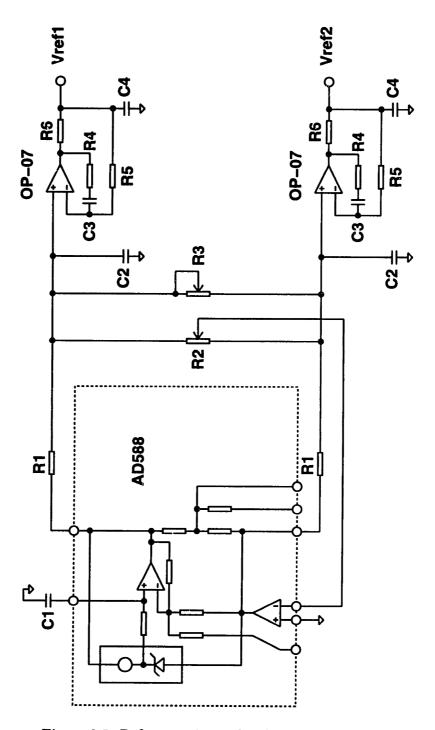

| 9.7          | Reference circuit for the pipeline ADC                                |      |     |       |   | <br>  | 133         |

| 9.8          | External bias circuit for the pipeline ADC                            |      |     |       |   |       | 134         |

| 10 1         | M 1 DDM -1-4 0 07500 LH - : 0 lD :                                    | D.C. |     |       |   |       | 105         |

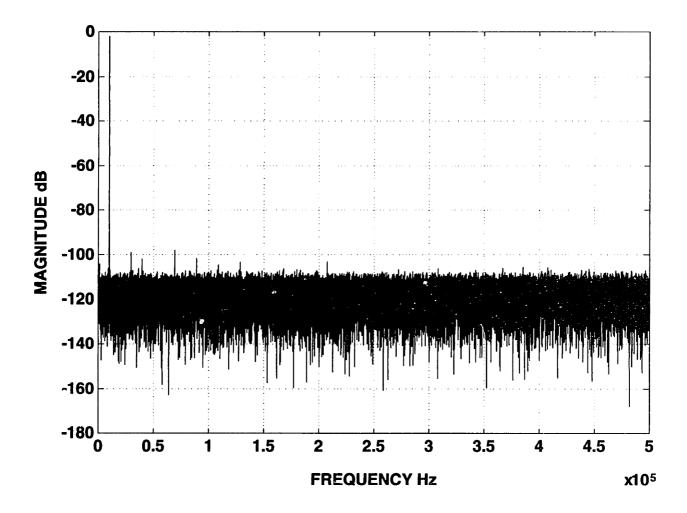

|              | Measured FFT plot, 9.87560 kHz sine-wave input, -2dB                  |      |     |       |   |       | 137         |

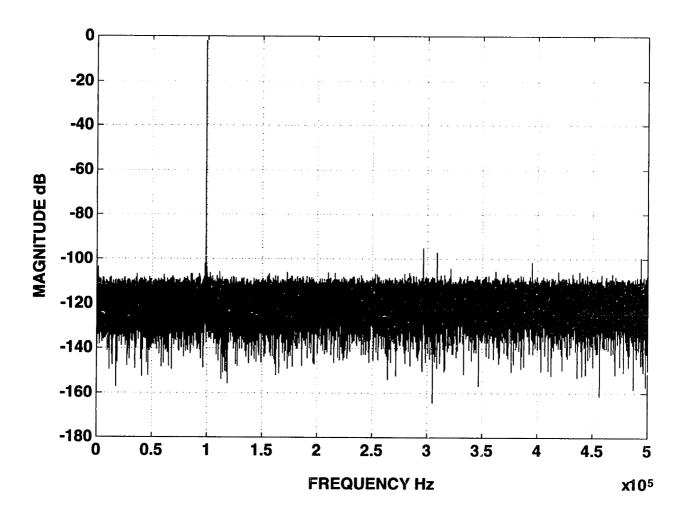

|              | Measured FFT plot, 98.7560 kHz sine-wave input, -2dB                  |      |     |       |   |       | 138         |

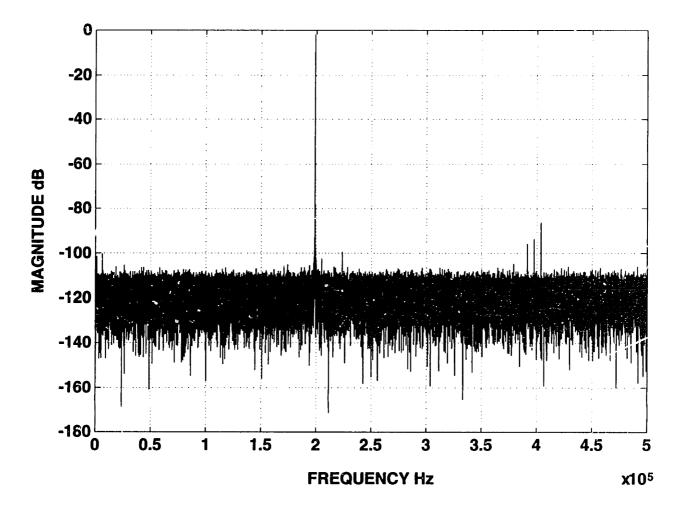

| 10.3         | Measured FFT plot, 198.756 kHz sine-wave input, -2dB                  | r D. | •   | <br>• |   | <br>  | 139         |

14 LIST OF FIGURES

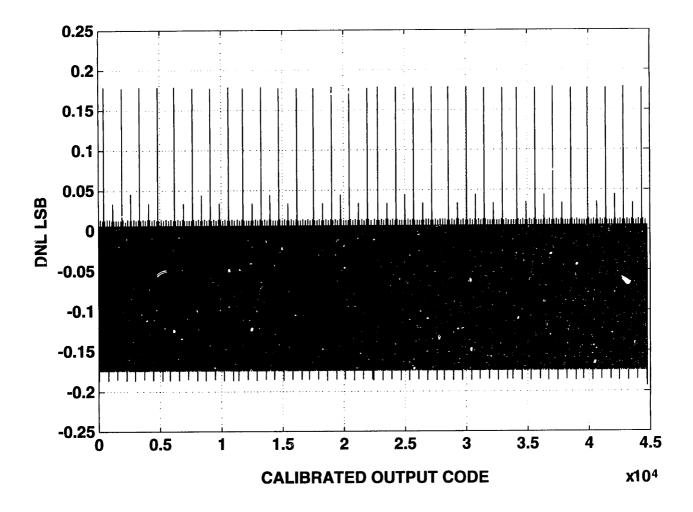

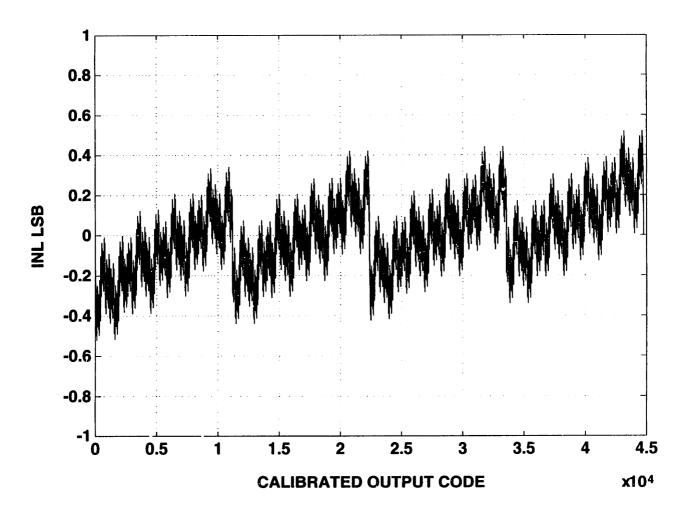

| 10.4        | Measured DNL plot                                                                                    | 142 |

|-------------|------------------------------------------------------------------------------------------------------|-----|

| 10.5        | Measured INL plot                                                                                    | 143 |

| 10.6        | Pipeline ADC die photograph                                                                          | 145 |

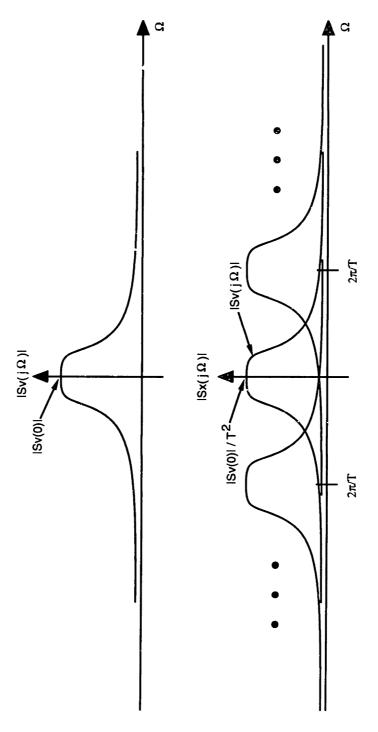

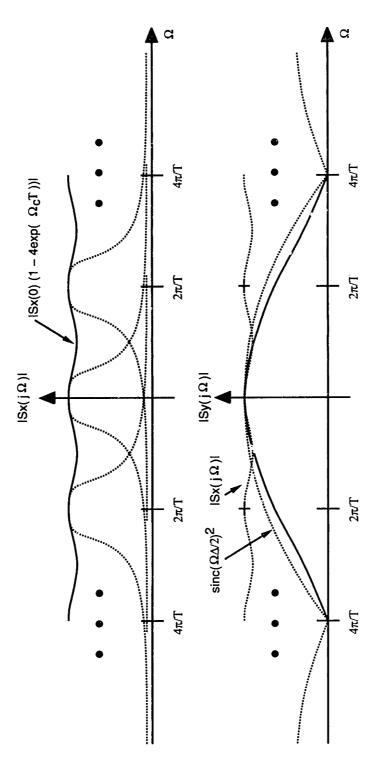

| <b>A</b> .1 | $ S_v(j\Omega) $ and $ S_x(j\Omega) $ plotted with the $S_v(j\Omega)$ replicas scaled and shifted in |     |

|             | frequency as a function of $\Omega$                                                                  | 151 |

| <b>A.2</b>  | $ S_x(j\Omega) $ and $ S_y(j\Omega) $ plotted as a function of $\Omega$                              | 154 |

| B.1         | Wire-bond diagram for pipeline ADC IC                                                                | 160 |

| <b>B.2</b>  | Pin-out diagram for pipeline ADC IC                                                                  | 161 |

## List of Tables

| 3.1  | Gain parameters $A_0$ , $A_1$ and $A_2$ for pipeline and cyclic ADCs as a function of the number of bits resolved per stage, $M.$ | 42  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1  | Parameters of a pipeline section as a function of $V_{in}$ . $G=2, K=6$                                                           | 62  |

| 4.2  | Parameters of a pipeline section as a function of $V_{in}$ . $G < 2$ , $K = 6$                                                    | 63  |

| 4.3  | Parameters of a pipeline section as a function of $V_{in}$ . Digital calibration                                                  |     |

|      | applied. $G < 2$ , $K = 6$                                                                                                        | 65  |

| 7.1  | Op-amp performance summary                                                                                                        | 117 |

| 7.2  | Pre-amp performance summary                                                                                                       | 117 |

| 7.3  | Latch performance summary                                                                                                         | 117 |

| 10.1 | Harmonic analysis, 9.87560 kHz sine-wave input, -2 dB FS                                                                          | 140 |

| 10.2 | Harmonic analysis, 98.7560 kHz sine-wave input, -2 dB FS. HD7 is aliased                                                          |     |

|      | into the baseband.                                                                                                                | 140 |

| 10.3 | Harmonic analysis, 198.7560 kHz sine-wave input, -2 dB FS. HD5, HD4,                                                              |     |

|      | HD19, HD7 and HD3 are aliased into the baseband                                                                                   | 140 |

| 10.4 | Chip performance                                                                                                                  | 144 |

## Chapter 1

### Introduction

### 1.1 Description of the Problem

#### 1.1.1 Overview

An increasing demand for high-performance Digital Signal Processing (DSP) systems motivates an increasing desire for high-resolution, high-speed Analog-to-Digital Converters (ADCs). These ADCs are used in a wide variety of environments, including industrial, communication, medical and aerospace. The use of ADCs in such systems permits so-phisticated DSP algorithms to be utilized, which alleviates complexity in the analog signal processing required otherwise. The analog signal presented to the input of high-resolution, high-speed ADC is frequently a zero-order hold type originating from an imaging array, multiplexer or Sample-and-Hold Amplifier (SHA). Because of the zero-order hold nature of such signals, delta-sigma ADC approaches can not be used to accomplish high-resolution quantization, independent of conversion speed.

Traditional high-resolution, high-speed ADCs rely on expensive, hybrid or discrete implementation and thus are not amenable to low cost manufacturing. The use of monolithic Integrated Circuit (IC) techniques has been repeatedly demonstrated in the digital and analog circuit domains to be economical for synthesizing complex systems. Furthermore, the integration of ADCs with other realms of monolithic systems has been an increasing trend to increase system versatility. The combination of ADCs with other signal processing, transducer, communication, control or ranging systems results in a higher value-added system. Thus, monolithic integration of high-accuracy, high-speed ADCs with other systems requires that the ADC architecture is amenable to the properties of the host processes. However, the desire to integrate high-speed, high-resolution ADCs in low cost, IC processes presents algorithmic, circuit and process design challenges.

#### 1.1.2 Pipeline ADC Architecture

The pipeline ADC architecture is desirable for achieving high-speed, high-resolution ADCs. As a sampled-data system, a pipeline ADC can quantize either continuous or zero-order hold

inputs. One advantage of the pipeline ADC architecture is that it exhibits linear growth in hardware, compared to exponential growth with flash ADCs, for increasing resolution. In addition, pipeline ADCs require fewer clock cycles than successive approximation or oversampled ADCs, which is important for high-speed. However, pipeline ADCs are capable of achieving only 8-10 bits of linearity in most IC processes without the use of component trimming or self-calibration techniques.

#### 1.1.3 Limitations to Switched-Capacitor ADCs

Switched-Capacitor (SC) circuit techniques are efficient for integration of sampled-data systems, such as pipeline ADCs, in Metal Oxide Semiconductor (MOS) based technologies. A SC integration platform combines discrete time signal processing, analog signal processing and algorithmic execution of signal processing functions using charge based signals [1, 2, 3, 4]. These functional attributes can be tedious to duplicate in non-MOS based technologies.

Typically, component values in ADC algorithms are fundamentally related to each other by ratios of the component values. Thus, ratiometric limitations are fundamental limitations of achievable ADC resolution. MOS based technologies share the traditional limitations common to IC processes including mask resolution limits, mask misalignment, nonuniform deposition and nonuniform etching.

Device related errors in MOS based SC systems include channel charge injection, clock feed-through and substrate coupling. MOS devices and other IC components contribute to wide-band thermal noise limitations. Other important aspects of MOS device physics that limit performance include threshold voltage relaxation [5, 6] and 1/f noise [7].

### 1.1.4 Digital Self-Calibration for Pipeline ADCs

In order to achieve precise ratios, high-precision component tolerances are required in traditional ADC approaches, which are not compatible with low cost, MOS IC processes. As a result, the use of calibration techniques is important to eliminate the need for high-precision matching.

Self-calibration refers to an algorithmic means for correcting ADC errors without the need for high-precision matched components and without the need for special trimming or alignment using mechanical components. This thesis will present a digital self-calibration technique developed for pipeline ADCs with a 1-bit-per-stage, or multiple-bits-per-stage design. The digital self-calibration technique can also be applied to cyclic ADCs. The technique removes ratiometric errors and is simultaneously tolerant to comparator errors. The technique described here accomplishes digital self-calibration without requiring external data converters, complex microprocessor based calibration engines or special calibration training signals. This approach uses innate properties of pipeline ADCs to an advantage for self-calibration. The use of digital self-calibration is important to minimize the quantity, and hence expense, of precision analog circuitry. In contrast, digital circuits are much cheaper to construct. The digital self-calibration will be presented in this thesis from the perspective of a synthesis strategy for a wide range of high-accuracy ADCs. A 15-bit, 1

MS/s prototype was integrated in a  $2.4\mu m$  BiCMOS process to demonstrate the digital self-calibration technique.

#### 1.1.5 Digital Error-Correction and Digital Self-Calibration

Digital error-correction refers to methods of correcting comparator errors that occur in pipeline subranging ADCs. These error-correction schemes do not account for ratiometric errors. Error-correction schemes for pipeline subranging ADCs generally assume certain errors that can occur due to comparator errors and then correct for those errors digitally, without measuring any errors. As a result, it is important to dissociate error-correction schemes, which do not measure errors, from self-calibration schemes, which involve measurement of errors. Some self-calibration schemes involve the use of error-correction principles so that both ratiometric and comparator errors are removed. The digital self-calibration presented in this thesis accounts for ratiometric errors and is tolerant to comparator errors, without additional action needed.

### 1.2 Application Realms

#### 1.2.1 General High-Accuracy High-Speed Data Acquisition

#### Video Applications

With the advent of powerful, and cheap, integrated circuits that perform a variety of analog and digital functions, the electronic subsystem of a video camera oriented for television use has evolved into an efficient structure, in terms of physical size, power consumption and function. Even with these advances, video cameras still retain a substantial amount of complexity because of the frequent requirement for image transmission in natural color [8]. The reduction of user controls and the corresponding increase of automatic systems in consumer oriented video cameras has spawned an increase in electrical and mechanical complexity [9, 10]. However, the image sensor systems remains at the center of the camera complexity.

Semiconductor image sensors have evolved on a slower path compared to semiconductor circuits [11, 12]. However, advances in Very Large Scale Integration (VLSI) technology, combined with Charge Coupled Device (CCD) circuits, have resulted in practical implementation of silicon based image sensors for video cameras. The use of solid-state CCD image sensors, combined with VLSI circuit techniques, has permitted the overall cost of manufacture of video cameras to drop to the point where mass consumer production is viable [8].

Digital signal transmission, storage and processing schemes for television systems motivates the need for high-performance ADCs to digitize the output signal of the CCD imager. Since the data is already zero-order held, delta-sigma approaches are not appropriate. High-volume production of such systems requires low overall cost and high-performance simultaneously. Other digital video applications include high-speed electronic shuttering CCD

imager based cameras for motion analysis. In order to provide accurate data analysis for such an application, the resolution and speed requirements for the ADC are substantially higher compared to television applications. Overall, the use of monolithic ADCs in solid-state imager based digital cameras is important when the size, weight and power dissipation of the camera systems are critical.

#### Medical Applications

The medical advantages of noninvasive imaging techniques motivates the use of DSP to perform complex imaging functions. The use of X-Ray Computer Axial Tomography (CAT) requires that high-performance ADCs are used to digitize the output of the crystal and photomultiplier tube detector system [13]. ADC artifacts can impair the analytical capabilities of CAT [14].

The use of nuclear Magnetic Resonance Imaging (MRI) techniques has been motivated from the desire to avoid ionizing radiation for patient evaluation. The use of MRI requires high-sensitivity receivers and high-performance ADCs to digitize the attenuated RF signals after passing through tissues. Because of the extremely large dynamic range requirement of MRI techniques, the receiver and ADC design is particularly challenging. Even more challenging is to perform real-time imaging of tissues [13].

One advantage of ultrasonic imaging compared to CAT or MRI is the absence of ionizing radiation or powerful magnetic and RF fields [13]. Another advantage of ultrasonic imaging is that the stimulus and analysis hardware is intrinsically simpler and less costly than either CAT or MRI systems. However, the tomographic techniques used to reassemble the image are similar among ultrasound, CAT and MRI. The use of DSP to analyze the receiver transducer output requires a high-performance ADC for analytical capabilities. In order to produce a low cost, high-performance, portable ultrasound imaging instrument, low cost techniques for high-performance ADCs are required.

#### 1.2.2 Transducer Based Signal Processing Systems

An important signal processing structure frequently used involves the use of a transducer and an ADC system to quantize the electrical signals so that digital processing can be utilized. The transducers derive electrical signals in response to physical quantities including, but not limited to, pressure, temperature, acceleration and position. Since manipulation of analog signals is challenging from a packaging viewpoint, it is desirable to perform the ADC function as close to the sensor as possible. The combination of silicon micro-machined sensors with ADCs and signal processing capabilities results in a more versatile system. The use of efficient ADC structures is important with silicon micro-machined sensors because of the additional constraints imposed by the host sensor process and the sensor design itself.

#### 1.2.3 Communication Systems

The advantages of digital communication techniques are well established and are increasingly prevalent in high-capacity telecommunication and personal communication links. The combination of communication systems and transducer systems is powerful because once the transducer data is quantized, complex arrangements of transducers can be employed in a network. The ability to use large numbers of sensors to perform wide-area monitoring of physical phenomenon at low cost means that the ADC must be included with each sensor.

The use of ADCs in radio systems presents several potential advantages. Reduction of analog circuitry in combination with advanced DSP algorithms is increasingly important to allow design flexibility in chief radio system parameters such as modulation methods, transmitter power and antenna design. One use of ADCs in superheterodyne based radio systems is to convert the IF signal to digital by sampling at the IF frequency. An ADC used in this capacity can be thought of as a digital demodulator in the radio system. The ability of networked radio systems to change transmitter power depending on node distance is important to minimize interference effects for close proximity nodes yet achieve communication at long distance. As a result, the dynamic range of radio signals can be large and demand high-performance ADCs.

#### 1.2.4 Control Systems

The use of DSP and algorithmic based signal processing methods for control systems provides an impetus for high-performance ADCs used to quantize wide dynamic range analog signals present in such systems. The use of a pipeline architecture presents advantages for realizing high-resolution ADCs used in such applications. As described above, flash ADCs present unfavorable hardware growth for increased resolution, regardless of speed. One of the disadvantages of a pipeline architecture used in control systems is that the latency of the pipeline presents delay. This delay may add excessive phase shift in a control system loop. However, the total delay depends on the number of stages employed so a pipeline architecture has design flexibility to reduce latency to comparable or lower level than successive approximation ADCs, for example. The use of delta-sigma ADCs for high-resolution applications in control systems normally presents greater latency than a pipeline ADC used in a high-performance environment. This latency originates from the long impulse response present in the high-order FIR filter used in the decimator.

#### 1.2.5 Ranging Systems

Both RADAR and SONAR systems present challenging applications of DSP and algorithmic based signal processing. This setting demonstrates another application of high dynamic range ADCs. The use of hybrid construction techniques may be sufficient for traditional applications primarily oriented towards aerospace applications. However, the potential use of sophisticated ranging techniques for automotive collision avoidance systems would likely require a lower cost ADC solution.

### 1.3 Organization of the Thesis

This thesis is organized in a top-down fashion, overall. Chapter 1 presents the introduction to this thesis. The description of the problem will be stated and the direction of this thesis will be motivated. With this established, the design methodology that the digital self-calibration provides will be outlined. The scope of applications that rely on high-accuracy, high-speed ADCs will be presented.

Chapter 2 discusses the background in this research area. A summary of common ADC techniques, and the relative merits of each approach, are discussed with the focus placed on high-accuracy, high-speed ADCs. Previous studies relating to pipeline ADC calibration techniques are then covered. This includes both analog and digital calibration methods. The advantage of the digital self-calibration presented in this thesis concludes this chapter.

The specific pipeline architecture used in the ADC presented in this thesis is discussed in Chapter 3. The errors present in the pipeline architecture are discussed for 1-bit and multi-bit pipeline ADCs.

Chapter 4 is the central focus of this thesis and will present the digital self-calibration principle. The properties of the digital self-calibration will be discussed including a discussion of the design methodology that the digital self-calibration provides.

A discussion of the simulator used to evaluate the digital self-calibration is discussed in Chapter 5. Simulation results obtained from the simulator are presented.

The SC system design used to implement the Radix < 2 ADC is presented in Chapter 6. Limitations to the SC circuits are discussed.

The analog IC design is shown in Chapter 7. The op-amp, pre-amp and latch circuits are principally discussed.

The layout design is important for achieving a high-performance system and is discussed in Chapter 8.

The overall design of the test system is presented in Chapter 9. The test system design principally reflects the need to maintain signal integrity in the evaluation of a high-performance ADC.

Experimental results are shown in Chapter 10. The sine-wave Fast Fourier Transform (FFT) results are presented. The Differential Nonlinearity (DNL) and Integral Nonlinearity (INL) results are then shown.

Observations derived from this work are presented along with future directions in Chapter 11.

Various appendices follow to discuss specific, detailed issues arising in this thesis. Appendix A presents a detailed SC noise analysis for a pipeline ADC, Appendix B shows the PGA package employed for the ADC, Appendix C shows the digital self-calibration simulator C code programs and Appendix D shows the test system C code programs.

## Chapter 2

## **Background**

In this chapter, various ADC techniques are presented in order to establish a context for comparison and contrast to pipeline subranging ADC techniques. With this context established for pipeline subranging ADCs, prior studies in calibration schemes are discussed. The advantages of the proposed digital self-calibration technique are then outlined.

### 2.1 Summary of ADC Techniques

#### 2.1.1 Flash ADCs

#### Full Flash ADCs

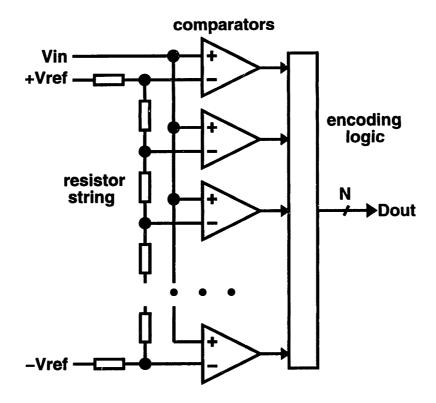

One of the most direct ADC approaches is the flash ADC [15]. Fig. 2.1 shows that a comparator is assigned for each decision level in the flash ADC. All of the comparator inputs of the same polarity are connected in parallel to the analog input  $V_{in}$ . A reference voltage ladder is used to provide the decision level spacing which each comparator compares against. The flash ADC operates by strobing all of the comparators simultaneously. The resulting output codes are usually termed a thermometer code because ideally all the comparator results above the analog signal level will result in 0 and below the analog signal level will result in 1. Combinational logic is then used to translate the thermometer code into a linear binary output, or other desired digital output form. Sophisticated logic error-detection schemes can be used to correct for various error scenarios that may occur.

The advantage of the flash ADC architecture is speed. In principle, no op-amps or SHAs are required. Only a single clock cycle is needed for a conversion cycle. Flash ADCs are used when conversion rate is a primary design consideration [16, 17, 18]. As a result of this architecture, for N bits of resolution,  $2^N - 1$  comparators are required. Since each comparator must have a resolution that is consistent with the full converter accuracy, the comparator design dictates the primary complexity of the flash ADC. A primary limitation of this structure to high-accuracy is the exponential growth of hardware with resolution because the number of comparators required is proportional to  $2^N$ . Related to this limitation, the input capacitance, the number of ladder taps, the size of the combinational logic

Figure 2.1: Flash ADC architecture.

and the total power dissipation increase exponentially for increased resolution. In practice, 8-bit resolution, corresponding to 255 comparators, is frequently a practical limit based on these collective considerations. The direct approach of the flash ADC leads to high-speed but not high-resolution for practical ADCs.

#### Folding and Interpolating Flash ADCs

A method for alleviating the comparator requirement in the flash ADC is the use of folding and interpolating structures [16, 19, 18, 20, 21, 22]. The main objective of these structures is to arrive at an ADC that has comparable speed to a full flash ADC, uses less power and area than a full flash ADC and avoids the speed limitation of subranging ADCs. Unfortunately, the hardware growth for folding and interpolating structures is still an exponential function of the number of bits needed, however the proportionality constant is reduced.

#### 2.1.2 Subranging ADCs

The basic principle of a subranging ADC is to divide the quantization into ranges, beginning with an upper MSB section. Progressively lower bit weight sections are then quantized by succeeding stages [15]. This quantization in any particular stage may be performed using a variety of ADC methods. Once the upper MSB section bits are determined, a reconstruction level is produced using a DAC and a residue is produced corresponding to the difference between the analog input and the DAC output. This residue is then processed by another subranging stage. If desired, the subranging stages may be pipelined. When pipelining is not employed, interstage SHAs are eliminated but the throughput usually suffers as a result. The subranging structure is illustrated in Fig. 2.2 for a particular subranging stage.

A commonly used arrangement is a 2-step subranging ADC where 2 subranging stages are used in cascade [23, 24, 25, 26]. Medium resolution, high-speed ADCs typically employ a 2-step subranging architecture. For low-to-medium resolution, usually in the range of 8-bit to 10-bit, component mismatch properties in modern analog IC processes are favorable enough so that self-calibration is not required. In some cases, laser trimming can be used to calibrate the unit once. However, comparator errors can limit resolution. A digital error-correction algorithm can be used to correct the comparator errors, but not any ratiometric errors [27, 28, 29]. Thus, the final accuracy will be limited by the process matching properties.

#### 2.1.3 Pipeline ADCs

Pipeline ADCs are special types of subranging ADCs where clock phases of adjacent stages are opposite. In this fashion, each stage processes the input to that stage and the result is sampled to the next stage. The throughput is improved, because each stage can process new input every two clock phases.

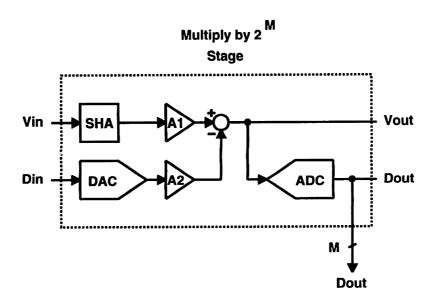

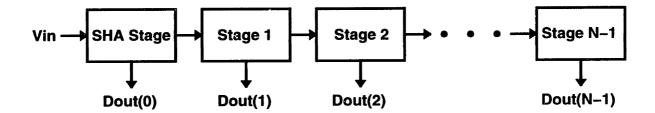

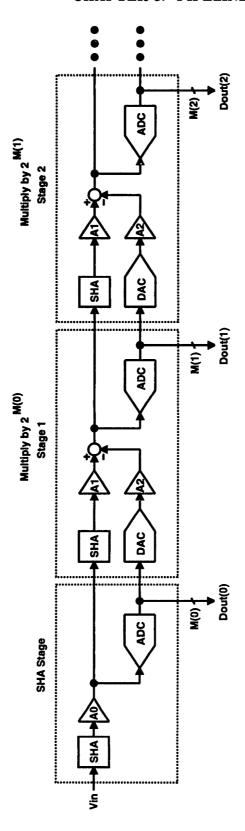

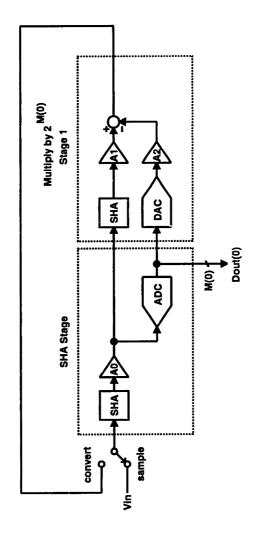

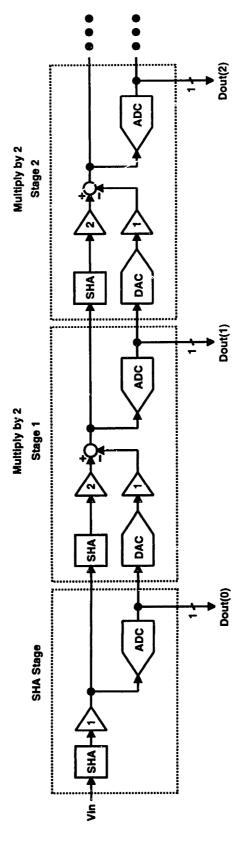

A generalized pipeline structure is shown in Fig. 2.3. The overall approach of a pipeline ADC is to provide a cascade of stages for processing the analog input signal  $V_{in}$ . Once the

Figure 2.2: One stage of a subranging ADC architecture.

Figure 2.3: Pipeline ADC architecture.

first stage has processed a particular analog input, the result is passed to the next stage. A pipeline ADC is a sampled-data system so means for storing intermediate analog and digital results are necessary. This usually entails interstage SHAs and latches. As a result, the first stage can then acquire a new analog input. Because the data must pass through all of the stages before the answer is complete, the digital results need to be stored intermediately for final time alignment. A shift register function can be used in hardware, or software, in order to perform the time alignment. Once the pipeline and shift register functions are initially filled, the pipeline throughput is limited by the delay of a single processing stage, assuming each stage has the same delay. In sharp contrast to the flash ADC structure, pipeline ADCs only require linear growth in hardware for increasing resolution. Notice that adding another stage to the pipeline will increase the resolution by at least 1-bit, depending on the resolution of the stage. The latency of the pipeline is the summation of all of the processing stage delays. Notice that the latency only grows linearly for increased resolution. Many applications are not sensitive to latency that is on the order of N times larger than the throughput time. However, control systems are one example where latency may be important to consider. This is because of stability concerns arising from the increased phase shift in the loop transmission attributed to the latency.

Pipeline ADCs offer high-speed capability because the throughput of the ADC is determined by the delay of a single stage. The pipeline ADC architecture is general and various methods may be employed within the stages. A 1-bit-per-stage pipeline subranging ADC offers the combination of simplicity and speed in the circuit design for each stage [30, 31, 32, 33, 34, 35]. Multi-bit per stage pipeline subranging ADCs have been demonstrated [36, 37, 27, 28, 29]. This thesis will outline in Chapter 4 an all-digital self-calibration technique that is particularly amenable to pipeline subranging ADCs structures in general and will present a 1-bit-per-stage pipeline ADC with all-digital self-calibration technique implementation [31, 32].

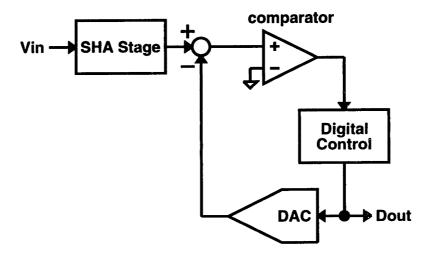

#### 2.1.4 Successive Approximation ADCs

The basic principle of a successive approximation ADC is to arrange a DAC circuit in a feedback system so that the error signal composed of the difference of the analog input and the DAC output is minimized [15]. A digital control system is used to schedule operations that lead to minimization of the error over a number of sequential operations. As the system state evolves, the output resolution improves, assuming that the error is reduced at each sequential operation. The overall structure of this ADC is shown in Fig. 2.4. Notice that this a feedback structure and is thus subject to stability concerns. For instance, the monotonicity of the DAC is very important. If the DAC output decreases for increasing input, then the digital controller will continue incrementing the DAC input until the error is minimized. This results in missing codes. Depending on the digital controller algorithm, limit cycles are possible if the DAC is not monotonic.

Successive approximation ADCs have been traditionally used for medium-resolution, medium-speed ADCs [38]. Digital error-correction schemes which employ faster settling strategies have been reported [39]. The successive approximation ADC is amenable to either

Figure 2.4: Successive approximation ADC architecture.

factory calibration [40, 41] or self-calibration resulting in a high-accuracy ADC [42, 43, 44]. The primary disadvantage to successive approximation ADC is that many clock cycles are needed to complete a single conversion. This presents a disadvantage when high-speed, high-accuracy ADCs are desired.

#### 2.1.5 Delta-Sigma Oversampled ADCs

Delta-Sigma oversampled ADCs have been used successfully for high resolution signal conversion at low frequencies, such as in audio applications [45]. However, a large class of signals that need to be quantized are zero-order held. This includes video data signals originating from CCD imaging systems and multiplexed data signals. Delta-sigma oversampled ADCs can not be employed for these important classes of high-speed signals that in many cases require quantization at high-accuracy.

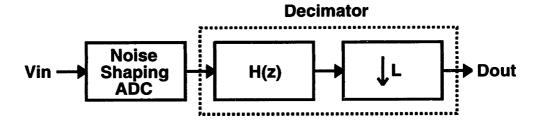

Fig. 2.5 shows a delta-sigma oversampled structure. A large oversampling ratio is employed in order to achieve high resolution when using low resolution quantizer and reconstruction circuits in a delta-sigma modulator. However, the use of such a delta-sigma modulator to accomplish high-resolution, high-speed with a low resolution quantizer in the delta-sigma results in unacceptably large oversampling ratios, and thus unacceptably large clock rates. In order to relax the oversampling ratio required, a multi-bit quantizer and reconstruction circuits in the delta-sigma modulator can be used. However, the advantages of 1-bit delta-sigma ADCs are less pronounced when multi-bit quantizer and reconstruction circuits are needed, thus limiting the attainable accuracy. The use of self-calibration techniques on the low resolution quantizer and reconstruction circuits is promising for medium to high-resolution at high-speed [46]. Even with a lower oversampling ratio compared to 1-bit delta-sigma ADC designs, the sampling rate required can becomes prohibitively high for present silicon implementations.

In addition, a decimation filter is required to attenuate the out-of-baseband quantization noise resulting from the delta-sigma modulator. One advantage of the oversampling and subsequent decimation approach is that the analog anti-alias filter requirements are relaxed. This advantage of oversampling and decimation can be exploited by any ADC by sampling at super-Nyquist. The particular need for a sharp anti-alias filter function, whether largely accomplished in the analog or digital domain, depends on the application. In situations where input filtering is not required, the delta-sigma oversampled ADC presents the disadvantage of requiring oversampling and decimation to attenuate out-of baseband quantization noise. In a limited set of situations that can tolerate the elevated sampling rate and the resulting data redundancy, the decimation can be waived. If the resulting data needs to be stored in memory or recorded on to media of finite size, then decimation is required, regardless of ADC type.

#### 2.1.6 Cyclic ADCs

These ADCs are a class of algorithmic structures [15] similar to subranging ADCs except the same stage is reused. The digital self-calibration technique can be applied to a cyclic

Figure 2.5: Delta-sigma oversampled ADC architecture.

ADC resulting in a compact structure capable of high-resolution. An advantage of the cyclic ADC is that the analog and digital hardware required is reduced. Thus, the digital self-calibration logic requirements collapse to a single accumulator, small memory and controller for the cyclic ADC. The cyclic ADC technique can potentially replace delta-sigma structures because of the simplicity of the digital self-calibration technique. If oversampling is elected to relax the input filtering requirements, then the comparison to be made is between the cyclic ADC employing digital self-calibration and a high-order delta-sigma modulator. If decimation is needed, then either approach would require the same decimator structure. The cyclic approach, with digital self-calibration applied, decouples the achievable resolution from oversampling ratio. Thus, if oversampling is chosen to relax the input filtering requirements, the oversampling ratio can be chosen independent of the resolution. In many cases, oversampling ratios between 2 and 8 are sufficient to greatly relax the input filtering requirements.

# 2.2 Previous Studies in Pipeline ADC Calibration Techniques

## 2.2.1 A 12 bit 600 kS/s Digitally Self-Calibrated Pipelined Algorithmic ADC

This paper [33] discusses a digital self-calibration scheme for a radix-2, 1.5-bit per stage pipeline ADCs. This scheme employs 2 comparators per stage in order to resolve 1.5 bits per stage. A digital error-correction scheme is used so that the pipeline ADC is tolerant to large comparator error. In the design presented,  $\pm 0.25$  Least Significant Bit (LSB) comparator offset can be tolerated per stage. This is an important advantage for high-speed, low cost implementation in MOS based processes.

#### **Digital Error-Correction**

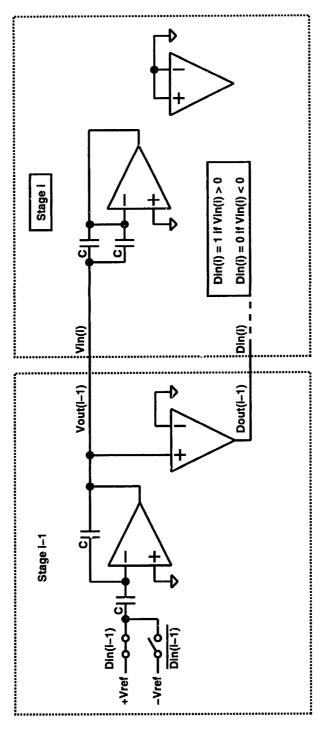

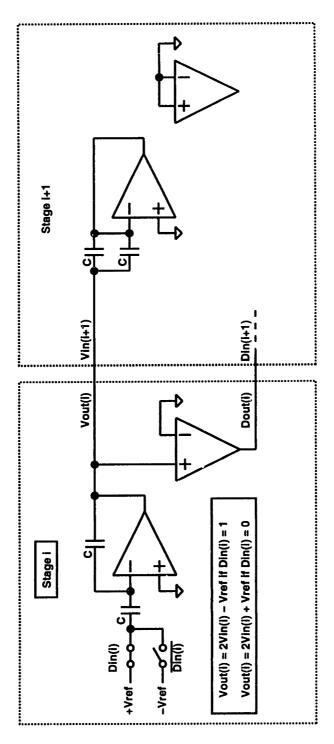

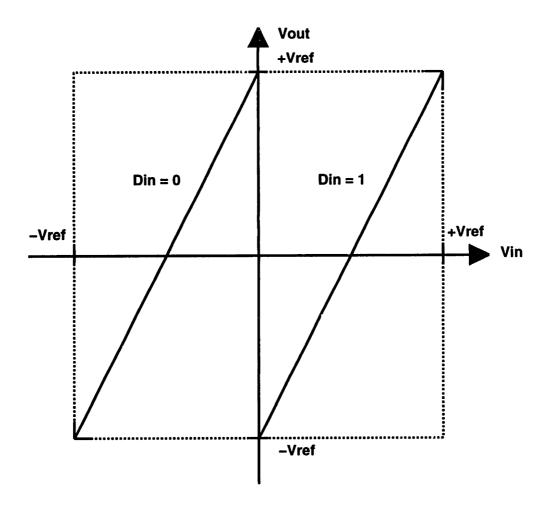

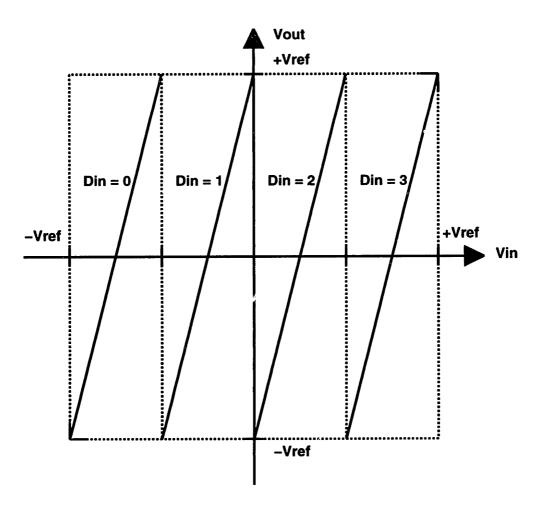

Two comparators are used to determine which of three contiguous regions the residue output is within. The output of each stage is  $V_{out} = 2V_{in}(i) - D(i)V_{ref}$  where i is the stage index and where D(i) = -1, 0, +1. The operation of this scheme is outlined in detail in [47]. The basic idea is to use a redundant coding scheme so that multiple digital output words can represent the same analog input, even in the presence of large comparator errors. Digital logic is then used to derive the correct digital output.

#### **Digital Self-Calibration**

The basic approach used is to measure the offset and gain error resulting from each stage by applying certain analog inputs to each stage and observing the digital output that results. In this scheme, each stage in the pipeline is measured without using results from stages deeper in the pipeline. The scheme depends on the offset and gain error being relatively small. However, one disadvantage of this digital self-calibration scheme is that it measures

the calibration data under different conditions in the calibration mode compared to the actual run mode so that the achievable accuracy is more limited compared to the digital self-calibration technique presented in this thesis [34].

## 2.2.2 Digital-Domain Calibration of Multistep Analog-to-Digital Converters

This work [48, 49] outlines a digital self-calibration technique for multi-step ADCs. Digital error-correction is used to relax comparator offset requirements. This digital error-correction makes use of 1-bit of overlap between the first and second stage of a two-step, subranging ADC. This scheme avoids the use of external DACs used for calibration in traditional approaches. As a result, only digital logic needs to be added to the basic, digital error corrected two-step ADC described in this paper.

#### **Multi-Step Architecture**

The primary disadvantage of this technique is that it employs a capacitor array in order to obtain accurate closed loop gain for the two-step implementation shown in this work. For pipeline ADCs with many stages, capacitor arrays consume large area and present large load capacitance to high-speed op-amps. The digital-domain calibration here also introduces accumulation of truncation error leading to interstage gain error for many stages employed in pipeline ADCs.

#### **Segmented Transfer Characteristic**

The principle used in this work is to consider the ADC transfer characteristic as a synthesis of segments. Ideally, the segments are collinear. However, for a two-step ADC, errors in the DAC reconstruction levels leads to disjoint segments. The calibration must span the entire transfer characteristic and the number of calibration points needed depends on how many segments are desired. It is desirable to use as many segments as possible in order to relax the linearity required for each segment. This is a disadvantage for high-resolution ADCs based on the large number of segments that would become necessary. A competing concern is the digital truncation error that this scheme introduces, which is minimized when the number of segments is minimized.

## 2.2.3 A 13 bit 2.5MHz Self-Calibrated Pipelined A/D Converter in $3\mu m$ CMOS

In this work [50, 37, 51], a self-calibrating pipeline ADC is described. This approach utilizes digital error-correction to account for comparator errors. Binary weighted capacitor arrays are used to correct for gain stage errors. This scheme avoids the use of external data converters for the calibration.

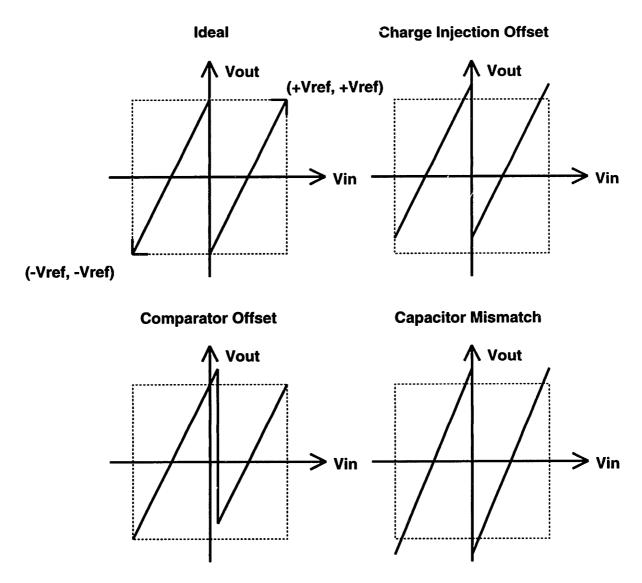

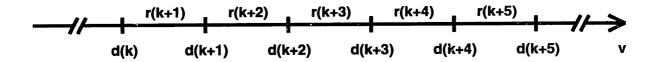

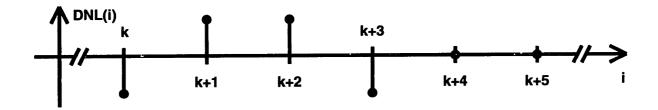

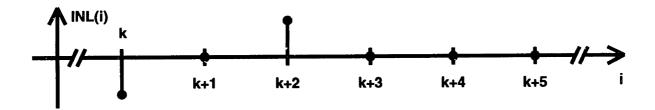

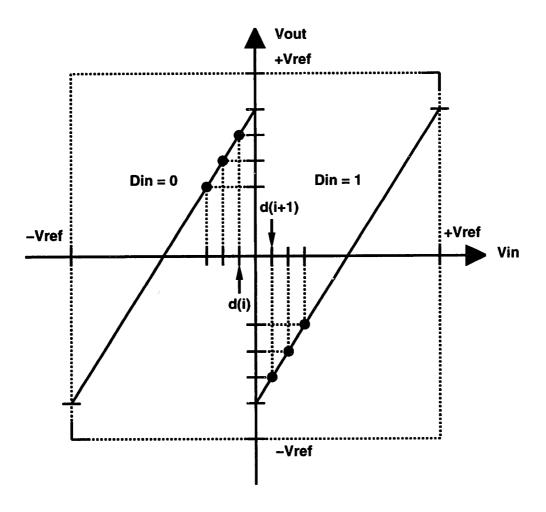

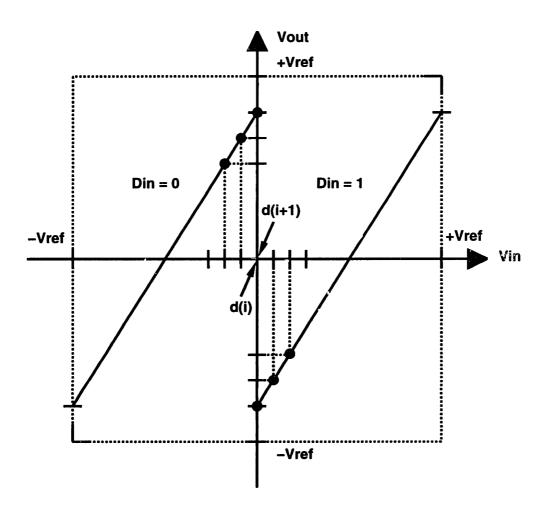

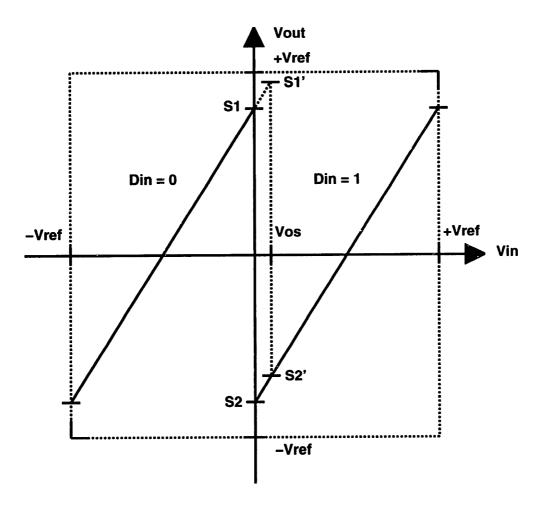

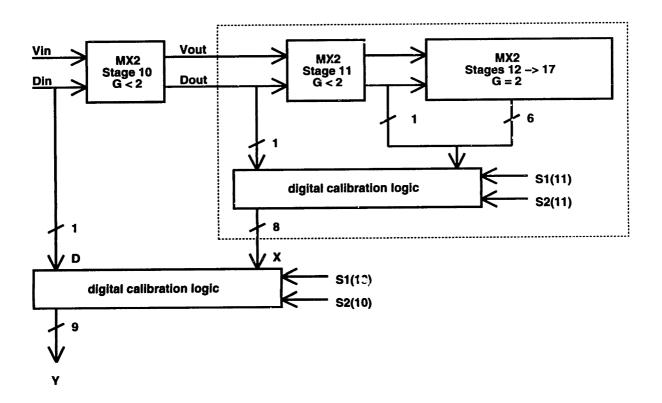

#### **Analog Calibration**