### Development of a Scalable Superconducting Memory

by

Brenden A. Butters

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2018

© Massachusetts Institute of Technology 2018. All rights reserved.

## Signature redacted

Author ...... Department of Electrical Engineering and Computer Science August 31, 2018

# Signature redacted

Certified by ...... Kafl K. Berggren Professor of Electrical Engineering and Computer Science Thesis Supervisor

# Signature redacted

Accepted by .....

Leslie A. Kolodziejski Professor of Electrical Engineering and Computer Science Chair, Department Committee on Graduate Students

77 Massachusetts Avenue Cambridge, MA 02139 http://libraries.mit.edu/ask

### DISCLAIMER NOTICE

Due to the condition of the original material, there are unavoidable flaws in this reproduction. We have made every effort possible to provide you with the best copy available.

Thank you.

The images contained in this document are of the best quality available.

#### **Development of a Scalable Superconducting Memory**

by

Brenden A. Butters

Submitted to the Department of Electrical Engineering and Computer Science on August 31, 2018, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

#### Abstract

Superconducting computers promise very high computation speeds while also consuming far less power than their conventional counterparts. However, much of the progress in this field has been stymied by the lack of a scalable superconducting memory technology. In this thesis, I present the design of, and demonstrate the operation of, a superconducting nanowire-based memory cell. In contrast to existing designs, this cell operates by means of kinetic rather than geometric inductance. Thus, the cell size can be made much smaller than would otherwise be possible. With the successful operation of the single cell, paths to larger arrays are explored, and a small array demonstrated. The further development of the technology demonstrated in this work will allow for the production of large-scale superconducting processors, and the eventual development of superconducting supercomputers.

Thesis Supervisor: Karl K. Berggren Title: Professor of Electrical Engineering and Computer Science

### Acknowledgments

Much of the work presented in this thesis would not be possible without the efforts of many of my colleagues. I would like to acknowledge:

My advisor, Prof. Karl Berggren, for his insights, his encouragement, and his dedication to the development of his students. His enthusiasm for our work really kept the project going – even when everything seemed to be going wrong.

Adam McCaughan, for his development of the nanocryotron devices, used extensively in this work, and for his initial efforts towards the superconducting memory project.

Qing-Yuan Zhao, for his contribution towards the non-destructive memory covered in chapter 2, and for the fabrication of the devices covered in chapters 2 and 3.

Reza Baghdadi, for the contributions towards, and fabrication of, the devices presented in chapter 4.

Emily Toomey, for her helpful discussions, and extensive experimental assistance.

Murat Onen, for his help with simulating designs, and experimental assistance.

Dorothy Fleischer, for helping keep me organized, and for her ever-helpful attitude and generosity.

Di Zhu, Marco Colangelo, and Andrew Dane, for their input, collaborations, and experimental assistance.

The work that I conducted in pursuit of this thesis, and other in other related projects, was only made possible by the support and advice that I received from my family, and friends. In particular, I would like to thank:

Dr. Raad Raad, for supporting my research, for all his help and encouragement, and for the many hours of discussions we have had over the years. Without his influence I would likely not have made it to where I am today.

Tony and Joe – truly the best MIT has to offer.

Finally, I would particularly like to thank my parents for their unwavering support and dedication. I am forever grateful for the sacrifices that they have made in order for me to pursue the path that has lead to this thesis being written.

## Contents

| 1 | Introduction 47                |                             |                                                     |          |  |  |  |

|---|--------------------------------|-----------------------------|-----------------------------------------------------|----------|--|--|--|

|   | 1.1                            | Supere                      | conductivity and superconducting circuit components | 47       |  |  |  |

|   |                                | 1.1.1                       | Josephson junctions                                 | 48       |  |  |  |

|   |                                | 1.1.2                       | Superconducting nanowires                           | 51       |  |  |  |

|   |                                | 1.1.3                       | Kinetic inductance in nanowires                     | 52       |  |  |  |

|   |                                | 1.1.4                       | Circuit model of superconductivity                  | 53       |  |  |  |

|   |                                | 1.1.5                       | The cryotron                                        | 54       |  |  |  |

|   | 1.2                            | conducting nanowire devices | 56                                                  |          |  |  |  |

|   |                                | 1.2.1                       | Constriction                                        | 57       |  |  |  |

|   |                                | 1.2.2                       | nTron                                               | 59       |  |  |  |

|   |                                | 1.2.3                       | hTron                                               | 62       |  |  |  |

|   |                                | 1.2.4                       | yTron                                               | 65       |  |  |  |

|   | 1.3                            | Superc                      | conducting memories                                 | 67       |  |  |  |

|   |                                | 1.3.1                       | Need for a cryogenic-compatible memory              | 68       |  |  |  |

|   |                                | 1.3.2                       | Existing memory technologies                        | 68       |  |  |  |

|   | 1.4                            | Thesis goal                 |                                                     |          |  |  |  |

|   | 1.5                            | Thesis                      | outline                                             | 70       |  |  |  |

| 2 | Non-destructive readout memory |                             |                                                     |          |  |  |  |

| - | 2.1 Memory approach            |                             |                                                     |          |  |  |  |

|   | 2.1                            |                             |                                                     |          |  |  |  |

|   | 4.4                            | 2.2.1                       | O cell operating principals                         | 77<br>78 |  |  |  |

|   |                                | 2.2.1                       |                                                     | 80       |  |  |  |

|   |                                | 4.4.4                       | Reading from the memory                             | ðU       |  |  |  |

|   |     | 2.2.3        | Cell design limitations and trade-offs     | 82   |

|---|-----|--------------|--------------------------------------------|------|

|   |     | 2.2.4        | Cell layout                                | 85   |

|   | 2.3 | Cell si      | mulation                                   | 87   |

|   | 2.4 | Basic        | NDRO cell measurements                     | 92   |

|   |     | 2.4.1        | General immersion measurement procedure    | 93   |

|   |     | 2.4.2        | Initial NDRO measurement setup             | 96   |

|   |     | 2.4.3        | IV Curves                                  | 96   |

|   |     | 2.4.4        | Experimental setup                         | 100  |

|   |     | 2.4.5        | Memory operation results                   | 105  |

|   | 2.5 | Revise       | ed design                                  | 111  |

|   |     | 2.5.1        | Revised cell design                        | 111  |

|   |     | 2.5.2        | Low error rate measurement setup           | 113  |

|   |     | 2.5.3        | Experimental results                       | 115  |

| 3 | ND  | RO ar        | ray design                                 | 119  |

|   | 3.1 |              | architecture                               | 119  |

|   |     | 3.1.1        | Resistively isolated design                | 120  |

|   |     | 3.1.2        | Multiplexed column design                  | 126  |

|   |     | 3.1.3        | Array design size and power comparison     | 128  |

|   | 3.2 | Multi        | plexer design                              | 132  |

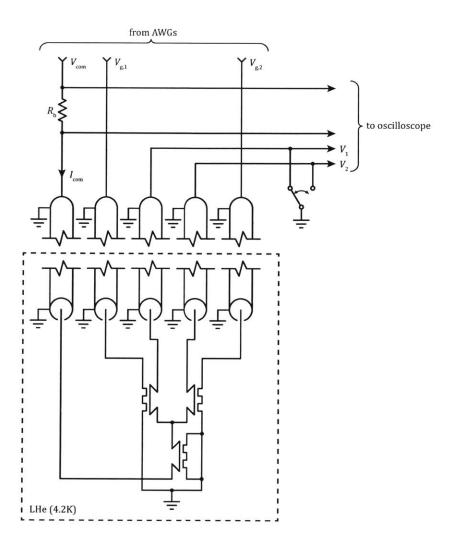

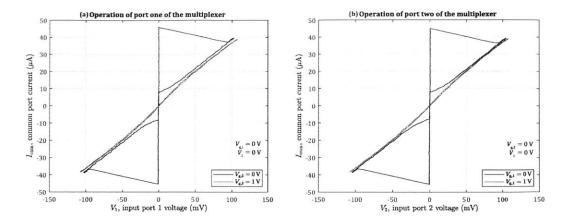

|   |     | 3.2.1        | Multiplexer operation                      | 133  |

|   |     | 3.2.2        | Superconducting multiplexer implementation | 135  |

|   |     | 3.2.3        | Prototype multiplexer testing              | 137  |

|   | ъ   | , , <b>.</b> |                                            | 1 40 |

| 4 |     |              | ve readout cell and array design           | 143  |

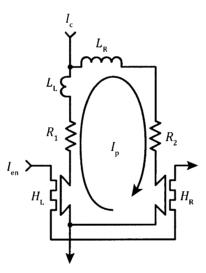

|   | 4.1 | -            | ting principal of the DRO cell             | 144  |

|   |     | 4.1.1        | Writing to the memory                      | 145  |

|   |     | 4.1.2        | Reading from the memory                    | 146  |

|   |     | 4.1.3        | Cell design limitations and trade-offs     | 147  |

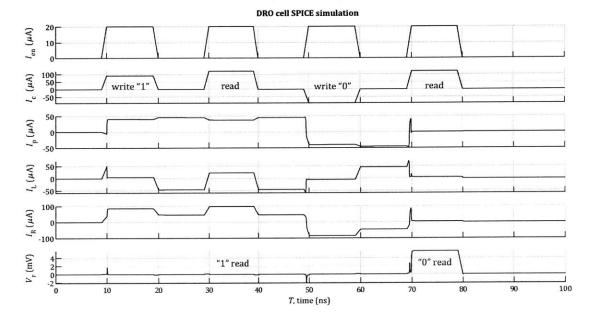

|   |     | 4.1.4        | Cell simulations                           | 149  |

|   |     | 4.1.5        | Cell layout                                | 152  |

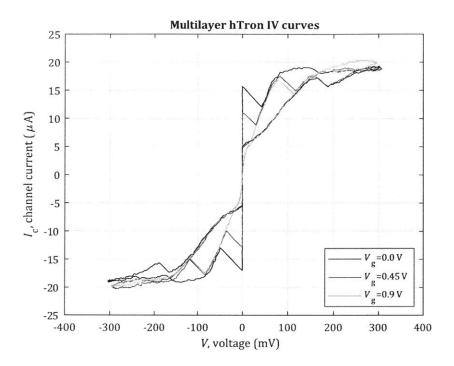

|   | 4.2                                        | 4.2 Multilayer hTron |                                                                         |       |  |  |  |  |

|---|--------------------------------------------|----------------------|-------------------------------------------------------------------------|-------|--|--|--|--|

|   |                                            | 4.2.1                | Design                                                                  | 154   |  |  |  |  |

|   |                                            | 4.2.2                | Experimental results                                                    | 156   |  |  |  |  |

|   | 4.3                                        | DRO                  | array design                                                            | 158   |  |  |  |  |

|   |                                            | 4.3.1                | Array design                                                            | 159   |  |  |  |  |

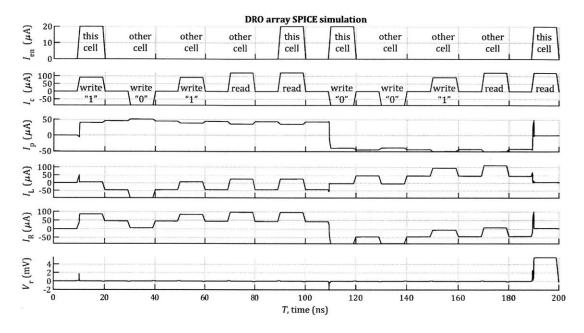

|   |                                            | 4.3.2                | Array simulations                                                       | 161   |  |  |  |  |

|   | 4.4                                        | Testin               | g the initial DRO array design                                          | 163   |  |  |  |  |

|   |                                            | 4.4.1                | Initial cell experiments                                                | 163   |  |  |  |  |

|   |                                            | 4.4.2                | Debugging design – magnetic modulation of cell switching curren         | nt167 |  |  |  |  |

|   | 4.5                                        | Design               | n revision                                                              | 170   |  |  |  |  |

|   |                                            | 4.5.1                | Automated array testing                                                 | 172   |  |  |  |  |

|   |                                            | 4.5.2                | Isolated unselected cell testing                                        | 175   |  |  |  |  |

|   |                                            | 4.5.3                | h<br>Tron distributions in helium immersion measurements                | 177   |  |  |  |  |

|   | 4.6                                        | Refine               | d test procedure and experimental results $\ldots \ldots \ldots \ldots$ | 179   |  |  |  |  |

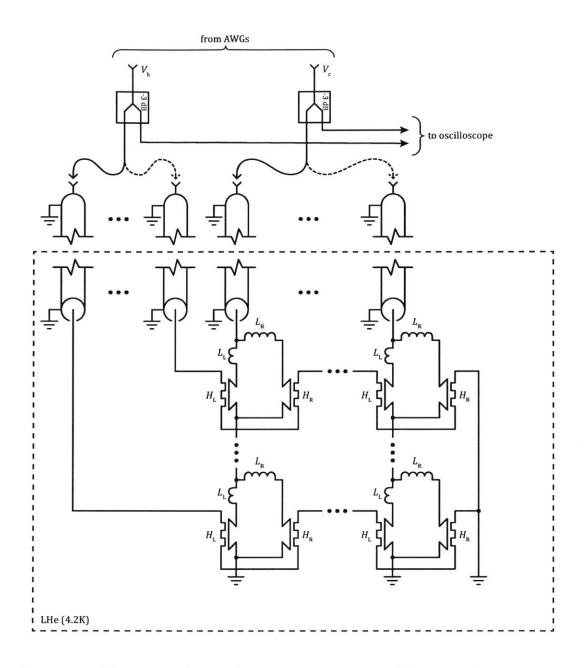

| 5 | Experimental setup and apparatus design 18 |                      |                                                                         |       |  |  |  |  |

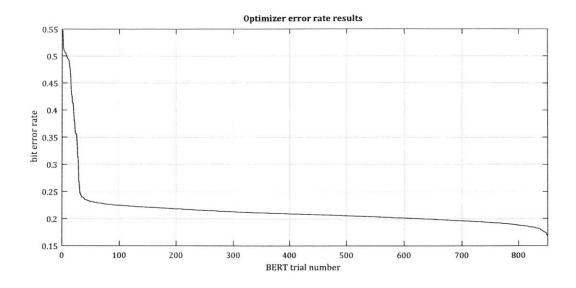

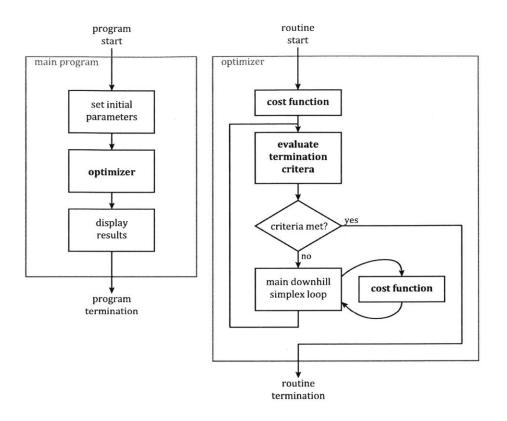

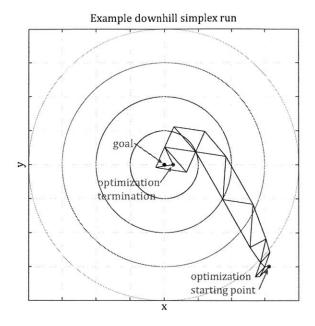

|   | 5.1                                        | Automated testing    |                                                                         |       |  |  |  |  |

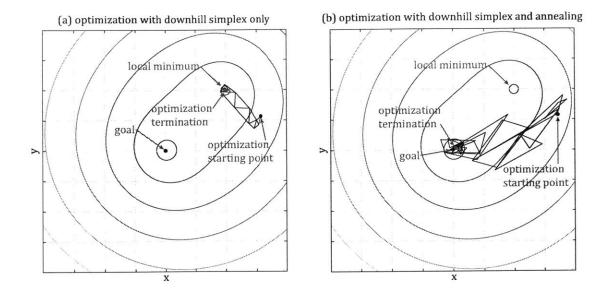

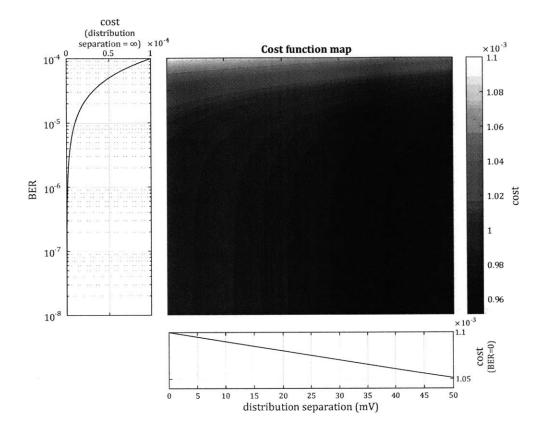

|   |                                            | 5.1.1                | Integrated optimizer                                                    | 189   |  |  |  |  |

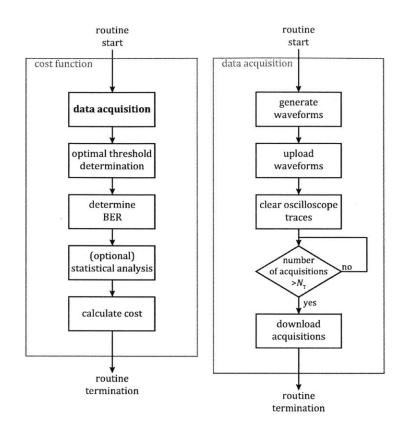

|   |                                            | 5.1.2                | Cost function                                                           | 192   |  |  |  |  |

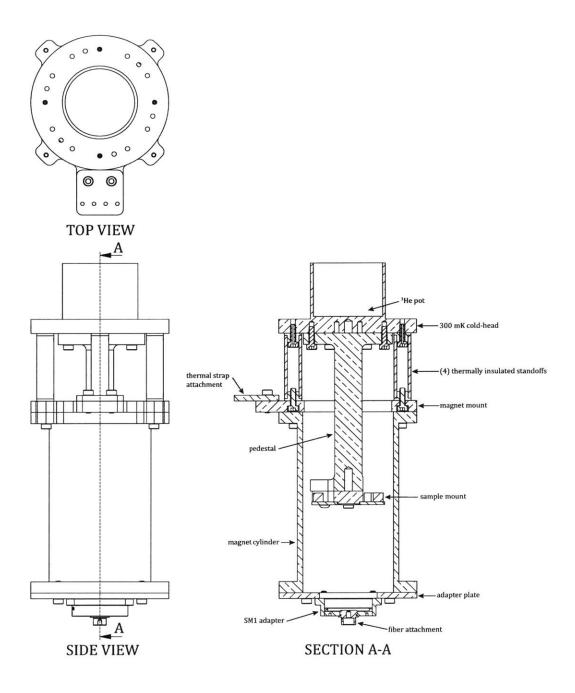

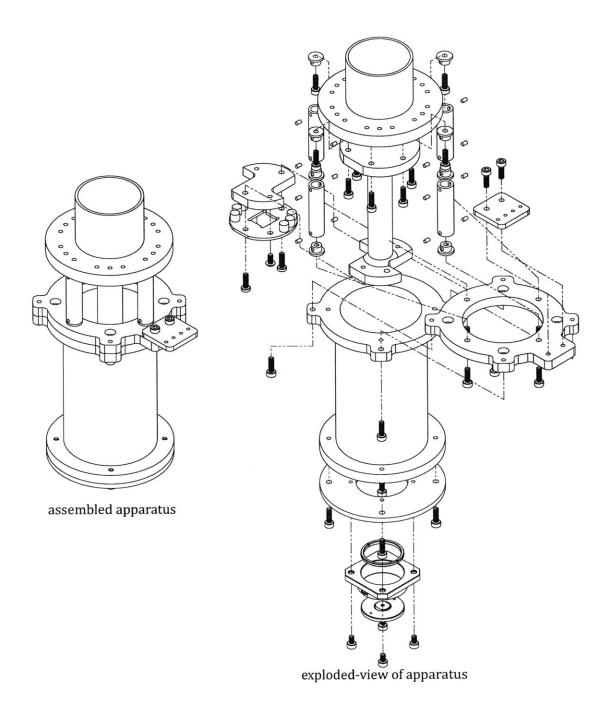

|   | 5.2                                        | Desigr               | and construction of cryogen-free magnetic-modulation experi-            |       |  |  |  |  |

|   |                                            | menta                | l apparatus                                                             | 199   |  |  |  |  |

|   |                                            | 5.2.1                | Overview of design                                                      | 200   |  |  |  |  |

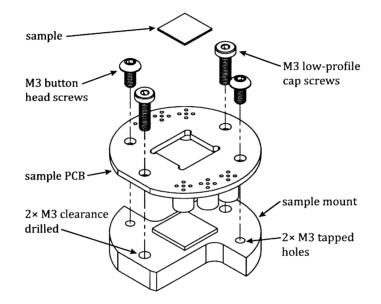

|   |                                            | 5.2.2                | Sample mount                                                            | 204   |  |  |  |  |

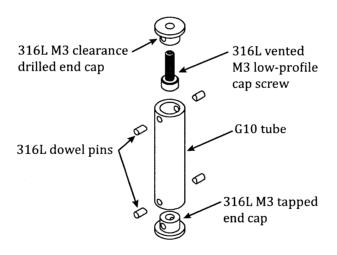

|   |                                            | 5.2.3                | Thermally insulated standoffs                                           | 206   |  |  |  |  |

| 6 | Con                                        | clusio               | n and future work                                                       | 211   |  |  |  |  |

## List of Figures

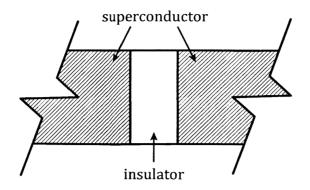

1-1 Schematic showing the basic structure of a Josephson junction. The distance between the two superconducting materials must be very small in order for tunneling to occur. When an insulator is used to separate the superconductors the junction is referred to as a SIS junction. It is also possible to use a normal metal, in place of the insulator, to crease a SNS junction, it is even possible to use a weaker superconductor to form a SsS junction.

49

50

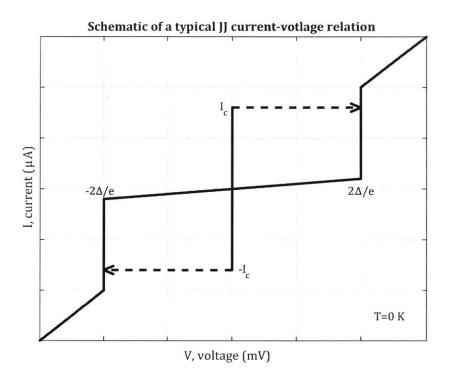

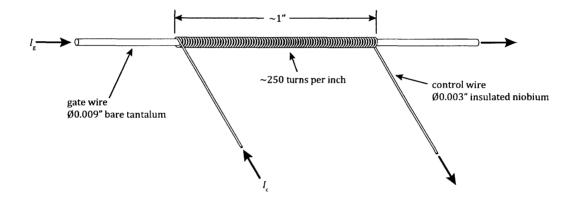

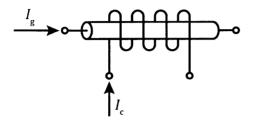

1-2 Current-voltage relation of a typical Josephson junction. The junction can pass a current with no voltage drop provided the current is less than the critical current  $I_c$ . When the critical current is exceeded the junction switches operating mode and presents a voltage  $2\Delta/e$ where  $\Delta$  is the superconducting gap, and e is the elementary charge. If the current is increased the junction behaved as a resistor. Upon decreasing the current, when close to zero the junction will return to a zero voltage drop. Note that the IV curve is rotationally symmetric, and that structure of the junction is intrinsically symmetric. . . . . 1-3 Schematic drawing of a typical cryotron used by Buck. The device consists of a  $\emptyset 0.009$ " uncoated tantalum gate wire wrapped with around 250 turns of a  $\emptyset 0.003$ " insulated niobium control wire. When a current  $I_c$  is applied to the control wire, a magnetic field is induced in the solenoid. This field suppresses superconductivity in the gate wire. As  $I_c$  is increased, the gate current  $I_g$  that the wire can support without transitioning to the normal region will progressively decrease. A greater suppression of superconductivity occurs in the gate wire than the control wire owing to the gate having a lower  $T_c$ , and lower  $B_c$ .

54

55

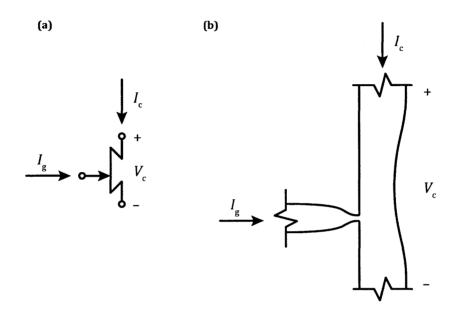

- 1-4 Schematic symbol for a cryotron, as proposed by Buck. This symbol is derived from the structure of the cryotron with the control wire depicted as a coil around a thicker conductor, that being the gate. Additionally, the symbol graphically demonstrates that the cryotron does not behave differently if the currents  $I_c$  and/or  $I_g$  are reversed in direction, as only their magnitudes is of importance.

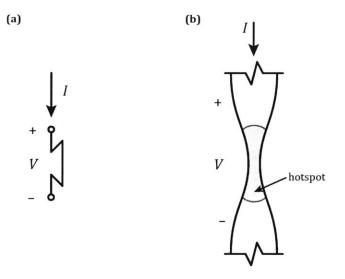

- 1-5 Schematic symbol for a superconducting nanowire constriction (a), and a sketch of the layout of a constriction (b). There is no generally accepted symbol for a nanowire, we will use this symbol throughout this work. The constriction shown in (b) has been switched to the "normal" state. While the vast majority of the wire is still superconducting, there exists a hotspot at the narrowest region of the wire – where the current density is the highest. As a current I is being applied to the constriction, a voltage V will be dropped across the normal region. The magnitude of the current I can cause the hotspot to grow or shrink. If the bias I is lowered sufficiently then the hotspot will vanish and the constriction return to the superconducting state. The jog lines indicate where the constriction would be connected to the rest of a circuit.

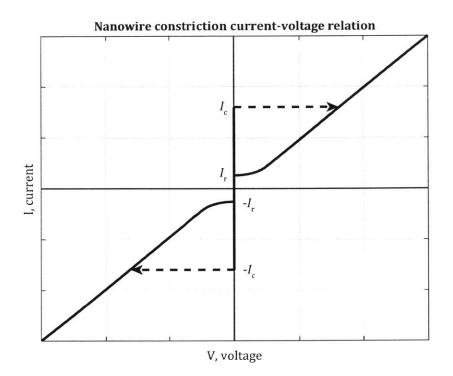

1-6 Sketch of the current-voltage relation for a single current-biased superconducting constriction. The constriction can carry any current without developing a voltage, provided that the magnitude of the current is less than the critical current  $I_c$ . If  $I_c$  is exceeded, then the device will enter the resistive state. Once in the resistive state, the device behaves similar to a resistor. From the resistive state, if the current is lowered to below the retrapping current  $I_r$ , then the device will return to the superconducting state. Note that the IV curve is rotationally symmetric, and that switching and retrapping only depends on the magnitude of the current.

59

60

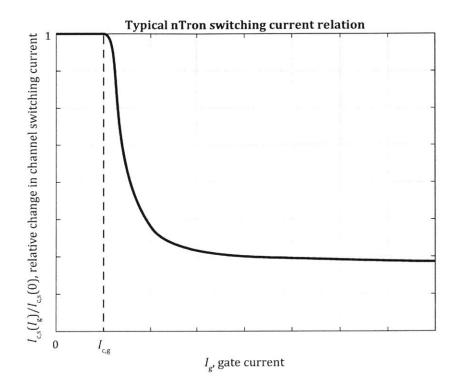

1-8 Sketch of a typical nTron suppression curve. The switching current of the channel  $I_{c,s}$  is a function of the gate current  $I_g$ . The switching current of the channel is largely unaffected by the gate current while the gate is superconducting. That is, when the gate current is less than its critical value  $I_{c,g}$  and no hot spot has formed, there is little modulation of the channel switching current by the gate current. Once the gate switches, and a hotspot forms, the channel is rapidly suppressed by the gate current. This rapid suppression leads to an operating region in which the nTron possesses a very high gain. This effect begins to diminish with the application of increasing gate current.

61

63

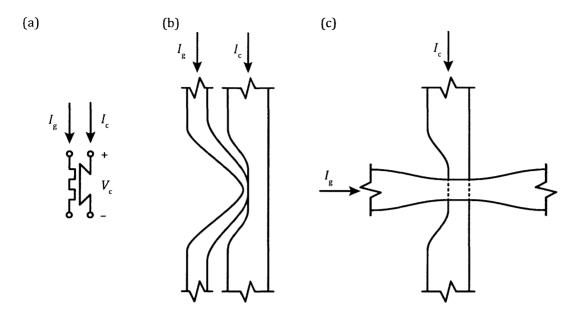

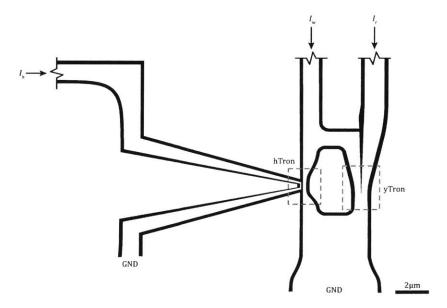

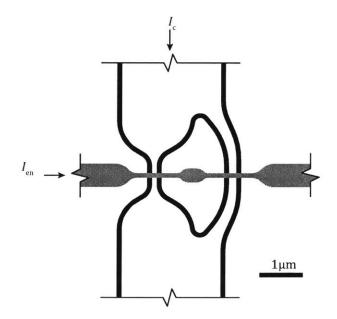

1-9 The schematic symbol (a) for the hTron, a sketch of an in-plane hTron layout (b), and a sketch of the layout for a multilayer, or stacked, hTron (c). The in-plane hTron is typically constructed from the same superconducting film. This allows the gate to be located relatively close to the channel – within 100 nm. The multilayer hTron can be fabricated with either a normal or superconducting gate. The gate can be within 30 nm of the channel as it is only separated by a dielectric layer. For the in-plane hTron the geometry of the channel and gate are limited by the need to keep them in close proximity, while also avoiding current crowding in the channel. For the multilayer hTron design, the channel and gate can have almost any geometry required, provided there is some location where they overlap – or at last come close to each other. While many different geometries are possible, typically, the gate and channel cross at a right angle, as shown here. . . . . . .

64

66

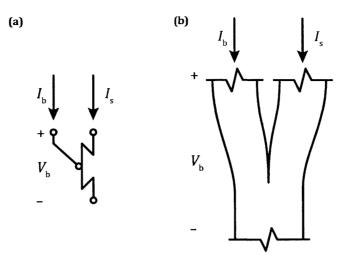

1-11 Schematic symbol for a yTron (a), and a sketch of a typical yTron layout. The sense current  $I_s$ , is the current to be measured nondestructively. If the yTron is operated correctly, this current should never be interrupted. The sense current is determined by applying a bias current  $I_b$  while monitoring the bias voltage  $V_b$ . With a low sense current, a relatively low bias current is required to switch the bias port, due to the high current crowding that occurs on the yTron corner. On the other hand, when a high positive sense current is applied, the bias current that is required to switch the bias port is comparatively higher than in the low bias case. This increase in switching current is due to the decreased current crowding that occurs when the biases applied to the ports are similar.

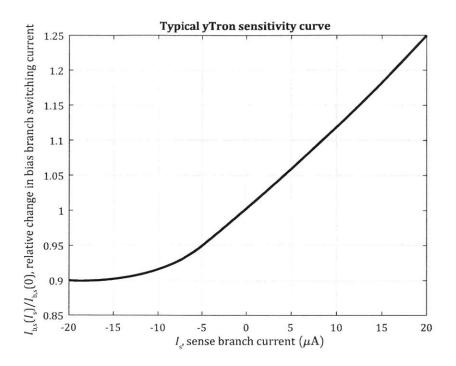

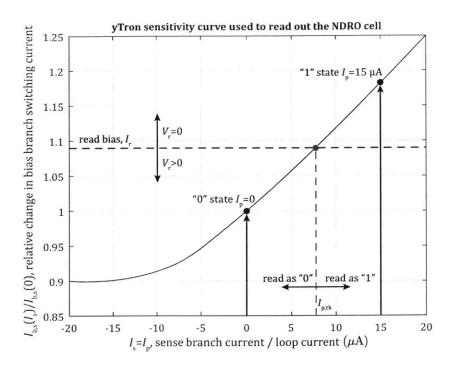

- 1-12 Sketch of the sensitivity curve of a typical yTron. This sketch is adapted from experiential results. In contrast to the other nanowire devices presented here, the switching current of the yTron increases with the increased application of an external current – the sense current. This effect will only occur over a region where the sense arm has not switched. Once the sense arm switches, then the yTron begins to behave as an nTron. While the sense arm is superconducting, we have that the bias arm switching current  $I_{m,s}(I_s)$  increases with increasing sense current  $I_s$ . With the application of a negative sense branch current, the switching current can be seen to decrease, but only to around 90% of its zero-bias value. The yTron is intended to operate with positive  $I_s$ . The sensitivity curve of the yTron is injective, and thus allows for the sense current to be measured without disrupting the supercurrent. 67

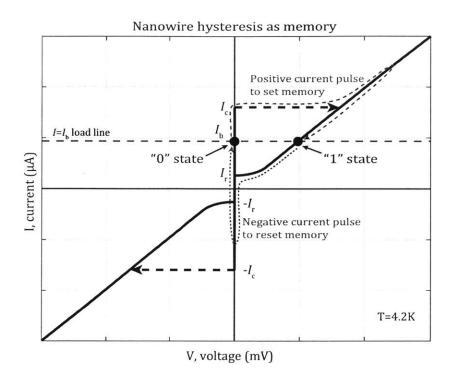

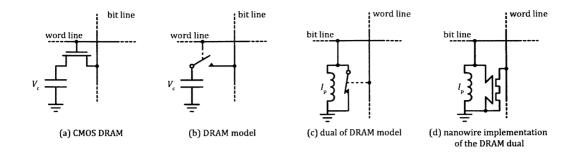

- 2-2 Derivation of a superconducting dual of a CMOS DRAM cell. (a) a typical DRAM cell as implemented in CMOS; (b) a simplified model of the CMOS DRAM cell where the enhancement mode MOSFET has been replaced by a normally open switch; (c) the dual of the simplified circuit, note that the switch is now normally closed. The capacitor voltage  $V_c$  which previously held the state of the cell is now a persistent current  $I_p$ , the magnitude and/or sign of which can now be used to store the state of the cell; (d) a nanowire implementation of the dual circuit where the normally closed switch has been replaced with a hTron. . .

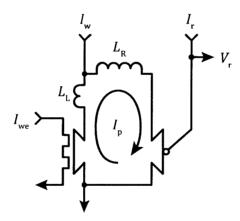

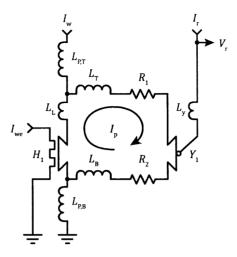

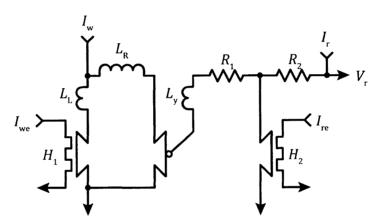

- 2-3 Simplified schematic of a basic NDRO cell. The device has three ports, namely a write enable, a write port, and a read port. The loop which carries the persistent current  $I_p$ , consists of the channel of the hTron, the yTron, and the two inductors  $L_L$  and  $L_R$  where  $L_L < L_R$ . The write enable port is galvanically isolated from the loop. . . . . . .

- 2-5 Sketch of a typical yTron sensitivity curve based on experimental results, that has been annotated to show the operation of the yTron memory readout. When the yTron is used to read the loop current, we have the sense current is the loop current,  $I_{\rm s} = I_{\rm p}$ . In this example, the yTron is biased at  $I_{\rm r} = 1.09I_{\rm b,s}(0)$ , that is 9% over the zero bias switching current of the yTron. At this point we have the corresponding loop current  $I_{\rm p,th}$  is approximately mid-way between the "0" state loop current and the "1" state loop current. Thus, the yTron voltage  $V_{\rm r}$  will be zero if the memory is in the "1" state, since the loop current will be  $I_{\rm b,s}(I_{\rm p}) > I_{\rm r}$ . Conversely, if the memory is in the "0" state, then the loop current will be low and  $I_{\rm b,s}(I_{\rm p}) < I_{\rm r}$ , so the read bias will be sufficient to switch the bias arm of the yTron and so  $V_{\rm r} > 0$ . . . . . .

76

79

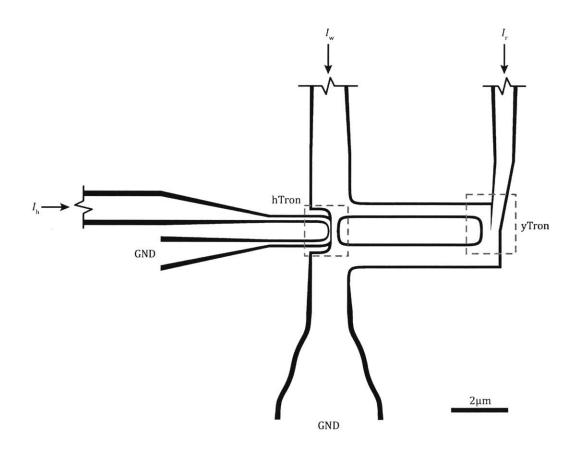

- 2-6 Layout of a compact NDRO cell used in the first set of measurements. The design shown is the exact layout of the device tested in section 2.4. The black area indicates where NbN has been etched away (leaving the bare substrate below), and the white area is where NbN remains. The drawing is shown this way because a positive tone resist was used, so the black area is where the resist was exposed. The jog lines indicate leads that extent to connection pads. Note, the hTron and yTron have been highlighted by a dashed box around each device. . . . . . . . .

- 2-7 Schematic used in the LTspice simulation of the NDRO cell. Note the inclusion of the two resistors  $R_1$  and  $R_2$  which are not physical, but are included so that LTspice will reliably converge. This approximation is valid for small values of these resistors and for short time scales. . . .

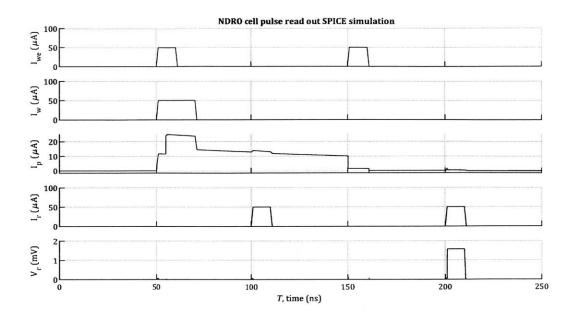

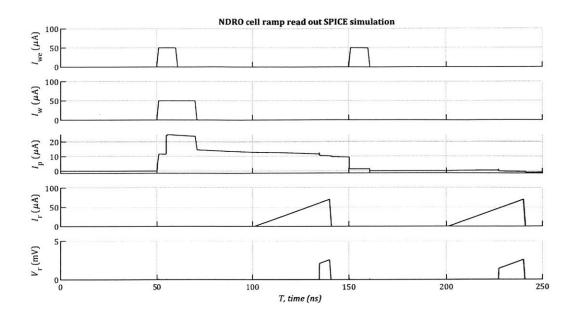

- 2-8 Results of a simple LTspice simulation of a single NDRO cell operated in the pulse readout modus. In this simulation, the cell is set (placed in the "1" state) at 50 ns. At this time, the loop current  $I_p$  can be seen to increase – indicating that the write was successful. The cell is then read at 100 ns. During the read, the yTron does not switch, as expected when the cell is set. The cell cleared (placed in the "0" state) at 150 ns. Again, the loop current can be seen to respond accordingly by reducing to zero. Finally, at 200 ns the memory is read again, but this time the yTron switches. The switching of the yTron indicates that the read was successful, and that, at least in this simulation, the memory is working as expected. Note that the loop current can be seen here to be decaying. This decay is an artifact of the simulation, specifically the resistors  $R_1$ , and  $R_2$ . In reality there is no decay in the loop current.

85

- 2-9 Results of a simple LTspice simulation of a single NDRO cell operated in the ramp readout modus. The write portions of this simulation are identical to those used in figure 2-8. The ramped readout current can be seen to show the switching current of the read port being modulated by the persistent current  $I_p$ . When the cell is in the "1" state with a high persistent current, the read port switching current can be seen to be higher than when the cell is in the "0" state with a zero persistent current.

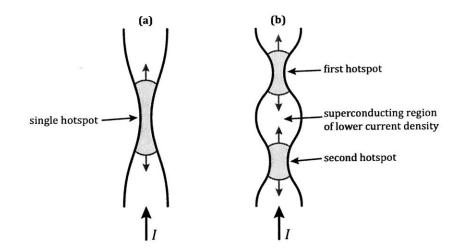

- 2-11 Depiction of the theorized hotspot growth in two different nanowire geometries. Both nanowires are exposed to a monotonically increasing current *I*. This current eventually leads to the switching of the single constriction in (a) and the first constriction in (b). As the current continues to increase, the hotspots will grow in the directions indicated by the gray arrows. In (a), the IV curve will not exhibit any steps other than the first switching event; however, due to the non-constant cross section of the nanowire, the IV curve will depict a curve. In (b), the IV curve will be similar to (a) at first, as the hot spot continues to grow. At some point however, the current density at the second construction will cause superconductivity to breakdown at this location, and a second hotspot will form. The formation of this second hotspot will result in a second step in the IV curve (separate from the first constriction switching). Thus, we can see how the non-constant width of the nanowire can lead to the IV curve exhibiting curves and steps.

97

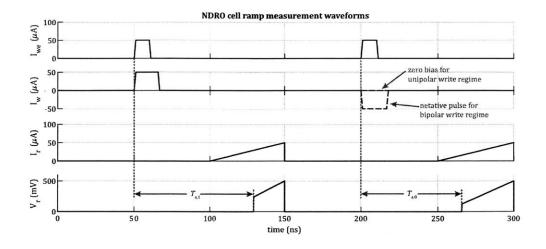

2-12 Schematic of the NDRO cell write and ramp readout scheme. This figure features two write/read cycles. The first operation, at 50 ns, is a set operation. Note that the channel bias is applied held after the deassertion of the write enable. The yTron switching current is them measured by applying a ramp to the read port. At some point the yTron switches and a voltage is seen at the read port. The time delay between the start of the write operation and the switching of the yTron is used to determine the current required to switch the yTron. At 200 ns the memory is cleared, for the unipolar wire scheme, the write bias is set to zero for this operation, and for the bipolar write scheme, the write bias is a negative pulse (the inverse of the set pulse shape). Again the memory is read out by applying a ramping current to the yTron. After a clear the switching current of the yTron should be lower than after a set, so we expect the skew times  $T_{s,0} < T_{s,1}$ . The time until the device switches is used as the oscilloscope has more time resolution than voltage resolution, and so a better estimate of the switching current can be obtained by this method. . . . . . . . . . . 101

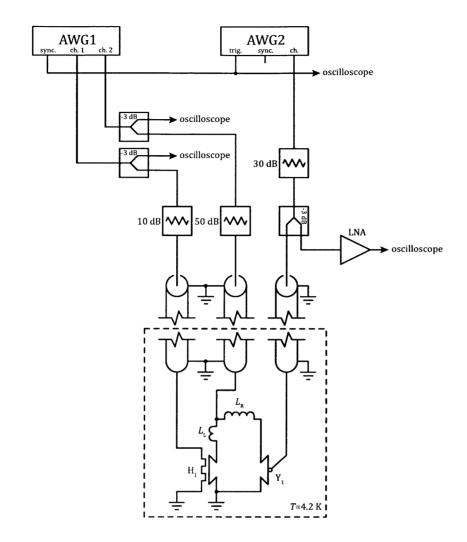

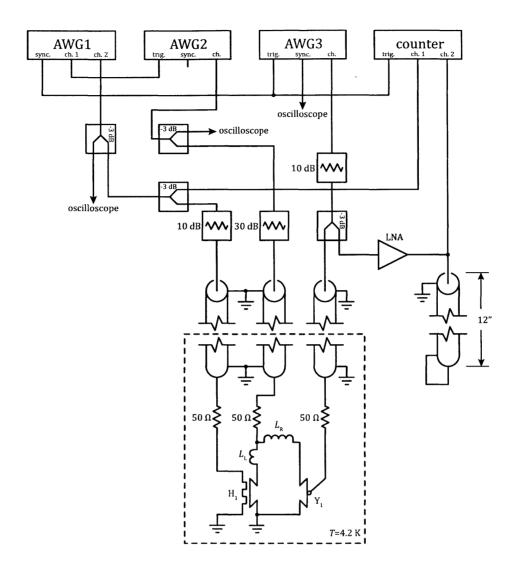

2-13 Experimental setup for basic NDRO measurements. AWG1 was used to control the write operation. AWG2 is triggered by AWG1, and after some delay, initiates the read operation. In order to minimize reflections, and enable high-speed operation, a system impedance of  $Z_0 = 50 \Omega$  was used. As the devices required relatively small currents to operate, attenuators were used to reduce signal amplitudes. To enable the oscilloscope to monitor the signals, splitters were added. 103

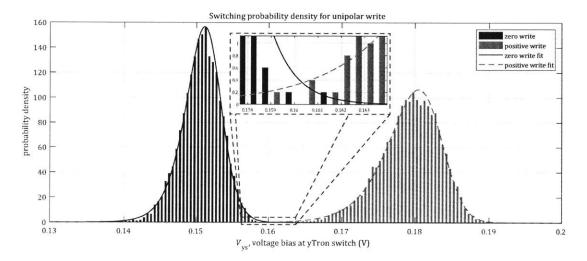

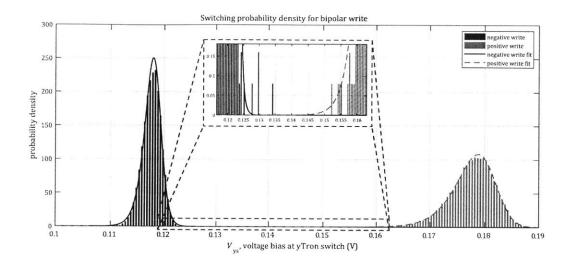

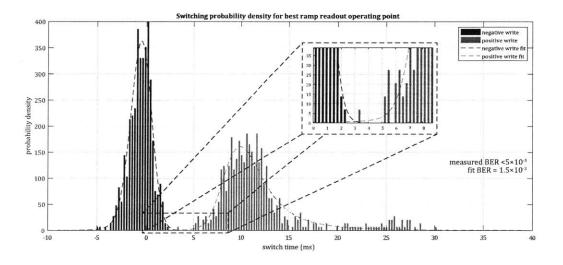

- 2-15 Switching probability density estimations, using a bipolar write pulse of a positive write current for the set signal, and a negative current pulse for the reset signal. The horizontal axis represents the voltage bias that, through the bias network, resulted in a sufficient current to switch the yTron. The solid and dashed lines show a maximum likelihood fit of a Burr distribution to each histogram. The insert is a magnified section of the plot showing the overlap between the two distributions. It can be seen that there were no errors observed, and that the overlap between the tails of the fits are very small, thus resulting in a very low fit-estimated error rate. . . . . . . . . . . . . 109

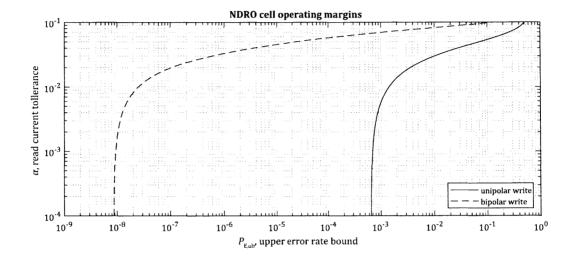

- 2-17 Layout for the revised NDRO cell used in the low error rate measurements. The design shown is the exact layout of the device that was tested in the following section. The black area indicates where NbN has been etched away (leaving the bare substrate below), the white area is where NbN remains. The jog lines indicate leads that extend to the connection pads. Note the hTron and yTron have been highlighted by a dashed line around each device. This layout can be seen to be a stretched version of the original layout shown in figure 2-6. Two additional changes were made. First, the ground connection was made narrower than the cell, and shifted below the hTron channel so as the further increase  $L_{\rm R}$ . Second, the design of the hTron was modified in an attempt to reduce the hotspot size.

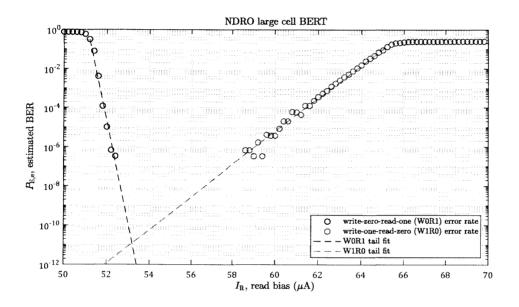

- 2-18 Experimental setup for the final, low BER NDRO cell measurements. A known PRBS is generated by AWG1 and used to trigger AWG2 which provides the write bias. The second channel of AWG1 provides the write enable signal. AWG3 is synchronized to AWG1, and provides the read bias pulse, which is swept during the experiment. A counter is used to track the number of writes, and the number of zeros read from the cell. From the counter's results, the error rate can be estimated since we know the intended number of zeros written. To reduce reflections 50 Ω series termination resistors were added close to the sample on the sample PCB.

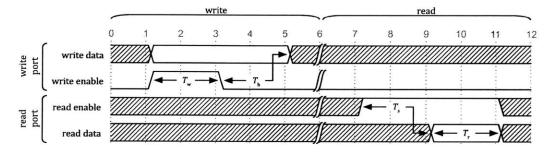

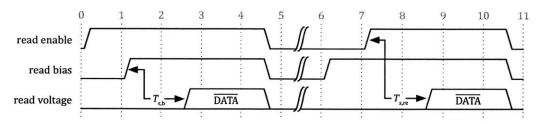

3-2 Timing diagram showing the two types of timing-limited read operations. On the left is a read-bias-setup-time  $T_{s,b}$  limited operation, and on the right is a read-enable-setup-time  $T_{s,re}$  limited operation. It can be seen that in both cases, there is a setup time between the application of the bias and the data becoming valid  $T_{s,b}$ , and between the application of the read enable signals and the data becoming valid  $T_{s,re}$ . It should be noted that regardless of the order in which the enable and the bias signals are applied, both setup times must be satisfied. . . . 122

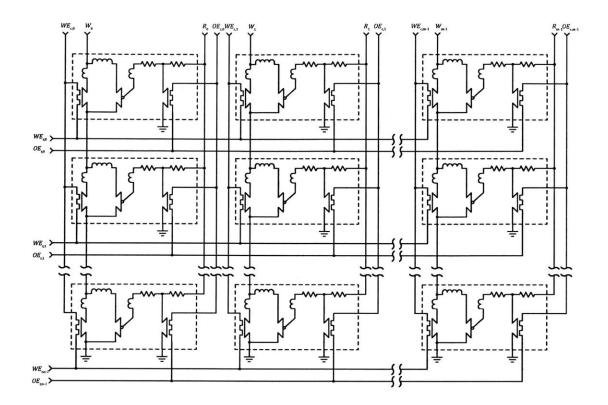

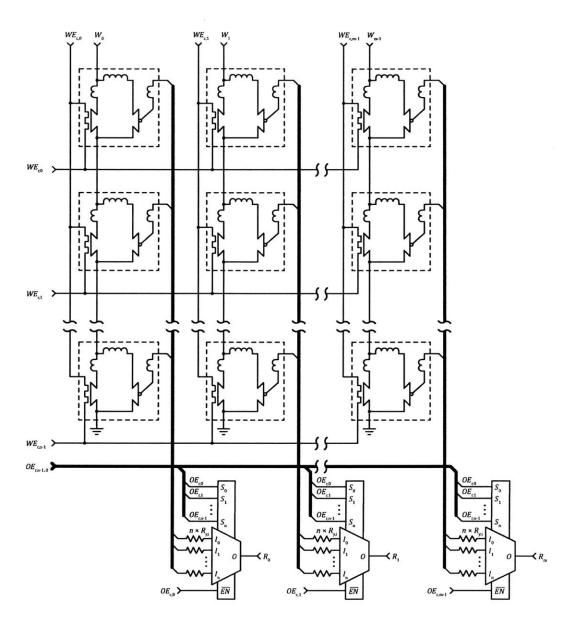

3-3 Schematic showing the connections between resistively isolated NDRO cells to form an *m*-bit word, *n*-row bank. In this figure the use of resistive hTron gates is assumed (provided bit-access is desired), if superconducting gates are used then series resistors are required. It can be seen that forming an array from the resistively isolated cells involves the hTron gates being connected in cross-bar arrangements, read ports connected in parallel along columns, and cell write ports stacked along the common ports in columns.

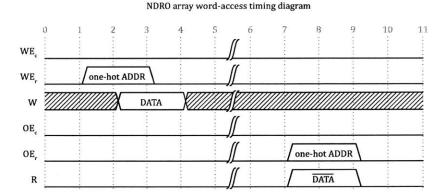

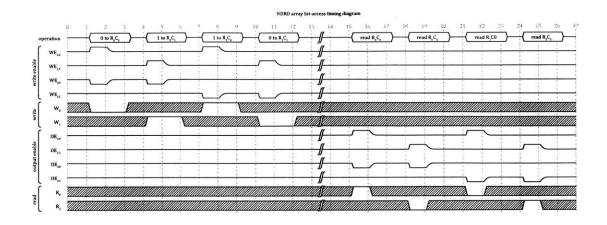

3-4 Timing diagram for word-access write and read to the NDRO cell array of either the resistively isolated or multiplexed design. The signal labels in this figure reference buses, specifically  $WE_c$  is a bus formed by the column write enable lines,  $WE_r$  is the row write enable lines, W is the write signals,  $OE_c$  is the column output enable lines,  $OE_r$  is the row output enable lines, and finally R is the read lines. For the word access scheme, the column lines, both write and read enables, are all grounded; alternatively, these could be held at a high potential and active-low row signals could be used. The first step in order to perform a write is to assert the desired rows write enable signal. The selection of the desired row is equivalent setting  $WE_r$  to be the one-hot address of the desired cell. Upon the falling edge of the write enable signal, the write data must be valid. That is, the data to be written to that row must be present at the W port. Once the write enable signal has been deasserted, the write port can be set arbitrarily. For a read operation, the desired row is selected by asserting the corresponding output enable signal. This operation is equivalent to setting the  $OE_r$  to the one-hot address of the desired row. The read bias current is also applied to the read port. The output enable and read bias signals can be applied in any order, or simultaneously – as shown here. The read port will then present the result of the read asynchronously. The presented output will be the complement value stored at the selected address. The data will be held, and is valid, for as long as the output enable and read bias is maintained. When the read is complete the biases are simply removed and the state of array will be unaffected. . . . . . . . . . .

3 - 5Timing diagram demonstrating the bit-access applied to a NDRO array of either the resistively isolated or multiplexed design. This timing diagram shows both write and read accesses to a  $2 \times 2$  array, although the operation could be extended to an array of any size. This diagram shows four writes and four reads, one to each cell of the array. In order to achieve bit-access, tri-state write enable and/or column enable drivers are required (depending on if bit-access is only needed for writes, reads or both). A write operation to a single cell requires a current to be passed through that cell's write enable hTron gate. This can be achieved by the WE column and row drivers presenting a high impedance to all lines other than those corresponding to the desired cell. For the lines corresponding to the desired cell, one line, say the column signal, must be high, and the other, say the row, must be low. With the write enable signals set, the data to be written to the selected cell is applied to the corresponding column write port. Other columns can have any signals applied as they are not selected. The selected write enable lines are then either returned to the high impedance state, or all set to the same level. Once this is complete, the write bias can be removed, and the write operation is complete. A read operation is conducted in a similar manner. One of either the column or row output enable signals that corresponds to the selected cell is set high, and the other set low. The read bias is then applied to the read port corresponding to the column in which the desired cell resides. The voltage of this port can then be measured to determine the state of the cell. Like in the word-access scheme, the read voltage will be the complement of the data stored in that cell. . . . . . . .

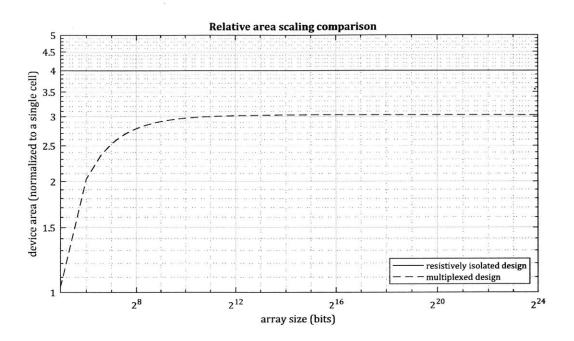

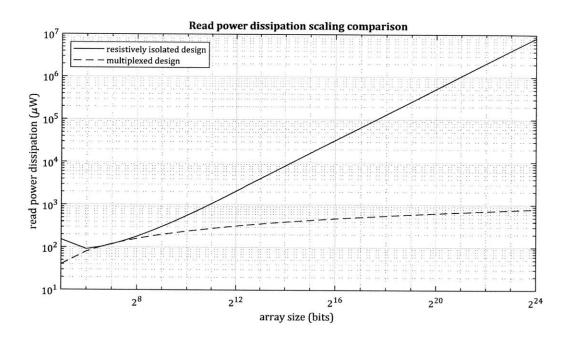

3-7 Comparison of the effective cell size for both a resistively isolated and a multiplexed column design. The relative size is computed with respect to the area of a single cell that contains a single hTron. Note that for this calculation, a word with of 32-bits was assumed. It can be seen that the resistively isolated array has a constant size of four times that of the single cell. In contrast, the multiplexed design starts the same size as a single cell for a bank containing one row, and grows as the bank size grows. The multiplexed design asymptotically approaches the limit of 3 + 1/m = 3.03125 for an array of infinite size. Thus, the multiplexed array is always smaller than the resistively isolated array - when ignoring interconnects and the like.

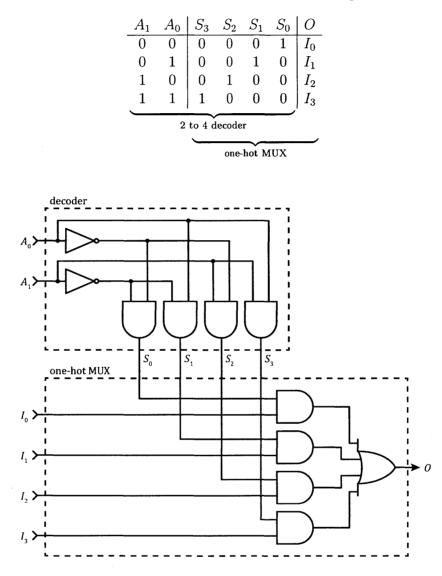

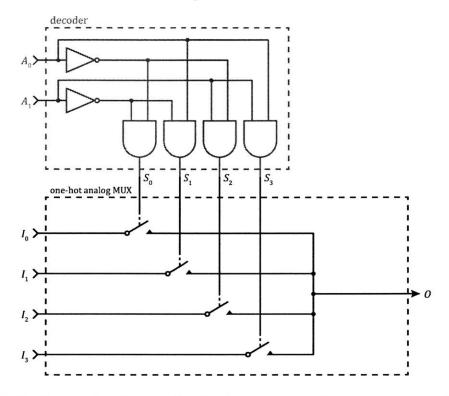

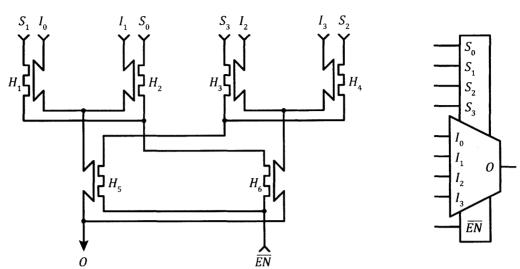

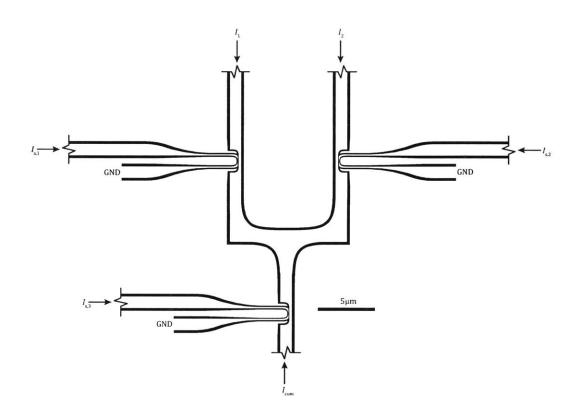

- 3-9 The logic that governs a typical four-to-one digital multiplexer. The schematic has been broken into two sections, with one being a two-input decoder, and the other being a four-to-one one-hot multiplexer. In this case, the select inputs to the multiplexer must be one-hot signal, and this requirement satisfied by the output of the decoder. Porting this design into nanowire devices would yield a very poorly performing device, for this reason an adaptation of this design is used instead. . . 134

- 3-12 Layout of the prototype two-to-one hTron multiplexer. The design shown is the exact layout of the device tested in this section. The black area indicates where NbN has been etched away (leaving the bare substrate below), and the white area is where NbN remains. The jog lines indicate leads that extent to connection pads. While this design is only a two-to-one multiplexer, with the third hTron it becomes one half of the four-to-one multiplexer shown in figure 3-11. One side of each heater is connected to ground.

4-2 Schematic used in the LTspice simulation of the DRO cell. Note the inclusion of the two resistors  $R_1 = R_2 = 1 \text{ p}\Omega$  which are not physical but are included so that LTspice will reliably converge. This approximation is valid for small values of these resistors and for short time-scales. . . 149

- 4-3 Results of a LTspice simulation of a single DRO cell operated in the pulse readout modus and using the write enable signal. In this simulation, the cell is set (placed in the "1" state) at 10 ns. At this time the, loop current  $I_p$  can be seen to increase indicating that the write was successful. The cell is then read at 30 ns. During the read, the memory does not switch as expected when the cell is set. The cell is cleared (placed in the "0" state) at 50 ns. Again, the loop current can be seen to respond accordingly reducing to a negative value. Finally, at 70 ns the memory is read again, but this time the memory switches. The switching of the loop, and the corresponding production of a voltage  $V_r$  during a read "0", and the lack thereof for a read "1" indicate that, at least in this simulation, the memory is working as expected. In this figure, the values  $I_L$  and  $I_R$ , are the currents through the channels of the left and right hTron constructions, respectively.

- 4-4 Layout of the first single DRO cell. The black area indicates where NbN has been etched away (leaving the bare substrate below), and the white area is where NbN remains. The gray area indicates the location where resist will be exposed and developed such that an oxide and metal can be evaporated and later lifted off to form the heater. The jog lines indicate leads that extent to the connection pads. . . . . . 152

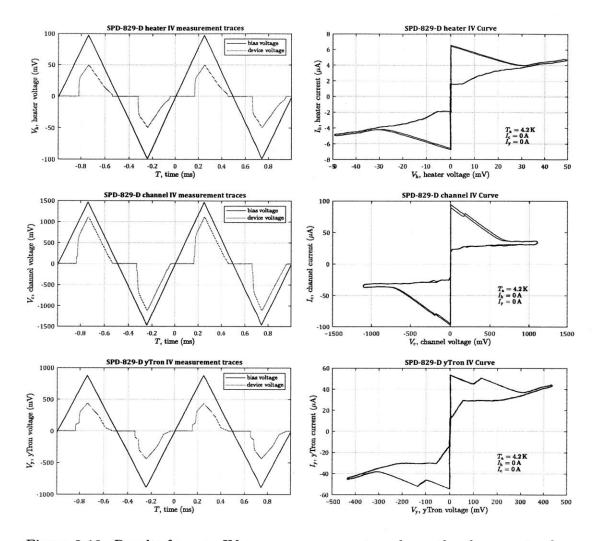

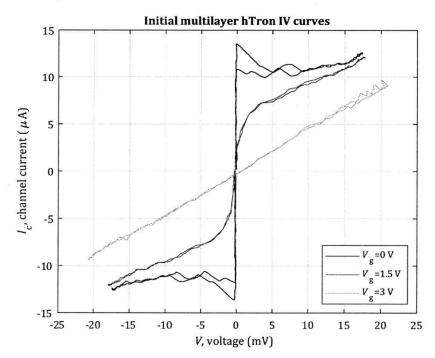

4-5 IV curve of one of the first working hTron device conducted at three gate voltage biases. The experimental data was moving-average filtered prior to being decimated by a factor of 25 in preparation for this figure. It can be seen in the  $V_{\rm g} = 0$  V curve that the switching and retrapping currents are very close together, within around 20%. Typically, the retrapping current is around 20% of the switching current. Thus, this figure here suggests that, even without the application of a current to the gate, the channel is suppressed substantially. With increasing gate bias voltage, an increase in the suppression is seen. With ultimately at a gate bias of  $V_{\rm g} = 3$  V the channel appearing totally resistive. . . . 156

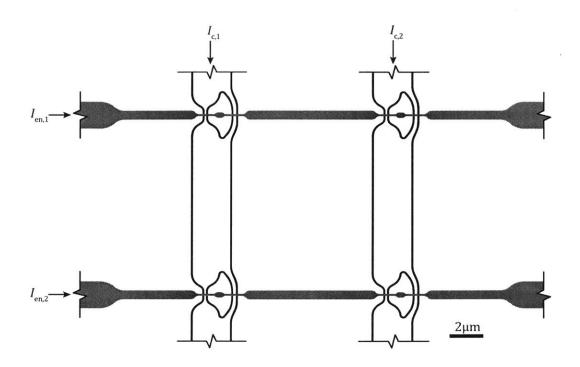

4-7 Layout for the first DRO array. This array features four DRO cells of the same design as that presented in section 4.1.5, which have been arranged into a 2 × 2 configuration. The word size for this memory is 2 b, and there are two rows in the bank. It can be seen that the cell design shown in figure 4-4 was simply repeated four times with the terminals connected to form the desired array. A large space was placed between the cells to ensure that in initial tests there was no inter-cell interference – later tests showed that this space is unnecessary, and that cell heating is highly localized. On the extremes of the heater lines, the connections to the pads were made wide so as to reduce the resistance, and hence power dissipation, in the interconnects. Additionally, the connections from the heaters to the pads were made to be equal in length, so that their resistances would be equal, and as a result the biases applied to the heaters would be the identical for each row. . . .

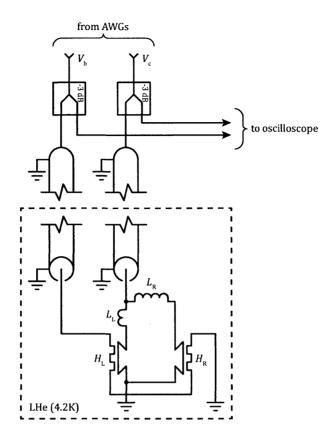

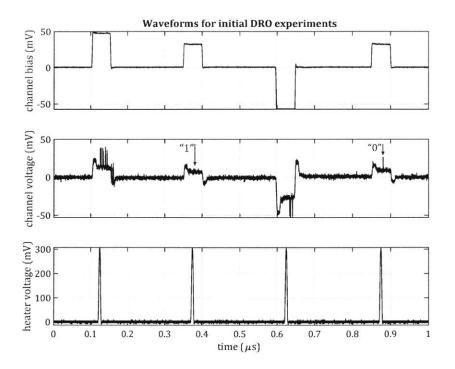

4-10 Oscilloscope traces of the signals applied to, and read from, the DRO cell. The channel bias is the signal that was generated by the AWG. Channel voltage is the combination of the signal applied to the cell and the reflections from the cell – see figure 4-9. Finally, the heater voltage trace is the signal applied to the heater. The markers on the channel voltage plot show where the voltage is sampled to determine if the device switched. The first pulse sets the cell into the "1" state. Following a short pause, the state of the cell is read out. The voltage is sampled at the first arrow. This voltage is below some threshold voltage  $V_{\rm th}$ . After another pause, the cell is then cleared to the "0" state. Again, the cell is read out using the identical read pulse to that used in the first read. This second read resulted in the cell switching, and the resultant voltage pulse is above our threshold voltage  $V_{\rm th}$ , thus indicating a "0" read. The threshold voltage is  $V_{\rm th}$  determined experimentally, and chosen to give the best error rate. . . . . . . . . . .

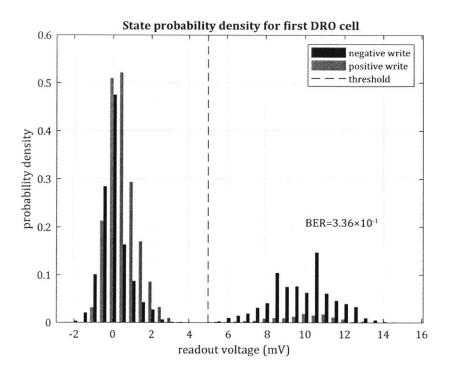

4-11 Probability density of the read pulse amplitude for reads that occurred after a "0" was written (negative write) and after a "1" was written (positive write). The horizontal axis in this plot corresponds to the amplitude of the two markers shown in figure 4-10, and should not be confused with the switching current. This figure is composed of 10,000 write/read cycles, each of which alternated between writing a "1" and writing a "0". The results are divided into two by a threshold voltage  $V_{\rm th}$ . Any sample whose read voltage was below  $V_{\rm th}$  is determined to be a read that resulted in a "1", and those above the threshold a read that resulted in a "1". The threshold was chosen to be  $V_{\rm th} = 5 \,\mathrm{mV}$  since this gave the lowest error rate, which was 33.6%. . . . . . . . . . . . . . . . . .

165

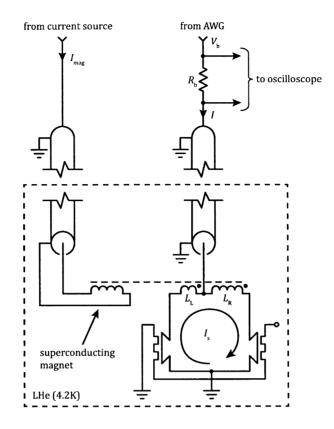

4-12 Setup used to test the magnetic modulation of the DRO cell's switching current. In this setup, the memory chip was placed in close proximity to a custom-made superconducting magnet. The leads of the magnet were attached to copper wires within the LHe. The ground for the magnet was kept separate from the ground for the chip. This separation was made since the current through the magnet very high, and would result in voltage drops along the cables. The presence of these voltages could interfere with the measurement of the switching current of the memory. The magnetic field couples to the loop, and induces a screening current  $I_{\rm s}$ . It is this screening current that we are attempting to measure by performing switching current measurements on the memory loop. The hTrons were not used in this experiment, so one side of the gate was grounded and the other left floating. The same setup used in previous IV curve measurements was again used here with a bias resistor of 168

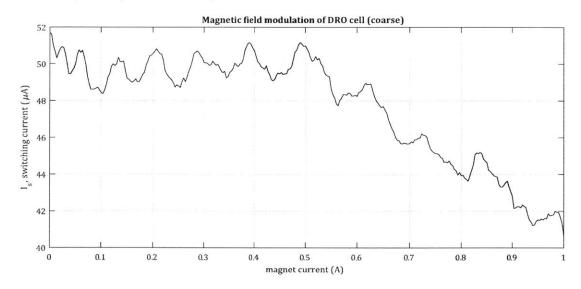

4-13 Modulation of the memory's switching current by the application of an external magnetic field. The magnet current was incremented in steps of 3.33 mA. Two modulation effects can be seen. The first being a periodic modulation, consistent with the existence of a screening current, as expected in SQUID measurements. The second being a suppression of the switching current with the increased application of magnetic field. Each point in this plot corresponds to the median of 40 switching current measurements. A moving-average filter was applied with a length of five samples.

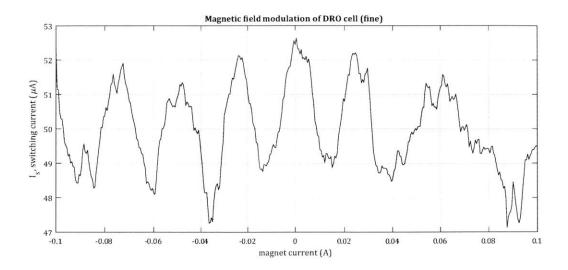

- 4-14 Fine sweep of the magnetic modulation of the memory's switching current. The magnet current was incremented in steps of 0.5 mA. In this result, only the periodic modulation of the switching current can be seen. This indicates that the memory readout mechanism is functional. Each point in this plot corresponds to the median of 40 switching current measurements. A moving-average filter was applied with a length of five samples.

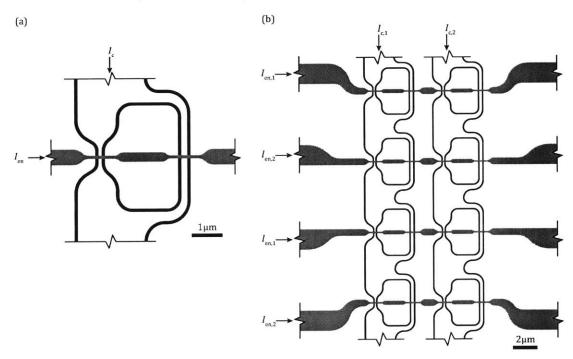

- 4-15 Layout for the revised cell (a) and an array composed of eight of the new cells (b). The inductance ratio for this cell is based on that shown in figure 4-4, with the inductance ratio changed to  $L_{\rm L}$ :  $L_{\rm R} = 4$ : 9. The array can be seen to be based on that shown in figure 4-7. . . . 171

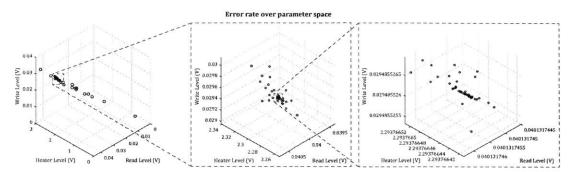

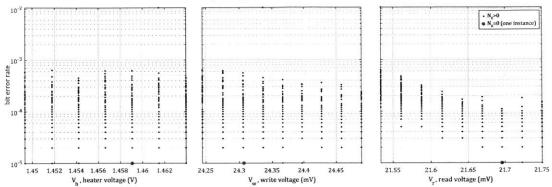

- 4-17 Plot of the error rate over all three operating parameters. These results were generated during the progression of the optimizer. The size of the circle represents the error rate, the larger the circle the higher the error rate. The leftmost figure represents all points the optimizer explored, the center figure is a smaller selection of these points, and the rightmost is an even smaller selection. Throughout the progress of the optimizer, it can be seen that as it approaches the optimal point it explores a progressively smaller operating parameter space.

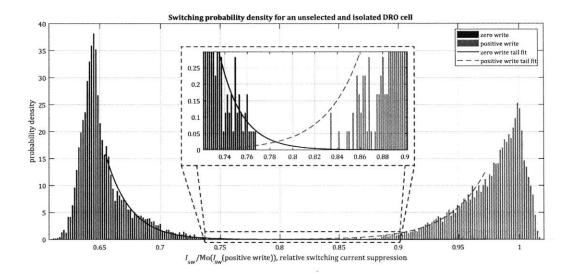

4-19 Approximation of the probability density function of the switching current suppression for an isolated and unselected DRO cell. One histogram represents the read current after a "0" write, and the other after a "1" write. The results have been normalized to the mode of the positive write switching current distribution. Two exponential fits are added to the histograms tails, one for the zero write switching current and one for the one write switching current. The insert is a magnified view of the overlap, or lack thereof, between the two distributions. Note that there are no errors observed, that is there is no overlap between the histograms – although there is an overlap between the fits. . . . 176

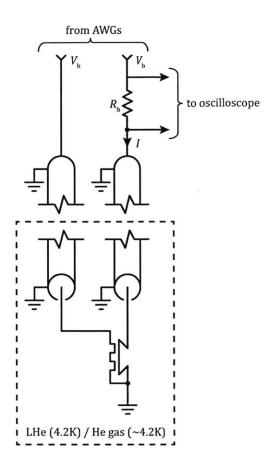

- 4-20 Experimental setup for performing the hTron switching current distribution measurements. The hTron tested here is a multilayer device with a normal-metal gate, one side of which is grounded and the other side supplied a voltage bias. The switching current was measured in the same manner as was done in previous IV curve measurements. A bias resistance of  $R_{\rm b} = 10 \,\mathrm{k}\Omega$  was used. The experiment was conducted once with the device submerged in LHe, and a second time with it suspended above the LHe with the device only exposed to cold He gas. 178

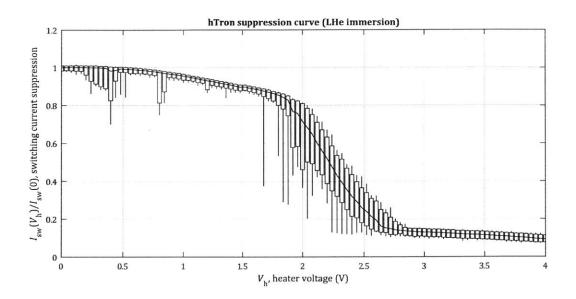

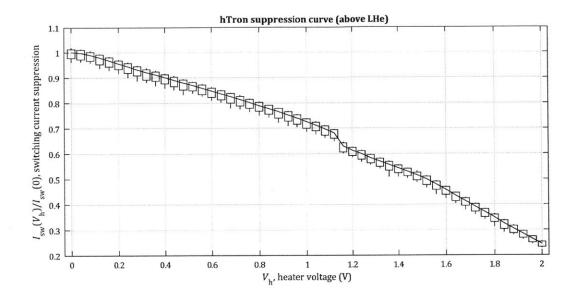

- 4-21 hTron suppression curves captured with the device immersed in LHe. Each point in this plot represents 1,000 switching current measurements. The line plot indicates the median, the box the extents of the 1% and 99% quantiles for that particular heater bias, and the whiskers are the maximum and minimum of the measurements. It can be seen that at low and high heater biases the switching distributions are relatively narrow, and at intermediate suppressions, the distribution is extremely wide. The very high variations in the switching current are suspected to be due to the formation of He gas bubbles on the surface of the chip.

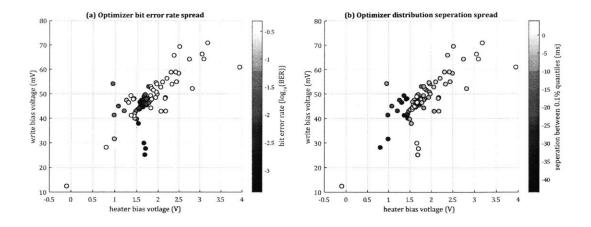

- 4-24 Scatter plot of the bit error rate (a) and separation between distributions (b) at each operating point the optimizer explored. For (a), a lower error rate (darker colored point) is better, and for (b), a higher separation (lighter colored point) is better. Since the error rate varies over a wide range the color was plotted in a log scale of the error rate. Interestingly, points with low error rate, do not necessarily have good separation between distributions, hence why the cost function incorporates both parameters.

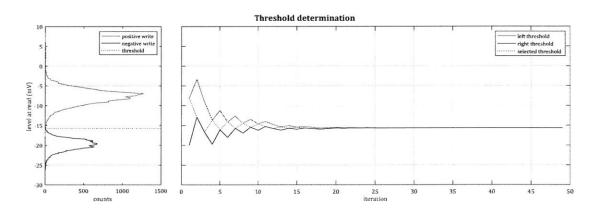

5-5 Histograms of the read data provided by the data acquisition routine (left), and a graphical illustration of the process used to find the optimal threshold (right). In this evaluation, a tolerance value of 10<sup>-5</sup> was used. The threshold determination algorithm starts by choosing an initial threshold equal to the mean of the modes of each distribution. Two trial thresholds to the left and to the right of this initial threshold are considered. The better of these two thresholds (one with the least number of errors if used to divide the data) is then used as the new threshold. This process is repeated with ever decreasing separation of the left and right trial thresholds. Finally, the process stops once the tolerance value is satisfied. At this point, the threshold value that gave the lowest number of errors is chosen for the final BER evaluation. . .

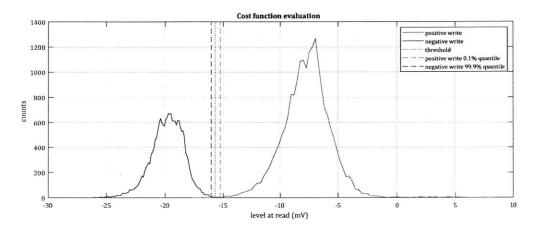

- 5-6 Example distribution generated and analyzed by the cost function routine – taken from a measurement of a DRO array. Each curve is a histogram representing the samples measured during that particular BERT. The "level at read" is the voltage level applied to the cell (which through the impedance of the splitter) is converted to a current at the cell. The optimal threshold is shown, and was calculated using algorithm 1. The quantiles of each histogram are also shown. The distance between these quantiles, along with the BER, are the basis of the ramp-base readout cost function.

- 5-9 Isometric assembled (left) and exploded (right) views of the new apparatus. The thermal strap, and superconducting wire are not shown in these figures. In this figure no sample is attached to the sample mount. A fiber attachment is shown mounted in the SM1 adapter. . . . . . 202

# List of Tables

| 2.1 | NDRO unipolar ramp readout operating point                         | 105 |

|-----|--------------------------------------------------------------------|-----|

| 2.2 | NDRO cell ramp readout error rate estimates.                       | 110 |

| 2.3 | Revised NDRO pulsed readout operating point.                       | 116 |

|     |                                                                    |     |

| 3.1 | Truth table for a four-to-one multiplexer                          | 134 |

| 3.2 | Truth table for the four-to-one hTron tree multiplexer. $\ldots$ . | 137 |

| 11  | Final simulation DBO cell device personators                       | 150 |

| 4.1 | Final simulation DRO cell device parameters.                       | 190 |

# Chapter 1

# Introduction

# 1.1 Superconductivity and superconducting circuit components

Superconductivity was discovered in 1911 by Heike Kamerlingh Onnes [1]. Onnes was attempting to extend the resistance-temperature curve of mercury to lower temperatures using liquid helium which had just recently been produced. In his experiment, he found that his resistance measurements would suddenly drop to an immeasurably small value when the sample was cooled to below a certain temperature. What Onnes had just observed is the transition of mercury from a normal metal to a superconductor. In subsequent years, other materials were found to exhibit this same property; in particular niobium nitride (NbN), the material used in the experiments presented in this work, was found to superconduct at a temperature above 14 K in 1941 [2].

As stated above, superconductors are characterized by their ability to carry a current without any resistive dissipation, when cooled below their transition temperature. Below this temperature, the resistance of these materials is exactly zero. Superconductors should not be confused with perfect conductors. A hypothetical perfect conductor would have zero resistance and requires a constant magnetic flux within the conductor [3]. A superconductor, on the other hand, shares the zero resistance property, but imposes a strict requirement that the magnetic field within

the bulk must be exactly zero. In addition to this distinction, superconductors can only maintain their superconductivity provided a number of conditions are met, in particular restrictions on temperature, current density, and magnetic field exist. Additionally, the bulk properties of superconductors do not hold at the surface, or in thin films. These limitations are primarily a consequence of the finite number of superconducting charge carriers. In a perfect conductor none of these limitations exist.

Superconductors possess many properties that behave non-linearly. For example, the transition between the superconducting state and normal state is highly non-linear. The bulk material changes from a resistance of zero, to a resistance typically  $10^{-3}$  to  $10^{-1}$  that of its room temperature resistance, by only changing the temperature a fraction of 1 K. The existence of such non-linearities, and the fact that these can be modulated electrically, means that it is possible to build useful electronic components with superconductors. The following sections outline a number of these devices and their basic operation.

#### **1.1.1** Josephson junctions

The Josephson junction (JJ) has been the main device used in superconducting circuits from the device's inception, to the current day [4]. These devices have a relatively simple construction. As shown in figure 1-1, a JJ comprises of three layers. The outer two layers are superconductors, and the inner layer is an insulator to form a superconductor-insulator-superconductor (SIS) junction, or a normal metal to form a superconductor-normal-superconductor (SNS) junction. There exists other constructions which feature more complex layer structures. While such devices are typically also referred to as JJs, we will only refer to SIS and SNS junctions as JJs.

In 1962, B. D. Josephson predicted that paired electrons (Cooper pairs), which are the means by which a superconductor carries a supercurrent, could tunnel through a thin, non-superconducting barrier [5]. Further, Josephson predicted that such a current could flow with no dissipation, that is, with no voltage drop – up until a certain critical current  $I_c$ . This operation is referred to as the DC Josephson effect.

Figure 1-1: Schematic showing the basic structure of a Josephson junction. The distance between the two superconducting materials must be very small in order for tunneling to occur. When an insulator is used to separate the superconductors the junction is referred to as a SIS junction. It is also possible to use a normal metal, in place of the insulator, to crease a SNS junction, it is even possible to use a weaker superconductor to form a SsS junction.

This operation cab be seen graphically as the vertical line from  $-I_c$  to  $I_c$ , in figure 1-2. If one were to bias a JJ with a voltage V, then the junction would begin oscillating at a frequency of f = 2eV/h, where e is the charge of an electron, V is the applied voltage, and h is Plank's constant. This operation is referred to as the AC Josephson effect [6].

Superconductivity is one of the most notable examples of a macroscopic quantum phenomenon. The supercurrent carrying Cooper pairs, consisting of two electrons, can be considered a compound boson. Treating Cooper pairs as such allows them to be described by the quantum mechanical wave function  $\Psi = \Psi_0 \exp(j\theta)$ , where  $\theta$  is the temporal and spatially varying phase. The lack of a superconducting link between either side of a JJ allows for it to sustain a phase difference  $\varphi := \theta_2 - \theta_1$ , referred to as the JJ's phase. Josephson predicted that the supercurrent through the junction would be

$$I_{\rm s} = I_{\rm c} \sin(\varphi). \tag{1.1}$$

The superconducting wave function's phase can be related back to the voltage that

Figure 1-2: Current-voltage relation of a typical Josephson junction. The junction can pass a current with no voltage drop provided the current is less than the critical current  $I_c$ . When the critical current is exceeded the junction switches operating mode and presents a voltage  $2\Delta/e$  where  $\Delta$  is the superconducting gap, and e is the elementary charge. If the current is increased the junction behaved as a resistor. Upon decreasing the current, when close to zero the junction will return to a zero voltage drop. Note that the IV curve is rotationally symmetric, and that structure of the junction is intrinsically symmetric.

is developed across any two points in a superconductor (and across a JJ) as

$$V = \frac{\Phi_0}{2\pi} \frac{d\Delta\theta}{dt},\tag{1.2}$$

where  $\Phi_0 = h/2e$  is the magnetic flux quantum,  $\Delta \theta$  is the phase difference between the two points of interest, and t is time.

One of the major consequences of superconductors being governed by a wave equation is that, for a supercurrent to be sustained, we must ensure coherence. This means that along any closed path in a superconductor, we must have the phase being zero modulo  $2\pi$ . This has the most notable consequence that the flux through any superconducting path is an integer multiple of  $\Phi_0$ . This can be derived as such:

Extending equation 1.2 to the continuous case we have

$$E = \frac{\Phi_0}{2\pi} \frac{d^2\theta}{dtds}.$$

(1.3)

Now, we apply Faraday's law to find that the flux through any superconducting loop is

$$\Phi = -\int \oint E \cdot ds \, dt = -\int \oint \frac{\Phi_0}{2\pi} \frac{d^2\theta}{dtds} \, ds \, dt = -\frac{\Phi_0}{2\pi} \theta = n\Phi_0, \tag{1.4}$$

where  $n \in \mathbb{Z}$ . It should be noted that this holds for within the superconductor as well as for superconducting loops around a non-superconducting region.

### 1.1.2 Superconducting nanowires

Currently, the JJ is the dominant device for building superconducting circuits; however, devices based on the thermal switching of small superconducting wires are increasingly being considered for applications traditionally dominated by JJs. These small wires can have dimensions on the nano-scale, and are thus referred to as nanowires. The operation of these devices relies on the fact that superconductivity can only be sustained provided three conditions are met:

- 1. The temperature T is below its critical value  $T_{\rm c}(J, B)$ ,

- 2. The current density J is below its critical value  $J_{c}(T, B)$ , and

3. The magnetic field density B is below either  $B_c(T, J)$  for a type I superconductor, or below  $B_{c2}(T, J)$  for a type II superconductor.

It should be noted that each of these three critical values depends on the other two parameters. Superconducting nanowires take advantage the fact that if any of these three limits is exceeded, it will invoke a phase transition from the superconducting to the normal state. Once in the normal state, the device will exhibit a resistance – as any normal metal would.

#### **1.1.3** Kinetic inductance in nanowires

All conductors have kinetic inductance [7]. The kinetic inductance  $L_k$ , is calculated by equating the kinetic energy of the charge carriers, with an equivalent inductive energy. For a normal metal this gives

$$\frac{1}{2}(mv^2)(nlA) = \frac{1}{2}L_{\rm K}I^2 \tag{1.5}$$

which, combined with I = evnA yields

$$L_{\rm K} = \frac{ml}{Ane^2},\tag{1.6}$$

where m is the charge carrier mass, v is the average carrier velocity, n is the density of carriers, l is the length of the conductor, A is the cross-sectional area of the conductor, and I is the applied current. For a superconductor, we have that the charge carriers are Cooper pairs. Thus, we have the same expression as above with the substitution  $n \rightarrow n_{\rm s}, m \rightarrow 2m, e \rightarrow 2e$ , which yields

$$L_{\rm K} = \frac{ml}{2An_{\rm s}e^2}.\tag{1.7}$$

The expressions in equation 1.6 and equation 1.7 are very similar, so one might expect that a superconductor and a normal metal would have similar kinetic inductance values. This assumption holds for many materials; however, for some materials, such as NbN, this is certainly not the case. The reason that kinetic inductance is typically not readily observed in normal metals is that for most materials the carrier density is very high, and so  $L_{\rm K}$  is very small in comparison to the geometric inductance. The kinetic inductance of a normal metal only becomes large when the carrier density becomes very small, as this means that for the same current the velocity of the carriers must become very high. For a normal metal with such a low enough carrier density that a high kinetic inductance is easily observable, the resistance is typically so high that the inductance is negligible contribution to the total impedance, at least for frequencies less than ~ THz. In contrast, a superconductor will have a zero resistance provided there exists at least one Cooper pair. Thus, materials with low carrier concentration, and hence high kinetic inductance, can be used as to create inductances in circuits.

From examination of equation 1.7, we can see that  $L_{\rm K}$  has the same dependence on l and A as the resistance does for a normal metal. Since we are dealing with thin films, we can use a inductive analog of sheet resistance, that is, a sheet inductance. For thin NbN films we have a sheet kinetic inductance of  $L_{\rm K}^{\Box} \approx 14 \,\mathrm{pH}/\Box$  for a 20 nm film, and  $L_{\rm K}^{\Box} \approx 60 \,\mathrm{pH}/\Box$  a 5 nm film. For most of the circuits presented here, the exact value of inductance is not of particular importance, rather the ratios of the inductance between two branches is important. Thus, it is sufficient to simply design circuit considering only the ratio of the number of squares – which can easily be determined.

# 1.1.4 Circuit model of superconductivity

As we saw in section 1.1.1 and section 1.1.2, our traditional approach to the design of electronic circuits is not sufficient for the design of superconducting circuits. On top of current and voltage, we need to take into account the superconducting wave function's phase. Like how the complexities of current flow through a resistor can be reduced to a lumped resistance value, the superconducting phase variance across a superconductor can be treated as a lumped inductance. Such a simplification, allows for the phase to be treated, along with voltage, as a nodal term. The particulars of superconducting devices, such as JJs and nanowires, can be treated as a black-box, and given a circuit symbol – as is done for conventional circuits. Thus, we can come up with a set of rules for designing and analyzing superconducting circuits as such

- 1. Kirchhoff's current law (KCL) the sum of current into any node is zero;

- 2. Kirchhoff's voltage law (KVL) the sum of voltage around any loop is zero;

- 3. Superconducting phase "law" the sum of phase around any superconducting loop is zero modulo  $2\pi$ .

As with conventional circuits, care should be taken when applying these rules. It should be noted that these rules are only true when lumped element models are applicable.

#### 1.1.5 The cryotron

In the 1950s, there was a concerted effort to develop the device that would take over from the vacuum tube – in particular for digital computing applications. During this period, Dudley Buck invented an electrically actuated switch that operated by transitioning from a superconducting state to a resistive normal state by means of an applied magnetic field. He published the device along with a collection of logic circuits built with this device that Buck called the cryotron [8].

Figure 1-3: Schematic drawing of a typical cryotron used by Buck. The device consists of a  $\emptyset 0.009$ " uncoated tantalum gate wire wrapped with around 250 turns of a  $\emptyset 0.003$ " insulated niobium control wire. When a current  $I_c$  is applied to the control wire, a magnetic field is induced in the solenoid. This field suppresses superconductivity in the gate wire. As  $I_c$  is increased, the gate current  $I_g$  that the wire can support without transitioning to the normal region will progressively decrease. A greater suppression of superconductivity occurs in the gate wire than the control wire owing to the gate having a lower  $T_c$ , and lower  $B_c$ .

A drawing of the cryotron as used by Buck is shown in 1-3. The device operates by passing a control signal through the control wire. The passage of this current leads to the development of a magnetic field within the solenoid formed by the control wire. With the proper design, this field is substantial enough that it can suppress superconductivity in the gate wire. The gate and control wire see similar magnetic fields. Since it is desired that the control wire remains superconducting at all times, it is necessary for the control wire to be constructed from a superconductor that can withstand a higher field than the gate.

Figure 1-4: Schematic symbol for a cryotron, as proposed by Buck. This symbol is derived from the structure of the cryotron with the control wire depicted as a coil around a thicker conductor, that being the gate. Additionally, the symbol graphically demonstrates that the cryotron does not behave differently if the currents  $I_c$  and/or  $I_g$  are reversed in direction, as only their magnitudes is of importance.

Buck proposed the symbol shown in figure 1-4, which is inspired by the physical construction of the device. It should be noted that Buck utilized a naming scheme that, with the advent of field-effect transistors, became the opposite of the current conventions. Buck named the switched path of the cryotron, the gate, and the switching path, the control. In a field-effect transistor, the channel is the modulated path and the gate is the modulating potential. Here we will use the field effect naming convention, and only use Buck's convention when discussing the original cryotron.

The cryotron was pitted again the vacuum tube. While the cryotron was smaller and more power efficient than vacuum tubes, this came with many downsides. The cryotron was faster than electromechanical relays, but slower than contemporary vacuum tubes and transistors. With the device requiring cryogenic temperatures to operate, and with its slow speed, it was no match for transistors, which at the time were beginning to gain traction. Thus, the cryotron seemed relegated to the past at least until the advent of the nano-scale planar devices discussed in the following section.

# 1.2 Superconducting nanowire devices

The cryotron utilized the critical magnetic field density, and a control electromagnet, to induce a transition of a conductive channel from the superconducting state, to the normal state. Similar operations can be performed by exceeding the critical temperature or critical current density – both of these effects were avoided in the original cryotron. With the advent of modern lithography techniques, we can make such devices on the nano-scale. Reduction of the device size has a number of advantages, including reducing power dissipation and increasing the speed at which operations can occur. Devices that utilize the destruction of superconductivity in small features are collectively referred to as superconducting nanowire devices, and as a result of their similarity to the original cryotron, also referred to as cryotrons themselves.

In the context of the work presented here, a superconducting nanowire is a structure patterned into a superconducting thin film. Structure widths on the order of 100 nm and film thicknesses on the order of 10 nm are used here. While a strict definition of a nanowire would typically entail the device being able to be modeled as one dimensional, here we will use a relaxed definition, and consider two-dimensional devices as nanowires.

All of the devices we will be utilizing in this work are all composed of a single layer of superconducting material, in particular thin film NbN, which was deposited by means of reactive sputtering. In the latter part of this work, a second normal metal layer, which is insulated from the NbN by means of an oxide, will be placed on top of the NbN. NbN is a superconductor with a particularly high kinetic inductance in comparison to other materials. Such a high kinetic inductance is particularly useful for our applications as it gives us two desirable properties. First, high a kinetic inductance means that the devices and structures that we build with NbN are particularly insensitive to magnetic fields, as coupling to the loop magnetically is very difficult. Second, the high kinetic inductance means that structures can be very small, as we simply need to consider the number of squares to calculate the inductance, rather than requiring large areas to produce the desired geometric inductance. In fact, the kinetic inductance of NbN is so much greater than geometric inductance that we can, for most applications, ignore the geometric inductance [9].

With our thin NbN films, it is possible to produce a number of different devices. As all of these devices operate by means of the destruction of superconductivity, and as such, can all be considered switches. The mechanism by which each device switches is dependent on the structure of the device. In the following sections, each of these devices is briefly introduced.

#### **1.2.1** Constriction

While the nanowire constriction is not typically referred to as a cryotron, an understanding of it and its operation, is vital if the other cryotron devices are to be understood. The most trivial example of a nanowire device is a constriction. This device is simply a nanowire that has a region of reduced width, as shown in figure 1-5. The narrow portion of the wire must, of course, carry the same current as the rest of the wire. This means that at the narrow region, the current density will be higher than at other locations in the wire. If the current density in this narrow region is greater than the critical current density  $J_c$ , then the narrow region will transition to the normal state, leading to the development of a hotspot.

A sketch of a typical IV curve for a NbN nanowire is shown in figure 1-6. If we consider a nanowire that is in the superconducting state, then we can vary the current through the device within  $-I_c < I < I_c$ , and the wire will behave as an inductor with zero resistance; that is V = L(I)i'(I), where L(I) is the inductance of the wire at the current *i*. The inductance of the wire is the combination of a geometric inductance  $L_g$ , and a kinetic inductance  $L_k(I)$ , that is  $L(I) = L_g + L_k(I)$ . The variation in the kinetic inductance with current is often ignored, as doing so typically will not result in a significant error.

If the nanowire is in the superconducting state, and the current through the device exceeds  $I_c$ , then a hotspot will form in the nanowire. The hotspot is a region in which the material from which the nanowire is constructed behaves as a normal material. Once the hotspot has formed, a DC voltage can be sustained across the constriction.

Figure 1-5: Schematic symbol for a superconducting nanowire constriction (a), and a sketch of the layout of a constriction (b). There is no generally accepted symbol for a nanowire, we will use this symbol throughout this work. The constriction shown in (b) has been switched to the "normal" state. While the vast majority of the wire is still superconducting, there exists a hotspot at the narrowest region of the wire – where the current density is the highest. As a current I is being applied to the constriction, a voltage V will be dropped across the normal region. The magnitude of the current I can cause the hotspot to grow or shrink. If the bias I is lowered sufficiently then the hotspot will vanish and the constriction return to the superconducting state. The jog lines indicate where the constriction would be connected to the rest of a circuit.

While the current through the wire is greater than the retrapping current  $I_r$ , the device will behave as a resistor (in series with an inductor) – at least in the ideal case, see section 2.4.3 for a description of non-ideal effects. It should be noted that the critical current  $I_c$  is the theoretical current at which a breakdown of superconductivity occurs, in practice this current is unobtainable due to many non-ideal effects including noise. The experimentally obtained current at which superconductivity breaks down is called the switching current  $I_s < I_c$ , to distinguish it from its theoretical counterpart.

When in the normal regime, if we reduce the current through the device to below  $I_r$ , then the device will transition back to the superconducting state. The reason that this hysteresis exists is due to the fact that Joule heating occurs within the hotspot. This heating leads to a rise in the local temperature of that region of the wire. Given that the critical current is dependent on the temperature, and in fact, reduces as

Figure 1-6: Sketch of the current-voltage relation for a single current-biased superconducting constriction. The constriction can carry any current without developing a voltage, provided that the magnitude of the current is less than the critical current  $I_c$ . If  $I_c$  is exceeded, then the device will enter the resistive state. Once in the resistive state, the device behaves similar to a resistor. From the resistive state, if the current is lowered to below the retrapping current  $I_r$ , then the device will return to the superconducting state. Note that the IV curve is rotationally symmetric, and that switching and retrapping only depends on the magnitude of the current.

temperature increases, then the retrapping current is lower than the critical current.

# 1.2.2 nTron

The nanocryotron (nTron) is a three terminal nanowire device [10]. This device is the first nanowire electrical component (other than the constriction) that was developed. The nTron can be considered a triggerable constriction. The device consists of a relatively wide channel and a narrow gate terminal that is attached to the channel to form a T-shape. The device symbol along with a typical layout are shown in figure 1-7. The channel behaves exactly as a constriction while no current is applied to

the gate. That is, the channel will remain superconducting while the applied current is less than the channel critical current. Provided the gate switching current is not exceeded, then the application of a current to the gate simply adds to the channel current, and provided this total is less than the channel critical current, then the device will remain superconducting. In this regime, the nTron simply behaves as a current combiner.

Figure 1-7: Schematic symbol for the nTron (a), and a sketch of a typical nTron layout (b). In the absence of a gate current  $I_{\rm g}$ , a high channel current  $I_{\rm c}$  can be sustained without the device switching and a channel voltage  $V_{\rm c}$  forming. However, in the presence of a sufficient gate current, a hotspot will form at the gate. This hotspot reduces the effective width of the channel and increases the local temperature, thus leading to a reduction in the magnitude of current  $I_{\rm c}$  that can be sustained without the channel switching. The narrowest region of the channel is located to one side of the gate such that during retrapping, the gate will become superconducting prior to the channel. The symbol for the device was designed such that it depicts which side of the narrow region of the channel the gate lies.

If the gate current is high enough that the gate constriction switches, then a substantial reduction in the channel switching current occurs. This switching current suppression is due to the fact that the gate constriction is in close proximity to the channel. This close proximity, in turn, means that heating that occurs at the gate constriction will lead to two effects. First, the gate hotspot can begin to expand into the channel, thereby reducing its effective width. Secondly, the rise in the local temperature of the channel will lead to a reduction in the channel's switching current. This suppression of the channel switching current is plotted in figure 1-8. If the current being carried by the channel is less than the channel switching current with no gate bias  $I_{c,s}(0)$ , but greater than the plateau seen in figure 1-8, then the application of a sufficient gate current will lead to the switching of the channel.

Figure 1-8: Sketch of a typical nTron suppression curve. The switching current of the channel  $I_{c,s}$  is a function of the gate current  $I_g$ . The switching current of the channel is largely unaffected by the gate current while the gate is superconducting. That is, when the gate current is less than its critical value  $I_{c,g}$  and no hot spot has formed, there is little modulation of the channel switching current by the gate current. Once the gate switches, and a hotspot forms, the channel is rapidly suppressed by the gate current. This rapid suppression leads to an operating region in which the nTron possesses a very high gain. This effect begins to diminish with the application of increasing gate current.

Like a constriction, after the channel switches, the current must be lowered to below the retrapping current in order for it to become superconducting again. During the process of resetting the channel, it may be preferable to have the gate become superconducting prior to the channel. In order to achieve this operation, the narrowest region of the channel is made offset from the gate. This direction of this offset is typically chosen to be away from the terminal closest to ground. Through this design, when the channel bias is reduced, the hotspot will remain at the narrowest portion of the channel, while the region surrounding the location were the gate is attached has already become superconducting again.

The nTron can be seen to be similar to the original cryotron in that they are both electronically controlled switches. They differ in that the nTron is a three terminal device, and the cryotron is a four terminal device, and the nTron is thermally actuated, whereas the cryotron is magnetically actuated.

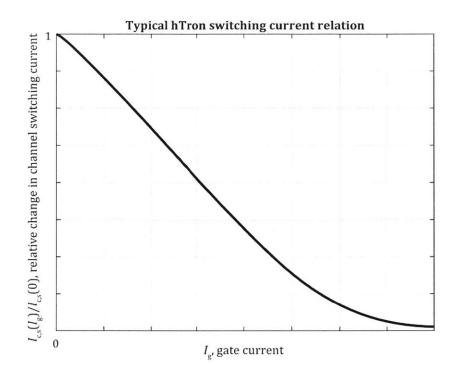

# 1.2.3 hTron