### MIT Open Access Articles

## Large Area 1.2 kV GaN Vertical Power FinFETs with a Record Switching Figure-of-Merit

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

**Citation:** Zhang, Yuhao et al. "Large Area 1.2 kV GaN Vertical Power FinFETs with a Record Switching Figure-of-Merit." IEEE Electron Device Letters 40, 1 (January 2019): 75 - 78 © 2018 IEEE

**As Published:** http://dx.doi.org/10.1109/led.2018.2880306

**Publisher:** Institute of Electrical and Electronics Engineers (IEEE)

Persistent URL: https://hdl.handle.net/1721.1/121563

**Version:** Author's final manuscript: final author's manuscript post peer review, without

publisher's formatting or copy editing

Terms of use: Creative Commons Attribution-Noncommercial-Share Alike

# Large Area 1.2 kV GaN Vertical Power FinFETs with a Record Switching Figure-of-Merit

Yuhao Zhang, Member, IEEE, Min Sun, Josh Perozek, Student Member, IEEE, Zhihong Liu, Member, IEEE, Ahmad Zubair, Student Member, IEEE, Daniel Piedra, Nadim Chowdhury, Student Member, IEEE, Xiang Gao, Kenneth Shepard, Fellow, IEEE, and Tomás Palacios, Fellow, IEEE

Abstract—This work presents the first experimental study on capacitances, charges and power-switching figure-of-merits (FOMs) for a large-area vertical GaN power transistor. A 1.2 kV, 5 A GaN vertical power FinFET was demonstrated in a chip area of 0.45 mm², with a specific on-resistance of 2.1 mΩ·cm² and a threshold voltage of 1.3 V. Device junction capacitances were characterized and their main components were identified. This was used to calculate the switching charges and practical switching frequencies. Device FOMs were then derived that take into account the trade-offs between conduction and switching power losses. Our GaN vertical FinFETs exhibit high frequency (~MHz) switching capabilities and superior switching FOMs when compared to commercial 0.9-1.2 kV Si and SiC power transistors. This work shows the great potential of GaN vertical FinFETs for next-generation medium-voltage power electronics.

Index Terms— gallium nitride, vertical power transistors, FinFETs, power switching, junction capacitances, switching charges, switching frequency, power switching figure of merits.

#### I. INTRODUCTION

aN devices are excellent candidates for next-generation power electronics. Vertical GaN transistors have several potential advantages over lateral GaN transistors: 1) higher breakdown voltage (BV) and current for a given chip area; 2) superior reliability and 3) easier thermal management [1]. Until now, several structures have been demonstrated for vertical GaN power transistors, such as current-aperture vertical electron transistors (CAVETs) [2]–[4] and trench MOSFETs [5]–[7]. However, the fabrication of these devices requires either the epitaxial regrowth or p-type GaN layers, which either greatly increases the fabrication complexity and cost, or limits

This work was supported by the ARPA-E SWITCHES program monitored by Dr. Isik Kizilyalli. (*Corresponding authors: Yuhao Zhang and Tomás Palacios*).

- Y. Zhang was with the Microsystems Technology Laboratories (MTL), Massachusetts Institute of Technology (MIT), Cambridge, MA 02139 USA. He is now with the Center for Power Electronics Systems (CPES), Virginia Polytechnic Institute and State University, Blacksburg, VA 24061 USA (e-mail: yhzhang@vt.edu).

- M. Sun was with the MTL, MIT. He is now with the Energy Internet Research Institute, Tsinghua University, Chengdu, Sichuan 262500 China.

- J. Perozek, A. Zubair, N. Chowdhury and T. Palacios are with the MTL, MIT, Cambridge, MA 02139 USA (e-mail: <a href="mailto:tpalacios@mit.edu">tpalacios@mit.edu</a>).

- Z. Liu is with the Singapore-MIT Alliance for Research and Technology, Singapore 138602.

- D. Piedra was with the MTL, MIT. He is now with the Analog Devices Inc., Wilmington, MA 01887 USA.

- X. Gao is with IQE RF LLC, Somerset, NJ 08873 USA.

- K. Shepard is with the Bioelectronic Systems Laboratories, Columbia University, New York, NY 10027 USA.

Accepted version. Digital Object Identifier 10.1109/LED.2018.2880306

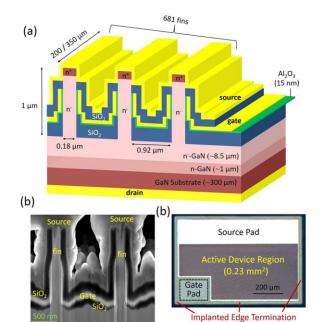

Fig. 1. (a) 3-D schematics of the GaN vertical power FinFETs with multiple fin channels. (b) Cross-sectional SEM image of the fin area in the fabricated device, taken in a focused ion beam system. (c) Optical microscopy image of the fabricated large-area device.

the channel carrier mobility.

Recently, the GaN vertical power FinFET [8]-[10] (Fig. 1 (a)) was demonstrated. This transistor overcomes most of the challenges of CAVETs and trench MOSFETs as it only needs n-GaN layers and does not require epitaxial regrowth. The current in this device is controlled through the fin-shaped n-GaN channels with all-around gate stacks. In narrow fin channels, all electrons can be depleted at zero gate bias due to the work function difference between the gate metal and GaN, enabling normally-off operation. A BV of 1.2 kV and a specific on-resistance ( $R_{\text{on,sp}}$ ) of 1 m $\Omega$ ·cm<sup>2</sup> have been demonstrated [8] on small devices with tens of fins. 10 A transistors have also been fabricated but their BV was limited to 800 V [8]. To advance the device applications in power converters, large-current 1.2 kV devices are typically required. Critical device parameters for switching considerations, such as capacitance and charges, also need to be characterized.

In this work, we demonstrate a 1.2 kV, 5 A GaN vertical power FinFET by incorporating edge termination structures. Besides BV and  $R_{\text{on,sp}}$ , device capacitance and charges were

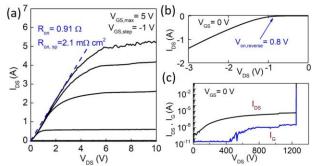

Fig. 2. (a) Device output curves and the extracted  $R_{on}$  and  $R_{sp,on}$ . (b) Reverse conduction curves and the extracted reverse turn-on voltage. (d) Off-state leakage characteristics at  $V_{\rm GS}$ =0 V with a BV of 1250 V.

characterized for power switching considerations. Switching FOMs were derived and then used to benchmark these devices with other existing 0.9-1.2 kV power transistors.

#### II. DEVICE FABRICATION & STATIC PERFORMANCE

The epitaxial structure in this work consists of a 0.3 µm-thick n<sup>+</sup>-GaN cap layer (Si: ~2×10<sup>19</sup> cm<sup>-3</sup>) and 9.5 µm-thick n<sup>-</sup>-GaN drift layer (N<sub>D</sub>~4×10<sup>15</sup> cm<sup>-3</sup>), grown by MOCVD on 2-inch n<sup>+</sup>-GaN substrates. As shown in Fig. 1(c), the large-area device consists of 498 fins with 350-µm fin length and 183 fins with 200-um fin length. The fin width, fin spacing and height are 0.18 µm, ~0.92 µm and ~1 µm, respectively. The area of active device regions is 0.23 mm<sup>2</sup>. The total device area, including the source/gate pad areas, is ~0.45 mm<sup>2</sup>. Device fabrication started with the fin etch and corner rounding [9][11]. Edge termination was then formed, for the first time in vertical GaN FinFETs, below the gate pad edges by argon implantation [12][13]. The details of edge termination will be elaborated in a future paper. After edge termination, the remaining fabrication steps for spacer oxides and gate, source and drain contacts were similar to our previous report [8]. Fig. 1 (b) shows a cross-section scanning electron microscopy (SEM) image of the fin region.

Fig. 2 (a) shows the device output characteristics. The extracted threshold voltage ( $V_{th}$ ) is 1.3 V (at  $I_{DS}$ =2 mA) with almost no hysteresis. A high drain current over 5 A and a  $R_{\rm on}$  of  $0.9 \Omega$  (a  $R_{\text{on,sp}}$  of  $2.1 \text{ m}\Omega \cdot \text{cm}^2$  normalized with the active device area) were obtained. Fig. 2 (b) shows the reverse conduction characteristics, revealing a reverse turn-on voltage ( $V_{\text{on,reverse}}$ ) of 0.8 V, which is much smaller than the one in SiC/GaN MOSFETs (typically 2~3 V) as no pn junctions are present in our FinFETs. This low  $V_{\text{on,reverse}}$  can reduce the power loss and eliminate the need for paralleling a freewheeling diode in many switching applications. Fig. 2 (c) shows the off-state characteristics, revealing a destructive BV over 1.2 kV (occurring at edge termination regions) with a µA-level leakage current at BV. The leakage current at high bias exhibits a  $ln(I) \propto V$  relation, indicating the variable-range-hopping through dislocations as the dominant leakage mechanism [14].

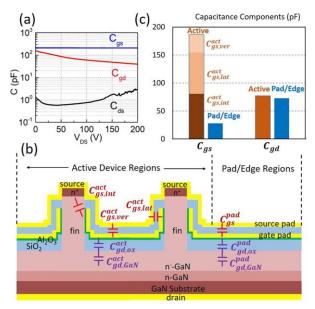

Device junction capacitances  $C_{ds}$ ,  $C_{gs}$  and  $C_{gd}$  were measured as a function of  $V_{\rm DS}$  (Fig. 3 (a)).  $C_{gs}$  and  $C_{gd}$  dominate the device capacitance, while  $C_{ds}$  is very small as the fin region is fully depleted at zero gate bias. Fig. 3 (b) illustrates the main components of  $C_{gs}$  and  $C_{gd}$  in in both device active regions and pad/edge regions. The  $C_{gs}$  in device active regions

Fig. 3. (a) Device junction capacitances  $C_{ds}$ ,  $C_{gs}$  and  $C_{gd}$  measured by using the Agilent B1505A power device analyzer and a custom-built RC circuit. (b) Schematics of different  $C_{gs}$  and  $C_{gd}$  components in the active and pad/edge regions of a GaN vertical FinFET. (c) Calculated components break-out for the measured  $C_{gs}$  and  $C_{gd}$ .

consists of three parts: intrinsic gate-source capacitance,  $C_{gs,int}^{act}$ , vertical parasitic capacitance,  $C_{gs,ver}^{act}$ , and lateral parasitic capacitance,  $C_{gs,ver}^{act}$ , and lateral parasitic capacitance,  $C_{gs,ver}^{act}$ . The  $C_{gs}$  in the pad/edge regions only has the  $C_{gs,ver}^{act}$  component. The  $C_{gd}$  consists of two parts: MOS capacitance,  $C_{gs,ox}$ , and drift-layer-depletion capacitance,  $C_{gs,GaN}$ . With the geometry parameters extracted from Fig. 1 (b), all oxide-based capacitances can be calculated based on the parallel-plate approximation (calculation details will be elaborated in a future paper). Fig. 3 (c) shows the calculated components break-out for  $C_{gs}$  and  $C_{gd}$ . The parasitic capacitance in the pad/edge regions can be further reduced by optimizing the device layout to minimize the source-gate overlap and gate pad areas in these regions.

Input capacitance  $C_{iss}$  (=  $C_{gs} + C_{gd}$ ), output capacitance  $C_{oss}$  (=  $C_{gd} + C_{ds}$ ), and reverse capacitance  $C_{rss}$  (=  $C_{gd}$ ), were then calculated for our GaN FinFETs, showing lower values than comparable 1.2 kV SiC and Si power transistors (see Table I).

#### III. SWITCHING CHARGES & FOMS

In general, device power loss under switching operations consists of the conduction losses, switching losses and the losses related to device/diode reverse conduction [15]–[17]:

$$P = P_{cond} + (P_{gate} + P_{Qoss}) + P_{rr}$$

$$= I^2 R_{on} D + Q_G V_G f_{sw} + Q_{gd} V_{DS} f_{sw} I_{DS} / I_G + P_{rr} \text{ (Hard SW)}$$

$$= I^2 R_{on} D + Q_G V_G f_{sw} + Q_{oss} V_{DS} f_{sw} + P_{rr} \text{ (Soft SW)}$$

where  $D$  is the duty cycle and  $f_{sw}$  is the switching frequency.

Based on the dominant switching loss in specific switching applications, different FOMs have been proposed to benchmark the performance of power devices, such as the  $R_{on} \cdot Q_{gd}$  for high-voltage hard-switching [16] and the  $R_{on} \cdot (Q_{oss} + Q_G)$  for resonant and soft-switching [17]. In these FOMs, the  $R_{on}$  accounts for conduction losses and the charges account for

| Device Technology               | Manufacturer /<br>Maker | $R_{ m on,sp} \ ({ m m}\Omega{ m cm}^2) \ (R_{ m on})$ | BV<br>(kV) | I <sub>rate</sub> (A) | Chip<br>Area<br>(mm²) | V <sub>TH</sub> (V) | C <sub>ISS</sub> (pF) | Coss<br>(pF) | Q <sub>G</sub> (nC) | Q <sub>GD</sub> (nC) | Q <sub>rr</sub> (nC) | Switching FOM $(n\Omega \cdot C)$ $R_{on} \cdot (Q_G + Q_{GD})$ $R_{on} \cdot (Q_G + Q_{GD} + Q_{TD})$ |

|---------------------------------|-------------------------|--------------------------------------------------------|------------|-----------------------|-----------------------|---------------------|-----------------------|--------------|---------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------|

| GaN Vertical FinFET (this work) | MIT                     | <b>2.1</b> (0.91 Ω)                                    | 1.2        | 5                     | 0.45                  | 1.3                 | 248.3*                | 42.2*        | 1.24                | 2.42                 | ~0                   | 3.3<br>~2.0 (pad optimized)                                                                            |

| SiC MOSFET<br>(CPM2-1200-0160B) | Cree                    | 2.7 [19]<br>(0.16 Ω)                                   | 1.2        | 20                    | 6.28                  | 2.5                 | 525                   | 47           | 34                  | 14                   | 105                  | 7.68 24.48 (include $Q_{rr}$ )                                                                         |

| SiC JFET Cascode<br>(UJN1208Z)  | United SiC              | 1.7**<br>(0.15 Ω)                                      | 1.2        | 18.4                  | >1.13***              | 4.4                 | 738                   | 58           | 30                  | 6                    | 63                   | 5.4 14.85 (include $Q_{\rm rr}$ )                                                                      |

| Si IGBT<br>(NGTB15N120FLWG)     | ON Semi                 | ~20<br>(~0.25 Ω)                                       | 1.2        | 15                    | 320                   | 2                   | 3600                  | 110          | 150                 | 68                   | 1500                 | 54.5 429.5 (include $Q_{\rm rr}$ )                                                                     |

| Si CoolMOS<br>(IPD90R1K2C3)     | Infineon                | ~8****<br>(1.2 Ω)                                      | 0.9        | 5                     | ~23.6                 | 3                   | 710                   | 35           | 28                  | 12                   | 3700                 | $48$ $4488 \text{ (include } Q_{rr})$                                                                  |

| GaN HEMT Cascode [20]           | Transphorm              | $(0.19 \Omega)$                                        | 1.2        | >20                   | N.A.                  | 2.3                 | N.A.                  | 43.1         | 10                  | N.A.                 | N.A.                 | N.A.                                                                                                   |

| Vertical GaN MOSFET [5]         | TOYODA GOSEI            | 2.7                                                    | 1.2        | 23.2                  | 2.25                  | 3.5                 |                       |              |                     | N                    | . A.                 |                                                                                                        |

| Vertical GaN CAVET [2]          | Avogy                   | 2.2                                                    | 1.5        | 2.3                   | 0.17                  | 0.5                 |                       |              |                     |                      |                      |                                                                                                        |

TABLE I. Summary and benchmark of device technologies and their key device metrics for 900-1200 V power switching applications.

Note:  $*(V_{DS}=200 \text{ V}; **Source: \frac{\text{http://unitedsic.com/cascodes}; ****Calculated by using the <math>R_{on}$  in the data sheet and the reported  $R_{on,sp}$ , reflecting the active device area (not including pad/edge areas); \*\*\*\*Source: Infineon's application note titled "CoolMOS<sup>TM</sup> C7: Mastering the Art of Quickness".

switching losses. To evaluate the performance of our new GaN vertical FinFETs in a broad range of power switching applications, the following power switching FOM is used considering all possible conduction and switching losses:

$$FOM_{sw} = R_{on}(Q_G + Q_{gd} + Q_{rr}) \tag{2}$$

This FOM is independent of device area or current ratings, and is suitable for evaluating our devices for both hard and soft switching (as  $Q_{oss} \approx Q_{gd}$  for our devices). As only majority carriers are involved in our devices,  $Q_{rr} \approx 0$ .  $Q_G$  is the amount of charge provided by the gate driver circuit to charge/discharge the  $C_{iss}$  during the device switching. As  $C_{iss}$  changes very little with junction biases,  $Q_G \approx C_{iss}V_G$ , where  $V_G$  is the gate bias for device on-state operation.  $Q_{gd}$  is the amount of charge depleted in the drift region in the off-state. As the drift layer is designed to be fully depleted at 1.2 kV for our device (punch-through model),  $Q_{gd} = qN_Dt_DA$ . Then the FOM of our GaN vertical FinFETs is given by:

$$FOM_{sw}^{FinFETs} = R_{on}(C_{iss}V_G + qN_Dt_DA) = 3.3 \ n\Omega \cdot C$$

(3) where  $V_G$  of 5 V is used;  $N_D$  ( $\sim$ 4×10<sup>15</sup> cm<sup>-3</sup>) and  $t_D$ (8.5 µm) is the net donor concentration and thickness of the drift region between the gate and drain, respectively; and  $A$  is the total device area ( $\sim$ 0.45 mm<sup>2</sup>).

Switching frequency of power devices is a compromise between the conduction and switching losses. Sound design typically requires these two losses to be about the same [18]. Given this design approach, from Eqn. (1), a practical  $f_{sw}$  of ~3.5 MHz is calculated for our 1.2 kV GaN vertical FinFETs, which is much higher than 1.2 kV Si IGBTs (10-20 kHz).

Table I summarizes the key device metrics of our 1.2 kV GaN vertical FinFETs, including the chip area,  $R_{\rm on}$  BV,  $V_{\rm th}$ , capacitances, switching charges and FOMs, benchmarked against state-of-the-art commercial 0.9-1.2 kV Si and SiC [19] power transistors. Other large-area 0.9-1.2 kV GaN devices at the R&D level [2][5][20] are also included, although, to the best of our knowledge, there is no complete experimental data reported so far for the capacitance and charges of these devices.

As shown, our device exhibited the best power switching FOMs among all 0.9-1.2 kV power transistors. This is attributable to the combination of the superior physical properties of GaN (high critical electric field and high mobility) and the merits of our vertical FinFET (small capacitances, low  $V_G$  and no  $Q_{TT}$ ).

Despite the excellent performance, there is still much room for improvement in our GaN vertical FinFETs. For example, if the pad capacitances can be minimized, the FOM could be reduced to ~2  $n\Omega \cdot C$ . On the other hand, the fin spacing currently used in our devices (0.92  $\mu$ m) is relatively large compared to the fin width (0.18  $\mu$ m). This indicates large room for improvement in  $R_{\text{on,sp}}$ , junction capacitances and charges by shrinking the fin spacing. From the fabrication point of view, the fin spacing could be well reduced to below 0.3  $\mu$ m, while the derivation of the optimum fin spacing requires a more comprehensive consideration of spreading resistance, capacitances and heat dissipation. We will do this derivation in the future work.

#### IV. SUMMARY

This work demonstrates a large-area 1.2 kV, 5 A GaN vertical power FinFET. Systematic device characterization of  $R_{\rm On}$ , BV,  $V_{\rm th}$  and capacitances is presented, followed by the charge analysis and FOM derivation for power switching applications. Our device shows superior power switching FOMs when compared to commercial 0.9-1.2 kV Si and SiC power transistors. This performance demonstrates the great potential of GaN vertical FinFETs for next-generation medium-voltage and high-frequency power applications.

#### REFERENCES

- [1] Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.-S. Lee, F. Gao, T. Fujishima, and T. Palacios, "Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2224–2230, Jul. 2013. DOI: 10.1109/TED.2013.2261072.

- [2] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, and I. C. Kizilyalli, "1.5-kV and 2.2-mΩ·cm² Vertical GaN Transistors on Bulk-GaN Substrates," *IEEE Electron Device Lett.*, vol. 35, no. 9, pp. 939–941, Sep. 2014. DOI: 10.1109/LED.2014.2339197.

- [3] S. Chowdhury, M. H. Wong, B. L. Swenson, and U. K. Mishra, "CAVET on Bulk GaN Substrates Achieved With MBE-Regrown AlGaN/GaN Layers to Suppress Dispersion", *IEEE Electron Device Lett.*, vol. 33, no. 1, pp. 41-43, Jan. 2012. DOI: 10.1109/LED.2011.2173456.

- [4] D. Ji, A. Agarwal, H. Li, W Li, S. Keller, and S. Chowdhury, "880V/2.7mΩcm² MIS Gate Trench CAVET on Bulk GaN Substrates" *IEEE Electron Device Lett.*, vol. 39, no. 6, pp. 863-865, Jan. 2018. DOI: 10.1109/LED.2018.2828844.

- [5] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "Over 10 A operation with switching characteristics of 1.2 kV-class vertical GaN trench MOSFETs on a bulk GaN substrate," in 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 459–462. DOI: 10.1109/ISPSD.2016.7520877.

- [6] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "1.8 mΩ·cm² vertical GaN-based trench metal—oxide—semiconductor field-effect transistors on a free-standing GaN substrate for 1.2-kV-class operation," *Appl. Phys. Express*, vol. 8, no. 5, p. 054101, May 2015. DOI: 10.7567/APEX.8.054101.

- [7] D. Ji, C. Gupta, S. H. Chan, A. Agarwal, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of large-area devices," in 2017 IEEE International Electron Devices Meeting (IEDM), 2017, pp. 9.4.1-9.4.4. DOI: 10.1109/IEDM.2017.8268359.

- [8] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, "1200 V GaN vertical fin power field-effect transistors," in 2017 IEEE International Electron Devices Meeting (IEDM), 2017, pp. 9.2.1-9.2.4. DOI: 10.1109/IEDM.2017.8268357.

- [9] M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-Performance GaN Vertical Fin Power Transistors on Bulk GaN Substrates," *IEEE Electron Device Lett.*, vol. 38, no. 4, pp. 509–512, Apr. 2017. DOI: 10.1109/LED.2005.860882.

- [10] M. Sun, M. Pan, X. Gao, and T. Palacios, "Vertical GaN power FET on bulk GaN substrate," in 2016 74th Annual Device Research Conference (DRC), 2016, pp. 1–2. DOI: 10.1109/DRC.2016.7548467.

- [11] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, and T. Palacios, "Trench formation and corner rounding in vertical GaN power devices," *Appl. Phys. Lett.*, vol. 110, no. 19, p. 193506, May 2017. DOI: 10.1063/1.4983558.

- [12] Y. Zhang, M. Sun, Z. Liu, D. Piedra, M. Pan, X. Gao, Y. Lin, A. Zubair, L. Yu, and T. Palacios, "Novel GaN trench MIS barrier Schottky rectifiers with implanted field rings," in 2016 IEEE International Electron Devices Meeting (IEDM), 2016, pp. 10.2.1-10.2.4. DOI: 10.1109/IEDM.2016.7838386.

- [13] Y. Zhang, M. Sun, H. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N. A. de Braga, R. V. Mickevicius, and T. Palacios, "Origin and Control of OFF-State Leakage Current in GaN-on-Si Vertical Diodes," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2155–2161, Jul. 2015. DOI: 10.1109/TED.2015.2426711.

- [14] Y. Zhang, H. Y. Wong, M. Sun, S. Joglekar, L. Yu, N. A. Braga, R. V. Mickevicius, and T. Palacios, "Design space and origin of off-state leakage in GaN vertical power diodes," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, pp. 35.1.1-35.1.4. DOI: 10.1109/IEDM.2015.7409830.

- [15] R. K. Williams, M. N. Darwish, R. A. Blanchard, R. Siemieniec, P. Rutter, and Y. Kawaguchi, "The Trench Power MOSFET—Part II: Application Specific VDMOS, LDMOS, Packaging, and Reliability," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 692–712, Mar. 2017. DOI: 10.1109/TED.2017.2655149.

- [16] A. Q. Huang, "New Unipolar Switching Power Device Figures of Merit," IEEE Electron Device Lett., vol. 25, no. 5, pp. 298–301, May 2004. DOI: 10.1109/LED.2004.826533.

- [17] D. Reusch and J. Strydom, "Evaluation of gallium nitride transistors in high frequency resonant and soft-switching DC-DC converters," in 2014 IEEE Applied Power Electronics Conference and Exposition - APEC 2014, Fort Worth, TX, USA, 2014, pp. 464–470. DOI: 10.1109/APEC.2014.6803349.

- [18] A. Q. Huang, "Power semiconductor devices for smart grid and renewable energy systems," in *Proceedings of IEEE*, vol. 105, no. 11, pp. 2019–2047, Nov. 2017. DOI: 10.1109/JPROC.2017.2687701.

- [19] J. W. Palmour, L. Cheng, V. Pala, E. V. Brunt, D. J. Lichtenwalner, G.-Y. Wang, J. Richmond, M. O'Loughlin, S. Ryu, S. T. Allen, A. A. Burk, and C. Scozzie, "Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV," in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Waikoloa, HI, USA, 2014, pp. 79–82. DOI: 10.1109/ISPSD.2014.6855980.

- [20] Y.-F. Wu, J. Gritters, L. Shen, R. P. Smith, and B. Swenson, "kV-Class GaN-on-Si HEMTs Enabling 99% Efficiency Converter at 800 V and 100 kHz," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2634–2637, Jun. 2014. DOI: 10.1109/TPEL.2013.2284248.