# MIT Open Access Articles

# Materials and processing issues in vertical GaN power electronics

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

**Citation:** Hu, Jie, Yuhao Zhang, Min Sun, Daniel Piedra, Nadim Chowdhury and Tomás Palacios. "Materials and processing issues in vertical GaN power electronics." Materials Science in Semiconductor Processing 78 (2017).

As Published: 10.1016/j.mssp.2017.09.033

Publisher: Elsevier BV

Persistent URL: https://hdl.handle.net/1721.1/121717

**Version:** Author's final manuscript: final author's manuscript post peer review, without publisher's formatting or copy editing

Terms of use: Creative Commons Attribution-NonCommercial-NoDerivs License

Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

### Materials and processing issues in vertical GaN power electronics

Jie Hu<sup>\*,1</sup>, Yuhao Zhang<sup>1</sup>, Min Sun, Daniel Piedra, Nadim Chowdhury, Tomás Palacios

Microsystems Technology Laboratories, Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA 02139, USA

### ARTICLE INFO

Keywords: Vertical GaN Power transistor Rectifier Corner rounding Edge termination GaN-on-GaN P-GaN activation Implantation Power electronics Device processing

### ABSTRACT

Silicon-based power devices are reaching their fundamental performance limit. The use of wide-bandgap semiconductors with superior material properties over silicon offers the potential for power electronic systems with much higher power densities and higher conversion efficiency. GaN, with a high critical electric field and carrier mobility, is considered one of the most promising candidates for future high-power, high frequency and high temperature applications. High voltage transistors and diodes based on both lateral and vertical structures are of great interest for future power electronics. Particularly, vertical GaN power devices have recently attracted increasing attention due to their many unique properties. This paper reviews recent progress and key remaining challenges towards the development of high-performance vertical GaN transistors and diodes with emphasis on the materials and processing issues related to each device architecture.

#### 1. Introduction

Power electronics is the application of electronic switching devices for efficient conversion and the control of electrical power [1]. For the past 60 years, silicon-based power devices have been the dominant player used in power circuits to accomplish these tasks. The design of new device structures such as thyristors and insulated gate bipolar transistors (IGBT) and the optimization of the fabrication processes have enabled a significant improvement in device performance. However, Si-based power devices are now reaching their theoretical limit. Innovation in power devices is needed to further improve the performance of power electronics and bring us closer to realize a sustainable society.

Wide-bandgap (WBG) semiconductors such as silicon carbide (SiC) and gallium nitride (GaN) are promising material candidates for the next generation power devices. Due to their high critical electric field, WBG semiconductors can enable the fabrication of power devices with lower capacitance and resistance for a given breakdown voltage than their Si counterparts. Table 1 shows the comparison of material parameters for GaN with Si and SiC. The Baliga's figure of merit (BFOM) ( $\epsilon_S \mu_n E_c^3$ ) [2,3], which describes the fundamental relationship between on-resistance and breakdown voltage (BV), shows that GaN promises the best performance among the current candidates for power electronics. GaN-based devices can meet the increasing performance demands of the evolving power systems, operating at higher power densities and temperatures than existing Si power devices.

Lateral power transistors and diodes based on AlGaN/GaN heterostructures have already demonstrated excellent electrical characteristics [4-9], and enhancement-mode GaN products are commercially available since June 2009 [10]. However, the power handling of GaN transistors with a lateral configuration is typically limited to a few kW. For higher power ratings, the chip size of lateral GaN transistors increases significantly, resulting in inefficient utilization of the material, difficult current extraction, and poor reliability. The vertical buffer breakdown also limits the operating voltage of the device below 1 kV due to the difficulty of growing thicker (Al)GaN layers on a silicon substrate [11]. Additionally, lateral GaN transistors and diodes suffer from electron trapping at the surface due to the presence of high surface electric field under off-state operation [12,13]. This current collapse phenomenon can severely degrade the device performance and affect its long-term stability and reliability, especially for very high-voltage operations [14,15].

Power devices based on vertical GaN are promising candidates to overcome the challenges described above for the lateral GaN transistors. The breakdown voltage in vertical GaN devices can be increased by increasing the thickness of the drift region, while keeping the device footprint constant. The maximum electric field in vertical GaN devices is far away from the surface, which minimizes trapping effects and reduces dynamic on-resistance. Moreover, the vertical current extraction in vertical GaN transistors allows for the delivery of much higher power density than in lateral GaN devices. In vertical GaN devices, the electric field is more uniform and current distribution is much more

https://doi.org/10.1016/j.mssp.2017.09.033

Received 18 July 2017; Received in revised form 22 September 2017; Accepted 27 September 2017 1369-8001/ © 2017 Elsevier Ltd. All rights reserved.

<sup>\*</sup> Corresponding author.

E-mail address: JieHu@mit.edu (J. Hu).

<sup>&</sup>lt;sup>1</sup> Contribute equally to this review paper.

#### J. Hu et al

#### Table 1

Comparison of material parameter and BFOM for Si, SiC and GaN.

| 9.7  | 0.0          |

|------|--------------|

| 1100 | 8.9<br>1100  |

| 2    | 3.75<br>3713 |

|      | 2<br>675     |

spread, giving rise to a superior thermal performance than lateral GaN devices [16]. Recently, various transistor and diode architectures based on vertical GaN have been reported. Vertical GaN p-n diodes with breakdown voltage over 4 kV [73] and vertical GaN trench metal-oxide-semiconductor field effect transistor (MOSFET) with blocking voltage of 1.6 kV [18] have been demonstrated on free-standing GaN substrate. To reduce the substrate cost, quasi- and fully vertical GaN-on-Si power diodes with excellent performance have also been recently demonstrated with a BV over 500 V [19].

This paper summarizes the recent progress of vertical GaN power electronics and highlights the issues related to the material growth and device fabrication. The paper is organized as follows. Section 2 deals with the material growth and doping control. Section 3 introduces various vertical GaN transistors and discuss the issues of device processing. Section 4 reviews the progress on vertical GaN diodes/rectifiers on both free-standing GaN substrate and Si substrate, and benchmarks the performance.

#### 2. Materials growth and doping

#### 2.1. GaN substrate

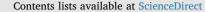

The demands for high-quality bulk GaN in solid-state lighting and power electronics have driven the development and commercialization of bulk GaN substrate. The classical Czochralski crystal growth process commonly used for the growth of silicon and GaAs cannot be used for GaN, due to its extreme conditions of melting. Therefore, the most common and cost-effective approach for manufacturing GaN substrates today is the hydride vapor phase epitaxy (HVPE) [17,18], which is able to produce high-quality material at high growth rate [22]. The HVPE growth of GaN substrate is described in Fig. 1(a). Freestanding GaN crystals are typically grown on foreign substrates followed by substrate lift-off process. Fig. 1(b) shows the thermal expansion coefficient of typical substrates and their lattice mismatch with GaN [20]. The first HVPE-GaN was reported by Maruska et al. in 1969, using sapphire as the substrate [23]. However, the large mismatch in the thermal expansion coefficients between GaN and the sapphire substrate typically creates cracking in the GaN layer. The lower mismatch in the thermal

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

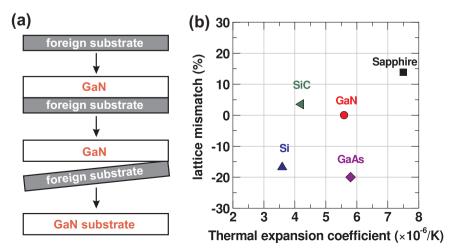

expansion coefficient makes GaAs a better substrate candidate to avoid cracks and reduce wafer bending [20]. Furthermore, GaAs can be etched away easily by aqua regia [24] or by mechanical grinding and lapping [20]. In 2000, Motoki et al. successfully prepared 2-inch freestanding GaN substrates using GaAs as a starting substrate for the first time. However, a large number of dislocations (in the order of  $10^9 \text{ cm}^{-2}$ ) form at the interface between GaN and the foreign substrates, due to the large mismatch in crystal lattice. The threading dislocation density (TDD) of the GaN layers on GaAs can be reduced to  $10^{6}$ – $10^{7}$  cm<sup>-2</sup> by utilizing the void associated separation (VAS) method [25]. By using additional dislocation-reduction techniques [26], the TDD can be even reduced to  $10^4 \text{ cm}^{-2}$  over an area of  $\sim \text{ mm}^2$ . To illustrate the importance of foreign substrate selection on the TDD. Fig. 2 compares the dislocation density of GaN crystal grown on sapphire and GaAs by using HVPE. Bulk GaN substrate with low TDD is of particular importance for vertical GaN power devices. In [25], a p-n diode with breakdown voltage over 3000 V has been fabricated by using VAS GaN substrate with reduced dislocation density. Currently, "native" GaN substrates are available in wafer diameters up to 6-in. However, the substrate cost is high and becomes a significant component of the total cost of the device due to limited production volume.

To reduce the cost of the substrate, there is an important effort worldwide to grow GaN on large silicon wafers. This growth is, however, challenging due to the large mismatch in thermal expansion coefficient and lattice constant between GaN and silicon [Fig. 1(b)], which results in difficulties to grow high-quality and thick n<sup>+</sup>-GaN/n<sup>-</sup>-GaN layers by using silicon as a carrier. The TDD of GaN epilayers grown on silicon is ~  $10^9$  cm<sup>-2</sup>, and the thickness of the entire GaN stack is limited to a few microns, making the fabrication of high voltage vertical devices very difficult.

#### 2.2. n-type GaN by metal-organic chemical vapor deposition

For high-voltage vertical GaN devices, the thickness and doping of the  $n^-$ -GaN drift region that blocks most of the voltage needs to be well-designed and controlled. This layer is typically grown by using metal-organic chemical vapor deposition (MOCVD) for both GaN-on-GaN and GaN-on-Si technologies. Fig. 3 shows the cross-section of the basic device epitaxial-structure, highlighting the lightly doped GaN drift region and the electric field profile in the drift layer when the critical electric field ( $E_{\rm C}$ ) is reached. From electrostatics, the breakdown voltage (BV) can be described as [27]

$$BV = E_C W - \frac{q N_D W^2}{2\epsilon_S} \tag{1}$$

where *W* is the thickness of the n<sup>-</sup>-GaN drift layer, *q* is the electron charge,  $\epsilon_s$  is the permittivity of GaN, and  $N_D$  is the net carrier density of

**Fig. 1.** (a) Preparation process of GaN substrate by using HVPE method. (b) Thermal expansion coefficient of substrate and lattice mismatch with GaN [20].

#### J. Hu et al.

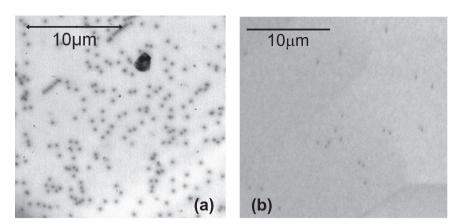

the n<sup>-</sup> GaN layer. Fig. 4 benchmarks the breakdown voltage vs drift layer thickness in vertical GaN power devices on GaN and silicon substrates from literature. The solid lines represent the theoretical limit of the BV as a function of the drift layer thickness for 3 different doping concentration levels in the drift layer. As shown in the figure, the thickness of the GaN drift layer in GaN-on-silicon technology is currently limited to about 5 µm.

From the equation above and the results in Fig. 4, it is clear that the net carrier concentration in the drift layer plays a crucial role and that it should be kept below  $10^{16}$  cm<sup>-3</sup> to achieve high breakdown voltage. It is however difficult to achieve reproducible doping densities in the  $10^{15}$ - $10^{16}$  cm<sup>-3</sup> range by MOCVD [28]. It was reported that the MOCVD-(Al)GaN epitaxial layers can be incoporated with impurities including Oxygen, Carbon, etc. Oxygen as a shallow donor in Wurtzite GaN with a transition to a DX-like state under hydrostatic pressure has been studied by first-principle calculation and experiments [29,30]. It was also found out that Oxygen incorporation was less susceptible to growth conditions than that of carbon [31]. The carbon incorporation is introduced by the gallium source in MOCVD (i.e. trimethyl gallium (TMG) or triethyl gallium) [32]. By growing the GaN under an optimized MOCVD conditions at high temperature, high growth pressure and a high V:III ratio, the carbon background doping can be reduced to  $10^{15}$ - $10^{16}$  cm<sup>-3</sup> range [28]. Thus the net doping (N<sub>D</sub>-N<sub>A</sub>) in the GaN drift region can be controlled through the silicon concentration (donor N<sub>D</sub>), which is determined by the flow rate of diluted silane [28,32]. It should be noted that the control of the net doping in GaN should take into account of all impurities (O, H, C, etc.). It is generally assumed that carbon creates deep acceptor states in GaN by sitting at the nitrogen site, compensating the intentional donors. However, Tanaka et al. recently reported that donor-like CGa (gallium-site carbon) can appear when the carbon concentration is low. Ref. [32] proposes a two-level C<sub>Ga</sub> – C<sub>N</sub> model which highlights that the control of the residual carbon

### (a) (b) $E_c$ channel/junction ► E 0 N GaN drift layer W $E_{c} - qN_{D}W/\varepsilon_{o}\varepsilon_{r}$ substrate ohmic metal

depth

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 2. Plan-view cathodluminescience (CL) images showing threading dislocation as dark spots for GaN grown on sapphire substrate (a) and on GaAs substrate (b) [21].

Fig. 4. The breakdown voltage versus drift layer thickness for various vertical GaN transistors and diodes. The solid lines represent the theoretical limit of the BV as a function of the drift layer thickness for different doping concentration of the drift layer.

concentration in the n-GaN drift layer is essential to maintain highvoltage operation of GaN power devices without degrading the on-resistance.

#### 2.3. Activation of implanted p-type GaN

The success of many vertical Si and SiC power devices relies on the p-type regions to form junction termination extension (JTE) structures [35] and avoid electric field crowding at the edge of the junction, thus achieving high breakdown voltage [36]. Vertical GaN power devices can benefit from selective p-type doping in implanted guard rings for

> Fig. 3. (a) Cross-section schematic of the device epi-structure highlighting the lightly doped GaN drift layer. (b) The electric field profile in the drift layer when breakdown phenomenon is occurring.

electric field spreading, merged pn/Schottky (MPS) structures to protect surge currents, and current blocking layers (CBL) for the current aperture vertical electron transistors (CAVET) [37,38]. However, the activation of implanted p-type dopant (i.e. Mg) requires an annealing temperature over 1300 °C [39], which causes the decomposition of GaN at atmospheric pressure. The decomposition brings about a loss of nitrogen, surface damage and the creation of nitrogen vacancies [33,40]. In order to prevent the loss of nitrogen loss at the GaN surface, it is desirable to deposit a high-quality capping layer before the annealing step, followed by a reliable removal process after annealing [41]. Moreover, permanent clusters can be formed during the Mg implantation, and N vacancy complexes can prevent Mg diffusion into the Ga vacancy sites during the activation annealing [41]. Due to these issues, the energy and dose of the implanted Mg species are currently limited [41].

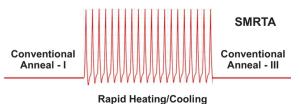

To overcome the issues above, Feigelson et al. combined a multicycle rapid thermal annealing (MRTA) process in a controlled  $N_2$  overpressure with an AlN cap deposited by chemical vapor deposition (CVD) [39]. The MRTA process enabled the activation of implanted Mg with activation efficiency of over 8% and the demonstration of p-type conductivity [42]. Although the implantation-induced lattice damage can be restored by the proposed MRTA process, additional structural changes in the GaN sample were created because of the process with rapid heating and cooling cycles [33]. To overcome this issue, a modified MRTA process has been developed by introducing an conventional annealing step after the multi rapid heating and cooling cycles as shown in Fig. 5. It was also demonstrated that this symmetric MRTA (SMRTA) process can improve the p-type conductivity in the samples compared with those annealed with the MRTA process [33].

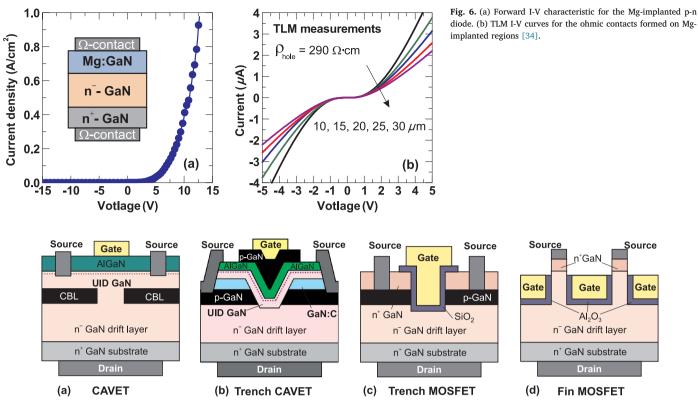

High performance vertical GaN junction barrier Schottky (JBS) rectifiers have been recently demonstrated by using implanted Mg in n-GaN followed by activation using the SMRTA process [34]. The annealing procedure consists of a 1000 °C anneal for 30 min, followed by 40 pulses of 20 s up to 1350 °C for each cycle, and another 1000 °C anneal for 30 min. Fig. 6 (a) shows the rectifying behavior of the implanted Mg pn diode with a turn-on voltage of ~ 3.5 V. Fig. 6(b) presents the I – V curves for the "ohmic" contacts formed on implanted Mg regions. Due to a low acceptor concentration (~ 5 × 10<sup>16</sup> cm<sup>-3</sup>) in the p-GaN, the TLM I-V curves are not perfectly linear. These device results demonstrate the successful p-type implant activation, which will be a key enabling step for next-generation vertical GaN power electronics [34].

#### 3. Vertical GaN power devices

Thanks to the recent progress in GaN material growth and device processing, several device architectures based on vertical GaN have been proposed. In this section, we will introduce each device structure and discuss their specific processing challenges.

Pulses - II

Fig. 5. Schematic of the temperature profiles for the Symmetric Multicycle Rapid Thermal Annealing (SMRTA) process. The SMRTA process includes three stages: a preliminary conventional anneal, rapid heating/cooling cycles, and a final conventional anneal [33].

#### 3.1. Vertical GaN transistor

Fig. 7 shows four different architectures for vertical GaN transistors fabricated on free-standing GaN substrate. In 2004, Ben Yaacov et al. [37] proposed a current aperture vertical electron transistor (CAVET) structure [Fig. 7(a)], similar to a double diffused metal-oxide-semiconductor (DMOS) structure. One of the key challenges in the CAVET is to design a robust current blocking layer (CBL) to suppress the leakage current in the vertical direction. In the first demonstration of CAVET, the CBL was formed with Mg-doped GaN grown by MOCVD to create an energy barrier below the source. In this case, the aperture region requires dry-etching of the Mg-doped GaN and a regrowth of the n-GaN channel. It was reported that etching of the aperture region exposes non-c planes and regrowth on such facets can result in a non-planar surface. This leads to severe gate leakage current [37]. Other studies showed that high concentration of n-type impurities tend to incorporate in the aperture region. This causes an increase of the peak electric field in the channel and a reduction of the device breakdown voltage. To circumvent these issues, a selective Mg-ion-implanted GaN layer was used as the CBL without the regrowth of the GaN in the aperture region [38]. However, the AlGaN/GaN layers were grown by MOCVD on top of the Mg-doped CBL. Memory effects related to Mg induced Mg out-diffusion into the AlGaN/GaN layers [43], giving rise to reliability issues. To suppress the diffusion of Mg and improve the yield and reproducibility, Chowdhury et al. used Plasma-MBE technique to grow AlGaN/ GaN layers at low temperature (720 °C) [44]. AlGaN/GaN CAVET with a combination of MOCVD and MBE-growth techniques has demonstrated excellent performance with good repeatability, making it very promising for power electronics.

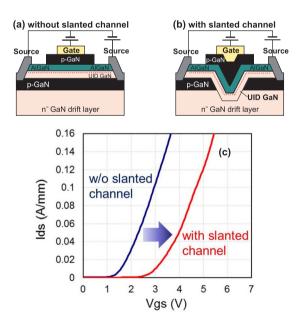

Another critical issue related to the original CAVET structure is its intrinsic normally-on operation and poor pinch-off capability [38,46]. Shibata et al. proposed a new vertical GaN transistor by using a trench CAVET structure [45]. The device features a regrowth of p-type gate/ AlGaN/GaN epitaxial layers over the V-groove [Fig. 7(b)]. It was shown that the polarization charges at the AlGaN/GaN heterojunction reduce with the increase of the titled angle from the c-plane. Fig. 8 shows that the lateral p-type gate transistor with a slanted channel leads to 1.5 V higher  $V_{\rm TH}$  compared to the transistor fabricated on the c-plane. By implementing the trench CAVET structure, a high  $V_{TH}$  of 2.5 V was achieved. In both CAVET and trench CAVET structures, the leakage path through the CBL causing the punch-through current can limit its high-voltage operation. It is mainly attributed to the activation inefficiency of the Mg-doped p-type layer. In [45], a thin carbon-doped GaN layer was inserted to reduce the leakage current in the p-GaN region. A hybrid blocking layers (HBLs) with a carbon-doped GaN and ptype GaN well layer successfully reduces the punch-through effect and improves the BV from 580 V to 1.7 kV.

A second type of vertical GaN transistor is the vertical trench MOSFET [Fig. 7(c)] which has the advantage of high packing density and the absence of the JFET region [48,49]. One of the main challenges of trench MOSFET is to obtain a reliable positive  $V_{\rm TH}$  for real normallyoff operation. In [50], the channel of the GaN MOSFET is fabricated on (0001) plane, where spontaneous and piezo-electric polarization effects are present. This channel formation results in poor pinch-off capability of the MOSFET due to the charges induced at the GaN/dielectric interface. Therefore, it is attractive to use a non-polar surface by trench etching on (0001) plane GaN [51]. The dry etching for the trench formation is performed by using Cl<sub>2</sub>/BCl<sub>3</sub> gases. However, the increased surface roughness and the damage by the ion bombardment make the dry-etched surface unsuitable for the gate channel region. Therefore, post-treatment of the etched surface is necessary for smoothing the surface and removing the damage [52]. Itoh et al. reported a smooth (1100) plane by using KOH wet etching [53]. To avoid the contamination from alkaline metal, TMAH-based wet clean was used to achieve smooth non-polar (1100) plane [51]. Recently, a damage-free corner rounding technology was developed bv using

J. Hu et al.

Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 7. Schematic of representative vertical GaN transistors: (a) current aperture vertical electron transistor (CAVET), (b) trench CAVET with V-shaped regrowth channel, (c) trench metal-oxide-semiconductor field effect transistor (MOSFET), (d) vertical fin MOSFET.

**Fig. 8.** (a) Lateral transistor with a p-type gate without using a slanted channel. (b) The lateral transistor with a p-type gate structure in a slanted channel. (c) The comparison of the transfer characteristics of the two transistors. By using a slanted channel, 1.5 V higher  $V_{\rm TH}$  can be obtained compared to the transistor without slanted channel [45].

Tetramethylammonium hydroxide wet etching and piranha clean [52]. By optimizing the ICP dry etching conditions and applying the rounding technology, different trench shapes such as flat-bottom rounded trench and tapered-bottom rounded trench have been demonstrated. The U-shape trench with rounded corners and smooth sidewalls is optimal to achieve high-voltage vertical GaN power devices, due to the suppression of the electric field crowding at the corners [52].

Due to the lack of suitable native oxide, the gate stability is always a concern for GaN-based MOSFET. In [49], an AlN/SiN dielectric stack grown by MOCVD was used. However, a hysteresis of ~ 0.6 V was observed from gate bias double-sweeps. This hysteresis indicates the existence of interface states at the gate dielectric and the p-GaN sidewall or border traps in the gate dielectric. To ensure an improved step coverage, atomic layer deposited (ALD) SiO<sub>2</sub> was deposited as gate dielectric in [54]. A hysteresis of ~ 0.5 V was also seen in the GaN MOSFET with ALD SiO<sub>2</sub> as the gate dielectric.

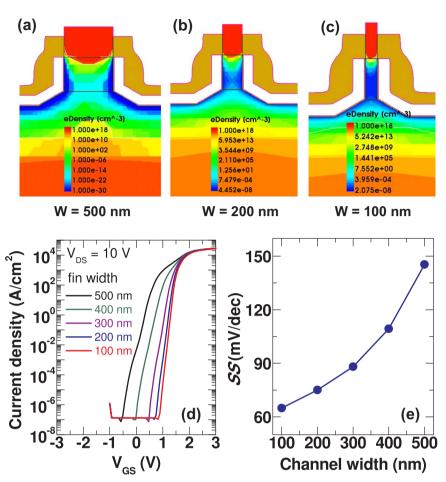

In the GaN CAVET and Trench MOSFET structures, epitaxial regrowth or p-GaN layer for the CBL or channel layer is required. This increases the process complexity and introduces additional epitaxial cost. Additionally, the poor transport properties of the inverted p-GaN channel results in high on-resistance [54-56,48]. Recently, a normallyoff GaN vertical fin MOSFET [Fig. 7(d)] with excellent performance has been demonstrated [47]. One key feature of this novel fin MOSFET is that only n-GaN epitaxial layers are used, while no regrowth or p-GaN layer is needed to achieve high-voltage blocking capability at VGS of 0 V. The enhancement-mode operation of this fin vertical MOSFET relies on the submicron fin technology and the control of the doping in the n-GaN channel. Fig. 9(a)-(c) show the simulated electron density in the fin structure for different fin width, where the Si doping concentration in the n-GaN drift layer is  $\sim 2 \times 10^{16}$  cm<sup>-3</sup>. As the fin width scales down to 200 nm or below, the channel in the fin is fully depleted. This allows for normally-off operation and the suppression of punchthrough leakage currents. Moreover, the subthreshold slope of the transfer curves is also improved by scaling down the fin width without sacrificing the on-state current [Fig. 9(d)-(e)]. With a channel fin width of 180 nm, the GaN fin MOSFET with a threshold voltage of 1.0 V and an excellent subthreshold swing of 75 mV/dec was demonstrated. The normalized on-resistance (to the total active fin area) of this device is  $0.36 \text{ m}\Omega \text{ cm}^2$ . A further reduction of the on-resistance can be achieved by optimizing the ohmic annealing temperature, although a careful optimization is needed to not increase the gate leakage current [47].

J. Hu et al.

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

**Fig. 9.** (a)-(c) Simulated electron density distribution in the fin at equilibrium for fin width of 500 nm, 200 nm, and 100 nm, respectively. (d) Simulated transfer characteristics for different fin width at VDS of 10 V. (e) Simulated subthreshold slope (SS) as a function of the fin width.

In order to obtain smooth sidewalls in the fin, a Cl<sub>2</sub>/BCl<sub>3</sub>-based dry etch is performed followed by a wet etch based on hot TMAH [47,57]. It was found out that the sidewalls are very rough showing many triangular shapes, when the fins were aligned to m-plane ( $< 1\overline{100} >$ ), since wet etching of GaN is dependent on the crystal orientation [53]. By aligning the fin to the a-plane instead of m-plane, a much smoother sidewalls of the fin were obtained. In the gate fabrication, a 15-nm Al<sub>2</sub>O<sub>3</sub> is used as the gate dielectric by atomic layer deposition (ALD). A sputtered molybdenum is deposited as the gate metal. The conformal process enabled by ALD and sputtering is essential to avoid electrical short between gate and source. Additionally, a SiO<sub>2</sub> spacer was used to allow the isolation between the gate and source electrodes.

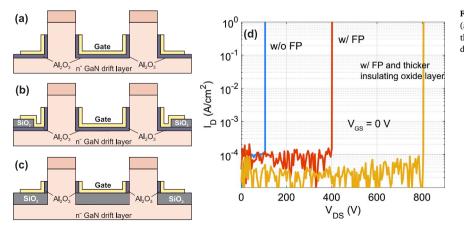

In the vertical fin transistors under off-state operation, a high peak electric field is present at the edge of the gate and at the bottom of the fins in the GaN. Without a design of edge termination structure [Fig. 10(a)], the breakdown voltage (BV) is limited to 100 V. With the implementation of a gate field plate [Fig. 10(b)], the BV is increased to 400 V. The breakdown mechanism in these structures is attributed to the failure of the gate dielectric due to a concentrated electric field at the edge. To avoid this pre-mature degradation, a 100-nm thick oxide layer was deposited in the etched trench to reduce the electric field in the ALD  $Al_2O_3$  gate dielectric. This has increased the BV up to 800 V. From gate bias double-sweeps, no hysteresis was observed indicating a very good interface between the ALD  $Al_2O_3$  and the GaN sidewalls. Extensive reliability studies on this device are still on-going to investigate its degradation mechanisms [58].

**Fig. 10.** Cross-section schematic of transistor without field plate (a), with a gate field plate at the device edge (b), with an oxide in the trench (c). (d) Breakdown measurements on three transistor designs [47].

#### J. Hu et al

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

#### 3.2. Vertical GaN diodes

#### 3.2.1. Vertical GaN-on-GaN diodes

The first demonstration of vertical GaN power diodes dates back to over 16 years ago [59]. There are two basic types of vertical power diodes, i.e. pn diodes and Schottky barrier diodes (SBDs). Vertical GaN pn diodes with a specific on-resistance ( $R_{ON}$ ) of  $2 \, m\Omega \, cm^2$  for a breakdown voltage (BV) of 2.6 kV and 2.9 m $\Omega \, cm^2$  for a BV of 3.7 kV [26] have been demonstrated. A more recent paper reported a specific  $R_{ON}$  of 0.95 m $\Omega \, cm^2$  for a BV of 3.48 kV [60]. These performances showed near-theoretical power figure of merit. Avalanche breakdown capability with excellent device robustness were also been demonstrated in GaN vertical pn diodes [61].

Despite the high BV and low leakage of GaN pn diodes, their large turn-on voltage ( $V_{ON} > 3 V$ ), due to the large bandgap of GaN, can result in high conduction loss in a power switching circuit. Vertical GaN SBDs have a much lower  $V_{ON}$  (< 1 V), but suffer from high OFF-state leakage current. State-of-the-art vertical GaN SBDs have been reported with a BV of 1.1 kV and  $R_{ON}$  of  $2 m\Omega \text{ cm}^2$  [62].

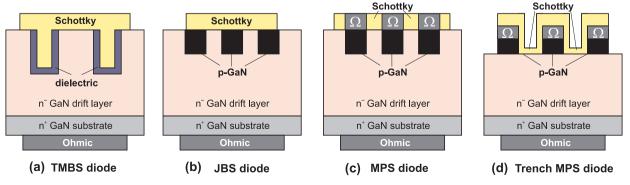

Several advanced structures have been developed in Si and SiC devices to combine the good forward characteristics of SBDs (e.g. low turn-on voltage) and reverse characteristics of pn diodes (e.g. low leakage current and high BV). The key concept for these advanced diodes is to move the peak electric field from the top Schottky contact into the bulk semiconductor device at high reverse biases, while maintaining good Schottky-like forward characteristics. For example, the trench metal-insulator-semiconductor (MIS) barrier Schottky (TMBS) diode [Fig. 11(a)] consists of multiple trenches and utilizes the MIS structures at the trench bottoms and sidewalls to reduce the electric field at the top Schottky barrier contact. The junction barrier Schottky (JBS) diodes [Fig. 11(b)] benefit from the pn junctions in the lateral direction to reduce the electric field at the Schottky contact. The merged pn-Schottky (MPS) diodes [Fig. 11(c)] have similar structures with JBS diodes, but the top anode forms Ohmic contacts to p-type grids, which could sustain a large inductive surge current.

Vertical GaN TMBS diodes were demonstrated in 2016 by combining the TMBS structure and field rings [63]. These devices showed 10<sup>4</sup>-fold lower leakage current and a significantly improved BV compared to conventional vertical GaN SBDs. Vertical JBS diodes were also demonstrated by selective p-type ion implantation and activation [34,64]. Due to the difficulties in p-type ion activation in GaN, the lateral pn junctions in vertical JBS diodes were also made by n-type ion implantation into epitaxial p-GaN layers [34]. Vertical GaN MPS diodes were demonstrated by making trenches through the epitaxially-grown p-GaN layers [Fig. 11(d)] [65,66], a BV close to 2 kV was reported [66]. Second turn-on in forward characteristics was demonstrated in these MPS diodes, indicating the capability to sustain large inductive currents. However, compared to MPS diode structure incorporating lateral pn junctions in semiconductor devices [Fig. 11(c)], these trench-MPS diodes could not take the advantage of the lateral depletion of pn junctions at high reverse biases.

In spite of the great progress of these advanced vertical diodes, the full potential of vertical GaN SBDs and advanced SBDs has not been exploited yet. The BV demonstrated in these devices, with no avalanche capability reported, is still much lower than the avalanche BV in vertical GaN pn diodes. The lack of avalanche capability greatly compromises the device robustness when operating in inductive switching environments. Although the nature of avalanche breakdown is still not fully understood in GaN devices, a key factor is believed to be good edge termination technologies and a way to remove holes from the structure, which is still lacking in vertical GaN unipolar diodes.

The development of advanced vertical GaN SBDs is also at an early stage. From the discussion on JBS and MPS diodes, it can be seen that a key issue is to make high-quality and defect-free patterned lateral pn junctions. In particular, p-type ion implantation and activation in GaN are far from mature. The activation ratio for acceptors is typically below 5%, resulting in very low concentration and mobility for the activated free holes. This makes it difficult to form Ohmic contact onto implanted p-GaN regions, greatly limiting the performance of MPS diodes with pn junctions incorporated into the drift region.

#### 3.2.2. Vertical GaN-on-Si diodes

While most vertical devices utilize expensive GaN substrates, the commercialization of vertical GaN power devices has been hindered by the high cost of bulk GaN substrates. The mainstream GaN substrates are 2-in., while 4- and 6-in. GaN substrates are available very recently in small volumes. The wafer cost (per area) for 2-in. GaN-on-GaN is  $60-100/\text{cm}^2$ , still much higher than the cost for 4-in. SiC (~  $8/\text{cm}^2$ ) and 8-in. GaN-on-Si (~  $1/\text{cm}^2$ ) [57,8]. The demonstration of vertical GaN devices on Si substrates could allow for almost 100-fold lower wafer and epitaxial cost as well as access to 8-in. fabrication facilities [8].

There are, however, two main challenges for the demonstration of high performance vertical GaN-on-Si devices: (a) high dislocation (typically  $\sim 10^9 \, {\rm cm}^{-2}$ ) in GaN layers grown on Si substrates, and (b) limited thickness for the GaN layer that can be grown on Si substrates and buffer layers, due to the lattice and thermal stress.

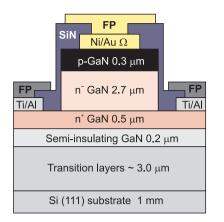

First vertical GaN-on-Si power diodes were demonstrated in 2014, by utilizing a quasi-vertical structure [67], where a mesa structure was created and the anode and cathode located on the same side of the wafer. With only 1–1.5–µm-thick drift region, these diodes exhibited a BV of 200–300 V with a  $R_{ON}$  of 6–10 m $\Omega$  cm<sup>2</sup>. Three advanced processes, including the plasma treatment, Tetramethylammonium hydroxide wet etching and field ring implantation, greatly reduced the parasitic leakage current along the etching sidewalls in the quasi-vertical devices [57]. By increasing the drift region thickness, lowering the carrier concentration in the drift region and optimizing the current spreading layer to reduce device  $R_{ON}$  [19], a BV over 500 V with a  $R_{ON}$  below 1 m $\Omega$  cm<sup>2</sup> as well as the capability to operate up to 300 °C have been demonstrated in quasi-vertical GaN-on-Si pn diodes [19] (Fig. 12).

Fig. 11. Schematics of (a) TMBS diodes, (b) JBS diodes, (c) MPS diodes and (d) trench-MPS diodes.

Fig. 12. Device cross-section of a quasi-vertical GaN-on-Si pn diode.

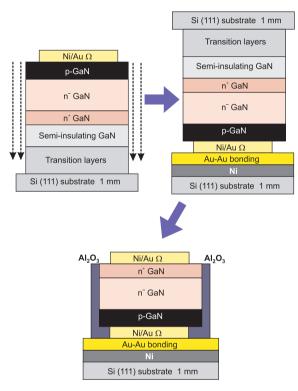

Fig. 13. The main steps to fabricate fully-vertical GaN-on-Si pn diodes by layer transfer technologies.

Fully-vertical GaN-on-Si power diodes have also been recently developed. The fully-vertical structure, where the electrodes are located at different sides of the wafer, could allow for a more uniform current distribution and a smaller device area, but is difficult to implement in GaN-on-Si structures due to the highly resistive and defective buffer layers. This challenge has been addressed by two methods: (a) layer transfer technologies (Fig. 13) [19,69], where the original wafer was flipped over and bonded to another Si substrate, followed by the removal of the original Si substrate and buffer layers; (b) conductive buffer layers [70], where the whole buffer layers were highly doped (Si: over  $10^{19}$  cm<sup>-3</sup>) to make them conductive. The state-of-the-art fully-vertical GaN-on-Si power diodes shows a BV over 500 V with a R<sub>ON</sub> below 1 m $\Omega$  cm<sup>2</sup> [19,71].

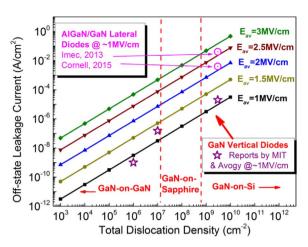

To understand the full potential of vertical GaN-on Si devices, it is important to study the origin and design space of the off-state leakage current [68]. This leakage is dominated by the variable-range hopping through threading dislocations and the device breakdown is typically given by trap-assisted space-charge limited current [68]. In

Fig. 14. Design space of the off-state leakage current of vertical GaN diodes as a function of the total dislocation density level in the structure, and the average electric field in the drift layer ( $E_{AV} = 13 \text{ MV/cm}$ ). The different dislocation density represents vertical GaN diodes fabricated on different substrates. The leakage currents of state-of-the-art GaN lateral diodes with similar Eav and dislocation density are also shown [68].

comparison, vertical GaN-on-GaN pn diodes have similar leakage mechanisms but show avalanche breakdown. In Ref. [68], the MIT group and Synopsys demonstrated a simulation model for the leakage current in vertical GaN power devices, with the simulation model well calibrated by the experimental data of vertical GaN power diodes on Si, sapphire and GaN substrates. From the simulation, they derived the design space of leakage current of vertical GaN power devices (Fig. 14). It can be seen that although the leakage current of GaN-on-Si vertical devices is  $10^2 - 10^3$ -fold higher than that in GaN-on-GaN device, it is much lower than that in lateral AlGaN/GaN diodes, for a similar reverse electric field level. In addition, it was recently reported that vertical GaN-on-Si pn diodes could survive repetitive avalanche tests with surge current and voltages, indicating similar breakdown ruggedness to the avalanche breakdown [72]. These results support the great potential of the cost-effective vertical GaN-on-Si devices for high-voltage applications.

#### 4. Conclusion

In this review, we summarized several key aspects of vertical GaN power electronics including material growth, device architectures, device physics, and processing issues. High-performance vertical GaN transistors and diodes have been demonstrated on free-standing GaN substrate and low-cost silicon wafer. With the advances in substrate technology and the optimization of the field engineering, vertical GaN power devices with breakdown voltage beyond 5 kV can be realized. There are however, very limited reliability studies on vertical devices so far. A careful study of the origin of the breakdown mechanism in these devices is also needed. The maturity of the substrate technology together with the optimization of the device processing will soon enable the commercialization of vertical GaN power devices.

#### Acknowledgements

The authors would like to acknowledge partial funding support from the ONR PECASE and the ARPA-E SWITCHES programs with grant numbers 2(GG008553) and N00014-16-2230, respectively.

#### References

- N. Mohan, T.M. Undeland, Power Electronics: Converters, Applications, and Design, John Wiley & Sons, 2007.

- B. Baliga, Semiconductors for high-voltage, vertical channel field-effect transistors, J. Appl. Phys. 53 (3) (1982) 1759–1764.

#### J. Hu et al.

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

- [3] B.J. Baliga, Power semiconductor device figure of merit for high-frequency applications, IEEE Electron Dev. Lett. 10 (10) (1989) 455–457.

- [4] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, D. Ueda, Gate injection transistor (GIT)A normally-off AlGaN/GaN power transistor using conductivity modulation, IEEE Trans. Electron Dev. 54 (12) (2007) 3393–3399.

- [5] Y. Cai, Y. Zhou, K.J. Chen, K.M. Lau, High-performance enhancement-mode AlGaN/ GaN HEMTs using fluoride-based plasma treatment, IEEE Electron Dev. Lett. 26 (7) (2005) 435–437.

- [6] B. De Jaeger, M. Van Hove, D. Wellekens, X. Kang, H. Liang, G. Mannaert, K. Geens, S. Decoutere, Au-free CMOS-compatible AlGaN/GaN HEMT processing on 200 mm Si substrates, in: Proceedings of the 2012 24th International Symposium on Power Semiconductor Devices and ICs (ISPSD), IEEE, 2012, pp. 49–52.

- [7] S. Lenci, B. De Jaeger, L. Carbonell, J. Hu, G. Mannaert, D. Wellekens, S. You, B. Bakeroot, S. Decoutere, Au-free AlGaN/GaN power diode on 8-in Si substrate with gated edge termination, IEEE Electron Dev. Lett. 34 (8) (2013) 1035–1037.

- [8] J. Hu, S. Stoffels, S. Lenci, B. Bakeroot, B. De Jaeger, M. Van Hove, N. Ronchi, R. Venegas, H. Liang, M. Zhao, et al., Performance optimization of Au-free lateral AlGaN/GaN Schottky barrier diode with gated edge termination on 200-mm silicon substrate, IEEE Trans. Electron Dev. 63 (3) (2016) 997–1004.

- [9] J. Hu, S. Stoffels, S. Lenci, B. De Jaeger, N. Ronchi, A.N. Tallarico, D. Wellekens, S. You, B. Bakeroot, G. Groeseneken, et al., Statistical analysis of the impact of anode recess on the electrical characteristics of AlGaN/GaN Schottky diodes with gated edge termination, IEEE Trans. Electron Dev. 63 (9) (2016) 3451–3458.

- [10] A. Lidow, J. Strydom, M. De Rooij, D. Reusch, GaN Transistors for Efficient Power Conversion, John Wiley & Sons, 2014.

- [11] D. Marcon, Y. Saripalli, S. Decoutere, 200 mm GaN-on-Si epitaxy and e-mode device technology, in: Proceedings of the 2015 IEEE International on Electron Devices Meeting (IEDM), IEEE, 2015, pp. 16–2.

- [12] R. Vetury, N.Q. Zhang, S. Keller, U.K. Mishra, The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs, IEEE Trans. Electron Dev. 48 (3) (2001) 560–566.

- [13] J. Hu, S. Stoffels, S. Lenci, B. Bakeroot, R. Venegas, G. Groeseneken, S. Decoutere, Current transient spectroscopy for trapping analysis on Au-free AlGaN/GaN Schottky barrier diode, Appl. Phys. Lett. 106 (8) (2015) 083502.

- [14] G. Meneghesso, G. Verzellesi, F. Danesin, F. Rampazzo, F. Zanon, A. Tazzoli, M. Meneghini, E. Zanoni, Reliability of GaN high-electron-mobility transistors: state of the art and perspectives. IEEE Trans. Dev. Mater. Reliab. 8 (2) (2008) 332–343.

- [15] J. Hu, S. Stoffels, S. Lenci, G. Groeseneken, S. Decoutere, On the identification of buffer trapping for bias-dependent dynamic RON of AlGaN/GaN Schottky barrier diode with AlGaN: C back barrier, IEEE Electron Dev. Lett. 37 (3) (2016) 310–313.

- [16] Y. Zhang, M. Sun, Z. Liu, D. Piedra, H.-S. Lee, F. Gao, T. Fujishima, T. Palacios, Electrothermal simulation and thermal performance study of GaN vertical and lateral power transistors, IEEE Trans. Electron Dev. 60 (7) (2013) 2224–2230.

- [17] H. Geng, H. Sunakawa, N. Sumi, K. Yamamoto, A.A. Yamaguchi, A. Usui, Growth and strain characterization of high quality GaN crystal by HVPE, J. Cryst. Growth 350 (1) (2012) 44–49.

- [18] Y. Oshima, T. Yoshida, T. Eri, K. Watanabe, M. Shibata, T. Mishima, Freestanding GaN wafers by hydride vapor phase epitaxy using void-assisted separation technology, Technology of Gallium Nitride Crystal Growth, 2010, pp. 79–96.

- [19] Y. Zhang, D. Piedra, M. Sun, J. Hennig, A. Dadgar, L. Yu, T. Palacios, High-performance 500 V quasi-and fully-vertical GaN-on-Si pn diodes, IEEE Electron Dev. Lett. 38 (2) (2017) 248–251.

- [20] K. Motoki, Development of gallium nitride substrates, SEI Tech. Rev. 70 (2010) 28–35.

- [21] K. Motoki, T. Okahisa, R. Hirota, S. Nakahata, K. Uematsu, N. Matsumoto, Dislocation reduction in GaN crystal by advanced-DEEP, J. Cryst. Growth 305 (2) (2007) 377–383.

- [22] T. Paskova, D.A. Hanser, K.R. Evans, GaN substrates for III-nitride devices, Proc. IEEE 98 (7) (2010) 1324–1338.

- [23] H.á. Maruska, J. Tietjen, The preparation and properties of Vapor-Deposited singlecrystal-line GaN, Appl. Phys. Lett. 15 (10) (1969) 327–329.

- [24] K. Motoki, T. Okahisa, N. Matsumoto, M. Matsushima, H. Kimura, H. Kasai, K. Takemoto, K. Uematsu, T. Hirano, M. Nakayama, et al., Preparation of large freestanding GaN substrates by hydride vapor phase epitaxy using GaAs as a starting substrate, Jpn. J. Appl. Phys. 40 (2B) (2001) L140.

- [25] Y. Otoki, T. Tanaka, H. Kamogawa, N. Kaneda, T. Mishima, U. Honda, Y. Tokuda, Impact of crystal-quality improvement of epitaxial wafers on RF and power switching devices by utilizing VAS-method grown GaN substrates with low-density and uniformly distributed dislocations, in: Proceedings of the CS MANTECH Digest, 2013, pp. 109–112.

- [26] I.C. Kizilyalli, A.P. Edwards, O. Aktas, T. Prunty, D. Bour, Vertical power pn diodes based on bulk GaN, IEEE Trans. Electron Dev. 62 (2) (2015) 414–422.

- [27] B.J. Baliga, Fundamentals of Power Semiconductor Devices, Springer Science & Business Media, 2010.

- [28] I. Kizilyalli, T. Prunty, O. Aktas, 4-kV and 2.8-mΩcm<sup>2</sup> vertical GaN pn diodes with low leakage currents, IEEE Electron Dev. Lett. 36 (10) (2015) 1073–1075.

- [29] C. Wetzel, H. Amano, I. Akasaki, J.W. Ager, I. Grzegory, B.K. Meyer, Dx-like behavior of oxygen in gan, Phys. B: Condens. Matter 302 (2001) 23–38.

- [30] A.F. Wright, Substitutional and interstitial oxygen in wurtzite gan, J. Appl. Phys. 98 (10) (2005) 103531.

- [31] G. Parish, S. Keller, S. Denbaars, U. Mishra, Sims investigations into the effect of growth conditions on residual impurity and silicon incorporation in gan and alxga1xn, J. Electron. Mater. 29 (1) (2000) 15–20.

- [32] T. Tanaka, N. Kaneda, T. Mishima, Y. Kihara, T. Aoki, K. Shiojima, Roles of lightly doped carbon in the drift layers of vertical n-GaN Schottky diode structures on

freestanding GaN substrates, Jpn. J. Appl. Phys. 54 (4) (2015) 041002.

- [33] J.D. Greenlee, B.N. Feigelson, T.J. Anderson, J.K. Hite, K.D. Hobart, F.J. Kub, Symmetric multicycle rapid thermal annealing: enhanced activation of implanted dopants in GaN, ECS J. Solid State Sci. Technol. 4 (9) (2015) P382–P386.

- [34] Y. Zhang, Z. Liu, M.J. Tadjer, M. Sun, D. Piedra, C. Hatem, T.J. Anderson, L.E. Luna, A. Nath, A.D. Koehler, et al., Vertical GaN junction barrier schottky rectifiers by selective ion implantation, IEEE Electron Dev. Lett. 38 (8) (2017) 1097–1100.

- [35] Gan Feng, Jun Suda, Tsunenobu Kimoto, Space-modulated junction termination extension for ultrahigh-voltage pin diodes in 4H-SiC, IEEE Trans. Electron Dev. 59 (2) (2012) 414–418.

- [36] A. Mahajan, B. Skromme, Design and optimization of junction termination extension (JTE) for 4H-SiC high voltage Schottky diodes, Solid-State Electron. 49 (6) (2005) 945–955.

- [37] I. Ben-Yaacov, Y.-K. Seck, U.K. Mishra, S.P. DenBaars, AlGaN/GaN current aperture vertical electron transistors with regrown channels, J. Appl. Phys. 95 (4) (2004) 2073–2078.

- [38] S. Chowdhury, B.L. Swenson, U.K. Mishra, Enhancement and depletion mode AlGaN/GaN CAVET with Mg-ion-implanted GaN as current blocking layer, IEEE Electron Dev. Lett. 29 (6) (2008) 543–545.

- [39] B. Feigelson, T. Anderson, M. Abraham, J. Freitas, J. Hite, C. Eddy, F. Kub, Multicycle rapid thermal annealing technique and its application for the electrical activation of Mg implanted in GaN, J. Cryst. Growth 350 (1) (2012) 21–26.

- [40] S. Jain, M. Willander, J. Narayan, R.V. Overstraeten, III-nitrides: growth, characterization, and properties, J. Appl. Phys. 87 (3) (2000) 965–1006.

- [41] M.J. Tadjer, B.N. Feigelson, J.D. Greenlee, J.A. Freitas, T.J. Anderson, J.K. Hite, L. Ruppalt, C.R. Eddy, K.D. Hobart, F.J. Kub, Selective p-type doping of GaN: Si by Mg ion implantation and multicycle rapid thermal annealing, ECS J. Solid State Sci. Technol. 5 (2) (2016) P124–P127.

- [42] T. Anderson, B. Feigelson, F. Kub, M. Tadjer, K. Hobart, M. Mastro, J. Hite, C. Eddy Jr., Activation of Mg implanted in GaN by multicycle rapid thermal annealing, Electron. Lett. 50 (3) (2014) 197–198.

- [43] H. Xing, D.S. Green, H. Yu, T. Mates, P. Kozodoy, S. Keller, S.P. DenBaars, U.K. Mishra, Memory effect and redistribution of Mg into sequentially regrown GaN layer by metalorganic chemical vapor deposition, Jpn. J. Appl. Phys. 42 (1R) (2003) 50.

- [44] S. Chowdhury, M.H. Wong, B.L. Swenson, U.K. Mishra, CAVET on bulk GaN substrates achieved with MBE-regrown AlGaN/GaN layers to suppress dispersion, IEEE Electron Dev. Lett. 33 (1) (2012) 41–43.

- [45] D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, T. Ueda, 1.7 kV/1.0 mΩcm<sup>2</sup> normally-off vertical GaN transistor on GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure, in: Proceedings of the 2016 IEEE International on Electron Devices Meeting (IEDM), IEEE, 2016, pp. 10–1.

- [46] H. Nie, Q. Diduck, B. Alvarez, A.P. Edwards, B.M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, I.C. Kizilyalli, 1.5-kV and 2.2-mΩcm<sup>2</sup> vertical GaN transistors on bulk-GaN substrates, IEEE Electron Dev. Lett. 35 (9) (2014) 939–941.

- [47] M. Sun, Y. Zhang, X. Gao, T. Palacios, High-performance GaN vertical fin power transistors on bulk GaN substrates, IEEE Electron Dev. Lett. 38 (4) (2017) 509–512.

- [48] C. Gupta, C. Lund, S.H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, U.K. Mishra, In situ oxide, gan interlayer-based vertical trench MOSFET (OG-FET) on bulk GaN substrates, IEEE Electron Dev. Lett. 38 (3) (2017) 353–355.

- [49] R. Li, Y. Cao, M. Chen, R. Chu, 600 V/1.7Ω normally-off GaN vertical trench metaloxide-semiconductor field-effect transistor, IEEE Electron Dev. Lett. 37 (11) (2016) 1466–1469.

- [50] K. Matocha, T.P. Chow, R.J. Gutmann, High-voltage normally off GaN MOSFETs on sapphire substrates, IEEE Trans. Electron Dev. 52 (1) (2005) 6–10.

- [51] M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, T. Kachi, GaN-based trench gate metal oxide semiconductor field-effect transistor fabricated with novel wet etching, Appl. Phys. Express 1 (2) (2008) 021104.

- [52] Y. Zhang, M. Sun, Z. Liu, D. Piedra, J. Hu, X. Gao, T. Palacios, Trench formation and corner rounding in vertical GaN power devices, Appl. Phys. Lett. 110 (19) (2017) 193506.

- [53] M. Itoh, T. Kinoshita, C. Koike, M. Takeuchi, K. Kawasaki, Y. Aoyagi, Straight and smooth etching of GaN (1100) plane by combination of reactive ion etching and KOH wet etching techniques, Jpn. J. Appl. Phys. 45 (5R) (2006) 3988.

- [54] T. Oka, Y. Ueno, T. Ina, K. Hasegawa, Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV, Appl. Phys. Express 7 (2) (2014) 021002.

- [55] H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, H. Ohta, Vertical GaN-based trench gate metal oxide semiconductor field-effect transistors on GaN bulk substrates, Appl. Phys. Express 1 (1) (2008) 011105.

- [56] T. Oka, T. Ina, Y. Ueno, J. Nishii, Over 10 a operation with switching characteristics of 1.2 kV-class vertical GaN trench MOSFETs on a bulk GaN substrate, in: Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), IEEE, 2016, pp. 459–462.

- [57] Y. Zhang, M. Sun, H.-Y. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, et al., Origin and control of OFF-state leakage current in GaNon-Si vertical diodes, IEEE Trans. Electron Dev. 62 (7) (2015) 2155–2161.

- [58] M. Ruzzarin, M. Meneghini, D. Bisi, M. Sun, T. Palacios, G. Meneghesso, E. Zanoni, Instability of dynamic-R<sub>ON</sub> and threshold voltage in GaN-on-GaN vertical field-effect transistors, IEEE Trans. Electron Dev. 64 (8) (2017) 3126–3131.

- [59] G.T. Dang, A.P. Zhang, F. Ren, X.A. Cao, S.J. Pearton, H. Cho, J. Han, J.-I. Chyi, C.-M. Lee, C.-C. Chuo, et al., High voltage GaN schottky rectifiers, IEEE Trans. Electron Dev. 47 (4) (2000) 692–696.

- [60] K. Nomoto, Z. Hu, B. Song, M. Zhu, M. Qi, R. Yan, V. Protasenko, E. Imhoff, J. Kuo, N. Kaneda, et al., GaN-on-GaN pn power diodes with 3.48 kV and 0.95 mΩcm<sup>2</sup>: a

#### J. Hu et al.

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

record high figure-of-merit of 12.8 GW/cm2, in: Proceedings of the 2015 IEEE International on Electron Devices Meeting (IEDM), IEEE, 2015, pp. 9–7.

[61] O. Aktas, I. Kizilyalli, Avalanche capability of vertical GaN pn junctions on bulk GaN substrates, IEEE Electron Dev. Lett. 36 (9) (2015) 890–892.

- [62] Y. Saitoh, K. Sumiyoshi, M. Okada, T. Horii, T. Miyazaki, H. Shiomi, M. Ueno, K. Katayama, M. Kiyama, T. Nakamura, Extremely low on-resistance and high breakdown voltage observed in vertical GaN Schottky barrier diodes with highmobility drift layers on low-dislocation-density GaN substrates, Appl. Phys. Express 3 (8) (2010) 081001.

- [63] Y. Zhang, M. Sun, Z. Liu, D. Piedra, M. Pan, X. Gao, Y. Lin, A. Zubair, L. Yu, T. Palacios, Novel GaN trench MIS barrier Schottky rectifiers with implanted field rings, in: Proceedings of the 2016 IEEE International on Electron Devices Meeting (IEDM), IEEE, 2016, pp. 10–2.

- [64] A.D. Koehler, T.J. Anderson, M.J. Tadjer, A. Nath, B.N. Feigelson, D.I. Shahin, K.D. Hobart, F.J. Kub, Vertical GaN junction barrier schottky diodes, ECS J. Solid State Sci. Technol. 6 (1) (2017) Q10–Q12.

- [65] W. Li, K. Nomoto, M. Pilla, M. Pan, X. Gao, D. Jena, H.G. Xing, Design and realization of GaN trench junction-barrier-Schottky-diodes, IEEE Trans. Electron Dev. 64 (4) (2017) 1635–1641.

- [66] T. Hayashida, T. Nanjo, A. Furukawa, M. Yamamuka, Vertical GaN merged PiN Schottky diode with a breakdown voltage of 2 kV, Appl. Phys. Express 10 (6) (2017)

061003.

- [67] Y. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima, T. Palacios, GaN-on-Si vertical Schottky and pn diodes, IEEE Electron Dev. Lett. 35 (6) (2014) 618–620.

- [68] Y. Zhang, H.-Y. Wong, M. Sun, S. Joglekar, L. Yu, N. Braga, R. Mickevicius, T. Palacios, Design space and origin of off-state leakage in GaN vertical power diodes, in: Proceedings of the 2015 IEEE International on Electron Devices Meeting (IEDM), IEEE, 2015, pp. 35–1.

- [69] X. Zou, X. Zhang, X. Lu, C.W. Tang, K.M. Lau, Fully vertical GaN pin diodes using GaN-on-Si epilayers, IEEE Electron Dev. Lett. 37 (5) (2016) 636–639.

- [70] S. Mase, Y. Urayama, T. Hamada, J.J. Freedsman, T. Egawa, Novel fully vertical GaN p-n diode on Si substrate grown by metalorganic chemical vapor deposition, Appl. Phys. Express 9 (11) (2016) 111005.

- [71] X. Zhang, X. Zou, X. Lu, C.W. Tang, K.M. Lau, Fully-and quasi-vertical GaN-on-Si pin diodes: high performance and comprehensive comparison, IEEE Trans. Electron Dev. 64 (3) (2017) 809–815.

- [72] X. Zou, X. Zhang, X. Lu, C.W. Tang, K.M. Lau, Breakdown ruggedness of quasivertical GaN-based pin diodes on Si substrates, IEEE Electron Dev. Lett. 37 (9) (2016) 1158–1161.

- [73] H. Ohta, N. Kaneda, F. Horikiri, Y. Narita, T. Yoshida, T. Mishima, T. Nakamura, Vertical GaN pn junction diodes with high breakdown voltages over 4 kV, IEEE Electron Dev. Lett. 36 (11) (2015) 1180–1182.