# A 12-Bit 500 MHz GaAs MESFET Digital-to-Analog Converter with p+Ohmic Contact Isolation

by Peter R. Nuytkens

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering at the Massachusetts Institute of Technology

May 8, 1992

© Peter R. Nuytkens 1992

The author hereby grants to M.I.T. the permission to reproduce and distribute copies of this thesis in whole or in part.

| Signature of author: |                                                                       |

|----------------------|-----------------------------------------------------------------------|

|                      | Department of Electrical Engineering and Computer Science May 8, 1992 |

| Certified by:        | Associate Professor Jesus A. del Alamo Thesis Supervisor (MATA)       |

| Accepted by:         | Chairman, Department Departmental Graduate Committee                  |

ARCHIVES

MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

**JUL 10** 1992

LIBRARIES

## A 12-Bit 500 MHz GaAs MESFET Digital-to-Analog Converter with p+ Ohmic Contact Isolation

by

Peter R. Nuytkens

May 8, 1992

#### **Abstract**

Digital GaAs MESFET processes have recently achieved both extremely high levels of integration (1.2 million transistors) and sub-100 psec gate delays. However, analog GaAs MESFET circuit performance in these processes has been limited because of the threshold non-uniformity, sidegating/backgating, and frequency-dependent output conductance effects characteristic of MESFET devices. Several GaAs MESFET process improvements have been put forth that mitigate these effects including low temperature MBE-grown insulating buffer layer and oxygen proton implant isolation. While these process techniques do improve device performance, none of these techniques are compatible with a high-density, high-volume, low-cost digital GaAs MESFET process.

In order to achieve this capability, p<sup>+</sup> ohmic bulk biasing with n<sup>+</sup> ohmic guard ring isolation process technology and source-to-bulk bootstrapped cascode circuit design techniques were developed. High-performance analog and mixed-mode circuits were then able to be produced in an existing high-performance digital GaAs MESFET process. The performance-limiting physics of the digital GaAs MESFETs employed in analog circuit topologies were examined, modeled, and confirmed through experiments. A set of process enhancements and circuit techniques were developed to support high-performance analog and mixed-mode GaAs MESFET designs. These techniques were modeled and experimentally confirmed. Finally, a 12-Bit GaAs MESFET digital-to-analog converter based on the developed techniques was designed, fabricated, and tested.

Thesis Supervisor: Jesús A. del Alamo

#### Acknowledgments

The author would like to express special thanks to the following individuals, without whom this work would have been impossible:

Associate Professor Jesús A. del Alamo for his enthusiastic support and constructive comments; Lou Tomasetta, Jim Mikkelson, Tom Dugan and Ray Milano of Vitesse Semiconductor for providing the design challenge and for fabricating the devices; my wife, Margaret, for editing and helping pull it together; my parents for all their guidance, support and emphasis on education; and my parents<sup>2</sup> for their encouragement.

This thesis is dedicated to Margaret who makes it all worthwhile

## **Table of Contents**

| Abstract                                                                         |

|----------------------------------------------------------------------------------|

| Acknowledgments                                                                  |

| List of Figures                                                                  |

| List of Tables                                                                   |

| 1 - Introduction                                                                 |

| 1.1 - Limitations of GaAs MESFET Devices for Analog and Mixed-Mode Circuits . 10 |

| 1.2 - GaAs MESFET Threshold Uniformity                                           |

| 1.3 - GaAs MESFET Isolation                                                      |

| 1.4 - GaAs MESFET Frequency-Dependent Output Conductance 12                      |

| 1.5 - Overview                                                                   |

| 2 - GaAs MESFET Device and Circuit Modeling                                      |

| 2.1 - GaAs MESFET Device Physics                                                 |

| 2.1.1 - Enhancement/Depletion GaAs MESFET Process 18                             |

| 2.2 - Large-Signal and Small-Signal Model                                        |

| 2.2.1 - Threshold Voltage Model                                                  |

| 2.2.2 - Channel Current Model                                                    |

| 2.3 - Frequency-Dependent-Output-Conductance Model                               |

| 2.4 - Device-to-Substrate Model                                                  |

| 3 - Process Enhancements and Design Methodology for Mixed-Mode Circuits 35       |

| 3.1 - GaAs MESFET Process Enhancements                                           |

| 3.1.1 - Buried p- Buffer Layer                                                   |

| 3.1.2 - P+ Ohmic Contact Isolation                                               |

| 3.1.3 - P-well Isolation                                                         |

| 3.1.4 - N+ Ohmic Contact Isolation                                               |

| 3.2 - GaAs MESFET Circuit Design Methodology                                     |

| 3.2.1 - Current Source                                                           |

| 3.2.2 - Bootstrapped Cascode Amplifier                                           |

| 3.2.3 - Current Switch                                                           |

| 3.2.4 - Voltage-Level Shift Buffer                                               |

| 4 - GaAs MESFET Mixed-Mode Process and Design Test Structures                    |

| 4.1 - Diffused Resistors                                                         |

| 4.2 - Single Transistor Devices                                                  |

| 4.3 - Differential Transistor Pairs                                       |  |

|---------------------------------------------------------------------------|--|

| 4.4 - Dual-Gate MESFET                                                    |  |

| 4.5 - High-Impedance Current Source                                       |  |

| 4.6 - Split Current Source Loads                                          |  |

| 4.7 - Unity Gain Buffer                                                   |  |

| 4.8 - Ring Oscillator                                                     |  |

| 5 - 500 MHz 12-bit GaAs MESFETDigital-to-Analog Converter 80              |  |

| 5.1 - Design Goals                                                        |  |

| 5.2 - Architecture Overview                                               |  |

| 5.2.1 - R-2R Topology                                                     |  |

| 5.2.2 - Segmented 2 <sup>N</sup> R Topology                               |  |

| 5.2.3 - Multiple Current Source Array Topology 83                         |  |

| 5.2.4 - Dynamic Element Matching Topology 83                              |  |

| 5.3 - 12-bit Multiplexed Current Digital-Analog Converter Architecture 84 |  |

| 5.4 - Circuits                                                            |  |

| 5.4.1 - Input Receiver                                                    |  |

| 5.4.2 - Multiplexer                                                       |  |

| 5.4.3 - DCFL Pass Transistor Latch                                        |  |

| 5.4.4 - Current Source Array                                              |  |

| 5.4.5 - Operational Amplifier                                             |  |

| 5.4.6 - Voltage Reference                                                 |  |

| 5.5 - Die Layout and Package                                              |  |

| 5.6 - High-Speed Printed Circuit Board                                    |  |

| 5.7 - Performance                                                         |  |

| 5.7.1 - Dynamic Test                                                      |  |

| 5.7.2 - Settling Time                                                     |  |

| 5.7.3 - AC Test                                                           |  |

| 6 - Mixed-Mode Process Circuits Applications                              |  |

| 6.1 - High-Voltage Current Source                                         |  |

| 6.2 - High-Voltage-Swing 10 mV Resolution Comparator 127                  |  |

| 7 - Conclusion                                                            |  |

| Bibliography                                                              |  |

| Biography                                                                 |  |

## List of Figures

| 2.1  | Gateless MESFET                                                                                                                                   | 15 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Biased MESFET                                                                                                                                     | 16 |

| 2.3  | Comparison of MESFET IV hysterisis characteristics                                                                                                | 20 |

| 2.4  | HSPICE models for transient, ac, and ac-noise analysis                                                                                            | 21 |

| 2.5  | Comparison of $I_{DS}$ vs $V_{DS}$ for $V_{GS}$ = 0.1 to 0.6 for a 10 $\mu m$ -wide x 10 $\mu m$ -long enhancement mode MESFET                    | 24 |

| 2.6  | Enhanced HSPICE frequency-dependent-output-conductance MESFET model                                                                               | 27 |

| 2.7  | Transient response of HSPICE model and frequency-dependent-output-conductance-enhanced-HSPICE-MESFET model                                        | 27 |

| 2.8  | Inverter stage with source-to-bulk and drain-to-bulk diodes                                                                                       | 29 |

| 2.9  | Inverter stage with source-to-bulk and drain-to-bulk diodes small-signal equivalent                                                               | 30 |

| 2.10 | HSPICE simulation showing the inverter stage bulk node                                                                                            | 31 |

| 2.11 | Enhanced HSPICE models for transient analysis, ac analysis and ac-noise analysis                                                                  | 33 |

| 3.1  | GaAs MESFET analog and mixed-mode process technology                                                                                              | 38 |

| 3.2  | Self-aligned GaAs MESFET process with p buried implant                                                                                            | 39 |

| 3.3  | Mg acceptor concentration profile $N_A(x)$ and resulting electron concentration profile $n(x)$ for various doses                                  | 41 |

| 3.4  | Views of GaAs MESFET p + ohmic isolation process                                                                                                  | 43 |

| 3.5  | Views of GaAs MESFET p-well isolation process                                                                                                     | 45 |

| 3.6  | Views of GaAs MESFET analog and mixed-mode process technology                                                                                     | 47 |

| 3.7  | Depletion-mode transistor current source I-V characteristics                                                                                      | 49 |

| 3.8  | Cascoded transistor topologies                                                                                                                    | 51 |

| 3.9  | Cascoded transistor small-signal equivalent                                                                                                       | 52 |

| 3.10 | Soure-coupled differential pair biased at Io                                                                                                      | 53 |

| 3.11 | Voltage-level shift buffer schematic and small-signal equivalent                                                                                  | 55 |

| 4.1  | Resistor arrays                                                                                                                                   | 60 |

| 4.2  | Discrete 20 $\mu m \times 1.0 \mu m$ depletion-mode transistor with p <sup>+</sup> ohmic ring isolation                                           | 62 |

| 4.3  | Differential pairs with p+ ohmic ring isolation                                                                                                   | 64 |

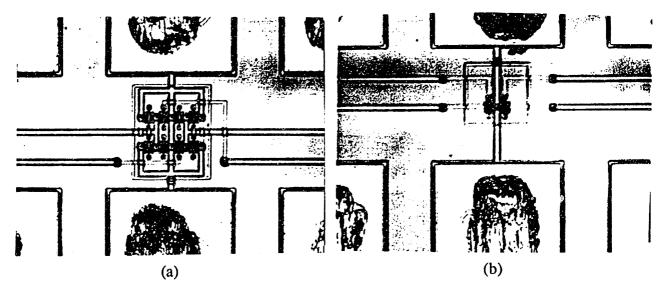

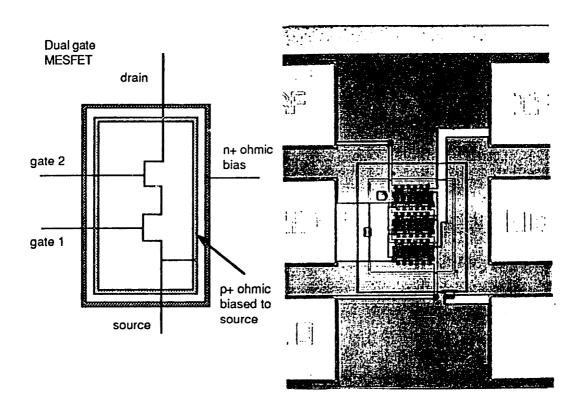

| 4.4  | Dual-gate MESFET with p+ ohmic ring bulk bias and n+ guard ring isolation                                                                         | 65 |

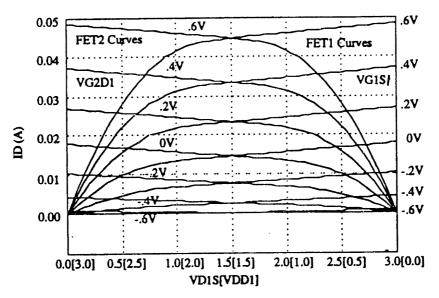

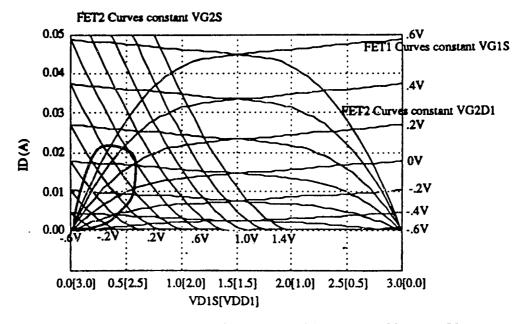

| 4.5  | I-V characteristics of J <sub>1</sub> and J <sub>2</sub>                                                                                          | 66 |

| 4.6  | I-V characteristics of J <sub>1</sub> and J <sub>2</sub> with J <sub>1</sub> V <sub>bulk</sub> =J <sub>2</sub> V <sub>bulk</sub> =V <sub>S1</sub> | 67 |

| 4.7  | Source-degenerated cascode current source schematics                                                                                              | 68 |

| 4.7  | Source-degenerated cascode current source schematics                                            | 68  |

|------|-------------------------------------------------------------------------------------------------|-----|

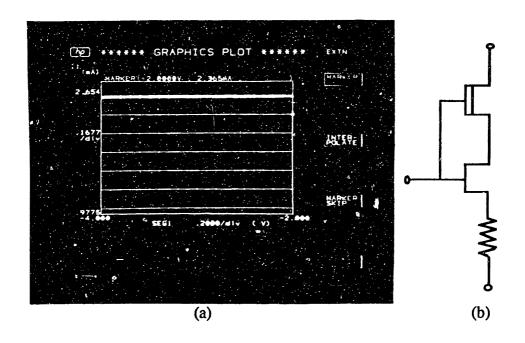

| 4.8  | Source-degenerated cascode current source schematic and dc output impedance                     |     |

|      | 2x10 <sup>6</sup> ohms                                                                          | 70  |

| 4.9  | Split-load test structure composed of three cascoded MESFETs                                    | 71  |

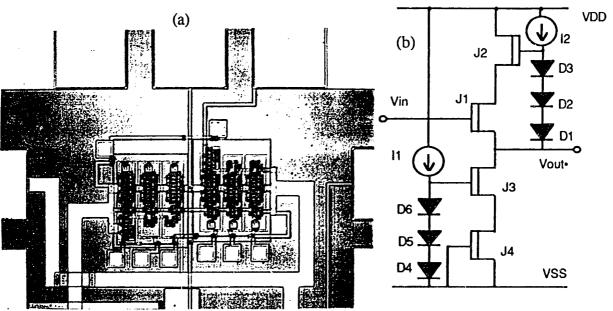

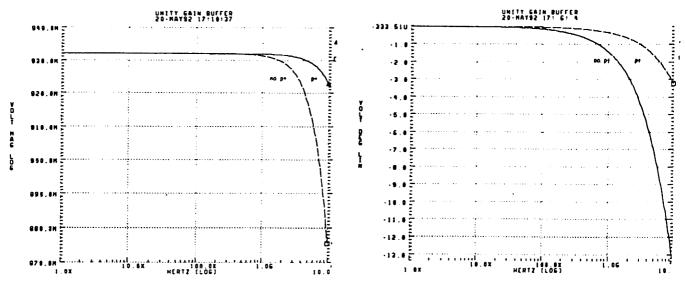

| 4.10 | Bootstrapped unity gain buffer layout and circuit                                               | 72  |

| 4.11 | Bootstrapped unity gain buffer magnitude response and phase response                            | 73  |

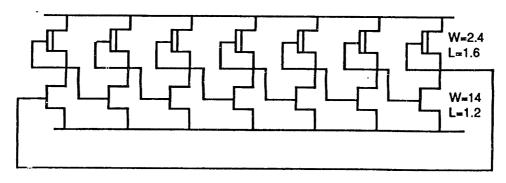

| 4.12 | Ring oscillator                                                                                 | 74  |

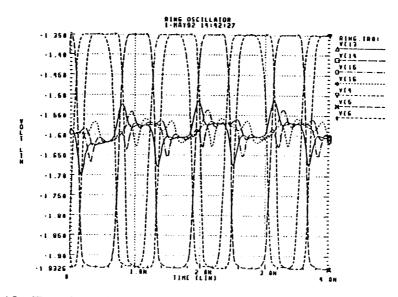

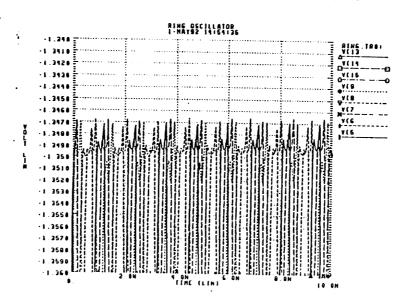

| 4.13 | Transient simulation of two stgages of the ring oscillator                                      | 74  |

| 4.14 | Enlargement of transient simulation                                                             | 74  |

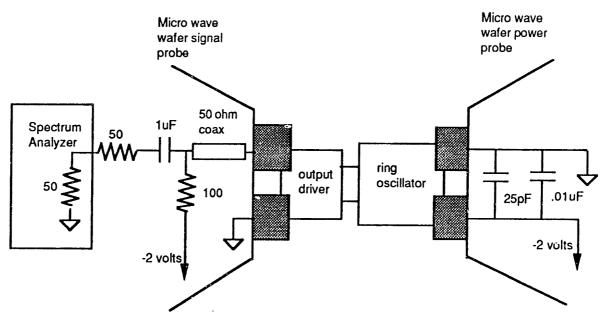

| 4.15 | Ring oscillator ac probe test configuration                                                     | 75  |

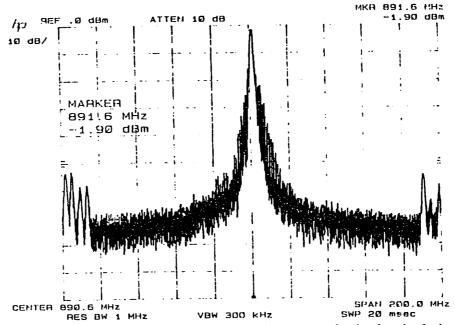

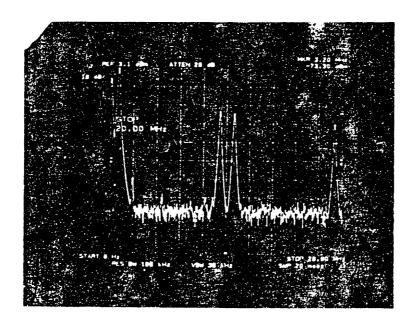

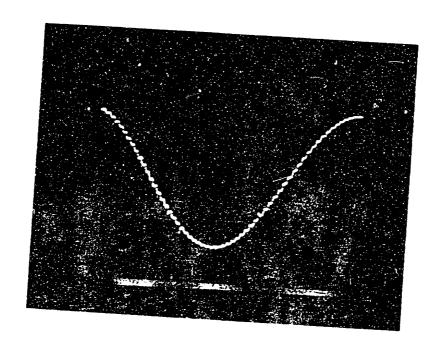

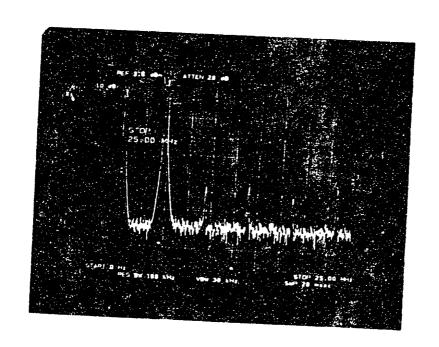

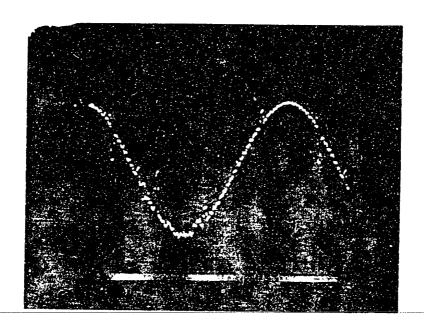

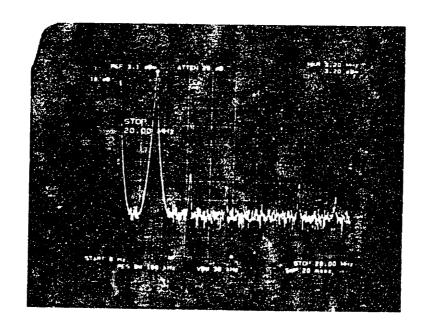

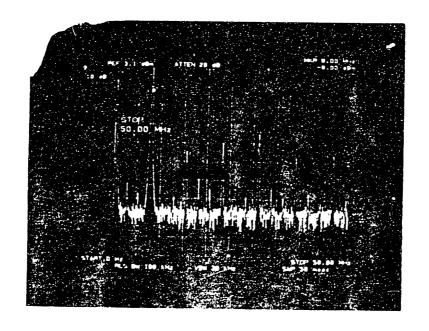

| 4.16 | Ring oscillator ac performance without p+ ohmic ring isolation                                  | 76  |

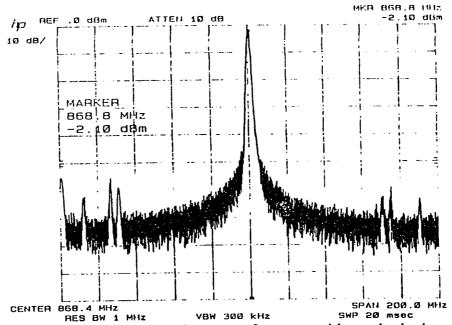

| 4.17 | Ring oscillator ac probe test performance with p+ ohmic ring isolation                          | 76  |

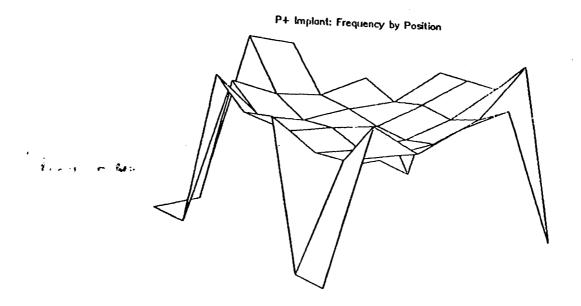

| 4.18 | Ring oscillator frequency as a function of position without p <sup>+</sup> ohmic ring isolation | 77  |

| 4.19 | Ring oscillator frequency as a function of position with p+ ohmic ring isolation                | 78  |

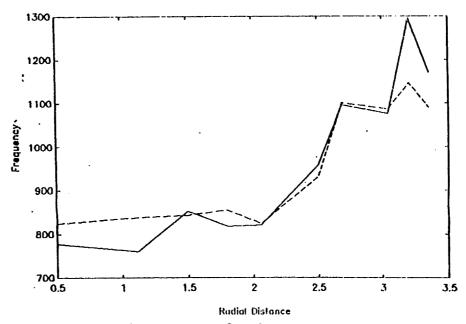

| 4.20 | Ring oscillator frequency as a function of radial distance                                      | 78  |

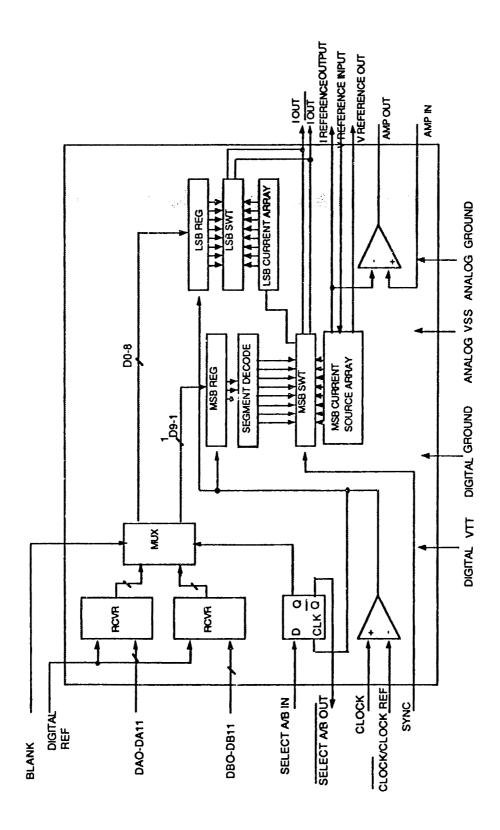

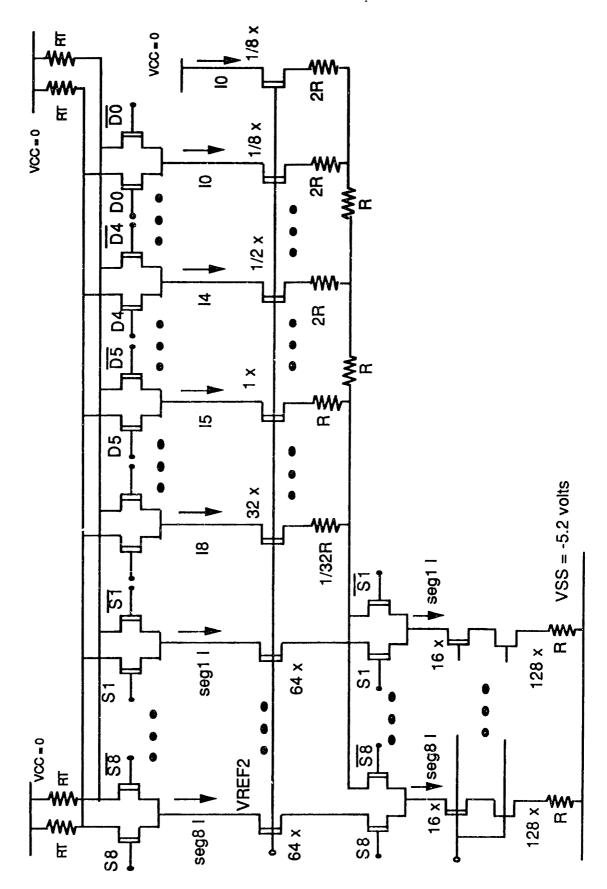

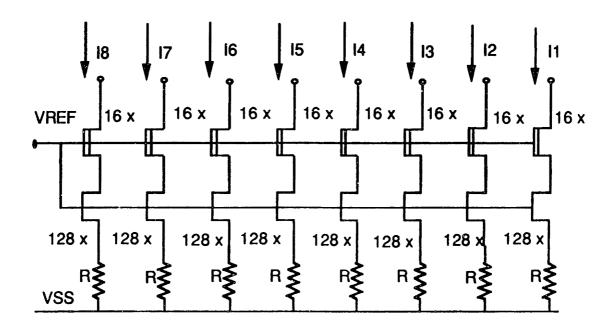

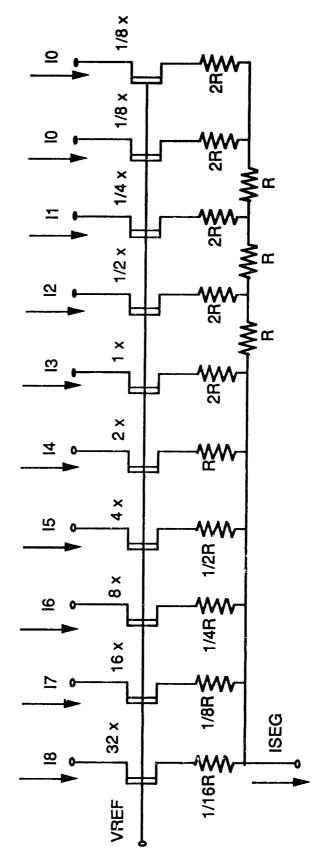

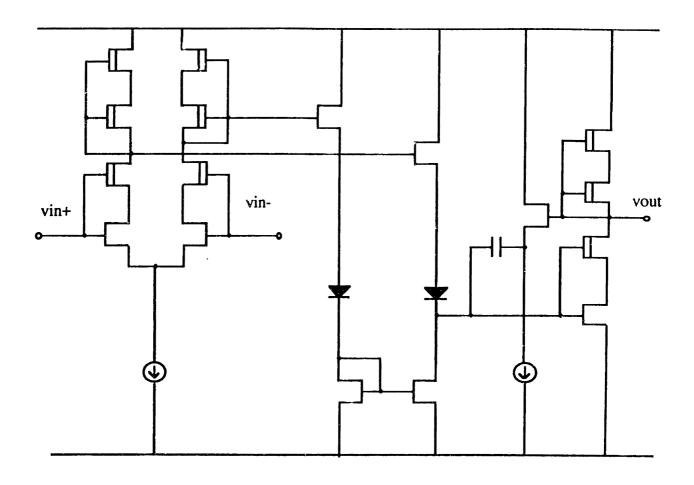

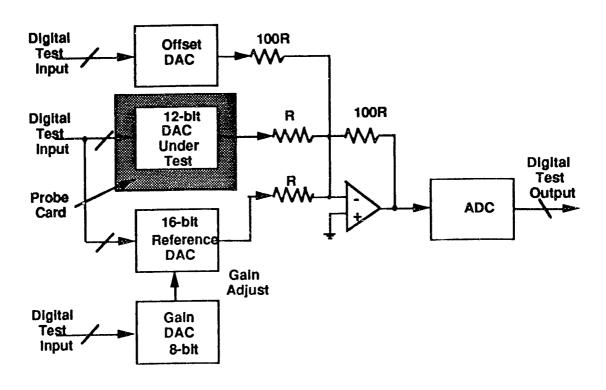

| 5.1  | Digital-to-analog converter functional block diagram                                            | 86  |

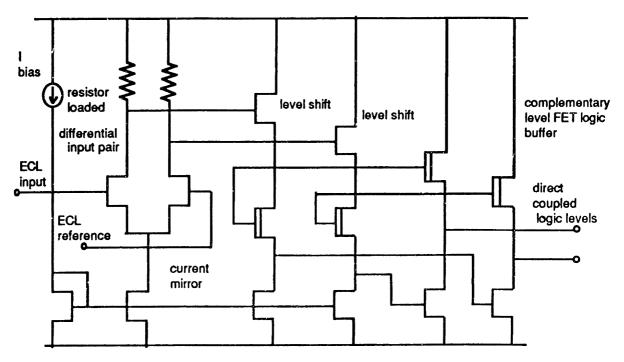

| 5.2  | ECL input receiver                                                                              | 88  |

| 5.3  | MSB and LSB current source array and switches                                                   | 91  |

| 5.4  | MSB current source array                                                                        | 92  |

| 5.5  | LSB current source array                                                                        | 93  |

| 5.6  | Current source reference operational amplifier                                                  | 95  |

| 5.7  | Delta V <sub>T</sub> voltage reference circuit                                                  | 96  |

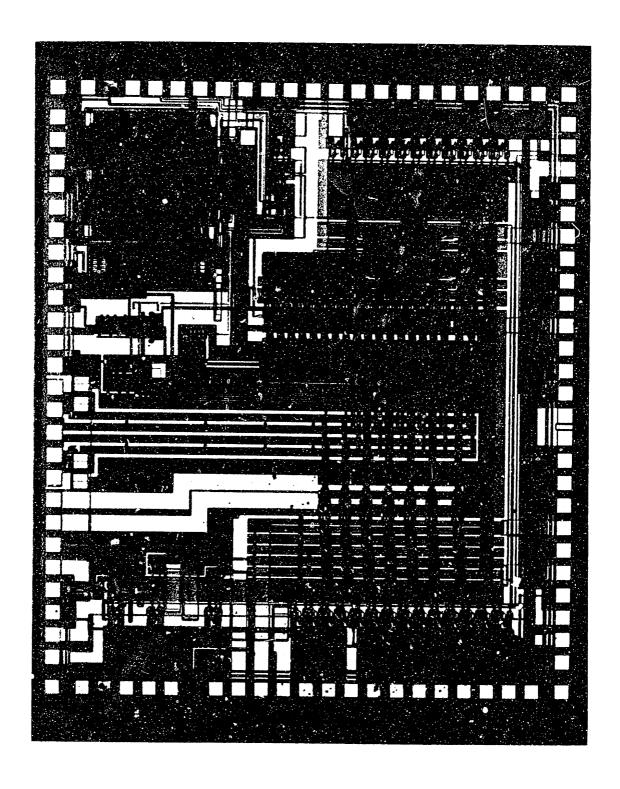

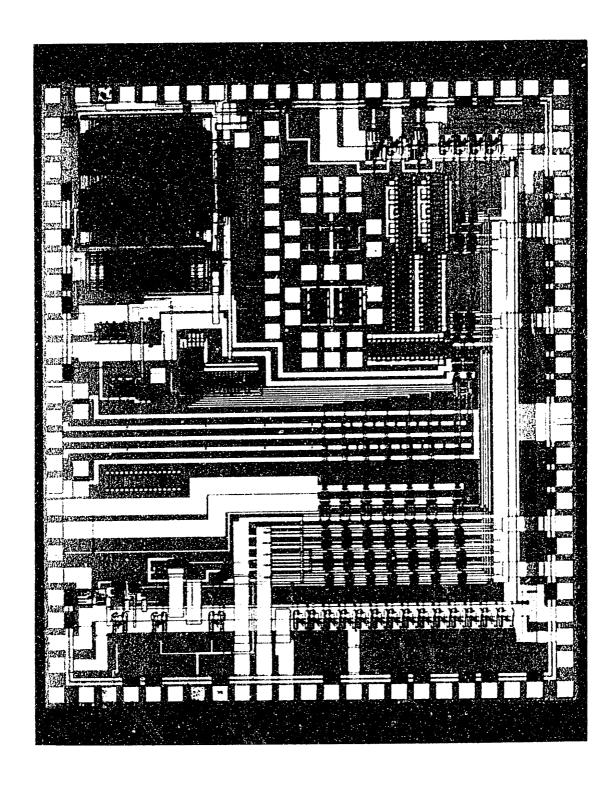

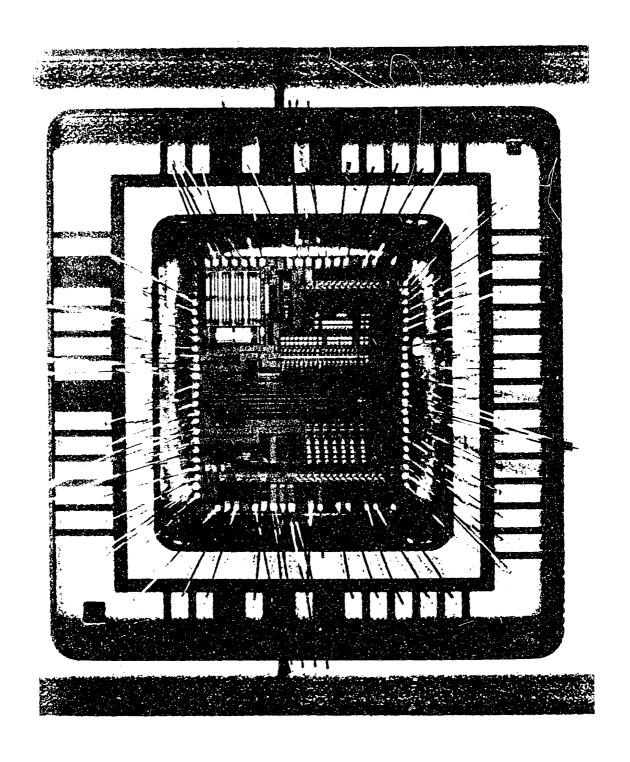

| 5.8  | 12-bit digital-to-analog converter                                                              | 98  |

| 5.9  | 9-bit digital-to-analog converter and test structures                                           | 99  |

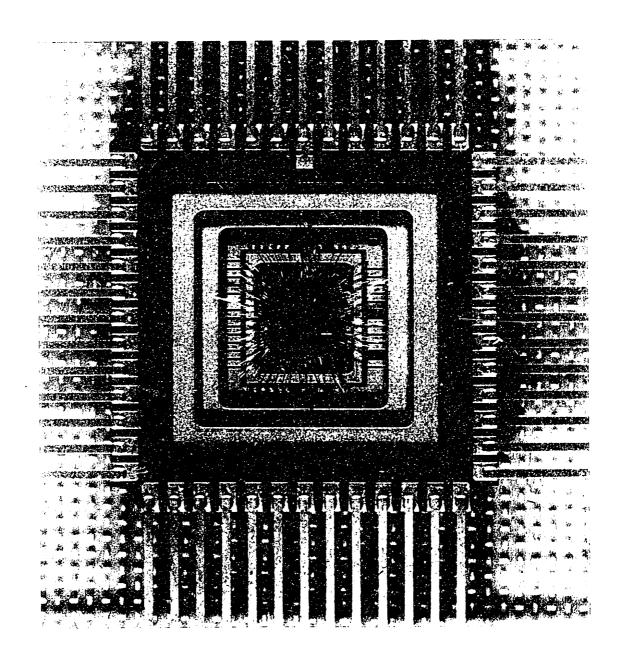

| 5.10 | 12-bit digital-to-analog converter packaged in 52-pin leaded-chip carrier                       | 101 |

| 5.11 | 12-bit digital-to-analog converter packaged in 52-pin leaded chip carrier detail                | 102 |

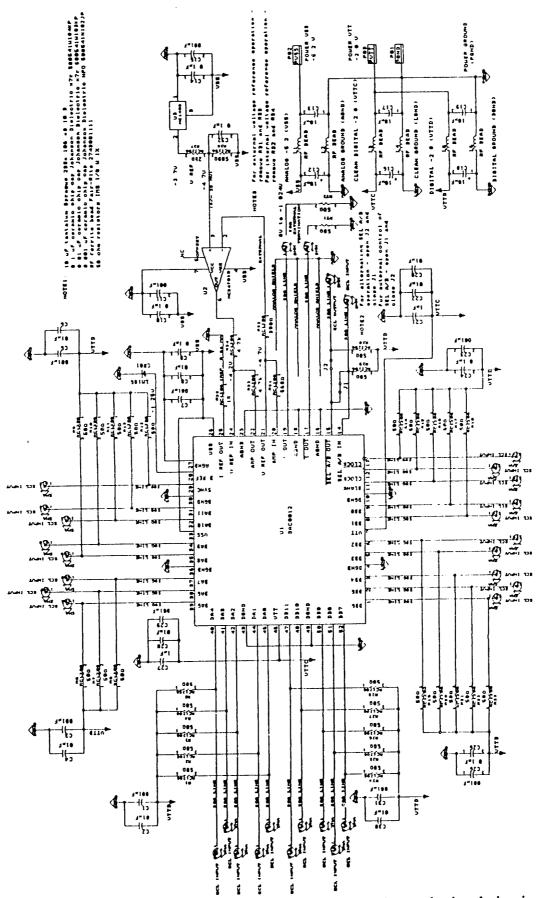

| 5.12 | 12-bit digital-to-analog converter high-speed printed-circuit-board schematic                   | 106 |

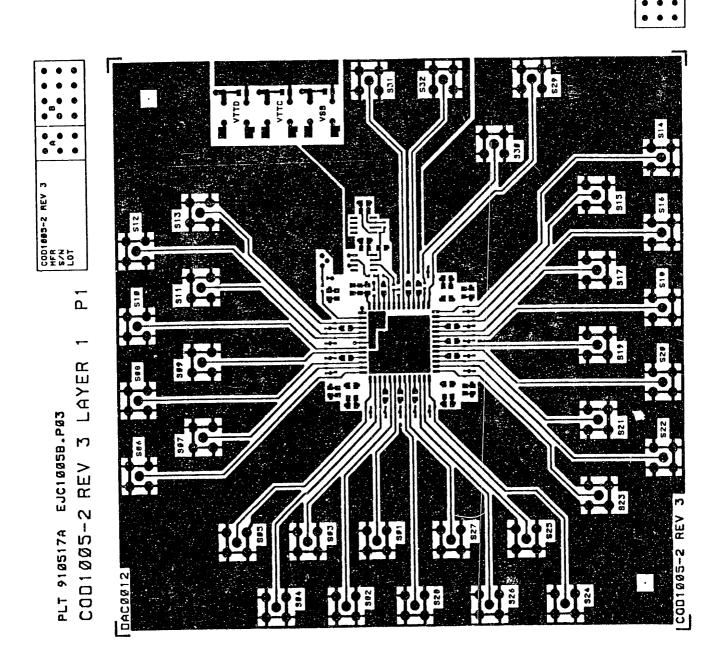

| 5.13 | 12-bit digital-to-analog converter high-speed printed circuit board layer 1                     | 107 |

| 5.14 | Digital-to-analog converter dynamic test                                                        | 108 |

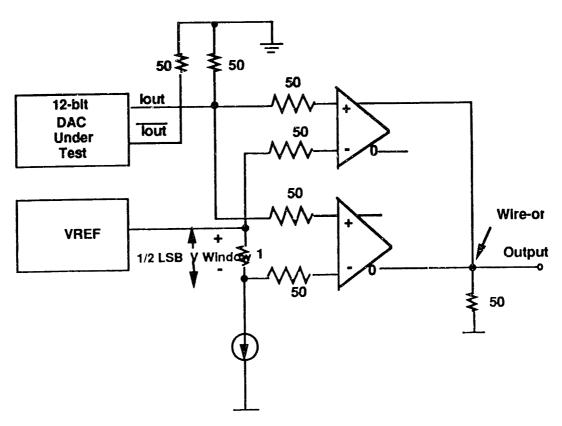

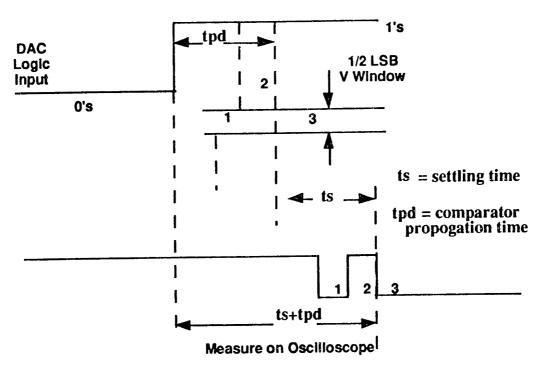

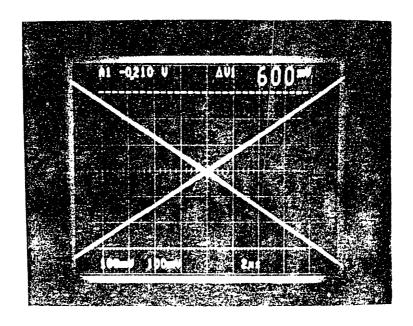

| 5.15 | Digital-to-analog converter settling time test                                                  | 109 |

| 5.16 | Settling time diagram                                                                           | 109 |

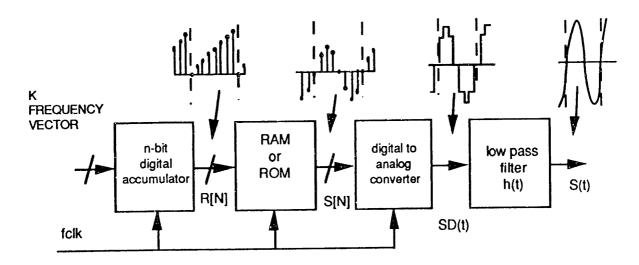

| 5.17 | Functional block diagram of sinewave direct digital frequency synthesizer                       | 111 |

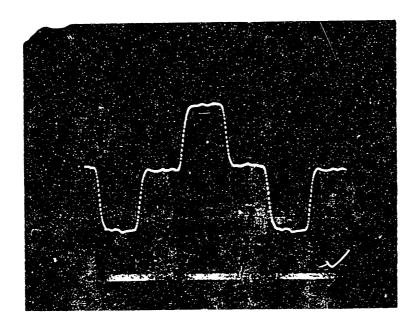

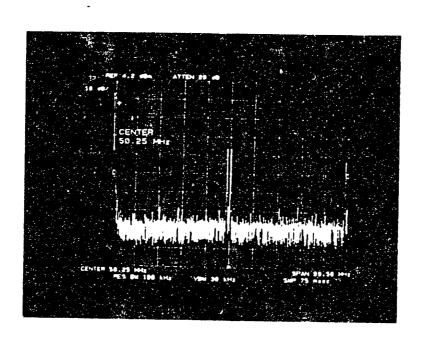

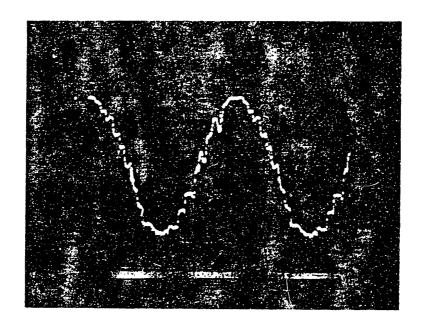

| 5.18 | Clock frequency 300 MHz 4-step sine wave                                                        | 113 |

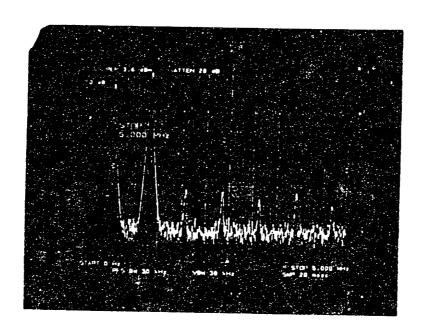

| 5.19 | Clock frequency 100 MHz 2nd harmonic -46 dB                                                     | 113 |

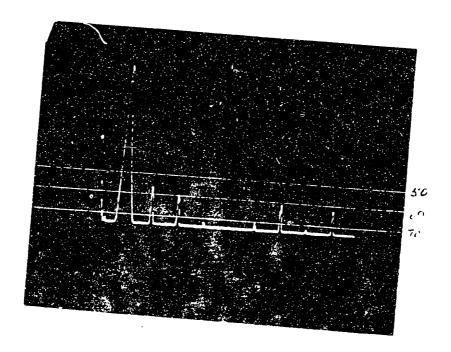

| 5.20 | Clock frequency 100 MHz square wave using only three most significant bits                      | 114 |

| 5.21 | Clock frequency 510 MHz 4-step sine wave                                                                                | 114 |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

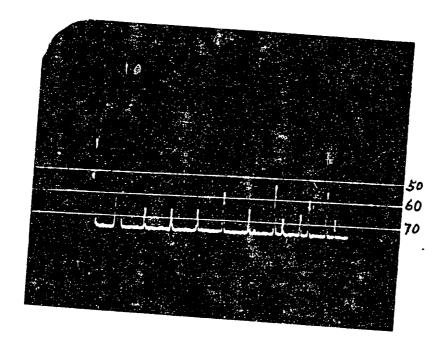

| 5.22 | Clock frequency 50 MHz 64-step sine wave                                                                                | 115 |

| 5.23 | Clock frequency 100 MHz 64-step sine wave                                                                               | 115 |

| 5.24 | Clock frequency 128 kHz 64-step sine wave                                                                               | 116 |

| 5.25 | Clock frequency 80 kHz 16-step sine wave                                                                                | 116 |

| 5.26 | Clock frequency 10 MHz 16-step sine wave                                                                                | 117 |

| 5.27 | Clock frequency 625 kHz 6th harmonic -51 dB                                                                             | 117 |

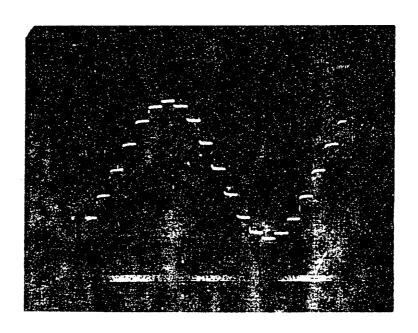

| 5.28 | Clock frequency 300 MHz 64-step sine wave                                                                               | 118 |

| 5.29 | Clock frequency 4.68 MHz, 2nd harmonic -56 dB                                                                           | 118 |

| 5.30 | Clock frequency 400 MHz 64-step sine wave                                                                               | 119 |

| 5.31 | Clock frequency 200 MHz 64-step sine wave                                                                               | 119 |

| 5.32 | Clock frequency 500 MHz 64-step sine wave                                                                               | 120 |

| 5.33 | Clock frequency 600 MHz 64-step sine wave                                                                               | 120 |

| 5.34 | Clock frequency 120 MHz 4096-step triangle wave                                                                         | 121 |

| 5.35 | Clock frequency 120 MHz 4096-step triange wave with 60 MHz alternating blanks                                           | 121 |

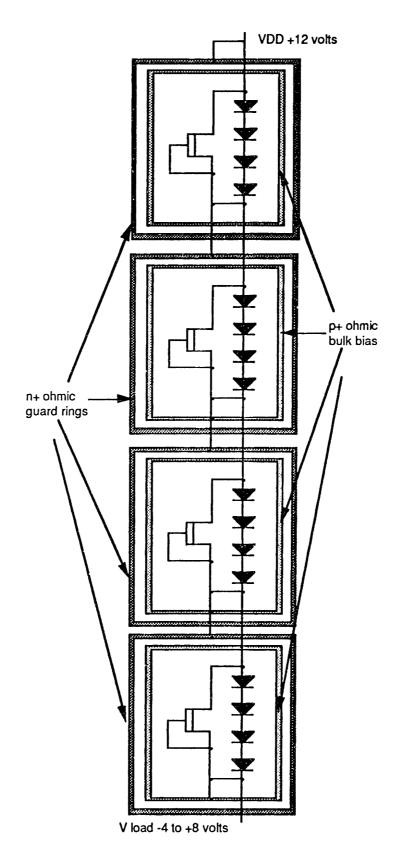

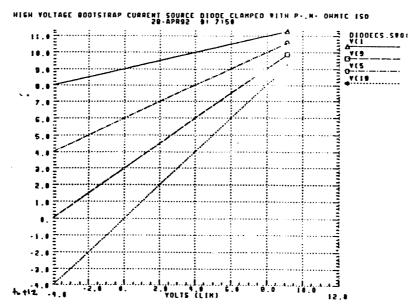

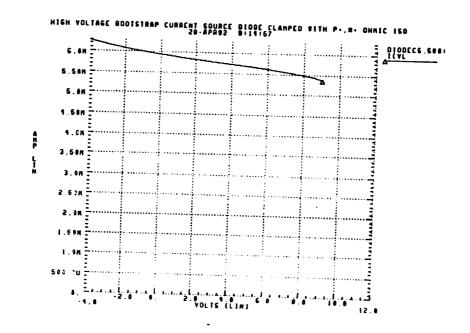

| 6.1  | High voltage current source schematic composed of a series of isolated current sources                                  | 124 |

| 6.2  | Voltage drops across each of the stacked current sources as the load voltage is swept from -4 to +8 volts               | 125 |

| 6.3  | Current output of the stacked current sources as the load voltage is swept from 4 to +8 volts                           | 125 |

| 6.4  | Voltage drops across each of the 5% mismatches stacked current sources as the load voltage is swept from -4 to +8 volts | 126 |

| 6.5  | Current output of the 5% mismatched stacked current sources as the load voltage is swept from -4 to +8 volts            | 127 |

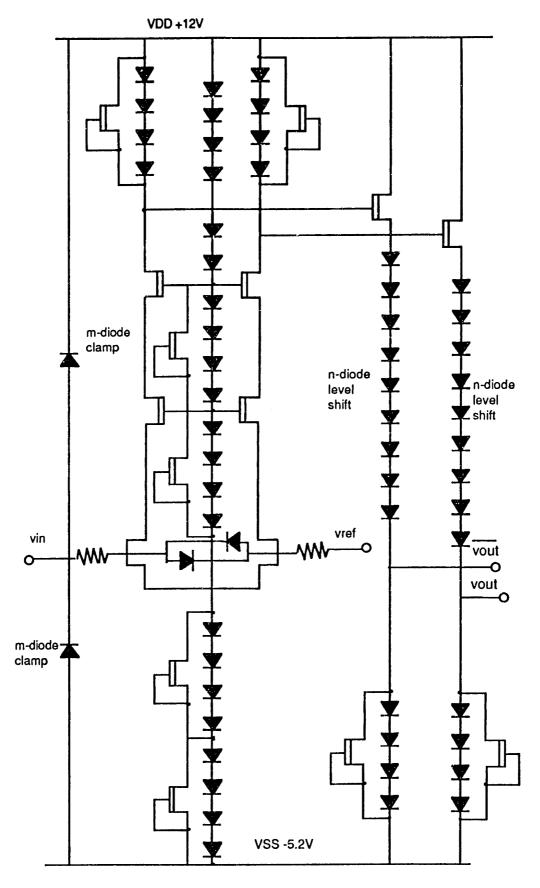

| 6.6  | Comparator topology                                                                                                     | 129 |

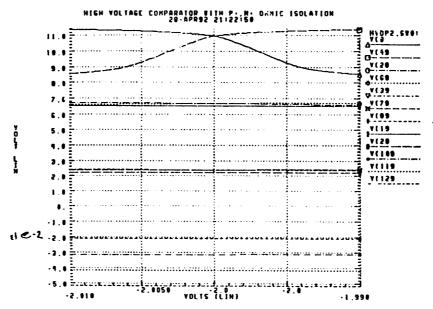

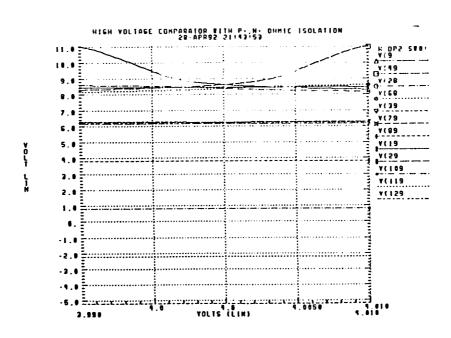

| 6.7  | Comparator output and internal node voltages for reference voltage of -2 volts                                          | 130 |

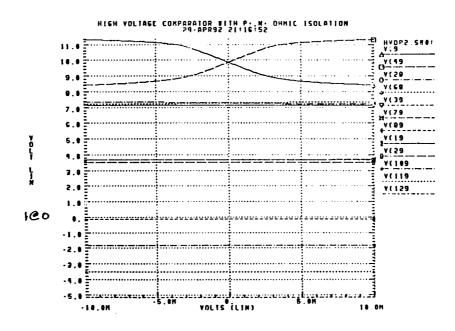

| 6.8  | Comparator output and internal node voltages for reference voltage of -0 volts                                          | 130 |

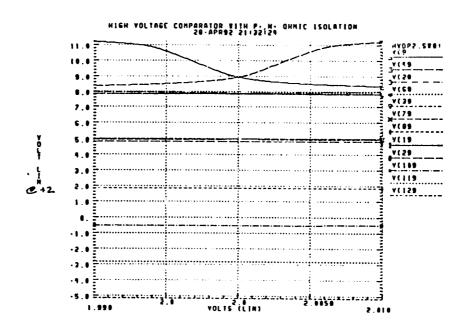

| 6.9  | Comparator output and internal node voltages for reference voltage of +2 volts                                          | 131 |

| 6.10 | Comparator output and internal node voltages for reference voltage of +4 volts                                          | 131 |

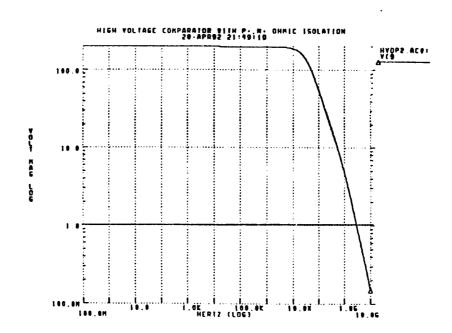

| 6.11 | Comparator small signal magnitude response showing a 2 GHz bandwidth                                                    | 132 |

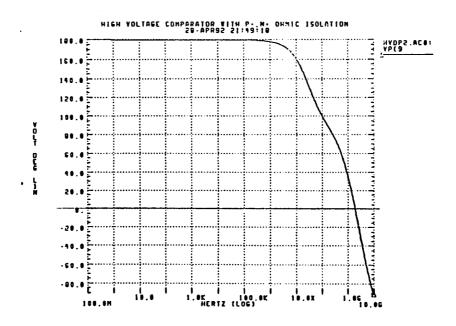

| 6.12 | Comparator small-signal phase response                                                                                  | 132 |

## List of Tables

| 2.1 | Large- and Small-Signal GaAs MESFET HSPICE Model Parameters                             | 34  |

|-----|-----------------------------------------------------------------------------------------|-----|

| 4.1 | Diffused Resistor Characteristics                                                       | 59  |

| 4.2 | Single Transistor Threshold Measurement Statistics on 35 Reticles                       | 63  |

| 4.3 | Single Transistor Threshold Measurement Statistics on 35 Reticles with Outliers Removed | 63  |

| 4.4 | Differential Transistor Threshold Measurement Statistics on 35 Reticles                 | 64  |

| 4.5 | Source-Degenerated Cascode Current Source Measurement Statistics                        | 69  |

| 5.1 | Design Goals for the Digital-to-Analog Converter                                        | 81  |

| 5.2 | Digital-to-Analog Converter Pin Assignments                                             | 103 |

| 5.3 | 12-bit Digital-to-Analog Converter Best Performance                                     | 121 |

#### Chapter 1

#### Introduction

## 1.1 Limitations of GaAs MESFET Devices for Analog and Mixed-Mode Circuits

The high-electron-mobility material properties of gallium arsenide (GaAs) based devices have enabled high-speed, low-power, and high-density digital circuits to be realized. Mobility of electrons in undoped GaAs is a factor of five higher than silicon (Si) -- 8000 cm²/volt-sec compared to 1500 cm²/volt-sec at room temperature. This high-electron-mobility property leads to a speed-power product for GaAs digital integrated circuits that are fabricated with metal-semiconductor-field-effect-transistor (MESFET) devices that are a factor of four higher than the most advanced silicon bipolar or metal-oxide-semiconductor-field-effect-transistor (MOSFET) process. However, the hole mobility of GaAs is slower than Si: 300 cm²/volt-sec compared to 450 cm²/volt-sec, which constrains high-speed circuit designs to use only n-channel FETs. Digital GaAs MESFET circuits are therefore built in an n-channel MOS (NMOS)-like circuit design methodology known as direct-coupled-FET-logic (DCFL). Using DCFL design methodologies, circuit designers have achieved VLSI circuit densities.

The high-speed, low-power, and high-density properties demonstrated by GaAs digital designs are process-technology prerequisites for high-speed analog and mixed-mode circuits, including analog-to-digital conversion and signal processing topologies. In addition to these properties, analog circuit designs require device isolation, threshold uniformity, flat transconductance and output conductance. Unfortunately, GaAs MESFET

devices suffer from local ( $100 \times 100 \,\mu\text{m}$ ) and global (across wafer) threshold non-uniformity, backgating/sidegating effects, and frequency-dependent output conductance. In order to realize high-performance-analog and mixed-mode GaAs MESFET circuits, process enhancements and circuit design methodologies that eliminate these problems must be developed.

#### 1.2 GaAs MESFET Threshold Uniformity

A GaAs-MESFET structure with improved threshold uniformity was achieved by adding a beryllium (Be)-implanted p<sup>-</sup> layer buried under the n-channel.<sup>1</sup> The n-channel/p<sup>-</sup> layer junction formed in this structure provides a controllable interface of uniform thickness and, therefore, uniform threshold control, in contrast to the conventional n-channel/ intrinsic GaAs junction, which forms a fluctuating tail region that results in large threshold fluctuation. However, the increase in control and uniformity of the channel achieved with a buried p<sup>-</sup> implant, through the increase in substrate conductivity, adversely increases both the backgate/sidegate and device crosstalk sensitivity.

#### 1.3 GaAs MESFET Isolation

The use of a low-temperature-molecular-beam-epitaxy (MBE)-grown insulating buffer layer<sup>2</sup> is effective as an isolation technique, but current MBE costs are too high for volume production. An oxygen-proton-implant-isolation process is also effective at isolating devices, but it corrupts threshold uniformity.<sup>3</sup> After channel formation, any subsequent process step that damages the channel/substrate interface will adversely affect threshold uniformity. This, therefore, eliminates the use of an oxygen-proton-implant isolation process step. Finally, biasing a buried p<sup>-</sup> implant layer to the lowest potential will reduce the cross talk between devices that are spaced far enough apart so that the resistance

<sup>&</sup>lt;sup>1</sup> Y. Umemoto et al., "GaAs MESFETs with a Buried p-Layer for Large Scale Integration," *IEEE GaAs IC Symposium Technical Digest*, 1982.

<sup>&</sup>lt;sup>2</sup> F. W. Smith et al., "Sidegating Reduction for GaAs Integrated Circuits by Using a New buffer Layer," *IEDM*, 1988, p. 838.

<sup>&</sup>lt;sup>3</sup> W. M. Paulson et al., "The Effects of Implanted Oxygen on the Backgating Characteristics of GaAs ICs," *IEEE GaAs IC Symposium Technical Digest*, 1987.

connecting the backgates is much greater than the resistance from device to device.

However, for any reasonable p<sup>-</sup> implant dopant concentration, diffusion depth, and wafer thickness, the required spacing between devices becomes incompatible with a tightly packed transistor layout design.

#### 1.4 GaAs MESFET Frequency-Dependent Output Conductance

The small signal output conductance,  $g_0$ , of a GaAs MESFET depends on both frequency and temperature. Typically, an increase of 5 times in output conductance is found between 10 Hz and 100 kHz depending on temperature and other process parameters. This phenomenon has been attributed to the emission time constant of electrically active defects in the semi-insulating substrate near the channel/substrate interface.<sup>4</sup> The variable output conductance produces a step response behavior that contains two exponential terms: a fast exponential (order of  $\tau$ =1e-11s) followed by a much slower exponential (order of  $\tau$ =1e-6s), resulting in undesirably long settling-time characteristics similar to that of a lag-compensated linear network.<sup>5</sup>

#### 1.5 Overview

Each of the above performance limitations of GaAs MESFET process technology for developing mixed-mode circuits was considered in detail leading to the synthesis of a GaAs-MESFET-analog and mixed-mode process technology that incorporates p<sup>+</sup> ohmic bulk biasing with n<sup>+</sup> ohmic guard ring isolation and a design methodology that incorporates source-to-bulk bootstrapped cascode topology, which combined reduces or eliminates each of these effects. GaAs MESFET device physics were analyzed to develop relationships between frequency-dependent output conductance, backgating, crosstalk isolation, device hysteresis, duty-cycle modulation and circuit performance. A large-signal and small-signal device model was developed that accurately represents frequency-dependent output

<sup>&</sup>lt;sup>4</sup> E. P. Finchem, "Reduction of the Backgating Effect in GaAs MESFETs by Charge Confinement at the Backgate Electrode," *IEEE GaAs IC Symposium Technical Digest*, 1988.

<sup>&</sup>lt;sup>5</sup> P. Nuytkens laboratory experiments, 1985.

conductance, substrate backgating, and device crosstalk. HSPICE, with the incorporation of this large-signal and small-signal device model, was then used to model the performance of this mixed-mode process enhancement and design methodology. Test structures were designed and fabricated to verify both the GaAs-MESFET process enhancements and design methodology and the analytical, large-signal, and small-signal device model. Finally, a 12-bit digital-to-analog converter based on the process enhancements, design methodology, and device models was designed, fabricated, and tested.

#### Chapter 2

#### GaAs MESFET Device and Circuit Modeling

#### 2.1 GaAs MESFET Device Physics

The GaAs MESFET was first demonstrated in 1967 by Hooper and Lehrer<sup>1</sup> after being proposed by Mead in 1966.<sup>2</sup> The operation of the MESFET can easily be understood by examining the underlying physics of the depletion-mode device with subsequent modification of the doping levels to attain an enhancement-mode device.

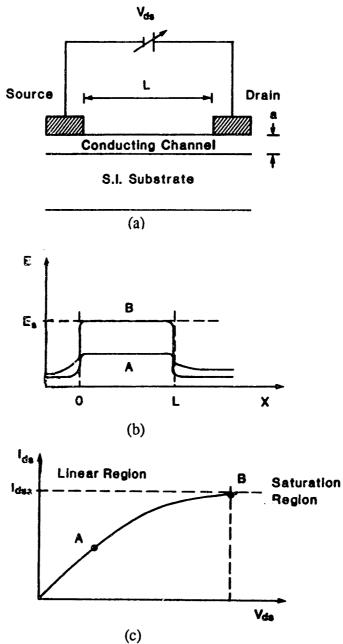

Consider the gateless depletion-mode device in Figure 2.1. The conducting channel allows current to flow as the drain-source bias potential is increased. The I-V relationship is linear for low bias potential directly following the velocity-field characteristics, which become quadratic as the saturation condition is approached. The electric field is uniform along the conducting channel. If the gate electrode is now connected to the source electrode as in Figure 2.2, a depletion region is formed under the gate metal that nearly pinches the channel at the source side of the gate electrode. If a further reverse bias is applied, the channel resistance increases until the device turns completely off. For modern processes, the conducting channel has sub-micron nominal printed gate lengths, and the depletion region that forms under the Schottky contact efficiently controls the flow of current in the

<sup>&</sup>lt;sup>1</sup> W. Hooper et al., "An Epitaxial GaAs Field-Effect Transistor," *Proc. IEEE*, Vol. 55, 1967.

<sup>&</sup>lt;sup>2</sup> C. Mead, "Schottky Barrier Gate Field-Effect Transistor," *Proc. IEEE*, Vol. 54, 1966.

thin channel layer. The device, therefore, behaves as a voltage-controlled switch that can be modulated at high rates. A complete description of MESFET physics is given by Sze.<sup>3</sup>

Figure 2.1 - (a) cross-sectional view of a gateless FET; (b) internal electric field for the structure biased in the linear and saturation regions; (c) the IV characteristic for the device.<sup>4</sup>

<sup>&</sup>lt;sup>3</sup> S. Sze, *Physics of Semiconductor Device*, 2nd ed., Wiley & Sons, NY, 1981.

<sup>&</sup>lt;sup>4</sup> I. Bahl et al., Microwave Solid State Circuit Design, John Wiley & Sons, NY, 1987.

Figure 2.2 - (a) cross-sectional view of biased FET; (b) internal electric field for the structure biased in the linear and saturation regions; (c) the IV characteristic for the device.<sup>5</sup>

For an ideal MESFET operating in the linear region, the drain current  $I_{DS}$  is given by Equation 2.1, and in the saturation region  $I_{DS}$  is given by Equation 2.3:

MESFET linear operation region:  $V_{DS} < V_{DSAT}$ ,  $V_{GS} > V_{T}$ ;

<sup>&</sup>lt;sup>5</sup> I. Bahl et al, Microwave Solid State Circuit Design, John Wiley & Sons, NY, 1987.

$I_{DS} = (W/L)q\mu N_dt\{V_{DS} - 2/3 \cdot V_P^{-1/2} \cdot [(V_{DS} + V_{BI} - V_{GS})^{3/2} - (V_{BI} - V_{GS})^{3/2}]\}$  2.1 where L is the gate length, W is the gate width, t is the channel thickness,  $V_{BI}$  is the built in junction potential,  $V_{GS}$  is the gate to source voltage,  $V_{DS}$  is the drain to source voltage,  $V_T$  is the threshold voltage  $(V_{BI} - V_P)$ . The pinch-off voltage,  $V_P$ , follows from Poisson's Equation and is given by:

$$V_{P} = qN_{d}t^{2}/2\varepsilon_{s}$$

2.2

where q is the charge on an electron, ND is the doping concentration, t is the channel thickness,  $\varepsilon_s$  is the permeability of GaAs.

MESFET saturation operation region: V<sub>DS</sub>> V<sub>DSAT=</sub>V<sub>GS</sub> - V<sub>T</sub>;

$$I_{DS} = (W/L)q\mu N_{dt} \{ V_{P}/3 - (V_{BI} - V_{GS}) + 2/3 \cdot (V_{BI} - V_{GS})^{3/2} / V_{P}^{1/2} \}$$

2.3

For circuit design, two useful MESFET expressions are the small-signal-equivalent transconductance,  $g_m$ , and output conductance,  $g_o$ . For the ideal MESFET expression of Equation 2.1, the partial derivative,  $\partial I_{DS}/\partial V_{GS}$ , leads to the saturation transconductance given by:

$$g_{\rm m} = \partial I_{\rm DS}/\partial V_{\rm GS} = (W/L)q\mu N_{\rm d}t \{1-(V_{\rm GS} + V_{\rm BI})^{1/2}/V_{\rm P}\}$$

2.4

The saturation-output conductance,  $g_0$ , is proportional to the channel-length modulation,  $\lambda$ , and the bias current,  $I_{DS}$ , is given by:

$$g_0 = \partial I_{DS}/\partial V_{DS} = 1/\lambda I_{DS}$$

2.5

These approximations are only valid for computing the static (dc) behavior of a GaAs MESFET where it is assumed that the channel is controlled primarily by the depletion region under the gate electrode. In fact, even the dc operation is a strong function of the potential of the bulk electrode, which acts as a backside channel gate, hence the name backgate. Equations 2.1 and 2.3 can be modified to accurately model the dc-static-backgate effect through a simple linear threshold adjustment given by Equation 2.6, where V<sub>BS</sub> is the bulk-to-source potential, and k is the backgate transconductance parameter: <sup>6</sup>

<sup>&</sup>lt;sup>6</sup> N. Scheinberg, "A Low Frequency GaAs MESFET Circuit Model," *IEEE Journal of Solid State Circuits*, Vol. 23, No. 2, April 1988.

$V_{T} = V_{To} - kV_{BS}$  2.6

where V<sub>To</sub> is V<sub>T</sub> at zero V<sub>BS</sub>. However, for accurate modeling of transients and spurious response of circuits, it is necessary to develop a model that incorporates the physical dynamics of the bulk potential. Dynamic substrate modeling enhancements of the intrinsic HSPICE model are described in sections 2.3 and 2.4.

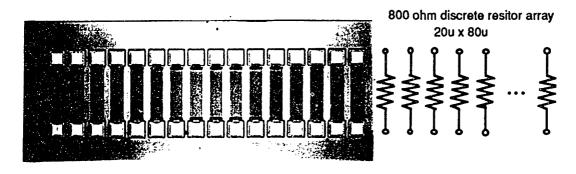

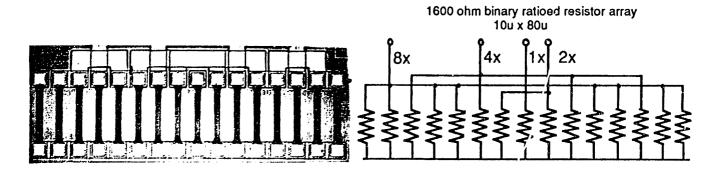

#### 2.1.1 Enhancement/Depletion GaAs MESFET Process

The Vitesse enhancement/depletion mode MESFET foundry process selected for this research is tailored for the fabrication of high-performance GaAs VLSI digital circuits. To achieve these characteristics, high-performance, self-aligned MESFETs are used with multiple levels of interconnect. Two active devices exist in the process: an enhancement-mode MESFET and a depletion-mode MESFET. Schottky-barrier diodes are built from either depletion mode or enhancement mode MESFETs and can be used as references and level-shifting in current-mode-logic (CML) buffer topologies. Two passive devices exist in the process: an n+ diffused resistor and a metal-insulator-metal capacitor. The nominal sheet resistance is 200 ohms per square. Implant resistors of this type have been constructed and show performance of relative matching of less than 0.5 percent.<sup>7</sup>

The choice of the mean value of the enhancement-mode threshold ( $V_{TE}$ ) and depletion-mode threshold ( $V_{TD}$ ) in the Vitesse process is optimized for the direct-coupled-FET-logic (DCFL) family. The thresholds are centered at values that give the lowest propagation delay and power. Nominal VTE is 250 mV for an enhancement-mode device, and nominal VTD is -800 mV for the depletion-mode device. The amount of variation in the threshold voltage,  $\sigma V_T$ , determines the relative size of the gate widths of the transistors and switching speed of the logic.

In addition to the n-channel MESFET devices, a p+ ohmic contact process has been developed that allows localized biasing of the substrate. The ability to bias the substrate

<sup>&</sup>lt;sup>7</sup> P. Nuytkens, laboratory data, 1989.

<sup>&</sup>lt;sup>8</sup> Vitesse Foundry Design Manual, Verison 4.0, 1991.

provides control of the backgate potential and, therefore, the threshold as well as transconductance of the device. Since GaAs is a semi-insulating material, two circuits located within distances of 100 µm from each other typically "talk" to each other through the substrate. By using the p<sup>+</sup> ohmic contact, a designer can isolate various circuit topologies from one another. Chapter 3 develops the p<sup>+</sup> ohmic process technology, while Chapter 4 shows test circuit performance of the process that demonstrates a reduction of gate crosstalk between two adjacent circuits by more than 30 dB. Finally, Chapter 5 describes performance of p<sup>+</sup> ohmic-ring-isolated current sources of the digital-to-analog converter design. Here, the p<sup>+</sup> ohmic-ring-biased current sources show increased isolation from substrate transients generated by the current switches and input receivers and also show improved relative matching.

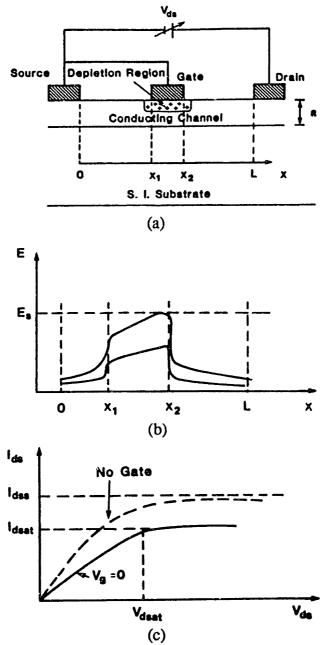

In addition to improving isolation, use of the p<sup>+</sup> ohmic contact reduces device hysteresis. This phenomena is shown in Figure 2.3, which graphs the  $I_{DS}$  versus  $V_{DS}$  characteristics of a differential transistor pair (gate width of 10  $\mu$ m and gate length of 1.2  $\mu$ m) with both an applied bulk bias and without an applied bulk bias (floating). Even at very low sub-hertz measurement frequencies, hysteresis is present for devices in which the bulk floats. The data indicates that when a p<sup>+</sup> contact backgate is electrode biased, the slow charge build up of the substrate in the p<sup>-</sup> buried layer, due to device-to-bulk leakage, is removed. This eliminates  $I_{DS}$  versus  $V_{DS}$  device hysteresis.

Figure 2.3 - MESFET IV hysteresis characteristics comparing (a) floating substrate to (b) p<sup>+</sup> ohmic contact biased substrate.

#### 2.2 Large-Signal and Small-Signal Model

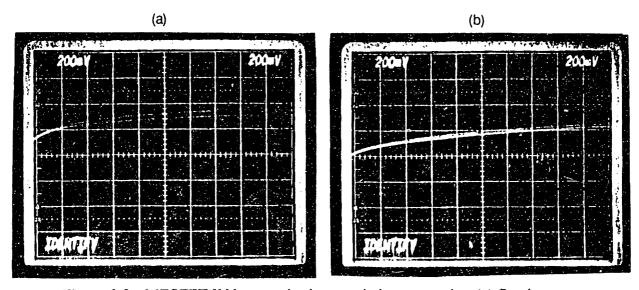

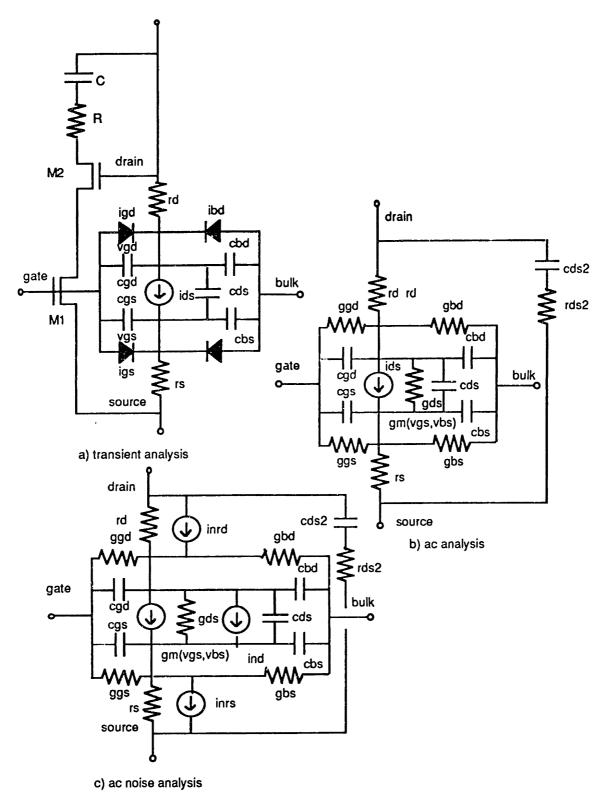

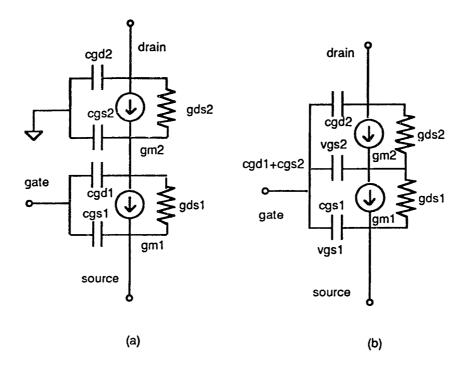

HSPICE<sup>9</sup> has developed a GaAs MESFET model for circuit simulations of the Vitesse enhancement-mode/depletion-mode digital MESFET process circuits that is a variation of the Statz model.<sup>10</sup> The improvement HSPICE has made over the published model is to design model inputs as process parameters. The primary advantage of this approach is the ability to implement statistical design procedures based on known parameter variations. The model is developed from process parameters and, therefore, attains high correlation with actual chip-test parameters. The corresponding equivalent circuit models used to describe the MESFET are shown in Figure 2.4. The controlled source determines the channel current as a function of VT and the applied bias potentials. The resistances rs and rd represent the total series resistance between the channel and the specified external contact. As predicted by the device physics, the Schottky gate diode is divided into a gate-source and gate-drain component. Capacitors cgs and cgd are the voltage-dependent

<sup>&</sup>lt;sup>9</sup> Meta Software HSPICE User's Manual Version H9001 1990.

<sup>&</sup>lt;sup>10</sup> H. Statz et al., "GaAs FET Device and Circuit Simulation in SPICE," *IEEE Transactions on Electron Devices*, Vol. ED-34, No. 2, February 1987.

capacitors associated with the Schottky barrier gate. Noise sources inrd and inrs model the equivalent current noise source of gate to drain and gate to source diodes. Noise source ind models the equivalent channel current themal noise component.

Figure 2.4 - HSPICE models for (a) Transient, (b) ac, and (c) ac noise analysis.

The HSPICE model is similar to that proposed by Statz, Newman, Smith, Busell, and House, but it contains several important differences. The I<sub>DS</sub> equations and two orders of derivatives are continuous, and, hence, functions describing I<sub>DS</sub>, gm, and V<sub>DS</sub> are continuous over the bias range of interest. This tends to eliminate HSPICE convergence problems. The main differences between the HSPICE and the Statz model are the method of including velocity saturation and the use of V<sub>T</sub>, which is function of the V<sub>BS</sub>, V<sub>GS</sub>, length, and width rather than a constant voltage. The advantage of using this form is that a good fit is attained between the model and measured data of the MESFET I<sub>DS</sub> verses V<sub>DS</sub> characteristics in the transition region from linear to saturated behavior. A comparison of the calculated and measured I<sub>DS</sub> versus V<sub>DS</sub> for various gate dimensions and threshold voltages is extremely good in this model.

The process enhancements and circuit design techniques, described in Chapter 3, that simultaneously improve threshold uniformity, reduce backgating, increase isolation, and reduce frequency-dependent output conductance of GaAs MESFET devices were all modeled using HSPICE.

#### 2.2.1 Threshold Voltage Model

The threshold voltage of a MESFET is a function of bias conditions including backgating, device geometry, temperature, doping concentration and the built in voltage of the Schottky barrier gate. In HSPICE, the threshold voltage for MESFET is expressed:

$$V_{TO}=V_{BI}-V_{P}$$

where V<sub>P</sub> and V<sub>BI</sub> are the pinch-off voltage, and built-in potential as earlier defined.

However, in HSPICE,  $V_{TO}$  is a model input parameter and may be derived from experimental data. As such,  $V_P$  and  $V_{BI}$  are not required inputs. In order to calculate the DC  $I_{DS}$  -  $V_{DS}$  curves for a device as a function of  $V_{GS}$  and temperature,  $V_{TO}$  is modified according to:

$$V_{T0} = V_{T0} + (GAMDS \cdot V_{DS}) + (k \cdot V_{BS}) - (TCV \cdot \Delta T)$$

2.8

where GAMDS is a multiplication factor that accounts for bias dependence,  $k(V_{BS})$  is the functional relationship for the backgating effect, and TCV is the temperature coefficient of the threshold voltage. The  $V_{DS}$  dependence is primarily due to the voltage variation with short-channel effects. The values of GAMDS and k are determined from experimental data using a least-squares-optimization curve fit. TCV was experimentally determined for discrete enhancement-mode and depletion-mode transistors of width 10  $\mu$ m and length 1.0  $\mu$ m as 0.95 mV - 1.1mV/°C over the commercial temperature range 0°C to +70°C.

#### 2.2.2 Channel Current Model

The HSPICE MESFET model to be employed in the proposed research is similar to that developed by Statz, Newman, Smith, Busell and Haus, <sup>11</sup> but it contains several important differences. The expression used to describe the controlled current source, IDS, is given by:

$$I_{DS} = \beta_{eff}(V_{GS}-V_{TO})VGEXP(1+\lambda V_{DS})[1-(1-ALPHA\bullet V_{DS}/3)^{SATEXP}] + I_{SUB}$$

2.9

where ALPHA determines the slope of the linear region of the  $I_{DS}$  versus  $V_{DS}$  curve and  $\lambda$  is the channel-length-modulation parameter described in Equation 2.6. The original Statz model sets VGEXP = 2 and SATEXP = 3. These factors were changed to VGEXP = 2.4 and SATEXP = 3.2 to give the best curve fit as determined by a least-squares-curve optimization. The choice of these values is critical when designing 12-bit precision circuits.

Velocity saturation occurs at high  $V_{GS}$  and  $V_{DS}$  biases where channel scattering reduces the electron mobility. This effect is accounted for in the expression for  $\beta_{eff}$  given by:

$$\beta_{\text{eff}} = (\beta \cdot W/L)/[1 + VCRIT \cdot (V_{GS} - V_{TO})]$$

2.10

where VCRIT represents the critical field for the onset of mobility degradation. The factor  $(V_{GS}-V_{TO})$  is used to reduce the approximately square law dependence at high  $V_{GS}$  potential. The combined effect of VGEXP and velocity saturation results in a slightly superlinear dependence of  $I_{DS}$  on  $V_{GS}$  and a compression of the transconductance. This shows that true velocity saturation is occurring over only a portion of the channel length. As the gate length decreases (for equal bias conditions) the composite power law behavior will tend toward unity.

Finally, subthreshold current is modeled in empirical form as given by:

<sup>11</sup> H. Statz et al., "GaAs FET Device and Circuit Simulation in SPICE," *IEEE Transactions on Electron Devices*, Vol. ED-34, No. 2, February 1987.

$I_{SUB} = I_{o}e^{ND \cdot V}_{DS \cdot e^{-NG \cdot V}GS}$  2.11

where Io is a constant that depends on geometry and ND and NG are empirically determined parameters.

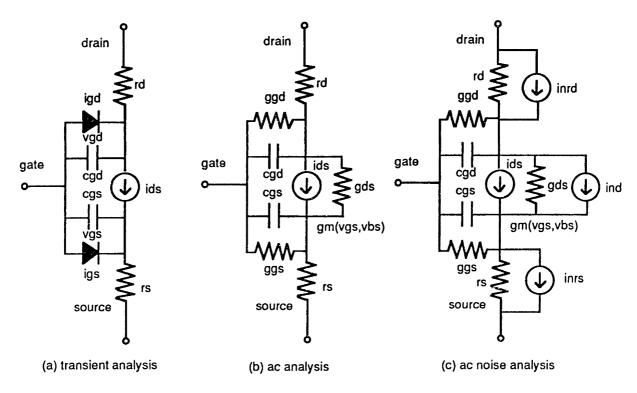

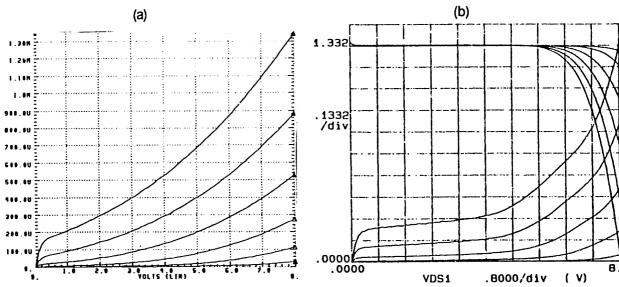

For this HSPICE model there is excellent comparison of the calculated and measured  $I_{DS}$  versus  $V_{DS}$  for various gate dimensions and threshold voltages. Figure 2.5 compares HSPICE simulated and measured dc characteristics of  $I_{DS}$  versus  $V_{DS}$  for  $V_{GS}$  = 0.1 to 0.6 volts of a 10  $\mu$ m-wide by 1.0  $\mu$ m-long enhancement-mode MESFET with the bulk biased at the source voltage.

Figure 2.5 - Comparison of IDS vs  $V_{DS}$  for  $V_{GS} = 0.1$  to 0.6 for a 10  $\mu$ m-wide by 1.0  $\mu$ m-long enhancement-mode MESFET with the bulk biased at the source voltage between (a) HSPICE simulation and (b) measured data.

For design calculations, the simpler physics expressions are used. HSPICE expressions and simulations are used to only to predict final physical layout performance and confirm analytical circuit calculations. Useful expressions that predict first-order performance are as follows: For gate voltage near threshold, I<sub>DS</sub> can be approximated by the square-law relationship given by:

$$I_{DS} = (W/L)N_d\mu\epsilon/2t(V_{GS} - V_T)^2$$

2.12

The ideal transconductance,  $g_m = \partial I_{DS}/\partial V_{GS}$ , is proportional to the incremental gate bias and is given by:

$$g_{m}=(W/L)N_{d}\mu\epsilon/2t(V_{GS}-V_{T})$$

2.13

#### 2.2.3 Capacitance Model

The HSPICE capacitance model uses the normal expressions for diode capacitances under both forward- and reverse-junction bias conditions shown in Equations 2.14 - 2.17.

CGS and CDS reverse bias condition:

$$C_{GS} = C_{GS_0} \cdot (1 - V_{GS}/V_{BI})^N$$

2.14

$$C_{DS} = C_{DSo} \cdot (1 - V_{DS}/V_{BI})^{N}$$

2.15

C<sub>GS</sub> and C<sub>DS</sub> forward bias condition:

$$C_{GS} = TT \cdot \partial I_{GS} / \partial V_{GS} + C_{GSo} \cdot (1 - V_{GS} / V_{BI})^{N}$$

2.16

$$C_{DS} = TT \cdot \partial I_{GD} / \partial V_{GD} + C_{DSO} \cdot (1 - V_{DS} / V_{BI})^{N}$$

2.17

where TT is the junction transit time,  $C_{GSo}$  and  $C_{DSo}$  are the zero bias junction capacitances, and  $V_{BI}$  is the junction potential. A more complicated option is available that includes the effects of velocity saturation and subthreshold biases on  $C_{GS}$  and  $C_{GD}$ . However, these expressions were found to give optimistic capacitance values and, therefore, were not employed in the device modeling. Instead, the model capacitance values employed are based on extracted S-parameter data measured with a Cascade Microtech probe station.  $^{12}$

#### 2.3 Frequency-Dependent Output Conductance Model

For mixed-mode conversion circuits, the large-signal MESFET circuit model must accurately predict dc, ac, and transient-analysis-frequency-dependent output conductance. For ac analysis, the drain lag effect describes in section 1.4 can be modeled by a simple pole-zero network connected in parallel with the drain and source regions. However, this model is insufficient for transient analysis of pulse waveforms because the MESFET will

<sup>&</sup>lt;sup>12</sup> P. Nuytkens, laboratory measurements, 1991.

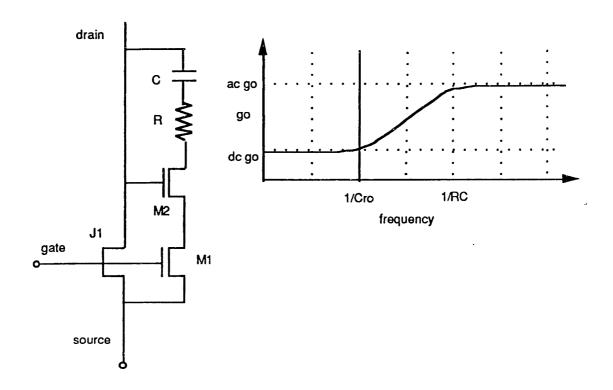

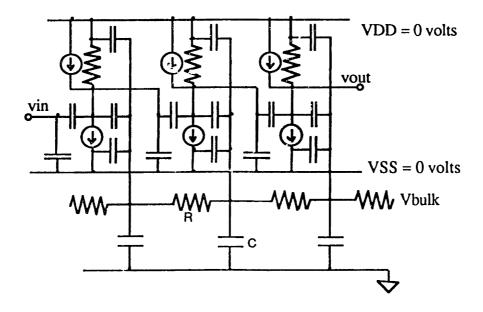

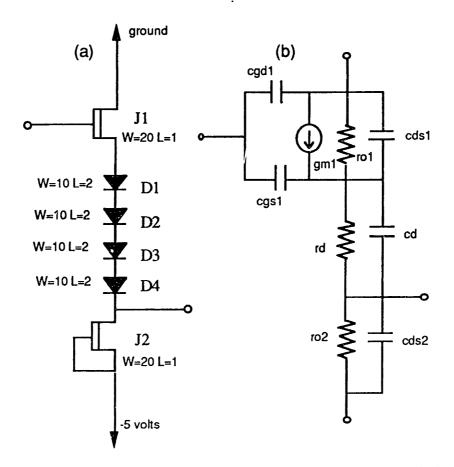

not shut off at low gate biases. In order to accurately model the transient response, a nonlinear device with the correct linear frequency on performance is placed in parallel with the intrinsic MESFET. An equivalent circuit model, shown in Figure 2.6, that exhibits these characteristics employs a series capacitor, C, and resistor-, R, loaded cascoded MOSFET in parallel with the intrinsic MESFET.<sup>13</sup> The parasitic MOSFET acts only as a parallel conduction during ac and transient operation. The MOSFET's intrinsic capacitances are set small compared to the MESFET's intrinsic capacitances, and the W/L ratio is set so the series on resistance is small compared to R. The ac-output conductance is set by selection of R with 1/RC determining the break-point frequency into the ac region and 1/Cr<sub>0</sub> determining the break-point frequency out of the dc region of operation. Figure 2.7 compares the HSPICE step response of the foundry-supplied SPICE parameters and the enhanced HSPICE large-signal model. As Figure 2.7 indicates, the response of this nonlinear-lag-network mechanization accurately represents measured transient and ac performance.

<sup>&</sup>lt;sup>13</sup> L. Larson, "GaAs MESFET Equivalent Circuit Model," *IEEE Journal of Solid State Circuits*, Vol. SC-22, No. 4, August 1987, p. 572.

Figure 2.6 - Enhanced HPSICE frequency-dependent-output-conductance-MESFET model.

Figure 2.7 - Transient response of HSPICE model and frequency-dependent-output-conductance-enhanced-HSPICE-MESFET model.

#### 2.4 Device-to-Substrate Model

The HSPICE GaAs MESFET model incorporates the backgate effect on both the depletion-mode and enhancement-mode devices by modifying the threshold voltage, V<sub>T</sub>, of each device proportional to bulk-to-source voltage, as given by:

$$V_T = V_{To} + [GAMDS \cdot vds + k(vbs)]$$

(2.18)

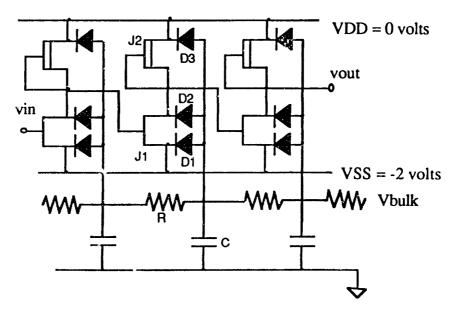

where V<sub>To</sub> is threshold voltage at zero V<sub>BS</sub>, GAMDS is the drain voltage induced threshold voltage lowering coefficient, vgs is the internal gate-source voltage, vbs is the internal bulk-to-source voltage, vds is the internal drain-to-source voltage, k is the threshold-voltage sensitivity to bulk voltage. This equation accurately expresses the backgate effect on a discrete device assuming the bulk voltage is predetermined and set to a known value. However, in the absence of a bulk-voltage source, the HSPICE model incorrectly drives this voltage to the highest power supply potential and produces erroneous simulation results. In fabricated circuits, this voltage is either set to the lowest potential by biasing the bulk electrode to VSS (the most negative power supply voltage) or is left floating where the substrate charge drives the bulk potential to a voltage between VSS and one diode drop above VSS. For the floating case, this voltage can be accurately determined by modeling and adding each transistor's contribution to the bulk charge. The charge contribution of a single inverter stage composed of a common source enhancementmode transistor, J<sub>1</sub>, and depletion-mode load transistor, J<sub>2</sub>, can be modeled through the addition of diodes D<sub>1</sub>, D<sub>2</sub>, and D<sub>3</sub> and capacitor C as shown in Figure 2.8. In this circuit,  $D_1$  models the n<sup>+</sup>/p<sup>-</sup> source-to-bulk diode of  $J_1$ ,  $D_2$  models the n<sup>+</sup>/p<sup>-</sup> drain-to-bulk diode of  $J_1$  in parallel with the n<sup>+</sup>/p<sup>-</sup> source-to-bulk diode of  $J_2$ , and diode  $D_3$  models the n<sup>+</sup>/p<sup>-</sup> drain-to-bulk diode of J<sub>2</sub>. Capacitor C includes the bulk-to-V<sub>DD</sub> and bulk-to-V<sub>SS</sub> parallel plate capacitances. Resistor R models the substrate conductivity between devices.

28

Figure 2.8 - Inverter stage with source-to-bulk and drain-to-bulk diodes.

This model can be used for understanding and demonstrating both crosstalk and duty-cycle modulation effects observed in digital GaAs MESFET circuits. Since all of the backgates of a digital GaAs MESFET circuit are connected to each other through the resistivity of the p<sup>-</sup> implanted buffer layer, the connection may be modeled with discrete resistors, R, sized in proportion to the distance a device is located from its nearest neighboring devices. Crosstalk can be reduced by either increasing the resistivity of the p<sup>-</sup> buffer layer or ac-grounding the bulk. As described earlier, increasing the resistivity of the p<sup>-</sup> buffer layer decreases threshold uniformity, which in turn limits integration size by reducing noise margins. Ac-grounding the bulk by either biasing the back of the die to Vss, or directly biasing the p<sup>-</sup> implant layer through a p<sup>+</sup> ohmic contact to Vss, reduces device crosstalk at the cost of increased backgating of devices biased above Vss. It is therefore necessary to develop a process technology that provides a heavy, p<sup>-</sup> buried layer implant and at the same time isolates devices. This is accomplished by adding n<sup>+</sup> ohmic guard rings that isolate p<sup>+</sup> ohmic biased regions. This device and circuit isolation technique is described in Chapter 3. Input duty-cycle modulation of output levels observed in digital

GaAs MESFET circuits can be seen through the small signal equivalent inverter model of Figure 2.9.

Figure 2.9 - Inverter stage with source-to-bulk and drain-to-bulk diodes small signal equivalent.

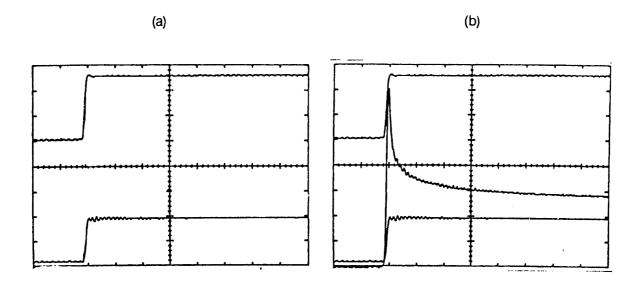

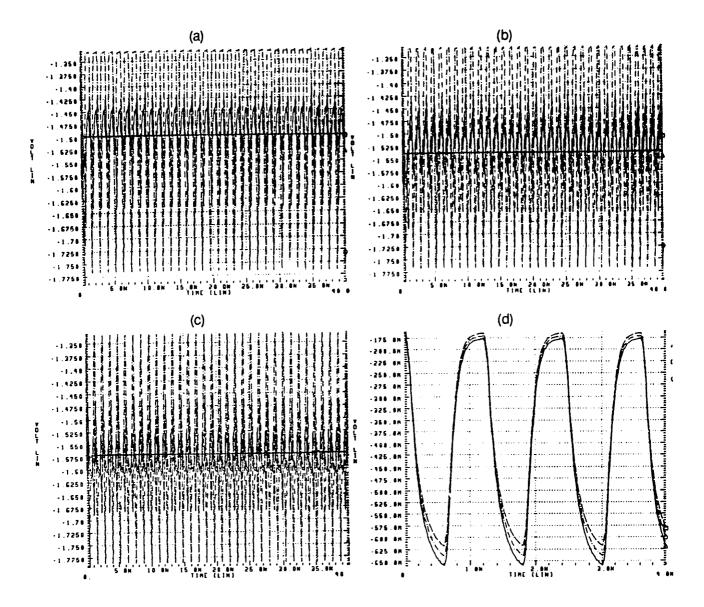

The voltage switching transients charge and discharge the diode capacitances, which are filtered by the low pass filter formed from the p<sup>-</sup> layer resistance and capacitance. This low-pass filter averages the switching transients to produce a dc-bulk-voltage potential proportional to the input wave form duty-cycle. An HSPICE simulation comparing the inverter stage bulk node with (a) 25 % high - 75% low periodic pulse train, (b) 50 % high - 50% low periodic pulse train, and (c) 75 % high - 25% low periodic pulse train, is shown in Figure 2.10. The bulk voltage of -1.575 in Figure 2.10 (a) reduces the pulse swing in by 25 mV while the bulk voltage of -1.500 in Figure 2.10 (c) increases the pulse swing by 25 mV over the nominal voltage pulse swing of Figure 2.10 (b).

Figure 2.10 - HSPICE simulation showing the inverter stage bulk node with (a) 25 % high - 75% low periodic pulse train, (b) 50 % high - 50% low periodic pulse train, and (c) 75 % high - 25% low periodic pulse train and (d) output level shifts due to modulation.

Input duty-cycle modulation of output levels can be eliminated by ac-grounding the bulk through either biasing the back of the die to V<sub>SS</sub> or directly biasing the p<sup>-</sup> implant layer through a p<sup>+</sup> ohmic contact to V<sub>SS</sub>.

The complete, enhanced HSPICE model that incorporates reverse-bias diodes for the MESFET's channel substrate interface to accurately model the dynamic backgating effect and parallel MOSFET and RC to accurately model frequency-dependent output

conductance is shown in Figure 2.11. Capacitor cds has a fixed value determined primarily by the layout and parasitics. Capacitors cbs and cbd are the capacitances due to the channel substrate p-n junction. Capacitor csd2 and resistor rds2 in the ac and ac noise model are the are the small signal equivalent of R and C of the transient model. This four-terminal model was used to simulate critical circuit performance of the digital-to-analog converter including glitch energy of the switching transients, settling time, and switch-to-current-source crosstalk.

Figure 2.11 - Enhanced HSPICE models for (a) transient analysis, (b) ac analysis, and (c) ac noise analysis.

The measured test structures described in Chapter 3 resulted in the HSPICE model parameters for the Vitesse GaAs MESFET process as shown in Table 2.1.

Table 2.1 - Large- and Small-Signal GaAs MESFET HSPICE Model Parameters (for 1  $\mu m$  gate lengths)

| <u>Parameter</u>                       | Enhancement-mode* | Depletion-mode** |

|----------------------------------------|-------------------|------------------|

| $V_{\mathrm{T}}$                       | 250 mV            | 800 mV           |

| $\sigma V_T$ (local 100 x 100 $\mu$ m) | 15 mV             | 45 mV            |

| $I_{DSS}$                              | 60 mA/mm          | 60 mA/mm         |

| $\sigma I_{DSS}$                       | 2.5%              | 6.3%             |

| gm                                     | 240 ms/mm         | 150 ms/mm        |

| $\sigma g_{m}$                         | 2%                | 4.2%             |

| cgs                                    | 1.2 pF/mm         | 1.9 pF/mm        |

| cgd                                    | 330 fF/mm         | 300 fF/mm        |

| cds                                    | 200 fF/mm         | 210 fF/mm        |

| rgs (1/ggs)                            | 2.2 kΩ•mm         | 28 kΩ•mm         |

| rgd (1/ggd)                            | 32 kΩ•mm          | 40 kΩ•mm         |

| r <sub>o</sub> s (1/gds,1/go)          | 180 mΩ•mm         | 100 mΩ•mm        |

| a <sub>vo</sub>                        | 23 V/V            | 16 V/V           |

| $f_T$                                  | 15.5 GHz          | 16.5 GHz         |

Bias Conditions:

<sup>\*</sup>  $V_{GS} = 0.5 \text{ V}, \text{VDS} = 1.0 \text{ V}$

<sup>\*\*</sup>  $V_{GS} = 0.0 \text{ V}, \text{ VDS} = 1.0 \text{ V}$

#### Chapter 3

# GaAs MESFET Process Enhancements and Design Methodology for Mixed-Mode MESFET Circuits

#### 3.1 GaAs MESFET Process Enhancements

Based on the device physics and circuit analysis presented in Chapter 2, process enhancements and circuit design methodology for simultaneously reducing backgating, increasing isolation, and maintaining high threshold uniformity of GaAs MESFET devices were designed. These include: 1) an additional buried p<sup>-</sup> implant inserted prior to active area patterning of the transistor to control device-threshold uniformity and short-channel effects, 2) a p<sup>+</sup> ohmic contact process step in the circuit design that can be used to bias the p<sup>-</sup> buried layer background implant and isolate bulk regions, and 3) an n<sup>+</sup> ohmic contact ring placed around the p<sup>+</sup> contact regions and biased to a positive potential to form a depletion region through the p<sup>-</sup> layer to the semi-insulating substrate that increases device isolation.

The digital direct-coupled-FET-logic (DCFL) and complementary-level-FET-logic (CLFL) cells, biased with depletion transistor loads connected to ground (V<sub>CC</sub>) and enhancement-mode switches connected to -2 volts (V<sub>TT</sub>), are isolated with p<sup>+</sup> ohmic contact rings connected to V<sub>TT</sub> to prevent turn-on of the bulk-to-source diode of the enhancement-mode transistor. In both the DCFL and CLFL circuit topologies, the enhancement-mode source is always connected to V<sub>TT</sub> setting V<sub>BS</sub> equals zero, which eliminates backgate of this device. The high-voltage output of either a DCFL or CLFL circuit stage is clamped by the next stage's enhancement-mode input transistor's gate-to-source Schottky diode to 0.6 volts above V<sub>TT</sub>. For a logic-high-voltage level, the driving

stage's depletion-mode load source-to-bulk voltage is therefore limited to -0.6 volts, which is above the depletion-mode threshold of -0.8 volts. For a logic-low-voltage level, the driving stage's depletion-mode load source to bulk voltage is limited to -0.1 volts (IDSS of the depletion-mode load multiplied by the enhancement-mode on resistance), which is significantly above the depletion-mode threshold of -0.8 volts. Thus, for the depletion-mode load, there is a positive backgate effect. It is therefore necessary to size the enhancement-mode device large enough to handle the worst-case depletion current occurring during a logic low. This design constraint limits the minimum circuit  $\beta$  ratio, defined in Equation 3.1, to 10 in order to have sufficient negative voltage-level noise margins. <sup>1</sup>

$$\beta \text{ ratio} = (W_E/L_E)/(W_D/L_D)$$

3.1

The 0.5 volt depletion-mode backgate modulation does reduce switching speed because the load current is reduced as the device switches from logic low to high in a conventional inverter stage. However, circuits employing feedback in the output stage overcome the switching speed limitation and are discussed in Chapter 4.

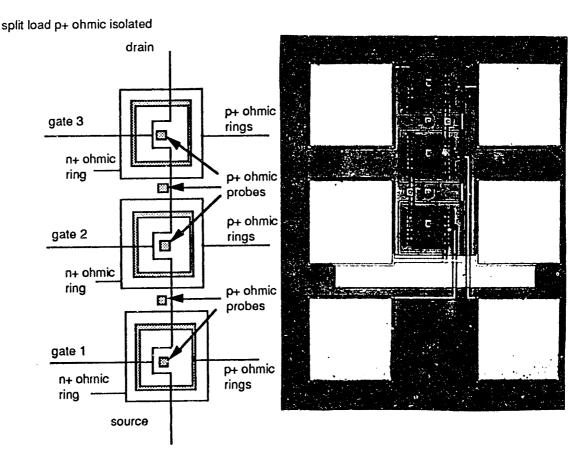

The analog cell's discrete transistors are isolated with p<sup>+</sup> ohmic contact rings connected to the source of the transistor forcing VBS equal to zero independent of source voltage bias. To reduce the substrate currents generated in analog circuits with transistor sources biased at large voltages differences (greater than 1 volt), an n<sup>+</sup> ohmic contact ring placed around the p<sup>+</sup> contact regions and biased to the drain of the transistor is used to form a depletion region through the p<sup>-</sup> layer to the semi-insulating substrate. This depletion region increases the device isolation and reduces the substrate current, thereby allowing higher transistor packing over prior art. Analog transistors biased at the same source potential are grouped within a single p<sup>+</sup> ohmic ring bulk bias and n<sup>+</sup> ohmic guard ring. The combination of concentric p<sup>+</sup> ohmic and n<sup>+</sup> ohmic ring topology is similar to a well-

<sup>&</sup>lt;sup>1</sup> Vitesse Foundry Design Manual, Version 5.0, 1991.

isolated CMOS process. In a further development, the initial p<sup>-</sup> buried implant could be patterned only under the active area of the MESFET, which would reduce the need for an n<sup>+</sup> ohmic isolation ring at the cost of an additional mask step. However, removal of the n<sup>+</sup> ohmic isolation is not an advantage in analog circuit designs where device density is not a priority.

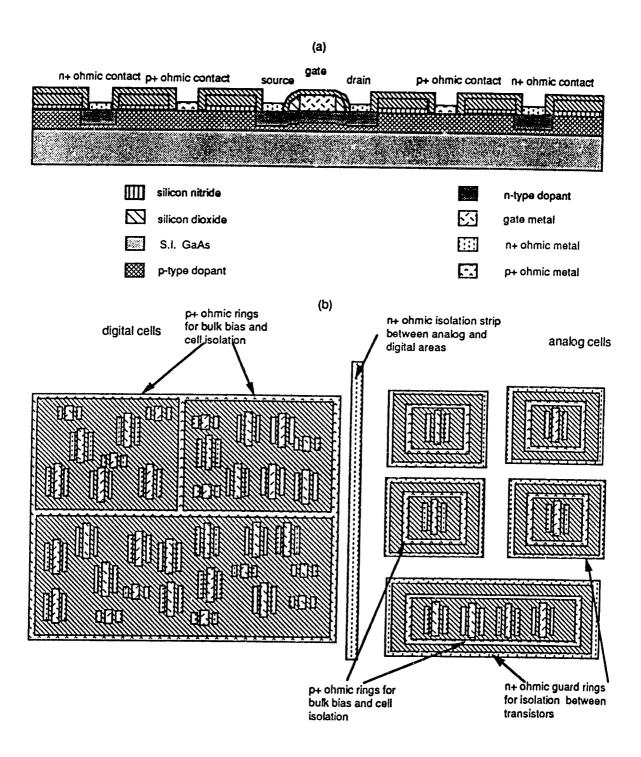

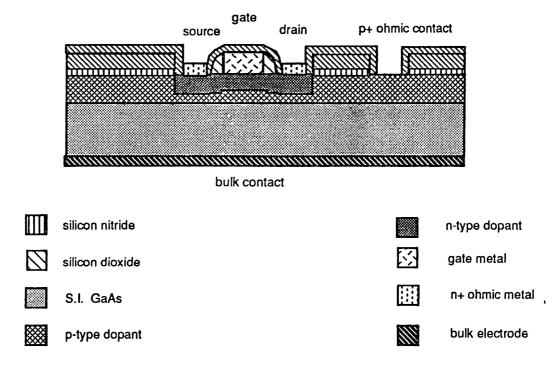

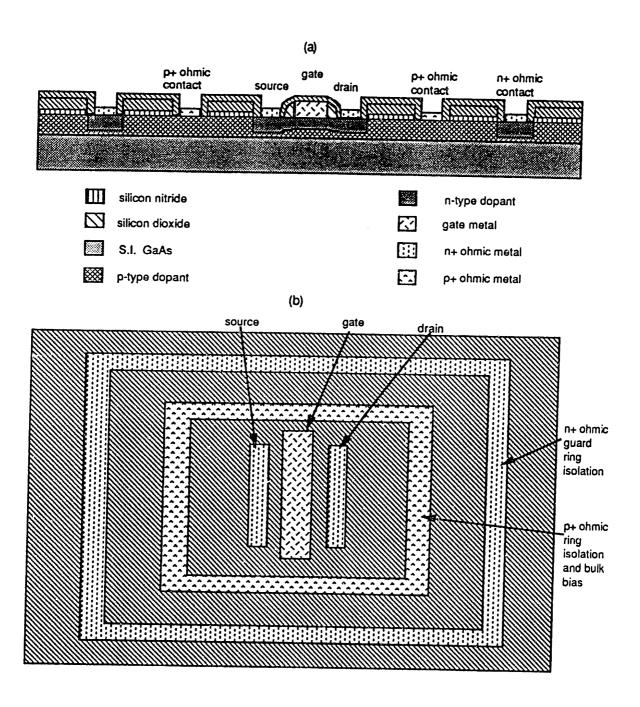

A cross section of the GaAs MESFET p<sup>+</sup> ohmic ring bulk bias and n<sup>+</sup> ohmic ring isolation mixed-mode process technology is shown in Figure 3.1 (a). The layout of a generic mixed-mode system containing digital macro cells isolated with p<sup>+</sup> ohmic contact rings biased to V<sub>TT</sub> and analog cells with discrete transistors isolated with concentric n+ ohmic contact guard rings surrounding p<sup>+</sup> ohmic bulk biased to the source of the individual transistors is shown in Figure 3.1 (b). With this methodology, an acceptably high digital device density is achieved while maintaining high isolation. The increase in device isolation reduces jitter and phase noise characteristics of digital clock, comparator, latch, and switch circuits. In addition, backgate uniformity is improved because the substrate is pinned to a known reference. This improves relative matching of current sources. Highperformance clocks, comparators, latches, switches, and current sources are all required components in the development of high-precision and high-speed analog and mixed-mode circuits. The design rationale for using each of the bulk-biasing and isolation techniques employed in this mixed-mode process is examined in the next sections including use of the buried p layer implant, p ohmic contact bulk bias and isolation, p-well isolation and n+ ohmic guard ring isolation. All of these techniques except p-well isolation were used in the design of the 12-bit digital-to-analog converter. The p-well isolation technique is included here for completeness.

Figure 3.1 - GaAs MESFET analog and mixed-mode process technology: (a) horizontal view of self-aligned gate MESFET process with p+ ohmic and n+ ohmic ring isolation; (b) top view of layout showing analog and digital cell isolation and bulk bias.

# . 3.1.1 Buried p. Buffer Layer

The use of an ion-implanted buried p<sup>-</sup> layer implant to control the short-channel effects in GaAs MESFETs was proposed by Yamasaki and Hirayama in 1983.<sup>2</sup> Both Mg and Be p-type dopants have been successfully employed as the p<sup>-</sup> buffer layer. The p<sup>-</sup> buffer layer has also been shown to reduce threshold spreads by mitigating the effects of background acceptor concentrations and variations of the base wafer. Figure 3.2 shows a cross section of a self-aligned gate GaAs MESFET process with a p<sup>-</sup> buried implant layer. The bulk is biased by plating the back of the wafer.

Figure 3.2 - Self-aligned GaAs MESFET process with p buried implant.

A high-dose buried p<sup>-</sup> layer implant has resulted in an enhancement-mode MESFET (σV<sub>T</sub>) of 8 mV across a 3 inch wafer.<sup>3</sup> Large variations in enhancement-mode V<sub>T</sub> directly reduce noise margins. Therefore, reducing and controlling σV<sub>T</sub> across the wafer and from wafer

<sup>&</sup>lt;sup>2</sup> K. Yamasakai et al., "Theoretical Approach in Gate Shortening of n+ Self-Aligned GaAs FETs," in *Proceedings of Japan IECE National Conference on Semiconductors*, 1983.

<sup>&</sup>lt;sup>3</sup> R. Sadler et al., "A High-Yield Buried p-Layer Fabrication Process for GaAs LSI Circuits," *IEEE Transactions on Electron Devices*, Vol. 38, No. 6, 1991.

lot to wafer lot is the single most important requirement necessary to achieve high yields of VLSI direct-coupled-FET-logic circuits. In mixed-mode applications, small  $\sigma V_T$  increases comparator resolution, reduces operational amplifier offsets, and reduces glitch energy of switches in a digital-to-analog converter. An adverse effect of employing a p<sup>-</sup> buffer layer is the increased gate-to-bulk, source-to-bulk, and drain-to-bulk parasitic capacitances, which reduce switching speed, increase gate delay, and reduce amplifier bandwidth. A second negative effect of employing a high p<sup>-</sup> buffer layer implant is a reduction in device isolation, which causes an increase in crosstalk because the substrate resistivity has been decreased up to two orders of magnitude over that of the base wafer. This increased substrate conductivity causes increased phase noise in analog circuits and a reduction of noise margin in digital circuits. The increased substrate conductivity enables the local charge pumping of the substrate to undesirably affect adjacent cell backgates. This is analyzed for ring oscillators in Chapter 4.

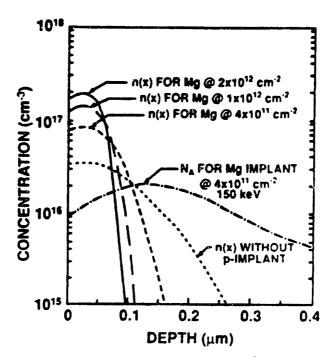

The effect of a 150-keV Mg buried p<sup>-</sup> implant on a device's electron concentration profile is shown in Figure 3.3 where the channel has been implanted with Si at 90-keV. Without the p-buried implant at all, the n(x) profile is broad and has a fluctuating tail region caused by the overlap of the adjacent n<sup>+</sup> region in the self-aligned device structure. The extent of this tail is not controlled, which results in variations in MESFET threshold and IDSS. With the p<sup>-</sup> buried implant, the electron concentration profile is sharpened, resulting in a steeper tail and higher peak concentration, which clearly defines the channel depth and therefore threshold.

Figure 3.3 - Mg acceptor concentration profile  $N_A(x)$  and resulting electron concentration profile n(x) for various doses.<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> R. Sadler et al., "A High-Yield Buried p-Layer Fabrication Process for GaAs LSI Circuits," *IEEE Transactions on Electron Devices*, Vol. 38, No. 6, 1991.

### 3.1.2 P+ Ohmic Contact Isolation

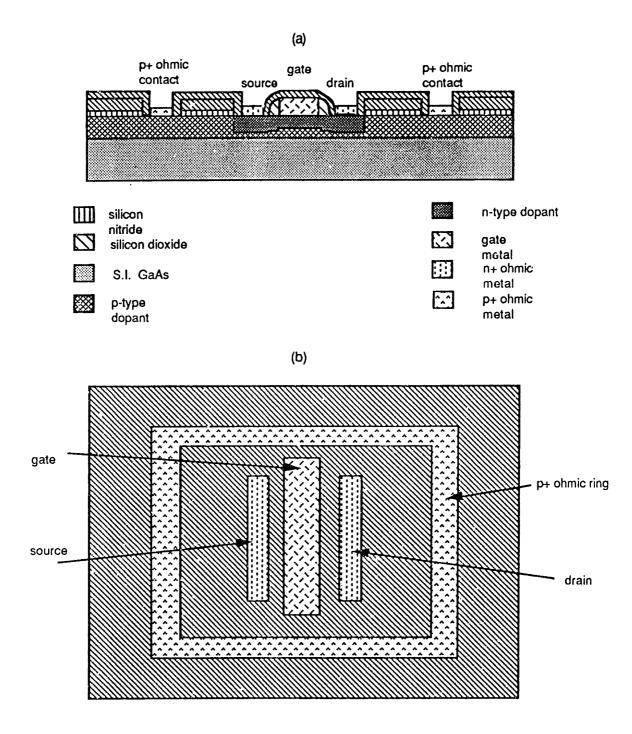

A p<sup>+</sup> ohmic-ring contact is used to both dc-bias and ac-ground the p<sup>-</sup> buried buffer layer. This enables the p<sup>-</sup> buried buffer to be used in order to increase MESFET threshold uniformity, while at the same time maintaining device isolation. Without the p<sup>+</sup> ohmic contact bias, the p<sup>-</sup> buried implant layer potential would be charge pumped to a value between VSS and VSS + 1 diode drop, depending upon the dc-average of the duty cycle, clock risetime/falltime, and  $\beta$  ratio of digital gates of all the switching circuits of a specific design. Since the p<sup>-</sup> buried buffer layer is not a perfect conductor, the averaging of the charge pumping is both a localized area- and device-geometry-dependent effect. The backgate potential contains higher frequency components that crosstalk to adjacent devices causing close-in side band modulation. The p<sup>+</sup> ohmic contact rings ac-short the substrate and attenuate the crosstalk modulation. The p+ ohmic contact rings also enable the backgates of large areas of one circuit to be biased at one potential that is several volts different from a second area on the same die. This feature is particularly useful in combining 2-volt DCFL circuits with 5 volt SCFL circuits. SCFL and DCFL circuits are often combined in high-speed, time-division multiplexers that contain a single high-speed SCFL input, which sequentially drives an array of lower-speed DCFL outputs. A cross section and layout of the p<sup>+</sup> ohmic ring isolation process is shown in Figure 3.4.

Figure 3.4 - GaAs MESFET p<sup>+</sup> ohmic isolation process (a) horizontal view of Self-Aligned Gate MESFET Process with p<sup>+</sup> ohmic isolation; (b) top view of transistor layout showing p+ ohmic ring isolation and bulk bias.

### 3.1.3 P-Well Isolation

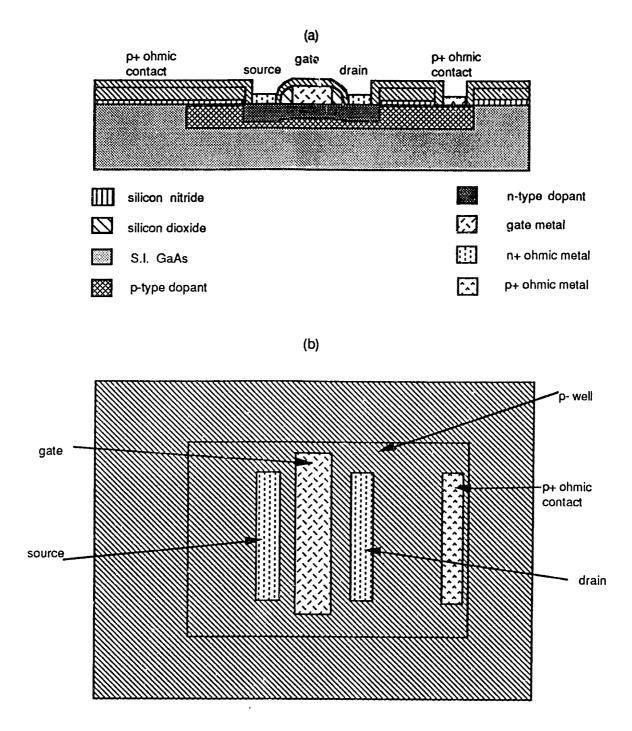

Adding the p<sup>-</sup> buffer layer only under the active area of the transistor and biasing this p-well to the source of the transistor can be used as an effective technique to reduce the backgate effect in analog circuits.<sup>5</sup> The source-to-bulk connection insures that this n<sup>+</sup> ohmic/p- buffer layer junction neither becomes forward biased nor modulated by gate-tosource or drain-to-source voltage transients. As mentioned in section 1.4, MESFET frequency-dependent output conductance has been attributed to the charging and discharging of EL2 traps in the substrate. This topology also insures that the channel to pwell potential is independent of changes in the charge states of the EL2 traps. A more subtle effect and advantage of the p-well isolation is the bootstrapping of parasitic substrate capacitances in circuits, including unity-gain-buffer and current-source-load circuits. Highfrequency designs of these topologies employ bootstrapping techniques to clamp VDS and VGS to reduce the effect of CDS and CGS and to achieve high bandwidths that are limited by the parasitic source-to-p buffer layer and drain-to-p buffer layer capacitances. Actively driving the p<sup>-</sup> buffer layer reduces these capacitances to that of the p<sup>-</sup> buffer-layer-to-bulkparallel-plate capacitance. This p-well structure is similar to the p-well NMOS device used in silicon CMOS processes. Two problems associated with this process and circuit technique are first, the requirement of an additional mask and processing step to pattern the p- buried layer implant and, second, the resulting reduction in digital-device density due to the area requirement of the p+ ohmic biasing contact. A cross section and layout of the pwell isolation process is shown in Figure 3.5.

<sup>&</sup>lt;sup>5</sup> P. Canfield et al., "A p-Well GaAs MESFET Technology for Mixed-Mode Applications," *IEEE Journal of Solid State Circuits*, Vol. 25, No. 6, December 1990.

Figure 3.5 - GaAs MESFET p-well isolation process: (a) horizontal view of self-aligned gate MESFET process with p-well isolation; (b) top view of transistor layout showing p- well isolation and bulk bias.

## 3.1.4 N+ Ohmic Contact

An n<sup>+</sup> ohmic contact cell ring was placed concentrically around the p<sup>+</sup> ohmic cell ring to provide a second ac-ground shield and increase the substrate resistivity between analog cells. The n<sup>+</sup> ohmic guard rings are made at the same time and with the same implant as the source/drain implants and therefore do not require an additional processing step. The n<sup>+</sup> ohmic ring acts like a two-dimensional Faraday shield, which terminates horizontal electric field lines generated by external-cell circuits, thereby reducing electromagnetic coupling between cell circuits. In a similar fashion, radiating electric fields produced by the cell itself are terminated on the n<sup>+</sup> ohmic ring. N<sup>+</sup> ohmic metal was selected to provide the shield instead of gate metal, metal 1, metal 2, or metal 3 because when the n<sup>+</sup> ohmic metal is biased to a positive potential, a depletion region forms under the vertical n<sup>+</sup>ohmic/p<sup>-</sup> buffer layer diode. For sufficient applied-positive n<sup>+</sup> ohmic-tobulk voltage, the depletion region extends through the p buffer layer to the semi-insulating substrate, increasing the sheet resistance between cells two orders of magnitude back to that of the original semi-insulating substrate without the p-buffer layer. A cross section and layout of the p<sup>+</sup> ohmic bulk bias and n<sup>+</sup> ohmic guard ring isolation process is shown in Figure 3.6.

Figure 3.6 - GaAs MESFET analog and mixed-mode process technology: (a) horizontal view of self-aligned gate MESFET process with p+ ohmic bulk bias and n+ ohmic guard ring isolation; (b) top view of layout showing single analog transistor isolation and bulk bias.

# 3.2 GaAs MESFET Circuit Design Methodology

The p+ ohmic ring bulk isolation and n+ ohmic guard ring process enable circuit topologies incorporating cascode and self-bootstrap techniques to achieve high performance. The combined cascode and self-bootstrap techniques hold V<sub>DS</sub> of the primary transistor constant, which reduces the frequency-dependent output conductance. Connecting the bulk to source of transistor sets V<sub>BS</sub> to zero. It is important to note that only the *combination* of the bulk isolation process and the cascode/self-bootstrap circuit technique act to reduce the frequency-dependent output conductance. It is necessary to hold constant both V<sub>DS</sub> and V<sub>BS</sub> to reduce frequency-dependent output conductance. Clamping one without the other results in marginal performance. The circuit performance of a current source, cascode transistor current switch, and voltage-level shifter are examined in this process. Each topology shows improved performance over prior art and forms the core technology on which the 12-bit digital-to-analog converter described in Chapter 5 was developed.

### 3.2.1 Current Source

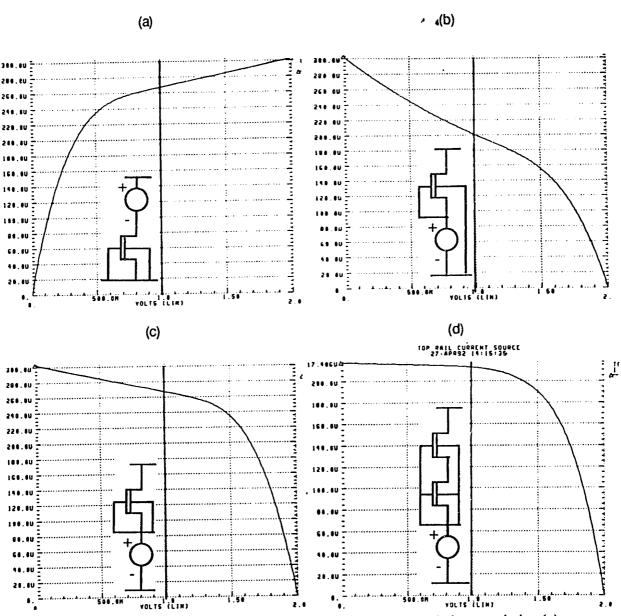

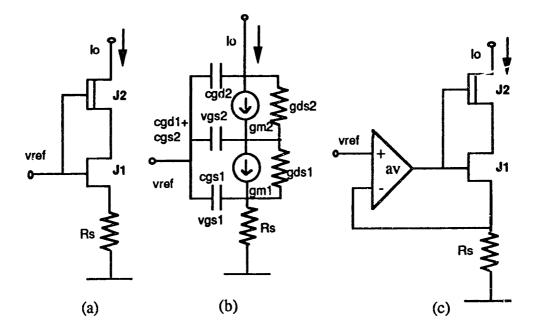

High-precision analog and mixed-mode circuits all require current sources with high output impedance, low- temperature and process sensitivity, precise scaling and matching, and positive and negative voltage biasing. GaAs MESFET enhancement-mode/depletion-mode processes lacking a p-channel device are limited to NMOS-like current-source topologies. The simplest current source is a single depletion-mode transistor with its gate and source connected together and biased at VDS to be greater than VSAT, which results in a current source output impedance of 1/λI<sub>bias</sub> where λ is defined as the channel length modulation parameter. The ideal 1/λI<sub>bias</sub> output impedance occurs only when this current source is operated from the negative voltage rail where VBS is equal to zero. This current source suffers from the backgate effect when operated from the positive voltage rail where VBS is not zero. Figures 3.7 (a) and (b) show the simple current source IV characteristics operating under both described bias conditions, while

Figure 3.7 (c) simulates a third condition where the substrate is biased to the source node of the simple depletion mode transistor connected to a positive voltage rail. Note that Figures 3.7 (a) and 3.7 (c) are linear and symmetric around ground, while that of 3.7 (b) has a significant nonlinear tail as VDS is increased above 1 volt.

Figure 3.7 - Depletion-mode transistor current source I-V characteristics (a) negative voltage rail biased depletion current source ( $V_{BS}=0$ ); (b) positive voltage-rail-biased depletion current source showing backgate effect ( $V_{BS}$  dependent on bias); (c) positive voltage rail biased depletion current source without backgate effect ( $V_{BS}=0$ ); (d) cascode depletion current source ( $V_{BS}=0$ ).

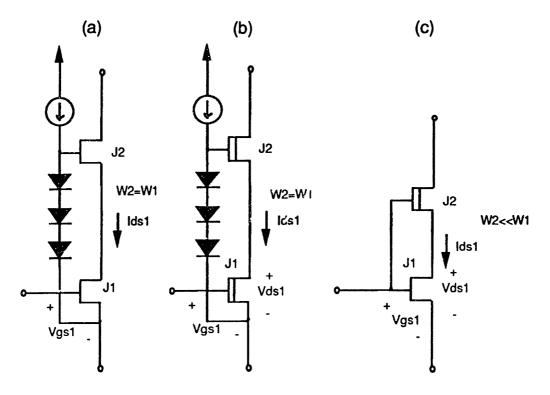

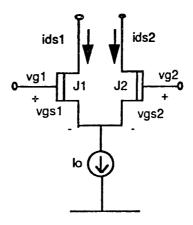

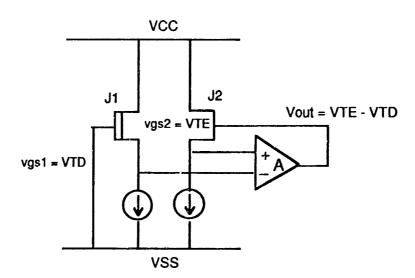

The simple current source output impedance can be improved by using the two-transistor (J<sub>1</sub>, J<sub>2</sub>) self-bootstrapped current source methodology shown in Figure 3.7 (d). The circuit is self-bootstrapped because V<sub>GS1</sub>=0 and, therefore, I<sub>DS1</sub>=I<sub>DSS</sub>; J<sub>2</sub> is now biased at a constant I<sub>DS</sub>, and, for J<sub>2</sub> operating in early saturation, V<sub>GS2</sub> is constant, which in turn clamps V<sub>DS1</sub>. The circuit relies on the early-saturation phenomenon to maintain J<sub>1</sub> and J<sub>2</sub> in saturation.<sup>6</sup> The widths of transistors J<sub>1</sub> and J<sub>2</sub> are chosen to operate both devices in the saturation region, which increases the output impedance of the current source by 1+ gm<sub>1</sub>r<sub>0</sub>1. All of the top voltage rail current sources impedances are increased through the source-substrate technique. Also, matching between positive and negative voltage-rail biased current sources is significantly improved through the source-biased-substrate technique. This results in higher performance current mirrors, which are an integral building block of analog designs.

### 3.2.2 Cascode Amplifier