### **GaN Electronics for High-Temperature Applications**

by

Mengyang Yuan

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Computer Science and Engineering

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2020

© Massachusetts Institute of Technology 2020. All rights reserved.

### Signature redacted

. . . . . . . . . . . . . . . . .

Author ...... Department of Electrical Engineering and Computer Science January 30, 2020

### Signature redacted

Certified by .....

. . . . . . . . . .

Professor of Electrical Engineering and Computer Science Thesis Supervisor

### Signature redacted

Accepted by.

UU Leslie A. Kolodziejski

Professor of Electrical Engineering and Computer Science

Chair, Department Committee on Graduate Students

.

. · · ·

$\mathbf{2}$

#### **GaN Electronics for High-Temperature Applications**

by

Mengyang Yuan

Submitted to the Department of Electrical Engineering and Computer Science on January 30, 2020, in partial fulfillment of the requirements for the degree of Master of Science in Computer Science and Engineering

#### Abstract

Gallium nitride is a promising candidate for high-temperature applications. However, despite the excellent performance shown by early high-temperature prototypes, several issues in traditional lateral AlGaN/GaN HEMTs could cause early degradation and failure under high-temperature operation (over 300 °C). These include ohmic degradation, gate leakage, buffer leakage, and poor passivation. Besides, enhancement-mode HEMTs are preferred from the application point of view by reducing the circuit complexity and cost. At the same time, the two-dimensional electron gas induced by AlGaN/GaN heterostructures makes HEMTs be naturally depletionmode devices.

This thesis aims to demonstrate devices capable of high-temperature operation without extra cooling systems by combing gate injections transistors (GITs) with ion-implanted refractory metal contacts. The Si ion implantation in AlGaN/GaN heterostructures was comprehensively studied here regarding implantation conditions, activation annealing conditions, metallization schemes. A self-aligned gate-first process, together with etch-stop process, was developed and optimized to improve fabrication efficiency and device uniformity for large-scale integration. Basic logic building blocks, including inverters, NAND gate, NOR gate, SRAM, and ring oscillator, have been demonstrated and characterized at both room temperature and high temperature.

Thesis Supervisor: Tomás Palacios Title: Professor of Electrical Engineering and Computer Science

### Acknowledgments

This thesis has been postponed over a year due to many unexpected issues, and I am not able to accomplish it without the support from my advisor, collaborators, other group members, my friends, and my family. Here I would like to express my sincere appreciation to all of them:

First, I would like to thank my advisor Prof. Tomás Palacios, for his continued support and encouragement. His enthusiastic and optimistic attitudes towards research have strongly inspired me working on challenging but exciting projects. He also provided me enough freedom and essential resources to push research progress forward.

Second, I would like to thank my collaborators outside MIT. Prof. Yuji Zhao from Arizona State University provided the GaN on sapphire wafers. Dr. Kai Cheng from Enkris Semiconductor Inc. provided GaN on Si wafers. Dr. Aseem Srivastava and Dr. Arif Zeeshan from Applied Materials helped me with ion implantation and gave me useful suggestions. Last, but not least, I would like to thank Prof. Marisa López-Vallejo for helping me with the design of GaN microcontroller. This work is supported in part by the National Aeronautics and Space Administration (NASA) under grant number no. 80NSSC17K0768, and Masdar Institute of Technology (UAE).

Third, I would like to thank every member of Palacios' group. Joe helped me schedule meetings with Tomás, ship package, and order equipment. Only because of him, I can focus on research. I also want to thank Daniel Piedra, Min Sun, and Yuhao Zhang for their kind mentorship and guidance on my research. In particular, I want to thank Yuhao for helping me learn and do basic cleanroom processes at the beginning. I want to thank Qingyun Xie and Nadim Chowdhury. Discussions with them are always encouraging and fruitful. Besides, I would like to thank Ahmad Zubair, Bin Lu, Marek Hempel, Elaine Mcvay, Josh Perozek, Pao-Chuan Shih, Xu Zhang, Yuxuan Lin, and Zhihong Liu for their support for my work.

Besides, I want to thank the staff of the Microsystems Technology Lab. None of my work would happen without their help. They are always there when you need training or have tool problems.

Finally, I would like to thank my friends and family for their love and support.

# Contents

| 1 | Intr | roduct  | ion                                                          | 17 |

|---|------|---------|--------------------------------------------------------------|----|

|   | 1.1  | Applie  | cations of High-Temperature Electronics                      | 17 |

|   | 1.2  | Challe  | enges of High-Temperature Electronics                        | 19 |

|   |      | 1.2.1   | Increasing Intrinsic Carrier Density with Temperature        | 19 |

|   |      | 1.2.2   | Increasing Junction Leakage with Temperature                 | 20 |

|   |      | 1.2.3   | Decreasing Carrier Mobility with Temperature                 | 23 |

|   |      | 1.2.4   | Other Issues                                                 | 23 |

|   | 1.3  | Wide    | Bandgap Materials for High-Temperature Applications          | 23 |

|   | 1.4  | Challe  | enges of Gallium Nitride and Scope of Thesis                 | 27 |

| 2 | Stu  | dy of ( | the Ion-implanted Refractory Metal Contact                   | 31 |

|   | 2.1  | Introd  | luction                                                      | 31 |

|   | 2.2  | Degra   | dation of AlGaN/GaN Heterostructure and Activation Annealing |    |

|   |      | Cappi   | ng Layer                                                     | 33 |

|   |      | 2.2.1   | Device Structure                                             | 33 |

|   |      | 2.2.2   | Results and Discussion                                       | 34 |

|   | 2.3  | Study   | of the Si-ion Implanted Refractory Contact                   | 35 |

|   |      | 2.3.1   | Epitaxial Structure and Fabrication                          | 38 |

|   |      | 2.3.2   | Results and Discussion                                       | 40 |

|   |      | 2.3.3   | High Temperature Degradation Test                            | 49 |

|   | 2.4  | Concl   | usion                                                        | 51 |

.

| 3 | Sel | f-Align | ed Gate-First Gate Injection Transistors (GITs) with Etch                           | -   |

|---|-----|---------|-------------------------------------------------------------------------------------|-----|

|   | Sto | p Proc  | cess                                                                                | 55  |

|   | 3.1 | Introd  | luction                                                                             | 55  |

|   | 3.2 | Simul   | ation of GITs Epitaxial Structure                                                   | 57  |

|   | 3.3 | Optin   | nization of GIT's Process                                                           | 58  |

|   |     | 3.3.1   | Etch-Stop Process of p-GaN                                                          | 58  |

|   |     | 3.3.2   | Self-Aligned Gate Metallizations                                                    | 62  |

|   | 3.4 | Fabric  | cation of GITs                                                                      | 64  |

|   |     | 3.4.1   | Device Structure                                                                    | 64  |

|   |     | 3.4.2   | Results and Discussion                                                              | 65  |

|   | 3.5 | Concl   | usion                                                                               | 66  |

| 4 | Log | ic Buil | lding Blocks Based on GaN Electronics for High-Temperat                             | ure |

|   | Ор  | eration | L                                                                                   | 69  |

|   | 4.1 | Mono    | lithically Integration of $E/D$ -mode HEMTs and Uniformity Test                     | 70  |

|   |     | 4.1.1   | Device Structure                                                                    | 70  |

|   |     | 4.1.2   | Results of E/D-mode HEMTs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 71  |

|   |     | 4.1.3   | Comparison of E/D-mode Inverter and E/E-mode Inverter $% {\rm (Inverter)}$ .        | 72  |

|   |     | 4.1.4   | Uniformity Test                                                                     | 75  |

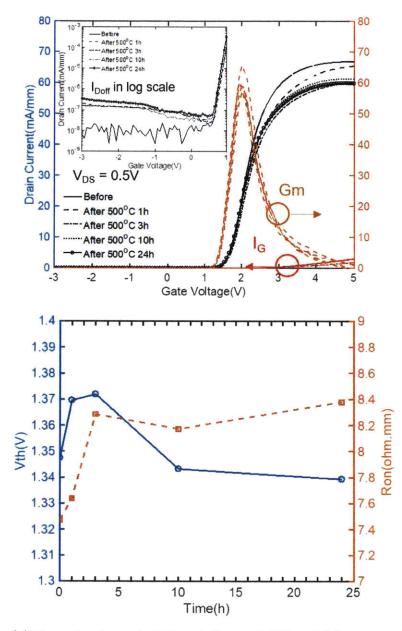

|   |     | 4.1.5   | High Temperature Degradation Test                                                   | 75  |

|   | 4.2 | Comp    | act Modeling of E/D-mode HEMTs                                                      | 77  |

|   | 4.3 | Logic   | Building Blocks for High-Temperature Operation                                      | 79  |

|   |     | 4.3.1   | Epitaxial Structure and Fabrication                                                 | 79  |

|   |     | 4.3.2   | NAND/NOR Gates                                                                      | 79  |

|   |     | 4.3.3   | SRAM                                                                                | 81  |

|   |     | 4.3.4   | Ring Oscillator                                                                     | 85  |

| 5 | Cor | nclusio | n and Future Work                                                                   | 91  |

|   | 5.1 | Thesis  | S Conclusion                                                                        | 91  |

|   | 5.2 | Future  | e Work                                                                              | 92  |

# List of Figures

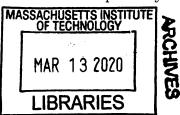

| 1-1 | Semiconductor intrinsic carrier concentration $(n_i)$ versus temperature |    |

|-----|--------------------------------------------------------------------------|----|

|     | for silicon, 6H-SiC, 4H-SiC and wurtzite GaN which has a weaker poly-    |    |

|     | type dependence.                                                         | 21 |

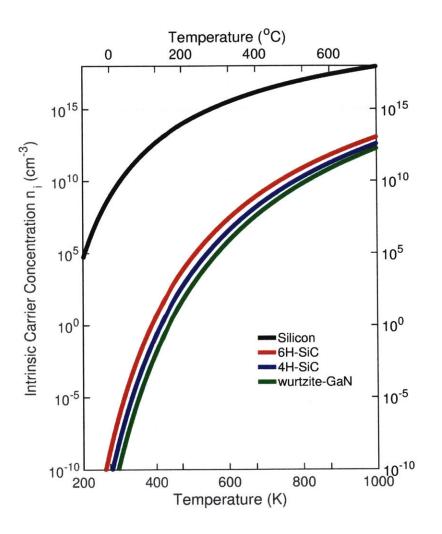

| 1-2 | Materials properties of Si, SiC and GaN                                  | 25 |

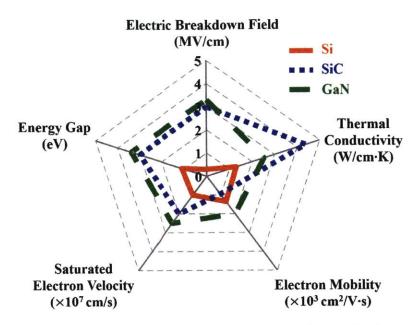

| 1-3 | (a) Band diagram of the most common Ga-face AlGaN/GaN het-               |    |

|     | erostructure; (b) Directions of spontaneous and piezoelectric polar-     |    |

|     | ization in the same structure.                                           | 27 |

| 2-1 | Comparison of contact surfaces between traditional alloyed contact and   |    |

|     | implanted refractory metal contact.                                      | 32 |

| 2-2 | Epi-structure of standard AlGaN/GaN HEMTs                                | 34 |

| 2-3 | 2DEG density and mobility versus activation annealing condition for      |    |

|     | GaN-on-sapphire samples.                                                 | 36 |

| 2-4 | 2DEG density and mobility versus activation annealing condition for      |    |

|     | GaN-on-Si samples                                                        | 37 |

| 2-5 | (Left) Cracks on the sample surface caused by large CTE difference;      |    |

|     | (Right) Microcracks of $SiO_2$ after activation annealing                | 37 |

| 2-6 | Pseudo-process flow.                                                     | 38 |

| 2-7 | TLM and Hall patterns with different implantation schemes: (1) No        |    |

|     | implantation, used as a reference; (2) All implanted (including both     |    |

|     | ohmic and channel region); (3) Selective implantation in the ohmic       |    |

|     | region                                                                   | 39 |

| 2-8 | Doping profiles simulated by SRIM                                        | 40 |

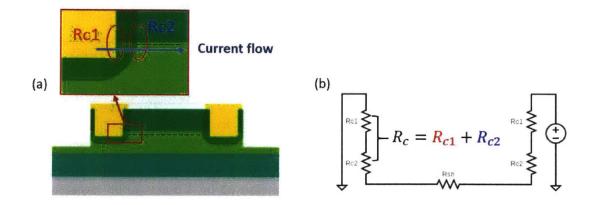

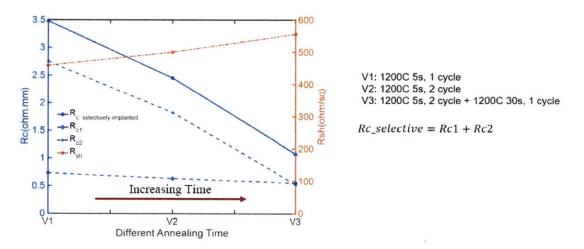

| 2-9 (a) Cross-section of selectively implanted contacts; (b) Circuit schematic.                         |    |

|---------------------------------------------------------------------------------------------------------|----|

| $R_{c1}$ is the contact resistance in the metal/semiconductor surface, while                            |    |

| $R_{c2}$ is the access resistance in the transition region from the implanted                           |    |

| region to the 2DEG channel                                                                              | 42 |

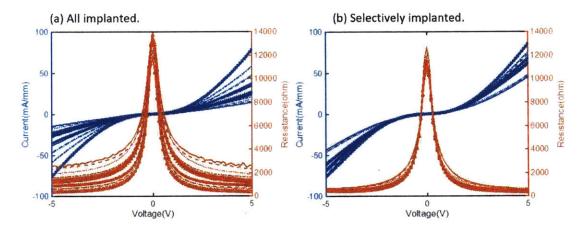

| 2-10 (a) TLM IV curves with the distance ranging from 2 to 42 um for                                    |    |

| sample #1 all implanted at 30 keV with a dose of $1^{14} cm^{-2}$ ; (b) Same                            |    |

| parameters as (a), but sample was selectively implanted. $\ldots$ $\ldots$                              | 43 |

| 2-11 (a) TLM IV curves with the distance ranging from 2 to 42 um for                                    |    |

| sample #4 all implanted at 60 keV with a dose of $1^{14} cm^{-2}$ ; (b) Same                            |    |

| parameters as (a), but sample was selectively implanted. $\ldots$ .                                     | 44 |

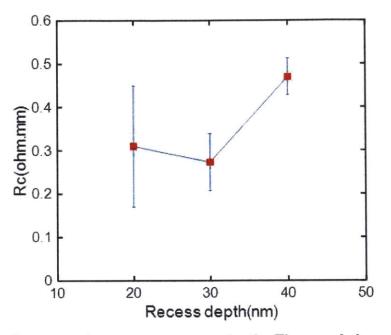

| 2-12 Contact resistance versus recess depth. The sample here was implanted                              |    |

| at 60 keV with a dose of $2 \times 10^{15} \ cm^{-2}$                                                   | 45 |

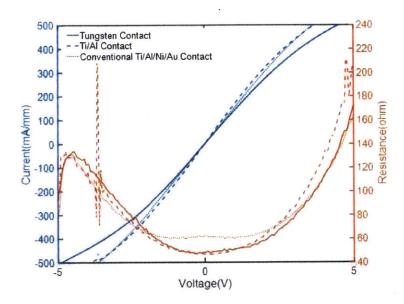

| 2-13 IV curve of a TLM pattern with a distance of 4 um from Tungsten                                    |    |

| contact, non-alloyed Ti/Al contact and alloyed Ti/Al/Ni/Au contact,                                     |    |

| respectively.                                                                                           | 45 |

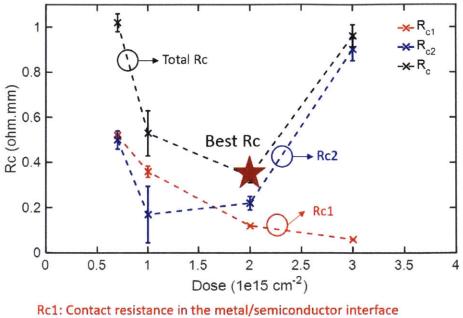

| 2-14 $R_c$ , $R_{c1}$ and $R_{c2}$ versus dose.                                                         | 47 |

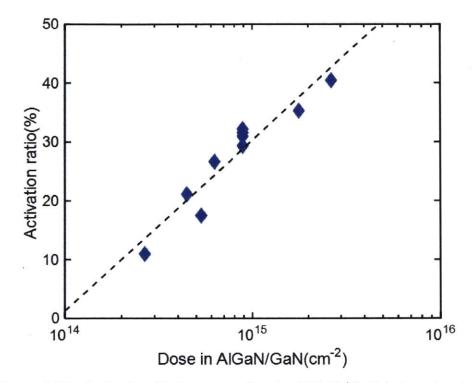

| 2-15 Activation Ratio versus dose in AlGaN/GaN heterostructure                                          | 48 |

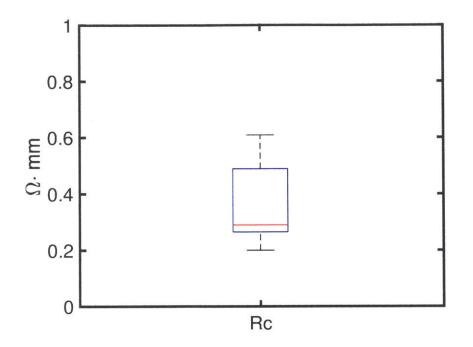

| 2-16 Contact resistance of sample $\#11$ which is implanted at 60 keV with a                            |    |

| dose of $2 \times 10^{15} \ cm^{-2}$ and annealed at 1200°C for 30 s                                    | 49 |

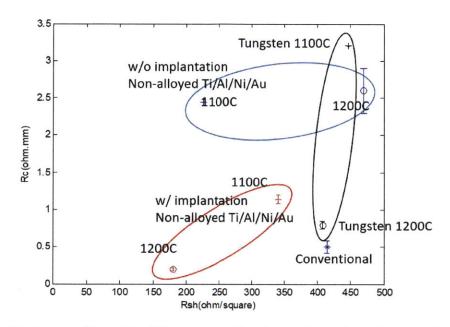

| 2-17 $R_c$ v.s. $R_{sh}$ with different combinations of metals and activation an-                       |    |

| nealing conditions. The contact activated at $1200^{\circ}\text{C}$ shows much better                   |    |

| performance. It is worth noting that only samples with tungsten con-                                    |    |

| tacts were selectively implanted, while the samples with non-alloyed                                    |    |

| $\mathrm{Ti}/\mathrm{Al}/\mathrm{Ni}/\mathrm{Au}$ contacts were all-implanted which means that the mea- |    |

| sured contact resistance is $R_{c1}$ in this case                                                       | 50 |

| 2-18 $R_c$ and $R_{sh}$ versus annealing condition.                                                     | 50 |

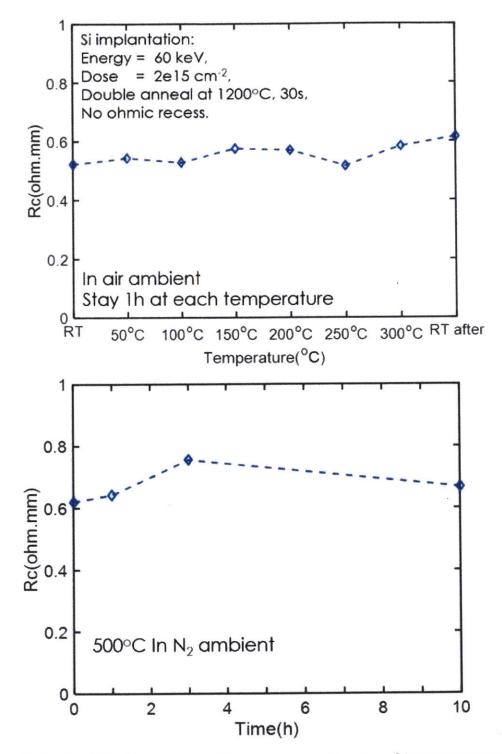

| 2-19 (top) In-situ contact resistance measured in air ambient versus tem-                               |    |

| perature. (bottom) ex-situ contact resistance measured in $N_2$ ambient                                 |    |

| versus time stayed at 500°C.                                                                            | 53 |

-

10

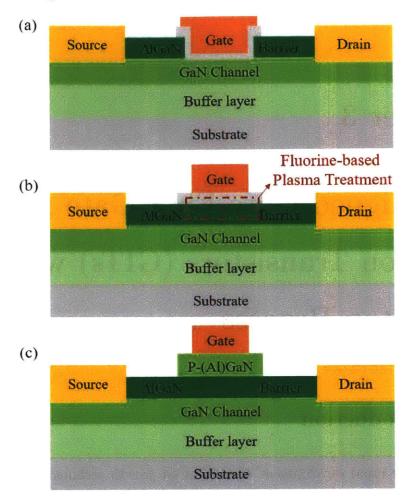

| 3-1  | (a) Cross-section of MISHEMTs. Gate recess depths might vary from                                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | a partial removal of AlGaN to a full removal of AlGaN with partial                                                                                          |    |

|      | removal of GaN underneath. (b) Cross-section of fluorine implanted                                                                                          |    |

|      | HEMTs. Fluorine-based plasma treatment can also etch part of AlGaN                                                                                          |    |

|      | depending on the etching process. Insulation layer is not required. (c)                                                                                     |    |

|      | Cross section of GITs. The top layer could be p-doped AlGaN or GaN.                                                                                         | 56 |

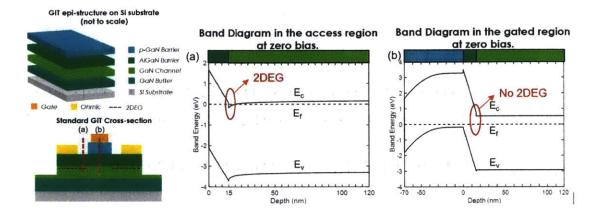

| 3-2  | Schematic of GITs wafer structure and cross section of GITs; Band                                                                                           |    |

|      | diagram at (a) access and (b) gated region                                                                                                                  | 58 |

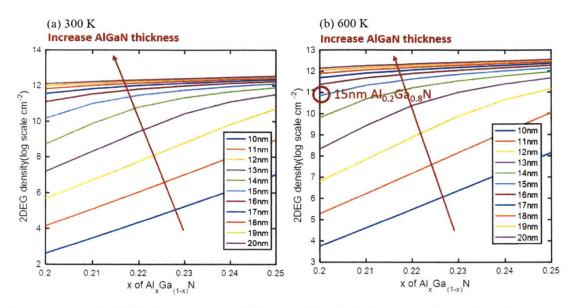

| 3-3  | (a) 2DEG density with different AlGaN thickness and mole fraction                                                                                           |    |

|      | under 300 K with 110 nm p-GaN cap; (b) 2DEG density with different                                                                                          |    |

|      | AlGaN thickness and mole fraction under 600 K with 110 nm p-GaN                                                                                             |    |

|      | cap                                                                                                                                                         | 59 |

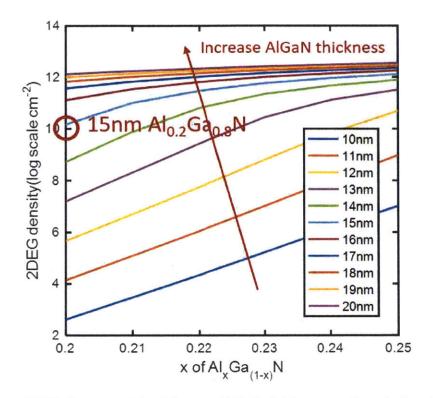

| 3-4  | 2DEG density with different AlGaN thickness and mole fraction under                                                                                         |    |

|      | 600 K with 70 nm p-GaN cap                                                                                                                                  | 60 |

| 3-5  | Schematic of the etch-stop technique.                                                                                                                       | 61 |

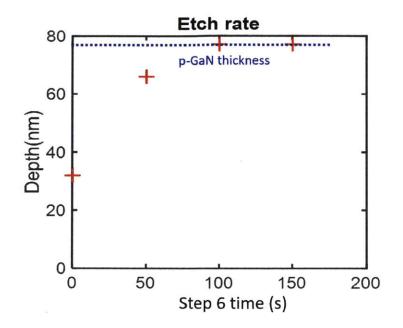

| 3-6  | Etching depth versus time in step 6                                                                                                                         | 62 |

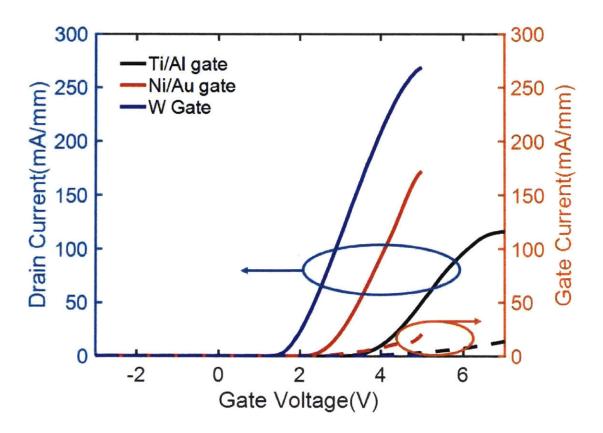

| 3-7  | Transfer characteristics of GITs with Ti/Al, Ni/Au and W gate                                                                                               | 64 |

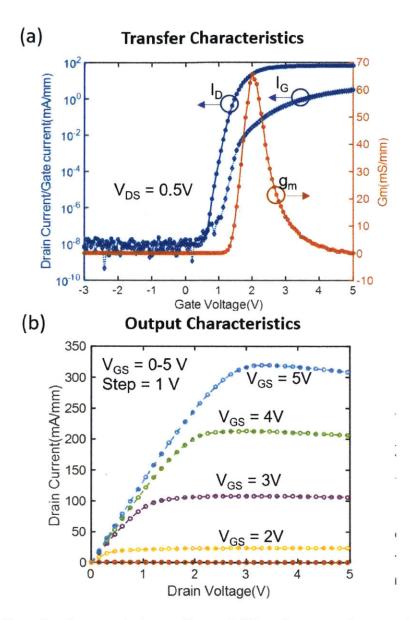

| 3-8  | Transfer characteristics at $V_{DS} = 0.5V$ and output characteristics at                                                                                   |    |

|      | $V_{GS}$ from 0 V - 5 V with step = 1 V at room temperature. $L_G$ =                                                                                        |    |

|      | $L_{GD} = L_{GS} = 2 \ \mu m. \qquad \dots \qquad $ | 66 |

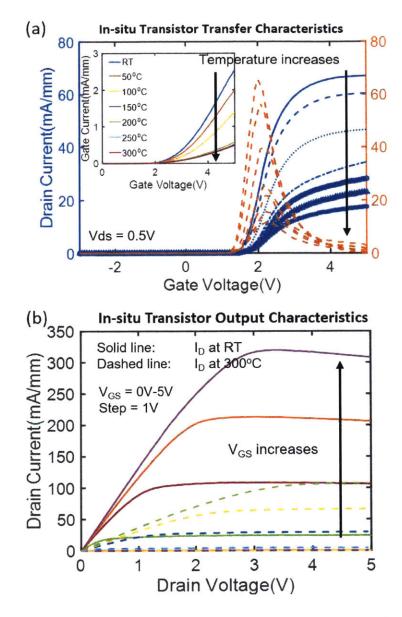

| 3-9  | (a) Transfer characteristics at $V_{DS} = 0.5V$ and output characteristics                                                                                  |    |

|      | at (b) $V_{GS}$ ranging from 0 V - 5 V with step = 1 V at room temperature                                                                                  |    |

|      | to 300°C. $L_G = L_{GD} = L_{GS} = 2 \ \mu m.$                                                                                                              | 67 |

| 3-10 | (a) Transfer characteristics at $V_{DS} = 0.5V$ and (b) output characteris-                                                                                 |    |

|      | tics at $V_{GS}$ ranging from 0 V - 5 V with step = 1 V at room temperature                                                                                 |    |

|      | to 300°C. $L_G = L_{GD} = L_{GS} = 2 \ \mu m$                                                                                                               | 68 |

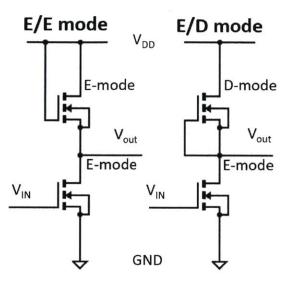

| 4-1  | Circuit diagram of E/E-mode and E/D-mode inverter. $\ldots$                                                                                                 | 70 |

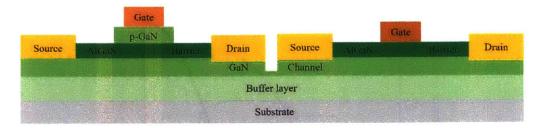

| 4-2  | Cross section of monolithically integrated $E/D$ mode GaN HETMs.                                                                                            | 71 |

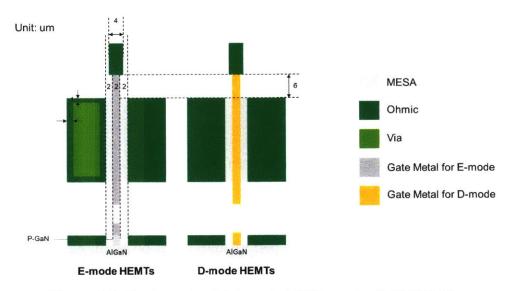

| 4-3  | Design rule of integrated E/D mode GaN HEMTs                                                                                                                |    |

| 4-0  | Design rule of integrated D/D mode Galv mbm 18                                                                                                              | 71 |

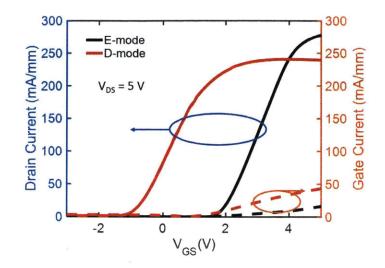

| 4 | <b>-</b> 4 | Transfer characteristics of monolithically integrated $E/D$ mode GaN                                                 |    |

|---|------------|----------------------------------------------------------------------------------------------------------------------|----|

|   |            | HETMs with $L_g = L_{gs} = L_{gs} = 2 \ \mu m$ at $V_{DS} = 5 \ \text{V.} \dots \dots \dots$                         | 72 |

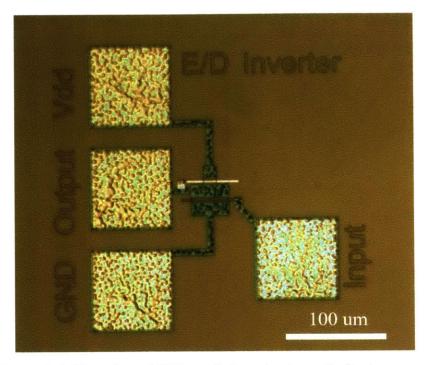

| 4 | -5         | Top view of $E/D$ -mode inverter in optical microscope                                                               | 73 |

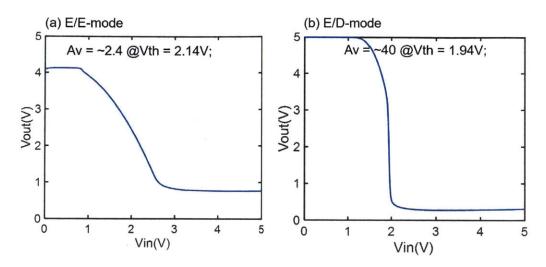

| 4 | -6         | Voltage transfer curve of both $\mathrm{E}/\mathrm{E}\text{-mode}$ and $\mathrm{E}/\mathrm{D}\text{-mode}$ inverters | 74 |

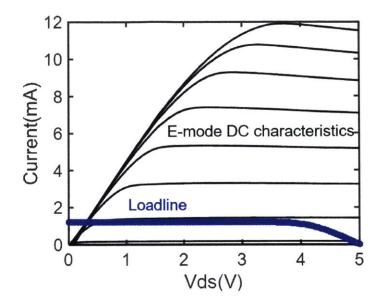

| 4 | -7         | Measured output characteristics and load line of $E/D$ -mode inverter                                                |    |

|   |            | with $W_E=36~\mu m$ and $W_D=12~\mu m$                                                                               | 75 |

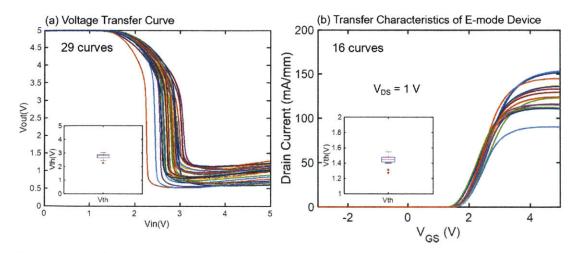

| 4 | -8         | (a) Different voltage transfer curves on one piece at room temperature;                                              |    |

|   |            | (b) Different transfer characteristics on one piece at room temperature.                                             | 76 |

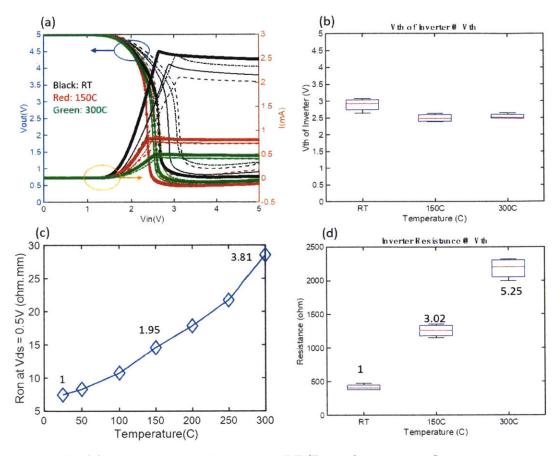

| 4 | -9         | (a) 4 voltage transfer curves of $E/D$ -mode inverters from room temper-                                             |    |

|   |            | ature to 300°C with $I_{DD}$ plotted on the right side; (b) $V_{TH}$ of VTCs in                                      |    |

|   |            | (a) from room temperature to 300°C; (c) On-resistance of E-mode tran-                                                |    |

|   |            | sistor from RT to 300°C; (d) Inverter resistance $\left(\frac{V_{DD}}{I_{DD,max}}\right)$ from room                  |    |

|   |            | temperature to 300°C.                                                                                                | 77 |

| 4 | -10        | Transient characteristics of the $E/D$ mode inverter with a 10 kHz                                                   |    |

|   |            | square wave input.                                                                                                   | 78 |

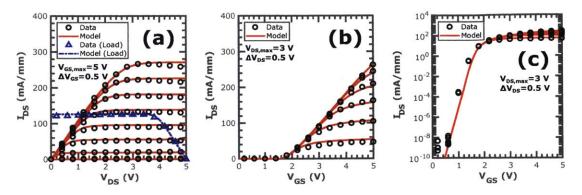

| 4 | -11        | (a) Output characteristics of the E-mode transistor and load lines of                                                |    |

|   |            | the D-mode transistor based on both simulation and experimental re-                                                  |    |

|   |            | sults; (b) Simulated and measured transfer characteristics of the E-                                                 |    |

|   |            | mode transistor in linear scale; (c) Simulated and measured transfer                                                 |    |

|   |            | characteristics of the E-mode transistor in log scale                                                                | 79 |

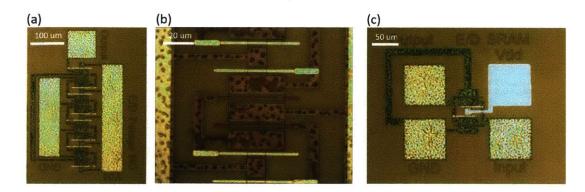

| 4 | -12        | (a) Top view of a $E/D$ -mode 7-stage ring oscillator in optical micro-                                              |    |

|   |            | scope; (b) Zoomed-in top view of the same ring oscillator in (a); (c)                                                |    |

|   |            | Top view of SRAM in optical microscope.                                                                              | 80 |

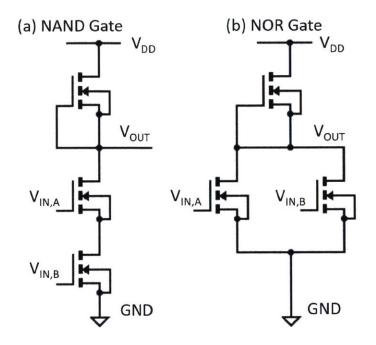

| 4 | -13        | (a) Circuit diagram of NAND gate; (b) Circuit diagram of NOR gate.                                                   | 81 |

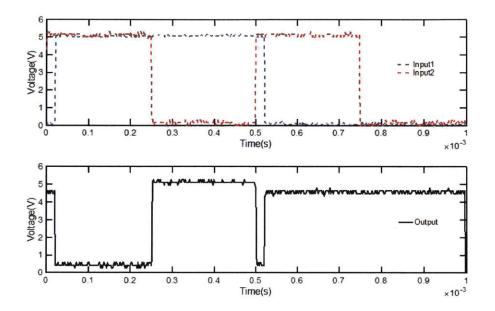

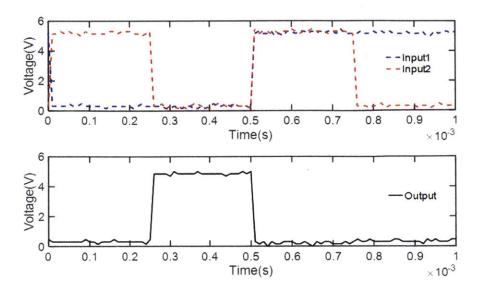

| 4 | -14        | Input and output signals of a NAND gate at room temperature                                                          | 82 |

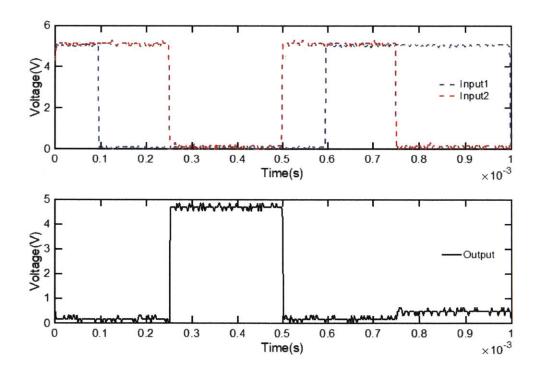

| 4 | -15        | Input and output signals of a NOR gate at room temperature                                                           | 82 |

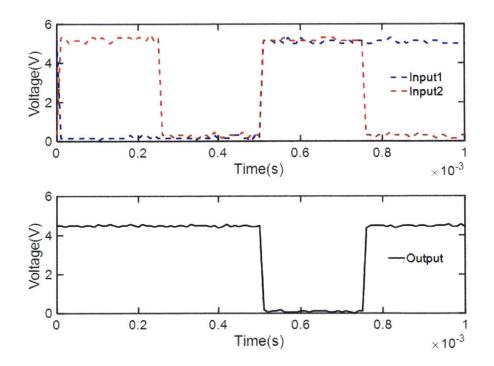

| 4 | -16        | Input and output signals of a NAND gate at 150 $^{\circ}\mathrm{C},$ where the output                                |    |

|   |            | signal is relative to the minimum output voltage.                                                                    | 83 |

| 4 | -17        | Input and output signals of a NOR gate at 150°C, where the output                                                    |    |

|   |            | signal is relative to the minimum output voltage.                                                                    | 83 |

|   |            |                                                                                                                      |    |

| 4-18 | Circuit schematic of simplified SRAM.                                                               | 84 |

|------|-----------------------------------------------------------------------------------------------------|----|

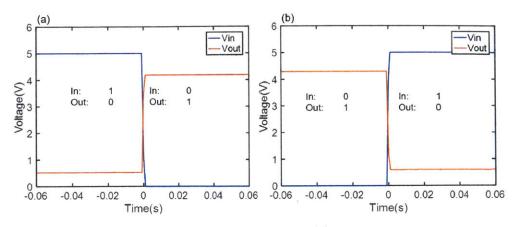

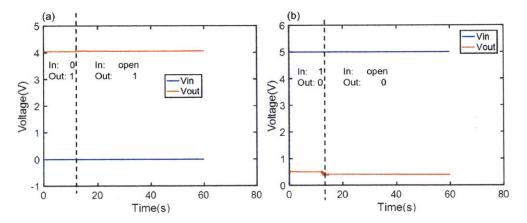

| 4-19 | Output and Input voltage of SRAM; (a) Input changes from logic state                                |    |

|      | 1 to 0; (b) Input changes from logic state 0 to 1                                                   | 85 |

| 4-20 | Output and Input voltage of SRAM; (a) Input changes from logic state                                |    |

|      | 0 to open; (b) Input changes from logic state 1 to open                                             | 85 |

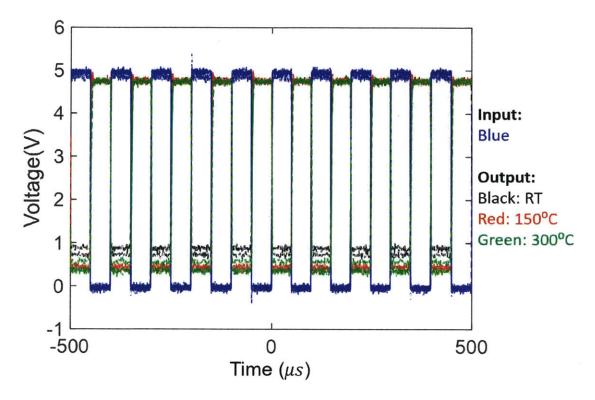

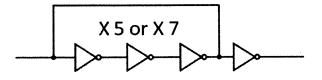

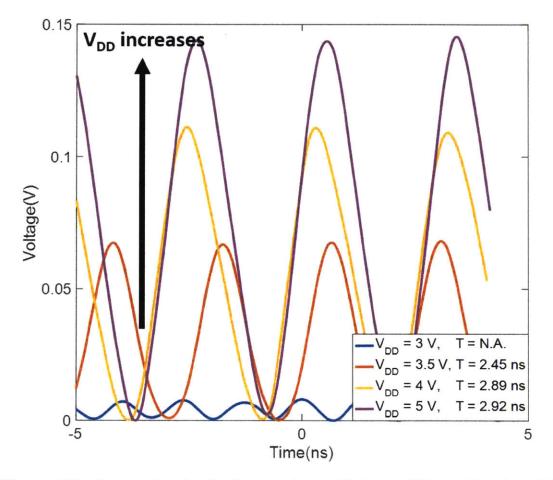

| 4-21 | Circuit schematics of 5- and 7-stage ring oscillators                                               | 87 |

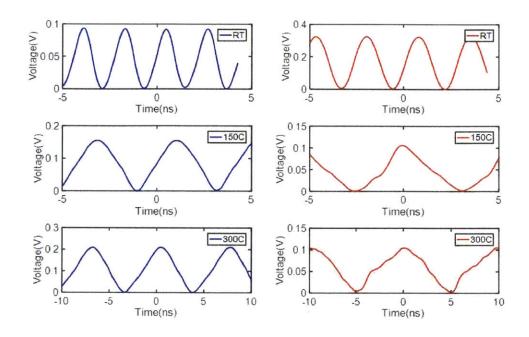

| 4-22 | Output signals of 5- and 7-stage ring oscillators from room temperature                             |    |

|      | to 300°C. It is worth noting that voltages are relative to the minimum                              |    |

|      | output voltage.                                                                                     | 88 |

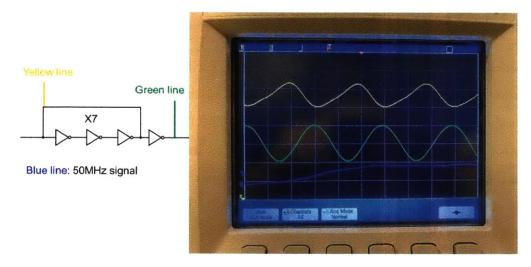

| 4-23 | Output signals measured at different locations of a 7-stage ring oscillator.                        | 88 |

| 4-24 | Output signals of a 7-stage ring oscillator at different bias from 3 V,                             |    |

|      | $3.5~\mathrm{V},~4~\mathrm{V},~5~\mathrm{V}.$ It is worth noting that voltages here are relative to |    |

|      | the minimum measured voltage                                                                        | 90 |

14

.

.

# List of Tables

| 1.1 | Spontaneous and piezoelectric parameters of AlN and GaN [1]  | 26 |

|-----|--------------------------------------------------------------|----|

| 2.1 | Different activation annealing conditions.                   | 36 |

| 2.2 | Ion implantation parameters of samples in the $1^{st}$ batch | 40 |

| 2.3 | Ion implantation parameters of samples in the $2^{nd}$ batch | 41 |

| 2.4 | Ion implantation parameters of samples in the $3^{rd}$ batch | 41 |

| 2.5 | $R_c$ of samples in the 1 <sup>st</sup> batch                | 44 |

| 3.1 | Parameters for the etch-stop process.                        | 61 |

| 4.1 | Table of inputs and outputs of NAND/NOR                      | 81 |

.

### Chapter 1

### Introduction

In the past few decades, there have been increasing demands for microelectronics working reliably in the harsh environment, including extremely high temperature over 300°C on a large variety of applications, such as automotive, aerospace, petroleum, geothermal industry and other industrial systems. Conventional semiconductors such as Silicon (Si) and Gallium Arsenide (GaAs) are physically limited by their bandgaps and show limitations in high-temperature operation.

Traditionally, for operating electronics above specified temperature range, additional thermal management approaches, including either active or passive cooling systems, are required to maintain the normal operation. Extra cost, complexity, unwanted size, weight, noise, and lower reliability [2, 3] introduced by these cooling approaches become major obstacles for high-temperature applications. Devices capable of high-temperature operations without external cooling are desirable to reduce the cost and improve system reliability.

### **1.1** Applications of High-Temperature Electronics

High-temperature electronics are commonly required in applications where the high ambient temperature is present, and self-heating effects may also be taken into account for systems with high power dissipation and dense packaging.

The underhood temperature of traditional automotive could easily reach 140 °C

either on the engine or in the transmission [4, 5]. The integration of power electronics with electric motors will increase the operating temperature above 200 °C. With the proliferation of hybrid, fuel cell, and fully electric automobiles, it also drives incremental demand for higher temperature electronics.

Similar to the automotive industry, high-temperature electronics are also critical in aerospace. It is desirable to put the monitor and control section close to the jet engine in order to reduce the complexity of interconnections [6] with the ambient temperature above 225°C, and to improve the system efficiency and reliability. Besides, space exploration brings more challenging goals such as Venus exploration with the surface temperature above 465°C [7].

Deep oil/gas extraction is one of the most traditional applications of high-temperature electronics. The operating temperature of electronics used to in-situ monitor or control drilling operation will increase with the underground depth of well and could exceed 200°C for deep wells with high pressure involved. In such applications, cooling systems are usually not efficient and quite complex, and therefore it is quite challenging to ensure the system reliability, considering the high cost of potential failure. With high-temperature electronics, it is feasible to drill deeper and avoid redundant cooling systems.

Geothermal energy, as one of the renewable energy resources, has been widely used around the world. It was reported in 2015 that the amount of energy used was 587,786 TJ/year, with an annual growth rate of 6.8% [8]. The critical point of water occurs at 374°C and 22.2mPa, while the critical point of seawater is even higher at 407°C and 29.8mPa with salt dissolved [9]. An Iceland Deep Drilling Project (IDDP) study showed that a geothermal well producing supercritical fluid with a temperature over 400°C would have one order of magnitude higher power-producing potential than a conventional geothermal well producing steam [10]. With the help of high-temperature electronics, it is possible to access hotter and deeper geothermal resources and further improve the power output of the existing geothermal fields.

### **1.2** Challenges of High-Temperature Electronics

Commercially available electronics based on SOI technology are limited to 200-250 °C maximum [6]. At extremely high temperature above 300 °C, several fundamental limitations of traditional semiconductors should be taken into concerns, which make Si-based device operation inherently impossible. Those limiting factors are well summarized by several review papers [2, 3, 6] in the past few decades and will be briefly illustrated below.

#### **1.2.1** Increasing Intrinsic Carrier Density with Temperature

One of the most dominant physical limitations for high-temperature operation is the increasing number of thermal electron and hole carriers, also as known as intrinsic carriers in the semiconductor crystal. Free electron and hole carriers introduced by intentionally doping impurities into designed regions is the fundamental of traditional semiconductor devices operation. Typically, the concentration of free electrons or holes is roughly equal to the dopant concentration due to small ionization energies with trap assistance and high activation ratios at room temperature. Depending on the specific structure and design, the doping level might vary between  $10^{13}$  cm<sup>-3</sup> to  $10^{18}$  cm<sup>-3</sup>. When the temperature increases, the concentration of intrinsic carriers  $(n_i \text{ in } cm^{-3})$  also increases exponentially [11],

$$n_i = \sqrt{N_c N_v} exp\left(-\frac{E_G}{2kT}\right) \tag{1.1}$$

where T is the temperature in Kelvin, k is the Boltzmann constant  $(8.62 \times 10^{-5} eV/K)$ ,  $E_G$  is the energy bandgap in eV,  $N_C$  and  $N_V$  are, respectively, effective density of states of the conduction/valence band in  $cm^{-3}$  and they both have a weaker temperature dependence [11],

$$N_C = 2 \left(\frac{2\pi m_{de}^* kT}{h^2}\right)^{3/2}$$

(1.2)

$$N_V = 2 \left(\frac{2\pi m_{dh}^* kT}{h^2}\right)^{3/2}$$

(1.3)

where h is the Planck constant  $(4.14 \times 10^{-15} eV \cdot s)$ ,  $m_{de}^*$  and  $m_{dh}^*$  are the density of state effective mass for electrons and holes in  $eV \cdot s^2/cm^2$ . Notice that, both  $m_{de}^*$  and  $m_{dh}^*$  are not quite constant in temperature but much less dominant because  $N_C$  and  $N_V$  don't exactly follow  $T^{3/2}$ .

In summary, the temperature dependence of intrinsic carrier concentrations could be simplified in terms of Eq. 1.1. Intrinsic carrier concentrations from different materials are shown in Fig. 1-1. For standard Si devices working at room temperature, the  $n_i$  around  $10^{10}cm^{-3}$  is negligible compared to the doping levels mentioned above. When the temperature increases well beyond 300°C, the device will gradually move to the intrinsic region where intrinsic carriers become dominant, and show an undesirable influence on lightly-doped regions. Wide bandgap materials have much lower intrinsic carrier concentrations with much wider bandgaps (> 3eV) compared to the bandgap of silicon (1.1eV), as seen from Fig. 1-1.

#### 1.2.2 Increasing Junction Leakage with Temperature

As a consequence of low energy bandgap and high intrinsic carrier concentration, the increase of junction leakage currents of traditional semiconductors will further degrade device performance. Almost all the devices have junctions like PN junctions or Schottky junctions. They strongly rely on the rectifying property of junctions, which is conducting current at forward bias and blocking current at reverse bias, for regular operation. For example, for power diodes or power transistors in buck/boost converters, low leakage currents are required at a high reverse bias to achieve designed performance and improve power efficiency. The ideal current-voltage (I-V) characteristics of the most common p-n diode structure with a "long" diode assumption can be

Figure 1-1: Semiconductor intrinsic carrier concentration  $(n_i)$  versus temperature for silicon, 6H-SiC, 4H-SiC and wurtzite GaN which has a weaker polytype dependence.

modeled approximately as [11],

$$J = (J_{es} + J_{hs}) \left[ \exp\left(\frac{qV}{kT}\right) - 1 \right]$$

(1.4)

$$=qn_i^2\left(\frac{1}{N_A}\sqrt{\frac{D_e}{\tau_e}} + \frac{1}{N_D}\sqrt{\frac{D_h}{\tau_h}}\right)\left[\exp\left(\frac{qV}{kT}\right) - 1\right]$$

(1.5)

where  $J_{es}$  and  $J_{hs}$  are, respectively, the saturation currents of electrons and holes, V is the bias voltage applied,  $N_A$  and  $N_D$  are acceptor and donor concentrations,  $D_e$  and  $\tau_e$  are diffusion coefficient and minority carrier lifetime for electrons in the p-doped region and vice versa.

With space charge generation and recombination taken into account, the upper limit of space charge region (SCR) current in the p-n diode can be computed by assuming that the maximum recombination rate applies everywhere [11],

$$J_{SCR,max} = \frac{qn_i x_{SCR}}{2\sqrt{\tau_{eo}\tau_{ho}}} \left[ \exp\left(\frac{qV}{2kT}\right) - 1 \right]$$

(1.6)

where  $x_{SCR}$  is the width of space charge region (depletion region),  $\tau_{eo}$  and  $\tau_{ho}$  are constants scaling inversely with trap concentration. And the total current of p-n diode is the sum of Eq. 1.5 and Eq. 1.6.

Other than the p-n junction, another junction structure is the metal-semiconductor junction, also known as the Schottky junction. A Schottky diode is a majority-carrier device as opposed to the p-n diode driven by minority carrier injection. The I-V characteristics could be described by a thermal emission model in which the current is limited by the electron emission process over the tip of the energy barrier at metalsemiconductor interface [11],

$$J = A^* T^2 \exp\left(\frac{-q\varphi_B}{kT}\right) \left[\exp\left(\frac{qV}{kT}\right) - 1\right]$$

(1.7)

where  $A^*$  is Richardson constant,  $\varphi_B$  is the effective barrier height between metal and semiconductor.

From Eq. 1.5-1.6, we see a strong relationship between reverse saturation current and intrinsic carrier concentration  $n_i$ , which means that the leakage current will increase exponentially with temperature and greatly influence the normal operation of devices with such structure. From Eq. 1.7, we know the leakage current could be kept relatively low by increasing junction barrier height, which is more feasible with wide bandgap materials. Again, with wider bandgaps and lower intrinsic carrier concentrations, wide bandgap materials are considered to be more potential candidates capable of high-temperature operation over 300°C.

#### 1.2.3 Decreasing Carrier Mobility with Temperature

Sheet resistance is one of the dominant components of device on-resistance and scales inversely with the carrier mobility in most of the cases. For a non-zero temperature, the atoms in the lattice of a semiconductor vibrate around their equilibrium positions. The vibration is usually quantized as a phonon (an acoustic phonon or an optical phonon) to simplify the energy-exchange process between lattice and electrons. The interaction between phonons and electrons is known as phonon (lattice) scattering. At higher temperature, phonon scattering is the dominant scattering mechanism over ionized impurity scattering, which dominates at low temperature. When the temperature increases, the phonon scattering tends to increase with more phonons generated, leading to lower mobilities for both traditional semiconductors and wide bandgap materials [12, 13, 14].

#### 1.2.4 Other Issues

In the previous section, several physical limitations on device operation have been discussed. However, the development of high-temperature electronics is not only a problem at the device level which could be solved right away by choosing proper materials and structures, but a system problem involving growth, fabrication, packaging techniques, device models of a wide temperature range for circuit design, and reliability evaluation.

## 1.3 Wide Bandgap Materials for High-Temperature Applications

As discussed above, wide bandgap materials show fundamental advantages over standard semiconductors such as Si and GaAs for high-temperature operation. Silicon Carbide (SiC), III-nitride (III-N), Gallium Oxide ( $Ga_2O_3$ ), Diamond are the most common wide bandgap materials [2, 3, 6, 15, 16, 17] and properties of SiC and GaN compared to that of Si are shown in Fig. 1-2 [18, 19]. Due to the difficulty in crystal growth, low material quality, lack of process technology, and difficulty in making p-channel devices,  $Ga_2O_3$ - and Diamond-based devices are not considered to be ideal candidates for high-temperature operation in the near future. Here the discussion will be mainly focused on the comparison between SiC and Gallium Nitride (GaN) regarding materials properties, growth technology, process technology.

In the past few decades, SiC was considered to be a superior choice and has been intensively studied not only because SiC has a slightly better thermal conductivity which drops quickly with temperature, but also relying on better technological infrastructure and maturity together with the possibility for vertical power devices. SiC is known to have great wafer quality such as very low micropipe density [20], which is good for device operation and to improve the yield for both large area and vertical devices. 4-inch SiC wafers have been commercialized more than a decade, and 6-inch SiC wafers are now also available in the market, while 8-inch SiC wafers might not happen shortly. There are currently several kinds of SiC diodes and switches available [21, 22], including SiC Schottky diode, junction barrier Schottky (JBS) diode, PIN diode, JFET and MOSFET. A commercialized SiC MOSFET with operating temperature up to 200°C was demonstrated by General Electric (GE) [23] in 2014. Besides, stable operation of 6H-SiC JFETs and ICs at 500°C up to 3000 h in air ambient was reported by NASA Glenn Research Center [24] in 2008.

Meanwhile, Gallium Nitride is first known as a wide bandgap material for high brightness blue light-emitting diode (LED). Due to its high critical electric field, it then becomes a promising candidate for electrical devices as well. As shown in Fig. 1-2, even both SiC and GaN show better performance than Si, GaN still has a higher breakdown electrical field than SiC. Besides, the polarization nature of GaN [18] enables the invention of AlGaN/GaN high electron mobility transistors (HEMTs) by forming a high-quality two-dimensional electron gas (2DEG) in the heterojunctions.

Most common AlGaN/GaN HEMTs are grown in the Ga-face with the wurtzite crystal structure, which is inherently asymmetrical. The intrinsic asymmetry of wurtzite lattice and difference of spontaneous polarization between AlGaN and GaN lead to a net spontaneous polarization charge in the AlGaN/GaN interface, as shown

Figure 1-2: Materials properties of Si, SiC and GaN.

in Fig. 1-3. Besides, AlN is known to have a smaller lattice constant than GaN and the same for AlGaN, which could be approximated by linear interpolation between lattice constants of AlN and GaN. Thus, the AlGaN layer grown on the GaN channel is typically under tensile stress, and a piezoelectric polarization charge is then induced by such mechanical stress inside the AlGaN layer, while there is no piezoelectric polarization present from the relaxed GaN channel due to the lack of strain. The piezoelectric polarization induced by tensile stress in AlGaN is parallel to the spontaneous polarization, which means that both of them have negative signs along the axis [0001], as shown in Fig. 1-3. The net charge in the interface is then the sum of charges induced by both spontaneous polarizations from AlGaN and GaN and piezoelectric polarization from AlGaN[1],

$$\sigma = \left(P_{SP,GaN} - P_{SP,Al_xGa_{(1-x)}N}\right) - P_{PZ,Al_xGa_{(1-x)}N}$$

(1.8)

where  $\sigma$  is the net polarization charge in the interface, x is the Al composition,  $P_{SP}$ and  $P_{PZ}$  are spontaneous and piezoelectric polarization, respectively. By substituting the parameters in the table 1.1 and linear interpolation,

$$\sigma = \left(P_{SP,GaN} - P_{SP,Al_xGa_{(1-x)}N}\right) - P_{PZ,Al_xGa_{(1-x)}N}$$

$$(1.9)$$

$$= [P_{SP,GaN} - (1-x)P_{SP,GaN} - xP_{SP,AlN}] - 2\frac{a-a_0}{a_0}\left(e_{31} - e_{33}\frac{C_{13}}{C_{33}}\right)$$

(1.10)

$$= \left\{ 5.2x - 2\frac{0.077x}{3.189 - 0.077x} \left[ -11x - 49 - (73x + 73)\frac{5x + 103}{-32x + 405} \right] \right\} \times 10^{-6} C/cm^2$$

(1.11)

$$\approx \left[ 5.2x + \left( 3.32x + 1.65x^2 \right) \right] \times 10^{-6} C/cm^2$$

(1.12)

where  $a_0$  is the lattice constant of AlGaN in the thermal equilibrium, a is the lattice constant of the AlGaN grown on the GaN channel which is equal to the equilibrium lattice constant of GaN, in this case,  $e_{31}$  and  $e_{33}$  are piezoelectric coefficients,  $C_{13}$  and  $C_{33}$  are elastic constants. All the  $Al_xGa_{(1-x)}N$  parameters above are approximated by linear interpolation. Considering x is in the range of [0, 1], Eq. 1.11 could be simplified to Eq. 1.12 by using linear approximation (first-degree Taylor Polynomial). With an assumption of x = 0.2 in this case, the net polarization charge is positive, which means there will be the same amount of free electrons in the AlGaN/GaN interface to compensate the fixed polarization charge, and the charge density  $\frac{\sigma}{q}$  is around  $1.1 \times 10^{13} cm^{-2}$ . The unique 2DEG shows a high peak drift velocity and a high electron mobility, allowing for high voltage and low on-resistance applications.

| Parameters | $P_{SP}$              | $a_0$ | $e_{31}$             | $e_{33}$             | C <sub>13</sub> | C <sub>33</sub> |

|------------|-----------------------|-------|----------------------|----------------------|-----------------|-----------------|

|            | $[C/cm^2]$            | [Å]   | $[C/cm^2]$           | $[C/cm^2]$           | [GPa]           | [GPa]           |

| GaN        | $-2.9 \times 10^{-6}$ | 3.189 | $-49 \times 10^{-6}$ | $73 \times 10^{-6}$  | 103             | 405             |

| AlN        | $-8.1 \times 10^{-6}$ | 3.112 | $-60 \times 10^{-6}$ | $146 \times 10^{-6}$ | 108             | 373             |

Table 1.1: Spontaneous and piezoelectric parameters of AlN and GaN [1].

GaN is mostly grown on SiC, sapphire, and silicon substrates. Among all those possible substrate materials, Si is the most attractive choice due to its large wafer diameter (8-inch and beyond) and lower cost compared to other candidates. However, due to the large mismatches in lattice constants and coefficients of thermal expansion

Figure 1-3: (a) Band diagram of the most common Ga-face AlGaN/GaN heterostructure; (b) Directions of spontaneous and piezoelectric polarization in the same structure.

(CTE) between GaN and Si (111) substrate, it is quite challenging to grow highquality GaN buffers on large Si substrates. 650V GaN-on-Si e-mode devices in a 200 mm CMOS fab were demonstrated by IMEC in 2015 [25, 26]. Meanwhile, 750V fully vertical GaN-on-Si power diodes were reported by MIT in 2018 [27], which shows the potential and possibility of fully vertical GaN devices. Recently, p-channel GaN transistors were also successfully demonstrated with the capability of integration with n-channel e-mode GaN HEMTs on one chip [28]. Stable operation of GaN-based devices up to 1000°C was also reported [29, 30]. Given the rapid development in recent years of GaN technology in the aspects mentioned above, we need to reconsider GaN as a potential enabler in the field of high-temperature electronics.

### 1.4 Challenges of Gallium Nitride and Scope of Thesis

Despite the excellent performance shown by early high-temperature prototypes[31, 32, 29], several issues in traditional lateral AlGaN/GaN HEMTs could cause early

degradation and failure under high-temperature operation (over  $300^{\circ}C$ ). These include ohmic degradation, gate leakage, buffer leakage, and poor passivation.

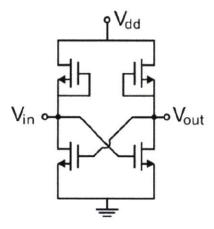

Besides, to enable digital circuit processing, it is critical to have normally-off or enhancement-mode HEMTs, while two-dimensional electron gas (2DEG) induced by AlGaN/GaN heterostructure makes HEMTs be natural depletion-mode devices. Two main approaches have been proposed to achieve the enhancement-mode behavior: recess-gate metal-insulator-semiconductor HEMTs (MISHEMTs) [33] and gate injection transistors (GITs) [34].

This thesis aims to solve the problems mentioned above, including ohmic contact reliability, e-mode operation, and large scale integration for possible high-temperature integrated circuits (ICs). A new ohmic contact scheme, GITs suitable for hightemperature operation and large scale integration, and logic building blocks for ICs will be developed and optimized. In particular, the thesis is divided into the following parts:

- Chapter 2: Study of ion-implanted tungsten contacts on HEMTs structure for high-temperature operation;

- Chapter 3: Self-aligned gate-first enhancement-mode Gate injection transistors (GITs) with the etch stop process for large scale integration and hightemperature operation;

- Chapter 4: Logic building blocks such as NAND/NOR gate performance based on transistor technology demonstrated above and high-temperature degradation test.

Chapter 2 introduces a comprehensive study conducted on the ion-implanted refractory metal contact on AlGaN/GaN HEMTs, including the high-temperature degradation of AlGaN/GaN heterostructure; the optimization of implantation condition based on the SRIM simulation results, the optimization of activation annealing condition; the influence of different metals on contact performance; ohmic recess technology to improve contact performance.

Chapter 3 presents self-aligned gate-first enhancement-mode GITs with the etchstop process. The wafer structure was first designed based on the TCAD simulation, following with a study of the etch-stop process to selectively remove p-GaN. The effects of different gate metals on threshold voltages and gate leakage currents will be discussed. Finally, the results of high-temperature measurements on the devices with those optimized processes will be shown.

In chapter 4, compact modeling for both E/D-mode HEMTs will be demonstrated based on MIT Virtual Source GaN (MVSG) model [35]. The experimental results of the fabrication and characterization of several critical logic building blocks, including inverter, NAND/NOR gate, SRAM, and ring oscillators, will be presented. A comparison between E/D-mode and E/E-mode direct-coupled FET logic (DCFL) will also be included.

## Chapter 2

# Study of the Ion-implanted Refractory Metal Contact

### 2.1 Introduction

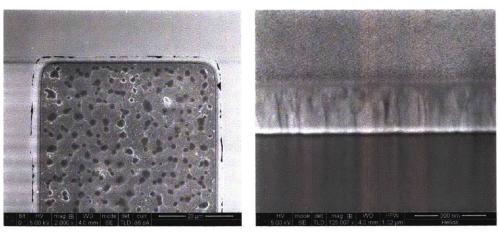

Ohmic contacts in AlGaN/GaN HEMTs are typically made of Ti/Al/(Ni, Ti, Pt, Mo, etc.)/Au metal stacks annealed around 800 °C [36] to obtain a low ohmic contact resistance around  $1 \times 10^{-6} \ \Omega \cdot cm^2$ . Although these contacts have shown excellent performance at room temperature, they are typically unstable above 250 °C, due to the diffusion of Ti, Al, and Au into the structure [37]. This metallization scheme leads to a rough surface morphology as shown in Fig. 2-1 and has been linked to degradation and failure[37, 38].

There are several potential approaches to replace the traditional alloyed contact including the ion-implanted metal contact [39, 40, 41], which locally dopes the materials n-type by implantation and reduces the contact resistance, and regrown ohmic contact, which selectively remove the AlGaN in the contact region and regrown ntype (Al)GaN [42]. Considering the negligible dopant diffusion under 600 °C in wide bandgap materials [3] and potential defects in regrown surface, ion implantation is considered to be a superior choice for high-temperature operation. Besides, benefiting from the n-doped ohmic region, a large variety of Si CMOS compatible metals could be used as contacts, and better surface morphology could be achieved as well

(a) Top view of conventional Ti/Al/Ni/Au contacts by SEM.

(b) Tilt view of ion implanted tungsten (W) contacts by FIB-SEM.

Figure 2-1: Comparison of contact surfaces between traditional alloyed contact and implanted refractory metal contact.

to improve the subsequent photo-lithography performance without post-annealing. However, unlike the ion implantation technology ubiquitously used in Si-based devices, ion implantation technology in the AlGaN/GaN heterostructure requires further optimizations in many aspects: doping profile, implantation energy, dose, dopant activation, and damage recovery.

Implantation energy, dose, and ion beam incident angle need to be carefully engineered to obtain the desired doping profile and best contact performance. Moreover, dopant activation is also a crucial step in ion implantation technology due to the inert nature of AlGaN and GaN. A successful activation annealing at 1500 °C in nitrogen was reported [39], which is well beyond the capabilities of typical Si processing tools and higher than the growth temperature of GaN by either metal-organic chemical vapor deposition (MOCVD) or molecule beam epitaxy (MBE) [43]. Besides, the massive differences in coefficients of thermal expansion (CTE) between AlGaN, GaN, and Si substrate would degrade the heterostructure integrity and reduce the 2DEG density and mobility at high annealing temperature [44]. Thus, it is preferable to have a lower annealing temperature to preserve the crystalline integrity and achieve a similar dopant activation ratio.

# 2.2 Degradation of AlGaN/GaN Heterostructure and Activation Annealing Capping Layer

In standard AlGaN/GaN HEMTs, the on-resistance mainly consists of two parts: contact resistance and channel resistance, which includes access resistance from sourceand drain-to-gate region and channel resistance at the gated region. The former could be improved by increasing the activation ratio of the implanted Si-ions usually by increasing activation annealing time and temperature, while the latter has a strong dependence on sheet resistance. The sheet resistance is proportional to the product of mobility and carrier density of 2DEG, and tends to increase after high-temperature activation annealing.

Before we start to test the effects of activation annealing conditions on dopant activation, we first need to figure out the degradation of 2DEG density and mobility caused by the activation annealing in order to keep a low sheet resistance.

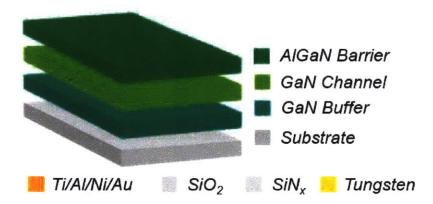

#### 2.2.1 Device Structure

The epitaxial structures investigated here were grown by metal-organic chemical vapor deposition (MOCVD) on both the sapphire substrate from Arizona State University (ASU) and the silicon substrate from Lincoln Lab (LL). The epitaxial structure of GaN-on-sapphire wafer has a 15 nm  $Al_{0.2}Ga_{0.8}N$  barrier layer, while the epi-structure of GaN-on-Si wafer has a 17 nm  $Al_{0.2}Ga_{0.8}N$  barrier layer. It is worth mentioning that wafers from LL compared with wafers from ASU has an additional AlN spacer at AlGaN/GaN interface in order to increase the mobility. Fig. 2-2 shows the epistructure of GaN-on-sapphire samples were  $8.2 \times 10^{12} \text{ cm}^{-2}$  and  $1732 \text{ cm}^2V \cdot s$  and those of GaN-on-Si samples were  $\sim 1 \times 10^{13} \text{ cm}^{-2}$  and  $\sim 2000 \text{ cm}^2V \cdot s$ , respectively.

The fabrication started with the deposition of 60 nm  $SiO_2$  by plasma-enhanced chemical vapor deposition (PECVD) at 350°C. No implantation was performed on the samples to avoid possible influence on the subsequent measurements of carrier

Figure 2-2: Epi-structure of standard AlGaN/GaN HEMTs.

density and mobility. Samples were annealed at different combinations of time and temperatures by rapid thermal annealing (RTA). After activation annealing, thermal annealed  $SiO_2$  was then removed by buffered oxide etch (BOE). The standard Ti/Al/Ni/Au (20/100/25/50 nm) metal stack was subsequently e-beam evaporated and lifted off, following with 800°C post-annealing for 30 s in  $N_2$  ambient by RTA to form ohmic contacts. ~ 140 nm mesa isolation was carried out by  $BCl_3/Cl_2$ based electron cyclotron resonance reactive-ion etching (ECR-RIE). Van der Pauw structures were made to characterize carrier density and mobility.

#### 2.2.2 Results and Discussion

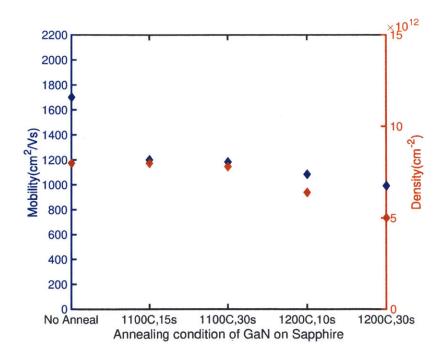

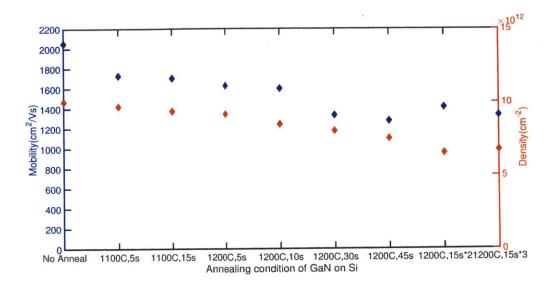

Table 2.1 shows the different activation annealing conditions for both GaN-on-sapphire and GaN-on-Si samples. Ideally, GaN-on-sapphire samples should have less built-in stress compared to GaN-on-Si samples due to the smaller difference between lattice constants of GaN and sapphire, and were annealed longer at the beginning. Besides, our main interest was focused on GaN-on-Si samples, and more activation annealing conditions were tested subsequently. Hall measurements were conducted at room temperature to characterize the 2DEG densities and mobilities of both samples, as shown in Fig. 2-3 and Fig. 2-4.

Both GaN-on-sapphire and GaN-on-Si samples show degradations of 2DEG densities and mobilities, implying damage to the lattice integrity caused by activation annealing. As expected, increasing temperature and extending annealing time would further degrade both mobility and carrier density.

Compared with GaN-on-sapphire samples, GaN-on-Si samples shows less degradation on mobility due to the AlN spacer between AlGaN and GaN, which significantly reduces the alloy disorder scattering. At room temperature or above, phonon scattering is usually the dominant scattering mechanism limiting the 2DEG mobility [12, 13, 14, 45]. However, the decrease of mobility indicates an increase in scattering mechanisms which could be explained by several reasons: increase of charged ion impurity due to the increase of vacancies and dislocations caused by nitrogen out-diffusion in the bulk, alloy and charged dislocations at the interface due to AlN interlayer degradation, more interface roughness, increase of piezoelectric scattering due to the decrease of 2DEG density. All the aspects mentioned above will permanently reduce the 2DEG mobility at room temperature. Similarly, the degradation of lattice integrity, which influences both spontaneous polarization and piezoelectric polarization, will also have a negative impact on polarization charge density.

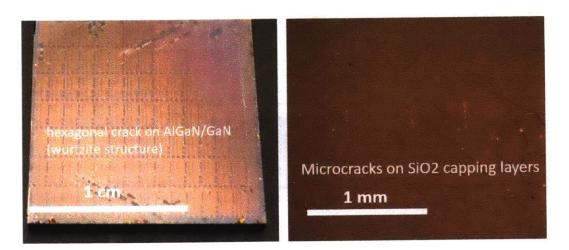

Besides, cracks were also observed on both the GaN surface and on the SiO<sub>2</sub> surface, as shown in Fig. 2-5. Microcracks were observed after activation annealing at 1200°C for 30 s. After replacing the SiO<sub>2</sub> layer with a zero stress  $SiN_x$  deposited by mixed frequency PECVD, no microcracks were observed.

Based on the results shown in Fig. 2-3 and Fig. 2-4, activation annealing at  $1200^{\circ}C$  for 30 s in  $N_2$  ambient was selected as a preferred annealing condition in the following sections. Activation annealing effect on contact performance will be discussed in the following sections.

### 2.3 Study of the Si-ion Implanted Refractory Contact

The idea of the ion-implanted ohmic contact is to n-dope the ohmic region to help electrons tunnel through the metal-semiconductor junction and form a direct electrical

| Sample          | Temperature | Time                          |

|-----------------|-------------|-------------------------------|

|                 | 1100°C      | $15 \mathrm{s}$               |

| CoN on comphine | 1100 C      | 30 s                          |

| GaN-on-sapphire | 1200°C      | 10 s                          |

|                 | 1200 C      | 30 s                          |

|                 | 1100°C      | 5 s                           |

|                 | 1100 C      | 15 s                          |

|                 |             | 5 s                           |

| GaN-on-Si       |             | 10 s                          |

| Gain-oil-Si     | 1200°C      | 30 s                          |

|                 | 1200 C      | $45 \mathrm{s}$               |

|                 |             | $15 \text{ s} \times 2^{[2]}$ |

|                 |             | $15 \text{ s} \times 3^{[3]}$ |

Table 2.1: Different activation annealing conditions<sup>[1]</sup>.

<sup>1</sup> All the activation annealings were performed in  $N_2$  ambient. <sup>2</sup> Sample was first heated up to 1200°C for 15 s, cooled down to 700°C and then heated up to 1200°C for 15 s again.

<sup>3</sup> Similar to the previous condition, sample was heated up to 1200°C for 15 s for three times.

Figure 2-3: 2DEG density and mobility versus activation annealing condition for GaN-on-sapphire samples.

Figure 2-4: 2DEG density and mobility versus activation annealing condition for GaN-on-Si samples.

Figure 2-5: (Left) Cracks on the sample surface caused by large CTE difference; (Right) Microcracks of  $SiO_2$  after activation annealing.

path to the 2DEG at the AlGaN/GaN interface. Silicon and Germanium are common n-type dopants in the GaN. In this work, silicon would be used due to its smaller atomic number, and thus lower energy is required to have a similar doping profile, while less damage is expected from Si implantation.

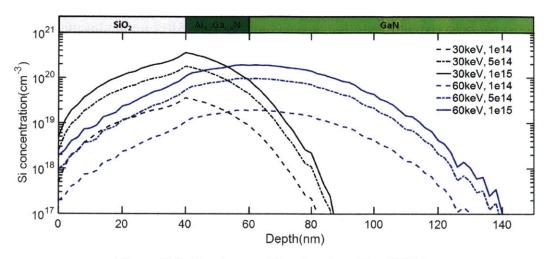

Doping profile and dopant concentration are critical to successful ion implantation, which is determined by implantation energy and dose. First, a Monte Carlo simulation was conducted to estimate the ion distribution through a software named Stopping and Range of Ions in Matter (SRIM) [46]. Single energy implantation would give us a Gaussian profile, while a box profile could be obtained with double energy implantation. Besides, to avoid ion channeling, the incident beam was tilted 7 degrees following the standard rules of implantation for Si-based devices.

### 2.3.1 Epitaxial Structure and Fabrication

The epitaxial stack used in this work was grown by MOCVD on a 6 inch Si (111) substrate. The structure from top to bottom is 2 nm GaN, 17 nm  $Al_{0.2}Ga_{0.8}N$ , GaN channel, carbon-doped GaN buffer, and Si (111) substrate. The 2DEG density and hall mobility at room temperature were ~  $1 \times 10^{13} \ cm^{-2}$  and ~ 2000  $\ cm^{2}V \cdot s$ , respectively.

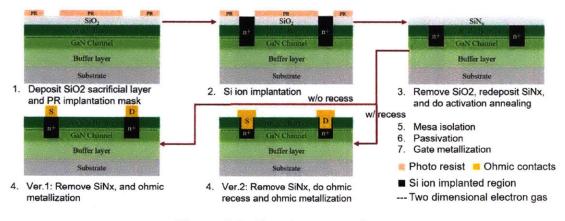

Figure 2-6: Pseudo-process flow.

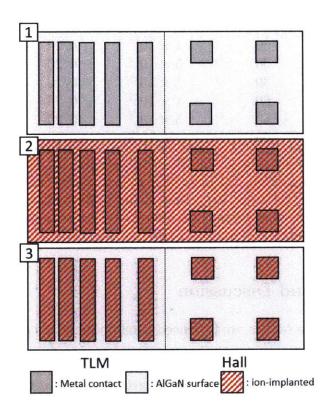

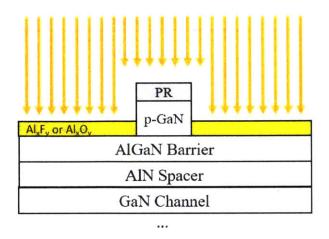

Given the pseudo-process flow shown in Fig. 2-6, the fabrication was started with 40 nm  $SiO_2$  deposition by PECVD to avoid possible contamination during implantation, and to randomize implanted ions incident angle and to adjust peak position of doping profile. Different Si-ion implantation conditions were simulated by SRIM, as listed in Tab.2.2, 2.3, and 2.4. Key simulation results are shown in Fig. 2-8. Two peak locations of doping profiles were chosen: either at the top surface or AlGaN/GaN interface. There are three implantation schemes summarized in Fig. 2-7: (1) No implantation, used as a reference; (2) All implanted (including both ohmic and channel region); (3) Selective implantation in the ohmic region. After implantation,  $SiO_2$  was removed by BOE, and 40 nm  $SiN_x$  was then deposited by PECVD on top to protect the sample surface and prevent possible nitrogen diffusion. Activation annealing was carried out at 1200°C for 30 s in  $N_2$  ambient by RTA, following with  $SiN_x$  removal by BOE. 20 nm ohmic recess was partially performed by ICP-RIE on a Si holder to test the effect of ohmic recess, which should reduce the resistance induced by the AlGaN region. The recess depth was examined by atomic force microscope (AFM). After ohmic recess, two different metal schemes were adopted: tungsten metal contacts were sputtered and dry-etched by RIE with  $SF_6/O_2$  mixture; Ti/Al metal contacts were defined by e-beam evaporation. There was no post-annealing process for both contact schemes. ~ 140 nm mesa isolation was then performed by ECR-RIE with  $BCl_3/Cl_2$ .

Figure 2-7: TLM and Hall patterns with different implantation schemes: (1) No implantation, used as a reference; (2) All implanted (including both ohmic and channel region); (3) Selective implantation in the ohmic region.

Figure 2-8: Doping profiles simulated by SRIM.

Table 2.2: Ion implantation parameters of samples in the  $1^{st}$  batch.

| Sample | $1^{st}$ -Energy | $1^{st}$ -Dose     | Recess | Contact       |

|--------|------------------|--------------------|--------|---------------|

| #      | [keV]            | $[cm^{-3}]$        | [nm]   |               |

| 1      | 30               | $1 \times 10^{14}$ | 0/20   | $Ti/Al^{[2]}$ |

| 2      | 30               | $5 \times 10^{14}$ | 0/20   | Ti/Al         |

| 3      | 30               | $1 \times 10^{15}$ | 0/20   | Ti/Al         |

| 4      | 60               | $1 \times 10^{14}$ | 0/20   | Ti/Al         |

| 5      | 60               | $5 \times 10^{14}$ | 0/20   | Ti/Al         |

| 6      | 60               | $1 \times 10^{15}$ | 0/20   | Ti/Al         |

$^1$  Implanted ion species was Si. Tilt/Twist angles were all 7/23 degrees, and implantation were all performed at room temperature. All the activation annealings were performed at 1200°C for 30 s. Same for the following batches.

$^2$  Ti/Al (20/100 nm) were defined by e-beam evaporation. No post-annealing was conducted afterward.

## 2.3.2 Results and Discussion

Before we dive into the results, we first need carefully to define the contact resistance of implanted contacts. General contact resistance is typically referred to as the total resistance from metal contact to the conductive channel. In the case of selectively implanted contact, the situation becomes complicated due to the large additional resistance between the implanted contact region and the 2DEG channel without implantation, as shown in Fig. 2-9. Contact resistance, in this case, could be divided into two components:

| Sample | $1^{st}$ -Energy | $1^{st}$ -Dose     | Recess | Contact                 |

|--------|------------------|--------------------|--------|-------------------------|

| #      | $[\mathrm{keV}]$ | $[cm^{-3}]$        | [nm]   |                         |

| 7      | 60               | $7 \times 10^{14}$ | 20     | Tungsten <sup>[1]</sup> |

| 8      | 60               | $1 \times 10^{15}$ | 20     | Tungsten or Ti/Al       |

| 9      | 60               | $2 \times 10^{15}$ | 20     | Tungsten                |

| 10     | 60               | $3 \times 10^{15}$ | 20     | Tungsten                |

Table 2.3: Ion implantation parameters of samples in the  $2^{nd}$  batch.

<sup>1</sup> 100 nm Tungsten was sputtered and dry etched. No post-annealing was performed. The Resistivity of Tungsten film is ~ 0.158  $\mu\Omega \cdot m$  measured by 4 point probe measurement. Same for the subsequent experiment.

Table 2.4: Ion implantation parameters of samples in the  $3^{rd}$  batch.

| Sample     | 1 <sup>st</sup> -Energy | $1^{st}$ -Dose       | 2 <sup>nd</sup> -Energy | $2^{nd}$ -Dose       | Recess   | Contact  |

|------------|-------------------------|----------------------|-------------------------|----------------------|----------|----------|

| #          | [keV]                   | $[cm^{-3}]$          | $[\mathrm{keV}]$        | $[cm^{-3}]$          | [nm]     |          |

| $11^{[1]}$ | 60                      | $2 \times 10^{15}$   | \                       | \                    | 20/30/40 | Tungsten |

| 12         | 60                      | $1.5 \times 10^{15}$ | 30                      | $0.5 \times 10^{15}$ | 20       | Tungsten |

<sup>1</sup> Implantation at 60 keV with a dose of  $2 \times 10^{15}$  and 20 nm ohmic recess was performed on multiple samples to test the repeatability.

$R_{c1}$ : Contact resistance in the metal/semiconductor surface.

$R_{c2}$ : Access resistance in the transition region from implanted region to 2DEG channel caused by lattice damage.

#### Method to Extract $R_c$ , $R_{c1}$ and $R_{c2}$

$R_{c1}$  can be extracted by TLM measurements from the patterns shown in Fig. 2-7 (2) with both ohmic and channel implanted. In this case, doped AlGaN/GaN serves as channel and no  $R_{c2}$  is present.  $R_c$  can be directly measured by the structure in Fig. 2-7 (3) with selectively implanted ohmic region.  $R_{c2}$  could be approximated by  $R_c - R_{c1}$ .

The goal of contact optimization is to reduce both  $R_{c1}$  and  $R_{c2}$  by choosing proper implantation and activation conditions.

Figure 2-9: (a) Cross-section of selectively implanted contacts; (b) Circuit schematic.  $R_{c1}$  is the contact resistance in the metal/semiconductor surface, while  $R_{c2}$  is the access resistance in the transition region from the implanted region to the 2DEG channel.

#### Effects of Ohmic Recess and Implantation Energy

A preliminary study of ohmic recess and implantation energy effect was conducted on batch 1 samples. The TLM IV curves without ohmic recess from sample 1, which was implanted at 30 keV with a dose of  $1 \times 10^{14} \text{ cm}^{-2}$ , are shown in Fig. 2-10. Schottky behaviors can be observed, indicating that the dose and activation ratio are not high enough to help electrons tunneling through the Schottky barrier in the metal/semiconductor interface and form a good ohmic contact. As expected, similar behaviors can also be observed from Fig. 2-11 for sample 4 implanted at 60 keV with a dose of  $1 \times 10^{14} \text{ cm}^{-2}$  and no ohmic recess involved, which proves our assumption.

Compared with sample 1, sample 4 shows a higher contact resistance, which means that without ohmic recess, shallower implantation (30 keV) would help reduce ohmic contact due to higher doping concentration close to the interface with the same dose.

The results from sample 2-3 and 5-6 in Tab. 2.5 indicate that a better contact performance can be obtained by implantation at 60 keV and ohmic recess. Ohmic recess will remove the AlGaN barrier, which has a higher resistivity and bandgap, and form a direct contact to the GaN underneath where the peak doping concentration is located. It is worth noting that the contact resistance of standard alloyed Ti/Al/Ni/Au is ~ 0.5  $\Omega \cdot mm$  [39].

Besides, a further study was conducted on sample #11 about the contact resistance dependence on recess depth. A low  $R_c$  of ~ 0.3  $\Omega \cdot mm$  was obtained when the sample was implanted at 60 keV with a dose of  $2 \times 10^{15} \ cm^{-2}$  and a recess depth of 20 nm. As can be seen in Fig. 2-12, similar  $R_c$  can be achieved with different recess depths. A small increase of  $R_c$  can be observed with a recess depth of 40 nm. The results indicate that the ohmic recess technique demonstrated here has a high tolerance for recess depth with the help of ion implantation.

In summary, for single energy implantation, the optimum implanted contact scheme is to set the peak of the doping profile close to the AlGaN/GaN interface, and perform ohmic recess. In this case, Si implantation at energy of 60 keV and 20 nm recess is preferred, and there is no strict requirement on ohmic recess depth, which could range from 20 nm to 40 nm.

Figure 2-10: (a) TLM IV curves with the distance ranging from 2 to 42 um for sample #1 all implanted at 30 keV with a dose of  $1^{14} \ cm^{-2}$ ; (b) Same parameters as (a), but sample was selectively implanted.

#### Effects of Different Ohmic Metals

Alloyed Ti/Al/Ni/Au is the most common contact scheme in AlGaN/Gan HEMTs with several disadvantages, such as bad surface morphology, requirements of a specific metal stack, and post-annealing. It is appealing to use Si CMOS compatible metals as contacts. With the help of a highly doped ohmic region, many metals become

Figure 2-11: (a) TLM IV curves with the distance ranging from 2 to 42 um for sample #4 all implanted at 60 keV with a dose of  $1^{14} \text{ cm}^{-2}$ ; (b) Same parameters as (a), but sample was selectively implanted.

| Sample | $1^{st}$ -Energy | $1^{st}$ -Dose     | Recess | Contact  | $R_c$               |

|--------|------------------|--------------------|--------|----------|---------------------|

| #      | [keV]            | $[cm^{-3}]$        | [nm]   |          | $[\Omega \cdot mm]$ |

| 2      | 30               | $5 \times 10^{14}$ | 0      | Schottky | 3.83                |

|        | 50               | $0 \times 10$      | 20     | Ohmic    | 1.84                |

| 3      | 30               | $1 \times 10^{15}$ | 0      | Ohmic    | 2.56                |

|        | 50               | 1 × 10             | 20     | Ohmic    | 2.05                |

| 5      | 60               | $5 \times 10^{14}$ | 0      | Schottky | 4.45                |

|        |                  |                    | 20     | Ohmic    | 1.68                |

| 6      | 60               | $1 \times 10^{15}$ | 0      | Schottky | 2.67                |

|        |                  | 1 × 10             | 20     | Ohmic    | 0.65                |

Table 2.5:  $R_c$  of samples in the 1<sup>st</sup> batch.

available, and tungsten, also known as a kind of refractory metal, was chosen here for high-temperature applications.

Sample # 8 was designed to compare the difference of  $R_c$  between non-alloyed Ti/Al and tungsten contacts. It can be observed from Fig. 2-13 that all three contact schemes have similar  $R_c$ . It shows the possibility of an Au-free CMOS compatible process.

Figure 2-12: Contact resistance versus recess depth. The sample here was implanted at 60 keV with a dose of  $2 \times 10^{15} \ cm^{-2}$

Figure 2-13: IV curve of a TLM pattern with a distance of 4 um from Tungsten contact, non-alloyed Ti/Al contact and alloyed Ti/Al/Ni/Au contact, respectively.

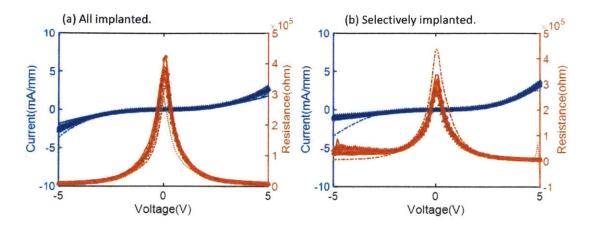

## Effects of Implantation Dose on $R_c$ and Activation ratio

A comprehensive dose test was performed at batch 2 based on the results from batch 1. Implantation energy and ohmic recess depth were set as 60 keV and 20 nm, respectively. The dose was ranging from  $7 \times 10^{14} \text{ cm}^{-2}$  to  $3 \times 10^{15} \text{ cm}^{-2}$ . TLM results are shown in Fig. 2-14.  $R_{c1}$  decreases with dose, while  $R_{c2}$  shows a minimal value with a dose of  $1 \times 10^{15} \text{ cm}^{-2}$ . A best  $R_c$  of  $\sim 0.3 \ \Omega \cdot mm$  was obtained with a dose of  $2 \times 10^{15} \text{ cm}^{-2}$ .

The activation ratios shown in Fig. 2-15 are estimated by the number of activated ions over the number of implanted ions:

Activation Ratio =

$$\frac{\# \text{ of Activated Ions}}{\# \text{ of Implanted Ions}}$$

(2.1)

where the number of activated ions can be estimated by subtracting the 2DEG density from the measured Hall density, the number of implanted ions is the integral of the Si doping concentration in AlGaN/GaN structure based on the results from TRIM simulation.

A linear dependence of the activation ratio on the dose in AlGaN/GaN in log scale can be observed, and the highest activation ratio could increase up to  $\sim 40\%$ . With a fixed activation annealing condition at 1200°C for 30 s, the linear dependence in log scale can be fitted as:

Activation Ratio =

$$\left[30 + 29 \log\left(\frac{\text{dose}}{1 \times 10^{15} \ \text{cm}^{-2}}\right)\right]\%$$

(2.2)

The linear dependence of activation ratio on dose indicates that the vacancies and interstitials created by implantation might enhance the electrical activation of the ions implanted.

The decrease of  $R_{c1}$  versus dose could be explained by the increase of dose and activation ratio. While  $R_{c1}$  is defined as the contact resistance between metal/semiconductor. The increasing number of free electrons close to the interface will help electrons tunneling through the Schottky barrier and thus reduce the  $R_{c1}$ .  $R_{c2}$  is the access resistance

Rc1: Contact resistance in the metal/semiconductor interface Rc2: Access resistance caused by implantation lattice damage Rc: Total measured contact resistance with selective implantation

Figure 2-14:  $R_c$ ,  $R_{c1}$  and  $R_{c2}$  versus dose.

between the 2DEG channel and the implanted region. On the one hand, increase doping level would help to reduce the resistance, on the other hand, the increase of lattice damage and charged impurities would degrade 2DEG density and mobility close to the implanted region and thus increase the resistance, which explains the well curve of  $R_{c2}$ .

#### **Repeatability Test**

To test the repeatability of this implanted ohmic scheme, the same implantation scheme was conducted on multiple samples, and the results are shown in Fig. 2-16. The mean value is  $\sim 0.3 \ \Omega \cdot mm$ , while the large variation is introduced by large sheet resistance.

Figure 2-15: Activation Ratio versus dose in AlGaN/GaN heterostructure.

#### Effects of Activation Annealing Conditions

In section 2.2, the effect of activation annealing condition on 2DEG carrier density and mobility was studied. It shows that high temperature and "long" time annealing by RTA would cause irreversible lattice degradation and thus increase sheet resistance. In this section, activation annealing condition on the activation ratio would be studied.

Activation annealing temperature effect on contact resistance was fist studied. The AlGaN/GaN structure had a 20 nm  $Al_{0.25}Ga_{0.75}N$  barrier layer. The 2DEG sheet density and mobility at room temperature were  $8.8 \times 10^{12} \ cm^{-2}$  and  $1704 \ cm^{2}V \cdot s$ , respectively. Device fabrication was started with the deposition of 40 nm  $SiO_2$  by PECVD as a protection layer. Si ions were then implanted with a dose of  $2 \times 10^{15} \ cm^{-2}$  at an energy of 20 keV and 60 keV. Activation annealing was performed under  $1100^{\circ}$ C or  $1200^{\circ}$ C in  $N_2$  ambient for 5 s. After annealing and removing the  $SiO_2$ , different metallization schemes were carried out, including non-alloyed Ti/Al/Ni/Au and tungsten contact without ohmic recess. After device isolation by ECR-RIE,

Figure 2-16: Contact resistance of sample #11 which is implanted at 60 keV with a dose of  $2 \times 10^{15} \ cm^{-2}$  and annealed at 1200°C for 30 s.

the transmission line method (TLM) was then performed to determine the contact resistance and sheet resistance. The results in Fig. 2-17 shows that 1200 °C is critical to have dopant activated.