# Using Defect Data to Characterize Assembly Process Capabilities and Constraints for Printed-Circuit-Board Design for Assembly

# by Eric Martin Soederberg

B.S. Electrical Engineering, Worcester Polytechnic Institute (1983)

Submitted to the Sloan School of Management and the Department of Electrical Engineering in Partial Fulfillment of the Requirements of the Degrees of

Master of Science in Management and Master of Science in Electrical Engineering

at the Massachusetts Institute of Technology June, 1992

© Massachusetts Institute of Technology, 1992. All rights reserved.

| Signature of Author                                               |

|-------------------------------------------------------------------|

| Certified byJohn'G Kassakian, Professor of Electrical Engineering |

| Certified by Anant Balakrishnan, Assoc. Professor of Management   |

| Certified by                                                      |

# Using Defect Data to Characterize Assembly Process Capabilities and Constraints for Printed-Circuit-Board Design for Assembly

### by Eric Martin Soederberg

Submitted to the Sloan School of Management and the Department of Electrical Engineering on May 10, 1992, in Partial Fulfillment of the Requirements of the Degrees of Master of Science in Management and Master of Science in Electrical Engineering

#### Abstract

Printed circuit boards (PCBs), the heart of most electronic products, are built using highly automated assembly processes. Currently available Design for Manufacturability and Assembly (DFMA) tools focus on combining parts and enhancing ease of assembly relative to manual and dedicated automatic assembly processes. Lacking design tools that can predict PCB assembly problems, manufacturers often rely on the iterative fabrication of prototype hardware and the intuition of product engineers to design electronic products that are producible in large volumes. DFMA methods, capable of capturing manufacturer specific process and part-related design constraints, are needed to ensure that new products are compatible with existing assembly processes early in the design cycle.

This research demonstrates how PCB assembly defect data can be used to characterize assembly process capabilities and constraints and outlines a method for communicating these constraints the the appropriate design engineers.

Typically a PCB assembly operation is faced with continuously changing product requirements and likewise a continuously changing set of process technologies and capabilities. This thesis stresses the importance of a continuously updated system for documenting and communicating process constraints to PCB designers.

Thesis Advisors:

Dr. John G. Kassakian

Dr. Anant Balakrishnan

Professor of Electrical Engineering

Assoc. Professor of Management

#### Acknowledgements

The work presented in this thesis was sponsored by the MIT Leaders for Manufacturing Program, a partnership between the MIT School of Engineering, the MIT Sloan School of Management and several major U.S. manufacturing companies. I would like to gratefully acknowledge the backing of this program and the resources it has provided during my two years at MIT.

The research for this thesis was done at Delco Electronics in Kokomo, Indiana. I would like to thank Delco for their very generous sponsorship. I would especially like to thank my company supervisor, Klaus Gschwend, for his support and encouragement.

Finally I would like to thank my thesis advisors, Anant Balakrishnan and John Kassakian, for their help and guidance in pulling this project and thesis together.

### **Table of Contents**

| 1. | Motivation                                                      | 7  |

|----|-----------------------------------------------------------------|----|

| 2. | Background                                                      | 14 |

|    | 2.1. Delco Electronics                                          | 14 |

|    | 2.2. The PCB Assembly Process at Delco Powertrain               | 15 |

| 3. | Method of Analysis                                              |    |

|    | 3.1 Identification of Design Related Manufacturability Problems | 18 |

|    | 3.2. In-circuit Rework Data and Analysis                        | 19 |

|    | 3.2.1. Compilation of Rework Data                               | 21 |

|    | 3.2.2. Estimated Cost of Rework                                 | 23 |

|    | 3.2.3. Pareto Problem Areas by Cost or Rework                   | 27 |

|    | 3.2.4. Perform a Causal Analysis on Top 30 Problem Areas        | 28 |

|    | 3.2.5. Current Design Related Manufacturability Problems        | 30 |

|    | 3.2.6 Examples of DFMA Problems                                 | 33 |

| 4. | Evaluation of Available DFMA Tools                              | 37 |

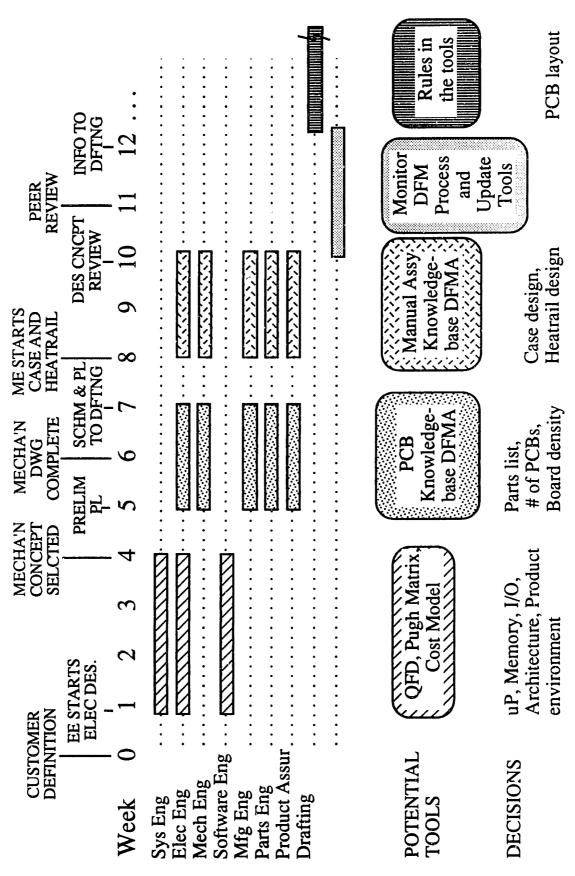

|    | 4.1. The Boothroyd Dewhurst Inc. DFMA Toolkit                   | 38 |

|    | 4.1.1. Manual DFMA                                              | 40 |

|    | 4.1.2. BDI Printed Circuit Board DFMA                           | 41 |

|    | 4.2. The Texas Instruments/BDI PCB DFMA Tool                    | 42 |

|    | 4.3. Rules-in-the-Tools                                         | 43 |

|    | 4.4. Product Design Specifications and Checklists               | 43 |

|    | 4.5. Comparison of Available Tools                              | 45 |

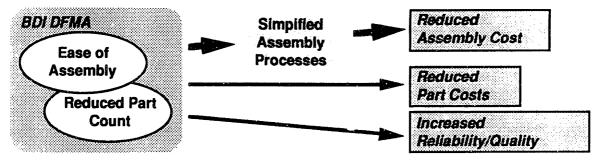

| 5. | A Dynamic Approach to DFMA for PCB Assemblies                   | 47 |

|    | 5.1. Design Decisions                                           | 50 |

|    | 5.2. Making Design Tradeoffs                                    | 51 |

|    | 5.3. General Types of Design Tools                              | 52 |

|    | 5.4. Proposed Dynamic DFMA Method                               | 54 |

|    | 5.4.1. Process Oriented Design Specifications                   | 56 |

|    | 5.4.2. Knowledge-based PCB DFMA                                 | 57 |

|    | 5.4.2.1 Defining Metrics for Evaluating Design Tradeoffs        |    |

|    | 5.4.2.2 Modeling First Pass Assembly Yield                      | 62 |

|    | 5.4.3 Rules in the CAD Tools                                    |    |

| 6. | Conclusions                                                     | 69 |

|    | eferences                                                       |    |

|    | opendix A. Analysis of Variance–Missing Bottom Side Chips       |    |

# List of Figures and Tables

| Figure 1.1.  | Design constraints on electronic assemblies.                         | 8    |

|--------------|----------------------------------------------------------------------|------|

| Figure 1.2.  | Product designed to match manufacturing processes                    |      |

| Figure 2.1.  | Assembly process flow                                                |      |

| Figure 3.1.  | The DPP Matrix.                                                      | .22  |

| Figure 3.2.  | Relative performance of different process/part-type categories       | .23  |

| Figure 3.3a. | Frequency distribution of the most important (rank 1) defects        | .28  |

| Figure 3.3b. | Frequency distribution of defects for rank 6: Short/Heatrail/ECMC    |      |

| Figure 3.4.  | Hole sizes for crystal mounting                                      |      |

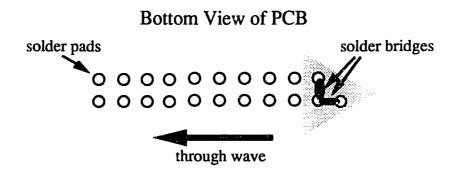

| Figure 3.5.  | Solder shorts on J3.                                                 |      |

| Figure 3.6.  | Solder thieves used to prevent solder shorts                         |      |

| Figure 3.7.  | Standard serial communications circuit                               | .35  |

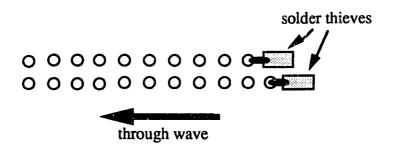

| Figure 4.1.  | The Boothroyd Dewhurst manual assembly DFMA approach                 | .39  |

| Figure 5.1.  | A typical design cycle and the design tools pertinent to each stage  |      |

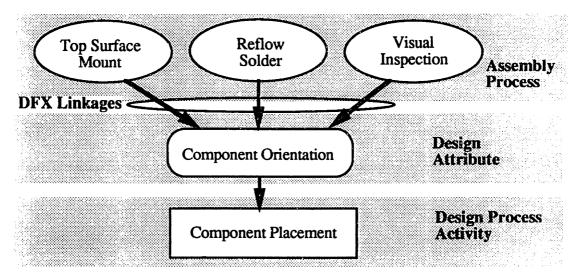

| Figure 5.2.  | Gatenby's DFX concept                                                | .51  |

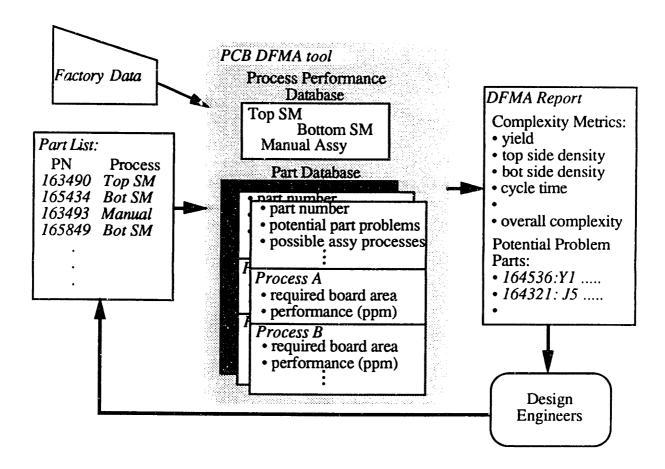

| Figure 5.3.  | A dynamic tool for DFMA of printed circuit board assemblies          | .55  |

| Figure 5.4.  | Process oriented product design specification                        | .57  |

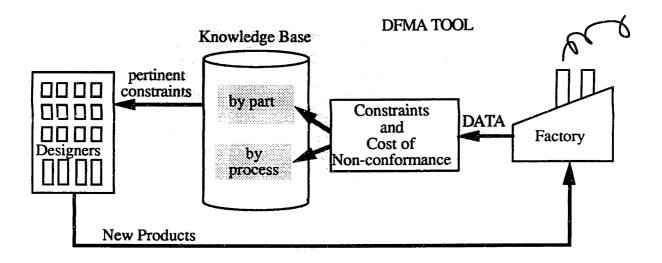

| Figure 5.5.  | Knowledge-based PCB DFMA                                             |      |

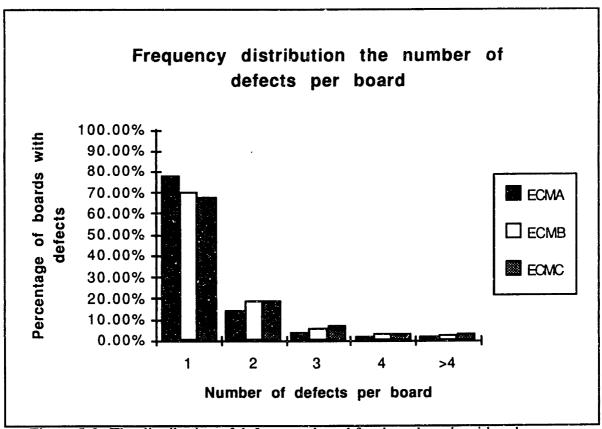

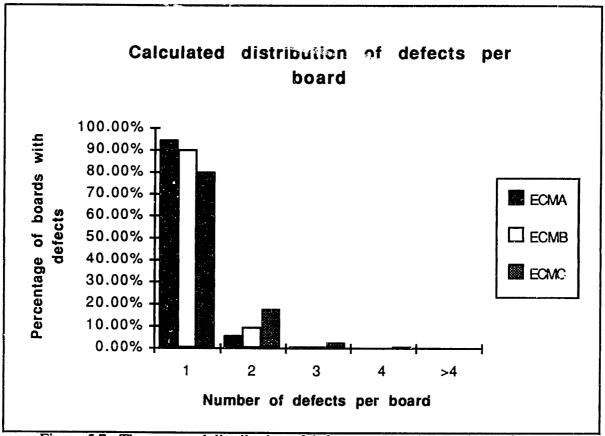

| Figure 5.6.  | The distribution of defects per board                                | .62  |

| Figure 5.7.  | The expected distribution of defects per board                       | .63  |

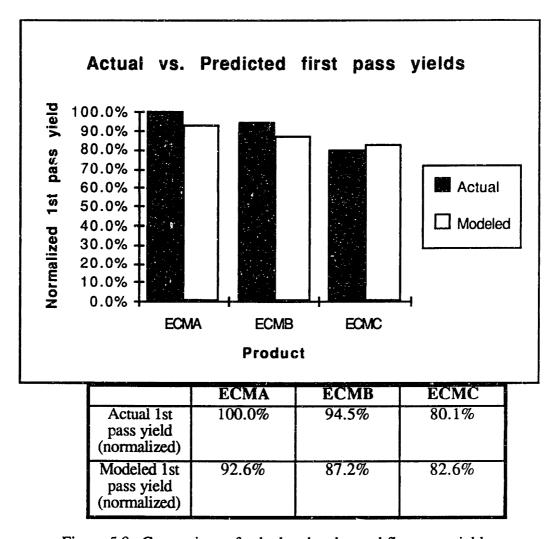

| Figure 5.8.  | Comparison of calculated and actual first pass yields                | .66  |

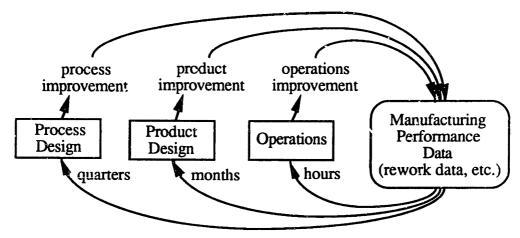

| Figure 6.1.  | Product performance data routed to design                            |      |

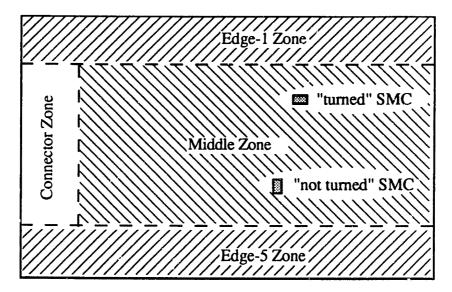

| Figure A1.   | SMC location and orientation on the bottom side of the ECMC product. | . 74 |

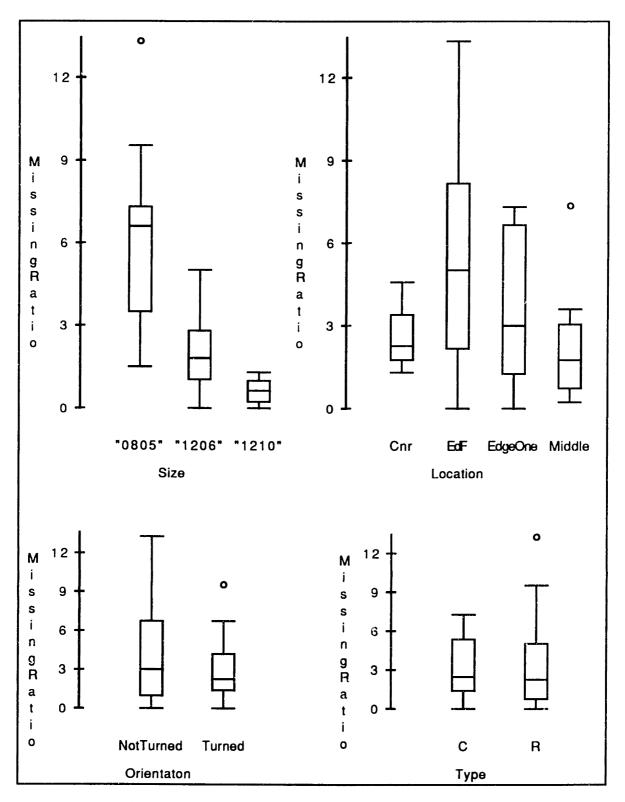

| Figure A2.   | Boxplots of the raw "missing component" data                         | .76  |

| Table 3.1.   | Part count comparison for the products under study                   |      |

| Table 3.2.   | The DPP Matrix in normalized defects per million parts placed        | .24  |

| Table 3.3.   | Estimated repair times.                                              | .25  |

| Table 3.4.   | Estimated cost of replacement parts                                  | .26  |

| Table 3.5.   | The top 20 defect categories.                                        |      |

| Table 3.6.   | Causal analysis results                                              | .31  |

| Table 3.7.   | $10\Omega$ resistor failure rate                                     | .36  |

| Table 4.1.   | DFMA tool comparison.                                                | .37  |

| Table 4.2.   | DFMA tools ability to address the problems found at DE               | .46  |

| Table 5.1.   | Relative performance of assembly processes                           | .52  |

| Table 5.2.   | Results of a 15 board multiple defect analysis                       | .64  |

| Table A1.    | Missing chip data broken into 40 experiments                         |      |

| Table A2.    | Analysis of variance for all main effects and 2-way interactions     |      |

| Table A3.    | Analysis of variance for the seven most significant effects          | .78  |

#### 1. Motivation

A printed circuit board (PCB) is flat non-conducting substrate that has one or more conducting layers patterned to interconnect electronic devices that are mounted on the board. Electronic components are assembled onto PCBs with various automated part insertion and soldering techniques to form PCB assemblies which are the heart of most electronic products.

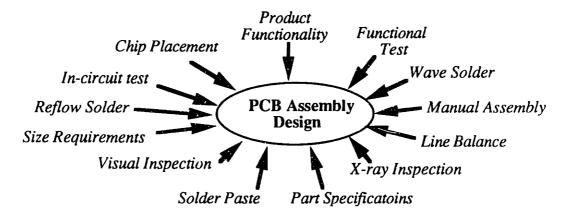

Printed circuit board (PCB) assembly can be thought of as an assortment of discrete assembly processes strung together to form a composite assembly process that suits a manufacturer's product requirements. Each assembly process, within the combined assembly process, constrains the product design. In other words, a PCB design is constrained by the summation of all of the constraints from a number of individual assembly processes. The individual processes typically range from manual part insertion to completely automated part placement and solder processes. The standard part packages that are assembled onto the PCB further constrain the design. Most designers of other products, with their ability to define the form and function of major assembly components, are challenged by the near infinite degrees of freedom at their disposal. The PCB designer, on the other hand, is challenged by the large number of standards and process constraints, both explicit and hidden, that must be met. Here are several examples: if two surface mount components are positioned too close together on the side of a PCB that is being wave soldered, the two components will likely be shorted with a bridge of solder; if a bypass capacitor is located too far from the power pins of the integrated circuit (IC) that it is buffering, it will not buffer the IC and the circuit could fail; if all nodes of a PCB circuit are not available for test on the bottom side of the board then the in-circuit tester cannot verify the presence of all of the circuit components; if the leaded component holes in the

PCB are too big, the parts will likely fall out before it is soldered down; if the holes are too small, the assembly operators will have to struggle to get them in. Fig. 1.1 shows some of the sources of constraints that PCB designers are faced with.

Figure 1.1. Design constraints on electronic assemblies.

The design constraints imposed by the processes and parts are not only numerous, they are also dynamic. The assembly processes and component packages used to build PCBs are changing rapidly as the electronics industry drives towards smaller more complex products. Brindley [6] points out that the package styles, dictated by the component manufacturers, once drove the assembly methods used to build electronic products. Now, however, the product manufacturers are driving the component package styles to fit their product requirements and assembly constraints. Recent examples include: fine-pitch surface mount technologies, flip-chip and tape bonding methods for securing integrated-circuit dies to PCBs, and soldering methods that do not require toxic solvents for cleaning. Hence, PCB design constraints are not only large in number, they are also changing rapidly.

It is no longer practical to rely on the intuition of the design engineers to develop PCB assemblies that take into account all pertinent design constraints. A DFMA tool that takes into account many individual and dynamic processes and part requirements is needed.

Shorter product life-cycles and market pressures to shorten time to market underline the need for design-process improvements in electronics.

Some argue that DFMA tools over-constrain designers and unduly inhibit their creativity. It should be pointed out that while design for assembly tools can require more effort in the early stages of product design, DFMA tools do not add design constraints—rather they attempt to illuminate *existing* constraints early in the design process. Highlighting the known constraints early in the design process allows more time to find creative solutions within the capability of the parts and the assembly processes.

DFMA tools are, by nature, specific to a particular assembly process. One cannot design a product for ease of assembly without defining an assembly method. For example, surface mount components are difficult to assembly by hand, even when using special tools. However, when a surface mount placement machine is available, these components can be assembled very quickly with ease. Various design tools are available for use in simplifying product designs that are built using manual assembly processes. However, PCB assembly requires many different automated assembly processes that are designed to handle many different part packages.

Most of the assembly processes and part packages used are standard throughout the industry [16]; however, very few manufacturers use the same combination of parts and processes. Even if two manufacturers do use the same processes and parts, they will likely have different levels of competence in using the processes and different process capacity constraints that would result in different product design criteria. The processes and the part packages, as well as the manufacturer's skill level, are constantly changing.

The most popular DFMA tools, such as the Boothroyd Dewhurst Inc. (BDI) DFMA toolkit [5], are based on the manual assembly process where there are many degrees of freedom in the part design and assembly process. These tools stress reduced part counts and ease of manual part insertion. Neither of these goals is applicable to PCB DFMA. Depending on one's process capabilities, a board with ten additional surface mount components (SMCs) may be easier to build than the same board with one additional leaded component.

Designers need to know the specifics of their process capability and constraints in order to make intelligent design tradeoffs. For example, how much more should a designer be willing to pay for a surface mount component vs. a leaded version of the component given that it is easier to assemble the surface mount version? Design tools like the BDI DFMA tool allow designers to evaluate design tradeoffs while the design can still be changed easily. Design specifications are good for laying out the ground rules but they do not typically allow designers to evaluate tradeoffs, nor do they promote an active interchange between the designers and the manufacturers.

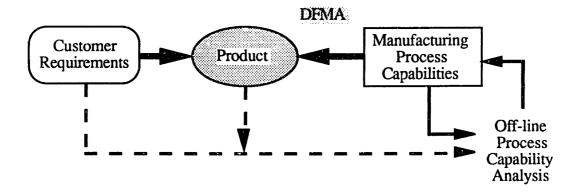

This thesis argues that the primary purpose of DFMA is to match products to process capabilities. (Fig. 1.2 shows this graphically) The following three steps are required to accomplish this:

Figure 1.2. Product designed to match manufacturing processes.

- 10 -

- The first step in matching product and process is to define the process capabilities and constraints. For example, how close can surface mount components be mounted to each other to insure reliable wave soldering given a manufacturer's current wave solder capabilities or, how close to the edge of the board can a component be placed such that it is not knocked off when the board is moved from one assembly process to the next? Some general guidelines and industry standards are published [16] but the surface mount processes are still not mature and some assembly machines have different constraints than others. When these process constraints are documented, they are typically proprietary to the company that developed them.

- Once the process capabilities are well defined, they must be communicated to the designers in such a way that the designers are made aware of all process constraints while the design is still fluid and intelligent design tradeoffs can be made. For example, if a designer cannot satisfy all of the design constraints or guidelines, which constraint should be violated first, the distance to the edge of the board constraint or the component to component spacing? This constraint-communication scheme can take several forms including written manuals and design tools (e.g., computer aided PCB layout tools) with built in rule checking.

- Finally, new and improved process capabilities should be developed to support current

and future product requirements. If new product designs are consistently constricted by

one's ability to reliably place leaded components, then one should consider improving the

leaded assembly process.

These three steps imply that all new products should be designed to match existing processes. While this is desirable, it is not always possible. For example, if you were to

design a wrist-watch television you would be seriously constrained by the available PCB assembly processes and available part packages. A new assembly method, perhaps a dedicated assembly machine would have to be developed simultaneously with the product development in order to meet the product's requirements. On the other hand, if you were designing the TV control circuitry for a 21 inch living room model, you would design the PCB assembly to be built with your existing assembly equipment. At any rate, a PCB assembly should not be designed without a specific set of assembly processes in mind.

It is tempting to minimize the importance of DFMA for electronic products since the assembly costs are generally a small fraction of total product cost. Assembly costs represent less than 6% of total production cost of products in the electronics industry. [21] Assembly cost reduction, however, is only one of the potential benefits that DFMA offers. Keith Brindley, in "Newnes Electronics Assembly Handbook" [6], estimates that 85 to 90% of all electronic assembly defects are a result of assembly problems. By facilitating a better match between product design and assembly process capabilities, production yields will increase and thus the likelihood of delivering defective products to the customer will decrease. Improved quality, less frustrated assembly workers or machine operators and fewer prototype revisions are all likely by-products of DFMA.

This thesis demonstrates how manufacturing defect data can be used to measure and characterize the match between assembly process and PCB design. This is done by comparing the relative production performance of three different PCB products that are built in the same assembly area using the same assembly processes. The effectiveness of some currently available DFMA tools is evaluated by first identifying the types of producibility problems that are experienced at a high volume board assembler, and then assessing the tools' ability to address these problems early in the design process. Learning from this comparison of available DFMA tools, the producibility problems isolated in the

defect data, and the types of decisions that designers make, a dynamic method for capturing and communicating process constraints to the designers is outlined.

Chapter 2 describes the setting in which this thesis research was conducted and a brief description of the PCB assembly process that was studied. Chapter 3 outlines the method used to uncover producibility problems, specifically those related to product design using assembly defect data. An evaluation of currently available DFMA tools is presented in Chapter 4 and a new DFMA approach is defined in response to these findings in Chapter 5. Conclusions are contained in Chapters 6.

#### 2. Background

The analysis and results presented in this thesis is based on data collected and research conducted at Delco Electronics in Kokomo, Indiana.

#### 2.1. Delco Electronics

Delco Electronics (DE) is a subsidiary of GM Hughes Electronics which is a wholly owned subsidiary of General Motors (GM). DE builds virtually all of General Motors' automotive electronics subassemblies (e.g. engine control modules, radios and air conditioning control units) and supplies electronic assemblies to several other automobile manufacturers as well. Seven business units operate production facilities in England, Singapore, Mexico, Wisconsin and Indiana. This thesis work was hosted by the Powertrain Electronics (PE) Business Unit in Kokomo, Indiana. PE designs and builds engine-control and transmission-control electronics.

An engine control module is typically built on a 5 by 8 inch PCB. The majority of the small components (resistors and capacitors) are surface mounted to the bottom side of the board and the larger components are surface mounted and through hole mounted on the top of the board. The newer Powertrain control modules combine electronic transmission control with engine control functions, and require two PCBs. Control modules that are mounted in the passenger compartment are packaged in aluminum sheet-metal boxes, while under-hood mounted modules are sealed in die-cast aluminum cases. PE builds roughly a dozen different engine controller board types in high volume (100,000 to 500,000 per year) and a dozen or so in low volumes (10,000 to 100,000 per year). GM car divisions purchase the majority of these controllers.

#### 2.2. The PCB Assembly Process at Delco Powertrain

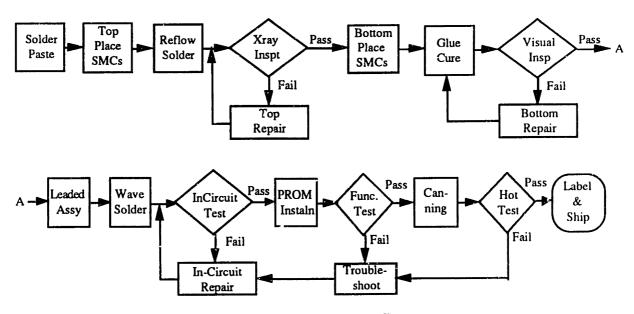

The individual assembly processes used at DE Powertrain are standard for the electronics industry. These include; surface mount components (SMC) onto solder paste; surface mount onto glue dots; manual component insertion; wave solder; in-circuit test; and so forth. The assembly process flow at DE, combining the individual assembly and test processes, is similar to the assembly process flow seen at other electronics manufactures, though the exact order of the assembly and test steps may be unique to DE. The following paragraphs describe the DE process flow. This process flow is described here as an example of the steps required to assemble a printed circuit board, and as a reference for the analysis presented in Chapter 3.

Figure 2.1. Assembly process flow.

The DE assembly process flow, shown in Fig. 2.1 above, begins with the automatic placement of the top SMCs onto a PCB that has been printed with solder paste. (Refer to Brindley [6] or Noble [19] for detailed descriptions of these assembly processes.) An infra-red oven then reflows the solder paste to secure these parts. An automated X-ray inspection machine then inspects the solder joints before the boards move to bottom-side

placement. Glue dots are applied to the bottom side of the board with an automated process that uses a product specific die with a glue pin positioned in the center of each chip location. The bottom surface mount parts (chips) are placed on the glue dots with a second automated placement machine, the glue is cured in an infra-red oven, and then the bottom side of the board is visually inspected by hand. Upon passing visual inspection, the boards are carried to the manual assembly area where the convector assembly (the heat-sink) and leaded components are inserted by hand. The bottom side of the board is then carried through a wave of molten solder to solder both the bottom surface mount parts and the leaded components in place. In-circuit and functional tests verify the proper installation and operation of the components through a "bed of nails" test fixture. Finally the PROM is installed, the unit is functionally tested, mounted in a case, tested again at an elevated temperature, and then shipped. Three different rework sites—top repair, bottom repair and in-circuit repair—rework the boards that fail the various inspections and tests shown in Fig. 2.1.

#### 3. Method of Analysis

As argued in Chapter 1, designing products for assembly requires:

- 1. a clear understanding of the process capabilities and constraints, and

- 2. a method for communicating these constraints to the designers.

This thesis addresses both of these issues, process constraint identification and constraint communication.

#### Identifying Process Constraints:

In order to evaluate the type of constraint information that needs to be conveyed to PCB assembly designers, a list of current manufacturing problems that could be attributed to product design was compiled. This was done by measuring and comparing the manufacturing performance of three different products that are built using the same assembly line at DE. The relative performance of the various assembly methods employed at DE (e.g. reflow surface mount vs. wave soldered surface mount vs. manual insertion) was also compared.

#### Communicating Process Constraints:

Constraint communication was addressed by first evaluating available DFMA tools. The design-related manufacturing problems compiled in the constraint analysis were analyzed to determine which problems could have been avoided using which types of DFMA tools. A dynamic DFMA method is proposed that is capable of addressing all of the design problems found in the constraint analysis, and is maintainable as processes and a manufacturer's understanding of the processes change.

The next two sections (3.1 and 3.2) describe constraint identification analysis in more detail. Chapter 4 compares available DFMA tools and Chapter 5 describes the proposed dynamic DFMA method.

#### 3.1 Identification of Design Related Manufacturability Problems

Manufacturability problems were found by measuring and contrasting the assembly performance of three different products that were currently in production.

Three engine control products—referred to here as ECMA, ECMB and ECMC—were selected for manufacturability analysis. They are all single-board designs and were built in the same focused factory. Table 3.1 lists the number of circuit board components used in each product as an indication of the products' relative complexities. Because the operators and assembly processes used to build these products are constant, differences in assembly performance can be attributed to differences in product design.

| Part Category                     | ECMA | Product<br>ECMB | ECMC |

|-----------------------------------|------|-----------------|------|

| Top SMC Integrated Circuits       | 6    | 9               | 13   |

| Top SMC (w/o Integrated Circuits) | 46   | 52              | 112  |

| Bottom SMC<br>(Chips)             | 162  | 223             | 223  |

| Leaded Components                 | 7    | 9               | 18   |

| Heat-Rail Leaded<br>Components    | 6    | 9               | 11   |

| Total                             | 227  | 302             | 377  |

Table 3.1. Part count comparison for the products under study.

It was not feasible to collect detailed manufacturing performance data (i.e. not only the aggregate yield at a given process, but the reason for and location of the defects that occur) at every assembly process step in the PCB assembly process with the resources available for this project. Aggregate total process yield data (the percentage of boards passed divided by the number of boards tested) was collected for all of the processes, but was not

sufficient for identifying and comparing the performance of specific product design attributes. Detailed data was, and is often, available at the in-circuit test operation (refer to the process flow in Fig. 2.1.). At DE, detailed defect data was entered into a computer database by the rework operators at in-circuit test. At the other test stations, only the aggregate test yields were recorded in note books, and they were not connected to the information system.

#### 3.2. In-circuit Rework Data and Analysis

The cost of rework performed after the in-circuit test was selected as the primary manufacturing performance measure for several reasons including the following:

- The total rework represents the largest single cost in the production area under study. [24]

- Detailed data is often available at rework. Upon receiving boards rejected by in-circuit test, the rework operators enter a description of each part they replace and the presumed reason why it needed to be replaced; e.g. "nosolder," "missing" or "off-location." This is the only comprehensive failure data that is recorded in the PE focused factories.

- Rework cost is a reasonable metric for producibility. It provides an indication of how well a product design matches the process capabilities.

- The vast majority of assembled parts are verified at the in-circuit test. The

major production processes, those responsible for nearly all of the

assembly errors, are up-stream from this test and as such are verified, to

some extent, at in-circuit test.

Because there are two test and rework stations up-stream (earlier in the process flow) of incircuit rework, in-circuit rework data is not a comprehensive or fair picture of all product

performance or manufacturability issues. However, a wide cross-section of product design problems are captured in this data and offer a significant basis from which to measure the effectiveness of DFMA methods and tools.

Four steps were taken to extract the most prominent DFMA issues from the rework data.

- 1. Compile Rework Data: All post in-circuit defect data for the three products under investigation was collected over an eight week period (approximately 18,000 defect data records). Each data record represents rework performed on one component of the circuit board and included the time that the rework was performed, the part and the location of the part that was reworked or replaced, the type of problem that was fixed, and the serial number of the product that was repaired. This data was broken down and categorized by product, by assembly process/part-type (e.g., bottom surface mount is a process/part-type category, it defines both the type of part and the process(s) used to assemble and secure the part to the PCB) and by type of defect (e.g., missing or no-solder).

- 2. Estimate Cost of Rework: Cost of repair was estimated for the various defect types and part categories. This was done to illuminate the most significant design problems.

- 3. Prioritize Problems by Cost of Rework: The cost of rework for each defect area (classified by product, process and type of defect) was calculated on a cost per board basis and then listed in descending order of cost.

- 4. Perform a Causal Analysis on Top 30 Problem Areas: The top 30 problem areas were disaggregated to the individual PCB component level and the probable causes for each component defect were assigned.

Causes were attributed to one of three activities: the assembly operations

(e.g.the assembly workers or the machine operators), the assembly process (e.g. the placement or solder machines) or the product design.

These four steps are now described in more detail.

#### 3.2.1. Compilation of Rework Data

Eight weeks of in-circuit defect data, for all three products, was compiled on the host information system.

Each part that was replaced during this time period was recorded as one event. It is important to note that rework failures were not recorded for each opportunity of failure, e.g. 68 opportunities for "no solder" conditions on a 68 pin part package, but rather there was one defect entry per part that was reworked or replaced. Albin and Friedman [1] point out that using the number of defects, counted by the opportunities for failure method, to prioritize problem areas is misleading due to the clustering and high variability of these types of counts. They recommend using board yield loss measurements to quantify the relative impact of a class of assembly defects. Because more than one rart is often reworked on one board, the number of parts reworked is not a true board yield loss measure. However, it is rare that a large number of parts are reworked on one board. Ninty-five percent of the boards built over the two month data collection period had three or fewer defects. Large differences between problem ranking by relative board yields and problem ranking by number of parts reworked per board are unlikely.

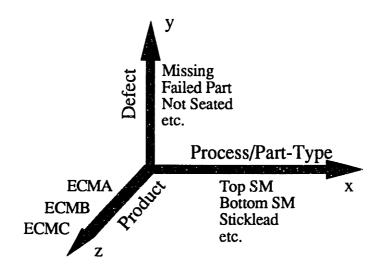

Process and defect categories were defined to be sufficient for both problem isolation and cost estimation purposes. Categories were defined on three dimensions:

• Product; (three categories: ECMA, ECMB or ECMC)

- Type of Part that needed rework, and thus the manufacturing Process used;

(five categories: Top SMC Quad¹, Top SMC other, Bottom SMC, Leaded

Component, Leaded Component Mounted to the Heatrail)

- Defect Reason, the reason rework was required; (fourteen categories including: Missing, Failed Part, Not Seated, Wrong Part, No Solder, Off Location, and Short)

Figure 3.1. The DPP Matrix.

The Defect by Process by Product (DPP) Matrix, shown in Fig. 3.1, was created as the basis for most of the defect data analysis. The DPP Matrix is simply a three-dimensional array of defect data that allows defect data comparisons across three axes. Each cell of this array is calibrated in rework dollars per board and in defects per million parts placed. Looking down the product axis (the Z-axis) indicates whether a particular defect/process problem is product-related or process-related. Looking down the process categories (the X-axis) the relative capabilities of each process can be analyzed for each product. Looking down the defect description axis offers clues as to the root cause within the process

<sup>&</sup>lt;sup>1</sup>A Quad is an integrated circuit packaged with leads on all four sides.

category in question. (e.g. a stuck glue pins would likely cause "missing" bottom SMCs, whereas a bad placement pipet might cause "off-location" defects)

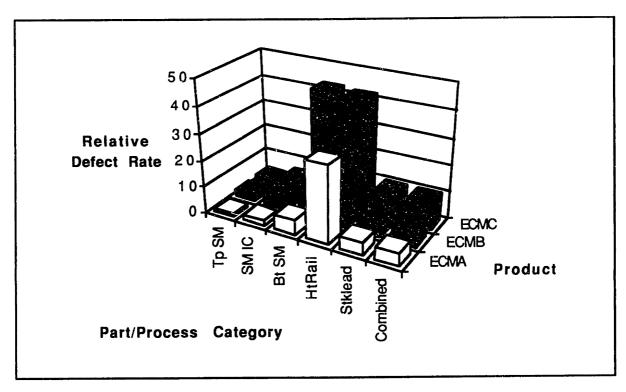

Table 3.2 shows the DPP matrix that was derived form the eight week data sample. The data has been disguised for confidentiality such that the aggregate performance for ECMA is equal to 100. Fig. 3.2 compares the performance of the three products by part/process category.

Figure 3.2. Relative performance of different process/part-type categories

# 3.2.2. Estimated Cost of Rework

As a means to weigh the significance of each problem area (i.e. each cell in the DPP matrix), the cost of rework labor and replacement parts was estimated for each defect-type and part category. The replacement part cost was added to the labor cost when a replacement part was required (e.g. for missing, failed part, or damaged part defect types).

| <b>DEFECTS PER x MILLION PARTS</b>        | MILLI       | ON PAR           |                | CED (8  | 3/27 to 1 | PLACED (8/27 to 10/23/91)* | *(       |                            |         |       |       |                            |          |                                                                                      |       |

|-------------------------------------------|-------------|------------------|----------------|---------|-----------|----------------------------|----------|----------------------------|---------|-------|-------|----------------------------|----------|--------------------------------------------------------------------------------------|-------|

|                                           | <b>ECMA</b> | ECMA Failures at | s at Incircuit | cuit    |           | ECMB                       | Failures | ECMB Failures at Incircuit | cuit    |       | ECMC  | ECMC Failures at Incircuit | at Incir | cuit                                                                                 |       |

| Defects                                   | Tp SM       | Tp SM SM IC Hi   | HtRail         | Stklead | Bt SM     | Tp SM                      | SM IC    | HtRail                     | Stklead | Bt SM | Tp SM | SM IC                      | HtRail   | Rail Siklead Bt SM Tp SM SM IC HtRail Stklead Bt SM Tp SM SM IC HtRail Stklead Bt SM | Bt SM |

| Missing                                   | 6.0         | 9.0              | 14.2           | 315.4   | 19.1      | 9.8                        | 2.1      | 9.89                       | 269.0   | 36.2  | 2.8   |                            | 112.7    | 327.1                                                                                | 48.9  |

| Failed Part                               | 13.8        | 32.3             | 11.6           | 18.8    | 15.9      | 26.3                       | 71.7     | 23.2                       | 20.0    | 22.9  | 28.4  | 75.3                       | 67.3     | 52.7                                                                                 | 37.0  |

| No Solder                                 | 0.2         |                  | 5.2            |         | 23.4      | 0.2                        |          | 1.1                        | 1.1     | 23.4  | 2.3   | 3.2                        | 2.8      | 1.2                                                                                  | 17.7  |

| Short                                     | 0.3         | 3.2              | 48.4           | 1.7     | 8.2       | 0.4                        | 23.2     | 26.4                       | 2.1     | 1.7   | 1.7   | 11.2                       | 595.9    | 2.9                                                                                  | 30.4  |

| Off Location                              | 1.3         |                  |                |         | 14.2      | 0.5                        |          |                            |         | 13.2  | 1.4   | 1.6                        | 5.7      | 9.0                                                                                  | 25.7  |

| <b>TroubleNotFound</b>                    | 3.8         |                  |                | !       | 4.5       | 7.3                        |          |                            |         | 7.3   | 24.1  | 4.0                        | 6.0      | 21.4                                                                                 | 28.0  |

| Wrong Part                                | 0.3         |                  | 32.3           | 41.5    | 7.0       | 0.5                        | 1.1      | 66.4                       | 3.2     | 14.7  | 0.8   |                            | 54.9     | 94.4                                                                                 | 12.8  |

| Not Seated                                | 0.2         |                  | 6.5            | 221.9   | 0.2       | 2.6                        |          | 27.4                       | 186.7   | 0.3   | 1.0   | 7.2                        | 51.2     | 320.1                                                                                | 0.1   |

| Excess Glue                               |             |                  |                |         | 6.3       | 0.4                        |          |                            |         | 6.9   |       |                            |          |                                                                                      | 8.6   |

| Reversed                                  |             | 1.3              | 9.0            | 20.5    |           | 2.2                        |          |                            | 93.9    |       | 0.3   | 8.0                        | 4.7      | 75.8                                                                                 | 0.0   |

| Damaged                                   | 0.7         |                  | 2.6            | 3.3     | 1.9       | 1.6                        |          | 10.5                       | 3.2     | 1.5   | 1.7   | 8.0                        | 17.1     | 1.7                                                                                  | 3.6   |

| Not Calibrated                            |             | 3.2              |                |         |           |                            | 1.1      |                            | •       |       |       | 18.4                       |          |                                                                                      |       |

| Too Much Solder                           |             |                  |                |         | 0.2       | 0.4                        |          |                            |         | 0.2   | 0.1   |                            | 6.0      | 1.2                                                                                  | 0.5   |

| Extra Part                                |             | 9.0              |                | 9.0     | 0.2       |                            |          |                            | 1.1     | 0.0   |       |                            | 6.0      |                                                                                      | 0.3   |

| TOTAL                                     | 21.5        | 41.3             | 121.4          | 623.6   | 101.1     | 50.9                       | 99.1     | 223.6                      | 581.2   | 128.3 | 64.6  | 122.6                      | 915.1    | 899.0                                                                                | 213.5 |

| Defects/ x million parts placed/ product: | parts p     | aced/pr          | oduct:         |         | 100       |                            |          |                            |         | 130   |       |                            |          |                                                                                      | 219   |

Table 3.2. Defect/Process/Product (DPP) Matrix, all numbers in normalized defects per million parts placed.

\*This data has been disguised (normalized) so as not to divulge confidential performance data, the relative performance has been maintained.

The cost of labor includes both the rework operator's time and the in-circuit test operator's time for retest. No charge was included for equipment time or incidental rework supplies.

Because the rework operators in this factory record their repair operations on a computer database in real-time, it was possible to objectively measure the actual repair times of a large number of repairs without looking over the rework operators' shoulders with a stopwatch in hand. A stop-watch was used to corroborate the time values calculated from the database. Table 3.3 shows the results of the time study. Because the timed and calculated repair time measurements had large standard deviations, the estimated repair times were rounded to the nearest unit. Most repairs took the rework operators roughly 3 units of time to complete.

| ESTIMATED REWORK TIMES, normalized* |                   |             |                |        |               |  |

|-------------------------------------|-------------------|-------------|----------------|--------|---------------|--|

|                                     | Part/Proces       | s Category  |                |        |               |  |

| Defect Type                         | Top SMC (non ICs) | Top SMC ICs | On<br>Heatrail | Leaded | Bottom<br>SMC |  |

| Missing                             | 3.00              | 7.00        | 3.00           | 3.00   | 3.00          |  |

| Failed Part                         | 3.00              | 7.00        | 3.00           | 3.00   | 3.00          |  |

| No Solder                           | 2.00              | 2.00        | 2.00           | 2.00   | 2.00          |  |

| Short                               | 2.00              | 2.00        | 2.00           | 2.00   | 2.00          |  |

| Off Location                        | 2.00              | 7.00        | 2.00           | 2.00   | 2.00          |  |

| TroubleNotFound                     | 2.00              | 2.00        | 2.00           | 2.00   | 2.00          |  |

| Wrong Part                          | 3.00              | 7.00        | 3.00           | 3.00   | 3.00          |  |

| Not Seated                          |                   |             | 2.60           | 2.00   |               |  |

| Excess Glue                         |                   |             |                |        | 2.00          |  |

| Reversed                            | 2.00              | 7.00        | 2.00           | 2.00   |               |  |

| Damaged                             | 3.00              | 7.00        | 3.00           | 3.00   | 3.00          |  |

| Not Calibrated                      |                   | 7.00        |                |        |               |  |

| Too Much Solder                     | 2.00              | 2.00        | 2.00           | 2.00   | 2.00          |  |

| Extra Part                          | 2.00              |             | *****          |        | 2.00          |  |

<sup>\*</sup> These times do not include time for retest; roughly one additional unit.

Table 3.3. Estimated repair times.

Using the estimated repair times shown in Table 3.3 and the number of repairs performed over the eight week period, 78% of available rework time was accounted for. This is consistent with the rework operator idle time that was observed during this period.

The cost of replacement parts was estimated for each rework category by taking the weighted average of the actual part costs incurred over the eight week data collection period. See Table 3.4.

| Estimated Replacement Parts C  | stimated Replacement Parts Cost* |             |             |          |  |  |

|--------------------------------|----------------------------------|-------------|-------------|----------|--|--|

|                                | <b>Product:</b>                  |             |             |          |  |  |

| Part Type Category             | ECMB                             | <b>ECMA</b> | <b>ECMC</b> | Combined |  |  |

| Heat Rail                      |                                  |             |             |          |  |  |

| Total Replaced (count)         | 96                               | 94          | 266         | 456      |  |  |

| Cost of Replaced ICs (dollars) | 148.50                           | 169.77      | 232.17      | 550.44   |  |  |

| Est. Cost per Part (dollars)   | 1.55                             | 1.81        | 0.87        | \$1.21   |  |  |

| SM ICs                         |                                  |             |             |          |  |  |

| Total Replaced (count)         | 72                               | 56          | 118         | 246      |  |  |

| Cost of Replaced ICs (dollars) | 443.24                           | 292.47      | 618.69      | 1354.40  |  |  |

| Est. Cost per Part (dollars)   | 6.16                             | 5.22        | 5.24        | \$5.51   |  |  |

| Leaded                         |                                  |             |             |          |  |  |

| Total Replaced (count)         | 276                              | 667         | 822         | 1765     |  |  |

| Cost of Replaced ICs (dollars) | <i>58.81</i>                     | 110.98      | 130.96      | 300.75   |  |  |

| Est. Cost per Part (dollars)   | 0.21                             | 0.17        | 0.16        | \$0.17   |  |  |

| SM Top and Bot                 |                                  |             |             |          |  |  |

| Est. Cost per Part (dollars)   |                                  | Estimated   |             | \$0.01   |  |  |

<sup>\*</sup>The cost of each part replaced, over a given period of time, is summed and then divided by the total number of parts changed.

Table 3.4. Estimated cost of replacement parts.

Using these time and part-cost estimates, the total cost of rework for each problem area in the DPP Matrix was calculated.

#### 3.2.3. Pareto Problem Areas by Cost or Rework

The DPP Matrix entries are listed in descending order of rework cost per board in order to prioritize the defect categories. As implied by the DPP Matrix definition, each problem category is defined by a *defect* description, an assembly *process* and part-type, and a *product*; e.g. "missing, bottom SMCs on the ECMC product" tops the list. Each problem area is assigned a rank number that corresponds to its position on the list, "rank 1" being the most costly. Table 3.5 lists the top 20 defect categories.

|             |            |                 | Normalized        | Normal  | ized |

|-------------|------------|-----------------|-------------------|---------|------|

| Defect C    | Category:  |                 | <b>Total Cost</b> | Cost/Bo | ard  |

| product     | part type  | defect descptn  | of Rework         |         | rank |

| ECMC        | Bottom SMC | Missing         | 1.00              | 1.000   | 1    |

| ECMC        | Bottom SMC | Failed Part     | 0.76              | 0.756   | 2    |

| ECMB        | Bottom SMC | Missing         | 0.71              | 0.648   | 3    |

| ECMC        | Sticklead  | Missing         | 0.57              | 0.575   | 4    |

| ECMC        | Bottom SMC | Short           | 0.46              | 0.464   | 5    |

| ECMC        | Heatrail   | Short           | 0.45              | 0.449   | 6    |

| ECMC        | Bottom SMC | TroubleNotFound | 0.43              | 0.430   | 7    |

| <b>ECMB</b> | Bottom SMC | Failed Part     | 0.45              | 0.410   | 8    |

| <b>ECMC</b> | Sticklead  | Not Seated      | 0.39              | 0.395   | 9    |

| ECMC        | Bottom SMC | Off Location    | 0.39              | 0.392   | 10   |

| <b>ECMC</b> | SMC IC     | Failed Part     | 0.38              | 0.379   | 11   |

| ECMB        | Bottom SMC | No Solder       | 0.33              | 0.297   | 12   |

| ECMC        | Top SMC    | Failed Part     | 0.29              | 0.291   | 13   |

| ECMC        | Bottom SMC | No Solder       | 0.27              | 0.270   | 14   |

| ECMB        | Bottom SMC | Wrong Part      | 0.29              | 0.263   | 15   |

| <b>ECMC</b> | Bottom SMC | Wrong Part      | 0.26              | 0.262   | 16   |

| ECMA        | Bottom SMC | Missing         | 0.67              | 0.248   | 17   |

| ECMB        | SMC IC     | Failed Part     | 0.27              | 0.242   | 18   |

| ECMA        | Bottom SMC | No Solder       | 0.58              | 0.216   | 19   |

| ECMB        | Sticklead  | Missing         | 0.23              | 0.209   | 20   |

Table 3.5. The top 20 defect categories.

#### 3.2.4. Perform a Causal Analysis on Top 30 Problem Areas

The top 30 (rank 1 through 30) problem areas were investigated in detail to determine the major cause(s) of failure. Each problem area (a cell in the DPP matrix) potentially has causes that can be attributed to any or all of the following:

- an operations problem,

- a process problem, or,

- a product design problem.

This thesis concentrates on the design aspects of each production problem area.

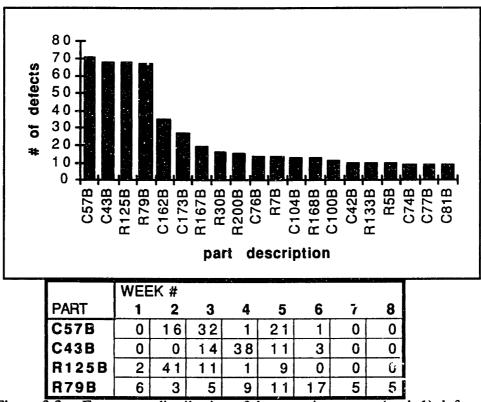

Figure 3.3a. Frequency distribution of the most important (rank 1) defects: Missing/Bottom SMC/ECMC.

Figure 3.3b. Frequency distribution of defects for rank 6: Short/Heatrail/ECMC.

The first step taken to isolate the defect causes was to disaggregate the individual defects within each problem area. Fig. 3.3 shows the frequency distribution of defects per individual PCB parts for the rank 1 and rank 6 problem areas. A week by week breakdown of the parts that fail most often provides evidence as to the nature of the cause, e.g., a one-time occurrence or a consistent problem. This specific part failure information was brought to the repair workers, the assembly machine operators and the manufacturing engineers to determine the most likely problem causes.

## 3.2.5. Current Design Related Manufacturability Problems

Table 3.6 lists the results of the causal analysis. Each problem area in the first column is the combination of problems found with all three products. The product distinctions were needed for the causal analysis, but are not needed for the tool analysis. Problem areas are now defined by defect description and process/part description (e.g. missing, bottom

surface mount), and the relative importance of each problem area is indicated by the rank numbers of each product problem area (determined by cost per board, see Table 3.5) from which each new problem area was derived.

The number of defects and total rework cost, in the second and third columns, give an absolute measure of the cost in this particular production area over the two month period studied. The forth column contains a normalized measure of problem severity in defects per million parts placed.

As mentioned earlier, the problem causes found could be assigned to one of three possible areas: operational, product design and process design. This table lists all three areas, though the design causes are of primary concern to this investigation.

| In-Circuit<br>Problem Area<br>Rank:(ECMA,B,C)<br>by rework \$1bd | Operational Cause                                                                                                                          | Product Design Cause                                                                                                                                                                                  | Process Design Cause                                                                                     |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Missing/Bottom SM<br>Rank: 1,3,17                                | <ul> <li>Stuck Glue Pins</li> <li>Visual missed it</li> <li>Rough handling at stkld Assy</li> <li>Boards stacked at visual insp</li> </ul> | Scattered chip layout Empty pads near chips Chip located near edge of board Chips located near screw High profile 0805s easy knock off Transistor on bot, hard to inspect                             | Glue pins unreliable     Visual inspection unreliable     Too much handling     0805's easy to knock off |

| Failed Part/Bottom SM<br>Rank: 2,8,21                            | Failed Part/Bottom SM • Pogo pins not working • "Feiled" parts are not retested                                                            | • Tight tolerance (1%) parts used • Parallel capacitors hard to test • Extreme R&C values hard to test                                                                                                | No pogo-pin continuity check     Tight Tolerances     Inconsistent test limits                           |

| Missing/Sticklead<br>Rank: 4,20,22                               | Conveyer jump knocks out part     Sticklead worker forgets part                                                                            | <ul> <li>Unsecured parts fall out easily</li> <li>Top heavy, loose parts fall out</li> <li>Parts located in random locations</li> <li>Holes too big</li> <li>Difficult visual verification</li> </ul> | Time too tight for operator inspin                                                                       |

| Short/BottomSM<br>Rank: 5,60,41                                  | <ul> <li>Solder wave out of tolerance</li> </ul>                                                                                           | <ul> <li>Unmasked runner near chip pad</li> <li>Exit pad too small for 1206 caps</li> </ul>                                                                                                           | Solder wave requires tight specs                                                                         |

| Short/Heatrail<br>Rank: 6,67,63                                  | Solder wave out of tolerance                                                                                                               | <ul> <li>Triangled wave exit. 65 pin header</li> <li>Solder wave requires tight specs (use solder thief)</li> <li>Via hole close to sticklead pin</li> <li>Long leads on heatrail IC</li> </ul>       | <ul> <li>Solder wave requires light specs</li> </ul>                                                     |

| TrbiNotFnd/Bot SM<br>Rank: 7,33,48                               | • Improper troubleshooting                                                                                                                 | Tight tolerance (1%) parts used Parallel capacitors hard to test Extreme R&C values hard to test Insufficient design for test                                                                         | No pogo-pin continuity check     Tight Tolerances     Inconsistent test limits     Poor test diagnostics |

Table 3.6 Causal analysis results. Page 1 of 2

| In-Circuit<br>Problem Area            | Operational Cause                                                                                                | Product Design Cause                                                                                               | Process Design Cause                                     |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Not Seated/Sticklead<br>Rank: 9,31,37 | Conveyer jump knocks out parts  Unsecured parts fall out easilt  Holes too big                                   | <ul> <li>Varistor on top of other parts</li> <li>Unsecured parts fall out easily</li> <li>Holes too big</li> </ul> | <ul> <li>Time too tight for operator inspin</li> </ul>   |

| Off Location/Bot SM<br>Rank: 10,25,28 | Pipet not working                                                                                                |                                                                                                                    | Pipets not reliable                                      |

| Failed Part/SM 1C<br>Rank: 11,18,44   | <ul> <li>Improper troubleshooting</li> <li>"Failed" parts are not retested</li> <li>Part not soldered</li> </ul> | <ul> <li>Insufficient design for test</li> </ul>                                                                   | Poor test diagnostics                                    |

| Failed Part/Top SM<br>Rank: 13,29,46  | • "Failed" parts are not retested                                                                                |                                                                                                                    | • Tight Tolerances, pass E/C, Xray                       |

| No Solder/Bottom SM<br>Rank 14,12,19  | No Solder/Bottom SM • Board not fully seated in pallet  Rank 14,12,19                                            | <ul> <li>Chips in wake of screw head</li> <li>No runner bottleneck to ground</li> </ul>                            | Pallets can be loaded improperly     Pallets out of spec |

| Wrong Part/Bot SM<br>Rank: 16,15,36   | <ul> <li>Wrong part loaded in MCMV</li> <li>Bottom repair used wrong part</li> </ul>                             | <ul> <li>Large number of part types used</li> </ul>                                                                | Bottom rework is required                                |

Table 3.6 Causal analysis results. Page 2 of 2

#### 3.2.6 Examples of DFMA Problems

Three examples of manufacturability problems found with this analysis are outlined here to illustrate the types of design problems that need to be addressed by DFMA methods.

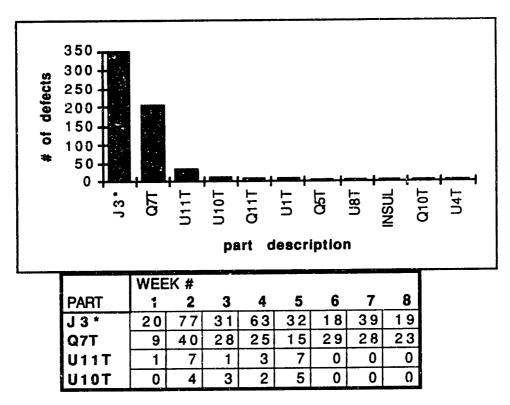

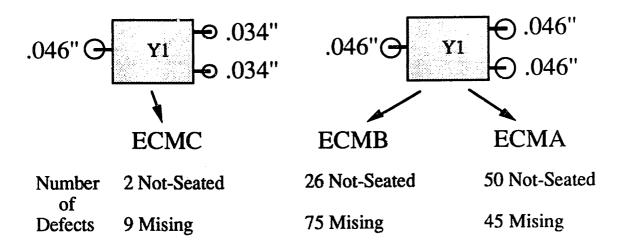

#### Example 1. Missing Crystals

All three products use identical crystals for the microprocessor clock. The ECMC board has an order of magnitude fewer "Not-Seated" defects than the ECMB and ECMA products. As shown in Fig. 3.4, the ECMA and ECMB boards use a different hole pattern than the ECMC board.

Figure 3.4. Hole sizes for crystal mounting.

Originally the hole pattern on the ECMC board was identical to that shown for the ECMB and ECMA boards. A manufacturing engineer recognized the missing crystal problem in an early version of the ECMC board and corrected it by using smaller holes for the active leads as shown in the ECMC configuration in Fig. 3.4. The ECMA board, the newest of

the three products, has not benefited from the ECMC experience due to a lack of communication between engineers.

#### Example 2. Wave Solder Shorts

The ECMC product consistently fails in-circuit test with solder shorts. The most common short occurs on a 65 pin connector (J3) shown in Fig. 3.5. This problem is likely much larger than the numbers suggest. The in-circuit test operator for this product typically removes the "J3" shorts before running the test. Solder bridges like these are a common at the end of a consecutive string of component leads. This effect is documented by Brindley [6] and Elliott [11].

Figure 3.5. Solder shorts on J3.

Brindley and Elliott recommend the use of dummy pads, called solder thieves, at the end consecutive rows of solder pads such that the excess solder accumulation does not cause an undesired short. See Fig. 3.6.

Figure 3.6. Solder thieves used to prevent solder shorts.

#### Example 3. Tight Part Tolerance on a current limit resistor

All three products use the same serial interface circuit which contains a  $10\Omega$ , 1% resistor in a DE standardized serial communications circuit. As shown in Fig. 3.7, the function of the  $10\Omega$  resistor is to protect the serial interface IC from an excess current condition. The serial interface circuit, with its required components, are considered a proven design and used in all recent engine controllers. As shown in Table 3.7, the ECMC and ECMB products have this part replaced for "failed part" failures 20 times more often than the ECMA product does. The rework operator enters a problem as "failed part" when there is no other apparent reason for failure, such as no-solder, off-location or missing problems. The removed parts are generally not retested.

Figure 3.7. Standard serial communications circuit.

| Product | Part Designator | # of "Failed-Part" Defects |

|---------|-----------------|----------------------------|

| ECMC    | R23, Bottom SMC | 49                         |

| ECMB    | R79, Bottom SMC | 40                         |

| ECMA    | R49, Top SMC    | 5                          |

Table 3.7.  $10\Omega$  resistor failure rate.

Small resistance values are difficult to test through the "pogo" or spring loaded test pins of the in-circuit "bed of nails" test interface because the contact resistance of the connection to the PCB is often larger than the allowed tolerance of the resistor.

On the ECMA product, this resistor is mounted on the reflow-solder side (top) of the PCB while the ECMB and ECMC products mount this resistor on the wave-solder side.

Unfortunately, it is not clear whether the test limits; the part spec; or the assembly process; is the most significant cause of failure; however, the magnitude of the performance difference between the three products clearly indicates that some aspect of the problem is design-related and tight tolerances are difficult to measure at in-circuit test. Chevalier [8] has modeled the electronic testing problem and has derived equations for minimizing the total expected cost of quality based on where one inspects for defects and to what tolerance one accepts or rejects boards.

## 4. Evaluation of Available DFMA Tools

The object of this evaluation is to identify which types of available DFMA tools are capable of affecting the design decisions at the appropriate time in the design process of electronic products, i.e., before the design is frozen. An ideal DFMA system would be capable of evaluating the relative complexity of a design with a minimum amount of design information, be capable of predicting any and all downstream assembly difficulties, be easy to use, and be able to indicate clearly what steps need to be taken to improve the design under analysis. Of course, there are no ideal systems; however, it is important to have a clear goal for the ultimate tool.

DFMA tools and methods can be broken into two basic categories: those that use fixed experience databases to evaluate designs and those with user definable databases. As show in Table 4.1, the tools can be further broken down by those that are computer automated and those that are not.

| DFMA Tools/Methods    | Manual                  | Computer Automated    |

|-----------------------|-------------------------|-----------------------|

| Fixed Database        | GE/Hitachi/Westinghouse | BDI Toolkit           |

| User Defined Database | Product Design Specs    | Texas Instruments/BDI |

|                       | Checklists              | "Rules in the Tools"  |

Table 4.1. DFMA tool comparison.

The tools listed in Table 4.1 are discussed below in more detail. They are then evaluated relative to their ability to address the design problems identified in the causal analysis. The

following tools were selected to be representative of the DFA tools that are currently available to electronic product manufacturers:

- The Boothroyd Dewhurst Inc. Manual DFMA Tool (BDI Toolkit) [5]. This

computer based tool is very similar to the manual General

Electric/Hitachi/Westinghouse DFA method.

- The Texas Instruments/BDI PCB DFMA tool [4]. Originally developed for in-house use by Texas Instruments (TI), this product is being marketed jointly by TI and BDI.

- "Rules in the Tools". This is a Hewlett Packard expression [2] and [20] that refers to the concept of integrating design rules into the CAD tools that the engineers and draftsmen use to layout PCBs.

- Written Product Design Specifications (PDS) and Checklists. This is a

written collection of design rules and guidelines used as a reference for

designers and potentially as a design screening tool in product design

reviews. The Institute for Interconnecting and Packaging Electronic

Circuits (IPC) publishes a comprehensive PCB design specification [16].

The first two tools listed are commercially available personal computer programs. The remaining two tools are commonly used company-specific tools that are typically developed in-house.

# 4.1. The Boothroyd Dewhurst Inc. DFMA Toolkit

While this paper looks at the BDI Toolkit, it should be noted the manual assembly portion of the BDI Toolkit is very similar to the GE/Hitachi/Westinghouse (GE) method. Shina [21] has compared the methods by applying both the BDI and the GE manual assembly analyses to several different mechanical products. According to Shina's study, the two methods estimate assembly time to within 20% of each other and both methods are

repeatable to within 20%. The BDI manual assembly tool is used here to represent the entire class of tools that calculate assembly times and design efficiencies based on manual assembly time studies.

Written for an IBM compatible personal computer, the BDI DFMA software package<sup>2</sup> offers a number of tools to aid in the development of products that are easier to build. In general they guide the designers towards minimizing the number of parts and simplifying the required assembly operations.

The manual BDI assembly tool calculates measures of efficiency so that various design implementations can be compared for relative ease of assembly. The two primary measures of efficiency are the total estimated assembly time and the theoretical minimum number of parts required divided by the number of parts specified. The BDI DFMA tool was not designed to be a conceptual design aid, but rather a design analysis tool that can be applied to a design after the preliminary drawings are available. By encouraging part count reduction and ease of assembly, these tools minimize assembly costs by simplifying the assembly and part handling processes required to build a product.

Figure 4.1. The Boothroyd Dewhurst manual assembly DFMA approach.

\_

<sup>&</sup>lt;sup>2</sup>Boothroyd Dewhurst Inc., "DFMA Toolkit", version 5.1a

The notion that BDI-like manual assembly tools are only good for analyzing mechanical products is not accurate. These tools are applicable to products that are built with manual assembly processes. In the case of PCBs, manual assembly is only a small part of the over-all assembly process and the BDI tool can be effective for this part of the assembly.

Two of the tools provided in the BDI DFMA Toolkit, the Manual Assembly DFMA Tool and the PCB DFMA Tool, are discused here. There are several other tools provided in this toolkit that are less pertinent to electronics assembly. [5].

#### 4.1.1. Manual DFMA

The heart of the BDI Toolkit, the manual DFMA tool, systematically enforces the following set of rules [5]:

- Minimize the number of parts and part types.

- Eliminate adjustments.

- Design parts to be self-aligning and self-locating.

- Ensure adequate access and unrestricted vision.

- Ensure ease of handling from bulk.

- Minimize unneeded operations during assembly.

- Design parts that cannot be assembled incorrectly.

- Maximize part symmetry.

The manual analysis estimates the time and cost of assembling a given design by analyzing each part and each operation required to build a given assembly. The software penalizes (with additional assembly time) parts or operations that violate any of the above design rules. The assembly costs associated with each component are tabulated for reference during redesign.

Questions as to the fundamental necessity of a part lead the design team to reduce part count. Questions regarding the complex handling of individual parts lead the designer to part designs that are easy to assemble. The exercise of applying this analysis (i.e., answering the questions) leads a design team towards addressing the largest assembly cost areas in a systematic and insightful manner. The results of the analysis do not recommend specific design improvements; rather the exercise of applying this tool pushes the design team towards creative design improvements.

#### 4.1.2. BDI Printed Circuit Board DFMA

The BDI Toolkit provides a printed circuit board tool to estimate the cost of assembling a PCB assembly. The theory behind this tool is that if you can estimate the cost of assembly up front, you can iterate on the design to come up with the least cost solution and thus the design that is easiest to build. However, this tool does very little to lead the designer to a better solution. Geoffrey Boothroyd describes it as an "after-the-fact" analysis tool that was added to the Toolkit for mechanical DFMA users who happened to have PCBs. The BDI PCB tool is described here for completeness, but is not considered in the tool evaluation section.

The PCB routine operates like a spreadsheet, calculating the cost of assembly by multiplying the number of parts inserted in a given part and process category by that category's cost per insertion and summing over all part categories. The cost of some process operations, such as wave solder, are simply added to the bottom line since the costs are considered fixed regardless of the number of parts on the board. All cost per insertion, time per insertion (for manually inserted components) and cost per operation data is stored in a database that can be modified by the user.

In summary, the BDI Manual DFMA tool has been proven to be effective in assessing ease of assembly relative to the manual-assembly process. It is most effective when a prototype is available to analyze. It is often argued that a good design for manual assembly is a good design for automated assembly and vice versa. This may be a convenient coincident for some automatic assembly processes, but the argument clearly does not hold for many of the automated PCB assembly processes which have no manual counterpart, such as surface mount and wave solder.

## 4.2. The Texas Instruments/BDI PCB DFMA Tool

This tool is a cleaned-up version of a program that TI has been using in-house for several years. It is based on a standard parts database that can be customized by the user. When fed a parts list, it calculates four PCB assembly metrics: PCB density, maximum board height, the ratio of auto-insert parts to manual insert parts, and the number of parts with special quality or handling requirements.

The heart of this tool is the parts database. Organized by part name, the part database is supplied with the most common electronic parts already entered and it can be modified and expanded by the user. The database contains information on the dimensions of each part, the assembly processes needed to assemble each part to the PCB, and a field for special-handling or quality-problem codes related to each part.

In addition to predicting possible board sizing conflicts, this tool has the ability to incorporate user specific lessons learned, indexed by part. This software tool was first released in October of 1991 without the ability to handle surface mount parts and processes. A surface mount version was due to be released in mid December of 1991.

#### 4.3. Rules-in-the-Tools

Rules-in-the-tools [2, 20] refers to the incorporation of design constraints in computer aided design (CAD) tools. Whereas the TI tool aids the electrical design engineer in selecting components, CAD tools with built-in rule checking are used by draftsmen and engineers for PCB layout. For instance, a PCB layout CAD tool would not allow surface mount components to be mounted too close together or too close to the edge of a board. This is simply an automated implementation of the rules and specifications that most electronics manufacturers have written in design documents. With the proliferation of personal computers and workstations, there are literally hundreds of PCB design software packages on the market [15]. Most offer design rule verification (clearances and orientation) and schematic-to-layout checking. Some go far beyond the simple layout considerations and address complex and application specific issues, e.g. radio frequency and microwave simulations of microstrip and stripline designs.

When the design rules are written on paper, it is easy to accidentally violate them, or treat them as design guidelines instead of design rules. The rules-in-the-tools methodology effectively brings the specification information to the right place at the right time. By never granting the designer illegal degrees of freedom, complex design tasks can become less frustrating.

## 4.4. Product Design Specifications and Checklists

As mentioned above, design specifications are the written guidelines that every design engineer is expected to follow when developing a product. Most manufacturers have internal design specifications based on their own production experience as well as external standards such as part dimensions and material properties. For example, The Institute for Interconnecting and Packaging Electronic Circuits (IPC) publishes a widely accepted

standard, IPC-D-275, for the design of PCBs [16]. Adopted by the Department of Defense and the American National Standards Institute, IPC-D-275 addresses issues such as conductor spacing, land pattern design, laminate materials, component layout, and design for test. These guidelines are often violated in state of the art applications that push the process limits. In these instances a method for making tradeoffs among the different guidelines is needed, i.e., a list of guidelines is insufficient.

A checklist is a list of questions that verify conformance to design specifications and conformance to product development procedures. The lists allow a systematic review of the appropriate specification and procedures in a design review or audit. Examples of checklist questions for a circuit board layout audit include:<sup>3</sup>

Are all holes standard sizes?

Are all holes 1.5 times the laminate thickness from the board edge?

Have copper areas been waffled on the wave side? (so that the solder mask