## Fabrication and Electrical Characterization of BESOI

by

#### Mousumi Bhat

B.Tech., Indian Institute of Technology(1988) M.S., University of Maryland, College Park(1990)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### September 1991

| <b>©</b> | ${\bf Massachusetts}$ | Institute | of Technology | 1991. | All rights | reserved |

|----------|-----------------------|-----------|---------------|-------|------------|----------|

|----------|-----------------------|-----------|---------------|-------|------------|----------|

| Author           | PPPPPPP                                                               |

|------------------|-----------------------------------------------------------------------|

|                  | ent of Electrical Engineering and Computer Science                    |

|                  | September 5th, 1991                                                   |

| Certified by     | · · · · · · · · · · · · · · · · · · ·                                 |

|                  | Martin A. Schmidt                                                     |

| Assistant Profes | sor of Electrical Engineering and Computer Science  Thesis Supervisor |

|                  | Thesis Supervisor                                                     |

| Accepted by      |                                                                       |

|                  | C.L.Searle                                                            |

| Chairma          | n, Departmental Committee on Graduate Students                        |

|                  | MASSACHUSETTS INSTITUTE OF TECHNOLOGY                                 |

NOV 0 4 1991

**ARCHIVES**

64 LIBHAHIES

#### Fabrication and Electrical Characterization of BESOI

by

#### Mousumi Bhat

Submitted to the Department of Electrical Engineering and Computer Science on September 5th, 1991, in partial fulfillment of the requirements for the degree of

Master of Science

#### Abstract

The development of a method for preparation of Silicon-On-Insulator by the Bond and Etch-back technique is reported in this thesis. Targets set for the project were good oxide quality and superior quality of device layer silicon.

Experiments were performed on SiGe, SiGeB and boron-doped layers as etchstops and  $KOH: H_2O$  and  $NH_4OH: H_2O$  as etchants, to decide on the optimum combination of etch-stop and etchant. Etching conditions were varied to obtain the set of parameters which gave the best wafer surface and good stopping on the etchstop.

Assessment of the quality of the BESOI substrate was done through electrical measurements and defect analysis. Leakage current measurements and breakdown measurements were performed to evaluate the oxide quality. Leakage currents of the order of picoamperes were obtained. The oxide did not degrade at voltages as high as 350V. IR inspection of the bonded interface showed good bonding. Thickness uniformity measurements across the wafer showed a thickness variation of  $\pm 300 \text{\AA}$ . Defect-etch studies and optical microscopy indicated good device layer quality.

Thesis Supervisor: Martin A. Schmidt

Title: Assistant Professor of Electrical Engineering and Computer Science

#### Acknowledgments

First of all I would like to thank my advisor Professor Martin Schmidt for all the help, guidance and constant encouragement he provided during the course of this research. In addition to his support, the independence he gave me in doing my research, helped me build confidence in my convictions. For this, I shall be ever grateful to him. His help in the timely editing of the thesis will not be forgotten.

I would also like to thank Professor R. Reif, Professor D.A. Antoniadis and Professor J. Chung for their helpful suggestions and guidance.

My team-mates Vince, Javad, Mike, Mark and Chris have contributed in a big way by providing me with various perspectives of graduate life at MIT. Conversations with them was always an eyeopener.

This work was fully funded by the Semiconductor Research Corporation, contract# 90-SP-080. Special thanks go to members of SRC for their participation in the project, to Pat for being an excellent secretary and to Octavio Hurtado, Tim Tyson and Rob Cuikay for their help and patience during processing.

Finally, I would like to express my gratitude to my husband, Naveen, who was with me through thick and thin and without whose constant love and support the completion of this thesis would have been difficult.

## Contents

| 1 | SI  | LICON ON INSULATOR TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (   |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 1.1 | SOI Performance Advantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10  |

|   | 1.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11  |

|   | 1.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12  |

| 2 | BE  | SOI: SALIENT FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14  |

|   | 2.1 | SOI by Wafer Bonding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14  |

|   |     | 2.1.1 Wafer Preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14  |

|   |     | 2.1.2 Wafer Bonding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16  |

|   |     | 2.1.3 Wafer Thinning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16  |

|   | 2.2 | C' 10 CT. I D. I D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17  |

|   | 2.3 | Conventional Etch-Back Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19  |

|   | 2.4 | The Lagrangian and the Lagrangia | 20  |

|   |     | 0.41 Ft 1.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20  |

|   |     | 0.40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22  |

|   | 2.5 | Requirements for an Optimized Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23  |

| 3 | EX  | PERIMENTAL PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24  |

|   | 3.1 | Etch-Stop Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24  |

|   |     | 3.1.1 Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26  |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27  |

|   | 3.2 | Fell (CI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29  |

|   | 3.3 | Madadal Observation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R 1 |

|   | 3.4                                   | Electi  | rical Characterization                  | 33  |

|---|---------------------------------------|---------|-----------------------------------------|-----|

|   |                                       | 3.4.1   | Fabrication Summary                     | 33  |

|   |                                       | 3.4.2   | Leakage Current Measurements            | 33  |

|   |                                       | 3.4.3   | Breakdown Measurements                  | 35  |

|   |                                       | 3.4.4   | Capacitance-Voltage Measurements        | 35  |

| 4 | FA]                                   | BRICA   | ATION RESULTS                           | 36  |

|   | 4.1                                   | Etch-   | Stop Results                            | 36  |

|   | 4.2                                   | Etcha   | ant Results                             | 39  |

| 5 | BES                                   | SOI: S  | UBSTRATE PROPERTIES                     | 42  |

|   | 5.1                                   | Mater   | rial Characteristics                    | 42  |

|   |                                       | 5.1.1   | SEM Inspection Results                  | 42  |

|   |                                       | 5.1.2   | Defect Etch Results                     | 44  |

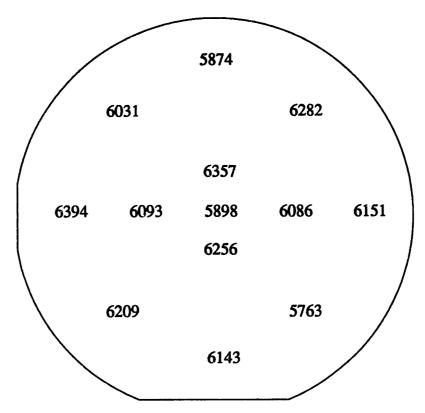

|   |                                       | 5.1.3   | Uniformity of Wafer Thickness           | 44  |

|   | 5.2                                   | Electr  | ical Characterization                   | 46  |

|   |                                       | 5.2.1   | Interface Quality                       | 46  |

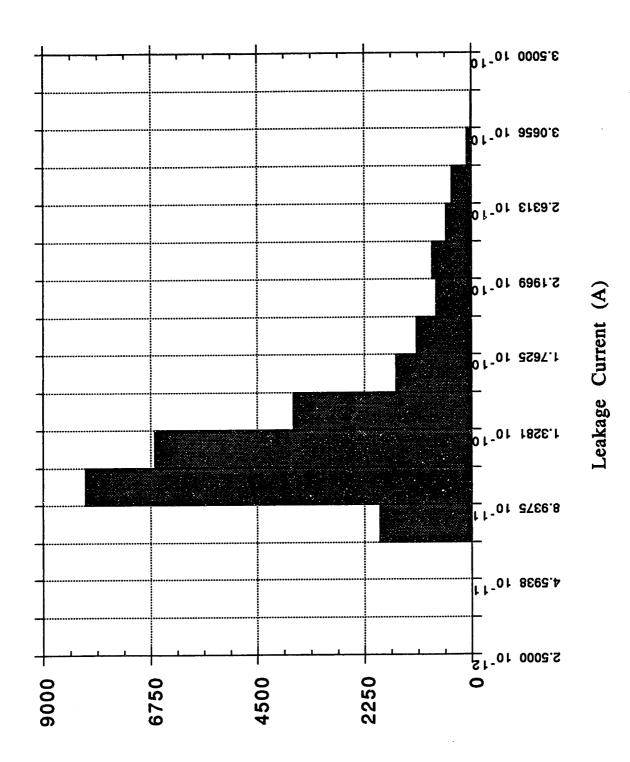

|   |                                       | 5.2.2   | Leakage Current Measurement Results     | 47  |

|   |                                       | 5.2.3   | Breakdown Voltage Measurement Results   | 47  |

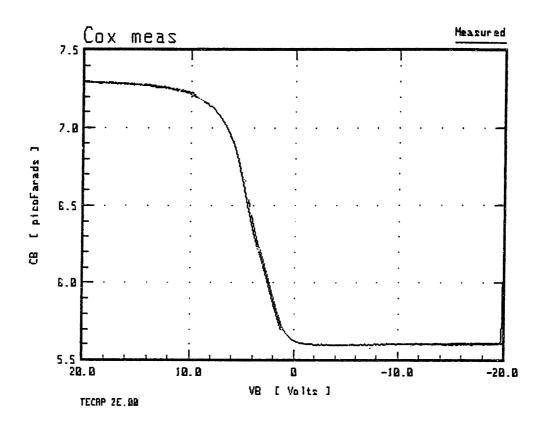

|   |                                       | 5.2.4   | Capacitance-Voltage Measurement Results | 47  |

| 6 | COI                                   | NCLU    | SIONS                                   | 51  |

| A | Etch rates of $Si$ and $SiO_2$ in KOH |         |                                         | 53  |

| В | REF                                   | LUX     | CONDENSER                               | 55  |

|   | B.1                                   | Part L  | ist                                     | 56  |

| С | PRO                                   | CED     | URE: Preparation of BESOI Substrate     | 62  |

| D | Step                                  | s for I | Fabrication of Capacitors on RESOI      | 0.4 |

## List of Figures

| 1-1 | An SOI CMOS circuit                                                              | 9  |

|-----|----------------------------------------------------------------------------------|----|

| 2-1 | Fabrication sequence for preparation of BESOI                                    | 15 |

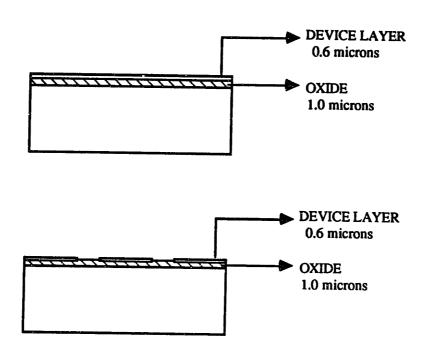

| 2-2 | Control of film uniformity by etch-back technique                                | 18 |

| 3-1 | Experimental sequence                                                            | 25 |

| 3-2 | Expected plot                                                                    | 26 |

| 3-3 | Test samples                                                                     | 28 |

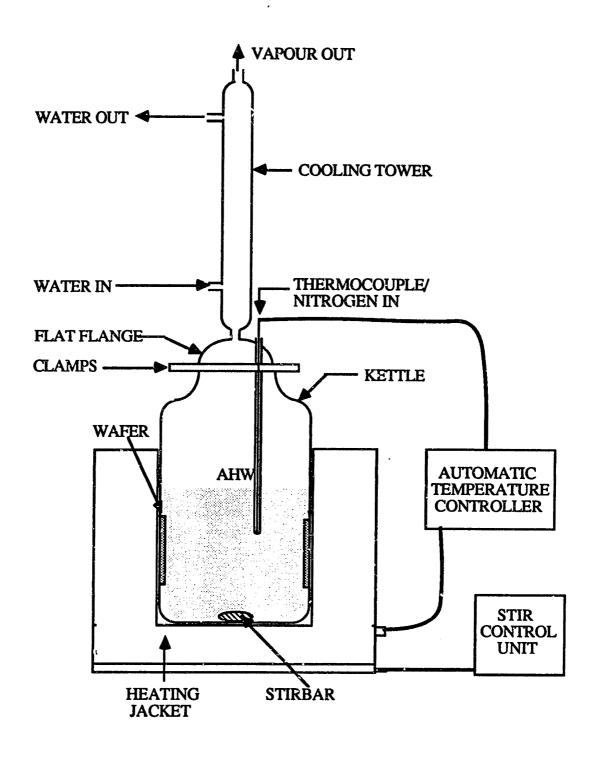

| 3-4 | Schematic of Reflux Condenser                                                    | 32 |

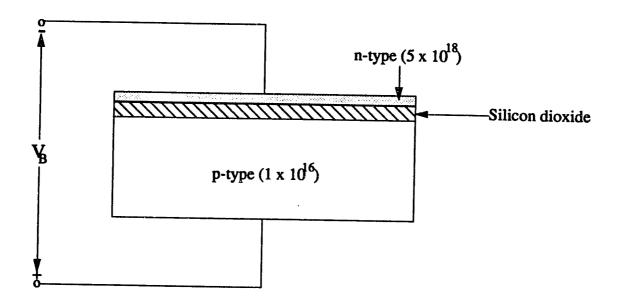

| 3-5 | Fabrication of capacitors: starting material and final structure                 | 34 |

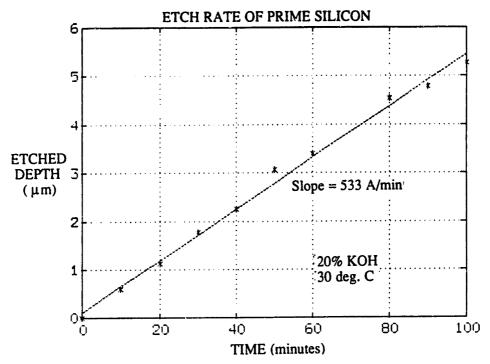

| 4-1 | Calibration etch                                                                 | 37 |

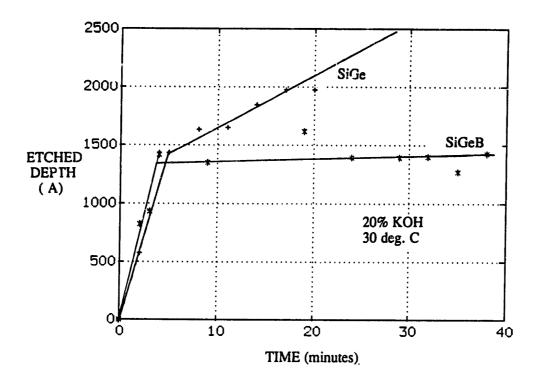

| 4-2 | Comparison of etch-selectivities of $Si_xGe_{1-x}$ and $Si_xGe_yB_{1-x-y}$ etch- |    |

|     | stop layers                                                                      | 38 |

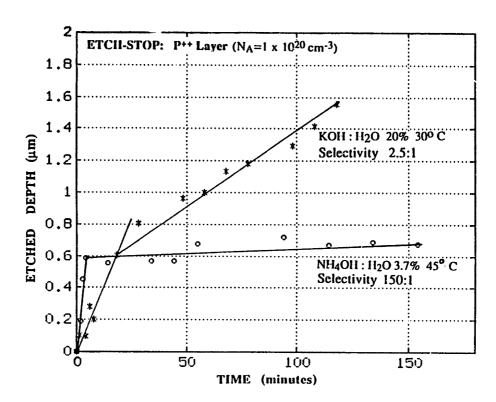

| 4-3 | Comparison of etch-selectivity of AHW and KOH as etchants                        | 40 |

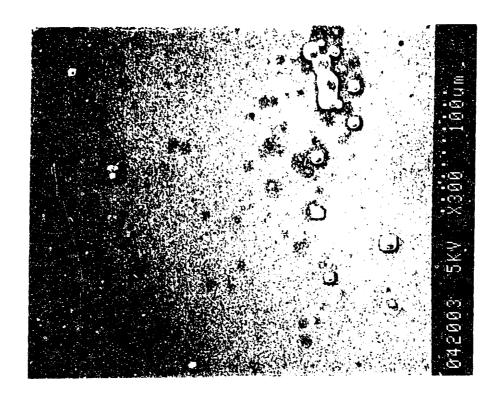

| 5-1 | SEM picture of BESOI wafer surface                                               | 43 |

| 5-2 | SEM picture of magnified defect                                                  | 43 |

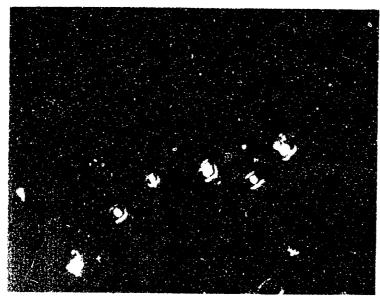

| 5-3 | Etch pits on BESOI waser surface (linear magnification: 400)                     | 44 |

| 5-4 | Defect-etched surface of BESOI wafer surface (linear magnification: 400)         | 45 |

| 5-5 | Defect-etched surface of prime wafer surface (linear magnification: 200)         | 45 |

| 5-6 | Measure of thickness uniformity across the wafer                                 | 46 |

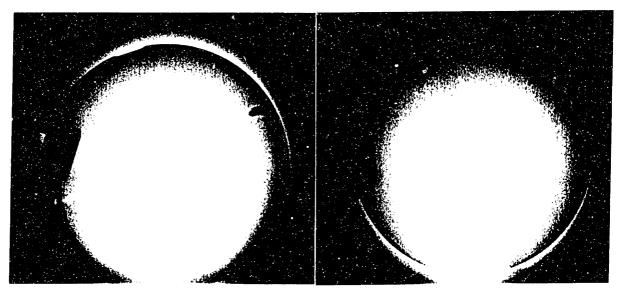

| 5-7 | IR picture of bonded interface before and after anneal                           | 47 |

| 5-8 | Distribution of leakage current                                                  | 48 |

| 5-9 | Capacitor structure and connections for C-V measurements                         | 40 |

| ••  | 5-10 | High-frequency plot of capacitance against voltage | 50 |

|-----|------|----------------------------------------------------|----|

| er. | B-1  | Schematic of reflux condenser setup                | 57 |

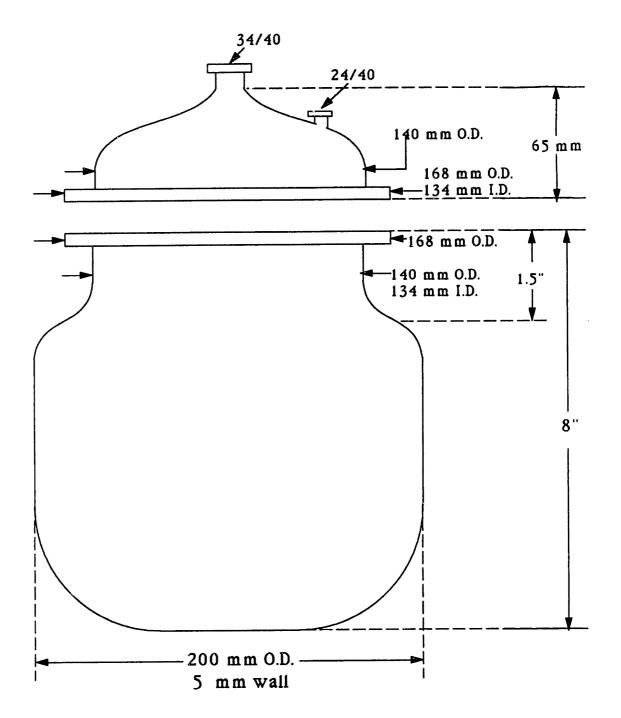

|     | B-2  | Detailed diagram of reflux condenser               | 58 |

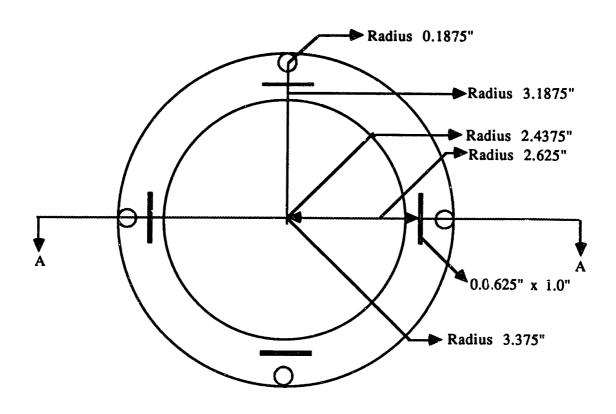

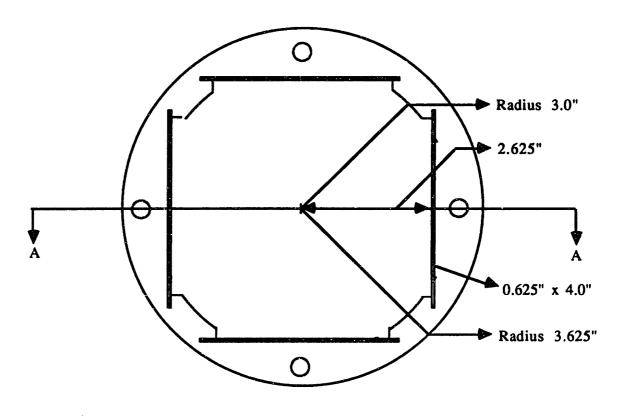

|     | B-3  | Top view of bottom plate of teflon jig             | 59 |

|     | B-4  | Top view of top plate of teflon jig                | 60 |

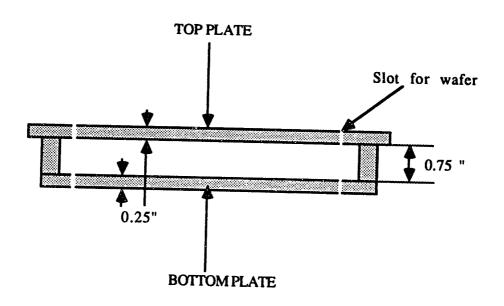

|     | B-5  | Cross section of teflon jig                        | 61 |

## List of Tables

| 4.1 | Summary of etch-selectivities of different etch-stop materials: Etch at |    |

|-----|-------------------------------------------------------------------------|----|

|     | $30^{\circ}C$ in $20\%$ $KOH: H_2O$                                     | 37 |

| 4.2 | Effect of germanium concentration on etch-selectivity: Etch at 45°C     |    |

|     | in $3.7\% NH_4OH : H_2O$                                                | 39 |

| A.1 | $< 100 > { m silicon\ etch\ rate\ in\ } \mu{ m m/hr}$                   | 54 |

| A.2 | < 100 > silicon-dioxide etch rate in nm/hr                              | 54 |

| D.1 | Silicon Plasma Etch (Recipe #10)                                        | 65 |

## Chapter 1

# SILICON ON INSULATOR TECHNOLOGY

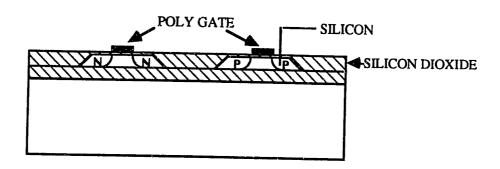

There has been a growing interest in Silicon On Insulator (SOI) substrates over the past few years. The advantages of SOI devices over bulk devices have impact in markets such as military, high temperature and power electronics. The factors that make SOI subtrate attractive have been pointed out by several groups who are actively involved in SOI research [1, 2, 3]. The advantages of SOI material can be seen by comparing a bulk CMOS circuit against an SOI CMOS circuit: fig.(1-1). The following section highlights some of the obvious advantages of SOI over bulk CMOS.

Figure 1-1: An SOI CMOS circuit

## 1.1 SOI Performance Advantages

There are many advantages of CMOS SOI circuitry over bulk CMOS circuits. As indicated in fig. (1-1):

- 1. Complete dielectric isolation: SOI technology allows for complete isolation of closely spaced components. This feature helps one to get around problems like latch-up in CMOS which limit the scaling of geometry. With the reduction in device size and separation, isolation between devices becomes difficult. For submicron structures, conventional bulk isolation no longer works. In the SOI structures, one can etch away the silicon between devices and fill it up with silicon dioxide. This kind of isolation technique allows the spacing between devices to be the minimum feature size. The overall effect of this is increased packing density.

- 2. Low capacitance: In thin film SOI structures, the source and drain regions extend all the way to the buried  $SiO_2$  layer. Thus there is no junction at the bottom of the source/drain implants. In addition, the side walls can extend to an  $SiO_2$  layer. All these features lead to a reduction in the junction area, hence the junction capacitance. The RC time constant is reduced providing for high operating speeds and low dynamic power consumption.

- 3. Radiation hardness: SOI devices first found their place in military applications due to the property of radiation hardness. Incident radiations such as protons, alpha particles, gamma rays and x-rays generate electron-hole pairs in the material. These charges collect at nodes in the circuit giving rise to "soft errors". In SOI structures, the dielectric layer protects the electrons and holes from collecting in the active devices.

- 4. Fully depleted MOSFETs: SOI technology allows for the fabrication of very thin film substrates thus creating a potential for the fabrication of fully depleted MOSFETs. Fully depleted MOSFETs exhibit many attractive properties such

as low electric fields, high transconductance, excellent short-channel behavior and a quasi-ideal subthreshold slope.

5. New technologies: SOI technology opens up the field for the fabrication of a whole new array of novel structures like power devices, transducers, and 3-D circuits.

#### 1.2 SOI Technologies

Many technologies have been developed for producing a film of single-crystal silicon on top of an insulator (usually Silicon Dioxide). The four major techniques used for fabricating SOI substrates are: Zone Melting Recrystallization (ZMR), Full Isolation by Porous Oxidation (FIPOS), Separation by Implantation of Oxygen (SIMOX) and Direct Wafer Bonding (DWB) [1, 2, 3].

SOI generated by the ZMR technique involves scanning a focused laser beam/e-beam/graphite-strip-heater across the surface of a polysilicon layer deposited on an oxide surface. The polysilicon melts and recrystallizes as large grains of crystalline silicon. The limitation of the ZMR techniques lies in the fact that rapid cooling of the melted zone causes defects to be generated near the seed.

A technique for forming SOI using porous oxidized silicon has been developed and is called FIPOS. Phosphorus islands are first implanted in the p-type silicon wafer. An anodic reaction in HF is then used to transform the 'p' region surrounding the phosphorus implants to porous silicon. The porous silicon is then selectively oxidized. The final structure is obtained after annealing for oxide densification. FIPOS stands as inexpensive material which offers variable thickness of the insulator and good crystalline quality. Fabrication and material quality issues have limited the use of this material.

SIMOX is prepared by implanting high oxygen doses into a silicon wafer. Most of the residual defects in the device layer can be removed during a post-implant high temperature anneal. SIMOX material is a good candidate for VLSI and rad-hard applications because of its reproducibility. However, cost of fabrication is high due

to the need for a high current implanter.

An SOI wafer prepared by the DWB technique is produced by bonding together two wafers, a handle wafer and a device wafer, and then thinning the device wafer back to the required thickness. The process begins when a thermal oxide is grown on the handle wafer and/or the device wafer. After a surface hydration step, these ultraflat surfaces are brought in contact. The Van-der-waal forces hold the two smooth surfaces in contact. These wafers are then annealed at high temperature at which time the bonding of the two wafers occurs. The device wafer is then thinned back to produce the SOI material by the DWB technique.

The Bond and Etch-Back technique for making SOI material (BESOI) uses the DWB technique followed by a chemically selective etch to thin the device wafer. The device wafer is thinned by etching away the excess silicon with an anisotropic etchant. The etching stops at an etch-stop layer. The etch-stop layer is then removed with another selective etchant producing the SOI structure.

BESOI technique has advantages over other techniques for forming SOI since it produces a bulk quality single-crystal-silicon device layer and a thermal oxide quality insulator. The device layer does not have to undergo implantation damages as in the case of SIMOX and the insulator sandwiched between the silicon layers is thermally grown  $SiO_2$  rather than  $SiO_x$  as in the case of SIMOX. The excellent quality of the device layer and the insulator obtained by the BESOI technique makes this technology potentially superior to the others. Hence, optimization of the BESOI process steps and evaluation of the substrate quality has been chosen as the goal of this thesis. The next chapter presents a detailed discussion of BESOI.

#### 1.3 Objective and Layout of Thesis

The aim of this thesis is to illustrate the importance of the Bond and Etch Back technique for the fabrication of SOI substrate with particular focus on the formation of thin layers ( $< 1\mu m$ ). The thesis presents methods of characterizing etch-stop materials and etchants that are used during the fabrication sequence. Finally, material

and electrical evaluation of the substrate is done to assess the quality of the material.

The body of the thesis is divided into five principal chapters.

- Chapter II is a review of SOI prepared by the Bond and Etch Back technique.

This chapter discusses the significance of the bond and etch back method and throws light on the salient features of fabrication.

- Chapter III is an illustration of the experiments done for characterization of the etch-stop material and the etchant. It also includes the methods used for evaluation of the substrate quality.

- Chapter IV has experimental results and discussions of the observations made.

It sets the milestones for the standardized procedure for fabrication of the BE-SOI substrate.

- Chapter V presents the electrical and material properties of the samples prepared at MIT.

- Finally, the main conclusions and suggestions for future work are summarized in Chapter VI.

## Chapter 2

## **BESOI: SALIENT FEATURES**

This chapter has two important objectives. The first is to present some of the conventional techniques used for the fabrication of BESOI. Each of the process steps involved in the fabrication are described and a summary of the popularly used process flow is presented. The second section of the chapter points out the advantages and disadvantages of individual processes or materials. Reasons that make BESOI a more attractive fabrication technique as compared to other popularly used techniques are also illustrated.

## 2.1 SOI by Wafer Bonding

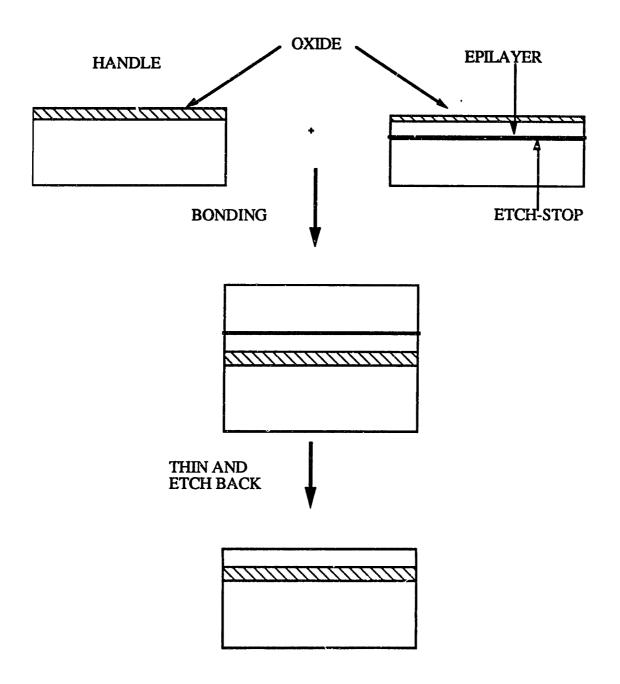

SOI wafers are created in three basic steps: (i) preparation of the handle wafer and the device wafer, (ii) contacting the polished faces of the two wafers and bonding them, (iii) thinning the seed wafer back to the desired thickness fig(2-1).

#### 2.1.1 Wafer Preparation

Two wafers, the handle wafer and the device wafer, are needed to produce a BESOI substrate. The handle wafer is usually n/p-type prime grade silicon. A layer of thermal  $SiO_2$  is grown on the handle wafer, where this layer will form the insulator in the SOI structure.

Preparation of the device wafer is more complicated. Depending on the thin-

Figure 2-1: Fabrication sequence for preparation of BESOI

ning mechanism used, the device wafer goes through different kinds of preparation steps. Wafer-thinning may be done mechanically or chemically. Mechanical thinning involves the formation of a polish-stop in the device wafer [4]. The polish-stop is usually an imbeded grid of slow polishing material. In the case of chemical etch-back, an etch-stop layer has to be incorporated in the device wafer by epitaxy, implantation or diffusion. An epi-layer is then grown on top of the etch-stop layer. This is the layer which eventually forms the device layer.

#### 2.1.2 Wafer Bonding

Two mirror polished wafers are hydrated to form hydrophillic surfaces, brought together at room temperature, and then annealed at high temperature when the oxide flows and forms a permanent bond. The handle wafer usually has a layer of thermally grown silicon dioxide which electrically isolates the handle wafer and the device wafer. When the ultraflat surfaces are brought in contact at room temperature, Van der Waals forces caused by the mutual interaction of all the induced dipoles on both wafers results in an attractive force that keeps the wafers in contact. The bond strength increases monotonically with temperature. The proposed reaction that occurs at the interface is as follows:

$$\equiv SiOH + HOSi \equiv \Longrightarrow Si - O - Si + H_2O \tag{2.1}$$

The viscous flow of oxide at higher temperatures leads to complete bonding [4, 7, 8])

#### 2.1.3 Wafer Thinning

In the mechanical polishing technique, the bonded wafer pair is supported on a polishing machine, the exposed surface of the handle wafer is used as a reference and the device wafer is mechanically lapped. Since lapping causes sub-surface damage, the subsurface layer is removed by a chemomechanical polishing techniques. This is done by tribochemical polishing [7]. However, it is hard to obtain submicron thick layers with uniform thickness, since the reference surface (handle wafer) may itself

be non-uniform in thickness, causing the non-uniformity to propagate. In practice, manufacturers have been able to achieve  $\pm 0.3 \mu \mathrm{m}$  thickness control by using a handle wafer with comparable total thickness variations.

Chemical etching helps to solve the problem of non-uniformity. The wafer is mechanically polished till very close to the etch-stop layer and then it is chemically etched in a solution which has a high etch-selectivity to the etch-stop material. The etching process can be summarized by the following reaction

$$Si + 2OH^{-} + 2H_{2}O \Longrightarrow SiO_{2}(OH)_{2}^{--} + 2H_{2}$$

(2.2)

## 2.2 Significance of Etch-Back Process

Most of the methods used for producing SOI substrates have several drawbacks. The first category includes laser recrystallization and selective epitaxy. The quality of the silicon layer is inferior to that normally associated with bulk silicon processing. The second category is comprised of methods which form an oxide layer beneath an existing high quality silicon layer. Examples are FIPOS and SIMOX. These methods result in inferior quality of oxide and also degradation of the silicon top layer during oxide formation.

SOI formed by wafer bonding helps get around the drawbacks of the above methods. The oxide in the case of wafer bonded SOI is thermally grown and hence of better quality than implanted  $SiO_x$ . The device layer is epitaxially grown on bulk silicon and hence not degraded from its original quality. Another attractive feature of SOI prepared by the bond and etch-back technique is the fact that it allows for the fabrication of ultrathin device layers with excellent uniformity of thickness across the wafer.

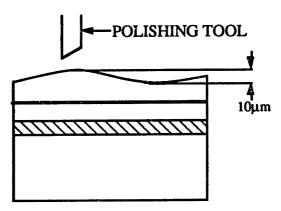

The reason for the excellent controllability of film thickness and uniformity is demonstrated in fig(2-2). We start with a wafer that has a certain amount of non-uniformity and chemically etch it back. If, for example, the non-uniformity is  $10\mu m$ , and the selectivity of the etch-stop layer is 100:1, then over time as etching proceeds,

#### **MECHANICALLY POLISHED WAFER**

#### AFTER ETCHING IN ETCH SOLUTION

SELECTIVITY = 100:1

NON-UNIFORMITY =  $0.1 \, \mu m$

Figure 2-2: Control of film uniformity by etch-back technique

the non-uniformity gets reduced to  $10/100 = 0.1 \mu m$ . If we now use another selective etchant of selectivity 10:1 to remove the etch-stop layer, then the non-uniformity can furthur be reduced to  $(.1/10)\mu m$ . Hence as is obvious from the above discussion, the higher the selectivity of the etch-stop, the higher is the degree of uniformity obtainable.

#### 2.3 Conventional Etch-Back Process

The standard procedure used for the etch-back process is as follows.

- Thermal oxide is grown on the handle wafer.

- An etch-stop layer, usually a heavily doped boron layer with concentration higher than 10<sup>20</sup>cm<sup>-3</sup>, is diffused, implanted, or epitaxially grown onto the device wafer, followed by the epitaxial growth of a lightly-doped layer.

- A thin oxide may or may not be grown on the device wafer.

- The wafers are brought together on their polished surfaces and bonded at 1000°C.

- The silicon on the device wafer end is mechanically polished to within a few microns of the etch-stop layer.

- The remaining silicon is removed with an anisotropic etchant like aqueous KOH,

CsOH, Ethylene Diamine Pyrochatecol(EDP) or Hydrazine.

- The etch-stop layer is then removed using an 8:3:1 solution of acetic acid, nitric acid and hydrofluric acid giving us the final structure [5].

- Surface staining caused by the formation of  $SiO_x$  is removed in  $HF KMnO_4$  solution [7].

#### 2.4 Etch-Stops and Etchants Used in Thesis

In this section the advantages and disadvantages of the etch-stop material and etchants investigated as a part of the thesis are discussed.

#### 2.4.1 Etch-Stops

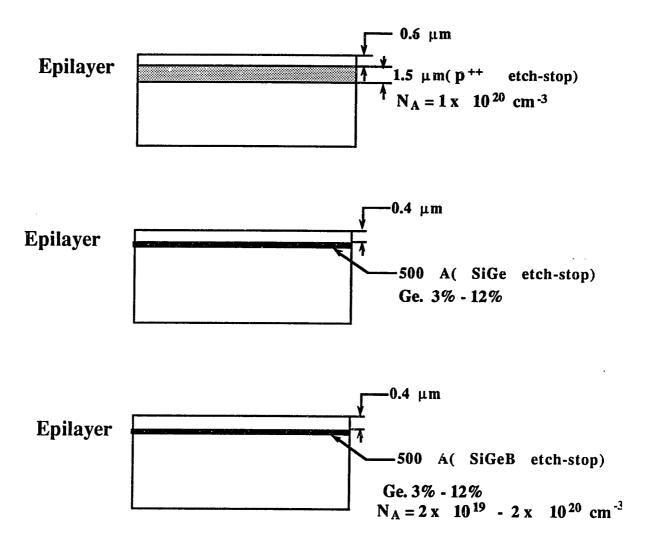

The etch-stop materials that we have investigated are (i) heavily boron-doped layers (concentrations >  $10^{20}cm^{-3}$ ), (ii) Strained Silicon-Germanium ( $Si_xGe_{1-x}$ ) layers, (iii) Silicon-Germanium layers doped with boron ( $Si_xGe_yB_{1-x-y}$ ).

#### Boron-Doped Layers:

Heavily boron-doped layers with concentrations higher than  $10^{20}cm^{-3}$  form excellent etch-stops. Researchers have noted etch-selectivities of  $p^+$  layer to silicon in excess of 100:1. These high doses of boron can be incorporated by implantation or by solid source diffusion of boron using BN or  $B_2O_3$  dopant wafers at  $1100^{\circ}$  C. The solid solubility of boron in silicon being higher at elevated temperatures yields a surface concentration as high as  $2 \times 10^{20}cm^{-3}$  [9]. Finally it is possible to grow the etch-stop layer epitaxially and successfully obtain concentrations in excess of  $10^{20}cm^{-3}$  [6].

However, there are several problems associated with using such high boron concentrations. The first disadvantage arises from the tensile stresses in silicon introduced by the high concentration of boron. At boron concentrations higher than  $8 \times 10^{19} cm^{-3}$ , misfit dislocations start to form due to the stress, which is believed to be caused by the differing atomic radii of boron in comparison to silicon. Since the device layer is grown epitaxially on the  $p^+$  layer, the epi-layer will have dislocations which are imprints of the heavily doped layer. A related problem arises when a secondary etchant is used to remove the etch-stop layer. The defects in the epi-layer get decorated and etch-pits begin to form on the surface of the epi-layer. Another major handicap of using heavily doped boron layer is the problem of out-diffusion of boron during high temperature processes like bonding and growth of the epi-layer. Out-diffusion of boron not only lowers the peak concentration and hence reducing etch-selectivity,

it also dopes the epi-layer. Furthermore, if the boron is implanted into the sample to create the etch-stop layer, then the device layer will have residual defects due to ion bombardment.

#### Silicon-Germanium Layers:

Silicon-germanium is found to form a good etch-stop [11, 12, 13]. The etch-stop layer consists of a strained  $Si_{0.7}Ge_{0.3}$  layer. Using a selective etchant that attacks the silicon over the  $Si_xGe_{1-x}$  layer selectively, Godbey et.al. [12] have managed to produce BE-SOI films with silicon film thickness between  $0.2 - 0.3 \mu m$ . Silicon-germanium layers were found to present etch-selectivity of 17:1. Thermal studies indicated that high temperature altered the selectivity only slightly. Advantages of silicon-germanium layers over boron doped layers are: silicon-germanium layers produce defect free device layers, thermal cycles do not alter etch rates [12] and problems of out-diffusion do not exist. However, silicon-germanium does not form as excellent an etch-stop as boron does. It has been observed that higher germanium concentrations form better etch-stops, however, incorporating doses as high as 30% germanium involves complicated processing.

#### Silicon-Germanium-Boron Layers:

Hunt et.al. [14] have shown that using boron doped silicon-germanium layers helps to form good etch-stops with reduced defect density in the epi-layer. Since boron induces tensile strains in silicon and germanium introduces compressive strains, presence of both species in the etch-stop layer compensates the strain. A Ge:B ratio of 3.5:1 was found to form stress compensated layers. Hence, it was possible to have stress compensated layers with high boron concentration and low germanium concentration (3%). These features make the Si-Ge-B layer particularly attractive because the high etch-selectivity due to high boron is retained and the germanium required is only 3%. However, the problem of boron out-diffusion at high temperatures still remains and the step taken by us to reduce this problem are discussed in the next chapter.

#### 2.4.2 Etchants

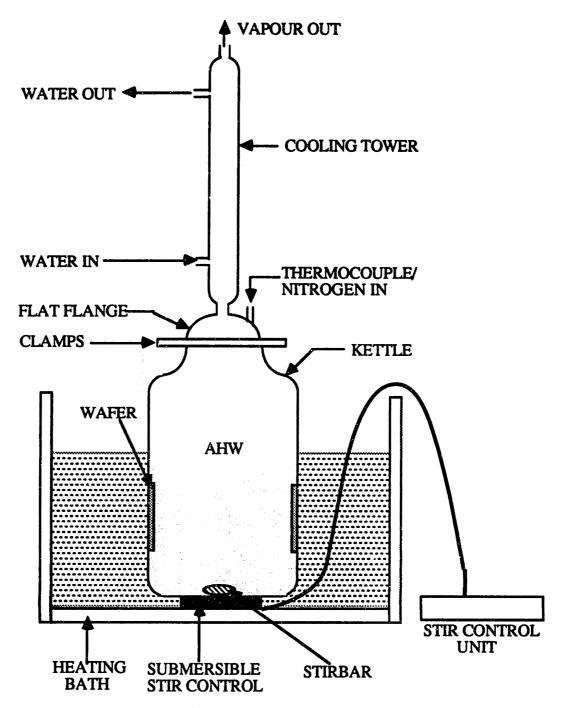

The two etchants investigated in this thesis are aqueous potassium hydroxide and aqueous ammonium hydroxide (AHW) Listed here are their respective advantages and disadvantages. While a number of different etchants have been investigated for BESOI, we chose  $KOH: H_2O$  and  $NH_4OH: H_2O$  solutions because of their ease of handling and minimal safety risk.

#### Aqueous Potassium Hydroxide:

Potassium hydroxide has been extensively used as silicon etchant for micromachining [18, 19, 20, 21, 22, 23]. Advantages of aqueous potassium hydroxide as an etchant are: ease of handling, simple and established process, and it produces smooth etching surfaces. However, aqueous potassium hydroxide is not IC compatible because of the concern of alkali ion contamination. Potassium hydroxide also has a significant silicon dioxide etch rate, posing a problem when  $SiO_2$  is used as an etching mask. Finally, as results presented in chapter 4 will also indicate, potassium hydroxide does not present as high selectivities with  $p^+$  etch-stops as compared to certain other etchants.

#### Aqueous Ammonium Hydroxide:

Ammonium hydroxide not only yields excellent selectivity with  $p^+$  layers [15], it also has the advantage of being IC compatible. Literature reflects that the etch rate of  $SiO_2$  with ammonium hydroxide is very low. Etch rate ratio of  $SiO_2$  to Si of 1:8400 has been reported by Benecke et. al. [15]. Despite all these attractive features of AHW, handling of AHW can be difficult. It is volatile and ammonia evaporates leaving the solution degraded and necessitating the need for a reflux condenser. AHW also has the problem of producing very rough etched surfaces [15, 16, 17]. Ways to get around these problems will be discussed in the following chapters.

## 2.5 Requirements for an Optimized Process

The above discussion can be summarized for the optimum etch-back process that would produce the best quality material.

#### • Etch-Stop Material:

- The etch-stop material should be one that has very high etch-selectivity.

- It should be easy to incorporate in the device wafer.

- It should be one that produces defect free etch-stop layers and hence defect free epi-layers.

- The material should not undergo thermal changes which will worsen its etch-selectivity ratios.

- The etch-stop layer should not affect the epi-layer during subsequent processing steps.

#### • Device Layer:

- The device layer essentially needs to be free of defects. Processing steps should be such that it is possible to control the defect count and contamination from etch-stop layer through the process steps.

- It should be possible to produce very thin device layers with a high degree of thickness uniformity across the wafer.

#### • Etchants:

- The combination of the etchant and the etch-stop material should produce excellent etch-selectivity.

- Etchants should not cause chemical contamination of the substrate.

- Etchant should be easy to handle.

## Chapter 3

## EXPERIMENTAL PROCEDURE

This thesis aims at investigating two major issues regarding SOI prepared by the bond and etch-back technique. The first issue involves characterization of the etch-stop and the etch-back step. The idea is to find the optimum combination of etch-stop materials, etchant and etching conditions. The second criterion is to evaluate the quality of BESOI prepared from the above conditions. Methods used to perform the material and electrical assessment are presented in this chapter. All detailed information about the apparatus and sample preparation are contained in the Appendices of this thesis.

## 3.1 Etch-Stop Characterization

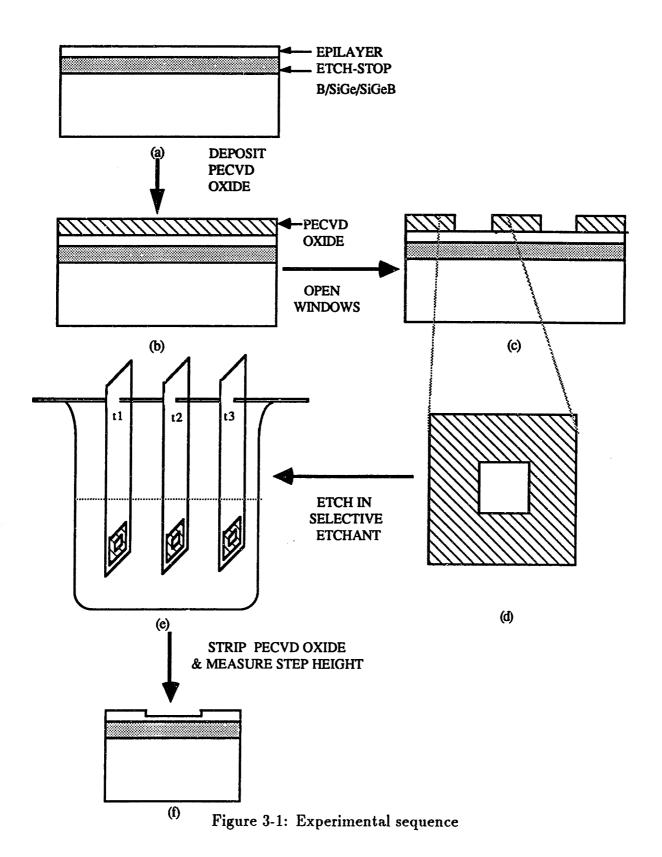

The most important criterion for evaluation of the etch-stop material is to determine its etch-selectivity. To measure the etch-selectivity of the etch-stop material, we have performed experiments by which it is possible to determine the etch rates of the individual layers. The starting material for the experiment is a sample which has the etch-stop layer (Boron,  $Si_xGe_{1-x}$  or  $Si_xGe_yB_{1-x-y}$ ), and an epi-layer of low doped silicon on top of the etch-stop layer fig(3-1a).

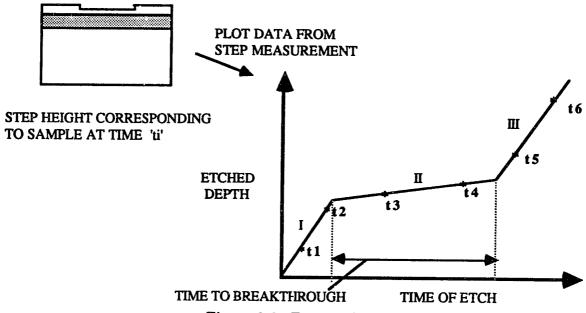

Figure 3-2: Expected plot

#### 3.1.1 Procedure

A layer of PECVD oxide ( $\sim 2.5 \mu m$ ) which acts as an etch mask is deposited on the top of the sample as shown in fig(3-1b). PECVD oxide is used instead of thermal oxide because PECVD oxide can be deposited at 300° C as opposed to thermal oxide which has to be grown at elevated temperatures. It is important to avoid the thermal cycle so that one can preserve the peak of the etch-stop layer. The PECVD oxide mask is then patterned to open square windows (2mm  $\times$  2mm), exposing small areas of silicon fig(3-1c). The wafer is broken into small pieces such that each piece has an exposed area in the center surrounded by the oxide along all four sides fig(3-1d).

These pieces are then mounted on teflon strips that are suspended into the etching solution  $(KOH: H_2O \text{ or } AHW)$  after a brief 7:1 HF dip. The time of etching of each sample piece is monitored and each piece is pulled out after different time intervals fig(3-1e). The oxide layer is then stripped with 7:1 BOE. The etched depth from the unetched silicon surface to the etched silicon surface is then measured using a commercial surface profilometer fig(3-1f). The measured etch-depth is then plotted against time. The expected graph is shown in fig(3-2).

The plot can be explained as follows. Since the etchant sees the lightly doped