## **Extending Memory System Semantics to Accelerate Irregular Applications**

by

Guowei Zhang

B.S. in Microelectronics and B.S. in Economics Tsinghua University (2014)

M.S. in Electrical Engineering and Computer Science Massachusetts Institute of Technology (2016)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2021

© 2021 Massachusetts Institute of Technology. All rights reserved.

Author..... Department of Electrical Engineering and Computer Science December 28, 2020

Certified by..... Daniel Sanchez Associate Professor of Electrical Engineering and Computer Science Thesis Supervisor

Accepted by.... Leslie A. Kolodziejski Professor of Electrical Engineering and Computer Science Chair, Department Committee on Graduate Students

## **Extending Memory System Semantics to Accelerate Irregular Applications**

by

Guowei Zhang

Submitted to the Department of Electrical Engineering and Computer Science on December 28, 2020, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

# Abstract

Computer systems are increasingly bottlenecked by data movement, and rely on sophisticated memory hierarchies to address this issue. However, conventional memory systems suffer from poor performance on many irregular access patterns. This is because memory systems use an inexpressive interface that does not convey sufficient program semantics: they organize data in fixed-sized chunks and access data with only reads and writes. As a result, memory systems incur significant performance loss on several common patterns. In this thesis, we identify three such patterns: accesses to small data fragments suffer poor locality; concurrent updates introduce excessive traffic and serialization; and dependent reads incur long latencies that are on the critical path.

To tackle these issues, this thesis proposes techniques that extend the semantics of the memory system. We apply this insight to address each of the three issues and propose solutions with different degrees of generality. COUP and COMMTM provide general architectural support by exploiting commutative updates to reduce communication and synchronization. COUP supports strict single-instruction commutativity by extending the cache coherence protocol, while COMMTM supports multi-instruction and semantic commutativity by leveraging hardware transactional memory. Whereas COUP and COMMTM are general, HTA and GAMMA target a specific data structure and a specific application, respectively. HTA addresses the inefficiencies of small fragments in the context of hash tables. It exploits the associativity in hash tables and leverages caches to reduce runtime overheads and to improve spatial locality. GAMMA is a sparse matrix-matrix multiplication accelerator. Its novel storage idiom, FIBERCACHE, combines caching and decoupled execution to ensure low latency for dependent reads with irregular reuse. This enables GAMMA to adopt an efficient dataflow, Gustavson's algorithm, to minimize off-chip traffic. In return, these techniques improve the performance and reduce the data movement of challenging applications significantly.

Thesis Supervisor: Daniel Sanchez Title: Associate Professor of Electrical Engineering and Computer Science

# Contents

| Ab | Abstract 3 |                                                  |    |  |

|----|------------|--------------------------------------------------|----|--|

| Ac | know       | vledgments                                       | 9  |  |

| 1  | Intro      | oduction                                         | 11 |  |

|    | 1.1        | Challenges                                       | 11 |  |

|    |            | 1.1.1 Small Fragments                            | 11 |  |

|    |            | 1.1.2 Concurrent Updates                         | 12 |  |

|    |            | 1.1.3 Dependent Reads                            | 12 |  |

|    | 1.2        | Contributions                                    | 12 |  |

|    |            | 1.2.1 COUP                                       | 13 |  |

|    |            | 1.2.2 СоммТМ                                     | 14 |  |

|    |            | 1.2.3 HTA                                        | 15 |  |

|    |            | 1.2.4 GAMMA                                      | 16 |  |

| 2  | Bacl       | kground                                          | 17 |  |

|    | 2.1        | Memory System Architecture                       | 17 |  |

|    |            | 2.1.1 Caches                                     | 17 |  |

|    |            | 2.1.2 Explicitly managed storage structures      | 19 |  |

|    |            | 2.1.3 Summary                                    | 19 |  |

|    | 2.2        | Improving Memory System Performance              | 21 |  |

|    |            | 2.2.1 Improving Locality                         | 21 |  |

|    |            | 2.2.2 Reducing Communication and Synchronization | 22 |  |

|    |            | 2.2.3 Hiding Memory Access Latency               | 23 |  |

| 3  | Cou        | P                                                | 25 |  |

|    | 3.1        | Motivation                                       | 25 |  |

|    | 3.2        | COUP Example: Extending MSI                      | 26 |  |

|    |            | 3.2.1 Structural changes                         | 26 |  |

|    |            | 3.2.2 Protocol operation                         | 27 |  |

|    | 3.3        | Generalizing COUP                                | 29 |  |

|    | 3.4        | Coherence and Consistency                        | 31 |  |

|    | 3.5        | Implementation and Verification Costs            | 32 |  |

|    | 3.6        | Motivating Applications                          | 33 |  |

|    |            | 3.6.1 Separate Update- and Read-Only Phases      | 34 |  |

|    |            | 3.6.2 Interleaved Updates and Reads              | 35 |  |

|   | 3.7  | 7 Evaluation                                            |          |  |

|---|------|---------------------------------------------------------|----------|--|

|   |      | 3.7.1 Methodology 35                                    | 5        |  |

|   |      | 3.7.2 Comparison Against Atomic Operations              | 3        |  |

|   |      | 3.7.3 Case Study: Reduction Variables 39                | )        |  |

|   |      | 3.7.4 Case Study: Reference Counting 40                 | )        |  |

|   |      | 3.7.5 Sensitivity to Reduction Unit Throughput          | 1        |  |

|   | 3.8  | Additional Related Work                                 | 1        |  |

|   | 3.9  | Summary                                                 | 2        |  |

| 4 | Сом  | A 1                                                     | <b>,</b> |  |

| 4 | 4.1  | мТМ 43<br>Motivation                                    |          |  |

|   | 4.1  | 4.1.1         Semantic Commutativity         44         | -        |  |

|   |      |                                                         |          |  |

|   | 4.0  | 5 5                                                     |          |  |

|   | 4.2  | COMMTM Programming Interface and ISA                    |          |  |

|   | 4.3  | COMMTM Implementation                                   |          |  |

|   |      | 4.3.1 Eager-Lazy HTM Baseline 46                        |          |  |

|   |      | 4.3.2 Coherence protocol                                |          |  |

|   |      | 4.3.3 Transactional execution                           |          |  |

|   |      | 4.3.4 Reductions                                        |          |  |

|   |      | 4.3.5 Evictions                                         |          |  |

|   | 4.4  | Putting it all Together: Overheads                      |          |  |

|   | 4.5  | Generalizing COMMTM                                     |          |  |

|   | 4.6  | СоммТМ vs Semantic Locking 53                           |          |  |

|   | 4.7  | Avoiding Needless Reductions with Gather Requests    53 |          |  |

|   | 4.8  | Experimental Methodology 55                             |          |  |

|   | 4.9  | СоммТМ on Microbenchmarks 56                            | 5        |  |

|   |      | СоммТМ on Full Applications 58                          | 3        |  |

|   | 4.11 | Additional Related Work                                 | 1        |  |

|   | 4.12 | Summary                                                 | 2        |  |

| 5 | НТА  | 63                                                      | 2        |  |

| Ū | 5.1  | Motivation                                              |          |  |

|   | 0.1  | 5.1.1 Hash Tables                                       |          |  |

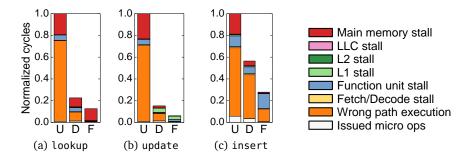

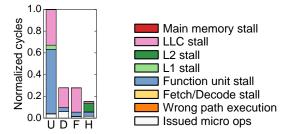

|   |      | 5.1.2 Hash table performance analysis                   |          |  |

|   |      | 5.1.3 Prior work in accelerating hash tables            |          |  |

|   |      | 5.1.4 Memoization                                       |          |  |

|   | 5.2  | HTA Hardware/Software Interface                         |          |  |

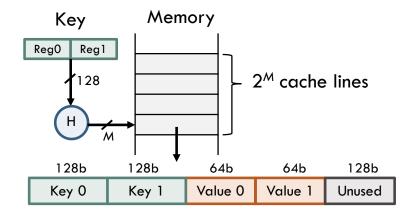

|   | 5.2  | 5.2.1 HTA hash table format                             |          |  |

|   |      | 5.2.2 HTA ISA extensions                                |          |  |

|   |      | 5.2.3 ISA design alternatives                           |          |  |

|   | 5.3  |                                                         |          |  |

|   | 5.3  | 1                                                       |          |  |

|   |      | 5.3.1 Core pipeline changes                             |          |  |

|   |      | 5.3.2 Hardware costs                                    |          |  |

|   |      | 5.3.3 Software path                                     |          |  |

|   | F 4  | 5.3.4 Parallel hash table implementation                |          |  |

|   | 5.4  | HIERARCHICAL-HTA Implementation   72                    |          |  |

|   | 5.5  | HTA-Accelerated Memoization                             |          |  |

|   | 5.6  | Methodology                                             | )        |  |

|    |       | 5.6.1   | Hash table workloads                 | 76   |

|----|-------|---------|--------------------------------------|------|

|    |       | 5.6.2   | Memoization workloads                | 77   |

|    | 5.7   | Evalua  | ation                                | 78   |

|    |       | 5.7.1   | HTA on single-threaded applications  | 78   |

|    |       | 5.7.2   | HTA on multithreaded applications    | 79   |

|    |       | 5.7.3   | HTA with hierarchy-aware layout      | 79   |

|    |       | 5.7.4   | HTA on multiprogrammed workloads     | 80   |

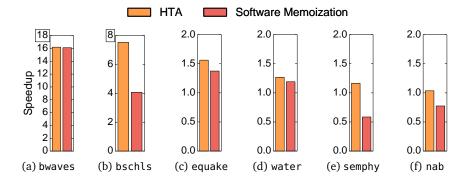

|    |       | 5.7.5   | HTA on memoization                   | . 81 |

|    | 5.8   | Summ    | ary                                  | 84   |

| 6  | GAM   | IMA     |                                      | 85   |

|    | 6.1   | Motiva  | ation                                | 86   |

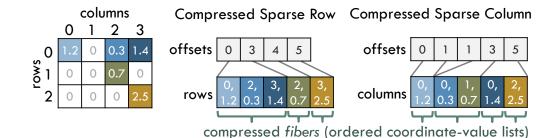

|    |       | 6.1.1   | spMspM                               | 86   |

|    |       | 6.1.2   | Compressed sparse data structures    | 86   |

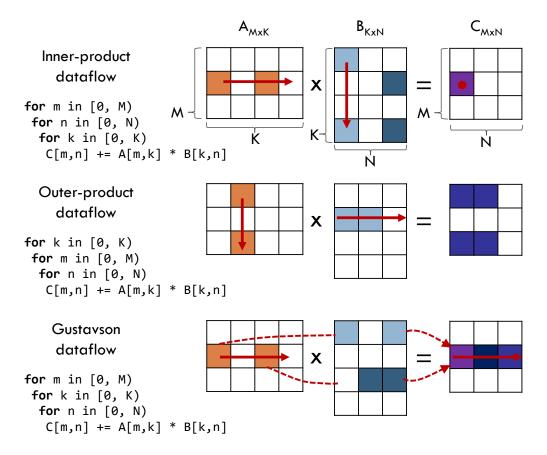

|    |       | 6.1.3   | SPMSPM dataflows                     | 87   |

|    |       | 6.1.4   | SPMSPM accelerators                  | 88   |

|    | 6.2   | Gamm    | Α                                    | 90   |

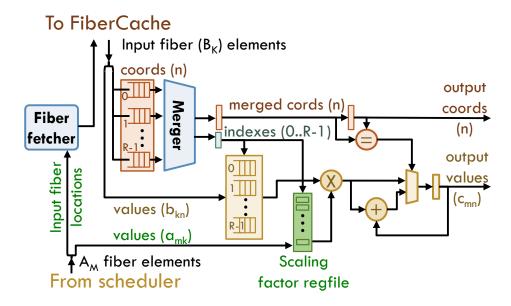

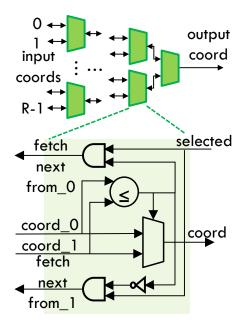

|    |       | 6.2.1   | Processing element                   | 92   |

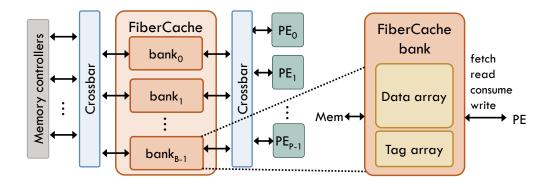

|    |       | 6.2.2   | FIBERCACHE                           | 94   |

|    |       | 6.2.3   | Scheduler                            | 95   |

|    |       | 6.2.4   | Memory management                    | 96   |

|    | 6.3   |         | Decessing for GAMMA                  | 96   |

|    |       | 6.3.1   | Affinity-based row reordering        | 96   |

|    |       | 6.3.2   | Selective coordinate-space tiling    | 97   |

|    | 6.4   |         | dology                               | 98   |

|    | 6.5   | Evalua  | ation                                | 99   |

|    |       | 6.5.1   | Performance on Common-set matrices   | 99   |

|    |       | 6.5.2   | Performance on Extended-set matrices |      |

|    |       | 6.5.3   | Effectiveness of GAMMA preprocessing |      |

|    |       | 6.5.4   | GAMMA area analysis                  |      |

|    | 6.6   |         | onal Related Work                    |      |

|    | 6.7   | Summ    | ary                                  | 103  |

| 7  |       | clusion |                                      | 105  |

|    | 7.1   | Future  | e Work                               | 106  |

| Bi | bliog | raphy   |                                      | 128  |

# Acknowledgments

First and foremost, I owe thanks to my research advisor, Professor Daniel Sanchez. I cannot imagine how this thesis would have happened without his guidance. For me, Daniel is a perfect supervisor. It always amazes me how incredibly knowledgeable and experienced he is. Daniel guided me to the field of computer architecture, and taught me patiently how to conduct research. I learned from him how to think of big picture challenges, formulate research problems, and validate ideas with carefully conducted analysis and experiments as quickly as possible. Daniel provided me enormous freedom, yet he has always been available when I needed his help. In fact, Daniel has been supportive of me no matter what happened, which I shall never forget.

I would like to thank my thesis committee members, Professor Joel Emer and Professor Mengjia Yan. It was my privilege to collaborate with Joel in the GAMMA project. I have benefited so much from his warm and empathetic mentorship and his principled approach to conduct research. Joel taught me the importance of naming: a consistent terminology for diverse research problems and solutions is invaluable as it forces and enables reasoning about the core insights rather than the superficial implementations. Though I have not collaborated with Mengjia on a research project, she has provided me with valuable support and insightful feedback on both my thesis and my teaching experience in the course 6.823.

I am especially grateful to my great co-authors, Webb Horn, Virginia Chiu, and Nithya Attaluri. I have benefited so much from the enjoyable and memorable collaborations with them.

I owe thanks to many other professors at MIT. Professor David Perreault has been my academic advisor throughout the years. He always made sure that I was on the right path to complete a successful thesis. I thank Professors Arvind, Srini Devadas, and Vivienne Sze for their valuable feedback on my research. Additionally, I thank Professors Michael Sipser, Gregory Wornell, Stefanie Jegelka, and Samuel Madden for their excellent lectures as part of my degree.

I also would like to thank the administrative staff, Sally Lee and Mary McDavitt from system groups and Janet Fischer and Alicia Duarte from EECS administration who helped me to complete my PhD.

I am thankful to the members of Sanchez group: Maleen Abeydeera, Nathan Beckmann, Nosayba El-Sayed, Axel Feldmann, Yee Ling Gan, Mark Jeffrey, Harshad Kasture, Hyun Ryong Lee, Anurag Mukkara, Quan Nguyen, Nikola Samardzic, Suvinay Subramanian, Po-An Tsai, Cong Yan, Yifan Yang, and Victor Ying. It is my great pleasure to receive their valuable feedback on my research and discuss all kinds of fun stuff. I truly enjoy interacting with them no matter when, where, and how: during regular research meetings, random discussions in offices, travels to conferences, group outing activities, Thanksgiving dinners, or virtual Friday game nights.

I appreciate my friends in both China and the United States for making my life outside research exciting and wonderful.

Last but not least, I would love to thank my family, especially my mother and my wife. Though we are often separated by a 12- or 13-hour time difference, they have provided me the best love and encouragement I could ever imagine. I could not have completed this thesis without their support. I am grateful for financial support from an MIT EECS Grier Fellowship; C-FAR, one of six SRC STARnet centers by MARCO and DARPA; NSF under grants CAREER-1452994 and SHF-1814969; DARPA SDH under contract HR0011-18-3-0007; and research grants from IBM and SRC. This research was, in part, funded by the U.S. Government. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the U.S. Government.

# Introduction

Computer systems are increasingly bottlenecked by *data movement*. For instance, in a chip manufactured at 28 nm technology, a 64-bit floating-point multiply-add, a complex arithmetic operation, consumes 20 pJ. However, shipping its operands across the chip consumes 1 nJ, 50× higher [72, 131, 231]. Shipping the operands from off-chip DRAM is even worse, and can require 16 nJ, 800× more expensive than the arithmetic operation. The gap between the cost of data movement and computation has a growing impact as the system size increases, making memory system design increasingly critical.

One key approach to reduce data movement is to exploit *temporal* and *spatial locality* in the memory system. To do this, most memory systems use a hierarchy of caches. Caches adopt sophisticated hardware mechanisms such as the cache replacement policy to exploit locality dynamically without requiring accesses to be known ahead. Such generality ensures its central role in conventional memory systems.

However, there is a large semantic gap between conventional memory systems and applications. This gap often causes a significant performance penalty. Specifically, conventional memory systems typically organize data in *fixed-sized chunks*. Examples include lines in caches and pages in virtual memory. In contrast, applications use much more diverse data structures, such as trees and hash tables. Furthermore, conventional memory systems typically support only two primitive operations: read and write. This is not the case for applications: they can access data with various other operations such as push, enqueue, and insert. While this narrow interface is general enough and allows for a simple implementation, this interface is overly restrictive and hurts performance on many important access patterns.

# Challenges

We identify three patterns that can cause conventional systems to suffer poor performance: *small fragments, concurrent updates, and dependent reads.*

## **Small Fragments**

Accesses to small fragments incur poor spatial locality and can waste significant capacity. This is caused by the fixed-sized data representation in a conventional memory system. For instance, caches organize data in fixed-sized lines, and expect all the bits in a line to be accessed at least once before an eviction. However, a small fragment typically will not occupy a full cache line. Therefore, a significant portion of the cache capacity can be wasted.

Typical examples of small fragments include the key-value pairs in a hash table and the nodes in a tree. Such pairs and nodes consist of only a few words, much smaller than a typical cache line (e.g., 64 B). Such fragments are usually accessed in a data-dependent fashion. This is especially true for the pairs in a hash table: to reduce mapping conflicts, hashing intentionally spreads the pairs uniformly across the hash table's allocated memory.

11

1.1

1.1.1

1

### 1.1.2 Concurrent Updates

Concurrent updates to shared data cause expensive communication and serialization in a conventional memory system. This happens because of the *exclusive* nature of a write. Specifically, in a conventional memory system, an update must be expressed as a *read-modify-write* sequence. While reads are *non-exclusive*, i.e., they can access the same data concurrently without communication or synchronization, writes are *exclusive*: concurrent writes must communicate and synchronize with each other to ensure serializability.

For instance, consider a counter that is updated by multiple cores in a shared memory system. On each update, the updating core first fetches an exclusive copy of the counter's cache line into its private cache, invalidating all other copies, and modifies it locally using an atomic operation such as fetch-and-add, Each update incurs significant *traffic* and *serialization*: traffic to fetch the line and invalidate other copies, causing the line to ping-pong among updating cores; and serialization because only one core can perform an update at a time.

#### 1.1.3 Dependent Reads

Dependent reads introduce long access latencies on the critical path, limiting system performance significantly. This is because a read introduces a *roundtrip* of a request and a response. In a conventional cache, such a roundtrip is typically coupled with the long-latency data movement between the cache and the main memory. When such reads are dependent upon each other, i.e., the address of a read is computed from the return value of a previous read, e.g., A[B[i]], long roundtrip latencies accumulate, bottlenecking system performance severely.

One example is accessing a compressed sparse matrix. Such an operation typically requires indirections in the form of A[B[i]]. If both the accesses to B[i] and A[B[i]] miss in the cache, the system can incur a long critical-path latency that requires expensive mechanisms to hide.

Conventional memory systems were not designed or optimized for these access patterns. While prior work has proposed techniques to address them, these techniques work for only *regular applications*, where accesses are known ahead of time. For example, in a regular application like Dense Matrix-Matrix Multiplication (MM), tiling improves spatial locality, software-based variable privatization avoids concurrent updates, and prefetching hides the long latency incurred by reads.

However, *irregular applications*, i.e., applications where accesses are not known ahead, cannot exploit these techniques. Sparse matrix-matrix multiplication (SPMSPM) is one example. SPMSPM may access small fragments with dependent reads frequently to traverse matrices, and may issue concurrent updates to produce the output. Techniques for regular applications do not work well for irregular applications because of the lack of access knowledge. What's even worse is that such irregular applications are growing rapidly in many crucial domains, such as databases [144], graph analytics [93, 136, 160, 210], bioinformatics [175], and deep learning [105, 199, 267]. Therefore, it is crucial to design architectural support to address these patterns in irregular applications.

# 1.2 Contributions

The key insight that this thesis develops is that the memory system can be extended with rich semantics to address the aforementioned *irregular* patterns. In this way, the memory system no longer reasons in terms of only reads and writes. Instead, by codesigning hardware and software, activities in the memory system are expressed more explicitly. This thesis applies this insight to address each of the

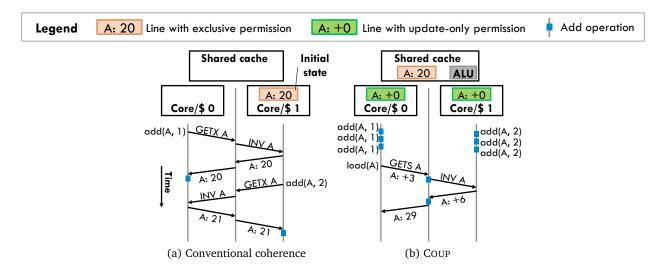

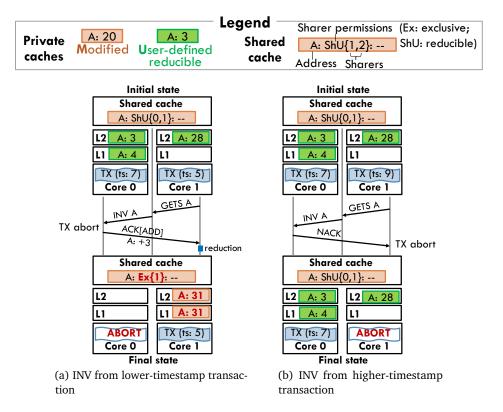

Figure 1.1: Example comparing the cost of commutative updates under two schemes. Two cores add values to a single memory location, A. (a) With conventional coherence protocols, A's fetches and invalidations dominate the cost of updates. (b) With COUP, caches buffer and coalesce updates locally, and reads trigger a reduction of all local updates to produce the actual value.

three challenges mentioned above, and proposes solutions tailored to various degrees of generality. For instance, we propose general architectural support for concurrent updates, but for dependent reads, we narrow the scope down to a specific application, SPMSPM, and build a customized memory system for it in an accelerator:

- COUP and COMMTM target the issues caused by *concurrent updates*. The key insight they exploit is that many read-modify-write updates are *commutative*. Commutative operations produce the same final result regardless of the order they are performed in. These operations need not read the data they update, so they do not introduce true data dependencies and therefore can be processed concurrently and coalesced locally before the data is read. Hence, updates can proceed concurrently, *without communication or synchronization*. COUP extends the cache coherence protocol so that single-instruction commutative updates can be performed locally and concurrently. COMMTM further exploits multi-instruction commutativity by leveraging hardware transactional memory.

- HTA mainly addresses the problems caused by *small fragments*. The key insight is that many such fragments are parts of an *unordered associative* container, i.e., a hash table, and can be optimized through hardware-software codesign. HTA adopts a table format that leverages characteristics such as cache line sizes and boundaries to avoid accessing disjoint small fragments. This new interface allows HTA to accelerate most operations with simple hardware, and to leave corner cases to a software path.

- GAMMA targets the issues of *dependent reads* in the context of sPMSPM. We show that Gustavson's algorithm is an efficient dataflow for sPMSPM, but it introduces dependent reads with irregular reuse that make conventional designs expensive. The key insight is that caching and decoupled execution can be combined: decoupled execution hides the long latency of dependent reads, while caching captures the irregular reuse patterns. GAMMA exploits this insight with a new storage idiom, FIBERCACHE. In return, GAMMA outperforms state-of-the-art sPMSPM accelerators significantly.

## COUP

COUP (Chapter 3) is a general technique that extends coherence protocols to allow local and concurrent commutative updates. Specifically, COUP decouples read and write permissions, and introduces a limited

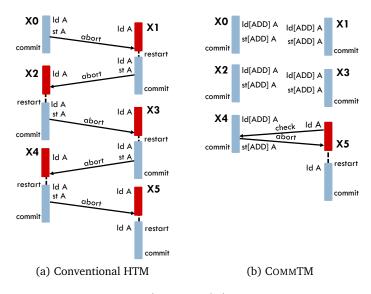

Figure 1.2: Example comparing (a) a conventional HTM and (b) COMMTM. Transactions X0–X4 increment a shared counter, and X5 reads it. While conventional HTMs serialize all transactions, COMMTM allows commutative operations (additions in X0–X4) to happen concurrently, serializing non-commutative operations (the load in X5) only.

number of commutative-update primitive operations, in addition to reads and writes. With COUP, multiple caches can acquire a line with *update-only* permission, and satisfy commutative-update requests locally, buffering and coalescing updates. On a read request, the coherence protocol gathers all the local updates and *reduces* them to produce the correct value before granting read permission. For example, multiple cores can concurrently add values to the same counter. Unlike conventional systems that suffer from excessive traffic and serialization shown in Figure 1.1a, COUP reduces communication and synchronization by exploiting commutativity. Updates are held in their private caches as long as no core reads the current value of the counter. When a core reads the counter, all updates are added to produce the final value, as shown in Figure 1.1b.

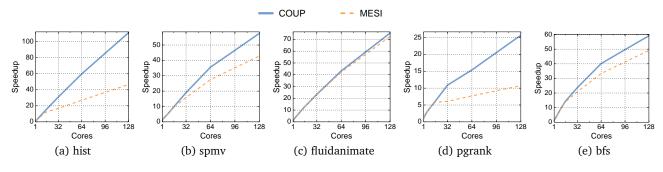

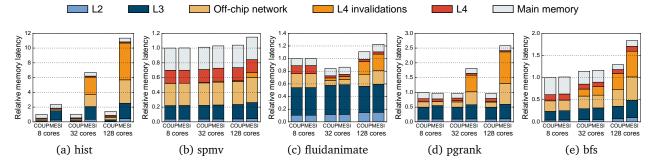

COUP provides significant benefits at minimal cost. COUP introduces minor hardware overheads, preserves coherence and consistency, and imposes small verification costs. We identify several update-heavy parallel applications where current techniques have clear shortcomings, and discuss how COUP addresses them. Specifically, COUP supports a limited number of *single-instruction* commutative operations, such as addition and bitwise logical operations. We evaluate COUP under simulation, using single- and multi-socket systems. At 128 cores, COUP improves the performance of update-heavy benchmarks by 4%–2.4× and reduces traffic by up to 20×.

#### 1.2.2 СоммТМ

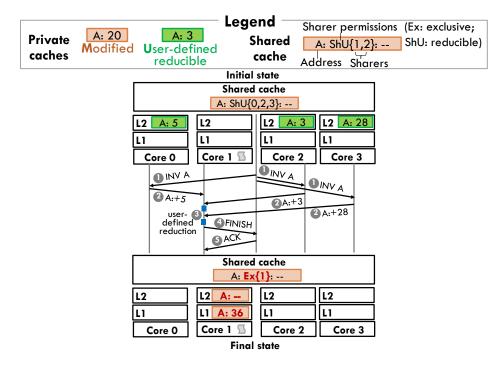

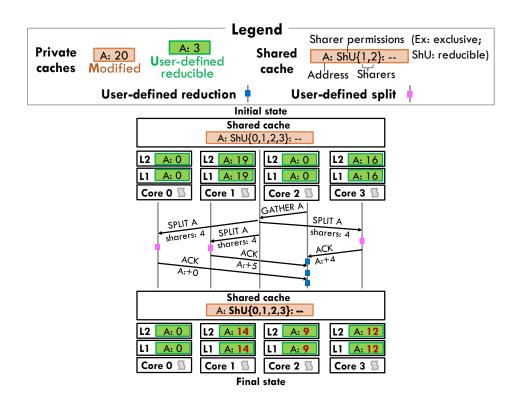

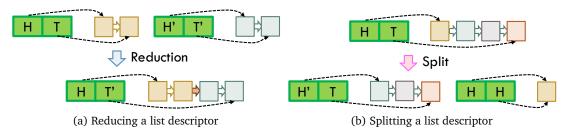

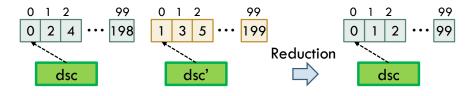

COMMTM (Chapter 4) is a <u>Comm</u>utativity-aware Hardware <u>Transactional Memory</u> (HTM) that extends COUP to support an unlimited number of user-defined commutative operations that cannot be expressed as single instructions. Specifically, COMMTM supports a much broader range of *multi-instruction, semantically commutative* operations, such as set insertions and ordered puts. We find that commutativity and transactional memory are complementary: transactions benefit commutativity by guaranteeing the atomicity of multi-instruction operations, and commutativity benefits transactions by avoiding unnecessary conflicts and wasted work, as shown in Figure 1.2. COMMTM extends the coherence protocol with a *reducible* state that generalizes COUP's update-only state. Lines in this state must be tagged with a user-defined *label*. Multiple caches can hold a given line in the reducible state with the same label, and transactions can implement commutative operations through labeled loads and stores that keep the line in the reducible state. These commutative operations proceed concurrently, without triggering conflicts or incurring any communication. A non-commutative operation (e.g., a conventional load or store) triggers a user-defined reduction that merges the different cache lines and may abort transactions with outstanding reducible updates.

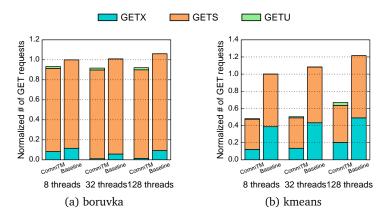

We explore several variants of COMMTM that trade precision for hardware complexity. We first present a basic version of COMMTM that achieves the same precision as software *semantic locking* [149, 265]. We then extend COMMTM with *gather requests*, which allow software to distribute reducible data among caches, achieving much higher concurrency in important use cases.

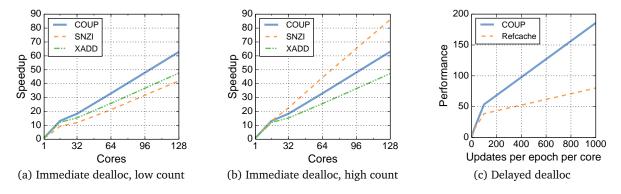

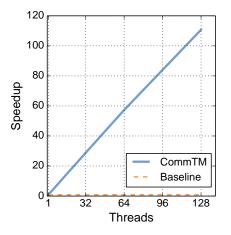

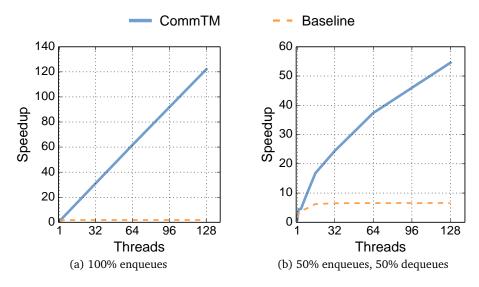

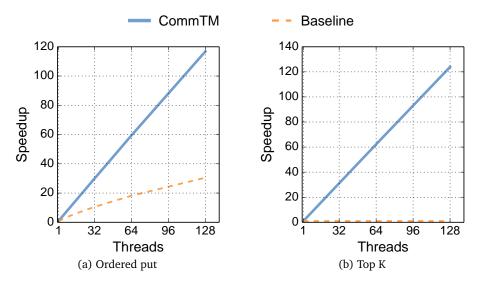

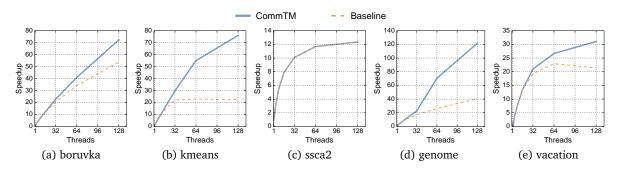

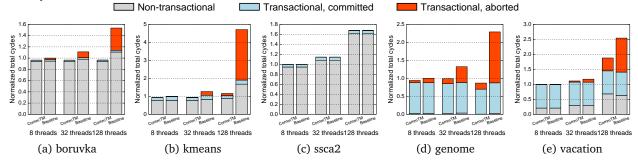

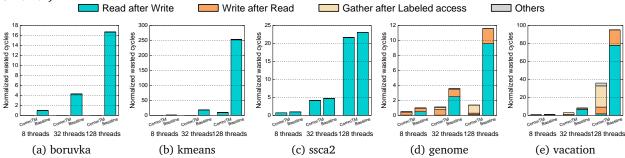

We evaluate COMMTM with microbenchmarks and full TM applications. Microbenchmarks show that COMMTM scales on a variety of commutative operations, such as set insertions, reference counting, ordered puts, and top-K insertions, which allow no concurrency in conventional HTMs. At 128 cores, COMMTM improves full-application performance by up to 3.4×, lowers private cache misses by up to 45%, and reduces or even eliminates transaction aborts.

### HTA

1.2.3

HTA (Chapter 5) is a Hash Table Acceleration technique that addresses the inefficiencies of hash table operations. Hash tables are widely used and consume the majority of cycles on key applications in databases [144] and genomics [175]. While hash tables have been extensively studied and optimized in software, they leave significant performance on the table in conventional systems.

Specifically, hash tables suffer from two key inefficiencies in conventional systems:

- **Poor core utilization:** Each hash table operation consists of a long sequence of instructions to compute hash values, memory accesses to keys and values, and comparisons. These instructions include hard-to-predict, data-dependent branches that add wasted cycles, and incur long-latency cache misses that limit instruction-level parallelism.

- **Poor spatial locality:** To reduce mapping conflicts, hashing spreads key-value pairs uniformly across the hash table's allocated memory. This causes poor spatial locality when key-value pairs have mixed reuse, e.g., the same-line neighbors of a frequently accessed pair are rarely accessed. This wastes a significant portion of cache capacity.

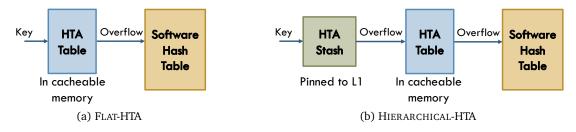

HTA address the issues through the combination of expressive ISA extensions and simple hardware changes. HTA adopts a hash table format that leverages the associative nature of caches. With this new format, multiple probes in a single lookup need access only one whole line instead of multiple small fragments spread across multiple lines. HTA accelerates most operations in hardware, and leaves rare cases to software.

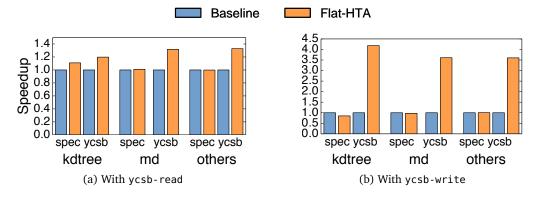

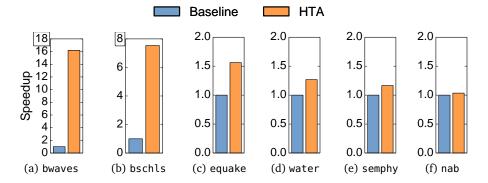

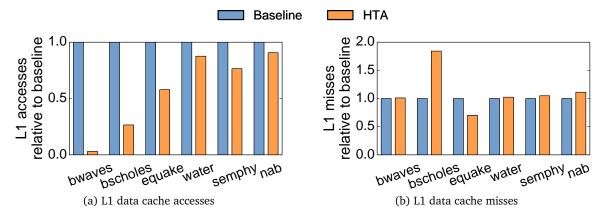

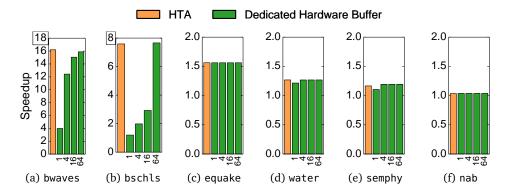

We present two implementations of HTA, FLAT-HTA and HIERARCHICAL-HTA. FLAT-HTA adopts a simple, hierarchy-oblivious layout and reduces runtime overheads with simple changes to cores. HIERARCHICAL-HTA is a more complex implementation that uses a hierarchy-aware layout to improve spatial locality at intermediate cache levels. It requires some changes to caches and provides modest benefits over FLAT-HTA.

We evaluate HTA on hash table-intensive benchmarks and use it to accelerate *memoization*, a technique that caches and reuses the outputs of repetitive computations. FLAT-HTA improves the performance of the state-of-the-art hash table-intensive applications by up to 2×, while HIERARCHICAL-HTA outperforms FLAT-HTA by up to 35%. FLAT-HTA also outperforms software memoization by 2×.

## 1.2.4 GAMMA

GAMMA is a <u>Gustavson-Algorithm Matrix-Multiplication Accelerator</u>. It features architectural support for dependent reads to enable an efficient *dataflow* of spMspM, i.e., Gustavson's dataflow, in accelerators.

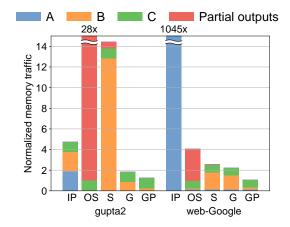

Specifically, SPMSPM is a key kernel that lies at the heart of many sparse algorithms [39, 105, 136, 140, 199, 274]. First, SPMSPM is bottlenecked by memory traffic and data movement, and admits three *dataflows* (i.e., computation schedules) with different tradeoffs: *inner-product* [109, 207], *outer-product* [196, 291], and *Gustavson's algorithm* [99]. Though Gustavson often achieves the least amount of memory traffic and requires simpler operations, prior accelerators exploit either inner-product or outer-product dataflows. This is because Gustavson has more *irregular reuse* across data structures, demanding a storage organization that can accommodate them to effectively reduce memory traffic.

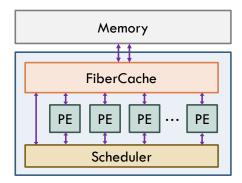

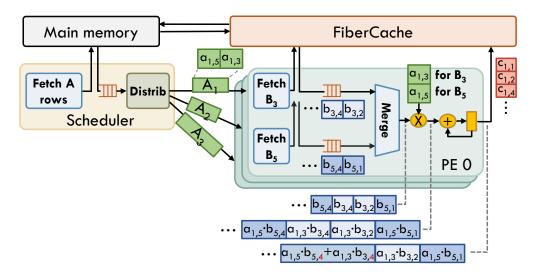

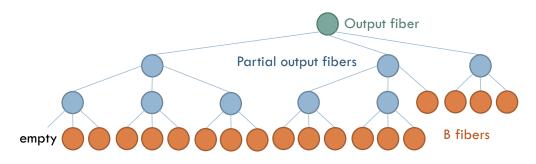

GAMMA addresses this issue. GAMMA performs SPMSPM's computation using specialized processing elements (PE) with simple high-radix mergers, and performs many merges in parallel to achieve high throughput. GAMMA uses a novel on-chip storage structure that combines features of both caches and explicitly managed buffers. This structure captures Gustavson's irregular reuse patterns and streams thousands of concurrent sparse *fibers*, i.e., variable-sized rows from inputs or partial outputs, with explicitly decoupled data movement. FIBERCACHE fetches the needed fibers ahead of time so that when the processing element reads each input fiber element, the data is served from the FIBERCACHE without incurring memory accesses. This avoids PE stalls and lets the FIBERCACHE pull double duty as a latency-decoupling buffer, and saves megabytes of dedicated on-chip buffers. GAMMA features a new dynamic scheduling algorithm to achieve high utilization despite irregularity. We also present new preprocessing algorithms that boost GAMMA's efficiency and versatility.

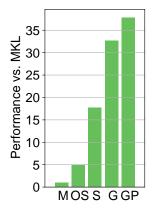

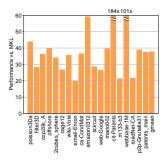

We synthesize GAMMA and evaluate its performance on a wide range of sparse matrices. With a similar hardware budget, compared to state-of-the-art accelerators, GAMMA reduces total DRAM traffic by  $2.2 \times$  on average, non-compulsory DRAM traffic by  $12 \times$  on average, and achieves nearly full DRAM bandwidth utilization. Moreover, GAMMA is effective on a much broader range of sparse matrices.

In summary, the goal of this thesis is to address the patterns that used to be challenging for conventional memory systems: concurrent updates, small fragments, and dependent reads. By codesigning hardware and software, the memory system can be extended with high-level semantics. COUP and COMMTM are general support for concurrent updates, by exploiting operation-level commutativity. HTA is tailored to leverage the knowledge of a data structure, hash table, while GAMMA is tailored to an important application, SPMSPM. In return, the techniques proposed by this thesis improve performance significantly.

# Background

Modern memory systems should allow fast (e.g, nanoseconds) accesses to large (e.g., gigabytes) volumes of data. But this is hard to achieve with a single storage structure: storage structures with large capacity incur high access latencies, and fast storage structures cannot be made sufficiently large.

Therefore, memory systems combine fast/small and slow/large storage structures in a hierarchy. The off-chip main memory made of DRAM is the root of the tree: it typically has gigabytes of capacity with an access latency of hundreds of nanoseconds. On-chip storage components are the internal nodes and the leaves of the tree. They are typically made of kilobytes to megabytes of SRAM, with access latencies ranging from one to tens of nanoseconds. As a result, most accesses are fulfilled by the fast/small on-chip structures, while others are served by the off-chip main memory.

On-chip storage can be implemented as various structures with tradeoffs in their interfaces, overheads, and capabilities. Section 2.1 presents various storage structures, and then Section 2.2 summarizes prior software and hardware techniques proposed to improve the performance of memory systems.

# Memory System Architecture

## Caches

A cache is a storage structure that receives accesses, i.e., reads and writes, from processors, and *transparently* retains recently accessed data. Subsequent accesses to data present in the cache (hits) are served directly by the cache; otherwise (misses), the cache accesses the next level of the hierarchy. Caches are widely adopted in CPUs, GPUs, and some accelerators to reduce access latency and save memory bandwidth.

**Transparency:** A cache can be made architecturally invisible while retaining good performance in most cases at a reasonable cost. Such transparency to software is a critical property for an on-chip structure to be widely adopted, especially in general-purpose CPUs and GPUs, as it simplifies programming and enhances compatibility significantly. To achieve this, caches support only *global accesses*, i.e., accesses based on global addresses rather than structure-specific locations, and require additional synchronization mechanisms to provide a *shared-memory* illusion when there are multiple private caches caching the same data.

**Supporting global accesses:** A cache maps multiple memory locations to the same cache location, and introduces a *tag* for each cache line slot to differentiate them. Such a mapping may have different levels of flexibility. A *direct-mapped* cache allows no flexibility as it maps each memory location to only one cache location. In contrast, a *fully-associative* cache enjoys the most flexibility as a line in memory may

2.1

map to all locations. An *N*-way set-associative cache sits in the middle, as it allows a line in memory to map to a set of *N* locations. Higher associativity leads to fewer conflict misses but higher area and energy costs.

Such flexibility of mapping in fully-associative and *N*-way set-associative caches introduces a decision problem: a cache must determine which line to evict when there is not enough capacity for a new line. Because cache accesses typically do not control evictions explicitly <sup>1</sup>, such decisions are made in hardware by a *cache replacement policy*. The optimal replacement policy is MIN [28, 171]. But it is impractical to implement as it requires knowing future accesses. Practical replacement policies use heuristics, e.g., access history, to approximate MIN. Therefore, they do not require knowing accesses ahead, and are effective as long as the accesses exhibit good locality. Common policies include LRU, DIP [208], PDP [83], SHiP [271], and RRIP [121].

**Supporting the shared-memory model:** In a multicore system, it is common to have multiple private caches, each attached to a different core to improve performance. This poses challenges on providing a shared-memory programming model as these caches must synchronize on writes to shared data transparently.

Cache coherence is a property of a cache hierarchy that makes private caches invisible to applications. Coherence can be expressed as two invariants [68]: *write propagation*, that writes eventually become visible to all cores, and *write serialization*, that writes to the same address are observed in the same order by all processors.

Coherence is enforced by the *cache coherence protocol*. The cache coherence protocol can be implemented in various styles: write-invalidate or write-update depending on how to ensure write propagation, and snooping-based [95] or directory-based [42] depending on how to track states and serialize requests. Coherence can be implemented as hardware-managed, software-managed, or hybrid. Hardware coherence protocols [42, 95, 247, 281] are widely adopted in cache-based multicore systems. Typical examples include the MSI, MESI, and MOESI protocols [247]. Software-managed protocols [133, 148] and hybrid protocols [57, 132, 134, 135] such as DeNovo [57] and WayPoint [135] often leverage self-invalidations to avoid high-latency critical paths and are often seen in GPUs. One issue of the conventional cache coherence protocol is that it is limited by the narrow read-write interface: updates must be expressed as read-modify-write sequences and hence concurrent updates may introduce excessive traffic and serialization.

*Cache coherence* simplifies the implementation of common *memory consistency models*. The memory consistency model is an interface between software and hardware that precisely specifies how the memory system behaves with respect to reads and writes. Coherence concerns what values a read can return, while consistency concerns when writes become visible to reads. Coherence concerns reads/writes to a single memory location, while consistency concerns reads/writes to multiple memory locations. Common memory consistency models include sequential consistency [155], total store order (TSO), and release consistency [91].

**Drawbacks:** Caches may suffer from significant performance loss on several access patterns as explained in Section 1.1. Besides, caches introduce high area and energy overheads attributed to tag arrays, replacement policies, and coherence events. Therefore, when caches' costs outweigh their benefits, explicitly managed storage structures can be promising substitutes.

<sup>&</sup>lt;sup>1</sup>Some processors have instructions for evictions, such as CLFLUSH in x86.

## Explicitly managed storage structures

Explicitly managed storage structures include scratchpads [26, 193], stashes, queues, and buffets. Compared to caches, they have two characteristics. First, they adopt a more *explicit* programming interface: they grant applications more precise control of data organization and movement and typically accept only local addresses, while sacrificing the generality and simplicity of the programming model. Maintaining the shared-memory model may require expensive software coherence protocols [14]. Second, they allow simpler hardware implementations at the cost of reduced capability to exploit irregular data reuse.

**Scratchpad** [26, 193] is a storage structure that grants software full control over its content, by mapping its storage locations to an address range exposed to the applications. Therefore, a scratchpad avoids all the expensive hardware designed for global accesses such as the tag array and the cache replacement policy. As a result, it is a nice fit for GPUs and accelerators. Typical GPU applications bear enormous data-level parallelism and incur regular accesses that can be easily structured.

**Stash** [147] combines the characteristics of a scratchpad and a cache. Like a scratchpad, it unifies its content into the global address space, and allows a flexible data organization. Instead of controlling data movement *eagerly* as in a scratchpad, a stash records a mapping between a local region and a global address region to enable *lazy* data movement on misses and writebacks. Such a mapping requires more hardware but saves data movement when there is dynamic coarse-grain data reuse.

Caches, scratchpads, and stashes use the read-write interface, and incur long access latency when the data is off-chip. To overlap the long latency with other useful work, CPUs and GPUs adopt sophisticated mechanisms, e.g., out-of-order execution in CPUs and multithreading in GPUs. However, accelerators cannot afford such overheads as they are designed to be efficient and simple. Instead, accelerators typically adopt other storage structures that exploit *decoupled execution* to hide the latency.

**Queue-based communication** is the simplest form of decoupled execution. With a queue, the producer and the consumer can run simultaneously. Because of its simple synchronization and low hardware cost, queues are widely adopted in decoupled access-execute architectures [94, 102, 236, 244] and streaming multicores [67, 76, 250]. However, in-place updates, needed by many applications [54, 167], are hard to support in queues.

**Buffet** [201] is a storage structure proposed for accelerators to preserve the decoupling of a queue while supporting offset-based indexing and inexpensive in-place updates. A buffet achieves so by restricting the four operations performed on data, i.e., fill, read, update, and shrink, to form a fixed sequence and managing the sequence with a finite-state machine. Buffets and queues both exhibit good composability and simple synchronization, and allow decoupled execution to hide long access latencies.

## Summary

2.1.3

As explained above, there are a diverse set of on-chip storage structures that can be used in a memory system. Pellauer et al. [201] introduced a taxonomy for *data orchestration*, i.e., transferring data into and out of a storage structure.

Specifically, for an on-chip storage structure, reusable data should not be evicted when they are on-chip, and should be staged on chip early when they are off-chip. Depending on how these two aspects are

2.1.2

| Data Orchestration | Implicit                                                 | Explicit                       |

|--------------------|----------------------------------------------------------|--------------------------------|

| Coupled            | Cache                                                    | Scratchpad<br>Stash            |

| Decoupled          | Decoupled Access-Execute (DAE)<br>FIBERCACHE (Chapter 6) | Scratchpad (w/ DMAs)<br>Buffet |

Table 2.1: Taxonomy of data orchestration approaches as used in typical scenarios. A scratchpad can be combined with Direct Memory Access (DMA) engines to achieve decoupling. A stash explicitly maps local addresses to global addresses, though data movement may be triggered implicitly by load misses.

implemented, storage structures can be classified as either *explicit* or *implicit*, and can be used in either *coupled* or *decoupled* manner, as summarized in Table 2.1.

#### **Explicit vs. Implicit Data Orchestration**

Broadly speaking, the content of an on-chip storage structure can be managed in two styles: *explicit* or *implicit*. Explicitly orchestrated structures allow applications to directly control what to retain or remove, while implicitly orchestrated structures infer such decisions implicitly based on read/write accesses.

Based on this criteria, scratchpads, queues, and buffets are all explicit: they determine whether to keep or forfeit data based on direct operations such as enqueue and dequeue, or fill and shrink. In contrast, caches are implicit. A cache predicts what to evict based on the previous accesses, tracked and analyzed by the cache replacement policy.

Implicitly orchestrated structures are widely adopted in general-purpose computing. Though they incur high hardware overheads, implicitly orchestrated structures are typically equipped with hardware, such as the cache replacement policy, to exploit locality in irregular accesses. Compared to the resource budget of the on-chip storage, general-purpose systems are more concerned with the poor performance caused by irregular access patterns. These accesses exhibit locality that can be extracted only at runtime, and therefore cannot be exploited by explicitly orchestrated structures.

In contrast, domain-specific accelerators prefer explicitly orchestrated structures. Though explicitly orchestrated structures do not capture irregular data reuse, they require simple hardware and incur low energy consumption. Accelerators aim to be efficient in area and energy. Therefore, accelerator designers often choose applications and algorithms that avoid irregular accesses so that they can minimize area and energy overheads by adopting explicitly orchestrated structures such as queues and buffets (Section 6.1.4).

#### Coupled vs. Decoupled Data Orchestration

A storage structure can be used in either *coupled* or *decoupled* manner depending on whether the data needed is pre-staged ahead of processing to hide the memory access latency. They differ in whether the requester that initiates data movement from/to main memory is the same as the actual consumer of the data. With coupled data orchestration, the requester and the consumer are the same; with decoupled data orchestration, they are different units.

Coupled staging of data, commonly used in caches, stashes, and scratchpads without DMA engines, enjoys intuitive synchronization between data demand and data availability. However, the read roundtrip incurs long memory access latency, and requires sophisticated mechanisms to hide, such as those that exploit instruction-, memory-, or thread- level parallelism.

Decoupled staging of data, such as in scratchpads with DMA engines, buffets, and queues used in decoupled access-execute architectures, separates the requester that initiates data movement from memory and the data consumer. This decoupling allows the consumer to have low-latency accesses, as the data needed is staged ahead of processing. For instance, decoupled access-execute architectures are based on queues, and separate the units for sending read requests and receiving read responses. Though they may work well on regular applications, on irregular applications, they may suffer from load imbalance and lack of control-flow mechanisms [192]. Finally, decoupled data orchestration must also incorporate careful synchronization: too aggressive staging may overwrite live data, too conservative staging may result in poor efficiency.

FIBERCACHE (Chapter 6) is a storage structure with implicit and decoupled data orchestration. It orchestrates data implicitly to exploit irregular data reuse, and uses decoupled execution to hide the long memory access latencies incurred by dependent reads.

## **Improving Memory System Performance**

Despite the diversity in organizing on-chip storage, there are common challenges in memory systems:

- Accesses that exhibit *poor locality*, e.g., accesses to small fragments, waste storage capacity.

- Concurrent updates in shared-memory systems incur excessive communication and synchronization.

- Dependent reads accumulate a *long access latency* that is expensive to hide in systems with implicitly orchestrated storage structures.

## **Improving Locality**

The performance of an on-chip storage structure can be hurt significantly if accesses do not exhibit good locality. To address this issue, prior work has proposed many techniques. They either change the data representation or modify the compute schedule.

**Changing the data representation** can be effective on improving the locality of accesses. This can be performed either in software, such as graph/tensor preprocessing [16, 69, 103, 124, 203, 264, 282] and cache-aware data structures [293], or in hardware, such as compressed caches [11, 101, 209], texture caches [100], and storage structures with variable-sized lines [152] or object awareness [252]. Besides increased locality, modifying the data representation can unlock potential for SIMD operations, as data needed by similar operations are likely to be grouped together.

HTA exploits this with a table format that maps multiple key-value pairs to the same cache line. This allows multiple probes in a single lookup to be performed in parallel with only one memory access.

**Changing the compute schedule** is the other approach to improve locality and can be performed by either software or hardware.

Some techniques do not require changes in data representation. Instead, they schedule compute to maximize data reuse, either statically [7, 243, 275], or dynamically [3, 50, 115, 122, 234, 276]. Others are combined with modifications in data representation [90, 160, 185]. For instance, tiling [6, 107, 116, 239, 255, 290, 294] typically works on a nested loop: Based on knowledge of accesses, tiling sometimes reorganizes data in storage-fitting chunks [107, 116, 290, 294], which effectively increases the iteration levels in the loop, and then reorders the iteration levels to improve data reuse. Since it is effective on

2.2

2.2.1

regular accesses, many accelerators built on explicitly orchestrated storage structures rely on tiling to improve locality and avoid overflows [107].

#### 2.2.2 Reducing Communication and Synchronization

Concurrent updates can incur excessive traffic and serialization. This is an especially serious problem for shared memory systems with cache coherence. Many software and hardware optimizations seek to reduce the cost of updates. Though often presented in the context of specific algorithms or implementations, we observe these techniques can be classified into two categories: *Privatization* [21, 62, 190] exploits commutativity to avoid communication and serialization. *Delegation* [37, 38] is more general, in that it does not require operations to be commutative, but it suffers from serialization and complexity in the memory consistency model.

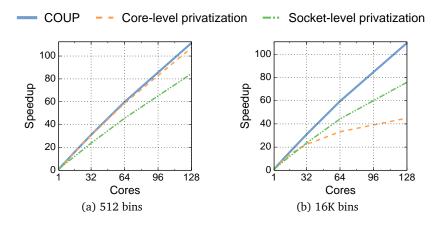

**Privatization** lowers the cost of commutative updates by using thread-local variables [21, 62, 190]. Privatization schemes buffer updates in thread-private storage, and require reads to reduce these thread-private updates to produce the correct value. Privatization is most commonly used to implement reduction variables efficiently, often with language support (e.g., reducers in MapReduce [77], OpenMP pragmas, and Cilk Plus hyperobjects [90]). Privatization is generally used when updates are frequent and reads are rare.

Privatization is limited to commutative updates, and works best when data goes through long updateonly phases without intervening reads. However, privatization has two major sources of overhead. First, software reductions are much slower, making finely-interleaved reads and updates inefficient. Second, with N threads, privatized variables increase the memory footprint by a factor of N. This makes naïve privatization impractical in many contexts (e.g., reference counting). Dynamic privatization schemes [62, 190, 278] can lessen space overheads, but add time overheads and complexity.

**Delegation** sends updates to a single location to reduce data movement and hence the cost of updates. Delegation does not leverage commutativity. This limits their performance benefits, but makes them applicable for non-commutative operations.

Specifically, in software, delegation schemes send updates to a single thread [37, 38]. They divide shared data among threads and send updates to the corresponding thread, using shared-memory queues [37] or active messages [225, 258]. Delegation is common in architectures that combine shared memory and message passing [225, 270] and in NUMA-aware data structures [37, 38]. Although delegation reduces data movement and synchronization, it still incurs global traffic and serialization.

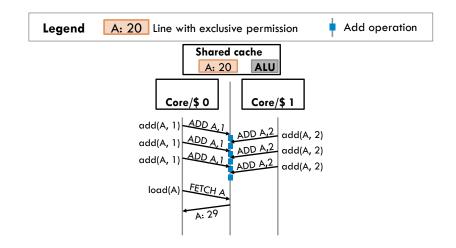

*Remote memory operations (RMOs)* [97, 114, 228, 287] are the hardware counterpart of delegation. Rather than caching lines to be updated, update operations are sent to a fixed location, as shown in Figure 2.1. The NYU Ultracomputer [97] proposed implementing atomic fetch-and-add using adders in network switches, which could coalesce multiple requests on their way to memory. The Cray T3D [137], T3E [228], and SGI Origin [157] implemented RMOs at the memory controllers, while TilePro64 [114] and recent GPUs [268] implement RMOs in shared caches. Prior work has also proposed adding caches to memory controllers to accelerate RMOs [287] and data-parallel RMOs [9].

Although RMOs reduce update costs for both commutative and non-commutative operations, they suffer from two issues. First, while RMOs avoid ping-ponging cache lines, they still require sending every update to a shared, fixed location, causing global traffic, a serious issue in shared-memory systems. RMOs are also limited by the throughput of the single updater. For example, in Figure 2.1, frequent remote-add requests drive the shared cache's ALU near saturation. Second, consistency models must be considered because there can be concurrent users of the data, but strong consistency models are

challenging to implement with RMOs, as it is harder to constrain memory operation order. For example, TSO requires making stores globally visible in program order, which is feasible with local store buffers, but much more complicated when stores are also performed by remote updaters. As a result, most implementations provide weakly-consistent RMOs. Timestamp-based order validation [153, §5] allows strong consistency with RMOs, but it is complicated.

## Hiding Memory Access Latency

Irregular applications often leverage implicitly orchestrated storage structures, such as caches, to capture irregular data reuse. However, the high latency of reads that access main memory can be a serious issue. Such high latency can accumulate on dependent reads, eventually bottlenecking the system performance. Therefore, techniques that hide the memory access latency for implicitly managed storage structures are necessary.

Prior work can be classified into two categories, they either tolerate the long latency by exploiting parallelism, i.e., finding something else to do, or prefetching and specialized fetching.

**Exploiting parallelism** is effective as it overlaps the long memory access latency with other useful work. This works because of Little's law [163]. By allowing multiple long-latency events to happen simultaneously, the system can maintain its high throughput that would otherwise be degraded by the long latency.

Modern CPUs, GPUs, and accelerators exploit various levels of parallelism, such as instruction-level parallelism in out-of-order execution, thread-level parallelism in multicore CPUs and GPUs, operation-level parallelism in accelerators [106, 144, 151], and pipeline parallelism [67, 118, 138, 192]. However, they do not work well when there is little parallelism to begin with, e.g., on dependent reads.

**Prefetching and specialized fetching** are crucial to get some of the benefits of explicit data orchestration in a cache-based system. In this way, accesses from the real consumers can incur low latency since the needed data is already resident in the cache.

Prefetching allows data to be speculatively fetched into the cache ahead of accesses, so that actual accesses are likely to hit, reducing the latency drastically. Prefetching can be implemented in either

2.2.3

hardware [10, 27, 53, 127, 168, 187, 280] or software [182, 183]. Hardware prefetchers capture dynamic patterns at runtime. However, simple prefetchers can be limited by the access patterns they can handle, while complex prefetching techniques such as runahead execution [187] and indirect prefectures [10, 27, 280] incur high hardware overheads. Software prefetchers allow direct control from applications, but can incur high instruction overheads and poor cross-platform compatibility. Specialized fetchers [144, 151, 185, 192] are capable of fetching data non-speculatively into the cache. They rely on customized hardware and are often limited to specific access patterns and applications.

In this thesis, we propose GAMMA, a SPMSPM accelerator that adopts a novel storage idiom FIBER-CACHE. FIBERCACHE is customized for an efficient SPMSPM dataflow. It combines decoupled execution and caching to both hide memory access latency and exploit irregular data reuse.

# COUP

In this chapter, we present COUP, a general technique that extends coherence protocols to allow *local and concurrent commutative updates*. COUP allows multiple caches to acquire a line with *update-only* permission, and satisfy commutative-update requests locally, buffering and coalescing updates. Upon a read, the coherence protocol collects all the local updates and *reduces* them to produce the correct value before granting read permission.

Unlike RMOs (Section 2.2.2) that suffer from serialization and complicate memory consistency, COUP confers significant benefits over RMOs, especially when data receives several consecutive updates before being read. Moreover, COUP maintains full cache coherence and does not affect the memory consistency model. This makes COUP easy to apply to current systems and applications. Note that COUP's advantages come at the cost of a more restricted set of operations: COUP is limited to commutative updates, while RMOs support non-commutative operations such as fetch-and-add and compare-and-swap.

COUP also completes a symmetry between hardware and software schemes to reduce the cost of updates. Just as remote memory operations are the hardware counterpart to delegation, COUP *is the hardware counterpart to privatization*. COUP has two benefits over software privatization. First, transitions between read-only and update-only modes are much faster, so COUP remains practical in many scenarios where software privatization requires excessive synchronization. Second, privatization's thread-local copies increase memory footprint and add pressure to shared caches, while COUP does not.

We demonstrate COUP's utility by applying it to improve the performance of *single-word update operations*, which are currently performed with expensive atomic read-modify-write instructions.

Overall, we make the following contributions:

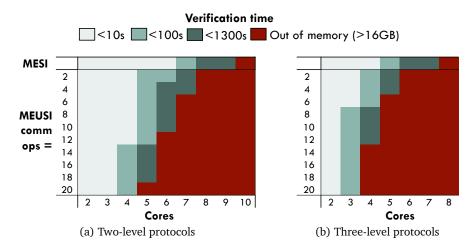

- We present COUP, a technique that extends coherence protocols to support concurrent commutative updates (Section 3.2 and Section 3.3). We show that COUP preserves coherence and consistency (Section 3.4), and imposes small verification costs (Section 3.5).

- We identify several update-heavy parallel applications where current techniques have clear shortcomings (Section 3.6), and discuss how COUP addresses them.

- We evaluate COUP under simulation, using single- and multi-socket systems (Section 3.7). At 128 cores, COUP improves the performance of update-heavy benchmarks by 4%–2.4×, and reduces traffic by up to 20×.

In summary, COUP shows that extending coherence protocols to leverage the semantics of commutative updates can substantially improve performance without sacrificing the simplicity of cache coherence.

# Motivation

Historically, exploiting *commutativity* has been a fruitful approach to reduce the cost of updates. Commutativity [265] has been widely exploited in parallel systems, such as databases [21, 190], parallelizing compilers [204, 219], and runtimes [149, 204].

3.1

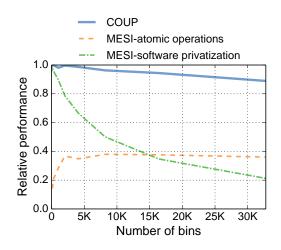

Figure 3.1: Performance of parallel histogram implementations using atomics, software privatization, and COUP. More bins reduce contention and increase privatization overheads, favoring atomics. COUP does not suffer these overheads, so it outperforms both software implementations.

Commutative updates are common in many cases. *Strictly commutative* operations produce exactly the same final state when reordered. For instance, consider two additions to a counter. Reordering them does not affect the final result at all, and therefore integer addition is strictly commutative. Besides addition, multiplication, minimization, maximization and bitwise logical operations are all strictly commutative. Such operations are typically implemented as single instructions in non-speculative parallel system.

*Privatization* is the software technique that exploits commutativity to reduce the costs of updates. However, it incurs significant overheads that often make privatization underperform conventional updates. For instance, Jung et al. [126] propose parallel histogram implementations using both atomic operations and privatization. These codes process a set of input values, and produce a histogram with a given number of bins. Jung et al. note that privatization is desirable with a few output bins, but works poorly with many bins, as the reduction phase dominates execution time and hurts locality. Figure 3.1 shows this tradeoff. It compares the performance of histogram implementations using atomic fetch-and-add, privatization, and COUP, when running on 64 cores (see Section 3.7 for methodology details). In this experiment, all schemes process a large, fixed number of input elements. Each line shows the performance of a given implementation as the number of output bins (*x*-axis) changes from 32 to 32 K. Performance is reported relative to COUP's at 32 bins (higher numbers are better). While the costs of privatization impose a delicate tradeoff between both implementations in software, COUP robustly outperforms both. In fact, COUP is the *hardware counterpart of privatization*.

## 3.2 COUP Example: Extending MSI

We first present the main concepts and operation of COUP through a concrete, simplified example. Consider a system with a single level of private caches, kept coherent with the MSI protocol. This system has a single shared last-level cache with an in-cache directory. It implements a single commutative-update operation, addition. Finally, we restrict this system to use single-word cache blocks. We will generalize COUP to other protocols, operations, and cache hierarchies in Section 3.3.

## 3.2.1 Structural changes

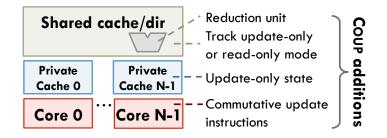

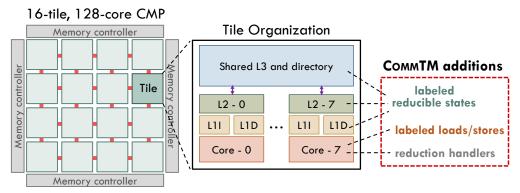

COUP requires modest changes to hardware structures, summarized in Figure 3.2 and described below.

Figure 3.2: Summary of additions and modifications needed to support COUP.

**Commutative-update instructions:** In most ISAs, COUP needs additional instructions that let programs convey commutative updates, as conventional atomic instructions (e.g., fetch-and-add) return the latest value of the data they update. In this case, we add a *commutative-addition* instruction, which takes an address and a single input value, and does not write to any register.

Some ISAs may not need additional instructions. For instance, the recent Heterogeneous System Architecture (HSA) includes atomic-no-return instructions that do not return the updated value [2]. While these instructions were likely introduced to reduce the cost of RMOs, COUP could use them directly.

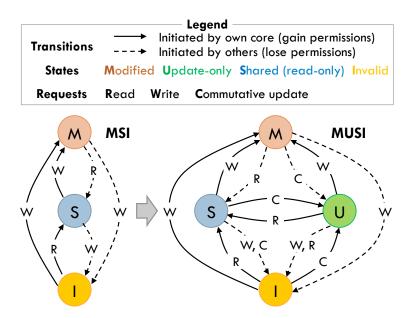

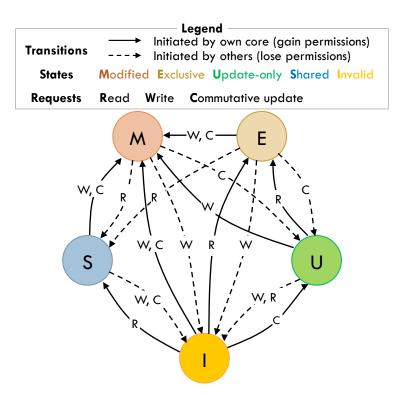

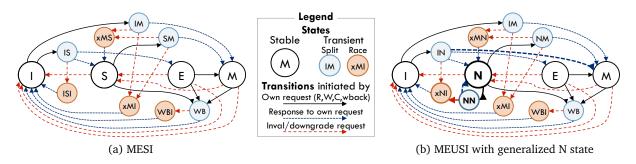

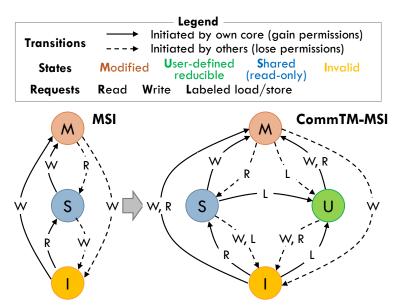

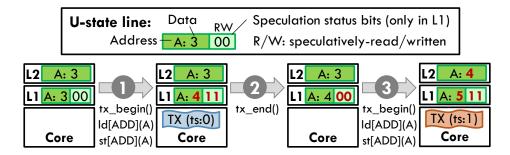

**Update-only permission:** COUP extends MSI with an additional state, *update-only (U)*, and a third type of request, *commutative update (C)*, in addition to conventional reads (R) and writes (W). We call the resulting protocol MUSI. Figure 3.3 shows MUSI's state-transition diagram for private caches. MUSI allows multiple private caches to hold read-only permission to a line and satisfy read requests locally (S state); multiple private caches to hold update-only permission to a line and satisfy commutative-update requests locally (U state); or at most a single private cache to hold exclusive permission to a line and satisfy all types of requests locally (M state). By allowing M to satisfy commutative-update requests, interleaved updates and reads to *private* data are as cheap as in MSI.

MUSI's state-transition diagram shows a clear symmetry between S and U: all transitions caused by R/C requests in and out of S match those caused by C/R requests in and out of U. We will exploit this symmetry in Section 3.5 to simplify our implementation.

**Directory state:** Conventional directories must track both the sharers of each line (using a bit-vector or other techniques [45, 223, 284]), and, if there is a single sharer, whether it has exclusive or read-only permission. In COUP, the directory must track whether sharers have exclusive, read-only, or update-only permission. The sharers bit-vector can be used to track both multiple readers or multiple updaters, so MUSI requires only one extra bit per directory tag.

**Reduction unit:** Though cores can perform local updates, the memory system must be able to perform reductions. Thus, COUP adds a reduction unit to the shared cache, consisting of an adder in this case.

### Protocol operation

3.2.2

**Performing commutative updates:** Both the M and U states provide enough permissions for private caches to satisfy update-only requests. In M, the private cache has the actual data value; in U, the cache has a partial update. In either case, the core can perform the update by atomically reading the data

Figure 3.3: State-transition diagrams of MSI and MUSI protocols. For clarity, diagrams omit actions that do not cause a state transition (e.g., R requests in S).

from the cache, modifying it (by adding the value specified by the commutative-add instruction) and storing the result in the cache. The cache cannot allow any intervening operations to the same address between the read and the write. This scheme can reuse the existing core logic for atomic operations. We assume this scheme in our implementation, but note that alternative implementations could treat commutative updates like stores to improve performance (e.g., using update buffers similar to store buffers and performing updates with an ALU at the L1).

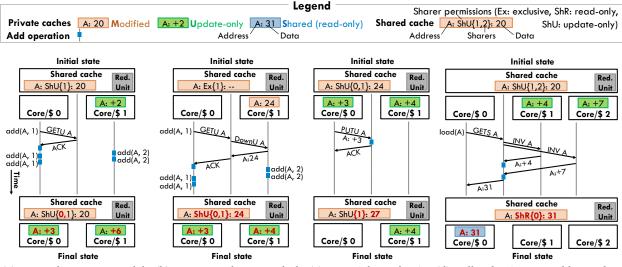

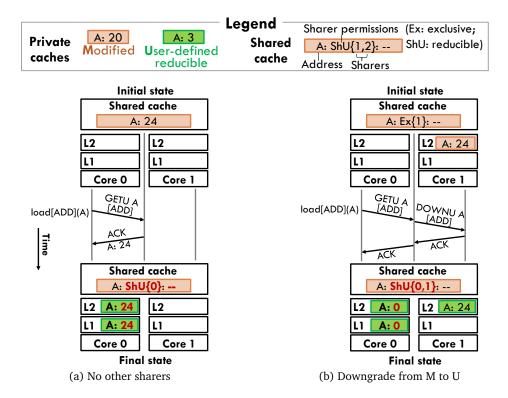

**Entering the U state:** When a cache has insufficient permissions to satisfy an update request (I or S states), it requests update-only permission from the directory. The directory invalidates any copies in S, or downgrades the single copy in M to U, and grants update-only permission to the requesting cache, which transitions to U. Thus, there are two ways a line can transition into the U state: by requesting update-only permission to satisfy a request from its own core, as shown in Figure 3.4a; or by being downgraded from M, as shown in Figure 3.4b.

When a line transitions into U, its contents are always initialized to the *identity element*, 0 for commutative addition. This is done even if the line had valid data. This avoids having to track which cache holds the original data when doing reductions. However, reductions require reading the original data from the shared cache.

Leaving the U state: Lines can transition out of U due to either evictions or read requests.

Evictions initiated by a private cache (to make space for a different line) trigger a *partial reduction*, shown in Figure 3.4c: the evicting cache sends its partial update to the shared cache, which uses its reduction unit to aggregate it with its local copy.

The shared cache may also need to evict a line that private caches hold in U. This triggers a *full reduction*: all caches with update-only permission are sent invalidations, reply with their partial updates, and the shared cache uses its reduction unit to aggregate all partial updates and its local copy, producing the final value.

(a) Upgrade to U caused by(b) Downgrade caused by(c) Partial reduction(d) Full reduction caused by read recommutative-update request caused by eviction quest

Figure 3.4: MUSI protocol operation: (a) granting update-only (U) state; (b) downgrade from M to U due to an update request from another core; (c) partial reduction caused by an eviction from a private cache; and (d) full reduction caused by a read request. Each diagram shows the initial and final states in the shared and private caches.

Finally, read requests from any core also trigger a full reduction, as shown in Figure 3.4d. Depending on the latency and throughput of the reduction unit, satisfying a read request can take somewhat longer than in conventional protocols. Hierarchical reductions can rein in reduction overheads with large core counts (Section 3.3). In our evaluation, we observe that reduction overheads are small compared to communication latencies.

# Generalizing COUP

We now show how to generalize COUP to support multiple operations, larger cache blocks, other protocols, and deeper cache hierarchies.

**Multiple operations:** Formally, COUP can be applied to any *commutative semigroup*  $(G, \circ)$ .<sup>1</sup> For example, *G* can be the set of 32-bit integers, and  $\circ$  can be addition, multiplication, *and*, *or*, *xor*, *min*, or *max*.

Supporting multiple operations in the system requires minor changes. First, additional instructions are needed to convey each type of update. Second, reduction units must implement all supported operations. Third, the directory and private caches must track, for each line in U state, what type of operation is being performed. Fourth, COUP must serialize commutative updates of different types, because they do not commute in general (e.g., + and \* do not commute with each other). This can be accomplished by performing a full reduction every time the private cache or directory receives an update request of a type different from the current one.

$<sup>{}^{1}(</sup>G, \circ)$  is a commutative semigroup iff  $\circ : G \times G \to G$  is a binary, associative, commutative operation over elements of set G, and G is closed under  $\circ$ .

Figure 3.5: State-transition diagram of MEUSI. Just as MESI grants E to a read request if a line is unshared, MEUSI grants M to an update request if a line is unshared. For clarity, the diagram omits actions that do not cause a state transition (e.g., C requests in U).

**Larger cache blocks:** Supporting multi-word blocks is trivial if  $(G, \circ)$  has an *identity element* (formally, this means  $(G, \circ)$  is a commutative monoid). The identity element produces the same value when applied to any element in *G*. For example, the identity elements for addition, multiplication, *and*, and *min* are 0, 1, all-ones, and the maximum representable integer, respectively.

All the operations we implement in this work have an identity element. In this case, it is sufficient to initialize every word of the cache block to the identity element when transitioning to U. Reductions perform element-wise operations even on words that have received no updates. Note this holds *even if those words do not hold data of the same type*, because applying  $\circ$  on the identity element produces the same output, so it does not change the word's bit pattern. Alternatively, reduction units could skip operating on words with the identity element.

In general, not all operations may have an identity element. In such cases, the protocol would require an extra bit per word to track uninitialized elements.

Finally, note we assume that data is properly aligned. Supporting commutative updates to unaligned data would require more involved mechanisms to buffer partial updates. If the ISA allows unaligned accesses, they can be performed as normal read-modify-writes.

**Other protocols:** COUP can extend protocols beyond MSI. Figure 3.5 shows how MESI [197] is extended to MEUSI, which we use in our evaluation. Note that update requests enjoy the same optimization that E introduces for read-only requests: if a cache requests update-only permission for a line and no other cache has a valid copy, the directory grants the line directly in M.

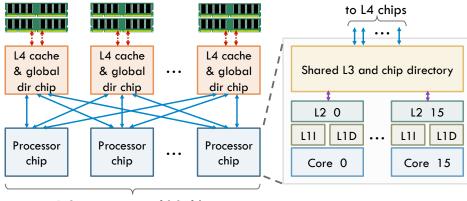

**Deeper cache hierarchies:** COUP can operate with multiple intermediate levels of caches and directories. COUP simply requires a reduction unit at each intermediate level that has multiple children that can issue update requests. For instance, a system with private per-core L1s and L2s and a fully shared L3 needs reduction units only at L3 banks. However, if each L2 was shared by two or more L1Ds, a reduction unit would be required in the L2s as well.

Hierarchical organizations lower the latency of reductions in COUP, just as they lower the latency of sending and processing invalidations in conventional protocols: on a full reduction, each intermediate level aggregates all partial updates from its children before replying to its parent. For example, consider a 128-core system with a fully-shared L4 and 8 per-socket L3s, each shared by 16 cores. In this system, a full reduction of a line shared in U state by all cores has 8 + 16 = 24 operations in the critical path—far fewer than the 128 operations that a flat organization would have, and not enough to dominate the cost of invalidations.

**Other contexts:** We focus on single-word atomic operations and hardware cache coherence, but note that COUP could apply to other contexts. For example, COUP could be used in software coherence protocols (e.g., in distributed shared memory).

## **Coherence and Consistency**

COUP maintains cache coherence and does not change the consistency model.

**Coherence:** A memory system is coherent if, for each memory location, it is possible to construct a hypothetical serial order of all operations to the location that is consistent with the results of the execution and that obeys two invariants [68, §5.1.1]:<sup>2</sup>

- 1. Operations issued by each core occur in the order in which they were issued to the memory system by that core.

- 2. The value returned by each read operation is the value written to that location in the serial order.

In COUP, a location can be in exclusive, read-only, or update-only modes. The baseline protocol that COUP extends already enforces coherence in and between exclusive and read-only modes. In update-only mode, multiple cores can concurrently update the location, but because updates are commutative, *any serial order* we choose produces the same execution result. Thus, the first invariant is trivially satisfied. Moreover, transitions from update-only to read-only or exclusive modes propagate all partial updates and make them visible to the next reader. Thus, the next reader always observes the last value written to that location, satisfying the second property. Therefore, COUP maintains coherence.

**Consistency:** As long as the system restricts the order of memory operations as strictly for commutative updates as it does for stores, COUP does not affect the consistency model. In other words, it is sufficient for the memory system to consider commutative updates as being equivalent to stores. For instance, by having store-load, load-store, and store-store fences apply to commutative updates as well, systems with relaxed memory models need not introduce new fence instructions.

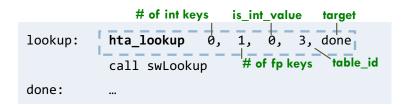

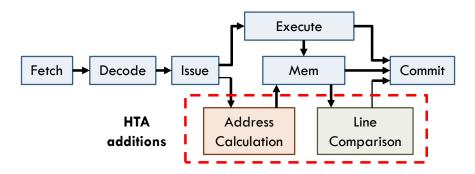

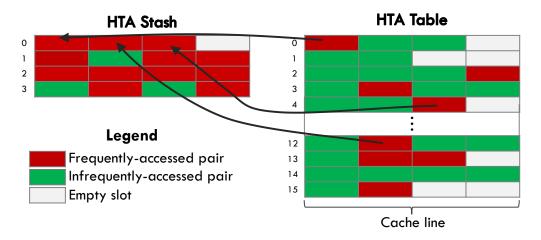

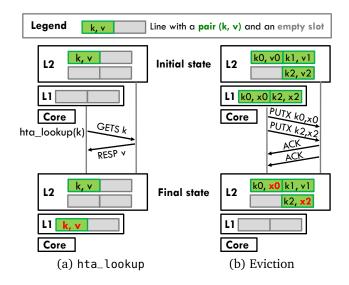

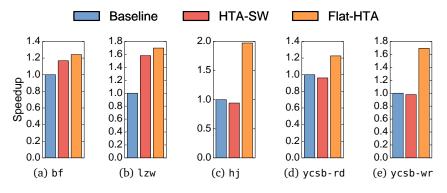

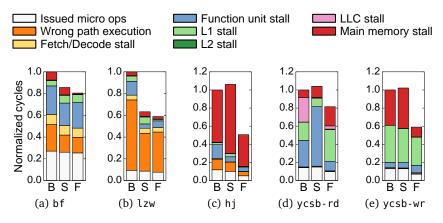

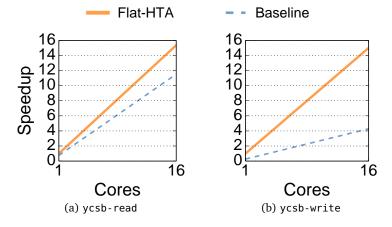

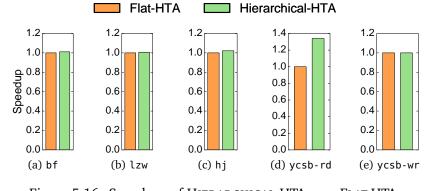

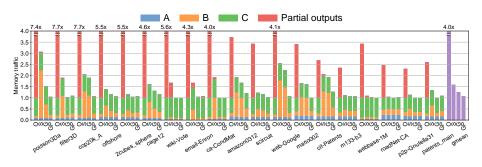

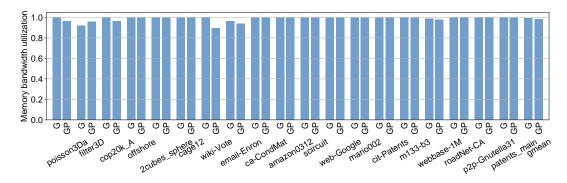

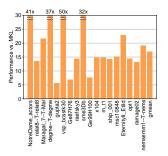

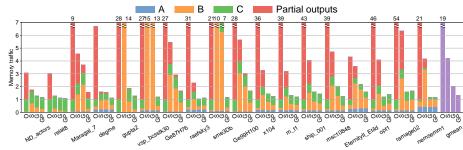

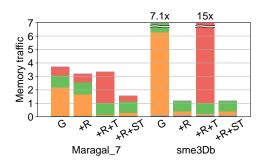

3.4