#### LOW POWER HIGHLY LINEAR CMOS OUTPUT BUFFER

FOR

#### LOW TEMPERATURE INFRARED FOCAL PLANE ARRAYS

Вy

#### David Paul Foley

B.S. Physics, M.I.T. (1980)

B.S. Elec. Eng., M.I.T. (1980)

M.S. App. Physics, Stanford University (1982)

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE IN PARTIAL FULFILLMENT OF THE REGUIREMENTS FOR THE DEGREE OF

#### MASTER OF SCIENCE

at the

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY June, 1992

© David Paul Foley, 1992. All rights reserved

The auther hereby grants to MIT permission to reproduce and to distribute copies of this thesis document in whole or in part.

| Signature | of | Author Department of Electrical Engineering and Computer Science, May, 1992 |

|-----------|----|-----------------------------------------------------------------------------|

| Certified | by | Charles G. Sodini, Associate Profesor of Electrical Engineering             |

| Centified | bу | Dr. Neal Butler, Loral Infrared and Imaging Systems                         |

| Accepted  | by | Arthur C. Smith, Department Committee on Graduate Students                  |

**ARCHIVES**

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

# LOW POWER HIGHLY LINEAR CMOS OUTPUT BUFFER FOR

#### LOW TEMPERATURE INFRARED FOCAL PLANE ARRAYS

By

David Paul Foley

#### **ABSTRACT**

A design for a low power highly linear CMOS output buffer is presented. The buffer is designed for use on NASA's Atmospheric Infrared Sounder's scanning focal planes, and is intended to operate at 60 K. Given the requirements for power dissipation, load capacitance, and settling time a class A output buffer would be unsuitable. The approach taken uses a class AB amplifier configured as a charge integrator. Thus, it converts a charge packet in the focal plane multiplexer to a voltage which is the output of the focal plane array.

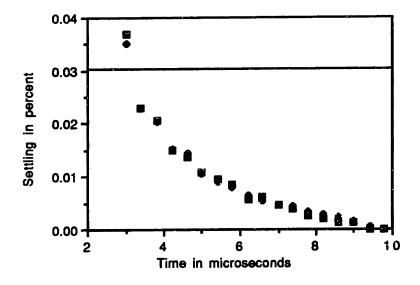

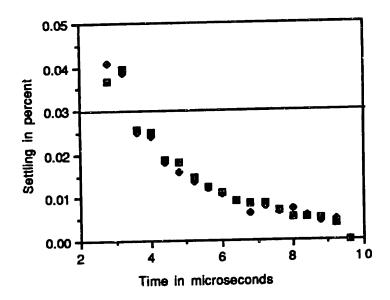

Measured performance meets or exceeds design goals in the majority of devices tested. With a quiescent current of 18 microamperes, and a load capacitance of 100 picofarads, settling to .03 % is obtained in less than 3.5 microseconds. Integral nonlinearity is less than .03% over 5.5 volts with a 6 volt supply. An output current limit imposed by device mismatch is responsible for low slew rate in some units.

Measured performance agrees with predicted performance in most areas. Excess high frequency noise is noted in the amplifier input referred noise voltage, but consistently high levels are also found in device measurements. Excess sampled noise contributions from the switch elements is observed, with RMS noise 3.5 times greater than the theoretical value. Measured maximum positive output current is larger than expected.

A technique for calculation of loop gain, suitable for numerical computation, is presented and shown to give results consistent with traditional approaches.

Thesis Supervisor: Neil R. Butler, PhD

Title: Engineering Fellow, LORAL Infrared and

Imaging Systems

# TABLE OF CONTENTS

| Abstract                                                       |     |  |  |  |  |  |

|----------------------------------------------------------------|-----|--|--|--|--|--|

| Table of Contents                                              | 3   |  |  |  |  |  |

| Acknowledgements                                               |     |  |  |  |  |  |

| 1.Introduction                                                 |     |  |  |  |  |  |

| 1.1 Overview of NASA's Atmospheric Infrared Sounder            | 6   |  |  |  |  |  |

| 1.2 Output Buffer Characteristics                              | 7   |  |  |  |  |  |

| 1.3 Development of Design Requirements for Output Buffer       | 8   |  |  |  |  |  |

| 1.4 Review of Previous FPA Output Buffer designs               |     |  |  |  |  |  |

| 1.4.1 Hybrid IR Focal Plane Array                              |     |  |  |  |  |  |

| 1.4.1.1 Source follower with voltage input                     | 14  |  |  |  |  |  |

| 1.4.1.2 Source follower with charge input                      |     |  |  |  |  |  |

| 1.4.1.3 Source follower with bipolar buffer                    |     |  |  |  |  |  |

| 1.4.2 Monolithic CCD Image Sensor Output Amplifier             |     |  |  |  |  |  |

| 1.5 Review of Class AB CMOS Amplifiers                         |     |  |  |  |  |  |

| 1.5.! Pynamic Amplifiers                                       |     |  |  |  |  |  |

| 1.5.2 Adaptive Biased Amplifiers                               | 31  |  |  |  |  |  |

| 1.5.3 Quasi-Complementary Approaches                           | 36  |  |  |  |  |  |

| 1.6 Design Approach for AIRS output buffer                     | 37  |  |  |  |  |  |

| 2. Theory of Operation: Operational Transconductance Amplifier | 40  |  |  |  |  |  |

| 2.1 General Principle of Operation                             | 40  |  |  |  |  |  |

| 2.2 Minor Loop Stability                                       |     |  |  |  |  |  |

| 2.3 Small Signal Frequency Response                            | 44  |  |  |  |  |  |

| 2.4 Dynamic Cascode Biasing                                    | 51  |  |  |  |  |  |

| 2.5 Large Signal Performance                                   | 54  |  |  |  |  |  |

| 2.6 Noise Performance                                          | 62  |  |  |  |  |  |

| 3. Theory of Operation: Output Buffer                          | 72  |  |  |  |  |  |

| 3.1 Small Signal Frequency Response                            | 72  |  |  |  |  |  |

| 3.2 Large Signal Considerations                                | 80  |  |  |  |  |  |

| 3.2.1 Integration Capacitor Reset                              |     |  |  |  |  |  |

| 3.2.2 Reset Voltage Selection                                  |     |  |  |  |  |  |

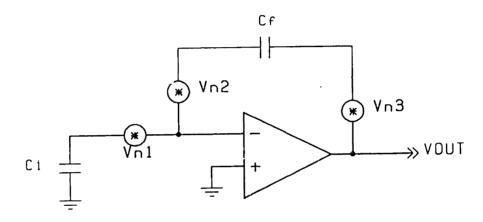

| 3.3 Noise Performance                                          |     |  |  |  |  |  |

| 3.3.1 Input Referred Noise Voltage                             |     |  |  |  |  |  |

| 3.3.2 Switch Elements                                          |     |  |  |  |  |  |

| 3.4 Power Dissipation                                          |     |  |  |  |  |  |

| 2.5 Crosstalk                                                  |     |  |  |  |  |  |

| 4. Predicted Performance                                       | 103 |  |  |  |  |  |

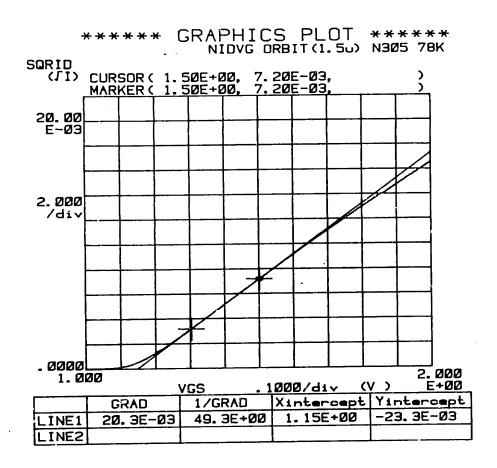

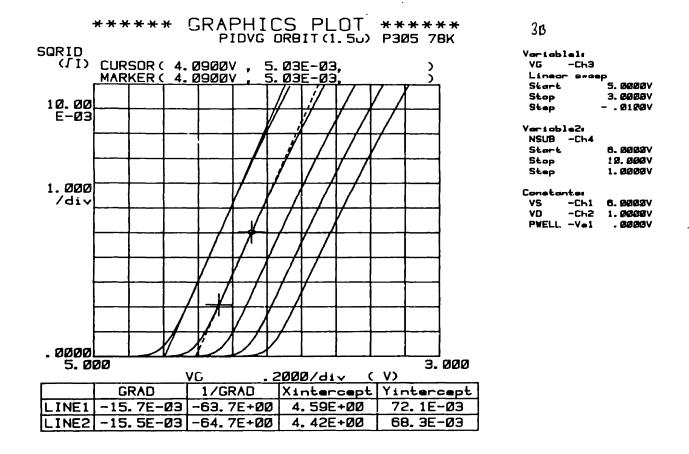

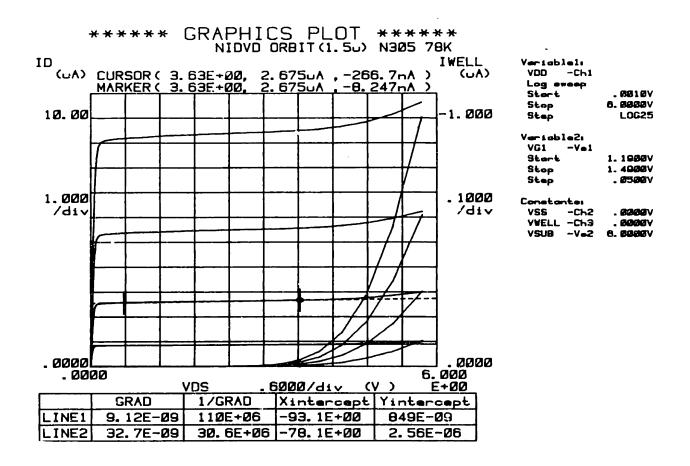

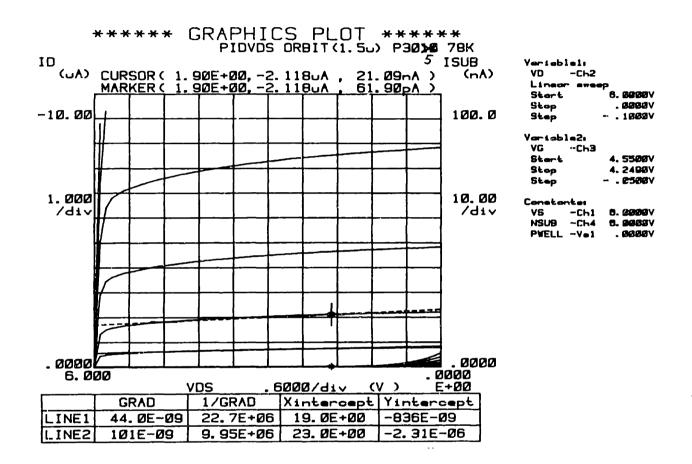

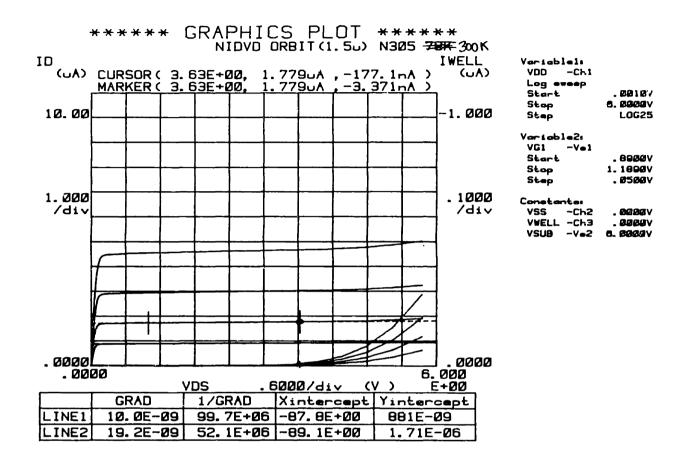

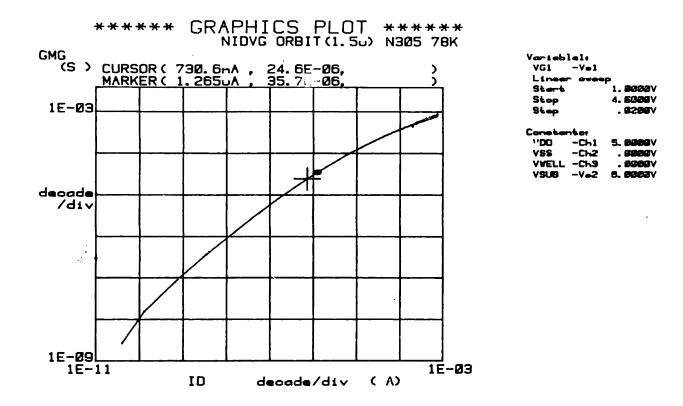

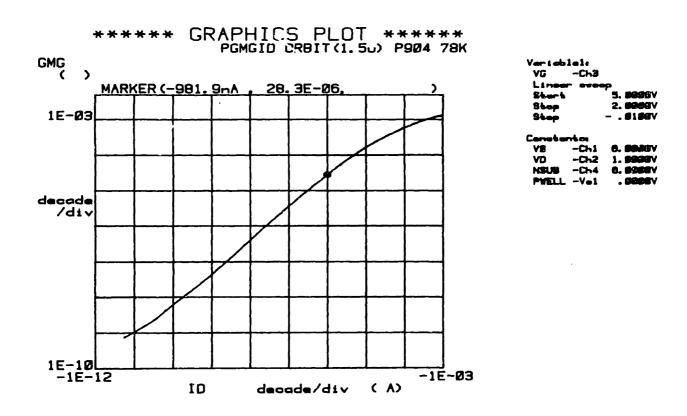

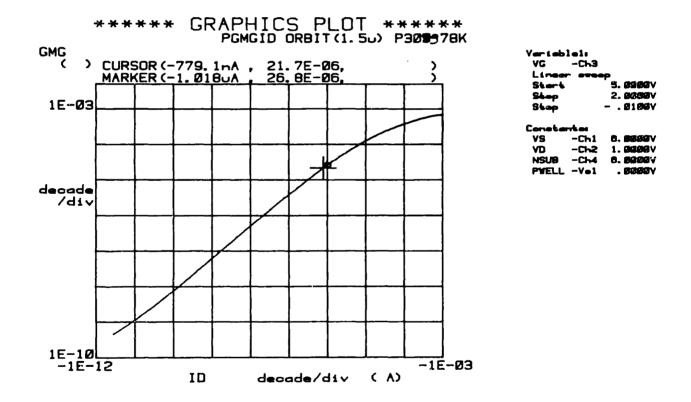

| 4.1 Orbit 1.5 μm P-well Device Parameters                      | 103 |  |  |  |  |  |

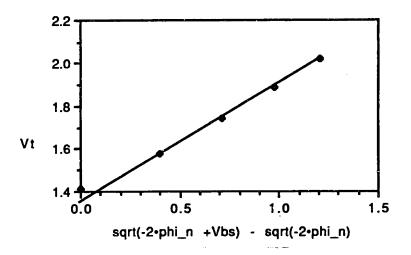

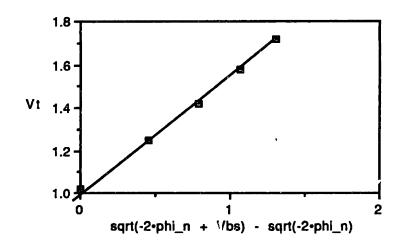

| 4.1.1 Threshold Voltage                                        |     |  |  |  |  |  |

| 4.1.2 Transconductance                                         |     |  |  |  |  |  |

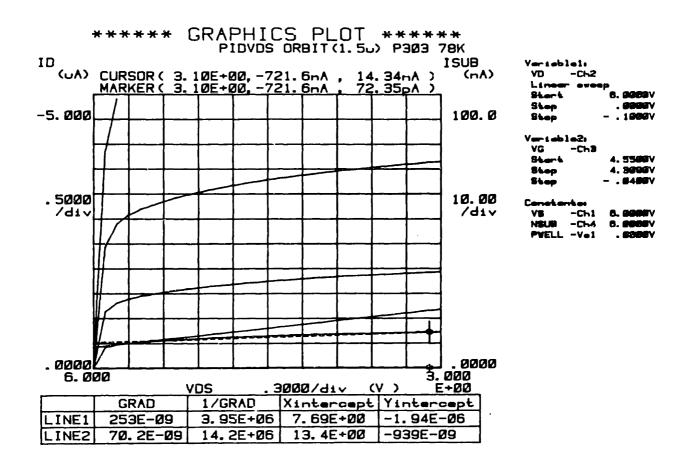

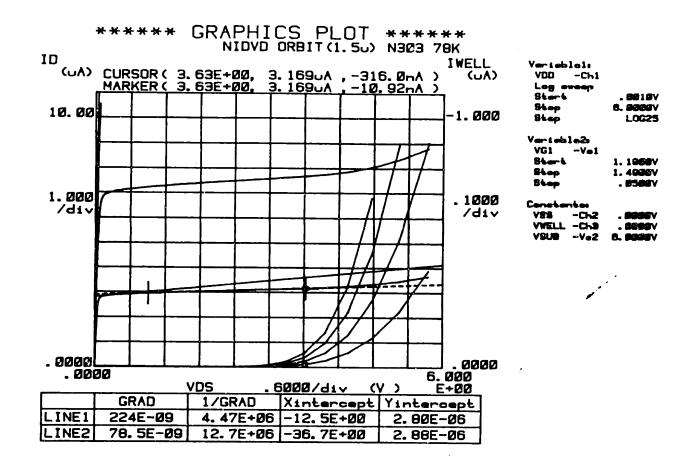

| 4.1.3 Back Gate Effect                                         |     |  |  |  |  |  |

| 4.1.4 Output Conductance                                       |     |  |  |  |  |  |

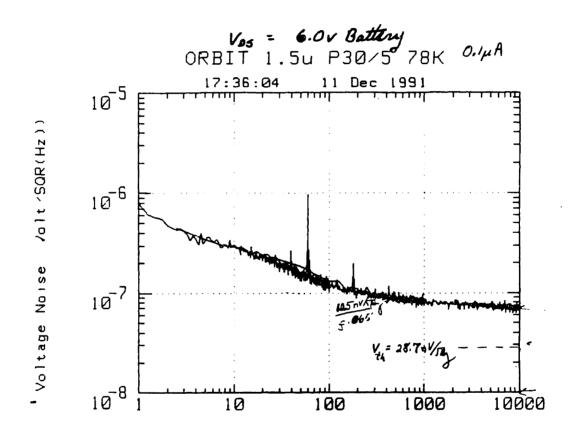

| 4.1.5 Noise                                                    | 117 |  |  |  |  |  |

| 4.2 Test Chip Output Circuits                                  | 122 |  |  |  |  |  |

| 4.3 Predicted Amplifier Performance                            | 128 |  |  |  |  |  |

| 4.3.1 Transconductance                                         |     |  |  |  |  |  |

| 4.3.2 Output Conductance                                       | 130 |  |  |  |  |  |

| 4.3.3 Small Signal Frequency Response                          | 134 |  |  |  |  |  |

| 4.3.4 Large Signal Performance                 |     |

|------------------------------------------------|-----|

| 4.3.5 Noise Performance                        |     |

| 4.4 Predicted Buffer Performance               |     |

| 4.4.1 Small Signal Frequency Response          | 140 |

| 4.4.2 Large Signal Performance                 | 142 |

| 4.4.3 Noise Performance                        | 142 |

| 4.4.3.1 Amplifier Input Referred Voltage Noise | 143 |

| 4.4.3.2 Switch Elements                        | 144 |

| 4.4.4 Linearity                                | 145 |

| 4.4.5 Crostalk                                 | 146 |

| 5. Experimental Results                        | 147 |

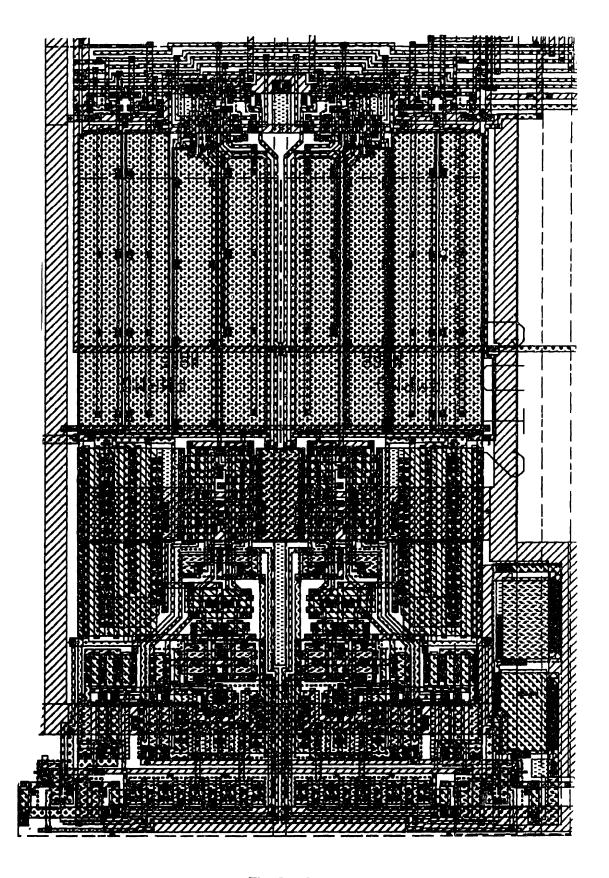

| 5.1 Layout                                     | 147 |

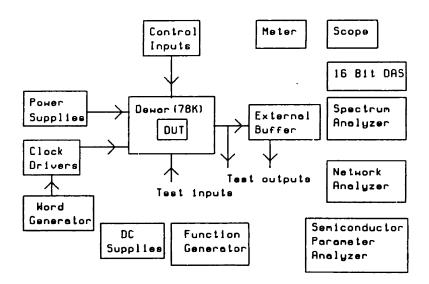

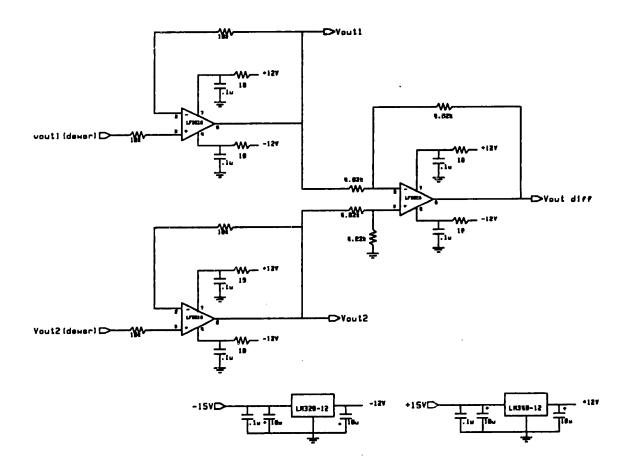

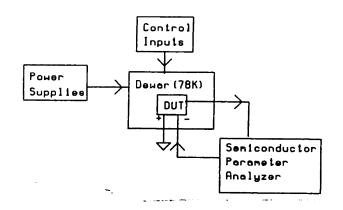

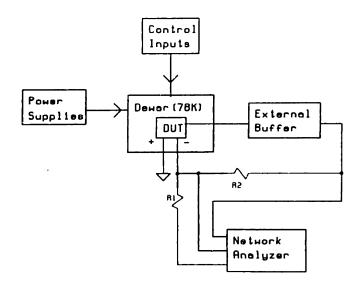

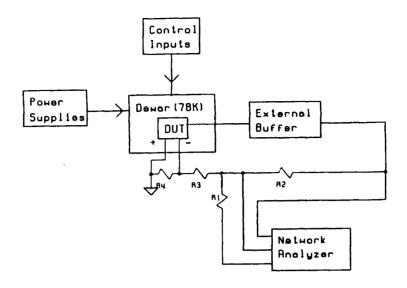

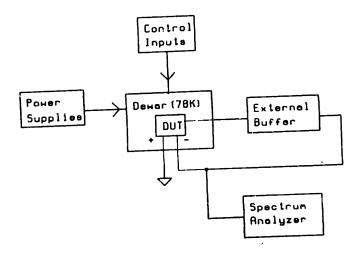

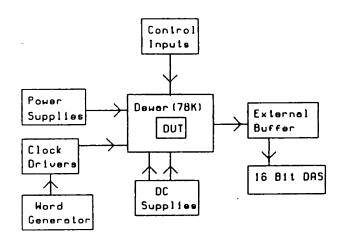

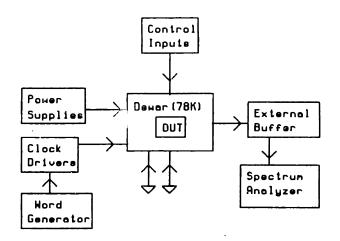

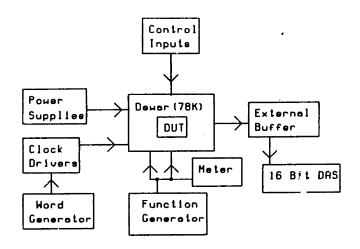

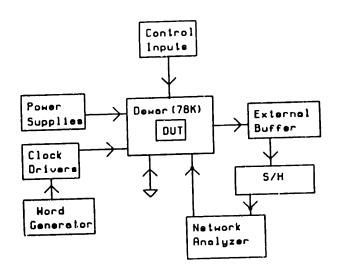

| 5.2 Test Station and Support Electronics       | 147 |

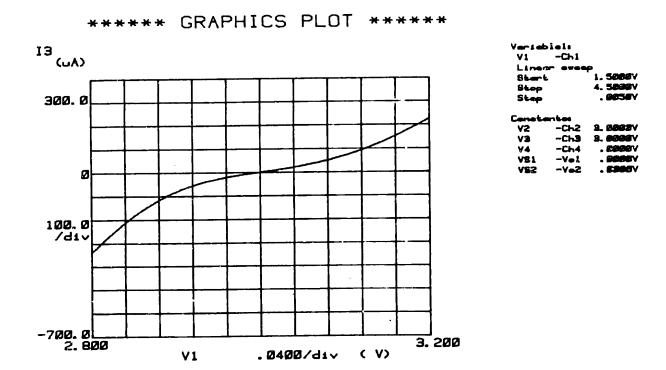

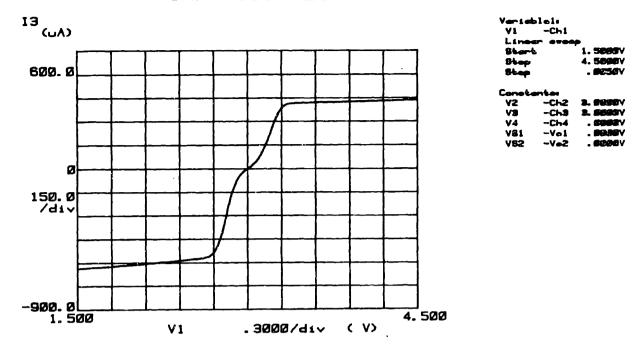

| 5.3 OTA Measurements                           | 151 |

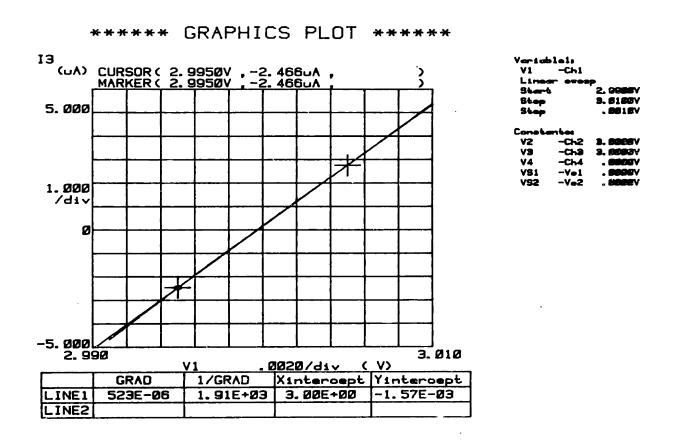

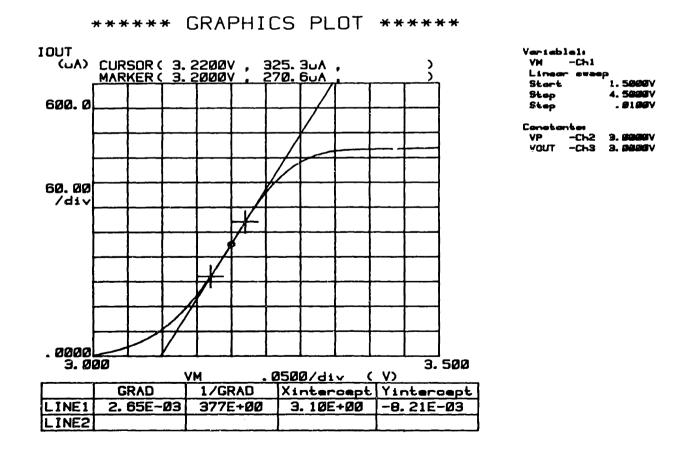

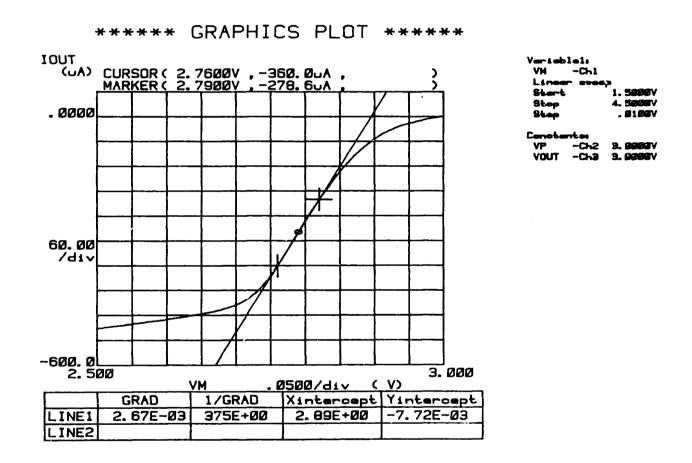

| 5.3.1 Transconductance                         |     |

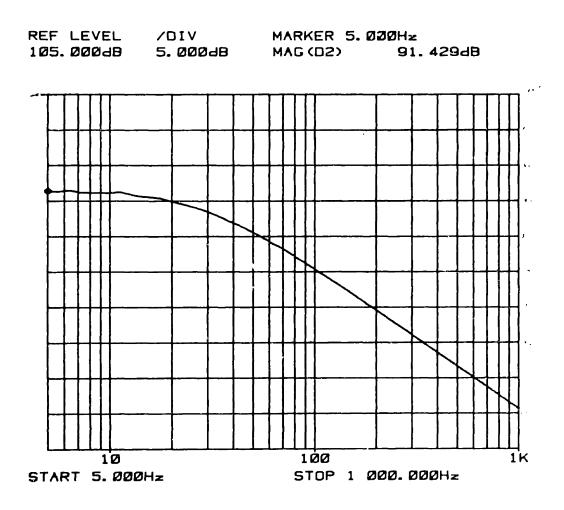

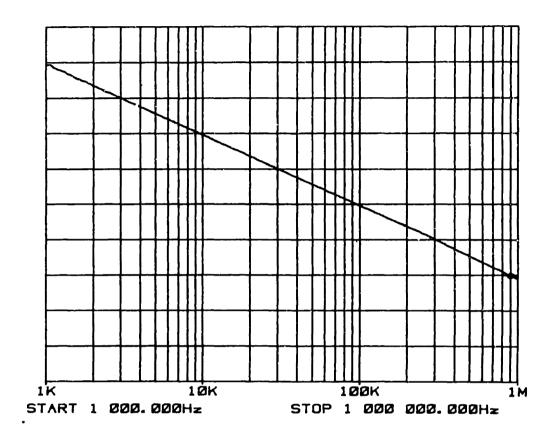

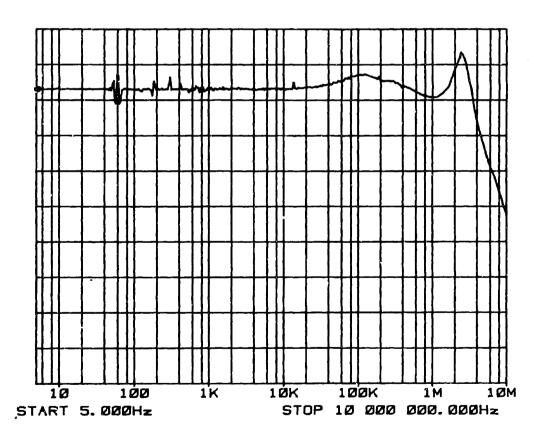

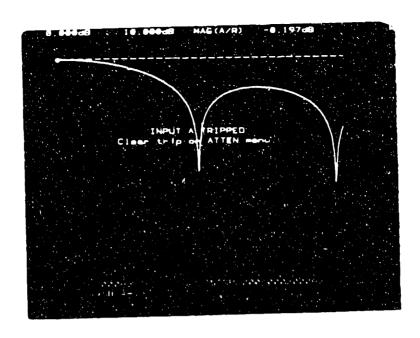

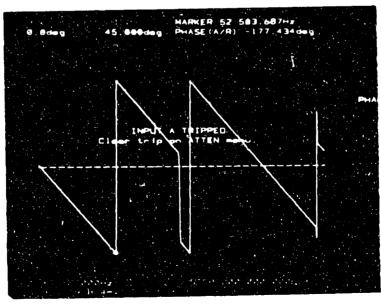

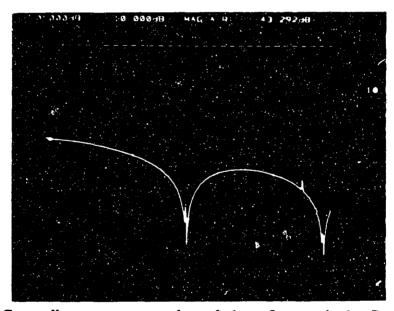

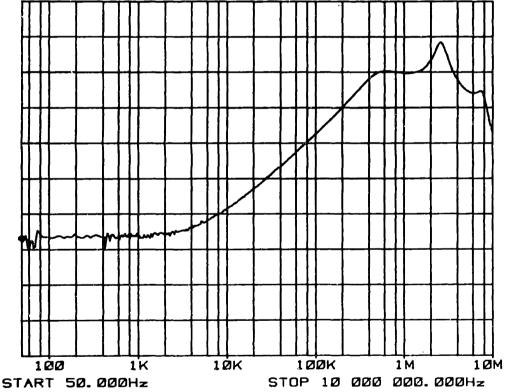

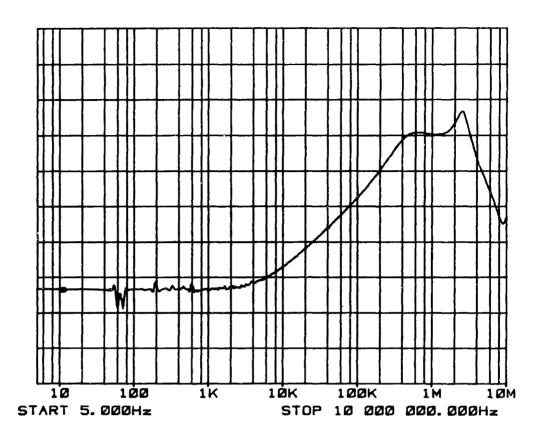

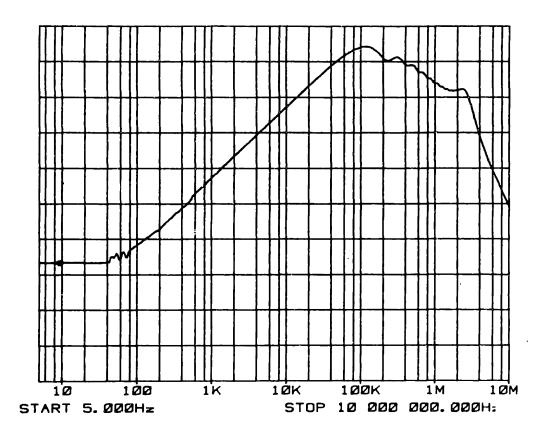

| 5.3.2 Small Signal Frequency Response          |     |

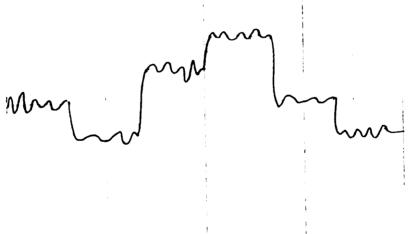

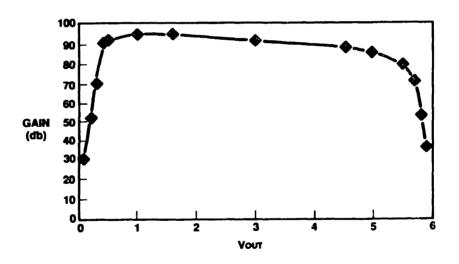

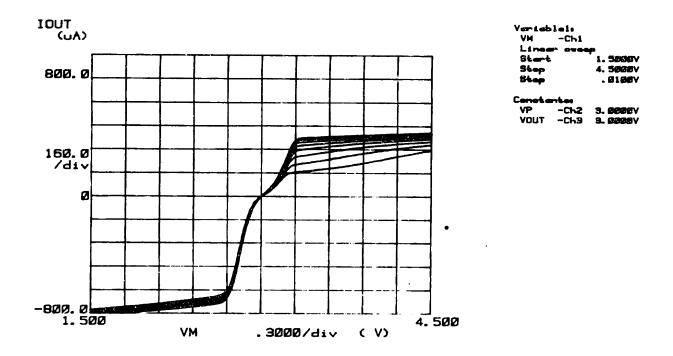

| 5.3.3 Large Signal Performance                 | 158 |

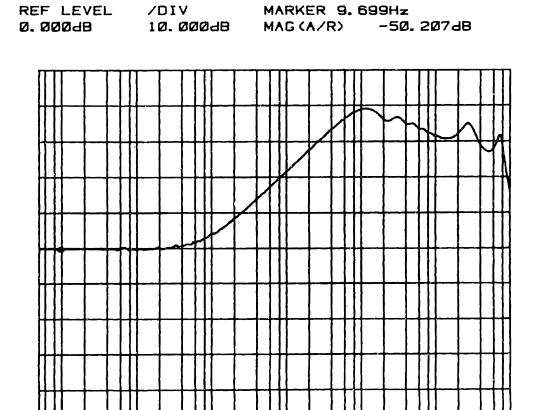

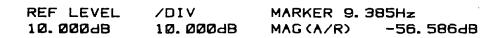

| 5.3.4 Noise Performance                        |     |

| 5.4 Output Buffer Measurements                 | 166 |

| 5.4.1 Output Impedance                         | 167 |

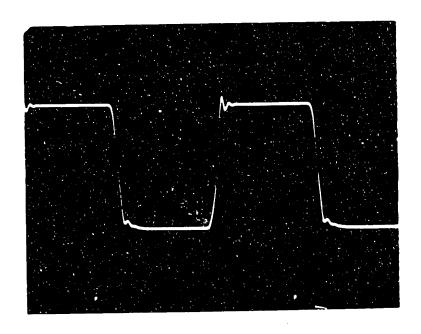

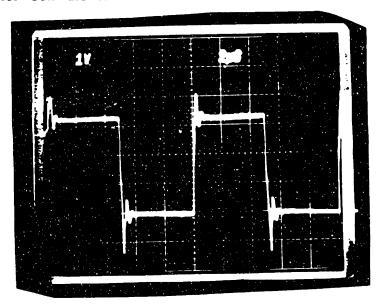

| 5.4.2 Slew Rate                                | 169 |

| 5.4.3 Large Signal Settling Time               |     |

| 5.4.4 Noise Performance                        | 174 |

| 5.4,4.1 Without Clocks Running                 |     |

| 5.4.4.2 With Clocks Running                    |     |

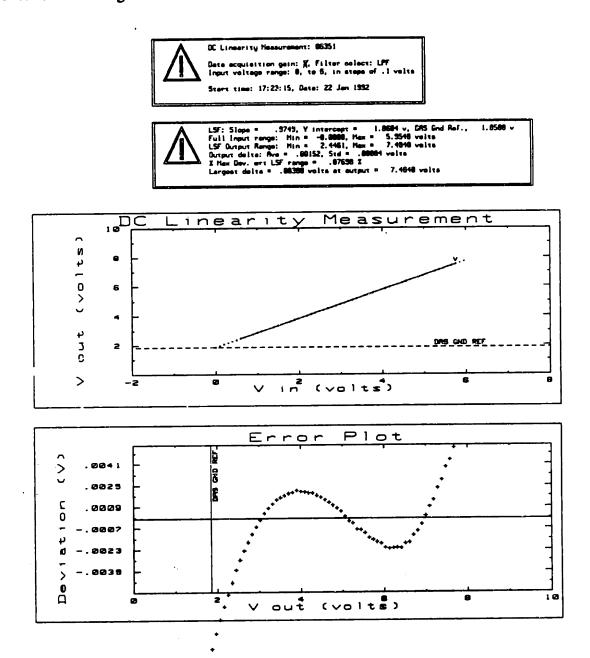

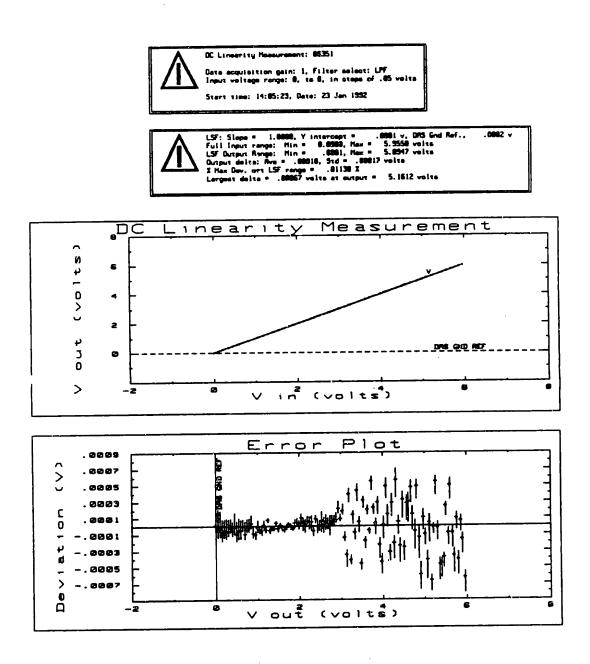

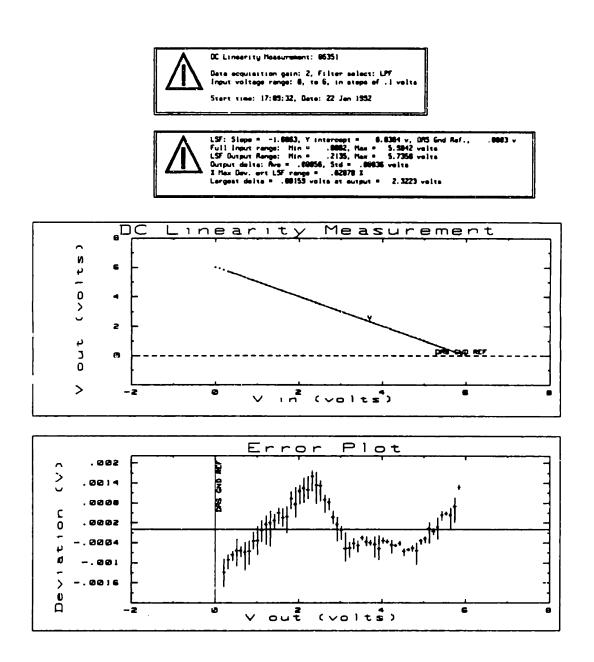

| 5.4.4 Linearity                                | 180 |

| 5.4.6 Crosstalk                                |     |

| 5.4.7 Supply Rejection                         | 190 |

| 6. Summary and Conclusions                     | 194 |

| 6.1 Result Summary                             | 194 |

| 6.2 Suggested Improvements                     | 196 |

| 6.3 Suggestions for Further Work               | 198 |

| A1 Minor Loop Stability                        | 200 |

| References                                     | 209 |

#### **ACKNOWLEDGEMENTS**

First and foremost I wish to thank my wife, Maureen. For this undertaking, sacrifices were made. More than any other single factor, her support was responsible for the success of this thesis.

I wish to thank Dr. Jill Wittels for establishing the Masters of Industry program at LORAL. For at least one person this program has provided a path where there was none.

I wish to thank Professor Charles Sodini for his comments and advice regarding this document. Dr. Neal Butler is greatly appreciated for introducing this topic to me and providing many insightful discussions which kept things on track.

I wish to thank the AIRS program team for providing a vehicle for this research. Special thanks go to Jim Stobie for his efforts to maintain an atmosphere in which this research could be conducted as part of an ongoing development program. Jim has also helped with many useful suggestions. I wish to thank David Verville and Jay Baker for help in setting up and maintaining the test set as well as assistance in performing measurements. I wish to thank Jim Stobie and Maureen Griffis for providing much of the device measurements that I have used in this analysis. I wish to acknowledge the tireless efforts of Margene Gustafson at ADS in laying out the test chip and those of Rosanne Tinkler in checking it.

I am grateful to Dr. Sato Iwasa, as head of the Focal Plane Lab at LORAL, for his efforts to provide the right environment for all of the programs and individuals in his group to thrive.

Finally I wish to thank all my co-workers in the the Focal Plane Group at LORAL. Their help and friendship was very important in making this research effort successful. In particular I wish to thank all those who refrained from borrowing my equipment while I was away at school.

This research was supported by JPL under contract 958970, and NASA prime contract NAS 7-918. This support is gratefully acknowledged.

#### 1. INTRODUCTION

### 1.1 Overview of NASA's Atmospheric Infrared Sounder

The Atmospheric Infrared Sounder (AIRS) is a research instrument that has been selected to fly on the first Earth Observing System (EOS) polar orbiting platform (4th qtr. 1996 launch)[1]. The EOS is designed to improve understanding of the earth as a system through remote observation of our environment with a comprehensive suite of instruments.

AIRS is the chief atmospheric sounder on EOS and will provide data for NASA's earth science research programs as well as NOAA operational programs (i.e. weather prediction). A major objective of AIRS is providing data which can be used to determine atmospheric temperature profiles accurate to 1° K in a vertical resolution of 1km.

To meet these and other requirements AIRS spectral resolution will cover the range from 3.4 um to 15.4 um with more than 3600 spectral measurements at a resolving power of  $\lambda/\Delta\lambda=1200$ . The noise equivalent change in temperature must be 0.2° K.

The AIRS instrument design consists of two multi-aperture, pupil imaging grating spectrometers. One spectrometer covers the spectral region (3.4-8.6 um) while the other (8.6-15.4 um). Each spectrometer contains an echelle grating and utilizes detection in several grating orders. The optical design provides spectral separation by imaging different spectral regions to different locations on the focal plane.

The focal plane/dewar assembly consists of optical filters, IR detectors, multiplexers, and dewar elements with stringent performance and alignment requirements. There are two focal planes within a common dewar both of which operate at 60°K by means of a closed cycle refrigerator. The dewar assembly

isolates the 60°k focal planes from the 155°k optical benches. The focal planes are comprised of linear mercury cadmium telluride (HgCdTe) detector arrays. Each linear array is covered by a different optical bandpass filter to isolate the proper grating order and reject stray radiation.

Every 2.667 seconds AIRS will scan a +/- 49.5 degree swath in a direction perpendicular to the EOS satellite's ground track. The scanner employs a continuously rotating 45 degree mirror and provides a spectral calibration, and a two point radiometric calibration. The AIRS instantaneous field of view (IFOV) is 1.1 degree, providing a 13.5 km diameter footprint while looking straight down from a 705 km orbital altitude.

After considerable flowdown from the system requirements, a set of design goals for the output buffers of the focal plane multiplexers were determined.

#### 1.2 Output Buffer Characteristics

Before considering the design goals for the AIRS output buffer a general discussion of output buffer characteristics is appropriate. As a circuit block the function of a buffer is to accept a signal from a previous circuit block and present it as input to a following circuit block. In the simplest case the input and output signals are circuit voltages. The signal domain of the buffer may be continuous or discrete. The same distinction can be made with the time domain. The AIRS buffer will deal with a continuous value, discrete time signal.

Figure 1.1 shows an idealized buffer for which Vout=Vin. Real buffers have performance limitations which must be considered when considering there suitability for a particular application.

Fig. 1.1

When a signal passes from one stage in a circuit to another it is generally reduced and distorted by the voltage divider that is comprised by the output impedance of one stage and the input impedance of the following stage. The principal reason for using a buffer is to improve the impedance relation that would otherwise exist between two portions of a circuit. An ideal buffer would have infinite input impedance and zero output impedance which would eliminate that portion of signal distortion which arises from this voltage divider. The input and output impedances of real buffers must be designed to interface with adjacent circuit blocks.

Aside from impedance considerations a buffer may introduce additional errors into the signal. For DC signals these limitations may be classified as input range, offset, gain, and nonlinearity. An ideal buffer would have an input range equal to the entire signal range, an offset of zero, a gain of one, and a nonlinearity of zero.

For AC signals these limitations may be classified as bandwidth, supply rejection, noise, and slew rate. An ideal buffer would have an infinite bandwidth, infinite supply rejection, infinite slew rate and zero noise.

Other buffer characteristics would include power consumption, physical size and semiconductor process. To design the AIRS output buffer values for the above characteristics need to be developed.

#### 1.3 Development of Design Requirements for Output Buffer

Some of the design requirements for the AIRS output buffer follow quite naturally from system requirements, others have arisen from baseline budgets which represented a system designer's best estimate of an optimal configuration. With a projected 4th qtr. 1996 launch, the AIRS system will certainly undergo many revisions before that date. The requirements form the starting point for An appreciation of the rational for these requirements is important the design. for a number of reasons. First it indicates the relative importance of the design requirements. This is important because it may be possible to achieve better than spec performance. In this case the designer should improve performance in that area of the design which will give the most system return. A better overall design will result if the specifications convey more information than minimum Secondly, the designer may judge for himself the validity of the requirements. An inaccurate or overly conservative requirement may render a solution impossible or overly complex. A designer should know when to challenge a requirement in order to achieve overall system improvement.

To minimize heat loss from the 60°K focal plane to the off focal plane electronics which will be at a substantially higher temperature, it is planned to use interconnections which have low thermal, and therefore unfortunately low electrical conductance. For this reason undesirable ground potential differences between the focal plane and the electronics are expected. To combat this signal corruption differential outputs are a requirement. For increased common mode rejection the differential output must be balanced. This is to say, that the impedance of each of the two lead outs must be matched. In this way their response to external stimuli will be as matched as is possible and greater rejection of common mode signals will result.

Due to the physical layout of the AIRS instrument, it is expected that three feet of cable will connect the focal plane to the electronics. The capacitive load due to this cable is projected to be 100pF.

The largest detector array is baselined to have 208 channels. Each channel integrates photocurrent for 1.23 milliseconds. This time results from a dwell time of 22.22 ms and a desire to have 18 samples per dwell in order to perform image smear compensation. The output data rate from the largest FPA multiplexer must therefore be greater than 208/1.23ms = 169 kHz. Because all channels are designed to integrate simultaneously a sample and hold function must be performed prior to readout and the output data rate requirement has been specified at 200 kHz. This leaves 5 microseconds to output each pixel.

Available cooling capacity limits focal plane active power dissipation to 60 milliwatts. 8.5 milliwatts of this amount has been budgeted to outputs. NASA redundancy requirements dictate two output buffers per multiplexer and with 17 multiplexers on the short wave focal plane this leaves 8.5 mw/(17 x2) = 250 uW available for each output.

A 1.5 micron CMOS process has been selected for the focal plane multiplexers. VDD-VSS is set for 6 volts. As large a signal range as possible is desired as it increases the dynamic range of the system. A minimum signal range of 3 volts has been baselined.

It is certainly desired that the output buffer not degrade the signal to noise ratio of the signal being output. On the other hand as long as the noise introduced by the output buffer is small compared to other noise sources then it is not worth trading off other performance parameters in order to reduce the noise still further. If one considers the channel of the AIRS instrument servicing the wavelength 3.4um one finds that taking into account the scene which is being viewed, the optics of the instrument, and the detector characteristics that the

maximum number of signal photoelectrons that can be collected in the 1.23 ms integration time is  $4x10^4$ . It is desired to integrate this charge onto a capacitor small enough to generate a full signal range of 3V but the smallest capacitor that can be consistently fabricated is estimated to be around 20 femtofarads. On this size capacitor a signal of .3V results. The input cell on the focal plane multiplexer which couples with the 3.4 um HgCdTe detector has an input referred rms noise of These numbers indicate that the signal to noise ratio for this channel will in no case be any better than about 1000 to 1. By providing gain to this channel, the output signal could be brought up to 3Volts. In this case the rms noise level of the signal would be 3mV. Analysis of each channel shows that at the output of the focal plane the signal will always have a rms noise greater than 1 millivolt. Based on this the rms noise of the output buffer has been specified at 500 microvolts. Since independent noise source combine in quadrature, output read noise would always contribute less than 12% of the total noise.

Settling time requirements depend on off chip sample and hold characteristics and the maximum signal change from one pixel to another. As neither of these have been fixed, the author has adapted a goal of settling to .03% (1 part in 3000) in 4µsec for a 3V step output change. This leaves 1µsec for the external sample and hold to acquire the output which will have settled to within a millivolt for a full signal range step change.

An initial estimate of available real estate was set at .5x.75 mm<sup>2</sup>. As only two output buffers exist on each focal plane this specification is not a very hard limit and somewhat more space could probably be made available without very much difficulty.

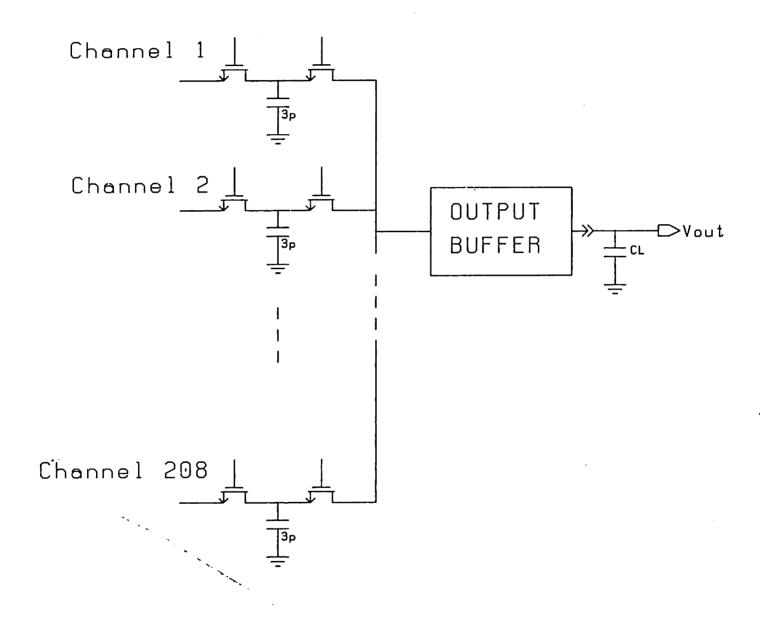

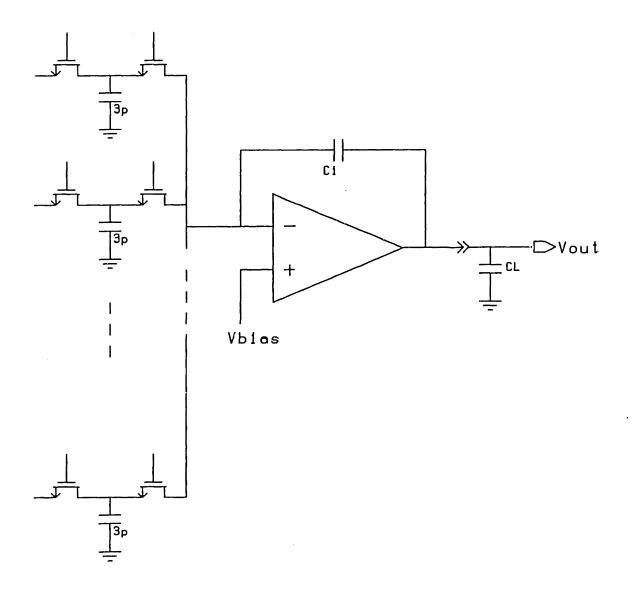

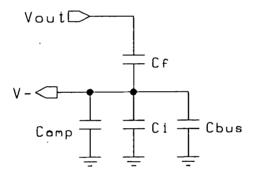

Focal plane multiplexer architecture dictated that the output buffer must take charge as its input signal from a bus shared by up to 208 channels. Pixel pitch is set at 50 microns which determines the length of the bus and therefore its

capacitance. Including the capacitance from 208 source/drain diffusions hanging on the bus, the total stray input capacitance is 1.7 picofarads. The sample capacitor feeding the bus from each channel is 3pF (fig.1.2).

Nonlinearity of the multiplexer is targeted to be better than .5%. The output buffer itself hase been budgeted to have .1% nonlinearity. This figure is interpreted as integral nonlinearity over the specified output range. A summary of output buffer requirements is given in Table 1.1

|  | Semiconductor | Process | Orbit | 1.5u | twin | well |

|--|---------------|---------|-------|------|------|------|

|--|---------------|---------|-------|------|------|------|

Operating Temperature 60°K

Data Rate 200 KHz

Settling Time(to .03% for 3V step) 4µs

Output Range 3 volts

Integral Nonlinearity .1%

Noise  $500 \,\mu\text{V}$  RMS

Power  $250 \,\mu\text{W}$

Capacitive load 100 pF

Area  $.375 \text{ mm}^2$

TABLE 1.1

Fig. 1.2

#### 1.4 Review of Previous Output Buffer Designs

#### 1.4.1 Hybrid IR Focal Plane Arrays

#### 1.4.1.1 Source follower with voltage input

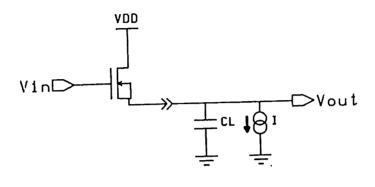

The simplest output structure is the source follower (fig.1.3).

Fig 1.3

Because of it's simplicity, this has been enormously popular. This circuit comes in p and n channel varieties which may have their wells connected to there sources if the fabrication allows. Characteristics of this circuit can be found in introductory circuit texts. The current source is generally located off chip to reduce on chip power dissipation. Because it is the prevalent output buffer a summary of its characteristics follow.

Signal range: The output for the n channel follower is one  $V_{gs}$  below the input. This  $V_{gs}$  drop is often lost from the overall signal range. Unfortunately, MOS transistor threshold increase by about .4 volts when cooled to LN2 temperatures so zero bias thresholds of up to 1.4 volts may be anticipated. If the output transistor is not source connected a further increase in threshold occurs due to  $V_{sb}$ . When operating in strong inversion the transistor  $V_{gs}$  exceeds the threshold by an amount  $\Delta v$  which depends on the bias current.

$$\Delta v = \sqrt{((2I/k(W/L)))}$$

(1.1)

Equation 1.1 is derived from the square law relation for MOS drain current and is valid for Vgs sufficiently above threshold yet small enough so that mobility degradation effects have not yet become apparent. Even at LN2 temperatures (77°K) MOS device equations such as those used in SPICE are generally valid. Certain parameter values do change in a way which is not consistent with the temperature dependance assumed in SPICE. This is because SPICE was not designed for cyrogenic operation. One must extract parameters from device data measured at operating temperature to use for cryogenic circuit design. In order to recover some of the lost signal range the source of an n channel follower can be allowed to go below VSS if it's well is tied to it's source. In this configuration the voltage on the well substrate junction exceeds VDD-VSS. This may be acceptable because the well to substrate breakdown voltage is generally larger than the source/drain diffusion to wel! breakdown voltage because it is a more lightly doped junction.

Offset, Gain, Linearity: The offset of a voltage follower has just been described. The small signal gain of a source connected follower is given by

$$a_v = g_m r_0 / (1 + g_m r_0)$$

(1.2)

This figure can be very close to unity at low currents because the product  $g_{m} r_{0}$  increases with decreasing current until the subthreshold region of operation is entered. However n channel followers can suffer severe degradation of  $r_{0}$  at high  $V_{ds}$  due to impact ionization. This degradation results in a drop in small signal gain and a nonlinearity in the overall transfer characteristic.

Impact ionization occurs because the electric field in the pinch off region of the transistor channel becomes quite large as the Vds increases. Despite fabrication steps to keep this field low scaling laws dictate that smaller geometry processes must use higher doping densities and the mechanisms for large electric

field strengths are ever present. When electric field strengths reach a certain value known as  $E_{sat}$  the energy acquired by a drift electron between collisions is enough to create an electron hole pair. This energy loss mechanism is sufficient to keep the drift velocity of the electron from increasing as the electric field is increased beyond  $E_{sat}$ . This is why  $E_{sat}$  is known as the saturation field strength. At large  $V_{ds}$  the field in the pinch off region is often large enough for impact ionization to be a major effect. Because the electron created in the electron hole pair is free to itself cause further ionizations avalanche multiplication takes place and the drain current increases rapidly with  $V_{ds}$ . In an n channel device the excess electrons created in the pinch off region are attracted to the drain while the holes are attracted to the substrate. For this reason a corresponding increase is seen in substrate current when impact ionization is taking place. Impact ionization is not generally a problem in p channel transistors because holes have lower mobilities and therefore larger saturation field strengths.

A follower which is not source connected will have a nonlinearity due to the back gate effect. The back gate effect increases the threshold of the transistor by an amount which depends nonlinearly on voltage between the source of the transistor and the well of the transistor.

Bandwidth: The small signal bandwidth of a follower is given by

$$\omega_{3db} = gm / CL \tag{1.3}$$

As it consists of a single transistor, all the power dissipated by a source follower is used in generating  $g_m$  and hence bandwidth. In subthreshold operation the  $g_m$  of the transistor is given by

$$g_{m} = I/\eta \cdot V_{th}$$

(1.4)

while in strong inversion it is given by

$$g_{\rm m} = \sqrt{(2 \cdot I \cdot k \cdot W/L)} \tag{1.5}$$

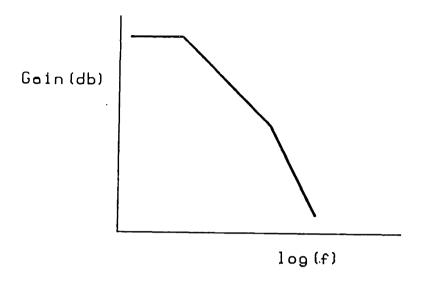

The transition between these expressions can be more than a decade broad in drain current (fig 4.14). In order to obtain the most  $g_m$  for a given current it is desirable to operate the transistor in the subthreshold region. In the subthreshold region the  $g_m$  does not depend on the width and length of the transistor so that if the transistor is too deeply into the subthreshold region it is larger than it need be and has more gate and stray capacitance than it need be to obtain a given  $g_m$ . A good tradeoff of these characteristics exists in the transition region between subthreshold and strong inversion. Actual device measurements are required to determine  $g_m$  accurately in the transition region.

Slew Rate: A serious drawback of the follower is its slew rate limitation. For the n channel follower shown in fig. 1.3 there is no positive slewing limitation, but

$$SR- = I/C_L \qquad (1.6)$$

This limitation can become severe if the capacitive load is large enough.

Operation at fixed power and speed can become impossible.

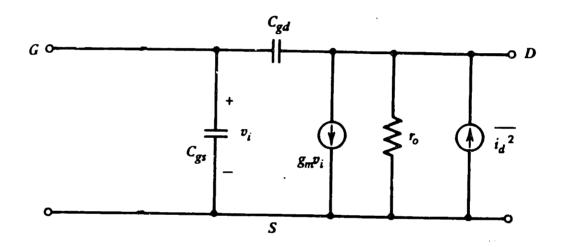

Noise: The input referred noise model of a MOS transistor has been given by

$$V_{eq}^{2}/\Delta f = 8kT/3g_{ni} + k_{F}/WLC_{ox}^{2}f$$

(1.7)

Since the source follower has relatively large  $g_m$  and large gate area for a given current it has good noise properties.

Input, Output Impedance: The source follower connection has good input impedance since only a fraction of the  $C_{gs}$  of the transistor appears as input impedance. Because the follower has near unity gain the voltage of the source follows the voltage at the gate. For this reason Vgs changes by a small fraction of the input voltage change and the effective capacitance presented by  $C_{gs}$  is diminished by this fraction. The gate to drain overlap capacitance  $C_{gd}$  can be quite small in all but very large devices. The output impedance is given by  $1/g_m$  and for a follower designed to give maximum bandwidth for a given power dissipation the impedance is minimized.

### 1.4.1.2 Source follower with charge input

Fig. 1.4

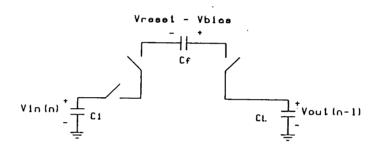

The source follower can also be configured to accept charge as an input. This technique was prevalent in hybrid IR focal plane arrays with CCD multiplexers and can also be used in CMOS multiplexers. It is basically the same as the floating diffusion amplifier used in silicon CCD imagers. All of what was said about a voltage input source follower applies here.

In addition, another noise term is present due to the resetting of the input When a capacitor is reset to a given voltage it is found that the capacitance. voltage on the capacitor after the reset operation differs in a random way from the reset voltage. This phenomenon is due the thermal noise in the switch The spectral voltage noise power in the switch element is proportional clement. to its resistance. The switch resistance and the capacitor form a low pass filter whose noise bandwidth is inversely proportional to the switch resistance. The mean square noise voltage is equal to the product of these terms and is independent of the switch resistance. This fluctuating noise voltage is sampled on the capacitor when the switch is opened. It is interesting to note that the switch opening may be looked on as the switch resistance becoming very large. model the noise bandwidth of the low pass filter becomes very small and the voltage on the capacitor is constrained to fluctuate quite slowly compared to when the switch was in the on state. In this way the fluctuating noise voltage becomes sampled when the switch is opened. The RMS value of this fluctuation is given by

$$V_{RMS}^2 = kT/C (1.8)$$

Unlike CCD imagers the noise already present in the input charge packet Q is generally larger than the read noise of the output amplifier. Read noise of the output amplifier is seldom a dominant noise source in hybrid IR focal plane arrays so amplifier designs are not driven by low noise requirements.

### 1.4.1.3 Source follower with bipolar buffer

In order to solve the negative slewing problem of the source follower, the circuit of fig 1.5 has been used.

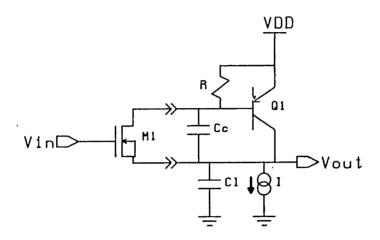

Fig. 1.5

A detailed analysis of this circuit shows similar small signal characteristics as the follower while the slewing characteristics can be determined by a much larger current than the on chip quiescent current. Unfortunately the number of lead brought off chip must be doubled in this configuration. The pair of leads brought off chip for this output buffer do not have matched impedance characteristics. To provide a differential balanced output would require four leadouts which is a doubling of the allotted two. This is not a problem for a focal plane with a single output, but the airs focal planes (long wave and short wave) have a total of 68 outputs with an allotted 132 leadouts. It would be a rather poor trade to double this number.

#### 1.4.2 Monolithic CCD Image Sensor Output Amplifiers

Charge Coupled Devices (CCD's) were invented in 1970 [2]. Although originally conceived as a memory device, the primary use of CCD's over the past two decades has been as an imaging sensor.

Evolution of output amplifiers for CCD operation has been in the direction of lower noise. These systems apparently have not required operation in a domain where speed, power, and capacitive load are incompatible. All outputs have been based on a single transistor and differ only in the way in which the signal charge is coupled to the transistor.

As process improvements in CCD manufacture improved the read noise of the output amplifier became the dominant noise source.[3] This provided a considerable impetus to improve the output amplifier design. This is especially true at low light levels where the shot noise of the signal packet is very small.

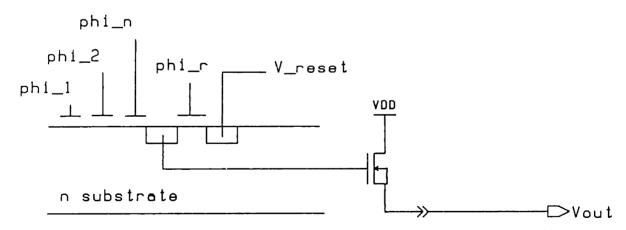

The first CCD output amplifier was the floating diffusion amplifier [4,5] which is shown in figure 1.6

Fig. 1.6

The signal charge is transferred to a floating diffusion where it generates a certain voltage according to the capacitance of the diffusion. This voltage appears at the gate of a MOS transistor where it can be read out with the transistor acting as a source follower. The diffusion is then reset to fixed voltage and the

circuit is ready for the next output. There are three sources of noise in this circuit. They are the kT/C reset noise of the floating diffusion, MOSFET 1/f noise and MOSFET thermal noise. The output noise voltage can be referred to the input by multiplying by the diffusion capacitance.

The reset noise of the diffusion capacitor was eliminated by a technique known as correlated double sampling (CDS) [6] in which two samples were taken for each output, one just after resetting the floating diffusion and another after the signal charge has been transferred to the floating diffusion. By subtracting these two measurements, the reset noise is eliminated from the measurement. This technique also reduces some of the low frequency 1/f noise.

The thermal noise is inversely proportional to the transconductance of the amplifier so to reduce this a large width transistor is desirable. The 1/f noise is inversely proportional to the gate area of a transistor so likewise a large geometry device is desirable. A small diffusion capacitance is desired because this increases the node sensitivity and reduces the input referred noise measured in electrons. No consideration is required of the floating diffusion reset noise since it has been eliminated by using CDS. The considerations to produce minimal noise come into conflict because a larger transistor (lower 1/f and thermal noise) introduces a larger parasitic gate to drain capacitance on the floating diffusion (smaller node sensitivity). Studies have been done to optimize these geometries for minimum input referred noise electrons.[7]

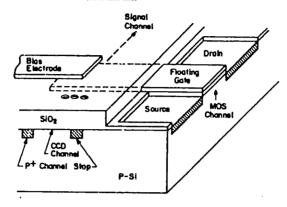

Wen introduced the floating gate amplifier in 1974.[8] Figure 1.7 is a diagram of a fioating gate amplifier. In the floating gate amplifier the charge packet is shifted directly under the transistor gate electrode. The signal is capacitively coupled to the transistor gate which can be operated as a follower. The charge is then shifted out from under the gate and the amplifier is ready for another input.

#### FLOATING GATE AMPLIFIER

Fig. 1.7

The important thing to note about this technique is that it is nondestructive. The same charge packet can be read out more than once. Reset noise is also eliminated since there is nothing to reset.

More recent amplifier designs[9-13]have utilized novel fabrication steps to achieve a higher node sensitivity and therefore smaller input referred noise electrons. Reducing parasitic capacitance at the transistor gate is one way to reduce the input capacitance and increase node sensitivity. Lightly Doped Drain (LDD) structures reduce the parasitic gate to drain capacitance by reducing the overlap of the gate over the diffusion. The LDD tip is driven to a shallower depth than a conventional source/drain diffusion and therefore diffuses laterally under the gate by a smaller amount. Dynamic range is also an issue with designs with high node sensitivity. Video sensors must operate with a wide bandwidth so achieving low noise is more challenging than with slower readout rate applications.

In astronomical applications readout rates can be much slower and thermal noise can be reduced by using a smaller bandwidth. New floating gate

designs[13-14] are designed to output designated pixels repeatedly and average the results off focal plane for a square root on N noise reduction.

# 1.5 Review of Class AB CMOS Amplifiers

Class AB CMOS amplifiers may provide potential solutions for the AIRS output buffer because the total current they can deliver to or pull from a load is larger than the dc quiescent current of the amplifier. This feature should allow large output voltage swings without slew rate limitations.

An amplifier used in a feedback application may provide better performance than a source follower output alone because the amplifier may have more than one stage of amplification. The dc gain of the amplifier is an important factor in determining the linearity of the buffer and with two stages of amplification a dc gain of the order of  $(g_m r_0)^2$  can be obtained. With unity feedback the closed loop gain will be of the form

$$a_v = (g_m r_o)^2 / (1 + (g_m r_o)^2)$$

(1.8)

When compared with the small signal gain of the follower it is apparent that better linearity can be obtained. The linearity of a follower will probably be determined by the amount of impact ionization. This is hard to estimate as it is very process dependant so that measured results should quantify this distinction.

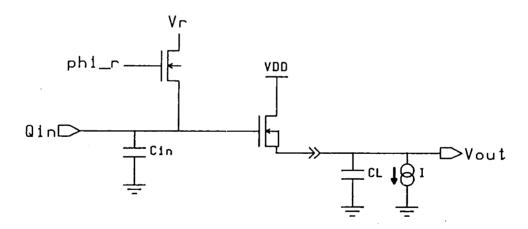

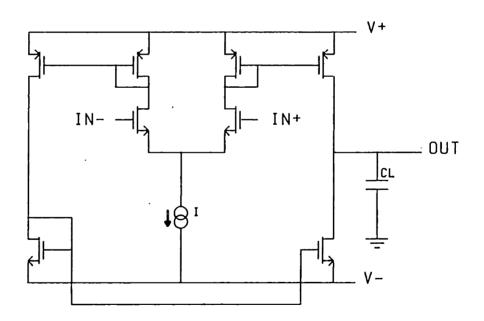

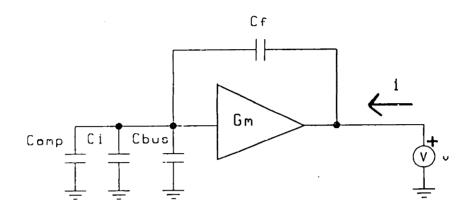

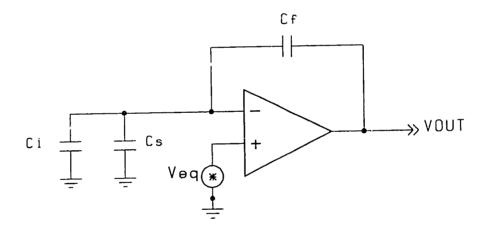

The architecture of figure 1.2 is easily achieved by configuring an amplifier as a charge integrator. With a differential amplifier the quiescent voltage on the bus is easily controlled with a bias voltage on the noninverting input. This concept is shown in figure 1.8

Fig. 1.8

Unfortunately a Class AB CMOS output stage with wide applicability does not exist. In bipolar design the complementary emitter follower stage has received widespread use. The CMOS analog to this circuit is the complementary source follower stage[15]. The drawback which has prevented this from becoming a standard is the reduction in output voltage range which is caused by the gate to source voltage drops of the n and p channel MOS transistors. Given the low supply voltages found in small geometry CMOS processes, threshold voltages in the .5v to 1.0v range, and the fact that one of the thresholds will be increased due to the back gate effect, the resulting output range is often inadequate. of this circuit is even more problematic at cryogenic temperatures due to the fact that threshold voltages increase by .4 volts as the temperature is reduced from 300 <sup>o</sup>K to 77 <sup>o</sup>K. Special process modifications can be employed to reduce thresholds, but with standard processing this circuit has limited applicability. In this case 3 volts of output range are needed with a 6 volt supply. If each threshold is assigned a magnitude of 1.15 V then the increase of threshold due to back gate affect must This is unlikely because in the complementary source be less than .7 volts. follower connection the back gate voltage is maximum when the limits of output range are encountered. Orbit semiconductor's 1.5 um twin well process has been selected for fabrication. Process options such as low threshold devices or bipolar transistors are not available. Only designs with standard process options are considered here.

#### 1.5.1 Dynamic Amplifiers

Dynamic MOS amplifiers were introduced by Copeland and Rabaey.[16] The idea is to allow the amplifier bias current to change as a function of time in switched capacitor circuits. The clocks used in switching charge from capacitor to capacitor are used within the amplifier itself to control its bias current.

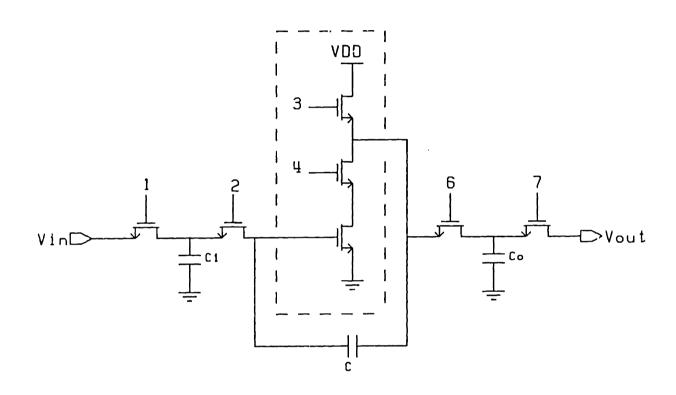

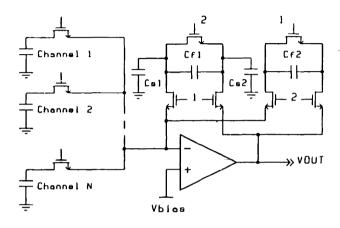

A charge integrator proposed in [16] is shown if figure 1.9 The amplifier is within the dotted line.

Fig. 1.9

Fig. 1.10

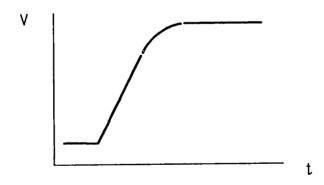

The circuit works as follows: The input voltage is sampled on C<sub>i</sub>. Next the output is pulled high and the sampled charge is dumped on the inverting node of the amplifier. Finally the transistor is connected with the output and it draws current from the output capacitor C<sub>0</sub> and the feedback capacitor C until the voltage at the inverting node returns to the threshold of the device. The bias current of the device can be quite large initially but will always approach subthreshold values at the end of the clock cycle. The potential for power savings from this circuit is clear since there are no dc bias currents. The dc accuracy is good because the current is at its lowest at the end of the cycle. This particular switching scheme resets the output at each cycle which is not a good feature with a large capacitive load since this can represent a significant power loss. Another modification which is necessary for use as a charge integrating output amplifier is a means of resetting the integration capacitor.

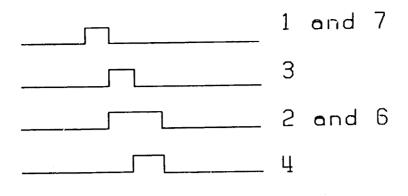

Hosticka[17] showed how classical amplifiers could be converted to dynamically biased amplifiers by replacing current sources by pulsed current sources. He uses pulsed current sources which are nothing more than capacitors that are periodically charged and discharged. Figure 1.11 shows a CMOS differential stage with such a current source.

During the clock period phi the tail capacitor is discharged and during the clock period phi-bar it becomes charged as the amplifier is operating. The size of

Co must be chosen properly since for classical topologies the total charge that the amplifier can put out in one cycle is directly proportional to the charge stored on a current source capacitor in the circuit. Also the size of the capacitor places a limit on how large a frequency the circuit can be run at. It is desired that the tail current drop to a subthreshold value by the end of the cycle so that high gain is obtained. If the tail capacitor is too large, the bias current may still be too large at the end of the cycle.

Fig. 1.11

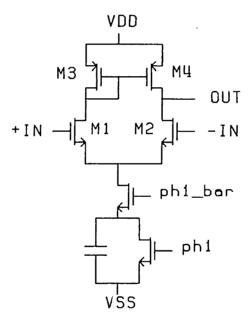

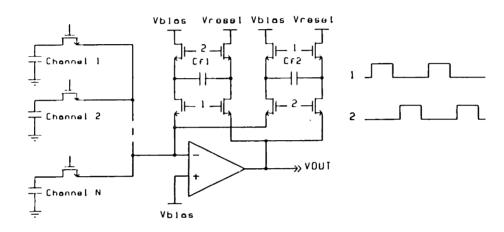

Hosticka also presented a switched capacitor integrator similar to that of Copeland and Rabaey. This is shown in figure 1.12. Phi and phi-bar are two phase nonoverlapping clocks. This is essentially a complementary version of the Copeland and Rabaey circuit where the M1 and M2 may pull the output up or down depending on the polarity of the input signal. Once again as the input mode is

returning to ground the bias current is dropping into the subthreshold region and high gain is obtained.

If this circuit is considered for use as an output buffer one must consider that while high gain is obtained at the end of the cycle, the subthreshold currents flowing will yield such a low g<sub>m</sub> that a problem develops with high output impedance. If the output is capacitively coupled to any unwanted signals, whatever there origin, the output impedance of the output buffer will determine how effectively these signals will be rejected. No requirement has been given for the output impedance of the AIRS buffer. Balanced differential outputs will help reject common mode pickup, but it is hard to quantify the amount of rejection obtainable or the amplitude of the spurious signals present.

Fig.1.12

In consideration of the output impedance issue it seems that a version of figure 1.12 in which the currents settle to a controlled finite value rather than to zero would be desirable.

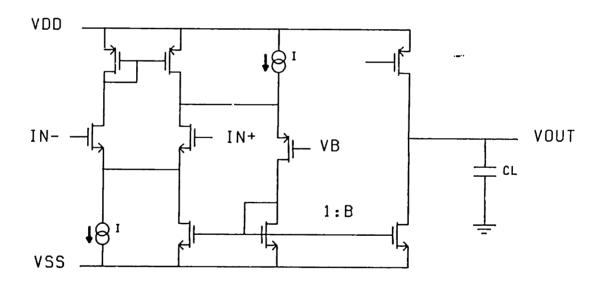

#### 1.5.2 Adaptive Biased Amplifiers

Degrauwe et al.[18] introduced a class of amplifiers in which the bias current is dependent on the input signal without requiring internal clocks in the amplifier. These amplifiers were not limited to sampled data analog circuits but are generally applicable.

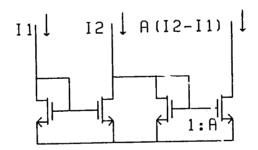

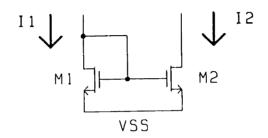

For an input differential stage the idea is to increase the tail current based on the amount of imbalance in the input stage currents. The imbalance is measured with a current subtractor as shown in figure 1.13

Fig. 1.13

The currents in each leg of the input stage are mirrored into the current subtractor. The output of the current subtractor augments the quiescent tail current bias. Subtractors must be added for both possible polarities of input stage imbalance since the bias current must be increased in either case. An operational transconductance amplifier (OTA) based on this principle is shown in figure 1.14. For simplicity, the current subtractor is only shown for one polarity

of imbalance. The effects of mismatches in the current mirrors as well as the stability of the local feedback are issues that must be considered.

An attractive feature of the adaptive bias concept is that if input signals are not present power dissipation remains at its quiescent value. Pulsed current sources in the dynamic amplifiers introduce large bias currents independent of the input signal. Thus an adaptively biased amplifier may show lower power dissipation than a dynamic amplifier.

Fig.1.14

Another attractive feature of the adaptive biased amplifier is that as the amplifier settles the bias current approaches a well controlled value. The bias current of the dynamic amplifiers approaches zero as the amplifier settles. Thus an adaptively biased amplifier will show lower output impedance than a dynamic amplifier.

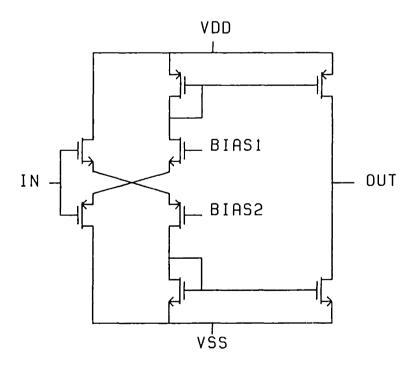

A class AB OTA which utilized n channel - p channel source coupled inputs was used by Costello and Gray.[19]. A simplified version of this is shown in figure.

1.15. Biasing for proper quiescent current and input range are issues with this design. A low voltage process coupled with high transistor thresholds can make this difficult to use for cyrogenic applications. The most severe problem however is the reduction of gm in the input due to the source coupled n/p transistors. The effective transconductance of a source coupled n/p pair is the parallel combination of the individual transconductances.

$$1/g_{\rm m} = 1/g_{\rm mn} + 1/g_{\rm mp}$$

(5.1)

Bandwidth for a given power is compromised due to this relationship.

Fig. 1.15

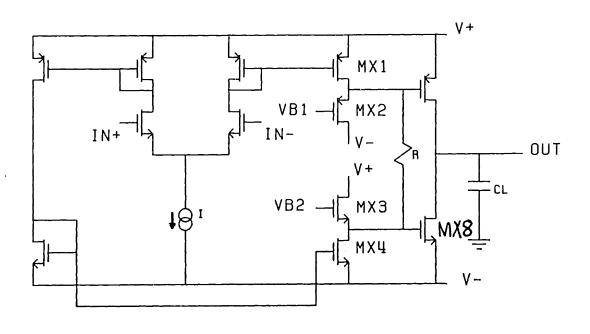

Wong and Salama[20] have modified a conventional OTA so that large gate to source voltages become available to the output transistors when the input stage is saturated. The conventional OTA is shown in figure 1.16. It is possible to look at this stage as a single transconductance stage or as a low gain wide bandwidth differential input stage followed by a high gain low bandwidth output stage. CL creates the dominant pole and if large enough stabilizes the amplifier. Wong and Solama have inserted a low gain wide bandwidth intermediate stage as shown in figure 1.17.

Fig.1.16

A gain of 3 is taken at the intermediate stage by the relative sizes of MX1 and MX2. Note that one extra inversion has taken place and the input is relabeled accordingly. Under slewing conditions with negative input MX1 is on with all available bias current while MX4 is off. The gate of MX8 is pulled up through R and large output currents flow. Under linear conditions little current flows through R and it does not determine the output biases. The major concern here is the proper selection of bias voltages to control the output quiescent current. The bias circuit of Wong and Salama is supply and process dependent and could show quite a large variability for small supply voltages and large device thresholds.

Fig. 1.17

Callewaert and Sansen[21] have developed another class AB circuit which increases input pair tail current as imbalance develops due to input signal. The circuit is shown in figure 1.18. The differential pair output current is routed through a cascode transistor to a current mirror which augments the tail current of the pair itself. In this case the input current becomes a quadratic function of input voltage. The input current is mirrored to the load. A complementary stage is required, but not shown, to drive a p channel output transistor and provide push pull action. As with the current subtractor approach details of current mirror matching is important for good performance. Bias current control is determined by the current sources and is relatively simple.

Fig. 1.18

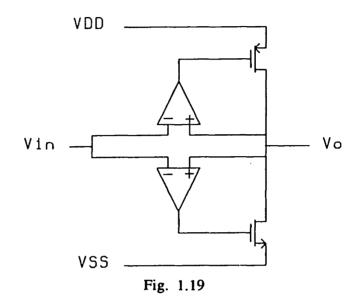

#### 1.5.3 Quasi-Complementary Approaches

Several designs have been of the quasi-complementary type as shown in figure 1.19[22,23] These designs have tended to be quite elaborate due to problems associated with properly controlling the quiescent current and insuring stable operation with large capacitive loads. These designs are more suited to delivering a lot of power to a load than they are for low power operation,

### 1.6 Design Approach for AIRS buffer

A source follower is the most common type of output buffer for IR hybrid focal plane arrays. It provides design simplicity and performance characteristics which make it a suitable choice for a wide class of output requirements. In this case it is not appropriate. The requirements on power dissipation, capacitive load, and slew rate are incompatible with the characteristics of a source follower. In Class A circuits, such as a source follower, the output current is limited by the bias current, and the slew rate is given by the ratio of the bias current to the load capacitance. Power dissipation limits the total bias current to 40 µa. The requirement for a balenced differential output implies that at most 1/2 of the

available bias current will be available for each output. The maximum slew rate for a Class A output is therefore.

$$SR = I / CL = 20 \mu a / 100 pf = .2 V/\mu s$$

(1.10)

This slew rate is to low to meet the settling time requirement by about an order of magnitude. A Class AB output is therefore called for.

If one assumes that the slewing problem has been solved then the bandwidth problem must be addressed. In order to settle to a given degree of precision in a given time there is a minimum bandwidth which will be required. In this case settling to .03% will requires roughly 9 time constants. This time constant can be no larger than  $CL/G_m$ , where  $G_m$  is the transconductance of the amplifier in the buffer or a stage of it. The maximum value of  $G_m$  which can be obtained in a single transistor is given as its weak inversion value.

$$Gm = I/(n \cdot Vth) \tag{1.11}$$

=

$$20 \mu a / (2 \cdot .0067) = 1490 \mu S$$

This gives a time constant of 67 ns if this transconductance is driving 100 pf. Nine such time constants is .6 µs. This implies that it is possible to achieve the degree of settling with the present power budget.

Because of the ability to achieve a well defined output impedance an adaptively biased design was chosen. The design of Costello was attempted first but the obtainable transconductance was too low, primarily due to the source coupled n and p input transistors. The designs of Degrauwe and Callewaert promise higher obtainable transconductances with well controlled bias currents in the output

stage. The topology of Callewaert was selected, although similar results could probably be obtained with that of Degrauwe.

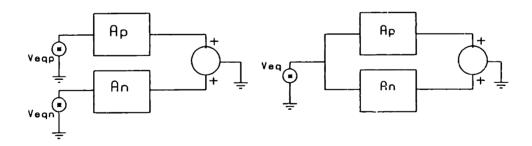

The AIRS output buffer calls for a differential output. In this instance it is proposed to use two output circuits. The first circuit provides a signal output as depicted in figure 1.8. The second circuit contains a duplicate buffer but the input voltage is constant so the output voltage is constant. Another approach would be to employ a fully differential OTA and provide a truly differential output. In this case differential inputs are not available to the output buffer, so a fully differential output would require changes to the focal plane architecture. It is proposed here to meet the requirements without requiring such changes.

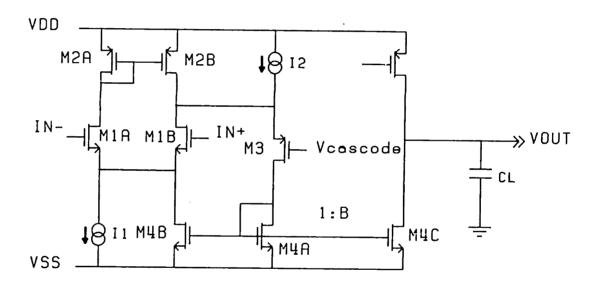

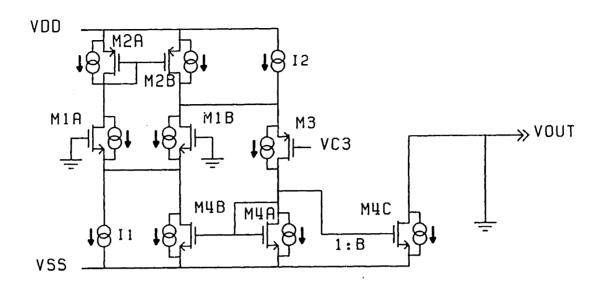

## 2. Theory of Operation, OTA

## 2.1 General Principle of Operation

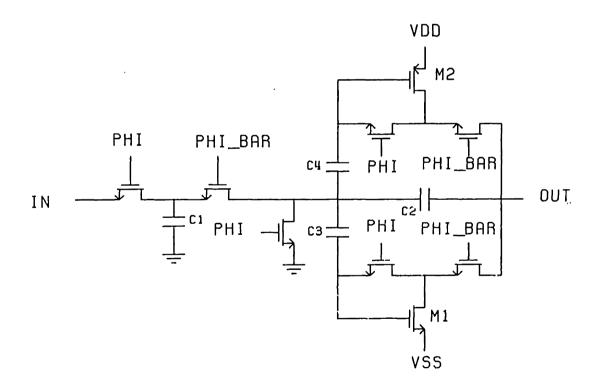

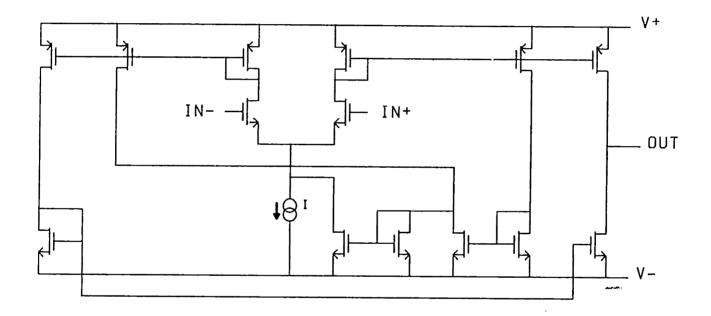

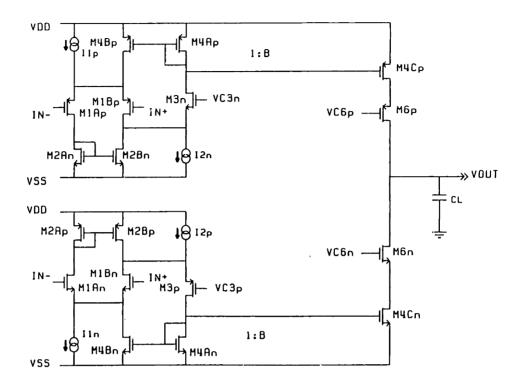

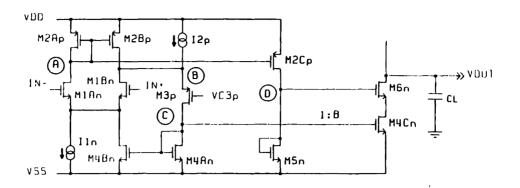

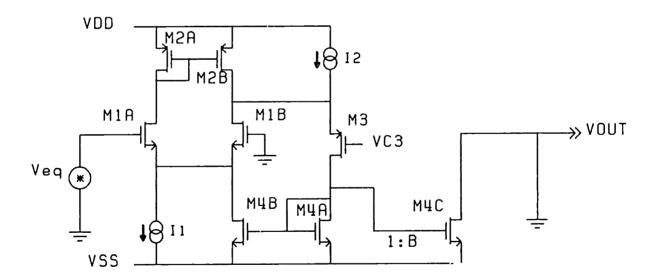

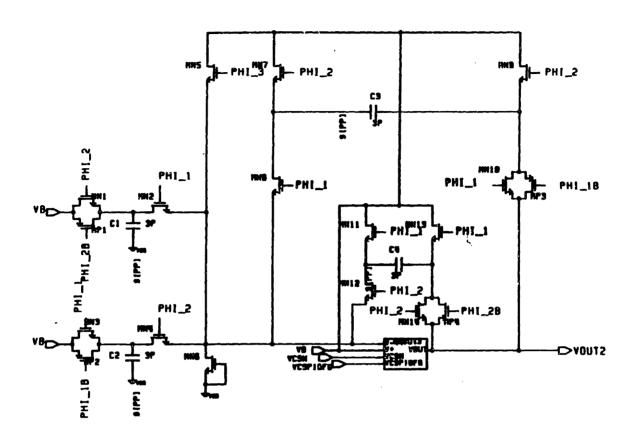

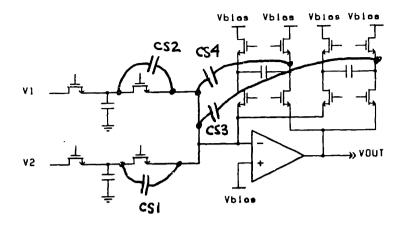

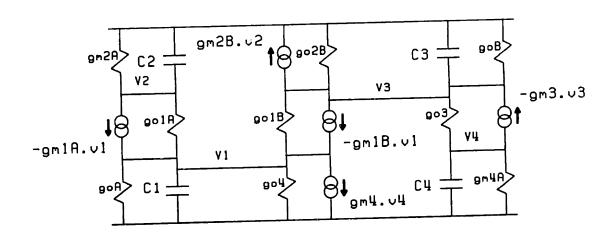

The Class AB Operational Transconductance Amplifier (OTA) used here is that proposed by Callewaert and Sansen[21]. A review of it operation is given here, including some aspects not elaborated in [21]. The basic circuit of the amplifier is shown in figure 2.1.

Fig. 2.1 OTA basic circuit

The input is differential and is applied to the gates of the source coupled pair M1A and M1B in the usual manner. A current source on the source node provides the quiescent bias current for the input stage. A current mirror load (M2A,M2B) directs the difference current from the input pair through a cascode transistor (M3). This current is then mirrored to two places. The first is via M4A

and M4B, and creates additional tail current for the input pair. The transistor M4B alters the bias current in the input stage and gives the amplifier its class AB operation. The second is via M4A and M4C, and provides current for the output load. A step up ratio of 1:B is conveniently taken at the M4A,M4C mirror to provide adequate drive for the load.

The input to the p channel drive transistor in the output stage is not shown in figure 2.1. It is driven by a parallel complementary input stage to provide symmetrical push pull drive capability. The differential input signal goes to two input stages. One input stage drives the n channel driver of the output stage, while the other input stage drives the p channel driver of the output stage.

A simple calculation, presented in [21], helps to explain the operation of the circuit. Suppose that the transistor M1A is conducting a dc current I1A. This current is mirrored with a ratio R2 to the source node of the cascode transistor M3. Applying Kirchoff's current law (KCL) to this node yields the equation

$$I3 = Ibias \cdot Rbias + I1A \cdot R2 - I1B . \tag{2.1}$$

Rbias and R2 are nominally equal to one but are included here for generality. The current I3 is mirrored back to the common source point of M1A and M1B with a ratio of R4. Using KCL at this node yields

$$I1A + I1B = Ibias + I3 \cdot R4$$

. (2.2)

Equations (2.1) and (2.2) can be used to solve for I1B and I3 in terms of Ibias and I1A.

IIB = Ibias •

$$(R4 \cdot Rbias + 1)/(R4 + 1) + IIA \cdot (R2 \cdot R4 - 1)/(R4 + 1)$$

(2.3)

The equation in [1] which corresponds to (2.3) disagrees due to a printing error. If all of the current ratios are replaced by their nominal values of one, these equations are drastically simplified.

$$I1B = Ibias (2.5)$$

$$I3 = I1A \tag{2.6}$$

These equations show that the local feedback loop acts in a way to maintain the current in M1B constant and equal to Ibias. The current through M4B increases or decreases as needed to maintain the current through M1B. If it is assumed that V+ is fixed, then it also follows that the source node of M1 is fixed. This follows because fixed current through M1B, and a fixed gate voltage on M1B, imply a fixed V<sub>gs</sub> for M1B. V+ will be a fixed bias voltage in the output buffer application considered here. Therefore the action of the local feedback loop can also be described as maintaining the source voltage of M1 equal to its quiescent bias value despite variations in the input signal V-. Assuming that M1A is in saturation and strong inversion, its drain current is given by the equation

IIA =

$$1/2 \cdot K \cdot W/L \cdot (V_g - V_s - V_{tn})2$$

$$= 1/2 \cdot K \cdot W/L \cdot (\Delta V - V_d) 2. \qquad (2.7)$$

$V_d$  is the differential input voltage (  $V_{+}$  -  $V_{-}$  ) and  $\Delta V$  is the quiescent value of the voltage above threshold (  $V_{gs}$  -  $V_{tn}$  ) for transistor M1.

Equation (2.7) shows that for large negative differential input voltages I1A increases quadratically. According to (2.6) I3 is equal to I1A. The current I3 is mirrored to the output via M4A and M4C so that for large negative differential input voltages large currents can be sunk from the load. For large positive differential input voltages the transistor M1A turns off and equation (2.7) is not valid. For large positive differential input voltages the operating current in the input stage which drives the P channel driver increases quadratically. This conditions sources large current to the load.

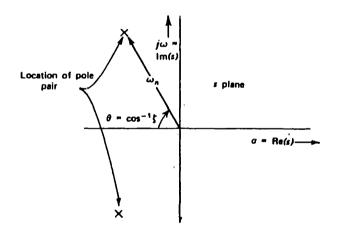

This amplifier has a single high impedance node at the output. The dominant pole in the frequency response is determined by the load capacitance. If large enough, the load capacitance will stabilize the amplifier, and produce a single pole response. In this case, the amplifier is well modeled as a single transconductance stage. It is also possible to look at the amplifier as having two stages. The first is a low gain wide bandwidth differential input stage. The second is a high gain low bandwidth output stage. The two stage description is more accurate because it models the internal poles of the amplifier. If the design is pushed to produce maximum bandwidth, these internal poles must necessarily come into play as limiting factors.

The inverting output stage has extremely good output range. Let  $\Delta V$  be the voltage above threshold  $(V_{gs}-V_{tn})$  of the n-channel drive transistors. The output voltage can approach within  $\Delta V$  of the lower rail before pushing the drive transistor into the triode region of operation. Similar considerations apply to the p-channel drive transistor. Without cascode transistors the output range goes virtually rail to rail.

To achieve highly linear operation, high dc gain is desirable. It is relatively straight forward to put cascodes on the output stage to increase the dc gain. Cascode transistors will decrease the output range of the amplifier, but if biased properly, this reduction can kept to a few tenths of volts off each end of the output range. The characteristics of this amplifier make it well suited for low power operation in applications where high linearity and large output swing are desired, and large load capacitance is encountered.

### 2.2 Minor Loop Stability

The stability of the local feedback loop is treated in Appendix 1. A new technique is used which does not require opening the loop. The new technique is suited for machine computation but is included in Appendix 1 for illustrative purposes.

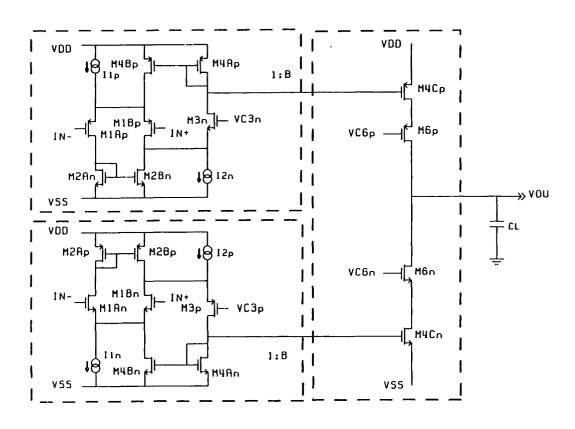

# 2.3 Small signal frequency response

A schematic of the amplifier with a cascoded output stage is shown in figure 2.2. There are two parallel signal paths in the amplifier. One path goes through the n channel driver of the output stage, while the other goes through the p channel driver of the output stage. The step up ratio at the current mirror M4A, M4C is denoted as B. It is assumed that the step up ratios for the n and p channel circuits are the same. All the results presented here could easily be modified to take into account different step up ratios if necessary.

The transconductance of the amplifier has contributions from each input stage stepped up by a factor of B. If only the n channel input stage is considered, and the output stage p channel driver were considered to have a constant bias, the amplifier transconductance would be

$$G_{m}(n) = B \cdot g_{m}(1An) . \qquad (2.8)$$

Fig. 2.2 OTA with cascoded output stage

Because the local feedback keeps the source at a fixed voltage there is no correction to account for the bulk to source transconductance. In a conventional source coupled connection, the transconductance is higher if the transistors are in there own well because of this effect. For this circuit there is no such distinction. If only the p channel input stage is considered, and the output stage n channel were considered to have a constant bias, the amplifier transconductance would be

$$G_{\mathbf{m}}(\mathbf{p}) = \mathbf{B} \cdot \mathbf{g}_{\mathbf{m}}(1\mathbf{A}\mathbf{p}) . \tag{2.9}$$

The amplifier transconductance is a small signal linear property so that these two contributions may be added together to obtain the total amplifier transconductance.

$$G_m = B \cdot (g_m(1An) + g_m(1Ap))$$

(2.10)

The amplifier output conductance is the sum of output conductances from the pull up and pull down portions of the output stage. For the case without a cascoded output stage the total output conductance is given by the sum of the device output conductance of the driver transistors.

$$G_0$$

(no cascodes) =  $g_0(4Cn) + g_0(4Cp)$  (2.11)

The configuration with the cascoded output stage is of primary interest here because it is adopted in this design to yield high dc gain. The cascode configuration yields an output conductance with is smaller than the device output conductance by a factor equal to the intrinsic gain  $g_m/g_0$  of the cascode transistor[24]. This is valid as long as the intrinsic gain of the cascode transistor is much greater than one, as it is in this case.

$$G_0 = g_0(4Cn) \cdot \frac{g_0(6n)}{g_m(6n)} + g_0(4Cp) \cdot \frac{g_0(6p)}{g_m(6p)}$$

(2.12)

The dc gain of the amplifier is given by the ratio of the amplifier transconductance to the amplifier output conductance.

$$A = G_m/G_o$$

$$= B \cdot \frac{g_{m}(1An) + g_{m}(1Ap)}{g_{o}(4Cn) \cdot g_{o}(6n)/g_{m}(6n) + g_{o}(4Cp) \cdot g_{o}(6p)/g_{m}(6p)}$$

(2.13)

This expression could also be expressed as the sum of the gain from each of the two parallel gain paths.

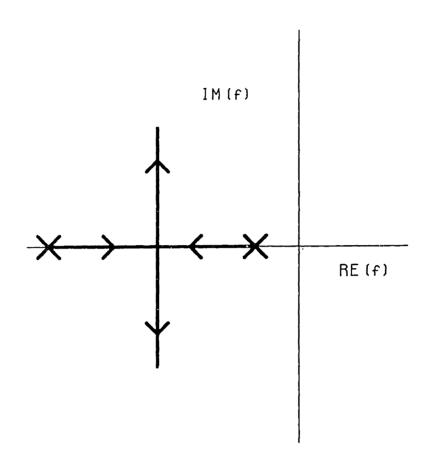

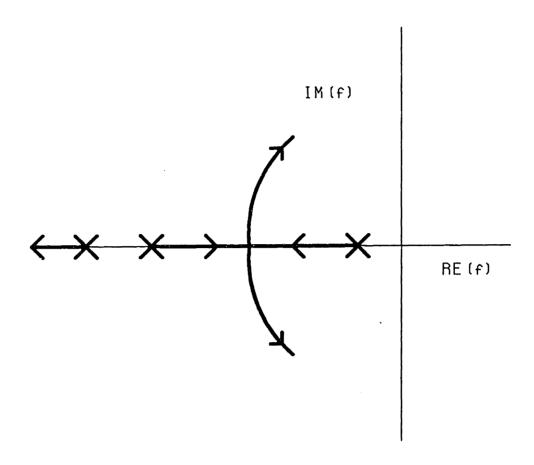

This OTA has a single high impedance node at the output. This is true for both the cascoded and noncascoded configuration. The load capacitance, which is estimated at 100 pf, and is much greater than any internal capacitance, also appears on the output node. The amplifier frequency response has a single dominant pole determined by the ratio of the output conductance to the load capacitance.

$$p1 = \frac{g_0(4Cn) \cdot g_0(6n)/g_m(6n) + g_0(4Cp) \cdot g_0(6p)/g_m(6p)}{C_I}$$

(2.14)

This result can be arrived at from a zero-value time constant analysis, where the time constant from the output node dominates the sum. It can also be arrived at in another way which is discussed now.

When two portions of a circuit have a high degree of isolation from each other, the poles from each portion of the circuit can be calculated independently. This can be argued physically by considering an experiment where one portion of the circuit is placed in an initial state. Its state variables then decay according to the natural frequencies of that portion of the circuit. The isolated portion of the circuit has no influence on these decay frequencies. For two circuits which are completely isolated this argument is rather obvious. The argument yields useful results in a case where unilateral information flow exists between the two

subcircuits. This is to say that, dependant sources can exist in one subcircuit which are driven by variables from the other, but not vice versa, In this case the above argument concerning decay frequencies is still valid. If either of the two subcircuits is placed in an initially excited state, while the other is unexcited, it will decay in a manner independent of the other subcircuit. The same result can be argued mathematically, although somewhat more abstractly, by showing that the determinant of the nodal matrix can be factored into two separate expressions.

Fig. 2.3 Three isolated subcircuits

Figure 2.3 shows how the amplifier under consideration can be considered to be three isolated subcircuits. This isolation was implicitly assumed in figure A.1 where the output stage was considered immaterial to the local feedback loop in the

from the output stage can calculated directly without further approximation. Equation 2.14 results where once again the intrinsic gain of the cascode transistors are assumed greater than one.

An advantage to looking at the circuit as three separate subcircuits is that zero-value time constant analysis may now be performed on the other two subcircuits to determine the position of the nondominant poles [25]. The impedance looking into each of the four nodes in the input stage is straight forward to calculate. The impedance of node 2 is affected by the local feedback loop, while the other three are not.

$$R_1 = 1/(2 \cdot g_{m1})$$

(2.15)

$$R_2 = 3/(2 \cdot g_{m2})$$

(2.16)

$$R_3 = 1 / g_{m3} \tag{2.17}$$

$$R_4 = 1 / g_{m4} \tag{2.18}$$

The zero-value time constant analysis predicts a dominant pole location for the input stage subcircuit as

$$p_2 = 1 / \tau_2$$

$$\tau_2 = \frac{C_1}{2 \cdot g_{m1}} + \frac{C_2}{(2/3) \cdot g_{m2}} + \frac{C_3}{g_{m3}} + \frac{C_4}{g_{m4}}. \quad (2.19)$$

Each of the input stage subcircuits will contribute its own set of poles and zeros. The frequency response of the entire amplifier will be the sum of the individual frequency responses of the two parallel signal paths. Each signal path shares the output stage so the dynamics of the output stage is common to both.

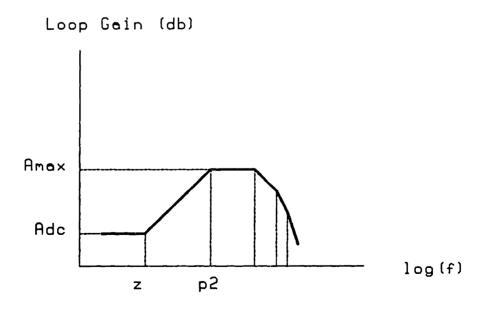

If each input stage subcircuit were modeled as having a single pole the open loop frequency response of the amplifier would be given as

$$a(S) = \frac{1}{S - p_1} \left[ \frac{A_n}{S - p_n} + \frac{A_p}{S - p_p} \right]. \quad (2.20)$$

$A_n$  and  $A_p$  are the dc gains for each of the two parallel signal paths. The pole locations of the n channel and p channel input stages are denoted by  $p_n$  and  $p_p$ . The dominant pole from the output stage is given as  $p_1$ . The dc gain of the amplifier is the sum of  $A_n$  and  $A_p$ , and has been given in equation (2.13). Equation (2.20) can be rearranged into a more useful form.

$$a(S) = \frac{A_n + A_p}{S - p_1} \cdot \frac{S - z}{(S - p_n)(S - p_p)}$$

(2.21)

$$z = \frac{A_n \cdot p_p + A_p \cdot p_n}{A_n + A_p}$$

(2.22)

A pole occurs at each of the subcircuit pole locations and a zero appears at a location between the two poles. If the two poles were at approximately the same location, then combination of two poles and one zero would behave approximately as a single pole at that location.

The gain bandwidth product of the amplifier is given by the product of the dc gain and the dominant pole location.

$$GBW = A \cdot p_1 = G_m / C_L$$

$$= B \cdot \frac{g_{m}(1An) + g_{m}(1Ap)}{C_{L}}$$

(2.23)

The input impedance of this amplifier differs somewhat from that of a conventional source coupled pair with current source bias. In a conventional source coupled pair, in the linear region of operation, the source node does not stay at a fixed voltage. As one input goes up in voltage, so does the source. The increase in current through one transistor is offset by a corresponding decrease in the current through the other, so that the sum is constant. To achieve this, the source node moves by 1/2 of the applied differential input voltage. As a result, the differential input capacitance is equal to 1/2 of the Cgs of an input transistor. In this amplifier the local feedback keeps the source voltage constant. The entire differential input voltage falls across one transistors gate and source nodes. The resulting differential input capacitance is given by

$$C_{in} = C_{gs}(1n) + C_{gs}(1p)$$

(2.24)

Higher input capacitance is one penalty that is incurred by the Class AB operation.

### 2.3 Dynamic cascode biasing

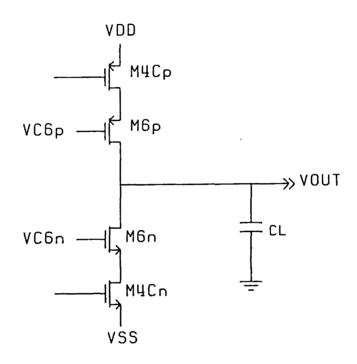

Cascode transistors provide a very useful technique in achieving high dc gains. One detail of proper cascode design is the generation of the bias voltage. Figure 2.2 did not show the circuitry needed to generate the cascode bias voltage for both the input stage cascode and the output stage cascode transistors. Figure 2.4 shows the output stage with cascode transistors included.

Fig. 2.4 Output stage with cascode transistors

The value of the bias voltage for the n channel cascode transistor, Vbiasn, is important. If it is too small, the drive transistor, M4cn, will be in the triode region and the voltage gain of the output stage will be too low. If it is too large, then it will limit the output range of the output stage. It is generally desirable to have the cascode bias only just large enough to guarantee that the drive transistor will be in the saturation region. Transient conditions may cause the operating current to increase over its quiescent value. The drain voltage on the drive transistor decreases as the output stage operating current increases. This is

because the Vgs voltage drop of the cascode transistor increases. The largest operating value of the output stage current must be used in determining the required bias voltage. Class A amplifier designs have generally used a constant voltage for the cascode bias with due regard to the above considerations.

Class AB operation causes a complication in the biasing of cascode transistors. It has been shown in section 2.1.1 that the amplifier operating current can become much greater than its quiescent value. The drive transistor M4C will fail to operate as a current mirror with M4A if it enters the triode region of operation. Output stage operating current will be limited to the value of current which causes this condition to take place. If the cascode biasing criteria discussed above is applied to the largest obtainable operating current, then the required cascode bias voltage may become so large that output range is severely reduced. To reduce the Vgs drop of the cascode transistors under maximum current conditions may require a prohibitively large cascode device. Dynamic cascode biasing was developed to address this problem [19].

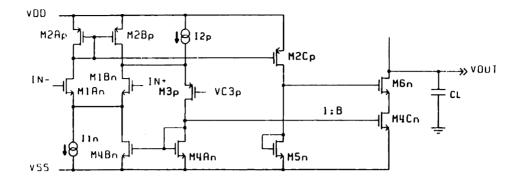

In a dynamically biased cascode, the bias voltage is generated from the amplifier operating current. The bias voltage for the n channel cascode is generated so that it will increase as the amplifier operating current increases. Maximum output range is obtained under quiescent conditions, which is when it is needed. Maximum operating current is obtained under transient conditions, which is when it is needed. Figure 2.5 shows how easily dynamic biasing can be incorporated into this amplifier design. Transistor M5n is sized to produce maximum output range under quiescent conditions. As operating current increases in the n channel input stage, the increase in the bias voltage for M6n is more than adequate to compensate for increases in the M6n Vgs drop. A complementary circuit can be used to provide bias for the p channel output stage cascode transistor.

Fig. 2.5 Dynamic output stage cascode biasing

#### 2.4 Large Signal Performance

Although the operating current increases quadratically for large differential input signals, there are at least two mechanisms which limit how large this current can become. The first is caused by limited supply voltage and has been discussed in reference 1. The second is caused by device mismatch and is introduced here for the first time.

As the differential input voltage increases, the operating current increases first linearly and then quadratically. As the operating current increases, the gate to source voltage of all the transistors in the signal path increases. Eventually one of the transistors will enter the triode region. The drain of M1A and M2A is a node where this condition can happen. The source of M3 and the drain of M2B is another. The onset of a transistor entering the linear region may place a limit on the operating current. The maximum obtainable operating current establishes the maximum output current. For a given load capacitance, this determines the slew rate. For acceptable settling time, the slew rate must be adequate. Transistors must be sized so that the maximum current increase is acceptable.

Fig. 2.6 Nodes sensitive to operating current increases

Figure 2.6 shows four nodes at which operating current increases could cause a transistor to enter the triode region of operation. The transistor which enters the triode region at the lowest current will limit the output current of the amplifier. At large operating currents the transistors in question are in strong inversion, so their currents should be accurately represented by the square law relation.

$$I_d = 1/2 \cdot K \cdot W/L \cdot (V_{gs} - V_t)2$$

for  $V_{ds} > V_{gs} - V_t$  (2.25)

It is assumed, in equation (2.25), that the currents are not so large that mobility degradation effects are significant.

At the node labeled A, operating current increases cause the drain voltage of M1A to decrease, and the gate voltage of M1A to increase. When the gate to drain voltage exceeds the threshold, M1A will enter the triode region of operation. A further increase in V- will only produce a small increase in the operating current. Using equation (2.25), the operating current at which this condition will occur is given as

$$I(An) = (1/2) \cdot K_n \cdot (W/L)_1 \cdot \left[ \frac{\Delta VM1B + (V_{DD} - V_+) + (V_{tn} - |V_{tp}|)}{(1 + g_{m1}A/g_{m2})} \right]^2. (2.26)$$

Vtn in (2.26) is the threshold of M1A, which may be increased by the back gate effect depending on its substrate connection. If the back gate effect is present the maximum current will be even larger than (2.26). The gm ratio in the denominator is the ratio when both M1A and M2 are in strong inversion. M1B need not be in strong inversion when this condition arises because it continues to conduct the bias current even while M1A may be conducting the maximum current. If it is assumed to be in strong inversion so that (2.25) is valid, then equation (2.26) may be expressed in a somewhat different form.

$$\frac{I(An)}{I_{BIAS}} = \frac{1}{(1 + g_{m1A}/g_{m2})^2} \cdot \left[ 1 + \frac{(V_{DD} - V_{+}) + (V_{tn} - |V_{tp}|)}{\Delta V_{M1B}} \right]^2 . (2.27)$$

Equation (2.26) should be more accurate, as it does not make this assumption. A simplified version of (2.27) is given in [21] where  $V_{tn}$  has been assumed equal to  $|V_{tp}|$  and  $g_{m \, 1\, A}$  has been assumed equal to  $g_{m \, 2}$ . I(A) is a potential current limit of the amplifier.

At the node labeled B, operating current increases will increase the drain voltage of M2B, and lower the gate voltage of M2B. When the voltage gate to drain falls below the threshold, transistor M2B will enter the triode region of operation. The current source I2 could conceivably enter the triode region but this is

unlikely because it continues to conduct only the bias current. With the onset of this condition, the operating current will level off. The maximum current is given by

$$I(Bn) = (1/2) \cdot Kp \cdot (W/L)_{2B} \cdot \left[ \frac{V_{DD} - V_{CASCODE} - |V_{tp}|}{1 + g_{m2B}/g_{m3}} \right]^{2} (2.28)$$

$$\frac{I(Bn)}{I_{BIAS}} = \begin{bmatrix} \frac{V_{DD} - V_{CASCODE} - |V_{tp}|}{\Delta V_{M2} \cdot (1 + g_{m2B}/g_{m3})} \end{bmatrix}^{2} . (2.29)$$

As before, the ratio of transconductances in the denominator is the value that applies with both M2 and M3 in strong inversion. Vtp is the threshold voltage of M3, which may be increased due to the back gate effect depending on its substrate connection. The back gate effect, if present, at this node will decrease the limiting current. To be conservative, it should be accounted for even though the magnitude of V<sub>SB</sub> will be small when this current limiting condition arises. Equation (2.29) is valid if M2 is in strong inversion under quiescent conditions. I(B) is a potential current limit for the amplifier.

At the node labeled C, operating current increases will increase the drain voltage of M3. When this voltage is large enough, M3 will enter the triode region of operation. When this happens, M3 will operate as a switch and further increases in current will begin to increase the source voltage of M3. Eventually M2B would enter the triode region of operation with the same effect as described with node B. For any reasonable values of cascode voltage, the current limiting condition at node B will occur first. The current at which M3 enters the triode region is given by

$$I(Cn) = 1/2 \cdot K_n \cdot (W/L)_{4A} \cdot (V_{CASCODE} - V_{SS} + |V_{tp}| - V_{tn})_2$$

(2.30)

$$\frac{I(Cn)}{I_{BIAS}} = \left[ \frac{V_{CASCODE} - V_{SS} + |V_{tp}| - V_{tn}}{\Delta V_{M4}} \right]^{2} . (2.31)$$

V<sub>tp</sub> is the threshold of M3, which may be increased by the back gate effect, depending on its substrate connection. Equation (2.31) is valid only if M4A is in strong inversion under quiescent conditions. I(C) does not, however, represent a current limiting value.

At the node labeled D in figure 2.6, operating current increases will raise the drain voltage of M2C and lower the gate of M2C. When the gate to drain voltage falls below the threshold, M2C will enter the triode region of operation. M2C will fail to mirror the operating current and the bias voltage for M6 will stop increasing. This condition is unlikely to limit the output current of the amplifier. The gate voltage on M6 is already quite large when this condition happens. It may even be large enough so that M6 is operating as a switch rather than a cascode transistor. This has no drawback. M6 is needed to operate in the saturation region only under quiescent conditions. The current at which M2C enters the triode region is given by

$$I(Dn) = (1/2) \cdot K_p \cdot (W/L)_{2C} \cdot \left[ \frac{V_{DD} \cdot V_{SS} \cdot V_{tn}}{1 + g_{m2C}/g_{m5}} \right]^2 (2.32)$$

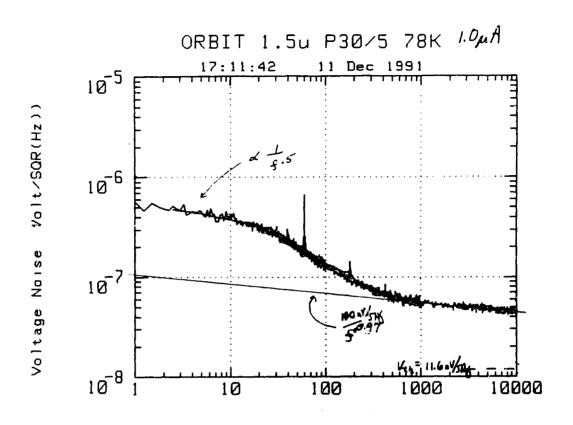

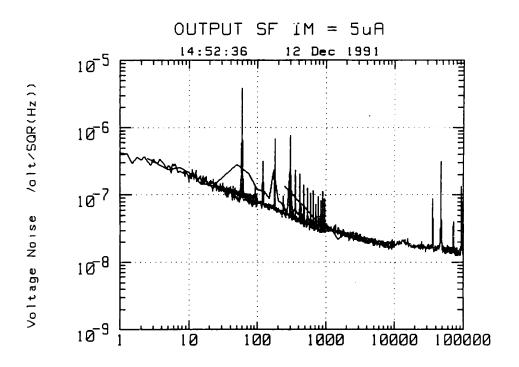

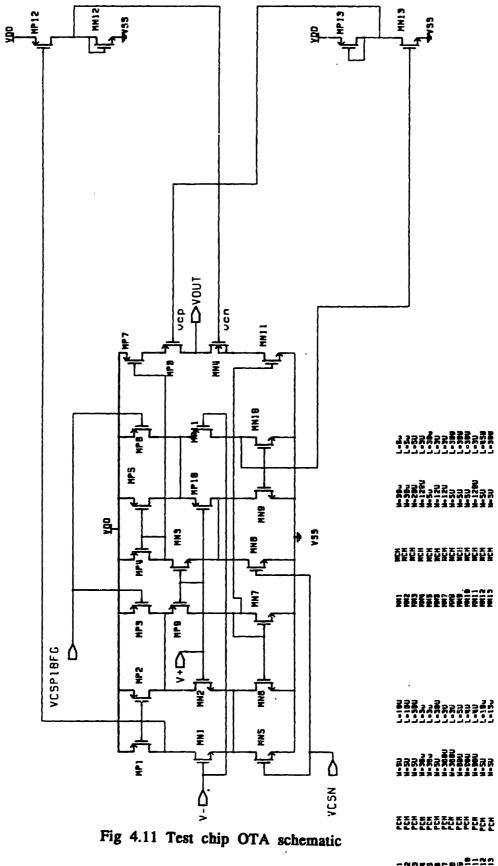

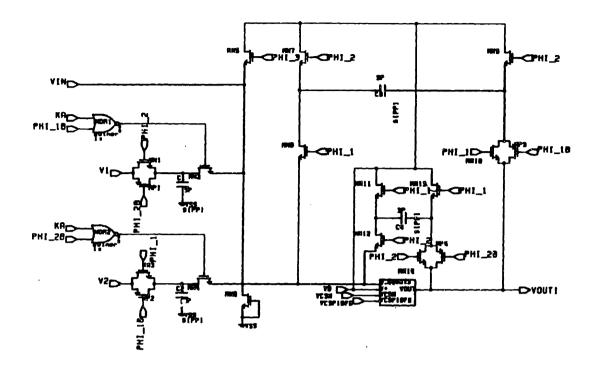

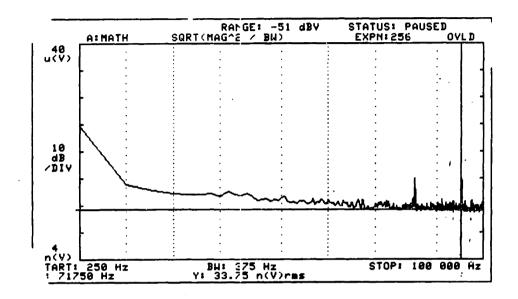

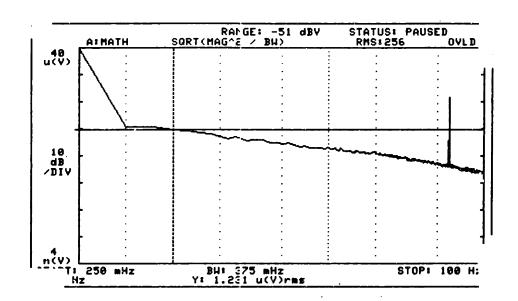

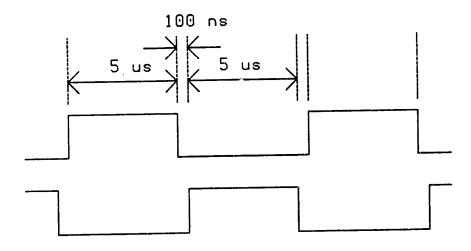

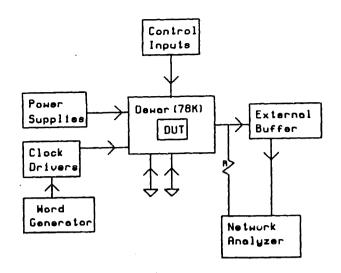

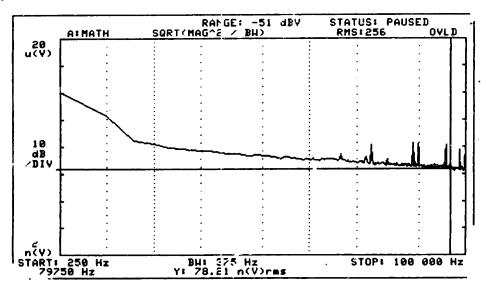

$$\frac{I(Dn)}{I_{BIAS}} = \begin{bmatrix} V_{DD} - V_{SS} - V_{tn} \\ \hline \Delta V_{M2C} \cdot (1 + g_{m2C}/g_{m5}) \end{bmatrix}^{2} . (2.33)$$