### Compilation-based Prefetching for Memory Latency Tolerance

by

Charles William Selvidge M.S., Massachusetts Institute of Technology (1987) B.S., Massachusetts Institute of Technology (1985)

Submitted to the

Department of Electrical Engineering and Computer Science

in Partial Fulfullment

of the Requirements for the Degree of

Doctor of Philosophy

at the

Massachusetts Institute of Technology

May, 1992

©Massachusetts Institute of Technology All rights reserved

| Signature of Author |                                                                          |

|---------------------|--------------------------------------------------------------------------|

| <b></b>             | Department of Electrical Engineering and Computer Science                |

|                     | 18 May 1992                                                              |

| Certified by        |                                                                          |

|                     | Stephen A. Ward Professor of Electrical Engineering and Computer Science |

|                     | Thesis Supervisor                                                        |

| Accepted by         |                                                                          |

|                     | Campbell L. Searle                                                       |

|                     | Chairman, Departmental Committee on Graduate Students                    |

MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

'JUL 1 0 1992

### Compilation-based Prefetching for Memory Latency Tolerance

by

Charles W. Selvidge

#### Abstract

Performance impacts of memory latency can be mitigated with hierarchical memory systems which exploit locality and with concurrent memory systems which exploit parallelism. As the relative performance of processors improves with respect to memory components it will be advantageous to simultaneously exploit locality and parallelism in order to achieve memory latency tolerant computation, computation in which the runtime performance is relatively insensitive to high memory latencies.

Program locality is typically considered at a macroscopic level corresponding to aggregate program behavior. We investigate locality behavior at a finer granularity, considering the behavior of individual memory reference instructions. By grouping together the dynamic memory references produced by each static memory reference instruction in a program, a large amount of structure is exposed in locality behavior. Miss rates of dynamic memory references arising from the same static instruction are highly correlated; thus it is meaningful to ascribe an individual miss rate to each static memory reference in a program. These individual miss rates are highly polarized, often displaying a bimodal distribution consisting of a set of references with very low miss rates and a set with very high miss rates. As a result of this polarized, bimodal distribution, one finds that essentially all program misses occur as a result of executing an instruction from the set of static memory reference instructions exhibiting high miss rates. Low miss rate static instructions account for a large fraction of total memory references, however. This behavior is summarized in the Static Locality Correlation Hypothesis and the Badref Hypothesis. Empirical evidence validates these hypotheses.

Prefetching provides a mechanism for achieving concurrent activity in processors, caches and main memory systems. While this concurrency can produce latency tolerance, it requires program parallelism. Operations cannot be performed concurrently if they are ordered by dataflow dependencies. The insights above regarding program locality behavior can be exploited to leverage limited program parallelism. By restricting the focus of latency tolerance specifically to the subset of high miss rate static memory reference instructions, parallelism is targetted at the source of misses. Furthermore, low miss rate memory references eliminated from consideration become an additional source of parallelism for high miss rate references. The non-semantic nature of transactions between memory and cache serves to further increase parallelism for memory latency tolerance. An empirical measurement technique demonstrates that ample parallelism is displayed in programs to allow tolerance to memory latencies of hundreds of instructions.

These results are put in practice in a prototype compiler which generates memory latency tolerant code. Two distinct scheduling algorithms are developed and implemented in order to schedule cache miss processing activity to occur concurrently with computation and cache hits. One technique applies to structured accesses within loops, predicting future addresses in order to software pipeline cache miss latency with loop computation. The second technique merges prefetches into sequential code. Simulations of code produced by the prototype compiler demonstrate speedups of 10 to 30% over unmodified code for a 20 cycle memory latency and speedups of factors of 2 to 6 over unmodified code for a memory system with 160 cycle latency and bandwidth sufficient to allow 8 concurrent miss transactions.

Thesis Supervisor: Stephen A. Ward

Title: Professor of Electrical Engineering and Computer Science

### Acknowledgements

I thank my wife Maureen for love, understanding, encouragement and much patience. Pursuit of a PhD has emotional ups and downs. The ups are focused at the end while the downs are distributed through the beginning and middle. Maureen helped me make it to the end.

I thank Steve Ward, my advisor, for providing me with a unique research opportunity. He allowed me great flexibility in the exploration of this topic while providing enough subtle direction to make sure I eventually finished. His many insights into the field of computer science as a whole and regarding the interactions of compilation and architecture, in particular, have helped form the basis of my own views.

A discussion with Greg Papadopoulos provided a catalytic moment for my thesis, helping to transform a set of vague ideas to a specific plan of action. This represented both the end of the beginning and the beginning of the end. Anant Agarwal, as a potential consumer of this type of technology, helped keep my work focused and realistic. I am grateful to both Greg and Anant for their participation on my thesis committee.

Andy Ayers has been my main sounding board for ideas and principle comiserant during the last 5 years. He also read a complete draft of the thesis and provided many useful comments. Larry Dennison provided me with constant prodding and encouragement to finish and graciously reviewed the document once I did.

Arthur Altman, my officemate, provided many needed diversionary discussions on work, politics and life.

Anne McCarthy and Sharon Thomas, each in their own way, oiled the wheels of progress in the research group in which I worked during this effort.

Over the years, students and staff have come, gone, and somtimes come again or changed from one to the other. Ken, Milan, John N., Pz, Russ, DG, Kubi, David Kranz and David Chaiken, Beng, Don, Mike, Peter, Steve and Rich all currently make the 6th floor of Tech Square a more interesting and enjoyable place. Joe and Joe, Cailein, Steve and Andy C. did the same during their stays.

Friends from BBN including Phil Carvey, Greg Bromley, Jerry Pianin and John Goodhue have encouraged me through the years.

Finally, I thank my parents for believing that I could finish and my brother and sister for graduating at the same time, thereby forcing me to do so as well.

## Table of Contents

| 1 | Intro | duction    | 1                                                                     | 10 |

|---|-------|------------|-----------------------------------------------------------------------|----|

|   | 1.1   | Preview of | f Technical Contributions and Results                                 | 10 |

|   |       | 1.1.1      | Static Locality Behavior                                              | 10 |

|   |       | 1.1.2      | Parallelism Behavior                                                  | 12 |

|   |       | 1.1.3      | Compiler Latency Tolerance Algorithms                                 | 14 |

|   |       | 1.1.4      | Performance Evaluation                                                | 14 |

|   | 1.2   | Thesis Ro  | admap                                                                 | 15 |

| _ | N /   |            | and Dadenson d                                                        | 16 |

| 2 |       | vation     | and Background                                                        |    |

|   | 2.1   |            | ory Latency Problem                                                   | 16 |

|   |       | 2.1.1      | Processors                                                            | 19 |

|   |       | 2.1.2      | Memory                                                                | 19 |

|   |       | 2.1.3      | Demand-Fetched Caching                                                | 19 |

|   |       | 2.1.4      | Interleaved Memory Pipelines                                          | 20 |

|   |       | 2.1.5      | Memory Interface Issues                                               | 21 |

|   |       | 2.1.6      | Memory Latency                                                        | 22 |

|   | 2.2   |            | Latency Tolerance Mechanisms                                          | 22 |

|   |       | 2.2.1      | Multilevel Caches                                                     | 22 |

|   |       | 2.2.2      | Cache Prefetching                                                     | 23 |

|   |       | 2.2.3      | Dynamic Scheduling                                                    | 24 |

|   | 2.3   |            | Memory Latency Tolerance                                              | 25 |

|   |       | 2.3.1      | Latency Tolerance Strategy                                            | 25 |

|   |       | 2.3.2      | Experimental Approach                                                 | 26 |

|   | 2.4   |            | Work                                                                  | 27 |

|   |       | 2.4.1      | Cache Behavioral Simulation and Modelling                             | 27 |

|   |       | 2.4.2      | Parallelism Measurement Techniques                                    | 27 |

|   |       | 2.4.3      | Compilation Techniques for Enhancing Locality                         | 28 |

|   |       | 2.4.4      | Compilation Techniques for Memory Latency Tolerance                   | 28 |

|   |       | 2.4.5      | Inline Profiling and Profile-based Compiler Optimization              | 29 |

|   |       | 2.4.6      | Code Scheduling for Hardware Concurrency                              | 30 |

|   |       | 2.4.7      | Speculative Computation                                               | 30 |

|   |       | 2.4.8      | Analysis of Software Prefetching Behavior                             | 31 |

|   | 2.5   |            | Support for Software Latency Tolerance                                | 31 |

|   |       | 2.5.1      | Memory System Support for Software Latency Tolerance                  | 31 |

|   |       | 2.5.2      | Instruction Set Access to Latency Tolerance Mechanisms                | 32 |

|   |       | 2.5.3      | Processor Memory Interface Issues                                     | 33 |

|   |       | 2.5.4      | High-Bandwidth Memory Systems                                         | 34 |

|   |       | 2.5.5      | Target Hardware Model                                                 | 35 |

| 3 | Stati | ام ا       | lity Correlation and the Badref Model                                 | 36 |

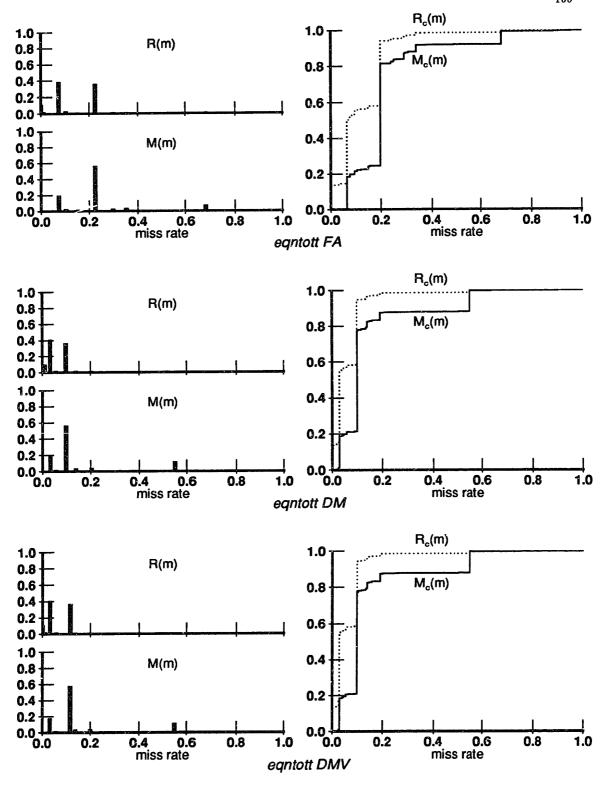

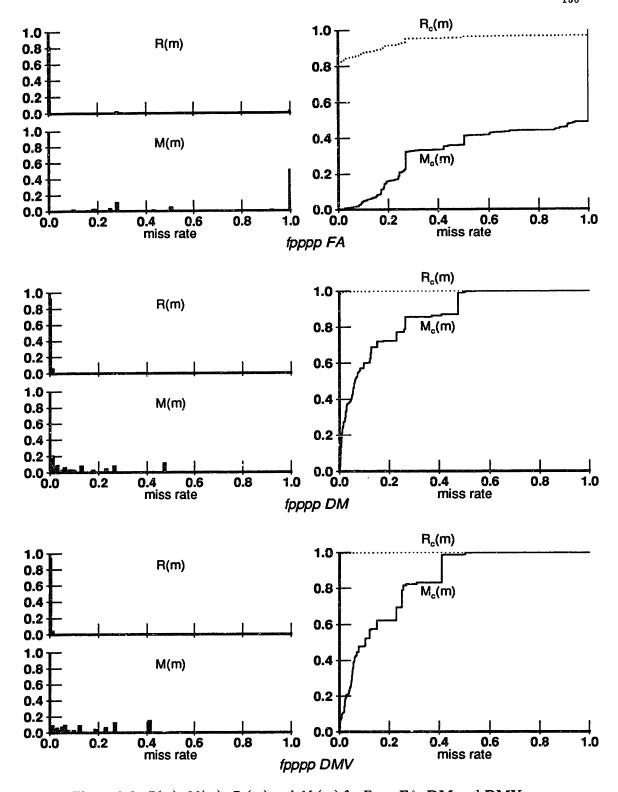

| 9 | 3.1   |            | Statistics of Individual Instruction                                  | 37 |

|   | 3.1   |            | on of Static Locality Correlation                                     | 39 |

|   | 3.3   | Program S  |                                                                       | 41 |

|   | 3.4   | •          | eer's Description of Static Locality Correlation and the Badref Model | 42 |

|   |       |            | - · · · · · · · · · · · · · · · · · · ·                               |    |

|   | 3.5   |            | of the Static Locality and Badref Hypotheses                          | 44 |

|   |       | 3.5.1      | Miss Rate Variability of Individual Static References                 | 44 |

|   |       | 3.5.2      | Cache Design Perturbations                                            | 50 |

|   |       | 3.5.2.1    | Impact of Cache Size                                                  | 50 |

|   |       | 3.5.2.2    | Impact of Block Size                                                  | 55 |

|   |       | 3.5.2.3    | Effects of Associativity and Conflict Misses                          | 60 |

|   | 0.0  | 3.5.3                | Perturbations From Data Set Variation                      | 65<br>65 |

|---|------|----------------------|------------------------------------------------------------|----------|

|   | 3.6  | Summary              |                                                            | 00       |

| 4 | Para | llelism              | For Memory Latency Tolerance                               | 67       |

| • | 4.1  |                      | of Parallelism and Latency Tolerance                       | 67       |

|   | 1.1  | 4.1.1                | Constraints on Parallelism                                 | 68       |

|   |      | 4.1.2                | Dependence Constraints, Cache Misses and Speculation       | 70       |

|   | 4.2  |                      | ntal Technique                                             | 71       |

|   | 4.3  | Results of           | Parallelism Measurements                                   | 73       |

|   | 1.0  | 4.3.1                | Parallelism                                                | 73       |

|   |      | 4.3.2                | Forward versus Reverse Parallelism                         | 77       |

|   |      | 4.3.3                | Badref Measurements                                        | 81       |

|   | 4.4  |                      |                                                            | 85       |

|   |      | -                    |                                                            |          |

| 5 | Com  | piler Al             | gorithms, Models and Heuristics                            | 87       |

| • | 5.1  | Memory F             | Reference Behavioral Modelling                             | 87       |

|   | 0.1  | 5.1.1                | Badref Identification Techniques                           | 88       |

|   |      | 5.1.1.1              | Analysis: The Path Not Taken                               |          |

|   |      | 5.1.1.2              | Miss Rate Measurement in C-flat                            |          |

|   |      | 5.1.2                | Memory System Modelling                                    |          |

|   | 5.2  | <del>-</del>         | Colerance Optimization                                     | 92       |

|   | 5.3  |                      | d Prefetching Heuristics                                   | 93       |

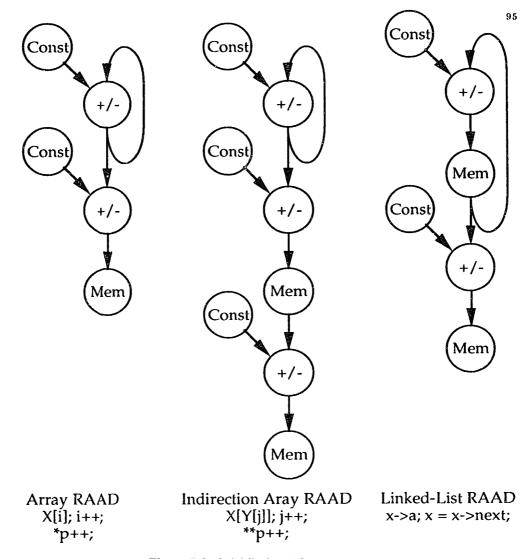

|   | 0.0  | 5.3.1                | RAAD Identification Algorithm                              | 93       |

|   |      | 5.3.2                | Array RAADs                                                | 95       |

|   |      | 5.3.3                | Indirection Array RAADs                                    | 98       |

|   |      | 5.3.4                | Linked-List RAADs                                          | 101      |

|   |      | 5.3.5                | Prefetch Iteration Count Selection                         | 104      |

|   |      | 5.3.6                | Cache-block Based Optimizations                            | 106      |

|   |      | 5.3.7                | Prologue Prefetching                                       | 109      |

|   | 5.4  |                      | efetching in Conditional Loops                             | 110      |

|   | 0.1  | 5.4.1                | Conditional Strategy                                       | 112      |

|   |      | 5.4.2                | Badref and IV Update on a Common Conditional Path          | 112      |

|   |      | 5.4.3                | Conditionally Executed Badref with Unconditional IV Update | 113      |

|   |      | 5.4.4                | Conditionally Updated IV: Single Update                    | 115      |

|   |      | 5.4.5                | Conditionally Updated IV: Multiple Updates                 | 116      |

|   | 5.5  |                      | endence Analysis                                           | 117      |

|   | 5.6  |                      | Miss Scheduling                                            | 118      |

|   | 0.0  | 5.6.1                | Sequential Miss Scheduling Algorithm                       |          |

|   |      | 5.6.1.1              | Address Interactions                                       | 120      |

|   |      | 5.6.1.2              | Miss Latency Interactions                                  | 122      |

|   | 5.7  |                      | RAAD Prefetching or Miss Scheduling for Loops              | 122      |

|   | 0.1  | 5.7.1                | Optimal Loop Scheduling                                    | 124      |

|   | 5.8  | <del>-</del> · · · - |                                                            | 124      |

|   | 0.0  | Summary              |                                                            |          |

| 6 | Com  | piler Re             | esults and Evaluation                                      | 126      |

| - | 6.1  |                      | ization of Badrefs                                         | 126      |

|   | 6.2  |                      | l Code Size                                                | 130      |

|   | 6.3  | -                    | Performance                                                | 131      |

|   |      | 6.3.1                | Processor and Interface Models                             | 131      |

|   |      | 6.3.2                | Memory System Modelling                                    | 132      |

|   |      | 6.3.3                | Time Accounting                                            | 133      |

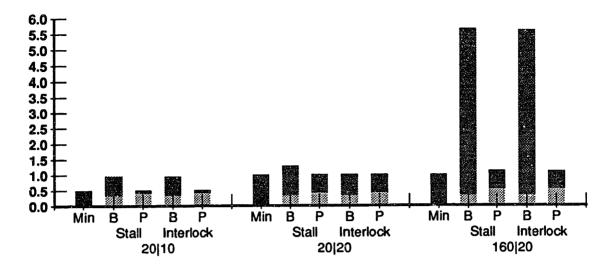

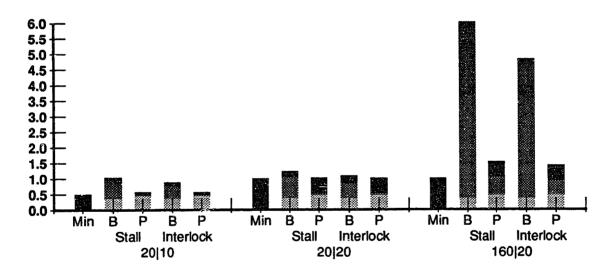

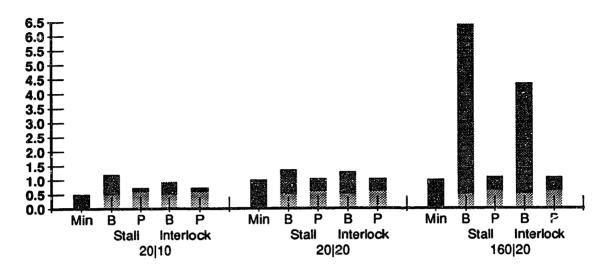

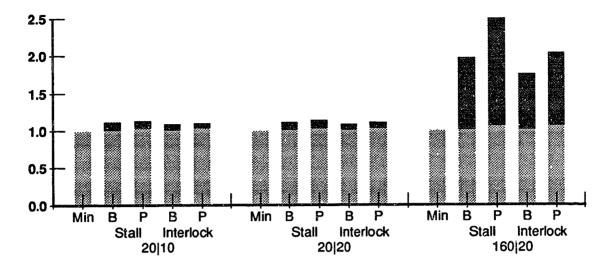

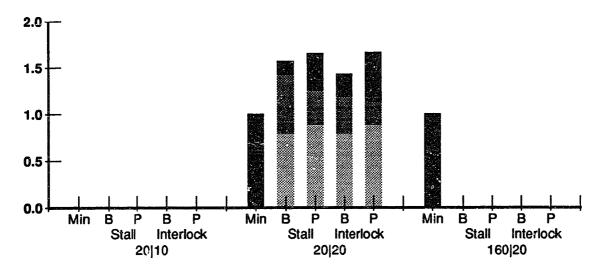

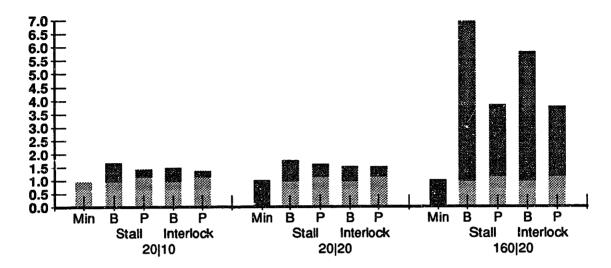

|   |      | 6.3.4                | Performance Results                                        | 133      |

|   |      | 6.3.4.1              | FA Data                                                    | 134      |

|   |      |                      |                                                            |          |

|   |       | 6.3.5 $6.3.5.1$ $6.3.5.2$ | DM Data                                                           | 139<br>141        |

|---|-------|---------------------------|-------------------------------------------------------------------|-------------------|

|   | 6.4   | Summary                   | Memory Behavior Perturbation                                      | $\frac{144}{145}$ |

| 7 | Cond  | clusions                  |                                                                   | 147               |

| • | 7.1   | Summary                   |                                                                   | 147               |

|   | 7.2   | v                         | Behavior                                                          | 148               |

|   | 1.2   | 7.2.1                     | Static Locality Correlation                                       | 148               |

|   |       | 7.2.2                     | Implications of Static Locality Correlation and Badref Behavior . | 149               |

|   |       | 7.2.3                     | Parallelism                                                       | 149               |

|   |       | 7.2.4                     | Parallelism Measurement                                           | 150               |

|   |       | 7.2.5                     | Implications of Forward vs Reverse Parallelism                    | 150               |

|   |       | 7.2.6                     | Badref Distribution                                               | 151               |

|   | 7.3   | Compiler I                |                                                                   | 151               |

|   | 1.0   | 7.3.1                     | Compiler Memory Modelling                                         | 151               |

|   |       | 7.3.2                     | Scheduling Algorithms                                             | 151               |

|   |       | 7.3.3                     | Characterization of Badrefs                                       | 152 $152$         |

|   |       | 7.3.4                     | Variations of Static Locality Correlation                         | 152               |

|   | 7.4   |                           | Performance                                                       | 153               |

|   | 7.5   |                           | ·····                                                             | 153               |

|   | · · - |                           |                                                                   | 100               |

| Α | Addi  | tional S                  | tatic Locality Correlation Data                                   | 154               |

|   | A 1   |                           | ocality Correlation Data                                          | 154               |

# Table of Figures

| Figure 2.1  | Component Performance vs. Time                                                                               | 16              |

|-------------|--------------------------------------------------------------------------------------------------------------|-----------------|

| Figure 2.2  | Normalized Latencies vs. Time                                                                                | 17              |

| D: 9 1      | P(m) $M(m)$ $P(m)$ and $M(m)$ for Single Hit Rate                                                            | 37              |

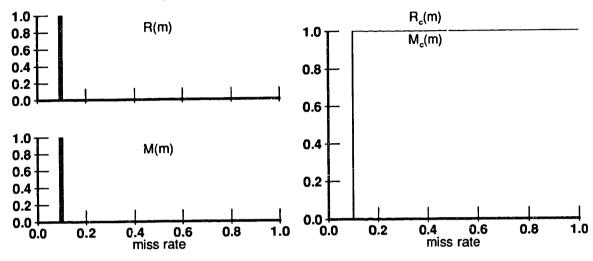

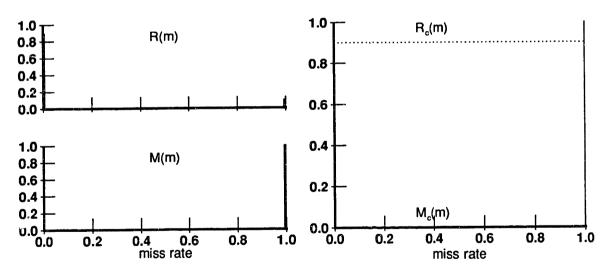

| Figure 3.1  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Single Hit Rate                                                  | 37              |

| Figure 3.2  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Two Distinct Hit Rates $R_c(m)$ and $M_c(m)$ for Badref Behavior | 38              |

| Figure 3.3  |                                                                                                              | 45              |

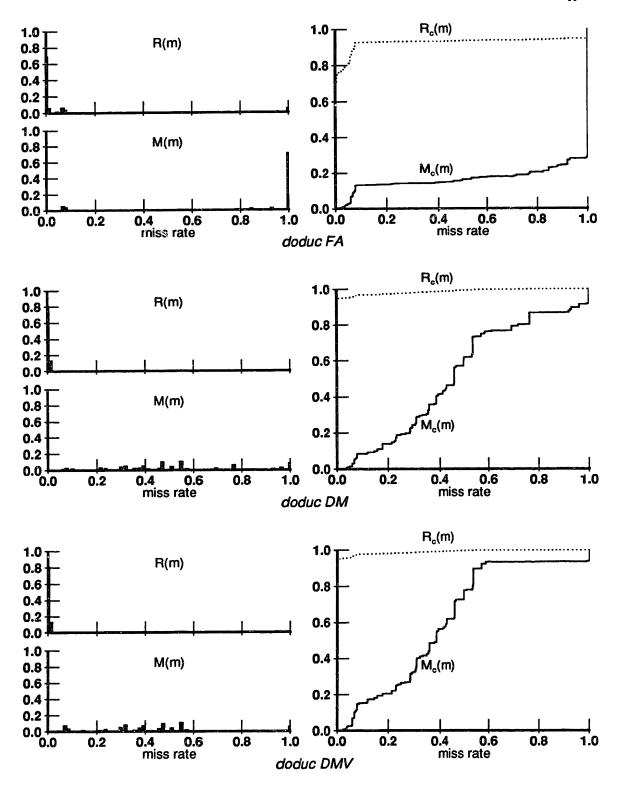

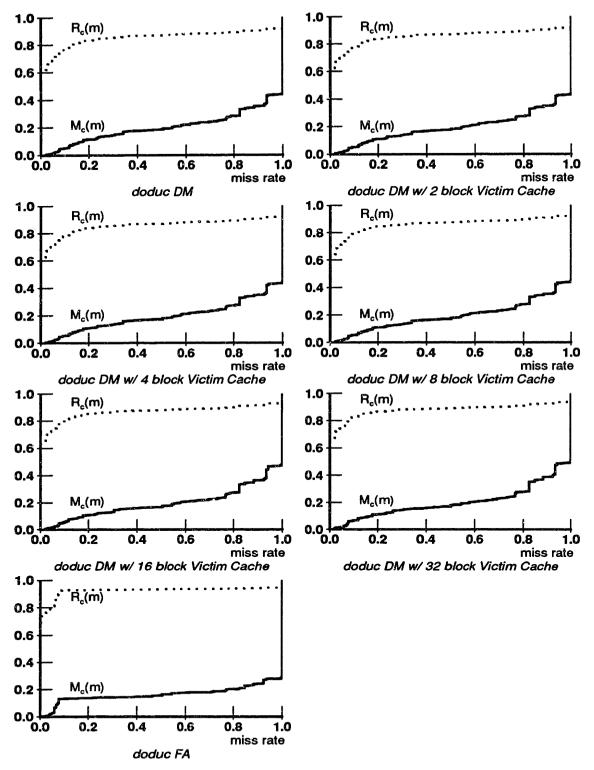

| Figure 3.4  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Doduc FA, DM and DMV                                             | 46              |

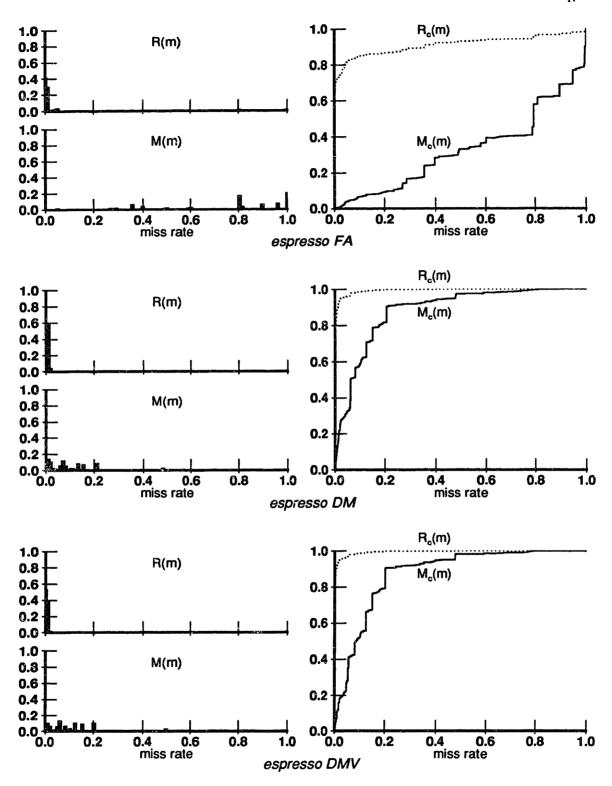

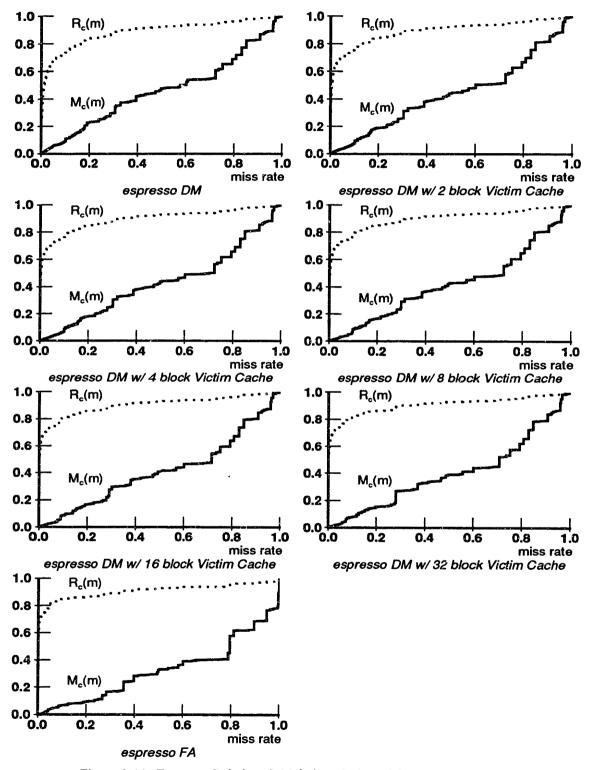

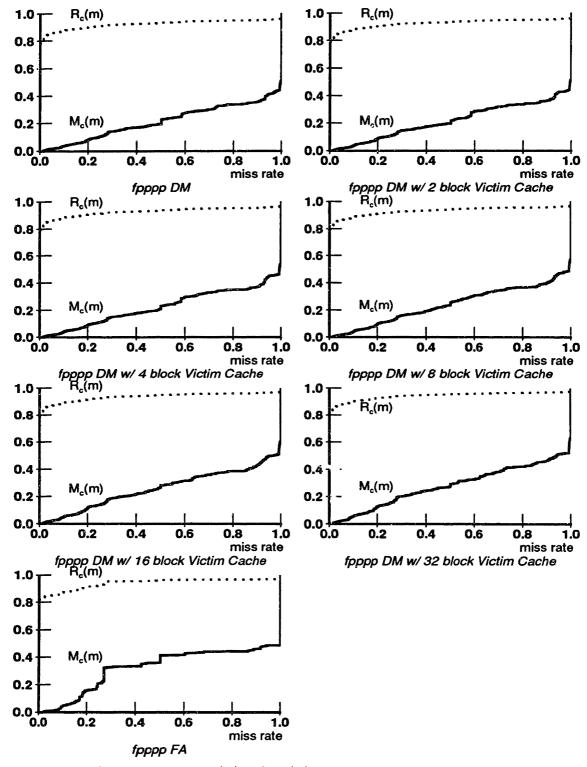

| Figure 3.5  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Espresso FA, DM and DMV                                          | 47              |

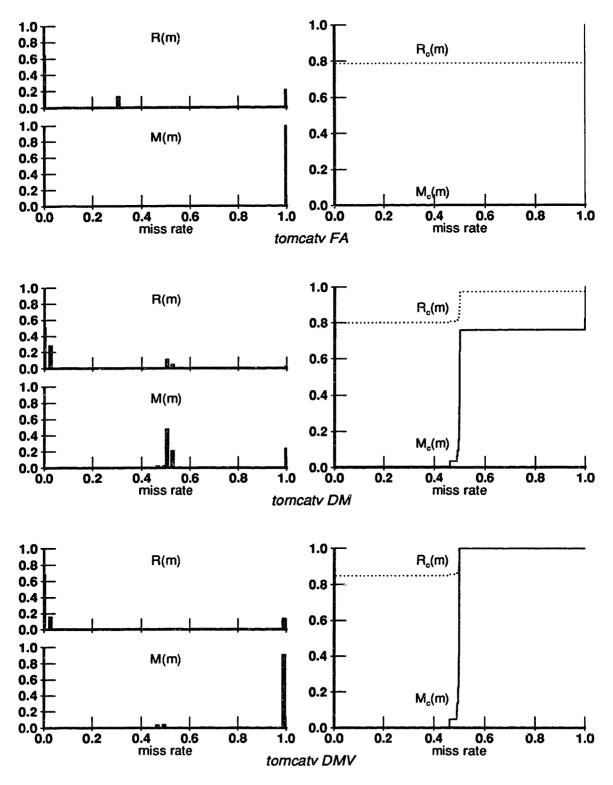

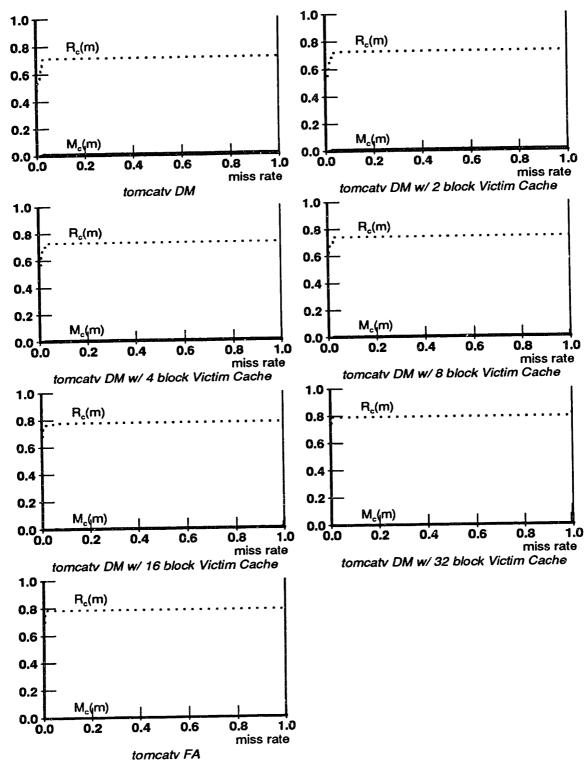

| Figure 3.6  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Tomcatv <b>FA</b> , <b>DM</b> and <b>DMV</b>                     | 50              |

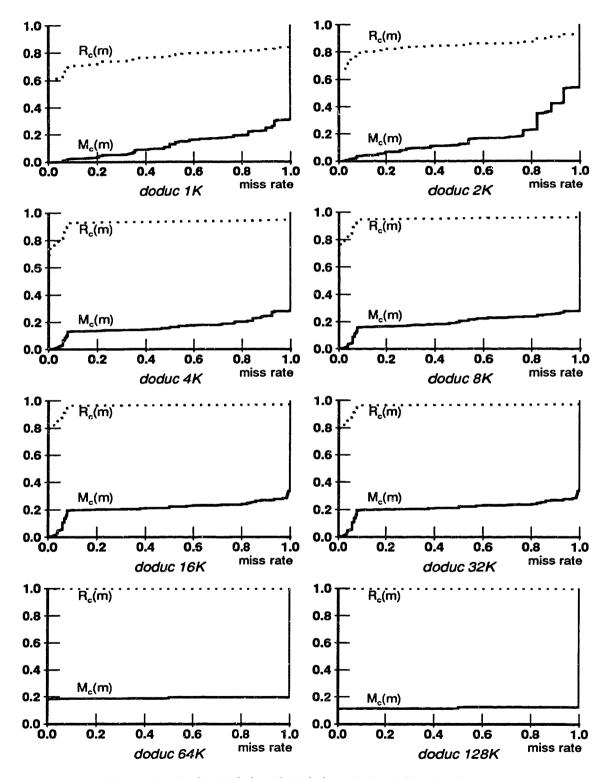

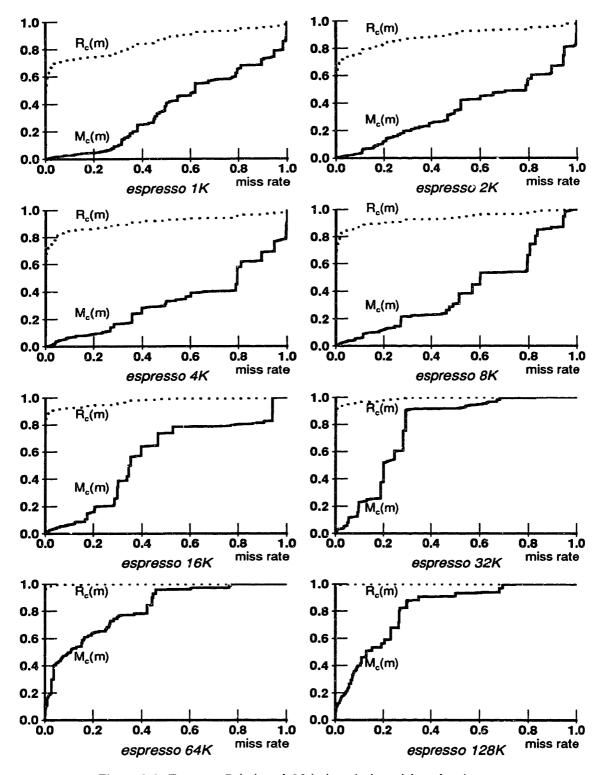

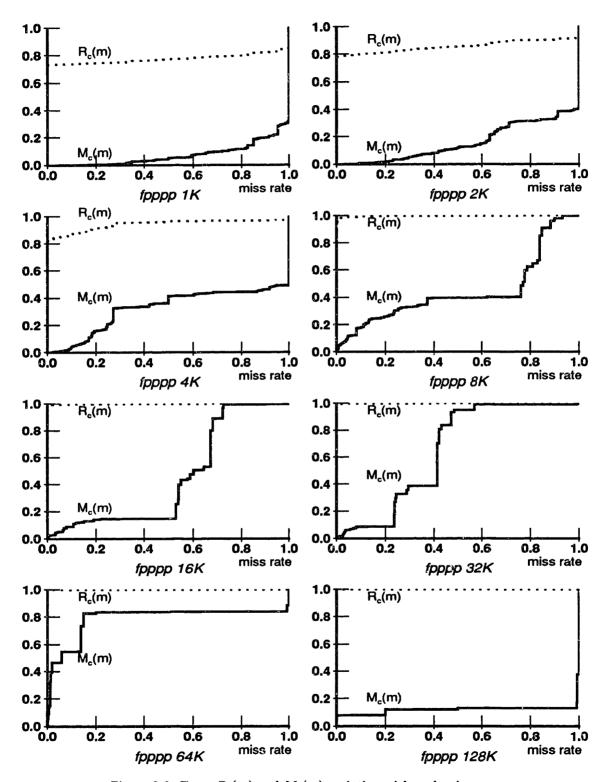

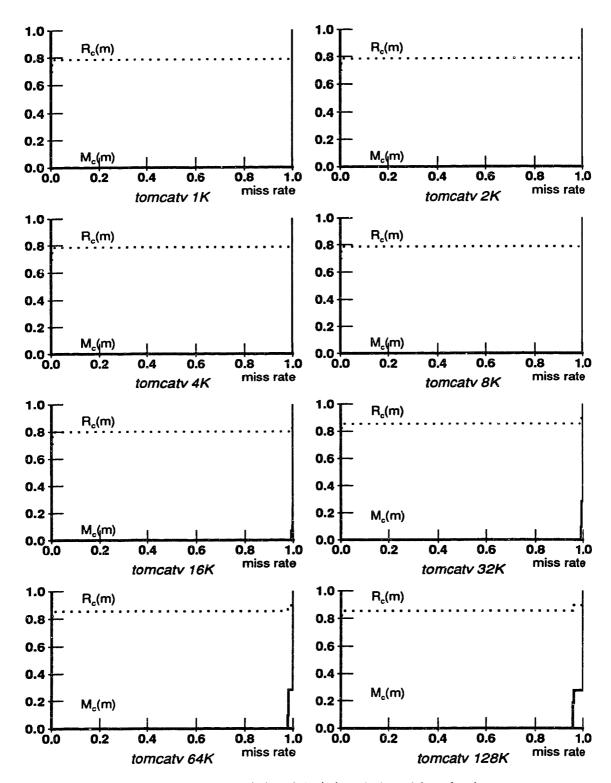

| Figure 3.7  | Doduc $R_c(m)$ and $M_c(m)$ variation with cache size                                                        |                 |

| Figure 3.8  | Espresso $R_c(m)$ and $M_c(m)$ variation with cache size                                                     | 51              |

| Figure 3.9  | Fppp $R_c(m)$ and $M_c(m)$ variation with cache size                                                         | $\frac{52}{52}$ |

| Figure 3.10 | Tomcatv $R_c(m)$ and $M_c(m)$ variation with cache size                                                      | 53              |

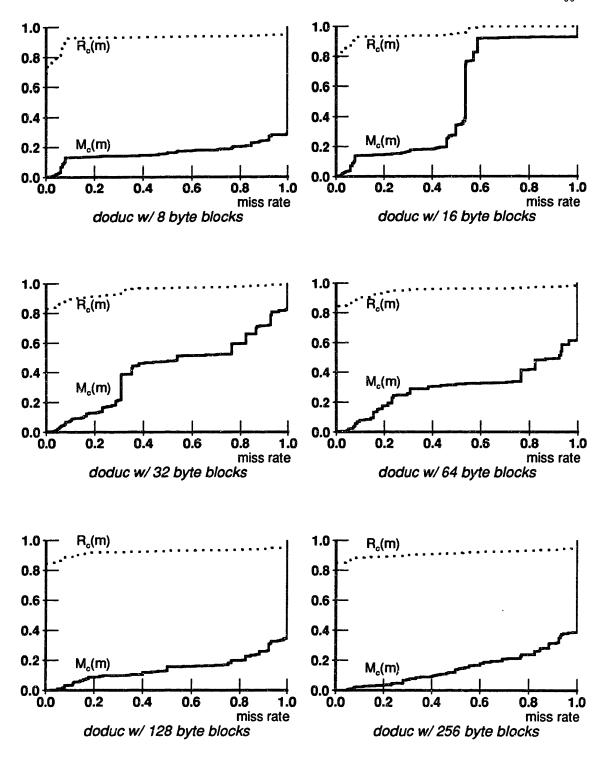

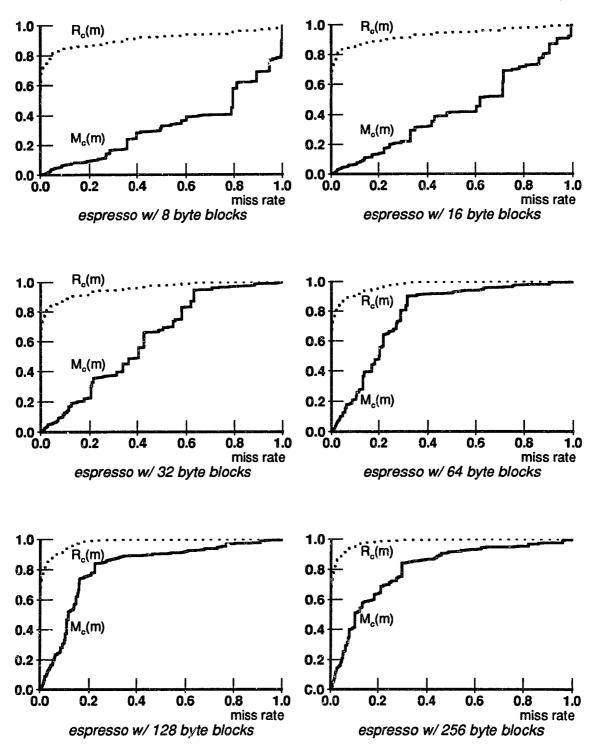

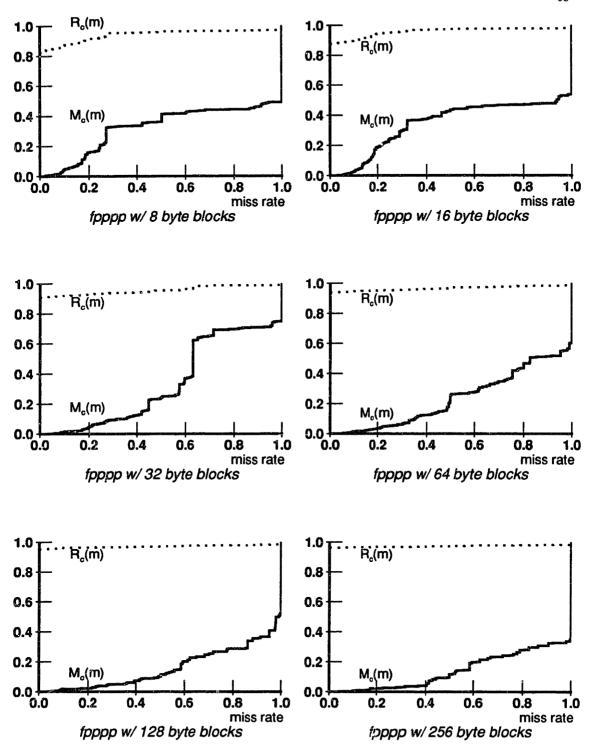

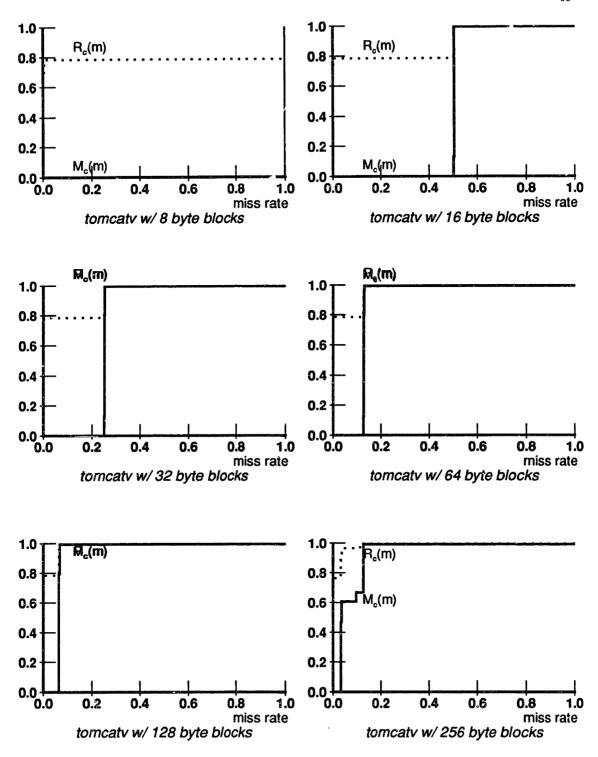

| Figure 3.11 | Doduc $R_c(m)$ and $M_c(m)$ variation with block size                                                        | 55<br>56        |

| Figure 3.12 | Espresso $R_c(m)$ and $M_c(m)$ variation with block size                                                     | 56              |

| Figure 3.13 | Fppp $R_c(m)$ and $M_c(m)$ variation with block size                                                         | 57              |

| Figure 3.14 | Tomcatv $R_c(m)$ and $M_c(m)$ variation with block size                                                      | 58              |

| Figure 3.15 | Doduc $R_c(m)$ and $M_c(m)$ variation with associativity                                                     | 60              |

| Figure 3.16 | Espresso $R_c(m)$ and $M_c(m)$ variation with associativity                                                  | 61              |

| Figure 3.17 | Fppp $R_c(m)$ and $M_c(m)$ variation with associativity                                                      | 62              |

| Figure 3.18 | Tomcatv $R_c(m)$ and $M_c(m)$ variation with associativity                                                   | 63              |

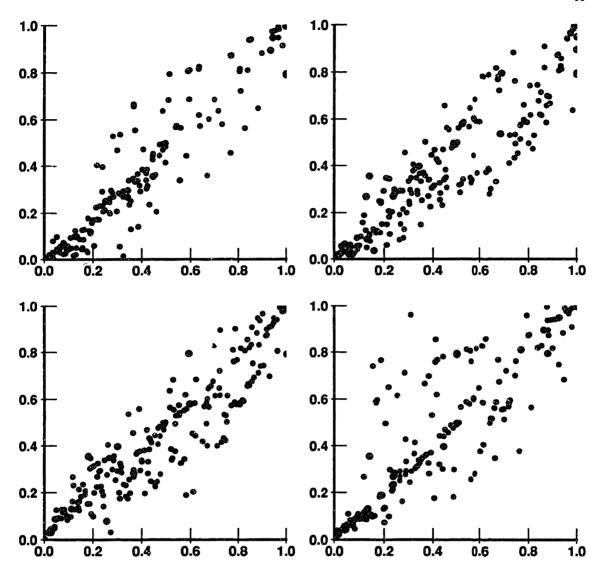

| Figure 3.19 | Miss Rate Variation with Input Data Perturbations in Espresso                                                | 65              |

| Figure 4.1  | Dataflow Constraints for Example 1                                                                           | 68              |

| Figure 4.2  | Dataflow Constraints for Example 2                                                                           | 68              |

| Figure 4.3  | Dataflow Constraints for Example 3                                                                           | 69              |

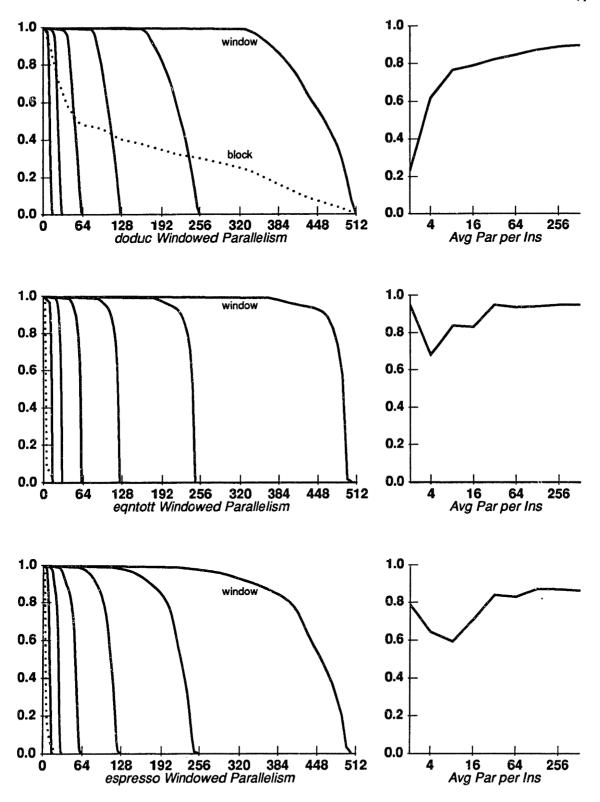

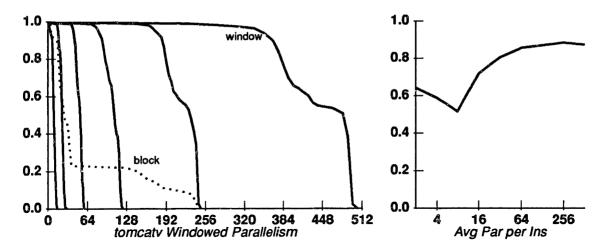

| Figure 4.4  | Windowed and Basic Block Parallelism for doduc, espresso and equtott                                         | 73              |

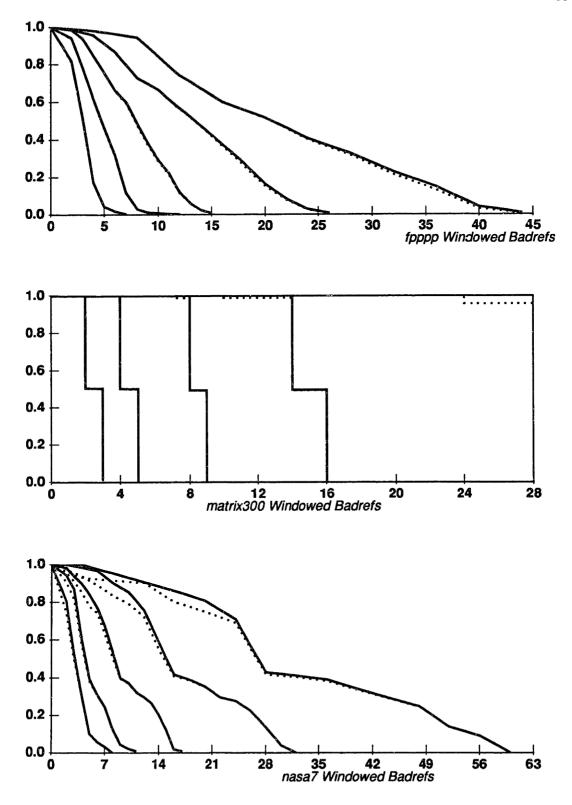

| Figure 4.5  | Windowed and Basic Block Parallelism for fpppp, matrix300 and nasa7                                          | 74              |

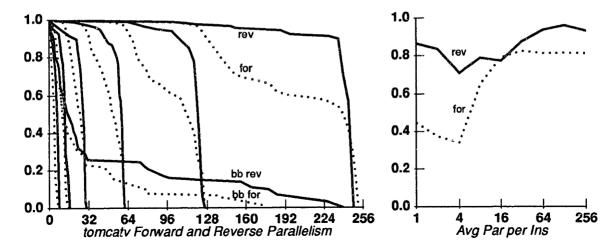

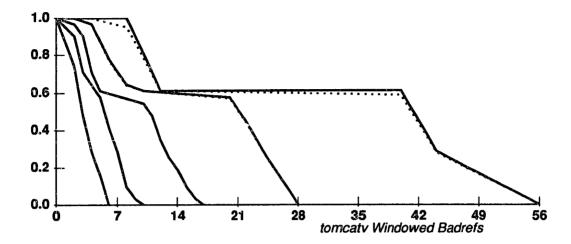

| Figure 4.6  | Windowed and Basic Block Parallelism for tomcatv                                                             | 75              |

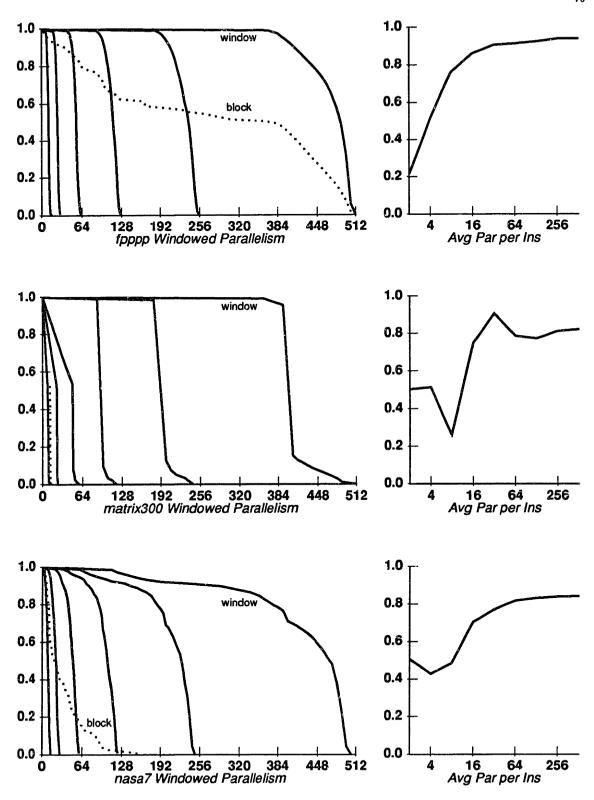

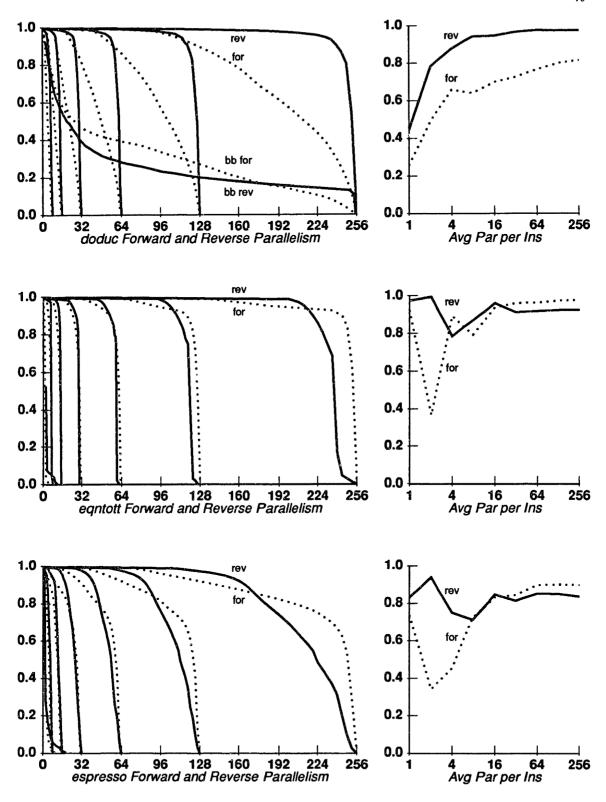

| Figure 4.7  | Reverse and Forward Parallelism for doduc, espresso and equtott                                              | 78              |

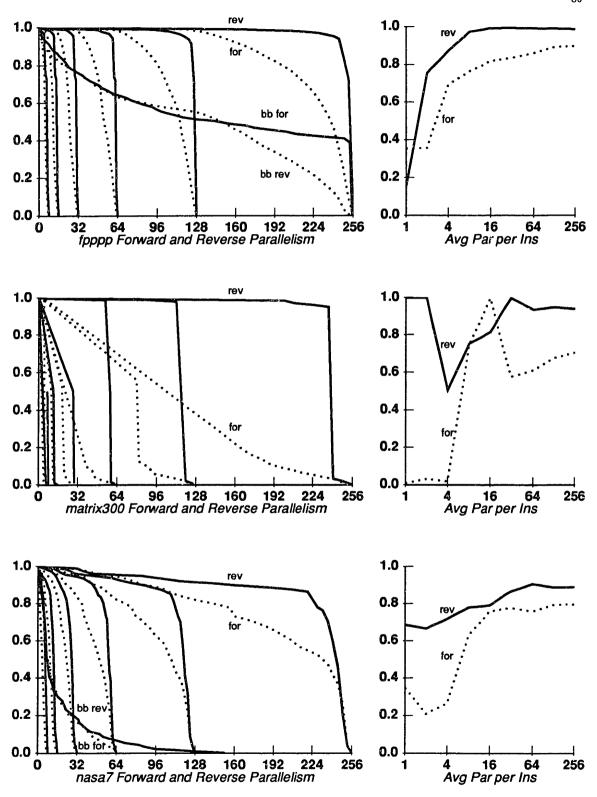

| Figure 4.8  | Reverse and Forward Parallelism for fpppp, matrix300 and nasa7                                               | 79              |

| Figure 4.9  | Reverse and Forward Parallelism for tomcatv                                                                  | 80              |

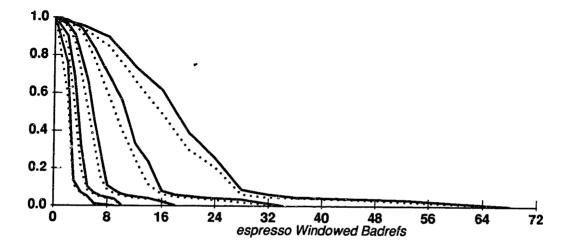

| Figure 4.10 | Windowed Badref Counts for doduc, espresso and equtott                                                       | 82              |

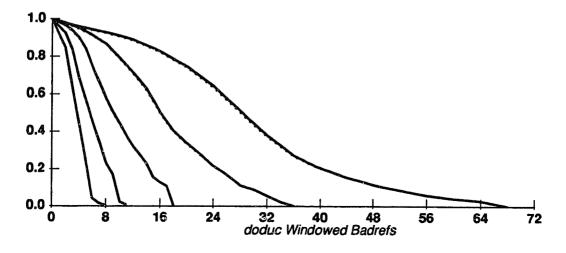

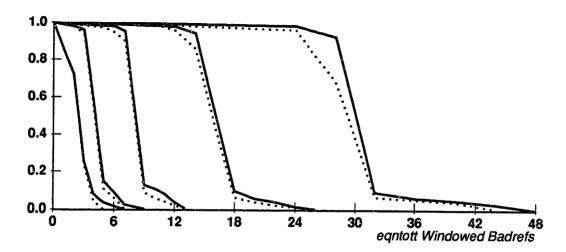

| Figure 4.11 | Windowed Badref Counts for fpppp, matrix300 and nasa7                                                        | 83              |

| Figure 4.12 | Windowed Badref Counts for tomcatv                                                                           | 84              |

| Figure 5.1  | Characteristic IVs and SCCs in C-flat                                                                        | 93              |

| Figure 5.2  | RAADs in C-flat                                                                                              | 94              |

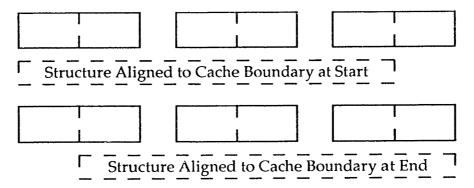

| Figure 5.3  | Block Alignments of 5 word Data Structure                                                                    | 106             |

| Figure 6.1  | Doduc FA Performance                                                                                         | 134             |

| Figure 6.2  | Equtott FA Performance                                                                                       | 134             |

| Figure 6.3  | Espresso FA Performance                                                                                      | 135             |

| Figure 6.4  | Fpppp FA Performance                                                                                         | 135             |

| Figure 6.5  | Matrix300 FA Performance                                                                                     | 136             |

| Figure 6.6  | Nasa7 FA Performance                                                                                         | 136             |

| Figure 6.7  | Tomcatv FA Performance                                                                                       | 137             |

| Figure 6.8  | Doduc DM Performance                                                                                         | 139             |

| Figure 6.9  | Equtott DM Performance                                                                                       | 139             |

| I IKUIU U.U | Editoro Este i ottorittomo                                                                                   | -00             |

| Figure 6.10 | Espresso DM Performance                                               | 140 |

|-------------|-----------------------------------------------------------------------|-----|

| Figure 6.11 | Fpppp DM Performance                                                  | 140 |

| Figure 6.12 | Matrix300 DM Performance                                              | 141 |

| Figure 6.13 | Nasa7 DM Performance                                                  | 141 |

| Figure 6.14 | Tomcatv DM Performance                                                | 142 |

| Figure A.1  | $R(m), M(m), R_c(m)$ and $M_c(m)$ for Equtott FA, DM and DMV          | 154 |

| Figure A.2  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Fppp FA, DM and DMV       | 155 |

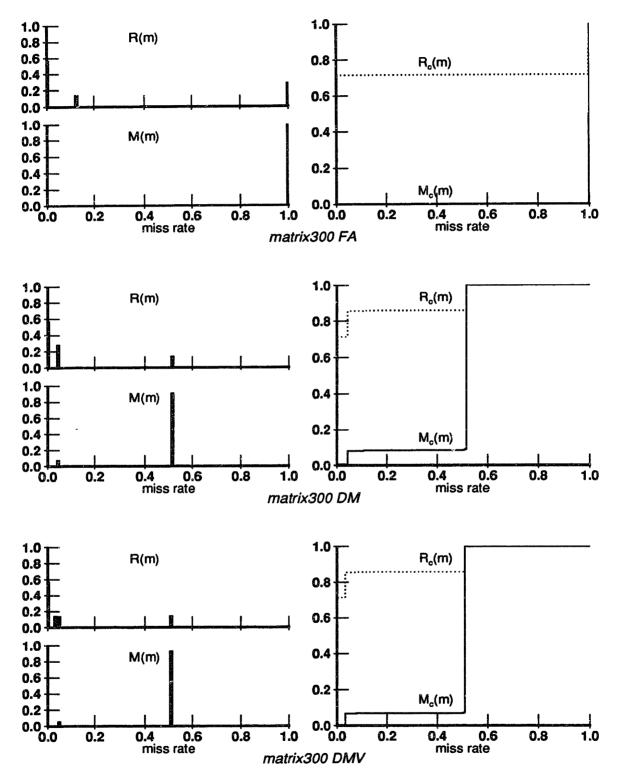

| Figure A.3  | $R(m)$ , $M(m)$ , $R_c(m)$ and $M_c(m)$ for Matrix 300 FA, DM and DMV | 156 |

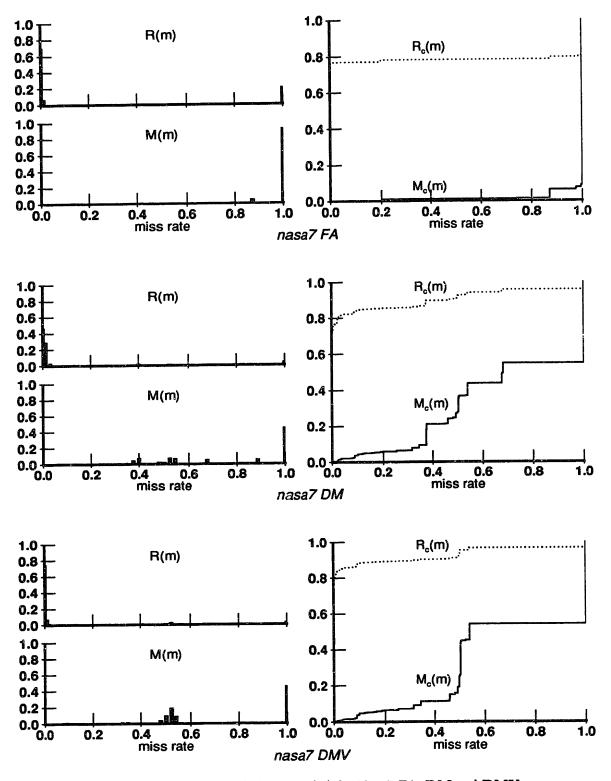

| Figure A.4  | $R(m), M(m), R_c(m)$ and $M_c(m)$ for Nasa7 FA, DM and DMV            | 157 |

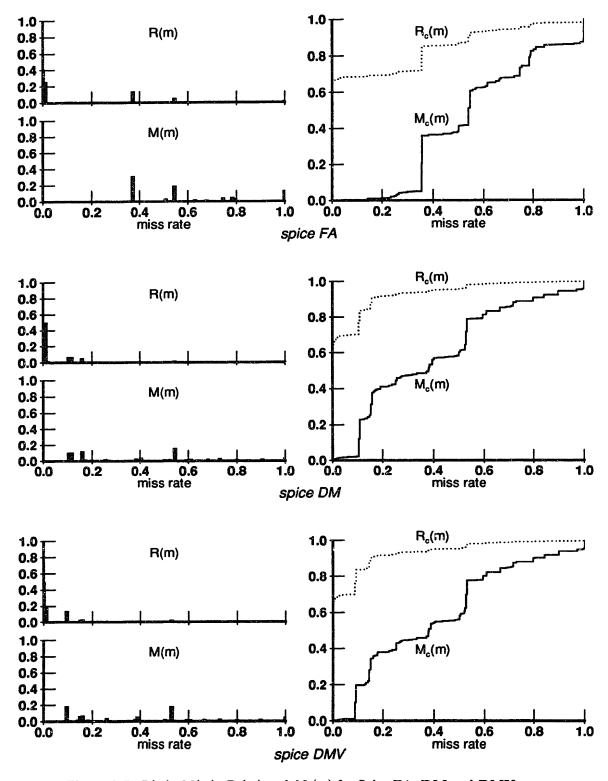

| Figure A.5  | $R(m), M(m), R_c(m)$ and $M_c(m)$ for Spice FA, DM and DMV            | 158 |

# Table of Figures

| Table 6.1 | Badref Categorization for Doduc and Eqntott   | 126 |

|-----------|-----------------------------------------------|-----|

|           | Badref Categorization for Espresso and Fpppp  | 127 |

| Table 6.2 | Badref Categorization for Matrix300 and Nasa7 | 127 |

| Table 6.3 | Badref Categorization for Spice and Tomcatv   | 128 |

| Table 6.4 | Fractional Increase in Optimized Code Size    | 130 |

| Table 6.5 | Ratios of Benchmark Speedups                  | 137 |

| Table 6 6 | Ratios of Delicititaty pheerings              |     |

### Chapter 1

### Introduction

Technological trends motivate a desire for memory latency tolerance mechanisms in computer system architectures. Memory latency tolerance in an architecture describes the ability to compute efficiently given an everincreasing ratio, over the lifetime of the architecture, between the latency required to access data from slow components of the memory and the time to perform elementary computations within the processor. Efficient computation in the face of high memory latency can be achieved by exploiting locality and parallelism inherent in a system's workload. Hierarchical, cache-based memory systems which dynamically exploit program locality have been the principle architectural tool for dealing with memory latency. Cache misses result in a residual memory latency component in cached systems. This thesis investigates the application of explicit, compilation-based management of processor/memory system concurrency, thereby exploiting parallelism to achieve tolerance to cache-miss latency.

#### 1.1. Preview of Technical Contributions and Results

Cache-miss latency is a potential performance limitation in computer systems. Our contributions with respect to the problem of cache miss latency tolerance can be divided into four main categories.

- We identify, characterize and measure an important new aspect of the locality behavior of programs termed static locality correlation.

- We characterize and measure program parallelism relevant in the context of memory latency tolerance.

- We devise and implement scheduling algorithms which can be used by a compiler to

produce latency tolerant code. These algorithms exploit our behavioral observations

concerning locality and parallelism.

- We measure the performance of mechanically-generated, latency-tolerant code. This serves to demonstrate both the feasibility and effectiveness of compilation-based latency tolerance.

#### 1.1.1 Static Locality Behavior

Architectural advances in computing, in contrast to technological advances, often arise from improved understanding of the behavior of programs. The study and identification of regularities in runtime program behavior allows better application of available technology. Analysis and characterization of program behavior relevant to memory latency and its tolerance leads to several insights which can be exploited in latency tolerant compilation.

The principle aspect of program behavior impacting memory performance in cached systems is locality. We make several related observations about the locality behavior of programs which are extremely important in the context of latency tolerance.

Distinct memory references at runtime which are produced by the same static instruction exhibit correlated locality behavior. Since caches adaptively modify their contents to reflect recent memory references, the hit/miss behavior of a particular memory reference at runtime is determined by the relationship of the addresses it uses to the addresses used by neighboring references. The juxtaposition of memory references does not occur by chance but instead occurs as a consequence of the structure of programs. Every time a particular memory reference instruction is executed the neighboring dynamic memory references are produced by the same neighboring static instructions. Thus the set of dynamic memory references produced by a particular static memory reference instruction all occur in a similar context, created by its neighboring instructions. As a consequence, these dynamic references are likely to exhibit the same hit/miss behavior systematically. Their locality behavior is correlated.

For many programs, the particular context in which references occur is independent or only weakly dependent on input data. References produced by the same instruction, even across multiple program runs, exhibit similar behavior. In contrast, even in the same program run, references arising from different static memory reference instructions have different contexts, each arising from its own local program structure. As a result, there is no reason to expect the behavior of dynamic references arising from different static instructions to be strongly correlated.

This behavior is elucidated through the Static Locality Correlation Hypothesis. This hypothesis states that program structure is a primary determinant of locality behavior. The hit/miss behavior of each individual static references can be characterized across multiple program runs while the behavior of different static references, even within a single program run, can vary widely.

The principle consequence of static locality correlation is to justify the distinct characterization of the hit/miss behavior of each static memory reference in a program with an individual miss rate. In the absence of static locality correlation the behavior of all static memory references would be essentially equivalent. This is simply not the way programs behave. Hit/miss behavior varies significantly between different static references and can be individually ascribed to each reference. Individual characterization of locality behavior of references is extremely useful in the context of generation of latency tolerant code.

Building on the static locality hypothesis, additional aspects of program locality are observed. Program structure frequently guarantees that some static memory reference instructions cannot produce misses by construction. Given that some fraction of static references produce no misses, it is an inevitable consequence for programs with a non-zero average miss rate that some other static references must have individual miss rates which exceed the program average. We observe two aspects regarding the distribution of miss rates of individual static memory references. First, static reference miss rate behavior is highly polarized, exhibiting some references with very low miss rates and some with relatively high miss rates. Second, far more dynamic references are produced by low miss rate references than high miss rate references, in most cases. The Badref Hypothesis encapsulates these observations regarding polarization of miss rates and distribution of references by instruction miss rate.

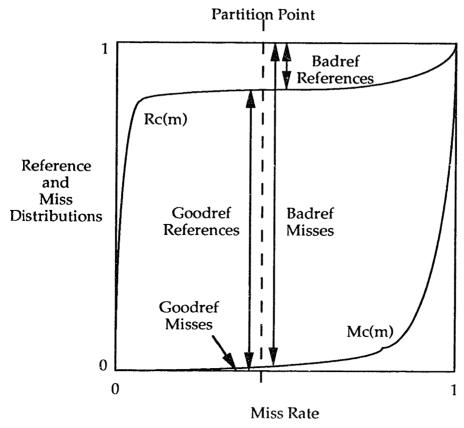

The Badref Hypothesis observes that static memory references can be partitioned into a low miss rate set, goodrefs, and a high miss rate set, badrefs. Goodrefs, static references with negligibly small miss rates, often account for a significant fraction of all dynamic memory references, between 60 and 90% or even more. Badrefs typically account for a much smaller fraction of dynamic references. Notice that 100% miss rate static references can account for a fraction of dynamic references no greater than the average program miss rate. Thus most dynamic references occur in conjunction with the execution of goodrefs.

The number of misses produced by a particular static reference is the product of the number of references and the miss rate exhibited by the reference. Even a large set of dynamic references produce zero or very few misses if they are produced by a static reference with a very low miss rate. A relatively small set of dynamic references which miss very frequently compared to the program average may well account for the preponderance of program misses. In fact, in many programs,

this is precisely the behavior exhibited. Badrefs, a subset of static references with high miss rates, produce a small set of dynamic references while accounting for most of the misses experienced by programs. Notice that this behavior reflects the three distinct aspects described. Not only do static references exhibit distinct miss rates but these miss rates are polarized far from the program average. Furthermore, the dynamic size of the low miss rate set dominates that of the high miss rate set, but not by enough that misses produced by the low miss rate set represent a signficant fraction of total misses.

These insights into memory behavior can be exploited in latency-tolerant compilation. Static locality correlation suggests individualized behavior modelling of each memory reference in a program, rather than the uniform treatment accorded all memory references in most compilers. Based on the polarization of miss rates described by the Badref Hypothesis, we develop a compiler model for memory system behavior, the Badref Model. This model partitions memory references into two sets, goodrefs and badrefs. Goodrefs are modelled as cache hits while badrefs are modelled as cache misses. The predominance of goodrefs in many programs serves to focus the problem of miss latency tolerance onto a small set of memory references, greatly simplifying the development of compiler techniques for scheduling this latency. Exploitation of these phenomena enables the practical application of software-scheduled concurrency as a memory latency tolerance technique.

With regard to understanding and exploiting locality behavior of programs, this thesis makes several distinct contributions. We develop and elucidate the concept of static locality correlation and the further refinement regarding the polarization of this behavior in the static locality and badref hypotheses. These insights are supported through qualitative and quantitative empirical evidence. Qualitative evidence takes the form of examples of frequently occurring program structures which lead both to goodrefs and badrefs. Quantitative evidence takes the form of benchmark simulation studies for a set of programs across a variety of cache configurations and focused studies addressing the impacts on badref behavior of changing cache design parameters including cache size, block size and the level of cache conflict misses. Finally, we demonstrate the technique by which this behavior can be exploited for latency tolerant code generation in the form of the badref model.

#### 1.1.2 Parallelism Behavior

Concurrency between the servicing of miss transactions and other computation and/or concurrency between the servicing of multiple misses is a means for achieving latency tolerance. Concurrent processing of distinct operations in programs requires parallelism or independence between the operations. Investigation of program behavior turns then from locality to parallelism. Do programs exhibit sufficient, accessible parallelism that software latency tolerance is a practical technique?

Measurements of instruction-level parallelism in the literature are typically relatively low, between two and five. These numbers should not be interpreted to mean that memory latencies beyond five cannot be tolerated through concurrency. Average instruction-level parallelism is simply not a suitable metric for evaluating parallelism for memory latency tolerance.

To allow complete concurrency between a processor and memory during the servicing of a 20 cycle long miss transaction, 20 instructions must be identified which are independent of the miss transaction. These instructions cannot produce data needed to initiate the miss transaction and similarly cannot use data fetched from memory by the miss transaction. It is by no means necessary for these instructions to be independent of one another, however. In fact, a linear sequence of 20 mutually dependent instructions is quite suitable for overlap with a 20 cycle miss transaction as long as each instruction in the sequence is independent of the miss. Such a construction involving a single miss operation and 20 dependent instructions, each independent of the miss, might be characterized as exhibiting an average parallelism of 1.05.

The observation above regarding parallelism can be coupled with the behavior described by the badref hypothesis, namely the fact that miss latency occurs primarily in conjunction with a small set of identifiable, memory reference instructions. This conjunction of ideas is essential. The key

to finding adequate parallelism to tolerate very high memory latencies lies in the specific ability to pinpoint this latency to a small, fixed and identifiable set of static memory references. Having isolated the sources of misses, limited program parallelism can be devoted exclusively to masking the associated latency, rather than squandered in untargetted efforts to tolerate potential latency for all memory references. Moreover, goodrefs, those memory reference instructions which produce no misses, become an additional source of parallelism for badrefs rather than a consumer of parallelism.

Thus the problem of latency tolerance can be viewed as finding parallelism between a small set of very slow but identifiable operations and a large set of fast operations. The relevant question to ask about parallelism in this context is how many fast operations are independent of each slow operation. Rather than looking at average program parallelism one should focus specifically on the issue of whether a group of instructions consisting of goodrefs and non-memory operations can be matched with each dynamic instance of a static badref, the source of memory latency. These instructions must be independent of the candidate badref instance but need not be independent of one another since they can be executed sequentially.

The insight above makes the problem of parallelism identification for latency tolerance somewhat more tractable. The operation of servicing a miss transaction has additional properties which can be exploited to further reduce constraints limiting parallelism. Caches operate transparently with respect to processors so the servicing of miss transactions has no semantic impact on programs. This property makes the speculative initiation of miss transactions an attractive option for eliminating both constraints associated with program control and potential but unlikely data dependencies for miss addresses. Furthermore, the disambiguation function performed by caches decouples the transfer of data from memory to cache from the act of modifying this data. As a consequence, one need not consider potential dependencies for transferred data in the form of undisambiguated store operations. Finally, storage reuse dependencies, *i.e.* antidependencies and output dependencies, can be eliminated when desired through storage replication. The only dependencies which remain after application of these techniques are real dataflow dependencies for addresses used to initiate miss transactions and dataflow dependencies resulting from the actual use of transferred data.

We measure parallelism for a set of benchmark programs using a measurement technique targetted specifically at identifying parallelism relevant for latency tolerance. Anticipating the application of constraint reduction techniques, program parallelism is measured in a context which relaxes away many constraints and pseudo-dependencies. Dependencies are only recognized for actual runtime dataflow dependencies for addresses used to initiate miss transactions and from transferred data to uses of the data. The measurement technique tabulates non-dependent instructions with respect to each dynamic badref instance in a program run.

The first place to look for parallelism, since it yields parallelism most easily exploited in the framework of static code scheduling, is in the neighborhood of instructions adjacent to badrefs in a sequential program schedule. In this context we find substantial amounts of parallelism, often comparable in size to the neighborhood or window over which we look. In a 256 instruction window adjacent to a badref it is not uncommon to find that 90% of the instructions in the window are independent of the badref.

In the context of discussing parallelism we contrast statically scheduled latency tolerance, i.e. latency tolerant code, with single-threaded hardware dynamic schedulers. We observe that hardware schedulers probably cannot exploit key aspects of program behavior and properties unique to cache transactions which make latency tolerance tractable. In particular, it is difficult for a hardware scheduler to distinguish badrefs from goodrefs, at which point the battle may already be lost. Even given such a differentiation, it would be difficult for a hardware scheduler to look far into the future to find badrefs and to resolve necessary intermediate dependencies by executing those key instructions which lead to computation of badref addresses. As a consequence, hardware schedulers are restricted primarily to exploiting parallelism between badrefs and instructions closely following them in sequential program schedules. In benchmark measurements we find that this is the least effective place to look for parallelism.

#### 1.1.3 Compiler Latency Tolerance Algorithms

Guided by insights regarding program locality and parallelism behavior, and emboldened by measurements indicating large quantities of parallelism, we proceed to develop code scheduling algorithms to access this parallelism to achieve concurrency for memory latency tolerance. These algorithms achieve their effectiveness by modelling memory behavior using the badref model. Focusing on badrefs leads to a viewpoint for the problem of generating latency tolerant code as one of explicitly scheduling miss activity within the memory system. This viewpoint proves to be effective.

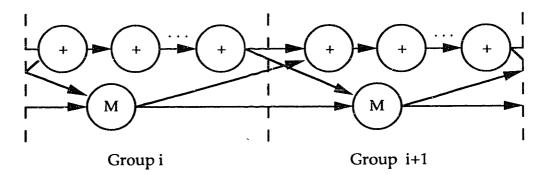

In pursuing the problem of developing miss scheduling algorithms it is helpful to turn once again to the structure and behavior of programs. Upon close examination, it turns out that in many programs badrefs occur primarily in conjunction with accessing large, aggregate, data structures within loops. Loops traversing arrays typify these accesses although other patterns exist as well. In loops traversing aggregate data structures, some set of the static memory references in each iteration perform the first access to components in the newest data structure element. These references often systematically result in misses, producing badrefs. References which perform subsequent accesses to components never miss and are goodrefs. Accesses to these Regularly Accessed, Aggregate Data structures will be referred to as RAADs. RAAD prefetching is a technique developed specifically to target this key class of badrefs. RAAD prefetching applies software pipelining via prefetching to overlap overlap computation from one loop iteration with miss transactions scheduled for one or more future iterations.

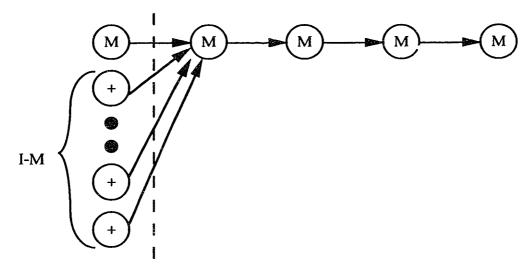

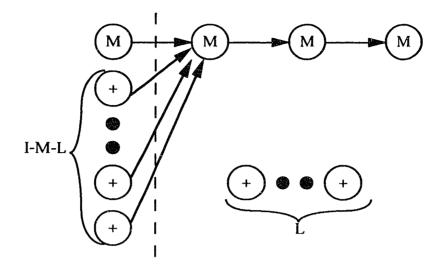

While RAAD prefetching addresses an important class of badrefs for many benchmarks, it is not a panacea. By specifically targetting references inside of explicitly recognizable loops it fails to be effective when badrefs arise in other contexts or when procedure boundaries obscure explicit looping constructs from their contained badrefs. A second scheduling technique termed sequential miss scheduling addresses a more general class of badrefs. From a long sequence of code a shorter sequence of miss transactions is constructed, one per badref in the original sequence. These two sequences are then merged together, subject to limited rescheduling of the original code sequence in order to satisfy address dependencies for the miss schedule. A technique akin to trace scheduling is used to construct long code sequences for miss scheduling.

A prototype compiler implementation performing RAAD prefetching and sequential miss scheduling and a suitable simulation environment provide a mechanism for measuring the runtime performance of latency tolerant code. Code for this system is generated completely mechanically, thus the system provides a proof-of-concept for compilation-based tolerance to memory latency for data accesses.

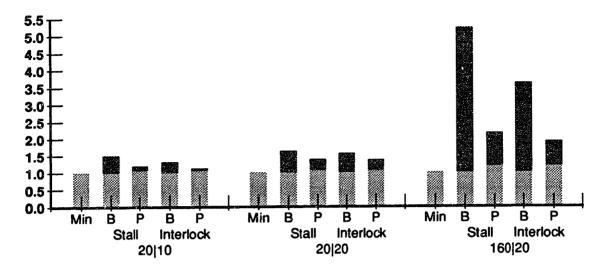

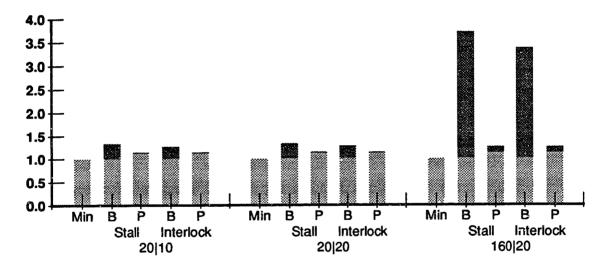

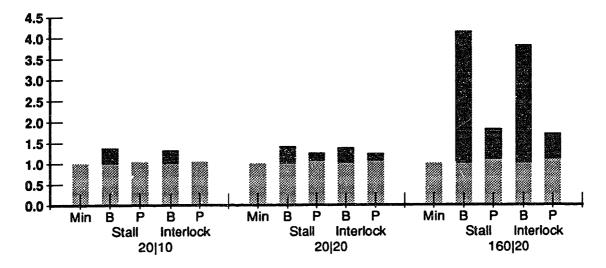

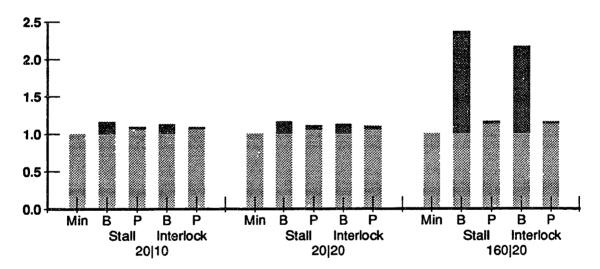

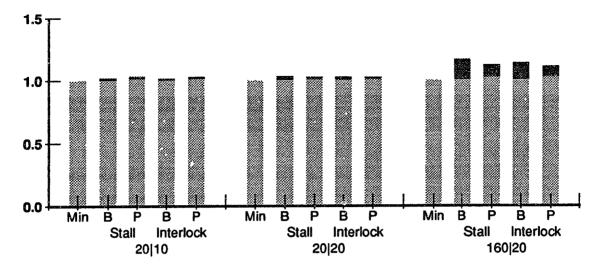

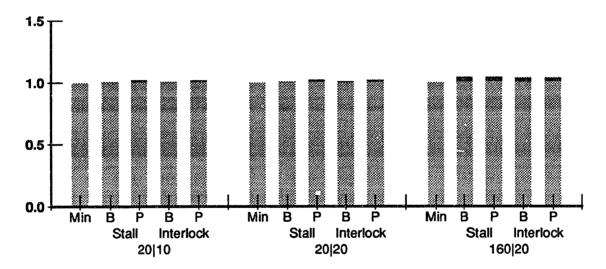

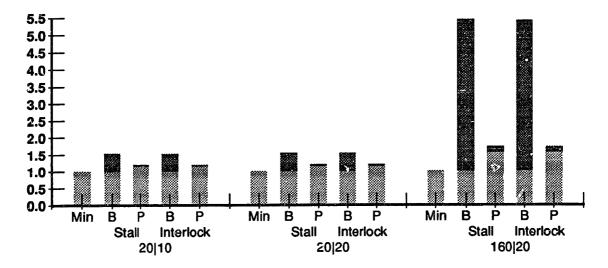

#### 1.1.4 Performance Evaluation

Despite the relatively primitive status of the prototype compiler, performance improvements are exhibited by benchmark programs. The specific speedup values depend upon the memory configurations assumed. For a small, fully-associative cache combined with a memory system with a latency of 20 cycles, speedups between 10 and 30% are exhibited by programs from the SPEC benchmark suite. For the same cache, coupled with a memory system with a latency of 160 cycles, but equivalent bandwidth, latency tolerant code outperforms unmodified code by factors between 2 and 6, i.e. modified code is sometimes 600% faster than unmodified code. Modified code for the 160 cycle memory system typically achieves performance within 25% of that of modified code for the 20 cycle memory system.

Performance is mixed for direct-mapped caches. While some benchmarks exhibit performance improvement comparable to the fully associative case for the same memory parameters, some benchmarks are actually degraded by latency tolerance optimization. We believe that this degradation reflects limitations in the current prototype compiler rather than fundamental problems associated with direct-mapped caches.

On balance, the results for the fully-associative cache test demonstrate the effectiveness of compilation based latency tolerance. Tests based on 20 cycle memory latencies exhibit modest improvements in conjunction with current memory latencies. That's using 160 cycle memory suggest that our techniqes can provide significant tolerance to much higher levels of relative memory latency which will accompany very fast processors in the future.

### 1.2. Thesis Roadmap

Subsequent chapters address the topics alluded to above in significantly more detail. This section provides a description of the forthcoming chapters in order to allow the intrigued reader to skip directly to chapters targetting his or her interest.

Chapter 2 provides introductory, background and motivational material. The problem of memory latency is motivated as an inevitable performance limitation for computing given current technological trends. Caching and interleaved memory systems are described, as well as difficulties in coupling these two techniques arising from limitations in current processor/memory system interfaces. Alternative memory latency tolerance techniques are surveyed, as is other related literature. This chapter is non-essential to subsequent chapters.

Chapter 3 discusses the static locality correlation and badref hypotheses. The hypotheses are developed and supported qualitatively, based on an intuitive, empirical analysis of program structure. The significance of these phenomena with respect to latency tolerant compilation is explained. Finally, quantitative, empirical evidence in the form of benchmark simulation data is provided to indicate the degree to which programs exhibit static locality and badref behavior for a single input data set across a variety of cache configurations. Evidence is also provided supporting the hypothesis that static locality behavior is consistent across multiple input data sets.

Chapter 4 analyzes parallelism requirements for memory latency tolerance. It explains why average parallelism and similar operation-blind metrics are not appropriate for characterizing parallelism for latency tolerance. A suitable measurement technique which relaxes away avoidable constraints and specifically measures parallelism with respect to badrefs in their neighborhood in a sequential program is developed. This measurement technique is used to characterize parallelism in benchmark programs. Empirical evidence shows that substantial parallelism exists.

Chapter 5 describes modelling techniques, algorithms and heuristics relevant to the problem of design and implementation of compilers to produce latency-tolerant code. The chapter describes two scheduling algorithms termed RAAD prefetching and sequential miss scheduling. It details heuristic tests to determine an appropriate scheduling technique in situations when both can be applied.

Chapter 6 provides empirical results gathered using a prototype compiler implementation based on the algorithms and techniques from Chapter 5. Two forms of results are provided. The compiler generates statistics describing the forms of badrefs encountered and the frequency of use and expected performance costs and benefits of the two code scheduling techniques. Code generated by the prototype compiler is executed in conjunction with a timing simulator to assess the latency tolerance of the code using a variety of cache configurations, processor/memory interface models and memory latency and bandwidth characteristics. In each case, the compiler is supplied with an accurate parameterization of the target memory system. Data on the speedups alluded to above is found in this chapter.

Chapter 7 draws conclusions based on this work.

### Chapter 2

### Motivation and Background

### 2.1. The Memory Latency Problem

Computer architecture and system design is a field which is partially driven by economics, and justifiably so. A frequently stated goal of system designers is to provide a system which maximizes performance subject to cost constraints or minimizes cost subject to performance constraints. Despite a general lack of agreement about precisely how to measure either cost or performance, economics often motivates the use of high-bandwidth, high-latency components in various subsystems within computers. High bandwidth is important since bandwidth imposes a hard upper bound on the performance of machines. High bandwidth can be achieved by repeatedly using a single low-latency component or concurrently using multiple, high-latency components. The latter solution may be more economical when it is applicable.

High bandwidth represents potential, but not necessarily actual performance, when it is achieved at high latency. Insofar as a computation is forced to wait for a data item from a high-latency component and this results in idle bandwidth, high bandwidth has not resulted in high performance. Significant effort in the computer research community is being applied to various incarnations of the problem of efficient use of high-bandwidth, high-latency computational resources and software latency tolerance can be classified as part of this effort.

The latency problem specifically addressed is that of memory latency for data accesses, latency associated with movement of data within the memory hierarchy of machines. We focus on uniprocessors with a memory hierarchy consisting of a single cache and an underlying main memory although latencies in memory systems with more caching levels or in multiprocessor systems should to some extent yield to a similar approach.

Latency for memory accesses associated with data are specifically addressed, as opposed to instruction accesses. Instructions show noticably higher spatial locality than data and sometimes higher temporal locality as well. If one measures spatial locality as the change in cache hit rate as a function of cache block size, data in [49] illustrates the heightened spatial locality associated with instructions. Enhanced spatial locality behavior for instructions makes them more amenable to various hardware prefetching mechanisms. Data latency tolerance is a harder problem.

With regard to data memory latency, one might ask a variety of questions.

- 1. Is there a memory latency problem? Under what situations does memory latency limit computational performance? To what extent does memory latency limit the achievable memory bandwidth of current and future machines?

- 2. Can high memory latencies be masked by overlap with other concurrent activity in systems which process miss transactions sequentially?

3. Can high latencies be masked by overlap with concurrent activity in systems which can concurrently process multiple miss transactions?

The first questions above will be answered within this chapter. The remainder of the thesis addresses the latter two questions. In order to assess the first question above, one can examine the relative changes in performance of processors and memory over time.

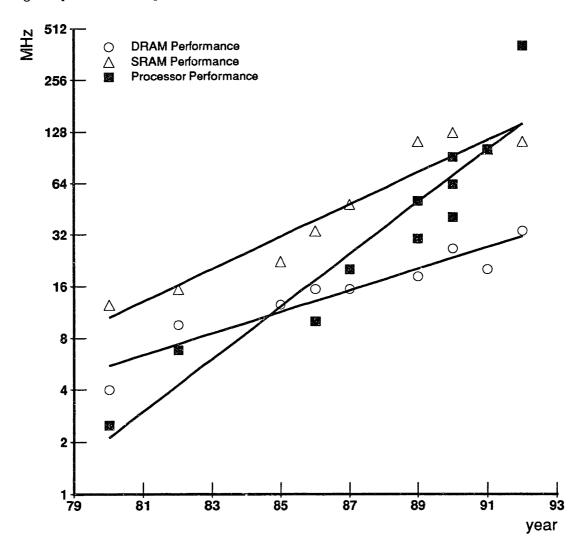

Figure 2-1: Component Performance vs. Time

Figure 2-1 shows the performance as a function of time of a sample of processor and memory components. The chart includes data for processors and CMOS DRAM and SRAM components. In order to get a uniform timebase, data is collected for each type of component from ISSCC proceedings [22]. Processor performance is measured as the bandwidth at which the processor can compute integer add instructions. Memory performance is measured as the inverse of the access time, address access time for SRAMs and row access time for DRAMs. The maximum density component reported each year is used since these components have the lowest per bit cost in production. Because of its source, data is based on research components rather than commercial availability. Bias produced by differing times for components to move from research into the commercial marketplace may skew

the results slightly in comparison to a graph based on performance and availability of commercial products but trends in the relative performance of components should not reflect this bias. The graph shows a significant relative increase in processor performance in comparison to memory components over the period examined. Based on this trend, is is evident that either now or in the future, there will be a memory latency problem.

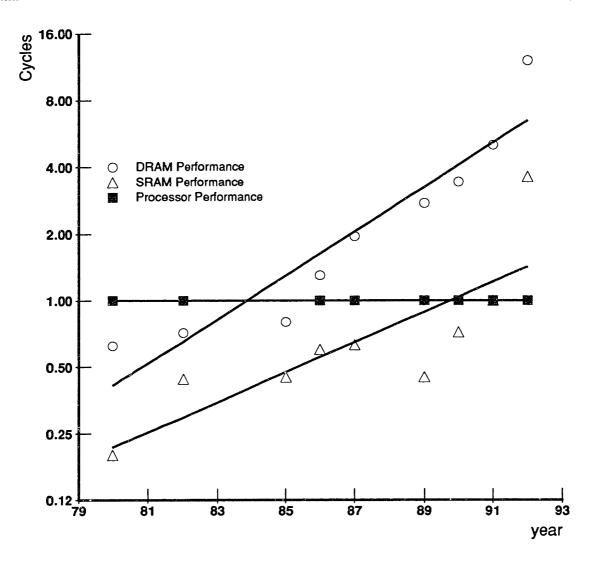

Figure 2-2 presents the same data in another way. In this graph all performance has been normalized to a time unit of processor cycles, the inverse of the integer add bandwidth of the fastest processor in a given year. Where the other graph showed inverse latencies, this graph shows relative latencies. DRAM and SRAM performance numbers indicate the relative latency of these components as measured in processor cycles. In this data it is even more evident that memory components, particularly DRAMs, are losing ground relative to processor performance. Since the scale is logarithmic, an exponential increase in relative latencies is indicated. The numbers in this graph do not reflect any time associated with bus access or address translation time. This further increases relative latency.

Figure 2-2: Normalized Latencies vs. Time

#### 2.1.1 Processors

Recent advances in processor technology have led to a large drop in computational latencies and a corresponding increase in bandwidth. Measured in terms of potential instructions or elementary computations per unit time, computational bandwidths have increased dramatically. Furthermore, architectural changes toward concurrent instruction issue have led to increases in computational bandwidth beyond that associated with decreased clock period. The result of these trends is that computational bandwidth costs, measured as dollars per Mips, have dropped.

The RISC trend in processor architecture [17] [42] which has occurred over the last ten to fifteen years can be attributed with producing significant computational latency and bandwidth improvements by the simple technique of allowing higher clock speeds. RISCs are characterized by load/store instruction sets, isolating interactions with external memory to a small set of instructions which initiate either read or write transactions. Computations are performed on data buffered in fast registers. The repertoire of elementary computational operations directly provided by these processors is limited to those which are both heavily used and simply implemented. This economy of functionality has produced simpler, less cluttered processors, allowing for clock speed improvements. Pipeline concurrency has been heavily employed, exploiting parallelism between instruction fetching, decoding and computation, inherent in the interpretation process performed by processors. This type of processor architecture has leveraged advances in semiconductor technology, resulting in the hundred-fold increase in bandwidth noted in Figure 2-1 from 1-2 Mips 10 years ago to hundreds of Mips today and potentially thousands of Mips in the near future.

A more specialized trend which has produced additional bandwidth increases above and beyond those which accrue from simple clock rate increases is the advent of superscalar machines. A byproduct of the RISC architectural trend has been the use of specialized dedicated hardware resources for various types of functionality; thus a RISC processor might have a data unit which provides for external data transactions, an integer computation unit, floating point computation units, etc. Superscalar machines provide a means for exploiting the potential concurrency between these independent, often pipelined, functional units, either explicitly through instructions sets which specify multiple actions with a single instruction or implicitly through the simultaneous issue of multiple instructions. The DEC alpha [9], at the far right corner of Figure 2-1, is a superscalar processor.

#### 2.1.2 Memory

Adequate memory systems must be provided if the low-cost computational bandwidth discussed above is to be used. Computer system architects, particularly those designing high clock speed systems, have properly turned to hierarchical memory systems to provide the memory bandwidth and latency characteristics required. Hierarchical memory systems incorporate two or more heterogeneous levels of storage with differing speeds, sizes and relative costs. At one end of the hierarchy is a modest amount of relatively expensive, low-latency, high-bandwidth storage, often managed as a cache. Further levels increase in size, but have increasing latencies and lower per bit costs. Hierarchical memory systems exploit locality in computations to leverage the limited quantities of low-latency, high-cost storage. Caches provide a hardware mechanism for dynamically exploiting locality. Interleaved memory describes a mechanism for providing memory systems with high bandwidths in comparison to their latencies. These systems exploit potential concurrency which often exists in memories constructed from many individual components, forming a high-bandwidth pipeline from multiple, high-latency components. Merging these two techniques potentially represents an attractive option for building memory systems with low, average latency and high bandwidth for processing miss transactions.

#### 2.1.3 Demand-Fetched Caching

Caches store a dynamic collection of recently used data, using hardware to maintain a dynamic mapping between cache locations and aliased locations at lower levels of the storage hierarchy.

Caches typically use a demand fetching policy in acquiring their collection of data. Under this policy, if a non-resident datum is needed during a computation, the value is fetched from high latency storage and added to the collection, replacing some other value.

Demand fetching results in a multimodal distribution of service times for memory transactions. Transactions for which the desired storage location is dynamically aliased by the cache (i.e. hits) are satisfied quickly, exhibiting the storage latency of the cache. Transactions which miss the cache exhibit the storage latency of underlying storage levels. Average memory response times depend on the sum of the product of the service times associated with satisfying requests at each level of the hierarchy and the relative frequency at which those levels service requests. Two-level systems are characterized by a hit rate, measuring the fraction of requests satisfied by a cache, and by hit and miss times corresponding to the times to service transactions by the cache and by the underlying storage.

Inherent in typical, demand-fetched cache memory systems is a necessity to pay the latency penalty associated with cache misses. As the relative latency of low-level storage in comparison to computational speed increases, time spent waiting for misses to be processed accounts for a larger fraction of program time. Demand-fetched caches rely on high hit rates to amortize miss costs. There is a class of applications, characterized by very large data sets, for which even rather large caches do not exhibit high hit rates. Furthermore, as the relative penalties of misses increase, ever higher hit rates are required to amortize these penalties. Higher hit rates require larger, more expensive caches or further levels of cache hierarchy. Latency tolerance techniques exploiting concurrency offer a potential escape from this cycle. A goal of our research is to measure the extent to which high latency memory transactions, corresponding to cache misses in a cache system, can be tolerated through the software-based exploitation of computational parallelism.

#### 2.1.4 Interleaved Memory Pipelines

Interleaving is a mechanism for using a set of high-latency storage components to construct a pipelined, high-bandwidth memory system. The components are organized into a set of banks. A high-bandwidth interface capable of supporting multiple pending transactions is provided between the processor and memory system. Transactions are initiated without waiting for the completion of prior transactions if they can be serviced by a bank not required by any pending transaction. In an interleaved system, a unit change in address results in a change of bank; thus for a typical N-way interleaved system, all addresses held by a bank are equal modulo N. This arrangement exploits spatial locality, the propensity for values adjacent in address space to be used together, although it is also somewhat effective under random transactions. Structured, transaction patterns with strides which are a divisor or factor of N result in overuse of banks and do not fully utilize the potential bandwidth of the interleaved memory system.

Large storage systems, consisting of many identical components, can be structured in an interleaved fashion. This has some impact on the medium connecting the storage and processor since transactions from multiple banks must be multiplexed over this channel, but it allows the use of unused bandwidth existent in many current systems. Further opportunities for pipelining exist within storage devices and even within the wires used for connecting components. [54] discusses a design for pipelined DRAMs to provide high-bandwidth, high-latency special purpose storage in supercomputers. [45] describes a new DRAM interface technology utilizing narrow datapaths at very high clock frequencies to achieve high bandwidth at relatively high latency.

An additional important source of increased bandwidth is the simultaneous use of multiple layers in hierarchical memory systems. Increases in latencies associated with data transfer and storage, while decreasing in absolute terms, seem unavoidable in relative terms compared with computational latency. Relative bandwidths, in contrast, can potentially retain more parity. Combining caching with some form of high-latency, high-bandwidth underlying memory is an attractive option for implementing economical, high-performance memory systems. Unfortunately, a variety of limitations in typical cache-based systems primarily associated with the processor/memory interface, coupled

with models for code generation which are not cognizant of memory latency, conspire to make this difficult.

#### 2.1.5 Memory Interface Issues

Memory interfaces couple processors to memory systems, supporting a series of transactions consisting of requests and replies. These interfaces provide needed synchronization and flow control mechanisms. Required synchronization functionality includes both a mechanism for matching replies with their requests and a mechanism for propagating data availability and transaction completion information to the processor. Flow control ensures that the processor does not produce more requests than the memory system can service. Synchronization, matching and flow control mechanisms can be provided either implicitly or explicitly. Many implicit mechanisms cause bandwidth to be directly limited by latency by preventing concurrent transaction processing.

If request and reply matching is achieved implicitly then reply order is highly constrained. Reply ordering can only be dependent on information implicitly available to both sides of the interface, which is limited essentially to the history of prior and pending transactions. The simplest implicit ordering mechanism imposes a limit of a single pending transaction. Reply delivery orders such as FIFO or LIFO are feasible for multiple transaction interfaces. Explicit matching, accomplished by tagging transactions, allows for flexible delivery order at a cost of some additional hardware complexity.

Communication of completion information can similarly be achieved either implicitly or explicitly. Implicit synchronization often takes the form of a hardware enforced upper bound on memory latency in processor virtual time. Transactions are guaranteed to be completed after a given number of processor cycles. Any transactions which would violate this guarantee produce stalls, stopping processor virtual time. A common upper bound used is one, whence transactions not completing in a single cycle produce stalls. Implicit data synchronization also achieves flow control since the number of memory transactions which can be produced before a stall occurs is limited.

Implicit mechanisms for reply matching and data synchronization are largely incompatible with software techniques for achieving concurrency between computation and slow memory transactions. Synchronization achieved by stalling to bound apparent latency at one provides no possibility for software latency tolerance. An interface which allows only a single transaction, avoiding the need for request/reply matching, does not provide any possibility for overlap of several slow transactions or simultaneous fast and slow transactions.

More sophisticated implicit mechanisms can be devised which might be appropriate for a pipelined memory system exhibiting uniform latency behavior. These mechanisms are incompatible with systems consisting of a cache overlaying a pipelined main memory system. If a stall enforced time bound provides synchronization, a dilemma arises in choosing this stall due to the bimodal response time of the memory. If a small bound value is used then high latency transactions unavoidably produce stalls. If a large bound value is used this eliminates the benefit of the cache since data values cannot be safely used until the bound has passed. Choice of a suitable ordering to allow implicit request reply matching is similarly confounding given bimodal response times. If two adjacent requests exhibit the same latency or a slow transaction follows a fast transaction then a FIFO ordering is desirable since the first request completes before the second. If a fast transaction follows a slow transaction, a LIFO ordering allows the latter to bypass the first, but LIFO is not suitable for the other three scenarios.

Interfaces providing explicit synchronization, matching and flow control provide the most flexible basis upon which to build software latency tolerance mechanisms. Explicit synchronization can be achieved through register scoreboarding, while explicit matching can be achieved by appending small tags to transactions and replies, allowing replies to cross the processor memory interface in any order. While scoreboarding is not uncommon in current RISC processors, tagged, multi-transaction, memory interfaces are essentially non-existent, at least in commercial processors.

#### 2.1.6 Memory Latency

A variety of limitations in most current processors prevent more than one memory transaction from occuring at once. This directly couples achievable memory bandwidth to average memory latency. Even based on current technology, memory latency produced stalls can account for a noticable fraction of program runtimes. As relative memory latencies, defined as the ratio of memory latency to the inverse of processing bandwidth, increase with time, the problem will only become worse. In the absence of revolutionary technological changes resulting in large, inexpensive, fast storage components, the memory latency problem will exist.

### 2.2. Hardware Latency Tolerance Mechanisms

A variety of hardware mechanisms exist to exploit either locality or parallelism to tolerate residual latency associated with cache misses. Most of these techniques have been implemented in research or commercial machines. Multilevel caching attempts to extract and exploit further locality in the transaction stream resulting from primary cache misses. Hardware prefetch techniques use speculative concurrency, exploiting parallelism to overlap movement of data blocks with computation. Dynamic rescheduling techniques depart from sequential program order, either reordering instructions within a single thread of program control or between multiple threads, to find instructions which can be executed concurrently with slow memory transactions.

#### 2.2.1 Multilevel Caches

As the relative latency of processors (and thus first-level caches), to main memories increases, adding additional levels of caching between the first-level cache and the main memory seems like a natural solution. If one cache is good, two caches must be better. (Use of multiple, hierarchical caches is different from the use of separate data and instruction caches. Separate data and instruction caching is implicitly assumed everywhere in the thesis). Additional levels of caching are quite likely to improve performance but this improvement must be justifiable when compared with its cost. Caching obeys a well known law of diminishing returns. An increase in cache size does not necessarily result in an equivalent relative increase in performance. This behavior applies to multilevel caches just as it applies to changes in capacity of a single cache.

Consider a two-level cache system composed of two direct-mapped caches with equal block sizes. Such a system conveniently obeys an inclusion property guaranteeing that any block in the smaller, first-level cache is also contained in the larger, second-level cache. Assume that the first-level cache exhibits a miss rate of  $m_1$  and in the absence of the first-level cache, the second-level cache exhibits a miss rate of  $m_2$  for the same workload. Since no value can be present in the first-level cache which is not present in the second-level cache, the second-level cache experiences an equivalent number of misses independent of the existence of the first-level cache. In a system containing both caches, the input stream to the second-level cache consists of misses from the first-level cache. The miss rate exhibited by the second-level cache when the first-level cache is included is thus  $m_2/m_1$ . If  $m_1$  is a small number, 0.1 or 0.01 for instance, the miss rate of the second-level cache is magnified by a factor of 10 or 100, respectively.

The phenomenon discussed above can be viewed in terms of locality. The locality in a stream of addresses produced as misses from a cache is much lower than the locality in the address stream initially applied to the cache. As a consequence of this behavior, second-level caches must be significantly larger than primary caches to have a large impact on residual latency associated with primary cache misses. Large, secondary caches potentially represent a large system cost.

#### 2.2.2 Cache Prefetching

Cache prefetching uses speculative concurrency to attempt to mask latency. Prefetch engines attempt to predict future memory needs using heuristic analysis of current memory transactions. Based on these predictions, the prefetch engine uses apparently idle bandwidth to move potentially useful data into the cache.