# A Network Element Based Fault Tolerant Processor

by

#### Todd A. Abler

Submitted to the

Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degrees of

Master of Science in Electrical Engineering and Computer Science

and

Bachelor of Science in Electrical Science and Engineering

at the

Massachusetts Institute of Technology

May 1988

©Todd A. Abler, 1988

The author hereby grants to M.I.T. permission to reproduce and to distribute copies of this thesis in whole or in part.

| Signature of Auth | 70                                                        |

|-------------------|-----------------------------------------------------------|

| O                 | Department of Electrical Engineering and Computer Science |

|                   | May 6, 198                                                |

| Certified by      | · rusum, eye · ~ veff                                     |

|                   | William J. Dall                                           |

|                   | Thesis Superviso                                          |

| Certified by      |                                                           |

|                   | Richard E. Harpe                                          |

|                   | Charles Star Draper Laborator                             |

| Accepted by       |                                                           |

|                   | Arthur C. Smith                                           |

|                   | Chairman, Departmental Committee on Graduate students     |

GIASEACHUSETTS INSTITUTE OF TECHNOLOGY

JUL 26 1988

LIBRARIES

ARCHIVES

## A Network Element Based Fault Tolerant Processor

by

#### Todd A. Abler

Submitted to the Department of Electrical Engineering and Computer Science on May 6, 1988 in partial fulfillment of the requirements for the degrees of Master of Science and Bachelor of Science

## **Abstract**

Fault tolerant computer architectures have typically increased reliability at the cost of performance. An architecture is proposed herein which satisfies the requirements for Byzantine failure resilience in an efficient manner, such that high reliability can be obtained at a higher performance level than that previously achieved. The architecture is based on a network element (NE) which provides a solution to the synchronization, communication and redundancy management requirements for malicious failure resilience. The NE is relatively compact and efficient, substantially reducing the performance cost of implementing fault tolerance.

Thesis Supervisor: William J. Dally

Title: Professor of Electrical Engineering

## Acknowledgments

This work was made possible by the expertise and support of the staff of the Systems Architecture Division of the Charles Stark Draper Laboratory. In particular, special thanks must be extended to Jay Lala, Richard Harper, Stuart Adams, and Steven Friend who have all contributed significantly to the development of this thesis. Additionally, I would like to thank Ross Dettmer for his aid in implementing and evaluating the NEFTP. Finally, I thank my thesis advisor William Dally for his assistance and direction.

This work was done at the Charles Stark Draper Laboratory under an internal research and development grant.

Publication of this report does not constitute approval by the Draper Laboratory of the findings or conclusions contained herein. It is published for the exchange and stimulation of ideas.

I hereby assign my copyright of this thesis to the Charles Stark Draper Laboratory, Inc., Cambridge, Massachusetts.

Todd A. Abler

Charles Stark Draper Laboratory hereby grants permission to the Massachusetts Institute of Technology to reproduce and to distribute this thesis in whole or in part.

## Contents

| 1 | Inti                         | roduct | ion                                                       | 10 |  |  |

|---|------------------------------|--------|-----------------------------------------------------------|----|--|--|

|   | 1.1                          | Proble | em Statement                                              | 10 |  |  |

|   | 1.2                          | Objec  | tive                                                      | 10 |  |  |

|   | 1.3                          | Appro  | oach                                                      | 10 |  |  |

| 2 | Fault Tolerance Fundamentals |        |                                                           | 12 |  |  |

|   | 2.1                          | Quant  | tification of a System's Fault Tolerance                  | 13 |  |  |

|   | 2.2                          | Motiv  | ation for Fault Tolerant Computing                        | 13 |  |  |

|   | 2.3                          | Two I  | Fundamental Approaches to Fault Tolerance                 | 14 |  |  |

| 3 | Bvz                          | antine | e Resilience                                              | 16 |  |  |

|   | 3.1                          |        | nal of the Byzantine Resilience Requirements              | 17 |  |  |

|   |                              | 3.1.1  | Synchronization                                           | 17 |  |  |

|   |                              | 3.1.2  | •                                                         | 17 |  |  |

|   |                              | 3.1.3  | Participants and Communication Rounds                     | 18 |  |  |

|   | 3.2                          |        | ntine Resilient Architectures                             | 21 |  |  |

|   |                              | 3.2.1  | The Software Implemented Fault Tolerance Computer (SIFT)  | 24 |  |  |

|   |                              | 3.2.2  |                                                           | 25 |  |  |

|   |                              | 3.2.3  | The Multicomputer Architecture for Fault Tolerance (MAFT) | 28 |  |  |

|   | 3.3                          | The N  | Network Element Based Fault Tolerant Processor (NEFTP)    | 29 |  |  |

| 4 | NE                           | FTP: ' | The Network Element Design                                | 34 |  |  |

| _ | 4.1                          |        |                                                           |    |  |  |

|   | 4.2                          |        | VE Functional Sub-Sections                                | 35 |  |  |

|   |                              | 4.2.1  |                                                           | 36 |  |  |

|   |                              | 4.2.2  | •                                                         | 41 |  |  |

|   |                              | 4.2.3  |                                                           | 48 |  |  |

|   |                              | 4.2.4  | The NE Fault Tolerant Clock                               | 49 |  |  |

|   |                              | 4.2.5  | The NE Scoreboard                                         | 56 |  |  |

|   |                              | 4.2.6  | The NE Global Controller                                  |    |  |  |

|   | 4.3                          | Status | s of The NE Prototype                                     |    |  |  |

| 5 | Eva                          | luatio | n of The NEFTP                                            | 68 |  |  |

|   | 5.1                          | Reliab | oility Analysis                                           | 68 |  |  |

|   |                              | 5.1.1  |                                                           | 68 |  |  |

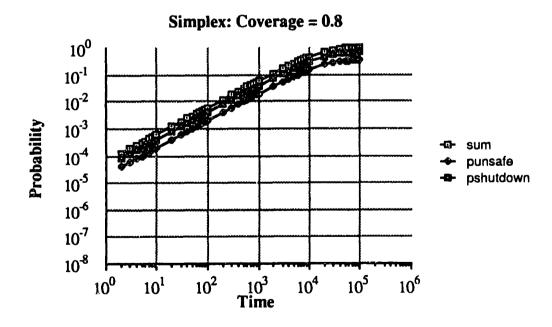

|   |                              | 5.1.2  | Simplex System Reliability Analysis                       | 70 |  |  |

|   |                              | 5.1.3  | NEFTP Reliability Analysis                                | 73 |  |  |

|   | 5.2                          |        | mance Evaluation                                          | 81 |  |  |

|              | 5.3        | 5.2.1<br>NEFT | - J                                              | 83<br>89 |

|--------------|------------|---------------|--------------------------------------------------|----------|

| 6            | Con        | clusio        | ns and Recommendations                           | 90       |

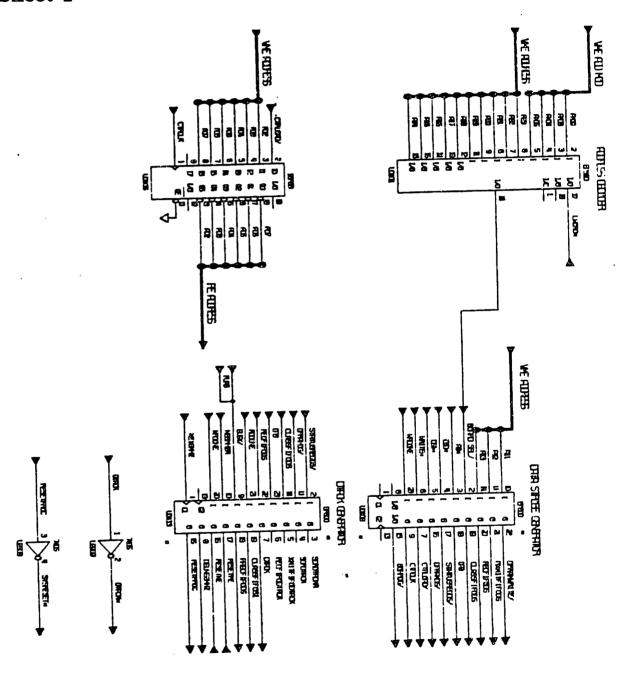

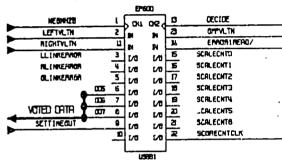

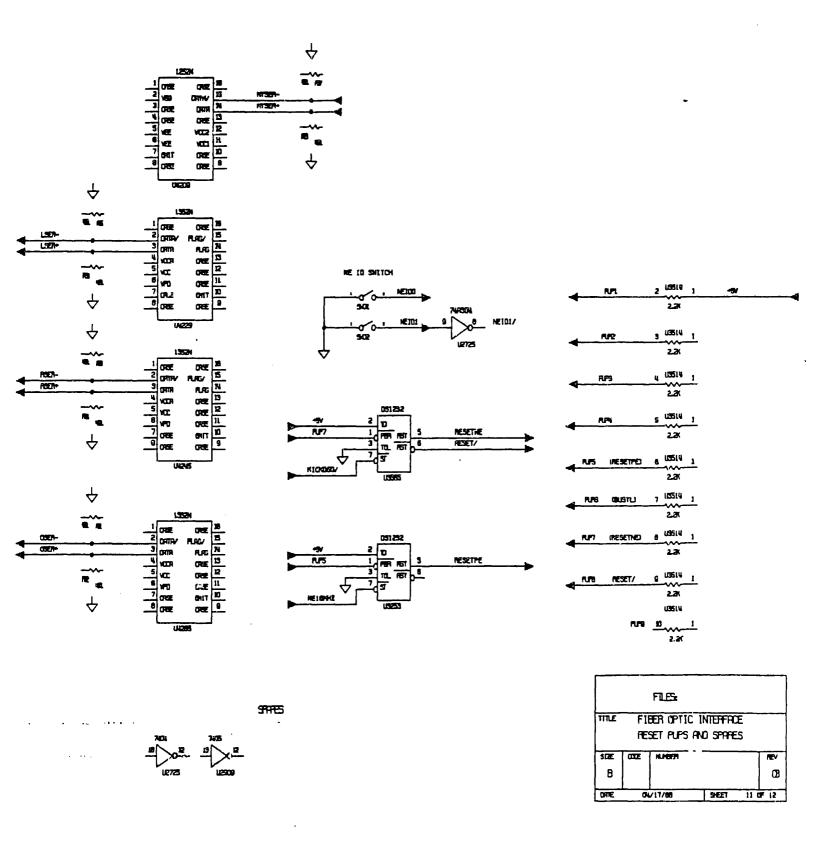

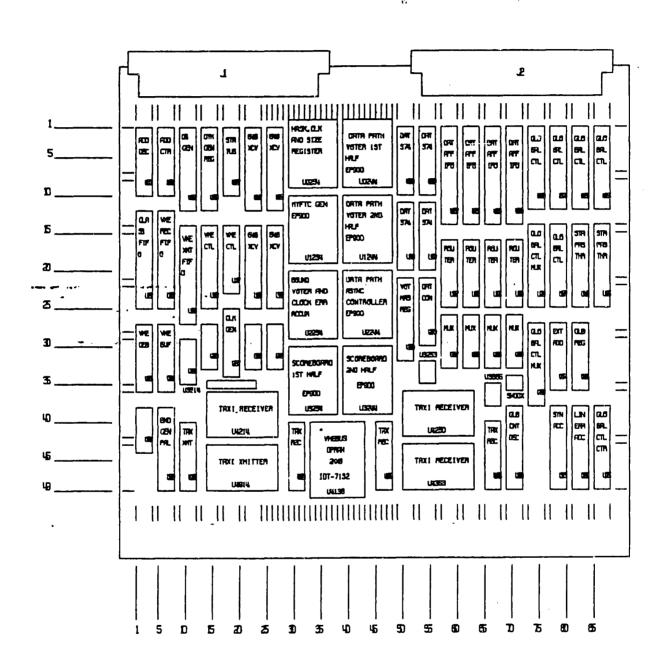

| $\mathbf{A}$ | NE         | Schen         | natics                                           | 94       |

|              | A.1        | Sheet         | 1                                                | 94       |

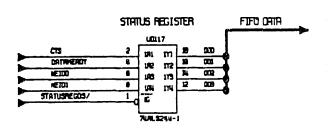

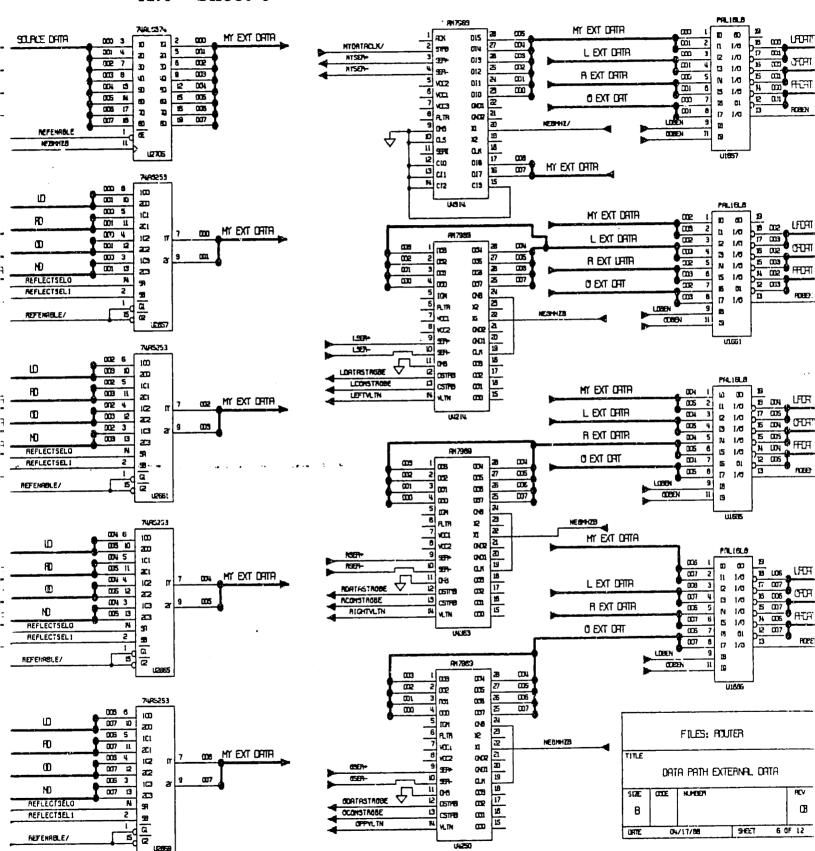

|              | <b>A.2</b> | Sheet         | 2                                                | 95       |

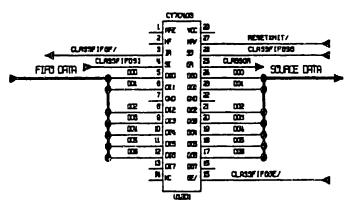

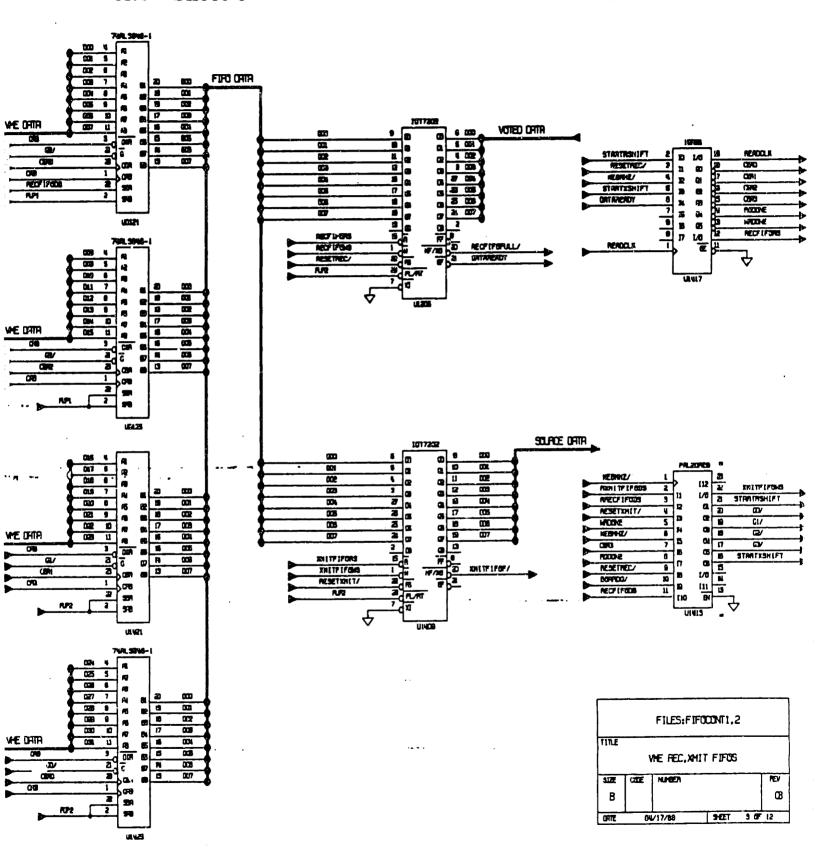

|              | <b>A.3</b> | Sheet         | 3                                                | 96       |

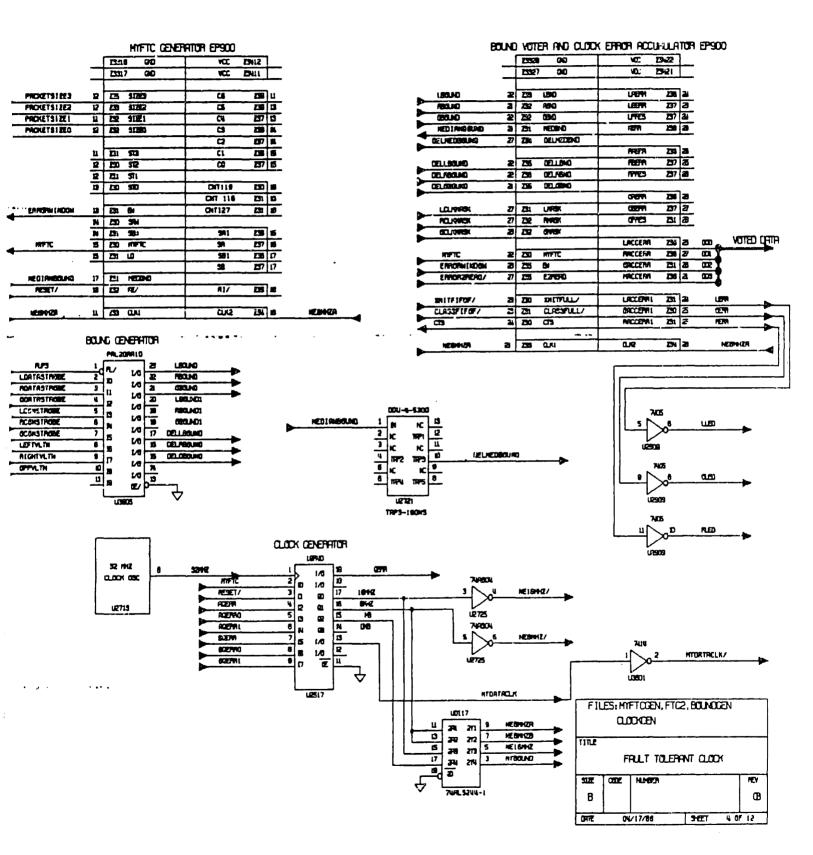

|              | A.4        | Sheet         | 4                                                | 97       |

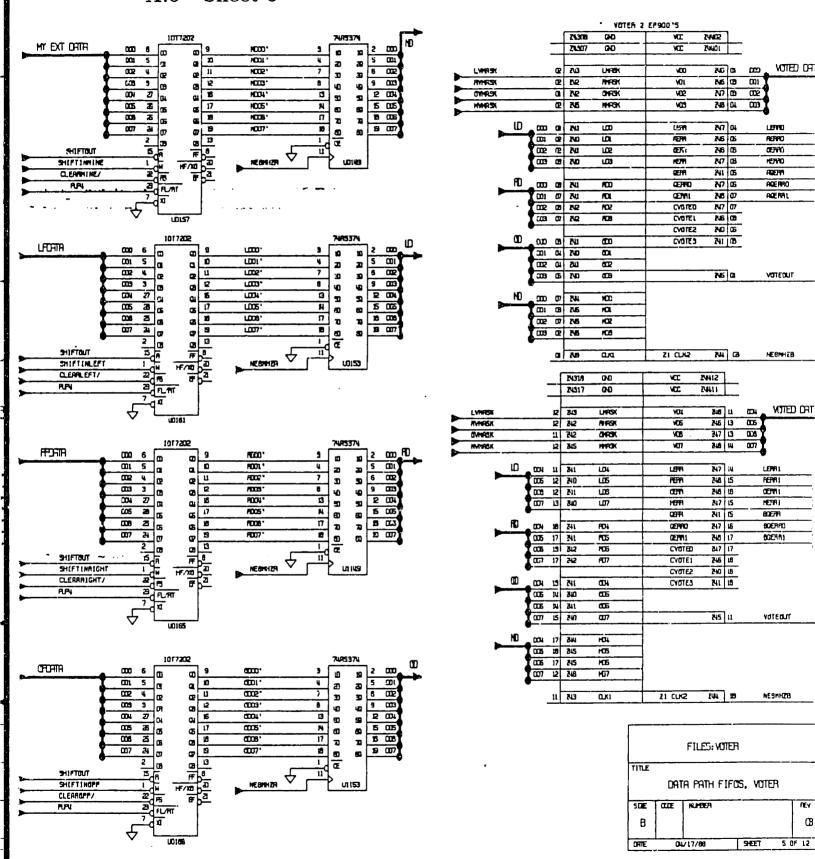

|              | A.5        | Sheet         | 5                                                | 98       |

|              | A.6        | Sheet         | 6                                                | 99       |

|              | A.7        | Sheet         | 7                                                | 100      |

|              | A.8        | Sheet         | • • • • • • • • • • • • • • • • • • • •          | 01       |

|              |            | Sheet         |                                                  | 102      |

|              |            |               | 10                                               |          |

|              |            |               | 11                                               |          |

|              |            |               | 12                                               |          |

|              | A.13       | Sheet         | 13                                               | .06      |

| В            |            | ) Equa        |                                                  | .07      |

|              | B.1        | VME           | Interface                                        |          |

|              |            | B.1.1         | Address Decoding                                 |          |

|              |            | B.1.2         | VME Block Transfer Address Counter               |          |

|              |            | B.1.3         | Data Strobe Generator                            |          |

|              |            | B.1.4         | DTACK Generator                                  |          |

|              |            | B.1.5         |                                                  | 111      |

|              |            | B.1.6         | VME FIFO Control 2                               |          |

|              | <b>B.2</b> |               | Tolerant Clock                                   |          |

|              |            | B.2.1         | MYFTC Generator                                  |          |

|              |            | B.2.2         | Median Bound Voter and Clock Error Accumulator 1 |          |

|              |            | B.2.3         | Bound Generator                                  |          |

|              |            | B.2.4         | System Clock Generator                           |          |

|              | B.3        |               | ${f Paths}$                                      |          |

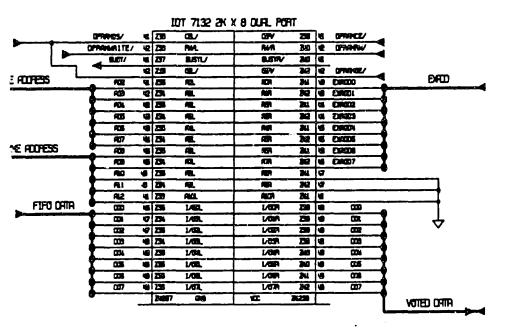

|              |            | B.3.1         | Data Path Voter Slice                            |          |

|              |            | B.3.2         | Debug Router                                     |          |

|              |            | B.3.3         | Synchronous Data Path Controller                 |          |

|              |            | B.3.4         | Asynchronous Data Path Controller                |          |

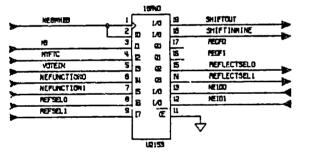

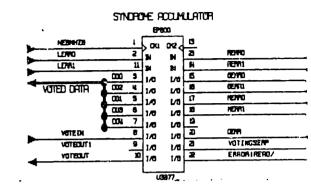

|              |            | B.3.5         | Syndrome Accumulator                             |          |

|              |            | B.3.6         | Link Error Accumulator                           |          |

|              | B.4        |               | $\mathbf{poard}$                                 |          |

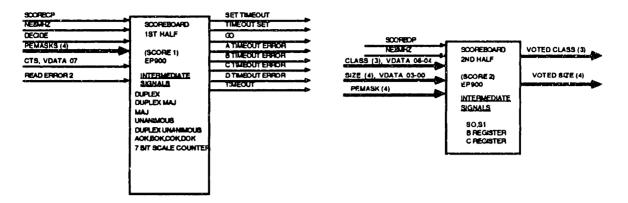

|              |            | B.4.1         | Scoreboard First Half                            |          |

|              |            | B.4.2         | Scoreboard Second Half                           | 34       |

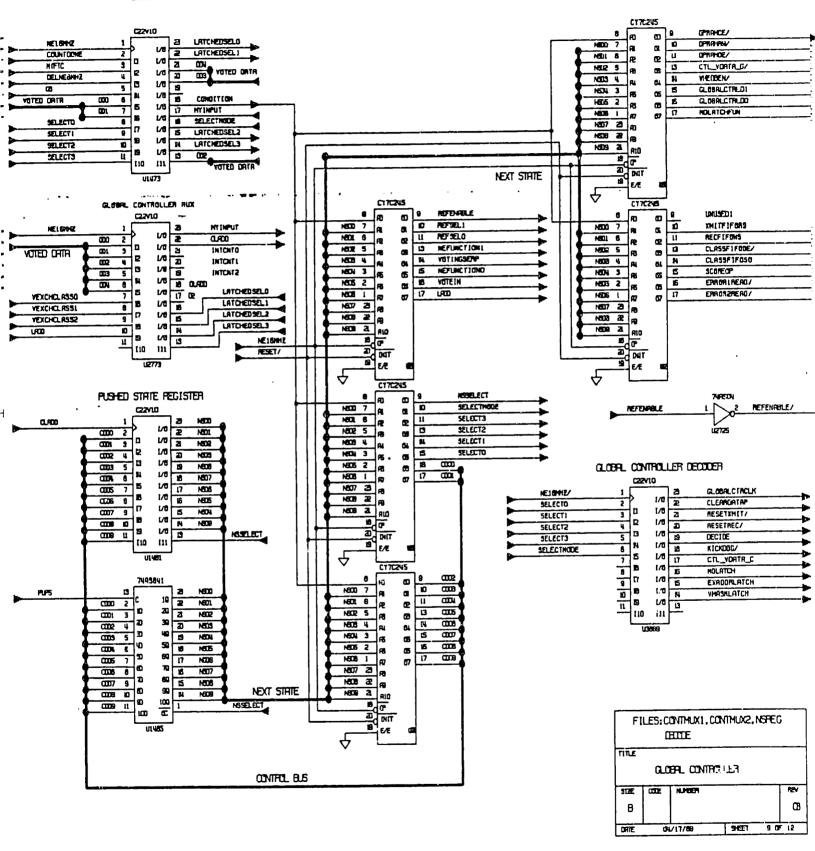

| B.5 | Global | Controller                      |

|-----|--------|---------------------------------|

|     | B.5.1  | Multiplexor First Half          |

|     | B.5.2  | Multiplexor Second Half         |

|     | B.5.3  | Next State Register             |

|     | B.5.4  | Controller Decoder              |

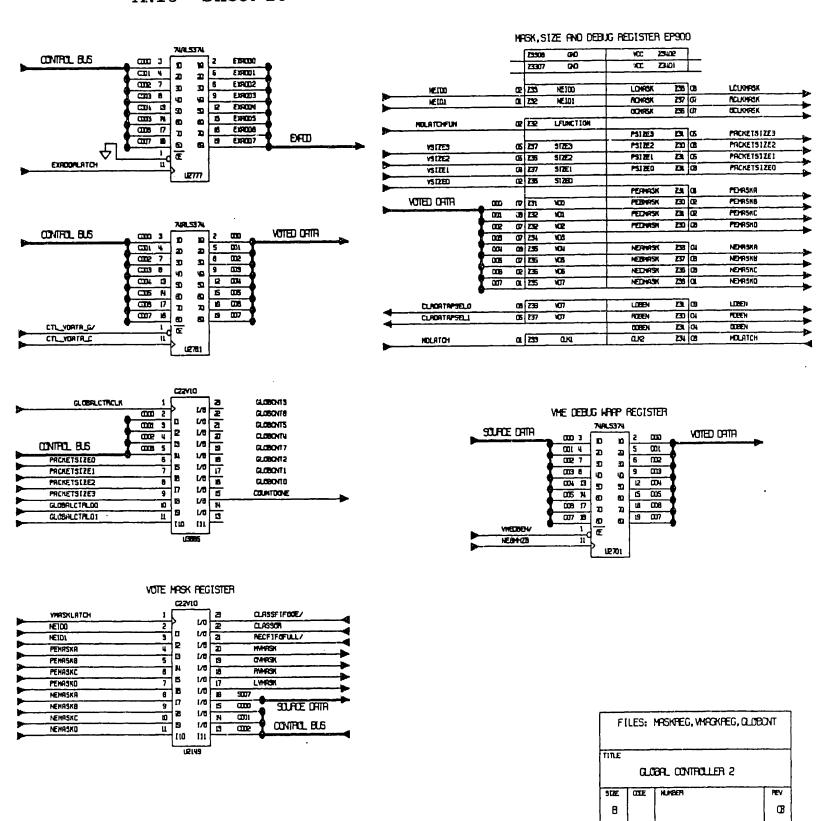

|     | B.5.5  | Mask, Size, and Debug Register  |

|     | B.5.6  | Data Path Voter Mask Register   |

|     | B.5.7  | Global Controller Event Counter |

# List of Figures

| 2.1               | Performability of Selected Architectures        | 13             |

|-------------------|-------------------------------------------------|----------------|

| 3.1<br>3.2<br>3.3 | Self Checking Pair Architecture                 | 18<br>19<br>20 |

| 3.4<br>3.5        | <u>-</u>                                        | 20<br>22       |

| 3.6               | •                                               | 26             |

| 3.7               | · · · · · · · · · · · · · · · · · · ·           | 28             |

| 3.8               |                                                 | 29             |

| 0.0               |                                                 |                |

| 4.1               | · • ·                                           | 34             |

| 4.2               |                                                 | 35             |

| 4.3               | 0                                               | 36             |

| 4.4               | 0 1                                             | 38             |

| 4.5               |                                                 | <b>4</b> C     |

| 4.6               |                                                 | 12             |

| 4.7               | NE Physical and Virtual Identifiers             | 13             |

| 4.8               | Inter-FCR Communication Link Block Diagram      | 18             |

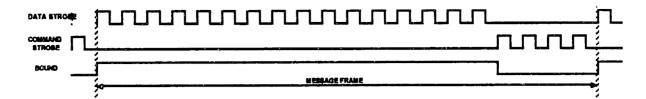

| 4.9               | Basic Message Transmission Frame Signals of FTC | 19             |

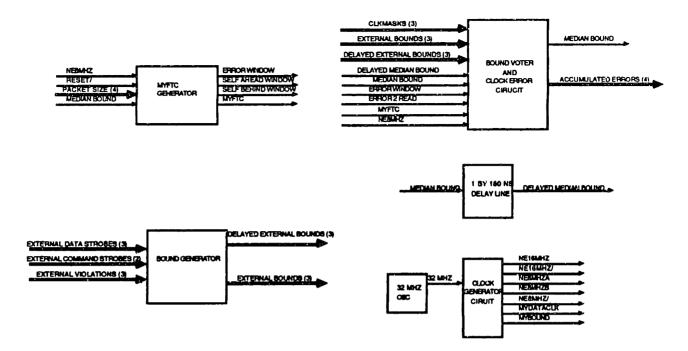

| 4.10              | FTC Block Diagram                               | 50             |

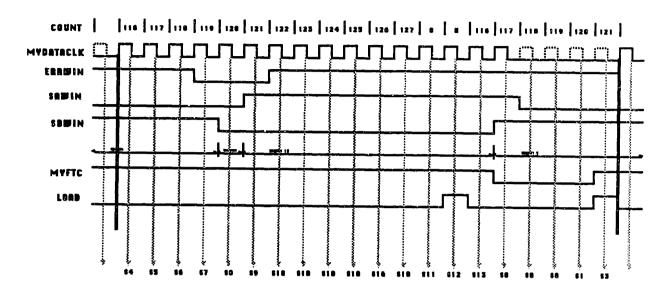

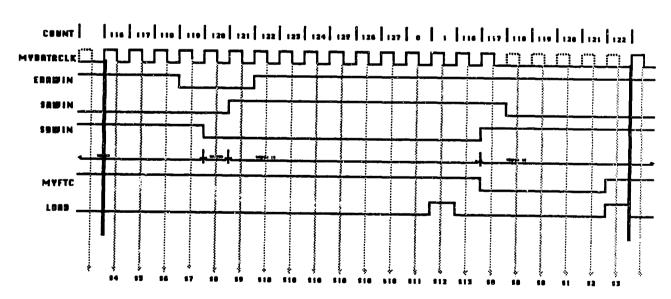

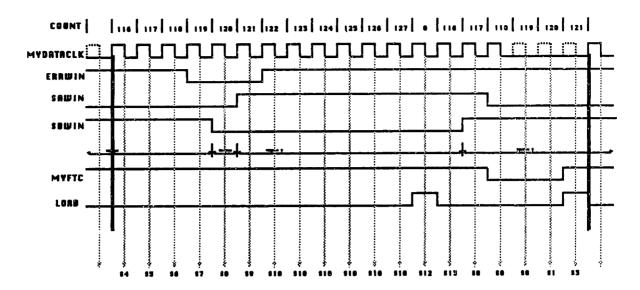

| 4.11              | Self Normal FTC Timing Signals of FTC           | 52             |

|                   |                                                 | 52             |

| 4.13              | Self Behind FTC Timing Signals of FTC           | 53             |

|                   |                                                 | 54             |

|                   |                                                 | 55             |

|                   |                                                 | 6              |

|                   |                                                 | 57             |

|                   |                                                 | 59             |

|                   | •                                               | 59             |

|                   |                                                 | 30             |

|                   |                                                 | 31             |

|                   | <u> </u>                                        | 6              |

|                   |                                                 | 67             |

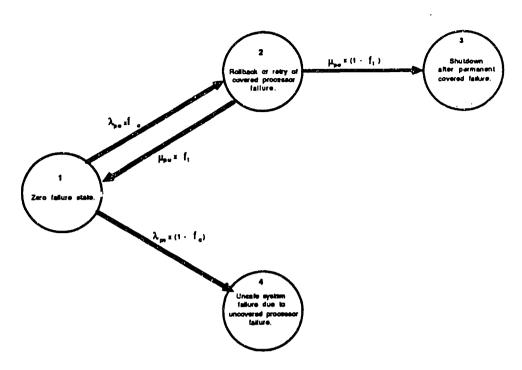

| 5.1               | Simplex Processor Markov Model                  | 71             |

| 5.2               | -                                               | 71             |

| 5.3               |                                                 | 72             |

| 5.4               |                                                 | 72             |

|                   |                                                 |                |

| 5.5  | NEFTP Markov Model: Redundancy Scheme I                                               | 74 |

|------|---------------------------------------------------------------------------------------|----|

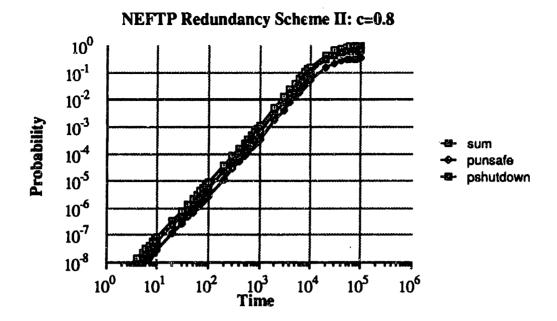

| 5.6  | $p_{unsafe}, p_{shutdown}$ , and $p_{unsafe} + p_{shutdown}$ For NEFTP Redundancy     | 75 |

|      | Scheme I                                                                              |    |

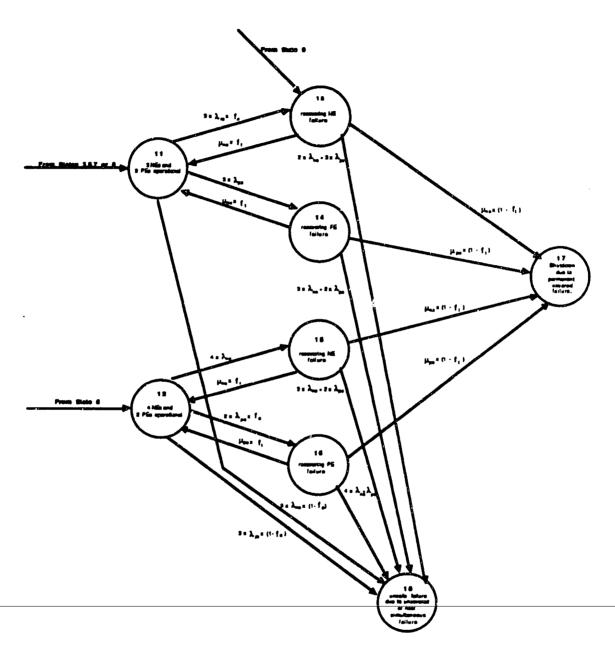

| 5.7  | Addition To NEFTP Markov Model For Redundancy Scheme II                               | 76 |

| 5.8  | $p_{unsafe}, p_{shutdown}, $ and $p_{unsafe} + p_{shutdown}$ For The NEFTP Redundancy |    |

|      | Scheme II                                                                             | 77 |

| 5.9  | Addition to NEFTP Markov Model For Redundancy Scheme III                              | 79 |

| 5.10 | $p_{unsafe}, p_{shutdown}, $ and $p_{unsafe} + p_{shutdown}$ For The NEFTP Redundancy |    |

|      | Scheme III                                                                            | 80 |

| 5.11 | Reliability Analysis Summary                                                          | 81 |

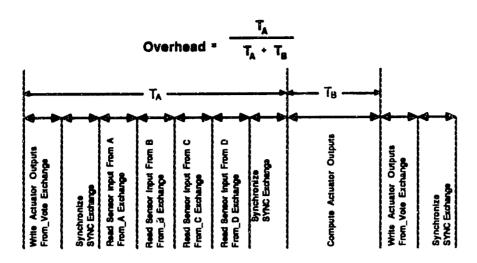

| 5.12 | Typical Control Loop                                                                  | 82 |

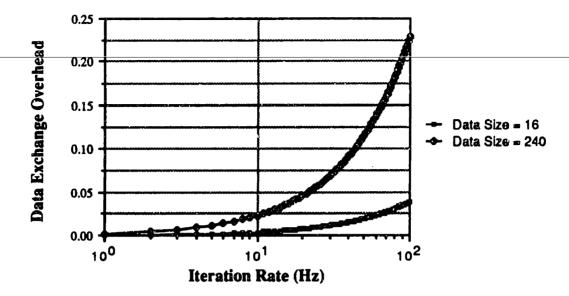

| 5.13 | NE Data Exchange Times and Throughput                                                 | 84 |

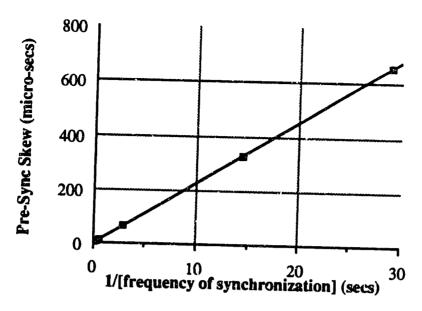

| 5.14 | Processor Pre-Synchronization Skew as a Function of Synchroniza-                      |    |

|      | tion Frequency                                                                        | 85 |

| 5.15 | Fault Tolerance Related Data Exchange Overhead as a Percentage                        |    |

|      | of Control Loop Length                                                                | 86 |

| 5.16 | Breakdown of Fault Tolerance Related Data Exchange Overhead                           |    |

|      | When Using Maximum Packet Size                                                        | 87 |

|      |                                                                                       |    |

# Chapter 1 Introduction

#### 1.1 Problem Statement

A requirement for ultra-reliable computation has generated much research in the area of fault tolerant computing. Several fault tolerant computer architectures have been designed, implemented, and evaluated. These include the following:

- 1. Software Implemented Fault Tolerance (SIFT) computer [Wen78].

- 2. Multi-Computer Architecture for Fault Tolerance (MAFT) [WKF85] [KWFT88].

- 3. Advanced Information Processing system Fault Tolerant Processor (AIPS FTP), and its derivatives [Lal84,Lal86,LAGD86,Smi83].

All such architectures have increased reliability through use of component redundancy. Typically this increased reliability has been accompanied by rigid programming constraints, substantial computational overhead, and/or significant additional hardware.

As will be shown later, many of the constraints imposed by the above architectures are not inherent in the theoretical requirements for failure resilience. The problem, therefore, is to design a fault tolerant processor architecture with a minimum loss of performance and flexibility.

## 1.2 Objective

The primary objective of this thesis is to design and develop a fault tolerant processor which does not unnecessarily constrain the programming model, and which has minimal computational and hardware overhead. Specifically, this involves understanding the necessary and sufficient requirements for failure resilience. An architecture is developed which incorporates these requirements. An implementation of this architecture is designed and fabricated. A secondary objective is to quantitatively illustrate the benefits of this architecture via performance and reliability comparisons with prior fault tolerant processor designs.

## 1.3 Approach

This study begins with a discussion of the basics of fault tolerant computing. Chapter 2 presents some of the background and terminology of fault tolerance.

Some examples motivating the necessity of fault tolerant computing are given. The current state of research in fault tolerant computing demonstrates the existence of two different fundamental approaches. Chapter 2 discusses the two approaches and examines their differences. Only one of the approaches, known as Byzantine failure resilience, is shown to be a viable solution to the problem. Byzantine resilience and its theoretical requirements are discussed in Chapter 3. It is shown how existing architectures, such as those mentioned above have satisfied these requirements; yet in doing so have placed severe, and perhaps unnecessary, constraints on the problem. The Network Element (NE) is introduced as a facility which provides for the requirements of Byzantine failure resilience in an efficient manner. The anticipated advantages of this architecture are suggested. Chapter 4 gives a detailed discription of the Network Element design that has been incorporated into a Network Element based Fault Tolerant Processor (NEFTP). The performance and reliability of the NEFTP is investigated in Chapter 5. This thesis concludes with some discussion of the actual performance and reliability measures of the NEFTP.

## Chapter 2

#### Fault Tolerance Fundamentals

This chapter is presented as an introductory overview of fault tolerance, and as such is not rigorously complete. It is hoped that the information presented herein will be sufficient for the purposes of this thesis. For situations in which this is not the case, more information may be found in the references.

Fault tolerant computing is defined as "the ability to execute specified algorithms regardless of hardware failures, total system flaws or program fallacies [Kim75]." A collective term for "hardware failures, total system flaws or program fallacies" is "faults." As implied by the definition, faults can be of a hardware or software nature. Hardware faults can either be permanent, intermittent or transient [SS82]. A fault may be active, currently manifesting erroneous behaviour in a part of the system, or a fault may be latent, producing no erroneous behavior at the given momment but having the potential to do so in the future.

Fault tolerance is achieved through the use of redundancy such that faults can be detected and corrected prior to the entrance of the aggregate logical machine into an erroneous state, or propagation of errors to the system outputs. This redundancy can be of many forms. Informational redundancy, such as over-specified simultaneous equations and error-correcting codes, can be used to detect and correct faults in a limited manner [Fri86]. However, informational redundancy schemes are difficult to devise to detect and correct ALU faults [SS82]. Hence, informational redundancy is ineffective against total system flaws since it cannot provide total system coverage. Temporal redundancy provides a means of tolerating transient hardware faults by re-executing an instruction stream several times [LS88]. Clearly temporal redundancy cannot tolerate permanent hardware failures. Hardware redundancy allows tolerance of permanent and transient hardware faults which are uncorrelated between the redundant components (correlated hardware faults can affect redundant elements simultaneously, and hence cannot be tolerated if redundant elements are identical). Software redundancy may be employed to tolerate uncorrelated software errors. Design deversity on behalf of redundant components is necessary (though not necessarily sufficient [KLJ85, AK84]) to protect against correlated faults.

Fault tolerant computers can be differentiated in terms of the type of faults tolerated, the definition and level of tolerance, and the architecture (type of redundancy) employed to provide the tolerance. In order to compare the types of fault tolerant computers there must exist some means of quantifying the fault tolerance of a system.

Figure 2.1: Performability of Selected Architectures

#### 2.1 Quantification of a System's Fault Tolerance

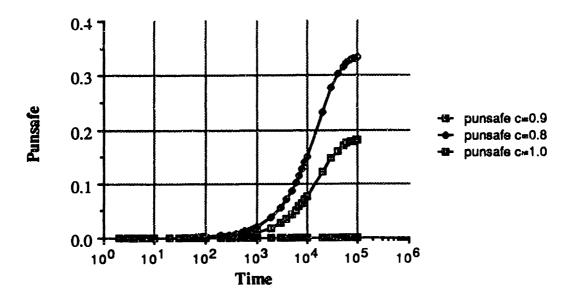

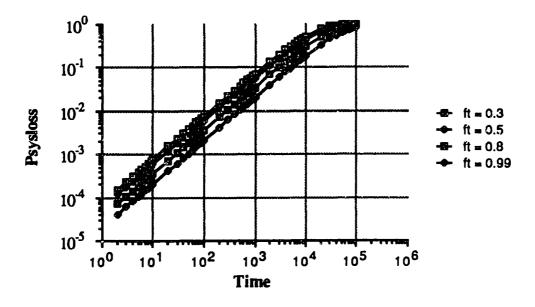

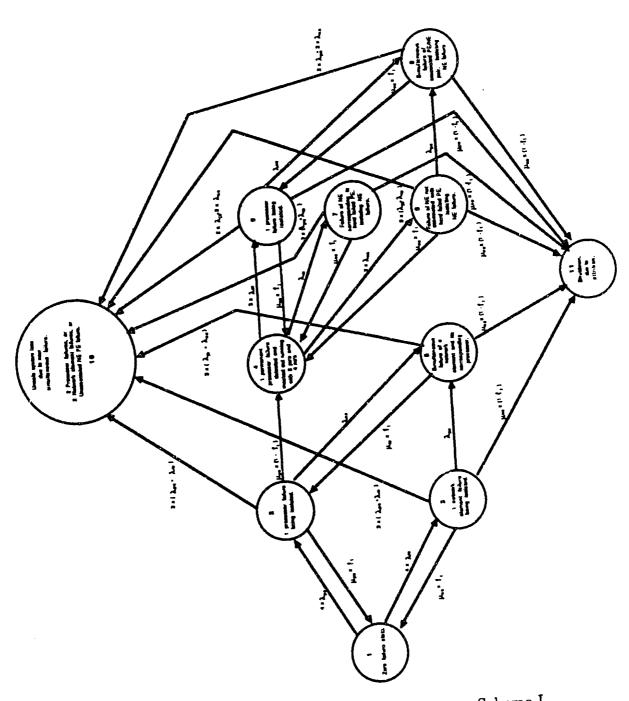

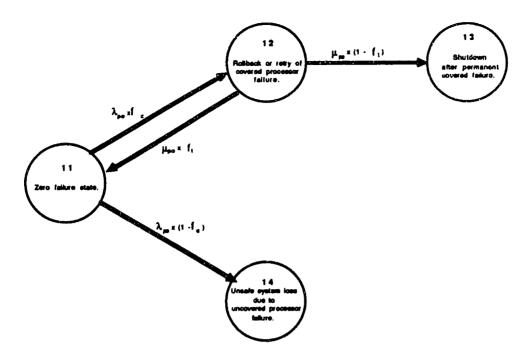

The fault tolerance of a system can be measured in terms of its reliability, availability, and coverage. The reliability of a system is expressed in terms of the probability that it functions correctly for a given duration. The less strict metric availability is the probability that the system will be able to function correctly at a given time (roughly corresponding to the ratio of the system failure rate to system repair time). Coverage is expressed in terms of the probability that the system will function correctly given the occurrence of an arbitrary fault. Recent study has suggested an interesting new metric called performability which is useful as a figure of merit of fault tolerant systems [Har87]. One way to express performability involves mapping systems onto a cartesian coordinate system which has performance (throughput) as the abscissa, and reliability as the ordinate. Figure 2.1 shows the performability of selected systems [Har87].

## 2.2 Motivation for Fault Tolerant Computing

There exist many applications today that require significant computation critical to the success of the task. A fault tolerant system must provide reliability at a level commensurate with the computation's criticality. Less stringent applications, such as electronic banking and investment, may allow for operator intervention to repair

or replace failed components with a finite interruption in service. Some applications, such as telephone swithching services, allow for operator intervention with no interruption in service. An area illustrating stringent requirements is in autonomous and semi-autonomous vehicle control. Here no operator intervention may be possible and the results of a system failure may be catastrophic. The reliability requirements of such a system are typically set at a failure rate  $10^{-7}$  per hour for military applications and  $10^{-10}$  failures per hour for civilian applications, [Bro87,Wen78]. A non-fault tolerant system composed of hundreds of typical VLSI components each having a failure rate of  $10^{-7}$  permanent failures per hour [Gol84], and other failure sources, is incapable of satisfying this reliability requirement. Therefore fault tolerance must be incorporated into computer architectures which perform these applications.

#### 2.3 Two Fundamental Approaches to Fault Tolerance

Neither informational redundancy nor temporal rendundancy can satisfy the reliability requirements mentioned above; this is a direct consequence of the fact that these redundancy schemes are incapable of tolerating failures of any system components with unity coverage. Hence, current efforts in ultra-reliable computing employ hardware redundancy. There currently exist two fundamentally different approaches to providing hardware redundancy for fault tolerance.

The approach taken by much of private industry is to use minimal hardware redundancy in designing systems which provide tolerance of only those failure modes which are predefined as "likely". This approach is ad hoc in nature and thus will be referred to as the ad hoc approach. The ad hoc approach is not based on any theory. It involves performing some failure mode analysis of the target system to determine the likelihood of a priori determined failure modes. Hardware redundancy can then be designed in to provide coverage of those failure modes with a sufficiently high probability of occurrence. System reliability is then related to the sum of the probabilities of the uncovered failure modes. For example, suppose a failure modes analysis of a given system yielded only three likely failure modes a, b, and c with probabilities of occurrence per unit time  $f_a, f_b$ , and  $f_c$  respectively. If unity coverage was provided for these modes, then, purportedly, the probability of system loss per unit time would be no more then  $1 - (f_a + f_b + f_c)$ .

The approach taken by the academic and defense research communities is that sufficient hardware redundancy must be employed to provide tolerance of all failure modes. Tolerance of arbitrary failure modes is known as Byzantine resilience. This is the design philosophy of the NEFTP and of those architectures to which it is compared. A detailed discussion of Byzantine resilience will be given in Chapter 3.

The validity of the ad hoc approach is seriously questioned when considering the assumptions, human biases and impracticalities involved. There are serious problems to validating or certifying such an architecture. To accurately assess the reliability of such a system, lifetime testing is not possible. In other words, to know if the system has a probability of failure of less than  $10^{-9}$  per hour, it is not feasible to build 100 identical systems and test them for 109 hours. Therefore, the only way to arrive at accurate reliability values using this approach would be to enumerate all possible failure modes. Yet digital systems have infinitely many failure modes. Pattern sensitive random access memory (RAM) failures evidence this fact. In fact, the only way to certify and validate a fault tolerant architecture is via analytical modeling coupled with empirical testing. Yet the ad hoc approach is not based on any theory and hence is not amenable to analytical modeling. These are serious problems. In addition to the above problems, most architectures produced by the ad hoc approach provide no coverage for malicious failures. Malicious failures just do not happen (almost). It is extremely foolhardy to dismiss malicious failures by saying that they just do not happen. This is incorrect. In [MG78], an in-flight failure of a non-Byzantine resilient architecture was recorded and attributed to lack of safeguards against malicious failure. Though one cannot measure how likely malicious failures are, one can estimate how unlikely they must be in order that a non-Byzantine fault tolerant computer would successfully complete its application. Such a calculation for a future space application illustrates that malicious processor failures would have to have a likelihood of less than 10<sup>-6</sup> that of other processor failures [Joh88] in order that sufficient reliability could be achieved in an architecture with no safeguards against them.

For these reasons Byzantine resilience can be seen to be the only approach to fault tolerance capable of meeting the reliability needs of life or mission critical applications. In order to provide tolerance to abitrary failure modes, a system must satisfy some stringent theoretical constraints (illustrated in the next chapter). This has typically resulted in architectures which have significantly increased cost and decreased performance compared to their non fault tolerant peers. The NEFTP architecture is anticipated to offer the high reliability of Byzantine resilience with a lower cost and performance penalty.

## Chapter 3

## Byzantine Resilience

The notion of Byzantine resilience derives from the solution of a distributed consensus protocol problem known as the Byzantine Generals Problem [LL82]. The problem scenario is as follows: several generals of the Byzantine army (one or more of whom may be traitors) are camped around an enemy city and can communicate only via messenger; derive a protocol to ensure that all non-traitorous generals agree on a common battle plan. This problem has been well studied, and theoretically demonstrable prerequisites for a solution exist. For a given number of traitor generals, the solution is constrained in the number of participating generals, the number of generals through which a message must be relayed, and to whom each general must relay the message. The prerequisites of a solution to the Byzantine generals problem are stated formally below.

A deterministic consensus protocol which is capable of correctly functioning in the presence of arbitrary behavior on behalf of f participants must meet the following requirements:

- 1. There must be at least 3f + 1 participants [PSL80].

- 2. Each participant must be connected to at least 2f + 1 other participants through unique communication links. [Dol82].

- 3. The protocol must consist of a minimum of f+1 communication rounds among participants [FL82].

- 4. The participants must be synchronized to within a known upper bound [DDS84].

An architecture which meets the above requirements is said to be f-Byzantine Pesilient. Such an architecture is capable of achieving near unity failure coverage.

A participant in the above protocol is known as a fault containment region (FCR). A FCR is a region to which faults are contained to the extent that the probabilities that faults occur in different FCRs are statistically independent. Fault containment is provided by three architectural features:

- physical isolation

- electrical isolation, including independent power

- independent clocking.

Many of the designs that will be discussed in this thesis take great liberties with these architectual guides for sound fault containment region design. It is excusable to the extent that it is merely a convenience for implementing the proof-of-concept prototype. Occasions in which these guidelines are violated in prototype by design decisions that make it impossible to remedy the situation in an actual production version of the machine will merit some discussion.

## 3.1 Rational of the Byzantine Resilience Requirements

This section is included to lend some plausibility to the requirements of Byzantine failure resilience and is in no way intended as proof, formal or otherwise (the references listed by the requirements provide such proof). In doing so, the failure modes of some commercially popular non-Byzantine resilient architectures will be used as counter examples, and the canonical 1-Byzantine resilient architecture will be introduced.

#### 3.1.1 Synchronization

Participating FCR's must be synchronized to within a known and bounded skew. No asynchronous protocol is capable of achieving consensus in the presence of failures because each such protocol has the possibility of non-termination [FLP85]. The rational behind the synchronization constraint is two-fold. First, some temporal bound must be placed on the behavior of a FCR in order that an inert failure in one FCR can be detected. Second, the mechanism used to compare values from participating FCRs must know when valid data has arrived from all non-faulty FCRs.

## 3.1.2 Connectivity

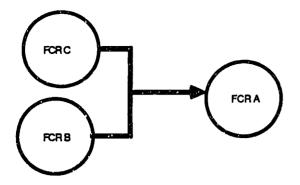

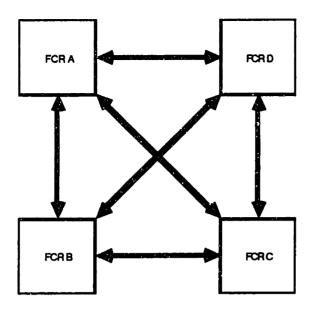

Unique communication links must be used to connect all participating FCRs. Without such links, a non-faulty FCR is not guaranteed of receiving valid information from all other non-faulty FCRs. This prohibits the participants from achieving consensus regardless of the number of communication rounds employed. For example, consider the situtation where two FCRs share a communication link to another FCR (Figure 3.1). It is possible for one of the transmitting FCRs (B) to fail in such a way as to corrupt messages from C to A. In this manner FCRs A and C effectively cannot communicate with one another; hence they will never be able to reach agreement on anything. Assuming for now that 3f + 1 participants are required, then the constraint for unique communication links dictates that there be 2f + 1 such links.

Protocols employing authenticated communication may be able to reduce the connnectivity constraint. Such authentication must ensure that a failure on behalf of a relaying node cannot corrupt message traffic through that node. Furthermore,

Figure 3.1: FCRs Connected via Shared Link

sufficient connectivity must still be provided to withstand the physical failure of f links.

#### 3.1.3 Participants and Communication Rounds

The remaining two requirements can best be motivated by demonstrating the existence of failure modes in architectures which do not satisfy them. Two non-Byzantine resilient architectures will be used for this purpose: the self checking pair, and the triple modular redundancy (TMR) technique. Specifically, these architectures will be shown to be incapable of achieving consensus in the presence of arbitrary failures, whereas Byzantine resilient architectures are guaranteed to be able to achieve consensus. Consensus of a singly sourced input is known as input data consistency. Input data consistency necessitates the properties of agreement and validity. Agreement means that all non-faulty FCRs will reach agreement on the input value. Validity means that if the FCR which sources the input data is non-faulty, then all non-faulty FCRs will agree on the value actual sent by the source. Consensus of commonly sourced output is known as output consensus.

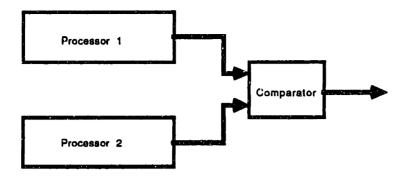

A typical self checking pair architecture (Figure 3.2) consists of two processors with a comparator attached to their outputs for output data comparison. Such an architecture clearly does not meet the requirements for minimal (f = 1) Byzantine resilience. There exists only two FCRs (at most three, if the comparator resides in its own FCR), when four are required. The requirement for number of participating FCRs will henceforth be known as the cardinality requirement. Similarly, this architecture does not satisfy the connectivity requirement. The two channels of a duplex cannot satisfy the property of agreement and hence cannot satisfy validity as well. This is a result of the Two Generals Problem [Gra79] which demonstrates that two generals who are isolated and initially undecided cannot reach consensus on a battle plan via communication through unreliable messangers. It can be shown that in  $\omega$  der that consensus be reached at a given point in time, the generals must have been in agreement initially. An additional problem of this duplex architecture is that it is not capable of consensus of outputs, hence it is not fault masking. In the

Figure 3.2: Self Checking Pair Architecture

Figure 3.3: TMR Architecture

presence of a fault the comparator signals the discrepancy seen on its inputs; yet valid output is not assured because the comparator has no way of knowing which input is correct. Furthermore the comparator is a single point of failure; therefore, even if the comparator had some reasonable method of determining which FCR is correct, the comparator itself could fail and generate incorrect output. The reliability of the comparator is obviously an upper bound of the system reliability.

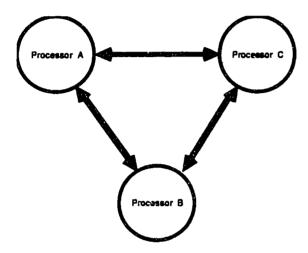

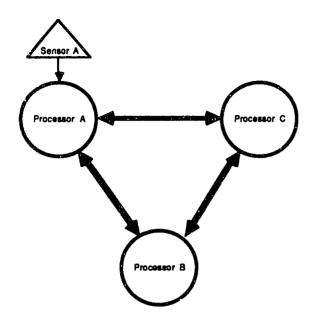

The architecture used in the TMR technique consists of three inter-connected processing sites (Figure 3.3). This architecture does not satisfy the cardinality and connectivity requirements of minimal Byzantine failure resilience. This renders it incapable of acheiving input data consistency. A TMR architecture with a simplex sensor (Figure 3.4) is used to illustrate the input consistency protocol in two scenarios.

Assume processor A hosts a simplex sensor, and the value of this sensor  $(x; x \in (0,1))$  needs to be distributed. In the first scenario processor A is faulty. An initial round of communication takes place and A sends a 0 to processor B and a 1 to processor C. Another round of communication is required in order that B tell C and A what A told it, and that C tell B and A what A told it. During this second

Figure 3.4: TMR Architecture with Simplex Sensor

round A does not source any data, because B and C have already heard what A had to say in the first round. At the end of the second communication round A, B and C have all the information that they can learn about the triad's status, hence no further communication rounds are required. At the end of the second communication round A, B and C both have a copy of the data set (0,1). Both B and C 'vote' this data set according to the following function

$$f(x_1, x_2) = x_1 \vee x_2$$

and arrive at the consistent result 1. The requirements for Byzantine failure resilience do not put any constraints on what happens in the faulty FCR A. The property of agreement of non-faulty FCRs is satisfied. Validity is not required since it is the source processor that is failed. This scenario evidences how an input consistency protocol would work for a TMR architecture. However, a second example illustrates the failings of this architecture.

The second scenario is the same as the first except that the failed processor is B, and that the actual sensor input is fixed as 0. The first exchange round takes place and A sends a 0 to B and C. The second round takes place and B sends C a 1 and A a 0, while C sends A and B both a 0. At the end of the second round the two non-faulty FCRs (A and C) have different data sets. A has the data set (0,0) while C has the data set (0,1). Applying these data sets to the voting function given above, A and C arrive at different results. Hence the properties of agreement and validity are violated. This is a disastrous problem. The non-faulty FCRs do not have a consistent view of the system status and subsequent computation in the two will therefore diverge. Furthermore the failed FCR B may actually recover the

valid input value causing the system as a whole to view FCR C as the source of the failure. An incorrect failure diagnosis has equally catastrophic ramifications for the system. This illustrates why the TMR architecture is not Byzantine resilient.

It should be pointed out that a cardinality of three would be sufficient for output consensus given input consistency. The output consensus protocol consists of a single communication round in which all FCRs broadcast their output value to all other FCRs. Thus in the presence of an arbitrary single fault all non-faulty FCRs will have a data set of three values of which at most one is incorrect. Hence a majority vote will yield agreement and validity of the output value among all non-faulty FCRs. Since output consensus is achieved in the presence of a single failure the TMR architecture is said to be a Fault Masking Group (FMG). The inherent problem here is that input consistency is not guaranteed. Therefore if an input (which is not guaranteed of being distributed consistently) is used to produce the output, then output consensus is not guaranteed.

The TMR example provides insight into the requirements of Byzantine resilience. The failure of the TMR architecture is in cardinality and connectivity. Two communication rounds are indeed sufficient for input data consistency for a minimal Byzantine resilient architecture. The problem is that at the end of the second round each FCR has only two values, one of which may be incorrect. Replicating sensors does not change this problem any. There will exist some finite skew between the sensor values from each FCR, and thus each must be exchanged through an input consistency protocol. The processors would each perform some mean value selection of their senor value set. As was shown in the example, no single sensor value can be distributed consistently, therefore the set of values is not guaranteed to be distributed consistently. The solution is to add another FCR such that each FCR will have three values at the end of the communication. Since at most one of the values can be incorrect, a majority vote function will guarantee agreement. Hence the 4 FCR requirement for minimal Byzantine resilience. The canonical 1-Byzantine resilient architecture is shown in Figure 3.5. This fourth FCR is not constrained to be a processing site. Only three processing sites are required to provide output consensus in the presence of a single fault. This fourth FCR can be a minimal hardware data exchanger capable of participating in the communication protocol.

## 3.2 Byzantine Resilient Architectures

Several architectures which satisfy the requirements for single Byzantine failure resilience have been designed and implemented. This section will analyze several of them in turn, illustrating how they meet the requirements of 1-Byzantine failure resilience. This discussion will form the foundation for the presentation of the NEFTP architecture. The NEFTP will be shown to have the property of Byzantine failure resilience, though it uses a synchronization scheme uncommon to other fault

Figure 3.5: Canonical 1-Byzantine Resilient Architecture

tolerant processors.

Much of the discussion below will focus on the synchronization schemes employed by the various architectures. The synchronization mechanism of the NEFTP is seen to be the crucial ingredient in the reliability, flexibility, cost and performance benefits which are anticipated. Indeed this is true of all such architectures. The synchronization mechanism directly affects an architecture's performance, reliability and flexibility. To aid this discussion some issues of synchronization and the necessary terminology are discussed here.

Granularity of action is a parameter of synchronization schemes indicating the temporal difference between identical actions on behalf of different participants. Schemes which achieve fine grain synchronization have a small temporal difference among participants. Correspondingly, coarse grain synchronization schemes leave a large temporal difference between participants. Another parameter of synchronization schemes is post-synchronization skew. This refers to the minimum skew that the participants can attain after execution of the synchronization task. Note that post-synchronization skew is a fundamental lower bound on the skew between FCRs. Granularity of action is affected by synchronization frequency - the rate at which synchronizations take place. This is because skew builds up between FCRs, due to the drift of their respective clocks, during the periods between synchronizations. Given a synchronization mechanism, granularity of action can be reduced by synchronizing more frequently. This can be done until synchronizations are taking place continuously, at which point the maximum possible skew will be no less than the post-synchronization skew.

Why does granularity of action matter? As long as the participants are synchronized to within a known and bounded skew, consensus can be achieved. The

catch is that granularity of action directly impacts performance and reliability. The impact on performance is straightforward. The machine can output data no more frequently than the rate at which data can be exchanged and compared. The time required for data comparison cannot be shorter than the maximum possible skew between FCRs, as any FCR must wait until it is guaranteed to have data from all non-faulty FCRs in order to compare redundant copies. The impact of granularity of action on reliability is more subtle, but nonetheless important. In the short run the probability of system loss due to near simultaneous failures of redundant components is linearly proportional to the mean fault latency time plus the time it takes the system to reconfigure around the first fault (denote this sum as  $1/\mu$ ). For a Byzantine resilient system, reconfiguring involves identifying and isolating a failed FCR by masking it out. This rate  $\mu$  cannot be faster than the rate at which outputs from all participating FCRs can be compared. Outputs can be compared no faster than the rate of 1/maximumskew. Hence the granularity of action of the synchronization mechanism directly affects the reliability; a finer granularity increases system reliability.

The choice of synchronization mechanism may also affect the architecture by imposing hardware and/or software constraints. These constraints are important not for implementation flexibility alone; they also impact reliability. An architecture which is free to employ design diversity in both the hardware and software of participating FCRs is arguably less susceptible to common mode design failures, hence more reliable. Design diversity in software may consists of scheduling tasks in different orders on different FCRs, or it may entail coding differently the versions of a task which are run on different FCRs (called *n*-version programming). Design diversity in hardware may consist of using single board computers from different vendors in different FCR's.

Some synchronization mechanisms impose a hardware constraint known as clock determinacy. This means that redundant processing sites must execute an identical number of instructions in a given number of clock cycles. To illustrate the importance of such a constraint, consider that clock determinacy constrains the hardware design of the processor tremendously, especially in light of the fact that commercially available computers are not clock deterministic. Typical problems include devices such as error correcting memories, floating point units, and memory managment units; where a given operation can take a variable number of clock cycles in the presence of a memory fault, overrun, or page fault. The system architect is left to design a clock deterministic processor by forcing worst case scenarios of such operations.

An example of a software constraint generated by the synchronization mechanism is when the applications programmer is required to know the maximum execution time of any task, and ensure that tasks are scheduled such that they ste guaranteed to complete by a given time. The programming model of such a machine is quite more complex than a canonical simplex Von-Nueman machine. Correspond-

ingly the cost of code development is increased. However, this is a constraint that is typically imposed by the real time nature of such systems anyway.

#### 3.2.1 The Software Implemented Fault Tolerance Computer (SIFT)

The SIFT architecture consisted of six processors configured with a point-to-point communication link between each pair of processors. This architecture obviously satisfies the cardinality and connectivity requirements. As will be explained below, the mechanism for synchronization and data comparision (i.e. voting) is provided by software. Aside from the somewhat specialized communication ports, the processors contain no hardware that is specific to fault tolerance.

The SIFT processors are synchronized by executing the synchronization task. Tasks must be allocated to frames, where each frame denotes a specified number of ticks of the local processors clock. Frames are approximately 100ms long, and are divided into 33 sub-frames of 3.2ms duration [PB86]. Each 1.6ms the processor is interrupted and decides whether to schedule a new task.

The synchronization task must be scheduled at the same hardware clock period on each processor. The synchronization task involves a processor broadcasting the value of its local clock to all processors during a set time window. Other windows denote a time for the processor to listen for the clock values broadcast from other participants. Upon receiving each value, the processor reads its local clock and notes the difference between the two. After all time windows have passed, a processor has a set of values representing the deviation of its local clock from all other processor clocks. Each processor uses these values to compute an adjustment to its local clock. A processor adjusts its local clock, and waits to begin the next frame when its local clock reads some a priori determined value.

Synchronization is achieved by this algorithm because fast processors will adjust their clocks such that they wait longer to begin the next frame than nominal processors. Correspondingly, slow processors will wait less time than nominal processors. No computation can be performed in the adjustment periods, as not all participants require the same number of them. This type of synchronization is known as framewise synchronization since adjustment is made at frame boundaries. The implementation of this algorithm has some significant drawbacks. Synchronization occurs with a low frequency (once a frame, or 100ms) due in part to the fact that the synchronization task takes a long time to complete (2ms) [PB86]. Hence this scheme has a large maximum skew, though indeed bounded  $(107\mu s)$  [PB86]. The large possible maximum skew means that SIFT processors are loosely synchronized. The SIFT scheme is thus a coarse grain synchonization scheme. The method used by a SIFT processor to "read" another's clock value involves polling a memory location and waiting for the arrival of the broadcast clock value. This implementation involves some significant "read error"  $(26\mu s)$  [PB86]; the post-synchronization skew is directly related to this quantization error of the synchronization task. Therefore the post-synchronization skew is large.

The loose synchronization of SIFT causes both performance and reliability penalties. Perhaps a more important penalty is the programming constraint imposed by this scheme. The applications programmer must ensure that tasks are allocated to a frame such that the computation of a frame always takes an a priori determined number of sub-frames. This is done to ensure that the synchronization task can be scheduled at the identical sub-frame by each processor. The fault tolerance is not transparent to the applications programmer, making the cost of changing the application of the machine tremendous. This scheme does allow for limited hardware diversity since no constraints are placed on the hardware other than the (rather significant) constraint that it be possible to acheive bit-for-bit consensus of processor outputs. The scheme also allows for limited software diversity. Redundant sites are framewise congruent but they need not be functionally congruent. Funtional congruency means that the processors are not only synchronized as far as the number of tasks executed is concerned, but that the tasks executed also are functionally equivalent. It is possible in SIFT for redundant processors to schedule different functions in a given task slot, which arguably makes it less susceptible to transient errors.

SIFT implements data comparison with the vote task. A processor receives data from other processors in its memory-mapped mail box. The vote task then performs a n-way, (4 < n < 6), bit-for-bit, maskable, majority vote on the redundant copies. The vote task also provides vote error information identifying any processor in disagreement. Such information is necessary to reconfigure around a permanently failed processor. This mechanism has some serious performance problems. A 5-way vote of a single data value (16 bit word) takes  $413\mu s$  [PB86] in the absence of errors. This means that fewer than 8 values can be voted in a sub-frame.

As can be seen here, much of the throughput of a SIFT processor is dedicated to implementing the fault tolerance (1 sub-frame for synchronization, and many for data comparison, per frame). More will be said about this in Chapter 5.

#### 3.2.2 The AIPS Architecture Fault Tolerant Processor (AIPS FTP)

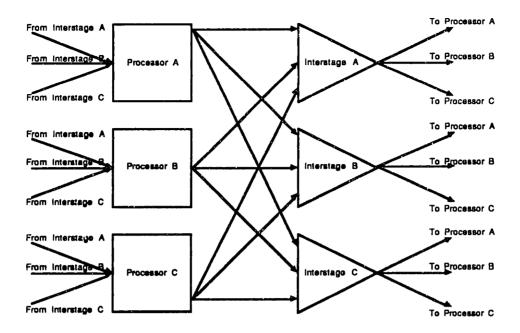

The AIPS FTP takes an approach different than that of SIFT in two fundamental ways. First, a minimally Byzantine resilient configuration of the AIPS FTP consists of three processors and three additional FCRs called interstages (Figure 3.6). An interstage is a minimal hardware implementation of a Byzantine resilience mechanism. The motivation for interstages derives from the previously mentioned fact that only three of the four FCRs required for 1-Byzantine failure resilience need be processors. The three processors are required to form a fault masking group for output data consensus, and the fourth FCR is required for correct input data consistency. Given flexibility as to the implementation of the fourth FCR, he issue of reliability was considered. A minimal data exchanger requires less complex hardware than a processor and therefore is less likely to fail. Choosing an interstage design for the fourth FCR thus increases system reliability. The second fundamen-

Figure 3.6: AIPS Fault Tolerant Processor (Triplex)

tal difference is that the mechanisms for synchronization and data comparison are provided in hardware in an attempt to reduce the overhead of implementing fault tolerance.

Figure 3.6 illustrates how the FTP satisfies the requirements for cardinality and connectivity. For clarification, the two rounds of the input consistency algorithm occur as follows. In the first round, the source processor forwards its value to all interstages. In the second round the interstages send what they received in the first round to each processor. At this point the processors each have three values which can be resolved to one by a 3-way, maskable, bit-for-bit, majority voter circuit. The important observation must be made that in the presence of an arbitrary failure on behalf of any single FCR (processor or interstage), at most one of the three values received by any processor is different from the others. Agreement will thus be reached. Given that the failure was not in the source processor FCR, then at most one of the three values received by any processor will be incorrect. Agreement and validity are thus ensured.

The FTP is synchronized by employing a digital phase lock loop circuit in each processor to generate a clock signal, called FTC - Fault Tolerant Clock, which is locked in phase in all FCRs. The local version of FTC, henceforth called LFTC, is approximately a 888 kHz clock with a 50 percent duty cycle. Each processor forwards its LFTC to the interstages and the interstages relay them (now denoted ILFTC, for Interstage LFTC) back to the processors. Note that additional connectivity is provided for these LFTC and ILFTC signals. Each processor receives three ILFTCs and generates FTC by selecting the median value. The phase of FTC is compared with the phase of LFTC, and the time until the next rising edge

of LFTC is adjusted depending on the deviation. Regardless of the adjustment, all processors receive the same number of processor clock (SYSCLK) ticks during a FTC period. If a FCR is fast it will wait longer till asserting LFTC and slow the frequency of SYSCLK accordingly so that no extra processor clock ticks are incurred. Synchronization is provided in that a fast processor will have its SYSCLK frequency reduced during the adjustment period relative to a nominal processor. Similarly a slow processor will have its SYSCLK frequency increased relative to a nominal processor. The synchronization scheme imposes a constraint of clock determinacy to guarantee that each processor executes the same number of instructions per FTC cycle. This allows data exchanges to simply be controlled by the FTC cycle due to clock determinacy. Hence the data exchange can be controlled by the phases of the FTC.

This is a fine grain synchronization mechanism. Synchronizations occur once each FTC cycle, which corresponds to a rate of 888 kHz. The post-synchronization skew is also very small, approximately 125ns. This translates directly into performance and reliability improvements over SIFT, as will be illustrated in Chapter 5. However, there are some constraints imposed by this scheme. First is clock determinacy, with its ramifications as previously discussed. Second, there exist some software issues. The fault tolerance of the FTP has been made relatively transparent to the user. The programming model is essentially identical to a simplex Von Neuman machine with some data exchange primitives mixed in. However, the clock determinacy constraint precludes the use of n-version programming techniques in the FTP core itself. A solution to the n-version programming problem has been provided via the use of attached processors in each FCR which are not clock deterministic [LA88]. The processors of the FTP achieve what is called framewise functional sycnhrony. They are sychronized to FTC frames, and because they are clock deterministic they are performing the same functional operation in each frame.

The data exchange mechanism is elegantly simple due largely to the clock determinacy constraint. A data exchange is performed by each processor during the same FTC cycle. For simplicity all data exchanges are two rounds. The data exchange is pipelined. A byte transaction between processor and interstage occurs every quarter FTC cycle. Data is forwarded to the interstages on the rising edge of FTC and sent back one quarter FTC cycle later. The duplicate copies received at the processor are compared using a maskable, bit-for-bit, majority vote circuit implemented in a programable logic device. The output of this circuit is guaranteed to be valid and readable by the processor at the following falling edge of FTC. Error information called *voter syndrome*, which indicates which processors, if any, were in disagreement during a vote, is accumulated in error registers which are readable by the processor. The steady state throughput of this mechanism is 16 bits per FTC cycle.

Figure 3.7: MAFT Architecture

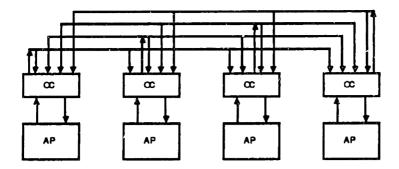

#### 3.2.3 The Multicomputer Architecture for Fault Tolerance (MAFT)

The MAFT architecture is another attempt at removing the overhead of fault tolerance from the application domain in order to increase performance and flexibility. The MAFT solution is to provide two entities per FCR, one handling the overhead of fault tolerance, the other running the application. Each MAFT FCR consists of an operations controller (OC), and an applications processor (AP) [WKF85,KWFT88]. The OC hosts the inter-FCR communication interface, and has two way communication with its AP. The OC is responsible for inter-FCR communication, synchronization, data voting, error detection, task scheduling, and reconfiguration. The AP is responsible for the application task and application dependent peripheral devices. The result is the architecture shown in Figure 3.7.

The MAFT machine consists of "several" (several = 4, Figure 3.7) FCRs fully interconnected via broadcast buses. This configuration satisfies the cardinality and connectivity requirements for 1-Byzantine failure resilience.

MAFT employs a framewise steady state synchronization scheme. A single iteration of this exchange involves broadcasting two versions of a synchronization message. At an a priori determined time, the OC executes a "pre-sync" synchronization exchange. The messages exchanged at this time are "time stamped" as they are received. A voted value of the received time stamps is compared with the local pre-sync time stamp and an adjustment is computed. The adjustment affects the time waited until the second version of the synchronization message ("sync") is broadcast. Note that unlike SIFT, the actual time value is not sent, rather reception of the pre-sync message implicitly generates timing information. Additionally, unlike FTP, no extra connectivity need be provided for the timing information; it can be sent over the data broadcast buses. The result is that the FCRs of MAFT are loosely synchronized. The highest frequency of synchronization is 357 Hz [KWFT88]. The maximum skew between FCRs is  $18\mu s$  [KWFT88].

Data comparison is performed in a unique manner in the MAFT architecture. The data from the AP which is being exchanged is tagged to identify AP and task. A "data flow"-like voter is implemented which votes values "on the fly". Exact or approximate agreement can be supported by the voter. The effective bandwidth

Figure 3.8: NEFTP Architecture

of the data communication mechanisim is quoted at one Mbps (million bits per second) [KWFT88].

It is argued that these aspects of MAFT make it amenable to hardware and software diversity [WKF85,KWFT88]. Implementation of approximate agreement in the voting algorithm removes the bit-for-bit agreement constraint, which is a stumbling block for n-version programming software diversity, and hardware diversity. "On the fly" voting coupled with the synchronization mechanism remove the need for tasks to be run in exact synchrony. However, there is the usual temporal constraint on the execution time of tasks. The programmer must know the maximum possible execution time of a given tasks. The OC function of scheduling is therefore dependent on the application. Furthermore, any software diversity must be accounted for in the scheduler.

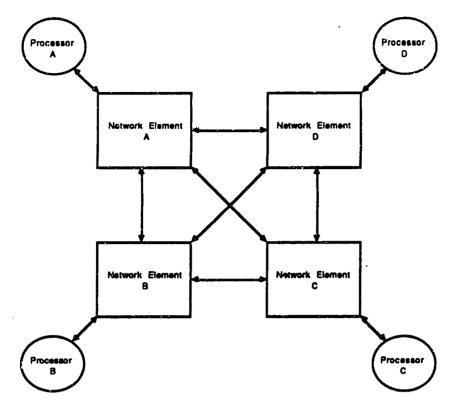

# 3.3 The Network Element Based Fault Tolerant Processor (NEFTP)

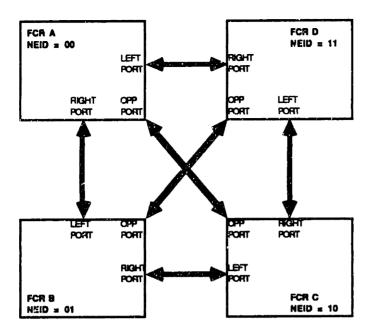

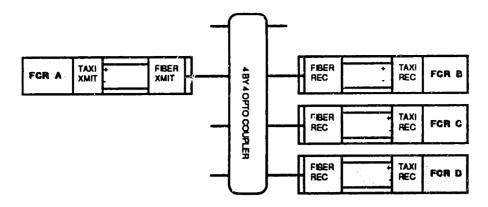

A new architecture known as the Network Element lessed Fault Tolerant Processor (NEFTP) has been developed (Figure 3.8). It consists of four FCRs connected with fiber optic broadcast links. Figure 3.8 illustrates that the cardinality and connectivity requirements are satisfied. The design of the NEFTP employs some

of the advantageous features of both the FTP and the MAFT.

The fault containment regions of NEFTP look similar to those of MAFT. Each FCR consists of a processing element (PE) and a network element (NE). The NE is a hardware implementation of the fault tolerance related functions of synchronization, data communication and data voting. The PE is a commercially available computer which performs the application, scheduling and reconfiguration tasks. The motivation for this architecture is two-fold. First, it removes a significant portion of the burden of fault tolerance from the processor. FTP achieved this by implementing the fault tolerance algorithms in dedicated hardware. MAFT achieved this via the operations controller. NEFTP also mitigates the overhead of fault tolerance by implementing the fault tolerance algorithms with dedicated hardware in the NE. Second, it provides for some flexibility in the implementation (both hardware and software) of the processing element. NEFTP avoids the necessity of clock deterministic processors by providing a means for the NEs to interactively arrive at a consistent view of the data exchange status of the system.

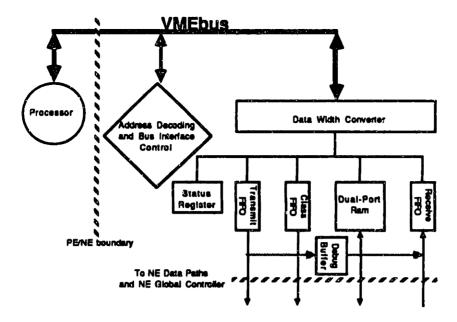

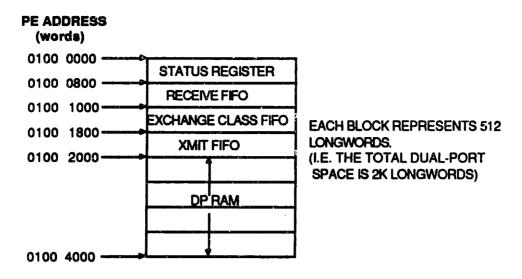

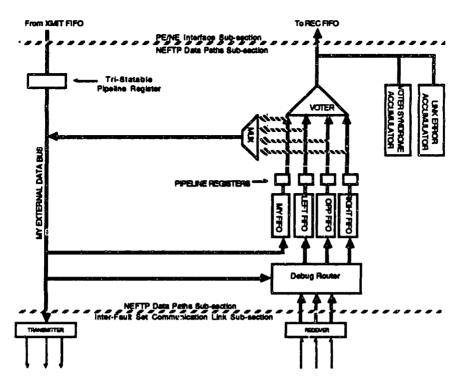

The basic operation of the NEFTP is described here. The PE views the NE as a memory-mapped, buffered I/O device resident on its PE/NE interface. The PE/NE interface in this implementation is Motorola's open architecture VMEbus. The PEs use their NEs to send messages among themselves. These messages are sent for the purposes of synchronization, output consensus, and interactive consistency. If the PE wishes to perform a data exchange, it merely writes the data (message) to its NE. Voted data from the exchange along with error information is eventually available for the PE to read at its NE. The NE appears as a buffered I/O device in that the processor may write many messages to its NE before reading the results from the first exchange. The NEs synchronously perform an interactive consistency exchange of the status of their PE/NE interfaces. Upon arriving at the consensus that a PE message needs to be exchanged, this exchange, either one or two rounds of communication, takes place. A two round exchange is required for input data consistency, but a one round exchange is sufficient to achieve output consistency. Upon completing the exchange, the NEs return to performing their interactive consistency exchange of system status.

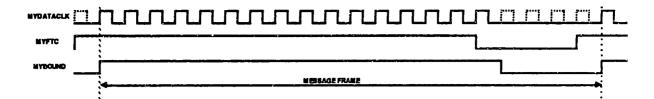

The NEs of the NEFTP are synchronized by message receptions. Since message transmission is a functional characteristic of this system, this synchronization scheme is known as functional synchronization. The NEs are clock deterministic, and are continuously exchanging messages, either the status message or a message from a PE. Each NE notes when it receives messages from the other NEs, and compares the median reception event with the time it sent the corresponding message. Based on the results of this comparison the NE will adjust the amount of time it waits till it starts transmission of the next message. The network elements achieve functional framewise synchrony. The NEs are seen to be framewise congruent (like SIFT, FTP, and MAFT) by defining a frame to be a message transmission. A frame is a variable size quantity in the NEFTP because variable message sizes are sup-

ported. The NEs are functionally congruent because they are clock deterministic and the same functional operation is taking place in the same frame on all NEs. The NEs are tightly synchronized because the frequency of synchronization is great, and the post-synchronization skew is small. Synchronization events occur no less frequently than the maximum message (or frame) size which is  $30\mu s$  (240 NE data clock periods). The post-synchronization skew is no greater than three NE data clock periods 375ns. What is the importance of a tightly synchronized NE? One important point is that the granularity of action of the NEs will be a lower bound of the granularity of action of the processors. Also the fact that message transmission is used to synchronize the NEs and that the frequency of synchronization is great, is indicative of the high bandwidth communication mechanism provided by the NE.

The PEs also use reception of messages for synchronization. In order to make reception of a message a synchronizing act for the processor, it must suspend useful computation pending arrival of the message (otherwise known as "busy waiting"). The resultant post synchronization skew is quite small because the messages are made available to the PEs synchronously by the NEs. The post synchronization skew is the NE skew plus the busy wait loop length. A PE need not busy wait for every message, but clearly the frequency with which it does busy wait affects the granularity of action of the system. The natural question to ask is, "... are the PEs, and hence the system as a whole, tightly synchronized or loosely synchronized?" The answer is "... well, it depends." The frequency of synchronization can be varied depending on the application. Applications requiring fine granularity of action can execute the busy wait with each message sent and use the smallest message size available. A mechanism is even provided for the processors to synchronize without actually sending any data in an attempt to maximize the achievable frequency of synchronization. The processor can send a SYNC message which must be enabled by the NE interactive consistency task, but once enabled the exchange consists of the NE writing some status information to the PE/NE interface. Busy waiting for the reception of this status information will indeed be a synchronization event, with the benefit of saving the time involved in sending a minimum length message. Cleary repeated SYNC exchanges would result in the tightest synchronization, but this is not sustainable, as a fault tolerant computer that never exchanges any data will never output any data and is therefore of limited use. An application where a high granularity of action may be desired is in a hardware and software design diversity test. Of course the NE must know the maximum PE skew, hence it is a programmable parameter (called the timeout) of the NE interactive consistency algorithm. The NEFTP sychronization scheme allows the system to tailor the granularity of action to the application.

There exist hardware constraints. The data produced by all PEs must be compatible with bit-for-bit majority voting. The only other constraint is that some common PE/NE interface be used. Currently it is the VMEbus, but could just as easily be any other open bus architecture, standard serial interface, or LAN pro-

tocol. The existing software constraints are also minimal. The current processor model is simplex Von Neuman with two additional primitives SEND and SCOOP¹. SEND enqueues a message for transmission in the PE/NE interface. If it is not possible to enqueue a message because the NE is full, SEND will read messages from the NE until it becomes clear to send. SCOOP will read all messages that have been sent since the last SCOOP, busy waiting if data is not available at the NE. SCOOP will then send a synchronization message and wait for its reception. Thus upon completion of a SCOOP, all messages that have been sent prior to calling SCOOP have been received and the PEs are synchronized. Tailoring the granularity of action of the NEFTP simply involves programming the NE with a new timeout and perhaps adjusting the ratio of SENDs to SCOOPs. For example, to make the finest grain NEFTP set the NE timeout to the minimum value, and call SCOOP after every SEND.

The data exchange mechanism provides for one and two round exchanges. The results are voted by a 4-way, maskable, bit-for-bit, majority vote algorithm implemented in a programmable logic device. The mechanism is ensured of voting the redundant copies of the same data because the NE preserves the total ordering of messages. The total ordering is preserved because of two reasons. First, the buffering in both directions at the PE/NE interface is implemented with first-in-first-out memories (FIFOs). Second, the NEs continuously perform an interactive consistency exchange of the status of their PE/NE interfaces; and they only enable a PE message for exchange when all participating PEs request the message, or when the timeout period elapses after a majority of participating PEs request the message. This ensures that a faulty PE cannot cause the total ordering of messages to be violated as viewed by non-faulty PEs. Unlike the FTP not all exchanges take two rounds. Regardless of the exchange, the completion of the exchange results in all NEs having sufficient redundant copies of the data to satisfy agreement by voting.

The NEFTP has been shown to satisfy the requirements for 1-Byzantine failure resilience. It does so with few constraints on other aspects of the architecture. The architecture can be tailored to be tightly synchronized for applications where fine granularity of action and high performance are required. Granularity of action can be traded for design diversity in processing hardware and software. This will have a corresponding detrimental impact on performance, however the impact on reliability is less clear. Larger granularity of action will tend to lessen reliability, but this may be compensated by increased resilience to common mode design failures in the processing hardware and software. The NEFTP also incorporates sound fault containment region design. The inter-FCR communication network employs fiber optic links which are quite well suited for fault tolerant applications. No other media has better isolation and attenuation properties. Fault containment regions can finally be truly isolated, both electrically and physically.

A prototype NEFTP has been built as part of this research. In the prototye the

<sup>&</sup>lt;sup>1</sup>These message exchange primitives have been designed and implemented by Steven A. Friend

processing elements are commercially available 32 bit, 68020 based, single board computers. The design of the network element is presented in Chapter 4.

## Chapter 4

## **NEFTP: The Network Element Design**

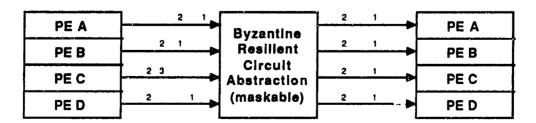

The Network Element (NE) is a hardware implementation of the fault tolerance related functions of synchronization, data communication, and data voting. The NE can be viewed as an abstract communication network. This abstract view of the NE is a simple case of the Byzantine Resilient Virtual Circuit Abstraction (BRVC) [Har87] The BRVC (Figure 4.1) has several interesting properties. It preserves the total ordering and integrity of all valid messages. It provides the resources to correctly manage sufficient redundancy for one and two round consensus exchanges, and allows for graceful degradation of this redundancy (i.e. it is Byzantine Resilient). The BRVC network is synchronizing. This means that if the input satisfies the property that redundant copies of the input message arrive at the network within some known  $t_{skewin}$  then this message will be output at all processors within a known  $t_{skewout}$ : ( $t_{skewout}$  max  $< t_{skewin}$  max). A desirable feature of such a network is that it have very high bandwidth so as to not degrade the throughput of the aggregate system. Also, it must be testable. The NE has been designed to satisfy these properties.

#### 4.1 The Basic NE cycle

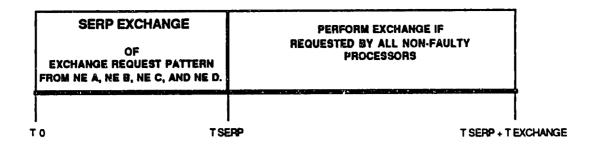

In order to fulfill the network abstraction, the NE executes the basic cycle shown in Figure 4.2.

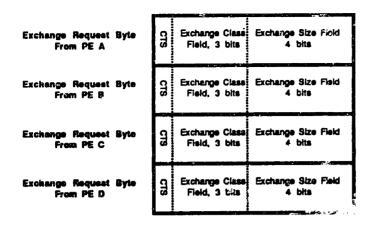

The processors of the NEFTP communicate via message exchanges. Message exchanges are used for the purposes of synchronization, output consensus, and input consistency. Each NE must tell all other NEs whether its associated processor has an exchange request pending. The NEs will then have sufficient information to arrive at a consensus regarding exchange requests. If an exchange request is valid (i.e. all non-faulty processors have requested the exchange), then the exchange will be honored. All NEs will perform the processor exchange and then return to exchanging processor requests. Essentially four input consistency exchanges occur in the

Figure 4.1: BRVC Abstraction

Figure 4.2: Basic NE Cycle

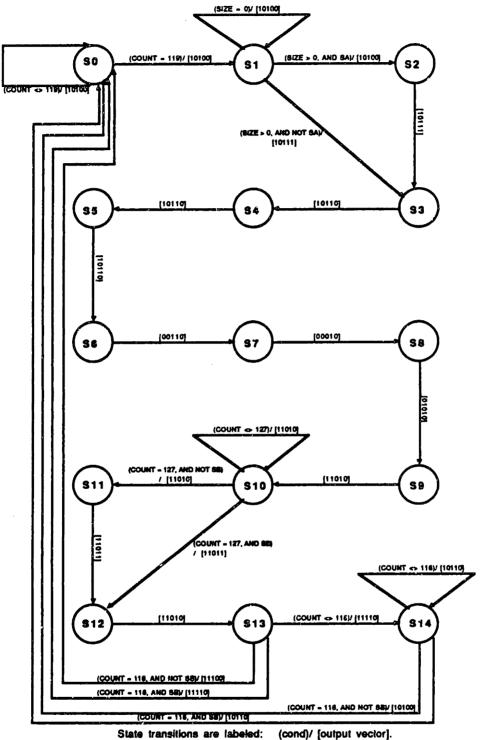

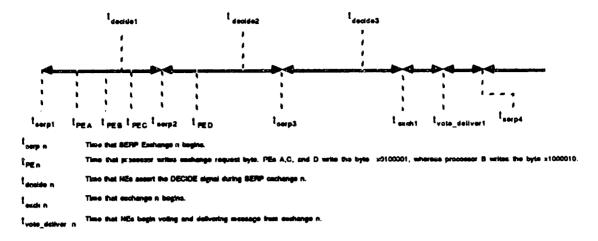

first half of this cycle. The data being input is an exchange request pattern. This sequence of four input consistency exchanges has been somewhat optimized and masquerades under the title system exchange request pattern (SERP¹) exchange. By executing the SERP exchange the NEs interactively arrive at a Byzantine resilient consistent view of the PEs' exchange requests, from which each NE can make the same decision about whether to perform the exchange. This SERP exchange is fundamental to BRVC abstraction discussed above. It is what allows the NE aggregate to be synchronizing and maintain total ordering of message transactions without imposing the constraint of clock determinacy on the processors.

#### 4.2 The NE Functional Sub-Sections

The NE can be considered to be composed of six sub-sections. They are the following:

- 1. The processor/network element interface.

- 2. The network element data paths.

- 3. The inter-FCR communication links.

- 4. The network element fault tolerant clock.

- 5. The network element scoreboard.

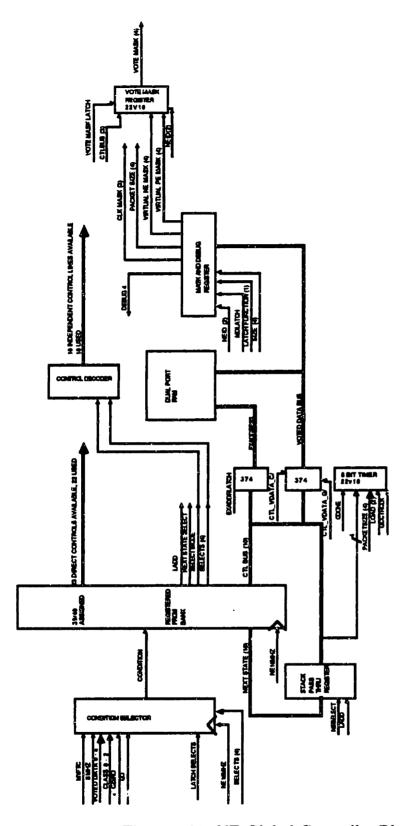

- 6. The network element controller.

The function performed by each subsection is depicted by its name (with the exception of "scoreboard"). The functionality of each subsection will be made clear below. Before beginning, some discussion of nomenclature is necessary. In general, names in uppercase letters refer to a network element signal (to be found on the schematic) or some acronym for a functional module of the NE (such as itself). Names of NE functional modules which are not acronyms will be introduced in slanted text. Also, signal names ending in "\*" or "/" denote a low true signal.