# MODELS AND DATA STRUCTURES FOR DIGITAL LOGIC SIMULATION

bу

## DONALD LEIGH SMITH

B.S., University of Kansas City 1962

S.B., Massachusetts Institute of Technology 1962

## SUBMITTED IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June, 1966

| Signature of Author | Department of Electrical Engineering May 20, 1966 |

|---------------------|---------------------------------------------------|

| Certified by        | Thesis Supervisor                                 |

| Accepted by         | Chairman, Departmental Committee                  |

### MODELS AND DATA STRUCTURES FOR DIGITAL LOGIC SIMULATION

bу

#### DONALD LEIGH SMITH

Submitted to the Department of Electrical Engineering on May 20, 1966 in partial fulfillment of the requirements for the degree of Master of Science.

### **ABSTRACT**

A digital logic simulation system is proposed for design verification. Logic to be simulated is specified with a high-level register transfer design language, and the simulation system operates on-line on a large time-shared computer. The problem of selecting adequate circuit and signal models for this purpose is considered. Models are proposed with sufficient timing detail to allow the simulation system to detect timing errors which currently are found by manual checking or prototype debugging.

A data structure for representing idealized circuit and signal models and a matching simulation algorithm is discussed. The data structure is a direct representation of a complete subset of the design language and is organized so that it can be incrementally modified to reflect design changes. The simulation algorithm is very efficient because combinational levels are re-evaluated only if their values are needed and may have changed since last evaluated.

The data structure is expanded to represent detailed circuit and signal models. A method of intermixing idealized and detailed models and efficiently simulating very large designs is discussed. Extensions are proposed to the design language so that it can be used to specify model parameters and serve as the simulation command language.

Thesis Supervisor: Jack B. Dennis

Title: Associate Professor of Electrical Engineering

## ACKNOWLEDGMENTS

The author would like to express his gratitude to Professor Jack B. Dennis, whose design language work directed the author's attention to this subject area, and whose advice and suggestions as thesis supervisor have been very helpful. He is also grateful to Professor Eric G. Manning and Messrs. Fred L. Luconi, Nathan R. Melborn and Ashok Malhotra, whose interest in this work has been most encouraging. He would like to express his appreciation to Norma L. Burns, who typed the manuscript, and Irene H. Ziemba, who assisted with the figures. Special thanks are expressed to The MITRE Corporation of Bedford, Massachusetts, who generously financed this work.

# TABLE OF CONTENTS

| SECT | ON          |                                                                                                      |                                                                                                                                                                                                                                        | PAGE                                                                 |

|------|-------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| A    |             | ACT<br>WLEDGMENTS<br>OF CONTENTS                                                                     |                                                                                                                                                                                                                                        | 2<br>3<br>4                                                          |

| I    | IN          | TRODUCTION                                                                                           |                                                                                                                                                                                                                                        | 7                                                                    |

| II   | DE          | SIGN LANGUAGI                                                                                        | Ε                                                                                                                                                                                                                                      | 11                                                                   |

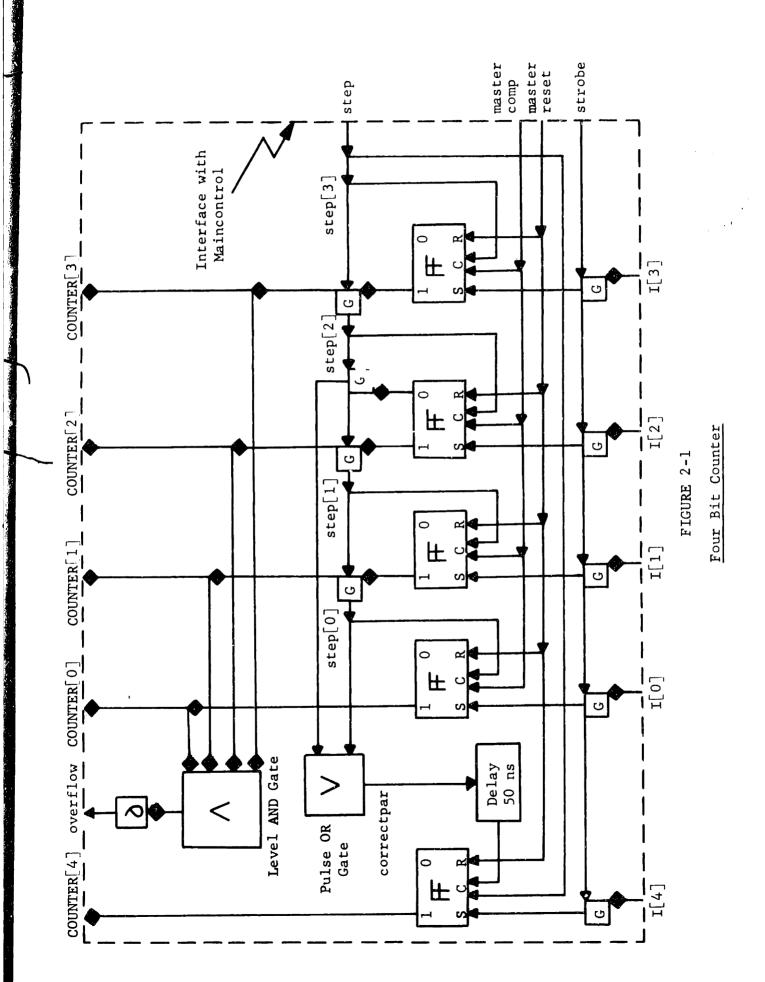

|      |             | Figure 2-1                                                                                           | Four Bit Counter                                                                                                                                                                                                                       | 12                                                                   |

| III  | CI          | RCUIT AND SIG                                                                                        | GNAL MODELS                                                                                                                                                                                                                            | 18                                                                   |

|      | A           | Circuit Dela                                                                                         | ау                                                                                                                                                                                                                                     | 19                                                                   |

|      | B<br>C<br>D | Figure 3-2 Figure 3-3 Figure 3-4 Figure 3-5 Figure 3-6 Figure 3-7 Figure 3-8 Figure 3-9 Register Tra | Level Signal Values Level Delay Line Model AND Gate Combinational Logic Block Model AND and OR Gate Hazard Values Output Hazard for 2-Input AND Gates Example of AND Gate Model Behavior AND or OR Gate Settling Times Flip-Flop Model | 20<br>22<br>22<br>23<br>23<br>25<br>26<br>28<br>30<br>32<br>32<br>33 |

| ΙV   | DΔ          |                                                                                                      | FOR IDEALIZED MODELS                                                                                                                                                                                                                   | 37                                                                   |

|      | A           | Level Logic<br>Figure 4-1<br>Figure 4-2                                                              | Combinational Level String Data Elements Delay and Flip-Flop Level String Data Elements                                                                                                                                                | 40<br>42<br>46                                                       |

|      |             | Figure 4-3                                                                                           | Constant Level and Fixed Memory Data Elements                                                                                                                                                                                          | 47                                                                   |

| SECTI | ON  |                                                                                       | PAGE             |

|-------|-----|---------------------------------------------------------------------------------------|------------------|

| IV    | В   | Control Logic Figure 4-4 Control Logic Data Elements Figure 4-5 Transfer Effect Table | 48<br>49<br>50   |

|       | С   | Time Queuing and Miscellaneous Lists Figure 4-6 Time Queuing Data Structure           | 5 <b>1</b><br>52 |

|       | D   | Simulation Algorithm                                                                  | 53               |

|       | E   | Discussion of Idealized Model Simulation<br>Figure 4-7 Unstable Circuit               | 57<br>58         |

| v     | DA' | TA STRUCTURE FOR DETAILED MODELS                                                      | 60               |

|       | A   | Level Logic Figure 5-1 Detailed Flip-Flop Level String                                | 60               |

|       |     | Data Elements Figure 5-2 Detailed Combinational Level String                          | 61               |

|       |     | Data Elements                                                                         | 62               |

|       | В   | Control Logic                                                                         | 65               |

|       |     | Figure 5-3 Detailed Control Logic Data Elements                                       | 66               |

|       | С   | , ,                                                                                   | 67               |

|       |     | Figure 5-4 Time Queuing Data Structure                                                | 68               |

|       | D   | Intermixing Ideal and Detailed Models                                                 | 70               |

|       | E   | Data Structure Partitioning                                                           | 71               |

|       | F   | Summary of Data Structure Characteristics                                             | 75               |

| VI    | SI  | MULATION COMMAND LANGUAGE                                                             | 76               |

|       | A   | Design Language Extensions                                                            | 77               |

|       | В   | Logic Testing Procedures                                                              | 88               |

| VII   | CO  | NCLUSIONS                                                                             | 90               |

| SECTION  |                                                                                                                                                                                                                                                                                                 | PAGE                                     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| APPENDIX | A INTERMIXED SIMULATION DATA STRUCTURE                                                                                                                                                                                                                                                          | 94                                       |

|          | Figure A-1 Detailed Level String Elements Figure A-2 Ideal Level String Elements Figure A-3 Level Output Specification Structure Figure A-4 Constants, Memories and Stacks Figure A-5 Control Logic Data Elements Figure A-6 Activity Queuing Data Structure Figure A-7 Temporary Storage Lists | 95<br>96<br>97<br>98<br>99<br>100<br>101 |

| APPENDIX | B INTERMIXED DATA STRUCTURE SIMULATION ALGORITHM                                                                                                                                                                                                                                                | 102                                      |

| 1.       | Outline                                                                                                                                                                                                                                                                                         | 108                                      |

| 2.       | Discussion of Simulator                                                                                                                                                                                                                                                                         | 123                                      |

| APPENDIX | C COMBINATIONAL LEVEL FORMULAS                                                                                                                                                                                                                                                                  | 125                                      |

| APPENDIX | D DESIGN LANGUAGE DESCRIPTION                                                                                                                                                                                                                                                                   | 130                                      |

| 1.       | Basic Structure                                                                                                                                                                                                                                                                                 | 130                                      |

| 2.       | Level Logic<br>Figure D-1 Basic Level Delay Unit                                                                                                                                                                                                                                                | 132<br>134                               |

| 3.       | Control Event and Transfer Statements                                                                                                                                                                                                                                                           | 134                                      |

| 4.       | Integers                                                                                                                                                                                                                                                                                        | 138                                      |

| 5.       | Delimiters                                                                                                                                                                                                                                                                                      | 138                                      |

| 6.       | Iteration Statements                                                                                                                                                                                                                                                                            | 139                                      |

| 7.       | Conditional Statements                                                                                                                                                                                                                                                                          | 141                                      |

| 8.       | Define Feature                                                                                                                                                                                                                                                                                  | 142                                      |

| 9.       | Summary                                                                                                                                                                                                                                                                                         | 143                                      |

| BIBLI    | OGRAPHY                                                                                                                                                                                                                                                                                         | 144                                      |

### I. INTRODUCTION

For more than ten years, engineers have been utilizing general purpose digital computers to aid in the design of new digital systems.

The most common form of this aid has been the use of computers to convert descriptions of system logic into wiring lists and other documentation for construction, debugging and maintenance.

Included in this conversion process are such things as logic minimization, wiring rule checking, component placement and wire routing. Computers have been used to a lesser extent to simulate designs to verify that the logic yields correct results. The inputs to these systems are generally some special form of Boolean equations specifying flip-flop input and combinational logic block output formulas. Listings of these logic equations have served to supplement or even replace the more traditional logic diagrams.

The large number of logic equations required to specify a digital system makes it difficult for anyone unacquainted with the design to deduce its behavior from listings of the equations. Likewise, it is tedious and time-consuming to formulate designs in such detail. More concise register transfer languages have been developed for design documentation and formulation early in the design process. Experience with design automation systems has led to the development of improved

The first paper on computer design automation was given by S. R. Cray and R. N. Kisch at the Western Joint Computer Conference in February, 1956 - Reference (1).

<sup>&</sup>lt;sup>2</sup>See References (2), (3), (4), (5), (6), (7) and (8).

The first of these register transfer languages was presented by I. S. Reed in References (9) and (10).

register transfer languages for precisely describing digital systems. These languages may describe machines at the register and decoder level, rather than the flip-flop and gate level of the logic equation languages. The great advantage of these new languages is that they describe hardware at a level of detail convenient to logic designers. Such a language has been under development at M.I.T. under the supervision of Professor J. B. Dennis. This design language has been used as a descriptive language for classroom exercises and to design a Microtape Controller for use with a modified PDP-1 computer. It is intended that the design language eventually serve as the input to a design automation and simulation system.

In this thesis we will be concerned with the development of a detailed simulation system for digital logic design verification. Models for logic circuitry are selected, data structures for representing these models are developed, and simulation algorithms are outlined. No simulation program has been written because of coming computer system change-overs at M.I.T., both at Project MAC and the Computation Center. 5

Most logic simulation programs have been written to simulate a single digital system, either for debugging software to be run on the future system or for detecting logic errors. Of those simulation programs designed for logic checkout, the large majority have been written for synchronous machines and, in all cases known to the author, idealized circuit models have been used. Such models exclude consideration of such

<sup>4</sup>See References (11), (12), (13), (14) and (15).

<sup>&</sup>lt;sup>5</sup>There are advantages to being forced to think about the program before being able to start any coding.

things as circuit delay, pulse width, delay tolerances and fan-out delay variations, and cannot be used to help locate the difficult to detect race conditions and timing errors which are especially important in asynchronous logic checkout. Relatively few simulation systems have been developed which translate special descriptions of designs into programs which simulate them.

Simulation for logic checkout has been widely used in the defense industry, where great emphasis is placed on short design lead time and production runs are short. High competition in the commercial side of the industry is also moving effort away from prototype debugging and toward simulation to detect logic errors as early as possible. With the introduction of third generation computer hardware the cost of constructing a prototype and modifying the design before production is increasing rapidly, again providing economic reasons for using simulation to verify a design before tooling up for prototype construction.

It is intended that this thesis be the basis for a simulation system which uses the Dennis Design Language as input and operates in a large time-shared computer environment. In addition to checking the overall operation of a design, this system would perform special simulations to test for suspected race conditions and logic hazards. It is not proposed that the system automatically check for all possible design errors, but rather that the judgment of the designer be relied upon to select likely problem areas and simulations for testing them. The advantages of this approach are that no additional restrictions need be placed on designs and the simulation system is fully compatible with current design techniques. Circuit and signal models are provided with sufficient timing

detail for race and hazard detection. The internal data structure is designed to facilitate on-line modification to the logic descriptions as errors are detected. These modifications do not require a complete reordering of the data structure; the data structure can be changed incrementally. Simulation efficiency is improved by evaluating only those combinational levels whose values are required and which may have changed since last evaluated.

Section II introduces the design language by way of a brief example and indicates the classifications of circuit and signal types in which a design is described. In the next section we select models for representing the important characteristics of each circuit and signal type.

Section IV presents a data structure for representing ideal circuit and signal models and outlines a simulation algorithm based on the structure. The structure is modified to represent detailed models in Section V and a method for intermixing ideal and detailed models in the same structure is discussed. Section VI proposes modifications to the design language so that circuit and signal timing parameters can be declared and the language can be utilized as the simulation command language. Conclusions are presented in Section VII.

### II. DESIGN LANGUAGE

In this section we will examine the design language description of a small part of a digital system. The motivation for doing this is to demonstrate the use of some of the features of the design language and to show that three different classes of signals are represented in such a design description. Separate models will be developed for each of these classes of signals and will be included in simulation data structures to be presented later. This will simplify translation from the design language into the data structure, but more importantly, the organization is a natural way of looking at complicated digital networks.

The logic network selected for demonstrating the design language is diagramed in Figure 2-1. The network is a four-bit counter with parity and is realized in common pulse-level hardware. Arrowheads represent pulse inputs and diamonds represent level inputs. Counter parity is generated using carry pulses when it is stepped. Signals are named, and the same names are used in the design language description.

In the following design language description, the counter is specified as a component interfacing with one other component called Maincontrol:

A complete syntax was written for the design language by G. J. Burnett in Reference (16). A discussion of the language more consistent with its present state of development is found in Reference (17), written for M.I.T. course 6.535 by H. F. Ledgard. Examples of the use of the language are found in a companion set of notes, Reference (18). Since these references may not be available, a brief outline of the basic design language is included in Appendix D.

```

component FOURBITCOUNTER;

1

interface MAINCONTROL;

2

input pulse strobe, step, masterreset, mastercomp;

3

input level I[0:4];

4

output pulse overflow;

5

output level COUNTER[0:4];

6

end interface MAINCONTROL;

7

register COUNTER[0:4]; * Bit 4 is parity bit;

8

strobe: I → COUNTER;

9

* Step control;

10

step[3];

11

step:

† COUNTER[4];

12

for i = 1 through \frac{3}{2} do

begin

13

t COUNTER[i];

step[i]:

14

if COUNTER[i] then step[i-1]; end;

15

† COUNTER[0];

step[0]:

16

correctpar;

17

if - COUNTER[2] then correctpar;

step[2]:

18

delay (50 ns);

correctpar:

19

t COUNTER[4];

20

```

- 21 \* Master Reset and Complement;

- 22 masterreset:  $0 \sim \text{COUNTER}[0:4]$ ;

- 23 mastercomp: † COUNTER[0:3]; \* Parity remains correct;

- 24 \* Overflow Detection;

- 25  $MAXCOUNT \equiv COUNTER[0:3] = 15;$

- 26 MAXCOUNT: overflow;

- 27 end component FOURBITCOUNTER;

The FOURBITCOUNTER component is delimited by lines 1 and 27. (Line numbers are not part of the design language but are used here to aid in the discussion.) Lines 2 - 7 declare the signal interface with the component MAINCONTROL. If the counter interfaced with any other components, the other signal interfaces would also be declared at this point. Next come the register declarations, which in this case consists only of the five flip-flop register COUNTER. Note that the syntax of the design language has much of the flavor of ALGOL syntax. Basic Symbols are underlined when they are more than one character long and semicolons are used to terminate statements. Asterisks are used to precede comment statements, as in lines 8, 10, 21, 23 and 24, rather than the ALGOL symbol comment. Identifiers made up of capital letters and digits are used to name level signals, identifiers made up of small letters and digits are used for pulses. When a pulse identifier appears in a statement label, hardware is to be included in the component to execute all statements down to the next label or delay statement whenever that pulse occurs. Therefore the meaning of lines 11 and 12 is:

whenever the pulse "step" is generated, the machine will generate the pulse "step[3]" and complement flip-flop COUNTER[4]. These actions are taken simultaneously, as opposed to the sequential execution of statements in an ALGOL program. This should not be surprising since the design language is used to specify computer hardware, which is generally highly parallel, while ALGOL is used to specify computer programs, which are at present sequentially executed.

Lines 13 through 15 constitute an iteration statement which describes the propagation of carrys when the counter is stepped. This feature of the design language is provided to save the logic designer the necessity of writing out descriptions for each duplication of the same hardware. Level and pulse names are indexed so that each name is unique. Lines 16 and 17 describe the carry into the last stage of the counter, which is slightly different from the others. Line 18 describes the gate on the false side of COUNTER[2] which is used to complement the parity flip-flop. Lines 19 and 20 indicate that the pulse "correctpar" is delayed 50 ns and used to complement the parity bit. The register reset and complement logic is described in lines 22 and 23.

Line 25 defines the combinational level MAXCOUNT and line 26 indicates that an "overflow" pulse is generated whenever MAXCOUNT changes from a zero to a one. This implies the level differentiator shown in Figure 2-1.

Note that the pulse "step[2]" occurs twice as a label: first, in the expansion of line 14 for i=2, and a second time in line 18. It is perfectly correct for a pulse identifier to be used as a label any

number of times. The meaning of this is that all statements labeled by the same pulse become active simultaneously whenever the pulse is generated.

From this example it can be noted that three distinct classifications of signals are represented in the design language.

## 1. Level Signals

This class consists of register, combinational logic and level delay line output signals. The important characteristic of a level signal is its logical value as a function of time.

#### 2. Events

These are the command signals of a digital system. They may be generated by oscillators, other Events or level transitions. The important characteristic of an Event is its occurrence time. In the design language these signals are called pulses because in many digital circuit families they are realized as short duration pulses. This is not always the case - in some systems transitions in regular level signals are used as control events. If a value transition is to be used to generate an Event (line 23 of example) in short duration pulse logic, a differentiator sensitive to that transition must be used. This is not required in all-level circuit families.

#### 3. Transfers

This group of signals set, reset, complement and jam transfer data into flip-flop registers. They are usually

realized in hardware in the same way as Events. In all-level circuit families, flip-flop inputs have diodecapacitor networks which are only sensitive to 0 to 1 value transitions. Register transfers appear in the design language functionally, as in line 9 of the example, and are unnamed.

## III. CIRCUIT AND SIGNAL MODELS

The keystone to a good computer simulation is an appropriate model of the mechanism being simulated. The appropriateness of the model depends on the questions to be answered by the simulation - too simple a model leads to inaccurate results or no results at all while an overly detailed model deteriorates simulation efficiency. In this section we shall develop circuit and signal simulation models to be used for logic design verification. Important weaknesses of these models will be pointed out and reasons for not correcting them will be given.

When we state that we are interested in simulation for design verification we mean that we are interested in checking not only on the overall behavior of the logic but also detecting such things as potential logic hazards, race conditions, and the sampling of unsettled levels. The logic designer checking his design should be able to formulate a simulation model to answer the following kind of questions:

- a) Does the multiply instruction work properly for these arguments?

- b) Does reduction in the maximum complement rate of the flip-flops affect performance?

- c) What is the maximum asynchronous transfer rate of this channel?

- d) What effect does this addition have on the rest of the logic?

e) How often can I step this counter and check its parity without risking the possibility of sampling a level before it is settled?

Provisions must be made for simulation at the circuit block level to answer questions of this type and provide the desired error detection capabilities. The logic designer should be able to formulate his problem by specifying both the depth of simulation and the important circuit and signal parameters for each part of the design. Therefore, the models must be capable of expressing relationships between components modeled at various depths in a compatible manner. Before considering models for the three classes of signals discussed in Section II and the circuit blocks which generate them, let us consider the general problem of modeling circuit delay.

# A. Circuit Delay

Logic designers use circuit delay calculations to determine at what times levels are settled and ready to sample and in what time intervals pulses occur. In many instances it is not necessary to make delay calculations because enough time is allowed between each command pulse for all levels to settle; the main reason for the predominance of synchronous logic is that most delay problems are eliminated. Even with synchronous logic there are occasions, such as carry propagation and parity checking, where maximum delay times are needed. In rare instances variables are sampled as input changes are being propagated; in these cases minimum delay times are required. 7

See Reference (19) for discussion of manual techniques for evaluating worst-case delay conditions.

Circuit delays cannot be treated as constants. They vary from one circuit to another of the same type and depend upon environmental factors such as electrical loading and operating temperature. In the signal models developed in this section, signal changes (either pulses or level transitions) will have both a starting time and a spread associated with them. The starting time will be the earliest possible time at which the change could occur and the spread will be the maximum interval of time in which the change could occur. The circuit block models will include minimum delay and ambiguity times, where the ambiguity time is the difference between minimum and maximum delay times through the circuit. Thus the starting time for a change in the output of a circuit block is the starting time of the input change plus the minimum delay of the block. Likewise, the spread of the output is the sum of the spread of the input and the ambiguity time of the circuit block.

# B. <u>Level Signals</u>

As mentioned in Section II, level signals are the outputs of flip-flops, combinational logic, and delay lines. These circuits are enough unlike each other to deserve their own individual models. Before going on to discuss those models, let us first develop a model for level signals. From the above discussion we find that whenever the logical value of a level signal changes there is an interval of time, called the signal spread, when the value may be changing. Normally, it is improper to attempt to sample a level during a spread interval, so it is not important what values the signal takes on during that time.

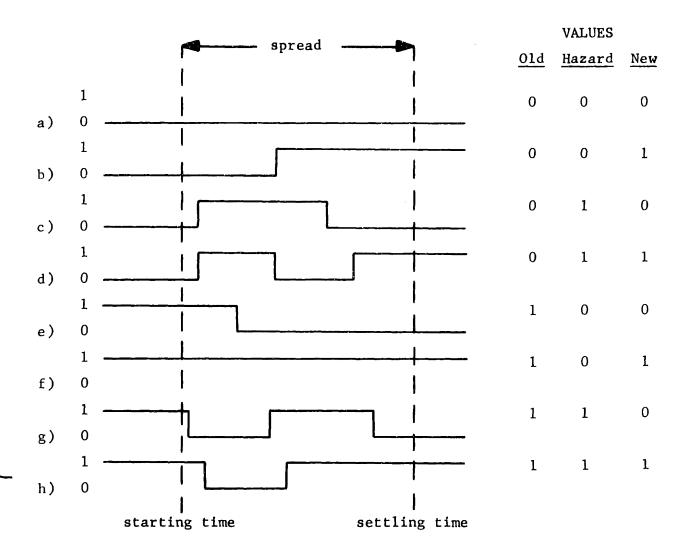

This is not true if the signal enters a circuit which is sensitive to level transitions. Such a circuit is the differentiator, which generates an output pulse whenever its input level changes from 0 to 1. possibility that a level signal might change values several times before settling is termed a hazard. A hazard occurring on differentiator inputs might produce false outputs. Therefore, it is necessary to be able to determine whether or not such levels have hazards during their transition spreads. Multiple hazards (the possibility of more than one double change in the value of a signal) are no worse than single hazards so there is no need to keep a count of them. It will be shown during the development of the combinational Logic Block that it is necessary that old value, hazard value, and new value be given for each input in order to calculate the hazard value (true if a hazard is present) of the output. Thus the value of a level signal is a three bit quantity old value, hazard value, and new value. The simplest waveform for each of the eight possible values is shown in Figure 3-1. If a level is changing there is a time, called the settling time, when the change will be completed.

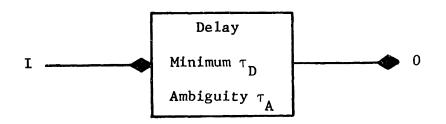

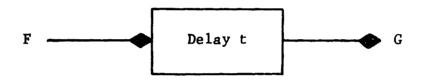

Delay Lines

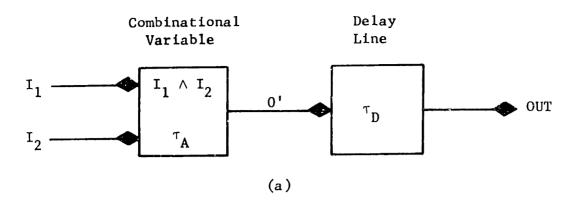

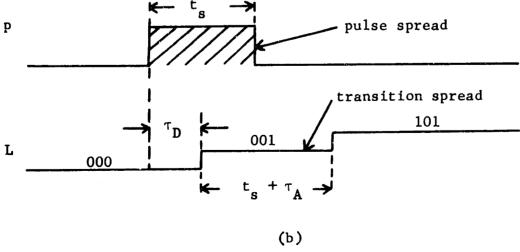

The model for a level delay line is shown in Figure 3-2. The important characteristics are the minimum delay,  $\tau_D$ , and the delay ambiguity,  $\tau_A$ . If level I makes a change beginning at t with spread  $t_s$ , the level 0 will make the same change at t +  $\tau_D$  with spread  $t_s$  +  $\tau_A$ .

<sup>&</sup>lt;sup>8</sup>See Sections VIII and IX of Reference (20) by D. A. Huffman.

FIGURE 3-1

Level Signal Values

FIGURE 3-2

Level Delay Line Model

Combinational Logic Block

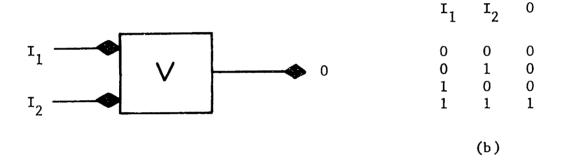

Combinational logic blocks are the standard level logic circuits whose outputs are some Bcolean function of their inputs. Examples include level inverters, AND gates, OR gates, NAND gates, etc. Typical of this type of circuit is the 2-input AND gate of Figure 3-3. The truth table for this circuit is shown in Figure 3-3 (b). Such a truth table can always be written for a member of this group and is the most important characteristic of the block.

FIGURE 3-3

## AND Gate

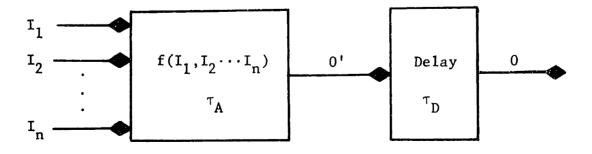

The detailed model for a combinational logic block is shown in Figure 3-4. It consists of a combinational block with zero minimum delay followed by a delay line with zero delay ambiguity.

FIGURE 3-4

### Combinational Logic Block Model

Note that the delay ambiguity is included in the left part of the model. Thus, in the many cases where minimum delay is unimportant, the left part can be used as the complete model. The function  $f(I_1, I_2 \cdots I_n)$  is a mapping of the old, hazard and new values of the inputs into old, hazard and new values of the output, 0'. The old value of 0' is a Boolean function of the old values of the inputs, just as the new value of 0' is the same Boolean function of the new values of the inputs. On the other hand, the hazard value of 0' is a Boolean function of the old, hazard and new values of the inputs.

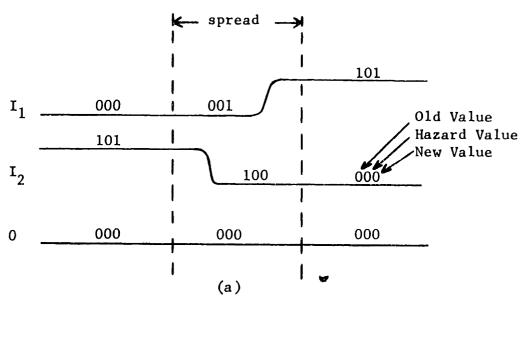

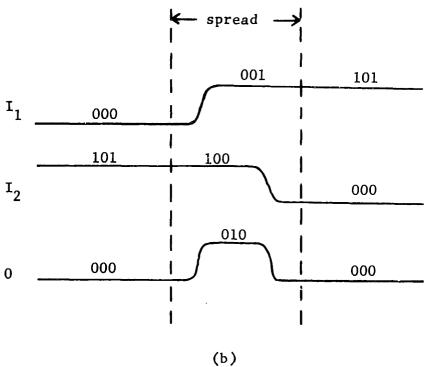

Karnaugh maps <sup>9</sup> for calculating the hazard value for the outputs of 2-input AND and OR gates are given in Figure 3-5. Again, leftmost bits of the arguments are the old values, the middle bits are the hazard values, and the rightmost are the new values. The method used to determine the entries in these graphs is illustrated in Figure 3-6. Two sample sets of waveforms for the case where the inputs to the AND gate of Figure 3-3 both change at the same time and the same spread are given. The minimum delay time and delay ambiguity of the gate are assumed to be zero.

Figure 3-6 (a) shows that if I<sub>2</sub> goes to "0" before I<sub>2</sub> goes to "1" then no transient pulse is generated. If the timing is reversed, as in Figure 3-6 (b), a transient pulse is generated. Since the only information given is that both signals are changing during the spread interval, either case is possible. Therefore, the hazard value is "1"

See pages 131-142 of Reference (21) by S. H. Caldwell.

| $I_2$ $I_1$ | $\mathbf{I}_1 \wedge \mathbf{I}_2$ |     |     |     |     |     |     |     |

|-------------|------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| -           | 000                                | 010 | 011 | 001 | 101 | 111 | 110 | 100 |

| 000         | 0                                  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 010         | 0                                  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 011         | 0                                  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 001         | 0                                  | 1   | 1   | 0   | 0   | 1   | 1   | 1   |

| 101         | 0                                  | 1   | 1   | 0   | 0   | 1   | 1   | 0   |

| 111         | 0                                  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 110         | 0                                  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 100         | 0                                  | 1   | 1   | 1   | 0   | 1   | 1   | 1   |

| ·           |                                    |     |     | (a  | )   |     |     |     |

$\mathbf{I}_1 \vee \mathbf{I}_2$ 111 110 001\_

FIGURE 3-5

AND and OR Gate Hazard Values

(b)

FIGURE 3-6

Output Hazard for 2-Input AND Gate

.

ľ

.

as shown in the shaded square of Figure 3-5. An examination of either part of Figure 3-6 indicates that the functions cannot be simplified to eliminate the need for one of the input value bits. Thus the old, hazard and new values of all inputs to a combinational logic block are required to compute the output hazard value.

Let us now propose and discuss a method for determining the settling time (and thus the spread) of the output level 0' of the combinational logic block model of Figure 3-4. Whenever an input to the combinational logic block changes, the output 0' is re-evaluated. The delay ambiguity,  $\tau_{\mathbf{A}}$ , is added to the settling time for the changing input level. If this sum is larger than the present settling time for level 0' then it replaces it. When time moves forward to the settling time of 0' the new value replaces the old value and the hazard value becomes zero. Thus, the unsettled level 0' becomes settled.

Figure 3-7 (a) shows the detailed model for a 2-input AND gate. Figure 3-7 (b) illustrates its behavior for the set of given input waveforms. Unsettled levels are indicated in this figure as being half way between a settled "1" and a settled "0". The signal OUT is just signal 0' delayed  $\tau_{\rm D}$  seconds. Signal 0' becomes unsettled whenever one of the inputs becomes unsettled and remains so until  $\tau_{\rm A}$  seconds after both inputs are settled. Note that level 0' takes on the unsettled value 000. This occurs because the initial change in input  $I_{1}$  does not change the output until input  $I_{2}$  also changes. Thus the value of a level may not be changing even though it is unsettled.

FIGURE 3-7

Example of AND Gate Model Behavior

A weakness in this method of computing settling times is illustrated in Figure 3-7 (b). The value t<sub>2</sub> for the second settling time for level 0' is incorrect; the correct value should be t<sub>2</sub>'. This is because level 0' should be settled T<sub>A</sub> seconds after either of the inputs has settled at "0". The simple approach of selecting the maximum possible settling time would tend to cause correct situations to be flagged as illegal during a simulation. At first this method was considered acceptable because it does not require evaluation of a combinational level's output value to calculate its settling time. In Section V we will find that it is necessary to re-evaluate combinational levels whenever an input changes. Therefore a more accurate method of calculating settling times can be used without great additional cost.

Figure 3-8 indicates how to calculate output settling times for 2-input AND and OR gates. If the output value is changing, the settling time of the change is calculated by adding the gate's ambiguity time,  $\tau_{\mathbf{A}}$ , to the settling time of one of the inputs, either  $t_1$  or  $t_2$ . The figure shows which input settling time to choose for each input value pair -  $t_1$ ,  $t_2$ , the maximum of the two or the minimum of the two. Zero entries indicate that no output changing is occurring and a settling time should not be calculated.

| 1 <sub>2</sub> 1 <sub>1</sub> | $\mathbf{I}_1 \wedge \mathbf{I}_2$ |                |                |                |                |                |                |                |

|-------------------------------|------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                               | 000                                | 010            | 011            | 001            | 101            | 111            | 110            | 100            |

| 000                           | 0                                  | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

| 010                           | 0                                  | Min            | t <sub>2</sub> | t <sub>2</sub> | t <sub>2</sub> | t <sub>2</sub> | Min            | Min            |

| 011                           | 0                                  | t <sub>1</sub> | Max            | Max            | t <sub>2</sub> | Мах            | t <sub>1</sub> | t <sub>1</sub> |

| 001                           | 0                                  | t <sub>1</sub> | Max            | Max            | t <sub>2</sub> | Max            | t <sub>1</sub> | t <sub>1</sub> |

| 101                           | 0                                  | t <sub>1</sub> | t <sub>1</sub> | t <sub>1</sub> | 0              | t <sub>1</sub> | t <sub>1</sub> | t <sub>1</sub> |

| 111                           | 0                                  | t <sub>1</sub> | Max            | Max            | t <sub>2</sub> | Max            | t <sub>1</sub> | t <sub>1</sub> |

| 110                           | 0                                  | Min            | t <sub>2</sub> | t <sub>2</sub> | t <sub>2</sub> | t <sub>2</sub> | Min            | Min            |

| 100                           | 0                                  | Min            | t <sub>2</sub> | t <sub>2</sub> | t <sub>2</sub> | t <sub>2</sub> | Min            | Min            |

(a)

| $I_2$ | $I_1 \vee I_2$ |                |                |                |     |                |                |                |  |

|-------|----------------|----------------|----------------|----------------|-----|----------------|----------------|----------------|--|

|       | 000            | 010            | 011            | 001            | 101 | 111            | 110            | 100            |  |

| 000   | 0              | t <sub>1</sub> | t <sub>1</sub> | t <sub>1</sub> | 0   | t <sub>1</sub> | t <sub>1</sub> | t <sub>1</sub> |  |

| 010   | t <sub>2</sub> | Max            | t <sub>1</sub> | t <sub>1</sub> | 0   | t <sub>1</sub> | Max            | Max            |  |

| 011   | t <sub>2</sub> | t <sub>2</sub> | Min            | Min            | 0   | Min            | t <sub>2</sub> | t <sub>2</sub> |  |

| 001   | t <sub>2</sub> | t <sub>2</sub> | Min            | Min            | 0   | Min            | t <sub>2</sub> | t <sub>2</sub> |  |

| 101   | 0              | 0              | 0              | 0              | 0   | 0              | 0              | 0              |  |

| 111   | t <sub>2</sub> | t <sub>2</sub> | Min            | Min            | 0   | Min            | t <sub>2</sub> | t <sub>2</sub> |  |

| 110   | t <sub>2</sub> | Max            | t <sub>1</sub> | t <sub>1</sub> | 0   | t <sub>1</sub> | Max            | Max            |  |

| 100   | t <sub>2</sub> | Max            | t <sub>1</sub> | t <sub>1</sub> | 0   | t <sub>1</sub> | Max            | Max            |  |

FIGURE 3-8

(b)

AND and OR Gate Settling Times

Flip-Flops

The same of the sa

In Allertan

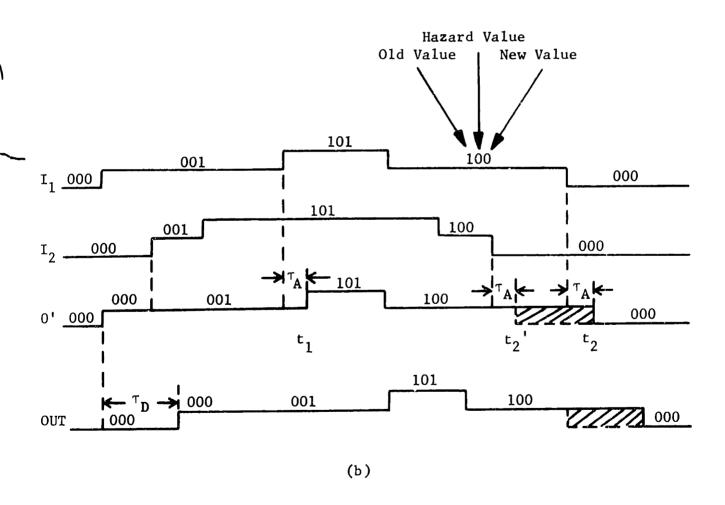

Flip-flop output levels are modeled the same way as other level signals. Old and New Values have the same meaning as before. A Hazard Value of "1" indicates the rapid recomplementation of the flip-flop before the previous change has settled. Again minimum delay time and delay ambiguity reflect the spread of possible transition delays whenever the flip-flop's output is changed. The spread of the output change is calculated by adding the flip-flop's ambiguity time,  $\tau_{\rm A}$ , to the spread of the transfer which caused the change.

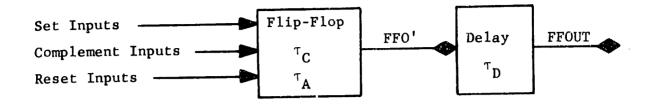

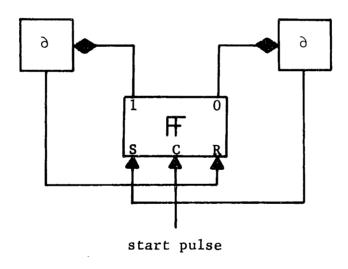

There are special restrictions on flip-flop inputs which should be included in the model. The first of these is that an attempt to simultaneously set and reset a flip-flop with different signals is improper and should flag an error during simulation. In many logic families the normal method for complementing a flip-flop is to use a single signal to both set and reset it. When two separate signals are used the result is ambiguous due to variances in arrival times and amplitudes. Similarly, an attempt to simultaneously complement and either set, reset or complement a flip-flop with different signals is improper. The last special restriction applies only to complement inputs. Attempts to strobe these too soon after the flip-flop output has begun to change can lead to incorrect output values. Therefore, the flip-flop model shown in Figure 3-9 includes a mechanism for detecting attempts to complement the output value before  $\tau_{\mathbf{C}}$  seconds (minimum complement time) after the output begins to change.  $\tau_{\mbox{\scriptsize C}}$  is a constant like  $\tau_{\mbox{\scriptsize A}}$  and  $\tau_{\mbox{\scriptsize D}}$  provided to the simulator by the logic designer.

FIGURE 3-9

## Flip-Flop Model

### Differentiators

These circuits produce output command events whenever their inputs make "O" to "1" transitions. The spread of the output event is the same as the spread of the input level change which generates it. If a differentiator input ever has a hazard value of "1", a simulation error flag is set.

# C. Register Transfers

The state of the s

These signals are modeled somewhat differently than the level signals we have been discussing. The important characteristic of this type of signal is its behavior when activated rather than its value at any instant of time. Therefore transfers are modeled in terms of their effects on registers. The complete specification of a register transfer includes:

- The type of transfer, such as jam transfer, ones transfer,

zeros transfer, or complement transfer.

- The name of the destination register and a specification of the bits affected.

- 3. The names of the source level signals to be transferred to the destination register. Source levels may be flipflop (register), combinational logic, or delay line outputs.

- 4. The delay ambiguity time for the transfer. This figure is used to represent the propagation difference between the minimum and maximum transfer paths when timing might be an important factor in a simulation. The spread of a register transfer is calculated by adding the transfer ambiguity time to the spread of the command event which activates the transfer.

- 5. If a transfer is ever attempted when one or more of the source levels is changing value, a simulation error is flagged.

# D. Control Events

Control events may cause register transfers to occur and, provided that certain level signals have the proper values, may cause other control events to become active immediately or at some later time. The model for a control event includes:

- A list of transfers which take place whenever the event becomes active.

- 2. A list of level signals which act as conditions for the events that may be triggered by this event. The value of each of the condition levels is sampled when the event becomes active. Associated with each level is a list of control event - delay time pairs. Those control events

made active after the paired delay time has elapsed. A sampled condition level whose value may be changing causes a simulation alarm to be flagged.

- 3. Control event minimum delay time.

- 4. Control event ambiguity time. When modeling timing very precisely this parameter is used to indicate maximum possible differences in arrival times of this signal to the various points it fans out to. The spread of any given activation of a control event is calculated by adding its ambiguity time to the spread of the control event or level transition which activated it.

This completes the development of detailed simulation models for signals and level circuit blocks. Before introducing simulation data structures based on these models, let us point out a serious weakness in the manner in which signal spreads are computed. The signal spread concept was introduced to detect logic design faults, either those involving level hazards feeding differentiators, or those caused by Events sampling Levels which may, depending on circuit variations, have more than one possible value. This second detection problem can be stated as follows. Given that Event p samples Level L at any time t within its spread of occurrence times, can Level L have more than one possible value? Unfortunately, the models do not keep track of the interdependence of signal spreads and can only determine whether or not the spreads overlap. This leads to the detection of logic faults which do not, in fact, exist. A simple example of this is illustrated in

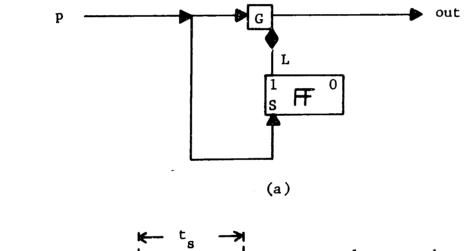

Figure 3-10. During a simulation run pulse p is found to have a spread  $(t_S)$  greater than the minimum delay time  $(\tau_D)$  of the flip-flop. Therefore, the spreads of pulse p and the transition of level L overlap, as shown in Figure 3-10 (b), and a false error detection is made. A situation which can generate a large number of incorrect fault detections is a signal feedback loop such as a delay line ring used as a time pulse distributor. If non-zero delay ambiguity is assigned to any circuit or signal in the loop the amount of spread in the signal increases each time it goes around the loop. Thus signals are generated with increasing spreads and cause more and more incorrect error detections.

FIGURE 3-10

Example of Signal Spread Fault

A timing model capable of avoiding these difficulties must retain additional information so that the dependence of signal spreads on the occurrence times of other signals can be calculated. One way of doing this is to keep track of signal histories. When possible sampling faults are detected the histories both the Event and Level are traced back to their common sources, if any. Then the signal spreads are recalculated forward from those points removing ambiguity common to both. Pre-simulation analysis can be used to determine in advance which parts of a signal's history should be retained and thus sharply reduce the amount of storage required. Designs which require extremely long signal histories could be rejected as not simulatable. An alternate approach would be to carry signal histories through only a fixed number of circuit blocks. This technique would not be able to establish remote signal dependencies, but the more common cases, such as the one in Figure 3-10, would be detected. Such modeling would still require longer running time and a greatly expanded data space and is not considered here. Instead, the responsibility for avoiding incorrect fault detection is assigned to the designer using the simulator.

Logic designers generally are aware of the areas of their designs which may contain timing errors. The most fruitful uses of detailed timing simulations are in specially tailored tests of such problem areas rather than exhaustive testing of complete designs. The fault detection problem discussed above is not as severe in these special cases if adequate means are provided for masking out obviously incorrect error detections. It is clear that as simulation becomes less expensive and more desirable, a more adequate method of establishing signal spread interdependences must be provided.

# IV. DATA STRUCTURE FOR IDEALIZED MODELS

Two categories of information can be provided by logic simulation based on the models of Section III. The first is used to check the overall behavior of the simulated design against design objectives and includes the values of registers or other level signals at selected times. The second category consists of information about possible logic hazards and timing errors; this aids the logic designer in tracking down and correcting these more difficult to detect design errors. The simulation data structure and matching simulation algorithm presented here are based on idealized circuit models - fan-out, delay and transition times are ignored and level hazard detection is not included. Only information in the first category can be provided by such a simulation. The data structure will be expanded to deal with the complete circuit and signal models in Section V.

This simulation system is designed to be operated on-line by the logic designer and communicates with him via a modified form of the design language. In order of importance, the system design goals are:

- a) Any design, synchronous or asynchronous, that can be described in the design language should be simulatable.

- b) Timing and parallel operation should be modeled as consistently and accurately as possible. Simulations must be repeatable.

- c) It should be possible to make incremental modifications to a simulation as the designer makes changes to his design language description.

- d) The simulation system should be densely packed to allow large designs to be simulated with a minimum of memory swapping.

- e) The simulation system should be organized to run as fast as possible.

- f) The data structure should be organized to ease translation back and forth between it and the design language.

- g) The logical complexity of the system should be minimized to reduce the effort needed to program and describe it.

A large number of digital simulations have been based on idealized circuit models similar to the ones used in this section. In some of these cases simulation systems have been provided to translate special forms of a design's logic equations into a program which simulates it; 10 often special simulation programs had to be written for each new design. 11 In each case, special code was included in the program to simulate each logic equation or circuit block of the design. The simulation systems developed here use a data structure, derived from the design language description of the logic to be simulated, as the input to a fixed, table-driven simulation procedure. There is a close correspondence between the design language description and the data structure it represents. This is because the data structure is actually a direct

<sup>&</sup>lt;sup>10</sup>See References (3), (13), (22) and (23) for examples. In all cases known to the author special descriptions of the designs had to be made for input to the simulation systems.

Examples of such programs and techniques for increasing their efficiency are found in References (24), (25), (26) and (27). An example of macroscopic simulation of digital systems is found in Reference (28).

representation of a subset of the design language. Thus it is fairly easy to translate back and forth between them and make incremental modifications to the data structure. This organization results in a densely packed simulation structure. The price paid for this is slower running speed, but the extra time is more than made up by re-evaluating a combinational level value only when its value is needed and its inputs may have changed since it was last evaluated.

The requirement for incremental changes to the data structure leads to consideration of list structures. Large parts of the data structure are formulated in this manner. It is often much more time-consuming to recover information from list structures than equivalent fixed data blocks. Fixed blocks are used to represent data whose size is not likely to be incrementally altered and in those cases where list structures would be unnecessarily wasteful of space or difficult to quickly access. Lists are used to describe variable length information which the designer may later wish to add to or delete from. This results in a mixture of interrelated lists and fixed blocks of many different lengths.

The total data structure can be divided into three separate interconnecting parts. The first two change size or shape only to reflect changes in the logic design being simulated. The third part of the structure is modified during a simulation run.

### 1) Level Logic

This structure describes the output values and interconnections of the registers, combinational logic blocks, level delay lines and differentiators. Special structures are also included to simulate constants and memory interfaces.

### 2) Control Logic

Control events, register transfers, and their interrelations are described in this part of the data structure. A special Transfer which terminates the simulation is included.

Time Queuing and Miscellaneous Lists

This part of the structure is used by the simulation program to queue up future activities and keep track of temporary information such as subroutine arguments and input-output data.

### A. Level Logic

Information describing output level signals is included as part of the data for each flip-flop, combinational logic block and level delay line. This information consists of the value of the level, 12 which may be sampled by Events or be a source for a Transfer, and a list of all circuit blocks with outputs dependent on the value or transitions of this level. It is convenient for the simulation program to be able to access this information no matter what the source of the output signal might be. Therefore output signal information is stored in the same format for flip-flops, combinational logic blocks and level delay lines.

Flip-flops are organized into n-length strings in the data structure, where the value of n depends on the machine the simulation is run on.

Registers of length n or less are represented as adjacent bits on the same string and larger registers are represented as adjacent bits on two or more flip-flop strings. This allows straightforward register

<sup>12</sup> Only single bit values are used in this Ideal Model structure because level hazard detection is not included.

transfer specifications. To preserve uniformity in accessing output signal information and to allow simplified specification of a group of levels for Transfers, combinational logic blocks and level delay lines are also organized in n-length strings. Levels which are sources for the same multiple-line Transfers, or which are indexed bits of the same level register in the design language description, are ordered together within the same string. This presents an optimization problem because the same level may be a source for several transfers.

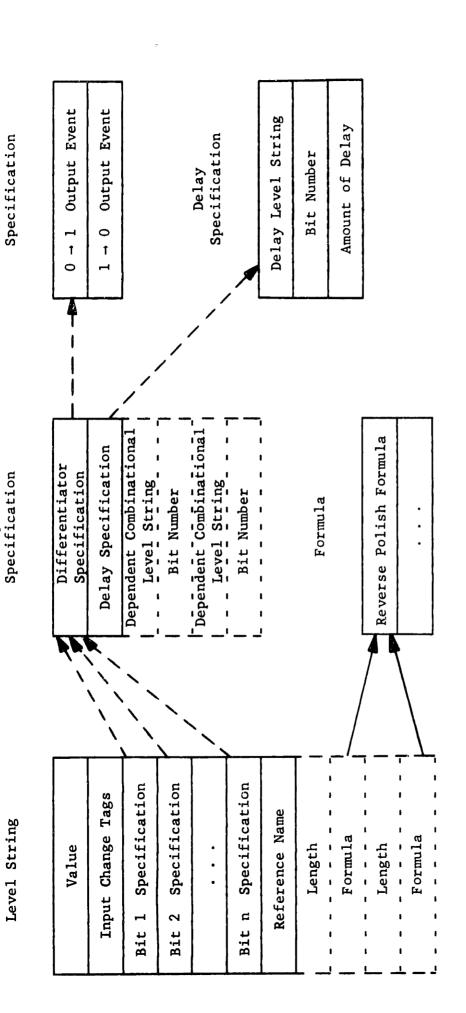

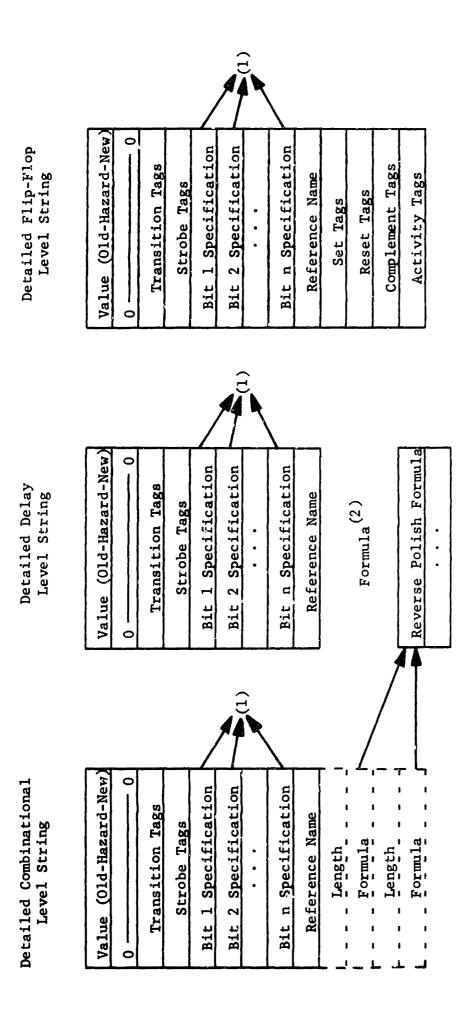

Figure 4-1 illustrates the data element representing a string of combinational logic blocks. The conventions used in the figures illustrating data elements are as follows:

- a) Small blocks containing information are called cells.

- b) Cells outlined in solid lines are part of fixed block made up of adjacent registers of memory.

- c) Cells outlined in dotted lines are part of a list made up of generally non-adjacent registers of memory threaded together with pointer addresses.

- d) Solid arrows between cells indicate that the source cell contains a pointer to a destination element of the type shown.

- e) Dotted arrows are the same as solid ones except that the source cell may contain the null pointer indicating a void destination.

Although all cells are represented in the figures by the same size blocks, this does not imply that all cells need be the same size in the

Differentiator

Output

Combinational

FIGURE 4-1

Combinational Level String Data Elements

data structure. The amount of information stored in a cell varies and there may be circumstances where it is worthwhile having different size cells. A case in point is a two-cell location specification of a combinational level bit. The first cell contains the address of the combinational Level String and the second cell contains the bit number. It is possible to include all of this information in a single word for many computers. Therefore cell is not necessarily synonymous with computer word or address field.

The data element for a combinational Level String consists of an n + 4 cell fixed block followed by a variable length list. The first cell in the element contains the values last calculated for the n output levels. Cell 2 contains an Input Tag bit for each of the output values. A "1" indicates that one of the inputs to that combinational logic block may have changed since the last time the output value was re-evaluated; a "0" indicates the output value is still valid. The next n cells contain pointers to Output Specifications for each of the combinational blocks. The next cell contains a reference name which is used by the routine which translates back and forth between the data structure and the design language.

The last cell in the element contains a pointer to a list specifying formulas to be used to compute the output level values. The first cell on this list contains the number of bits for which the first formula is valid. The second cell has a pointer to a formula for these bits.

Next follow pairs of lengths and formulas until the end of the list is reached. If some of the bits on the combinational Level String are unused, the list ends before the sum of the lengths totals up to n.

The formulas themselves are modified Reverse Polish representations of combinational formulas found in the design language description itself. <sup>13</sup> For example, the formula  $\{A[0:4] \land (\neg B[3:7] \lor C[0:4])\}$  would be translated  $\{A', a, B', b, \neg, C', c, \lor, \land\}$ , where A', B', and C' are pointers to the level strings representing A, B and C, and A, A and A and A are the bit numbers of A[0], A[0] and A[0] respectively. Each symbol is contained in its own cell on the formula and operators must be distinguishable from pointers to level strings. Figure 4-1 shows that Formulas are represented in fixed blocks. This is done because it is unlikely that a formula would be modified incrementally; more likely it would be completely changed.

The structure for an Output Specification is a three-cell fixed block and a variable length list. If the level feeds a differentiator, the first cell on the block points to a two-cell Differentiator Specification. The first cell on this fixed table points to the Event, if any, triggered by a "O" to "1" transition of the output level. The second cell is for "1" to "O" transitions. If the output level feeds a delay line the second cell of the Output Specification contains a pointer to a Delay Specification. The first two cells of the Delay Specification indicate the delay string and bit number of the delay line and the third cell specifies the amount of delay. There is never a need for a level to feed more than a single delay line because any parallel network of ideal delays and combinational logic can be converted

<sup>13</sup> See Appendix C for a detailed discussion of Formulas.

to an equivalent serial network. The third cell in the Output Specification points to the list of all combinational logic blocks which use the level output as an input. When an Input Change Tag is set for some level during a simulation, these lists are used to propagate input changes to all combinational logic blocks dependent upon that level.

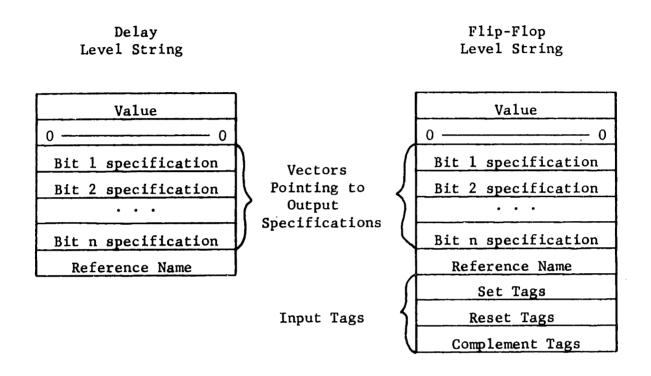

The data elements for Delay Level and Flip-Flop Level Strings are given in Figure 4-2. Note that values, output specification pointers and reference names are arranged as they were for combinational Level Strings. The values of delay lines and flip-flops are always kept up-to-date and their input change tags (second cell) are always zero. Thus it is not necessary for the simulation routines which evaluate combinational level values, test for transfer level values, or require output specification information, to distinguish between the three types of levels.

Level delay line inputs are specified at their source - only values, output specifications and reference names are included in Delay Level String data elements. Information about flip-flop inputs is included in the Transfer data elements. However it is quite possible for one Transfer to be resetting a flip-flop at the same instant another is setting or complementing it. This could be handled by the simulation program by arbitrarily allowing one or the other to have precedence depending on the order they are acted upon. Logic errors of this type are considered to be important enough, even at this level of simulation, to include additional information in the data structure for their detection. Therefore separate cells are included in Flip-Flop Level String elements to accumulate set, reset and complement input activations

during an instant of time. At the end of the instant, this information is used to re-evaluate the flip-flop values and detect flip-flop input timing errors.

4

FIGURE 4-2

Delay and Flip-Flop Level String Data Elements

The level elements of Figure 4-3 have been included to model constant levels (wires to power busses) and standard addressable memories. The Memory Block may be used to ease the modeling of interfaces with non-logic devices such as core memories, tape drives and drums. Input change tags are included as part of each constant Level String for compatibility with Combinational Level Strings, although the tags are always reset. The memory model is so different than the other level sources that no attempt was made to make it compatible with them. The first four cells

specify address length, location, <sup>14</sup> maximum value, m, and a reference name for use of the translation routine. The next m + 1 cells represent the simulated memory. If it is necessary to simulate a memory with word length greater than the memory cell size, two or more Memory Blocks with the same address must be used. Memories act as the sources or destinations of a special set of Transfer operations.

Constant Level String

Memory

**Value**0 ----- 0

Address Specification Address Length

Level String

High Order Bit Number

Maximum Address m

Reference Name

Word 0

Word 1

...

Word m

FIGURE 4-3

Constant Level and Fixed Memory Data Elements

This implies that the address field cannot be any longer than n, the number of bits in a level string. This is reasonable because it should not be necessary to simulate large memories.

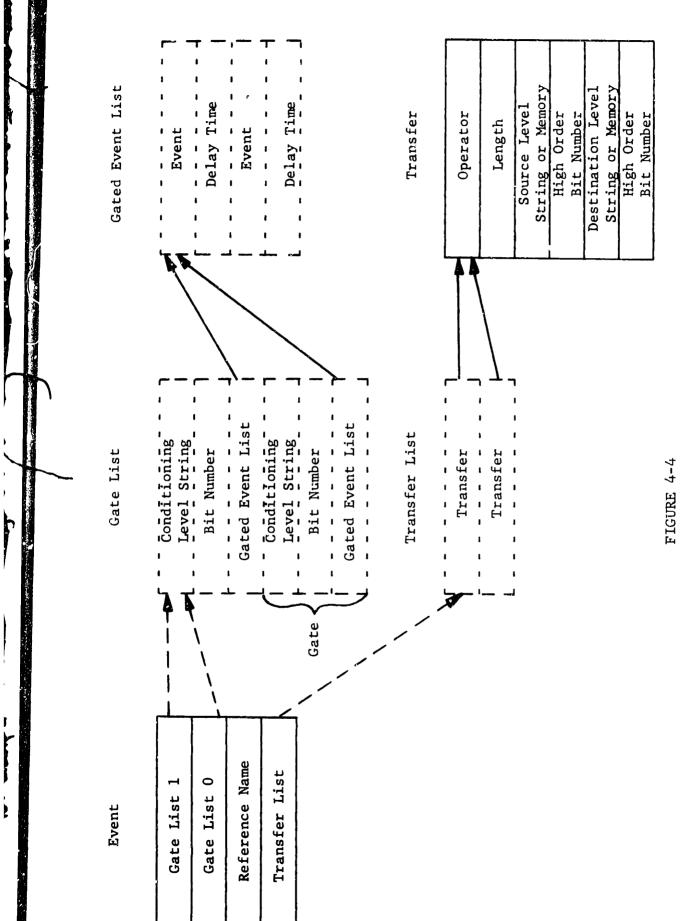

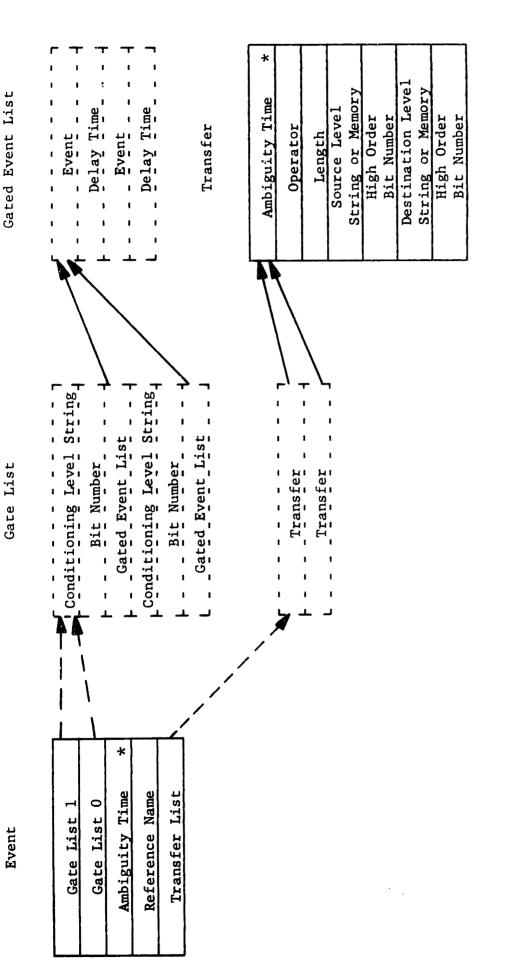

### B. Control Logic

The data elements representing control logic are shown in Figure 4-4. The first two cells of an Event element point to Gate Lists which represent the control gates strobed by the Event. The gates in Gate List 1 are conditioned by levels with value "1" and those on Gate List 0 by levels with value "0". The first two cells of each gate specification list the level string and bit number of the conditioning level.

The third cell points to the list of Events triggered if the conditioning level has the right value. Associated with each Event on an Event List is a delay time before activation; pulse delay lines are built in here.

by the routine which translates back and forth between the data structure and the design language. The last cell points to the list of Transfers which take place when the Event becomes active. Unlike the design language, all Transfers are unconditional. Conditional Transfers are achieved by introducing a new conditional Event which activates the Transfer. This simplifies the data structure by eliminating the need for equivalent of a "Transfer Gate List" without reducing the generality of the structure.

The first cell of a Transfer element specifies its type. Figure 4-5 contains the truth tables for the set of transfers available with standard set-reset-complement flip-flops. A complete set of eight is included to transfer source level strings to destination flip-flop strings. A second set is used to transfer Memory Block contents to flip-flop strings, a third if for level string to memory transfers and a fourth for memory to memory transfers. These sets must be distinguishable because of the format differences between Memory Blocks and level strings. Jam transfers

Control Logic Data Elements

| Transfer Name             | Symbo1                      | Resultant B Value |   |   |    |  |

|---------------------------|-----------------------------|-------------------|---|---|----|--|

| Jam                       | A ⇒B                        | 0                 | 0 | 1 | 1  |  |

| One's Set                 | <b>A</b> → <b>B</b>         | 0                 | 1 | 1 | 1  |  |

| Zero's Reset 15           | $A \sim B$                  | 0                 | 0 | 0 | 1  |  |

| One's Complement          | A † B                       | 0                 | 1 | 1 | 0  |  |

| Negative Jam              | — A ⇒ B                     | 1                 | 1 | 0 | 0  |  |

| Zero's Set                | — A → B                     | 1                 | 1 | 0 | 1. |  |

| One's Reset 15            | <b>−</b> <sub>1</sub> A ~ B | 0                 | 1 | 0 | 0  |  |

| Zero's Complement         | — A ↑ B                     | 1                 | 0 | 0 | 1  |  |

| Values Before Transfer    | <b>S</b> A                  | 0                 | 0 | 1 | 1  |  |

| , and a point it who have | <b>E</b> B                  | 0                 | 1 | 0 | 1  |  |

FIGURE 4-5

Transfer Effect Table

This is consistent with the present formulation of the design language. I would prefer that the meaning of the symbol "~" be changed so that a destination bit is reset if the corresponding source bit is a one rather than a zero, as it is presently defined. This makes the placement of the source gate on the true or false side of a flip-flop consistent with set and complement transfers and eliminates the need for an implied inverter when a combinational level is used as a reset transfer source.

are all that are absolutely necessary for memory reading and writing, but the additional transfers are easily and inexpensively included and may eliminate the need for a memory buffer register to be included on a flip-flop string. A special transfer is included which causes termination of a simulation when it is activated. The number of contiguous bits being transferred is contained in cell two of each Transfer element. Cells three and four specify the source level string or memory and the left-most bit number. Cells five and six do the same for the destination.

## C. Time Queuing and Miscellaneous Lists

This part of the data structure satisfies needs for data fields which vary during a simulation. This includes the queuing of future simulation activity, handling recursive subroutine arguments and providing a means for storing input and output data which varies in length during a simulation.

An important part of this structure is shown in Figure 4-6. The Activity Queue, AQ, is a time-ordered list of future Events to be activated and Delay values to be changed. When the simulation program determines that an Event or Delay Level value change is to occur at some time t, an entry is added to the Event List or Delay Value List associated with t. If there is no previous entry on the AQ at time t, one is inserted. The first cell on the AQ contains the present value of simulated time and is called the Clock. The Clock is stepped by deleting the first three cells of the AQ. The second cell points to the Event List which is presently active; this is called the Immediate Event List. Likewise, the third cell points to the Immediate Delay Value List.

| Flip-Flop Level String 4  Bit Number 4 Flip-Flop Level String 4 Flip-Flop Level String 4 L - Bit Number 5                                                  | Flip-Flop Tag List  [Flip-Flop_Level_String]    Bit_Number        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Event List  Time  Time  Event List  Delay Value List  Event List  Delay Value List | Delay Level String + Bit Number +   Bit Number +     Bit Number + |

Active Flip-Flop List

Event List

Activity Queue

FIGURE 4-6

Time Queuing Data Structure

A number of temporary storage lists are kept by the simulation program. Two of these, the Active Flip-Flip and Flip-Flop Tag Lists, are included in Figure 4-6. They are used to keep track of the flip-flops which are changing value at a given instant of time. Additional lists are used to store recursive subroutine arguments. Data lists are used by the simulator to accumulate output messages. A special Transfer operation is provided to add messages to these lists.

### D. Simulation Algorithm

A simulation begins by initializing flip-flop and delay line values, setting all combinational level Input Change tags and setting up the initial AQ. The Active Flip-Flop and Flip-Flop Tag lists are initially empty. The simulation takes off from there and continues until the Halt Transfer is executed or the AQ becomes empty. The algorithm proceeds as follows:

- The Events on the Immediate Event List are activated one at a time until it is emptied.

- a) When an event is activated it is removed from the list.

- b) All conditioning levels on the Event's Gate Lists are tested and new Events are added to the AQ 'C the values are correct.

- c) All transfers on the Event's Transfer List are activated one at a time. Whenever one of a flip-flop's input tags is set for the first time, the flip-flop's level string location and bit number are added to the Active Flip-Flop List. If an attempt is made to set a complement tag when

it is already set, the flip-flop's Reference Name and bit number are given to the translation routine so that the user can be informed that a flip-flop input error has been detected. If the special Terminate Transfer is activated the Simulation Terminate Tag is set and the Reference Name of the Event is stored. This causes the simulation to stop at the end of that instant of time.