## FUNDAMENTAL STUDY OF DC TO DC CONVERSION SYSTEMS

Ъy

#### DAN HOLDEN WOLAVER

B.E.E., Rensselaer Polytechnic Institute (1964)

S.M., Massachusetts Institute of Technology (1966)

# SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY January 22, 1969

| Signature of A | uthor                             |                       |

|----------------|-----------------------------------|-----------------------|

|                | Department of Electrical Engineer | ing, January 22, 1969 |

| Certified by_  | <del>-</del>                      | Thesis Supervisor     |

| Accepted by_   | Chairman, Departmental Committee  | on Graduate Students  |

Archives

MAR 28 1969

### FUNDAMENTAL STUDY OF DC TO DC CONVERSION SYSTEMS

bу

#### DAN HOLDEN WOLAVER

Submitted to the Department of Electrical Engineering on January 22, 1969 in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### **ABSTRACT**

What is the fundamental process common to every dc to dc conversion system? How is the operation of the system limited by the characteristics of the elements composing it? In seeking answers to these questions, the thesis establishes a well-defined framework for discussing the problem. Basic results are stated in purely mathematical form, but the main application here is to electrical networks.

Graph theory is used to find bounds on dc power, ac power, and average voltages and currents within a dc to dc conversion network. The main graph theorems are derived from a theorem by Berge and Ghouila-Houri which does not seem to have received much use previously in electrical network theory.

Optimization techniques, including Pontryagin's principle, are used to relate the dc power, ac power, and average voltage and current of an element to the element's characteristics.

Also included is a theorem bounding the dc gain of a positive operator feedback system with one time-varying unit. This result is applied to electrical networks to show that every dc to dc conversion network must include at least two resistors which are time-varying and/or nonlinear.

Thesis Supervisor: Roger W. Brockett

Title: Associate Professor of Electrical Engineering

#### ACKNOWLEDGMENT

The author's appreciation and respect for mathematical preciseness and rigour has increased greatly through the encouragement and example of Professor Roger Brockett. His guidance often brought valuable insight to fundamental concepts and approaches. The advice and suggestions of Professor James Roberge and Professor Amar Bose, who served as Readers, were also highly valued.

During discussions, many useful comments and criticisms were received from Ronald Skoog, Professor Paul Penfield, and Professor Jan Willems. Their contributions are greatly appreciated.

Clara Conover has done an excellent job of typing the thesis, correcting errors, and putting the manuscript in a clear, consistent form.

Part of the research was done while the author held a National Science Foundation fellowship. The research was also supported in part by NASA under Grant No. NGR-22-009(124) with the M.I.T. Electronic Systems Laboratory and by the U.S. Army Research Office -- Durham.

#### CONTENTS

| I.         | Introducti                       | page                                                                         | 1  |     |

|------------|----------------------------------|------------------------------------------------------------------------------|----|-----|

| II.        | Defining '                       |                                                                              | 8  |     |

| III.       | Previous Research On The Problem |                                                                              |    | 19  |

| IV.        | Graph Th                         |                                                                              | 21 |     |

| v.         | Resistors                        |                                                                              | 38 |     |

| VI.        | Reactance                        |                                                                              | 62 |     |

| VII.       | Element                          |                                                                              | 81 |     |

| vIII.      | Networks                         | With Only One Type Of Reactance                                              |    | 106 |

| IX.        | Summary                          |                                                                              |    | 113 |

| APPENDIX A |                                  | Discussion of Theorems 4.2 and 4.3 and an Extension of Theorem 4.4 to        |    |     |

|            |                                  | Fields In Three-Space                                                        |    | 118 |

| APP        | ENDIX B                          | A Direct Proof Of Corollary 4.4.1                                            |    | 130 |

| APPENDIX C |                                  | Dc Gain of a Positive Operator Feedback<br>System With One Time-Varying Unit |    | 133 |

#### LIST OF FIGURES

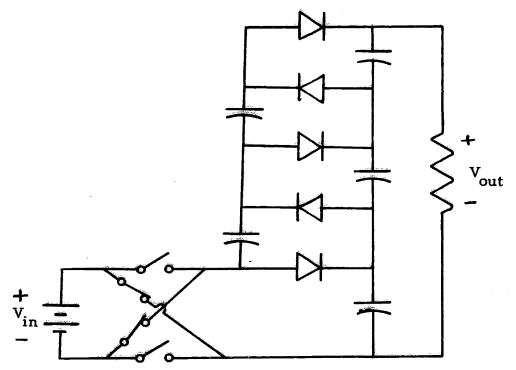

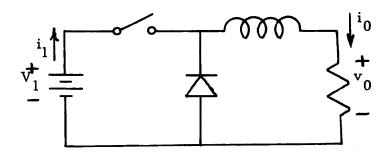

| 1.1 | "Ladder Step-Up" Dc to Dc Conversion Network page                              | 6   |

|-----|--------------------------------------------------------------------------------|-----|

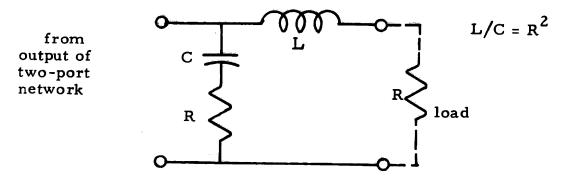

| 2.1 | Output Filter                                                                  | 15  |

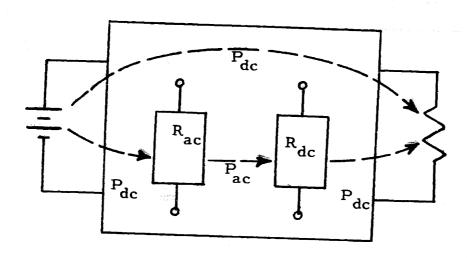

| 5.1 | Power Transfer In a Dc to Dc Conversion Network                                | 55  |

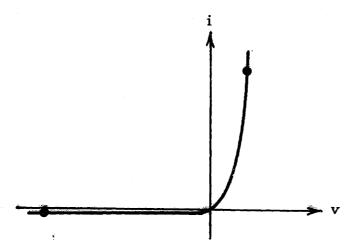

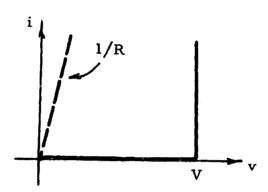

| 5.2 | v-i Characteristic Of a Diode                                                  | 55  |

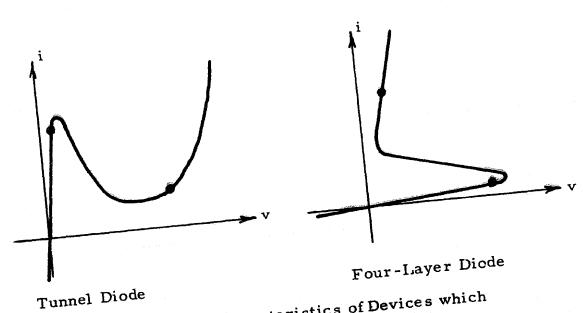

| 5.3 | v-i Characteristics Of Devices Which May Be In the Ac-Active set               | 56  |

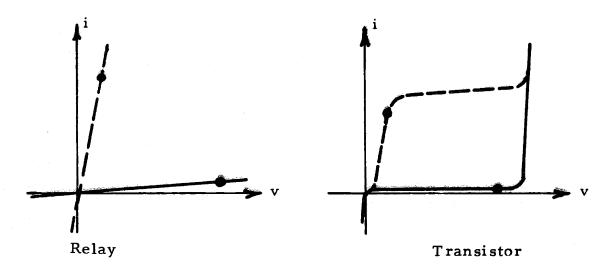

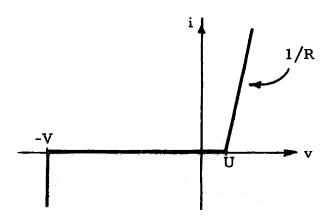

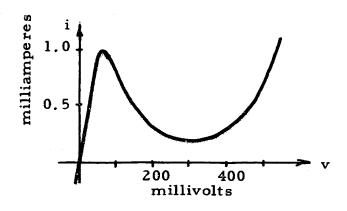

| 5.4 | v-i Characteristics Of Two Time-Varying Devices                                | 57  |

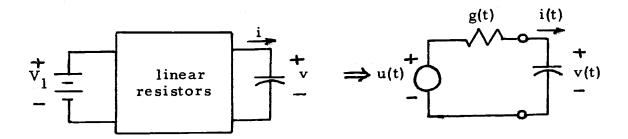

| 5.5 | Simple Dc to Dc Conversion Network                                             | 58  |

| 5.6 | Dc to Dc Conversion Network With Disjoint Primary and Secondary Sets           | 60  |

| 5.7 | Voltage Step-Down Dc to Dc Conversion Network                                  | 61  |

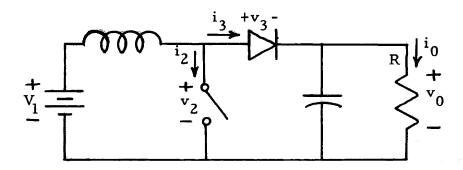

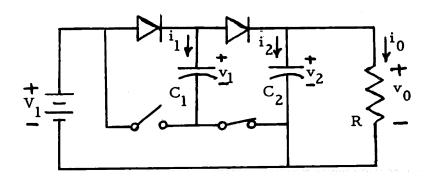

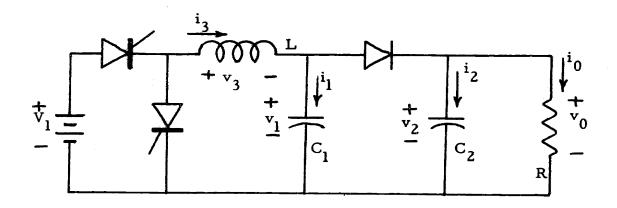

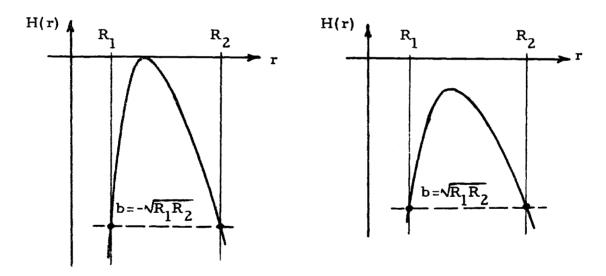

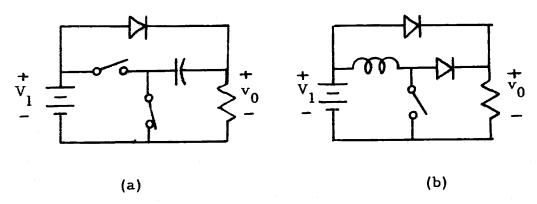

| 6.1 | Dc to Dc Conversion Network Without Inductors                                  | 74  |

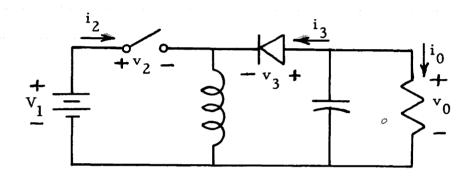

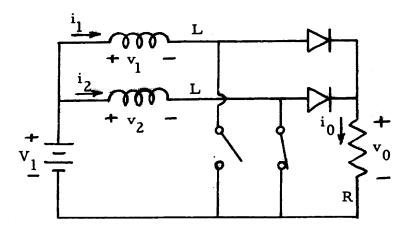

| 6.2 | Dc to Dc Conversion Network Without Capacitors                                 | 76  |

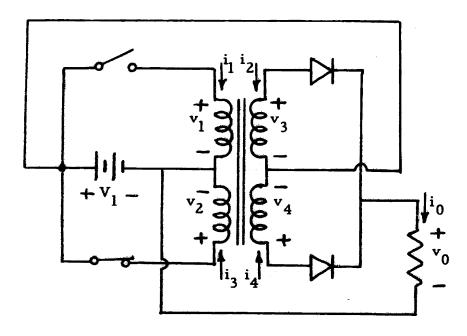

| 6.3 | Dc to Dc Conversion Network Using Inductors With Mutual Coupling               | 77  |

| 6.4 | Dc to Dc Conversion Network Using Both Inductive and Capacitive Energy Storage | 78  |

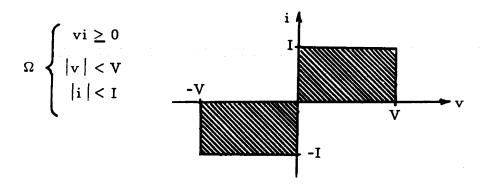

| 7.1 | Region of Allowable Controls                                                   | 82  |

| 7.2 | Loci of Constant Values of the Hamiltonian for p=-V/I                          | 83  |

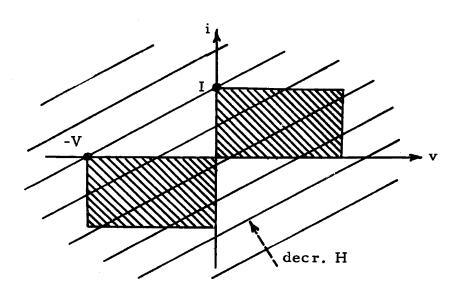

| 7.3 | Hamiltonian vs. Control r                                                      | 89  |

| 7.4 | Time-Varying v-i Characteristic                                                | 95  |

| 7.5 | v-i Characteristic                                                             | 96  |

| 7.6 | v-i Characteristic of Tunnel Diode                                             | 100 |

| 8.1 | Thevenin Equivalent                                                            | 107 |

| 8.2 | Dc to Dc Conversion Networks Using Only One Reactance                          | 111 |

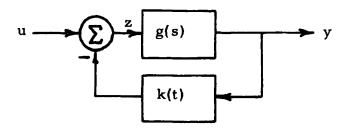

| C.1 | Block Diagram of Feedback System Characterized by Eq. (C.2)                    | 133 |

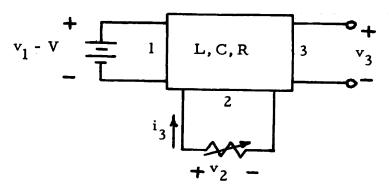

| C.2 | Network with Ports of Interest Extracted To Show No<br>Average Voltage Gain    | 140 |

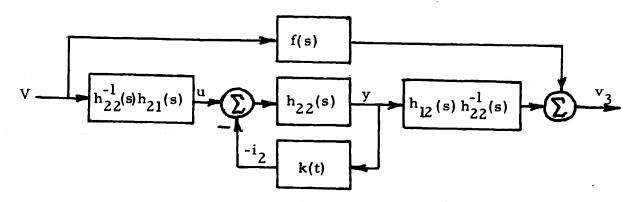

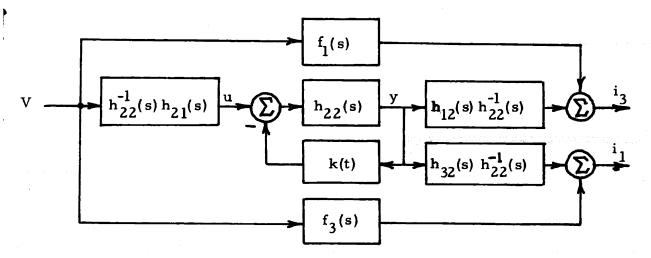

| C.3 | Block Diagram of System Equations                                              | 141 |

| C.4 | Network With Ports of Interest Extracted To Show No Average Current Gain.      | 142 |

| C.5 | Block Diagram of System Equations                                              | 143 |

#### LIST OF DEFINITIONS

| 2.1  | : | voltage across, current through. page                                     | 8  |

|------|---|---------------------------------------------------------------------------|----|

| 2.2  | : | resistor, time-invariant, linear, time-varying/nonlinear, quasi-active.   | 8  |

| 2.3  | : | dc voltage source, dc current source.                                     | 9  |

| 2.4  | : | inductor, linear inductor, inductors with mutual coupling.                | 9  |

| 2.5  | : | capacitor, linear capacitor, reactances.                                  | 10 |

| 2.6  | : | average,                                                                  | 11 |

| 2.7  | : | dc voltage gain, dc current gain.                                         | 11 |

| 2.8  | : | dc to dc conversion network, operating dc to dc conversion network, load. | 11 |

| 2.9  | : | power, average power.                                                     | 12 |

| 2.10 | : | dc power, ac power.                                                       | 12 |

| 4.1  | : | vertex, edge, graph, loop, cut-set, connected, nonseparable.              | 21 |

| 4.2  | : | directed graph.                                                           | 21 |

| 4.3  | : | oriented cut-set, aligned cut-set.                                        | 21 |

| 4.4  | : | oriented loop, aligned loop.                                              | 22 |

| 4.5  | : | flow, positive flow.                                                      | 22 |

| 4.6  | : | tension, positive tension.                                                | 23 |

| 4.7  | : | dual.                                                                     | 23 |

| 5.1  | : | dc-active set, ac-active set.                                             | 39 |

| 5.2  | : | corresponding dc network.                                                 | 39 |

| 5.3  | : | primary set, secondary set.                                               | 39 |

| 5.4  | : | directed graph generated by a network.                                    | 39 |

| 5.5  | : | dual,                                                                     | 39 |

#### I. INTRODUCTION

- 1.1 Objectives: The purpose of the thesis is to meet to some degree the following main objectives:

- 1. To establish a framework for the discussion and investigation of the dc to dc conversion problem. It is hoped that the definitions and approaches giver here will serve as a clear and rigorous foundation for this and future study of the problem. An attempt has been made to avoid leaving concepts undefined, making assumptions without justification, and using "folk lore".

- 2. To expose the basic concept behind the dc to dc conversion process--the features common to every dc to dc conversion system. As will be shown, every dc to dc conversion network must include at least two resistors\* which are time-varying and/or nonlinear. The conversion process can be viewed in terms of their operation.

- 3. To indicate the different types of dc to dc conversion systems.

Another feature common to all dc to dc conversion networks is that they include at least one reactance. The different types of networks can then be classified according to the types of reactances present.

- 4. To establish a relationship between the port parameters of a dc to dc conversion system and the parameters of the elements composing it. Most of the thesis is devoted to this objective, and the results throw some light on the other objectives. The two classes of parameters to be related might be called the converter and element specifications or the

Resistors are defined as the broadest sense of passive resistors (see Definition 2.2).

external and internal parameters. Below is a list of the parameters to be considered in this thesis.

#### External

- 1. Voltage (or current) step-up.

- 2. Output voltage (or current).

- 3. Output power.

- 4. Efficiency.

#### Internal

- 1. Number of switches.

- 2. Number of capacitors.

- 3. Number of inductors.

- 4. Presence of mutual coupling.

- 5. Power storage capability of reactances.

- Voltage and current capability of elements.

- 7. Lossiness of elements.

- 8. Frequency limitations of switches.

Other external parameters which are usually of importance are output ripple, regulation, stability, and nonelectrical considerations such as size, weight, and cost. The thesis will not be directly concerned with these parameters.

1.2 Scope: The term "systems" in the thesis title suggests considerations broader than just electrical networks. While application to electrical networks is the underlying motivation and primary focus of the thesis, an attempt has been made to keep the development general. All basic results are stated in purely mathematical terms so that they may be applied to any system which meets the conditions set forth.

As will be seen in the mathematical development, a dc to dc conversion system in the broadest sense is a system which can be reduced to a linear graph representation. One set of variables must be a flow (satisfy Kirchoff's current law), and a second set must be a tension

(satisfy Kirchoff's voltage law). There must be only one (source-like) edge of the graph for which the average of the product of its flow variable and tension variable is negative, and one of the two variables must be constant. There must be another edge for which the average of one of the variables is greater than the like (flow or tension) variable of the "source-like" edge. Any of the basic results of the thesis can be immediately applied to a system which meets these conditions.\*

In the broadest sense power conditioning may be defined as the process of receiving power with a given voltage or current waveform and delivering (almost all) that power with a different waveform. Then dc to dc conversion is a form of power conditioning since the average voltage or current level is changed.

Another type of power conditioning is frequency conversion; power is received "at a given frequency" (see Definition 2.10) and delivered at another. Examples of systems satisfying this description are modulation mixers, parametric amplifiers, do to ac inverters, and ac to do rectifiers. It will be shown in the thesis that a necessary part of do to do conversion is do to ac and ac to do power conversion within the network. Therefore this thesis also deals with frequency conversion where one of the frequencies is zero (dc).

An example of a nonelectrical system which meets the above conditions could be a system of one-way toll roads. The tolls can be adjusted to always satisfy Kirchoff's voltage law, and the flow of cars per minute satisfies Kirchoff's current law. Let one road have a fixed negative toll, and let this be the only road on which the net transfer of money at the end of some period is from the tollgate keeper to the drivers. If the number of cars passing over this road in the period is less than the number of cars passing over another road in the period, then the system is a dc to dc conversion system. If Theorem 4.3 is applied to this system, one result is that there are at least two roads for which the toll is not constant.

Several of the basic results of the thesis follow from Theorems 4.2 and 4.3, which might be called "positive decomposition theorems for positive flows and positive tensions." They appear to be due to Berge and Ghouila-Houri (3); the author has been unable to find them presented elsewhere in the literature.

Theorem 4.4, Corollary 4.4.1, and Theorem 4.5 make use of these theorems. Theorem 4.4 implies what may be a new necessary condition on resistive n-ports (see Theorem 4.6). In Appendix A Theorem 4.4 is generalized to fields in three-space. Corollary 4.4.1 implies that a set of resistors cannot produce a voltage or current greater than the sum of the voltages or currents of the sources to which it is connected (see Appendix B). This is believed to be the first that a topological proof of this intuitive fact has been given.

Theorems 5.1 and 5.2 imply that every dc to dc conversion network must include at least two resistors that are time-varying and/or non-linear. Appendix C proves this result from a different approach, giving a basic result for a feedback system with positive operators.

1.3 Need for Research: There has been a lack of basic research in the study of dc to dc conversion systems. Most works on the subject have dealt with specific network designs or narrowly restricted classes. To the author's knowledge, the only works dealing with dc to dc conversion in a broad, fundamental way have a master's thesis by the author (16) and a paper by Moore and Wilson (8). The work by Moore and Wilson, described in Chapter III, served as the starting point for several results in this thesis.

The objectives given in the first section indicate the gaps in knowledge which the thesis seeks to fill. The assumption is, of course, that the answers to such fundamental questions will aid in the design of dc to dc conversion networks. The method of design has generally been intuitive or "cut-and-try" as a result of not knowing basic relationships between element parameters and converter parameters.

A sample design problem will illustrate some of the difficulties encountered in trying to select a configuration and component values without the knowledge of basic relations. Suppose that an engineer is given the following specifications for a dc to dc converter:

voltage in: 10 volts dc

voltage out: 40 volts dc

current out: 2 amps dc

efficiency:  $\geq 85\%$

output ripple:  $\leq 5\%$

size, weight, and cost restrictions

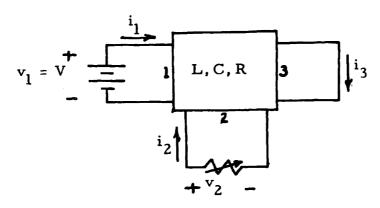

The engineer decides to try the design using no inductors since capacitors seem easier to work with than coils. An all-capacitor converter which he has seen frequently is the "ladder step-up configuration" shown in Fig. 1.1.

The configuration does not seem to require too many capacitors and switches, so the engineer decides to use this network.

He knows that it is good to use as large a capacitor as possible, so he chooses  $10,000~\mu f$ , the largest permitted by the size and weight restrictions. These also have a fairly small "equivalent series resistance" of 0.06~ohms, which should be good for efficiency.

For a low output ripple, the switching frequency should be high. The 0.6 ms time constant of the capacitors restricts the frequency of operation to 400 Hz.

Fig. 1.1 "Ladder Step-up" dc to dc Conversion Network

The engineer then measures or calculates the losses in the network: 4 watts in the switches, 5 watts in the diodes, and 13 watts in the equivalent series resistance of the capacitors. These losses reduce the output voltage to 40 from the ideal 50, as required, but the efficiency is only 78%! Besides that the output ripple is 10%.

Were the specifications given the engineer unrealistic, considering available components? Is there another "all-capacitor" configuration which will use less capacitors and do the job better? Was it wrong to try to do without inductors in this case?

It is hoped that the results of this thesis will answer questions of this nature. 1.4 Outline of Approach: After establishing some terminology and concepts in Chapter II, we will derive some basic theorems in graph theory in Chapter IV. Chapters V and VI apply these results to do to do conversion networks to obtain some bounds on power, voltage, and current associated with the elements in terms of the external network parameters. In Chapter VII the power, voltage, and current associated with an element are related to the element's characteristics. Thus a relationship is finally established between the external and the internal parameters of the network (see Objective 4).

#### II. DEFINING THE PROBLEM CONTEXT

There are many types of dc to dc conversion systems which are in use and many more which exist in theory. The treatment in this thesis is not so general as to include all these systems, but is restricted to purely electrical systems. This excludes systems which include rotating machines, intermediate stages of radiant or thermal energy, etc. The following definitions give a further and more precise description of the context of the investigation.

Definition 2.1: When the <u>voltage across</u> an element (or a port) and the <u>current through</u> an element (or a port) are referred to, the usual convention of the current entering the positive terminal of the voltage is assumed.

<u>Definition 2.2</u>: A <u>resistor</u> is an element which constrains the voltage v across it and the current i through it according to a relation

$$f(v,i,t) = 0$$

for which any v and i which satisfy the constraint for some time t also satisfy

$$vi \ge 0$$

Note that this definition classifies diodes, transistors, switches, and most passive devices without energy storage as resistors.

The element defined here is usually called a "passive resistor". However, there will never be need to refer to resistors that are not passive.

The resistor is called <u>time-invariant</u> if the constraint function f is not dependent on time.

The resistor is called linear if the constraint can also be written

$$v = r(t) i$$

A resistor that is either not time-invariant or not linear will be called <u>time-varying/nonlinear</u>.

A resistor is called <u>quasi-active</u> if the constraint is f(v,i,t) = 0, and there exist  $v_1$ ,  $i_1$ ,  $t_1$ ,  $v_2$ ,  $i_2$ , and  $t_2$  such that

$$f(v_1, i_1, t_1) = 0$$

$$f(v_2, i_2, t_2) = 0$$

$$v_2 > v_1$$

$$i_2 < i_1$$

Moore and Wilson (8) call a resistor so defined an "active resistor", but this is usually used to indicate a resistor that is not passive.

<u>Definition 2.3</u>: If the voltage v across an element and the current i through an element are constrained according to the relation

the element is called a dc voltage source.

If the constraint can be written

the element is called a dc current source.

<u>Definition 2.4</u>: An <u>inductor</u> is an element which constrains the roltage v across it and the current i through it according to the following relations:

$$v = d\lambda/dt$$

$$i = f(\lambda)$$

where  $f(\lambda)$  is a monotonic increasing function of  $\lambda$  such that f(0) = 0, and  $\lambda < \infty$  for  $f(\lambda) < \infty$ . If f is also linear, then the inductor is called a <u>linear inductor</u>.

Consider two n-vectors  $\underline{v}$  and  $\underline{i}$  where the entries of  $\underline{v}$  and  $\underline{i}$  indicate the voltage across and current through each of n elements. The elements are called inductors with <u>mutual coupling</u> if the constraint on the voltages and currents is given by

$$\underline{\mathbf{v}} = \mathrm{d}\underline{\lambda}/\mathrm{d}t$$

$$\underline{\mathbf{i}} = \underline{\mathbf{f}}(\underline{\lambda})$$

where  $\underline{\lambda}$  is an n-vector, and where the Jacobian matrix  $(\underline{\partial f})/(\underline{\partial \lambda})$  of  $\underline{f}$  is symmetric and positive definite for all  $\underline{\lambda}$ , and where the Euclidean norm  $\|\underline{\lambda}\|$  of  $\underline{\lambda}$  is finite for  $\|\underline{f}(\underline{\lambda})\|$  finite. (This treatment follows Stern (11), p. 24.)

Note that in the case when  $\underline{f}(\underline{\lambda})$  is a diagonal matrix, the elements become inductors without mutual coupling.

<u>Definition 2.5</u>: A <u>capacitor</u> is an element which constrains the voltage v across it and the current i through it according to the relations

$$i = dq/dt$$

$$v = f(q)$$

where f is a monotonic increasing function such that f(0) = 0, and  $q < \infty$  for  $f(q) < \infty$ . If f is also linear, then the capacitor is called a <u>linear capacitor</u>.

The class of reactances consists of inductors and capacitors.

<u>Definition 2.6</u>: The <u>average</u>  $\overline{x}$  of a function of time x is defined by

$$\overline{x} = \lim_{T \to \infty} \frac{1}{T} \int_{0}^{T} x \, dt$$

provided the limit exists. An over-bar is always used to indicate the average operation.

When x is periodic, this definition coincides with the usual concept of average over one period.

Definition 2.7: Consider a two-port with one of the ports designated the "input" and the other port the "output". The dc voltage (current) gain of the two-port is the magnitude of the average of the output voltage (current) divided by the magnitude of the average of the input voltage (current). If Gv represents the dc voltage gain, and voltage the input and output voltage, then

$$G_{v} = |\overline{v}_{0}|/|\overline{v}_{1}|$$

Definition 2.8: Consider a two-port network of resistors, inductors (including mutual coupling), and capacitors, with a dc voltage or current source at the input and a finite, linear, time-invariant resistor (called the <u>load</u>) at the output. If there exists an initial condition of the network such that the two-port has a dc voltage gain or dc current gain greater than unity, then the two-port network together with the dc source and the load is called a <u>dc to dc conversion network</u>. This is basically the same as the definition suggested by Moore and Wilson (8), p. 621.

Notice that a network with a dc voltage source at the input and a dc voltage gain always less than unity is considered a dc to dc conversion network if the dc current gain can be greater than unity.

A dc to dc conversion network, together with one of its solutions starting from an initial condition that gives a dc gain greater than unity, is called an operating dc to dc conversion network. We will then be able to speak of various voltages and currents in an operating network.

<u>Definition 2.9</u>: The <u>power</u> p(t) absorbed at time t by an element with voltage v(t) across it and current i(t) through it is given by the product

$$p(t) = v(t) i(t)$$

If the power p(t) is known for all t>0, the <u>average power  $\overline{P}$ </u> absorbed (or dissipated) by the element is given by the average of p:

$$\overline{P} = \overline{p} = \overline{vi}$$

<u>Definition 2.10:</u> Suppose that the voltage v(t) across an element and the current i(t) through the element are known for all t > 0. The <u>dc power</u>  $P_{dc}$  <u>absorbed</u> by the element is the product of the averages of v and i:

$$P_{dc} = \overline{v} T$$

When Pdc is negative, it is sometimes convenient to refer to -Pdc as the dc power delivered.

The <u>ac power</u> P ac <u>absorbed</u> by the element is defined as the average power less the dc power:

$$P_{ac} = \overline{P} - P_{dc} = \overline{vi} - \overline{v} \overline{i}$$

The ac power delivered is the negative of Pac.

NOTE: In the case when v and i are composed of a countable number of sinusoids

$$v(t) = V_0 + Re \sum_{i=1}^{\infty} V_i e^{j\omega_i t}$$

$$i(t) = I_0 + Re \sum_{i=1}^{\infty} I_i e^{j\omega_i t}$$

the average power is

$$P = V_0 I_0 + \frac{1}{2} Re \sum_{i=1}^{\infty} V_i I_i^*$$

Then the definition of dc power above coincides with the definition of dc power  $P_0$  as

$$P_0 = V_0 I_0 = \overline{v} \overline{i}$$

(see Penfield (9), p. 2). We also have in this case that the ac power is the sum of the powers at the frequencies other than zero, where the power  $P_i$  at the frequency  $\omega_i$  is

$$P_i = \frac{1}{2} \text{Re } V_i I_i^*$$

Some of the definitions that have been made may seem unnecessarily restrictive or too general. The following remarks will explain the motivation behind some of these definitions.

Remark 2.1: Although most dc to dc converters that are designed are periodic, the operation of averaging was defined in such a way that it did not require a period function. Thus the development in the thesis does not need to bother with specifying a period, although it applies, as a special case, to periodic systems. Also, we will gain some generality with hardly any increase in the complexity of the development.

Remark 2.2: Definition 2.8 has indicated that we will not be considering networks that include ideal transformers. The reason is that the ideal transformer is not a good model of the physical device at zero frequency (dc); and we will be very concerned with the dc characteristics of devices. In fact, if ideal transformers were allowed, the problem

of dc to dc conversion would become trivial in theory. Notice that we have allowed inductors with mutual coupling, which adequately model physical transformers, even down to zero frequency.

Remark 2.3: The definition of a dc to dc conversion network allows for only linear, time-invariant loads. This insures that the load remains distinct from those nonlinear and time-varying resistors within the network which perform the dc to dc conversion. It is true that many practical converters must deliver power to time-varying loads, and there are many problems involving transients and stability with such loads. However, the thesis will not deal with these problems. Also, specifying a linear, time-invariant load will often permit results to be expressed in a simple, meaningful way.

Remark 2.4: The definition of a dcto dc conversion network did not require that the voltage (or current) delivered to the load be constant. This coincides with reality and with most theory, where a small amount of "ripple" is always present at the output. While a good converter has only a small amount of ripple, it would be arbitrary to specify a percentage of ripple below which a network can be called a dc to dc conversion network. Therefore we require only that there be an increase in the level of the average voltage or average current.

Of the average power delivered to the load, only the dc power  $P_0$  is of interest here:

$$P_0 = \overline{v}_0 \overline{i}_0$$

where  $\mathbf{v}_0$  and  $\mathbf{i}_0$  are the voltage across and current through the load. We will not be concerned with how much ac power is delivered to the load. In practice, the ac power can be spearated arbitrarily well from

the dc power, so that as little ac power as desired reaches the load.

This is done by inserting the filter of Fig. 2.1 before the load.

Fig. 2.1 Output Filter

The ripple at the load (and thus the ac power reaching the load) can be made arbitrarily small by increasing L and C. Notice that the output of the two-port network still sees a pure resistance, as required by Definition 2.8.

The following facts point out some basic properties of the elements that have been defined. They are not difficult to prove and, in the case of Property 2.1, can be readily seen from the definitions. In that case no proof is given. Despite their simplicity, however, the properties are fundamental to the development and will be referred to in proving theorems.

Property 2.1: A quasi-active resistor is nonlinear and/or time-varying.

A linear resistor is quasi-active if and only if it is time-varying.

A time-invariant resistor is quasi-active if and only if it is nonlinear and a portion of its v-i characteristic has a negative incremental resistance. <u>Property 2.2</u>: The average voltage across an inductor is zero if the current remains finite. This implies that the dc power absorbed by the inductor is zero.

The average power absorbed by an inductor is zero if the current remains finite. Together with the first statement, this implies that the ac power absorbed by the inductor is zero.

<u>Proof:</u> The definition of an inductor gives us the following relation between the voltage across and the current through the inductor:

$$v = d\lambda/dt$$

$$i = f(\lambda)$$

Now,  $\overline{v} = \lim_{T \to \infty} \int_{0}^{T} v \, dt = \lim_{T \to \infty} \int_{\lambda(0)}^{\lambda(T)} d\lambda$

$$= \lim_{T\to\infty} \frac{1}{T} [\lambda(T) - \lambda(0)]$$

But since i remains finite,  $\lambda(t)$  is finite for all  $t \ge 0$ . Therefore

$$\overline{\mathbf{v}} = 0$$

which proves the first statement.

Now the average power absorbed is

$$\overline{iv} = \lim_{T \to \infty} \frac{1}{T} \int_{0}^{T} f(\lambda) (d\lambda/dt) dt$$

Since  $f(\lambda)$  is a monotonic increasing function of  $\lambda$ , this can be written

$$\overline{iv} = \lim_{T \to \infty} \frac{1}{T} \int_{\lambda(0)}^{\lambda(T)} f(\lambda) d\lambda$$

But  $i = f(\lambda)$  remains finite; say  $|f(\lambda)| \le M$  for  $\lambda$  between  $\lambda(0)$  and  $\lambda(T)$ , which are also finite. Then

$$\left|\overline{\mathrm{iv}}\right| \leq \lim_{T \to \infty} \frac{1}{T} M \left|\lambda(T) - \lambda(0)\right| = 0$$

Therefore

$$\overline{iv} = 0$$

Property 2.3: Consider a set of inductors with mutual coupling.

If the current in each inductor remains finite, the average voltage across each must be zero. This implies that the dc power absorbed by each inductor is zero.

The sum, over the set, of the average power absorbed by each inductor is zero if the currents remain finite. Together with the first statement this implies that the total, over the set, of the ac power absorbed by the inductors is zero.

<u>Proof</u>: The definition of inductors with mutual coupling relates the vectors representing the voltages and currents by

$$\underline{\mathbf{v}} = d\underline{\lambda}/dt$$

$$\underline{\mathbf{i}} = \underline{\mathbf{f}}(\underline{\lambda})$$

The proof that  $\overline{v} = \underline{0}$  proceeds in the same way as the proof for a single inductor.

The total average power absorbed (sum over the set of inductors) is given by

$$\frac{\overline{\underline{i'}\,\underline{v}}}{\overline{\underline{I'}\,\underline{v}}} = \lim_{T \to \infty} \frac{1}{T} \int_{0}^{T} \underline{f'}(\underline{\lambda}) (d\underline{\lambda}/dt) dt$$

Since  $(\partial \underline{f})/(\partial \underline{\lambda})$  is a symmetric, positive-definite matrix for all  $\underline{\lambda}$ , we may write

$$\frac{\underline{i'v}}{\underline{i'v}} = \lim_{T \to \infty} \frac{1}{T} \int_{\underline{\lambda}(0)}^{\underline{\lambda}(T)} \underline{f'(\underline{\lambda})} \ d\underline{\lambda}$$

where the integral is the same for any path between  $\underline{\lambda}(0)$  and  $\underline{\lambda}(T)$  in  $\underline{\lambda}$ -space (see Apostol (1), p. 296). But the current in each inductor remaining finite says  $\|\underline{f}(\underline{\lambda})\|$  is finite; say  $\|\underline{f}(\underline{\lambda})\| \leq M$  on the straight line between  $\underline{\lambda}'(0)$  and  $\underline{\lambda}(T)$ , which also have finite norms. Then

$$\frac{\boxed{\underline{i}'\underline{v}}|\leq \lim_{T\to\infty} \frac{1}{T} nM \|\lambda(T) - \lambda(0)\| = 0$$

Therefore  $\underline{\underline{i'v}} = 0$

<u>Property 2.4:</u> The average current through a capacitor is zero if the voltage remains finite. This implies that the dc power absorbed by the capacitor is zero.

The average power absorbed by a capacitor is zero if the voltage remains finite. Together with the first statement this implies that the ac power absorbed by the capacitor is zero.

The proof is the dual of the proof of Property 2.2.

Property 2.5: The ac power absorbed by a dc voltage source or dc current source is zero.

<u>Proof</u>: The ac power absorbed by an element is defined as  $\overline{vi} - \overline{vi}$ . Now, for a dc voltage source  $v = \overline{v}$ , and for a dc current source  $i = \overline{i}$ . In either case  $\overline{vi} = \overline{vi}$ , and zero ac power is absorbed.

#### III. PREVIOUS RESEARCH ON THE PROBLEM

As mentioned in Chapter I, the only previous general work on dc to dc conversion networks was done by Moore and Wilson (8). This chapter will summarize their contributions.

The objectives of the paper by Moore and Wilson are to establish some definitions as guidelines in discussing the dc to dc conversion problem, to state some "basic conditions" for dc to dc conversion, and to stimulate further basic research in the area of power conditioning.

A somewhat broader context is allowed by Moore and Wilson by allowing a "network" to include nonelectrical energy storage, mechanical power transfer, and time-varying reactances which are conservative. (Compare Definitions 2.2, 2.4, 2.5 and 2.8.) Other than this, their definition of a "dc to dc conversion network" is basically the same as that used in this thesis. (See Definitions 2.3, 2.7, and 2.8.) The "active resistor" defined by Moore and Wilson is the same as the quasi-active resistor of Definition 2.2.

Four basic conditions which all dc to dc conversion networks must satisfy are stated in the paper. These are given below, making use of some definitions in Chapter II. Statements 1) and 2) are proved by Duffin (4) and Leine (7), respectively. Statements 3) and 4) are proved later in this thesis (see Theorem 5.3 and Corollary 5.4.1).

1) A network cannot convert to ac power any portion of the power it receives from a dc source unless the dc source is in a loop which contains a quasi-active resistor and no capacitors. ("Loop" is used as defined by Seshu and Reed (11), p. 15.)

2) The ac power  $-P_{ac}$  which is delivered by a quasi-active resistor with the constitutive relation f(v,i,t) = 0 is bounded by

$$-P_{ac} \ge \max_{\substack{(v_1, i_1) \in S \\ (v_2, i_2) \in S}} [(v_2 - v_1)(i_1 - i_2)]$$

where S is the set of all pairs (v,i) which satisfy f(v,i,t) = 0 for some t.

- 3) A dc to dc conversion network must, within the network, convert at least a portion of the dc power it receives to ac power.

- 4) Let G be the dc voltage gain or dc current gain, which ever is greater than unity. Let  $P_0$  be the dc power delivered to the load. Then the total ac power delivered by some set S of elements in the dc to dc conversion network is bounded by

$$\sum_{k \in S} P_{ac}^{k} \ge \frac{G-1}{G} P_0$$

#### IV. GRAPH THEORY

This chapter will establish some theorems about directed graphs, flows, and tensions. In Chapters V and VI these will be applied to the dc to dc conversion problem. Most of the theorems presented here are not new results but are included to lay the groundwork for Theorems 4.4 and 4.5.

<u>Definition 4.1:</u> We will use the following common terms as defined by Seshu and Read (11): <u>vertex</u>, <u>edge</u>, <u>graph</u>, <u>loop</u>, <u>cut-set</u>, <u>connected</u>, and <u>nonseparable</u>.

The remaining definitions are patterned after Berge and Ghouila-Houri (3). When their term is different, it follows in parentheses the term used here.

<u>Definition 4.2</u>: A <u>directed graph</u> (graph) is a graph for which an orientation has been assigned to each edge in the graph by ordering the pair of endpoints of each edge.

Definition 4.3: An oriented cut-set (elementary coboundary) is a cut-set to which an orientation has been assigned by ordering the pair of maximal connected subgraphs into which the cut-set divides the graph.

Let the edges of a directed graph be ordered. Then an oriented cutset in the graph is identified with an ordered set  $\{q_k\}$  where

An <u>aligned cut-set</u> (cocircuit) is an oriented cut-set for which the orientation of the edges in the cut-set correspond with the orientation of the cut-set. Then if  $\{q_k\}$  is an aligned cut-set, each  $q_k$  is 0 or 1.

<u>Definition 4.4:</u> An <u>oriented loop</u> (elementary cycle) is a loop to which an orientation has been assigned by ordering the vertices in the loop such that successive vertices are the endpoints of an edge in the loop.

Let the edges of a directed graph be ordered. Then an oriented loop in the graph is identified with an ordered set  $\{b_k\}$  where

An <u>aligned loop</u> (circuit) is an oriented loop for which the orientation of the edges in the loop correspond with the orientation of the loop. If  $\{b_k\}$  is an aligned loop, then each  $b_k$  is either 0 or 1.

Definition 4.5: Let the n edges of a directed graph be ordered. A  $\frac{\text{flow}}{\text{flow}}, \text{ relative to the graph, is an ordered set } \{\phi_k\} \text{ of real numbers,}$  with each member of  $\{\phi_k\}$  corresponding to an edge of the graph, which satisfies

$$\sum_{k=1}^{n} q_k \phi_k = 0$$

for every oriented cut-set  $\{q_k\}$  in the graph.

It can be shown that it is sufficient if the condition is satisfied for every cut-set consisting of edges incident at a node.

A positive flow is a flow  $\{\phi_k\}$  for which each member  $\phi_k$  satisfies  $\phi_k \geq 0$  .

Notice that a linear combination of flows is a flow. If a flow is a function of time, then a linear function or a linear functional of the flow is a flow. That is, if  $\{\phi_k(t)\}$  is a flow for all t, then  $\{d\phi_k/dt\}$  and  $\{\int_a^b f(t)\phi_k(t)dt\}$  are flows.

In electrical engineering the condition on a flow is called Kirchoff's current law because the currents in a network are observed to satisfy the condition.

Definition 4.6: Let the n edges of a directed graph be ordered. A tension, relative to the graph, is an ordered set  $\{\theta_k\}$  of real numbers, with each member corresponding to an edge of the graph, which satisfies

$$\sum_{k=1}^{n} b_{k} \theta_{k} = 0$$

for every oriented loop  $\{b_k\}$  in the graph.

(

A positive tension is a tension  $\{\theta_k\}$  whose members satisfy  $\theta_k \ge 0$ . As for a flow, a linear combination of tensions is a tension. If  $\{\theta_k(t)\}$  is a tension for all t, then  $\{d\theta_k/dt\}$  and  $\{\int_a^b f(t)\theta_k(t)dt\}$  are tensions.

The condition on a tension is often called Kirchoff's voltage law because voltages in a network are observed to satisfy the condition.

<u>Definition 4.7:</u> Given a condition, result, or proof, the <u>dual</u> condition, result, or proof is obtained by interchanging the terms "loop" and "cut-set", and "flow" and "tension".

Theorem 4.1 (Berge and Ghouila-Houri (3), p. 147): Consider the space  $\mathbb{R}^n$  of ordered sets of n real numbers. Given a directed graph,  $\{\phi_k\}$  is a flow if and only if

$$\sum_{k=1}^{n} \theta_{k} \phi_{k} = 0$$

for every tension  $\{\theta_k^{}\}$  in  $\,{\rm R}^n^{}.\,$  Given a directed graph,  $\,\{\theta_k^{}\}\,$  is a tension if and only if

$$\sum_{k=1}^{n} \theta_k \phi_k = 0$$

for every flow  $\{\phi_k\}$  in  $R^n$ .

This may be stated: the space of flows and the space of tensions are orthogonal, and they span the space  $\,\mathbb{R}^n$ .

This important theorem is known in electrical engineering as

Tellegen's theorem after the author who first indicated its wide application to network theory (14). For a comprehensive discussion of the

history and application of Tellegen's theorem, see Penfield et al. (10).

Theorem 4.2 (Berge and Ghouila-Houri (3), p. 143): Given a directed graph with n edges, the set  $\{\phi_k\}$  is a positive flow if and only if

$$\phi_{k} = \sum_{\ell=1}^{m} b_{k\ell} \mu_{\ell}$$

; k=1,2,...,n

where the set  $\{b_{k\ell}\}$  over the index k is the  $\ell^{th}$  aligned loop of a set of m aligned loops, and the  $\mu_{\ell} \geq 0$ . As noted in Definition 4.4, each  $b_{k\ell}$  is either 0 or 1.

Since  $\mu_{\ell}\{b_{k\ell}\}$  is a positive flow for each  $\ell$ , this theorem amounts to expressing a positive flow as a sum of "positive loop flows". (See Appendix A for a descriptive discussion.)

Theorem 4.3 (Berge and Ghouila-Houri (3), p. 146): Given a directed graph with n edges, the set  $\{\theta_k\}$  is a positive tension if and only if

$$\theta_{\mathbf{k}} = \sum_{\ell=1}^{\mathbf{m}} q_{\mathbf{k}\ell} \omega_{\ell}$$

;  $k=1,2,\ldots,n$

where the set  $\{q_{k\ell}\}$  over the index k is the  $\ell^{th}$  aligned cut-set of a set of m aligned cut-sets, and the  $\omega_{\ell}$  corresponding to each cut-set satisfies  $\omega_{\ell} \geq 0$ . As noted in Definition 4.3, each  $q_{k\ell}$  is either 0 or 1.

Since  $\omega_{\ell}\{q_{k\ell}\}$  is a positive tension for each  $\ell$ , the theorem says that a positive tension can be expressed as the sum of "positive cut-set tensions". (See Appendix A for a descriptive discussion.)

Theorem 4.4: Consider a flow  $\{\phi_k\}$  and a tension  $\{\theta_k\}$  relative to a directed graph G. Let the set S of edges of the graph be divided into four sets  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  so that

$$\theta_{\mathbf{k}} \phi_{\mathbf{k}} \geq 0$$

;  $k \in S_4$

Then,

$$(a) \qquad \sum_{\mathbf{k} \in S_1} |\theta_{\mathbf{k}}| \sum_{\mathbf{j} \in S_2} |\phi_{\mathbf{j}}| - \sum_{\mathbf{k} \in S_2} |\theta_{\mathbf{k}} \phi_{\mathbf{k}}| + \sum_{\mathbf{k} \in S_3} |\theta_{\mathbf{k}} \phi_{\mathbf{k}}| \ge 0$$

(b)

$$\sum_{\mathbf{k} \in S_1} |\phi_{\mathbf{k}}| \sum_{\mathbf{j} \in S_2} |\theta_{\mathbf{j}}| - \sum_{\mathbf{k} \in S_2} \theta_{\mathbf{k}} \phi_{\mathbf{k}} + \sum_{\mathbf{k} \in S_3} |\theta_{\mathbf{k}} \phi_{\mathbf{k}}| \ge 0$$

<u>Proof</u>: Reorient the edges of G to form a new directed graph G' as follows: reverse the orientation of the  $k^{th}$  edge if and only if  $k \in S^-$ , where

$$S^- = \{k \in S : \phi_k < 0\}$$

Form a new set  $\{ heta_{\mathbf{k}}^{\mathbf{l}}\}$  by

$$\theta_{\mathbf{k}}' = \begin{cases} -\theta_{\mathbf{k}} & ; & \mathbf{k} \in S^{-1} \\ +\theta_{\mathbf{k}} & ; & \text{otherwise} \end{cases}$$

Form a new set  $\{\phi_k^{\dagger}\}$  by

$$\phi_{\mathbf{k}}^{\mathbf{I}} = |\phi_{\mathbf{k}}^{\mathbf{I}}| \tag{4.1}$$

It should be clear from the construction that  $\{\theta_k'\}$  is a tension relative to G',  $\{\phi_k'\}$  is a positive flow relative to G', and

$$\theta_{\mathbf{k}}^{\dagger} \phi_{\mathbf{k}}^{\dagger} = \theta_{\mathbf{k}} \phi_{\mathbf{k}}$$

;  $\mathbf{k} \in \mathbf{S}$  (4.2)

$$|\theta_{\mathbf{k}}^{'}| = |\theta_{\mathbf{k}}|$$

;  $k \in S$  (4.3)

$$\theta_{\mathbf{k}}' \geq 0$$

;  $\mathbf{k} \in S_4$  (4.4)

Now, from Theorem 4.2 we can find a set L of aligned loops  $\{b_{k\ell}\}$ ;  $\ell \in L$ , with

$$b_{kl} = 0,1$$

for all  $k \in S$ ,  $l \in L$

and a set  $\{\mu_{\boldsymbol{\ell}}\}$  with each member corresponding to a loop in L, and with

$$\mu_{I} \geq 0$$

;  $I \in L$

such that

$$\phi_{\mathbf{k}}' = \sum_{\boldsymbol{\ell} \in \mathbf{L}} b_{\mathbf{k}\boldsymbol{\ell}} \mu_{\boldsymbol{\ell}} \qquad ; \qquad \mathbf{k} \in \mathbf{S}$$

Define a new set  $\{\psi_{\mathbf{k}}^{\dagger}\}$  by

$$\psi'_{\mathbf{k}} = \sum_{\ell \in \mathbf{L}_2} \mathbf{b}_{\mathbf{k}\ell} \mu_{\ell}$$

;  $\mathbf{k} \in \mathbf{S}$

where

$$L_2 = \{l \in L : b_{kl} = 1, k \in S_2\}$$

Then by Theorem 4.2,  $\{\psi_k^i\}$  is a positive flow relative to  $G^i$ . Other properties of  $\{\psi_k^i\}$  are:

$$\psi_{\mathbf{k}}^{\prime} \leq \hat{\phi}_{\mathbf{k}}^{\prime}$$

;  $\mathbf{k} \in S$  (4.5)

$$\psi_{\mathbf{k}}' = \phi_{\mathbf{k}}' \qquad ; \qquad \mathbf{k} \in S_2$$

(4.6)

Then

$$\sum_{\mathbf{k} \in S_2} \phi_{\mathbf{k}}' = \sum_{\mathbf{k} \in S_2} \psi_{\mathbf{k}}' = \sum_{\mathbf{k} \in S_2} \sum_{\mathbf{l} \in \mathbf{L}_2} b_{\mathbf{k} \mathbf{l}} \mu_{\mathbf{l}} = \sum_{\mathbf{l} \in \mathbf{L}_2} \mu_{\mathbf{l}} \sum_{\mathbf{k} \in S_2} b_{\mathbf{k} \mathbf{l}}$$

But for each  $l \in L_2$ ,  $b_{kl} = 1$  for some  $k \in S_2$ . Therefore

$$\sum_{k \in S_2} b_{kl} \ge 1 \quad ; \quad l \in L_2$$

and

$$\sum_{k \in S_2} \phi_k' \geq \sum_{\ell \in L_2} \mu_{\ell}.$$

But

$$\psi_{\mathbf{k}}' = \sum_{\ell \in \mathbf{L}_2} b_{\mathbf{k}\ell} \mu_{\ell} \leq \sum_{\ell \in \mathbf{L}_2} \mu_{\ell} \quad ; \quad k \in S$$

Therefore

$$\psi_{\mathbf{k}}^{\prime} \leq \sum_{\mathbf{j} \in S_{\mathbf{n}}} \phi_{\mathbf{j}}^{\prime} \; ; \; \mathbf{k} \in S$$

(4.7)

Now, since  $\{\theta_k'\}$  is a tension and  $\{\psi_k'\}$  is a (positive) flow, Theorem 4.1 can be applied to give

$$\sum_{k \in S} \theta_k^{\prime} \psi_k^{\prime} = 0$$

or

$$\sum_{\mathbf{k} \in S_1} \theta_{\mathbf{k}}^{\prime} \psi_{\mathbf{k}}^{\prime} + \sum_{\mathbf{k} \in S_2} \theta_{\mathbf{k}}^{\prime} \psi_{\mathbf{k}}^{\prime} + \sum_{\mathbf{k} \in S_3} \theta_{\mathbf{k}}^{\prime} \psi_{\mathbf{k}}^{\prime} + \sum_{\mathbf{k} \in S_4} \theta_{\mathbf{k}}^{\prime} \psi_{\mathbf{k}}^{\prime} = 0$$

Observing that

$$\begin{aligned} &|\theta_{\mathbf{k}}^{\prime}| \geq \theta_{\mathbf{k}}^{\prime} &; & k \in \mathbf{S} \\ &|\theta_{\mathbf{k}}^{\prime}| \geq 0 &; & k \in \mathbf{S}_{\mathbf{4}} \\ &|\psi_{\mathbf{k}}^{\prime}| \geq 0 &; & k \in \mathbf{S} \end{aligned} \tag{4.4}$$

we obtain

$$-\sum_{\mathbf{k}\in \mathbb{S}_{1}}\left|\theta_{\mathbf{k}}^{!}\right|\psi_{\mathbf{k}}^{!}+\sum_{\mathbf{k}\in \mathbb{S}_{2}}\theta_{\mathbf{k}}^{!}\psi_{\mathbf{k}}^{!}-\sum_{\mathbf{k}\in \mathbb{S}_{3}}\left|\theta_{\mathbf{k}}^{!}\right|\psi_{\mathbf{k}}^{!}\leq 0$$

The properties of  $\psi_{\mathbf{k}}^{\prime}$  given in Eqs. (4.5), (4.6), and (4.7) then give us

$$-\sum_{\mathbf{k}\in S_1}|\theta_{\mathbf{k}}^{\prime}|\sum_{\mathbf{j}\in S_2}\phi_{\mathbf{j}}^{\prime}+\sum_{\mathbf{k}\in S_2}|\theta_{\mathbf{k}}^{\prime}\phi_{\mathbf{k}}^{\prime}-\sum_{\mathbf{k}\in S_3}|\theta_{\mathbf{k}}^{\prime}||\phi_{\mathbf{k}}^{\prime}|\leq 0$$

The parameters relative to the graph G' are related to the parameters relative to G by Eqs. (4.1), (4.2), and (4.3). Using these relations, we obtain

$$-\sum_{\mathbf{k}\in S_1} |\theta_{\mathbf{k}}| \sum_{\mathbf{j}\in S_2} |\phi_{\mathbf{j}}| + \sum_{\mathbf{k}\in S_2} |\theta_{\mathbf{k}}\phi_{\mathbf{k}}| - \sum_{\mathbf{k}\in S_3} |\theta_{\mathbf{k}}| |\phi_{\mathbf{k}}| \le 0$$

which gives result (a) of the theorem.

Result (b) of the theorem is the dual of result (a), and its proof is the dual of the above. Theorem 4.3 is used in place of Theorem 4.2 in the proof.

Appendix A gives a theorem involving fields in three-dimensional space. It is analogous to Theorem 4.4 and gives some insight.

Corollary 4.4.1: Consider a flow  $\{\phi_k\}$  and a tension  $\{\theta_k\}$  relative to a directed graph. Let the edges of the graph be divided into

two sets  $\tilde{S}_1$  and  $\tilde{S}_2$  so that

$$\theta_k \phi_k < 0$$

;  $k \in \tilde{S}_1$

$$\theta_{\mathbf{k}} \phi_{\mathbf{k}} \geq 0$$

;  $\mathbf{k} \in \tilde{S}_2$

Then

(a)

$$|\theta_{k}| \leq \sum_{j \in \tilde{S}_{1}} |\theta_{j}|$$

;  $k \in \tilde{S}_{2}$

(b)

$$|\phi_{k}| \leq \sum_{j \in \widetilde{S}_{1}} |\phi_{j}|$$

;  $k \in \widetilde{S}_{2}$

<u>Proof:</u> Consider result (a) of Theorem 4.4. Let a particular edge  $k_0$  of  $\tilde{S}_2$  correspond to  $S_2$ , and let the rest of  $\tilde{S}_2$  correspond to  $S_4$ . Let  $\tilde{S}_1$  correspond to  $S_1$ . Nothing corresponds to  $S_3$ , so that  $S_3$  is empty. Then Theorem 4.4 gives

$$\sum_{j \in \widetilde{S}_{1}} |\theta_{j}| |\phi_{k_{0}}| - \theta_{k_{0}} \phi_{k_{0}} \geq 0$$

Since  $\theta_{k_0} \phi_{k_0} \ge 0$ , we may write

$$\sum_{j \in \widetilde{S}_{1}} |\theta_{j}| |\phi_{k_{0}}| - |\theta_{k_{0}}| |\phi_{k_{0}}| \ge 0$$

Therefore  $|\theta_{k_0}| \leq \sum_{j \in \widetilde{S}_1} |\theta_j|$

But  $k_0$  was any edge of  $\tilde{S}_2$ , so that

$$|\theta_{\mathbf{k}}| \leq \sum_{\mathbf{j} \in \widetilde{\mathbb{S}}_1} |\theta_{\mathbf{j}}| \quad ; \quad \mathbf{k} \in \widetilde{\mathbb{S}}_2$$

which is result (a) of the corollary.

Result (b) of the corollary proceeds in a similar manner from result (b) of Theorem 4.4.

The results of Corollary 4.4.1 are well known in electrical engineering as the fact that a resistive network cannot give voltage gain or current gain. Talbot (13) proved the result for one source (one edge in  $S_1$ .) The result of Corollary 4.4.1, applied to a linear resistive network, is usually proved by applying superposition to Talbot's result.

To the author's knowledge, this is the first time that the results of Corollary 4.4.1 have been proved where more than one source is considered and nonlinear resistors are allowed by topological considerations only.

A direct proof of Corollary 4.4.1 (from Kirchoff's voltage and current laws) is given in Appendix B.

Theorem 4.5: Consider a flow  $\{\phi_k\}$  and a tension  $\{\theta_k\}$  relative to a directed graph G. Let the set S of edges of the graph be divided into four sets  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  so that

$$\theta_k \phi_k \ge 0$$

;  $k \in S_3$

$$\theta_k \phi_k \geq 0$$

;  $k \in S_4$

If (i)

$$|\theta_k| > \sum_{j \in S_1} |\theta_j|$$

;  $k \in S_3$

then (a)

$$|\phi_k| \leq \sum_{j \in S_2} |\phi_j|$$

;  $k \in S_3$

If (ii)

$$|\phi_k| > \sum_{j \in S_1} |\phi_j|$$

;  $k \in S_3$

(but (i) does not necessarily hold), then

(b)

$$|\theta_k| \leq \sum_{j \in S_2} |\theta_j|$$

;  $k \in S_3$

<u>Proof</u>: As in the proof of Theorem 4.4, reorient the edges of G to form a new directed graph G' as follows: reverse the orientation of the  $k^{th}$  edge if and only if  $k \in S^-$ , where

$$S^- = \{k \in S : \phi_k \le 0\}$$

Form a new set  $\{\theta_k^i\}$  by

$$\theta_{k}^{i} = \begin{cases} -\theta_{k} & \text{; } k \in S \\ +\theta_{k} & \text{; otherwise} \end{cases}$$

Form a new set  $\{\phi_k^i\}$  by

$$\phi_{\mathbf{k}}' = |\phi_{\mathbf{k}}| \quad ; \quad k \in S \tag{4.8}$$

It should be clear from the construction that  $\{\theta_k^I\}$  is a tension relative to  $G^I$ ,  $\{\phi_k^I\}$  is a positive flow relative to  $G^I$ , and

$$|\theta_{\mathbf{k}}'| = |\theta_{\mathbf{k}}| \; ; \; \mathbf{k} \in S$$

(4.9)

$$\theta_{\mathbf{k}}^{\prime} = |\theta_{\mathbf{k}}| \; ; \; \mathbf{k} \in S_3$$

(4.10)

$$\theta_{k}^{i} \geq 0$$

;  $k \in S_4$  (4.11)

From Theorem 4.2 we can find a set L of aligned loops  $\{b_{\mathbf{k}\ell}\}$ ;  $\ell \in L$ , with

$$b_{kl} = 0,1$$

for all keS,  $l \in L$

and a set  $\{\mu_{\boldsymbol{I}}\}$  with each member corresponding to a loop in L, and with

$$\mu_{1} \geq 0$$

;  $\ell \in L$

such that

$$\phi_{\mathbf{k}}' = \sum_{\ell \in \mathbf{L}} b_{\mathbf{k}\ell} \mu_{\ell} \quad ; \quad \mathbf{k} \in \mathbf{S}$$

Since  $\{b_{k}\}$  is a loop,  $\ell \in L$ ; and  $\{\theta_{k}'\}$  is a tension, we have by Definition 4.6

$$\sum_{\mathbf{k} \in \mathbf{S}} \mathbf{b_{k} \ell} \boldsymbol{\theta_{k}^{\prime}} = 0 \quad ; \quad \ell \in \mathbf{L}_{3}$$

where

$$\mathbf{L_{3}} = \{\ell \in \mathbf{L} : \mathbf{b_{k} \ell} = 1, \quad \mathbf{k} \in \mathbf{S}_{3}\}$$

or

$$\sum_{\mathbf{k} \in \mathbf{S}_{1}} \mathbf{b_{k} \ell} \boldsymbol{\theta_{k}^{\prime}} + \sum_{\mathbf{k} \in \mathbf{S}_{2}} \mathbf{b_{k} \ell} \boldsymbol{\theta_{k}^{\prime}} + \sum_{\mathbf{k} \in \mathbf{S}_{3}} \mathbf{b_{k} \ell} \boldsymbol{\theta_{k}^{\prime}} + \sum_{\mathbf{k} \in \mathbf{S}_{4}} \mathbf{b_{k} \ell} \boldsymbol{\theta_{k}^{\prime}} = 0 \quad ; \quad \ell \in \mathbf{L}_{3}$$

But

$$|\boldsymbol{\theta_{k}^{\prime}}| \geq \boldsymbol{\theta_{k}^{\prime}} \quad ; \quad \mathbf{k} \in \mathbf{S}$$

and

$$\boldsymbol{\theta_{k}^{\prime}} \geq 0 \quad ; \quad \mathbf{k} \in \mathbf{S}_{4} \quad (4.11)$$

Then

and

$$-\sum_{\mathbf{k}\in\mathbf{S}_{1}}|\theta_{\mathbf{k}}'|+\sum_{\mathbf{k}\in\mathbf{S}_{2}}b_{\mathbf{k}}\theta_{\mathbf{k}}'+\sum_{\mathbf{k}\in\mathbf{S}_{3}}b_{\mathbf{k}}\theta_{\mathbf{k}}'\leq0\quad;\quad \boldsymbol{\ell}\in\mathbf{L}_{3}$$

(4.12)

(4.11)

Assume that condition (i) of the theorem holds. Then substituting according to Eq. (4.9) and Eq. (4.10), the condition gives

$$\theta_k' > \sum_{j \in S_1} |\theta_j'|$$

;  $k \in S_3$

Since

$$b_{kl} = 1$$

for some  $k \in S_3$ , for all  $l \in L_3$

we may write

$$\sum_{\mathbf{k} \in S_3} \mathbf{b_{k\ell}} \; \theta_{\mathbf{k}}' > \sum_{\mathbf{j} \in S_1} |\theta_{\mathbf{j}}'| \quad ; \quad k \in L_3$$

Together with Ineq. (4.12) this requires

$$\sum_{k \in S_2} b_{kl} \theta_k < 0 \quad ; \quad l \in L_3$$

which implies

$$b_{kl} = 1$$

for some  $k \in S_2$ , for all  $l \in L_3$  (4.13)

Now,

$$\sum_{j \in S_2} \phi_j' = \sum_{j \in S_2} \sum_{\ell \in L} b_{j\ell} \mu_{\ell}$$

$$\geq \sum_{j \in S_2} \sum_{\ell \in L_3} b_{j\ell} \mu_{\ell} = \sum_{\ell \in L_3} \mu_{\ell} \sum_{j \in S_2} b_{j\ell}$$

Then, with Eq. (4.13), we have

$$\sum_{j \in S_2} \phi_j' \geq \sum_{\ell \in L_3} \mu_{\ell}$$

We also have

$$\phi_{\mathbf{k}}' = \sum_{\boldsymbol{\ell} \in \mathbf{L}} b_{\mathbf{k} \boldsymbol{\ell}} \mu_{\boldsymbol{\ell}} = \sum_{\boldsymbol{\ell} \in \mathbf{L}_3} b_{\mathbf{k} \boldsymbol{\ell}} \mu_{\boldsymbol{\ell}} \leq \sum_{\boldsymbol{\ell} \in \mathbf{L}_3} \mu_{\boldsymbol{\ell}} \quad ; \quad k \in S_3$$

Therefore

$$\phi_{k}' \leq \sum_{j \in S_{2}} \phi_{j}'$$

;  $k \in S_{3}$

The parameters in graph G' are then related back to the parameters in G by Eq. (4.8) to give

$$|\phi_{\mathbf{k}}| \leq \sum_{\mathbf{j} \in S_2} |\phi_{\mathbf{j}}|$$

;  $k \in S_3$

which proves result (a) of the theorem, given condition (i).

Condition (ii) and result (b) are duals of condition (i) and result (a).

The proof that result (b) follows from condition (ii) is the dual of the above proof.

Theorem 4.4 has a very direct result when applied to resistive n-ports. The following theorem will not be used later in the thesis, but its results may be of interest in characterizing the properties of resistive n-ports.

Theorem 4.6: Consider a resistive n-port (which includes no transformers) whose set S of ports, at a given time, has voltages and currents  $\{v_k\}$  and  $\{i_k\}$ ,  $k \in S$ . Let the ports be divided into three sets:  $\widetilde{S}_1$ ,  $\widetilde{S}_2$ , and  $\widetilde{S}_3$ . Then

$$\sum_{\mathbf{k} \in \widetilde{S}_1} |\mathbf{v}_{\mathbf{k}}| \sum_{\mathbf{j} \in \widetilde{S}_2} |\mathbf{i}_{\mathbf{j}}| + \sum_{\mathbf{k} \in \widetilde{S}_2} \mathbf{v}_{\mathbf{k}} \mathbf{i}_{\mathbf{k}} + \sum_{\mathbf{k} \in \widetilde{S}_3} |\mathbf{v}_{\mathbf{k}} \mathbf{i}_{\mathbf{k}}| \ge 0$$

and

$$\sum_{\mathbf{k} \in \widetilde{S}_{\mathbf{l}}} |\mathbf{i}_{\mathbf{k}}| \sum_{\mathbf{j} \in \widetilde{S}_{\mathbf{2}}} |\mathbf{v}_{\mathbf{j}}| + \sum_{\mathbf{k} \in \widetilde{S}_{\mathbf{2}}} |\mathbf{v}_{\mathbf{k}} \mathbf{i}_{\mathbf{k}}| + \sum_{\mathbf{k} \in \widetilde{S}_{\mathbf{3}}} |\mathbf{v}_{\mathbf{k}} \mathbf{i}_{\mathbf{k}}| \ge 0$$

<u>Proof:</u> Let an element be connected across each of the ports. Then the voltages and currents of the elements can be taken as  $\{v_k\}$  and  $\{-i_k\}$ . (Note that the reference convention necessitates changing the sign of either voltage or current.) Considering Theorem 4.4, let the set  $S_{\ell}$  be the set of elements across the ports in the set  $\widetilde{S}_{\ell}$ , and let  $S_{4}$  be the (linear, time-invariant) resistors in the n-port. Let the resistors and added elements generate the graph G. Then the currents through the resistors and elements are a flow relative to G, and the voltages across the resistors and elements are a tension relative to G. Application of Theorem 4.4 gives the results immediately.

Consider the case when a resistive n-port can be characterized by an impedance or admittance matrix. If ideal transformers are allowed, then any positive-semidefinite matrix can be realized. If ideal transformers are not allowed in the resistive n-port, then positive-semidefiniteness of the matrix is necessary but not sufficient for realizability. Another necessary condition is that the n-port not be capable of voltage gain or current gain (satisfies Corollary 4.4.1). A stronger necessary condition is that the matrix be paramount (see Weinberge (15)).

A resistive n-port must also satisfy Theorem 4.6. It is not known whether this theorem is implied by paramoncy, or whether it is a new condition on a resistive n-port.

The following example illustrates an application of Theorem 4.1, Corollary 4.4.1, and Theorem 4.5.

Example 4.1: A number of dc voltage sources with given current capabilities are available as follows:

Source 1: 1 volt at 15 amps (maximum)

Source 2: 2 volts at 8 amps (maximum)

Source 3: 2 volts at 4 amps (maximum)

Source 4: 3 volts at 2 amps (maximum)

Source 5: 4 volts at 1 amp (maximum)

It is desired to connect the sources through resistors (and wires) to a load such that the voltage across the load is seven volts. Find a bound on the current which can be delivered to the load.

We will try several approaches and compare the results. Let  $\mathbf{v}_k$  and  $\mathbf{i}_k$  represent the voltage and current of source k, and let  $\mathbf{v}_0$  and  $\mathbf{i}_k$  represent the voltage and current of the load. Let R be the set

of connecting resistors. Now since the voltages and currents of all the elements in the network form a tension and a flow, Theorems 4.1, 4.4, and 4.5 can be applied.

Considering Corollary 4.4.1, let the sources constitute  $S_1$ , and the load together with R constitute  $S_2$ . Since the load is a member of  $S_2$ , result (b) of Corollary 4.4.1 gives

$$|i_0| \le \sum_{k=1}^5 |i_k| \le 30 \text{ amps}$$

Considering Theorem 4.1 we have

$$\sum_{k=1}^{5} v_{k}^{i}{}_{k} + v_{00}^{i}{}_{0} + \sum_{k \in \mathbb{R}} v_{k}^{i}{}_{k} = 0$$

But

$$\mathbf{v_{o_{o_{o}}}} \geq 0$$

$$v_k i_k \geq 0$$

;  $k \in \mathbb{R}$

Therefore

$$|v_{00}| \le -\sum_{k=1}^{5} v_{kk}^{i} \le \sum_{k=1}^{5} |v_{kk}^{i}|$$

and

$$|i_0| \le \frac{1}{|v_0|} \sum_{k=1}^{5} |v_k^i| \le 49/7 = 7 \text{ amps}$$

Considering Theorem 4.5, let  $S_1 = \{1,2,3\}$ ,  $S_2 = \{4,5\}$ ,  $S_3 = load$ ,  $S_4 = R$ . Then condition (i) is satisfied:

$$|\mathbf{v}_{0}| = 7 > \sum_{\mathbf{k} \in S_{1}} |\mathbf{v}_{\mathbf{k}}| = 5$$

Result (a) of Theorem 4.5 then gives

$$|i_0| \le \sum_{k \in S_2} |i_k| \le 3 \text{ amps}$$

How good the bound obtained by this last method is depends, of course, on how the sources are assigned to  $S_1$  and  $S_2$ . An algorithm can probably be developed to find the lowest bound without trying all combinations.

A simple construction procedure shows that Theorem 4.4, properly applied, gives the lowest obtainable bound for this type of problem if

$$|i_k| \ge \sum_{j \in S_2} |i_j|$$

;  $k \in S_1$

## V. RESISTORS IN DC TO DC CONVERSION NETWORKS

As applied to networks, the flow and tension in the preceding chapter are the currents and voltages of the network and linear functions and functionals of them. The theorems of Chapter 4 require only that the network in which the currents are observed and the network in which the voltages are observed generate the same directed graph (see Definition 5.4 below). No other relation is necessary. The many applications of Theorem 4.1 (Tellegen's theorem) arise from making use of this fact. (See Penfield et al. (10).)

We will not take advantage of this flexibility of the theorems here; currents and voltages will be observed in the same network and under the same excitation. Rather we will use another kind of flexibility which Theorem 4.4 and Theorem 4.5 possess. Different applications of these theorems can be generated by dividing up the network elements into the four sets in different ways.

In this thesis we will be primarily concerned with the averages of the network parameters. Since the averaging operation (Definition 2.6) is a linear functional, the average of the currents in a network is also a flow, and the average of the voltages is also a tension. Then the operation of averaging may be performed either before or after one of the theorems in Chapter IV is invoked.

If the currents and voltages are averaged before using one of the theorems of Chapter IV, the effect is to ignore the role played by the reactances. This is because the average voltage across an inductor is zero (Properties 2.2 and 2.3), and the average current through a capacitor is zero (Property 2.4).

The following definitions will help in the study of the role of resistors in a dc to dc conversion network.

<u>Definition 5.1</u>: The <u>dc-active set</u> in an operating dc to dc conversion network is the set of elements which each absorb negative dc power (de-liver positive dc power). The <u>ac-active set</u> in an operating dc to dc converter is the set of elements which each absorb negative ac power (deliver positive ac-power). Definition 2.10 defines dc power and ac power.

Definition 5.2: Given a network of resistors, inductors, capacitors, and dc sources, the corresponding dc network is formed as follows:

Remove all capacitors from the network. Combine all nodes connected by inductors, and remove the inductors.

<u>Definition 5.3</u>: The <u>primary set</u> of a dc to dc conversion network is the set of elements in the maximal nonseparable portion of the corresponding dc network which includes the dc source. The <u>secondary set</u> is the set of elements in the maximal nonseparable portion of the corresponding dc network which includes the load.

The term "primary" follows Duffin's use of it (4). However, we use the term "secondary" in an entirely different way from Duffin.

Definition 5.4: The directed graph generated by a network is obtained in the obvious way: vertices correspond to nodes, edges to elements, and orientations to references. In fact, if the identity of the elements is ignored, a network is a graph. Therefore we will sometimes apply graphical terms to a network.

Definition 5.5: Given a condition, result, or proof, the <u>dual</u> condition, result, or proof is obtained by interchanging the terms "loop" and "cut-set", "flow" and "tension", "voltage" and "current", "inductor" and "capacitor", and "flux-linkage" and "charge".

The following properties should be clear from the definitions. No proofs are given.

Property 5.1: A linear, time-invariant resistor cannot absorb negative dc power or negative ac power.

This fact follows easily from the constraint imposed by the resistor: v=Ri.

Property 5.2: Any resistors in the dc-active set of an operating dc to dc converter must be time-varying/nonlinear.

This is merely a restatement of part of Property 5.1 in a specialized context.

Property 5.3: Any resistors in the ac-active set of an operating dc to dc converter must be time-varying/nonlinear.

Any resistors in the ac-active set of an operating dc to dc converter must be quasi-active (see Definition 2.2).

The first statement follows from Property 5.1. The second statement is stricter than the first, and is proved by Leine (7).

Property 5.4: The dc-active set and the ac-active set in an operating dc to dc conversion network are disjoint.

This is a result of the passivity of the resistors, inductors, and capacitors, and the fact that dc sources absorb zero ac power.

Property 5.5: Consider a network with currents  $\{i_k\}$  and voltages  $\{v_k\}$ . Let G be the graph generated by the network, and let  $\{\overline{i}_k\}$  and  $\{\overline{v}_k\}$  be the averages of  $\{i_k\}$  and  $\{v_k\}$ . Then  $\{i_k\}$  and  $\{\overline{i}_k\}$  are flows relative to G, and  $\{v_k\}$  and  $\{\overline{v}_k\}$  are tensions relative to G.

Property 5.6: Consider an operating dc to dc conversion network with currents  $\{i_k\}$  and voltages  $\{v_k\}$ . Let  $\overline{G}$  be the graph generated

by the corresponding dc network. Let the sets  $\{\overline{i}_k\}$  and  $\{\overline{v}_k\}$  be the averages of the  $i_k$  and  $v_k$  corresponding to elements in the corresponding dc network. Then  $\{\overline{i}_k\}$  is a flow relative to  $\overline{G}$ , and  $\{\overline{v}_k\}$  is a tension relative to  $\overline{G}$ .

Property 5.7: Consider an operating dc to dc conversion network with currents  $\{i_k\}$  and voltages  $\{v_k\}$ . Let  $\overline{G}$  be the graph generated by the primary set in the corresponding dc network. Let the sets  $\{\overline{i_k}^l\}$  and  $\{\overline{v_k}^l\}$  be the averages of the  $i_k$  and  $v_k$  corresponding to elements in the primary set. Then  $\{\overline{i_k}^l\}$  is a flow relative to  $\overline{G}^l$ , and  $\{\overline{v_k}^l\}$  is a tension relative to  $\overline{G}^l$ .

Property 5.8: Consider an operating dc to dc conversion network with currents  $\{i_k\}$  and voltages  $\{v_k\}$ . Let  $\overline{G}''$  be the graph generated by the secondary set in the corresponding dc network. Let the sets  $\{\overline{i}_k''\}$  and  $\{\overline{v}_k''\}$  be the averages of the  $i_k$  and  $v_k$  corresponding to elements in the secondary set. Then  $\{\overline{i}_k''\}$  is a flow relative to  $\overline{G}''$ , and  $\{\overline{v}_k''\}$  is a tension relative to  $\overline{G}''$ .

Theorem 5.1: There is at least one resistor which is in both the dcactive set and the secondary set of an operating dc to dc conversion network.

<u>Proof. Case 1:</u> The network achieves dc voltage gain greater than unity.

Let the sets  $\{\overline{i}_k^{"}\}$  and  $\{\overline{v}_k^{"}\}$  be the averages of the currents and voltages corresponding to elements in the secondary set. Then Property 5.8 says that we may apply Corollary 4.4.1 to  $\{\overline{i}_k^{"}\}$ ,  $\{\overline{v}_k^{"}\}$ , and the graph  $\overline{G}$  generated by the secondary set. Assume that no elements of the dc-active set, other than possibly the dc source, are in the secondary set. If the dc source is in the secondary set, then according

to Corollary 4.4.1 the set  $S_1$  consists of the dc source, and  $S_2$  consists of the other elements in the secondary set (resistors, including the load). Let the average of the voltage across the dc source be  $\overline{v}_1^{"}$ . Then result (a) of Corollary 4.4.1 gives

$$|\overline{\mathbf{v}}_{\mathbf{k}}^{"}| \leq |\overline{\mathbf{v}}_{\mathbf{l}}^{"}| \quad ; \quad k \in \mathbb{S}_{2}$$

(5.1)

But by Definition 5.3, the load is a member of  $S_2$ , and thus the average  $\overline{v}_0$  of the load voltage is a member of  $\{\overline{v}_k^{"}\}$ . The network has voltage gain greater than unity, so that

$$|\overline{v_0}''| > |\overline{v_1}''|$$

which contradicts Ineq. (5.1). Therefore an element in the dc-active set other than the dc source must be in the secondary set. This element must be a resistor since the secondary set includes no capacitors or inductors.

Case 2: The network achieves dc current gain greater than unity.

The proof in this case is the dual of the proof in Case 1. Result (b) of Corollary 4.4.1 is used in place of result (a).

Corollary 5.1.1: The secondary set of a dc to dc conversion network includes at least one time-varying/nonlinear resistor.

This follows from Property 5.2.

Lemma 5.2.1. (Penfield et al. (10)): Let  $P_{dc}^k$ ,  $P_{ac}^k$ , and  $\overline{P}^k$  be the dc power, ac power, and average power absorbed by the  $k^{th}$  element. Let S be the set of elements in the network. Then

$$\sum_{k \in S} P_{dc}^{k} = \sum_{k \in S} P_{ac}^{k} = \sum_{k \in S} \overline{P}^{k} = 0$$

Proof: Property 5.5 together with Theorem 4.1 imply

$$\sum_{k \in S} v_k i_k = 0 \tag{5.2}$$

and

$$\sum_{k \in S} \overline{v}_k \overline{i}_k = \sum_{k \in S} P_{dc}^k = 0$$

The average of Eq. (5.2) is

$$\sum_{k \in S} \overline{v_k^i}_k = \sum_{k \in S} \overline{P}^k = 0$$

Now the ac power absorbed by element k is

$$P_{ac}^{k} = \overline{P}^{k} - P_{dc}^{k}$$

;  $k \in S$

Therefore

$$\sum_{k \in S} P_{ac}^{k} = \sum_{k \in S} \overline{P}^{k} - \sum_{k \in S} P_{dc}^{k} = 0$$

which completes the results of the lemma.

Theorem 5.2. (after Duffin (4)): There is at least one resistor which is in both the ac-active set and the primary set of an operating dc to dc conversion network.

<u>Proof:</u> Let  $P_{dc}^k$ ,  $P_{ac}^k$ , and  $\overline{P}^k$  be the dc power, ac power, and average power absorbed by the  $k^{th}$  element. Let S be the set of elements in the network, and let S' be the primary set.

Property 5.6 and Theorem 4.1 imply

$$\sum_{k \in S'} P_{dc}^k = 0$$

we also have from Lemma 5.2.1

$$\sum_{k \in S} \bar{P}^k = 0$$

$$\sum_{k \in S'} \overline{P}^k + \sum_{k \in (S-S')} \overline{P}^k = 0$$

Therefore

$$\sum_{k \in S'} \overline{P}^k - \sum_{k \in S'} P_{dc}^k + \sum_{k \in (S-S')} \overline{P}^k = 0$$

or

$$\sum_{k \in S'} P_{ac}^k + \sum_{k \in (S-S')} \overline{P}^k = 0$$

(5.3)

<u>Case 1</u>: The load is in (S-S'). Now by Definition 5.3 the dc source is in S'; then  $\overline{P}^k \geq 0$ ,  $k \in (S-S')$ . But Definition 2.8 requires the load to be finite, so that the average power absorbed by the load is non-zero. Therefore

$$\sum_{k \in (S-S')} \overline{P}^k > 0$$

and Eq. (5.3) therefore implies

$$\sum_{k \in S'} p_{ac}^k < 0$$

Since the dc source absorbs no ac power, and S' includes no inductors or capacitors, there must be a resistor k' in S', for which  $P_{ac}^{k'} < 0$ ; that is, k' is in the ac-active set.

<u>Case 2</u>: The load is in S'. Then by Definition 5.3 S' is also the secondary set. Theorem 5.1 implies then that there is at least one resistor k'' in S' for which  $P_{dc}^{k''} < 0$ . But  $P_{ac}^{k''} = \overline{P}^{k''} - P_{dc}^{k''}$ , so that for this resistor  $P_{ac}^{k''} > 0$ .

Assume that no member of the ac-active set is in S'. Then  $P_{ac}^{k} \geq 0$ ;  $k \in S'$ . But  $k'' \in S'$ , and  $P_{ac}^{k''} > 0$ . Therefore

$$\sum_{k \in S'} P_{ac}^k > 0 \tag{5.4}$$

Also, since the dc source is in S',  $\overline{P}^k \ge 0$ ;  $k \in (S-S')$ , and

$$\sum_{\mathbf{k}\in(\mathbf{S}-\mathbf{S}')}\overline{\mathbf{P}}^{\mathbf{k}}\geq 0\tag{5.5}$$

But Ineq. (5.4) together with Ineq. (5.5) contradict Eq. (5.3). Then there must be at least one member k' of the ac-active set in S'. Since the dc source absorbs no ac power, and S' includes no inductors or capacitors, that member must be a resistor.

Corollary 5.2.1: The primary set of a dc to dc conversion net-work includes at least one time-varying/nonlinear resistor which is quasi-active.

This follows from Property 5.3.

Theorem 5.3: Consider an operating dc to dc conversion network. Let  $R_{dc}$  be the set of resistors in the dc-active set, and  $R_{ac}$  be the set of resistors in the ac-active set. If  $P_{dc}^{k}$  and  $P_{ac}^{k}$  are the dc power and the ac power absorbed by the  $k^{th}$  element, then

$$\sum_{k \in R_{ac}} P_{dc}^k \ge -\sum_{k \in R_{ac}} P_{ac}^k \ge \sum_{k \in R_{dc}} P_{ac}^k \ge -\sum_{k \in R_{dc}} P_{dc}^k > 0$$

Proof: Let the sets of resistors, inductors, and capacitors in the network be R, L, and C. Let the ac power absorbed by the dc source be Plac. According to Lemma 5.2.1, the total of the ac power absorbed by all elements in a network is zero:

$$P_{ac}^{l} + \sum_{k \in L} P_{ac}^{k} + \sum_{k \in C} P_{ac}^{k} + \sum_{k \in R} P_{ac}^{k} = 0$$

(5.6)

But we have from Properties 2.2, 2.3, 2.4, and 2.5,

$$\sum_{\substack{P_{ac}^{k} = 0 \\ P_{ac}^{k} = 0}} P_{ac}^{k} = 0 ; k \in \mathbb{C}$$

$$P_{ac}^{l} = 0$$

Then Eq. (5.6) becomes

$$\sum_{k \in \mathbb{R}} P_{ac}^{k} = 0$$

Let the set of resistors in neither  $R_{dc}$  nor  $R_{ac}$  be designated  $R^*$ . Then, observing Property 5.4, we may write

$$\sum_{k \in R_{dc}} P_{ac}^k + \sum_{k \in R_{ac}} P_{ac}^k + \sum_{k \in R^*} P_{ac}^k = 0$$

But by definition,  $P_{ac}^{k} \ge 0$ ;  $k \in \mathbb{R}^{*}$ . Therefore

$$-\sum_{k \in \mathbb{R}_{ac}} P_{ac}^{k} \ge \sum_{k \in \mathbb{R}_{dc}} P_{ac}^{k}$$

(5.7)

Now

$$P_{ac}^{k} = \overline{P}^{k} - P_{dc}^{k}$$

;  $k \in \mathbb{R}$  (5.8)

where  $\overline{P}^k$  is the average power absorbed, which is non-negative for a resistor. Applying this to  $k \varepsilon R_{dc}$

$$\sum_{k \in R_{dc}} P_{ac}^{k} \ge -\sum_{k \in R_{dc}} P_{dc}^{k}$$

(5.9)

Eq. (5.8), applied to  $k \in R_{ac}$ , gives

$$\sum_{k \in R_{ac}} P_{dc}^{k} \ge -\sum_{k \in R_{ac}} P_{ac}^{k}$$

(5.10)

Theorem 5.1 implies

$$\sum_{\mathbf{k} \in \mathbf{R}_{\mathbf{dc}}} \mathbf{P}_{\mathbf{dc}}^{\mathbf{k}} > 0 \tag{5.11}$$

Inequalities (5.7), (5.9), (5.10), and (5.11) together constitute the result of the theorem.

Theorem 5.4: The total dc power delivered by the set  $R_{dc}$  of resistors in the dc-active set of an operating dc to dc conversion network is bounded in terms of the dc voltage gain G and the dc power  $P_0$  delivered to the load by

$$-\sum_{k \in R_{dc}} P_{dc}^k \ge \frac{G-1}{G} P_0$$

The result also holds for G the dc current gain.

<u>Proof:</u> Property 5.6 says that we may apply Theorem 4.4 to the set of average currents  $\{\overline{i}_k\}$  and the set of average voltages  $\{\overline{v}_k\}$  corresponding to elements in the corresponding dc network and to the graph which it generates. Considering result (a) of Theorem 4.4, let  $S_1$  be the dc source with voltage  $v_1$ . Let  $S_2$  be the load with voltage  $v_0$  and current  $v_0$ . Let  $v_0$  be the set  $v_0$  and current  $v_0$ . Let  $v_0$  be the set  $v_0$  are sistors in the dcactive set. Let  $v_0$  be the remaining resistors in the corresponding dc network. Then result (a) of Theorem 4.4 is

$$|\overline{v}_1||\overline{i}_0| - \overline{v}_0\overline{i}_0 + \sum_{\mathbf{k}\in\mathbb{R}_{dc}} |\overline{v}_{\mathbf{k}}\overline{i}_{\mathbf{k}}| \ge 0$$