## The Locality-First Strategy for Developing Efficient Multicore Algorithms

by

Helen Jiang Xu

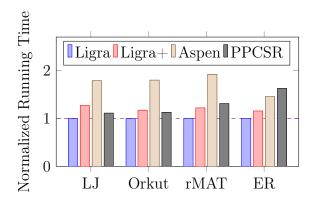

Submitted to the Department of Electrical Engineering and Computer Science

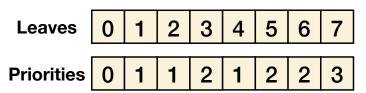

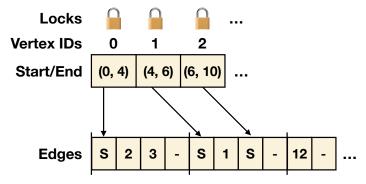

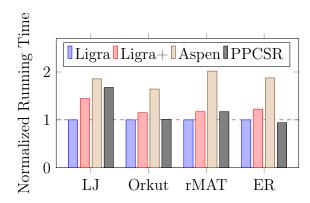

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science and Engineering

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2022

© Helen Jiang Xu, MMXXII. All rights reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now known or hereafter created.

| Author                                                    |

|-----------------------------------------------------------|

| Department of Electrical Engineering and Computer Science |

| January 26, 2022                                          |

| Certified by                                              |

| Charles E. Leiserson                                      |

| Professor of Computer Science and Engineering             |

| Thesis Supervisor                                         |

| Accepted by                                               |

| Leslie A. Kolodziejski                                    |

| Professor of Electrical Engineering and Computer Science  |

| Chair, Department Committee on Graduate Students          |

#### The Locality-First Strategy for

#### **Developing Efficient Multicore Algorithms**

by

Helen Jiang Xu

Submitted to the Department of Electrical Engineering and Computer Science on January 26, 2022, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science and Engineering

#### Abstract

To scale applications on multicores up to bigger problems, software systems must be optimized both for parallelism to take full advantage of the multiple cores and for locality to exploit the memory system for cache-friendliness. Parallelization alone does not suffice to reach peak performance due to the processor-memory gap: the increasing divergence of processor and memory speeds. Locality and parallelism are difficult to optimize for independently — and even more challenging to combine because they tend to conflict with each other.

I advocate that algorithm developers employ a *locality-first strategy* for developing efficient parallel and cache-friendly algorithms for multicores. That is, they should first understand and exploit locality as much as possible before introducing parallelism. I argue that an algorithm developer can achieve high-performing code more easily with the locality-first strategy than with either a parallelism-first strategy or a strategy of trying to optimize both simultaneously.

I present ten artifacts that leverage the locality-first strategy to create fast multicore algorithms that are simple to describe and implement. For example, locality-first data structure design in graph processing achieves about  $2\times$  speedup over the state of the art. Additionally, I prove mathematically that multicore cache-replacement algorithms that take advantage of locality outperform all other online algorithms. The other eight artifacts make similar contributions in their respective domains. Together, these artifacts demonstrate that the locality-first strategy provides an effective roadmap for algorithm developers to design and implement theoretically and practically efficient multicore code.

Thesis Supervisor: Charles E. Leiserson Title: Professor of Computer Science and Engineering

## Acknowledgments

This thesis would not have been possible without the steadfast support of my mentors, collaborators, friends, and family. I'd like to use this opportunity to thank as many of them as I can.

First and foremost, I want to thank my advisor, Charles E. Leiserson, for inspiring me to strive every day to challenge and improve myself a researcher, teacher, and all-around person. I am grateful to Charles for his guidance and support throughout my PhD as not only a brilliant researcher but also a phenomenal mentor. His performance engineering class enabled me to pursue many new exciting lines of research spanning algorithm design, analysis, and engineering. Since then, he has taught me invaluable lessons not only about research but also about writing, communication, and mentoring. In addition to the technical aspects, Charles has created a social lab environment in the Supertech group through events such as standup comedy classes and apple picking. Thanks to his efforts, my time at MIT has been full of fascinating collaborations and discussions. I look forward to carrying forward everything he has taught me onwards and upwards.

I would like to thank Tao B. Schardl for all of his help and support during my PhD. I first met TB before coming to MIT when he took the time to chat with me about the Supertech group. Since then, I have been lucky to work closely with him on algorithms problems as well as on this thesis, my defense, and endless statements and presentations. His contributions, patience, and openness to chat about any questions have been invaluable to this thesis.

Thanks to Julian Shun and Virginia Vassilevska Williams for their service on my thesis and RQE committees. I thank Julian for sharing his expertise in graph algorithms and processing. His input has shaped the work in this thesis (Terrace, PPCSR, PCSR) on dynamic graph processing. I thank Virginia for her guidance on sparse matrix algorithms and for including me in many fun games of tennis.

I would also like to thank my other mentors without whom I would not be here today.

- My undergraduate advisor, Michael Bender, was the first person who taught me that computer science could be beautiful and fun. As someone from a non-technical background, I was unsure that CS would be a good fit for me, and I was especially skeptical that I could be interested in research. In my first semester, he saw how to connect my other interests with CS and how to get me interested in the topics. Since then, he has supported me in so many other ways: introducing me to Charles and other members of our research community, inviting me to speak at Stony Brook, and sharing food and literature recommendations.

- Thanks to Cynthia Phillips for always inviting me to explore new opportunities. I spent my summer before my PhD working with her at Sandia, during which I got to see many beautiful landscapes as well as beautiful theorems.

- I thank Shahin Kamali for his invaluable career advice and his support throughout my PhD. Our work on parallel cache replacement was my first foray into parallel algorithms research: he helped me discover new topics in online algorithms to build on my theoretical interests. I am also grateful for his help and effort to improve my dissertation, statements, and presentations.

- I would also like to thank Michael Pellauer and Joel Emer for being a joy to work with and for their helpful suggestions on my thesis. Michael hosted me (virtually) at NVIDIA in 2020 as part of the Architecture Research Group. Thanks to his efforts to meet with me every day in the summer and to continue our collaboration, I was able to see a hardware architect's perspective on sparse problems and to incorporate it into multicore algorithm engineering.

Thanks to all of my coauthors for their indispensable contributions to the work presented in this thesis. My collaborators are all not only technically brilliant but also lovely to work with.

- Brian Wheatman coauthored the PCSR, PPCSR, and Terrace papers on dynamic graph processing. Many thanks to Brian for our discussions on cacheefficient parallel algorithms and data structures as well as for sharing his performance engineering expertise.

- Prashant Pandey coauthored the Terrace paper on dynamic graph processing. Prashant deserves thanks not only for sharing his expertise in data structures but also for inviting me along for many awesome hikes. I am also grateful for his and Kavita's hospitality while hosting me in India for their wedding.

- Quanquan Liu coauthored the scan-hiding and smoothed analysis papers. In addition, I also thank Quanquan for our discussions on graph algorithms and data structures. In addition to being an excellent researcher, she is a great tennis partner and fun company to visit local restaurants with (especially Mary Chung's).

- William (Bill) Kuszmaul coauthored the smoothed analysis paper. Thanks to Bill for many interesting discussions about theoretical algorithm design and analysis. Also, I am especially grateful for his and Rose's hospitality during the last part of my PhD.

- Peter Ahrens and Nicholas Schiefer coauthored the PHIL paper. Special thanks to Peter for introducing me to sparse problems and our visits to Tosci's when writing the paper and to Nick for helping with my first move in Cambridge.

- Sean Fraser coauthored the prefix-sums and included/excluded sums papers. I am grateful for his work in developing all of the algorithms in the aforementioned papers.

In addition to the mentors and coauthors mentioned so far, I am grateful to everyone I have worked with and discussed research with. I would like to thank the coauthors I have not yet mentioned: Aydın Buluç, Andrea Lincoln, Jayson Lynch, Rezaul Chowdhury, Rathish Das, Rob Johnson, Simon Mauras, Martín Farach-Colton, Tyler Mayer, James Aimone, Ojas Parekh, Ali Pinar, and William Severa. This thesis would not have been possible without their contributions. Thanks to the members of the Supertech group, especially Tim Kaler, Matthew Kilgore, Billy Moses, and Alexandros Iliopoulos, for fostering a lively and open research environment. Additional thanks to Cree Bruins for supporting the Supertech group and for her infallible cheer and friendliness. I would also to thank Deanna Montgomery for her service as the EECS Communication Lab manager. Being part of the Comm Lab has been one of the highlights of my time at MIT, and I am grateful for her input in all communication-related matters.

Finally, I am grateful to all of my friends and family for their encouragement and support. Thanks to my childhood friends: Nii for being my ride-or-die, Fay for the Shakespeare and adventures, Ash for the fun trips and good times, Kense for always coming through, and Dillon and Mimz for hanging out with me. Thanks to my more recent friends: Helena for the chats and weird snacks, Yen-Ling for carrying me through my TQEs and for the infinite hot pot, Wanrong for the plays, egg tarts, and tea times, and Ryan for always hyping up my aspirations. Special thanks to Ilia for the drinks, meat, and support in this last stretch of my grad school life. I thank my parents, Ye and Bryant, for supporting me in all of my endeavors and always keeping a place to return to, especially during the pandemic. Thanks to my brother, Allan, for the hikes, drives, and karaoke jams. I would not have made it this far without them.

I am grateful for the support of my research sponsors. This research was sponsored in part by: a National Physical Sciences Consortium Fellowship, the United States Air Force Research Laboratory and the United States Air Force Artificial Intelligence Accelerator under Cooperative Agreement Number FA8750-19-2-1000, Los Alamos National Laboratory (LANL) under Subcontract Number 531711, the National Science Foundation (NSF) under grant CCF-1533644, and the Intelligence Advanced Research Projects Activity (IARPA) under grant 138076-5093555.

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the United States Air Force or the U.S. Government. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation herein.

# Contents

| 1 Introduction |                                 |                                                                    |                      |

|----------------|---------------------------------|--------------------------------------------------------------------|----------------------|

| 2              | <b>The</b><br>2.1<br>2.2<br>2.3 | Locality-First Strategy<br>Creating efficient multicore algorithms | 17<br>17<br>23<br>25 |

|                | 2.4                             | Exploiting locality without changing the data layout               | 28                   |

| 3              |                                 | cace: A Hierarchical Graph Container for Skewed Dynamic            |                      |

|                | Gra                             | phs                                                                | 33                   |

|                | 3.1                             | Introduction                                                       | 34                   |

|                | 3.2                             | Preliminaries                                                      | 39                   |

|                | 3.3                             | Hierarchical data structure design                                 | 40                   |

|                | 3.4                             | Data structure choices                                             | 41                   |

|                | 3.5                             | Implementation of Terrace                                          | 46                   |

|                | 3.6                             | Evaluation                                                         | 48                   |

|                | 3.7                             | Related work                                                       | 56                   |

|                | 3.8                             | Conclusion                                                         | 58                   |

| 4              | A P                             | arallel Packed Memory Array to Store Dynamic Graphs                | 59                   |

|                | 4.1                             | Introduction                                                       | 60                   |

|                | 4.2                             | Packed Memory Array                                                | 63                   |

|                | 4.3                             | PMA modifications                                                  | 65                   |

|                | 4.4                             | Intra-operation parallelism                                        | 66                   |

|                | 4.5                             | Inter-operation parallelism                                        | 71                   |

|                | 4.6                             | Parallel Packed Compressed Sparse Row                              | 72                   |

|                | 4.7                             | Parallel graph operations                                          | 74                   |

|                | 4.8                             | Empirical evaluation                                               | 76                   |

|                | 4.9                             | Conclusion                                                         | 81                   |

| 5              | AF                              | ill Estimation Algorithm for Sparse Matrices and Tensors in        |                      |

|                |                                 | cked Formats                                                       | 83                   |

|                | 5.1                             | Introduction                                                       | 84                   |

|                | 5.2                             | Background                                                         | 91                   |

|                | 5.3                             | PHIL                                                               | 96                   |

|                |                                 | · · · · · · · · · · · · · · · · · · ·                              |                      |

|    | 5.4 Theoretical analysis                                    |        | 102 |

|----|-------------------------------------------------------------|--------|-----|

|    | 5.5 Experimental results                                    |        | 104 |

|    | 5.6 Conclusion                                              |        | 108 |

|    |                                                             |        |     |

| 6  | Write-Optimized Skip Lists                                  |        | 111 |

|    | 6.1 Introduction                                            |        | 112 |

|    | 6.2 Structure and operations of a write-optimized skip list |        | 116 |

|    | 6.3 Structural bounds                                       |        | 119 |

|    | 6.4 Simple runtime bounds                                   |        | 121 |

|    | 6.5 High probability insertion-only bounds                  |        | 122 |

|    | 6.6 High probability bounds with insertions and deletions   |        | 126 |

|    | 6.7 Conclusion                                              |        | 128 |

| 7  | Beyond Worst-Case Analysis of Multicore Caching Strategies  | 3      | 131 |

|    | 7.1 Introduction                                            |        | 132 |

|    | 7.2 Preliminaries                                           |        | 134 |

|    | 7.3 Cyclic analysis for online problems                     |        | 137 |

|    | 7.4 Cyclic analysis for multicore caching                   |        | 142 |

|    | 7.5 Advantage of LRU with locality of reference             |        | 144 |

|    | 7.6 Related multicore caching models                        |        | 149 |

|    | 7.7 Conclusion                                              |        | 145 |

|    |                                                             | • • •  | 101 |

| 8  | Multicore Paging Algorithms Cannot Be Competitive           |        | 153 |

|    | 8.1 Introduction                                            |        | 153 |

|    | 8.2 Non-competitiveness of lazy algorithms                  |        | 154 |

|    | 8.3 Conclusion                                              |        | 157 |

| 9  | Closing the Gap Between Cache-Oblivious and Cache-Ad        | laptiv | ve. |

|    | Analysis                                                    |        | 159 |

|    | 9.1 Introduction                                            |        | 160 |

|    | 9.2 Preliminaries                                           |        | 164 |

|    | 9.3 Technical overview                                      |        | 168 |

|    | 9.4 Cache-adaptivity of randomly shuffled profiles          |        | 174 |

|    | 9.5 Robustness of worst-case profiles                       |        | 190 |

|    | 9.5.1 Box-size perturbations                                |        | 192 |

|    | 9.5.2 Start-time perturbations                              |        | 194 |

|    | 9.5.3 Box-order perturbations                               |        | 196 |

|    | 9.6 Related work                                            |        | 198 |

|    | 9.7 Conclusion                                              |        | 200 |

|    |                                                             |        | 200 |

| 10 | Cache-Adaptive Exploration: Experimental Results and        | Scar   |     |

|    | TTT JTT I THE ALL ALL ALL ALL ALL ALL ALL ALL ALL AL        |        |     |

|    | Hiding for Adaptivity                                       |        | 201 |

|    | 10.1 Introduction                                           |        | 202 |

|    |                                                             |        |     |

|    | 10.4 Scan-hiding and Strassen's algorithm                                       | 208        |

|----|---------------------------------------------------------------------------------|------------|

|    | 10.5 Experimental study                                                         | 214        |

|    | 10.6 Conclusion                                                                 | 216        |

|    | West Description to Description of the Assess to Disstance Description          |            |

| 11 | Work-Efficient Parallel Algorithms for Accurate Floating-Point Pre-<br>fix Sums | -<br>219   |

|    | 11.1 Introduction                                                               | 219        |

|    | 11.2 Characterizing prefix-sum algorithms                                       | 220        |

|    | 11.3 Low sum-depth prefix sums                                                  | 220<br>224 |

|    | 11.4 Evaluation                                                                 | 224        |

|    | 11.5 Vectorizing prefix sums                                                    | 229        |

|    | 11.6 Conclusion                                                                 | 230        |

| 12 | Multidimensional Included and Excluded Sums                                     | 233        |

|    | 12.1 Introduction                                                               | 234        |

|    | 12.2 Preliminaries                                                              | 240        |

|    | 12.3 Included Sums                                                              | 241        |

|    | 12.4 Excluded sums and the box complement                                       | 243        |

|    | 12.5 Box-complement algorithm                                                   | 245        |

|    | 12.6 Experimental evaluation                                                    | 250        |

|    | 12.7 Conclusion                                                                 | 252        |

| 13 | Conclusion                                                                      | 253        |

|    | 13.1 Thesis summary                                                             | 253        |

|    | 13.2 Applicability of the locality-first strategy                               | 255        |

| Α  | Packed Compressed Sparse Row                                                    | 257        |

|    | A.1 Graph storage formats                                                       | 258        |

|    | A.2 Packed Compressed Sparse Row                                                | 260        |

|    | A.3 Results                                                                     | 262        |

| В  | Cache Adaptivity                                                                | 269        |

|    | B.1 What bad memory profiles look like                                          | 270        |

|    | B.2 Pseudocode for MM-Scan                                                      | 272        |

|    | B.3 Additional figures                                                          | 273        |

|    | B.4 Proof of Theorem 9.14 and Lemma 9.13                                        | 274        |

|    | B.5 Proof of the No-catch-up Lemma                                              | 275        |

|    | B.6 Standardizing $(a, b, c = 1)$ -regular algorithms                           | 276        |

|    | B.7 Triangle profiles                                                           | 278        |

|    | B.8 Pseudocode for AdaptiveStrassen                                             | 282        |

| С  |                                                                                 | 287        |

|    | C.1 Analysis of corners algorithm                                               | 287        |

|    | C.2 Pseudocode and proofs for BDBS-1D                                           | 290        |

|    | C.3 Pseudocode and proofs for box-complement                                    | 292        |

|    | C.4 Additional experimental data                                                | 294        |

## Bibliography

# Chapter 1 Introduction

This thesis is concerned with scaling applications on multicores by optimizing algorithms both for locality to take advantage of the memory system and for parallelism to make full use of the multiple cores. Parallelism alone is not enough because of the *processor-memory gap*: the divergence between processor and memory speeds [90, 299]. Unfortunately, as we shall see, locality and parallelism are hard to achieve independently. Furthermore, they are even more difficult to achieve together because they tend to trade off with each other.

The seemingly fundamental tension between locality and parallelism poses challenges to developing efficient codes on multicores. As we shall see, exploiting locality involves computing on the same or similar data over time. Computing on the same or similar data in parallel can result in correctness and performance issues, however. In this chapter, we will see concrete examples of how optimizing for one of these features can disrupt the other.

To overcome these tensions, I advocate a "locality-first strategy" for creating highperformance multicore algorithms that are optimized for both locality and parallelism. Specifically, I advocate the following thesis statement:

**Thesis statement:** To create efficient parallel algorithms for multicores, algorithm developers should use a *locality-first strategy*. That is, they should first *understand*, *enhance*, *and exploit locality* as much as possible as a first step before introducing parallelism.

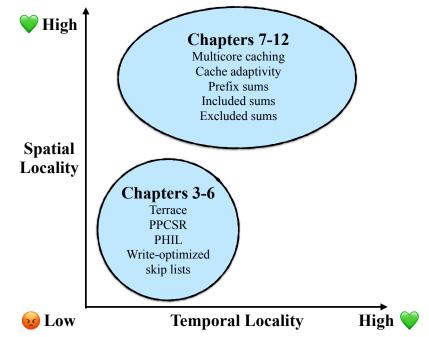

To employ the locality-first strategy, let us first understand the different kinds of locality. Algorithm developers take advantage of *spatial locality* and *temporal locality* in order to fit the underlying hardware. Spatial locality is the tendency of programs to access nearby memory locations in a short time period, whereas temporal locality is the tendency of programs to access the same memory location over time [124, 305]. A program may exhibit spatial locality, temporal locality, both, or neither, depending on the problem.

As we shall see in detail in Chapter 2, locality and parallelism tend to conflict with each other in fundamental ways. At a high level, exploiting locality involves computing on the same or similar data over time. Unfortunately, computing on

Figure 1-1: Graphical illustration of the main artifacts in this thesis.

the same data in parallel can cause nondeterministic behavior, and computing on similar data over time can cause contention. These issues disrupt correctness and performance in parallel programs.

#### Contributions

In support of the thesis statement, I present ten intellectual artifacts that demonstrate the potential for the locality-first strategy to overcome seemingly fundamental tensions between parallelism and cache-friendliness. These artifacts fall into two categories based on whether they enhance locality by changing the data layout or whether they exploit naturally-occurring locality in the algorithm's access pattern. Figure 1-1 illustrates the organization of the artifacts into these two categories.

The ten principal artifacts and their contributions are as follows:

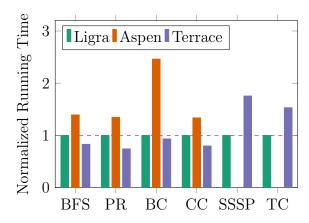

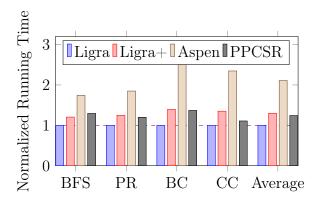

- The *Terrace* artifact [294]: A dynamic-graph-processing system optimized for skewed dynamic graphs. Terrace enhances spatial locality with a hierarchical data representation that takes advantage of naturally-occurring graph skewness. Terrace is on average 2× faster than Aspen [128], a state-of-the-art dynamic-graph-processing system, on graph queries. Furthermore, it overcomes traditional tradeoffs between queries and updates and supports similar updatability compared to Aspen. I developed the Terrace artifact with Prashant Pandey, Brian Wheatman, and Aydın Buluç.

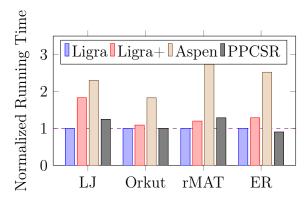

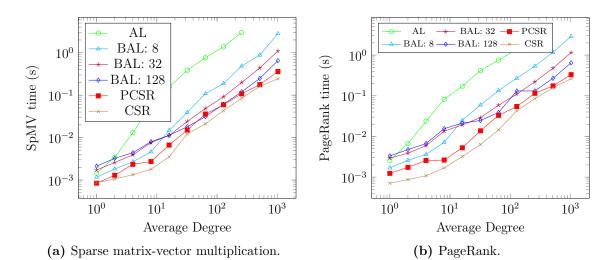

- The *Parallel Packed Compressed Sparse Row* (PPCSR) artifact [379]: A dynamic-graph-processing system optimized for spatial locality. PPCSR enhances spatial locality by storing all of the data contiguously in a "Packed Memory Array" data structure. PPCSR supports graph queries about 1.6× faster

than Aspen while maintaining competitive update throughput. I developed the PPCSR artifact with Brian Wheatman.

- The *PHIL* artifact [6], an efficient algorithm to speed up sparse tensor algebra via blocked formats. PHIL exploits spatial locality by estimating fill, an important quantity in blocked sparse tensor operations. PHIL estimates the fill with provable time and accuracy guarantees. Its advantage is evident in the empirical evaluation: it estimates the fill at least 2× faster than OSKI [371], a state-of-the-art fill-estimation algorithm, and up to 40-50× faster than OSKI. I developed the PHIL artifact with Peter Ahrens and Nicholas Schiefer.

- The *write-optimized skip list* artifact [49]: A cache-optimized randomized data structure. The write-optimized skip list enhances spatial locality in data structure design. It achieves write-optimized bounds in that it supports asymptotically optimal searches, inserts, and deletes. Furthermore, it supports inserts and deletes asymptotically faster than searches. I developed the write-optimized skip list artifact with Michael A. Bender, Martín Farach-Colton, Rob Johnson, Simon Mauras, Tyler Mayer, and Cynthia Phillips.

- The *cyclic analysis* artifact [210]: A measure for beyond worst-case analysis of online algorithms applied to parallel cache-replacement. Cyclic analysis mathematically supports the locality-first strategy for algorithms that exploit temporal locality. Specifically, it provides theoretical grounding for the established practical superiority of the Least-Recently-Used (LRU) [342] algorithm because LRU takes advantage of temporal locality. I developed the cyclic analysis artifact with Shahin Kamali.

- The *lower bounds* artifact [209]: Worst-case analysis of online algorithms for parallel cache-replacement. The lower bounds artifact motivates the study of beyond-worst-case analysis measures to mathematically explain the empirical superiority of algorithms that take advantage of temporal locality. The lower bounds show that a large class of online algorithms for parallel cache-replacement are equally arbitrarily far from optimal. I developed the lower bounds artifact with Shahin Kamali.

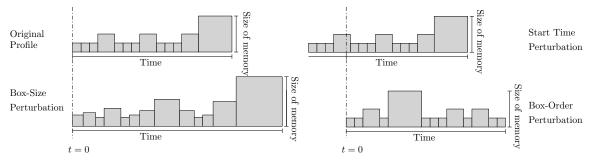

- The *smoothed analysis* artifact [41]: Beyond-worst-case analysis of cacheadaptive algorithms. The smoothed analysis for cache-adaptive algorithms provides mathematical grounding for algorithms that take advantage of temporal locality in shared memory. Specifically, it closes the gap between cache-oblivious and cache-adaptive algorithms. I developed the smoothed analysis artifact with Michael A. Bender, Rezaul A. Chowdhury, Rathish Das, Rob Johnson, William Kuszmaul, Andrea Lincoln, Quanquan C. Liu, and Jayson Lynch.

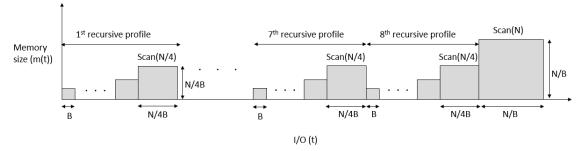

- The *scan-hiding* artifact [246]: A technique for converting non-cache-adaptive algorithms into cache-adaptive ones. Scan-hiding enhances temporal locality in a large class divide-and-conquer algorithms. I developed the scan-hiding artifact with Andrea Lincoln, Quanquan C. Liu, and Jayson Lynch.

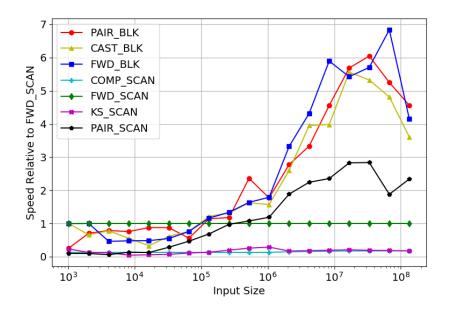

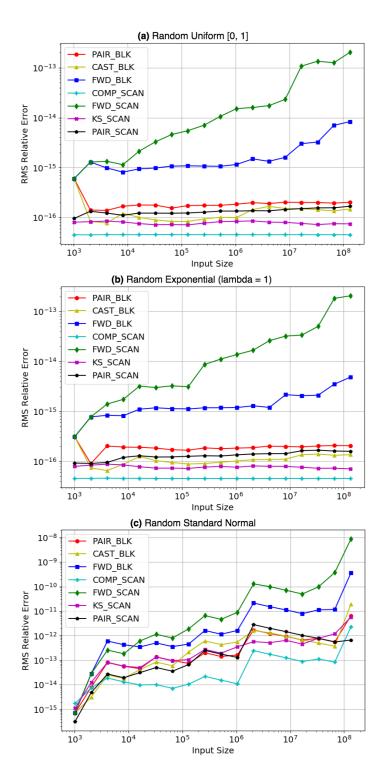

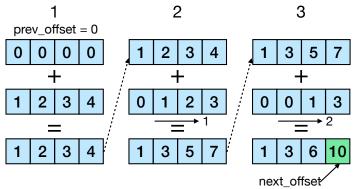

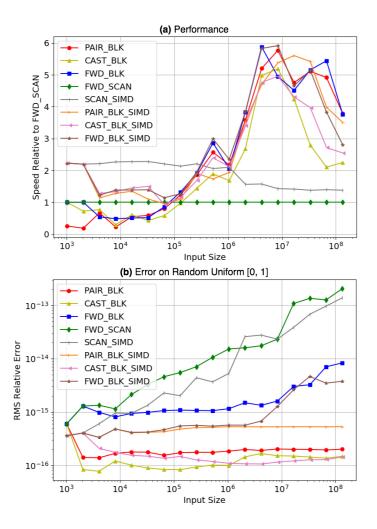

- The CAST\_BLK and PAIR\_BLK artifacts [151]: Two algorithms for fast-and-accurate parallel prefix sums. These algorithms exploit naturally-occurring spatial locality without changing the data representation. The CAST\_BLK and PAIR\_BLK algorithms achieve comparable performance to the state-of-the-art parallel prefix algorithm with at least 5× more accuracy. I developed the CAST\_BLK and PAIR\_BLK artifacts with Sean Fraser and Charles E. Leiserson.

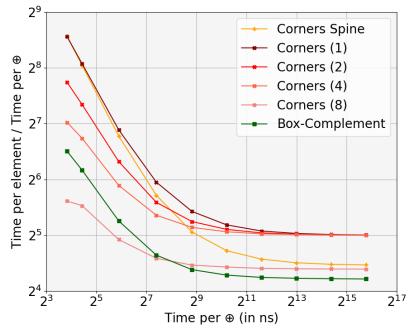

- The *bidirectional box-sum* and *box-complement* artifacts [389]: Two efficient algorithms for multidimensional included and excluded sums. These algorithms naturally achieve good spatial locality without changing the data layout. These artifacts improve the asymptotic work for the multidimensional included-sums and excluded-sums problems from exponential to linear in the number of dimensions. This improvement in higher-dimensions is borne out in the empirical evaluation. I developed the bidirectional box-sum and box-complement artifacts with Sean Fraser and Charles E. Leiserson.

#### Thesis organization

The rest of this thesis has a simple structure. Chapter 2 provides context for the locality-first strategy as a method for general algorithm engineering on multicores. Chapters 3-12 present the principal artifacts. Chapter 13 summarizes the thesis and takes a step back from the principal artifacts to discuss the broader applicability of the locality-first strategy.

The appendices present auxiliary technical material to several of the principal artifacts. Appendix A introduces Packed Compressed Sparse Row, a serial storage format for dynamic graphs that underlies the artifacts in the domain of dynamic graph processing (Chapters 3 and 4). Appendix B contains additional background material and proofs for the artifacts in the domain of cache-adaptive algorithms (Chapters 9 and 10). Appendix C supplements the proofs and experimental results in the included-sums and excluded-sums chapter (Chapter 12).

## Chapter 2

## The Locality-First Strategy

This chapter argues that the locality-first strategy provides a principled method for general multicore algorithm engineering in four parts.

Section 2.1 motivates the need for a principled method for algorithm engineering on multicores by describing the challenges involved in optimizing programs on multicores. As we shall see, both parallelism and locality are difficult to achieve separately. They are even more challenging to achieve simultaneously because they often conflict with each other.

Section 2.2 justifies why the locality-first strategy is a good method for general algorithm engineering with practical and principled reasons. For example, the localityfirst strategy simplifies multicore algorithm development by focusing on the serial execution first.

Section 2.3 shows how the locality-first strategy created the artifacts that enhance spatial locality — Terrace, PPCSR, PHIL, and the write-optimized skip list artifacts — by changing the data layout.

Section 2.4 explains how the locality-first strategy relates to the artifacts that exploit locality without changing the layout — the cyclic analysis, lower bounds, smoothed analysis, scan-hiding, CAST\_BLK, PAIR\_BLK, bidirectional box-sum, and box-complement artifacts.

### 2.1 Creating efficient multicore algorithms

Why do we need a principled method for creating efficient multicore algorithms? To get good performance for a multicore application, a performance engineer must design algorithms to exploit two principal multicore hardware features: a steep cache hierarchy and multiple cores numbering into the hundreds. Exploiting each of these features is complex and requires theoretical and practical expertise. Without a principled approach, optimizations for one feature may be pessimizations for the other.

To understand the issues involved more deeply, this section is broken into four parts. The first part reviews multicore hardware and argues that the cache hierarchy and the multiple cores are the salient hardware features in algorithm engineering on multicores. The second part explores cache-friendly algorithms and how they enable a performance engineer to take advantage of the cache hierarchy. The third part addresses task-parallel algorithms, which abstract and simplify the programming of multiple cores, and the issues of nondeterminism and scalability that complicate parallel programming. The fourth part illustrates the problems inherent in trying to optimize for both cache-friendliness and parallelism at the same time by providing concrete examples such as false sharing and contiguous data.

#### Multicore hardware features

To understand in detail the issues involved in cache-friendly algorithms, parallel algorithms, and their interaction, however, it will be helpful to review the characteristics of multicore hardware. Modern multicore processors are characterized by three salient architectural features — the cache hierarchy, multiple cores, and vector units — as well as a host of other architectural features such as prefetching, instruction-level parallelism, and symmetric multithreading, which we won't discuss.

The Amazon c5.metal instance [10] provides a good example of a modern multicore. It contains two Intel Cascade Lake [91] processors each with 24 cores for a total of 48 physical cores, and a clock speed of 3.4GHz. Each core is hyperthreaded (Intel's term for symmetric multithreading), so it has a total of 96 virtual cores. Each core has a private 32Kb L1 cache that takes about 0.5 seconds to access [115] and a 1MB L2 cache that takes about 7ns to access. Each processor also has a shared L3 cache of 1.375 MB/core for a total of 33 MB/processor that takes about 25ns to access [115]. The entire system has 192 GB of main memory that takes about 100ns to access [115]. Each core also has vector units capable of 8 simultaneous 64-bit floating point operations. The c5.metal instance has a steep cache hierarchy, almost 100 virtual cores, and vector units.

Of the three salient features of a multicore, vector processing is comparatively wellunderstood and exploited by applications because of advances in compiler technology [233,248,268]. In contrast, compilers cannot access a huge space of cache-friendly optimizations because they cannot arbitrarily rearrange data representations. Furthermore, although there has been progress on automatic task parallelism to take advantage of the multiple cores [142, 316, 366], these technologies are still immature and not widely used. For example, the automatic parallelization feature in gcc currently only applies to loops that the compiler can determine contain no dependencies [284, 380]. Although there remain many compelling open questions in the area of vectorization, this thesis focuses on the hard problem of creating multicore algorithms that exploit the cache hierarchy and the multiple cores.

Furthermore, although GPUs are a key part of today's computing substrate, GPU algorithm engineering is outside of the direct scope of this thesis because it is a separate subsystem from multicores. Multicore systems such as the Amazon p2 instance series may offer multicore processors with attached GPUs that rely on the multicore as a host processor to run programs and store data GPUs [314]. The CPU and GPU are separate computing systems: algorithms for CPUs and GPUs are written in different languages and are run on one of the platforms but not both simultaneously. Furthermore, not all multicore platforms have attached GPUs. For example, the c5.metal instance, one of Amazon's most powerful multicores, does not have

a GPU. Furthermore, although GPUs exhibit more parallelism than multicores can outperform GPUs by orders of magnitude on irregular workloads [89] because GPUs are optimized for regular workloads. These results demonstrate that especially for irregular applications such as dynamic graph processing in Chapters 3 and 4, multicores can achieve comparable or better performance compared to GPUs. Finally, the locality-first strategy also applies to GPU programming because GPUs have hierarchical memory [173]. Specifically, GPUs have on-chip shared memory and global memory. Accessing shared memory on a GPU is about  $100 \times$  faster than accessing global memory on a GPU [173]. Therefore, optimizing GPU programs for temporal locality has the potential for significant performance improvement by avoiding accesses to global memory [172]. The focus of this thesis is on multicore algorithm engineering because multicores can solve general problems efficiently.

Designing algorithms for both cache-friendliness and parallelism is necessary for peak performance on a multicore. In the Cascade Lake processor, the maximum speedup from cache-friendliness was about  $100 \times$  (the difference between a L1 and main memory access). Additionally, the maximum parallel speedup was almost  $100 \times$  (the number of cores). Optimizing algorithms for only one of these features leaves orders of magnitude of performance on the table.

#### Cache-friendly algorithms

To understand how to optimize programs on multicores, let us first turn our attention to how to exploit locality for cache-friendliness.

To understand in detail the issues involved in creating cache-friendly algorithms, it will be helpful to review the types of locality that algorithms can optimize for. As mentioned in Chapter 1, there are two types of locality: spatial locality — the tendency of programs to access nearby data over time — and temporal locality — the tendency of programs to access the same data over time. Depending on the problem, an algorithm may exploit either spatial locality, temporal locality, or both.

To see why exploiting locality is important for cache-friendliness, let us consider a simplified multicore memory system. The first main component of a memory system is the *cache hierarchy*: a sequence of memory stores with varying access speeds and sizes. For simplicity, let us consider a cache hierarchy with two levels: a large slow main memory and a small fast cache. Optimizing algorithms for temporal locality exploits the cache hierarchy by maximizing accesses to the cache and avoiding slow accesses to memory. The second main component of a memory system is the *cache line*: the unit of data transfer between cache and main memory. A computer's memory is divided into contiguous, non-overlapping units called cache lines. Cache lines are usually multiple bytes (e.g. 64 bytes). If a program requests data that is not already in the cache, the memory system brings the entire cache line that data resides in from main memory to cache. Optimizing algorithms for spatial locality exploits cache lines by maximizing the amount of contiguous useful data and minimizing memory block transfers.

The classical **Disk-Access Machine** (DAM) model [3] due to Aggarwal and Vitter formalizes this simplified memory system. It models two levels of memory: a small bounded-size cache of size M, and an unbounded-size memory. Any data must

be brought to the cache first before it is processed. Data is transferred in blocks of size B between the cache and the memory, and transfers have unit cost. Algorithms that achieve speedup in M in the DAM model take advantage of temporal locality to reuse data as much as possible while it is in cache. On the other hand, algorithms that achieve speedup in B in the DAM model take advantage of spatial locality to minimize cache-line transfers. The DAM model enables algorithm developers to reason about cache-friendliness in a straightforward way without requiring them to know the exact details of the underlying memory system [19, 367].

Unfortunately, the DAM model abstracts away important details of the real-world memory systems. In reality, memory systems have many levels of cache, so maximizing cache-friendliness requires reusing data optimally in all of the levels. These levels of cache and main memory make up Random Access Memory (RAM). Additionally, memory systems contain a disk: a larger and slower level of storage outside of RAM. Memory-block sizes differ between RAM and disk, so a single setting of the block size B may not capture all of the benefits of block transfers between multiple levels of memory.

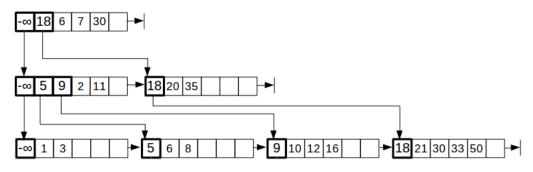

To understand a concrete example of the challenges that these details pose to engineering real-world cache-friendly algorithms, let us consider the classical B-tree [34], a widely-used data structure in large indexes and databases.

The gap between the theory and practice of B-trees illustrates the general complexity of developing cache-friendly algorithms. In theory, the B-tree [34] achieves asymptotically optimal performance in the DAM model when the tree-node size is set to the block-size parameter B [76]. Programming a theoretically optimal B-tree is difficult because it requires knowledge of the underlying memory-block size, which depends on the architecture. Furthermore, in practice, the optimal tree-node size depends not only on the underlying hardware but also on the workload [42]. The right tree-node size can even vary by orders of magnitude [42]. For example, Btrees in databases and file systems often use a node size of 16Kb [258, 266, 275], while B-trees optimized for range queries use larger node sizes around 1MB [289, 300]. The complexity of engineering efficient B-trees demonstrates that developing efficient cache-friendly algorithms involves expertise in both the hardware and the problem.

#### Parallel algorithms

Let us turn our attention to how to optimize programs for *task parallelism*, a type of parallelism that distributes tasks performed by threads across cores [134,231,322,353]. Since the focus of this thesis is on how to take advantage of the multiple cores, the remainder of this thesis will refer to "task parallelism" as *parallelism*.

Although tremendous progress has been made in mitigating challenges to developing efficient parallel algorithms, creating parallel algorithms is still notoriously difficult because of the issues of nondeterminism and scalability [203, 286, 319, 334]. *Dynamic multithreading* [24, 30, 155, 237] platforms have emerged as the dominant way to take advantage of task parallelism. Dynamic multithreading enables a *processor-oblivious* programming model that enables algorithm developers to expose parallelism without explicitly scheduling the physical cores. The fundamental challenges of nondeterminism and scalability remain, however, because they stem from the ability of parallel algorithms to perform logically discrete computations at the same time.

Nondeterminism is one of the key difficulties in developing correct and efficient parallel algorithms [238]. Parallel algorithms may exhibit *nondeterministic behavior* — different behavior on different runs even on the same input — due to how the operating system schedules and executes threads during any particular run of the program [319]. For example, parallel algorithms may contain determinacy races, or nondeterministic behavior due to two parallel threads accessing the same memory location and at least one updating it. Determinacy races may disrupt correctness and performance [145]. Additionally, determinacy races pose challenges to traditional debugging techniques, because the bug may not occur in every run of the program [145].

Researchers [54, 55, 62, 68, 145] have proposed *deterministic parallelism* in response to the problem of nondeterminism, but many practical parallel codes still exhibit nondeterministic behavior. Deterministic parallel programs avoid programmerobservable nondeterminism. They simplify testing and debugging by theoretically reducing reasoning about correctness to reasoning about the corresponding serial program. Additionally, deterministic algorithms can be practically fast [64]. Many real-world parallel codes exhibit nondeterministic behavior, however, because existing parallel-programming technologies do not provide a general framework for deterministic parallel programming [319]. Because of the nondeterminism issue, creating correct and efficient parallel codes requires theoretical and practical expertise.

Furthermore, tremendous research effort has been devoted to addressing the "scalability" issue, but developing general scalable parallel algorithms remains challenging. *Scalable* parallel algorithms achieve improved performance by computing with more cores. As we shall see, algorithm developers can use "work-span analysis" [108, Chapter 27] to theoretically characterize scalability by identifying and analyzing logically parallel tasks. Achieving good scalability requires insight, however, to parallelize seemingly serial computations in a clever way [65, 66, 129, 175, 203, 204, 239, 249, 319, 334, 339]. Moreover, profiling the scalability of parallel codes is much more difficult than profiling the runtime distribution in serial codes [177, 320]. To address this issue, researchers have introduced efficient scalability profilers based on "work-span analysis" [177, 320]. These technologies are immature, however, and may not apply to other threading models. Because of the scalability issue, developing efficient parallel codes requires both deep theoretical design and analysis as well as careful engineering.

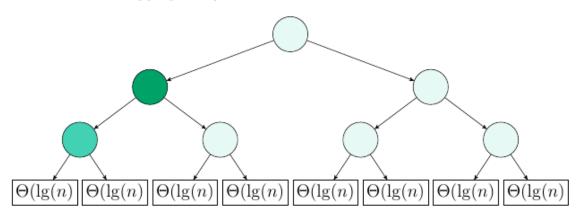

**Work-span analysis**<sup>1</sup> [108, Chapter 27] formalizes scalability by analyzing the cost of parallel algorithms in terms of their "work" and "span." For concreteness, let  $\mathcal{A}$  be an algorithm. The **work** of  $\mathcal{A}$ , denoted by Work( $\mathcal{A}$ ), is the total time to execute the entire algorithm in serial. The **span**<sup>2</sup>, denoted by Span( $\mathcal{A}$ ), is the longest serial chain of dependencies in the computation (or the runtime on an infinite number of processors). The **parallelism** of an algorithm is defined as the work divided by the span, or Work( $\mathcal{A}$ )/Span( $\mathcal{A}$ ). Algorithms with more parallelism are

<sup>&</sup>lt;sup>1</sup>This thesis omits the theoretical foundations of work-span analysis because the main contributions are not in the analysis of parallel algorithms, but the formal model is presented in tutorial fashion in [319, Chapter 2].

<sup>&</sup>lt;sup>2</sup>Sometimes called **critical-path length** [67] or **computational depth** [62].

more scalable because more of the work can be performed in parallel. Work-span analysis characterizes scalability in parallel algorithms without the exact details of the underlying machine.

Work-span analysis enables algorithm developers to predict how much speedup a parallel algorithm will achieve on a given machine. Given some program running on Pprocessors, let  $T_1$  be the time taken by the serial execution and  $T_P$  be the time taken by the P-processor execution. The **speedup** of the program is defined as  $T_1/T_P$ . In traditional work-span analysis, the potential speedup is upper bounded by P due to the Work Law, which states that  $T_P \geq \text{Work}(\mathcal{A})/P$ . If the program achieves speedup P, we say that the application exhibits **linear speedup**. In practice, to achieve linear speedup, a program should exhibit **ample parallelism**, or parallelism much larger than the number of processors [155].

Unfortunately, real-world parallel algorithms may not achieve the speedups predicted by work-span analysis due to other constraints on multicores. In practice, memory size and memory bandwidth bottleneck scalability for many applications [334,355]. For example, the parallel scalability of algorithms for the "graph-processing" problem studied in this thesis are limited by memory bandwidth because the problem often requires random memory access [334]. The complexity of interactions between parallelism and the memory system demonstrates the difficulty of achieving good practical scalability.

#### Tensions between parallelism and cache-friendliness

Cache-friendliness and parallelism are difficult to optimize for independently and even more difficult to combine because they tend to conflict with each other. At a high level, exploiting temporal locality involves computing on the same data over time, and exploiting spatial locality involves computing on similar (nearby) data over time. But computing on the same or similar data in parallel often leads to nondeterminism and cache-line contention, which may affect correctness and performance.

One example of this tension is false sharing: a performance bug that occurs when multiple workers access different locations in the same cache line in parallel, repeatedly invalidating that cache line in each worker's private cache and wasting system bandwidth [362]. One solution to false sharing is to pad each variable with extra bytes to force them onto different cache lines. Padding the elements disrupts cachefriendliness however, because the elements of interest are now further apart and require more cache-line reads.

Another example is the data representational choice of keeping data contiguous (e.g., in a list) or non-contiguous (e.g., in a tree). Keeping data in a list maximizes spatial locality by increasing the number of elements fetched per read and eliminating pointer-chasing. Concurrently modifying a list is much more complicated than concurrently modifying a tree, however, because a tree can support efficient concurrent updates by locking a small part at a time (e.g. with hand-over-hand lock-ing [181]), while a list-based data structure may have to lock the entire data in the worst case [379]. These examples demonstrate the conflicts between cache-friendliness and parallelism.

# 2.2 The locality-first strategy for general multicore algorithm engineering

This section presents rationale for why the locality-first strategy is a useful method for creating algorithms that achieve both cache-friendliness and parallelism. Specifically, it discusses both practical and principled reasons for a locality-first approach to algorithm optimization for multicores. It also concretizes those reasons by explaining how each one relates to the principal artifacts.

This section justifies the locality-first strategy in four parts. The first part explains that the locality-first strategy simplifies algorithm engineering by focusing on serial optimizations first before parallelism. The second part explains how the locality-first strategy creates efficient algorithms by optimizing for the total work. The third part demonstrates that optimizing for locality takes advantage of other types of hardware features available in multicores such as vector units and GPUs. Finally, the fourth part organizes the principal artifacts into categories based on the type of locality they exhibit and therefore how they relate to and support the locality-first strategy.

#### Enabling easier practical algorithm engineering

The locality-first strategy makes writing parallel codes easier because it focuses on optimizing the serial execution first. Section 2.1 shows that writing parallel algorithms is strictly more difficult than writing serial algorithms. Parallelism may introduce nondeterministic behavior and race conditions, which affect correctness and performance. Parallelism complicates performance measurement, an integral part of principled performance engineering, because of additional variability from nondeterminism in the thread scheduler [319]. Profiling the scalability of parallel codes is much more difficult than profiling the runtime distribution in serial codes [320]. The locality-first strategy simplifies algorithm design because it first produces a serial, working specification for a parallel code before moving on to parallelization.

The artifacts in this thesis concerning dynamic graph processing reflect this progression. Appendix A presents "Packed Compressed Serial Row", a serial "Packed Memory Array" data structure for dynamic graphs that enhances spatial locality before introducing parallelism. The Parallel Packed Compressed Sparse Row (PPCSR) artifact (Chapter 4) takes the next step and introduces parallelism on top of (serial) Packed Compressed Sparse Row. Since dynamic graph applications have ample parallelism, The Terrace artifact (Chapter 3) further improves performance by trading some of the parallelism in PPCSR for improved locality by taking advantage of problem structure.

#### A principled approach to creating efficient algorithms

The locality-first strategy draws inspiration from Cilk's *work-first principle* of minimizing the work of a serial algorithm, even if it adversely affects parallel scalability, because the work has a more direct impact on performance [155]. Although the Cilk multithreaded language presented the work-first principle in the context of dynamic multithreading, the artifacts in this thesis demonstrate its potential in general multicore software optimization. As we shall see later in this section, optimizing for spatial locality reduces work by taking advantage of other hardware features in multicores. In general, optimizing for cache-friendliness by exploiting locality reduces work in serial, which enables algorithms to reach their peak efficiency after parallelization.

Furthermore, in reality, exploiting temporal locality offers opportunities for continuous speedups due to the multiple levels of the cache hierarchy. For example, in modern multicores, there are multiple levels of cache (e.g. L1, L2, L3) before main memory. The DAM model expresses speedups in terms of a single memory block size B and a single memory size M. In reality, these analyses apply between any two levels of cache, resulting in more continuous speedups from exploiting locality. The maximum improvement available from taking advantage of the cache hierarchy can range up to orders of magnitude. For example, an L1 cache hit takes about 1 nanosecond, while a main memory access takes about 100 nanoseconds [115]. Additionally, a disk seek takes about 10 million nanoseconds. In contrast, speedups from parallelization are maximized at P, the number of processors. Therefore, optimizing for locality first offers multiple levels of improvement at the different levels of cache before parallelization. Chapter 9 concerns cache-oblivious algorithms, which use all levels of the cache hierarchy asymptotically optimally.

Although parallelism and cache-friendliness are in tension, the artifacts in this thesis demonstrate that trading off some parallelism for improved locality can still improve overall performance. The artifacts in this thesis support the observation in the original Cilk-5 presentation of the work-first principle that there is ample parallelism in the common case [155]. For example, "blocking" (e.g. the "blocked formats" in Chapter 5, or the "blocked prefix sums" in Chapter 11) improves overall performance by taking advantage of locality at the cost of some parallelism.

#### Taking advantage of other multicore hardware features

Optimizing for locality enables efficient usage of hardware features than enable different types of parallelism in multicores. In reality, multicores support other types of parallelism besides task parallelism, such as "instruction-level" and "data-level" parallelism. Optimizing for spatial locality enables better use of *instruction-level parallelism* such as cache prefetching, a hardware-supported optimization that brings data before it is needed into cache to reduce future latency [343]. For example, the PMA data structure in Chapter 4 achieves fast scan performance from cache prefetching because it exploits spatial locality by storing all of its data contiguously. Additionally, algorithms with good spatial locality can make better use of *data-level parallelism* via SIMD instructions that take advantage of hardware-level vector units [148]. Vectorizing the "Packed Memory Array" (PMA) data structure in Chapter 4 is more straightforward than vectorizing tree-based data structures because the PMA is contiguous in memory [379]. Optimizing for spatial locality by storing data contiguously enables other types of parallelism in multicores such as instruction-level and data-level parallelism.

## 2.3 Enhancing locality by changing the data layout

The Terrace, PPCSR, PHIL, and write-optimized skip list artifacts apply the localityfirst strategy to enhance spatial locality by changing the underlying data layout (Chapters 3-6).

The Terrace, PPCSR, and PHIL artifacts target sparse graph and sparse tensor applications and demonstrate that optimizing for spatial locality first, even at the cost of some parallelism, can improve overall performance. Many sparse computations, such as sparse graph applications, exhibit minimal temporal locality [249,276,334]. Therefore, these chapters focus on improving spatial locality by co-locating data through cache-friendly data structure design.

This section overviews this thesis's contributions regarding enhancing spatial locality in the domain of sparse applications in two steps. First, it presents challenges to locality in sparse applications. Next, it summarizes each of the artifacts in the domain of sparse applications and explains how each uses the locality-first strategy to address challenges to locality.

Finally, this section explains how to use the locality-first strategy to create the write-optimized skip list, a cache-friendly randomized data structure.

#### Background on sparse applications

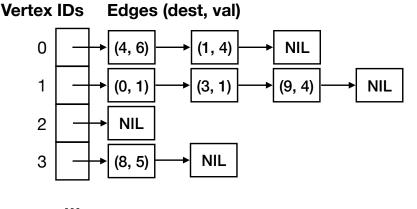

Sparse graphs and sparse tensors appear in many fundamental applications that range from scientific computing [87,369] to social networks [141,279]. **Sparse** datasets have many more zeroes than nonzeroes. For example, in social networks, most of the users are not connected to most of the other users. If the vertices are users and edges are connections between users, most of the entries representing connections would be empty.

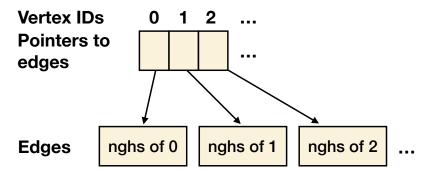

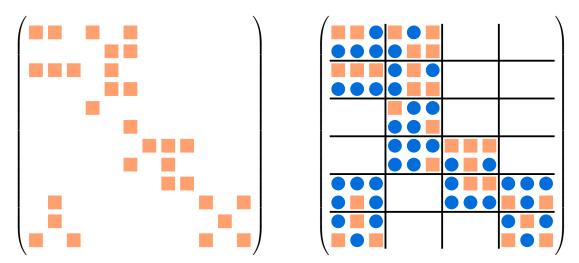

Sparsity disrupts spatial locality because of the presence of zeroes between actually present values, limiting the effectiveness of fetching multiple adjacent elements in a cache line. To illustrate this issue, let us consider an adjacency matrix representation of a graph [108]. In an adjacency matrix, a zero represents a lack of connection between vertices, while a nonzero represents an edge. Therefore, a naive representation of sparse data exhibits poor spatial locality because most of the data is zeroes.

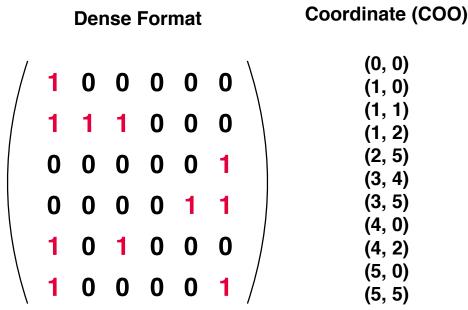

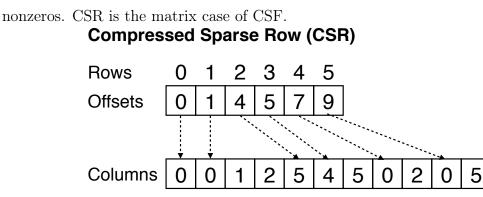

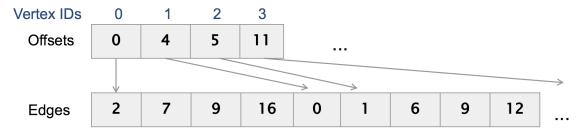

Performance engineers can improve spatial locality and algorithm complexity in sparse applications with compressed representations that store only the nonzeroes and the locations of the nonzeroes [361]. These compressed representations enable fast algorithms with work proportional to the number of nonzeroes. In practice, these data structures reduce the work by orders of magnitude because they allow direct computation over only the existing data.

As we shall see in the artifacts in this section, the introduction of *metadata*, or the locations of the nonzeroes, raises challenges and opportunities for designing scalable and cache-friendly data structures and algorithms to store and process the metadata.

#### Storing and processing dynamic graphs

Terrace and PPCSR apply the locality-first strategy to design and implement fast parallel dynamic-graph-processing systems that are optimized for spatial locality first.

Many real-world graphs ranging from machine learning graphs [303] to social networks [141,279] exhibit graph irregularity, or a sparse and skewed structure. These graphs have a skewed distribution of vertex degrees, where there are a few highdegree vertices and many low-degree vertices [279]. Furthermore, these graphs are often dynamic: they change over time. For example, dynamic-irregular graphs arise naturally in social networks, computational biology, and the Internet. Much larger problems on the order of gigabytes and up to terabytes can be efficiently solved by exploiting irregularity, which is crucial for scaling applications to handle large graphs [335].

Graph updates pose challenges to exploiting irregularity for locality because preprocessing the graph into a cache-friendly representation is infeasible when the graph changes over time. Existing static-graph-processing systems optimized for graph irregularity achieve high performance and low space usage by preprocessing a cachefriendly graph partitioning based on vertex degree [95]. In the dynamic setting, however, finding an optimal partitioning is not feasible in the presence of updates. Therefore, existing high-performance dynamic-graph-processing systems such as Aspen [128] use a **one-size-fits-all** representation, which pre-selects one type of data structure upfront for all vertices. The one-size-fits-all approach leaves performance on the table because it disrupts spatial locality by using separate per-vertex data structures.

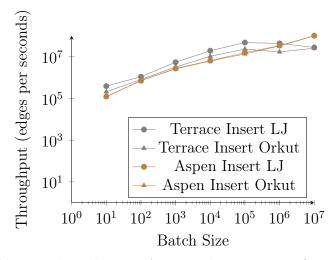

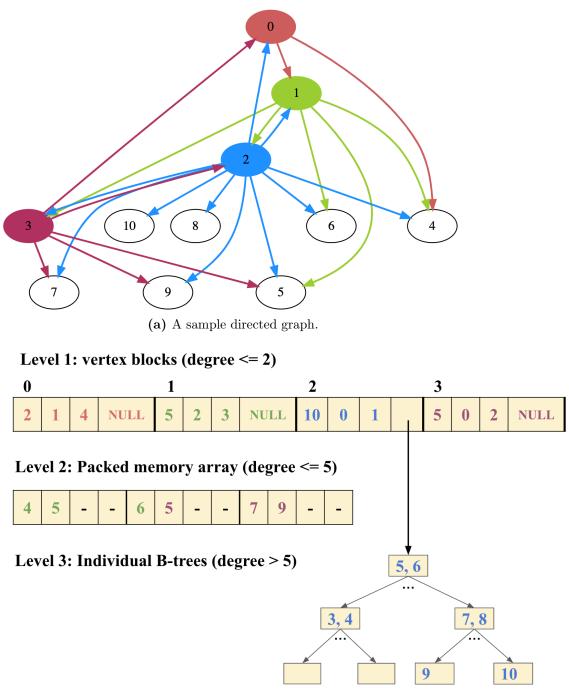

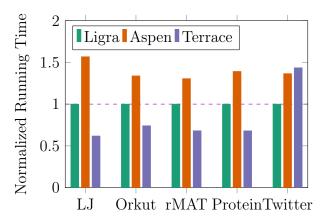

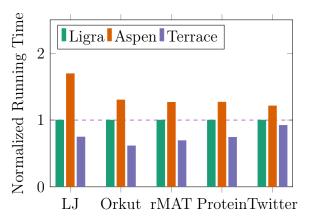

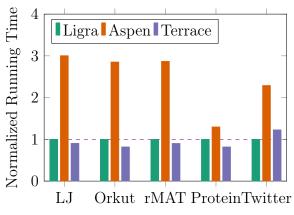

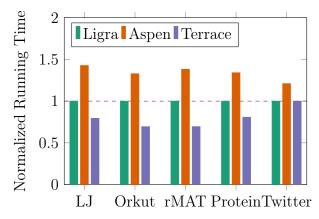

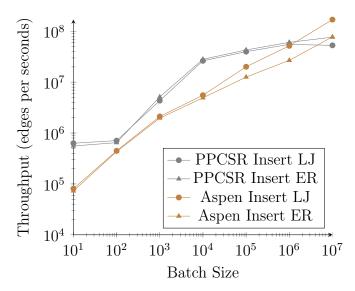

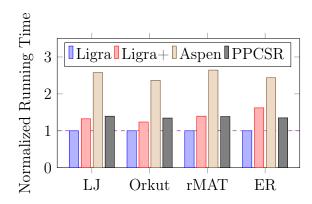

To address these challenges to locality, the **Terrace** artifact applies the localityfirst strategy to dynamic graph-processing by using cache-friendly data structures that adapt to naturally occurring irregular graph structure [294]. Terrace uses a hierarchical data structure design to dynamically partition vertices based on their degrees and adapt to skewness in the underlying graph. The evaluations in Chapter 3 show that Terrace supports faster batch insertions for batch sizes up to 1M when compared to Aspen [128]. On graph query algorithms, Terrace is between  $1.7 - 2.6 \times$  faster than Aspen. Surprisingly, in some cases Terrace is even faster (up to  $1.3 \times$  faster) than Ligra [335], a state-of-the-art static-graph-processing system, on graph queries. The reason for these performance gains is that Terrace experiences significantly fewer cache misses (in some cases, up to about  $3 \times$  fewer than Ligra and about  $6 \times$  fewer than Aspen) during graph queries because it exploits graph skewness for cache-friendliness.

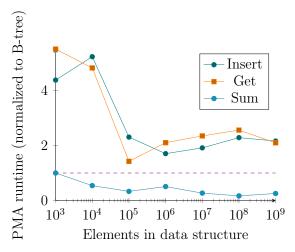

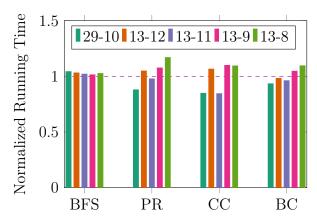

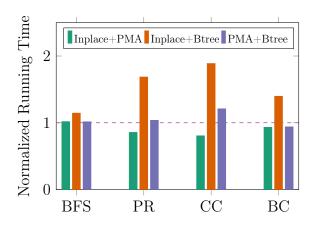

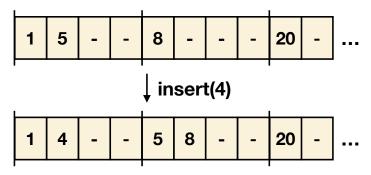

One of the main components of Terrace is the *Parallel Packed Compressed Sparse Row* (PPCSR) artifact, a dynamic-graph-processing system that applies the locality-first strategy to enhance spatial locality by co-locating all of its data [379]. PPCSR is built on top of a parallel Packed Memory Array (PMA) [44, 196] data structure. The PMA is well suited for storing and processing dynamic graphs because it supports updates and efficient scans by storing data in one contiguous block of memory [378]. Concurrently updating a PMA raises challenges, however, because an update requires rewriting the entire structure in the worst case [379]. The difficulty of updating a PMA exemplifies the tension between parallelism and cache-friendliness. Surprisingly, one of the main findings in Chapter 4 is that the PMA can achieve the best of both worlds. Specifically, the PMA is well-suited to concurrent updates despite occasionally requiring a rewrite of the entire structure because 1) most of the updates only write to a small part of the structure and 2) the worst case is highly parallel and cache-efficient [379]. These results demonstrate the performance benefits of optimizing for locality first via cache-friendly data structures in dynamic graph processing.

#### Finding block structure in sparse tensors

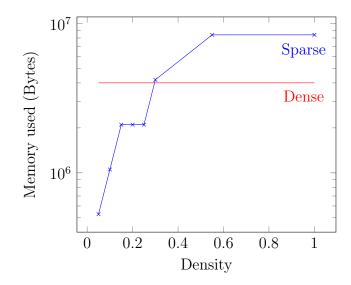

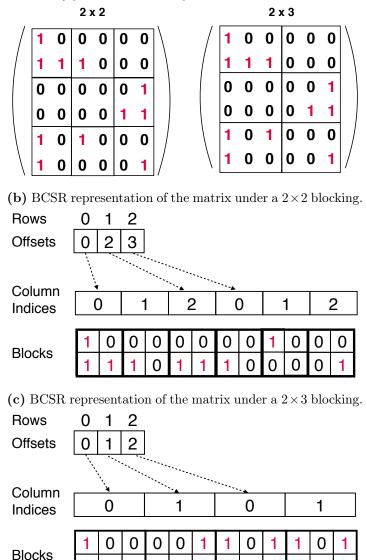

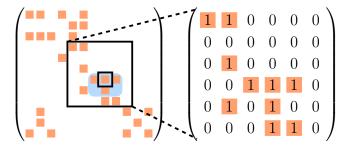

This thesis also studies the locality-first strategy in the domain of blocked formats, which address memory bandwidth issues in sparse tensor kernels by enhancing spatial locality. A common issue that arises in parallel implementations of sparse tensor algebra, such as sparse matrix-vector multiplication (SpMV), is limited memory bandwidth due to irregular memory traffic from the locations of the nonzeros.

To regularize memory traffic and improve memory bandwidth issues, researchers have developed **blocked storage formats** to take advantage of natural blocked structure, or clusters of nonzeroes, in sparse matrices [373]. Blocked storage formats store dense blocks of nonzeros instead of storing the nonzeros individually to take advantage of the natural blocked structure of some blocked sparse matrices and tensors. These blocked storage formats simplify memory traffic and enable instruction-level parallelism such as vectorization [212]. For example, choosing the correct blocking can speed up SpMV by more than a factor of 2 on matrices with blocked structure [372]. Blocked storage formats must choose a block size that is carefully tuned to match the structure of a tensor to avoid unnecessary overhead, however.

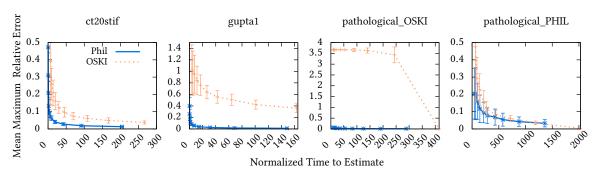

The **PHIL** artifact supports the locality-first strategy by enabling efficient usage of blocked storage formats. PHIL estimates the fill, a metric for block-size quality, with provable guarantees. The fill has important applications in autotuning pipelines, but computing the fill exactly is too expensive. As a result, researchers developed OSKI [371], an empirically fast-and-accurate heuristic for estimating the fill that samples matrix rows. In contrast to OSKI, the number of samples that PHIL requires is independent of the size of the input. This advantage of PHIL over OSKI is evident in the empirical evaluation in Chapter 5: PHIL estimates the fill at least  $2\times$  faster than OSKI on small matrices and  $40 - 50 \times$  faster on large matrices. Since PHIL has provable accuracy guarantees, it also provides useful estimates of the fill even in pathological test cases where OSKI fails to estimate the fill within any useful error. PHIL's empirical success demonstrates the potential for efficient algorithms to enhance spatial locality in sparse tensor applications.

#### Enhancing spatial locality in data structures

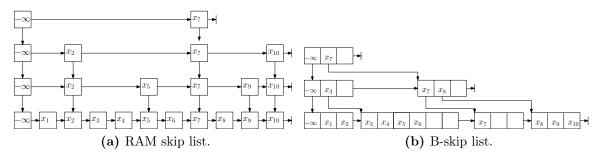

The *write-optimized skip list* artifact uses the locality-first strategy to enhance spatial locality in general data structures. Although the write-optimized skip list is a serial data structure, it is a first step towards an efficient parallel and cache-efficient skip list. The skip list is an elegant and simple randomized in-memory data structure that supports efficient searches, inserts, and deletes. As we shall see in Chapter 6,

there are theoretical challenges to getting the skip list to generalize well to external memory, however. The intuitive method to convert an in-memory skip list to an out-of-memory skip list does not achieve good high-probability guarantees. The write-optimized skip list overcomes these challenges and to achieve *write-optimized* bounds. That is, given a memory-block size B, for  $0 < \varepsilon < 1$ , a write-optimized skip list on N elements supports queries of size K in  $O(\log_{B^{\varepsilon}} N + K/B)$  I/Os with high probability (w.h.p.) and insertions and deletions in  $O((\log_{B^{\varepsilon}} N)/B^{1-\varepsilon})$  amortized I/Os w.h.p. That is, the write-optimized skip list supports asymptotically optimal searches, inserts, and deletes. Furthermore, it supports inserts and deletes asymptotically faster than searches. The write-optimized skip list applies the locality-first strategy by first exploiting spatial locality in data structure design as a step towards efficient parallel data structures.

# 2.4 Exploiting locality without changing the data layout

The cyclic analysis, lower bounds, smoothed analysis, scan-hiding, CAST\_BLK, PAIR\_BLK, bidirectional box-sum, and box-complement artifacts apply the locality-first strategy to exploit locality in problems without changing the data layout. These artifacts take advantage of naturally-occurring spatial and temporal locality by modifying algorithm access patterns to make them cache-friendly (Chapters 7-12).

The cyclic analysis and smoothed analysis artifacts theoretically ground the localityfirst strategy via "beyond-worst-case" analysis [315] and demonstrate that algorithms that are designed to fully exploit temporal locality are mathematically good despite potential disruptions to cache-friendly access patterns due to parallelism. These artifacts study the case where algorithms exhibit temporal locality, but multiple threads compete for space in a shared cache. These artifacts address a potential concern with the locality-first strategy that locality trades off with parallelism.

These artifacts characterize the practical benefits of the locality-first strategy by bringing theory and practice together via "beyond-worst-case" analysis. **Beyondworst-case** analysis is a class of algorithmic techniques that consider algorithm performance outside of a single worst-case input. Beyond-worst-case analysis closes the gap between theory and practice in cases where worst-case analysis fails to capture realistic inputs. For example, it compares algorithms on more realistic inputs, such as those with locality, whereas traditional worst-case analysis compares algorithms on a single worst-case input. As a result, beyond-worst-case analysis presents a more holistic view of algorithm performance.

This section overviews this thesis' contributions in mathematically grounding the locality-first strategy with respect to two problems: "multicore cache-replacement" and "cache-adaptive algorithms." Specifically, it summarizes the cyclic analysis and lower bounds artifacts for "multicore cache-replacement" and the smoothed analysis and scan-hiding artifacts for "cache-adaptive algorithms." For each problem, this section describes challenges to locality due to parallelism in shared caches, summarizes the relevant artifacts, and explains how they support the locality-first strategy.

Finally, this section demonstrates how to apply the locality-first strategy when the problem has spatial locality and not much temporal locality. Since spatial locality is easy to achieve in these problems, the main focus is on other optimizations. By understanding locality in the problem first and exploiting it as much as possible, the locality-first strategy created the CAST\_BLK and PAIR\_BLK artifacts for the "prefix sums" problem, the bidirectional box-sum artifact for the "included sums" problem, and the box-complement artifact for the "excluded sums" problem.

#### Multicore cache replacement

As we shall see in more detail in Chapter 8, multiple parallel threads in a multicore environment disrupt the cache-friendliness of each individual thread's memory access pattern by causing cache evictions due to threads contending for space. Every processor with a cache needs to implement a cache-replacement algorithm, or an algorithm that manages the data in cache by deciding what to evict and what to keep when the cache becomes full. Single-core cache-replacement is a classical problem in online algorithms [342] and has inspired a decades-long line of both theoretical and practical research [195,207]. The multicore setting differs significantly from the single-core setting, however: for example, López-Ortiz and Salinger [251] demonstrated that competitive ratio of canonical cache-replacement algorithms such as Least-Recently-Used and Furthest-In-Future grows with the length of the input in the multicore setting (as opposed to growing with the size of the cache in the single-core setting). This divergence between multicore and single-core cache-replacement mathematically validates the tension between parallelism and cache-friendliness.

The cyclic analysis and lower bounds artifacts mathematically ground the localityfirst strategy for the multicore cache-replacement problem by validating the empirical superiority of the Least-Recently-Used (LRU) algorithm because LRU takes advantage of locality.

The *cyclic analysis* artifact mathematically justifies the locality-first strategy by showing the advantage of LRU in the presence of temporal locality via the *cyclic analysis* artifact, a new technique for beyond-worst-case analysis [210]. Cyclic analysis compares online algorithms on the entire space of inputs rather than a single worst-case input. Under cyclic analysis, LRU is the single best online algorithm on inputs with (temporal) locality in the multicore setting. These results demonstrate the potential of alternative beyond-worst-case measures to separate multicore cache-replacement algorithms and to capture real-world performance. Specifically, cyclic analysis grounds the observed superiority of LRU in practice because it exploits naturally-occurring locality [8].

The *lower bounds* artifact motivates beyond-worst-case analysis for multicore caching algorithms by showing that all known deterministic algorithms are equally arbitrarily far from optimal [209]. This work answers an open question from past work about the existence of a competitive algorithm in the negative. This lower bound fails to capture real-world differences between algorithms due to naturally-occurring locality, however. Despite these negative equivalence results from worst-case analysis, algorithms exhibit different real-world performance due to locality, motivating alternative measures that capture these differences.

#### Cache-adaptive algorithms

Additionally, multiple programs sharing a cache each experience *memory fluctuations*, or dynamically changing cache sizes, that potentially disrupt each program's cache-friendliness [94, 122, 123]. Systems that require programs to share a cache such as shared-memory machines, multicore architectures, and time-sharing systems are ubiquitous in modern computing. Memory fluctuations are the common case in shared-memory machines such as multicores, where threads share cache and RAM. Multiple programs in a shared cache pose challenges to taking advantage of locality, however. For example, optimally cache-friendly algorithms in a fixed-size cache may not be optimal when the cache size changes over time. In the worst case, an algorithm may become logarithmically worse when the cache size fluctuates [45]. This divergence between algorithm performance in fixed-size and variable-size caches further reinforces the tension between parallelism and cache-friendliness.

To cope with memory fluctuations, experimentalists have developed heuristics and experimentally fast algorithms that perform well in practice but unfortunately are vulnerable to worst-case inputs [295, 296]. These algorithms include empirically efficient algorithms for major operations such as database sorts and joins. Although these empirical solutions achieve performance improvements on practical workloads, they lack theoretical analysis and worst-case guarantees.

To provide mathematical grounding for algorithms in the face of cache fluctuations, researchers have studied *cache-adaptive algorithms* that gracefully handle changes in cache allocation with worst-case guarantees [43,45]. An algorithm is cache adaptive if it achieves optimal utilization of the dynamically changing cache. Prior work on cache adaptivity, used worst-case analysis to separate algorithms, however, which may be overly pessimistic due to carefully constructed worst-case inputs.

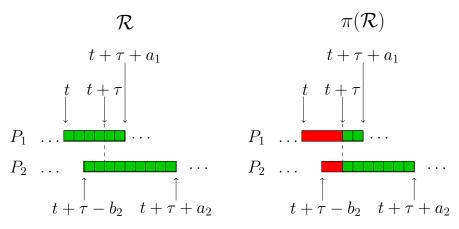

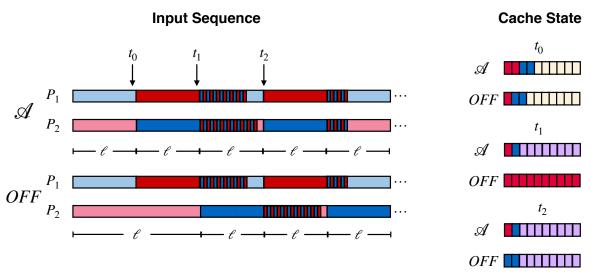

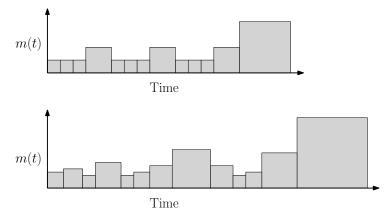

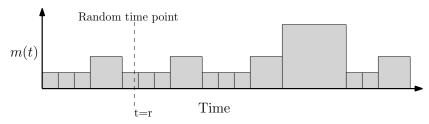

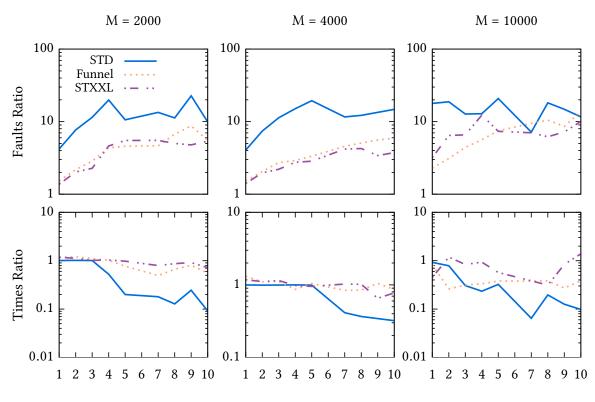

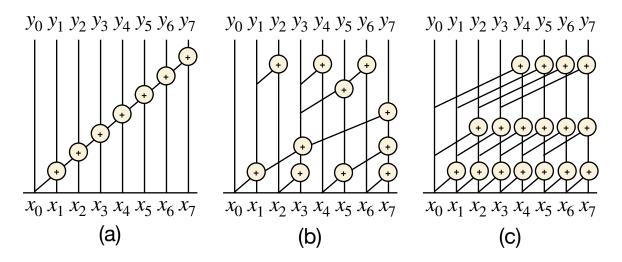

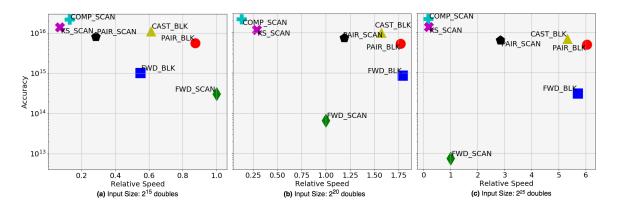

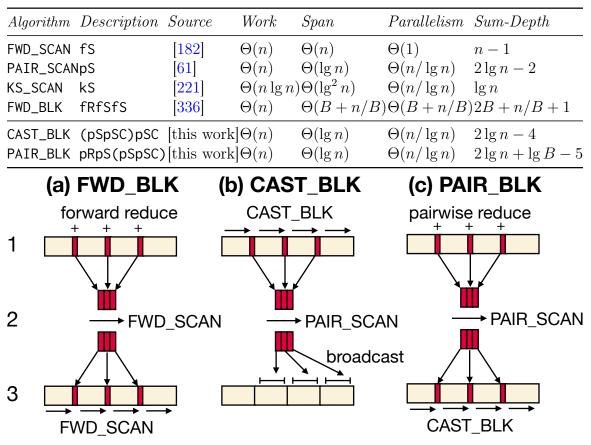

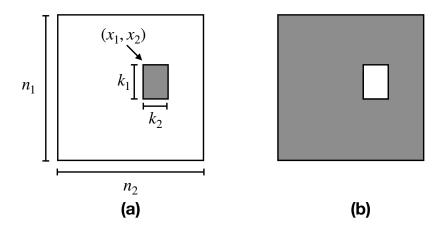

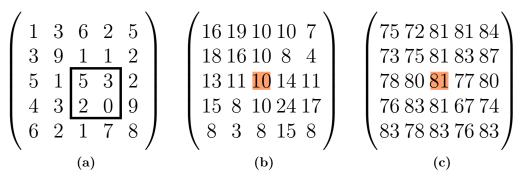

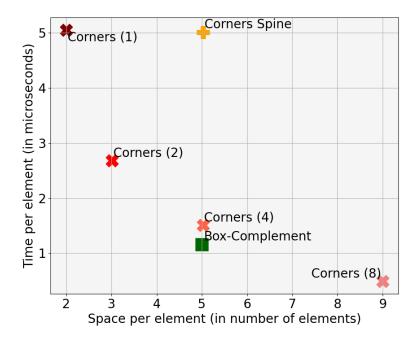

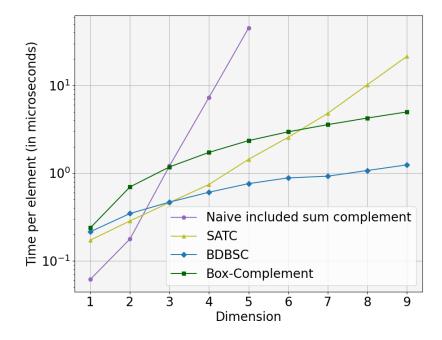

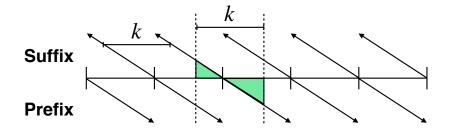

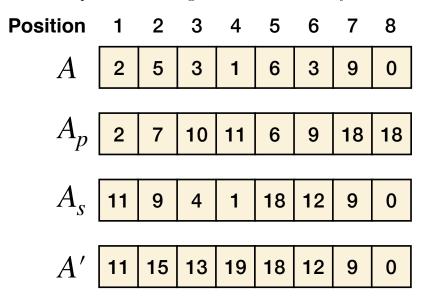

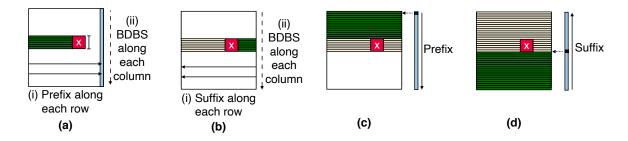

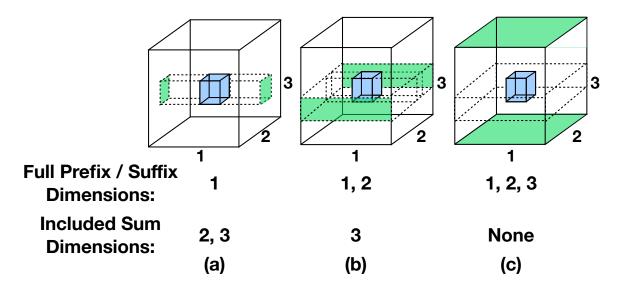

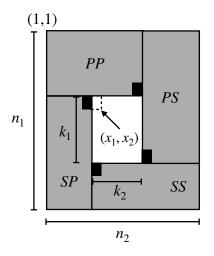

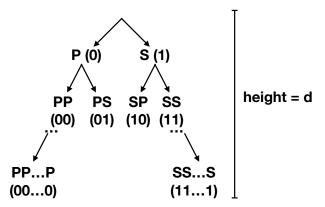

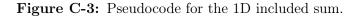

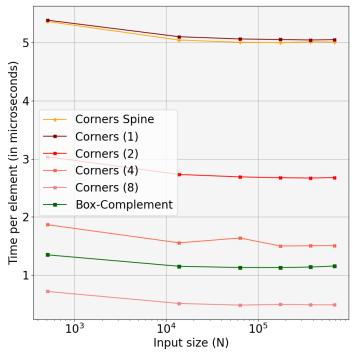

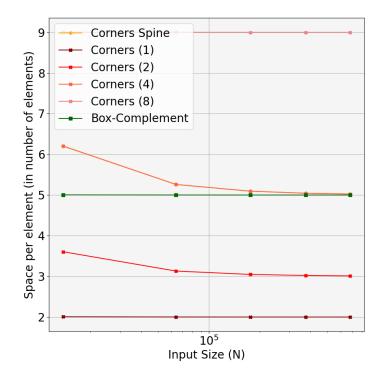

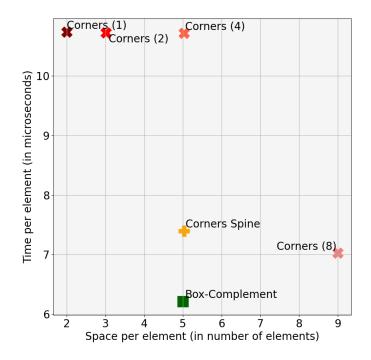

The smoothed analysis and scan-hiding artifacts mathematically ground the localityfirst approach for cache-adaptive algorithms. These artifacts prove that algorithms that take advantage of temporal locality as much as possible adapt well to cache fluctuations.