# **Accelerating Irregular Applications with Pipeline Parallelism**

by

# Quan Minh Nguyen

B.S., University of California, Berkeley (2014) S.M., Massachusetts Institute of Technology (2016)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2022

© Massachusetts Institute of Technology 2022. All rights reserved.

| 1                                                                                    |

|--------------------------------------------------------------------------------------|

| Nuthor                                                                               |

| Certified by                                                                         |

| Associate Professor of Electrical Engineering and Computer Science Thesis Supervisor |

| Accepted by Leslie A. Kolodziejsk                                                    |

| Professor of Electrical Engineering and Computer Science                             |

Chair, Department Committee on Graduate Students

# Accelerating Irregular Applications with Pipeline Parallelism by

# Quan Minh Nguyen

Submitted to the Department of Electrical Engineering and Computer Science on May 13, 2022, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

Irregular applications have frequent data-dependent memory accesses and control flow. They arise in many emerging and important domains, including sparse deep learning, graph analytics, and database processing. Conventional architectures cannot handle irregular applications efficiently because their techniques for improving performance, like exploiting instruction-level or data-level parallelism, are not tailored to them. Thus, continued progress in these crucial domains depends on exploring new avenues of parallelism.

Fortunately, irregular applications contain abundant but untapped *pipeline parallelism*: they can be divided into networks of stages. Pipelining not only exposes parallelism but also enables *decoupling*, which hides the latency of long events by allowing producer stages to run ahead of consumer stages. To properly decouple these applications, though, this pipeline parallelism must be exploited at *fine-grain*, with few operations per stage. Prior work has proposed architectures, compilers, and languages for pipelines, but focus on *regular* pipelines, and thus are unable to overcome several challenges of irregular applications. First, architectures need to support the efficient execution of many fine-grain pipeline stages. Second, such irregular pipelines suffer from load imbalance, as the amount of work in each stage varies rapidly as the program runs. Finally, these stages must communicate and coordinate changes in control flow.

This thesis demonstrates that exploiting fine-grain pipeline parallelism in irregular applications is effective and practical. To this end, this thesis proposes two hardware architectures and a compiler: Pipette, the first architecture, reuses existing structures in modern out-of-order cores to implement load-balanced decoupled communication between stages; and Fifer, the second architecture, makes the acceleration benefits of coarse-grain reconfigurable arrays available to irregular applications. Pipette achieves gmean 1.9× speedup over a data-parallel implementation, and Fifer achieves up to 47× speedup over an out-of-order multicore while using considerably less area. Both architectures also further accelerate challenging memory accesses and resolve the load balancing and control flow challenges that are ubiquitous in irregular applications. Finally, Phloem is a compiler that makes it easy for programmers to use these architectures by producing high-performance pipeline-parallel implementations of irregular applications from serial code. Phloem automatically achieves 85% of the performance of manually pipelined versions.

Thesis Supervisor: Daniel Sanchez

Title: Associate Professor of Electrical Engineering and Computer Science

## Acknowledgments

I am so lucky.

My fortune starts with my adviser, Daniel Sanchez, model scholar and without whom this thesis would not have been possible. Simply stated, he has taught me to be a better researcher. He kept me focused on the task at hand and has never hesitated to help me understand something, whether it's the first, second, or umpteenth time he's had to explain it. His breadth of knowledge, and his even bigger heart, is inimitable. Most of all, I will never forget the grace with which he welcomed me into his group, during a time in which I didn't believe in myself. I hope this thesis attests to how much I do now.

I would like to extend my gratitude to my thesis committee members, Joel Emer and Vivienne Sze. Joel has taught me that finding the answer to something often starts with finding the right name for it. I hope to emulate his ability to place every technological advance in the context of every one that came before it. Vivienne, who also served on my RQE committee, provided me with valuable perspectives and helped me truly understand the hardware-software interface.

Many professors have been instrumental to my growth and development as a student and as a person. Srini Devadas was the first to welcome me to MIT. Silvina Hanono Wachman and Arvind taught me what it meant to be a good teacher. Saman Amarasinghe and Mengjia Yan provided important insights, about programming languages, security, and more. Back at Berkeley, Krste Asanović started me down the road of computer architecture research. My thanks extend not only to these professors but also the teachers from Troy High School, Brea Junior High, and Fanning Elementary, who have all inspired me and motivated me and whose lessons I seek to pass on to my own students some day.

#### I extend my sincere appreciation:

To the fine gentlemen of the central committee of 32-G884: Victor Ying, Hyun Ryong (Ryan) Lee, Axel Feldmann, and Yifan Yang. You all made it worth going to the office every day. Within those four surprisingly square walls we learned much more than just computer architecture, and I will always remember the banter and laughter we shared together.

And the members of the broader Sanchez group: Nathan Beckmann, Suvinay Subramanian, Nosayba El-Sayed, Po-An Tsai, Mark Jeffrey, Guowei Zhang, Anurag Mukkara, Domenic Nutile (:fist-bump:), Maleen Abeydeera, Nikola Samardzic, Shabnam Sheikhha, Fares Elsabbagh, Robert

Durfee, Kendall Garner, and Aleksandar Krastev. There has been no more gratifying experience than to be in the presence of such caring, intelligent people. Whether it was through giving paper feedback or being in the mountains of Maine, you guys helped me find where I was (and not just in GeoGuessr). You all are part of this thesis, too.

To Ilia Lebedev and Kyle Hogan: thanks for all those coffee walks to Area Four and, more importantly, helping me through a low point in my graduate career. You two showed me the subtle power of a simple conversation. To Chris Fletcher, Albert Kwon, Alin Tomescu, Hsin-Jung Yang, Zachary Newman, Xiangyao Yu, Sabrina Neuman, Sang-Woo Jun, Andy Wright, Thomas Bourgeat, Sizhuo Zhang, and Murali Vijayaraghavan: you all provided mentorship and friendship during my many years here at the Institute. To Sally Lee for your administrative support and tolerating my chatter.

To the students I have had the privilege to teach and mentor, including SuperUROPs Parker Huntington, Shahir Rahman, and Nithya Attaluri and my 6.175 and 6.004 students. Nothing has made me feel quite as complete as the chance to teach all of you.

To the friends I've made while at MIT, Jon Zhu, Matt Melissa, Sumit Dutta, Jon Gjengset, and Greg Izatt: all of you made our fair city a terrific home for the last eight years. All too brief, but Daniel Mark, Victoria Preston, Sara Sheffels, and Anna Zeng of the Lindy Hop Society helped me find great joy in this last year at MIT. Willie Boag and Vishwak Srinivasan of the CSAIL Student Committee made it a delight to run SIGTBD not just once, but twice. Thanks to these folks, I indeed did have fun at MIT.

To *Thầy Bình*, *Nhi* (Jacquie), and *Tuấn-Anh*: you helped me learn my mother tongue at Harvard.

To my pals from Troy High School: Fady Barsoum, Sen Hirano, Aadil Hussaini, Jennifer Kadowaki, Albert Ou, Lisa Park, Amy Shieh, Aaron Tran, Nolan Vorck, Vivian Wang, and Wendy Yang, you guys are filled with fun medical facts and not everyone has the luck of having such a close group of friends that have stuck together for over a decade and going. Y'all raised me.

To my fellow Berkeley bears, who helped get me here: Mehrdad Niknami (hello), Michael Stephen Ting, Zachary Hargreaves, Stephen Twigg, Yunsup Lee, Andrew Waterman, and the Lindy on Sproul club, you helped set me up for success.

To Liz Chen, my partner, who helped get me out: thank you for your love and support, and for sticking it out with me for all these years. Thanks to Evie and Milo (*Felis catus*), who helped me prepare this thesis, kind of.

To  $Uy\hat{e}n$ , my loving, hardworking, intelligent baby sister: I know you will always have my back and I'll always have yours. To  $C\hat{o}$  Hai: thank you,  $c\acute{a}m$  on, for making it possible for me to go to grad school. To my cousins, aunts, uncles, and grandparents: you always supported my ambitions and gave indispensable life advice to take along with me.

Finally, to Ba and Má: my parents, my original teachers.

Q.M.N. Cambridge, Mass.

# **Contents**

| Ał | Abstract 3 |                                                        |    |  |  |  |

|----|------------|--------------------------------------------------------|----|--|--|--|

| 1  | Intr       | oduction                                               | 13 |  |  |  |

|    | 1.1        | Challenges                                             | 15 |  |  |  |

|    | 1.2        | Contributions                                          | 16 |  |  |  |

|    | 1.3        | Thesis Organization                                    | 18 |  |  |  |

| 2  | Bac        | kground and Related Work                               | 19 |  |  |  |

|    | 2.1        | A Fully Fledged Example: Breadth-First Search          | 20 |  |  |  |

|    | 2.2        | Related Work                                           | 22 |  |  |  |

| 3  | Pipe       | ette: Improving Core Utilization with Intra-Core       |    |  |  |  |

|    | Pipe       | eline Parallelism                                      | 29 |  |  |  |

|    | 3.1        | Introduction                                           | 29 |  |  |  |

|    | 3.2        | Pipette ISA                                            | 31 |  |  |  |

|    | 3.3        | Pipette Microarchitecture                              | 37 |  |  |  |

|    | 3.4        | Experimental Methodology                               | 42 |  |  |  |

|    | 3.5        | Evaluation                                             | 45 |  |  |  |

|    | 3.6        | Summary                                                | 53 |  |  |  |

| 4  | Fife       | r: Practical Acceleration of Irregular Applications on |    |  |  |  |

|    | Rec        | onfigurable Architectures                              | 55 |  |  |  |

|    | 4.1        | Introduction                                           | 55 |  |  |  |

|    | 4.2        | Background and Motivation                              | 57 |  |  |  |

|    | 4.3        | Baseline CGRA Architecture                             | 61 |  |  |  |

|    | 4.4        | Extracting Regular Stages from Irregular Applications  | 63 |  |  |  |

|    | 4.5        | Fifer Architecture                                     | 65 |  |  |  |

|    | 4.6        | Fifer Implementation                                   | 72 |  |  |  |

|    | 4.7        | Experimental Methodology                               | 73 |  |  |  |

|    | 4 8        | Evaluation                                             | 75 |  |  |  |

|     | 4.9   | Summary                                              | 81  |

|-----|-------|------------------------------------------------------|-----|

| 5   | Phlo  | em: Automatic Acceleration of Irregular Applications |     |

|     | with  | Fine-Grain Pipeline Parallelism                      | 83  |

|     | 5.1   | Introduction                                         | 83  |

|     | 5.2   | Baseline architecture                                | 86  |

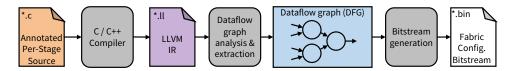

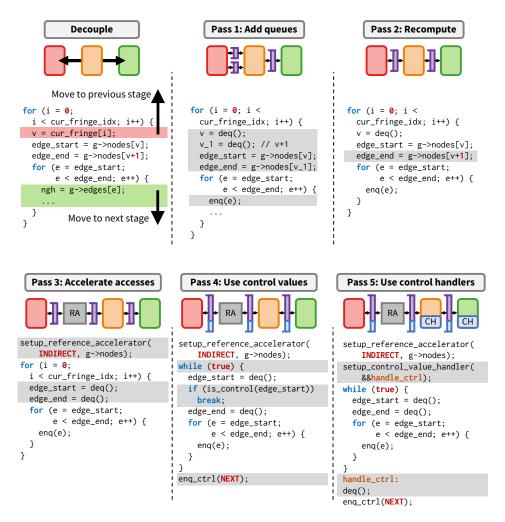

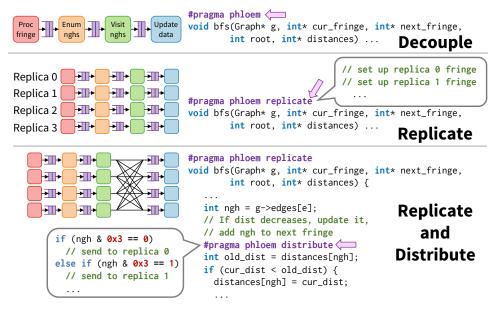

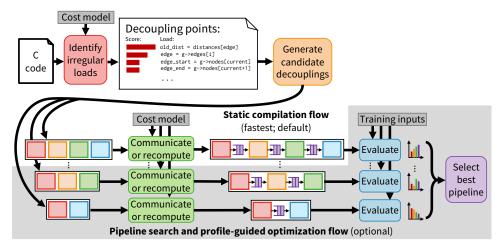

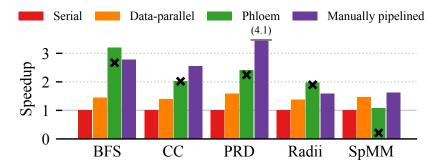

|     | 5.3   | Phloem Design                                        | 86  |

|     | 5.4   | Automatic Decoupling                                 | 94  |

|     | 5.5   | Methodology                                          | 96  |

|     | 5.6   | Evaluation                                           | 98  |

|     | 5.7   | Additional Related Work                              | 102 |

|     | 5.8   | Summary                                              | 104 |

| 6   | Con   | clusion and Future Work                              | 105 |

|     | 6.1   | Future Work                                          | 106 |

| Bil | oliog | raphy                                                | 109 |

| Со  | loph  | on                                                   | 127 |

# 1 Introduction

Advances in computer architecture have enabled significant improvements in the applications that run on them. In turn, these applications produce significant benefits for society in countless ways; as a result, computing is now embedded in all aspects of modern life.

Progress in architecture, silicon fabrication, and other fields have been important drivers of increased performance; in this thesis, we focus on parallelism. *Parallelizing* a program consists of dividing it into smaller units of work, or *tasks*, that can be run at the same time while preserving the semantics of the original program. By exploiting parallelism and performing these tasks simultaneously, we can improve performance by completing the workload faster and reaping its attendant benefits, such as consuming less energy.

As processors have become faster, the amount of data has ballooned and the ways we process it have become much more sophisticated. The result is that *sparse* applications have become much more common. A *sparse* application operates on sparse data structures, like sparse matrices, tensors, graphs, trees, hash tables, and more. These structures exploit the observation that the relationships represented by this data are themselves sparse. For example, a graph's millions of vertices may each have just a few edges to other vertices. Thus, efficiency benefits arise from not having to represent nonexistent relationships.

Leveraging sparsity this way introduces *irregularity*. In this thesis, we define an *irregular application* as one that has frequent, unpredictable (i.e., not statically known or easily computed ahead) data-dependent memory accesses and control flow. However, improvements in computer architecture over the last several decades have primarily benefited only *regular* applications—those that work on *dense, uncompressed* data structures, like dense vectors of matrices. Furthermore, with Moore's Law ending [34], we must be judicious in the way we use transistor budgets

to extract performance from irregular applications.

In this thesis, we consider organizing an application as a *pipeline*. Structuring an application as a pipeline involves further breaking down an algorithm into multiple smaller tasks, called *stages*, which are ordered to preserve the order of operations performed by the original algorithm. Each stage now receives operands from one or more preceding *producer* stages, carries out a subset of the original operations, and sends the results to one or more following *consumer* stages.

This division into multiple stages yields more tasks and exposes additional parallelism. Specifically, *pipeline parallelism* is the property of a pipeline that each stage can carry out its operations using only values received by the stage as well as that stage's internal state. Thus, stages can run independently of each other. There are plenty of examples of exploiting pipeline parallelism: processor pipelines [95] split the execution of each instruction across multiple stages. Image and video processing applications are also structured as pipelines, where each stage operates on an intermediate image or video frame, and application-specific integrated circuit (ASIC) accelerators [115] mirror this organization by structuring their compute as pipelines as well. Finally, pipelines are a common organization in software [103] as well, where an application can be structured as stages that communicate values through memory.

For this thesis, we focus on pipelines in which the stages are implemented as programmable (or configurable) hardware units that can perform these tasks. Stages in these pipelines are connected by queues: storage structures that contain outputs written (enqueued) by a producer stage that are read (dequeued) by a consumer stage. These stages are now decoupled from each other. If an output queue becomes full or an input queue becomes empty, the stage stalls, but other stages can continue to run. Decoupling grants a crucial property: latency tolerance—the ability to overlap long-latency events with useful work.

Finally, pipelines may operate at different *granularities*. The number of operations in each stage, the amount of data communicated between stages, and the frequency of communication, determine the granularity of the stages and the resulting pipeline. Granularity is relative; in this thesis, we set the finest unit of granularity to the fundamental operations (add, multiply, load, store) on a modern machine's word width (32 or 64 bits) that can be carried out in a single clock cycle. This granularity is comparable to an instruction executed by a RISC pipeline or a micro-op executed on a modern out-of-order processor. Thus, a *fine-grain* stage

carries out few operations on few values and communicates extremely frequently—once every few cycles.

We can leverage pipeline parallelism to accelerate irregular applications, but a careful choice of granularity is essential. Fine-grain pipelines confer numerous advantages: first, the ability to divide applications along sources of irregularity yields ample opportunities to insert latency tolerance mechanisms where needed. Second, dividing an application into fine-grain stages results in stages that contain substantially less work, making them simpler to implement and accelerate. Finally, even with queues of many tens or hundreds of elements, the overall storage area needed remains reasonably sized (comparable to today's L1 data caches on modern CPUs) for physical implementation.

## 1.1 Challenges

Adding hardware queues between compute units is not new: starting with James Smith's seminal 1982 paper on decoupled access-execute (DAE) [108], many systems [25, 30, 41, 45, 82, 83, 92, 102, 109, 119, 124, 138] also propose connecting compute units with hardware queues. Unfortunately, prior work fails to effectively support irregular applications structured as fine-grain pipelines. This lack of support is due to several challenges:

Applications need the flexibility to be decoupled at any point into arbitrarily many fine-grain stages. Irregular applications contain many sources of irregularity, and they may occur chained together, such as a series of memory accesses. To achieve good performance, sources of irregularity that happen frequently must be decoupled from each other. While fine-grain decoupling enables us to separate sources of irregularity, the underlying hardware must also be able to support these numerous stages. Many earlier designs, including DAE, only support two stages. Moreover, many prior designs limit the types of operations a stage can perform. For example, DAE requires memory accesses to be performed specifically by the access stage.

Stages must coordinate changes in control flow. Activity in one stage could affect control flow decisions made by another stage. For instance, stages may need to synchronize before moving onto the next phase of a program. For performance reasons, nested loops may need to be further decoupled into stages, but these stages need to match the semantics of

the original loop. The need to communicate control flow information between stages introduces additional complexity.

Fine-grain pipelines suffer from load imbalance, as the amount of work in each stage varies rapidly as the program runs. Related to the previous challenge, stages may experience rapid fluctuations in the amount of work in their input queues. One input element could produce many output elements for downstream stages, but the next one could produce few elements. Thus, it is not possible to statically scale or replicate stages to maintain balanced throughputs. Fine-grain pipelines thus have *load imbalance*, meaning that some stages may remain busy with lots of work and other stages may not have work to do at all. Prior work has suffered from poor utilization due to load imbalance, chiefly because they map stages to different compute units.

No tool automatically creates fine-grain pipelines of irregular applications from serial code, limiting the benefits of hardware support. Prior work in compilers of pipeline-parallel programs limit their tasks to be no larger than the innermost loop of an application [19, 43, 102]. However, irregular applications contain many nested control structures with possibly several long-latency events in each level. In order to make full use of hardware support for fine-grain pipeline parallelism, the compiler must recognize opportunities for creating pipelines that span control structures (like multiple loop nests) and properly decouple all long-latency events from each other.

### 1.2 Contributions

This thesis demonstrates that exploiting fine-grain pipeline parallelism in irregular applications is effective and practical. These are the key enabling insights:

- 1. Irregular applications can be structured as fine-grain pipelines.

- 2. Time-division multiplexing is cheap to implement and can be used to efficiently execute these pipelines while maximizing utilization.

- 3. These pipelines can be built systematically, and therefore automatically, from serial code, making this type of parallelism more accessible to programmers.

This thesis presents two novel hardware architectures and a compiler that leverage these three insights.

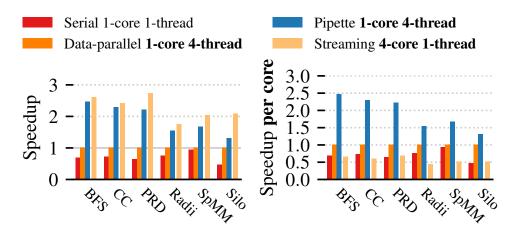

**Pipette:** The first hardware architecture, *Pipette* [82], exploits fine-grain pipeline parallelism using the threads of a multithreaded general-purpose core. Each thread executes a stage in the pipeline, and stages communicate using architecturally visible queues. An interface for passing control flow information between stages, as well as hardware support to make changing control flow efficient, make it practical to implement irregular applications as fine-grain pipelines. To cope with load imbalance, cores reuse the time-division multiplexing feature of modern out-of-order (OOO) cores—simultaneous multithreading—to always have work to issue, even if some stages are blocked. Pipette reduces implementation complexity by reusing other components of existing OOO cores, such as backing queue storage by reusing the physical register file. Pipette achieves gmean 1.9× speedup over a variety of challenging irregular applications.

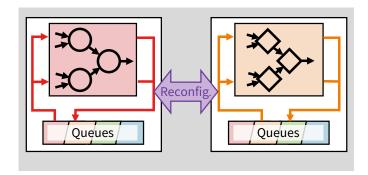

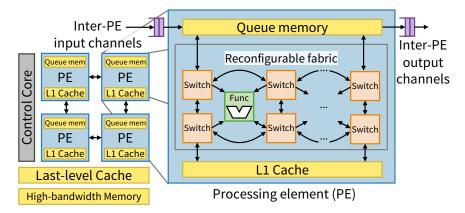

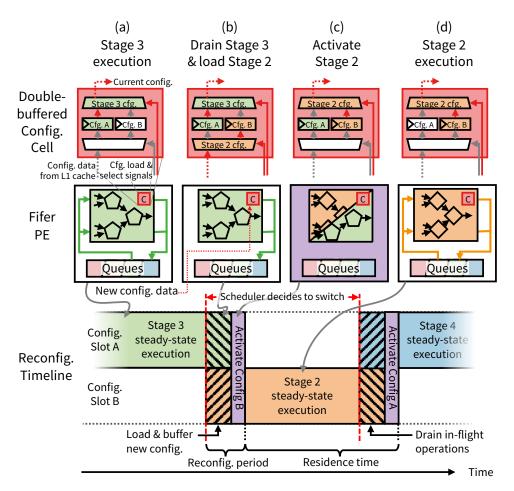

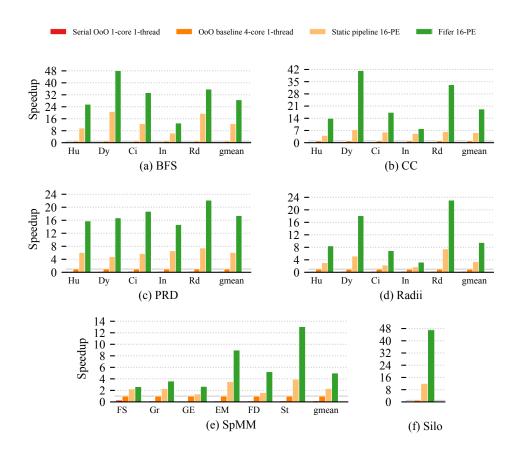

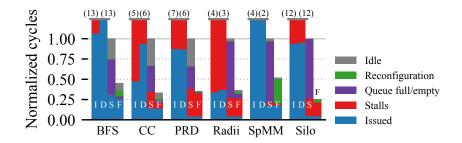

**Fifer:** The second hardware architecture, *Fifer* [83], extends Pipette's insights to specialized architectures. Fifer targets coarse-grain reconfigurable arrays (CGRAs), which have been traditionally used for accelerating regular computations but have been ineffective for accelerating irregular applications because of their rigid internal pipelining. Fifer demonstrates that CGRAs can be efficiently leveraged for irregular applications. Like Pipette, Fifer runs networks of pipeline stages and time-multiplexes many stages onto a single CGRA to achieve high utilization. To cope with irregularity, Fifer not only buffers the inputs and outputs to each CGRA, but also changes the currently executing stage in response to varying load. Support for rapid reconfiguration keeps the overhead of time-multiplexing low, and support for passing control information makes it feasible to implement an irregular application's complex control structures within a CGRA. Thanks to the increased compute density of the specialized fabric and improved utilization, Fifer achieves up to 47× speedup over an OOO multicore while using much less area.

**Phloem:** Finally, the compiler, *Phloem* [84], automatically transforms serial programs into high-performance pipeline-parallel implementations. It systematizes the process of creating pipelines, including accelerating memory accesses and coordinating changes in control flow across stages. Phloem achieves 85% of the performance attained through manual parallelization. Thus, a wide variety of applications can now benefit from hardware support for fine-grain pipeline parallelism.

# 1.3 Thesis Organization

The rest of this thesis is organized as follows: Chapter 2 reviews background and related work. Chapter 3 presents Pipette, which leverages fine-grain pipeline parallelism within a multithreaded core. Chapter 4 presents Fifer, which extends Pipette's insights to specialized architectures. Chapter 5 presents Phloem, a compiler that transforms serial programs into efficient pipeline-parallel implementations. Chapter 6 concludes this thesis and discusses future work.

# 2 Background and Related Work

Irregular applications have frequent data-dependent memory accesses and control flow. They are the norm in many domains, like graph analytics and sparse linear/tensor algebra, because irregularity arises from sparse data structures, like graphs and sparse matrices. Their data-dependent accesses and control are often unpredictable, causing poor performance on CPUs and GPUs. To drive the discussion of the background and related work, consider the following code:

```

for (int i = 0; i < N; i++)

if (A[i] > 0)

work(B[A[i]]);

```

This simple snippet is representative of the challenges of irregular applications (we will see fuller examples later on). Assume that work() takes few operations per call (e.g., about 10), and that it does not modify arrays A[] or B[]. This code will run very poorly on a CPU: if A[i] frequently alternates between positive and negative, the if (A[i] > 0) branch is unpredictable, serializing iterations and inducing a very low instructions per cycle (IPC). Moreover, the indirect access B[A[i]] will cause frequent memory misses that are hard to prefetch, making execution memory latency-bound. Data parallelism is of limited help: on a GPU or vector processor, if (A[i] > 0) induces conditional/masked execution that limits lane utilization, and the frequent memory gather B[A[i]] causes expensive uncoalesced accesses.

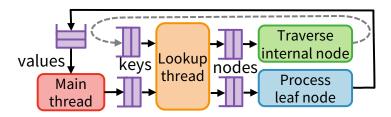

Instead, consider the following *pipeline-parallel* implementation of the above code snippet:

Each stage runs in parallel, e.g., in a separate CPU core. Stages produce streams of values and communicate them to other stages through queues.

This *decouples* their execution, allowing producers to run ahead of consumers. This decoupling also hides latencies and uses resources better. For example, each branch in the filter stage is resolved more quickly, since A[i] comes from a fast queue instead of main memory; and each misprediction in filter no longer fills the core with misspeculated instructions from work() or fetches from array B[].

The above pipeline is *fine-grained*: it has very frequent communication, with each stage enqueueing or dequeueing a value every 5–10 instructions. Thus, software-only queues (which take hundreds of cycles per operation [39, 104]) would add very high overheads. To enable fine-grained pipelining, much prior work has proposed adding hardware queues across cores or threads [25, 30, 41, 45, 82, 83, 92, 102, 108, 109, 119, 124, 138]. However, many of these systems only work well when every stage in the pipeline proceeds at a *regular*, predictable rate. By contrast, in an irregular application, stages undergo rapid variations in the amount of work, creating *load imbalance*. For instance, consecutive runs of positive or negative A[i] values affect the output rate of filter, quickly changing the ratio of work between the first and last two stages. If these stages were distributed spatially (e.g., scheduled on separate cores), some would idle often while others limit throughput.

## 2.1 A Fully Fledged Example: Breadth-First Search

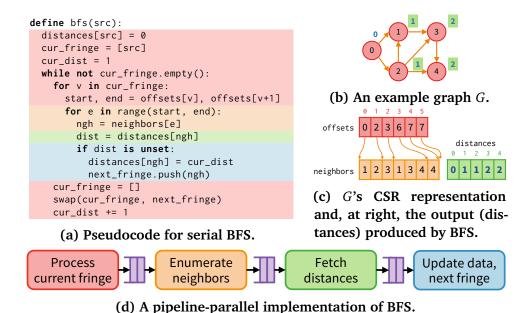

Although the previous example contains enough irregularity to cause serious problems, we turn to a more realistic example, breadth-first search (BFS), to fully illustrate the challenges of irregular applications. BFS is a common graph analytics algorithm that visits all vertices reachable from a source vertex src in a given input graph and tags them with the shortest distance to the source, in number of edges.

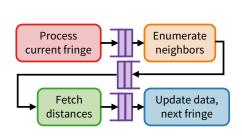

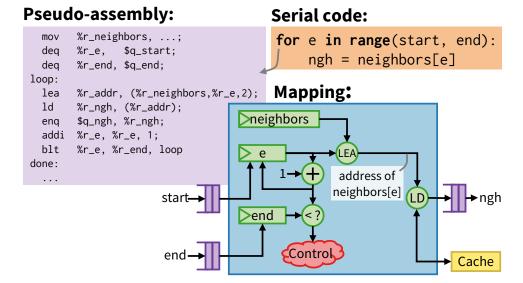

Figure 2-1(a) shows a serial implementation of BFS. This algorithm iteratively tags all vertices at a given distance from the source, cur\_dist, before moving on to the next distance. A *fringe* tracks the set of all vertices at the previous distance (cur\_dist-1). As BFS visits the neighbors of each vertex in the fringe, it checks whether the neighbor's distance has been set. If not, BFS sets its distance and adds it to the next iteration's fringe (next\_fringe). In the next iteration, BFS processes the vertices of the next fringe, continuing until an iteration results in an empty fringe—indicating that all vertices reachable from the source have been visited.

Figure 2-1: An implementation of breadth-first search (BFS).

The BFS implementation in Figure 2-1(a) uses a graph in compressed sparse row (CSR) format, the most commonly used representation [80, 106, 112]. Figure 2-1(b) shows an example graph and Figure 2-1(c) shows its CSR representation. CSR stores the graph using two arrays, offsets and neighbors. For each vertex id, the offsets array stores where its neighbors begin in the neighbors array. Thus, vertex v has edges to neighbors[i] for i in the half-open interval [offsets[v], offsets[v+1]). The neighbors array stores the vertex id of each neighbor.

Obtaining and setting the distance of a neighbor vertex thus manifests as four indirections in a three-level loop: reading the fringe for the current vertex, reading that vertex's edge list, finding the neighbor of each edge, and finally loading the distance of that neighbor.

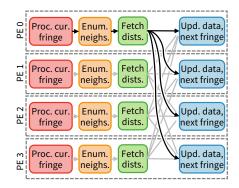

Like before, we mitigate the effects of these variable-latency indirections by separating BFS into a feed-forward network of pipeline stages. The stages are then *decoupled* with queues, which buffer work between stages and allow them to run ahead of each other. This decoupling is made possible by the observation that lookups of neighbor distances (at a given cur\_dist) do not depend on each other.

However, simply decoupling BFS and assigning each stage to a separate core or thread presents a new problem: load imbalance. Load

| Name                        | Flexible number of stages > 2 | Independent<br>control<br>flow | Dynamic<br>load<br>balancing | Reuses<br>core<br>structures |

|-----------------------------|-------------------------------|--------------------------------|------------------------------|------------------------------|

| DAE [108], DeSC [45]        | ×                             | ×                              | X                            | X                            |

| MT-DCAE [114]               | ×                             | ×                              | <b>/</b>                     | ×                            |

| Raw [119], MPPA [30]        | <b>~</b>                      | <b>✓</b>                       | ×                            | ×                            |

| Triggered instructions [92] | <b>~</b>                      | <b>✓</b>                       | <b>~</b>                     | ×                            |

| DSWP [102]                  | <b>~</b>                      | ×                              | ×                            | ×                            |

| Outrider [25]               | <b>✓</b>                      | X                              | <b>✓</b>                     | X                            |

Table 2-1: Feature comparison of related work.

imbalance occurs because work varies quickly throughout phases of execution. In BFS, load imbalance could occur because a vertex could have many neighbors, or no neighbors at all. This leads to poor utilization, in which some cores or threads remain idle while others run at full tilt.

### 2.2 Related Work

We break our discussion of related work into three major parts. First, we discuss techniques that employ decoupled execution. Second, we review prior specialized architectures and how they improve compute density over general-purpose cores but also why they fall short of our goals. Third, we explore why compiler support for these architectures is lacking, limiting the accessibility and effectiveness of hardware support.

### 2.2.1 Decoupled Architectures

In general, prior decoupled architectures suffer from two limitations: (i) their queue-based communication and control mechanisms target applications with regular control flow, and impose restrictions on the number of stages or the types of activities within each stage, so they are insufficient to decouple stages in irregular applications; and (ii) most of this prior work places each stage on a different core, which causes high load imbalance in irregular programs. Table 2-1 summarizes the shortcomings of this prior work.

**Decoupled Access-Execute (DAE)** architectures [108] feature two specialized units: an access core that performs memory operations and an execute core that performs compute operations. The cores are linked

to each other by queues, allowing the access core to run ahead. Software techniques for DAE [54] leverage the same insights, but without the need for specialized hardware. Unfortunately, DAE-based architectures and its descendants, including PIPE [41], ZS-1 [109], ACRI-1 [124], MT-DCAE [114], and DeSC [45], suffer from loss of decoupling because they allow only two stages, access and execute, and each stage has a limited set of operations, which causes tight two-way dependences between these stages. For example, DAE cannot decouple BFS as described.

Streaming multicores like Raw [119], Imagine [58], Merrimac [27], and Kalray's MPPA [30] introduce hardware support for decoupled communication between cores, which can stream values over the network [27, 29, 65, 120]. Unlike DAE, streaming multicores allow more than two pipeline stages and let each core execute arbitrary instructions. However, this cross-core decoupling is inefficient for irregular workloads due to *load imbalance*: since the work per stage varies quickly, cores incur many idle cycles. In fact, these streaming multicores were only used for *regular* pipeline-parallel applications. These systems relied on precise knowledge of the execution time and communication requirements of all stages, gathered through static analysis or annotations, to statically map stages to cores [65, 67, 94].

**Decoupled multithreaded cores** introduce support for queue-based communication among cores. Decoupled software pipelining (DSWP) [102] proposes the synchronization array, a hardware structure to facilitate communication between cores or the threads of a multithreaded core. But DSWP focuses on pipelining a single loop across different threads, which is too limiting for irregular applications. For example, BFS uses three levels of nested loops, with stages across several loop levels (and because inner loops are short, decoupling only within the inner loop is insufficient).

In addition to DSWP, Outrider [25] introduces hardware queues to decouple the threads of a single multithreaded core. In principle, this makes load-balancing across stages easy. However, Outrider was designed for applications with regular control flow, and *lacks the control-flow mechanisms needed to accelerate irregular applications*. Specifically, Outrider uses a global queue for control decisions and requires that all control instructions reside within the first thread to achieve any decoupling. For example, Outrider would not work for BFS, as three out of the four stages have control flow.

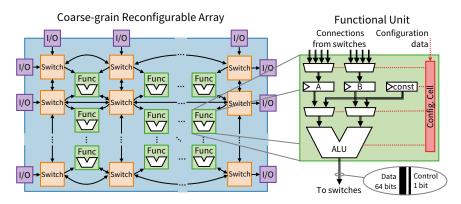

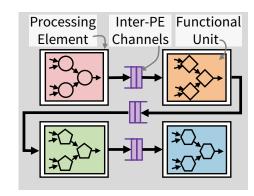

Figure 2-2: Coarse-grain reconfigurable array (CGRA, left) and functional unit design (right).

Helper Threads: Architectures with helper threads [74], including runahead execution [79], slipstream processing [113], and "flea-flicker" two-pass pipelining [12], perform redundant computation so that the main thread benefits from improved branch prediction and prefetched operands. Our goal is to instead create pipelines of threads whose work is never discarded.

### 2.2.2 Specialized Architectures

General-purpose cores, which continuously change the operations (instructions) on data kept in the same place (e.g., the register file), can be considered *temporal architectures*. On the other hand, a *spatial architecture* is structured as a spatially distributed grid of functional units that each perform a fixed, but configurable, operation. They perform computation by moving data from one functional unit to the next.

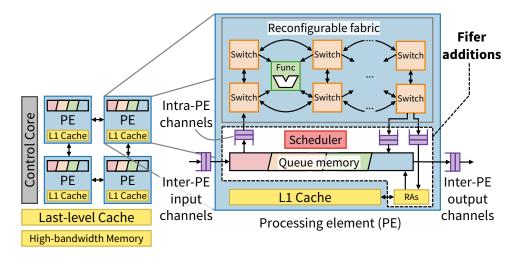

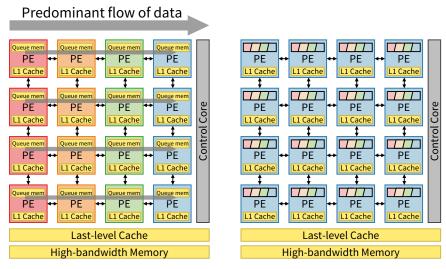

Coarse-grain reconfigurable arrays (CGRAs) are spatial architectures; they promise improved computational efficiency by arranging computation as a grid of functional units connected with configurable switches as shown in Figure 2-2. Functional units are composed to perform more complex computations, and data is moved among functional units through a network of simple switches. CGRAs achieve programmability without the need to continuously fetch and decode instructions.

Many CGRA-based architectures have been proposed, either as standalone accelerators [26, 40, 50, 77, 86, 125] or tightly integrated within the pipeline of a general-purpose processor [43, 72, 75, 107, 131]. Stream dataflow [86] provides an interface to express streaming semantics and

uses CGRAs to reduce instruction count. Plasticine [98], for instance, proposes a grid of specialized compute and memory units.

However, a purely spatial approach has disadvantages: the size of the program is limited by the number of functional units, and to achieve high performance, these units must be configured as a *pipeline*, to allow many functional units to be active simultaneously. Prior work relies on CGRAs' rigid internal pipelines for good performance, but their lack of latency tolerance mechanisms presents significant challenges when there is irregularity. Triggered Instructions [92] adds a temporal component to spatial architectures by allowing its functional units to dynamically select one of many operations to execute. Overheads are high, though, because each functional unit only supports a small number of instructions, e.g., sixteen. In Chapter 4, we show how to cheaply add latency tolerance mechanisms to make good use of highly efficient CGRAs on irregular applications.

Graphics processing units (GPUs) are massively data-parallel architectures that improve performance by simultaneously processing data over hundreds or thousands of vector lanes, and prior work has attempted to fit irregular applications to these architectures. UGC [14], G2 [15], IrGL [90], Gunrock [132], and Medusa [145] are frameworks for graph processing on GPUs, but must contend with awkward marshaling of data across GPU lanes. In BFS on a GPU, a neighbor could be added multiple times to the next fringe, but the optimal strategy is to add it just once; Gunrock, for instance, must filter out these duplicates. Some GPUs now include specialized units featuring spatial execution, like NVIDIA's Tensor Cores [23], which, though less programmable, resemble CGRAs. Inter-thread communication has also been extended to GPUs [131], but this communication is in service of the GPU's many data-parallel threads, rather than for making a pipeline.

Application-specific accelerators often employ spatial architectures to improve throughput and reuse, especially when faced with irregular applications' unpredictable compute latencies and memory access patterns. To cope with this, prior techniques specialize their hardware to the problem. For example, SCNN [93] targets compressed sparse convolutional neural networks by directly embedding knowledge of the data structure format into the accelerator. Graphicionado [47] proposes pipelines for graph processing, and Q100 [137] proposes a spatial accelerator for databases. Accelerators for sparse linear algebra, like GAMMA [140],

MatRaptor [110], ExTensor [48], SpArch [143], and OuterSPACE [91], are also organized as spatial architectures. These designs trade a high degree of specialization for high performance in a narrow problem domain. As a result, prior efforts to accelerate these irregular applications often culminate in accelerators that are heavily tuned to the specifics of an application—benefiting only those whose needs are exactly met by the technique.

Indirect prefetchers hide the latency of accesses common in irregular workloads. IMP [139] prefetches accesses of the form A[B[i]], which is insufficient work for BFS, as it has several indirections. Ainsworth and Jones propose a prefetcher tailored to BFS [5] and a more general event-driven prefetcher [6] that can handle multiple levels of indirection. Prodigy [116] uses hardware-software codesign to program a prefetcher to keep its prefetches in pace with the core's execution. However, these prefetchers are complex, taking significant energy to infer dependent accesses from memory traffic; they cannot handle all accesses accurately (like fetching the right set of offsets and neighbors in BFS, which requires iteration [6]); they can handle a limited set of access patterns; and they duplicate much of the work done in the cores, hurting efficiency.

**Data structure fetchers** are similar to prefetchers, but feed fetched data to cores to avoid duplicating work. HATS [78] performs graph traversals; Widx [62] accelerates hash indexing; and SQRL [66] handles vector, hash table, and tree traversals. SpZip [138] combines range-based scanning, indirection, and compression operators to efficiently traverse data structures before they reach the core. Fetchers avoid the inefficiencies of prefetchers, but are limited to specific data structures and to operations where data structure traversal and computation are not interleaved. Data structures are often tailored for a specific computation; the sparse linear algebra accelerators mentioned above all have hardwired assumptions about the input data structure, e.g., CSR.

### 2.2.3 Compiler support for pipeline parallelism

Prior work has proposed compiler techniques to exploit pipeline parallelism, but they fail to support irregular applications. Much of this prior work, including StreamIt [42, 121, 122], Piper [68], SGMS [65], and Team Scheduling [94], targets *regular programs*, where the throughput and input/output of each stage are known ahead of time. This information is used to produce fixed thread schedules that maintain load balance and

achieve decoupling with limited buffers. This approach does not extend to irregular applications, as stages incur an unknown and highly variable throughput.

Compilers for specialized architectures [37, 71, 88, 134] help applications take advantage of hardware specialized for specific application domains. These also target neural networks [118], data analytics [38, 130], and signal processing [96, 135].

Pattern-specific compilers and frameworks focus on a specific irregular pattern or data structure. HELIX [19] and HELIX-RC [18] seek to decouple communication from execution. HELIX-RC is a co-designed compiler and architectural support for inter-core communication, but is still limited to parallelizing a single loop. Irregular applications also need the flexibility to parallelize across loop levels (which in turn helps expand the search space for finding the best mapping of irregular applications to stages).

# 3 Pipette: Improving Core Utilization with Intra-Core Pipeline Parallelism

### 3.1 Introduction

Irregular workloads, such as graph analytics and sparse linear algebra, use high-performance cores poorly: these workloads suffer from frequent long-latency memory accesses and hard-to-predict branches that limit instruction-level parallelism and render out-of-order execution mechanisms ineffective. In this chapter we focus on non-invasive modifications to existing out-of-order cores to make these challenging workloads run efficiently.

Leveraging multithreaded cores is a common way to improve core utilization. But structuring irregular applications into multiple *data-parallel* threads suffers from three key problems: (i) latencies are larger than what can be effectively hidden by a moderately large number of threads per core (e.g., four); (ii) operating on disjoint parts of the input increases pressure on the memory hierarchy, limiting performance [44]; and (iii) data-parallel implementations suffer from overheads because they need to synchronize through shared memory.

We explore a different and more effective approach to improve utilization in simultaneous multithreading (SMT) cores: exploiting *pipeline parallelism*. As described in previous chapters, a pipeline-parallel program is structured as a series of feed-forward pipeline stages, with each stage executing on a separate thread. Decoupling stages with queues hides latency by allowing producer stages to run far ahead of consumer stages.

Abundant prior work has proposed *decoupled architectures* to exploit pipeline parallelism:decoupled access-execute (DAE) architectures [41,

45, 108, 109, 114, 124], streaming multicores [25, 30, 119], and spatial architectures [87, 92, 100, 137] use queues as latency-insensitive interfaces between cores, threads, or specialized processing elements (Section 2.2). Unfortunately, these architectures are ineffective for our use case because they (i) suffer from load imbalance, as they decouple stages across separate cores or processing elements, (ii) lack control-flow mechanisms, preventing decoupling of irregular applications, and/or (iii) fail to target threads within SMT cores, so their implementations miss opportunities to reuse already-existing resources to implement decoupling cheaply.

To address these limitations, we present *Pipette*. Pipette introduces architectural support for pipeline parallelism within the threads of a multithreaded core. Pipette's novel ISA (Section 3.2) allows threads to define inter-thread queues. By exploiting pipeline parallelism within a multithreaded core, Pipette hides latencies more effectively than the same number of data-parallel threads. Pipeline parallelism's naturally smaller memory footprint alleviates cache pressure and reduces the need to synchronize through shared memory.

By using SMT to time-multiplex stages in the same core, Pipette avoids load imbalance issues that arise when decoupling stages across separate cores or processing elements. Nevertheless, Pipette allows queues to span multiple cores, avoiding limitations on the number of stages (and thus opportunities for decoupling). Pipette also adds out-of-band control flow to keep producer and consumer loops running despite complex control flow. With these features, Pipette effectively decouples irregular applications, unlike prior work.

In addition to using SMT for load balancing, Pipette's microarchitecture (Section 3.3) features two more novel aspects. First, the implementation reuses core structures: it uses the physical register file to implement queues cheaply, avoiding the storage costs of prior techniques. Second, the implementation exposes a decoupled interface that cleanly accommodates *reference accelerators*, simple hardware units that further accelerate common memory accesses like indirections. Whereas prior work proposed coarse-grain specialized units to access complex data structures [62, 66, 78], Pipette enables composable, fine-grain interleaving of accelerated accesses and general-purpose computation.

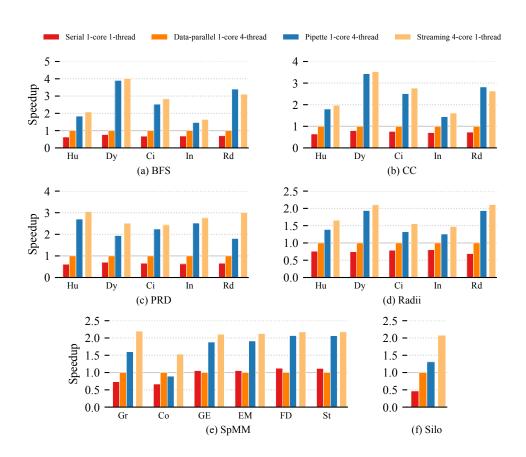

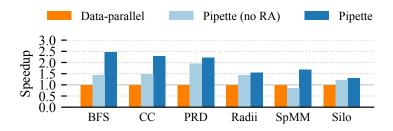

We evaluate Pipette on applications from graph analytics, sparse linear algebra, and databases (Section 3.5). It substantially outperforms prior work, by gmean  $1.9 \times$  and up to  $3.9 \times$  over SMT with data-parallel threads. Moreover, Pipette is more efficient because it achieves high core utilization.

In summary, we make the following contributions:

- We identify the architectural support needed to efficiently express many irregular applications as a pipeline of decoupled stages.

- We present a novel ISA and control flow primitives that enable effective decoupling in these applications.

- We present a novel implementation of this ISA that reuses existing core machinery to achieve decoupling and load-balanced execution cheaply, and adds simple, composable specialized units to accelerate common memory accesses.

- We demonstrate the effectiveness of this approach on a wide range of applications.

### 3.2 Pipette ISA

**Design goals:** Pipette's design is driven by three main goals:

- 1. Providing inter-thread queues at extremely low overheads, so that threads can communicate very frequently, potentially on almost every instruction. This enables a fine-grain slicing of the program into stages, which is crucial, as we saw in Chapter 2. For example, some stages of BFS have as little as one dereference per enqueue and dequeue.

- 2. Providing control flow primitives that avoid instruction overheads when a serial thread is split into multiple stages. For example, in BFS, stages must synchronize on distance changes. If each stage had to check on every dequeue whether a distance increase was needed, control overheads would negate the benefits of splitting work into stages.

- 3. Achieving an efficient implementation that reuses existing core structures and accelerates common access patterns.

Pipette's ISA is designed to achieve all these goals. We first discuss how the Pipette ISA achieves extremely low-overhead queues (Section 3.2.1), enabling the first design goal. We then present Pipette ISA's control primitives for efficient inter-stage coordination (Section 3.2.2), enabling the second goal. Section 3.3 presents Pipette's microarchitecture, which efficiently implements the Pipette ISA to achieve all design goals. Table 3-1 details the Pipette instruction set.

| Mnemonic              | Function                                                              |

|-----------------------|-----------------------------------------------------------------------|

| map_enq \$q, %rq      | Map writes to architectural register %rq as enqueues to queue \$q.    |

| map_deq \$q, %rq      | Map reads from architectural register %rq as dequeues from queue \$q. |

| unmap %rq             | Revert %rq to a non-queue register.                                   |

| peek %rd, %rq         | Peek top element from queue %rq, writing %rd without dequeueing %rq.  |

| enq_ctrl %rq, %rs     | Enqueue a control value (§ 3.2.2).                                    |

| skip_to_ctrl %rd, %rq | Skip to the next occurrence of a control value (§ 3.2.2).             |

Table 3-1: Pipette instruction set additions. \$q is a queue id; %rd, %rs, %rq are general-purpose registers used as a destination, source, or queue.

### 3.2.1 Enqueue and dequeue operations

Pipette provides a fixed number of FIFO queues per core (e.g., 16 in our implementation). To minimize overheads, Pipette does *not* have explicit enqueue or dequeue instructions. Instead, each thread can map the input or output of a queue to a general-purpose register. Each write to a queue input register implicitly enqueues the written value, and each read of a queue output register implicitly dequeues it. As we will see in Section 3.3, this register-mapped communication is cheap to implement through register renaming.

It is sometimes useful to read the value at the head of the queue without dequeueing it. To accomplish this, Pipette provides a peek instruction, as shown in Table 3-1.

Pipette queues have a maximum size (e.g., 32 values). To avoid full/empty checks, queues have blocking semantics: dequeue or peek operations to an empty queue block until a value is enqueued, and enqueues to a full queue block until free space is available. We later describe how producers and consumers can use *control values* to coordinate without adding instruction overheads in the common case.

Figure 3-1 shows why register-mapped, implicit enqueues and dequeues are crucial for performance in the enumerate neighbors stage of BFS (presented in Figure 2-1(a)). Figure 3-1(b) shows assembly code corresponding to the excerpt of C code in Figure 3-1(a). If a pipeline-parallel implementation used an enq instruction to enqueue values to queues, as done in Figure 3-1(c), it would expand the inner loop by one instruction,

```

int start = offsets[v];

int end = offsets[v+1];

for (int e = start;

e < end;

e++) {

int ngh = neighbors[e];

// fetch distances[ngh]

// if unset:

// update distance

// add to next fringe

}</pre>

```

(a) C code enumerating neighbors of a vertex.

```

loop:

lw    t1, 0(a2)

enq    q1, t1; overhead

addi    a2, a2, 4

blt    a2, a3, loop

```

(c) Pipeline-parallel assembly code using an enq instruction, which does not exist in Pipette, to manipulate a queue.

(b) Serial assembly code.

```

; writes to t1

; enqueue q1

map_enq q1, t1

...

loop:

; q1 enq ngh

lw t1, 0(a2)

addi a2, a2, 4

blt a2, a3, loop

```

(d) Pipette code tightens the inner loop by making writes to t1 enqueue q1.

Figure 3-1: Example showing the importance of tight inner loops: adapting the code from Figure 3-1(b) to Figure 3-1(c) using explicit enqueue instructions adds an instruction to a tight inner loop. Pipette addresses this in Figure 3-1(d) with its implicit queue semantics.

a 33% increase for this short loop. This instruction would add pressure to the core frontend (to fetch and decode it) and backend (to execute and commit a micro-op that merely copies a value). Instead, Pipette uses implicit communication, implemented through register renaming, to avoid all these overheads: the Pipette code in Figure 3-1(d) maps register t1 so that the load instruction directly enqueues q1.

### 3.2.2 Efficient control flow

Producers often need to communicate control flow changes or exceptional conditions to consumers. Doing this through normal enqueues and dequeues would be inefficient. Instead, Pipette provides *control values* (CVs). Control values are similar to other values passed through queues except that they convey changes to control flow instead of application data. To

Figure 3-2: Sparse matrix-matrix multiplication (SpMM), with one stage receiving two inputs.

differentiate them from application data, each CV is enqueued with the enq\_ctrl instruction, which sets the *control bit* for its queue entry.

CVs let programs avoid checks for infrequent conditions by using semantics similar to those of exceptions. Before starting execution, each thread registers a *dequeue control handler*, similar to an exception handler. A thread dequeueing from or peeking at a queue with a control value at its head instead jumps to the dequeue control handler (this jump happens entirely in user level and does not involve the operating system). The dequeue control handler receives the control value and the id of the queue that triggered it. The handler processes the control value, then jumps back to mainline Pipette code to continue computation.

Going back to the BFS example from Figure 3-1(d), it's easy to see why control values make execution efficient: the inner loop in Figure 3-1(d) does not check for termination or level switches in the inner loop. Instead, stages handle these conditions through control values and dequeue control handlers, leaving the inner loops to deal with data values only.

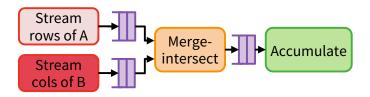

For a more sophisticated use of control values, consider the inner-product sparse matrix-matrix multiply (SpMM) kernel, shown in Figure 3-2. SpMM computes the dot product of a row of A and a column of B at a time. Both matrices are sparse, so the leftmost stages (stream rows/cols) stream the non-zero *coordinates* of a row and a column at a time. Then, the merge-intersect stage finds the matching non-zeros, which the accumulate stage fetches and accumulates.

Control values make SpMM efficient by letting the stream rows/cols stages *delineate each row and column*. For example, the stream rows stage enqueues all non-zeros for a row of A, followed by a control value denoting the index of the next row, and then the non-zeros of the next row. The merge-intersect code need not check for row or column termination, and the stream rows stage can fetch multiple rows ahead, which is useful as rows often have few non-zeros.

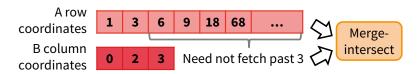

Figure 3-3: In SpMM, an inner product in which the input row and column differ greatly in length.

**Consumer-producer coordination:** So far, we have seen how producers can delimit data values with control values to communicate with consumers. The dual case is also desirable: consumers may need to communicate with producers. For example, a consumer may discover that the work a producer is enqueueing is no longer useful, and should alter the producer's control flow to reduce unnecessary work.

To achieve this, the skip\_to\_ctrl instruction finds and dequeues the next control value in a queue, discarding all earlier data values. If the queue does not have a control value, skip\_to\_ctrl blocks waiting for one, and the next time the producer attempts an enqueue, it jumps to an enqueue control handler instead. This lets the producer redirect control flow and enqueue a control value that unblocks the consumer.

SpMM shows why skip\_to\_ctrl and enqueue control handlers are useful. Figure 3-3 shows an inner product where *A*'s row is much longer than *B*'s column, and the last coordinate in *B*'s column is seen very early in *A*'s row, so no more matched coordinates are possible. It would be wasteful for stream rows to stream the full row of *A*, but only merge-intersect can detect this condition. To address this, when merge-intersect sees the end of *B*'s column (its dequeue control handler fires), it performs skip\_to\_ctrl on the rows queue to skip to the next row. If stream rows is still working on the same row, the queue has no control value, so on the next enqueue, the enqueue control handler of stream rows fires and moves to the next row. If stream rows is already on a later row, then skip\_to\_ctrl lets merge-intersect discard the current row without undue interruptions to stream rows.

In summary, control values and enqueue/dequeue control handlers enable producers and consumers to coordinate out-of-band, in a way similar to *user-level* exceptions. This avoids frequent checks on inner loops that would add significant overheads to the pipelined version. Beyond the two instructions required to enqueue and dequeue control values, this mechanism requires two control registers per thread to store the PCs of enqueue and dequeue control handlers.

### 3.2.3 Integrating Pipette into the system

**Code transformations to use Pipette:** We use a simple, systematic procedure to split applications into Pipette stages: we split programs along every long-latency indirect load, starting at the innermost loop and moving outwards. BFS in Chapter 2 demonstrated this procedure.

In this chapter, we transform applications manually (in Chapter 5 we show how to perform this transformation automatically). We transform source code rather than assembly, by using a simple C/C++ API that encapsulates Pipette functionality (e.g., abstracting the mapping and use of queue registers). Irregular applications have non-trivial considerations for pipelining, as their complex indirections may be impacted by aliasing and races.

For example, one such race condition arises in the last stage of BFS, update data. To decouple this stage from the previous one, the Pipette BFS implementation fetches distances in advance. However, this distance may be stale, as the neighbor may have been recently reached from another fringe vertex. It would be incorrect to use the distance as-is. Our manually transformed code uses this distance for an initial check, but if unset, it re-fetches the distance to ensure it was not set in the interim (this second access is cheap, as it hits in the L1).

Pipette is orthogonal to the memory consistency model, and programs behave like normal multithreaded programs.

Finally, if a Pipette application is incorrectly synchronized, it may deadlock. Deadlocks leave user-level threads blocked, but the OS can use interrupts to break those deadlocks (like e.g., a blocked monitor/mwait instruction).

Architectural state and context switches: Pipette queues are architectural state, and must be drained and saved across context switches. As is done for FPU state, operating systems (OSs) need not save and restore this state on every system call or interrupt, only when the process is descheduled. As these context switches occur infrequently, saving queue contents represents a negligible fraction of the time spent in OS code.

Draining and refilling queues can be done with normal Pipette instructions. In addition to the OS, debuggers could inspect queues by draining and refilling them.

**Privileged code and virtualization:** Since threads are an OS abstraction, and threads from multiple processes may share the same core, some of Pipette's operations must be privileged. Specifically, the map and

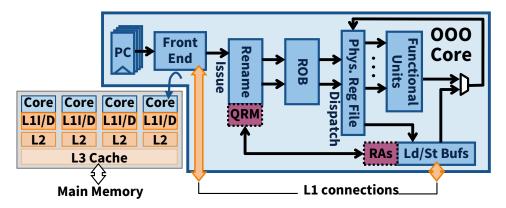

Figure 3-4: Pipette implementation overview and modified out-of-order pipeline. The key modifications, the queue register map (QRM) and reference accelerators (RAs), are shown in purple with dotted borders.

unmap operations and the registration of control handlers must happen though system calls. Similar to virtual memory, the OS can provide each process with a set of virtual queues, which it can then map to physical queue ids within each core. This allows descheduling and rescheduling individual threads in any order. Since each queue is shared between a producer and a consumer thread, the last of the two threads to be descheduled saves the queue's state. Threads can migrate across cores (using cross-core queues, Section 3.3.3). A producer/consumer thread can enqueue/dequeue to a queue while the other thread is descheduled; however, in practice it will quickly block on a full/empty queue. Thus, the OS should co-schedule the threads of a Pipette program, e.g., using gang scheduling [36].

OS-mediated queue mappings prevent accessing queues from other processes. Side channels are possible just like in normal SMT cores; to avoid them, Pipette threads should not be co-scheduled with other processes on the same core.

# 3.3 Pipette Microarchitecture

Figure 3-4 gives an overview of Pipette's implementation, focusing on its two distinguishing features. First, our Pipette implementation *uses* the physical register file to implement queues (Section 3.3.1). We observe that physical registers are underutilized in irregular applications, where deep out-of-order execution is not efficient. This enables a cheap imple-

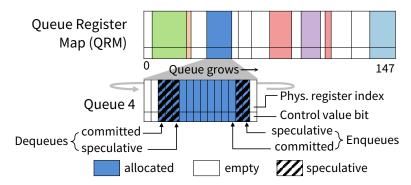

Figure 3-5: The Queue Register Map (QRM) tracks the physical registers of each Pipette queue. Each queue is managed as a circular buffer.

mentation that leverages existing OOO structures: physical registers and register renaming. Second, we introduce *reference accelerators* to speed up common access patterns (Section 3.3.2). We also introduce *connectors* to enable cross-core queues (Section 3.3.3), and evaluate Pipette's implementation costs (Section 3.3.4).

### 3.3.1 Register-based inter-thread queues

Pipette maintains queues within the *physical register file*, and adds minor changes to register renaming to implement FIFO queue semantics. Pipette prevents queues from starving threads of physical registers by sizing each queue and limiting the space all queues may collectively occupy. Since queues are embedded within speculatively managed structures, we first explain the basic Pipette bookkeeping structure, then how it interacts with speculative execution.

**Basic operation:** Figure 3-5 shows the Queue Register Map (QRM), the structure that tracks the state of all queues. The QRM has as many entries as the maximum capacity of all queues. Each queue takes a contiguous chunk of entries (shown in different colors in the figure), and manages it as a circular buffer. The chunk associated with each queue determines its capacity. This mapping is configurable by the OS, but cannot change while queues are active.

Figure 3-5 also shows how each queue is managed. Each queue has both *speculative* and *committed* pointers for *head* and *tail*. Enqueues happen to the tail of the queue, and dequeues happen from the head. We restrict each queue to be point-to-point, so there is a single enqueuer and dequeuer thread.

Each entry between the head and tail pointers tracks the physical register index that holds the enqueued value. Moreover, each entry has a *control value bit* that denotes whether the entry holds a control value (enqueued with enq\_ctrl).

The QRM is designed to require simple changes to register renaming. Enqueue operations are nearly identical to normal register writes. On issue, the rename stage acquires a free register index from the freelist, and uses it to store the enqueued value. As usual, the reorder buffer (ROB) stores the *previous* physical register index. The only difference is that, on commit, the ROB *does not free* the previous physical register index. Instead, the QRM manages it, as it is part of a queue.

Dequeue operations are also very similar to reads. For each dequeuemapped queue, the thread's register map simply holds the index for the *head* of the queue. A dequeue simply uses this value, and additionally modifies the register map to point to the next register in the queue, supplied by the QRM. On commit, the QRM returns the register to the freelist. Finally, peek operations are exactly like normal reads.

**Speculative value management:** Because registers are written and read speculatively, there are multiple value management options. We choose the simplest one: *enqueued values cannot be dequeued until they are non-speculative*.

This leads to a simple implementation: QRM's *speculative* head and tail pointers are the only eagerly managed values. Each enqueue advances the speculative tail pointer on issue, and the committed tail pointer on commit; similarly, each dequeue advances the speculative head pointer on issue, and the committed head pointer on commit. The queue is considered *empty* if the speculative head is about to catch up with the committed tail, and *full* if the speculative tail is about to catch up with the committed head. The issue stage stalls the thread on enqueues to full queues or dequeues from empty queues.

Recovery from misspeculation simply requires rolling back the speculative head and tail pointers, as well as releasing the registers from rolled-back enqueues to the freelist.

A key benefit of consuming only committed values is that *misspeculation in a producer thread does not propagate to the consumer thread*. This allows us to implement Pipette with simple changes to the issue and rename stages.

We also tried a more complex variant of Pipette that allowed dequeues to consume still-speculative enqueued values. This version barely improved performance (by about 1% on average), and occasionally caused minor performance degradations. Intuitively, this result makes sense because the point of Pipette is to keep threads decoupled, so while allowing dequeues to dip into the speculative region of the queue may get some out-of-order benefits, in well-decoupled programs producers should already run far ahead of consumers.

**Issue logic modifications:** Pipette requires minor changes to the issue logic. First, the per-thread issue logic stalls on a dequeue from an empty queue or an enqueue from a full queue. Second, every dequeue of a control value triggers a jump to the dequeue control handler. For simplicity, we reuse the exception logic to implement this redirection.

Our current Pipette implementation does not change the thread prioritization logic. We use the standard ICOUNT policy [128] to avoid issue queue clog. Further gains might be achieved by controlling thread priorities to increase decoupling, e.g., by prioritizing producers over consumers. However, we find Pipette works well with ICOUNT, and leave exploration of more advanced issue policies to future work.

### 3.3.2 Accelerating common access patterns

By exposing a queue-based interface, Pipette makes it easy to add specialized units to accelerate long-latency memory accesses. Pipette achieves this with *reference accelerators* (RAs), simple configurable units that perform indirect loads and communicate with threads through queues.

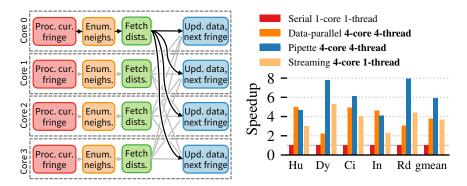

Benefits: BFS (in Figure 2-1(d)) showcases the two key benefits of RAs. First, some stages, like fetch distances in BFS, are very simple, performing indirect or strided accesses. Using a thread for such simple work is overkill: a simple RA can perform them much more efficiently. Second, to get decoupling, Pipette divides the code across each long-latency indirection. While this lets producers run ahead of consumers, *producers still suffer from long-latency loads*. For example, the process current fringe stage in BFS issues loads to the offsets array. These loads take a long time to commit and stress the ROB, limiting memory-level parallelism. RAs allow offloading these *producer* long-latency accesses. This results in producers with short, tight loops that do not stress OOO resources, improving performance. For example, in our RA-enhanced BFS, the process current fringe stage passes v to an RA, which fetches offsets[v] and offsets[v+1] autonomously and non-speculatively, producing start and end.

**Interface:** Each RA is a configurable unit with a single input and output queue. The RA takes in a stream of input elements, uses them to perform indirect accesses, and places the resulting data in its output queue. RA accesses are independent from those of general-purpose threads. With respect to consistency, programs simply see each RA as a separate thread.

RAs are configured once, by specifying which queues to use, a starting address A, an element size S, and the access *mode* with can be *indirect* or *scan*. The RA interprets A as an array with elements of size S. In *indirect* mode, the RA takes a stream of indices at its input, and for each index i, it fetches A[i]. In *scan* mode, the RA takes a stream of starting and ending indices at its input, and for each pair of input values {start, end}, it fetches elements A[start:end-1].

We find that these simple modes cover most indirection patterns and benefit all our applications. For instance, in BFS, the indirect mode covers the first and third stages, and the scan mode covers the second stage.

**Implementation:** RAs use existing core machinery. RAs opportunistically use spare rename and register bandwidth, and manipulate the QRM like ordinary threads on enqueues and dequeues. When performing memory accesses, RAs use the load/store unit and use virtual addresses. Each RA has a small completion buffer to track outstanding loads (Section 3.3.4 presents implementation costs). On a virtual memory exception, the core interrupts the producer thread associated with the RA.

# 3.3.3 Extending Pipette to cross-core queues

We have so far described how queues work within a core, but allowing queues to span threads in multiple cores is desirable for three reasons. First, although Pipette's main goal is to improve core utilization, achieving effective decoupling may require more stages than a core has threads. Second, as we will see later (Section 3.5.6), Pipette can scale and balance work across cores in new ways, by using inter-core queues to improve locality and avoid shared-memory synchronization costs. Third, as Section 3.2.3 discussed, it is desirable to let the OS schedule threads individually, in separate cores if needed.

We achieve this through *connectors*, simple hardware structures that stream a queue from a producer to a consumer core. Producer and consumer threads are both given intra-core queues. The connector is a simple FSM that sits on the producer's core. It has a similar but simpler implementation than RAs: rather than interacting with the load/store

| Component   | QRM entries<br>148 × 9 bits | QRM pointers<br>64 × 8 bits | Handler PCs<br>8 × 64 bits | -     | Int. PRF (for comparison) |

|-------------|-----------------------------|-----------------------------|----------------------------|-------|---------------------------|

| Size (bits) | 1,332                       | 512                         | 512                        | 2,356 | 13,568                    |

Table 3-2: Pipette storage requirements.

unit, it just sends values from the producer to the consumer core, using credit-based flow control to avoid saturating the on-chip network and strictly limits the receiver queue's state to its capacity. When descheduling a consumer thread, the OS must wait for its connectors to quiesce; this requires a simple teardown protocol on top of credit-based flow control.

### 3.3.4 Implementation costs

Pipette's storage and logic additions impose minimal overheads. Table 3-2 summarizes Pipette's storage requirements. In our configuration, Pipette can map up to 148 physical registers, and takes 1844 bits (231 bytes). This is only 14% of the physical register file, showing the benefits of leveraging physical registers to implement queue storage. Beyond the QRM, 512 bits (64 bytes) are required for the per-thread enqueue and dequeue control handler PCs. Overall, only 2356 bits (295 bytes) of additional storage are needed to implement Pipette, a small overhead for a modern core.

RAs, the other hardware addition, are small. We write complete RTL for RAs, including configuration registers, address generation, and a 32-entry completion buffer. We synthesize RAs using yosys [136] and the 45 nm FreePDK45 library [51]. Four RAs take 0.0014 mm<sup>2</sup> at 45 nm, adding an estimated 0.007% to core area, a tiny overhead.

# 3.4 Experimental Methodology

### 3.4.1 Simulated System

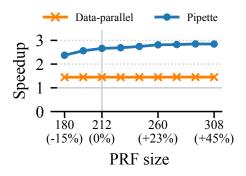

We implement Pipette on a detailed event-driven, cycle-level simulator based on Pin [73]. Table 3-3 lists the parameters of our simulated system, whose cores are modeled after Intel's Skylake [32], scaled to 4 SMT threads from the usual two. Core structures are sized as in Skylake; we grow the physical register file (PRF) from 180 to 212 entries to accommodate the 32 architectural registers of the two extra threads. Thus, the

| Cores                                        | 1 or 4 cores, 3.5 GHz, x86-64 ISA, Skylake-like: 6-wide out-of-order issue, 224-entry ROB, 97-entry issue window, 72-entry load buffer, 56-entry store buffer, 212 integer physical registers, 168 vector physical registers; 4-thread SMT with ICOUNT issue policy and dynamically shared ROB, issue window, PRF, and LSQs |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pipette                                      | QRM with 148 physical register entries, 16 queues max; 4 RAs; 4 connectors; queues are sized 24 elements deep by default                                                                                                                                                                                                    |

| L1 cache<br>L2 cache<br>L3 cache<br>Main mem | 32 KB/core, 8-way set-associative, 4 cycle latency 256 KB/core, 8-way set-associative, 12 cycle latency 2 MB/core, 16-way set-associative, 40 cycle latency 120-cycle minimum latency, 2 controllers, 25 GB/s each                                                                                                          |

Table 3-3: Configuration parameters of the evaluated system.

PRF entries left for renaming are the same as in Skylake. We extend cores to faithfully simulate Pipette additions, with the configuration shown in Table 3-3. We use McPAT [70] to model core and uncore energy at 22 nm, and Micron DDR3L datasheets [76] to model main memory energy.

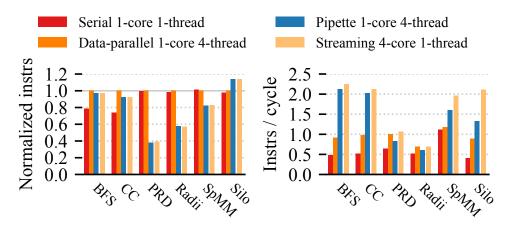

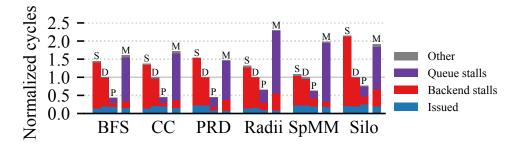

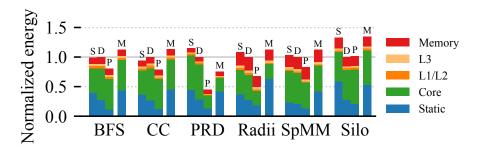

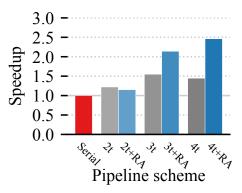

We evaluate 1- and 4-core systems. Since Pipette's main goal is to improve core utilization, we first compare Pipette and data-parallel programs on a single 4-thread SMT core. Then, we compare 1-core, 4-thread Pipette with a baseline decoupled architecture: a 4-core streaming multicore. Finally, we show that Pipette also scales across cores.

#### 3.4.2 Benchmarks

We evaluate Pipette on six applications from graph analytics, sparse linear algebra, and databases. For each application, we start from a state-of-the-art implementation that includes serial and data-parallel versions. We derive the Pipette version of each benchmark from the serial version. The wide variety of Pipette applications highlights its generality and the abundance of pipeline parallelism.

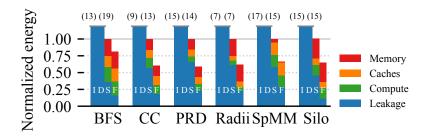

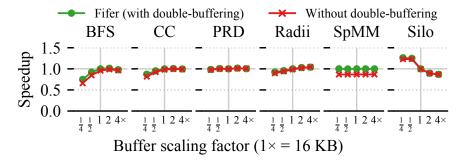

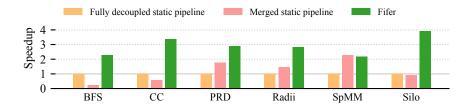

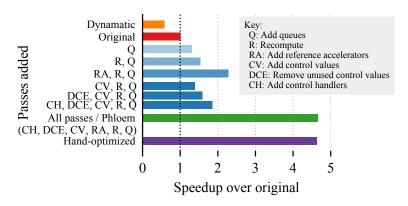

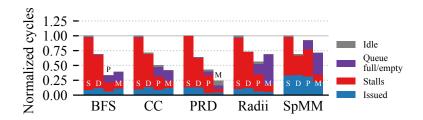

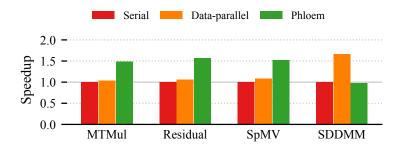

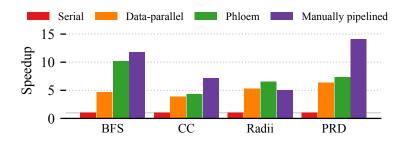

**Breadth-first search (BFS)**, first described in Chapter 2, determines the distance of graph vertices to a source vertex. We base our implementation on PBFS [69].