### MIT/LCS/TM-50

# AN ENCIPHERING MODULE FOR MULTICS

G. Gordon Benedict

July 1974

#### MAC TECHNICAL MEMORANDUM 50

AN ENCIPHERING MODULE FOR MULTICS

G. Gordon Benedict

July, 1974

This research was performed in the Computer Systems Research Division of Project MAC, an M.I.T. Interdepartmental Laboratory, and was sponsored in part by the Advanced Research Projects Agency (ARPA) of the Department of Defense under ARPA Order No. 2095 which was monitored by Office of Naval Research Contract No. N00014-70-A-0362-0006; in part by the Air Force Information Systems Technology Applications Office and by ARPA under ARPA Order No. 2641; and in part by Honeywell Information Systems, Inc.

This Technical Memorandum reproduces a June, 1974, M.I.T. Electrical Engineering Department S. B. Thesis of the same title.

page 2

#### ABSTRACT

Recently IBM Corporation has declassified an algorithm encryption usable for computer-to-computer for or computer-to-terminal communications. Their algorithm was implemented in a hardware device called Lucifer. A software implementation of Lucifer for Multics is described. A proof of the algorithm's reversibility for deciphering is provided. A special hand-coded (assembly language) version of Lucifer is described whose goal is to attain performance as close as possible to that of the hardware device. Performance measurements of this program are given. Questions addressed are: How complex is it to implement an algorithm in software designed primarily for digital hardware? Can such a program perform well enough for use in the I/O system of a large time-sharing system?

Author: G. Gordon Benedict Thesis Supervisor: Prof. Jerome H. Saltzer

page 3

### CONTENTS

| Title Page                                       | 1  |

|--------------------------------------------------|----|

| Abstract                                         | 2  |

| Contents                                         | 3  |

| Figures                                          | 4  |

| Tables                                           | 5  |

| Overview                                         | 6  |

| Section 1, Introduction to Enciphering           | 8  |

| Section 2, Enciphering Algorithms and Lucifer    | 12 |

| in Particular                                    |    |

| Section 3, A Proof of Lucifer's Reversibility    | 17 |

| Section 4, The Multics Software Implementation   | 19 |

| Section 5, Timing Measurements and Conclusions   | 22 |

| Appendix A, Operation of the Lucifer Hardware    | 24 |

| Appendix B, The PL/I Implementation              | 34 |

| Appendix C, The Assembly Language Implementation | 43 |

| Appendix D, Introduction to Multics Assembler    | 62 |

| Bibliography                                     | 68 |

FIGURES

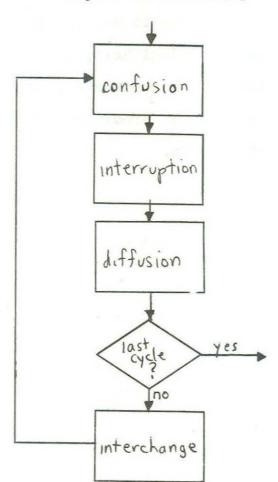

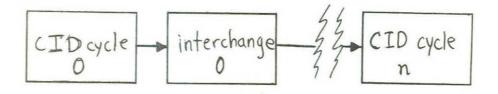

| Figure | 1, | Flowchart                          | 15 |

|--------|----|------------------------------------|----|

| Figure | 2, | Block Diagram                      | 15 |

| Figure | 3, | Bit Addresses in Registers         | 25 |

| Figure | 4, | Hardware Schematic                 | 26 |

| Figure | 5, | Exploded Key Bit Assignment        | 44 |

| Figure | 6, | Key Bit Assignment                 | 45 |

| Figure | 7, | Convolution Registers              | 47 |

| Figure | 8, | Postrotation Convolution Registers | 48 |

page 5

#### TABLES

| Table | l, | Key Byte Access Schedule             | 31 |

|-------|----|--------------------------------------|----|

| Table | 2, | Four-bit Permutations                | 33 |

| Table | 3, | Convolution Register Rotation Counts | 51 |

#### OVERVIEW

This thesis examines the enciphering algorithm recently released by IBM, Lucifer. This algorithm is described as a hardware mechanism in "The Design of Lucifer, a Cryptographic Device for Data Communications", by J. Lynn Smith; this was the primary source document.

A proof of Lucifer's reversibility is given, that it will in fact correctly decipher its previously-output ciphertext when provided with the same key used for enciphering. Two software implementations are described and their performance measured.

This paper is divided into five sections and four appendices. "Introduction to Enciphering" briefly explains the uses of enciphering in computer-to-computer and computer-to-terminal communication as a security enhancement. "Enciphering Algorithms and Lucifer in Particular" lists some criteria for a good computer-oriented cipher. The general operation of Lucifer is depicted without much detail. Sufficient detail is however given for understanding of "A Simple Proof of Lucifer's Reversibility". This section provides an informal proof that Lucifer works in that it correctly deciphers its own "The Multics Software Implementation" ciphertext. demonstrates how to use the enciphering programs. The final section, "Timing and Conclusions", presents performance

measurements of a PL/I and a Multics assembly language version of Lucifer. Appendix A, "Operation of the Lucifer Hardware", details the operation of the hardware device described by Smith. Appendix B, "The PL/I Implementation", details a software version in the PL/I language designed to simulate closely the Lucifer hardware in its operation and be readable and exportable. Appendix C, "The Assembly Language Implementation", details a version of Lucifer optimized for execution time. For those readers unfamiliar with the Multics hardware, "An Introduction to Multics Assembler" briefly explains those features of the Honeywell model 6180 processor used by Lucifer.

page 8

#### INTRODUCTION TO ENCIPHERING

Much attention has been paid recently to computer and data security. Computer security consists of regulating the use of computer facilities to only those people or those tasks authorized to use them. This has been attempted by such mechanisms as passwords, protection rings, and privileged instructions. Data security is becoming more important with the advent of government and corporate personal-data files. This problem is magnified if the computer system is available to many users via telecommunications. Given the above facilities for regulating computer facility use, access control is one mechanism that is available for preventing unauthorized access to data files. However, this mechanism fails when data is transmitted over telephone lines, radio links, or physical (mail or courier) shipments. Such communications are easily tapped without the legitimite user's knowledge. except for the case of a courier. Even more insidious than the traditional reading of sensitive data is the insertion of spurious data designed to confuse or misdirect the operation of a system. One mechanism for minimizing this problem is enciphering that data, which protects the data itself rather than the medium of transmitting the data.

Enciphering is a process whereby transformations are made on the message (cleartext), usually on a bit or

character level. If the algorithm is known the cipher may be breakable by analyzing the ciphertext, particularly if sample cleartext for some of the ciphertext is available. Since an enciphering algorithm must be reversible to be useful, a key known by both the message originator and the intended receiver is also used. Thus if the key is intercepted or deduced the cipher is now cracked. The essence of successful cryptology is in devising an enciphering algorithm which is not possible to crack in the time-span of the message's usefulness, and in keeping the key secret.

Enciphering helps in preventing insertion of spurious data to confuse a computer, as well as preventing reading of secret data. This is because a random message inserted onto the communication link will probably decipher to unrecognizable garbage. The algorithm implemented in this paper is so constructed that if one bit is changed in a legitimate enciphered message, the deciphered text will almost certainly be unrecognizable. This prevents the form of interference wherein a saboteur records (taps) the ciphertext, changes some bits randomly without even understanding the message, and inserts the text onto the telephone lines. Unrecognizable text can usually be rejected by the computer. There still remains the problem of the saboteur who records the ciphertext and replays it unchanged later. This can be extremely damaging to

unrepeatable or irreversible processes. A method of avoiding this problem is message chaining, whereby a part of the previous data exchange is enciphered in this data exchange, as a verification field. Thus the same message replayed tomorrow would contain an out-of-date verification field and be rejected. The operation of such a system is discussed at length in Smith's paper.

Enciphering can also be used for computer-to-terminal communications. The terminal would contain a hardware deciphering module; the algorithm described here was designed with this purpose in mind. The user could have his key on a magnetic card, or he could type it in on the terminal. The computer would contain a central file of all users' keys and a software or hardware version of the enciphering module.

Enciphering can add some security to online files against the possibility of random hardware or software failures or physical stealing of backup tapes, disk packs, etc. Enciphering in this application merely adds another dimension of security.

This paper details an enciphering algorithm developed by Feistel and Smith of IBM for computer-to-terminal communications. A software version has been prepared, intended to be used as part of the input/output software or the network interface of Multics. A command to encipher and decipher online segments has also been written. A proof of

the algorithm's reversibility is also given; this was hinted at but not proved in the Smith and Feistel papers.

and the second second

page 12

ENCIPHERING ALGORITHMS AND LUCIFER IN PARTICULAR

There are several desiderata in the design of an enciphering algorithm. One is needed which is easily implemented in hardware, yet would provide a great measure of security against cryptanalysts -- especially against those armed with computers of their own.

Many traditional algorithms have operated by performing one-for-one character substitutions based on the key. For example, the "Vignere-Vernam" ciphers use a square array of characters. To encipher, each character of cleartext is used as a column index into this array; the character of the key corresponding to this character of cleartext (i.e., the nth character of the key corresponds with the nth character of cleartext) is used as a row index. The character at the intersection is the corresponding ciphertext character. The key is repeated as many times as necessary to exhaust all characters of cleartext. The square array can contain essentially any characters. These ciphers' weakness arise from the key repitition and the simple substitution of a very short message element (a character). Such ciphers are subject to frequency analysis, particularly if a sample of cleartext is available. This oversimplified account is drawn from "Cryptology, the Computer, and Data Privacy" by M. B. Girdansky.

The algorithm developed by Smith and Feistel uses the

traditional enciphering mechanisms of substitution of strings and modulo arithmetic on strings. However, by repeated cycles, essentially a substitution is performed on not small characters but 128-bit blocks. Thus such methods as frequency analysis require computation time on the order of the lifetime of the universe.

This algorithm, called Lucifer, has the added advantages of simple hardware implementation with shift-registers and easy reversibility. A general description of the algorithm follows and then a proof of its reversibility.

The basic transformations used are one-to-one mappings and exclusive-ors (mod-2 addition). The input is divided into equal-sized blocks; each block is processed completely independently of the others. The following description refers to one block only. It is thus desirable from a cryptographic point of view to use as large a block size as possible, since the more bits which affect a given bit of ciphertext, the harder will be the job of the cryptanalyst. As mentioned before, a basic weakness in many ciphers is the small block size.

A block is broken into the top half and the bottom half. Without changing the bottom half, it is broken into easily manipulable units called bytes. Each byte undergoes one of two one-to-one transformations depending upon a bit of the key. This collection of transformed bytes is

referred to as confused bytes, and the operation is referred to as confusion. Next, each bit of the confused bytes is modulo-2 summed with a different bit of the key. This operation is referred to as interruption. Now these bytes are modulo-2 summed with the top half of the cleartext, the block previously unused. This is called diffusion. The two halves are swapped; this operation is called interchange. Sixteen such cycles occur. One complete confusion-interruption-diffusion cycle is called a CID cycle. The schedule for accessing key bits is so arranged that every key bit is used for both controlling the confusion transformation and for interruption. The interchange operation occurs on every cycle except the last.

1/2

page 15

Figure 1: Flowchart

Figure 1 shows a flowchart of the operation. Thus the algorithm consists of:

Figure 2: Block Diagram

The only difference between enciphering and deciphering is the order in which the key bits are accessed. Within CID cycle n during deciphering, key bits are accessed in the

page 16

same order as in CID cycle 15 - n in enciphering. These operations, explained in general here, are fully detailed in Appendix A - Operation of the Lucifer Hardware.

This leads to a simple proof of reversibility, as explained in the next section.

A PROOF OF LUCIFER'S REVERSIBILITY

Assume there are n + 1 CID cycles and thus n interchanges. Call output of the CID cycle n - 1 M0 || Ml (where MO is the first half of the message, M1 is the second half). Call the output of cycle n CO Cl. The double vertical bar represents concatenation. MO || M1 is transformed in the following manner by cycle n, which is the last cycle (the first is numbered 0). Confusion: A transformation T (M1) is applied. Which transformation depends on a bit of the key (one for each byte of M1) but since the same key bits will be accessed for the same byte positions during deciphering the specific transformations selected is irrelevent, as long as they are all one-to-one. Interruption: T (Ml) is exclusive-ored with specific key bits KI. Diffusion: T (M1) + KI is exclusive-ored with the top half. The total message is thus T (M1) + KI + M0 | M1. Remember that on cycle n no interchange occurs. On deciphering, this output will be fed into decipher cycle 0, which is the same as encipher cycle n. Since this cycle is exactly the same as the last encipher cycle, confusion and interruption will generate T (M1) + KI just as before. When this is exclusive-ored with the top half consisting of T (M1) + KI + M0 the original M0 will be regenerated.

Since the interchange before encipher cycle n occurs after decipher cycle 0, the output from the interchange will

also match. Thus the entire n - 1 interchange and n CID for encipher is equivalent to the 0 CID and 0 interchange. Thus these cycles can now be effectively stripped off; the same proof is applied to a Lucifer consisting of n CID cycles and n - 1 interchanges. Eventually a Lucifer of one CID cycle and zero interchanges remain; this has already been demonstrated above to be reversible.

In the actual specific operation of Lucifer, the diffusion operation does not consist of a simple exclusive-or; instead the bits are permuted in a fixed fashion before diffusion. This does not affect the reversibility, since the ciphertext will undergo the same permutation and thus each cycle will regenerate the input of the corresponding encipher cycle. However, this permutation is necessary for the cipher to be difficult to break. It ensures that small differences, say a one-bit change, in a given message block will propagate throughout all the bits of that block of ciphertext. Each bit of cleartext potentially affects every bit of ciphertext, within a 128-bit block.

#### THE MULTICS SOFTWARE IMPLEMENTATION

Two programs were written as implementations of the IBM hardware versions of Lucifer. One is a straightforward PL/I program which manipulates the bits in essentially the same fashion the hardware does. The other is a Multics assembly language program optimized for speed of execution. Details and listings of each may be found in the appendices. Instructions on using them are given here.

First, a key must be supplied. This is done by calling the set key entry:

declare lucifer \$set key entry (bit (128));

call lucifer \$set key (key);

This entry saves the key in internal static. This key will be used for all future enciphering and deciphering until set key is called again.

To encipher:

declare lucifer\_\$encipher entry (dimension (\*) bit (128), dimension (\*) bit (128), fixed binary precision (35));

call lucifer\_\$encipher (cleartext, ciphertext, code);

The packed bit array, cleartext, is enciphered and deposited in the equal-sized array ciphertext. The code argument will be set to zero unless the dimensions of cleartext and ciphertext do not agree, in which case code

will be set to one and the enciphering not performed. The ciphertext and cleartext may be the same variable.

To decipher:

call lucifer\_\$decipher (ciphertext, cleartext, code);

This entry is declared the same as encipher, and its operation is similar.

One problem with this implementation is that Lucifer requires a 128-bit block to encipher each 128-bit block of the cleartext. If the cleartext is not a multiple of 128 bits the last block could be padded with zeroes, but the output ciphertext corresponding to this block cannot be truncated. If it is information will be lost and it will not be deciphered correctly. This is because on decipher the truncated block will be padded to 128 bits (with zeroes, presumably) which is not identical to the original output of encipher before truncation. Therefore the primitive subroutines lucifer\_\$encipher and lucifer\_\$decipher require data to be passed in 128-bit blocks.

To make this more palatable to Multics users (to whom data tends to come in multiples of 9-bit characters or 36-bit words anyway) a command has been written to translate an entire segment. To set the key, type:

#### set\_key -key-

where -key- will be padded or truncated to 128 bits and is an octal string.

To encipher a segment, type:

encipher -cleartext- -ciphertext-

The segment whose relative pathname is -cleartext- will be enciphered. If the optional argument -ciphertext- is not given the original segment will be overwritten; otherwise the ciphertext will be written onto the segment named -ciphertext-.

The input will be padded to a mod 128 bit length with zeroes, and the output segment will be equal in length. Note that no additional pages can ever be required by this padding, since a page is 36\*1024 bits long, a multiple of 128.

To decipher, type:

decipher -ciphertext- -cleartext-

This command operates in the same way as encipher. Since the ciphertext segment must be a multiple of 128 bits long, exactly as produced by encipher, the output deciphered text will be exactly as long. This is because decipher has no way of knowing how long the original was. This can damage standard object segments which have significant words expected to be found at the end of the segment. Note that a better version of this command would encipher the original cleartext length into the ciphertext segment.

TIMING MEASUREMENTS AND CONCLUSIONS

One of the important questions addressed by this paper is "Is it possible to take an algorithm designed for easy hardware implementation and efficiently translate it to software?". Performance measurements by Feistel show that the Lucifer hardware module enciphered a 128-bit block in about 165 microseconds. A version written in 360 assembly langugage for the 360/67 required about 9 milliseconds. The current Multics hardware, the Honeywell model 6180, executes instructions at approximately the same rate as the IBM 360/67. The PL/I version, as expected, was extremely slow and required 10.4 seconds to encipher 72 blocks of 128 bits each, or 144 milliseconds/block. The assembly language version required .4 seconds/72 blocks, or 5.5 milliseconds/block. Multiplying by ten the number of blocks passed to lucifer did not substantially reduce the time/block, suggesting that 5.5 milliseconds represents real computation and not overhead. Since Multics characters are nine bits long, Lucifer requires 5.5 \* (9/128) = 390 microseconds per character enciphered. Currently the Multics I/O system requires about 100 microseconds per character for its processing; thus if Lucifer were used for all I/O a severe performance degradation could occur. However this speed probably suffices for the occasional use to which it might be put.

There are some possibilities for further speed-up of the assembly language version; this is discussed in Appendix C.

page 24

APPENDIX A - OPERATION OF THE LUCIFER HARDWARE

This appendix explains the details of the operation of Lucifer as it was originally designed, as a hardware device. This material is drawn from J. Lynn Smith's "The Design of Lucifer, a Cryptographic Device for Data Communications".

A copy of the PL/I program which implements the algorithm, duplicating very closely the exact bit flows within the hardware, is shown and explained in Appendix B.

Several cautions must be made in reading the hardware diagram given in figure 4. Individual bits of a given byte are arrayed vertically across registers; bytes are numbered right-to-left, bits of a byte top-to-bottom. Thus each vertical column below represents one byte of eight bits. Therefore if the bytes are adjacent (0, 1, 2...etc) the storage order in memory (in a two-dimensional array) is according to the ordered pairs in each bit position shown below.

| 7   | 6   | 5   | 4   | 3   | 2    | 1   | 0 、 | otit |

|-----|-----|-----|-----|-----|------|-----|-----|------|

| 7,0 | 6,0 | 5,0 | 4,0 | 3,0 | 2,0  | 1,0 | 0,0 | 0    |

| 7,1 | 6,1 | 5,1 | 4,1 | 3,1 | 2,1  | 1.1 | 0,1 | 11   |

| 7,2 | 6,2 | 5,2 | 4,2 | 3,2 | 2,2  | 1,2 | ù,2 | 2    |

| 7,3 | 6,3 | 5,3 | 4,3 | 3,3 | 2,3  | 1,3 | 0,3 | 3    |

| 7,4 | 6,4 | 5,4 | 4,4 | 3,4 | 2,4  | 1,4 | 0,4 | 4    |

| 7,5 | 6,5 | 5,5 | 4,5 | 3,5 | 2,5  | 1,5 | 0,5 | 5    |

| 7,6 | 6,6 | 5,6 | 4,6 | 3,6 | 2,6  | 1,6 | 0,6 | 6    |

| 7,7 | 6,7 | 5,7 | 4,7 | 3,7 | · ,7 | 1,7 | 0,7 | 7    |

Figure 3: Bit Addresses in Registers

SONTROL REGISTER NOITAM A092WAAT  $\oplus$ T La M 0 5 A ŧ A 1 A CONVOLUTION REGISTERS Œ Ð 9 8 ⊕ Ð 0 0 M E 120 1 ¢ 3 -41 tc 3 M 121 24 4 F 0010MJUNE CONFUSER 0 IS 5 KEY SHIFT RECISTERS SCURCE REGISTERS 0 5 07 9 5 7 5 51 1 1 4 1 1 A \* 1 1 4 51

Figure 4: Hardware Schematic

Note also that the author assumed that high-order bits are transmitted first; the Smith paper does not specify this. Thus bits are first loaded into position 0 of the convolution registers (top half), then position 1, 2 etc. on to position 0 of the source registers (bottom half).

Each of the registers shown is connected as a circular shift-register. In addition, bits can be shifted from the convolution registers to the source registers and back for the interchange operation.

A complete enciphering or deciphering operation for one 128-bit block consists of sixteen confusion-interruption-diffusion (CID) cycles, with an interchange cycle in between each CID cycle for a total of 15 interchange cycles.

At the start of a CID cycle, byte 0 of the key is copied into the transformation-control register. This register will supply eight bits for controlling the confusion operation; each bit will correspond with one byte of the source registers.

A CID cycle consists of eight shifts of the source, convolution, and transformation-control register (TCR). The TCR shifts vertically upward; other registers rotate horizontally, byte n going to byte mod (n - 1, 8).

An individual shift of a CID cycle occurs as follows. Byte 0 is taken from the source registers. It flows into the confusion box along with bit 0 of the TCR. A one-to-one

page 28

transformation is applied to this byte, according to the bit from the TCR. The output from the confusion box is an eight-bit confused byte. Each bit of the confused byte is exclusive-ored with some bit of the convolution registers; note that no two bit positions are in the same byte. Each of these result bits is exclusive-ored with some bit of the rightmost byte of the key; this constitutes the interruption function. The result of this operation is stored in the bit position of the convolution registers to the right of the pair of exclusive-or gates. Note that diffusion occurs before interruption, but this is immaterial since mod 2 addition is commutative. As the result bit is stored in the convolution registers, the convolution registers, source registers, and TCR undergo a shift. Thus the bit that previously was to the right of the exclusive-or gates in the convolution registers is not destroyed; it is shifted right, and the result of diffusion occupies its old position.

These shifts are executed eight times for each CID cycle. In addition, during each shift the 16-byte key registers each rotate right one position with one exception: during the last shift of each CID cycle the key register is not rotated during encipher; during decipher the key registers rotate two positions after the last shift. Thus seven key shifts occur per CID cycle on encipher and nine key shifts occur per CID cycle on decipher. This, coupled with an initial shift of nine positions before processing any blocks, constitutes the only difference between enciphering and deciphering.

When eight shifts of one CID cycle are complete, the source registers will be back to their original position. The convolution registers are also restored except that each of its 64 bits has been exclusive-ored with exactly one key bit exclusive-ored with exactly one source bit. This is guaranteed by the placing of the gates in a different byte position for each bit of the confused byte. The key registers have been rotated either seven times (for encipher) or nine times (for decipher). The TCR has yielded all its bits. An interchange cycle now occurs, unless this is the last CID cycle. This consists of connecting positions 0 and 7 of the source registers with positions 7 and 0 of the convolution registers, respectively; eight shifts now occur. This merely swaps the contents of the registers.

Now the next CID cycle begins. A new key byte is fetched into the TCR. On CID cycle 1 this will be byte 7 for encipher and byte 2 for decipher of the original key.

It is important that the key bits be accessed in the reverse order (between CID cycles) when deciphering as compared to enciphering, but in the same order within each CID cycle. This is to ensure reversibility, as explained earlier. In addition, for cryptographic strength each bit of the key should be accessed an equal number of times:

eight times for interruption and once for transformation control of one byte of the source registers. The following method of accessing key bytes was thus devised. If there is to be an encipher, the key is initialized by loading it into the key registers. If a decipher is to be performed, the key registers are then rotated so that the first CID cycle will use bytes 9 to 0 rather than 0 to 7. After each CID cycle there will be no key shifts on encipher, but there will be two shifts during decipher. This will cause the key

page 31

bytes to be accessed as shown in table 1.

| Table | 1: | Key | Byte | Access | Schedule |

|-------|----|-----|------|--------|----------|

|-------|----|-----|------|--------|----------|

| CID | cycle |    |    |    | er | ncip | her |    |    |    |    | dec | <b>i</b> ph | ler |    |    |    |  |

|-----|-------|----|----|----|----|------|-----|----|----|----|----|-----|-------------|-----|----|----|----|--|

|     | 0     | 0  | 1  | 2  | 3  | 4    | 5   | 6  | 7  | 9  | 10 | 11  | 12          | 13  | 14 | 15 | 0  |  |

|     | 1     | 7  | 8  | 9  | 10 | 11   | 12  | 13 | 14 | 2  | 3  | 4   | 5           | 6   | 7  | 8  | 9  |  |

|     | 2     | 14 | 15 | 0  | l  | 2    | 3   | 4  | 5  | 11 | 12 | 13  | 14          | 15  | 0  | 1  | 2  |  |

|     | 3     | 5  | 6  | 7  | 8  | 9    | 10  | 11 | 12 | 4  | 5  | 6   | 7           | 8   | 9  | 10 | 11 |  |

|     | 4     | 12 | 13 | 14 | 15 | 0    | 1   | 2  | 3  | 13 | 14 | 15  | 0           | 1   | 2  | 3  | 4  |  |

|     | 5     | 3  | 4  | 5  | 6  | 7    | 8   | 9  | 10 | 6  | 7  | 8   | 9           | 10  | 11 | 12 | 13 |  |

|     | 6     | 10 | 11 | 12 | 13 | 14   | 15  | 0  | 1  | 15 | 0  | 1   | 2           | 3   | 4  | 5  | 6  |  |

|     | 7     | 1  | 2  | 3  | 4  | 5    | 6   | 7  | 8  | 8  | 9  | 10  | 11          | 12  | 13 | 14 | 15 |  |

|     | 8     | 8  | 9  | 10 | 11 | 12   | 13  | 14 | 15 | 1  | 2  | 3   | 4           | 5   | 6  | 7  | 8  |  |

|     | 9     | 15 | 0  | l  | 2  | 3    | 4   | 5  | 6  | 10 | 11 | 12  | 13          | 14  | 15 | 0  | 1  |  |

|     | 10    | 6  | 7  | 8  | 9  | 10   | 11  | 12 | 13 | 3  | 4  | 5   | 6           | 7   | 8  | 9  | 10 |  |

|     | 11    | 13 | 14 | 15 | 0  | 1    | 2   | 3  | 4  | 12 | 13 | 14  | 15          | 0   | 1  | 2  | 3  |  |

|     | 12    | 4  | 5  | 6  | 7  | 8    | 9   | 10 | 11 | 5  | 6  | 7   | 8           | 9   | 10 | 11 | 12 |  |

|     | 13    | 11 | 12 | 13 | 14 | 15   | 0   | 1  | 2  | 14 | 15 | 0   | 1           | 2   | 3  | 4  | 5  |  |

|     | 14    | 2  | 3  | 4  | 5  | 6    | 7   | 8  | 9  | 7  | 8  | 9   | 10          | 11  | 12 | 13 | 14 |  |

|     | 15    | 9  | 10 | 11 | 12 | 13   | 14  | 15 | 0  | 0  | l  | 2   | 3           | 4   | 5  | 6  | 7  |  |

|     |       |    |    |    |    |      |     |    |    |    |    |     |             |     |    |    |    |  |

The byte of the key used for transformation control is in the left-hand column. Note that the decipher schedule is the same as the encipher schedule read upsidedown, but within a CID cycle, read horizontally, bytes are accessed in the same order. Also note that the key registers will be so positioned after sixteen CID cycles ready for the next

block: in byte 0 for encipher, byte 9 for decipher.

The exact nature of the confusion operation has not been explained yet. It is not important particularly what it is, as long as it is one-to-one and sufficiently random. It works as follows. Each byte to be confused (from the source registers) is split into two four-bit halves. If the key bit from the TCR for this byte is 1, the two halves are exchanged; otherwise no operation is performed. Next, each four-bit half undergoes a one-to-one mapping. The method in hardware used decoders, encoders, and permuted wires, but effectively a table look-up was done to associate with each the sixteen bit combinations a unique four-bit of replacement. The two mappings for the two halves are different; the one for the top half is called S0 and the one for the bottom half is Sl. Finally an 8-bit byte is generated by permuting the eight wires from these two mapping networks. The result of this entire confusion operation (and the way it is done in the software versions) is to consider the key bit concatenated with the source byte a nine-bit index into a 512 element table. Each element as an eight-bit confused byte. This is explained in is Appendix B, the PL/I implementation.

|       | Table | 2: | Four-bit | Permuta | ations |

|-------|-------|----|----------|---------|--------|

| input | t     |    | S        | )       | Sl     |

| 0000  |       |    | 110      | 00      | 0111   |

| 0001  |       |    | 111      | 11      | 0010   |

| 0010  |       |    | 011      | 11      | 1110   |

| 0011  |       |    | 101      | LO      | 1001   |

| 0100  |       |    | 111      | LO      | 0011   |

| 0101  |       |    | 110      | )1      | 1011   |

| 0110  |       |    | 101      | 11      | 0000   |

| 0111  |       |    | 000      | 00      | 0100   |

| 1000  |       |    | 001      | LO      | 1100   |

| 1001  |       |    | 011      | LO      | 1101   |

| 1010  |       |    | 000      | 11      | 0001   |

| 1011  |       |    | 000      | 01      | 1010   |

| 1100  |       |    | 100      | 1       | 0110   |

| 1101  |       |    | 010      | 00      | 1111   |

| 1110  |       |    | 010      | 1       | 1000   |

| 1111  |       |    | 100      | 00      | 0101   |

page 34

#### APPENDIX B - THE PL/I IMPLEMENTATION

The PL/I implementation is very similar to the hardware design. However, instead of rotating data toward the low address end of each register, index values into fixed arrays are decremented and wrapped around to the high order end. Note very carefully that each byte shown in the hardware diagram, those bits arrayed vertically, are rows of two-dimensional arrays. Thus if a conventional PL/I array is printed it will appear transposed as compared to the map of the registers. For consistency within this document all arrays will be transposed from the conventional order so that they appear identical to the hardware bit orderings.

Instead of doing 15 interchanges (unlike most other operations, a real movement of data occurs on interchange) 16 are done. This last interchange is undone by copying the source registers first into the result block followed by the convolution registers. This is to avoid checking within the loop for the special case of the last execution. Similarly rather than skipping a key-shift cycle on encipher and performing an extra one on decipher each CID cycle, eight increments of the key index interruption row are always performed. After a CID cycle is complete, a fixup variable added either one or minus one is modulo 16 to interruption row; this variable is -1 for encipher and 1 for decipher.

The program operates as follows. It copies the first half of a given 128-bit block into the convolution\_registers; the second half is copied into source\_registers. The interchange\_index loop counts the CID-interchange cycles, sixteen in number. Within that loop a CID cycle is performed by assigning interruption\_row to ks\_row; interruption\_row shows which byte of the key will next be used for interruption, ks\_row shows which byte will be used for transformation control. This assignment is the equivalent of copying the next byte of the key into the TCR at the start of a CID cycle. Now the data\_row loops eight times, once for each byte in source\_registers. The entire confusion operation is implemented by a 512 byte table; the first half for key bit = 0, the second half for key bit = 1. Thus the confused byte is found by indexing this table with the key bit identified by ks\_row and data\_row concatenated with the source byte identified by data\_row. Now convolution\_index loops eight times, once for each bit in the confused byte. Note that this is all done in parallel in the hardware version and in the assembly language version described in Appendix C. Each bit of the confused byte must be exclusive-ored with some bit of the key byte identified by interruption\_row. Just as the key interruption wires were permuted in the hardware, so key\_table tells which bit of that key byte is supplied for each bit of the confused byte. This interrupted bit is now exclusive-ored with some

bit of the convolution registers. The register in which the bit lies which will be diffused (the one to the right of the exclusive-or gates) is the one corresponding to the source register from which the interrupted bit was derived. The number of this register, the column in the PL/I sense (although it is horizontal on the diagrams) is therefore convolution\_index. The byte in which this bit lies is given by a table, convolution\_table. These positions rotate right around the registers, one position for each shift of the CID cycle, once for each incrementing of data\_row. Therefore the correct convolution\_table entry for this bit of the interrupted byte must be mod-8 summed with data\_row; this

supplies the byte or row number of the target bit.

After this byte is complete, interruption\_row is incremented mod 16 to simulate rotating the key registers once to the right. Now data\_row is incremented to have the effect of rotating the source, convolution, and transformation-control registers.

After the eight loops of data\_row, interruption\_row must be readjusted to simulate only seven key shifts on encipher but nine shifts on decipher. As explained before, a fixup variable either\_one\_or\_minus\_one is mod 16 added to interruption\_row; this fixup variable is set at the entry points. The two entry points also set the initial interruption\_row, either 0 for encipher or 9 for decipher.

After sixteen loops of interchange index, sixteen

page 37

CID-interchange pairs have been performed. The block is now copied into the result field; the source registers are copied first to undo the effect of the extra interchange cycle.

pare 38

Copyright (c) 1974, Massachusetts Institute of Technology and Honeyvell Information Systems, Inc. /\* This module implements the Lucifer enciphering algorithm as developed by IBP. Initially code' by C. Cordon Remedict 04/26/74 at the Computer Systems Pesearch division of Project MAC \*/ set key: procedure (a\_key); /\* this entry used to tell lucifer what key to use \*/ a key parameter hit (128); /\* key user has \*/ declare key hit (8) dimension (0 : 15) internal static; declare /\* iterate thru columns of key \*/ do data row = 0 to 15;/\* iterate thru rows of vey \*/ do ks\_row = 0 to 7; substr (key (data\_row), ks\_row + 1, 1) = /\* transpose \*/ substr (a\_key, 16 \* ks\_rov + data\_row + 1, 1); end; end; return; /\* Declarations for enciphering and deciphering entries follow \*/ declare (addr, hool. dim, fixed, mor, string, substr) builtin: (source\_registers, /\* the source registers (bottom half) \*/ declare convolution\_registers) /\* convolution registers (ton half) \*/ dimension (0 : 7) hit (8) unaligned; text\_position fixed binary precision (24, 0); /\* hits of input string processed so far \*/ declare (Interchange\_Index, /\* counts Interchange cycles (0 - 15) \*/ declare /\* what row of source or convolution register now munging \*/ data row, /\* what row of hey now using for transformation control \*/ ks row, convolution\_index, /\* which hit of confused byte (during one CID) convolving now \*/ convolution\_row, /\* which row of convolution registers contains XOD gate (hardware back) \*/ interruption\_row, /\* row of key used for interruption-diffusion \*/ /\* -1 for encimber, 1 for decimber \*/ either\_one\_or\_minus\_one) fixed binary; /\* output of confuser (1 byte) \*/ confused\_byte bit (8); declare /\* used merely for swapping source and convolution registers \*/ temp\_register hit (64); declare convolution\_table dimension (0 : 7) /\* which bit positions to mung in convolution registers \*/ declare

nare 30

initial (7, 6, 2, 1, 5, 0, 3, 4) static internal fixed binary precision (3): declare key\_table dimension (0 : 7) /\* gives permutation of key hits used for interruption \*/ initial (2, 5, 4, 0, 3, 1, 7, 6) internal static fixed binary precision (3): Sinclude confusion table; encipher: /\* enciphering entry \*/ entry (a\_in, a\_out, a\_code); declare (a in, /\* cleartext (cinhertext for decinher) \*/ a out) dimension (\*) hit (128) parameter; /\* ciphertext (cleartext for decipher) \*/ declare (a\_in\_ovly based (addr (a\_in)), a\_out\_ovly based (addr (a\_out))) bit (message\_length) unaligned; message\_length fixed binary precision (24); declare a code fixed binary precision (35); declare /\* status code \*/ either\_one\_or\_minus\_one = -1; /\* amount to add after a CID cycle to interruption row, because encipher resuses last byte \*/ interruption row = 0; /\* first byte of key to use is byte 0 \*/ goto ioin: /\* common code \*/ decipher: /\* deciphering entry -- note ciphertext is first are \*/ entry (a\_ir, a\_out, a\_code); either\_one\_or\_minus\_one = 1; /\* skin a byte of key when deciphering for each CID cycle \*/ interruption row = 9; /\* first byte of key to use when deciphering \*/ ioin: /\* common section \*/ message\_length = dim (a\_in, 1) \* 128; /\* number of bits in input \*/ if dim (a out, 1) \* 128 = message length then do; /\* harf at this \*/ a code = 1; return; end: /\* main loop follows. this consists of separately and independently processing each 128-bit block of input text (may be clear- or cipher-text). each block is processed by 16 interchange cycles interspersed with 16 CIP (confusion-interruption-diffusion) cycles. for more details see IPM papers and my thesis. \*/ do text\_position = 0 by 128 while (text\_position < message\_length); /\* each block \*/ string (convolution\_registers) = substr (a\_in\_ovly, text\_position + 1, F4); string (source\_registers) = substr (a\_in\_ovly, text\_nosition + F5, 64); do interchange\_index = 0 by 1 to 15; /\* 16 Interchange cycles \*/ ks\_row = interruption row; /\* transformation control is first byte of key used for interruntion in this fin cycle \*/ do data\_row = 0 to 7; /\* process & bytes of input each CID cycle \*/ confused byte = /\* look up in table to get confusion \*/ confusion\_table (fixed (substr (bey (bs\_row), data\_row +1, 1) ||

page 40

source\_registers (data\_row), 9, 0));

do convolution\_index = 0 to 7;

/\* convolve each hit of confused byte \*/

convolution\_row = /\* for each cycle

convolution positions rotate around registers \*/

substr (convolution\_registers (convolution\_row), convolution\_index +1, 1) =

hool (substr (key (interruption\_row),

key\_table (convolution\_index) + 1, 1),

bool (substr (confused\_byte, convolution\_index +1, 1),

substr (convolution\_registers (convolution\_row),

convolution\_index +1, 1), "nilo"b), "nilo"b);

end;

interruption\_row = /\* add 1 for next key byte with wraparound \*/

mod (interruption\_row + 1, 16);

end;

interruption\_row = /\* on encipher, so back 1 byte, decipher, skip 1 \*/

mod (interruption\_row + either\_one\_or\_minus\_one, 16);

/\* swap source and convolution registers \*/

```

string (temp_register) = string (source_registers (*));

string (source_registers (*)) = string (convolution_registers (*));

string (convolution_registers (*)) = string (temp_register);

end;

substr (a_out_ovly, text_position + 1, 64) = string (source_registers);

substr (a_out_ovly, text_position + 65, 64) = string (convolution_registers);

end;

a_code = 0;

return;

```

end set\_key;

page 11

/\* IMCLUPE FILE confusion\_table.incl.nll

This implements the confusion operation of Lucifer.

It should only be used by lucifer.nll \*/

declare confusion\_table initial (

| lare | contusion_ta                 | nie inicial ( |              |              |               |                                                                                                                 |              |                                                                                                                  |

|------|------------------------------|---------------|--------------|--------------|---------------|-----------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------|

|      | "01010111"h,                 | "11011111"ь,  | "11001111"h, | "11010011"5, | "1]0]01111"ь, | "01011111"",                                                                                                    | "11011011"h, | "01000011"h,                                                                                                     |

|      | "11000011"b,                 | "11000111"h,  | "11001011"h, | "піппіпії"ь, | "01011011"F,  | "01000111"h,                                                                                                    | "01001111"5, | "n1n1n011"h,                                                                                                     |

|      | "non10101"h,                 | "10011101"h,  | "10001101"5, | "10010001"5, | "10010101"ь,  | "00011101"5,                                                                                                    | "10011001"5, | "0000001"h,                                                                                                      |

|      | "10000001"h,                 | "10000101"h,  | "10001001"h, | "00001001"h, | "non11001"h,  | "00000101"h,                                                                                                    | "00001101"h, | "00010001"h,                                                                                                     |

|      | "01110101"h.                 | "11111101"h,  | "11101101"5, | "11110001"5, | "11110101"h,  | "01111101"ь,                                                                                                    | "11111001"5, | "01100001"ь,                                                                                                     |

|      | "11100001"b.                 | "11100101"h.  | "11101001"ь. | "01101001"h, | "01111001"h.  | "01100101"h,                                                                                                    | "01101101"h. | "01110001"h,                                                                                                     |

|      | "00110110"h,                 | "10111110"b.  | "10101110"h. | "10110010"ь. | "10110110"ь,  | "00111110"h,                                                                                                    | "10111010"h, | "00100010"h,                                                                                                     |

|      | "10100010"b,                 | "10100110"h,  | "10101010"5, | "00101010"h, | "00111010"ь,  | "00100110"5,                                                                                                    | "00101110"h, | "00110010"h,                                                                                                     |

|      | "00010111"b.                 | "10011111"b.  | "10001111"5. | "10010011"b. | "10010111"h.  | "00011111"h.                                                                                                    | "10011011"h. | "00000011"h,                                                                                                     |

|      | "10000011"b,                 | "10000111"5,  | "10001011"5. | "00001011"b. | "00011011"h.  | "00000111"6.                                                                                                    | "00001111"b. | "00010011"h,                                                                                                     |

|      | "00110111"ь,                 | "10111111""   | "10101111"5. | "10110011"5, | "10110111"h.  | "00111111"h;                                                                                                    | "10111011"5. | "00100011"h.                                                                                                     |

|      |                              | 200           | 100          | "00101011"5. | "00111011"5.  | "00100111"b.                                                                                                    | "00101111"5. | "00110011"h.                                                                                                     |

|      | "10100011"b,<br>"00010100"b, | "10100111"h,  | "10101011"5, |              |               | "00011100"F.                                                                                                    | "10011000"b. | "00000000"b.                                                                                                     |

|      |                              | "10011100"h,  | "10001100"h, | "10010000"h, | "10010100"b,  | "00000100"5.                                                                                                    | "00001100"5. | "00010000"h,                                                                                                     |

|      | "1000000"ь,                  | "10000100"ь,  | "10001000"h, | "00001000"h, | "00011000"5,  | And and the second s |              | And the second |

|      | "01010100"h,                 | "11011100"h,  | "11001100"ь, | "11010000"5, | "11010100"h,  | "01011100"ь,                                                                                                    | "11011000"h, | "01000000"h,                                                                                                     |

|      | "11000000"ь,                 | "11000100"ь,  | "11001000"h, | "01001000"5, | "01011000"5,  | "01000100"h,                                                                                                    | "01001100"5, | "01010000"b,                                                                                                     |

|      | "01110100"Ь,                 | "11111100"ь,  | "11101100"ь, | "11110000"ь, | "11310300"5,  | "01111100"ь,                                                                                                    | "11111000"ь, | "01100000"h,                                                                                                     |

|      | "11100000"Ь,                 | "11100100"5,  | "11101000"F, | "01101000"ь, | "01111000"ь,  | "01100100"ь,                                                                                                    | "01101100"F, | "01110000"ь,                                                                                                     |

|      | "о1110110"ь,                 | "11111110",   | "11101110"h, | "11110010""  | "11110110"b,  | "01111110"ь,                                                                                                    | "11111010"ь, | "01100010"b,                                                                                                     |

|      | "11100010"Ь,                 | "11100110"5,  | "11101010"F, | "01101010"5, | "01111010"h,  | "01100110"h,                                                                                                    | "01101110"ь, | "01110010"h,                                                                                                     |

|      | "00010110"h,                 | "10011110"ь,  | "10001110"5, | "10010010"h, | "10030110"F,  | "00011110"F,                                                                                                    | "10011010"h, | "00000010"5,                                                                                                     |

|      | "10000010"5,                 | "10000110"5,  | "10001010"h, | "00001010"h, | "00011010"F,  | "00000110"F,                                                                                                    | "00001110"h, | "00010010"5,                                                                                                     |

|      | "00110101"5,                 | "10111101"h,  | "10101101"h, | "10110001"ь, | "10110101"",  | "00111101"5,                                                                                                    | "10111001"h, | "00100001"5,                                                                                                     |

|      | "10100001"h,                 | "10100101"h,  | "10101001"h, | "00101001"h, | "00111001"h,  | "00100101"h,                                                                                                    | "00101101"ь, | "00110001"h,                                                                                                     |

|      | "01010101"h,                 | "11011101"5,  | "11001101"h, | "11010001"5, | "11010101"h,  | "01011101"5,                                                                                                    | "11011001"5, | "01000001"5,                                                                                                     |

|      | "11000001"h,                 | "11000101"5,  | "11001001"h, | "01001001"h, | "01011001"5,  | "01000101"5,                                                                                                    | "01001101"h, | "01010001"h,                                                                                                     |

|      | "01110111"b,                 | "11111111"5,  | "11101111"h, | "11110011"h, | "11110111"ь,  | "01111111"ь,                                                                                                    | "11111011"h, | "01100011"5,                                                                                                     |

|      | "11100011"h,                 | "11100111"5,  | "11101011"h, | "01101011"ь, | "пјјјјпј1"ь,  | "01100111"5,                                                                                                    | "01101111"h, | "01110011"5,                                                                                                     |

|      | "00110100"h,                 | "10111100"ь,  | "10101100"5, | "10110000"h, | "10110100""   | "00131100"h,                                                                                                    | "10111000"h, | "DO10000"F,                                                                                                      |

|      | "10100000"h,                 | "10100100"h,  | "10101000"h, | "nn1n1nnn"h, | "00111000"h,  | "no100100"h,                                                                                                    | "00101100"ь, | "00110000"h,                                                                                                     |

|      | "01010110"h;                 | "11011110"b,  | "11001110"5, | "11010010"h, | "11010110"h,  | "01011110"h,                                                                                                    | "11011010"5, | "01000010"h,                                                                                                     |

|      | "11000010"h,                 | "11000110"h,  | "11001010"h, | "01001010"h, | "01011010"h,  | "01000110"h,                                                                                                    | "n1n01111"h, | "01010010"5,                                                                                                     |

|      | "01010111"b,                 | "11011111"b,  | "11001111"5, | "11010011"5, | "11010111"",  | "01011111"ь,                                                                                                    | "11011011"Ь, | "01000011"h,                                                                                                     |

|      | "11000011"h,                 | "11000111"h,  | "11001011"h, | "01001011"h, | "01011011"h,  | "01000111"5,                                                                                                    | "01001111"b, | "01010011"h,                                                                                                     |

|      | "00010101"h,                 | "10011101"h,  | "10001]01"h, | "10010001"h, | "10010101"ь,  | "00011101"5,                                                                                                    | "10011001"h, | "00000001"5,                                                                                                     |

|      | "10000001"b,                 | "10000101"h,  | "10001001"b, | "00001001"h, | "ncn11001"h,  | "00000101"h,                                                                                                    | "00001101"5, | "non1nno1"h,                                                                                                     |

|      | "01110101"h,                 | "11111101"h,  | "11101101"h, | "11110001"5, | "11110101"h,  | "01111101"h,                                                                                                    | "11111001"h, | "01100001"h,                                                                                                     |

|      | "11100001"h,                 | "11100101"5,  | "11101001"ь, | "01101001"h, | "01111001"h,  | "01100101"h,                                                                                                    | "01101101"ь, | "01110001"h,                                                                                                     |

|      | "оо110110"ь,                 | "10111110"ь,  | "10101110"h, | "10110010"h, | "10110110"+,  | "00111110"h,                                                                                                    | "10111010"h, | "00100010"h,                                                                                                     |

|      | "10100010"h,                 | "10100110"ь,  | "10101010"ь, | "00101010"h, | "00111010"",  | "00100110"h,                                                                                                    | "00101110"h, | "00110010"ь,                                                                                                     |

|      | "000101111"b.                | "10011111"h.  | "10001111"b. | "10010011"5, | "10010111"h.  | "000111111"h,                                                                                                   | "10011011"h, | "00000011"h,                                                                                                     |

|      | "10000011"b.                 | "10000111"h.  | "10001011"5. | "00001011"5. | "00011011"b.  | "00000111"b.                                                                                                    | "00001111"5. | "00010011"b,                                                                                                     |

|      | "00110111"Ь.                 | "10111111"ь.  | "10101111"ь. | "10110011"h. | "10110111"5.  | "P0111111"b.                                                                                                    | "10111011"h. | "00100011"b.                                                                                                     |

|      | "10100011"ь,                 | "10100111"b.  | "10101011"h. | "00101011"h. | "00111011"h.  | "n0100111"b,                                                                                                    | "00101111"h, | "00110011"b,                                                                                                     |

|      | "00010100"b.                 | "10011100"5.  | "10001100"5. | "10010000"h. | "10010100"5.  | "00011100"b.                                                                                                    | "10011000"b. | "00000000"h.                                                                                                     |

|      | "10000000"h.                 | "10000100"b.  | "10001000"5. | "00001000"b. | "00011000"h.  | "00000100"b.                                                                                                    | "00001100"b. | "00010000"b.                                                                                                     |

|      | "01010100"5,                 | "11011100"b.  | "11001100"5. | "11010000"5. | "11010100"5.  | "01011100"5.                                                                                                    | "11011000"ь, | "01000000"h,                                                                                                     |

|      | "11000000"5.                 | "11000100"ь.  | "11001000"5. | "01001000"b. | "01011000"5.  | "01000100"b.                                                                                                    | "01001100"h. | "01010000"h.                                                                                                     |

|      | 11.00000 ",                  | TTOUDING "    | 11           | aloulut o uv | 010111.00     | The second second                                                                                               | THOTTOM IN   | and a state of the second s  |

page 42

| "01110100"ь, "1)111100"ь,              | "11101100"ь,              | "11110000"ь, | "11110100"6,   | "01111100"5,            | "11111000"ь, | "01100000"h. |

|----------------------------------------|---------------------------|--------------|----------------|-------------------------|--------------|--------------|

| TITO000005, "TITO0100%5,               | "11101000"b,              | "01101000"5. | "01111000"h    | "01100100"5             | "01101100"h  | "01110000"h  |

| "UTITOTIO", "TITITIO",                 | "11101110"b,              | "11110010"h. | "11110110"h    | "01111110"h             | 1111110101L  | 10110001011  |

| 11100010 D, 11100110 D,                |                           | "01101010"h, | "01111010"5.   | "01100110"b.            | "01101110"5  | "01110010"6  |

| """""""""""""""""""""""""""""""""""""" | "10001110"5,              | "10010010"h. | "10010110"b.   | "00011110"5.            | "10011010"5  | "00000010"h  |

| "10000010"ь, "10000110"ь,              | "10001010"b.              | "00001010"h. | "00011010"b.   | "00000110"b             | "00001110"5  | "00010010"b  |

| "00110101"b, "10111101"b,              | "10101101"h,              | "10110001"ь. | "10110101"h.   | "00111101"ь.            | "10111001"5  | "00100001"5  |

| "10100001"h, "10100101"h,              | "10101001"ь.              | "00101001"b. | "00111001"b.   | "00100101"5             | "00101101"5  | "00110001"h  |

| "01010101"h, "11011101"h,              | "11001101"h.              | "11010001"ь. | "11010101"     | "01011101"5             | "11011001"6  | "01000001"h  |

| "11000001"5, "11000101"5,              | "11001001"5.              | "01001001"5. | "01011001"h.   | "01000101"b.            | "01001101"5  | "01010001"6  |

| "01110111"ь, "11111111"ь,              | "11101111"ь.              | "11110011"5. | "11110111"h.   | "01111111"h.            | "11111011"h. | "01100011"h  |

| "11100011"5, "11100111"5,              | "111010111"h.             | "01101011"b. | "01111011"b.   | "01100111"h.            | "01101111"5. | "01110011"b  |

| "00110100"b, "10111100"b,              | "10101100"b.              | "10110000"5  | "10110100"5    | "00111100"b             | "10111000"b  | "00100000"h  |

| "10100000"F, "10100100"F,              | "10101000"5               | 1001010001th | 100111000UL    | llooloollh              | 10111100 0,  | 10011000011  |

| "01010110"5, "11011110"5,              | 111001110 <sup>10</sup> h | 111010010116 | 11101011011    | 101011100 0,            | U0101100 h,  | 1011000010UU |

| "11000010"b "11000110"b                | 11100101010               | 101001010Uh  | 101011010llb   | U1011110 <sup>0</sup> , | 1101101000,  |              |

| "11000010"ь, "11000110"ь,              |                           |              |                |                         |              |              |

| ) hit (8) unali                        | ener rimension            | יו (ובי יו ר | rternal static |                         |              |              |

/\* FND INCLUDE FILE confusion\_table.incl.nll \*/

APPENDIX C - THE ASSEMBLY LANGUAGE IMPLEMENTATION

The basic philosophy of the Multics assembly language version of Lucifer was to produce a program which could encipher or decipher at the highest speed. This does not contribute to the readibility of the program; therefore this explanation is quite detailed. If the reader is unfamiliar with Multics assembly language, a short introduction is given in Appendix D.

The set\_key entry does more than store the key in internal static. During ciphering the key is used in two places: transformation control and interruption. For reasons explained later, each purpose requires the key to be in a different format for optimal operation. To avoid key manipulation during ciphering, set\_key stores the key in two variables, key and exploded key.

In exploded\_key each bit of the key is given its own nine-bit byte. The high-order bit of each byte contains the key bit; the low order eight bits are zero. This key is for transformation control. In the diagram below showing the storage assignment, the ordered pair in each byte position gives the byte of the key number and the bit within the byte. As in the hardware diagrams adjacent bits of a byte are arrayed vertically, although it is more conventional to show memory words horizontally. Thus each byte of the key

page 44

requires two words; thirty-two words for 128 bits.

| 30  | 28  | 26  | 24  | 22 | 20 | 18 | 16 | 14 | 12 | 10 | 8  | 6  | 4  | 2  | 0 |

|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|---|

| 120 | 112 | 104 | 96  | 88 | 80 | 72 | 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8  | 0 |

| 121 | 113 | 105 | 97  | 89 | 81 | 73 | 65 | 57 | 49 | 41 | 33 | 25 | 17 | 9  | 1 |

| 122 | 114 | 106 | 98  | 90 | 82 | 74 | 66 | 58 | 50 | 42 | 34 | 26 | 18 | 10 | 2 |

| 123 | 115 | 107 | 99  | 91 | 83 | 75 | 67 | 59 | 51 | 43 | 35 | 27 | 19 | 11 | 3 |

| 124 | 116 | 108 | 100 | 92 | 84 | 76 | 68 | 60 | 52 | 44 | 36 | 28 | 20 | 12 | 4 |

| 125 | 117 | 109 | 101 | 93 | 85 | 77 | 69 | 61 | 53 | 45 | 37 | 29 | 21 | 13 | 5 |

| 126 | 118 | 110 | 102 | 94 | 86 | 78 | 70 | 62 | 54 | 46 | 38 | 30 | 22 | 14 | 6 |

| 127 | 119 | 111 | 103 | 95 | 87 | 79 | 71 | 63 | 55 | 47 | 39 | 31 | 23 | 15 | 7 |

Figure 5: Exploded Key Bit Assignment

For interruption, the key bits within a key byte are not accessed in the same order as the confused byte's bits, 0, 1, 2...7. Rather they are accessed 2, 5, 4, 0, 3, 1, 7, 6 as given in key\_table of the PL/I program or as shown by the wiring of the hardware. To avoid the use of such a table and lookup time during ciphering, the key bytes are presorted by set\_key. Each 8-bit byte of the key is stored in the high order part of a Multics 9-bit byte, the remaining bit being zero. Thus the storage assignment is as

shown in the diagram below.

| Figur | e 6: | Key | Bit | Ass | ignm | ent  |

|-------|------|-----|-----|-----|------|------|

| 5     | 4    | 3   | 2   | 1   | 0    | word |

| 4     | 0    | 12  | 8   | 4   | 0    | 0    |

| 5     | 1    | 13  | 9   | 5   | 1    | 1    |

| 6     | 2    | 14  | 10  | 6   | 2    | 2    |

| 7     | 3    | 15  | 11  | 7   | 3    | 3    |

Words 0 and 1 are copied into words 4 and 5. This is to permit directly addressing eight bytes starting at any byte between 0 and 15 without programming a complicated wraparound routine.

The basic idea underlying this program is to process all 64 bits of the source and convolution registers at once, each CID cycle. In order to do this, the key bits must be so arranged that each of its bits lies in the bit position corresponding to that of the source register bit with which it will be exclusive-ored during interruption. This explains the rearranging above.

When the encipher entry is called, it sets interruption\_row (held in index register 2) to zero as in the PL/I program. Since an entire CID cycle is done in parallel, interruption\_row will never be incremented along the horizontal line of the key byte access schedule given earlier. Instead it will be incremented each CID cycle to assume the values given in the schedule's left-hand column. Examining the schedule it can be seen that interruption\_row

should thus be incremented by 7 for encipher and -7 for decipher, modulo 16. Thus each entry also sets the variable either 7 or minus 7 to the appropriate value. This is added to x2 mod 16 each CID cycle.

After the argument extents are calculated and pointers to the strings fetched (bp -> input string, bb -> output string), the main loop is entered.

As in the PL/I program, the first 64 bits of each 128-bit block are placed into convolution\_registers, the next 64 into source\_registers. As with the key, each 8-bit byte is placed in the high order eight bits of a Multics 9-bit byte. This unpacking is accomplished by unpack\_loop. This loop depends on the fact that the assembler will assign source\_registers a location after convolution\_registers because it is declared afterward. The low order (high address) bytes are unpacked first.

Once this is complete, sixteen CID-interchange pairs are executed.

First, the convolution registers are prepared for the diffusion operation. Referring to the hardware diagram, one can see that each bit of a confused, interrupted byte (vertically arrayed) corresponds to a different byte but the same bit (i.e., horizontal register) of the convolution registers. As seen in the PL/I program, if a source register bit has address [i, j] (byte i, bit j) the convolution register bit corresponding to it is

[mod (i + convolution\_table [j], 8), j] where convolution\_table is [7, 6, 2, 1, 5, 0, 3, 4]. Instead of looping through each bit as the PL/I program does, the convolution registers are rotated so the bit positions for diffusions line up, corresponding with those

of the source registers.

Since the horizontal registers are the bits to rotate, the bits to rotate are not adjacent. Thus the bit addresses within the two-word convolution\_registers of each bit before rotation is as follows:

Figure 7: Convolution Registers

| 7      | 6  | 5  | 4  | 3  | 2  | 1   | 0 | exte |

|--------|----|----|----|----|----|-----|---|------|

| 63     | 54 | 45 | 36 | 27 | 18 | . 9 | 0 | 0    |

| 64     | 55 | 46 | 37 | 28 | 19 | 10  | 1 | 1    |

| <br>65 | 56 | 47 | 38 | 29 | 20 | 11  | 2 | 2    |

| 66     | 57 | 48 | 39 | 30 | 21 | 12  | 3 | 3    |

| 67     | 58 | 49 | 40 | 31 | 22 | 13  | 4 | 4    |

| 68     | 59 | 50 | 41 | 32 | 23 | 14  | 5 | 5    |

| 69     | 60 | 51 | 42 | 33 | 24 | 15  | 6 | 6    |

| 70     | 61 | 52 | 43 | 34 | 25 | 16  | 7 | 7    |

Notice that bits 8, 17, 26... 71 do not appear assigned on the matrix. This is due to the unpacking of each 8-bit byte to a 9-bit byte. The unassigned offsets are those of the pad bits. The purpose of this rotation is to align all the exclusive-or positions on the right edge of the matrix. Looking at the hardware schematic, the desired

position of each bit is as follows:

3,7

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0 \ | 1 xx |

|-----|-----|-----|-----|-----|-----|-----|-----|------|

| 6,0 | 5,0 | 4,0 | 3,0 | 2,0 | 1,0 | 0,0 | 7,0 | 0    |

| 5,1 | 4,1 | 3,1 | 2,1 | 1,1 | 0,1 | 7,1 | 6,1 | l    |

| 1,2 | 0,2 | 7,2 | 6,2 | 5,2 | 4,2 | 3,2 | 2,2 | 2    |

| 0,3 | 7,3 | 6,3 | 5,3 | 4,3 | 3,3 | 2,3 | 1,3 | 3    |

| 4,4 | 3,4 | 2,4 | 1,4 | 0,4 | 7,4 | 6,4 | 5,4 | 4    |

| 7,5 | 6,5 | 5,5 | 4,5 | 3,5 | 2,5 | 1,5 | 0,5 | 5    |

2,6 1,6 0,6 7,6 6,6 5,6 4,6 3,6

2,7 1,7 0,7 7,7 6,7 5,7 4,7

Figure 8: Postrotation Convolution Registers

This rotation is accomplished as follows. Row 0 (bits 0, 9, 18... 63) must be rotated right on the diagram (left in the AQ register as it happens) seven positions or 63 bits. Row 1 (bits 1, 10, 19 ... 64) must be rotated 6 positions or 54 bits, etc. An array of masks, and masks, has been prepared with a 1-bit in each bit position for a given register. They are ordered according to the number of positions of rotation needed. Since register 5 needs no rotation (because the exclusive-or gate is already in byte 0), the mask for it occurs first. It consists of four zeroes, a one, eight zeroes, a one, eight zeroes ... Thus, when convolution registers is loaded into the AQ register and is ANDed with this mask, only bits 5, 14, 23... 68 will remain. This register is rotated 0 bits left and then ORed into a previously zeroed doubleword, named "normalized".

6

7

Next, register 3 must be rotated left one position or nine bits. Thus the second mask has a one in bit 3 and a one every nine bits thereafter. After ANDing the convolution\_registers with this mask only bits 3, 12, 21... 66 remain. The AQ is rotated left nine bits, and ORed into "normalized".

There is a pointer to and masks called and masks ptr. It is referenced by using the add-delta (AD) type indirect reference. When an indirect reference is made through this word, after completion of the specified operation the contents of the delta field (here 2) will be added to the address field. Thus the next time the AQ is ANDed the next doubleword mask will be used. Similarly an AD word controls the shift count. The first time through the loop the AQ must be shifted zero bits so the address field of this word contains zero. After every indirect reference the address field will be incremented by the delta field, here nine. Thus the rotate counts will be 0, 9, 18... 63. In addition this word is used to control the number of times the loop will execute. After an add-delta reference is made the tally field of the word is decremented by one; if it reaches zero the tally runout indicator is set. This tally field is set to eight before beginning the loop. Thus the loop will iterate eight times, due to the transfer-tally-runout-flag off instruction at the end.

After preparing the convolution registers, the

confusion operation is performed on the source registers. This is done by loading the source registers into the AQ and shifting right one bit position. Now each 8-bit byte appears right justified in each Multics 9-bit byte of the AQ. The AQ is now ORed with some doubleword of exploded\_key. Each bit of exploded\_key occupies the high order bit of a 9-bit byte; thus each bit to be used for transformation control now resides to the left of the corresponding byte of the source.

exploded key to use The doubleword of for transformation control is equal to the byte of the key addressed by interruption row. This is because each byte of the key uses a doubleword of exploded key, and because interruption row (in x2) always addresses the first byte of the key to use for interruption this CID cycle which is also the byte to use for transformation control. Since even the doubleword instructions address in word indexes, interruption row must be doubled. This is done by adding it in twice, once in the epplb instruction and once in the oraq instruction itself.

The AQ is stored and translated by the mvt instruction. The confusion\_table used here is identical to the one in the PL/I program, except that each 8-bit result byte is as usual left justified within a 9-bit byte.

These confused bytes are now interrupted by exclusive-oring with the eight bytes of the key addressed by

interruption\_row. Diffusion is obtained by exclusive-oring with the prerotated convolution registers stored in "normalized".

The interchange operation must, as well as swapping the source and convolution (now stored in "normalized"), unrotate the convolution registers to undo the effect of lining up the exclusive-or gates described above. This is done via a very similar loop to rotate\_loop. A subtract-delta modifier references through and\_masks\_ptr. Since this modifier subtracts delta before indirecting the masks will be used in the reverse order. The shift counts needed are shown below; the add-delta word for shifting again supplies loop control.

Table 3: Convolution Register Rotation Counts

| Row | Previous | Rotation | Post-Rotation |

|-----|----------|----------|---------------|

| 5   |          | 0        | 72            |

| 3   |          | 9        | 63            |

| 2   |          | 18       | 54            |

| 6   |          | 27       | 45            |

| 7   |          | 36       | 36            |

| 4   |          | 45       | 27            |

| 1   |          | 53       | 18            |

| 0   |          | 63       | 9             |

The register accesses and rotate counts for the prerotating should be read down; for postrotation the table should be read up.

page 52

After sixteen CID-interchange pairs, one more interchange has been done than desired. This is undone by swapping the two registers. The bytes are now packed into the result field.

Some possibilities still exist for speeding up this program. The two loops controlled by tally words only loop eight times; they could be exploded into eight copies. Since the address of and masks and the rotate counts would in each copy be known at compile time no indirect words would be needed. In addition the loop control instruction ttf would be eliminated. Counting ttf as two memory accesses and each of the tally references as one, four memory accesses could be saved each rotation. Since eight are required in the loop, and there are two loops, 64 memory accesses would be saved. Eight more would be saved by eliminating the tally word setup instructions at the beginning of each loop, for a total of 72. Since there are sixteen CID cycles a total of 72 times 16 = 1152 memory cycles might be saved. This may total as much as a millisecond, thus saving about twenty percent of the cipher time for a given block. This demonstrates how sensitive a program's performance can be to minor changes in coding style. Other experiments are suggested, such as completely rewriting the program with all arrays transposed (so that the bits of a byte are not stored sequentially), or eliminating the padding bit on each byte.

#### page 53